RAMTRON FM3135-G, FM3135 Datasheet

Preliminary

NCN

N

NCN

FM3135

Integrated RTC/Alarm/F-RAM & Embedded Crystal

Features

High Integration Device Replaces Multiple Parts

• Serial Nonvolatile Memory

• Real-time Clock (RTC) with Alarm

• Clock Output (Programmable frequency)

64Kb Ferroelectric Nonvolatile RAM

• Internally Organized as 8Kx8

• Unlimited Read/Write Endurance

• 10 year Data Retention

• NoDelay™ Writes

Fast Two-wire Serial Interface

• Up to 1 MHz Maximum Bus Frequency

• Supports Legacy Timing for 100 kHz & 400 kHz

• RTC & F-RAM Controlled via 2-wire Interface

Description

The FM3135 integrates a real-time clock (RTC) and

F-RAM nonvolatile memory. The 32.768kHz crystal

is embedded inside the package. The device operates

from 2.7 to 3.6V.

The FM3135 provides nonvolatile F-RAM which

features fast write speed and unlimited endurance.

This allows the memory to serve as extra RAM for

the system microcontroller or conventional

nonvolatile storage. This memory is truly nonvolatile

rather than battery backed.

The real-time clock (RTC) provides time and date

information in BCD format. It can be permanently

powered from external backup voltage source, either

a battery or a capacitor. The timekeeper uses a crystal

integral to the package and provides a calibration

mode that allows software adjustment of timekeeping

accuracy.

Real-time Clock/Calendar

• Embedded 32.768 kHz Crystal

• Backup Current under 1 µA

• Seconds through Centuries in BCD format

• Tracks Leap Years through 2099

• Software Calibration

• Supports Battery or Capacitor Backup

Easy to Use Configurations

• Operates from 2.7 to 3.6V

• 20-pin “Green”/RoHS SOIC (-G)

• Low Operating Current

• Industrial Temperature -40°C to +85°C

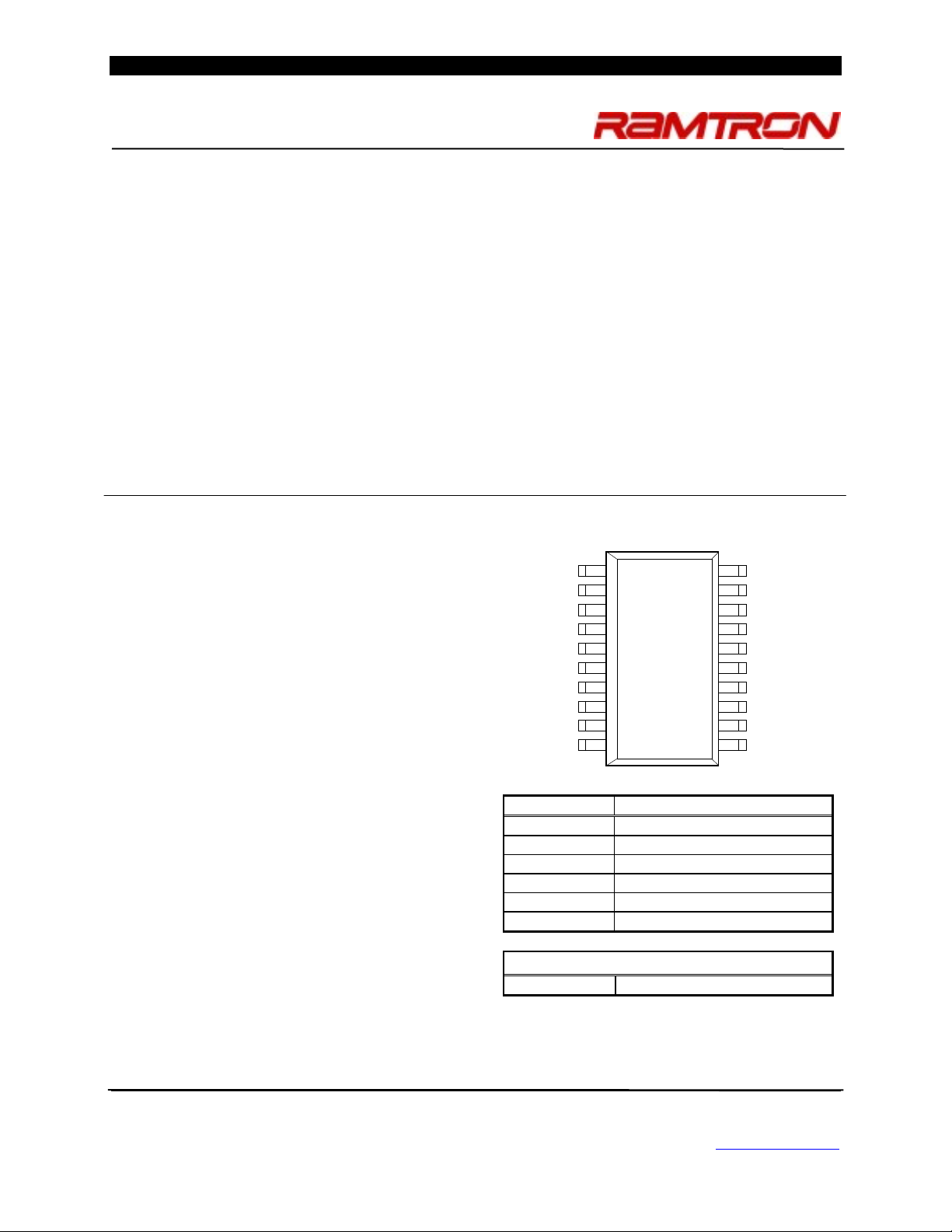

Pin Configuration

NC

NC

ACS

VDD

NC

NC

NC

NC

NC

NC

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

VSS

SCL

SDA

VBAK

VSS

C

C

C

Pin Name Function

ACS Alarm/Calibration/SqWave

SDA Serial Data

SCL Serial Clock

VBAK Battery-Backup Supply

VDD Supply Voltage

VSS Ground

Ordering Information

FM3135-G “Green”/RoHS 20-pin SOIC

This is a product that has fixed target specifications but are subject Ramtron International Corporation

to change pending characterization results. 1850 Ramtron Drive, Colorado Springs, CO 80921

(800) 545-FRAM, (719) 481-7000

http://www.ramtron.com

Rev. 1.1

Feb. 2008 Page 1 of 21

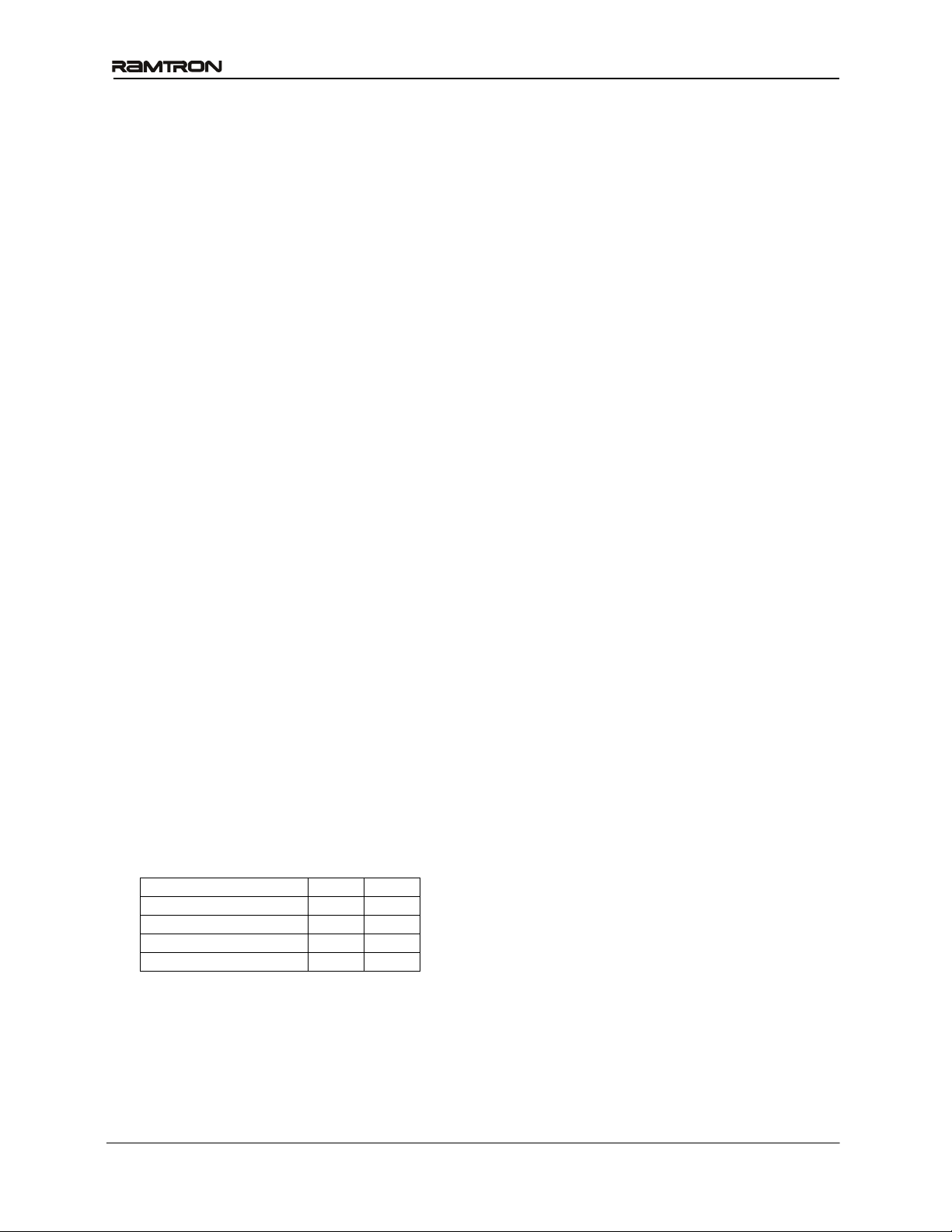

FM3135 Integrated RTC/Alarm/FRAM & Embedded Crystal

r

F-RAM

Array

SCL

SDA

2-Wire

Interface

LockOut

VDD

VBAK

Special

Function

Registers

RTC Cal.

VSW

-

+

Switched Powe

Nonvolatile

Battery Backed

RTC Registers

RTC

Alarm

Alarm

512Hz/SQW

ACS

Figure 1. Block Diagram

Pin Descriptions

Pin Name Type Pin Description

ACS Output Alarm/Calibration/SquareWave: This is an open-drain output that requires an external

pullup resistor. The alarm, calibration, and square wave functions all share this output.

In Alarm mode, this pin acts as the active-low alarm output. In Calibration mode, a 512

Hz square-wave is driven out. In SquareWave mode, the user may select a frequency of

1, 512, 4096, or 32768 Hz to be used as a continuous output. Refer to Table 3. Control

Bit Settings for ACS Pin to determine the bit settings for each mode.

SDA I/O Serial Data & Address: This is a bi-directional line for the two-wire interface. It is

open-drain and is intended to be wire-OR’d with other devices on the two-wire bus. The

input buffer incorporates a Schmitt trigger for noise immunity and the output driver

includes slope control for falling edges. A pull-up resistor is required.

SCL Input Serial Clock: The serial clock line for the two-wire interface. Data is clocked out of the

part on the falling edge, and data into the device on the rising edge. The SCL input also

incorporates a Schmitt trigger input for noise immunity.

VBAK Supply Backup supply voltage: A 3V battery or a large value capacitor. If no backup supply is

used, this pin should be tied to V

.

SS

VDD Supply Supply Voltage.

VSS Supply Ground

Rev. 1.1

Feb. 2008 Page 2 of 21

FM3135 Integrated RTC/Alarm/FRAM & Embedded Crystal

Overview

The FM3135 device combines a serial nonvolatile

RAM with a real-time clock (RTC) and alarm. These

complementary but distinct functions share a

common interface in a single package. Although

monolithic, the product is organized as two logical

devices, the F-RAM memory and the RTC/alarm.

From the system perspective, they appear to be two

separate devices with unique IDs on the serial bus.

The memory is organized as a stand-alone 2-wire

nonvolatile memory with a standard device ID value.

The real-time clock and alarm are accessed with a

separate 2-wire device ID. This allows clock/calendar

data to be read while maintaining the most recently

used memory address. The clock and alarm are

controlled by 15 special function registers. The

registers are maintained by the power source on the

VBAK pin, allowing them to operate from battery or

backup capacitor power when V

threshold. Each functional block is described below.

drops below a set

DD

Real-Time Clock Operation

The real-time clock (RTC) is a timekeeping device

that can be battery or capacitor backed for

permanently-powered operation. It offers a software

calibration feature that allows high accuracy.

The RTC consists of an oscillator, clock divider, and

a register system for user access. It divides down the

32.768 kHz time-base and provides a minimum

resolution of seconds (1Hz). Static registers provide

the user with read/write access to the time values. It

includes registers for seconds, minutes, hours, dayof-the-week, date, months, and years. A block

diagram (Figure 2) illustrates the RTC function.

The user registers are synchronized with the

timekeeper core using R and W bits in register 00h

described below. Changing the R bit from 0 to 1

transfers timekeeping information from the core into

holding registers that can be read by the user. If a

timekeeper update is pending when R is set, then the

core will be updated prior to loading the user

Memory Operation

The FM3135 integrates a 64Kb F-RAM. The

memory is organized in bytes, 8192 addresses of 8

bits each. The memory is based on F-RAM

technology. Therefore it can be treated as RAM and

is read or written at the speed of the two-wire bus

with no delays for write operations. It also offers

effectively unlimited write endurance unlike other

nonvolatile memory technologies. The two-wire

interface protocol is described further on page 12.

The memory array can be write-protected by

software. Two bits (WP0, WP1) in register 0Eh

control the protection setting as shown in the

following table. Based on the setting, the protected

addresses cannot be written and the 2-wire interface

will not acknowledge any data to protected addresses.

The special function registers containing these bits

are described in detail below.

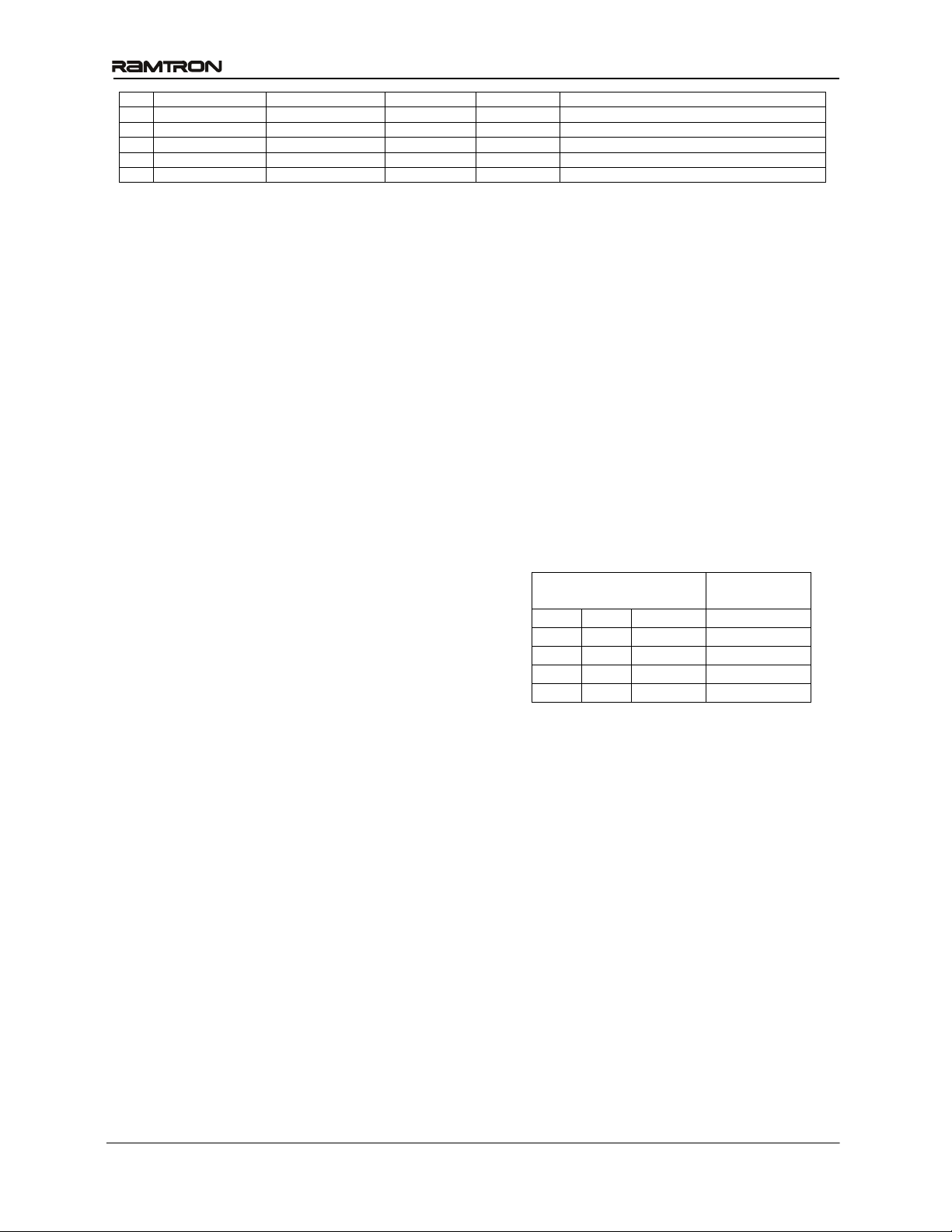

Table 1. F-RAM Write-Protect

Write-Protect Range WP1 WP0

None 0 0

Bottom 1/4 0 1

Bottom 1/2 1 0

Full array 1 1

The WP bits are battery-backed. On a powerup

without a backup source, the WP bits are cleared to a

‘0’ state.

registers. The registers are frozen and will not be

updated again until the R bit is cleared to ‘0’. R is

used to read the time.

Setting the W bit to ‘1’ locks the user registers.

Clearing it to a ‘0’ causes the values in the user

registers to be loaded into the timekeeper core. W is

used for writing new time values. Users should be

certain not to load invalid values, such as FFh, to the

timekeeping registers. Updates to the timekeeping

core occur continuously except when locked. All

timekeeping registers must be initialized at the first

powerup or when the LB bit is set. See the

description of the LB bit on page 11.

Backup Power

The real-time clock/calendar is intended to be

permanently powered. When the primary system

power fails, the voltage on the V

When V

is less than VSW, the RTC will switch to

DD

the backup power supply on V

pin will drop.

DD

. The clock

BAK

operates at extremely low current in order to

maximize battery or capacitor life. However, an

advantage of combining a clock function with FRAM memory is that data is not lost regardless of the

backup power source.

If a battery is applied without a V

the device has been designed to ensure the I

power supply,

DD

BAK

current does not exceed the 1µA maximum limit.

Trickle Charger

To facilitate capacitor backup the V

pin can

BAK

optionally provide a trickle charge current. When the

Rev. 1.1

Feb. 2008 Page 3 of 21

FM3135 Integrated RTC/Alarm/FRAM & Embedded Crystal

r

VBC bit (register 0Eh, bit 2) is set to a ‘1’, the V

pin will source approximately 80 µA until V

reaches V

. This charges the capacitor to VDD

DD

without an external diode and resistor charger.

There is a Fast Charge mode which is enabled by the

FC bit (register 0Eh, bit 1). In this mode the trickle

charger current is set to approximately 1 mA,

allowing a large backup capacitor to charge more

quickly.

BAK

BAK

• In the case where no battery is used, the V

pin should be tied to V

.

SS

BAK

!

! Note: systems using lithium batteries should clear

!!

the VBC bit to 0 to prevent battery charging. The

V

circuitry includes an internal 1 KΩ series

BAK

resistor as a safety element.

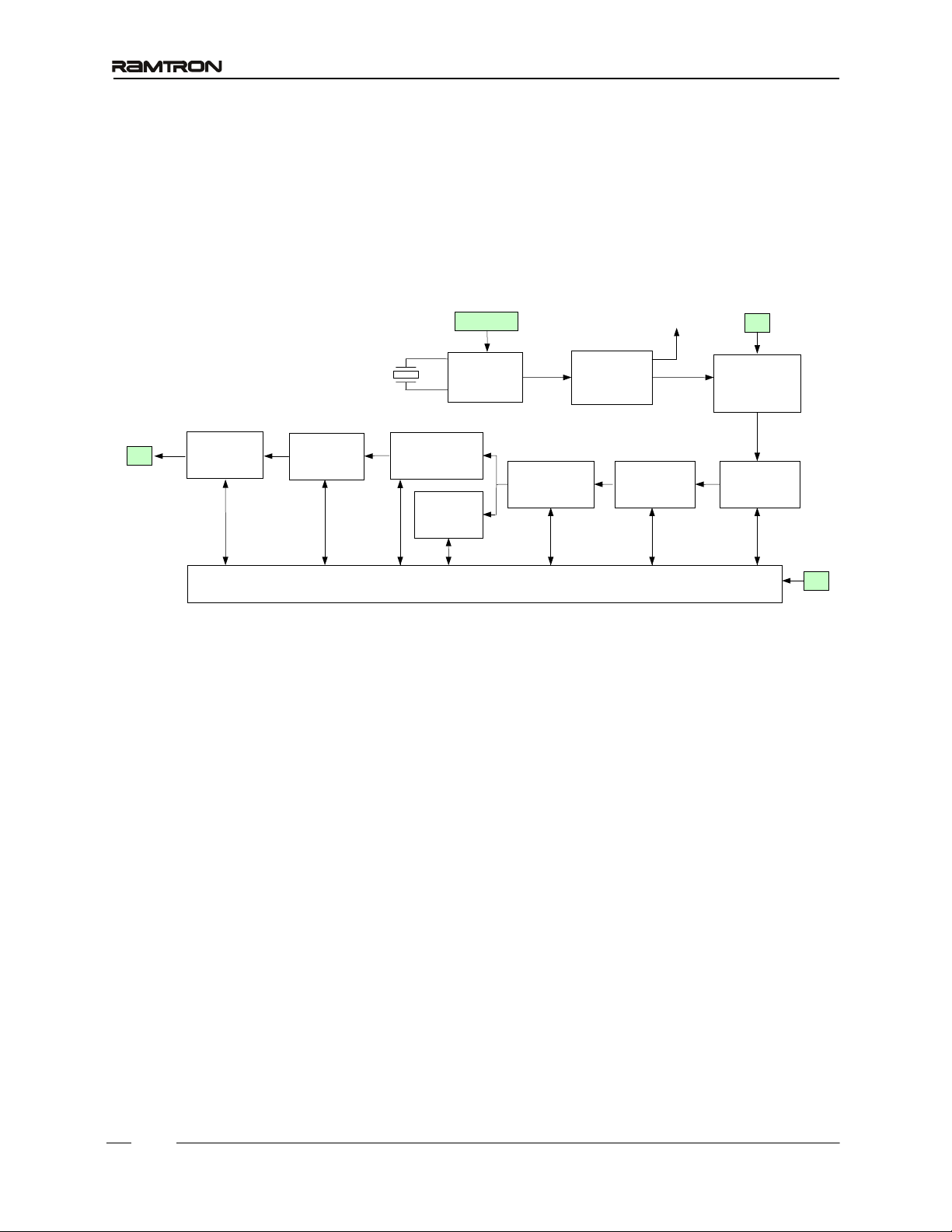

512 Hz or

SW out

/OSCEN

W

32.768 kHz

crystal

CF

Months

5 bits

Years

8 bits

Date

6 bits

Days

3 bits

User Interface Registers

Figure 2. Real-Time Clock Core Block Diagram

Calibration

When the CAL bit in register 00h is set to ‘1’, the

clock enters calibration mode. In calibration mode,

the ACS output pin is dedicated to the calibration

function and the power fail output is temporarily

unavailable. Calibration operates by applying a

digital correction to the counter based on the

frequency error. In this mode, the ACS pin is driven

with a 512 Hz (nominal) square wave. Any measured

deviation from 512 Hz translates into a timekeeping

error. The user converts the measured error in ppm

and writes the appropriate correction value to the

calibration register. The correction factors are listed

in the table below. Positive ppm errors require a

negative adjustment that removes pulses. Negative

ppm errors require a positive correction that adds

pulses. Positive ppm adjustments have the CALS

(sign) bit set to ‘1’, whereas negative ppm

adjustments have CALS = 0. After calibration, the

Oscillato

Hours

6 bits

Clock

Divider

Minutes

7 bits

1 Hz

Update

Logic

Seconds

7 bits

R

clock will have a maximum error of

±

0.09 minutes per month at the calibrated

±

2.17 ppm or

temperature.

The calibration setting is battery-backed and must be

reloaded should the backup source fail. It is accessed

with bits CAL.4-0 in register 01h. This value only

can be written when the CAL bit is set to a ‘1’. To

exit the calibration mode, the user must clear the

CAL bit to a ‘0’. When the CAL bit is ‘0’, the ACS

pin will revert to another function as defined in

Table 3. Control Bit Settings for ACS Pin.

Rev. 1.1

Feb. 2008 Page 4 of 21

FM3135 Integrated RTC/Alarm/FRAM & Embedded Crystal

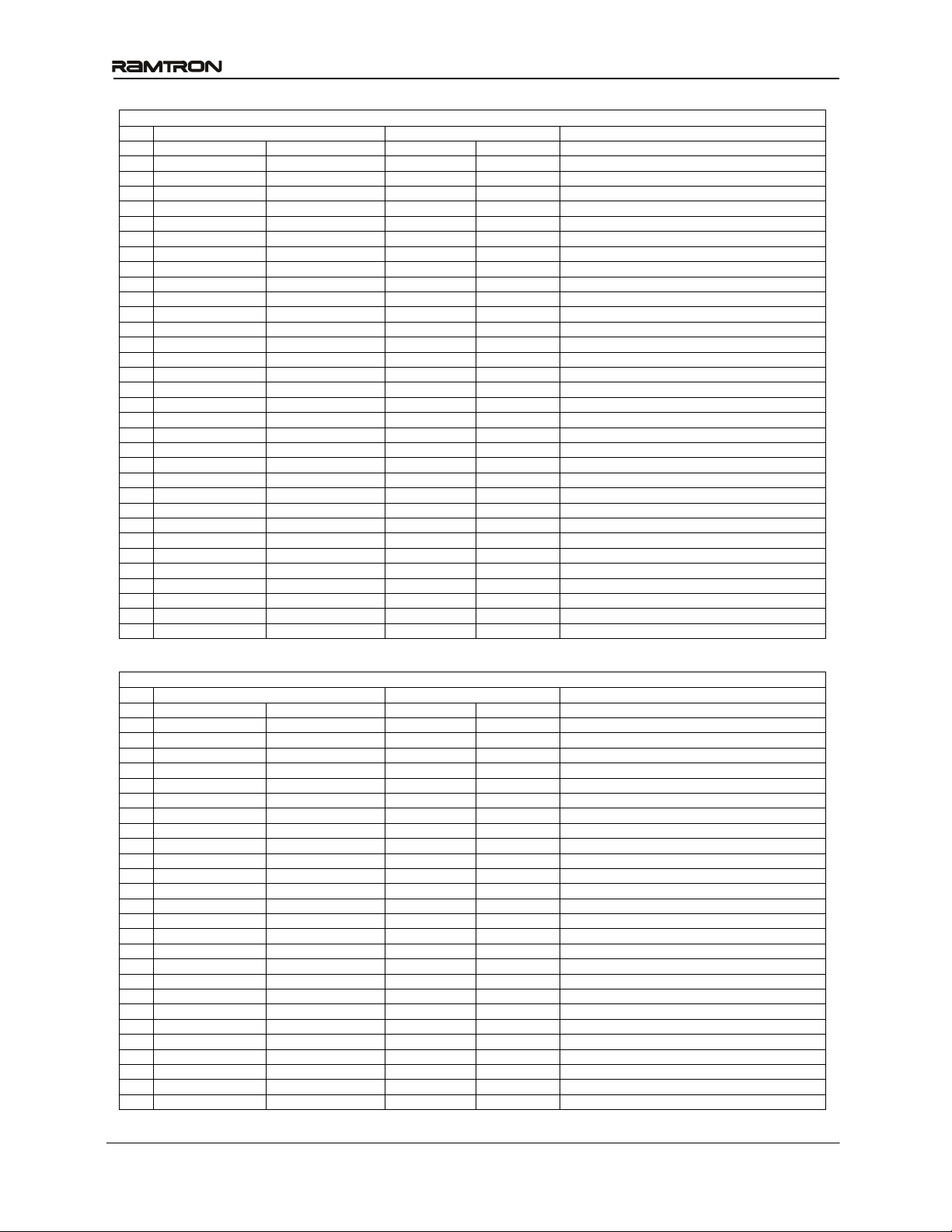

Table 2. Calibration Adjustments

Measured Frequency Range Error Range (PPM)

Min Max Min Max Program Calibration Register to:

0 512.0000 511.9989 0 2.17 000000

1 511.9989 511.9967 2.18 6.51 100001

2 511.9967 511.9944 6.52 10.85 100010

3 511.9944 511.9922 10.86 15.19 100011

4 511.9922 511.9900 15.20 19.53 100100

5 511.9900 511.9878 19.54 23.87 100101

6 511.9878 511.9856 23.88 28.21 100110

7 511.9856 511.9833 28.22 32.55 100111

8 511.9833 511.9811 32.56 36.89 101000

9 511.9811 511.9789 36.90 41.23 101001

10 511.9789 511.9767 41.24 45.57 101010

11 511.9767 511.9744 45.58 49.91 101011

12 511.9744 511.9722 49.92 54.25 101100

13 511.9722 511.9700 54.26 58.59 101101

14 511.9700 511.9678 58.60 62.93 101110

15 511.9678 511.9656 62.94 67.27 101111

16 511.9656 511.9633 67.28 71.61 110000

17 511.9633 511.9611 71.62 75.95 110001

18 511.9611 511.9589 75.96 80.29 110010

19 511.9589 511.9567 80.30 84.63 110011

20 511.9567 511.9544 84.64 88.97 110100

21 511.9544 511.9522 88.98 93.31 110101

22 511.9522 511.9500 93.32 97.65 110110

23 511.9500 511.9478 97.66 101.99 110111

24 511.9478 511.9456 102.00 106.33 111000

25 511.9456 511.9433 106.34 110.67 111001

26 511.9433 511.9411 110.68 115.01 111010

27 511.9411 511.9389 115.02 119.35 111011

28 511.9389 511.9367 119.36 123.69 111100

29 511.9367 511.9344 123.70 128.03 111101

30 511.9344 511.9322 128.04 132.37 111110

31 511.9322 511.9300 132.38 136.71 111111

Positive Calibration for slow clocks: Calibration will achieve ± 2.17 PPM after calibration

Measured Frequency Range Error Range (PPM)

Min Max Min Max Program Calibration Register to:

0 512.0000 512.0011 0 2.17 000000

1 512.0011 512.0033 2.18 6.51 000001

2 512.0033 512.0056 6.52 10.85 000010

3 512.0056 512.0078 10.86 15.19 000011

4 512.0078 512.0100 15.20 19.53 000100

5 512.0100 512.0122 19.54 23.87 000101

6 512.0122 512.0144 23.88 28.21 000110

7 512.0144 512.0167 28.22 32.55 000111

8 512.0167 512.0189 32.56 36.89 001000

9 512.0189 512.0211 36.90 41.23 001001

10 512.0211 512.0233 41.24 45.57 001010

11 512.0233 512.0256 45.58 49.91 001011

12 512.0256 512.0278 49.92 54.25 001100

13 512.0278 512.0300 54.26 58.59 001101

14 512.0300 512.0322 58.60 62.93 001110

15 512.0322 512.0344 62.94 67.27 001111

16 512.0344 512.0367 67.28 71.61 010000

17 512.0367 512.0389 71.62 75.95 010001

18 512.0389 512.0411 75.96 80.29 010010

19 512.0411 512.0433 80.30 84.63 010011

20 512.0433 512.0456 84.64 88.97 010100

21 512.0456 512.0478 88.98 93.31 010101

22 512.0478 512.0500 93.32 97.65 010110

23 512.0500 512.0522 97.66 101.99 010111

24 512.0522 512.0544 102.00 106.33 011000

25 512.0544 512.0567 106.34 110.67 011001

Negative Calibration for fast clocks: Calibration will achieve ± 2.17 PPM after calibration

Rev. 1.1

Feb. 2008 Page 5 of 21

FM3135 Integrated RTC/Alarm/FRAM & Embedded Crystal

26 512.0567 512.0589 110.68 115.01 011010

27 512.0589 512.0611 115.02 119.35 011011

28 512.0611 512.0633 119.36 123.69 011100

29 512.0633 512.0656 123.70 128.03 011101

30 512.0656 512.0678 128.04 132.37 011110

31 512.0678 512.0700 132.38 136.71 011111

Alarm

The alarm function compares user-programmed

alarm values to the corresponding RTC time/date

values. When a match occurs, an alarm event occurs.

The alarm event sets an internal flag AF (register

00h, bit 6) and drives the ACS pin low, if the

appropriate control bits are set in registers 00h and

0Eh. See Table 3. The alarm condition on the ACS

pin and the AF bit are cleared by reading register

00h.

The alarm operates under V

DD

or V

power. If the

BAK

system controller is being used to detect an alarm

while the FM3135 is powered on V

pin may cause extra I

current when the alarm is

BAK

only, the ACS

BAK

activated. To avoid battery drain, the ACS pin can be

tri-stated by reading the AF flag, located in the

RTC/Alarm Control register 00h.

There are five alarm match fields. They are Month,

Date, Hours, Minutes, and Seconds. Each of these

fields also has a Match bit that is used to determine if

the field is used in the alarm match logic. Setting the

Match bit to ‘0’ indicates that the corresponding field

will be used in the match process.

Depending on the Match bits, the alarm can occur as

specifically as one particular second on one day of

the month, or as frequently as once per second

continuously. The MSB of each Alarm register is a

Match bit. Examples of the Match bit settings are

shown in Table 4. Alarm Match Bit Examples.

Selecting none of the match bits (all ‘1’s) indicates

that no match is required. The alarm occurs every

second. Setting the match select bit for seconds to ‘0’

causes the logic to match the seconds alarm value to

the current time of day. Since a match will occur for

only one value per minute, the alarm occurs once per

minute. Likewise setting the seconds and minutes

match select bits causes an exact match of these

values. Thus, an alarm will occur once per hour.

Setting seconds, minutes, and hours causes a match

once per day. See Table 4 for other alarm setting

examples.

Function of the ACS Pin

The ACS pin is a multifunction pin. The alarm,

calibration, and square wave functions all share this

output. There are two ways a user can detect an alarm

event, by reading the AF flag or by monitoring the

ACS pin. An interrupt pin on the host processor may

be used to detect an alarm event. The AF flag in the

register 00h (bit 6) will indicate that a time/date

match has occurred. When a match occurs, the AF

bit will be set to ‘1’ and the ACS pin will drive low.

The flag and ACS pin will remain in this state until

the RTC/Alarm Control register is read which clears

the AF bit.

Table 3 that shows the relationship between register

control settings and the function of the ACS pin.

Table 3. Control Bit Settings for ACS Pin

State of Register Bit Function of

ACS pin

CAL AEN AL/SW

0 1 1 /Alarm

0 X 0 Sq Wave out

1 X X 512 Hz out

0 0 1 Hi-Z

Rev. 1.1

Feb. 2008 Page 6 of 21

FM3135 Integrated RTC/Alarm/FRAM & Embedded Crystal

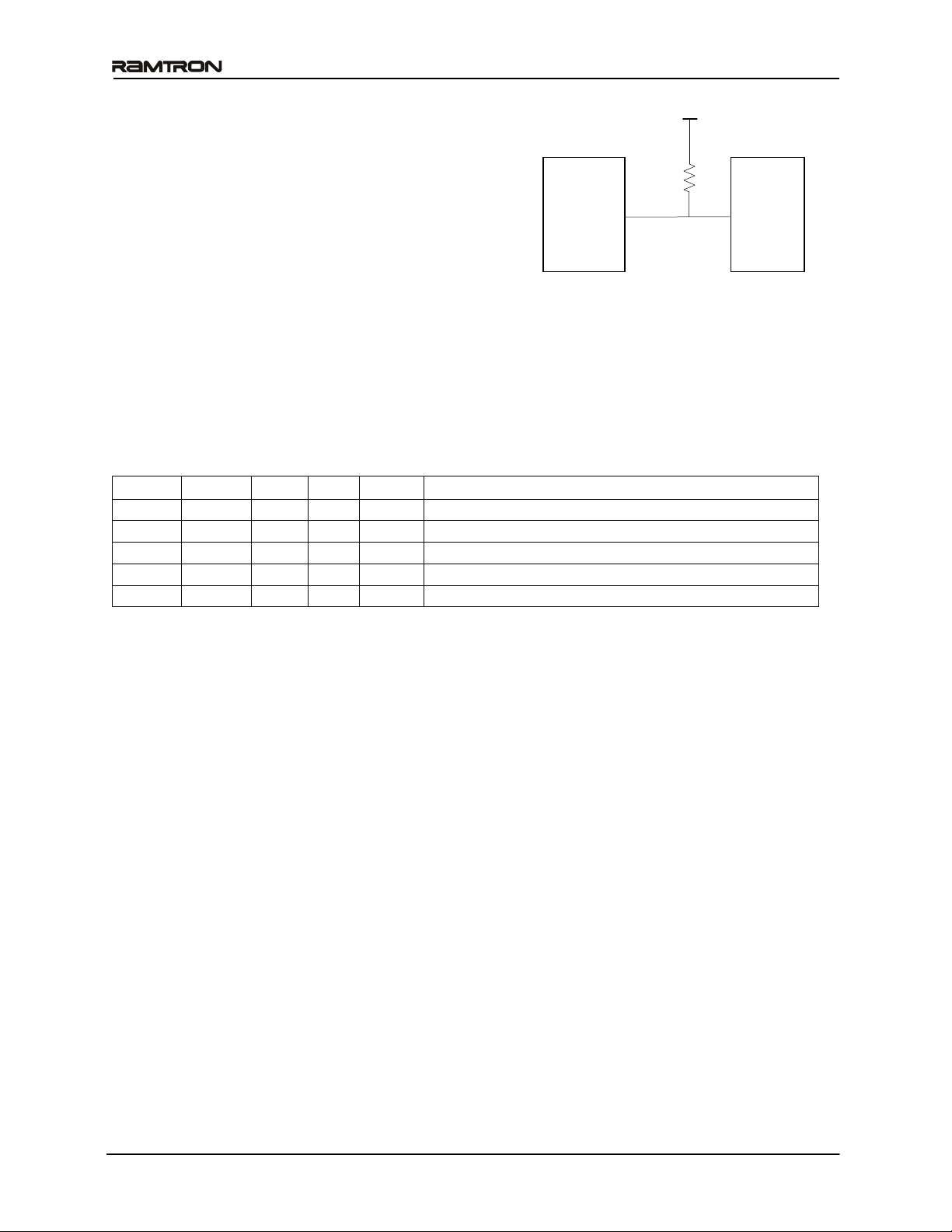

Cal Output/SquareWave Output

When the RTC calibration mode is invoked by

V

BAK

setting the CAL bit (register 00h, bit 2), the ACS

1M

output pin will be driven with a 512 Hz square wave

Ω

and the alarm will continue to operate. Since most

users only invoke the calibration mode during

production, this should have no impact on the

FM3135

ACS

otherwise normal operation of the alarm.

The ACS output may also be used to drive the system

with a continuous frequency. The AL/SW bit

(register 0Eh, bit 7) must be a ‘0’. A user-selectable

frequency is provided by F0 and F1 (register 0Eh,

bits 5 and 6). The frequencies are 1, 512, 4096, and

32768 Hz. If a continuous frequency output is

enabled by using the 512Hz or SquareWave out

functions, the alarm function will not be available.

The ACS pin is an open-drain output that needs to be

pulled up to a supply. The ACS pin and pullup

resistor draws current only when the alarm is

triggered.

Figure 4. ACS Pin Requires Pullup

Table 4. Alarm Match Bit Examples

Seconds Minutes Hours Date Months Alarm condition

1 1 1 1 1 No match required = alarm 1/second

0 1 1 1 1 Alarm when seconds match = alarm 1/minute

0 0 1 1 1 Alarm when seconds, minutes match = alarm 1/hour

0 0 0 1 1 Alarm when seconds, minutes, hours match = alarm 1/date

0 0 0 0 1 Alarm when seconds, minutes, hours, date match = alarm 1/month

MCU

Rev. 1.1

Feb. 2008 Page 7 of 21

Loading...

Loading...