Page 1

Page 2

TABLE OF CONTENTS

1 INTRODUCTION................................................................................................................... 5

2 TUNER....................................................................................................................................5

2.1 General description of DTT71307: ................................................................................. 5

2.2 Features of DTT71307:............................................................ ....................................... 5

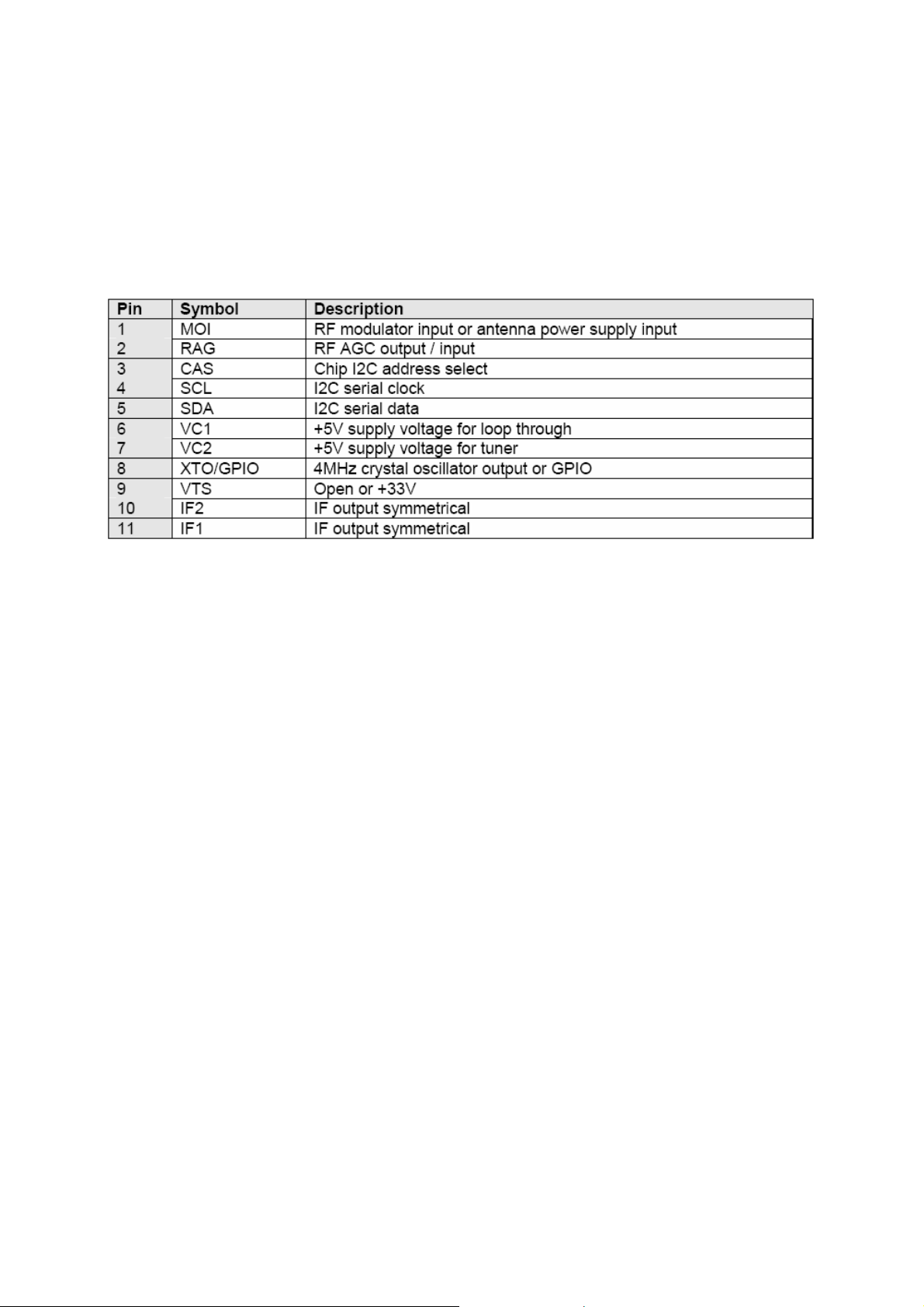

2.3 Pinning: ........................................................................................................................... 6

3 AUDIO AMPLIFIER STAGE WITH TDA8932................................................................... 6

3.1 General Description.........................................................................................................6

3.2 Features...........................................................................................................................6

3.3 Applications .................................................................................................................... 7

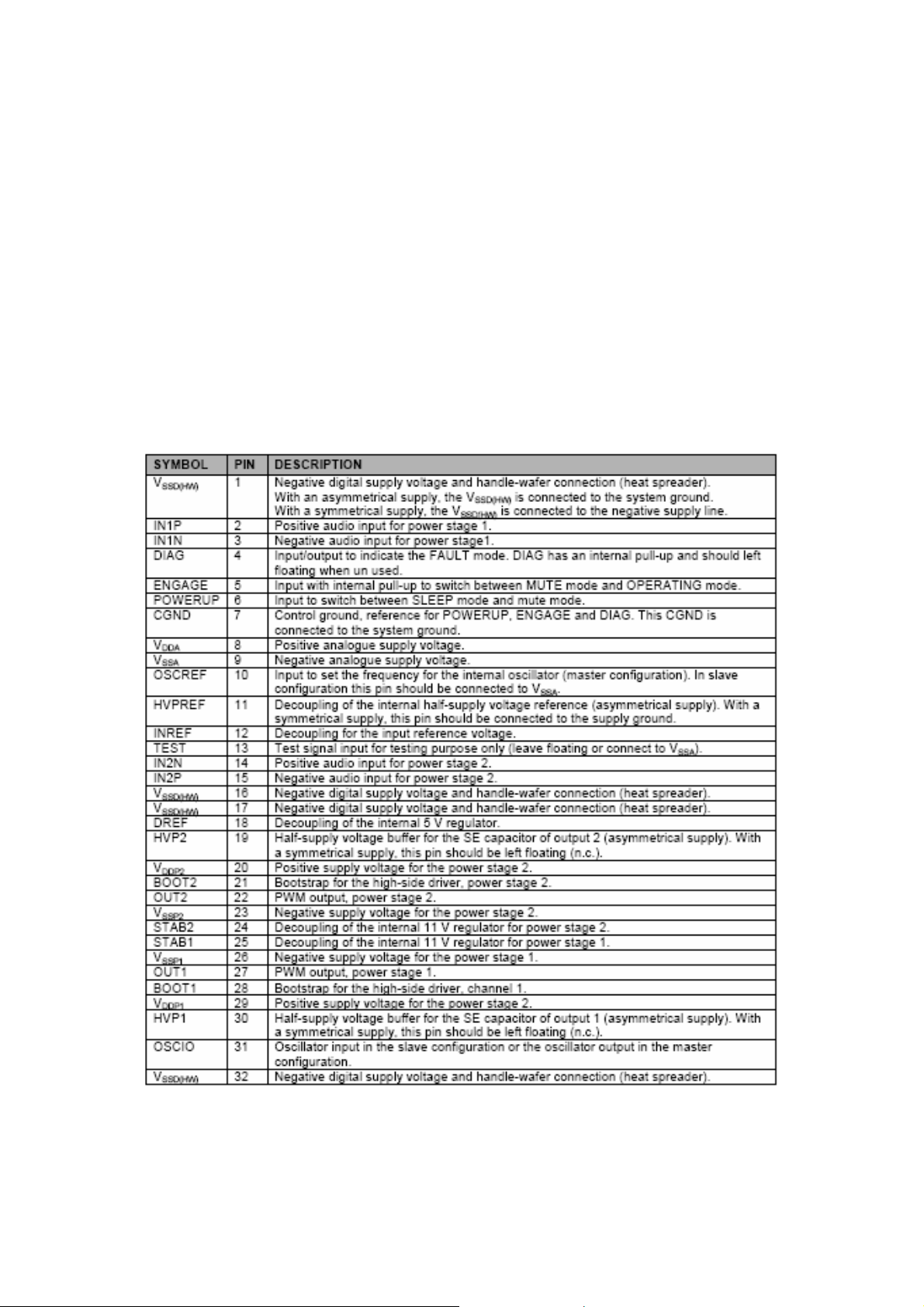

3.4 Pinning ............................................................................................................................7

4 POWER STAGE.....................................................................................................................7

5 MICROCONTROLLER (VCTP) ...........................................................................................8

5.1 General Features..............................................................................................................8

5.1.1 Controller:...............................................................................................................8

5.1.2 Audio:...................................................................................................................... 8

5.1.3 Video:...................................................................................................................... 8

5.2 Multistandard Sound Processor (MSP) Features .......................................................... ..9

5.3 Video Features............................................................................................................... 10

5.4 Controller Features........................................................................................................10

5.5 OSD & Teletext Features...................................... ... ................................ .....................11

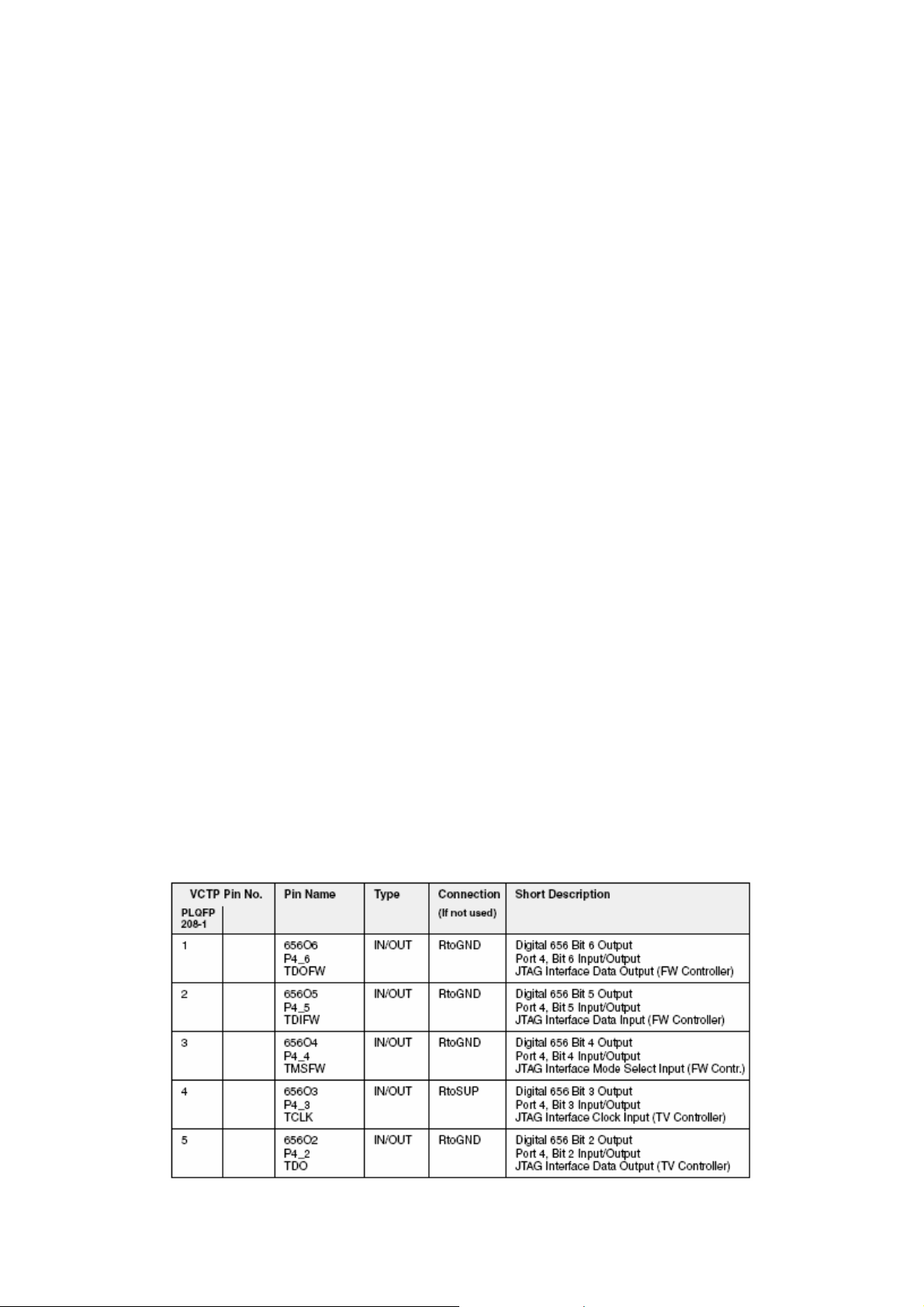

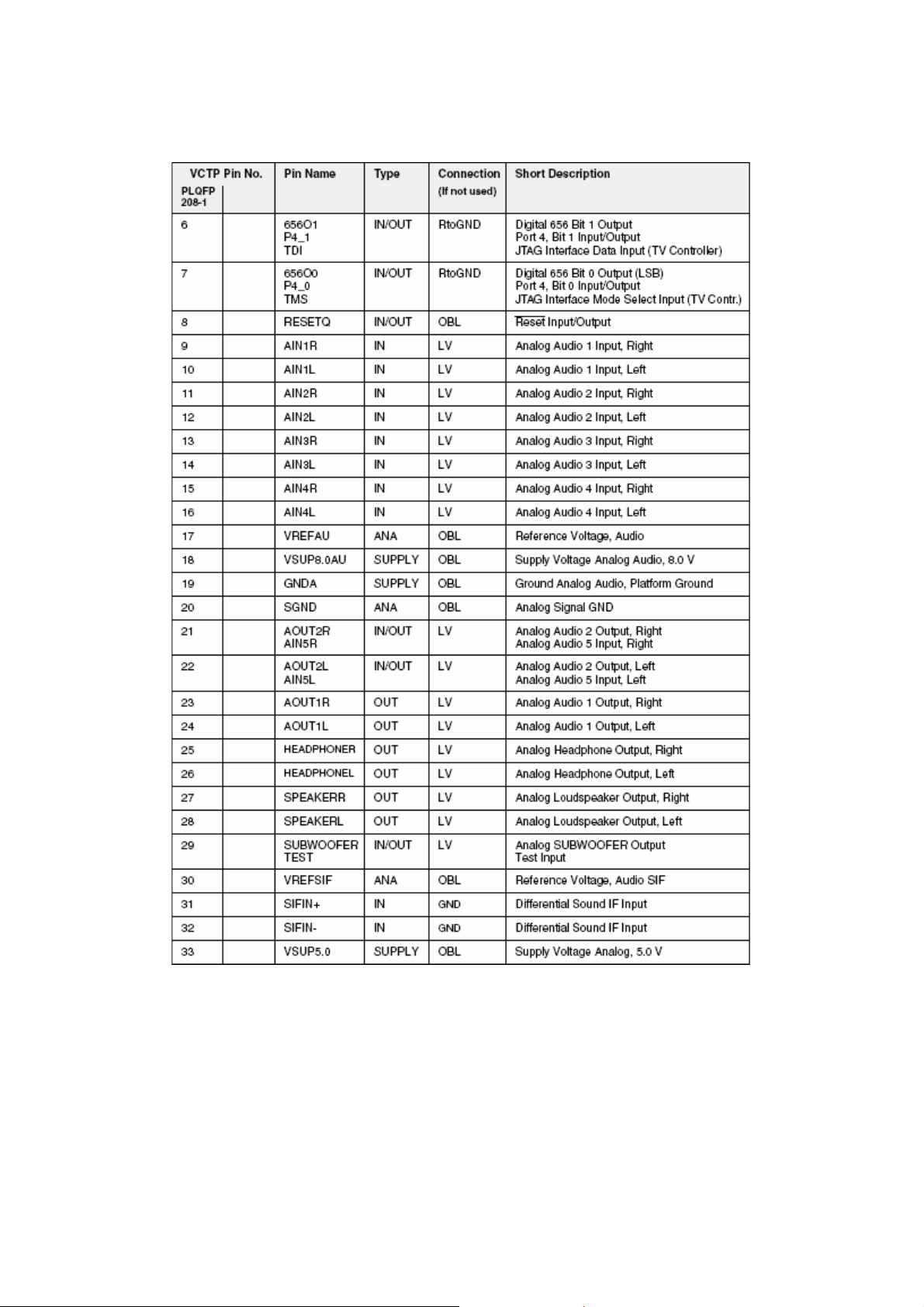

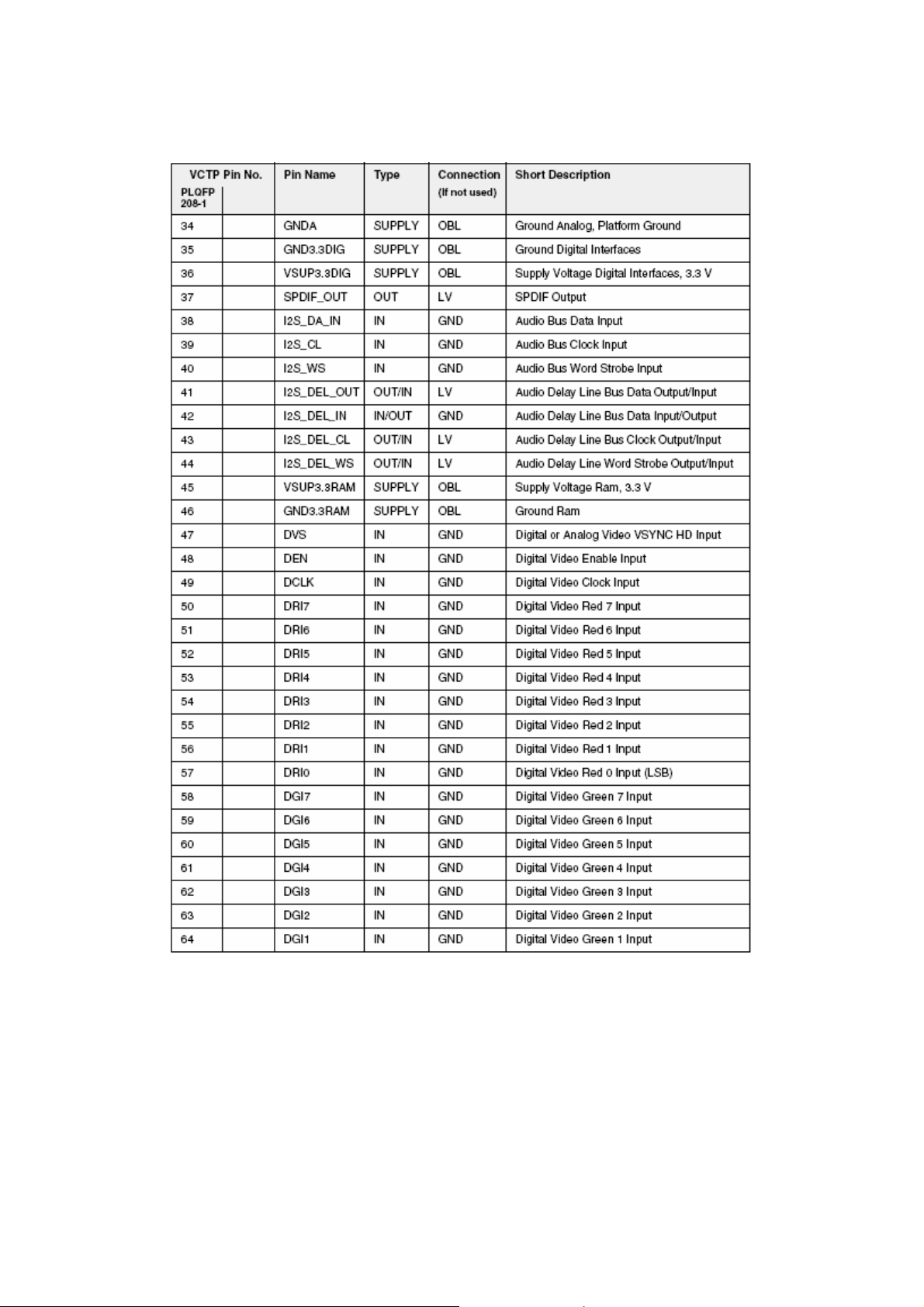

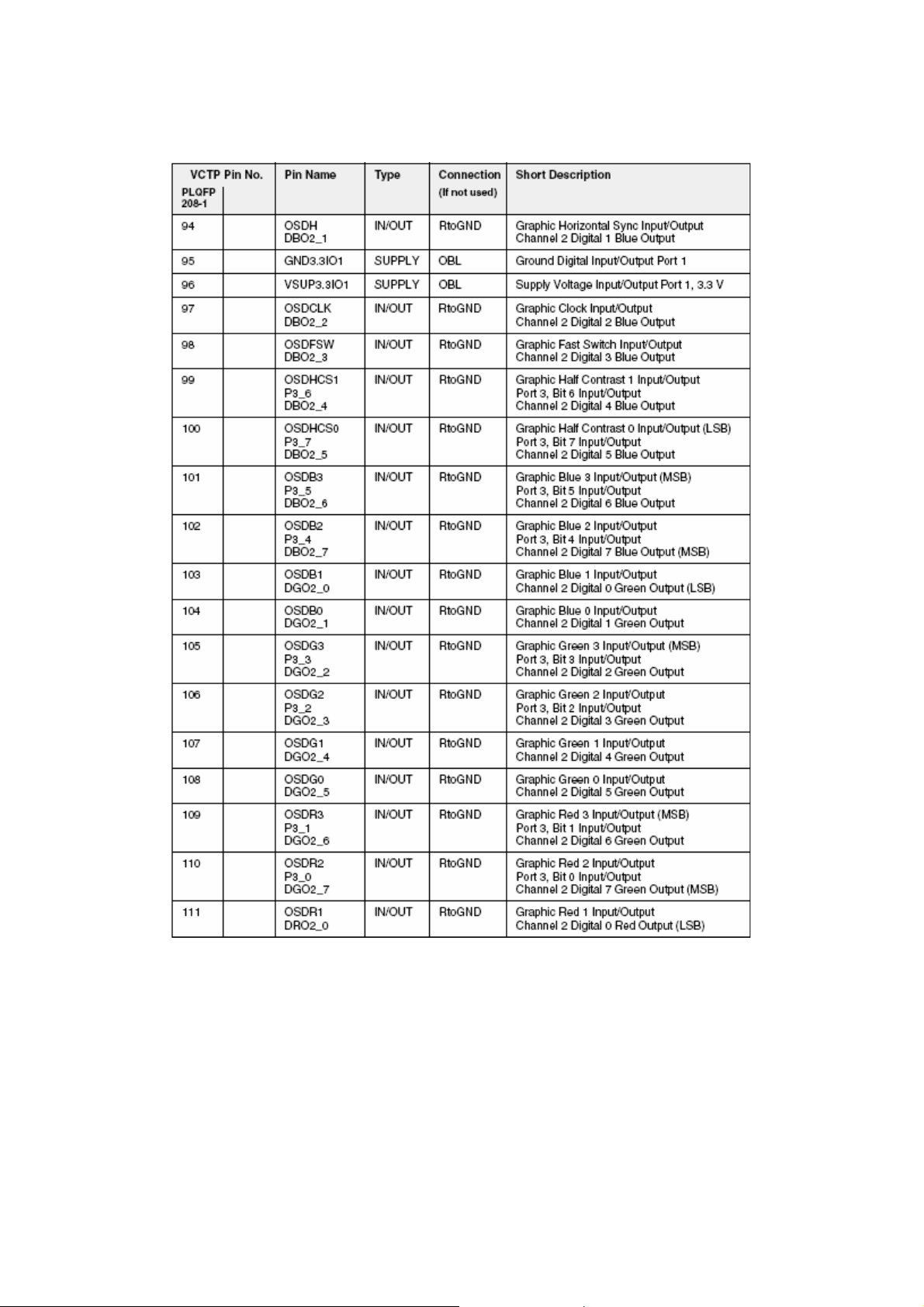

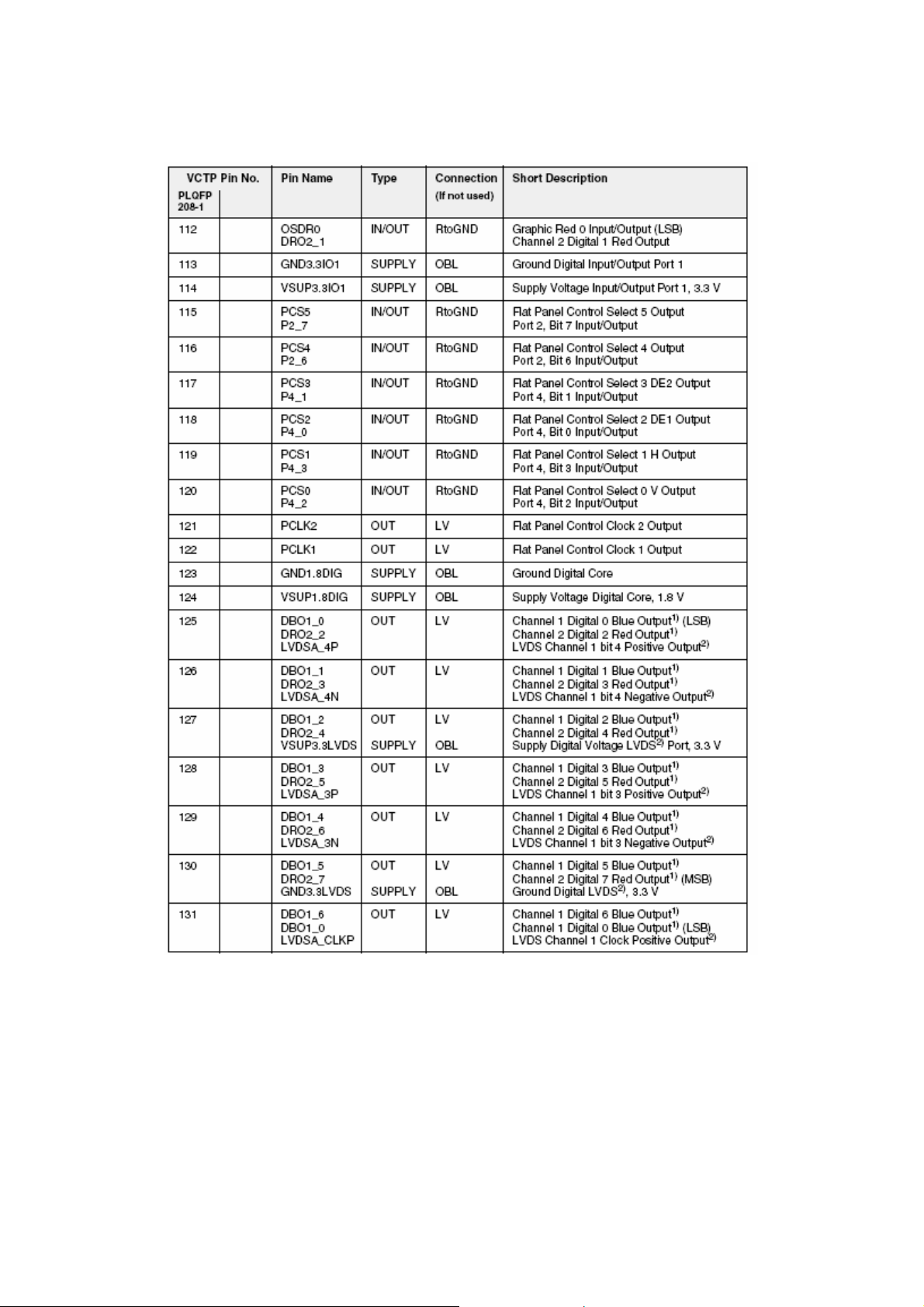

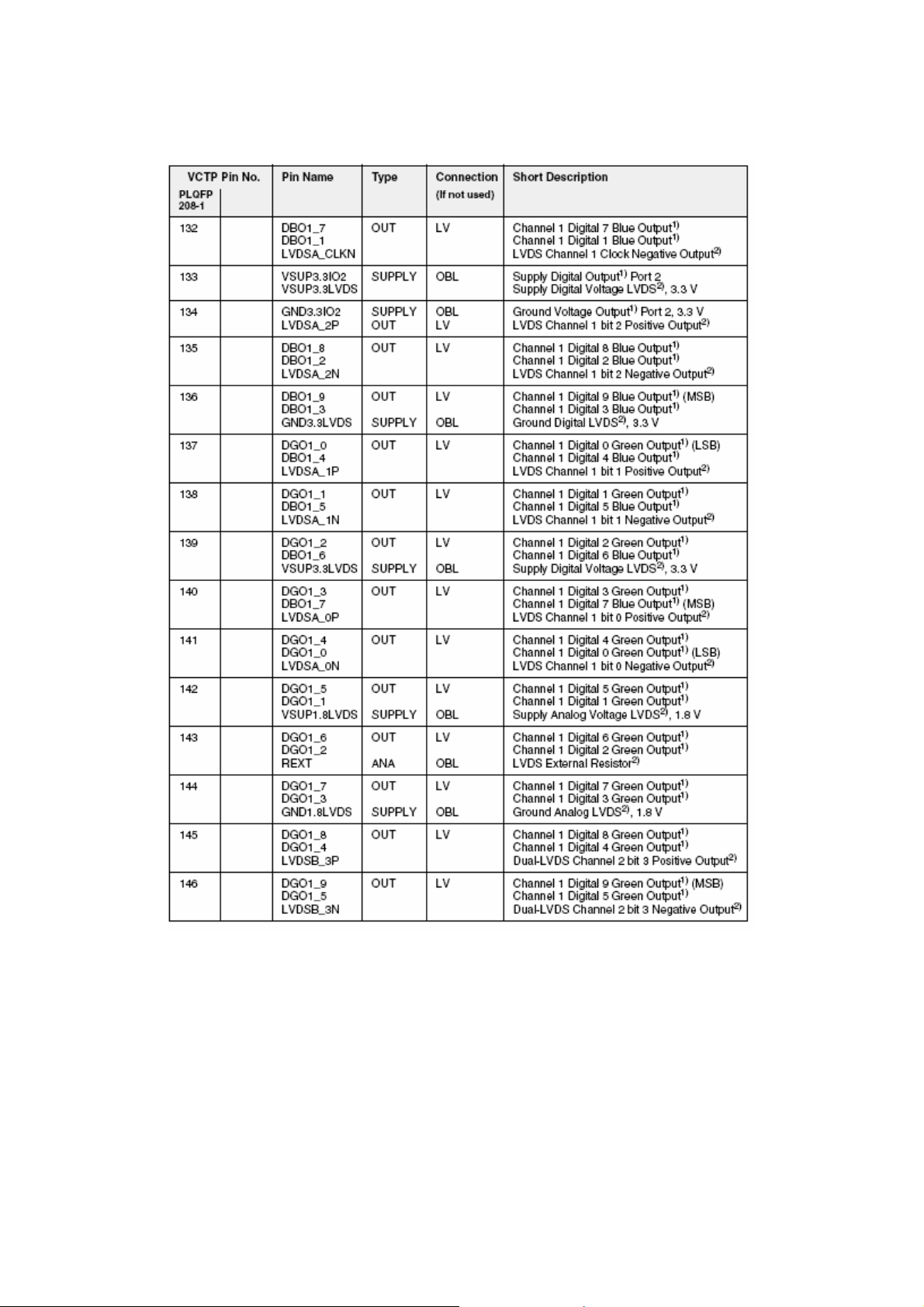

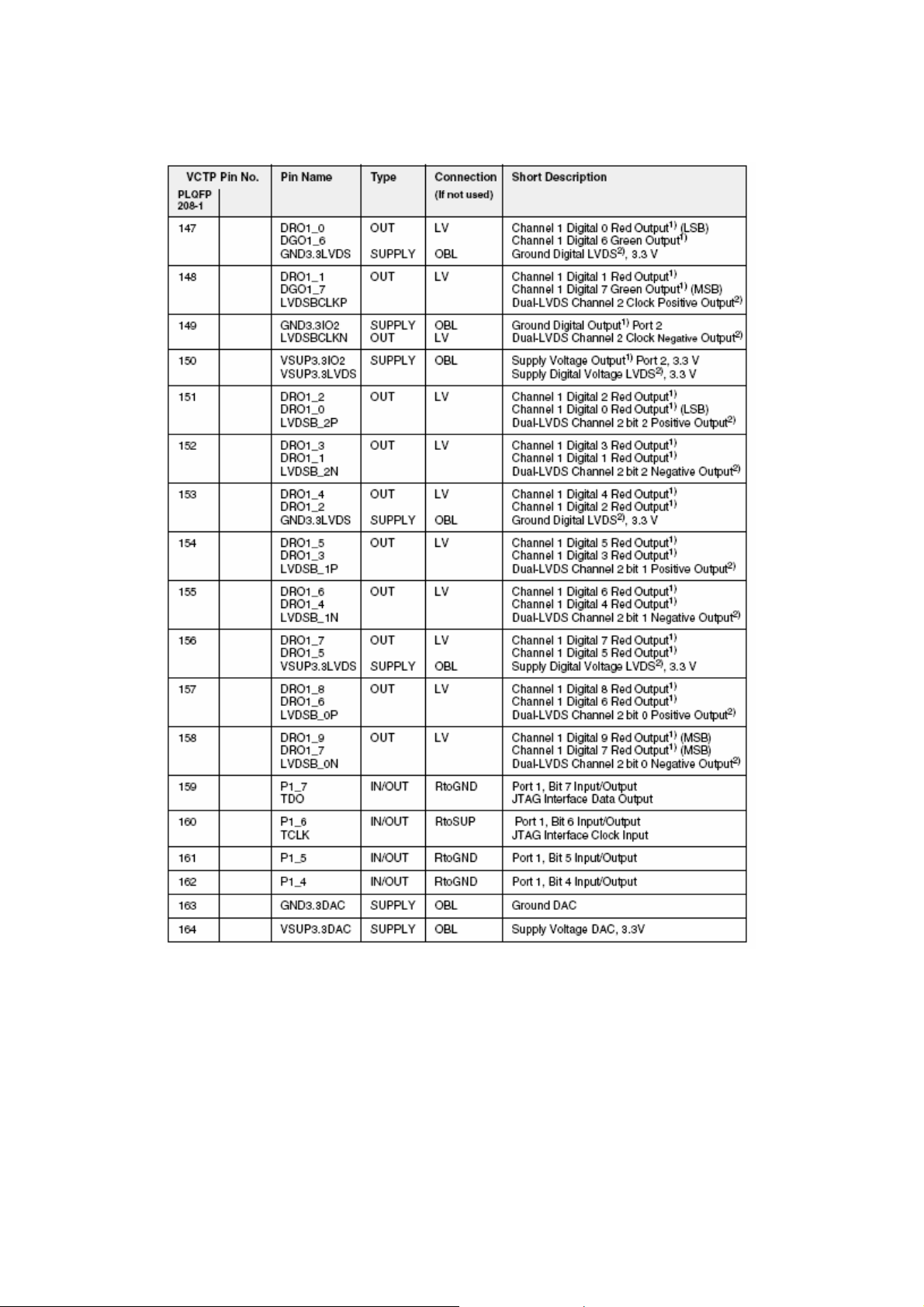

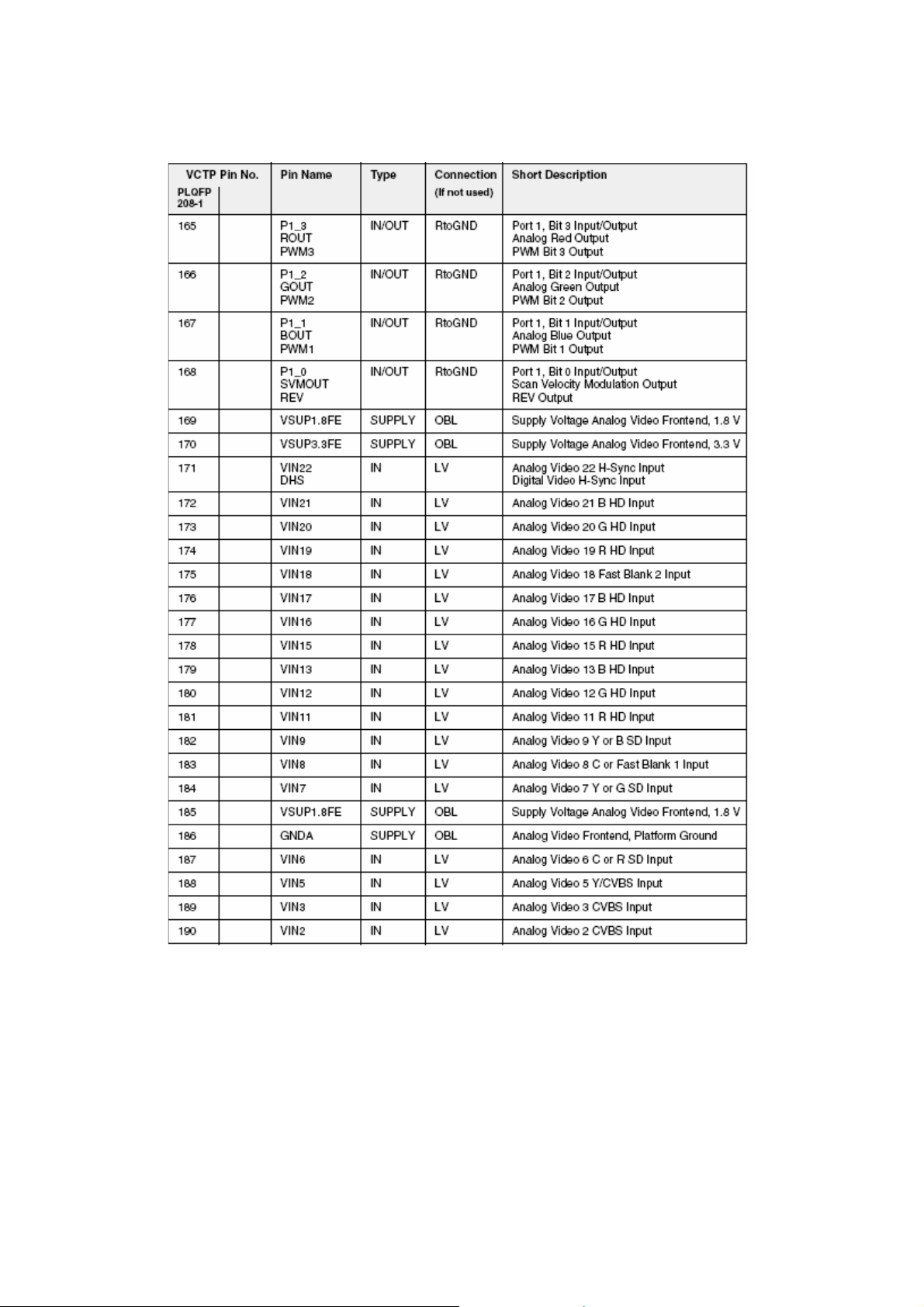

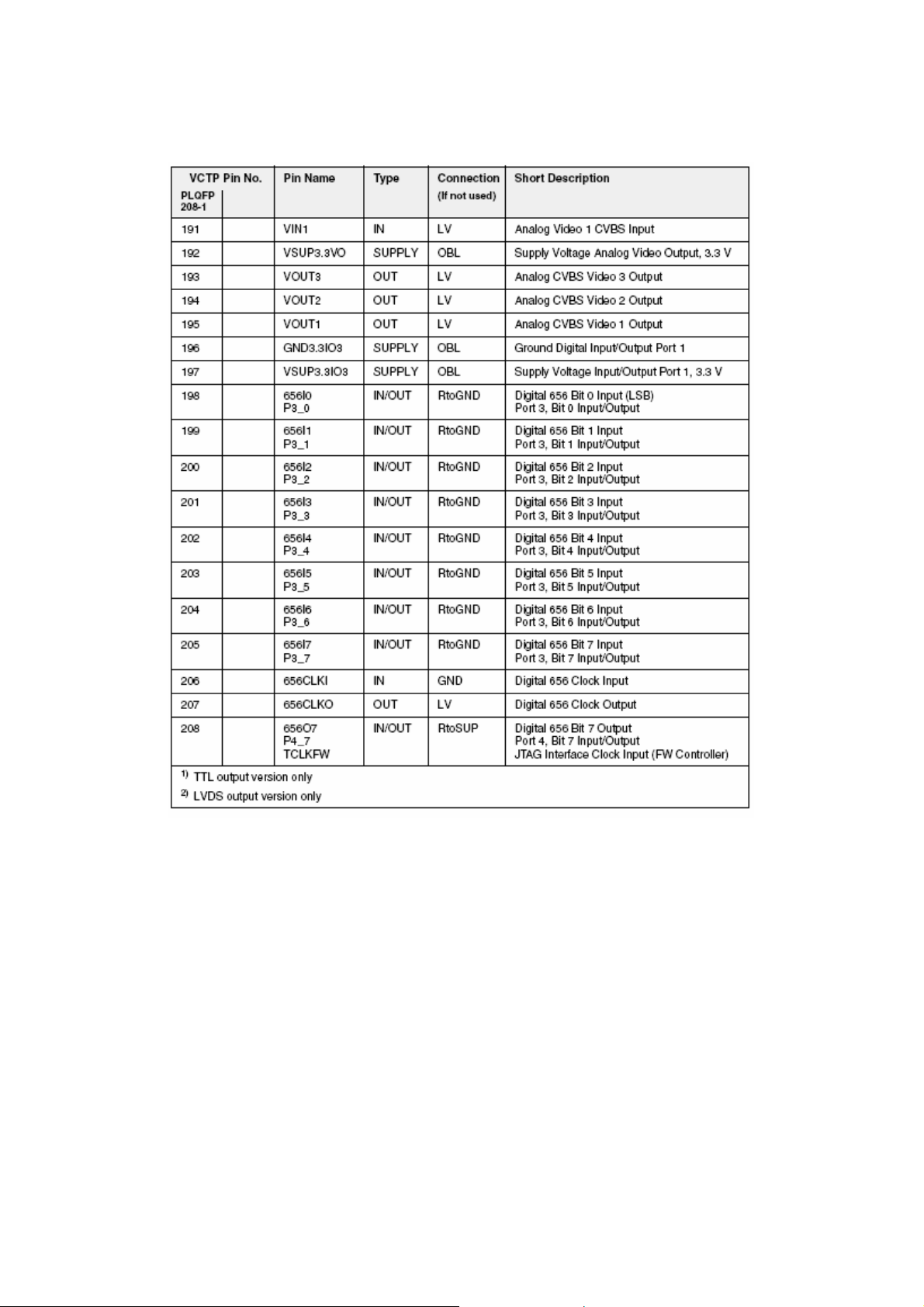

5.6 Port Allocation ..............................................................................................................11

6 DRX 3961A...........................................................................................................................20

6.1 General Desription ........................................................................................................20

6.2 Features.........................................................................................................................20

7 SERIAL 64K I2C EEPROM M24C64WBN6................................................. .....................21

7.1 General Description....................................................................................................... 21

7.2 Features.........................................................................................................................21

7.3 Absolute Maximum Ratings..........................................................................................22

7.4 Pinning ..........................................................................................................................22

8 CLASS AB STEREO HEADPHONE DRIVER TDA7050 .................................................22

8.1 General Description....................................................................................................... 22

8.2 Features.........................................................................................................................22

8.3 Pinning ..........................................................................................................................23

9 SAW FILTER X6966M........................................................................................................23

9.1 Features:........................................................................................................................23

9.2 Pin configuration:..........................................................................................................23

9.3 Frequency response:...................................................................................................... 23

10 MPEG DECODER µPD61115 ......................................................................................... 24

10.1 DESCRIPTION............................................................................................................. 24

10.2 FEATURES...................................................................................................................25

11 DRX 3973D.......................................................................................................................25

11.1 Introduction...................................................................................................................25

11.2 Features......................................................................................................................... 25

11.3 Applications ..................................................................................................................26

12 PI6CX100-27MHz 3.3V VCXO for Set-Top Box Applications ...................................... 26

12.1 Features......................................................................................................................... 26

12.2 Description.................................................................................................................... 26

13 74V1G08...........................................................................................................................27

14 FMS6145...........................................................................................................................27

15 IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM........................................ 28

Page 3

15.1 LM1117.........................................................................................................................28

15.1.1 General Description...............................................................................................28

15.1.2 Features.................................................................................................................29

15.1.3 Applications ..........................................................................................................29

15.1.4 Absolute Maximum Ratings.................................................................................. 29

15.1.5 Pinning ..................................................................................................................29

15.2 LM1086.........................................................................................................................29

15.2.1 General Description...............................................................................................29

15.2.2 Features.................................................................................................................30

15.2.3 Applications ..........................................................................................................30

15.2.4 Absolute Maximum Ratings.................................................................................. 30

15.2.5 Pinning ..................................................................................................................30

15.3 MP1593......................................................................................................................... 31

15.3.1 General Description...............................................................................................31

15.3.2 Features.................................................................................................................31

15.3.3 Applications ..........................................................................................................31

15.3.4 Absolute Maximum Ratings.................................................................................. 32

15.3.5 Electrical Characteristics....................................................................................... 32

15.3.6 Pinning ..................................................................................................................32

15.4 FDC642P.......................................................................................................................33

15.4.1 General Description...............................................................................................33

15.4.2 Features.................................................................................................................33

15.4.3 Absolute Maximum Ratings.................................................................................. 33

15.4.4 Pinning ..................................................................................................................34

15.5 ANX9021 ......................................................................................................................34

15.5.1 Features.................................................................................................................34

15.6 24LC02.......................................................................................................................... 35

15.6.1 General Description...............................................................................................35

15.6.2 Features.................................................................................................................35

15.6.3 10.6.3 Pinning .......................................................................................................36

15.7 µPA672T....................................................................................................................... 36

15.7.1 General Description...............................................................................................36

15.7.2 Features.................................................................................................................36

15.7.3 Absolute Maximum Ratings.................................................................................. 36

15.7.4 Pinning ..................................................................................................................37

15.8 M74HC4052..................................................................................................................37

15.8.1 General Description...............................................................................................37

15.8.2 Features.................................................................................................................37

15.8.3 Absolute Maximum Ratings.................................................................................. 37

15.8.4 Pinning ..................................................................................................................38

15.9 Max809..........................................................................................................................38

15.9.1 General Description...............................................................................................38

15.9.2 Features.................................................................................................................39

15.9.3 Absolute Maximum Ratings.................................................................................. 39

15.9.4 Pinning ..................................................................................................................40

15.10 24LC21...................................................................................................................... 40

15.10.1 General Description...........................................................................................40

15.10.2 Features.............................................................................................................40

15.10.3 Absolute Maximum Ratings.............................................................................. 40

15.10.4 Pinning ..............................................................................................................41

16 SERVICE MENU SETTINGS.......................... ................................ ................................41

Page 4

16.1 Video Setup...................................................................................................................41

16.2 AudioSetup....................................................................................................................42

16.3 Options 1....................................................................................................................... 42

16.4 Options 2....................................................................................................................... 43

16.5 Service Scan/Tuning Setup ...........................................................................................44

16.6 External Source Settings ............................................................................................... 44

16.7 Picture Mode.................................................................................................................44

16.8 Reset TV-Set................................................................................................................. 45

17 SOFTWARE UPDATE DESCRIPTION..........................................................................45

2

17.1 Analog Software Update Via I

C..................................................................................45

17.2 Analog Software Update Via UART ............................ ...... .. ...... ..... ... ..... ... ..... ..... ... .....46

18 BLOCK DIAGRAMS.......................................................................................................46

18.1 General Block Diagram.................................................................................................46

18.2 Power Management....................................................................................................... 48

18.3 DRX (IF Demodulator) Block Diagram........................................................................48

18.4 VCT Pro ........................................................................................................................49

18.4.1 General Block Diagram.........................................................................................49

18.4.2 MSP Block Diagram ........................................................... ................................ ..51

18.4.3 Video Processor of VCT 7wxyP Block Diagram................................................ 51

Page 5

1 INTRODUCTION

17MB12 Main Board is a single board IDTV project, consists of Micronas and NEC

concept. VCT_Pro and Emma2LL are used as controller for TV and IDTV side

respectively. VCT_Pro is capable of handling Audio processing, video processing,

motion adaptive upconversion (MAU), Scaling-Display processing and FPD control

(DPS), unified memory for audio video and Text, 3D comb filter-PC connectivity, OSD

and text processing. Emma2LL is capable of handling MPEG1 and MPEG2 decoding

and provide nearly all the functionality required to realise a high performance and costeffective digital set-top box or integrated digital TV.

TV supports DVB-T reception and following analog receptions PAL, SECAM, NTSC

colour standards and multiple transmission standards as B/G, D/K, I/I’, and L/L’

including German and NICAM stereo.

Sound system output is supplying 2x8W (10%THD) for stereo 8 speakers.

Supported peripherals are:

1 RF input VHF1, VHF3, UHF @ 75Ohm

1 FAV input

2 SCART sockets

1 SVHS input

1 Stereo Headphone input

1 YPbPr

1 PC input

2 HDMI input

1 Stereo audio input for PC and YPbPr

1 Stereo audio output

1 Subwoofer

1 Spdif

2 TUNER

Vertical mounted digital tuner is used in the product, which is suitable for analog

reception with DRX-A. The tuning is available through the digitally controlled I2C bus

(PLL). Below you will find info on the Tuner in use.

2.1 General description of DTT71307:

The DTT 755XX is designed for digital terrestrial reception in VHFIII and UHF,

compliance with the European digital terrestrial standard ETS 300 744. In addition the

tuner covers all analog channels from 44,25 MHz to 863,25 MHz. It is a two band

concept VHF and UHF,with VHF switch between VHF low (VHF I) and VHF high (VHF

III).

2.2 Features of DTT71307:

• VHF I/III/ UHF frequency range

• Antenna loop through (optional)

• Low phase noise

Page 6

• High level digital IF outputs

• RF-Modulator input for loop through to TV output (optional)

• Wide band AGC

• Indoor Antenna power feed through (optional)

2.3 Pinning:

3 AUDIO AMPLIFIER STAGE WITH TDA8932

3.1 General Description

The TDA8932 device is the high-power version that delivers an output power of 2 x 10

WRMS to 2 x 25 WRMS in a Single Ended (SE) configuration or 10 WRMS to 50 WRMS

in a Bridge Tied Load (BTL) configuration. The TDA8933 device is the low-power

version that delivers an output power of 2 x 5 WRMS to 2 x 15 WRMS in a Single Ended

(SE) configuration or 10 WRMS to 20 WRMS in a Bridge Tied Load (BTL) configuration.

This high efficiency SMA device is designed to operate without a heat sink and has the

flexibility to operate from either an asymmetrical supply or a symmetrical supply with a

wide range (10 V to 36 V or +/-5 V to +/-18 V). The TDA8932/33 device utilizes two

advanced features, respectively the thermal fold back and the cycle-by-cycle current

limiting to avoid audio holes (interruptions) during normal operation.

3.2 Features

• High efficiency Class-D audio amplifier due to a low RDS_ON

• Operates from a wide voltage range 10 V to 36 V (asymmetrical) or +/-5 V to +/-18 V

(symmetrical)

• Maximum power capability:

• TDA8932 is 2 x 25 WRMS maximum in 4 SE without heat sink

• TDA8933 is 2 x 15 WRMS maximum in 8 SE without heat sink

• Cycle-by-cycle current limiting to avoid interruption during normal operation

• Unique Thermal Foldback (TF) to avoid interruption during normal operation

• Integrated Half Supply Voltage (HVP) buffers for reference and SE output capacitance

(asymmetrical supply)

• Internal logic for pop-free power supply on/off cycling

• Low standby-current in SLEEP-mode for power saving regulations

Page 7

3.3 Applications

• Flat-TV application

• Flat panel monitors

• Multimedia systems

• Wireless speakers

• Micro systems

3.4 Pinning

4 POWER STAGE

The DC voltages required at various parts of the chassis and inverters are provided by a

main power supply unit and power interface board. The main power supply unit is

designed for 24V and 12V DC supply. Power stage which is on-chasis generates +24V

Page 8

for audio amplifier, 1.8V and 3.3V stand by voltage and 8V, 12V, 5V and 3.3Vsupplies

for other different parts of the chassis.

5 MICROCONTROLLER (VCTP)

5.1 General Features

The VCT 7wxyP is dedicated to high-quality FPD and double-scan TV sets. Modular

design and deep-submicron technology allow the economic integration of features in

LCD/plasma TV and in all classes of double-scan CRT TV sets. The VCT 7wxyP family

is based on approved functional blocks of existing Micronas products for audio and

video.

Each member of the family contains the entire audio, video, up-conversion processing

for 4:3 and 16:9 50/60 Hz progressive or 100/120 Hz interlaced stereo TV sets and the

control/data interface for flat-panel displays. The integrated microcontroller is supported

by a powerful OSD and graphics generator with integrated teletext acquisition.

5.1.1 Controller:

• High-performance 8-bit microcontroller, 8051 compatible

• Up to 512 kByte in system program Flash

• WST, PDC, VPS, and WSS acquisition

• Closed caption and V-chip acquisition

• Up to 10 page on chip teletext memory

• Up to 1000 pages with internal memory

• Up to 30 GPIO

5.1.2 Audio:

• Multistandard TV-sound demodulation:

-All A2/NICAM standards

-BTSC/SAP with DBX

-EIA-J

• Baseband sound processing for loudspeaker channel:

-Volume, bass, treble, loudness, balance

-Spatial effect (e.g. pseudo stereo)

-Micronas AROUND

(Virtual Dolby Surround optional)

-Micronas BASS

-BBE

-SRS WOW

-SRS TruSurround XT

-Lipsync function

5.1.3 Video:

• CVBS, S-VHS, YCrCb and RGB inputs

• HDTV YPrPb and RGB inputs

• ITU656 input

• Linedoubling with vertical detail enhancement (without internal memory)

Page 9

• State of the art motion adaptive up conversion (with internal memory)

• 4H adaptive comb filter for PAL/NTSC (without internal memory)

• 3D comb filter for PAL/NTSC (with internal memory) (Optional)

• Internal SDR RAM interface

• Powerful horizontal and vertical scaling inclusive

• Nonlinear horizontal scaling “panorama vision”

• picture adaptive image improvements (DCE, LSE, CTI, SCE, NCE)

• non-linear colorspace enhancement (NCE) with 32 programmable slopes and

sections per RGB component (blue stretch, static black stretch, gamma

correction).

• Dynamic contrast enhancement (DCE) (histogram based black stretch with peak

black and activity detection and contrast adaption)

• Luma sharpness enhancement (LSE)

• Color transient improvement (CTI)

• Selective color enhancement (SCE) for skin tone correction, blue and green

stretch

5.2 Multistandard Sound Processor (MSP) Features

The MSP receives the analog Sound IF signal from the tuner and converts it to digital

with its internal SIF-AD converter. The MSP is able to demodulate all TV sound

standards worldwide including the digital NICAM system. TV stereo sound standards

that are unavailable for a specific VCTP version are processed in analog mono sound of

the standard. In that case, stereo or bilingual processing will not be possible.

• Sound IF input

• Worldwide FM/AM-mono sound demodulation

• FM stereo sound demodulation (A2, EIA-J)

• BTSC/SAP demodulation with DBX

• NICAM demodulation

• FM radio & RDS/RBDS demodulation

• Automatic standard detection

• automatic volume correction (AVC)

• Automatic sound select

• Baseband processing for loudspeaker channel:

volume, bass, treble, loudness, balance

-spatial effect (e.g. pseudo stereo)

-Micronas AROUND

-Micronas BASS

-SRS WOW (optional)

-SRS TruSurround XT (optional)

-delayline for lipsync function (shared memory)

-Virtual Dolby Surround (optional)

• 1 I2S input for external ATSC/DVD decoder

• 1 I2S interface for audio delayline

• 1 SPDIF output

• Audio i/o switches

-4 analog stereo line inputs and 2 analog stereo line outputs (configurable 5

analog stereo line inputs and 1 analog stereo line output)

-1 analog stereo loudspeaker output

Page 10

-1 analog subwoofer output

-1 analog stereo headphone output

5.3 Video Features

The TVT is a Teletext decoder for decoding World System Teletext data, as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide-Screen

Signalling (WSS) data used for PALplus transmissions (line 23). The device also

supports Closed Caption acquisition and decoding.

The TVT provides an integrated general-purpose, fully 8051-compatible microcontroller

with television-specific hardware features. The microcontroller has been enhanced to

provide powerful features such as memory banking, data pointer, additional interrupts,

shared memory access etc.

The TVT has an internal XRAM of 32 KB and a BOOT ROM of 4 KB. For operation the

code is fetched from a 16bit FLASH, which can be addressed up to 1 MByte.

The controller with dedicated hardware does most of the internal TTX acquisition

processing, transfers data to/from external memory interface, and receives/transmits

data via I2C-bus interface. In combination with dedicated hardware, the slicer stores

TTX data in a VBI buffer of 1 KB. The microcontroller firmware performs all the

acquisition tasks (hamming and parity checks, page search, and evaluation of header

control bits) once per field. Additionally, the firmware can provide high-end Teletext

features like Packet-26 handling, FLOF/TOP and list-pages. The interface-to-user

software is optimized for minimal overhead. TVT is realized in deep submicron

technology with 1.8 V supply voltage and 3.3 V I/O (TTL compatible).

• 16 analog video inputs (4xCVBS/Y/C + 3xRGB/YCrCb/YPrPb)

• Video input switch matrix

• 3 analog video outputs (integrated Y+C adder)

• 24-bit RGB/H/V/clk input (e.g. ext. DVI decoder) or 656 8bit input

• 656 8bit input/output (e. g. for external high-end up conversion by FRCA)

• Multi-standard color decoder PAL/NTSC/SECAM including all substandards

• 2D adaptive comb filter for PAL/NTSC with vertical peaking

• 3D-comb filter for PAL/NTSC (Optional)

• Macrovision compliant multi-standard sync processing

• Trilevel sync slicer for HDTV

• Macrovision detection

• High-quality soft mixer controlled by Fast Blank (alpha blending)

• Fastblank monitor via I2C

• Noise measurement

• Letterbox detection (auto-wide)

• Split screen (OSD and video side by side) and AV PIP

5.4 Controller Features

The TVT is a Teletext decoder for decoding World System Teletext data, as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide-Screen

Signalling (WSS) data used for PALplus transmissions (line 23). The device also

supports Closed Caption acquisition and decoding.

The TVT provides an integrated general-purpose, fully 8051-compatible microcontroller

with television-specific hardware features. The microcontroller has been enhanced to

Page 11

provide powerful features such as memory banking, data pointer, additional interrupts,

shared memory access etc.

• High performance 8-bit microcontroller, 8051 instruction set compatible

• 81 MHz system clock, two machine cycles per instruction

• On-chip debug support (OCDS)

• Up to 512 kByte in system program Flash

• 256 byte on-chip program RAM

• 128 byte on-chip extended stack RAM

• 4-level, 24-input interrupt controller

• Patch module for 16 ROM locations

• Two 16-bit reloadable timers

• Capture compare timer for infrared decoding

• Watchdog timer

• Uart

• Real time clock

• PWM units (2 channels 14-bit, 6 channels 8-bit)

• 8-bit ADC (4 channels)

• I2C bus master/slave interface

• Up to 32 programmable I/O ports

5.5 OSD & Teletext Features

The on-chip display unit for displaying Level 1.5 Teletext data can also be used for

customer-defined onscreen displays.

The TVT has an internal XRAM of 32 KB and a BOOT ROM of 4 KB. For operation the

code is fetched from a 16bit FLASH, which can be addressed up to 1 MByte.

In combination with dedicated hardware, the slicer stores TTX data in a VBI buffer of 1

KB. The microcontroller firmware performs all the acquisition tasks (hamming and parity

checks, page search, and evaluation of header control bits) once per field. Additionally,

the firmware can provide high-end Teletext features like Packet-26 handling, FLOF/TOP

and list-pages. The interface-to-user software is optimized for minimal overhead.

5.6 Port Allocation

Page 12

Page 13

Page 14

Page 15

Page 16

Page 17

Page 18

Page 19

Page 20

6 DRX 3961A

6.1 General Desription

The DSP-based Analog TV IF Demodulator DRX 396xA performs the entire

multistandard Quasi Split Sound (QSS) TV IF processing, AGC, video demodulation,

and generation of the sound IF (SIF), requiring only one SAW filter. The IC is designed

for applications in TV sets, VCRs, PC cards, and TV tuners.

The alignment-free DRX 396xA does not need special external components. All control

functions and status registers are accessible via I2C bus interface.

6.2 Features

• Multistandard QSS IF processing with a single SAW

• Highly reduced amount of external components (no tank circuit, no

potentiometers, no SAW switching)

Page 21

• Programmable IF frequency (38.9 MHz, 45.75 MHz, 32.9 MHz, 58.75 MHz,

36.125 MHz etc.)

• Digital IF processing for the following standards: B/G, D/K, I, L/L’, and M/N

• Standard specific digital post filtering

• Standard specific digital video/audio splitting

• Standard specific digital picture carrier recovery:

-Alignment-free

-Quartz-stable and accurate

-Stable frequency lock at 100% modulation and overmodulation up to

150%

-Quartz-accurate AFC information

• Programmable standard specific digital group delay equalization

• Automatically frequency-adjusted Nyquist slope, therefore optimum picture and

sound performance over complete lock in frequency range

• Standard-specific digital AGC and delayed tuner AGC with programmable tuner

take-over point

• Fast AGC due to linear structure

• Adaptive back porch control, therefore fast positive modulation AGC

• No sound traps needed at video output

• SIF output with standard-dependent pre-filtering and amplitude-controlled output

level

• Optimal sound SNR due to carrier recovery without quadrature distortions

• FM radio capability without external components and with standard TV tuner

• Prepared for digital TV (DVB-C, DVB-T, ATSC)

• I2C bus interface

7 SERIAL 64K I2C EEPROM M24C64WBN6

7.1 General Description

M24C64WBN6 is a 64 Kbit Electrically Erasable PROM. These I2C-compatible

electrically erasable programmable memory (EEPROM) devices are organized as

8192x8 bits. It supports 400kHz Protocol I2C uses a two-wire serial interface,

comprising a bi-directional data line and a clock line.

The M24C64WBN6 is available in the standard 8-pin (Vcc, WC, SDA (i2c data), SCL

(i2c clock), Vss,E0,E1,E2). WC pin is critcal pin. If WP is high, writing is not possible to

EEPROM. If WP is low, writing is possible to EEPROM.

7.2 Features

• Two-Wire I2C Serial Interface Supports 400kHz Protocol

• Single Supply Voltage:

– 4.5 to 5.5V for M24Cxx

– 2.5 to 5.5V for M24Cxx-W

– 1.8 to 5.5V for M24Cxx-R

• Write Control Input

• BYTE and PAGE WRITE (up to 32 Bytes)

Page 22

• RANDOM and SEQUENTIAL READ Modes

• Self-Timed Programming Cycle

• Automatic Address Incrementing

• Enhanced ESD/Latch-Up Protection

• More than 1 Million Erase/Write Cycles

• More than 40-Year Data Retention

7.3 Absolute Maximum Ratings

7.4 Pinning

8 CLASS AB STEREO HEADPHONE DRIVER TDA7050

8.1 General Description

The TDA7050T is a low voltage audio amplifier for small radios with headphones (such

as watch, pen and pocket radios) in mono (bridge-tied load) or stereo applications.

8.2 Features

· Limited to battery supply application only (typ. 3 and 4 V)

· Operates with supply voltage down to 1,6 V

· No external components required

· Very low quiescent current

· Fixed integrated gain of 26 dB, floating differential input

· Flexibility in use - mono BTL as well as stereo

· Small dimension of encapsulation (see package design example).

Page 23

8.3 Pinning

9 SAW FILTER X6966M

9.1 Features:

- IF filter for digital cable TV

- Plastic package SIP5K

9.2 Pin configuration:

1 Input

2 Input - ground

3 Chip carrier - ground

4 Output

5 Output

9.3 Frequency response:

Page 24

10 MPEG DECODER µPD61115

10.1 DESCRIPTION

The µPD61115 device is a member of the second generation of multimedia processors

based on NEC’s Enhanced MultiMedia Architecture (EMMArchitecture). These devices

provide nearly all the functionality required to realise a high performance and costeffective digital set-top box or integrated digital TV.

Page 25

10.2 FEATURES

• MPEG1 and MPEG2-TS/PS compliant

• High performance MIPS32™ 4Kc™ main CPU core

• High performance MIPS32™ 4Km™ sub-CPU core

• Integrated DVB descrambling with family options for Irdeto and Multi2

• 36 PID filters, 32 section filters

• Video Outputs: 4 DACs for RGB, Component video, S-video and composite

output with support for PAL, NTSC and SECAM

• 4 graphics planes

• Audio Output: 2-channel PCM and SPDIF

• Peripherals support

two fast UARTs with 16byte FIFOs

I2C interface

infrared receiver

three wire clocked serial interface

• System timers, RTC and Watchdog timer

• Motorola/Intel Bus.

11 DRX 3973D

Fourth-Generation COFDM Demodul at or s

11.1 Introduction

The DRX 3973D and the DRX 3977D are fourth-generation COFDM demodulators that

offer today’s highest level of front-end integration resulting in ultimate DVB-T digital

reception, compliant to ETS 300 744, DTG D-Book, EICTA E-Book, and Nordig Unified

v1.0.2 .

The DRX 3973/77D applies cutting-edge digital filtering techniques in combination with a

high-performance A/D-converter and PLL configuration, resulting in superior

performance figures in the presence of digitaland analog adjacent channels.

Progressive channel estimator algorithms provide exceptional performance in multipathand dynamicecho

conditions – an especially important feature for single-frequency networks and indoor

reception.

The state-of-the-art impulsive noise cruncher suppresses interferences originating from

sources such as

cars, electrical motors, and household appliances.

11.2 Features

Highest level of front-end integration and flexibility:

Integrated PGA (programmable gain amplifier) 30 dB

Single 8 MHz SAW filter operation

Page 26

2 AGC control signals available for RF and IF amplifier control

Flexible clock reference options

Re-use of 4 MHz tuner clock reference

Pre-SAW sense input for optimal RF AGC setting and RF-level measurement

Excellent digital reception performance:

Superior digital and analog adjacent channel performance (> 40dB for QEF)

Impulsive noise cruncher

Multipath and dynamic echoes

The input IF frequency ranging up to 44 MHz ensures upward compatibility for new

tuner topologies

Integrated microprocessor to perform autonomous detection and operation of all

possible DVB-T

modes, without interaction with the host processor

Fully automatic and fast signal acquisition: UHF and VHF band-scan in <20 seconds

Meets all international DVB-T receiver specifications: Nordig Unified, DTG, EICTA

Comfortable software drivers for integration of tuner and COFDM demodulator

Secondary serial interface for tuner control

5 V tolerant AGC and secondary serial protocol outputs

2 general purpose I/O pins (GPIO)

Configurable parallel or serial MPEG-TS output

PMQFP64-2 package: footprint 1010 mm (DRX 3973D)

PQFN48-1 package: small footprint 77 mm (DRX 3977D)

IEEE 1149.1 boundary scan

11.3 Applications

IDTV / hybrid TV

Set-top boxes

PVR / DVDR

Network interface modules (NIM)

PC-TV applications

12 PI6CX100-27MHz 3.3V VCXO for Set-Top Box Applications

12.1 Features

• 3.3V operating voltage

• Uses an inexpensive external crystal

• On-chip VCXO with pull range of 240ppm

• VCXO tuning voltage from 0 to 3.3V

• 10mA output drive at CMOS levels

• Available in SOIC package

12.2 Description

The PI6CX100-27 is a low-cost, high-performance 3.3V VCXO, designed to replace

expensive VCXO modules. The on-chip Voltage Controlled Crystal Oscillator accepts a

Page 27

0 to 3.3V input voltage to cause clocks to vary by ±120ppm. This device uses an

inexpensive external pullable crystal at 27 MHz to produce the same output

frequency.The PI6CX100-27 is designed for Set-Top Box applications.

13 74V1G08

SINGLE 2-INPUT AND GATE

• HIGHSPEED: tPD = 4.3 ns (TYP.) atVCC= 5V

• LOWPOWERDISSIPATION:

• ICC =1 A (MAX.) at TA =25 oC

• HIGHNOISEIMMUNITY:

• VNIH=VNIL =28%VCC (MIN.)

• POWERDOWN PROTECTIONON INPUTS

• SYMMETRICAL OUTPUT IMPEDANCE:

• |IOH| = IOL = 8 mA(MIN)

• BALANCEDPROPAGATIONDELAYS:

• tPLH tPHL

• OPERATINGVOLTAGERANGE:

• VCC (OPR)= 2V to 5.5V

• IMPROVEDLATCH-UP IMMUNITY

• DESCRIPTION

• The 74V1G08 is an advanced high-speed CMOS SINGLE 2-INPUT AND GATE

fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS

technology.

14 FMS6145

Low Cost Five Channel 4th Order Standard Definition Video Filter Driver

Description

The FMS6145 Low Cost Video Filter (LCVF) is intended to replace passive LC filters

and drivers with a low-cost integrated device. Five 4th order filters provide improved

image Quality compared to typical 2nd or 3rd order passive solutions.

The FMS6145 may be directly driven by a DC-coupled DAC output or an AC-coupled

signal. Internal diode clamps and bias circuitry

may be used if AC-coupled inputs are required.

Page 28

The outputs can drive AC or DC-coupled single (150) or dual(75) loads. DC-coupling

the outputs removes the need for output coupling capacitors. The input DC levels will be

offset approximately +280mV at the output.

Features

• Five fourth-order 8MHz (SD) filters

• Transparent input clamping

• Dual video load drive (2Vpp, 75)

• AC or DC-coupled inputs

• AC or DC-coupled outputs

• DC-coupled outputs eliminate AC-coupling capacitors

• 5V only

• Lead (Pb) Free TSSOP-14 package

Applications

• Cable set top boxes

• Satellite set top boxes

• DVD players

• HDTV

• Personal video recorders (PVR)

• Video on demand (VOD)

15 IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM

LM1117

LM1086

MP1593

FDC642P

SIL9011

24LC02

µPA672T

M74HC4052

Max809

24LC21

15.1 LM1117

15.1.1 General Description

The LM1117 is a series of low dropout voltage regulators with a dropout of 1.2V at

800mA of load current. It has the same pin-out as National Semiconductor’s industry

standard LM317. The LM1117 is available in an adjustable version, which can set the

output voltage from 1.25V to 13.8V with only two external resistors. In addition, it is also

available in five fixed voltages, 1.8V, 2.5V, 2.85V, 3.3V, and 5V. The LM1117 offers

current limiting and thermal shutdown. Its circuit includes a zener trimmed bandgap

reference to as-sure output voltage accuracy to within ±1%. The LM1117 series is

available in SOT- 223, TO-220, and TO-252 D-PAK packages. A minimum of 10F

Page 29

tantalum capacitor is required at the output to improve the transient response and

stability.

15.1.2 Features

• Available in 1.8V, 2.5V, 2.85V, 3.3V, 5V, and Adjustable Versions

• Space Saving SOT-223 Package

• Current Limiting and Thermal Protection

• Output Current 800mA

• Line Regulation 0.2% (Max)

• Load Regulation 0.4% (Max)

• Temperature Range

• LM1117 0°C to 125°C

• LM1117I -40°C to 125°C

15.1.3 Applications

• 2.85V Model for SCSI-2 Active Termination

• Post Regulator for Switching DC/DC Converter

• High Efficiency Linear Regulators 15

• 32” TFT TV Service Manual 10/01/2005

• Battery Charger

• Battery Powered Instrumentation

15.1.4 Absolute Maximum Ratings

15.1.5 Pinning

15.2 LM1086

15.2.1 General Description

The LM1086 is a low dropout three terminal regulator with 1.5A output current capability.

Page 30

The output voltage is adjustable with the use of a resistor divider. Dropout is guaranteed

at a maximum of 500 mV at maximum output current. It's low dropout voltage and fast

transient response make it ideal for low voltage microprocessor applications. Internal

current and thermal limiting provides protection against any overload condition

that would create excessive junction temperature.

15.2.2 Features

• Low Dropout Voltage 500mV at 1.5A Output Current

• Fast Transient Response

• 0.015% Line Regulation

• 0.1% Load Regulation

• Current Limiting and Thermal Protecion.

• Adjustable or Fixed Output Voltage(1.8, 2.5, 2.85, 3.0, 3.3, 3.45, 5.0V)

• Surface Mount Package SOT-223 & TO-263 (D2 Package)

• 100% Thermal Limit Burn-in

15.2.3 Applications

• Battery Charger

Adjustable Power Supplies

•

Constant Current Regulators

•

•

Portable Instrumentation

High Efficiency Linear Power Supplies

•

High Efficiency "Green" Computer Systems

•

SMPS Post-Regulator

•

•

Power PC Supplies

• Powering VGA & Sound Card

15.2.4 Absolute Maximum Ratings

15.2.5 Pinning

Page 31

15.3 MP1593

15.3.1 General Description

The MP1593 is a step-down regulator with an internal Power MOSFET. It achieves 3A

continuous output current over a wide input supply range with excellent load and line

regulation. Current mode operation provides fast transient response and eases loop

stabilization. Fault condition protection includes cycle-by-cycle current limiting and

thermal shutdown. Adjustable soft-start reduces the stress on the input source at turnon. In shutdown mode the regulator draws 20A of supply current. The MP1593

requires a minimum number of readily available external components to complete a 3A

step down DC to DC converter solution.

15.3.2 Features

• 3A Output Current

• Programmable Soft-Start

• 100m Internal Power MOSFET Switch

• Stable with Low ESR Output Ceramic Capacitors

• Up to 95% Efficiency

• 20A Shutdown Mode

• Fixed 385KHz Frequency

• Thermal Shutdown

• Cycle-by-Cycle Over Current Protection

• Wide 4.75 to 28V Operating Input Range

• Output Adjustable from 1.22V

• Under Voltage Lockout

• Available in 8-Pin SOIC Package

15.3.3 Applications

• Distributed Power Systems

• Battery Chargers

Page 32

• Pre-Regulator for Linear Regulators

• Flat Panel TVs

• Set-Top Boxes

• Cigarette Lighter Powered Devices

• DVD/PVR Devices

15.3.4 Absolute Maximum Ratings

15.3.5 Electrical Characteristics

15.3.6 Pinning

Pin1:BS

High-Side Gate Drive Boost Input. BS supplies the drive for the high-side N-Channel

MOSFET switch. Connect a 10nF or greater capacitor from SW to BS to power the high

side switch.

Pin2:IN

Power Input. IN supplies the power to the IC, as well as the step-down converter

switches. Drive IN with a 4.75V to 28V power source. Bypass IN to GND with a suitably

large capacitor to eliminate noise on the input to the IC.

Pin3:SW

Power Switching Output. SW is the switching node that supplies power to the output.

Connect the output LC filter from SW to the output load. Note that a capacitor is required

from SW to BS to power the high-side switch

.

Page 33

Pin4:GND

Ground.

Pin5:FB

Feedback Input. FB senses the output voltage to regulate that voltage. Drive FB with a

resistive voltage divider from the output voltage. The feedback threshold is 1.222V.

Pin6:COMP

Compensation Node. COMP is used to compensate the regulation control loop. Connect

a series RC network from COMP to GND to compensate the regulation control loop. In

some cases, an additional capacitor from COMP to GND is required.

Pin7:EN

Enable Input. EN is a digital input that turns the regulator on or off. Drive EN high to turn

on the regulator, drive EN low to turn it off. An Under Voltage Lockout (UVLO) function

can be implemented by the addition of a resistor divider from VIN to GND. For complete

low current shutdown its needs to be less than 0.7V. For automatic startup, leave EN

unconnected.

Pin8:SS

Soft-Start Control Input. SS controls the soft-start period. Connect a capacitor from SS

to GND to set the soft-start period. A 0.1F capacitor sets the soft-start period to 10ms.

To disable the soft-start feature, leave SS unconnected.

15.4 FDC642P

15.4.1 General Description

This p-channel 2.5V specified MOSFET is produced using Fairchild’s advanced

PowerTrench process that has been especially tailored to minimize on state resistance

and yet maintain low gate charge for superior switching performance.

15.4.2 Features

15.4.3 Absolute Maximum Ratings

Page 34

15.4.4 Pinning

15.5 ANX9021

The ANX9021 is an advanced multimedia receiver compliant with High Definition Multimedia Interface

(HDMI) Specification 1.1. HDMI is the first transport standard to unify digital video, audio, and control data

over lowcost cables. It connects digital television, flat panel displays and project systems digitally to multimedia

sources: DVD players, high definition settop boxes, digital video tape recorders, and personal computers.

Digital transmission, in turn, delivers an uncompromising multimedia experience. HDMI also includes

encryption for premium contents pursuant to the Highbandwidth Digital Content Protection (HDCP) standard.

The ANX9021 embeds the HDCP keys and key selection vectors to reduce manufacturing complexity

and system cost.

15.5.1 Features

Dualchannel HDMI receiver supporting link

data rate up to 1.65 Gbps

HDMI 1.1, HDCP 1.1 and DVI 1.0 compliant

WideEye™ architecture for signal conditioning

and equalization

support cable length up to 20m

better than 10E12 bit error rate

Digital interface to video processor supporting

24bit RGB / YCbCr 4:4:4

16/20/24 bit YCbCr 4:2:2

8/10/12 bit YC bCr 4:2:2 (ITU BT656)

12bit double data rate interface

Color space conversion: RGB to/from YCbCr both

directions (601 and 709 standards)

Auto video mode configuration

Analog RGB/YPbPr output with 8bit linearity

Digital audio interface

32 to 192 kHz audio sampling rate

Up to 4 I2S interface for 8channel audio

S/PDIF interface supporting PCM, Dolby

Page 35

Digital™, DTS™ digital audio transmission

using IEC 60958 and IEC61937

Configurable soft mute

Integrated HDCP decryption engine and

preprogrammed keys

Programmable power management with

automatic shutdown for power conservation

Supports automated link integrity checking

144lead TQFP package supporting leadfree and

green requirements

Pinout compatible with Silicon Image

15.6 24LC02

15.6.1 General Description

24AA02/24LC02B (24XX02*) is a 2 Kbit Electrically Erasable PROM. The device is

organized as one block of 256 x 8-bit memory with a 2-wire serial interface. Low-voltage

design permits operation down to 1.8V, with standby and active currents of only 1µA

and 1mA, respectively. The 24XX02 also has a page write capability for up to 8 bytes of

data.

15.6.2 Features

• Single supply with operation down to 1.8V

• Low-power CMOS technology

-1mA active current typical

-1µA standby current typical (I-temp)

• Organized as 1 block of 256 bytes (1 x 256 x 8)

• 2-wire serial interface bus, I

• Schmitt Trigger inputs for noise suppression

• Output slope control to eliminate ground bounce

• 100 kHz (24AA02) and 400 kHz (24LC02B) compatibility

• Self-timed write cycle (including auto-erase)

• Page write buffer for up to 8 bytes

• 2ms typical write cycle time for page write

• Hardware write-protect for entire memory

• Can be operated as a serial ROM

• Factory programming (QTP) available

• ESD protection > 4,000V

• 1,000,000 erase/write cycles

• Data retention > 200 years

• 8-lead PDIP, SOIC, TSSOP and MSOP packages

• 5-lead SOT-23 package

• Pb-free finish available

• Available for extended temperature ranges:

-Industrial (I): -40°C to +85°C

-Automotive (E): -40°C to +125°C

2

C™ compatible

Page 36

15.6.3 10.6.3 Pinning

15.7 µPA672T

15.7.1 General Description

N-channel Mos-Fet array for switching.The µPA672T is a super-mini-mold device

provided with two MOS FET elements. It achieves high-density mounting and saves

mounting costs.

15.7.2 Features

• Two MOS FET circuits in package the same size as SC-70

• Automatic mounting supported

15.7.3 Absolute Maximum Ratings

Page 37

15.7.4 Pinning

15.8 M74HC4052

15.8.1 General Description

The M74HC4052 is a dual four-channel analog MULTIPLEXER/DEMULTIPLEXER

fabricated with silicon gate C2MOS technology and it is pin to pin compatible with the

equivalent metal gate CMOS4000B series. It contains 8 bidirectional and digitally

controlled analog switches.

15.8.2 Features

• LOW POWER DISSIPATION: ICC = 4mA(MAX.) at TA=25°C

• LOGIC LEVEL TRANSLATION TO ENABLE 5V LOGIC SIGNAL TO

COMMUNICATE

• WITH ±5V ANALOG SIGNAL

• LOW "ON" RESISTANCE:

70W TYP. (VCC - VEE = 4.5V)

50W TYP. (VCC - VEE = 9V)

• WIDE ANALOG INPUT VOLTAGE RANGE: ±6V

• FAST SWITCHING:

tpd = 15ns (TYP.) at TA = 25 °C

• LOW CROSSTALK BETWEEN SWITCHES

• HIGH ON/OFF OUTPUT VOLTAGE RATIO

• WIDE OPERATING SUPPLY VOLTAGE RANGE (VCC - VEE) = 2V TO 12V

• LOW SINE WAVE DISTORTION: 0.02% at VCC - VEE = 9V

• HIGH NOISE IMMUNITY: VNIH = VNIL = 28 % VCC (MIN.)

• PIN AND FUNCTION COMPATIBLE WITH 74 SERIES 4052

15.8.3 Absolute Maximum Ratings

Page 38

15.8.4 Pinning

VEE supply pin is provided for analog input signals. It has an inhibit (INH) input terminal

to disable all the switches when high. For operation as a digital

multiplexer/demultiplexer, VEE is connected to GND.

A and B control inputs select one channel out of four in each section. All inputs are

equipped with protection circuits against static discharge and transient excess voltage.

15.9 Max809

15.9.1 General Description

The MAX809 and MAX810 are costeffective system supervisor circuits designed to

monitor VCC in digital systems and provide a reset signal to the host processor when

necessary. No external components are required.

The reset output is driven active within 10 _sec of VCC falling through the reset voltage

threshold. Reset is aintained active for a timeout period which is trimmed by the factory

after VCC rises above the reset threshold. The MAX810 has an activehigh RESET

Page 39

output while the MAX809 has an activelow RESET output. Both devices are available

in SOT23 and SC70 packages.

15.9.2 Features

• Precision VCC Monitor for 1.5 V, 1.8 V, 2.5 V, 3.0 V, 3.3 V, and 5.0 V Supplies

• Precision Monitoring Voltages from 1.2 V to 4.9 V Available in 100 mV Steps

• Four Guaranteed Minimum PowerOn Reset Pulse Width Available (1 ms, 20

ms, 100 ms, and 140 ms)

• RESET Output Guaranteed to VCC = 1.0 V.

• Low Supply Current

• Compatible with Hot Plug Applications

• VCC Transient Immunity

• No External Components

• Wide Operating Temperature: 40°C to 105°C

• PbFree Packages are Available

15.9.3 Absolute Maximum Ratings

Page 40

15.9.4 Pinning

15.10 24LC21

15.10.1 General Description

The 24LC21 is a 1K bit electrically erasable programmable memory (EEPROM), organized by 8

bits.This device can operate in two modes: Transmit Only mode and I2C bidirectional mode.

When powered, the device is in Transmit Only mode with EEPROM data clocked out from the

rising edge of the signal applied on VCLK.

15.10.2 Features

• 1 MILLION ERASE/WRITE CYCLES

• 40 YEARS DATA RETENTION

• 2.5V to 5.5V SINGLE SUPPLY VOLTAGE

• 400k Hz COMPATIBILITY OVER the FULL RANGE of SUPPLY VOLTAGE

• TWO WIRE SERIAL INTERFACE I2C BUS COMPATIBLE

• PAGE WRITE (up to 8 BYTES)

• BYTE, RANDOM and SEQUENTIAL READ MODES

• SELF TIMED PROGRAMMING CYCLE

• AUTOMATIC ADDRESS INCREMENTING

• ENHANCED ESD/LATCH UP PERFORMANCES

15.10.3 Absolute Maximum Ratings

Page 41

15.10.4 Pinning

16 SERVICE MENU SETTINGS

In order to reach service menu,

• First Press “MENU”

• Then press the remote control code, which is “4725”

16.1 Video Setup

• Panel Select <..................................>

CHI MEI 16/9 32 inch

LG 16/9 26 inch

SAMSUNG 16/9 32 inch

• Picture Mute <.....>

If “Yes” selected, “Picture mute” feature is active.

• Blue Screen <.....>

If “Yes” selected, “Blue Background” item is seen in “Feature”

menu.

• YC Delay <...........>

Page 42

Tuner PAL <.....> Value between -8 to+7

Ext PAL <.....> Value between -8 to+7

SECAM <.....> Value between -8 to+7

NTSC <.....> Value between -8 to+7

• AGC (dB) <.....> Value between 0 to+8

16.2 AudioSetup

• Equalizer <.....>

If “Yes” selected, “Equalizer” item is seen in “Sound” menu.

• BBE

• SRS WOW

• Virtual Dolby Surround <.....>

If “Yes” selected, Virtual Dolby Surround feature is seen in “Sound”

menu with selected Virtual Dolby Text.

• Virtual Dolby Text The selected item is seen as Virtual Dolby Srround Text.

3DS

Virtual Dolby

3D Panorama

• AVL <.....>

If “Yes” selected, “AVL” item is seen in “Sound” menu.

• Carrier Mute <.....>

If “Yes” selected, “Carrier mute” feature is active.

• Audio Delay Offset

• Prescale

FM Presc. AVL On <.......> Value between 0 to +127

AM Presc. AVL On <.......> Value between 0 to +127

NICAM Presc. AVL On <.......> Value between 0 to +127

I2S Presc. AVL On <.......> Value between 0 to +127

SCART Presc. AVL On <.......> Value between 0 to +127

FM Presc. AVL Off <.......> Value between 0 to +127

AM Presc. AVL Off <.......> Value between 0 to +127

NICAM Presc. AVL Off <.......> Value between 0 to +127

I2S Presc. AVL Off <.......> Value between 0 to +127

SCART Presc. AVL Off <.......> Value between 0 to +127

• Dynamic Bass <.....>

If “Yes” selected, “Dynamic Bass ” item is seen in “Sound” menu.

• Subwoofer <.....>

If “Yes” selected, “Subwoofer” item is seen in “Sound” menu.

16.3 Options 1

• VCTP Version <.......>

Basic+

Basic

• Double Digit <.....>

If “Yes” selected, “Double Digit” button is active for channel

selection.

• TEA6415C Available <.....>

If “Yes” selected, video switch IC is active on hardware.

• TEA642X Available<.....>

Page 43

If “Yes” selected, audio switch IC is active on hardware.

• Power-Up Mode <.......>

StandBy If selected, TV opens in stand by mode.

L.State If selected, TV opens in Last State mode.

• TV Open Mode <.......>

Source

1st TV

Last TV

• Select Languages <.......> “Yes” selected languages are seen as option under

the “Language” item in “Feature” menu

Language Set 1

o German <.......>

o French <.......>

o Spanish <.......>

o Italian <.......>

o Danish <.......>

o Finnish <.......>

o Swedish <.......>

Language Set 2

o Greek <.......>

o Norwegian <.......>

o Dutch <.......>

o Portuguse <.......>

o Polish <.......>

o Turkish <.......>

o Russian <.......>

o Czech <.......>

Language Set 3

o Hungarian <.......>

o Slovak <.......>

o Slovenian <.......>

Romanian <.......>

o

o Bulgarian <.......>

o Croatian <.......>

o Serbian <.......>

o Hebrew <.......>

• First APS <.......>

If “Yes” selected, first time TV opens by asking APS.

• APS Volume <.......> value between 0 to+63

• Burn In Mode <.......>

If “Yes” selected, TV opens with Burn-In mode. This mode is

used in manufacturing.

• APS Test

• HDMI WP <.......>

If “Yes” selected, HDMI EDID ROM is write protected.

16.4 Options 2

Page 44

• Autostore <.......>

If “Yes” selected, Channel is automatically stored.

• Led Type <.............................>

1 Led 1 Colour

1 Led 2 Colours

2 Led 2 Colours

• PC PIP <.......>

• PC Stand By <.......>

16.5 Service Scan/Tuning Setup

• Search for L/L’ <.......>

• Pref. Search Standard <...........>

BG, DK, I

L/L’

M

• Station Ident <.......>

• ATS Delay Time (ms) <.......> Value between 20 to 250

• Color Killer Threshold <... ....> Value between 0 to +255

• Tuner Options <.......>

Control Byte <.......> Value between 0 to +255

Low-Mid – Low Byte <.......> Value between 0 to +255

Low-Mid – High Byte <.......> Value between 0 to +255

Mid-High – Low Byte <.......> Value between 0 to +255

Mid-High – High Byte <.......> Value between 0 to +255

BSW1 <.......> Value between 0 to +255

BSW2 <.......> Value between 0 to +255

BSW3 <.......> Value between 0 to +255

16.6 External Source Settings

• DTV <.......>

• DVD <.......>

• Ext 2 S-Video <.......>

• Ext 3 <.......>

• Ext 3 S-Video <.......>

• FAV <.......>

• BAV <.......>

• S-Video <.......>

• HDMI 1 <.......>

• HDMI 2 <.......>

• YPbPr <.......>

• PC <.......>

16.7 Picture Mode

• Sources <.......>

Tuner

CVBS

RGB

Page 45

SVHS

HDMI

YPbPr

PC

PIP

• Picture Mode <.......>

Dynamic

Natural

Cinema

• Colour Temp <.......>

Cool

Normal

Warm

• Contrast <.......> Value between 0 to +63

• Brightness <.......> Value between 0 to +63

• Sharpness <.......> Value between 0 to +15

• Colour <.......> Value between 0 to +63

• Backlight <.......> Value between 0 to +255

• R <.......> Value between -63 to +63

• G <.......> Value between -63 to +63

• B <.......> Value between -63 to +63

16.8 Reset TV-Set

• Initialize NVM from ROM

Press green button to reset the NVM from ROM

17 SOFTWARE UPDATE DESCRIPTION

17.1 Analog Software Update Via I2C

Step.1

Short the second and third pins of PL_402. Power ON and keep shorting the pins 3-5

seconds.

Step.2

Then connect the I

Step.3

Connect the other end of the tool to PL_402.

Step.4

Run Cosima_VCTP Visual I

Step.5

When you click to box near “0” at “Bootloader Version” item, you will see “42”.

If you couldn’t see “42” or a “No Acknowledge from Slave!” is appeared,

There may be a connection problem sourced from PC port, or update tool.

Or you may forget to power ON.

2

C update tool to parallel port of PC.

2

C software update program.

Page 46

Step.6

After “42” is seen, Click “Erase Flash”

Step.7

Select the bin. file from near the “Load Bin”

Step.8

Click “Load Bin” and load the required bin. file.

Step.9

Unpick the I

Step.10

Power off and on again TV set to produce hard reset.

Step.11

Initialize the NVM from “Reset TV-set” item from service menu

2

C cable from Chasis

17.2 Analog Software Update Via UART

Step.1

Connect the serial cable from PC Com port to PL104 connector on 17PRG01-1 module

card.

Step.2

Connect the programming cable from SCART(PL103) on 17PRG01-1 module card to

SCART1 connector on TV chassis side.

Step.3

Run a RS232 terminal tool like Hyper Terminal.

Step.4

Following settings of the terminal tool are necessary:

Protocol: Xmodem

Port: COMx

Baud Rate: 115200

Data Bits: 8

Parity: none

Stop Bits: 1

Com. Control: none

Step.5

Load the bin file from “Browse” and Click “Send”

Step.6

Power off and on again TV set to produce hard reset.

18 BLOCK DIAGRAMS

18.1 General Block Diagram

Page 47

Page 48

18.2 Power Management

18.3 DRX (IF Demodulator) Block Diagram

Page 49

18.4 VCT Pro

18.4.1 General Block Diagram

Page 50

Page 51

18.4.2 MSP Block Diagram

18.4.3 Video Processor of VCT 7wxyP Block Diagram

Page 52

Page 53

5V_TUNER

ACTIVE_ANT.

ACTIVE_ANT.

SCLK_TUNER

SCL_5V_IC

R100

3k3

PTC RES

S117

AGC 1

VT 2

C100

AS 3

SCL 4

SDA 5

NC 6

S120

TU100

VS 7

38.9MHz_TVTUN

NC/ADC 8

VST 9

IF2/GND 10

IF1 11

SHEET3

N.C.

SHORT

10n

50V

39p

C102

50V

39p

C103

R101

3k3

PTC RES

R102

4k7

S103

1 2Y1

2 2Y0

R103

R152

L102

10u

VCC_33V

4R7

R153

4R7

C109

10V

100n

C110

16V

12V_IF

C113

1u

25V

100n

25V

12V_IF

5V_TUNER

R112

R113

S112

R114

100R

47k

Q101 Q102

BF799 BF799

R115

47R

47k

470R

R116

47u

C112

50V

1n

C114

50V

C115

DIG_IF+

DIG_IF-

50V

1n

1n

C116

S113

S114

150R

R117

150R

R118

R119

150R

R120

150R

VCC_8V_VIDEO

S104

C101

10n

N.C.

16V

R104

5k1

N.C.

10V

100n

L101

BLM21A601S

C106

C105

100n

R108

5k1

16V

R105

5k1

S105

16V

S106

R106

100R

R107

100R

16V

1u

C104

4k7

1u

L100

5VL

VCC_5V

C107

5V_TUNER

3u3

50V

R109

1k

S122

S123

VCC_5V

5VL

12V_IF

VCC_3V3 3V3_DRX

S115

R121

100R

R122

47R

R124

470R

S116

R125

IN11

IN22

47k

47k

R126

Z100

X6966M

GND

50V

1n

C119

OUT1 4

OUT2 5

3

S124

S125

S127

DRX POWER SUPPLY

5V_DRX

L107

10u

L105

10u

5V_DRX

5V_DRX

47u

16V

47u

16V

C120

L108

10u

L110

330R_100MHZ_3A

10V

100n

C121

C123

10V

100n

C122

10V

100n

C124

10V

100n

C125

L109

600R_100MHZ_200mA

5V_DRX

L111

C126

Q105

Q106

BC857B

ACTIVE_ANT.

PTC RES

R133

3k3

R134

1R

5V_TUNER

IC101

S107

Q103

BC848B

R129

330R

1

2

34

6

5

S126

FDC642P

R130

10k

R127

R123

C117

100n

10V

10k

C118

100n

10V

antenna_control

5V_TUNER

16VCC

5V_TUNER

152Z

Q104

BC848B

S121

10k

R128

10k

shortcir.

shortcir.

R131

R132

3k3

6k8

FOR THE USE OF EXTERNAL CLOCK

C124,C134 IS 1NF [30012581]

X100 AND C123 IS REMOVED

5V_DRX

DRX_CLK

SHEET3 VCTP PIN80

1 AVSS_ADC

2 AVDD_ADC

3 ANATSTX

4 ANATSTY

5 AVDD_FE8

10V

100n

6 AVSS_FE8

7 AVSS_FE401

8 IFINX

9 AVDD_FE40

10V

100n

C127

10 IFINY

11 AVSS_FE402

10V

100n

C128

L112

R135

1k2

C129

50V

1n

27p

50V

C131

20.25Mhz

10V

100n

C130

43VREF

44SGND

12 AVDD_SYN

13 AVSS_SYN

3V3_DRX

27p

50V

C132

X100

L113

C133

40DVSS_ADC

41XTALIN

42XTALOUT

IC100

DRX3960A

14 SHIELD

15 TEST0

16 TEST1

6k2

R136

3V3_DRX

10u

10V

100n

38PORT5

39DVDD_ADC

17 TEST2

18 CVBS

S118

R138

37ADR_SEL

19 REF_SW

S119

3V3_DRX

QSS

R137

100R

6k2

R139

36PORT4

20 SIF

L114

5V_DRX

6k2

6k2

R140

34PORT2

35PORT3

21 AVDD_DAC

22 AVSS_DAC

C134

100n

10V

VCC_8V_VIDEO

47R

R141

Q107

BC848B

1k

R142

SHEET 8

SW_ENABLE1

CHROMA_SW

AUDIO_MUX_SW

DMP/DVD_SWITCH

SHEET3

33TUNER_AGC

32PORT1

31PORT0

30DVSS_CAP

29DVSS

28DVDD

27DVDD_CAP

26SCL

25SDA

24RESETQ

23TEST_EN

SHOUL BE CONNECTED TO DRX GND

C135

10u

16V

R143

75R

L115

R144

3V3_DRX

6k2

R145

3V3_DRX

6k2

C137

C136

33p

50V

50V

33p

C138

TUNER_CVBS_IN

5VL

1R

R146

6k2

R147

10V

100n

SHEET 3

C140

C141

C139

100n

10V

L116

R148

100R

R149

100R

3u3

50V

C142

33n

16V

SYNC_SW2

IDTV_YPbPr_SW

SHEET 3

3V3_DRX

10V

100n

C143

3V3_DRX

SCL_3V3_IC

SDA_3V3_IC

SHEET 3,5,6

3V3_DRX

1k

R150

C144

100n

R151

33k

10V

RESET_IC

SHEET3

100n

Q108

BC848B

10V

AGC_DVB

S100

D100

1N4148

S102

S101

AGC_DVB

3 3Y1

43Z

74HCT4053

5 3Y0

6E

7 VEE

8 GND 9S3

141Z

131Y1

121Y0

11S1

10S2

SDATA_TUNER

C108

TV/DVB_SWITCH

BC848B

10V

100n

Q100

S111

SDA_5V_IC

R110

4k7

R111

FROM 100 to 150

VESTEL ELECTRONICS

5V_TUNER

33k

SYNC_SW2

17MB12-1 TUNER-DRX.1of13

Date

17.04.2007

Author

ISMAIL YILMAZLAR

SADIK SEHIT

Page 54

SC2_AUDIO_L_OUT

SC2_AUDIO_R_OUT

C201

1n

50V

R200

330R

50V1nC203

R201

330R

1n

50V

C200

330R

R204

330R

R205

C202

1n

50V

SC1_AUDIO_R_IN

SC1_AUDIO_L_IN

TO SHT3

75R

R202

R203

PL200

1

2

3

4

5

6

7

8

9

DSUB_VGA_CONN

10

11

12

13

14

15

10k

R305

R304

10k

C270

150p

50V

Y

SPDF

PB PR

JUMPER_SMD_0402

S206

C272

100n

16V

C268

SC2_AUDIO_R_OUT

1u

25V

R302

330R

1n

50V

C269

SC2_AUDIO_L_OUT

1u

25V

R303

330R

1n

50V

VCC_3V3

R306

10k

C275

100n

10V

R307

LINE_R_OUT

LINE_L_OUT

L226

JK202

710

14

C273

C274

10k

SC2_SVHS_C

47k

L227

Q214

BC848B

R313

150R

300R

R308

L228

1n

50V

L229

1n

50V

R309

VCC_8V

R310

LIN-R

LOUT-L

2

R312

11

8

5

100R

R311

330R

10k

C276

Q213

BC848B

Q212

BC848B

470p

50V1nC277

S207

LOUT-R

SW

LIN-L

50V

470p

LINE_R_OUT

LINE_L_OUT

CHROMA_SW_INV

DMP_DVD_VS_IN

DMP_DVD_CVBS_IN

DMP_DVD_AUDIO_L_IN

SELECTED_C

912

36

SUBW

1n

C278

FERRITE

1u

10R

R314

C279

R315

VCC_5V

10u

L233

10u

25V

PL206

VCC_5V_EXT

C288

75R

75R

75R

R317

R318

12

75R

R333

75R

R325

R332

75R

R328

75R

34

56

78

DMP/DVD_SWITC

910

DMP_DVD_AUDIO_R_

RESET_IC

1112

1314

1516

VCC_5V_EXT

1718

1920

DVB_TX

DVB_RX

2122

2324

2526

SDA_3V3_IC

SCL_3V3_IC SW_ENABL

1n

50V

L231

L232

1n

50V

R322

47R

L230

C280

27p

50V

27p

50V

27p

50V

C281

C282

C283

SPDIF

VCTP_SPDIF10R

75R

R319

R323

47R

75R

R320

R324

47R

75R

R321

5V

D228

BAV99

C284

C285

330R

R326

330R

R327

2728

2930

1n

50V

C286

PC_AUDIO_R_IN

PC_AUDIO_L_IN

1n

50V

C287

R329

47R

YPBPR_Y

R330

47R

R331

47R

D230

D229

BAV99

BAV99

FROM 200 to 400

VESTEL ELECTRONICS

17MB12-1 PERIPHERAL.2of13

Date

13.01.2006

Author

ISMAIL YILMAZLAR

SADIK SEHIT

R316

DMP_DVD_

DMP_DVD_

DMP_DVD_

I/O_1

IR_DMP/DVD

IRQ

YPBPR_PB

YPBPR_PR

VCC_5V

SC2_CVBS_IN

47R

R256

D222

47R

R257

75R

R259

47R

C235

27p

50V

C234

27p

50V

C236

HP_DETECT

HP_OUT_L

HP_OUT_R

HP_OUT_R

HP_OUT_L

VCC_5V_VIDEO

10V

100n

R260

75R

C5V6

D223

75R

R258

1n

50V

C238

TO SHT3 VCTP

TO SHT4

C239

C240

C237

BC858B

Q201

R264

47R

TO SHT3 SHT7[TO VIDEO SW]

VCC_8V

SHT3

VCTP_AOUT1R

VCTP_AOUT1L

75R

R261

330R

R268

R262

330R

1n

50V

C243

1n

50V

L217

L218

1n

50V

C242

27p

50V

C244

C245

BC848B

R270

150R

SC1_CVBS_IN

R265

47R

R266

47R

R267

47R

1n

50V

1n

1n

R269

47R

50V

50V

Q202

C247

C248

50V

C249

50V

1n

1n

R271

100R

R272

100R

1n

470R

150R

50V

R277

L219

R273

BC858B

Q204

R274

C250

1u

16V

R280

C5V6

D224

C5V6

D225

C5V6

D226

R275

47R

R278

47R

R276

47R

PC_AUDIO_R_IN

PC_AUDIO_L_IN

330R

R279

330R

L220

1k

C251

50V

C252

50V

1n

1n

18k

BC858B

Q203

R281

VOUT2

VOUT1

JK200

FAV_CVBS_IN

SVHS_Y

SVHS_C

FAV_AUDIO_R_IN

FAV_AUDIO_L_IN

R282

1k

BC858B

A

BC

R283

Q205

18k

BC858B

Q206

C253

1u

25V

C254

SC1_AUDIO_L_OUT

1u

25V

L223

31245

L221

L222

123

470R

R284

Q207

BC848B

150R

R285

CHROMA_SW

SC1_AUDIO_R_OUT

C257

R290

330R

1n

50V

C255

27p

50V

C256

TO SHT7

VCC_8V

SHT3

VCTP_AOUT2R

VCTP_AOUT2L

JK201

JACK-AK16

R293

330R

R286

150R

1n

50V

C258

1n

50V

R288

47R

75R

R287

R289

47R

R291

100R

R292

100R

TO SHT7

R233

3k3

R234

100R

C5V6

R236

32

11

R237

4VSS

5 SDA

47R

47R

SC1_G

TV_LINK_3V3

Q200

R241

31

R239

75R

2

K

D213

10

75R

R240

D212

C5V6

C223

R238

D211

C5V6_SOD123

TO SHT3

3NC36 SCL

2NC2

ST24LC21

7 VCLK

PC_VSYNC

5V_STBY

4k7

C224

27p

50V

30

1

A

9

C222

27p

50V

25V

10n

29

8

R242

R243

vctpprog.

1NC1

8 VCC

D214

DDC_5V

S203

C5V6

47R

47R

SC1_R

D217

R245

28

7

75R

IC200

SC2_SVHS_C

47R

D215

47R

75R

27

6

R244

D216

PL202

4

3

2

1

PL201

R246

R247

C225

27p

50V

C5V6

1

2

3

FAV_HP

C5V6

26

5

47R

R248

47R

R249

SC1_FB

VCC_5V

C226

C227

25

4

D218

D219

24

3

75R

R250

C5V6

S204

FAV VIDEO

R251

47R

1n

50V

L210

L211

1n

50V

C228

27p

50V

C233

50V

23

22

2

1

C229

27p

50V

D220

SC1_CVBS_OUT

PL204

1

2

3

4

5

6

7

8

D221

1n

C230

1n

C231

TO SHT7

C5V6

27p

R254

75R

R253

C5V6

75R

R252

C232

27p

50V

L212

L213

C5V6

R255

47R

50V

50V

SC2_PIN8

TO SHT3

3V3_STBY

SC2_AUDIO_L_IN

SC2_AUDIO_R_IN

C212

1n

50V

C204

1n

50V

L200

C205

1n

50V

L201

1n

50V

C206

L202

L203

1n

50V

C207

75R

75R

C209

R206

27p

C208

DDC_5V

VCC_5V

R207

47R

R208

1k

R209

1k

R210

47R

50V

C210

27p

PL203

50V

1n

C214

C211

1n

50V

50V

27p

3k3

R211

47R

R212

47R

R213

47R

50V

R214

D201

C213

1n

50V

L204

R215

BAV99

R216

42

21

330R

10k

C215

1n

50V

330R

R218

330R

R217

C216

1n

50V

L206

L205

L208

41

40

L209

20