Page 1

W90N745CD/W90N745CDG

32-BIT ARM7TDMI-BASED MCU

W90N745

16/32-bit ARM microcontroller

Product Data Sheet

Page 2

W90N745CD/W90N745CDG

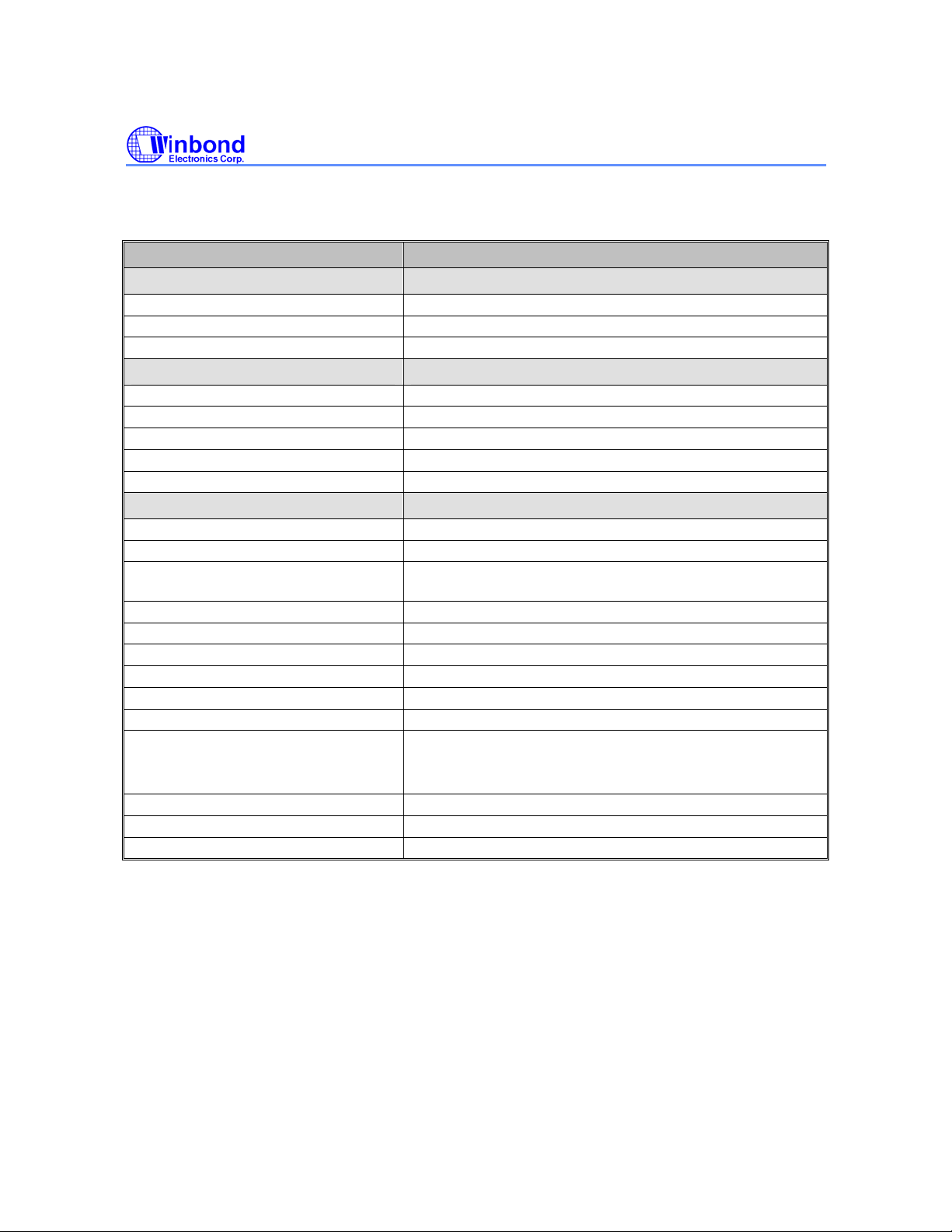

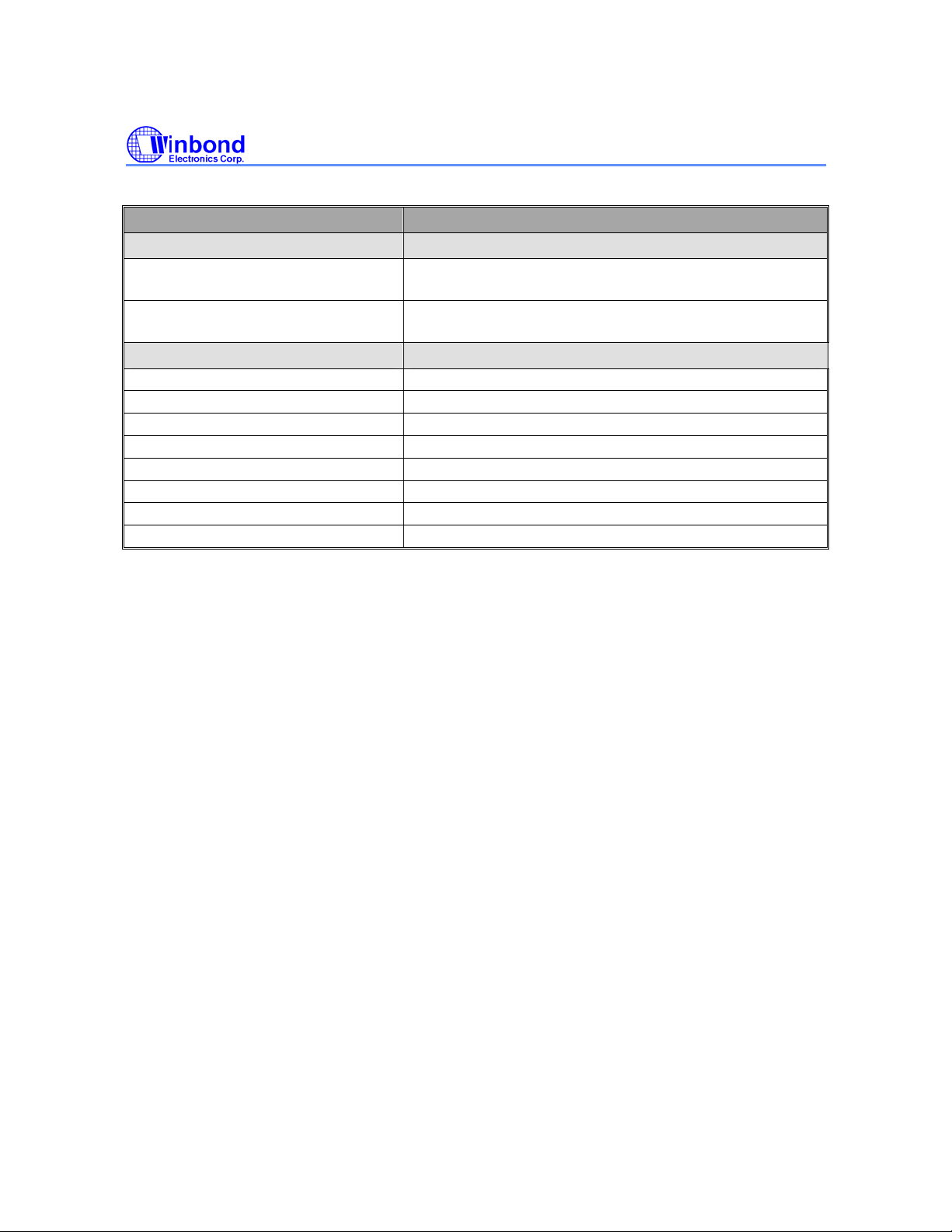

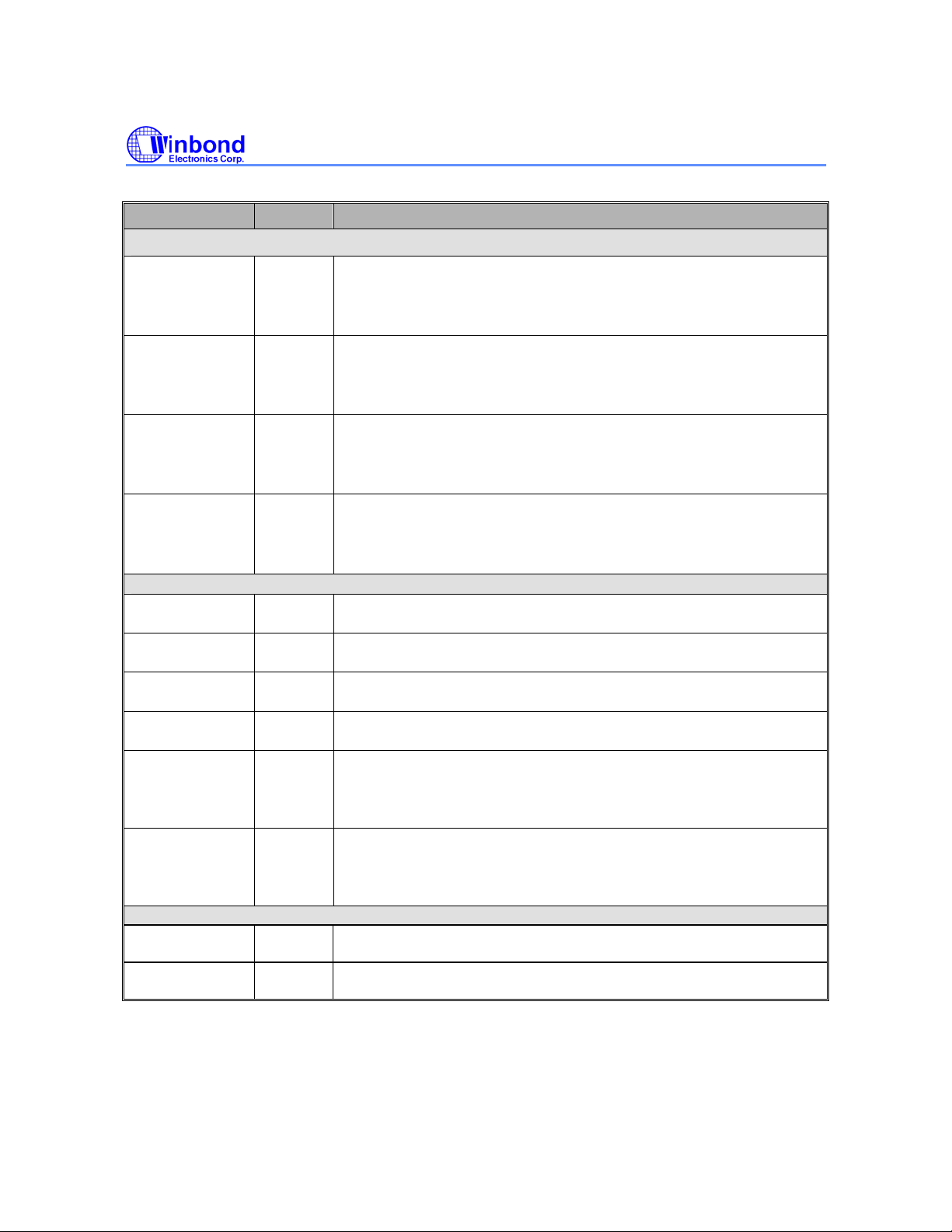

Revision History

REVISION DATE COMMENTS

A 2006/06/23 Draft

A1 2006/08/30 Add Electrical specification

A2 2006/09/22 Delete Chapter 6: BLOCK DIAGRAM

Publication Release Date: September 22, 2006

- I - Revision A2

Page 3

W90N745CD/W90N745CDG

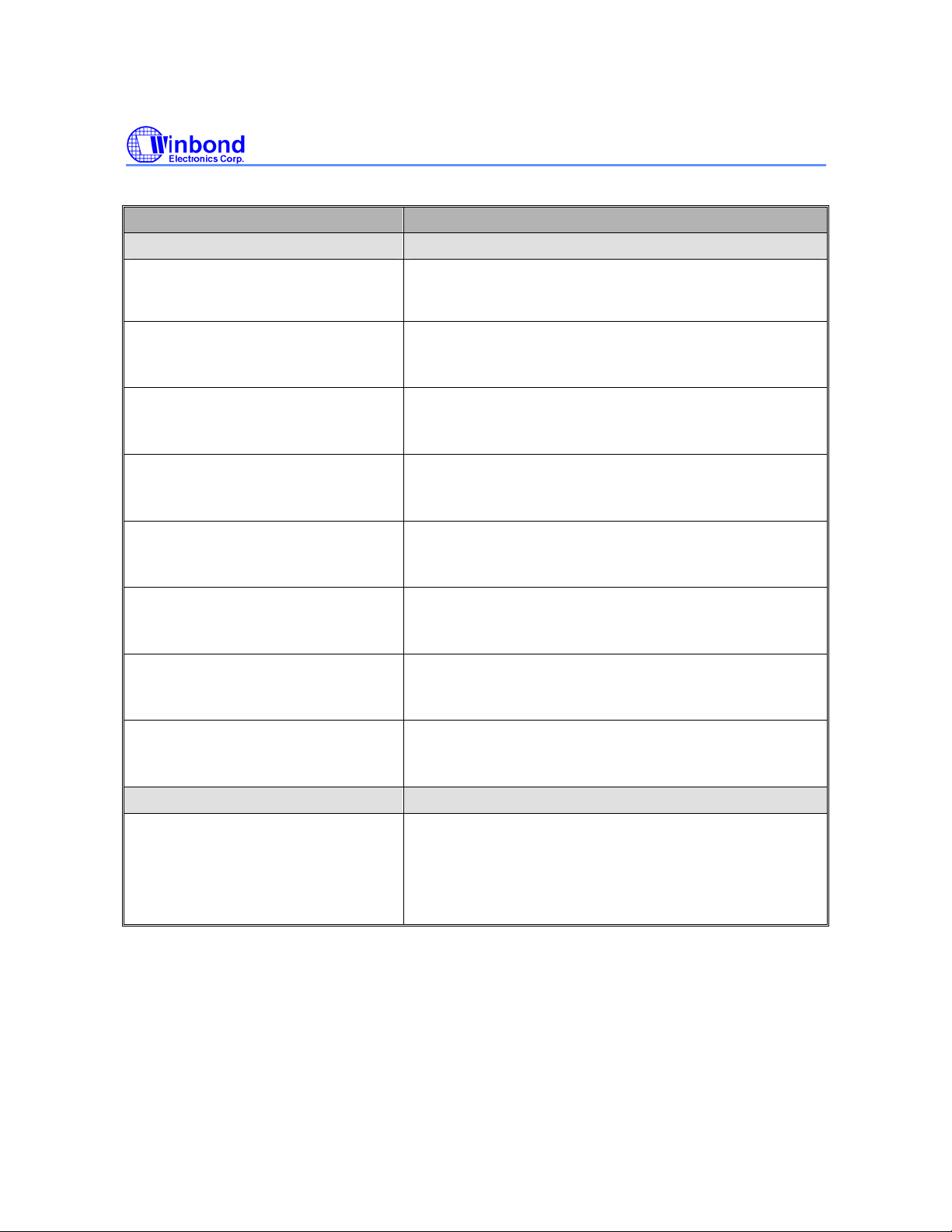

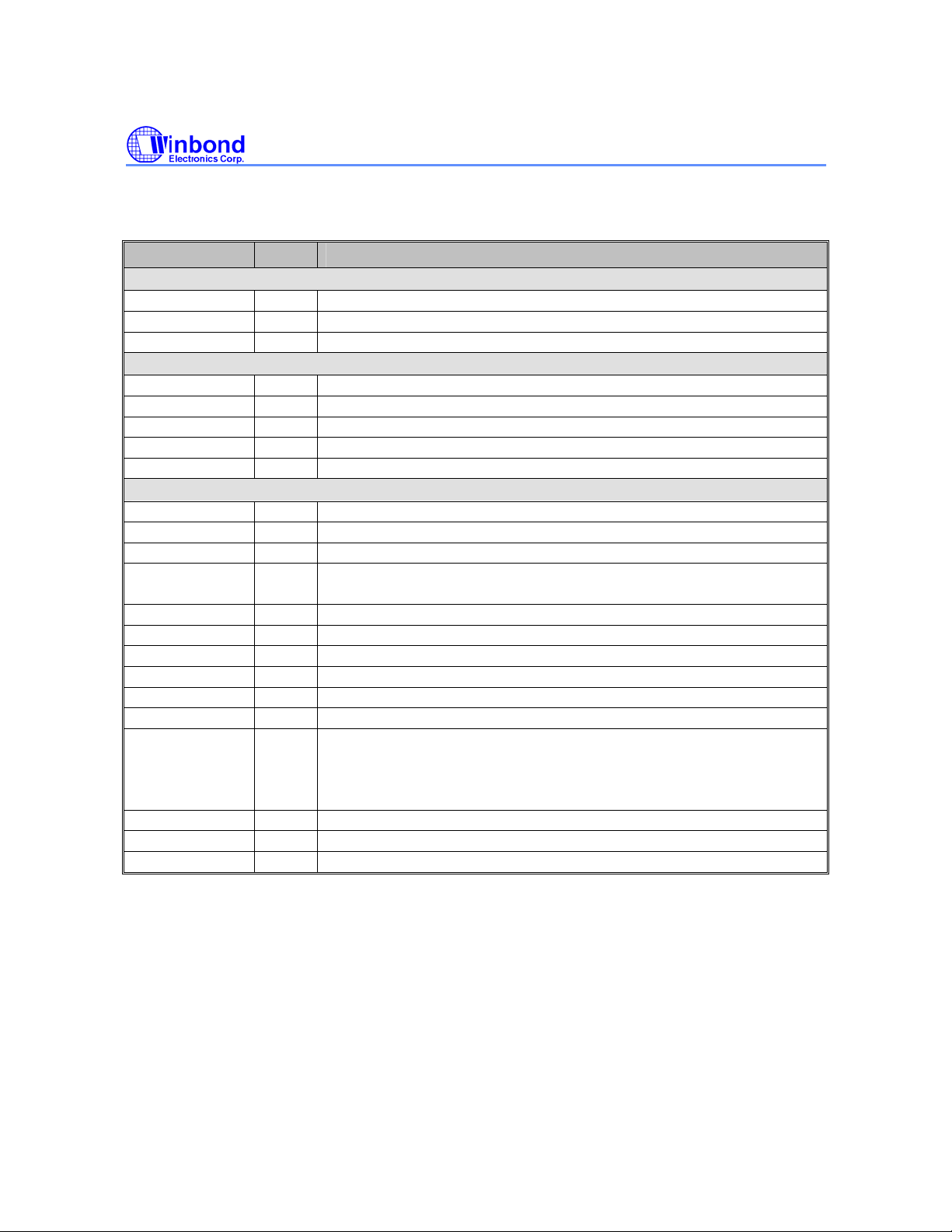

Table of Contents-

1. GENERAL DESCRIPTION ......................................................................................................... 1

2. FEATURES ................................................................................................................................. 2

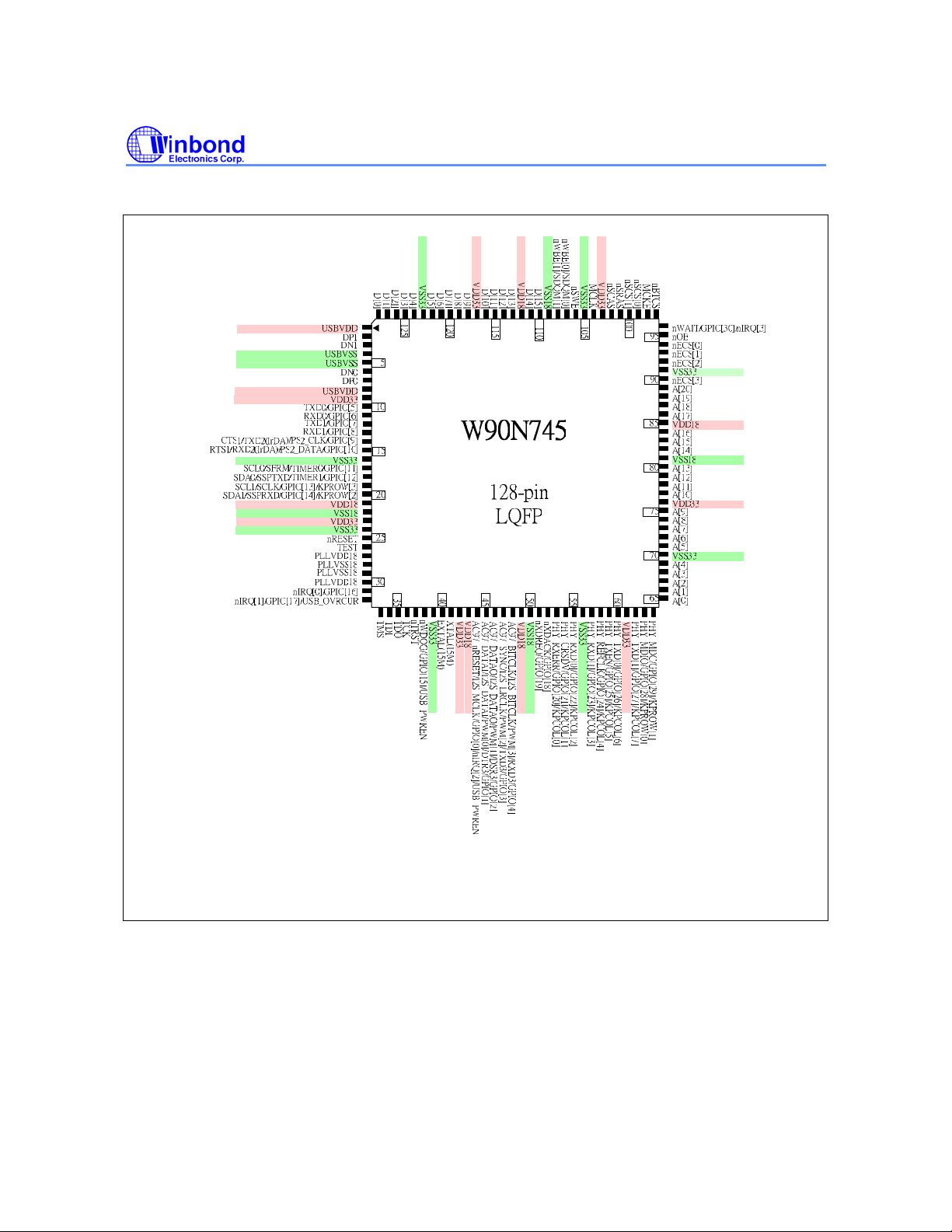

3. PIN DIAGRAM ............................................................................................................................ 7

4. PIN ASSIGNMENT ..................................................................................................................... 8

5. PIN DESCRIPTION................................................................................................................... 13

6. FUNCTIONAL DESCRIPTION ................................................................................................. 24

6.1 ARM7TDMI CPU CORE ............................................................................................... 24

6.2 System Manager........................................................................................................... 25

6.2.1 Overview ........................................................................................................................25

6.2.2 System Memory Map......................................................................................................25

6.2.3 Address Bus Generation ................................................................................................28

6.2.4 Data Bus Connection with External Memory ..................................................................28

6.2.5 Bus Arbitration................................................................................................................37

6.2.6 Power Management .......................................................................................................38

6.2.7 Power-On Setting ........................................................................................................... 41

6.2.8 System Manager Control Registers Map........................................................................41

6.3 External Bus Interface .................................................................................................. 56

6.3.1 EBI Overview..................................................................................................................56

6.3.2 SDRAM Controller ..........................................................................................................56

6.3.3 EBI Control Registers Map .............................................................................................60

6.4 Cache Controller........................................................................................................... 79

6.4.1 On-Chip RAM ................................................................................................................. 79

6.4.2 Non-Cacheable Area ......................................................................................................79

6.4.3 Instruction Cache............................................................................................................80

6.4.4 Data Cache ....................................................................................................................82

6.4.5 Write Buffer ....................................................................................................................84

6.4.6 Cache Control Registers Map.........................................................................................84

6.5 Ethernet MAC Controller............................................................................................... 92

6.5.1 EMC Functional Description ........................................................................................... 93

6.5.2 EMC Register Mapping ................................................................................................103

6.6 GDMA Controller ........................................................................................................ 158

6.6.1 GDMA Functional Description ......................................................................................158

6.6.2 GDMA Register Map ....................................................................................................159

6.7 USB Host Controller ................................................................................................... 168

6.7.1 USB Host Functional Description .................................................................................168

6.7.2 USB Host Controller Registers Map .............................................................................169

6.8 USB Device Controller................................................................................................ 192

6.8.1 USB Endpoints ............................................................................................................. 192

- II -

Page 4

W90N745CD/W90N745CDG

6.8.2 Standard Device Request.............................................................................................192

6.8.3 USB Device Register Description .................................................................................192

6.9 Audio Controller .......................................................................................................... 231

6.9.1 I²S Interface.................................................................................................................. 231

6.9.2 AC97 Interface .............................................................................................................232

6.9.3 Audio Controller Register Map......................................................................................235

6.10 Universal Asynchronous Receiver/Transmitter Controller ......................................... 254

6.10.1 UART0........................................................................................................................256

6.10.2 UART1........................................................................................................................256

6.10.3 UART2........................................................................................................................258

6.10.4 UART3........................................................................................................................260

6.10.5 General UART Controller ...........................................................................................261

6.10.6 High speed UART Controller ......................................................................................274

6.11 Timer/Watchdog Controller......................................................................................... 288

6.11.1 General Timer Controller ............................................................................................ 288

6.11.2 Watchdog Timer .........................................................................................................288

6.11.3 Timer Control Registers Map...................................................................................... 288

6.12 Advanced Interrupt Controller..................................................................................... 297

6.12.1 Interrupt Sources........................................................................................................298

6.12.2 AIC Registers Map .....................................................................................................301

6.13 General-Purpose Input/Output ................................................................................... 314

6.13.1 GPIO Register Description .........................................................................................316

6.13.2 GPIO Register Description .........................................................................................317

6.14 I2C Interface ................................................................................................................ 338

6.14.1 I2C Protocol ................................................................................................................339

6.14.2 I2C Serial Interface Control Registers Map .................................................................342

6.15 Universal Serial Interface............................................................................................ 349

6.15.1 USI Timing Diagram ...................................................................................................350

6.15.2 USI Registers Map .....................................................................................................351

6.16 PWM ........................................................................................................................... 358

6.16.1 PWM Double Buffering and Reload Automatically......................................................359

6.16.2 Modulate Duty Ratio ...................................................................................................359

6.16.3 Dead Zone Generator.................................................................................................360

6.16.4 PWM Timer Start Procedure ......................................................................................360

6.16.5 PWM Timer Stop Procedure.......................................................................................360

6.16.6 PWM Register Map ....................................................................................................361

6.17 Keypad Interface......................................................................................................... 371

6.17.1 Keypad Interface Register Map ..................................................................................372

6.17.2 Register Description ...................................................................................................373

Publication Release Date: September 22, 2006

- III - Revision A2

Page 5

W90N745CD/W90N745CDG

PS2 Host Interface Controller..................................................................................... 380

6.18

6.18.1 PS2 Host Controller Interface Register Map...............................................................381

6.18.2 Register Description ...................................................................................................382

7. ELECTRICAL SPECIFICATIONS........................................................................................... 386

7.1 Absolute Maximum Ratings ........................................................................................ 386

7.2 DC Specifications ....................................................................................................... 386

7.2.1 Digital DC Characteristics.............................................................................................386

7.2.2 USB Transceiver DC Characteristics............................................................................388

7.3 AC Specifications........................................................................................................ 389

7.3.1 EBI/SDRAM Interface AC Characteristics ....................................................................389

7.3.2 EBI/(ROM/SRAM/External I/O) AC Characteristics ...................................................... 390

7.3.3 USB Transceiver AC Characteristics............................................................................ 391

7.3.4 EMC RMII AC Characteristics ......................................................................................391

7.3.5 AC97/I2S Interface AC Characteristics.........................................................................393

7.3.6 I2C Interface AC Characteristics ...................................................................................395

7.3.7 USI Interface AC Characteristics..................................................................................396

7.3.8 PS2 Interface AC Characteristics ................................................................................. 397

8. ORDERING INFORMATION .................................................................................................. 399

9. PACKAGE SPECIFICATIONS................................................................................................ 400

10. APPENDIX A: W90N745 REGISTERS MAPPING TABLE .................................................... 401

- IV -

Page 6

W90N745CD/W90N745CDG

1. GENERAL DESCRIPTION

The W90N745 is built around an outstanding CPU core, the 16/32 ARM7TDMI RISC processor which

designed by Advanced RISC Machines, Ltd. It offers 4K-byte I-cache/SRAM and 4K-byte Dcache/SRAM, is a low power, general purpose integrated circuits. Its simple, elegant, and fully static

design is particularly suitable for cost sensitive and power sensitive applications.

One 100/10 Mbit MAC of Ethernet controller is built-in to reduce total system cost.

The W90N745 also provides one USB 1.1 host controller, one USB 1.1 device controller, one

AC97/I²S controller, one 2-channel GDMA, four independent UARTs, one watchdog timer, two 24-bit

timers with 8-bit pre-scale, up to 31 programmable I/O ports, PS2 keyboard controller and an

advanced interrupt controller. The external bus interface (EBI) controller provides for SDRAM,

ROM/SRAM, flash memory and I/O devices. The system manager includes an internal 32-bit system

bus arbiter and a PLL clock controller.

With a wide range of serial communication and Ethernet interfaces, the W90N745 is suitable for

communication gateways as well as many other general purpose applications.

Publication Release Date: September 22, 2006

- 1 - Revision A2

Page 7

W90N745CD/W90N745CDG

2. FEATURES

Architecture

• Fully 16/32-bit RISC architecture

• Little/Big-Endian mode supported

• Efficient and powerful ARM7TDMI core

• Cost-effective JTAG-based debug solution

External Bus Interface

• 8/16-bit external bus support for ROM/SRAM, flash memory, SDRAM and external I/Os

• Support for SDRAM

• Programmable access cycle (0-7 wait cycle)

• Four-word depth write buffer for SDRAM write data

• Cost-effective memory-to-peripheral DMA interface

Instruction and Data Cache

• Two-way, set-associative, 4K-byte I-cache and 4K-byte D-cache

• Support for LRU (Least Recently Used) protocol

• Cache can be configured as internal SRAM

• Support cache lock function

Ethernet MAC Controller

• DMA engine with burst mode

• MAC Tx/Rx buffers (256 bytes Tx, 256 bytes Rx)

• Data alignment logic

• Endian translation

• 100/10 Mbit per second operation

• Full compliance with IEEE standard 802.3

• RMII interface only

• Station Management Signaling

• On-chip CAM (up to 16 destination addresses)

• Full-duplex mode with PAUSE feature

• Long/short packet modes

• PAD generation

- 2 -

Page 8

W90N745CD/W90N745CDG

DMA Controller

• 2-channel general DMA for memory-to-memory data transfers without CPU intervention

• Initialed by a software or external DMA request

• Increments or decrements a source or destination address in 8-bit, 16-bit or 32-bit data transfers

• 4-data burst mode

UART

• Four UART (serial I/O) blocks with interrupt-based operation

• Support for 5-bit, 6-bit, 7-bit or 8-bit serial data transmit and receive

• Programmable baud rates

• 1, ½ or 2 stop bits

• Odd or even parity

• Break generation and detection

• Parity, overrun and framing error detection

• X16 clock mode

• UART1 supports Bluetooth, and UART2 supports IrDA1.0 SIR

Timers

• Two programmable 24-bit timers with 8-bit pre-scaler

• One programmable 20 bit with selectable additional 8-bit prescaler watchdog timer

• One-shot mode, periodical mode or toggle mode operation

Programmable I/Os

• 31 programmable I/O ports

• Pins individually configurable to input, output or I/O mode for dedicated signals

• I/O ports are configurable for multiple functions

Advanced Interrupt Controller

• 24 interrupt sources, including 4 external interrupt sources

• Programmable normal or fast interrupt mode (IRQ, FIQ)

• Programmable as either edge-triggered or level-sensitive for 4 external interrupt sources

• Programmable as either low-active or high-active for 4 external interrupt sources

• Priority methodology is encoded to allow for interrupt daisy-chaining

• Automatically mask out the lower priority interrupt during interrupt nesting

Publication Release Date: September 22, 2006

- 3 - Revision A2

Page 9

W90N745CD/W90N745CDG

USB Host Controller

• USB 1.1 compliant

• Compatible with Open HCI 1.0 specification

• Supports low-speed and full speed devices

• Build-in DMA for real time data transfer

• Two on-chip USB transceivers with one optionally shared with USB device controller

USB Device Controller

• USB 1.1 compliant

• Support four USB endpoints including one control endpoint and 3 configurable endpoints for rich

USB functions

Two PLLs

• The external clock can be multiplied by on-chip PLL to provide high frequency system clock

• The input frequency range is 3-30MHz; 15MHz is preferred.

• One PLL for both CPU and USB host/device controller

• One PLL for audio I²S 12.288/16.934MHz clock source

• Programmable clock frequency

4-Channel PWM

• Four 16-bit timers with PWM

• Two 8-bit pre-scalers & Two 4-bit dividers

• Programmable duty control of output waveform (PWM)

• Auto reload mode or one-shot pulse mode

• Dead-zone generator

2

C Master

I

2

• 2-channel I

• Compatible with Philips I

• Support multi master operation

• Clock stretching and wait state generation

• Provide multi-byte transmit operation, up to 4 bytes can be transmitted in a single transfer

• Software programmable acknowledge bit

• Arbitration lost interrupt, with automatic transfer cancellation

C

2

C standard, support master mode only

• Start/Stop/Repeated Start/Acknowledge generation

• Start/Stop/Repeated Start detection

• Bus busy detection

- 4 -

Page 10

W90N745CD/W90N745CDG

• Supports 7 bit addressing mode

2

• Software mode I

Universal Serial Interface (USI)

• 1-channel USI

• Support USI (Microwire/SPI) master mode

• Full duplex synchronous serial data transfer

• Variable length of transfer word up to 32 bits

• Provide burst mode operation, transmit/receive can be executed up to four times in one transfer

• MSB or LSB first data transfer

• Rx and Tx on both rising or falling edge of serial clock independently

• Two slave/device select lines

• Fully static synchronous design with one clock domain

2-Channel AC97/I²S Audio Codec Host Interface

C

• AHB master port and an AHB slave port are offered in audio controller.

• Always 8-beat incrementing burst

• Always bus lock when 8-beat incrementing burst

• When reach middle and end address of destination address, a DMA_IRQ is requested to CPU

automatically

KeyPad Scan Interface

• Scan up to 16 rows by 8 columns with an external 4 to 16 decoder and 4x8 array without auxiliary

component

• Programmable debounce time

• One or two keys scan with interrupt and three keys reset function.

• Wakeup CPU from IDEL/Power Down mode

PS2 Host Interface

• APB slave consisted of PS2 protocol.

• Connect IBM keyboard or bar-code reader through PS2 interface.

• Provide hardware scan code to ASCII translation

Publication Release Date: September 22, 2006

- 5 - Revision A2

Page 11

W90N745CD/W90N745CDG

Power management

• Programmable clock enables for individual peripheral

• IDLE mode to halt ARM core and keep peripheral working

• Power-Down mode to stop all clocks included external crystal oscillator.

• Exit IDLE by all interrupts

y Exit Power-Down by keypad,USB device and external interrupts

Operation Voltage Range

• 3.0 ~ 3.6 V for IO buffer

• 1.62 ~ 1.98 V for core logic

Operation Temperature Range

• TBD

Operating Frequency

• Up to 80 MHz

Package Type

• 128-pin LQFP

- 6 -

Page 12

3. PIN DIAGRAM

W90N745CD/W90N745CDG

Figure 3.1 Pin Diagram

Publication Release Date: September 22, 2006

- 7 - Revision A2

Page 13

W90N745CD/W90N745CDG

4. PIN ASSIGNMENT

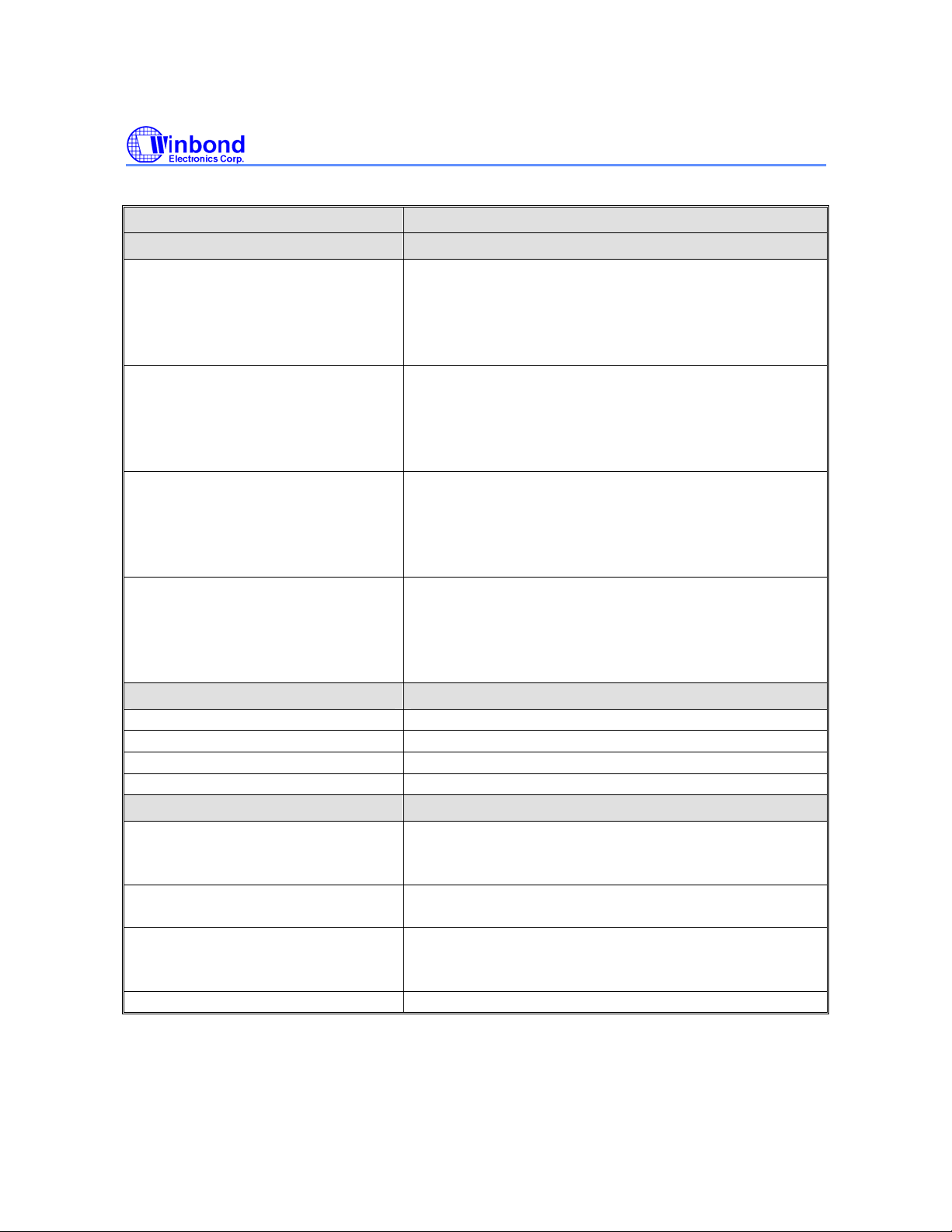

Table 4.1 W90N745 Pins Assignment

PIN NAME 128-PIN LQFP

Clock & Reset ( 3 pins )

EXTAL (15M) 40

XTAL (15M) 41

nRESET 25

JTAG Interface ( 5 pins )

TMS 33

TDI 34

TDO 35

TCK 36

nTRST 37

External Bus Interface ( 53 pins )

A [20:0] 89-86,84-82,80-77,75-71,69-65

D [15:0] 110-111,113-116,118-122,124-128

nWBE [1;0] /

SDQM [1:0]

nSCS [1:0] 100,99

nSRAS 101

nSCAS 102

MCKE 98

nSWE 106

MCLK 104

nWAIT /

GPIO [30] /

nIRQ [3]

nBTCS 97

nECS [3:0] 90,92-94

nOE 95

108,107

96

- 8 -

Page 14

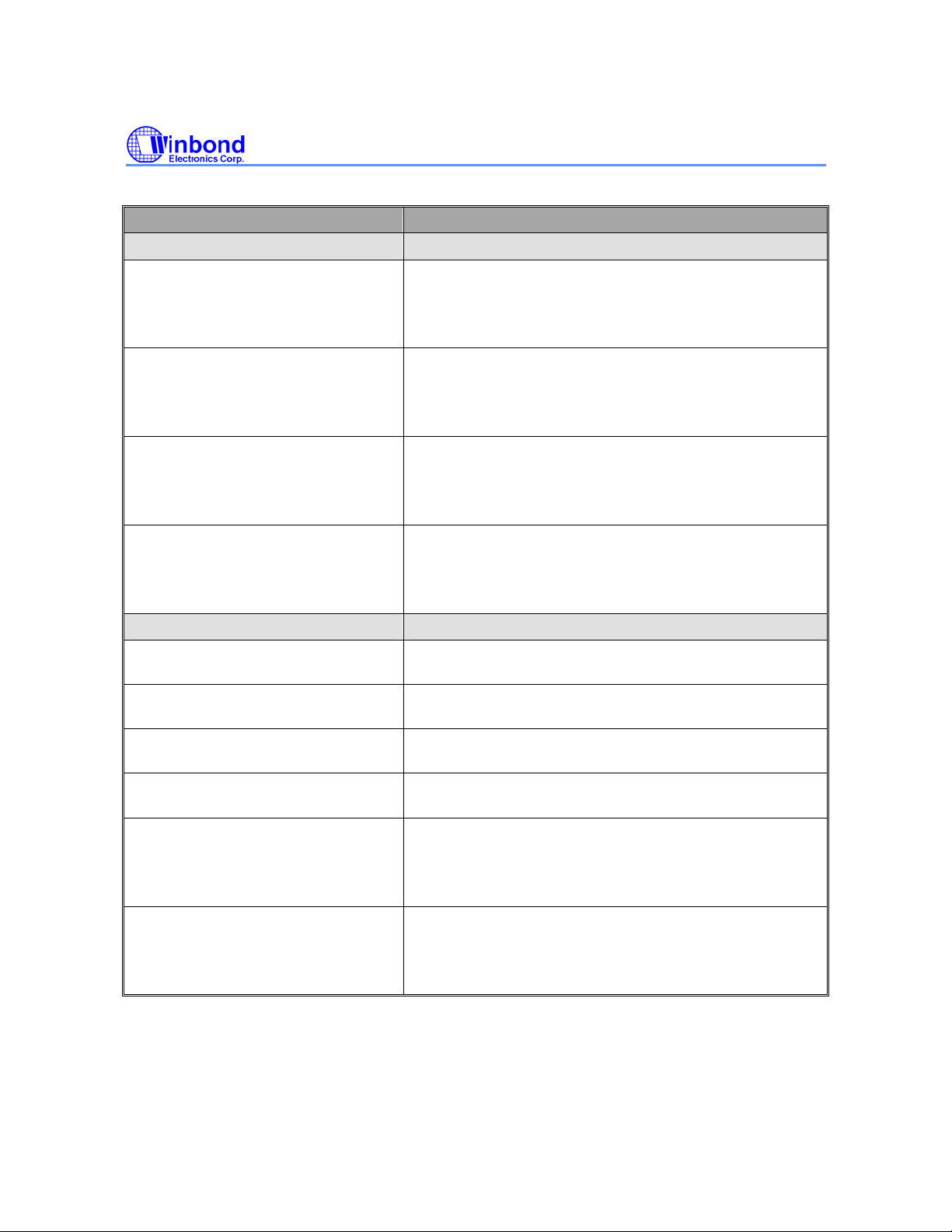

W90N745CD/W90N745CDG

Table 4.1 W90N745 Pins Assignment, continued

PIN NAME 128-PIN LQFP

Ethernet Interface ( 10 pins )

PHY_MDC /

GPIO [29] /

KPROW [1]

PHY_MDIO /

GPIO [28] /

KPROW [0]

PHY_TXD [1:0] /

GPIO [27:26] /

KPCOL [7:6]

PHY_TXEN /

GPIO [25] /

KPCOL [5]

PHY_REFCLK /

GPIO [24] /

KPCOL [4]

PHY_RXD [1:0] /

GPIO [23:22] /

KPCOL [3:2]

PHY_CRSDV /

GPIO [21] /

KPCOL [1]

PHY_RXERR /

GPIO [20] /

KPCOL [0]

AC97/I²S/PWM/UART3

AC97_nRESET /

I²S_MCLK /

GPIO [0] /

nIRQ [2] /

USB_PWREN

64

63

62,60

59

58

57,55

54

53

( 5 pins )

44

Publication Release Date: September 22, 2006

- 9 - Revision A2

Page 15

W90N745CD/W90N745CDG

Table 4.1 W90N745 Pins Assignment, continued

PIN NAME 128-PIN LQFP

AC97/I²S/PWM/UART3

AC97_DATAI /

I²S_DATAI /

PWM [0] /

DTR3 /

GPIO [1]

AC97_DATAO /

I²S_DATAO /

PWM [1] /

DSR3 /

GPIO [2]

AC97_SYNC /

I²S_LRCLK /

PWM [2] /

TXD3 /

GPIO [3]

AC97_BITCLK /

I²S_BITCLK /

PWM [3] /

RXD3

GPIO [4]

USB Interface ( 4 pins )

DP0 7

DN 0 6

DP1 2

DN1 3

Miscellaneous ( 7 pins )

nIRQ [1] /

GPIO [17] /

USB_OVRCUR

nIRQ [0] /

GPIO [16]

nWDOG /

GPIO [15] /

USB_PWREN

TEST 26

( 5 pins )

45

46

47

48

32

31

38

- 10 -

Page 16

W90N745CD/W90N745CDG

Table 4.1 W90N745 Pins Assignment, continued

PIN NAME 128-PIN LQFP

I2C/USI(SPI/MW)

SCL0 /

SFRM /

TIMER0 /

GPIO [11]

SDA0 /

SSPTXD /

TIMER1 /

GPIO [12]

SCL1 /

SCLK /

GPIO [13] /

KPROW [3]

SDA1 /

SSPRXD /

GPIO [14] /

KPROW [2]

UART0/UART1/UART2/PS2 ( 6 pins )

TXD0 /

GPIO [5]

RXD0 /

GPIO [6]

TXD1 /

GPIO [7]

RXD1 /

GPIO [8]

CTS1 /

TXD2(IrDA) /

PS2_CLK /

GPIO [9]

RTS1 /

RXD2(IrDA) /

PS2_DATA /

GPIO [10]

( 4 pins )

17

18

19

20

10

11

12

13

14

15

Publication Release Date: September 22, 2006

- 11 - Revision A2

Page 17

W90N745CD/W90N745CDG

Table 4.1 W90N745 Pins Assignment, continued

PIN NAME 128-PIN LQFP

XDMA ( 2 pins )

nXDREQ /

GPIO [19] /

nXDACK /

GPIO [18] /

Power/Ground ( 36 pins )

VDD18 21,43,49,85,112

VSS18 22,50,81,109

VDD33 9,23,42,61,76,103,117

VSS33 16,24,39,56,70,91,105,123

USBVDD 1,8

USBVSS 4,5

PLLVDD18 27,30

PLLVSS18 28,29

51

52

- 12 -

Page 18

W90N745CD/W90N745CDG

5. PIN DESCRIPTION

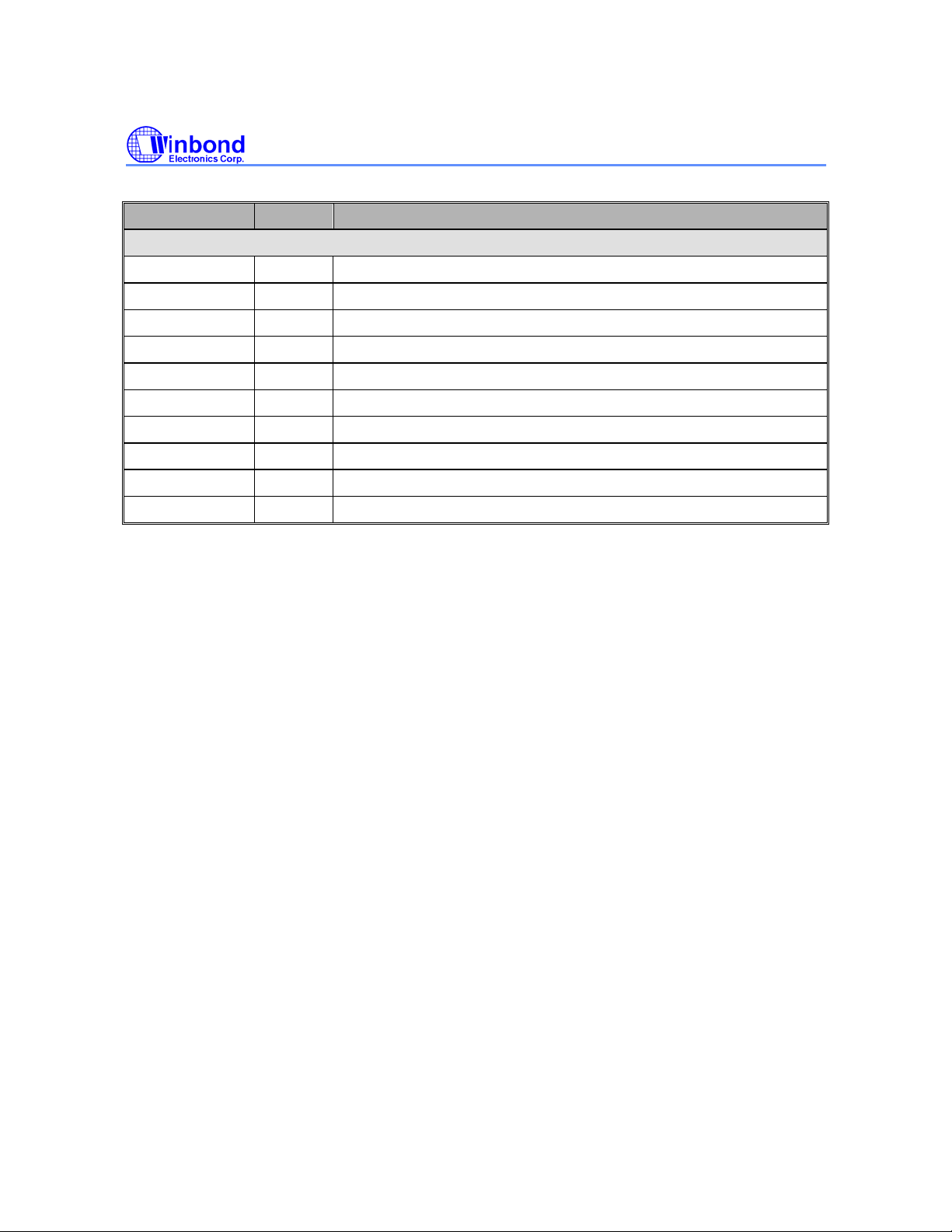

Table 5.1 W90N745 Pins Description

PIN NAME IO TYPE DESCRIPTION

Clock & Reset

EXTAL (15M) I 15MHz External Clock / Crystal Input

XTAL (15M) O 15MHz Crystal Output

nRESET IS System Reset, active-low

JTAG Interface

TMS IUS JTAG Test Mode Select, internal pull-up with 70K ohm

TDI IUS JTAG Test Data in, internal pull-up with 70K ohm

TDO O JTAG Test Data out

TCK IDS JTAG Test Clock, internal pull-down with 58K ohm

nTRST IUS JTAG Reset, active-low, internal pull-up with 70K ohm

External Bus Interface

A [20:18] O Address Bus (MSB) of external memory and IO devices.

A [17:0] IOS Address Bus of external memory and IO devices.

D [15:0] IOS Data Bus (LSB) of external memory and IO device.

nWBE [1:0] /

SDQM [1:0]

nSCS [1:0] O SDRAM chip select for two external banks, active-low.

nSRAS O Row Address Strobe for SDRAM, active-low.

nSCAS O Column Address Strobe for SDRAM, active-low.

MCKE O SDRAM Clock Enable, active-high

nSWE O SDRAM Write Enable, active-low

MCLK O System Master Clock Out, SDRAM clock, output with slew-rate control

nWAIT /

GPIO[30] /

nIRQ3

nBTCS O ROM/Flash Chip Select, active-low.

nECS [3:0] IO External I/O Chip Select, active-low.

nOE O ROM/Flash, External Memory Output Enable, active-low.

IOS

IUS

Write Byte Enable for specific device (nECS [1:0]).

Data Bus Mask signal for SDRAM (nSCS [1:0]), active-low.

External Wait, active-low. This pin indicates that the external devices need

more active cycle during access operation.

General Programmable In/Out Port GPIO[30]. If memory and IO devices in EBI

do not need wait request, it can be configured as GPIO[30] or nIRQ3.

Publication Release Date: September 22, 2006

- 13 - Revision A2

Page 19

W90N745CD/W90N745CDG

Table 5.1 W90N745 Pins Description, continued

PIN NAME IO TYPE DESCRIPTION

Ethernet Interface

PHY_MDC /

GPIO [29] /

KPROW [1]

PHY_MDIO /

GPIO [28] /

KPROW [0]

PHY_TXD [1:0] /

GPIO [27:26] /

KPCOL [7:6]

PHY_TXEN /

GPIO [25] /

KPCOL [5]

PHY_REFCLK /

GPIO [24] /

KPCOL [4]

PHY_RXD [1:0] /

GPIO [23:22] /

KPCOL [3:2]

PHY_CRSDV /

GPIO [21] /

KPCOL [1]

PHY_RXERR /

GPIO [20] /

KPCOL [0]

IOU

IO

IOU

IOU

IOS

IOS

IOS

IOS

RMII Management Data Clock for Ethernet. It is the reference clock of MDIO.

Each MDIO data will be latched at the rising edge of MDC clock.

General Programmable In/Out Port [29]

Keypad ROW[1] scan output.

RMII Management Data I/O for Ethernet. It is used to transfer RMII control and

status information between PHY and MAC.

General Programmable In/Out Port [28]

Keypad ROW[0] scan output.

2-bit Transmit Data bus for Ethernet.

General programmable In/Out Port [27:26]

Keypad column input [7:6], active low

PHY_TXEN shall be asserted synchronously with the first 2-bit of the preamble

and shall remain asserted while all di-bits to be transmitted are presented. Of

course, it is synchronized with PHY_REFCLK.

General Programmable In/Out Port [25]

Keypad column input [5], active low

Reference Clock. The clock shall be 50MHz +/- 50 ppm with minimum 35%

duty cycle at high or low state.

General Programmable In/Out port [24]

Keypad column input [4], active low

2-bit Receive Data bus for Ethernet.

General Programmable In/Out Port [23:22]

Keypad column input [3:2], active low

Carrier Sense / Receive Data Valid for Ethernet. The PHY_CRSDV shall be

asserted by PHY when the receive medium is non-idle. Loss of carrier shall

result in the de-assertion of PHY_CRSDV synchronous to the cycle of

PHY_REFCLK, and only on 2-bit receive data boundaries.

General Programmable In/Out port [21]

Keypad column input [1], active low

Receive Data Error for Ethernet. It indicates a data error detected by PHY.The

assertion should be lasted for longer than a period of PHY_REFCLK. When

PHY_RXERR is asserted, the MAC will report a CRC error.

General programmable In/Out port [20]

Keypad column input [0], active low

- 14 -

Page 20

W90N745CD/W90N745CDG

Table 5.1 W90N745 Pins Description, continued

PIN NAME IO TYPE DESCRIPTION

AC97/I²S/PWM/UART3

AC97_nRESET /

I²S_MCLK /

GPIO [0] /

nIRQ [2] /

USB_PWREN

AC97_DATAI /

I²S_DATAI /

PWM [0] /

DTR3 /

GPIO [1]

AC97_DATAO /

I

²S_DATAO /

PWM [1] /

DSR3 /

GPIO [2]

AC97_SYNC /

I²S_LRCLK /

PWM [2] /

TXD3 /

GPIO [3]

AC97_BITCLK /

I

²S_BITCLK /

PWM [3] /

RXD3 /

GPIO [4]

USB Interface

DP0 IO Differential Positive USB IO signal

DN0 IO Differential Negative USB IO signal

DP1 IO Differential Positive USB IO signal

DN1 IO Differential Negative USB IO signal

Miscellaneous

nIRQ [1:0] /

GPIO [17:16] /

USB_OVRCUR

nWDOG /

GPIO [15] /

USB_PWREN

TEST IDS This test pin must be short to ground or left unconnected

IOU

IOU

IOU

IOU

IOS

IOU

IOU

AC97 CODEC Host Interface RESET Output.

I²S CODEC Host Interface System Clock Output.

General Purpose In/Out port [0]

External interrupt request.

USB host power enable output

AC97 CODEC Host Interface Data Input.

I²S CODEC Host Interface Data Input.

PWM Channel 0 output.

Data Terminal Ready for UART3.

General Purpose In /Out port [1]

AC97 CODEC Host Interface Data Output.

²S CODEC Host Interface Data Output.

I

PWM Channel 1 output.

Data Set Ready for UART3.

General Purpose In/Out port [2]

AC97 CODEC Host Interface Synchronous Pulse Output.

I²S CODEC Host Interface Left/Right Channel Select Clock.

PWM Channel 2 output.

Transmit Data for UART3.

General Purpose In/Out port [3]

AC97 CODEC Host Interface Bit Clock Input.

I²S CODEC Host Interface Bit Clock.

PWM Channel 3 output.

Receive Data for UART3.

General Purpose In/Out port [4].

External Interrupt Request

General Purpose I/O

nIRQ1 is used as USB host over-current detection input

Watchdog Timer Timeout Flag and Keypad 3-keys reset output, active low

General Purpose In/output

USB host power switch enable output

Publication Release Date: September 22, 2006

- 15 - Revision A2

Page 21

W90N745CD/W90N745CDG

Table 5.1 W90N745 Pins Description, continued

PIN NAME IO TYPE DESCRIPTION

I2C/USI

SCL0 /

SFRM /

TIMER0 /

GPIO [11]

SDA0 /

SSPTXD /

TIMER1 /

GPIO [12]

SCL1 /

SCLK /

GPIO [13] /

KPROW [3]

SDA1 /

SSPRXD /

GPIO [14] /

KPROW [2]

UART0/UART1/UART2

TXD0 /

GPIO [5]

RXD0 /

GPIO [6]

TXD1 /

GPIO [7]

RXD1 /

GPIO [8]

CTS1/

TXD2(IrDA) /

PS2_CLK /

GPIO [9]

RTS1/

RXD2(IrDA) /

PS2_DATA /

GPIO [10]

XDMA

nXDREQ /

GPIO [19] /

nXDACK /

GPIO [18] /

IOU

IOU

IOU

IDU

IOU

IOU

IOU

IOU

IOU

IOU

IO

IO

I2C Serial Clock Line 0.

USI Serial Frame.

Timer0 time out output.

General Purpose In/Out port [11].

I2C Serial Data Line 0

USI Serial Transmit Data

Timer1 time out output

General Purpose In/Out port [12]

I2C Serial Clock Line 1

USI Serial Clock

General Purpose In/Out port [13]

Keypad row scan output [3]

I2C Serial Data Line 1

USI Serial Receive Data

General Purpose In/Out port [14]

Keypad scan output [2]

UART0 Transmit Data.

General Purpose In/Out [5]

UART0 Receive Data.

General Purpose In/Out [6]

UART1 Transmit Data.

General Purpose In/Out [7]

UART1 Receive Data.

General Purpose In/Out [8]

UART1 Clear To Send for Bluetooth application

UART2 Transmit Data supporting SIR IrDA.

PS2 Interface Clock Input/Output

General Purpose In/Out [9]

UART1 Request To Send for Bluetooth application

UART2 Receive Data supporting SIR IrDA.

PS2 Interface Bi-Directional Data Line.

General Purpose In/Out [10]

External DMA Request.

General Purpose In/Out [19]

External DMA Acknowledgement.

General Purpose In/Out [18]

- 16 -

Page 22

W90N745CD/W90N745CDG

Table 5.1 W90N745 Pins Description, continued

PIN NAME IO TYPE DESCRIPTION

Power/Ground

VDD18 P Core Logic power (1.8V)

VSS18 G Core Logic ground (0V)

VDD33 P IO Buffer power (3.3V)

VSS33 G IO Buffer ground (0V)

USBVDD P USB power (3.3V)

USBVSS G USB ground (0V)

DVDD18 P PLL Digital power (1.8V)

DVSS18 G PLL Digital ground (0V)

AVDD18 P PLL Analog power (1.8V)

AVSS18 G PLL Analog ground (0V)

Publication Release Date: September 22, 2006

- 17 - Revision A2

Page 23

W90N745CD/W90N745CDG

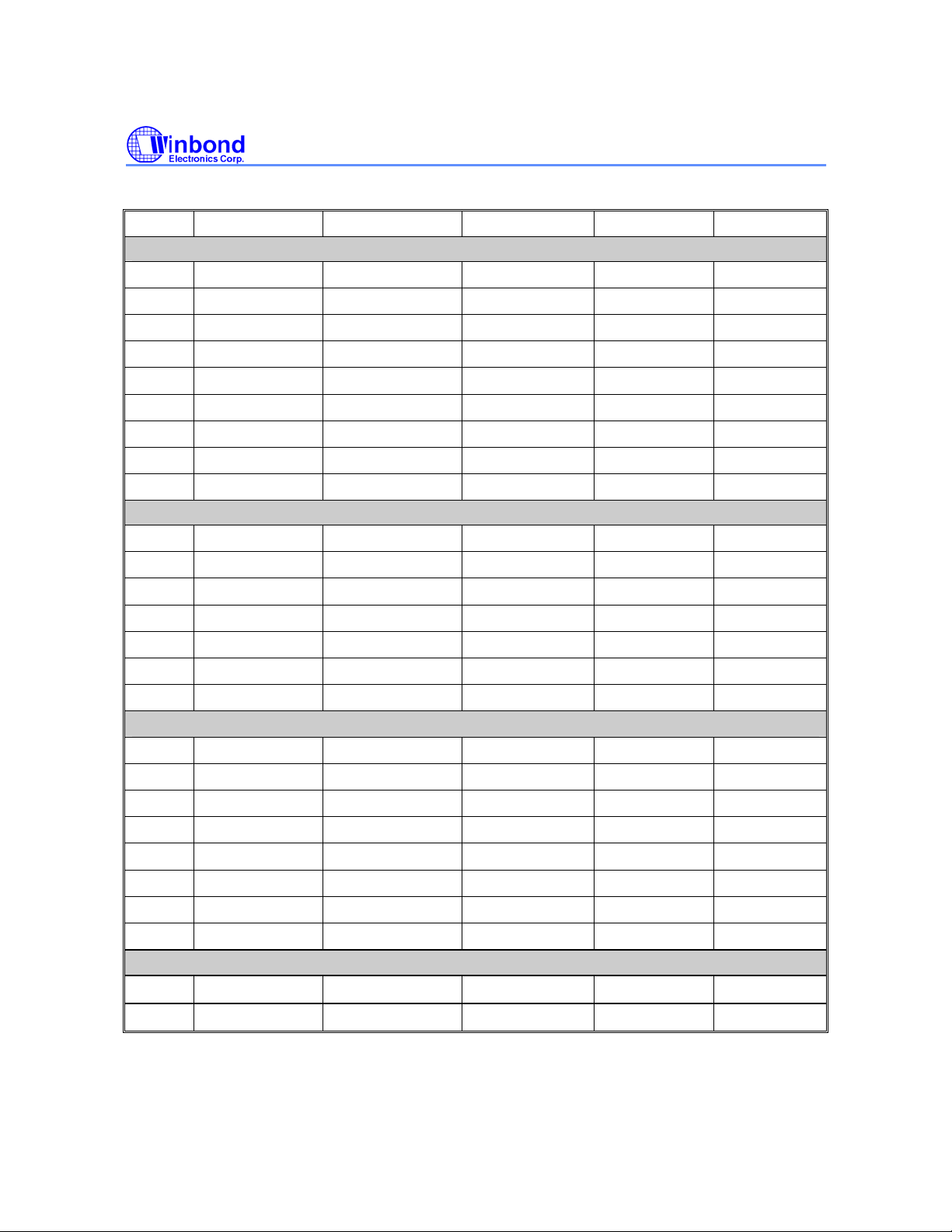

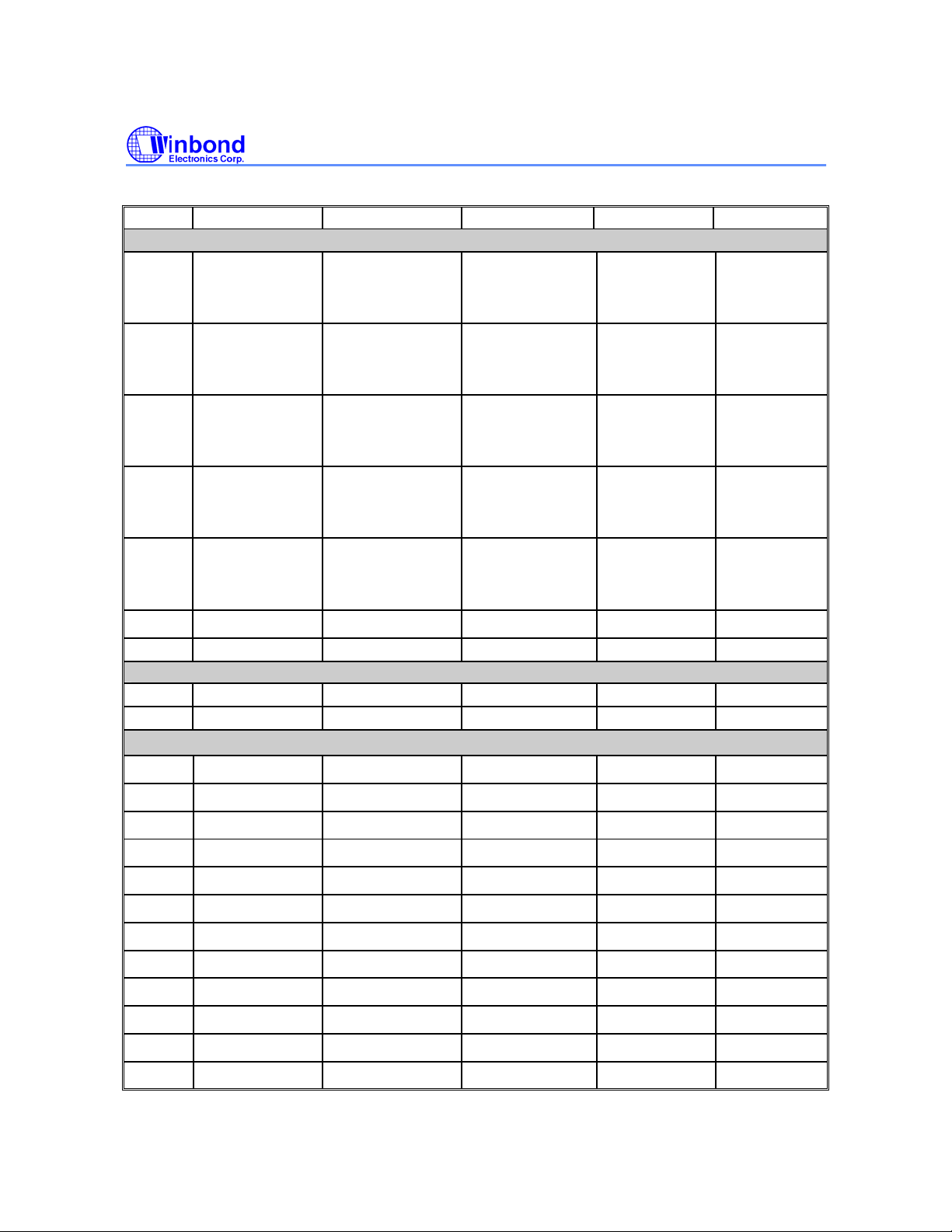

Table 5.2 W90N745 128-pin LQFP Multi-function List

PIN NO. DEFAULT FUNCTION0 FUNCTION1 FUNCTION2 FUNCTION3

USB1.1 Host/Device Interface

1 USBVDD

2 DP1

3 DN1

4 USBVSS

5 USBVSS

6 DN0

7 DP0

8 USBVDD

9 VDD33

10 GPIO[5]

11 GPIO[6]

12 GPIO[7]

13 GPIO[8]

14 GPIO[9]

15 GPIO[10]

16 VSS33

USBVDD - - -

DP1 - - -

DN1 - - -

USBVSS - - -

USBVSS - - -

DN0 - - -

DP0 - - -

USBVDD - - -

VDD33 - - -

UART[2:0]/PS2 Interface

GPIO[5] UART_TXD0 - -

GPIO[6] UART_RXD0 - -

GPIO[7] UART_TXD1 - -

GPIO[8] UART_RXD1 - -

GPIO[9] UART_TXD2 UART_CTS1 PS2_CLK

GPIO[10] UART_RXD2 UART_RTS1 PS2_DATA

VSS33 - - -

I2C/USI Interface

17 GPIO[11]

18 GPIO[12]

19 GPIO[13]

20 GPIO[14]

21 VDD18

22 VSS18

23 VDD33

24 VSS33

25 nRESET

26 TEST

GPIO[11]

GPIO[12]

GPIO[13]

GPIO[14]

VDD18 - - -

VSS18 - - -

VDD33 - - -

VSS33 - - -

System Reset & TEST

nRESET - - -

TEST - - -

I2C_SCL0

2

C_SDA0

I

I2C_SCL1

I2C_SDA1

SSP_FRAM TIMER0

SSP_TXD TIMER1

SSP_SCLK KPI_ROW[3]

SSP_RXD KPI_ROW[2]

- 18 -

Page 24

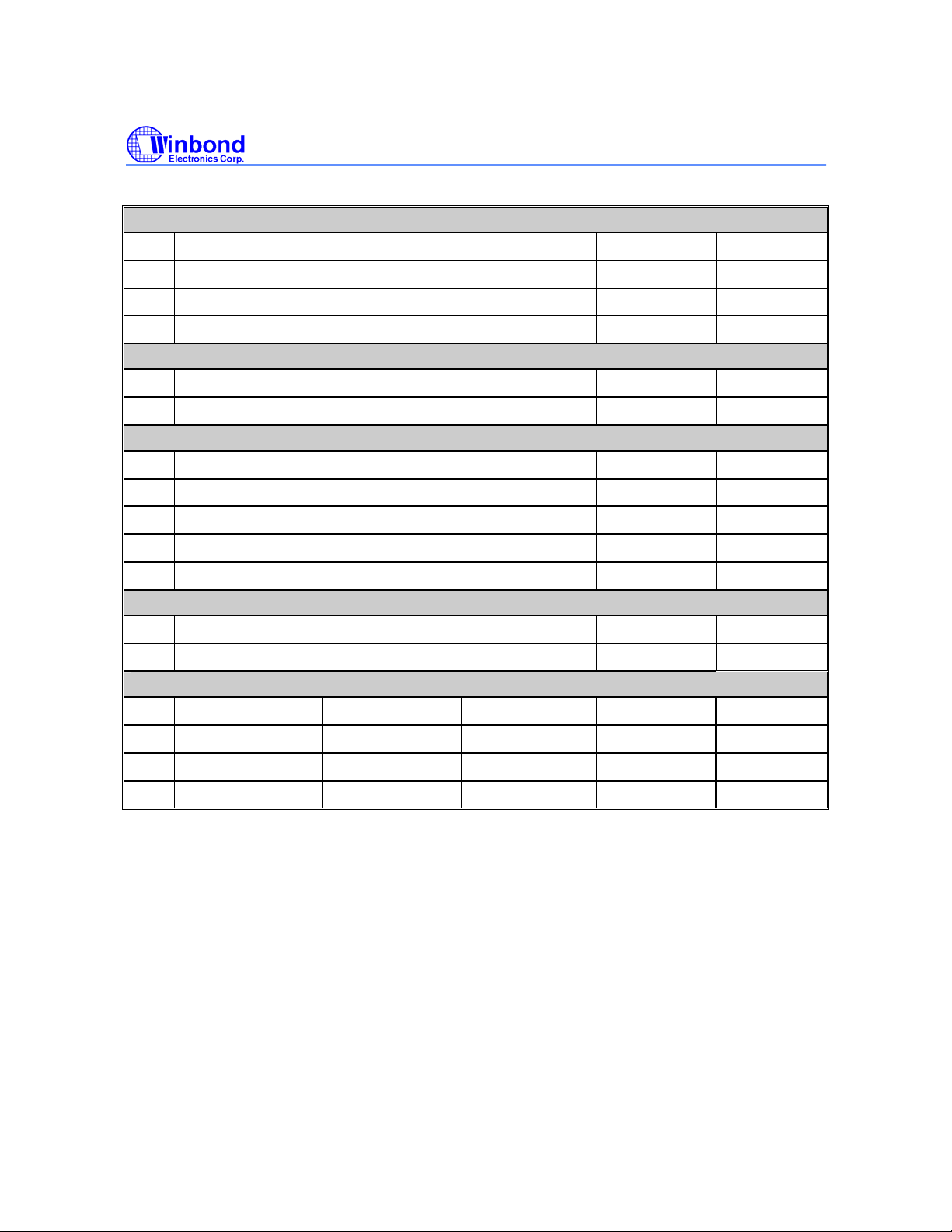

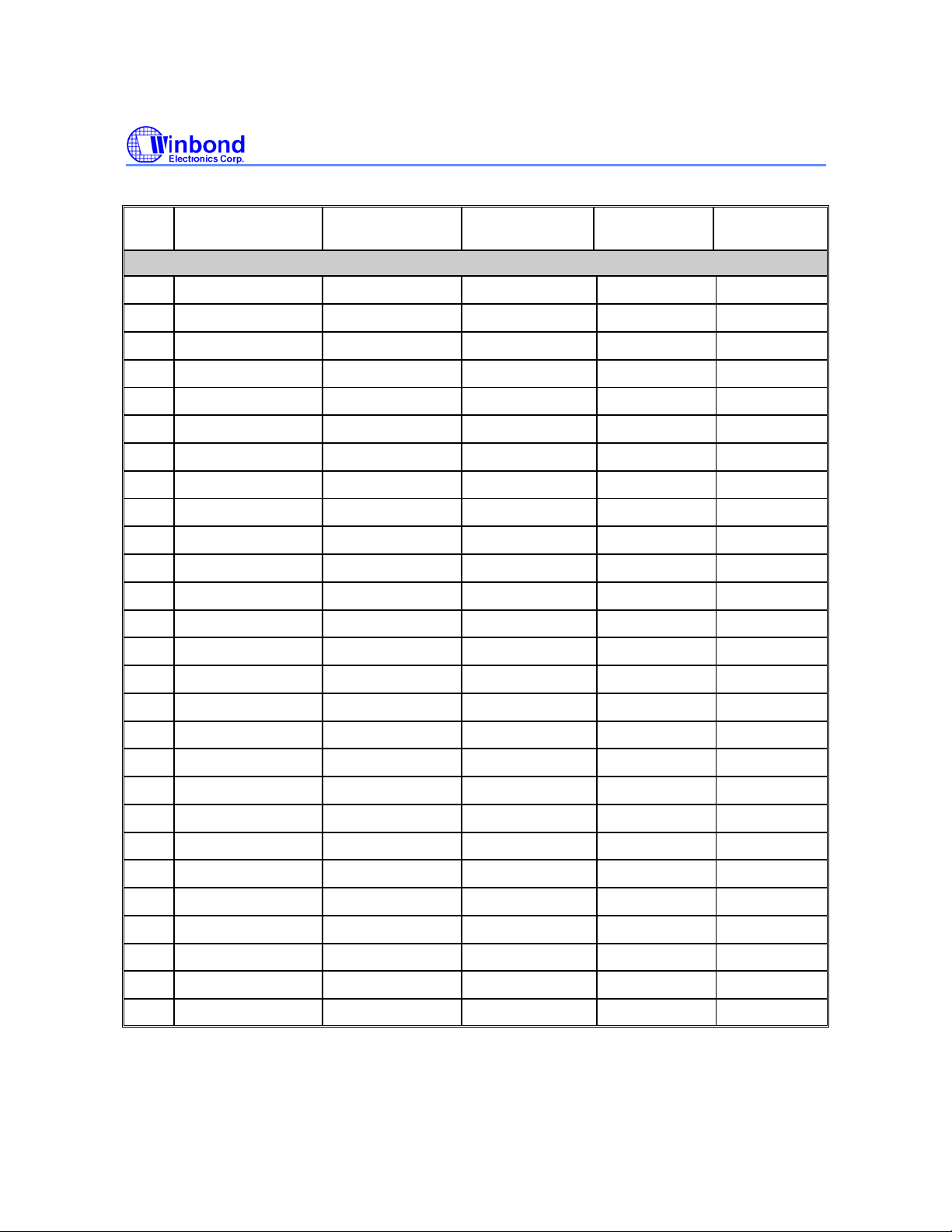

Table 5.2 W90N745 128-pin LQFP Multi-function List, continued

PLL Power/Ground

W90N745CD/W90N745CDG

27 PLL_VDD18

28 PLL_VSS18

29 PLL_VSS18

30 PLL_VDD18

31 GPIO[16]

32 GPIO[17]

33 TMS

34 TDI

35 TDO

36 TCK

37 nTRST

38 GPIO[15]

39 VSS33

PLL_VDD18 - - -

PLL_VSS18 - - PLL_VSS18 - - PLL_VDD18 - - -

External IRQ[1:0]/USB Over Current

GPIO[16] nIRQ [0] - -

GPIO[17] nIRQ [1] USB_OVRCUR -

JTAG Interface

TMS - - -

TDI - - -

TDO - - -

TCK - - -

nTRST - - -

WatchDog/USB Power Enable

GPIO[15] nWDOG USB_PWREN -

VSS33 - - -

System Clock

40 EXTAL(15M)

41 XTAL(15M)

42 VDD33

43 VDD18

EXTAL(15M) - - -

XTAL(15M) - - -

VDD33 - - -

VDD18 - - -

Publication Release Date: September 22, 2006

- 19 - Revision A2

Page 25

W90N745CD/W90N745CDG

Table 5.2 W90N745 128-pin LQFP Multi-function List, continued

PIN NO. DEFAULT FUNCTION0 FUNCTION1 FUNCTION2 FUNCTION3

AC97/I²S/PWM/UART3 Interface

AC97_nRESET

44 GPIO[0]

45 GPIO[1]

46 GPIO[2]

47 GPIO[3]

48 GPIO[4]

49 VDD18

50 VSS18

51 GPIO[19]

52 GPIO[18]

GPIO[0]

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[4]

VDD18

VSS18 - - -

XDMAREQ

GPIO[19] nXDREQ - -

GPIO[18] nXDACK - -

Ethernet RMII/KeyPad Interface

or

²SMCLK

I

AC97_DATAI

or

²SDATAI

I

AC97_DATAO

or

²SDATAO

I

AC97_SYNC

or

²SLRCLK

I

AC97_BITCLK

or

²SBITCLK

I

-

nIRQ [2] USB_PWREN

PWM0 UART_DTR3

PWM1 UART_DSR3

PWM2 UART_TXD3

PWM3 UART_RXD3

- -

53 GPIO[20]

54 GPIO[21]

55 GPIO[22]

56 VSS33

57 GPIO[23]

58 GPIO[24]

59 GPIO[25]

60 GPIO[26]

61 VDD33

62 GPIO[27]

63 GPIO[28]

64 GPIO[29]

GPIO[20] PHY_RXERR KPI_COL[0] -

GPIO[21] PHY_CRSDV KPI_COL[1] -

GPIO[22] PHY_RXD[0] KPI_COL[2] -

VSS33 - - -

GPIO[23] PHY_RXD[1] KPI_COL[3] -

GPIO[24] PHY_REFCLK KPI_COL[4] -

GPIO[25] PHY_TXEN KPI_COL[5] -

GPIO[26] PHY_TXD[0] KPI_COL[6] -

VDD33 - - -

GPIO[27] PHY_TXD[1] KPI_COL[7] -

GPIO[28] PHY_MDIO KPI_ROW[0]

GPIO[29] PHY_MDC KPI_ROW[1]

- 20 -

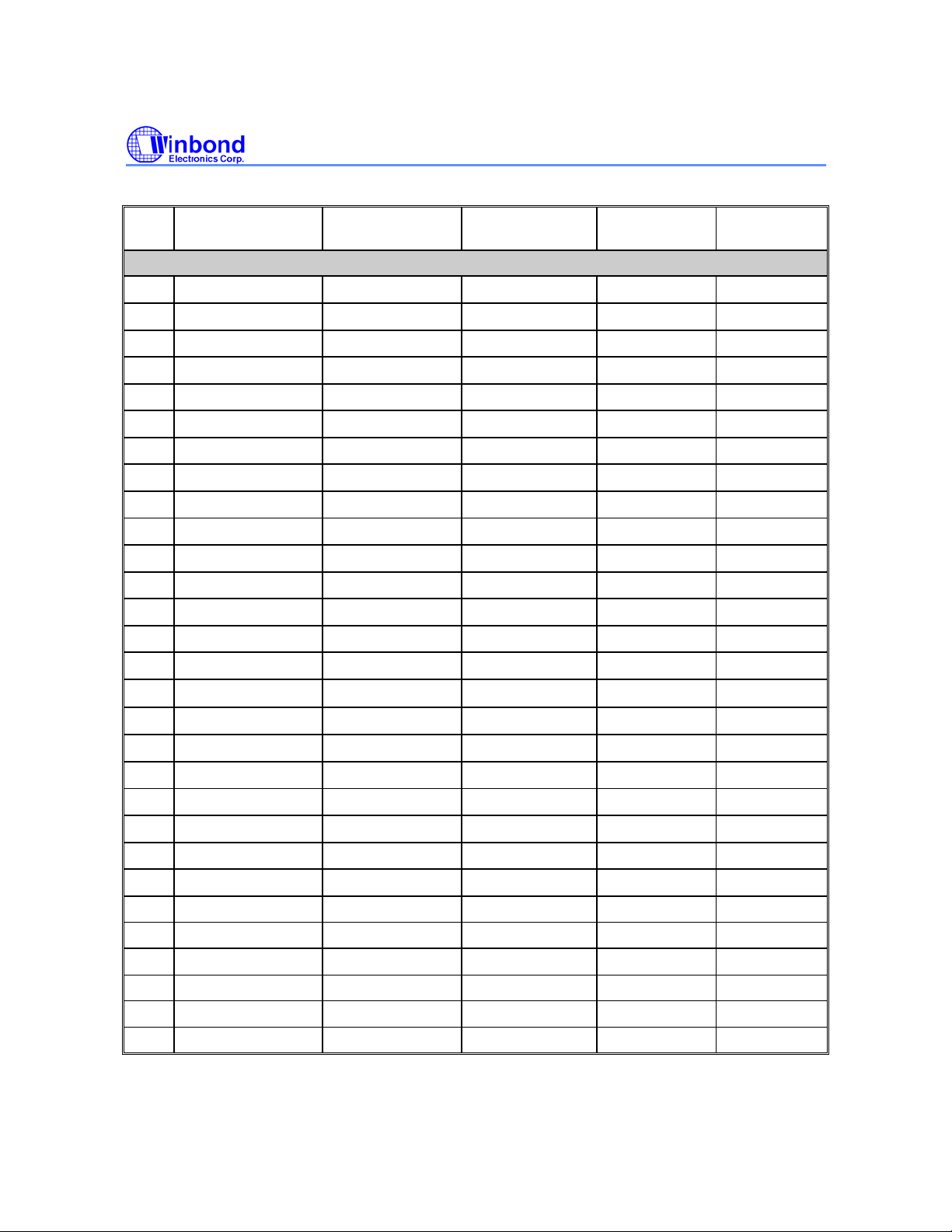

Page 26

Table 5.2 W90N745 128-pin LQFP Multi-function List, continued

W90N745CD/W90N745CDG

PIN

NO.

65 A[0]

66 A[1]

67 A[2]

68 A[3]

69 A[4]

70 VSS33

71 A[5]

72 A[6]

73 A[7]

74 A[8]

75 A[9]

76 VDD33

77 A[10]

78 A[11]

DEFAULT FUNCTION0 FUNCTION1 FUNCTION2 FUNCTION3

Memory Address/Data/Control

A[0] - - -

A[1] - - -

A[2] - - -

A[3] - - -

A[4] - - -

VSS33 - - -

A[5] - - -

A[6] - - -

A[7] - - -

A[8] - - -

A[9] - - -

VDD33 - - -

A[10] - - -

A[11] - - -

79 A[12]

80 A[13]

81 VSS18

82 A[14]

83 A[15]

84 A[16]

85 VDD18

86 A[17]

87 A[18]

88 A[19]

89 A[20]

90 nECS[3]

91 VSS33

A[12] - - -

A[13] - - -

VSS18 - - -

A[14] - - -

A[15] - - -

A[16] - - -

VDD18 - - -

A[17] - - -

A[18] - - -

A[19] - - -

A[20] - - -

nECS[3] - - -

VSS33 - - -

Publication Release Date: September 22, 2006

- 21 - Revision A2

Page 27

Table 5.2 W90N745 128-pin LQFP Multi-function List, continued

W90N745CD/W90N745CDG

PIN

NO.

92 nECS[2]

93 nECS[1]

94 nECS[0]

95 nOE

96 nWAIT

97 nBTCS

98 MCKE

99 nSCS[0]

100 nSCS[1]

101 nSRAS

102 nSCAS

103 VDD33

104 MCLK

105 VSS33

106 nSWE

DEFAULT FUNCTION0 FUNCTION1 FUNCTION2 FUNCTION3

Memory Address/Data/Control

nECS[2] - - -

nECS[1] - - -

nECS[0] - - -

nOE - - -

GPIO[30] nWAIT nIRQ [3] -

nBTCS - - -

MCKE - - -

nSCS[0] - - -

nSCS[1] - - -

nSRAS - - -

nSCAS - - -

VDD33 - - -

MCLK - - -

VSS33 - - -

nSWE - - -

107 nWBE/SDQM[0]

108 nWBE/SDQM[1]

109 VSS18

110 D[15]

111 D[14]

112 VDD18

113 D[13]

114 D[12]

115 D[11]

116 D[10]

117 VDD33

118 D[9]

119 D[8]

120 D[7]

nWBE or SDQM[0]

nWBE or SDQM[1]

VSS18 - - -

D[15] - - -

D[14] - - -

VDD18 - - -

D[13] - - -

D[12] - - -

D[11] - - -

D[10] - - -

VDD33 - - -

D[9] - - -

D[8] - - -

D[7] - - -

- 22 -

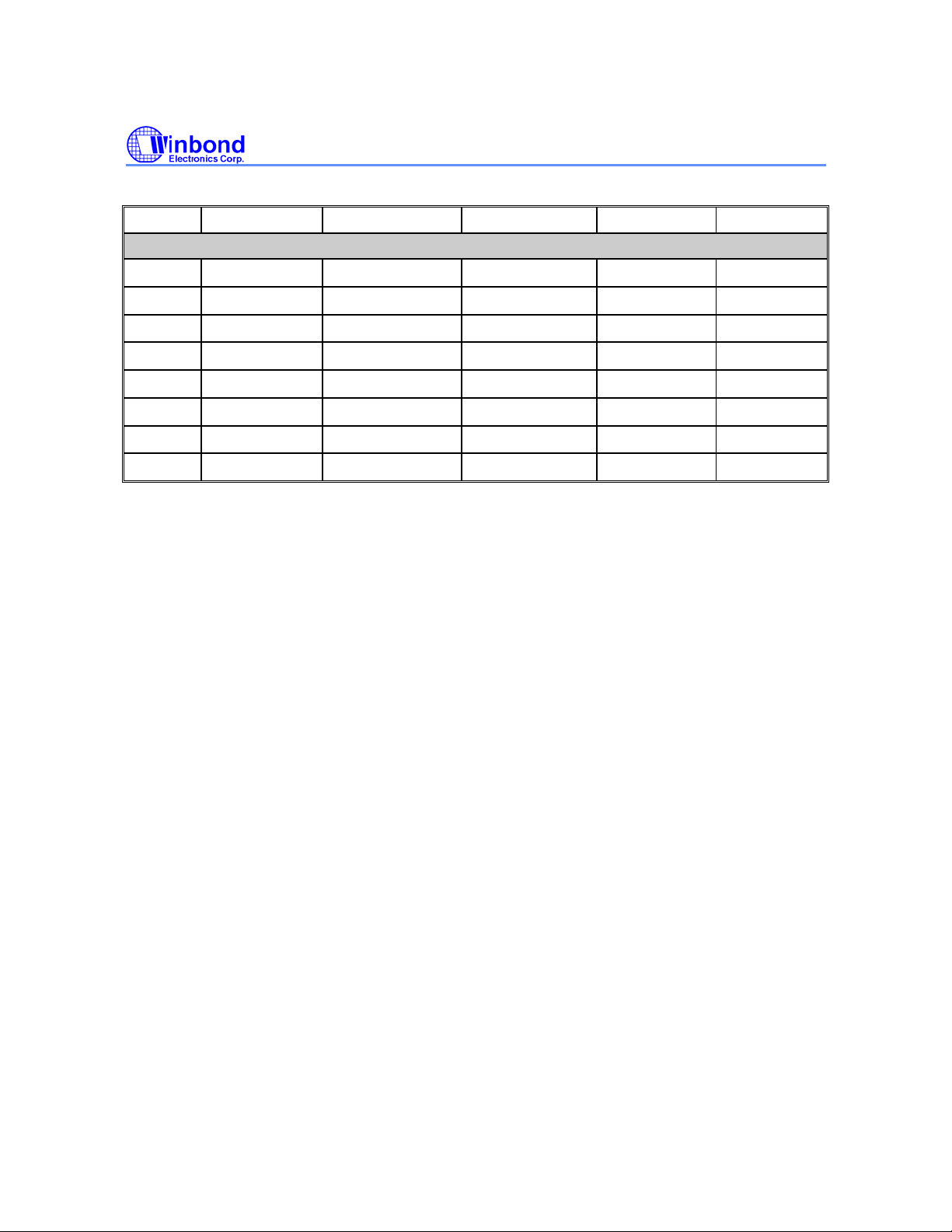

Page 28

W90N745CD/W90N745CDG

Table 5.2 W90N745 128-pin LQFP Multi-function List, continued

PIN NO. DEFAULT FUNCTION0 FUNCTION1 FUNCTION2 FUNCTION3

Memory Address/Data/Control

121 D[6]

122 D[5]

123 VSS33

124 D[4]

125 D[3]

126 D[2]

127 D[1]

128 D[0]

D[6] - - -

D[5] - - -

VSS33 - - -

D[4] - - -

D[3] - - -

D[2] - - -

D[1] - - -

D[0] - - -

Publication Release Date: September 22, 2006

- 23 - Revision A2

Page 29

W90N745CD/W90N745CDG

6. FUNCTIONAL DESCRIPTION

6.1 ARM7TDMI CPU CORE

The ARM7TDMI CPU core is a member of the Advanced RISC Machines (ARM) family of generalpurpose 32-bit microprocessors, which offer high performance for very low power consumption. The

architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and

related decode mechanism are much simpler than those of micro-programmed Complex Instruction Set

Computers. Pipelining is employed so that all parts of the processing and memory systems can operate

continuously. The high instruction throughput and impressive real-time interrupt response are the major

benefits.

The ARM7TDMI CPU core has two instruction sets:

(1) The standard 32-bit ARM set

(2) A 16-bit THUMB set

The THUMB set’s 16-bit instruction length allows it to approach twice the density of standard ARM core

while retaining most of the ARM’s performance advantage over a traditional 16-bit processor using 16-bit

registers. THUMB instructions operate with the standard ARM register configuration, allowing excellent

interoperability between ARM and THUMB states. Each 16-bit THUMB instruction has a corresponding

32-bit ARM instruction with the same effect on the processor model.

ARM7TDMI CPU core has 31 x 32-bit registers. At any one time, 16 sets are visible; the other registers

are used to speed up exception processing. All the register specified in ARM instructions can address

any of the 16 registers. The CPU also supports 5 types of exception, such as two levels of interrupt,

memory aborts, attempted execution of an undefined instruction and software interrupts.

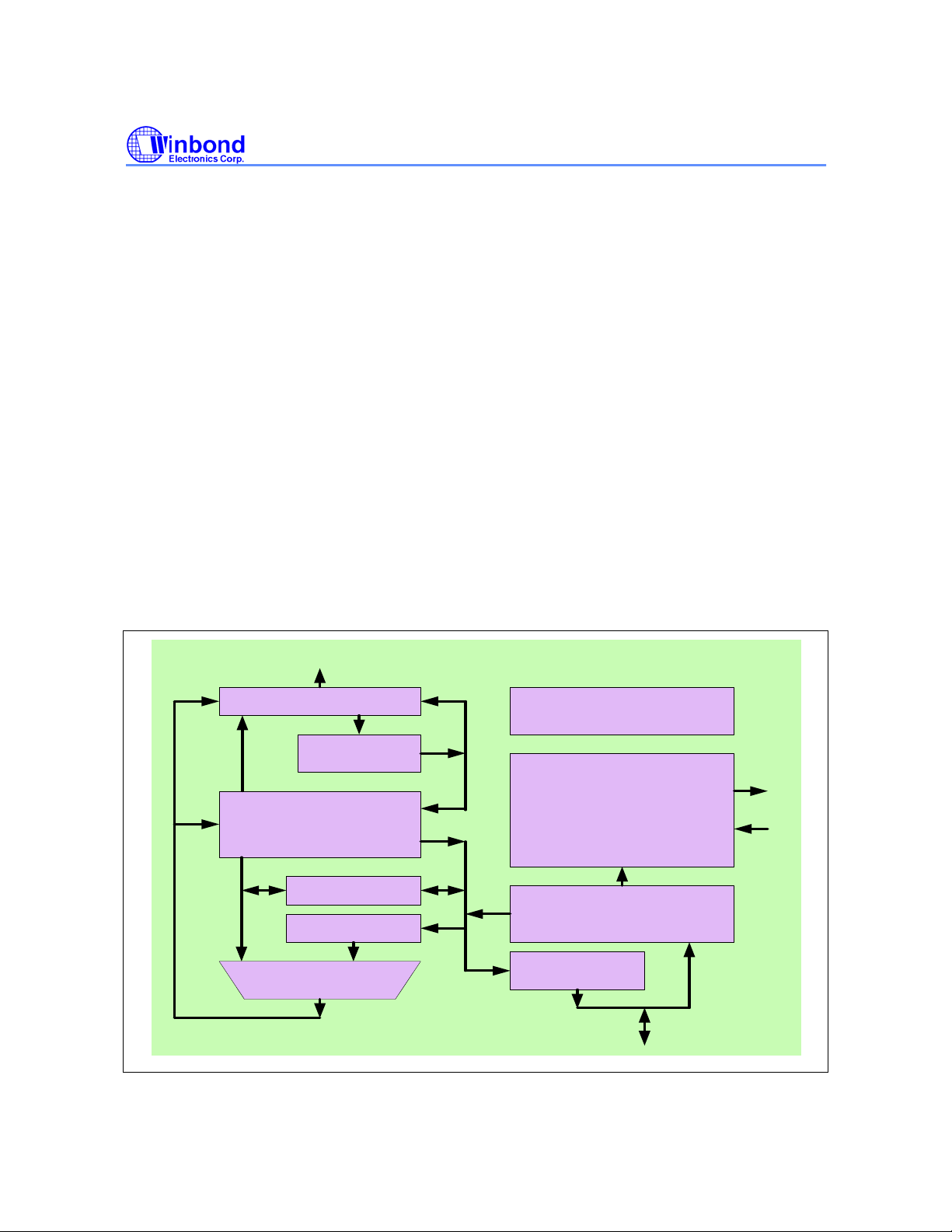

A[31:0]

Address Register

PC Bus

Register Bank

(31 x 32-bit registers)

(6 status registers)

ALU Bus

A Bus

Address

Incrementer

32 x8 Multiplier

Barrel Shifter

32-bit ALU

Incrementer Bus

B Bus

Thumb Instruction Decoder

Scan Control

Instruction Decoder

Control Logic

Instruction Pipeline

Read Data Register

Writer Data

Register

D[31:0]

Figure 6.1.1 ARM7TDMI CPU Core Block Diagram

- 24 -

Page 30

W90N745CD/W90N745CDG

6.2 System Manager

6.2.1 Overview

The W90N745 system manager has the following functions.

y System memory map

y Data bus connection with external memory

y Product identifier register

y Bus arbitration

y PLL module

y Clock select and power saving control register

y Power-On setting

6.2.2 System Memory Map

W90N745 provides 2G bytes cacheable address space and the other 2G bytes are non-cacheable. The

On-Chip Peripherals bank is on 1M bytes top of the space (0xFFF0_0000 – 0xFFFF_FFFF) and the OnChip RAM bank’s start address is 0xFFE0.0000, the other banks can be located anywhere (cacheable

space:0x0000_0000~0x7FDF_FFFF if Cache ON; non-cacheable space:

0x8000_0000~0xFFDF_FFFF).

The size and location of each bank is determined by the register settings for “current bank base address

pointer” and “current bank size”. Please note that when setting the bank control registers, the address

boundaries of consecutive banks must not overlap.

Except On-Chip Peripherals and On-Chip RAM, the start address of each memory bank is not fixed. You

can use bank control registers to assign a specific bank start address by setting the bank’s base pointer

(13 bits). The address resolution is 256K bytes. The bank’s start address is defined as “base pointer <<

18” and the bank’s size is “current bank size”.

In the event of an access requested to an address outside any programmed bank size, an abort signal is

generated. The maximum accessible memory size of each external IO bank is 4M bytes (by word

format), and 64M bytes on each SDRAM bank.

Publication Release Date: September 22, 2006

- 25 - Revision A2

Page 31

W90N745CD/W90N745CDG

0x7FFF_FFFF

512KB

(Fixed)

0x7F F8.0000

512KB

(Fixed)

0x7FF0 _0000

8KB

0x7 FE0_0000

EBI Space

RESERVED

RESERVED

RESERVED

RESERVED

External I/O Bank 3

256 KB - 4M B

External I/O Bank 2

256 KB - 4M B

External I/O Bank 1

256 KB - 4M B

External I/O Bank 0

256 KB - 4M B

0xFFFF_FFFF

512KB

(Fixed)

0xFFF8_0000

512KB

(Fixed)

0xFFF0_0000

8KB

0xFFE0_0000

EBI Space

On-Chip APB

Peripherals

On-Chip AHB

Peripherals

RESERVED

On-Chip RAM

4KB,4KB

External I/O Bank 3

256 KB - 4MB

External I/O Bank 2

256 KB - 4MB

External I/O Bank 1

256 KB - 4MB

External I/O Bank 0

256 KB - 4MB

0x0000 _0000

SDRAM Bank 1

2MB - 64MB

SDRAM Bank 0

2MB - 64MB

ROM/FLASH

256 KB - 4M B

Figure 6.2.1 System Memory Map

SDRAM Bank 1

2MB - 64M B

SDRAM Bank 0

2MB - 64M B

ROM/FLASH

256 KB - 4MB

0x8000_0000

- 26 -

Page 32

W90N745CD/W90N745CDG

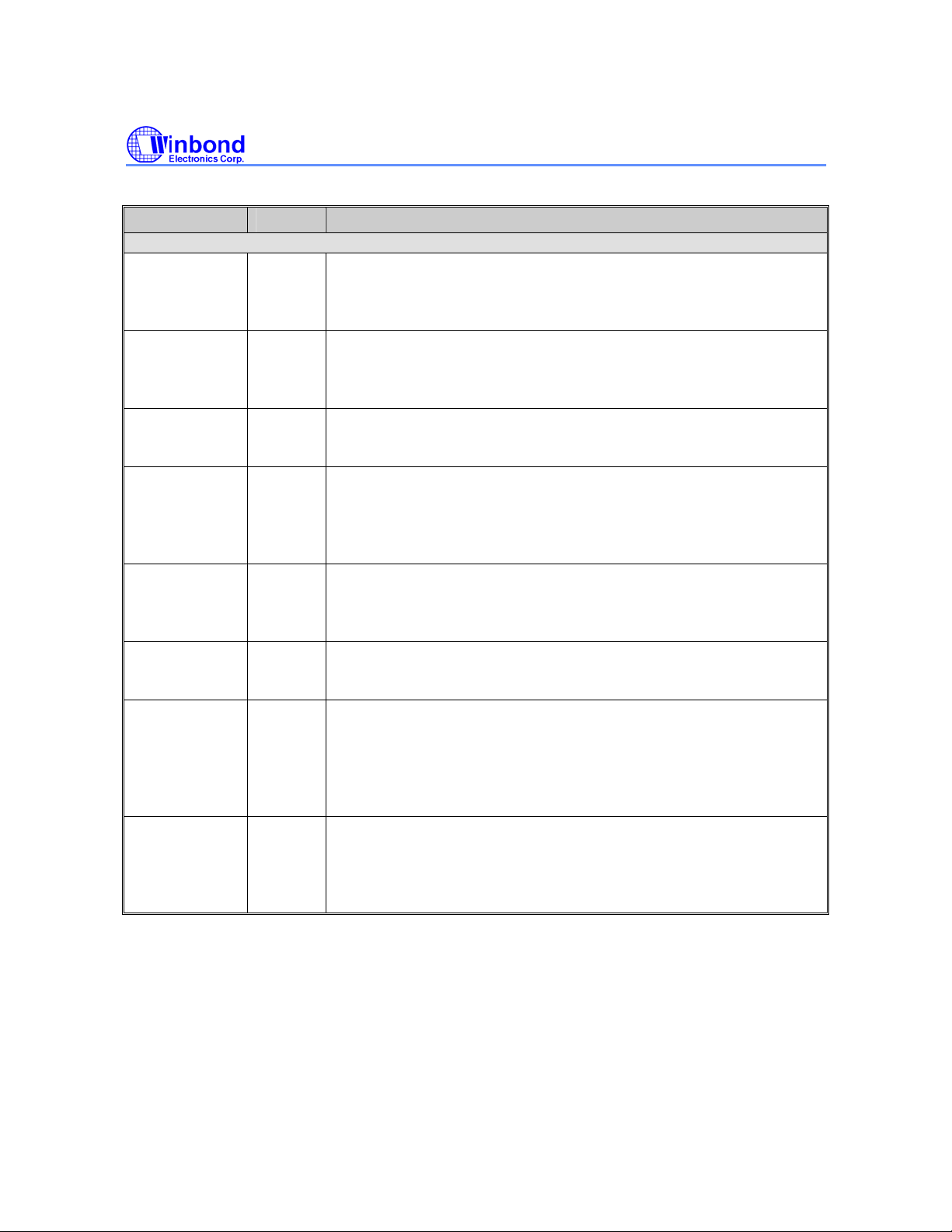

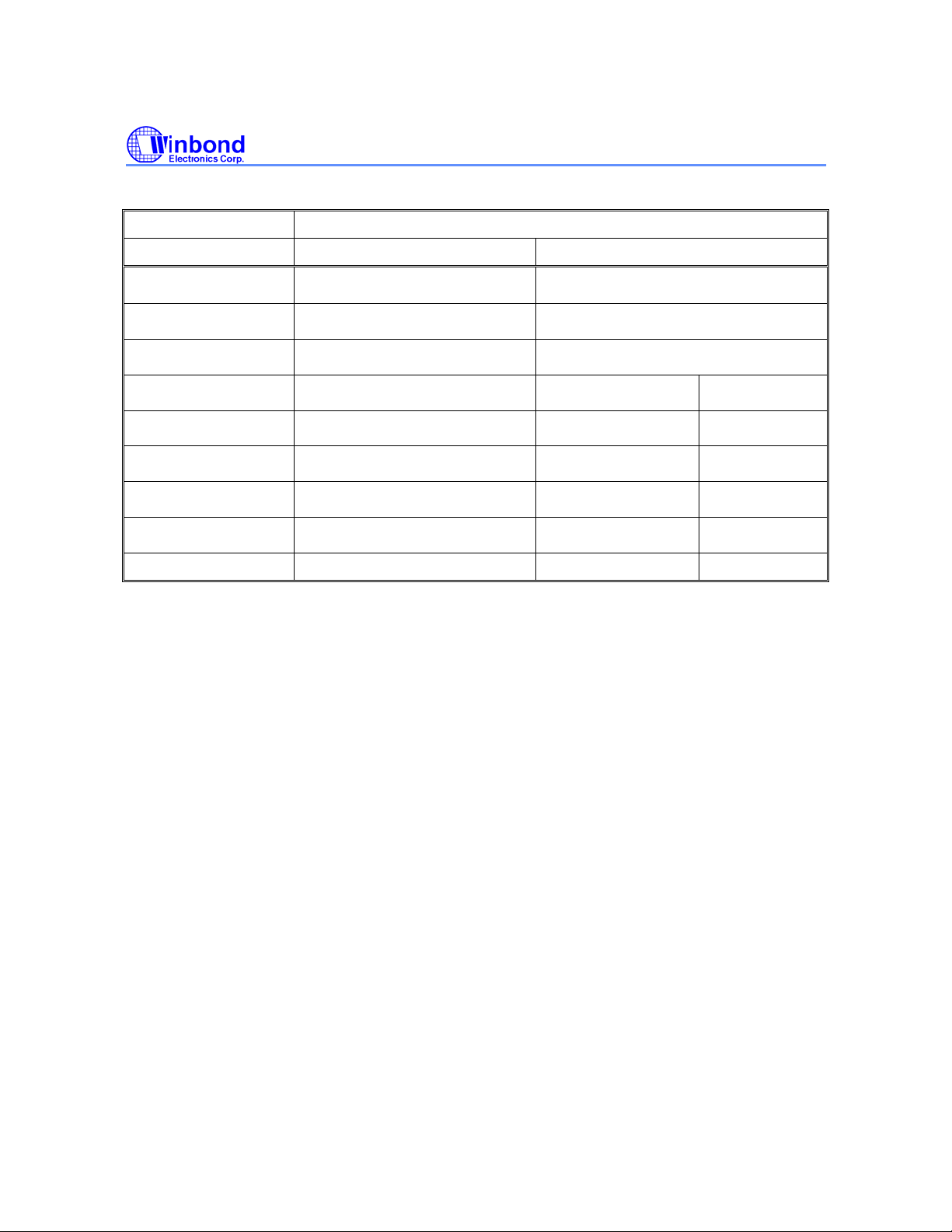

Table 6.2.1 On-Chip Peripherals Memory Map

BASE ADDRESS DESCRIPTION

AHB Peripherals

0xFFF0_0000 Product Identifier Register (PDID)

0xFFF0_0004 Arbitration Control Register (ARBCON)

0xFFF0_0008 PLL Control Register 0(PLLCON0)

0xFFF0_000C Clock Select Register (CLKSEL)

0xFFF0_0010 PLL Control Register 1 (PLLCON1)

0xFFF0_0014

0xFFF0_0020 IRQ Wakeup Control Register (IRQWAKEUPCON)

0xFFF0_0024 IRQ Wakeup Flag Register (IRQWAKEFLAG)

0xFFF0_0028 Power Manager Control Register (PMCON)

0xFFF0_0030 USB Transceiver Control Register (USBTXRCON)

0xFFF0_1000 EBI Control Register (EBICON) Control Registers

0xFFF0_1004 ROM/FLASH (ROMCON) Control Registers

0xFFF0_1008 SDRAM bank 0 – 1 Control Registers

0xFFF0_1018 External I/O 0 – 3 Control Registers

0xFFF0_2000 Cache Controller Control Registers

0xFFF0_3000 Ethernet MAC Controller Control Registers

0xFFF0_4000 GDMA 0 – 1 Control Registers

0xFFF0_5000 USB Host Controller Control Registers

0xFFF0_6000 USB Device Controller Control Registers

0xFFF0_9000 AC97/I²S Controller Control Registers

Audio I²S Clock Control Register (I²SCKCON)

APB Peripherals

0xFFF8_0000 UART 0 (Tx, RX for console)

0xFFF8_0100 UART 1 (Tx, Rx, for bluetooth)

0xFFF8_0200 UART 2 (bluetooth CTS, RTS/ IrDA Tx, Rx)

0xFFF8_0300 UART 3 (micro-print DTR, DTS, Tx, Rx)

0xFFF8_1000 Timer 0 – 1, WDOG Timer

0xFFF8_2000 Interrupt Controller

0xFFF8_3000 GPIO

0xFFF8_6000

0xFFF8_6100

0xFFF8_6200 USI Control Registers

0xFFF8_7000 Pulse Width Modulation (PWM) Control Registers

0xFFF8_8000 KeyPad Interface Control Register (KPI)

0xFFF8_9000 PS2 Control Registers

2

I

C-0 Control Registers

2

I

C-1 Control Registers

Publication Release Date: September 22, 2006

- 27 - Revision A2

Page 33

W90N745CD/W90N745CDG

6.2.3 Address Bus Generation

The W90N745 address bus generation is depended on the required data bus width of each memory

bank. The data bus width is determined by DBWD bits in each bank’s control register.

The maximum accessible memory size of each external IO bank is 4M bytes.

Table 6.2.2 Address Bus Generation Guidelines

DATA BUS EXTERNAL ADDRESS PINS

WIDTH A [20:0]

8-bit

16-bit

A20 – A0

(Internal)

A21 – A1

(Internal)

MAXIMUM ACCESSIBLE MEMORY SIZE

2M bytes

2M half-words

6.2.4 Data Bus Connection with External Memory

6.2.4.1. Memory formats

The W90N745 can be configured as big endian or little endian mode by pull up or down the external data

bus D14 pin. If D14 is pull up, then it is a little endian mode, otherwise, it is a big endian mode.

Little endian

In little endian format, the lowest addressed byte in a word is considered the least significant byte of the

word and the highest addressed byte is the most significant. So the byte at address 0 of the memory

system connects to data lines 7 through 0.

For a word aligned address A, Figure 6.2.2 shows how the half-word at addresses A and A+2, and the

bytes at addresses A, A+1, A+2, and A+3 map on to each other when D14 pin is High.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Half-word at address A

Half-word at address A+2

Byte at address A+1 Byte at address A

Byte at address A+3 Byte at address A+2

Figure 6.2.2 Little endian addresses of bytes and half-words within half words

- 28 -

Page 34

W90N745CD/W90N745CDG

Big endian

In Big endian format, the W90N745 stores the most significant byte of a word at the lowest numbered

byte, and the least significant byte at the highest-numbered byte. So the byte at address 0 of the memory

system connects to data lines 31 through 24.

For a word aligned address A, Figure 6.2.3 shows how the half-word at addresses A and A+2, and the

bytes at addresses A, A+1, A+2, and A+3 map on to each other when the D14 pin is Low.

15 14 13 12 1110987654321 0

Half-word at address A

Half-word at address A+2

Byte at address A Byte at address A+1

Byte at address A+2 Byte at address A+3

Figure 6.2.3 Big endian addresses of bytes and half-words within half words

6.2.4.2. Connection of External Memory with Various Data Width

The system diagram for W90N745 connecting with the external memory is shown in Figure 6.2.4. Below

tables (Table 6.2.3 through Table 6.2.14) show the program/data path between CPU register and the

external memory using little / big endian and word/half-word/byte access.

Figure 6.2.4 Address/Data bus connection with external memory

Publication Release Date: September 22, 2006

- 29 - Revision A2

Page 35

W90N745CD/W90N745CDG

Figure 6.2.5 CPU registers Read/Write with external memory

Table 6.2.3 and Table 6.2.4

Using big-endian and word access, Program/Data path between register and external memory

WA = Address whose LSB is 0,4,8,C X = Don’t care

nWBE [1-0] / SDQM [1-0] = A means active and U means inactive

Table 6.2.3 Word access write operation with Big Endian

ACCESS OPERATION WRITE OPERATION (CPU REGISTER Î EXTERNAL MEMORY)

XD WIDTH HALF WORD BYTE

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

XA

nWBE [1-0] /

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st write 2nd write 1st write 2nd write 3rd write 4th write

31 0

ABCD

WA WA

31 0

AB CD

15 0

AB

WA WA+2 WA WA+1 WA+2 WA+3

AA AA XA XA XA XA

15 0

AB

15 0

AB

15 0

CD

15 0

CD

15 0

CD

7 0

A

7 0

A

7 0

A

7 0

7 0

7 0

B

B

B

31 0

ABCD

31 0

A B C D

7 0

C

7 0

C

7 0

C

7 0

D

7 0

D

7 0

D

- 30 -

Page 36

W90N745CD/W90N745CDG

Table 6.2.4 Word access read operation with Big Endian

ACCESS OPERATION READ OPERATION (CPU REGISTER Í EXTERNAL MEMORY)

XD WIDTH HALF WORD BYTE

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

XA

31 0

CDAB

WA WA

31 0

CD AB

31 0

CD XX

WA WA+2 WA WA+1 WA+2 WA+3

31 0

CD AB

31 0

D X X X

31 0

D C X X

31 0

DCBA

31 0

D C B A

31 0

D C B X

31 0

D C B A

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st read 2nd read 1st read 2nd read 3rd read 4th read

AA AA XA XA XA XA

15 0

CD

15 0

CD

15 0

AB

15 0

AB

7 0

D

7 0

D

7 0

C

7 0

C

7 0

B

7 0

B

7 0

A

7 0

A

Table 6.2.5 and Table 6.2.6

Using big-endian and half-word access, Program/Data path between register and external memory.

HA = Address whose LSB is 0,2,4,6,8,A,C,E X = Don’t care

nWBE [1-0] / SDQM [1-0] = A means active and U means inactive

Table 6.2.5 Half-word access write operation with Big Endian

ACCESS OPERATION WRITE OPERATION (CPU REGISTER Î EXTERNAL MEMORY)

XD WIDTH HALF WORD BYTE

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

XA

nWBE [1-0] /

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st write 2nd write

31 0

ABCD

HA HA

31 0

CD CD

31 0

CD CD

HA HA HA+1

AA XA XA

15 0

CD

15 0

CD

31 0

CD CD

7 0

C

7 0

C

7 0

C

31 0

ABCD

31 0

CD CD

7 0

D

7 0

D

7 0

D

Publication Release Date: September 22, 2006

- 31 - Revision A2

Page 37

W90N745CD/W90N745CDG

Table 6.2.6 Half-word access read operation with Big Endian

ACCESS OPERATION READ OPERATION (CPU REGISTER Í EXTERNAL MEMORY)

XD WIDTH HALF WORD BYTE

Bit Number

CPU Reg Data

15 0

CD

15 0

DC

SA

Bit Number

SD

Bit Number

ED

XA

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st read 2nd read

HA HA

15 0

CD

15 0

CD

HA HA HA+1

AA XA XA

15 0

CD

15 0

CD

15 0

DX

7 0

D

7 0

D

15 0

DC

15 0

DC

7 0

C

7 0

C

Table 6.2.7 and Table 6.2.8

Using big-endian and byte access, Program/Data path between register and external memory.

BA = Address whose LSB is 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

BAL = Address whose LSB is 0,2,4,6,8,A,C,E BAU = Address whose LSB is 1,3,5,7,9,B,D,F

- 32 -

Page 38

W90N745CD/W90N745CDG

Table 6.2.7 Byte access write operation with Big Endian

ACCESS OPERATION WRITE OPERATION (CPU REGISTER EXTERNAL MEMORY)

XD WIDTH HALF WORD BYTE

Bit Number

CPU Reg Data

31 0

ABCD

31 0

ABCD

SA

Bit Number

SD

Bit Number

ED

XA

nWBE [1-0] /

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence

BAL BAU BA

31 0

D D D D

15 8

D

BAL BAL BA

AU UA XA

15 0

D X

15 8

D

31 0

D D D D

7 0

D

15 0

X D

7 0

D

31 0

D D D D

7 0

D

7 0

D

7 0

D

Table 6.2.8 Byte access read operation with Big Endian

ACCESS OPERATION READ OPERATION (CPU REGISTER Í EXTERNAL MEMORY)

XD WIDTH HALF WORD BYTE

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

7 0

C

BAL BAU BA

7 0

C

7 0

C

7 0

D

7 0

D

15 8

D

7 0

D

7 0

D

7 0

D

XA

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence

BAL BAL BA

AU UA XA

15 0

CD

15 0

CD

15 0

CD

7 0

D

7 0

D

Publication Release Date: September 22, 2006

- 33 - Revision A2

Page 39

W90N745CD/W90N745CDG

Table 6.2.9 and Table 6.2.10

Using little-endian and word access, Program/Data path between register and external memory

WA = Address whose LSB is 0,4,8,C X = Don’t care

nWBE [1-0] / SDQM [1-0] = A means active and U means inactive

Table 6.2.9 Word access write operation with little Endian

ACCESS OPERATION WRITE OPERATION (CPU REGISTER Î EXTERNAL MEMORY)

XD WIDTH HALF WORD BYTE

Bit Number

CPU Reg Data

31 0

ABCD

31 0

ABCD

SA

Bit Number

SD

Bit Number

ED

XA

nWBE [1-0] /

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st write 2nd write 1st write 2nd write 3rd write 4th write

15 0

15 0

15 0

WA WA

31 0

AB CD

15 0

CD

WA WA+2 WA WA+1 WA+2 WA+3

AA AA XA XA XA XA

CD

CD

AB

15 0

AB

15 0

AB

7 0

D

7 0

D

7 0

D

A B C D

7 0

C

7 0

C

7 0

C

31 0

7 0

B

7 0

B

7 0

B

Table 6.2.10 Word access read operation with Little Endian

ACCESS OPERATION READ OPERATION (CPU REGISTER Í EXTERNAL MEMORY)

XD Width Half Word Byte

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

31 0

XX CD

31 0

ABCD

WA WA

31 0

AB CD

31 0

AB CD

31 0

X X X D

31 0

X X C D

31 0

ABCD

31 0

A B C D

31 0

X B C D

31 0

A B C D

7 0

A

7 0

A

7 0

A

XA

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st write 2nd write 1st write 2nd write 3rd write 4th write

WA WA+2 WA WA+1 WA+2 WA+3

AA AA XA XA XA XA

15 0

CD

15 0

CD

15 0

AB

15 0

AB

7 0

D

7 0

D

7 0

C

7 0

C

7 0

B

7 0

B

7 0

A

7 0

A

- 34 -

Page 40

W90N745CD/W90N745CDG

Table 6.2.11 and Table 6.2.12

Using little-endian and half-word access, Program/Data path between register and external memory.

HA = Address whose LSB is 0,2,4,6,8,A,C,E X = Don’t care

nWBE [1-0] / SDQM [1-0] = A means active and U means inactive

Table 6.2.11 Half-word access write operation with little Endian

ACCESS OPERATION WRITE OPERATION (CPU REGISTER Î EXTERNAL MEMORY)

XD Width Half Word Byte

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

XA

nWBE [1-0] /

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st write 2nd write

31 0

ABCD

HA HA

31 0

CD CD

31 0

CD CD

HA HA HA+1

AA XA XA

15 0

CD

15 0

CD

31 0

CD CD

7 0

7 0

7 0

31 0

ABCD

31 0

CD CD

7 0

D

7 0

D

7 0

D

Table 6.2.12 Half-word access read operation with Little Endian

ACCESS OPERATION READ OPERATION (CPU REGISTER Í EXTERNAL MEMORY)

XD Width Half Word Byte

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

XA

15 0

CD

HA HA

15 0

CD

15 0

CD

HA HA HA+1

15 0

XD

15 0

CD

15 0

CD

15 0

CD

C

C

C

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence 1st read 2nd read

AA XA XA

15 0

CD

15 0

CD

7 0

D

7 0

D

7 0

C

7 0

C

Publication Release Date: September 22, 2006

- 35 - Revision A2

Page 41

W90N745CD/W90N745CDG

Table 6.2.13 and Table 6.2.14

Using little-endian and byte access, Program/Data path between register and external memory.

BA = Address whose LSB is 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

BAL = Address whose LSB is 0,2,4,6,8,A,C,E BAU = Address whose LSB is 1,3,5,7,9,B,D,F

Table 6.2.13 Byte access write operation with little Endian

ACCESS OPERATION WRITE OPERATION (CPU REGISTER Î EXTERNAL MEMORY)

XD Width Half Word Byte

Bit Number

CPU Reg Data

31 0

ABCD

31 0

ABCD

SA

Bit Number

SD

Bit Number

ED

XA

nWBE [1-0] /

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence

BAL BAU BA

31 0

D D D D

7 0

D

BAL BAL BA

UA AU XA

15 0

X D

7 0

D

31 0

D D D D

15 8

D

15 0

D X

15 8

D

31 0

D D D D

7 0

D

7 0

D

7 0

D

Table 6.2.14 Byte access read operation with Little Endian

ACCESS OPERATION READ OPERATION (CPU REGISTER Í EXTERNAL MEMORY)

XD Width Half Word Byte

Bit Number

CPU Reg Data

SA

Bit Number

SD

Bit Number

ED

7 0

D

BAL BAU BA

7 0

D

7 0

D

7 0

C

7 0

C

7 0

C

7 0

D

7 0

D

7 0

D

XA

SDQM [1-0]

Bit Number

XD

Bit Number

Ext. Mem Data

Timing Sequence

BAL BAL BA

UA AU XA

15 0

CD

15 0

CD

15 0

CD

7 0

D

7 0

D

- 36 -

Page 42

W90N745CD/W90N745CDG

6.2.5 Bus Arbitration

The W90N745’s internal function blocks or external devices can request mastership of the system bus

and then hold the system bus in order to perform data transfers. Because the design of W90N745 bus

allows only one bus master at a time, a bus controller is required to arbitrate when two or more internal

units or external devices simultaneously request bus mastership. When bus mastership is granted to an

internal function block or an external device, other pending requests are not acknowledged until the

previous bus master has released the bus.

W90N745 supports two priority modes, the Fixed Priority Mode and the Rotate Priority Mode,

depends on the ARBCON register PRTMOD bit setting.

6.2.5.1. Fixed Priority Mode

In Fixed Priority Mode (PRTMOD=0, default value), to facilitate bus arbitration, priorities are assigned to

each internal W90N745 function block. The bus controller arbitration requests for the bus mastership

according to these fixed priorities. In the event of contention, mastership is granted to the function block

with the highest assigned priority. These priorities are listed in Table 6.2.15.

W90N745 allows raising ARM Core priority to second if an unmasked interrupt occurred. If IPEN bit, Bit 1

of the Arbitration Control Register (ARBCON), is set to “0”, the priority of ARM Core is fixed to lowest.

If IPEN bit is set to “1” and if no unmasked interrupt request, then the ARM Core’s priority is still lowest

and the IPACT=0, Bit 2 of the Arbitration Control Register (ARBCON) ; If there is an unmasked

interrupt request, then the ARM Core’s priority is raised to first and IPACT=1.

If IPEN is set, an interrupt handler will normally clear IPACT at the end of the interrupt routine to allow an

alternate bus master to regain the bus; however, if IPEN is cleared, no additional action need be taken in

the interrupt handler. The IPACT bit can be read and written. Writing with “0”, the IPACT bit is cleared,

but it will be no effect as writing with “1”.

Table 6.2.15 Bus Priorities for Arbitration in Fixed Priority Mode

BUS FUNCTION BLOCK

PRIORITY IPACT = 0 IPEN = 1 AND IPACT = 1

1 (Highest) Audio Controller (AC97 & I²S) ARM Core

2 General DMA0 Audio Controller (AC97 & I²S)

3 General DMA1 General DMA0

4 EMC DMA General DMA1

5 USB Host EMC DMA

6 USB Device USB Host

7(Lowest) ARM Core USB Device

Publication Release Date: September 22, 2006

- 37 - Revision A2

Page 43

W90N745CD/W90N745CDG

6.2.5.2. Rotate Priority Mode

In Rotate Priority Mode (PRTMOD=1), the IPEN and IPACT bits have no function (i.e. can be ignored).

W90N745 uses a round robin arbitration scheme ensures that all bus masters have equal chance to gain

the bus and that a retracted master does not lock up the bus.

6.2.6 Power Management

W90N745 provide three power management scenarios to reduce power consumption. The

peripherals’ clocks can be enabled / disabled individually by controlling the co-responding bit in

CLKSEL control register. Software can turn-off the unused modules’ clocks to saving the unnecessary

power consumption. It also provides idle and power-down modes to reduce power consumption.

Figure 6.2.6 W90N745 system clock generation diagram

- 38 -

Page 44

W90N745CD/W90N745CDG

IDLE MODE

If the IDLE bit in Power Management Control Register (PMCON) is set, the ARM CORE clock source

will be halted, the ARM CORE will not go forward. The AHB or APB clocks still active except the clock

to cache controller and ARM are stopped. W90N745 will exit idle state when nIRQ or nFIQ from any

peripheral is revived; like keypad, timer overflow interrupts and so on. The memory controller can also

be forced to enter idle state if both MIDLE and IDLE bits are set. Software must switch SDRAM into

self-refresh mode before forcing memory to enter idle mode.

IDLE Period

FOUT

(PLL)

HCLK

idle_state

MCLK

(ARM)

HCLK

(cache)

HCLK

(memc)

Case1. IDLE=1, PD=0, MIDLE=0

Figure 6.2.7 Clock management for system idle mode

IDLE Period

FOUT

(PLL)

HCLK

idle_state

MCLK

(ARM)

HCLK

(cache)

HCLK

(memc)

Case2. IDLE=1, PD=0, MIDLE=1

Figure 6.2.8 Clock management for system and memory idle mode

Publication Release Date: September 22, 2006

- 39 - Revision A2

Page 45

W90N745CD/W90N745CDG

Power Down Mode

This mode provides the minimum power consumption. When the W90N745 system is not working or

waiting an external event, software can write PD bit “1” to turn off all the clocks includes system crystal

oscillator to let ARM CORE enter sleep mode. In this state, all peripherals are also in sleep mode

since the clock source is stopped. W90N745 will exit power down state when nIRQ/nFIQ is detected.

W90N745 provides external interrupt nIRQ[1:0], keypad, and USB device interfaces to wakeup the

system clock.

65536 clocks

EXTAL

HCLK

idle _state

pd_state

HCLK

(cache)

Case3. IDLE=0, PD=1, MIDLE=0

wake up by pheripheral's

interrupts

Figure 6.2.9 Clock management for system power down mode and wake up

- 40 -

Page 46

W90N745CD/W90N745CDG

6.2.7 Power-On Setting

After power on reset, there are eight Power-On setting pins to configure W90N745 system configuration.

POWER-ON SETTING PIN

Internal System Clock Select D15

Little/Big Endian Mode Select D14

Boot ROM/FLASH Data Bus Width

Default: Pull-Down in Normal Operation D9

Default: Pull-Up in Normal Operation D8

D15 pin:Internal System Clock Select

If pin D15 is pull-down, the external clock from EXTAL pin is served as internal system clock.

If pin D15 is pull-up, the PLL output clock is used as internal system clock.

D14 pin:Little/Big Endian Mode Select

If pin D14 is pull-down, the external memory format is Big Endian mode.

If pin D14 is pull-up, the external memory format is Little Endian mode.

D [13:12] : Boot ROM/FLASH Data Bus Width

D [13:12]

D [13:12] BUS WIDTH

Pull-down Pull-down 8-bit

Pull-down Pull-up 16-bit

Pull-up Pull-down RESERVED

Pull-up Pull-up RESERVED

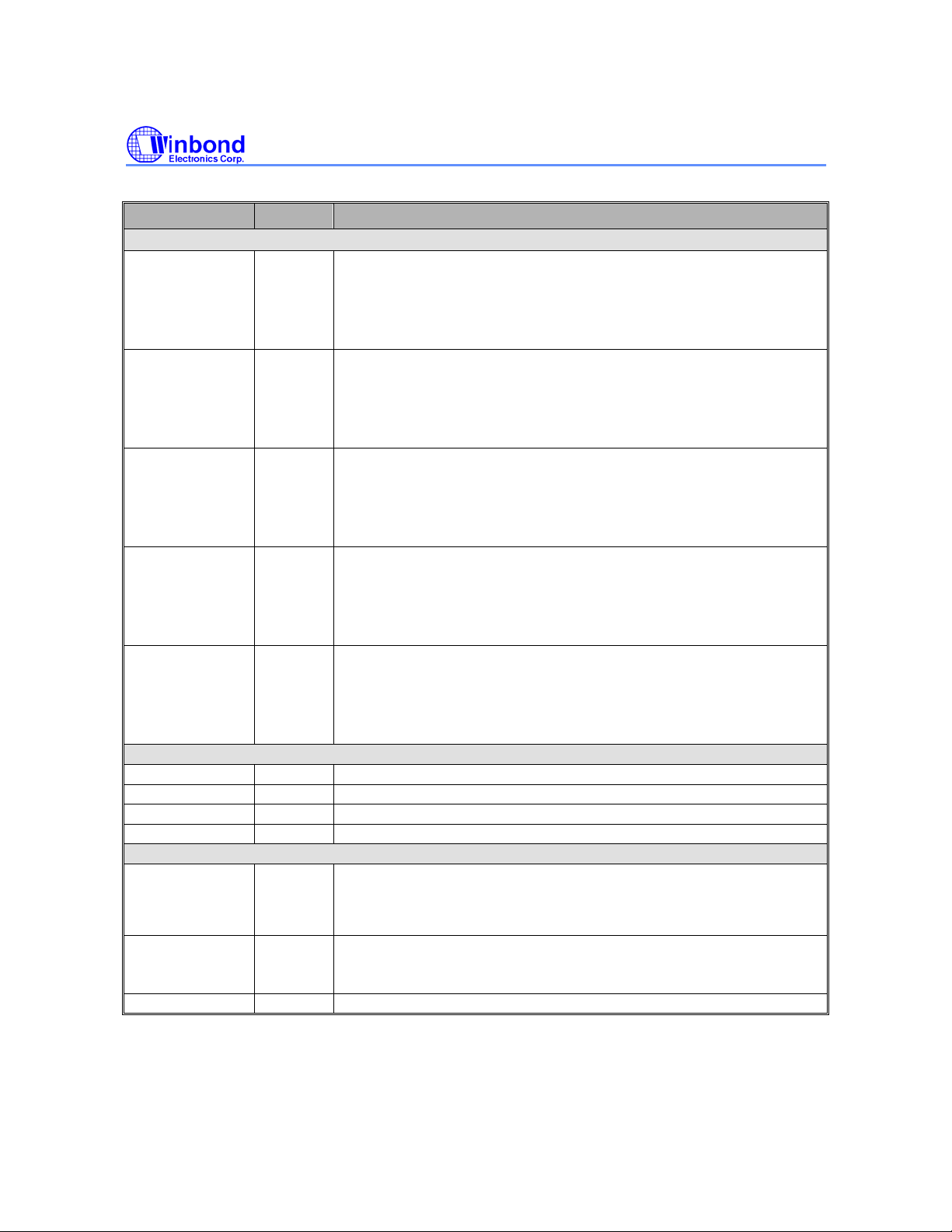

6.2.8 System Manager Control Registers Map

REGISTER ADDRESS R/W DESCRIPTION RESET VALUE

PDID 0xFFF0_0000 R Product Identifier Register 0xX090_0745

ARBCON 0xFFF0_0004 R/W Arbitration Control Register 0x0000_0000

PLLCON0 0xFFF0_0008 R/W PLL Control Register 0 0x0000_2F01

CLKSEL 0xFFF0_000C R/W Clock Select Register 0x1FFF_3FX8

PLLCON1 0xFFF0_0010 R/W PLL Control Register 1 0x0001_0000

I²SCKCON 0xFFF0_0014 R/W

IRQWAKECON 0xFFF0_0020 R/W IRQ Wakeup Control register 0x0000_0000

IRQWAKEFLAG 0xFFFF_0024 R/W IRQ wakeup Flag Register 0x0000_0000

PMCON 0xFFF0_0028 R/W Power Manager Control Register 0x0000_0000

USBTxrCON 0xFFF0_0030 R/W USB Transceiver Control Register 0x0000_0000

Audio I²S Clock Control Register

0x0000_0000

Publication Release Date: September 22, 2006

- 41 - Revision A2

Page 47

W90N745CD/W90N745CDG

Product Identifier Register (PDID)

This register is read only and lets software can use it to recognize certain characteristics of the chip ID

and the version number.

REGISTER ADDRESS R/W DESCRIPTION RESET VALUE

PDID 0xFFF0_0000 R Product Identifier Register 0xX090_0745

31 30 29 28 27 26 25 24

PACKAGE VERSION

23 22 21 20 19 18 17 16

CHPID

15 14 13 12 11 10 9 8

CHPID

7 6 5 4 3 2 1 0

CHPID

BITS DESCRIPTION

Package Type Select

[31:30] PACKAGE

[29:24] VERSION

[23:0] CHIPID

These two bits are power-on setting latched from pin D[9:8]

Package [31:30] Package Type

Version of chip

The chip identifier of W90N745 is 0x090.0745

0 1 128-pin Package

- 42 -

Page 48

W90N745CD/W90N745CDG

Arbitration Control Register (ARBCON)

REGISTER ADDRESS R/W DESCRIPTION RESET VALUE

ARBCON

31 30 29 28 27 26 25 24

23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8

7 6 5 4 3 2 1 0

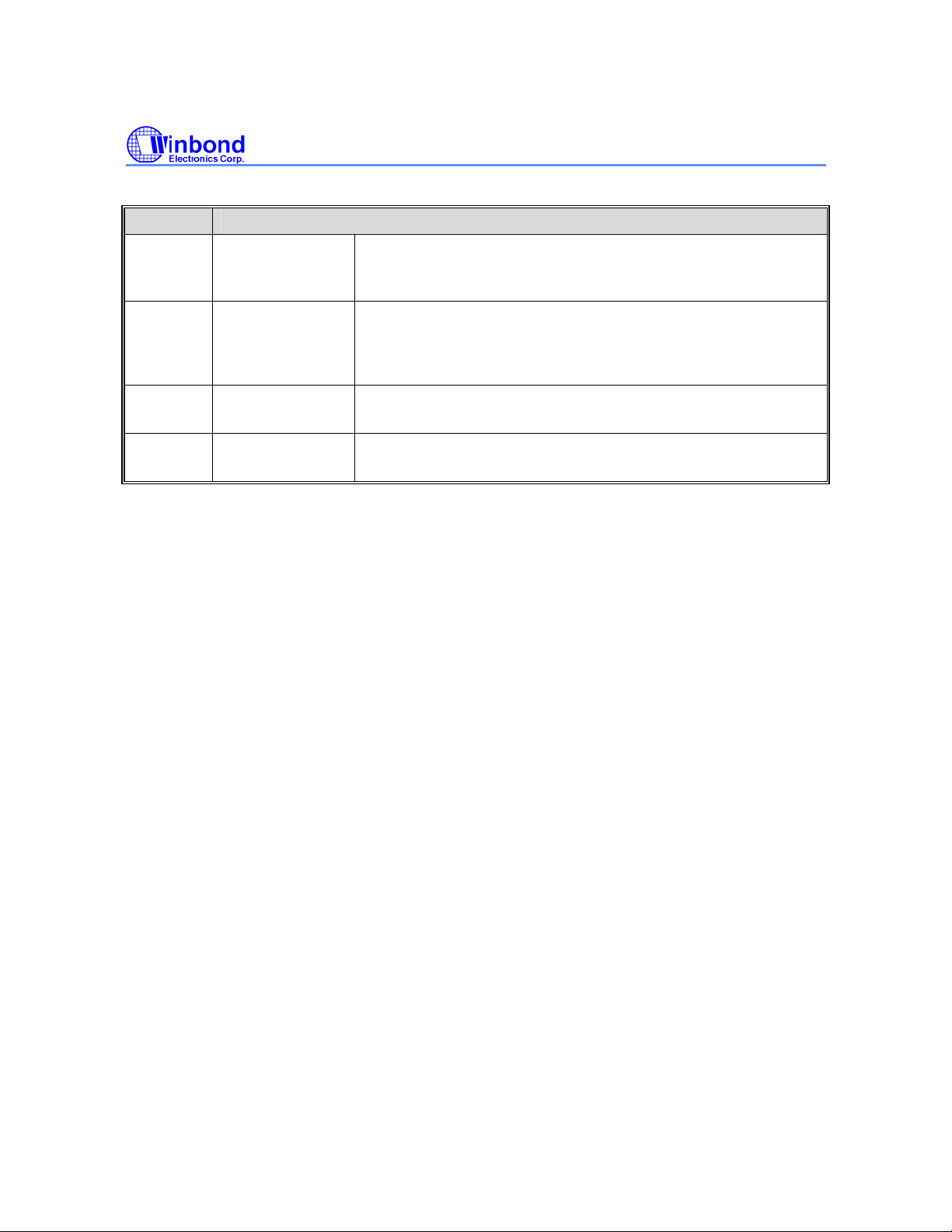

BITS DESCRIPTION

[31:3] RESERVED -

[2] IPACT

[1] IPEN

[0] PRTMOD

0xFFF0_0004 R/W

RESERVED IPACT IPEN PRTMOD

Interrupt priority active.

When IPEN=”1”, this bit will be set when the ARM core has an

unmasked interrupt request. This bit is available only when the

PRTMOD=0.

Interrupt priority enable bit

0 = the ARM core has the lowest priority.

1 = enable to raise the ARM core priority to second

This bit is available only when the PRTMOD=0.

Priority mode select

0 = Fixed Priority Mode (default)

1 = Rotate Priority Mode

Arbitration Control Register

RESERVED

RESERVED

RESERVED

0x0000_0000

Publication Release Date: September 22, 2006

- 43 - Revision A2

Page 49

W90N745CD/W90N745CDG

PLL Control Register0 (PLLCON0)

W90N745 provides two clock generation options – crystal and oscillator. The external clock via

EXTAL(15M) Minput pin as the reference clock input of PLL module. The external clock can bypass the

PLL and be used to the internal system clock by pull-down the data D15 pin. Using PLL’s output clock

for the internal system clock, D15 pin must be pull-up.

REGISTER ADDRESS R/W DESCRIPTION RESET VALUE

PLLCON

31 30 29 28 27 26 25 24

23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8

0xFFF0_0008 R/W

RESERVED

RESERVED PWDEN

PLL Control Register

0x0000_2F01

FBDV

7 6 5 4 3 2 1 0

FBDV OTDV INDV

BITS DESCRIPTION

[31:17] RESERVED -

Power down mode enable

[16] PWDEN

[15:7] FBDV

[6:5] OTDV

[4:0] INDV

0 = PLL is in normal mode (default)

1 = PLL is in power down mode

PLL VCO output clock feedback divider

Feedback Divider divides the output clock from VCO of PLL.

PLL output clock divider

OTDV [6:5] DIVIDED BY

0 0 1

0 1 2

1 0 2

PLL input clock divider

Input divider divides the input reference clock into the PLL.

1 1 4

- 44 -

Page 50

W90N745CD/W90N745CDG

O

EXTAL

FIN

INDV[4:0]

FBDV[8:0]

Input Divider

(NR)

PFD

Feedback

Divider

(NF)

Charge

Pump

Figure 6.2.10 System PLL block diagram

The formula of output clock of PLL is:

NF 1

FOUT = FIN

NR

∗∗

N

FOUT:Output clock of Output Divider

FIN:External clock into the Input Divider

NR:Input divider value (NR = INDV + 2)

NF:Feedback divider value (NF = FBDV + 2)

NO:Output divider value (NO = OTDV)

PLL

VCO

Output

Divider

(NO)

OTDV[1:0]

480MHz

FOUT

GP0

48MHz

Gen

Clock

Divider

&

Selector

CLKS[2:0]

USBCKS

1

0

0

1

ECLKS

USB

Module

Internal

System

Clock

Publication Release Date: September 22, 2006

- 45 - Revision A2

Page 51

W90N745CD/W90N745CDG

Clock Select Register (CLKSEL)

REGISTER ADDRESS R/W DESCRIPTION RESET VALUE

CLKSEL

31 30 29 28 27 26 25 24

23 22 21 20 19 18 17 16

UART3 UART2 UART1

15 14 13 12 11 10 9 8

USBCKS USBD GDMA RESERVED EMC RESERVED WDT

7 6 5 4 3 2 1 0

USBH TIMER UART ECLKS CLKS RESET

BITS DESCRIPTION

[31:29] RESERVED -

[28] PS2

[27] KPI

[26] RESERVED

[25] RESERVED

[24] USI

[23] UART3

[22] UART2

[21] UART1

0xFFF0_000C R/W

RESERVED PS2 KPI RESERVED SSP

PS2 controller clock enable bit

0 = Disable PS2 controller clock

1 = Enable PS2 controller clock

Keypad controller clock enable bit

0 = Disable keypad controller clock

1 = Enable keypad controller clock

-

-

USI controller clock enable bit

0 = Disable USI controller clock

1 = Enable USI controller clock

UART3 controller clock enable bit

0 = Disable UART3 controller clock

1 = Enable UART3 controller clock

UART2 controller clock enable bit

0 = Disable UART2 controller clock

1 = Enable UART2 controller clock

UART1 controller clock enable bit

0 = Disable UART1 controller clock

1 = Enable UART1 controller clock

Clock Select Register

2

I

C1 I2C0

0x1FFF_7FX8

RESERVED PWM AC97

- 46 -

Page 52

W90N745CD/W90N745CDG

Continued.

BITS DESCRIPTION

2

I

C1 controller clock enable bit

[20]

I

2

C1

0 = Disable I

1 = Enable I

2

I

C0 controller clock enable bit

[19]

I

2

C0

0 = Disable I

1 = Enable I

[18] RESERVED

-

PWM controller clock enable bit

[17] PWM

0 = Disable PWM controller clock

1 = Enable PWM controller clock

Audio Controller clock enable bit

[16] AC97

0 = Disable AC97 controller clock

1 = Enable AC97 controller clock

USB host/device 48MHz clock source Select bit

[15] USBCKS

0 = USB clock 48MHz input from internal PLL (480MHz/10)

1 = USB clock 48MHz input from external GPIO0 pin, this pin

direction must set to input.

USB device clock enable bit

[14] USBD

0 = Disable USB device controller clock