Page 1

19-5472; Rev 1; 1/11

EVALUATION KIT

AVAILABLE

Power-Management ICs for

ICERA E400/E450 Platform

General Description

The MAX8982A/MAX8982X are complete power-management ICs for the latest LTE/WCDMA/GSM/GPRS/

EDGE data card based on the new ICERA platform (E400/

E450). The MAX8982A operates from a 4.1V to 5.5V

supply and contains four efficient step-down converters,

nine low dropout linear regulators (LDOs) to power all

RF and baseband circuitry, three current regulators with

programmable current up to 24mA and embedded flash

timers, and an I

regulator output voltages as well as on/off control for flexibility. The linear regulators provide greater than 60dB

PSRR, less than 45FV of output noise, and minimal cross

coupling noise between LDOs.

The MAX8982X operates from a 2.9V to 5.5V supply. The

MAX8982X has the same features as the MAX8982A,

except it does not have BUCK3, BUCK4, and LDO8.

All buck converters and LDOs are enabled/disabled by

either I

This feature provides more flexibility in system design.

2

C or PWR_REQ control signal after power-up.

Applications

GSM, GPRS, EDGE, WCDMA, and LTE

Data Card with New ICERA Platform (E400/E450)

Ordering Information

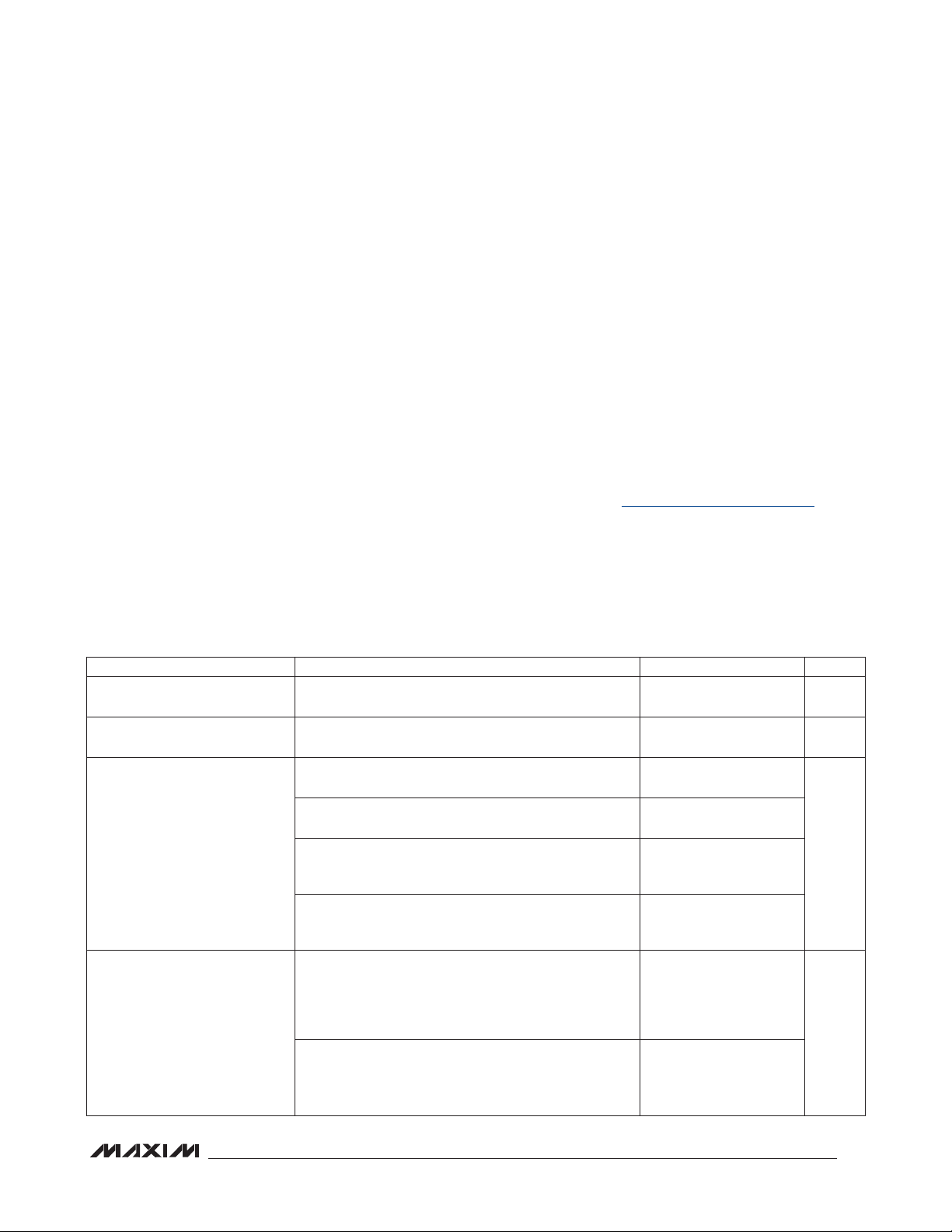

PART TEMP RANGE PIN-PACKAGE

MAX8982AEWO+T -40°C to +85°C 42 WLP

MAX8982XEWO+T -40°C to +85°C 42 WLP

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel. These devices have a minimum order inc-

rement of 1k pieces.

2

C serial interface to program individual

Features

S 4 High-Efficiency Buck Converters

0.9V at 1.2A for CORE with DVS Function (0.6V

to 1.2V in 25mV Steps) and Slew Rate Control

1.8V at 600mA for System IO

3.2V at 600mA for All LDO Inputs (2.9V to 3.65V

in 50mV Steps) (MAX8982A Only)

3.4V at 1.8A for GSM/WCDMA PA (3.0V to 3.75V

in 50mV Steps) (MAX8982A Only)

9 LDO Linear Regulators

S

2.7V at 300mA on LDO1 for RF Transceiver

1.8V at 150mA on LDO2 for RF Transceiver

2.8V at 150mA on LDO3 for Analogue BB

0.9V at 50mA on LDO4 for BB PLL with the

Separate Input for a Higher Efficiency

3.0V at 150mA on LDO5 for SD Card

2.7V at 150mA on LDO6 for TCXO

1.8V or 3.0V at 150mA on LDO7 for SIM

3.0V at 150mA on LDO8 for USB with the

Separate Input (MAX8982A Only)

0.9V at 50mA on LDO9 for BB with the Separate

Input for a Higher Efficiency

32 Programmable Voltage Options and External

S

Input on BUCK1 (0.9V Default) for DVS

S 16 Programmable Voltage Options for BUCK3

(MAX8982A Only)

S 16 Programmable Voltage Options on BUCK4

(MAX8982A Only)

S Programmable Voltage Options for All LDOs

(LDO8 for MAX8982A Only)

S BUCK2, BUCK3 (MAX8982A Only), LDO3, and

Internal 32kHz Clock Default On at Initial Startup

S Some Buck Converters and LDOs are Enabled by

Either I

After Power-Up

S 3 Current Regulators with 8 Dimming Current

Options Up to 24mA with Embedded Flash Timer

2

C or Power Request Control (PWR_REQ)

MAX8982A/MAX8982X

_______________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

Page 2

Power-Management ICs for

ICERA E400/E450 Platform

Table of ConTenTs

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

General Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Buck1 Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Buck2 Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Buck3 Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Buck4 Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

OUT1 (LDO1) Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

OUT2 (LDO2) Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

OUT3 (LDO3) Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

OUT4 (LDO4) Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

MAX8982A/MAX8982X

OUT5 (LDO5) Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

OUT6 (LDO6) Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

VSIM (LDO7) Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

OUT8 (LDO8) Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

OUT9 (LDO9) Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

RESET Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

IRQ Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Current Regulator Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Flash Timer Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

N32kHz Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Typical Operating Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Pin Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Power-On/Off Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

PWR_REQ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Active Discharge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

BUCK1, BUCK2, and BUCK3

Step-Down Converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Setting the Output Voltage on BUCK1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Dynamic Voltage Scaling (DVS) Function on Buck 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2

Page 3

Power-Management ICs for

ICERA E400/E450 Platform

Table of ConTenTs (ConTinued)

Ramp-Up/Down Slope Control on BUCK1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Setting the Output Voltage on BUCK2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Setting the Output Voltage on BUCK3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

BUCK4 Step-Down Converter for PA (Power Amplifier) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Setting the Output Voltage on BUCK4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Linear Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Reference Bypass (REFBP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Thermal Overload Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Undervoltage Lockout (UVLO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Overvoltage Protection (OVP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Power-On Reset (POR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Current Regulators (DR1, DR2, DR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Embedded Flash Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

IRQ Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

RESET SIGNAL to B/B Chipset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2

C Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

I

Bit Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

START and STOP Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

System Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Slave Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Write Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Read Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Applications Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Inductor Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Output Capacitor Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Input Capacitor Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

PCB Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Chip Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Package Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

MAX8982A/MAX8982X

3

Page 4

Power-Management ICs for

ICERA E400/E450 Platform

Table of ConTenTs (ConTinued)

List of Figures

Figure 1. MAX8982A Typical Application Circuit and Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 2. MAX8982X Typical Application Circuit and Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 3. Power-On/Off State Diagram with IN3 Connected to BUCK2 Output and IN4 Connected to IN1_.

Default PWR_REQ Regulators Are Shown.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 4. MAX8982A/MAX8982X Power-On Timing Diagram at Initial Startup with EN Connected to IN1_.

BUCK3 and OUT8 Are for the MAX8982A Only. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 5. MAX8982A/MAX8982X Power-On Timing Diagram in PWR_REQ ON Mode After Power-Up . . . . . . . . . . 37

Figure 6. Frequency Variation vs. Load Current with a 5V Input Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 7. DVS1 Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 8. BUCK1 Ramp-Up/Down Slope Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 9. POR State Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 10. Adding Series Resistors to Adjust LED Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 11. Flash Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

MAX8982A/MAX8982X

Figure 12. I

Figure 13. START and STOP Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 14. Master/Slave Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 15. I

Figure 16. I

Figure 17. Writing to the ICs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 18. Reading from the ICs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2

C Bit Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2

C Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2

C Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

List of Tables

Table 1. Summary of Power Supplies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 2. External Component List for Figure 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 3. External Component List for Figure 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Truth Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 4. BUCK1 Ramp-Up/Down Slope Control Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 5. Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 6. CHIPID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 7. IRQM Register (Interrupt Mask) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 8. IRQ Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 9. STATUS Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 10. LED1FT1 Register (LED1 (DR1) Flash Timer On/Off and TON Adjust) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 11. LED1FT2 Register (LED1 (DR1) Flash Timer t

Table 12. LED1FT3 Register (LED1 (DR1) Flash Timer t

Table 13. LED1FT4 Register (LED1 (DR1) Flash Timer t

4

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

1

Setting). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3

Page 5

Power-Management ICs for

ICERA E400/E450 Platform

Table of ConTenTs (ConTinued)

Table 14. LED1FT5 Register (LED1 (DR1) Flash Timer t4 Setting). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 15. LED1FT6 Register (LED1 (DR1) Flash Timer t

Table 16. LED2FT1 Register (LED2 (DR2) Flash Timer On/Off and t

Table 17. LED2FT2 Register (LED2 (DR2) Flash Timer t

Table 18. LED2FT3 Register (LED2 (DR2) Flash Timer t

Table 19. LED2FT4 Register (LED2 (DR2) Flash Timer t

Table 20. LED2FT5 Register (LED2 (DR2) Flash Timer t

Table 21. LED2FT6 Register (LED2 (DR2) Flash Timer t

Table 22. LED3FT1 Register (LED3 (DR3) Flash Timer On/Off and t

Table 23. LED3FT2 Register (LED3 (DR3) Flash Timer t

Table 24. LED3FT3 Register (LED3 (DR3) Flash Timer t

Table 25. LED3FT4 Register (LED3 (DR3) Flash Timer t

Table 26. LED3FT5 Register (LED3 (DR3) Flash Timer t

Table 27. LED3FT6 Register (LED3 (DR3) Flash Timer t

Table 28. BUCK1 Register (On/Off Control for BUCK1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 29. BUCK1DVS1 Register (Output Voltage Setting for BUCK1 (DVS1 = Low)) . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 30. BUCK1DVS2 Register (Output Voltage Setting for BUCK1 (DVS1 = High)) . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 31. BUCK2 Register (On/Off Control for BUCK2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 32. LDO1 Register (On/Off Control for LDO1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 33. LDO1V Register (Output Voltage Setting for OUT1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 34. LDO2 Register (ON/OFF Control for LDO2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 35. LDO2V Register (Output Voltage Setting for OUT2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 36. LDO3 Register (On/Off Control for LDO3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 37. LDO3V Register (Output Voltage Setting for OUT3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 38. LDO4 Register (On/Off Control for LDO4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 39. LDO4V Register (Output Voltage Setting for OUT4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 40. LDO5 Register (On/Off Control for LDO5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 41. LDO5V Register (Output Voltage Setting for OUT5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 42. LDO6 Register (On/Off Control for LDO6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 43. LDO6V Register (Output Voltage Setting for OUT6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 44. VSIM Register (On/Off Control for VSIM (LDO7)). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 45. VSIMV Register (Output Voltage Setting for VSIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 46. LDO8 Register (On/Off Control for LDO8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 47. LDO8V Register (Output Voltage Setting for OUT8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 48. LDO9 Register (On/Off Control for LDO9) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 49. LDO9V Register (Output Voltage Setting for OUT9) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 50. LED_EN Register (On/Off Control for 3 Current Regulators) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Setting). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

P

Adjust) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

ON

Setting). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

1

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

P

Adjust). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

ON

Setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4

Setting) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

P

MAX8982A/MAX8982X

5

Page 6

Power-Management ICs for

ICERA E400/E450 Platform

Table of ConTenTs (ConTinued)

Table 51. On/Off Register (On/Off Control for BUCK3, BUCK4, and the Internal 32kHz Clock) . . . . . . . . . . . . . . . . . 64

Table 52. BUCK3 Register (Output Voltage Setting for BUCK3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 53. BUCK4 Register (Output Voltage Setting for BUCK4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 54. CURRENTREG1 Register (Current Setting for Current Regulators DR1 and DR2) . . . . . . . . . . . . . . . . . . . 66

Table 55. CURRENTREG2 Register (Current Setting for Current Regulator DR3). . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 56. RAMP Register (Slope Setting for BUCK1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 57. BUCK1-4ADIS Register (Active Discharge Settings for BUCK1–BUCK4) . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 58. LDO1-8ADIS Register (Active Discharge Settings for LDO1–LDO8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 59. LDO9ADIS Register (Active Discharge Setting for LDO9) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 60. Recommended Inductors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

MAX8982A/MAX8982X

6

Page 7

Power-Management ICs for

ICERA E400/E450 Platform

ABSOLUTE MAXIMUM RATINGS

V

, V

DDA

REFBP, BUCK1, BUCK2, BUCK3, BUCK4,

EN to GND ...............................-0.3V to (V

SDA, SCL, PWR_REQ, DVS1, IRQ, RESET, IN3,

N32kHz to GND .............................. -0.3V to (V

OUT1, OUT2 to GND ............................. -0.3V to (V

OUT3, OUT5, OUT6, VSIM to GND ....... -0.3V to (V

OUT8 to GND ........................................... -0.3V to (V

OUT4, OUT9 to GND ............................... -0.3V to (V

PGND1, PGND2, PGND3, PGND4 to GND .........-0.3V to +0.3V

DR1, DR2, DR3 to GND ..........................-0.3V to (V

Note 1: LX1–LX4 have internal clamp diodes to PGND_, IN1A, and IN1B. Applications that forward bias this diode should take

Note 2: Package thermal resistance was obtained using the method described in JEDEC specification JESD51-7, using a four-

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

, IN4, IN1A, IN1B to GND ....................-0.3V to +6V

DDB

BUCK2

DDA

DDB

IN4

IN3

IN1_

+ 0.3V)

+ 0.3V)

+ 0.3V)

+ 0.3V)

+ 0.3V)

+ 0.3V)

+ 0.3V)

IN1A, VIN1B

care not to exceed the power dissipation limits of the device.

layer board. For detailed information on package thermal considerations, refer to www.maxim-ic/thermal-tutorial.

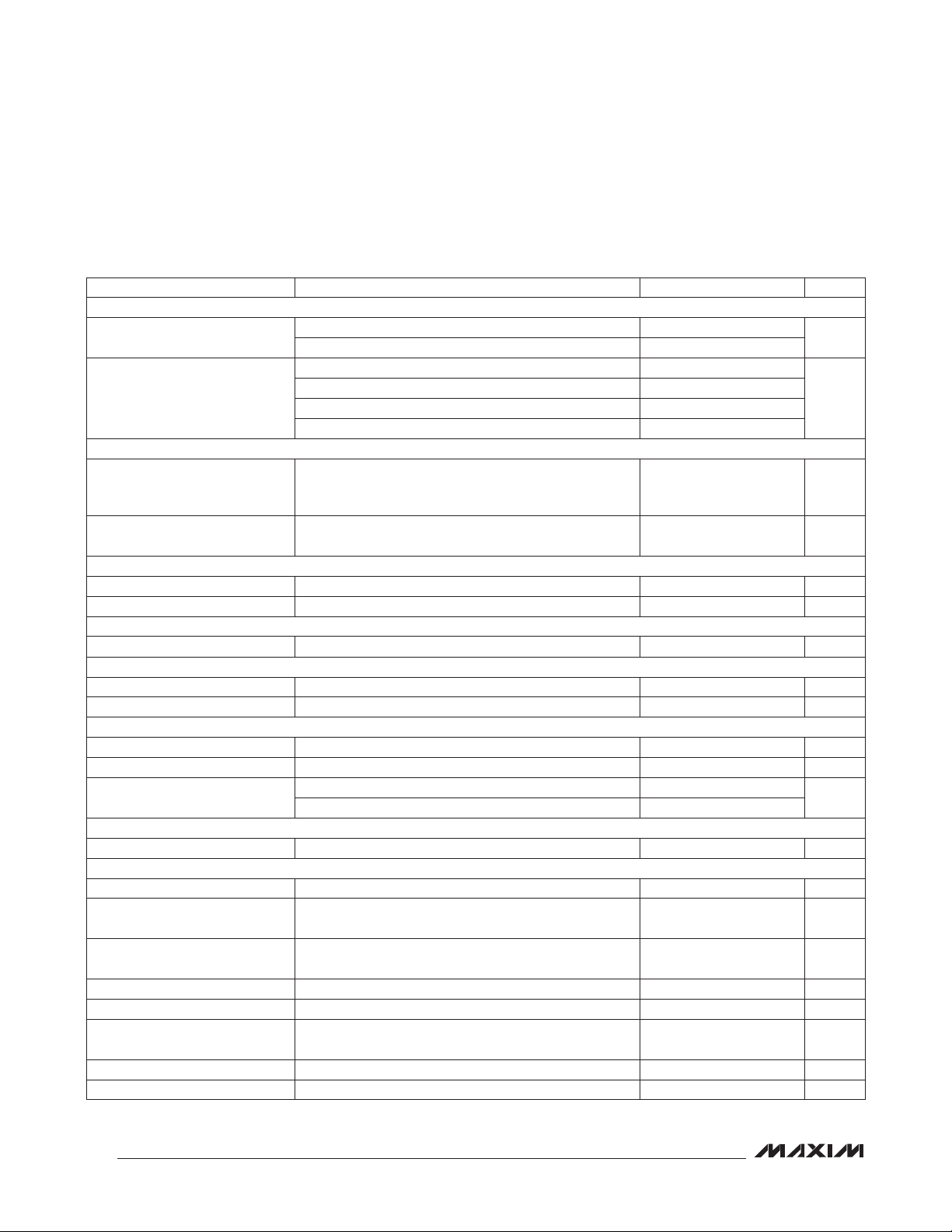

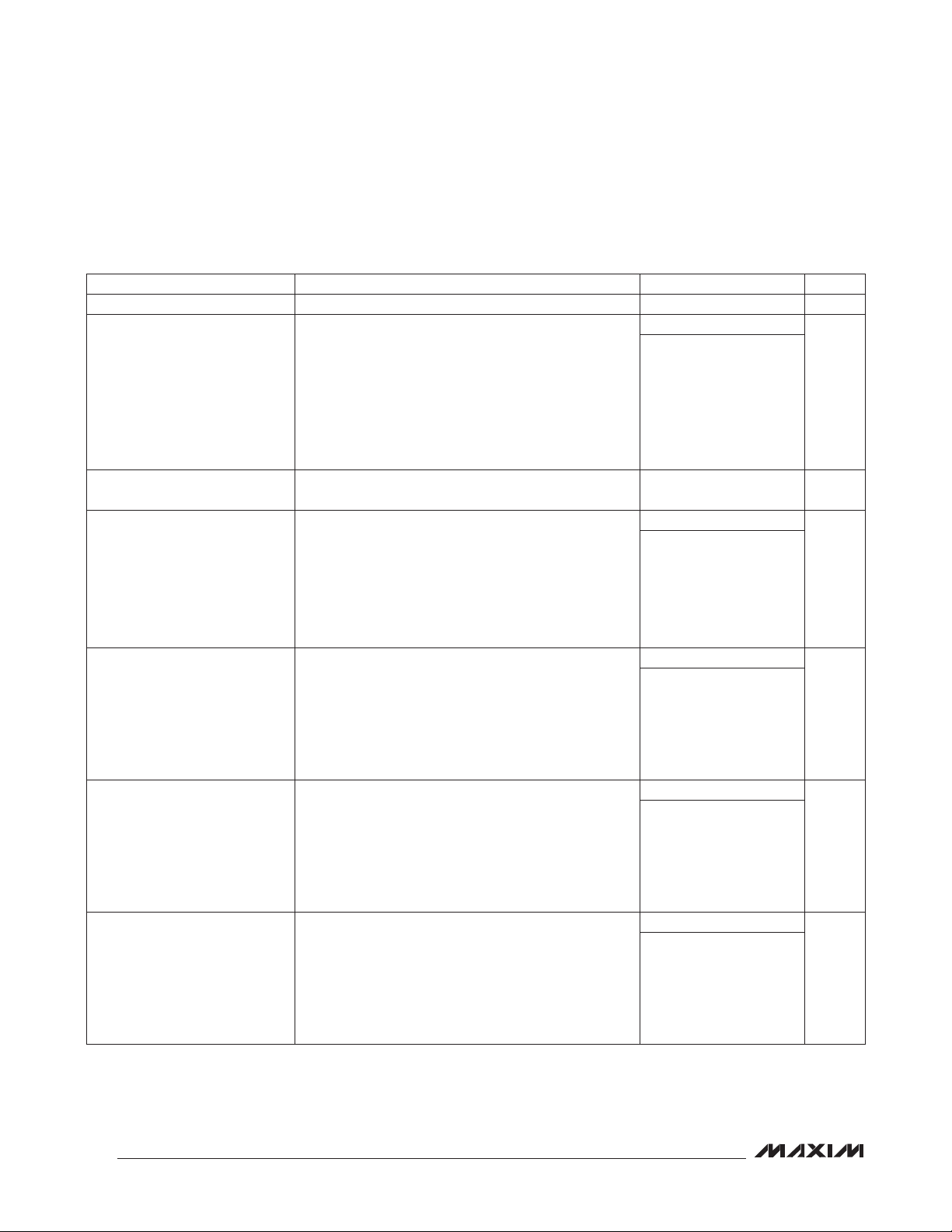

GENERAL ELECTRICAL CHARACTERISTICS

(MAX8982A: V

C

= 0.1FF, T

REFBP

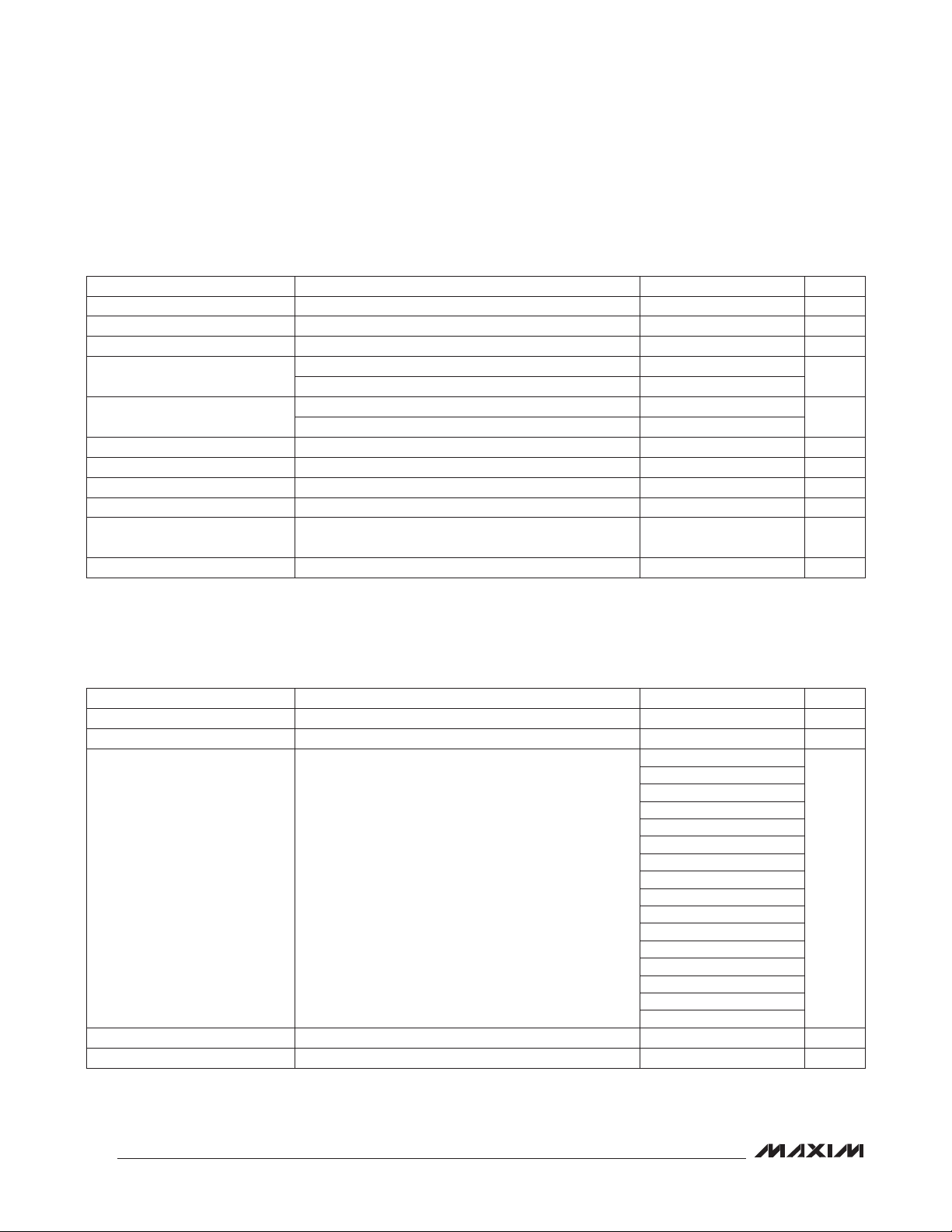

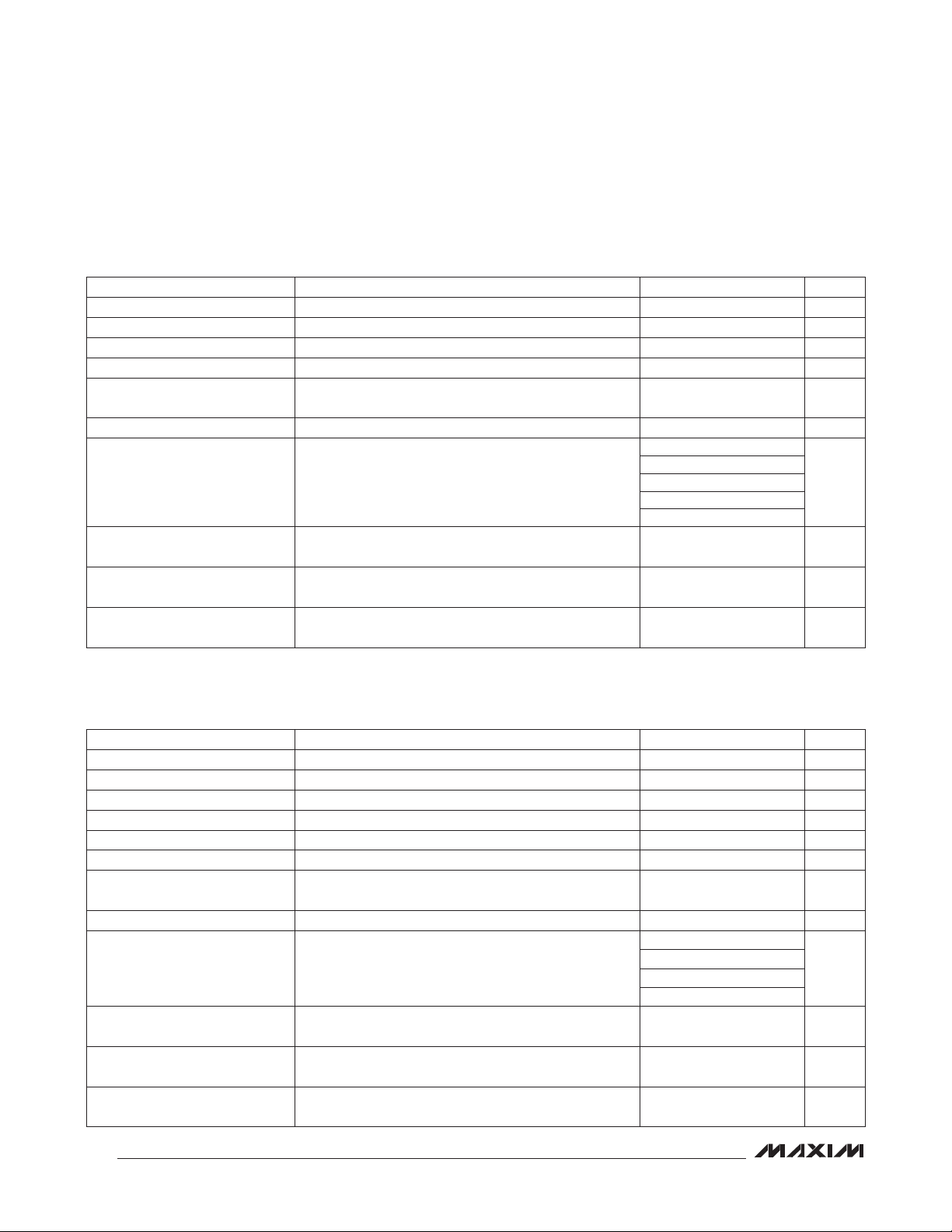

PARAMETER CONDITIONS MIN TYP MAX UNITS

IN1A, IN1B, IN4 ESD Protection

Shutdown Supply Current

(Note 4)

No Load Supply Current

Loaded Supply Current

IN1A

= V

A

= +5.0V and C

IN1B

= -40NC to +85NC. Typical values are at T

OUT1,2,3+CIN_

Module level ESD protection, in-circuit tested with 0.1FF

ceramic capacitor

EN = GND 10 FA

MAX8982A, V

output), all other regulators off

MAX8982X, V

other regulators off

MAX8982A, V

BUCK2 on (default output), BUCK3 on (default output),

all LDOs (except LDO8) default output ON

MAX8982X, V

BUCK2 on (default output), all LDOs (except LDO8)

default output ON

MAX8982A, V

(default output) with 200FA load, BUCK3 on (default

output), OUT3 on (default output) with 20FA load, OUT2

on (default output) with 100FA load, V

50FA load, OUT8 on (default output) with 100FA load

MAX8982X, V

(default output) with 200FA load, OUT3 on (default

output) with 20FA load, OUT2 on (default output) with

100FA load, V

= 1000FF, MAX8982X: V

= V

EN

IN1_

= V

EN

IN1_

= V

EN

IN1_

= V

EN

IN1_

= V

EN

IN1_

= V

EN

IN1_

= 3.0V with 50FA load

VSIM

LX1 Continuous Current (Note 1) ...................................1200mA

LX2, LX3 Continuous Current (Note 1) ............................600mA

LX4 Continuous Current (Note 1) ...................................1800mA

Continuous Power Dissipation (T

7x6 42-Bump WLP, 0.5mm Pitch, 3.75mm x 3.20mm

(derate 27.8mW/NC above +70NC) ................................ 2.22W

Junction-to-Ambient Thermal Resistance (B

(Note 2) ........................................................................36NC/W

Operating Temperature Range .......................... -40NC to +85NC

Junction Temperature .....................................................+150NC

Storage Temperature Range ............................ -65NC to +150NC

Soldering Temperature (reflow) ......................................+260NC

V

IN1A

= +25NC, unless otherwise noted.) (Note 3)

A

, BUCK3 and OUT3 on (default

, OUT3 on (default output), all

, BUCK1 on (default output),

, BUCK1 on (default output),

, 32kHz clock on, BUCK2 on

= 3.0V with

VSIM

, 32kHz clock on, BUCK2 on

=

IN1B

= +70NC)

A

= +3.3V and C

Q10 kV

300

300

600

600

1000

1000

)

JA

UT1,2,3+CIN_

O

= 20FF,

FA

FA

MAX8982A/MAX8982X

7

Page 8

Power-Management ICs for

ICERA E400/E450 Platform

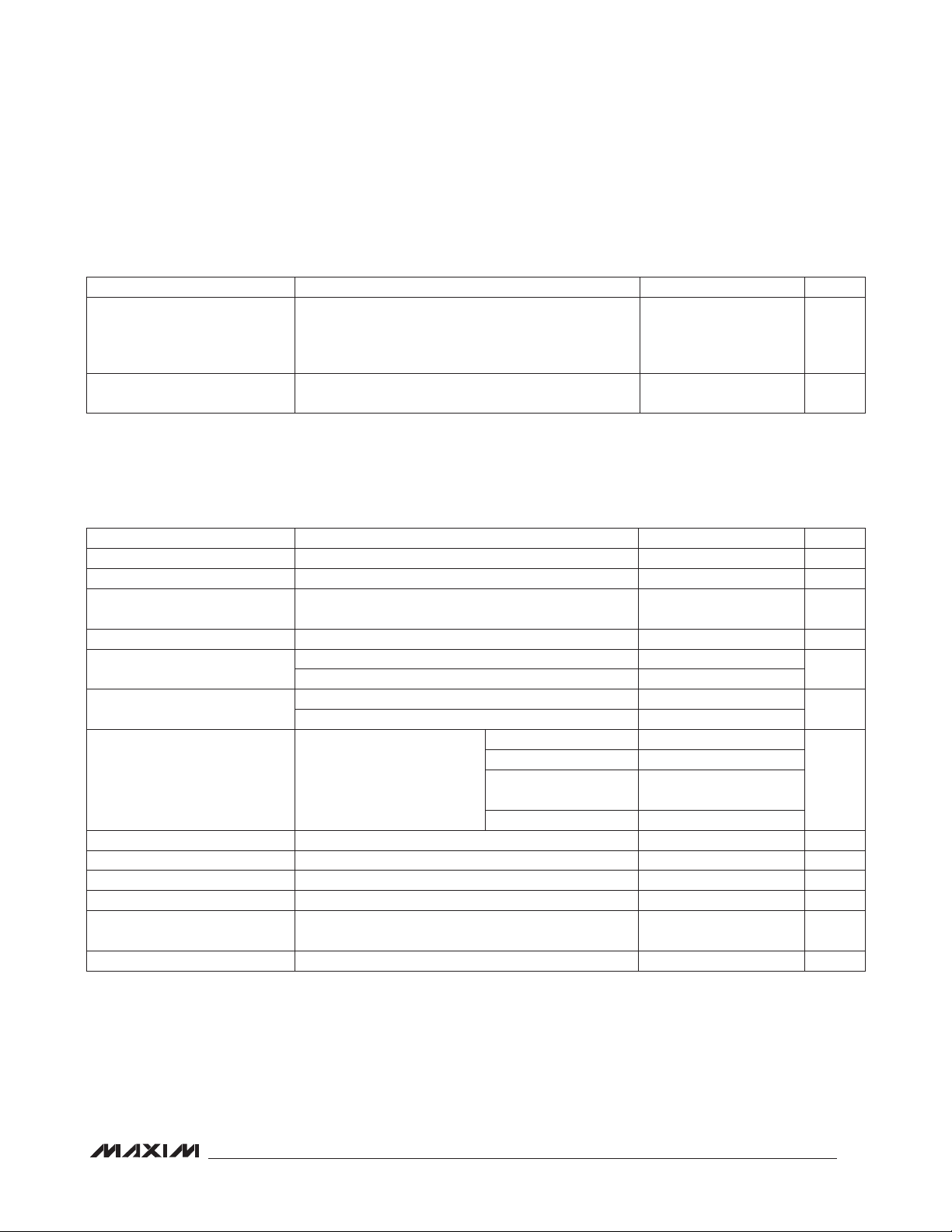

GENERAL ELECTRICAL CHARACTERISTICS (continued)

(MAX8982A: V

C

= 0.1FF, T

REFBP

PARAMETER CONDITIONS MIN TYP MAX UNITS

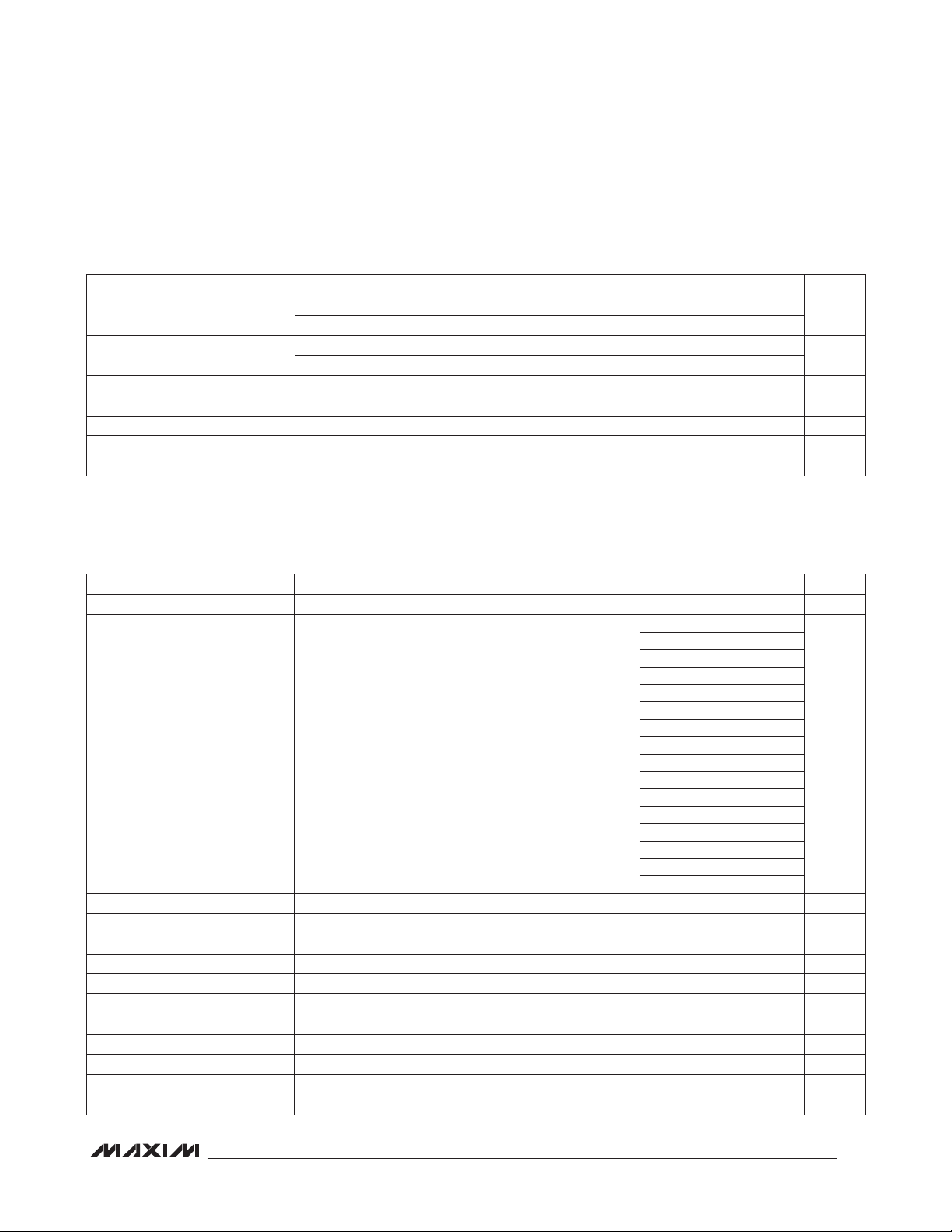

OPERATING VOLTAGE

IN1A, IN1B Operating Voltage

Undervoltage Lockout

OVERVOLTAGE LOCKOUT (OVP)

Overvoltage Lockout

(Shutdown All Outputs Including

LDO7)

IN1A, IN1B

Hysteresis

THERMAL SHUTDOWN

MAX8982A/MAX8982X

Threshold T

Hysteresis 10 NC

HOT TEMPERATURE DETECTION

Threshold Interrupt enabled, T

REFERENCE

REFBP Output Voltage 0 P I

Supply Rejection 4.1V P V

LOGIC AND CONTROL INPUTS (SDA, SCL, EN, DVS1, PWR_REQ)

Input Low Level T

Input High Level T

Logic Input Current

LOGIC AND CONTROL OUTPUTS

SDA Output Low Level I

2

I

C INTERFACE (V

Clock Frequency 400 kHz

Bus Free Time Between START

and STOP (t

Hold Time Repeated START

Condition (t

SCL Low Period (t

SCL High Period (t

Setup Time Repeated START

Condition (t

SDA Hold Time (t

SDA Setup Time (t

= V

IN1A

= -40NC to +85NC. Typical values are at T

A

Overvoltage

SCL

)

BUF

)

HD_STA

LOW

HIGH

)

SU_STA

HD_DAT

SU_DAT

= +5.0V and C

IN1B

= V

) 1.3 Fs

= 1.8V, Note 2, Figure 16)

SDA

) 0.6 Fs

) 0 Fs

) 100 ns

OUT1,2,3+CIN_

MAX8982A 4.1 5.5

MAX8982X 2.9 5.5

MAX8982A, V

MAX8982A, V

MAX8982X, V

MAX8982X, V

V

rising 5.75 5.93 V

IN1_

rising 160 NC

J

P 1FA 0.788 0.80 0.812 V

REFBP

IN1_

= +25NC 0.3 V

A

= +25NC 1.2 V

A

0V < V

0V < V

SDA

< 5.5V, TA = +25NC -1 +1

IN1_

< 5.5V, TA = +85NC 0.1

IN1_

= 6mA 0.4 V

= 1000FF, MAX8982X: V

= +25NC, unless otherwise noted.) (Note 3)

A

rising 3.5 3.8 4.1

IN1_

falling 3.5

IN1_

rising 2.5 2.7 2.9

IN1_

falling 2.4

IN1_

rising, typical hysteresis = +10NC +125 NC

J

P 5.5V 0.2 mV

IN1A

=

V

IN1B

= +3.3V and C

1.3 Fs

0.6 Fs

0.6 Fs

UT1,2,3+CIN_

O

250 mV

= 20FF,

V

V

FA

8

Page 9

Power-Management ICs for

ICERA E400/E450 Platform

GENERAL ELECTRICAL CHARACTERISTICS (continued)

(MAX8982A: V

C

= 0.1FF, T

REFBP

PARAMETER CONDITIONS MIN TYP MAX UNITS

Maximum Pulse Width of Spikes

that Must be Suppressed by the

Input Filter of Both SDA and SCL

Signals

Setup Time for STOP Condition

(t

SU_STO

)

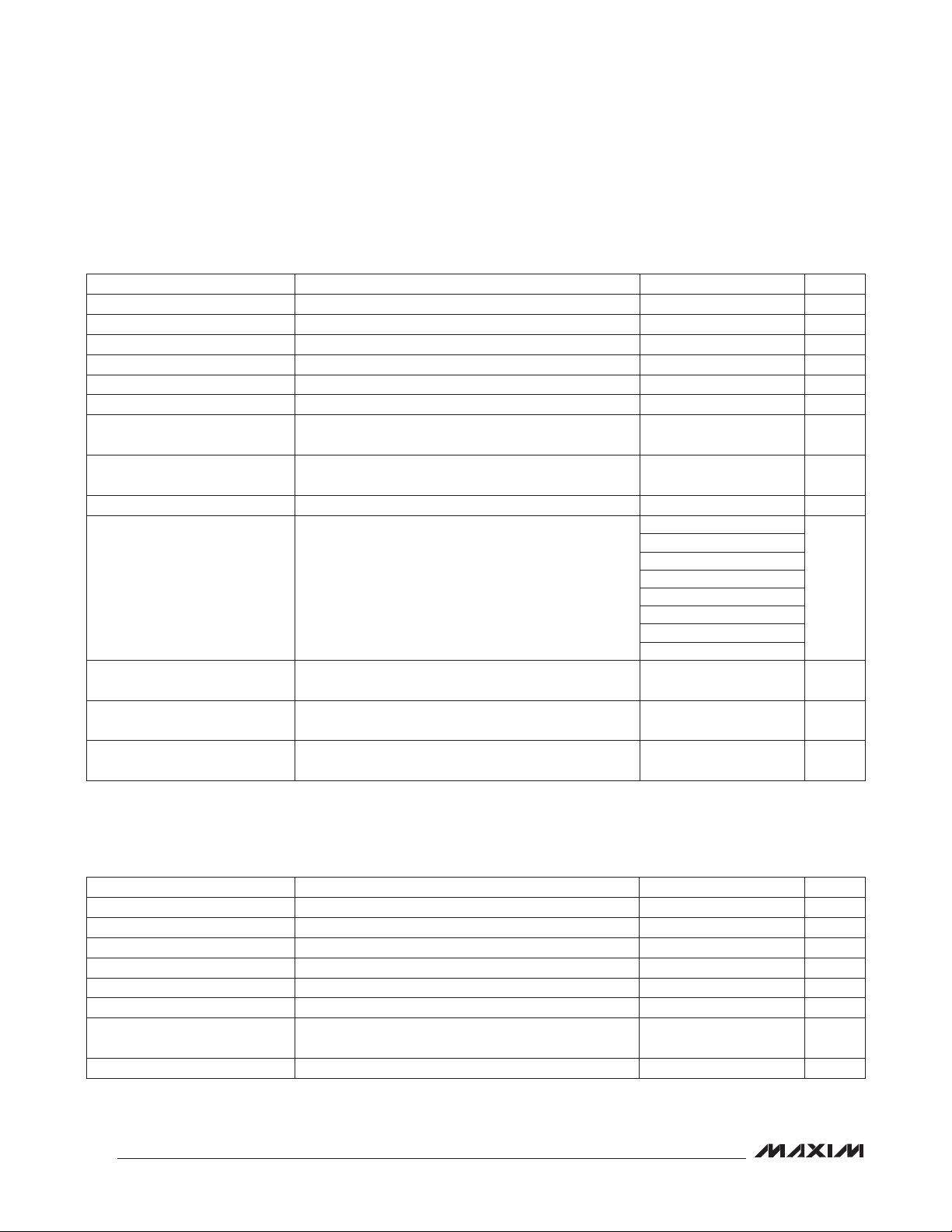

BUCK1 ELECTRICAL CHARACTERISTICS

(MAX8982A: V

C

= 0.1µF, C

REFBP

PARAMETER CONDITIONS MIN TYP MAX UNITS

Supply Current (Note 4) No load, no switching 65 FA

Default Output Voltage I

Output Voltage Accuracy

Maximum Output Current V

Current Limit

On-Resistance

Ramp-Up/Down Rate Control Same for both up and down

Rectifier Off Current Threshold 40 mA

Minimum On-Time t

Minimum Off-Time t

Efficiency (Note 4) V

Shutdown Output Resistance

(Active Discharge Resistance)

Output Load Regulation Equal to inductor DC resistance divided by 4 R

IN1A

IN1A

= V

A

= V

OUT

= +5.0V and C

IN1B

= -40NC to +85NC. Typical values are at T

= +5.0V and C

IN1B

= 10µF, L = 2.2µH, TA = -40NC to +85NC, unless otherwise noted. Typical values are at TA = +25NC.) (Note 3)

OUT1,2,3+CIN_

OUT1,2,3+CIN_

= 100mA 0.873 0.9 0.927 V

LOAD

I

= 100mA, V

LOAD

1.2V in production (0.6V to 1.2V in 25mV steps)

= 0.9V, TA = +25NC 1200 mA

BUCK1

pFET switch 1400 1800 2500

nFET rectifier 1000 1400 1900

pFET switch, I

nFET rectifier, I

ON

OFF

= 0.9V, I

BUCK1

2

I

C programmable, default OFF 1 kI

= 1000FF, MAX8982X: V

= +25NC, unless otherwise noted.) (Note 3)

A

= 1000µF, MAX8982X: V

tested at 0.6V, 0.775V, 1V,

BUCK1

= -150mA 0.3

LX1

= 150mA 0.15

LX1

RASD1[0:1] = 00 5

RASD1[0:1] = 01 10

RASD1[0:1] = 10

RASD1[0:1] = 11 25

= 400mA 85 %

LOAD

IN1A

IN1A

=

= V

V

= +3.3V and C

IN1B

= +3.3V and C

IN1B

0.6 Fs

-3 +3 %

UT1,2,3+CIN_

O

50 ns

OUT1,2,3+CIN_

12.5

(default)

40 ns

40 ns

/4 V/A

L

= 20FF,

= 20µF,

MAX8982A/MAX8982X

mA

I

mV/

Fs

9

Page 10

Power-Management ICs for

ICERA E400/E450 Platform

BUCK2 ELECTRICAL CHARACTERISTICS

(MAX8982A: V

C

= 0.1FF, C

REFBP

PARAMETER CONDITIONS MIN TYP MAX UNITS

Supply Current (Note 4) No load, no switching 26 FA

Output Voltage I

Output Current V

Current Limit

On-Resistance

Rectifier Off Current Threshold 40 mA

Minimum On-Time t

Minimum Off-Time t

Efficiency (Note 4) V

Shutdown Output Resistance

(Active Discharge Resistance)

Output Load Regulation Equal to inductor DC resistance divided by 4 R

MAX8982A/MAX8982X

IN1A

V

= +5.0V and C

IN1B

=

OUT

= 2.2FF, L = 1FH, T

OUT1,2,3+CIN_

= -40NC to +85NC, unless otherwise noted. Typical values are at T

A

= 100mA 1.746 1.8 1.854 V

LOAD

= 1.8V, TA = +25NC 600 mA

BUCK2

pFET switch 700 1100 1500

nFET rectifier 500 750 1200

pFET switch, I

nFET rectifier, I

ON

OFF

= 1.8V, I

BUCK2

2

I

C programmable, default ON 100

= 1000FF, MAX8982X: V

= -150mA 0.65

LX2

= 150mA 0.3

LX2

= 250mA 85 %

LOAD

IN1A

= V

= +3.3V and C

IN1B

OUT1,2,3+CIN_

= +25NC.) (Note 3)

A

70 ns

70 ns

/4 V/A

L

= 20FF,

mA

I

I

BUCK3 ELECTRICAL CHARACTERISTICS

(MAX8982A only, V

+85NC, unless otherwise noted. Typical values are at T

PARAMETER CONDITIONS MIN TYP MAX UNITS

Supply Current (Note 4) No load, no switching 40 FA

Default Output Voltage I

Programmable Output Voltage

Maximum Output Current V

Efficiency (Note 4) V

IN1A

=

V

IN1B

= +5.0V, C

LOAD

I

LOAD

programmable output voltage step = 50mV

OUT1,2,3+CIN_

= 100mA 3.10 3.2 3.29 V

= 100mA,

= 3.2V, TA = +25NC 600 mA

BUCK3

= 3.2V, I

BUCK3

= 1000FF, C

= +25NC.) (Note 3)

A

= 300mA 90 %

LOAD

REFBP

= 0.1FF, C

= 2.2FF, L = 2.2FH, T

OUT

2.90

2.95

3.00

3.05

3.10

3.15

3.20

3.25

3.30

3.35

3.40

3.45

3.50

3.55

3.60

3.65

= -40NC to

A

V

10

Page 11

Power-Management ICs for

ICERA E400/E450 Platform

BUCK3 ELECTRICAL CHARACTERISTICS (continued)

(MAX8982A only, V

+85NC, unless otherwise noted. Typical values are at T

PARAMETER CONDITIONS MIN TYP MAX UNITS

Current Limit

On-Resistance

Rectifier Off Current Threshold 80 mA

Minimum On-Time t

Minimum Off-Time t

Shutdown Output Resistance

(Active Discharge Resistance)

IN1A

=

V

IN1B

= +5.0V, C

pFET switch 700 1100 1500

nFET rectifier 500 750 1200

pFET switch, I

nFET rectifier, I

ON

OFF

2

I

OUT1,2,3+CIN_

LX3

LX3

C programmable, default off 1 kI

BUCK4 ELECTRICAL CHARACTERISTICS

(MAX8982A only, V

unless otherwise noted. Typical values are at T

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage I

Programmable Output Voltage

Efficiency (Note 4) V

Maximum Output Current 1800 mA

p-Channel On-Resistance I

n-Channel On-Resistance I

p-Channel Current-Limit Threshold 2700 mA

n-Channel Negative Current Limit 1500 mA

Maximum Duty Cycle 100 %

Minimum Duty Cycle 16.5 %

PWM Frequency f

Shutdown Output Resistance

(Active Discharge Resistance)

IN1A

= V

IN1B

= +5.0V, C

OUT1,2,3+CIN_

= +25NC.) (Note 3)

A

= 100mA 3.298 3.40 3.502 V

LOAD

= 100mA,

I

LOAD

programmable output voltage step = 50mV

= 3.4V, I

BUCK4

= 150mA 100 mI

LX4

= 150mA 100 mI

LX4

OSC

2

I

C programmable,

default off

= 1000FF, C

= +25NC.) (Note 3)

A

= -150mA 0.65

= 150mA 0.3

= 1000FF, C

= 500mA 90 %

LOAD

REFBP

REFBP

= 0.1FF, C

= 0.1FF, C

OUT

= 2.2FF, L = 2.2FH, T

OUT

70 ns

70 ns

= 20FF, L = 1FH, T

3.00

3.05

3.10

3.15

3.20

3.25

3.30

3.35

3.40

3.45

3.50

3.55

3.60

3.65

3.70

3.75

1.8 2.0 2.2 MHz

= -40NC to +85NC,

A

1 kI

= -40NC to

A

MAX8982A/MAX8982X

mA

I

V

11

Page 12

Power-Management ICs for

ICERA E400/E450 Platform

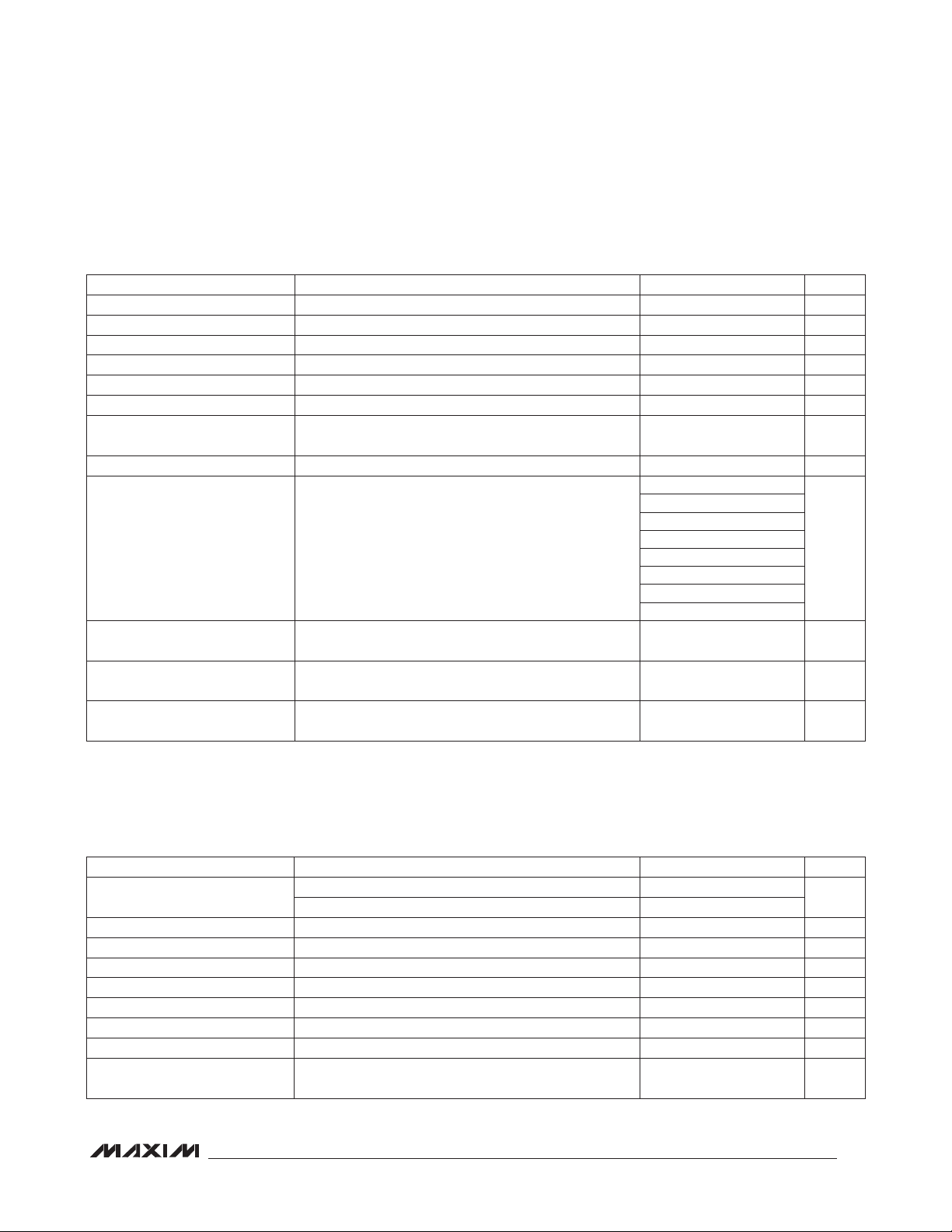

OUT1 (LDO1) ELECTRICAL CHARACTERISTICS

(MAX8982A: V

= -40NC to +85NC, unless otherwise noted. Typical values are at T

T

A

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage I

Maximum Output Current 300 mA

Current Limit (Note 4) V

Dropout Voltage (Note 4) I

Line Regulation 2.9V P V

Load Regulation 1mA < I

Transient Response

Power-Supply Rejection

DV

/DV

OUT

Output Noise Voltage 100Hz to 100kHz, I

MAX8982A/MAX8982X

Programmable Output Voltages I

Startup Time from Shutdown

(Note 4)

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

DDA

IN

= +3.2V and C

= 10FF, MAX8982X: V

VDD_

= 50mA 2.619 2.70 2.781 V

LOAD

= 90% of its regulation 310 550 940 mA

OUT1

LOAD

di/dt = I

= 200mA, T

DDA

LOAD

/0.1Fs, 1kHz < 1/T < 0.5MHz, where T is the

MAX

= +85NC 50 100 mV

A

P 3.65V, I

LOAD

< 300mA 12 mV

period of step load, 1mA to 300mA

f = 10Hz to 10kHz, I

LOAD

LOAD

= +3.3V and C

DDA

= +25NC.) (Note 3)

A

VDD_

= 20FF, C

REFBP

= 0.1FF, C

= 150mA 2.4 mV

50 mV

= 30mA 60 dB

= 30mA 45 FV

2.65

2.70

2.75

LOAD

= 50mA

2.80

2.85

2.90

2.95

3.00

= 300mA 40 100 Fs

I

LOAD

I

= 300mA 3 50 mV

LOAD

2

I

C programmable, default off 100

OUT1

= 4.7FF,

RMS

V

I

OUT2 (LDO2) ELECTRICAL CHARACTERISTICS

(MAX8982A: V

T

= -40NC to +85NC, unless otherwise noted. Typical values are at T

A

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage I

Maximum Output Current 150 mA

Current Limit (Note 4) V

Dropout Voltage (Note 4) I

Line Regulation 2.9V P V

Load Regulation 50FA < I

Power-Supply Rejection

DV

/DV

OUT

Output Noise Voltage 100Hz to 100kHz, I

12

DDA

IN

= +3.2V and C

= 10FF, MAX8982X: V

VDD_

= 50mA 1.746 1.80 1.854 V

LOAD

= 90% of its nominal regulation voltage 165 360 650 mA

OUT2

= 100mA, TA =+85NC 150 300 mV

LOAD

P 3.65V, I

DDA

< 150mA 25 mV

LOAD

f = 10Hz to 10kHz, I

LOAD

LOAD

LOAD

= +3.3V and C

DDA

= +25NC.) (Note 3)

A

VDD_

= 20FF, C

REFBP

= 0.1FF, C

= 100mA 2.4 mV

= 30mA 60 dB

= 30mA 45 FV

OUT2

= 1FF,

RMS

Page 13

Power-Management ICs for

ICERA E400/E450 Platform

OUT2 (LDO2) ELECTRICAL CHARACTERISTICS (continued)

(MAX8982A: V

T

= -40NC to +85NC, unless otherwise noted. Typical values are at T

A

PARAMETER CONDITION MIN TYP MAX UNITS

Programmable Output Voltages I

Startup Time from Shutdown

(Note 4)

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

OUT3 (LDO3) ELECTRICAL CHARACTERISTICS

(MAX8982A: V

T

= -40NC to +85NC, unless otherwise noted. Typical values are at TA = +25NC.) (Note 3)

A

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage I

Maximum Output Current 150 mA

Current Limit (Note 4) V

Dropout Voltage I

Line Regulation 3.2V P V

Load Regulation 50FA < I

Power-Supply Rejection

DV

/DV

OUT

Output Noise Voltage 100Hz to 100kHz, I

Programmable Output Voltage I

Startup Time from Shutdown

(Note 4)

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

DDA

DDB

IN

= +3.2V and C

= +3.2V and C

= 10FF, MAX8982X: V

VDD_

= 50mA

LOAD

= 150mA 40 100 Fs

I

LOAD

I

= 150mA 3 50 mV

LOAD

2

I

C programmable, default off 100

= 10FF, MAX8982X: V

VDD_

= 50mA 2.716 2.800 2.884 V

LOAD

= 90% of its regulation 165 360 650 mA

OUT3

= 100mA, T

LOAD

DDB

LOAD

f = 10Hz to 10kHz, I

= 50mA

LOAD

= 150mA 100 Fs

I

LOAD

I

= 150mA 50 mV

LOAD

2

I

C programmable, default off 100

= +85NC 150 300 mV

A

P 3.65V, I

< 150mA 25 mV

LOAD

LOAD

LOAD

= +3.3V and C

DDA

= +25NC.) (Note 3)

A

= +3.3V and C

DDB

= 100mA 2.4 mV

= 30mA 60 dB

= 30mA 45 FV

VDD_

VDD_

= 20FF, C

= 20FF, C

REFBP

EFBP

R

= 0.1FF, C

1.50

1.80

2.70

1.70

= 0.1FF, C

2.65

2.70

2.75

2.80

2.85

2.90

2.95

3.00

OUT2

OUT3

MAX8982A/MAX8982X

= 1FF,

V

I

= 1FF,

RMS

V

I

13

Page 14

Power-Management ICs for

ICERA E400/E450 Platform

OUT4 (LDO4) ELECTRICAL CHARACTERISTICS

(MAX8982A/MAX8982X: V

wise noted. Typical values are at T

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage I

Maximum Output Current 50 mA

Current Limit (Note 4) V

Load Regulation 50FA < I

Power-Supply Rejection

DV

/DV

OUT

IN

Output Noise Voltage 100Hz to 100kHz, I

Programmable Output Voltage I

Startup Time from Shutdown

(Note 4)

MAX8982A/MAX8982X

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

IN3

= V

= 1.8V, C

BUCK2

= +25NC.) (Note 3)

A

LOAD

OUT4

f = 10Hz to 10kHz, I

LOAD

I

LOAD

I

LOAD

2

I

C programmable, default off 100

= 2.2FF, C

IN3

REFBP

= 0.1FF, C

= 2.2FF, TA = -40NC to +85NC, unless other-

OUT4

= 10mA 0.873 0.9 0.927 V

= 90% of its regulation 55 120 220 mA

< 10mA 25 mV

LOAD

= 10mA 60 dB

LOAD

= 10mA 45 FV

LOAD

0.80

0.90

= 10mA

1.00

1.10

1.20

= 50mA 100 Fs

= 50mA 50 mV

RMS

V

I

OUT5 (LDO5) ELECTRICAL CHARACTERISTICS

(MAX8982A: V

T

= -40NC to +85NC, unless otherwise noted. Typical values are at TA = +25NC.) (Note 3)

A

= +3.2V and C

DDB

= 10FF, MAX8982X: V

VDD_

= +3.3V and C

DDB

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage I

= 50mA 2.91 3.00 3.09 V

LOAD

Maximum Output Current 150 mA

Current Limit (Note 4) V

Dropout Voltage (Note 4) I

Line Regulation 3.2V P V

Load Regulation 50FA < I

Power-Supply Rejection

DV

/DV

OUT

IN

Output Noise Voltage 100Hz to 100kHz, I

Programmable Output Voltage I

Startup Time from Shutdown

(Note 4)

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

= 90% of its regulation 165 360 650 mA

OUT5

= 100mA, T

LOAD

DDB

LOAD

f = 10Hz to 10kHz, I

= 50mA, V

LOAD

= 150mA 100 Fs

I

LOAD

I

= 150mA 50 mV

LOAD

2

I

C programmable, default off 100

= +85NC 150 300 mV

A

P 3.65V, I

< 150mA, V

LOAD

DDB

= 100mA 2.4 mV

LOAD

= 2.8V 25 mV

OUT

= 30mA 60 dB

LOAD

= 30mA 45 FV

= 3.4V for V

OUT

= 3.2V

VDD_

= 20FF, C

REFBP

= 0.1FF, C

2.80

2.90

3.00

3.20

OUT5

= 1FF,

RMS

V

I

14

Page 15

Power-Management ICs for

ICERA E400/E450 Platform

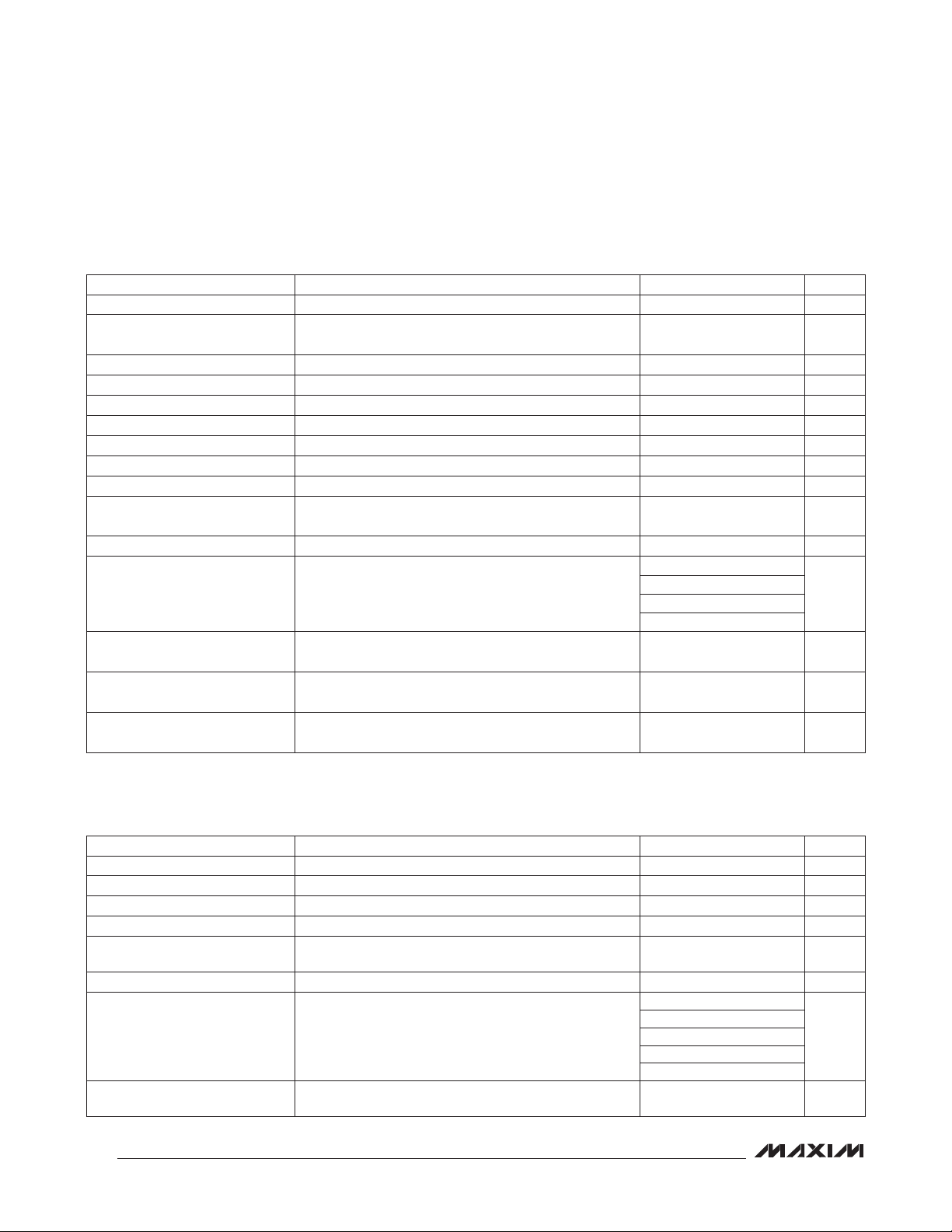

OUT6 (LDO6) ELECTRICAL CHARACTERISTICS

(MAX8982A: V

T

= -40NC to +85NC, unless otherwise noted. Typical values are at TA = +25NC.) (Note 3)

A

= +3.2V and C

DDB

= 10FF, MAX8982X: V

VDD_

= +3.3V and C

DDB

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage I

= 50mA 2.619 2.70 2.781 V

LOAD

Maximum Output Current 150 mA

Current Limit (Note 4) V

Dropout Voltage (Note 4) I

Line Regulation 2.90V P V

Load Regulation 50FA < I

Power-Supply Rejection

DV

/DV

OUT

IN

Output Noise Voltage 100Hz to 100kHz, I

Programmable Output Voltage I

Startup Time from Shutdown

(Note 4)

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

= 90% of its regulation 165 360 650 mA

OUT6

= 100mA, T

LOAD

DDB

LOAD

f = 10Hz to 10kHz, I

= 50mA

LOAD

= 150mA 100 Fs

I

LOAD

I

= 150mA 50 mV

LOAD

2

I

C programmable, default off 100

= +85NC 150 300 mV

A

P 3.65V, I

= 100mA 2.2 mV

LOAD

< 150mA 25 mV

= 30mA 60 dB

LOAD

= 30mA 45 FV

LOAD

VDD_

= 20FF, C

REFBP

= 0.1FF, C

2.65

2.70

2.75

2.80

2.85

2.90

2.95

3.00

O

UT6

= 1FF,

MAX8982A/MAX8982X

RMS

V

I

VSIM (LDO7) ELECTRICAL CHARACTERISTICS

(MAX8982A: V

T

= -40NC to +85NC, unless otherwise noted. Typical values are at TA = +25NC.) (Note 3)

A

PARAMETER CONDITION MIN TYP MAX UNITS

Output Voltage

Maximum Output Current 2.9V P V

Current Limit (Note 4) V

Dropout Voltage (Note 4) I

Line Regulation 2.9V P V

Load Regulation 50FA < I

Power-Supply Rejection f = 10kHz, I

Output Noise Voltage 100Hz to 100kHz, I

VSIM Discharge Resistance

(Active Discharge Resistance)

= +3.2V and C

DDB

= 10FF, MAX8982X: V

VDD_

50FA < I

50FA < I

= 90% of 1.8V mode 165 360 650 mA

VSIM

= 20mA, 3V mode 120 200 mV

LOAD

2

I

C programmable, default off 100

< 20mA, 1.8V mode 1.746 1.80 1.854

LOAD

< 20mA, 3.0V mode (default) 2.91 3.00 3.09

LOAD

P 3.65V, 1.8V mode 150 mA

DDB

P 3.65V, I

DDB

< 20mA (1.8V mode) 25 mV

LOAD

LOAD

LOAD

= 10mA 57 dB

LOAD

= +3.3V and C

DDB

= 50FA (1.8V mode) 0.1 mV

= 10mA 80 FV

VDD_

= 20FF, C

REFBP

= 0.1FF, C

O

= 1FF,

UT

V

I

15

Page 16

Power-Management ICs for

ICERA E400/E450 Platform

OUT8 (LDO8) ELECTRICAL CHARACTERISTICS

(MAX8982A only, V

Typical values are at T

PARAMETER CONDITION MIN TYP MAX UNITS

Input Operating Range Guaranteed by output voltage accuracy 3.0 5.5 V

Overvoltage Lockout

(Shutdown LDO8 Output)

Overvoltage Hysteresis 250 mV

Default Output Voltage I

Maximum Output Current 150 mA

Current Limit (Note 4) V

Dropout Voltage (Note 4) 100mA, T

Line Regulation 3.4V P V

Load Regulation 50FA < I

Power-Supply Rejection

DV

/DV

OUT

IN

Output Noise Voltage (RMS) 100Hz to 100kHz, I

MAX8982A/MAX8982X

Programmable Output Voltage I

Startup Time from Shutdown

(Note 4)

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

IN4

= V

= +5.0V, C

IN1_

= +25NC.) (Note 3)

A

= 1.0FF, C

IN4

V

rising, V

IN4

= 50mA 2.91 3.00 3.09 V

LOAD

= 90% of its regulation 165 360 650 mA

OUT8

A

IN4

LOAD

= V

IN1_

= +85NC 150 300 mV

P 5.5V, V

< 150mA 25 mV

f = 10Hz to 10kHz, I

= 0.1FF, C

REFBP

IN4

= 3.1V, I

OUT8

= 30mA 60 dB

LOAD

= 30mA 45 FV

LOAD

= 1FF, TA = -40NC to +85NC, unless otherwise noted.

OUT8

5.75 5.93 V

= 100mA 2.2 mV

LOAD

3.00

LOAD

= 50mA

3.10

3.20

3.30

= 150mA 100 Fs

I

LOAD

I

= 150mA 50 mV

LOAD

2

I

C programmable, default off 100

RMS

V

I

OUT9 (LDO9) ELECTRICAL CHARACTERISTICS

(MAX8982A/MAX8982X: V

wise noted. Typical values are at T

PARAMETER CONDITION MIN TYP MAX UNITS

Default Output Voltage ±I

Maximum Output Current 50 mA

Current Limit (Note 4) V

Load Regulation 50FA < I

Power-Supply Rejection

/DV

DV

OUT

IN

Output Noise Voltage 100Hz to 100kHz, I

Programmable Output Voltage I

Startup Time from Shutdown

(Note 4)

16

IN3

= V

= 1.8V, C

BUCK2

= +25NC.) (Note 3)

A

LOAD

OUT9

f = 10Hz to 10kHz, I

LOAD

I

LOAD

IN3

= 10mA, V

= 2.2FF, C

1.8V 0.873 0.900 0.927 V

IN3

=

REFBP

= 0.1FF, C

= 2.2FF, TA = -40NC to +85NC, unless other-

OUT9

= 90% of its regulation 55 120 220 mA

< 50mA 25 mV

LOAD

= 10mA 60 dB

LOAD

= 10mA 45 FV

LOAD

0.80

0.90

= 10mA

1.00

1.10

1.20

= 50mA 100 Fs

RMS

V

Page 17

Power-Management ICs for

ICERA E400/E450 Platform

OUT9 (LDO9) ELECTRICAL CHARACTERISTICS (continued)

(MAX8982A/MAX8982X: V

wise noted. Typical values are at T

PARAMETER CONDITION MIN TYP MAX UNITS

Startup Transient Overshoot

(Note 4)

Shutdown Output Impedance

(Active Discharge Resistance)

RESET ELECTRICAL CHARACTERISTICS

(MAX8982A: V

-40NC to +85NC, unless otherwise noted. Typical values are at T

PARAMETER CONDITION MIN TYP MAX UNITS

Output High Voltage Internal logic supply I

Output Low Voltage Internal logic supply I

RESET Enabled (Note 4) From BUCK2 enable (Figure 4) 625 Fs

RESET Disabled (Note 4) With respect to IRQ = low 26 78 Fs

Pullup Resistance to BUCK2 8 14 22 kI

IN1A

= V

= V

IN3

BUCK2

= +25NC.) (Note 3)

A

I

LOAD

2

C programmable, default off 100

I

= +5V, MAX8982X: V

IN1B

= 1.8V, C

= 50mA 50 mV

= 2.2FF, C

IN3

= V

IN1A

= 0.1FF, C

REFBP

= +3.3V, V

IN1B

= +25NC.) (Note 3)

A

SOURCE

SINK

= 0FA

= 500FA 0.3 V

BUCK2

= 2.2FF, TA = -40NC to +85NC, unless other-

OUT9

= 1.8V, C

BUCK2

V

BUCK2

- 0.3V

= 2.2FF, C

REFBP

= 0.1FF, TA =

MAX8982A/MAX8982X

I

V

IRQ ELECTRICAL CHARACTERISTICS

(MAX8982A: V

T

= -40NC to +85NC. Typical values are at T

A

PARAMETER CONDITION MIN TYP MAX UNITS

Output High Voltage Internal logic supply I

Output Low Voltage Internal logic supply I

Pullup Resistance to BUCK2 100 200 400 kI

IN1A

= V

= +5.0V, MAX8982X: V

IN1B

= V

IN1A

= +25NC, unless otherwise specified.) (Note 3)

A

SOURCE

SINK

= +3.3V, V

IN1B

= 0FA

= 500FA 0.3 V

BUCK2

= 1.8V, C

BUCK2

V

BUCK2

- 0.3V

= 2.2FF, C

REFBP

= 0.1FF,

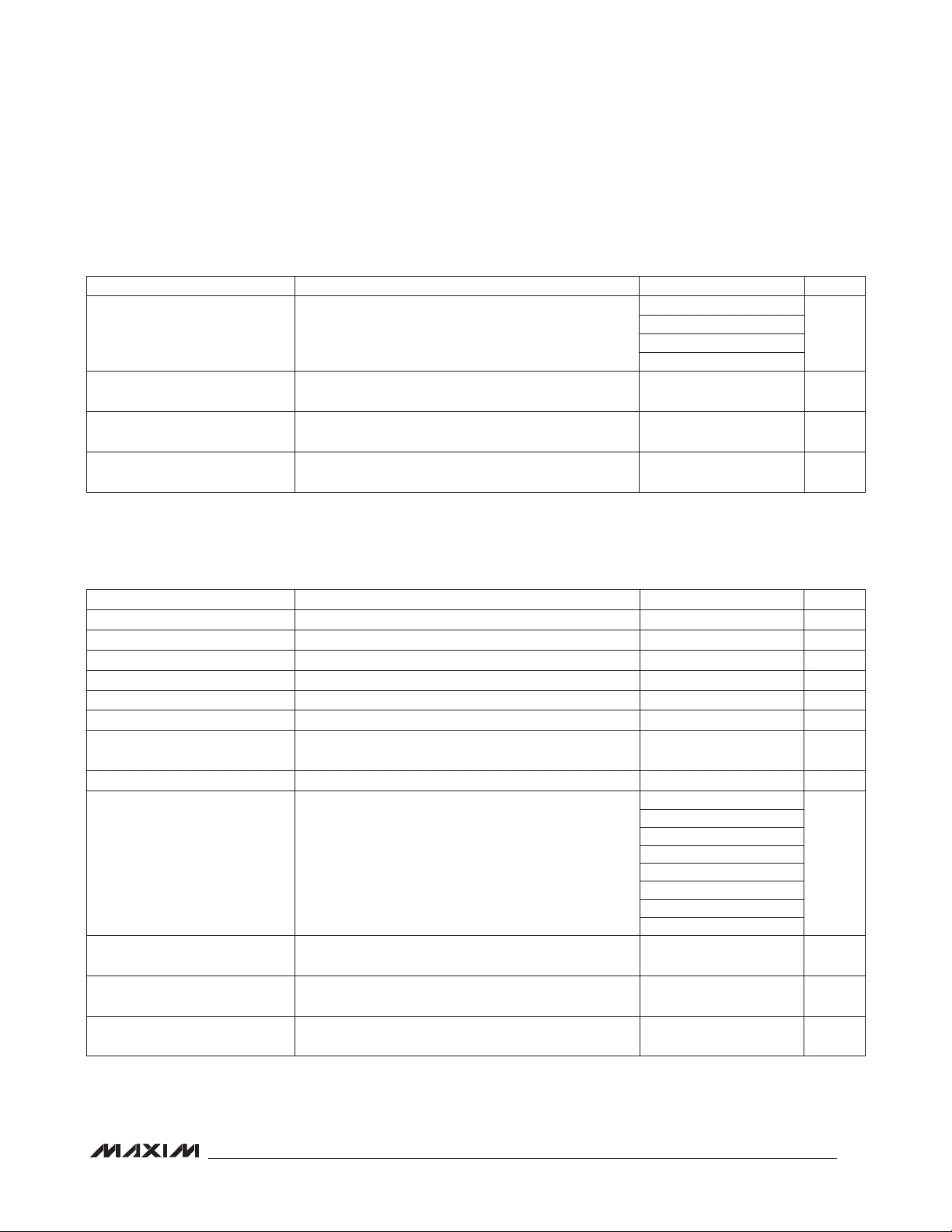

CURRENT REGULATOR ELECTRICAL CHARACTERISTICS

(MAX8982A: V

T

= -40NC to +85NC, unless otherwise noted. Typical values are at T

A

PARAMETER CONDITION MIN TYP MAX UNITS

DR_ Sink Current Range 3 24 mA

DR_ Current Sink Programmable

DR_ Sink Current Accuracy

(Note 4)

Voltage Drop I

V

DR_

IN1A

= V

= +5V and V

IN1B

= 3.2V, MAX8982X: V

DD_

DR_[2:0] = 000 3

DR_[2:0] = 001 6

DR_[2:0] = 010 9

DR_[2:0] = 011 12

DR_[2:0] = 100 15

DR_[2:0] = 101 18

DR_[2:0] = 110 21

DR_[2:0] = 111 (default) 24

= +25NC -10 +10

T

A

= -40NC to +85NC -15 +15

T

A

= 24mA 60 120 mV

DR_

= V

IN1A

= +25NC.) (Note 3)

A

= +3.3V and V

IN1B

= 3.3V, C

DD_

REFBP

= 0.1FF,

V

mA

%

17

Page 18

Power-Management ICs for

ICERA E400/E450 Platform

FLASH TIMER ELECTRICAL CHARACTERISTICS

(MAX8982A: V

= -40NC to +85NC, unless otherwise noted. Typical values are at T

T

A

PARAMETER CONDITIONS MIN TYP MAX UNITS

Flash Timer Resolution 25 ms

Pattern Period, t

= V

IN1A

7-bit programmable in 25ms steps

P

= +5V and V

IN1B

= +3.2V, MAX8982X: V

DD_

= V

IN1A

= +25NC.) (Note 4, Figure 11)

A

= +3.3V and V

IN1B

= +3.3V, C

DD_

0 3175

0 (0000000)

25 (0000001)

50

75

.

.

3175 (1111111)

REFBP

= 0.1FF,

ms

Number of Programmable On

Threshold

MAX8982A/MAX8982X

Time for Flash to Turn On, t

Time for Flash to Turn On, t

Time for Flash to Turn On, t

Time for Flash to Turn On, t

7-bit programmable in 25ms steps

1

7-bit programmable in 25ms steps

2

7-bit programmable in 25ms steps

3

7-bit programmable in 25ms steps

4

4

0 3175

0 (0000000)

25 (0000001)

50

.

.

3175 (1111111)

0 3175

0 (0000000)

25 (0000001)

50

.

.

3175 (1111111)

0 3175

0 (0000000)

25 (0000001)

50

.

.

3175 (1111111)

0 3175

0 (0000000)

25 (0000001)

50

.

.

3175 (1111111)

ms

ms

ms

ms

18

Page 19

Power-Management ICs for

ICERA E400/E450 Platform

FLASH TIMER ELECTRICAL CHARACTERISTICS (continued)

(MAX8982A: V

= -40NC to +85NC, unless otherwise noted. Typical values are at T

T

A

PARAMETER CONDITIONS MIN TYP MAX UNITS

Programmable On-Time, t

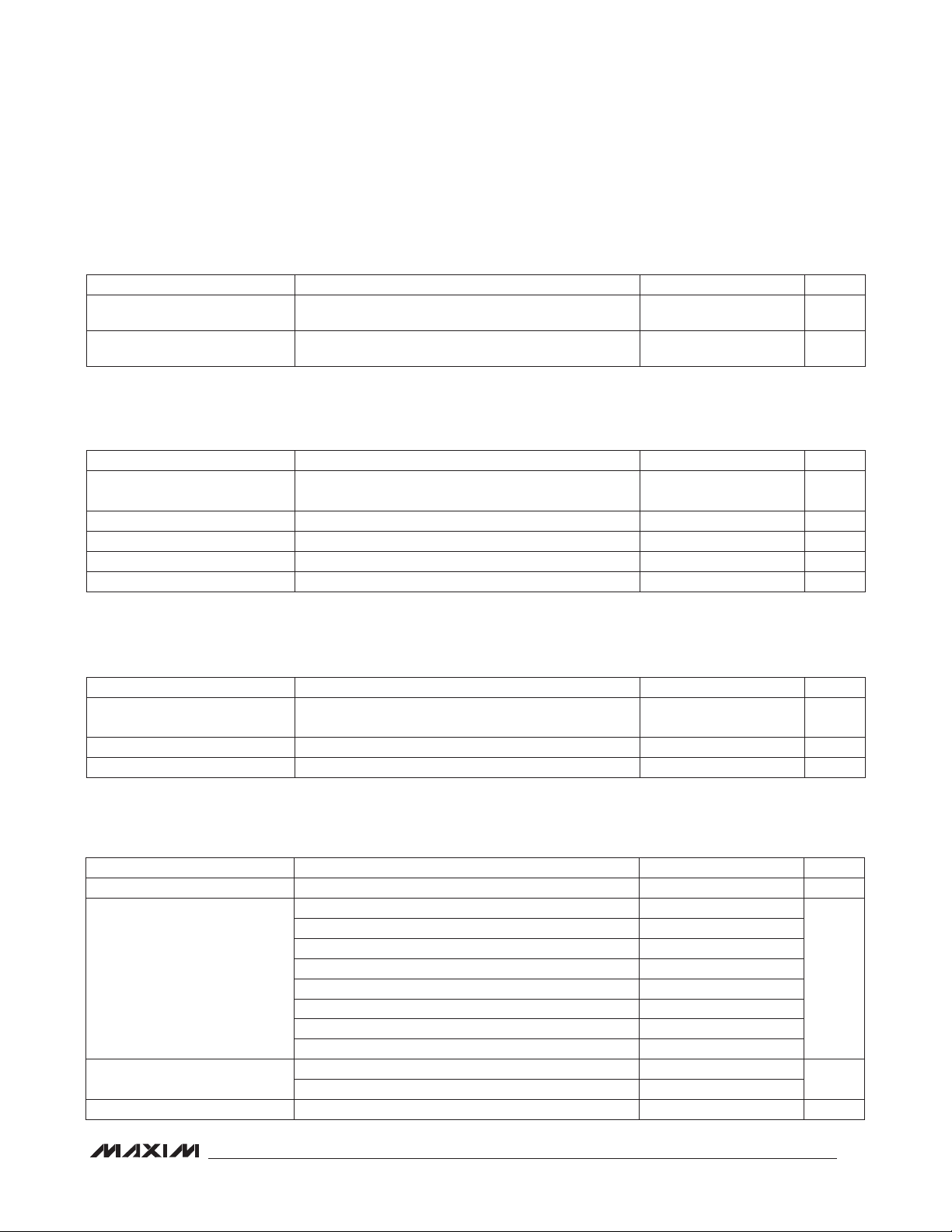

N32KHZ ELECTRICAL CHARACTERISTICS

(MAX8982A: V

unless otherwise noted. Typical values are at T

PARAMETER CONDITION MIN TYP MAX UNITS

Output High Voltage Internal logic supply I

Output Low Voltage Internal logic supply I

Output Duty Cycle 30 50 70 %

Output Frequency Range Including initial startup, 20% tolerance 25.6 32 38.4 kHz

Startup Time From BUCK2 enable (Figure 4) 225 Fs

Edge Jitter (Note 4) 10 ns

Note 3: Limits are 100% production tested at T

teed by design.

Note 4: Guaranteed by design, not production tested.

= V

IN1A

= +3.2V, MAX8982X: V

DD_

= +5V and V

IN1B

ON

= +3.2V, MAX8982X: V

DD_

= V

IN1A

= +25NC.) (Note 4, Figure 11)

A

= +3.3V and V

IN1B

4-bit programmable in 25ms steps, same for each flash

timer

= +3.3V, V

DD_

= +25NC.) (Note 3)

A

= +25NC, unless otherwise noted. Limits over the temperature range are guaran-

A

= 1.8V, C

BUCK2

SOURCE

SINK

= 2mA

= 2mA 0.45 V

BUCK2

= 2.2FF, C

= +3.3V, C

DD_

25 400

25 (0000)

50 (0001)

75

.

.

400 (1111)

= 0.1FF, T

REFBP

BUCK2

V

- 0.45V

= 0.1FF,

REFBP

= -40NC to +85NC,

A

MAX8982A/MAX8982X

ms

V

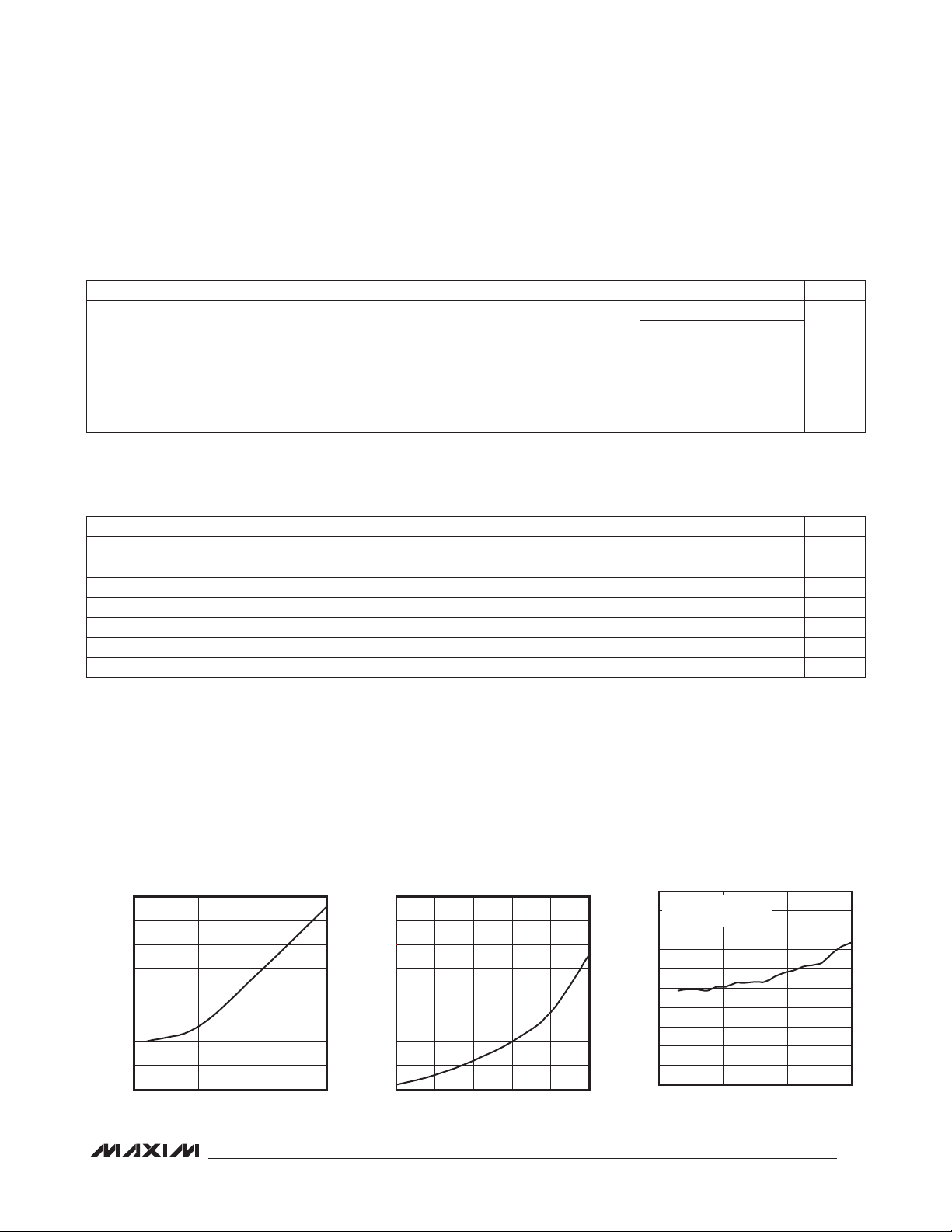

Typical Operating Characteristics

(MAX8982A: V

Circuits of Figures 2 and 3, unless otherwise noted. Typical values are at T

unless otherwise noted. Limits over the temperature range are guaranteed by design.

4.0

3.5

3.0

2.5

2.0

1.5

SHUTDOWN CURRENT (µA)

1.0

0.5

0

4.0 5.5

IN1A

= V

= 5V, MAX8982X: V

IN1B

SHUTDOWN CURRENT

vs. INPUT VOLTAGE (MAX8982A)

5.04.5

INPUT VOLTAGE (V)

= V

IN1A

4.0

3.5

MAX8982A toc01

3.0

2.5

2.0

1.5

SHUTDOWN CURRENT (µA)

1.0

0.5

0

3.0 5.5

IN1B

= V

DDA

= V

= V

DDB

= +25°C. Limits are 100% production tested at T

A

SHUTDOWN CURRENT

vs. INPUT VOLTAGE (MAX8982X)

5.04.53.5 4.0

INPUT VOLTAGE (V)

= 3.3V, C

IN4

)

REFBP

300

280

260

MAX8982A toc02

240

220

200

180

160

SHUTDOWN CURRENT (µA)

140

120

100

4.0 5.5

= 0.1µF, TA = -40°C to +85°C,

= +25NC,

A

NO LOAD SUPPLY CURRENT

vs. INPUT VOLTAGE (MAX8982A)

BUCK3, OUT3 ON

ALL OTHER OUTPUTS OFF

5.04.5

INPUT VOLTAGE (V)

19

MAX8982A toc03

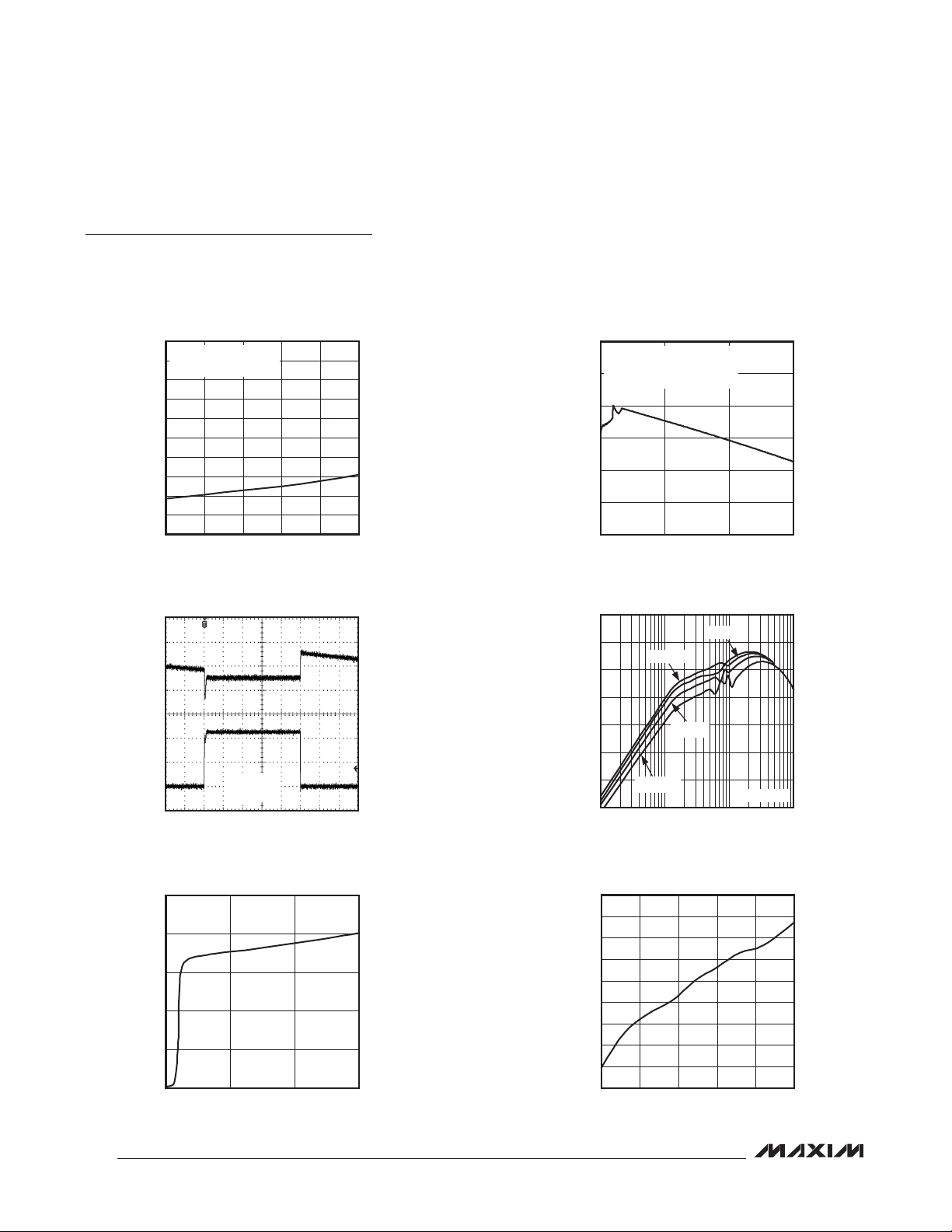

Page 20

Power-Management ICs for

ICERA E400/E450 Platform

Typical Operating Characteristics (continued)

(MAX8982A: V

Circuits of Figures 2 and 3, unless otherwise noted. Typical values are at T

unless otherwise noted. Limits over the temperature range are guaranteed by design.

300

280

260

240

220

200

180

160

SHUTDOWN CURRENT (uA)

140

120

100

MAX8982A/MAX8982X

V

BUCK1

IN1A

= V

= 5V, MAX8982X: V

IN1B

NO LOAD SUPPLY CURRENT

vs. INPUT VOLTAGE (MAX8982X)

OUT3 ON

ALL OTHER OUTPUTS OFF

4.54.03.53.0 5.5

INPUT VOLTAGE (V)

BUCK1 LOAD TRANSIENT

5.0

MAX8982A toc06

= V

IN1A

MAX8982A toc04

AC-COUPLED

200mV/div

IN1B

= V

DDA

= V

= V

DDB

= +25°C. Limits are 100% production tested at T

A

= 3.3V, C

IN4

= 0.1µF, TA = -40°C to +85°C,

REFBP

)

BUCK1 LOAD REGULATION

0.950

L = 2.2µH, HITACHI METALS LTD

KSLI-252012AG-2R2

0.925

DCR = 100m

0.900

0.875

0.850

OUTPUT VOLTAGE (V)

0.825

0.800

0 1200

I

700200

LOAD CURRENT (mA)

BUCK1 EFFICIENCY

vs. LOAD CURRENT

100

V

= 4.5V

90

80

V

= 4.1V

IN

IN

A

MAX8982A toc05

MAX8982A toc07

= +25NC,

V

= 1V

I

BUCK1

OUT

C

OUT

= 10µF

100µs/div

BUCK1 SWITCHING FREQUENCY

vs. LOAD CURRENT

2.5

2.0

1.5

1.0

SWITCHING FREQUENCY (MHz)

0.5

0

0 1200

LOAD CURRENT (mA)

70

1.2A

1mA

60

EFFICIENCY (%)

50

40

30

1 1000

V

= 5V

IN

V

= 5.5V

IN

LOAD CURRENT (mA)

10010

V

= 0.9V

OUT

BUCK1 SWITCHING FREQUENCY

vs. TEMPERATURE

2.200

2.150

MAX8982A toc08

700200

2.100

2.050

2.000

1.950

1.900

1.850

SWITCHING FREQUENCY (MHz)

1.800

1.750

-40 85

TEMPERATURE (°C)

603510-15

MAX8982A toc09

20

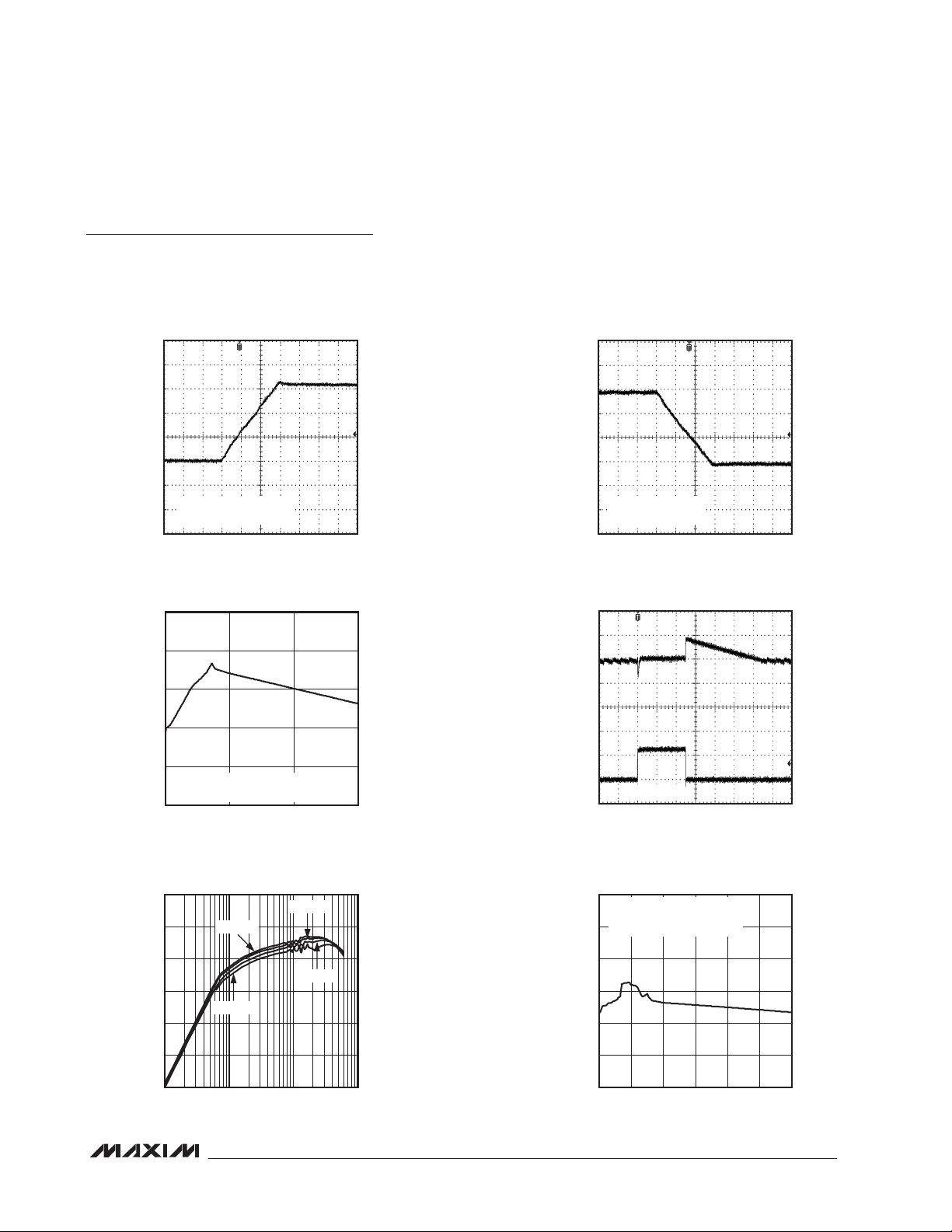

Page 21

Power-Management ICs for

ICERA E400/E450 Platform

Typical Operating Characteristics (continued)

(MAX8982A: V

Circuits of Figures 2 and 3, unless otherwise noted. Typical values are at T

unless otherwise noted. Limits over the temperature range are guaranteed by design.

IN1A

= V

= 5V, MAX8982X: V

IN1B

IN1A

= V

IN1B

= V

DDA

= V

= V

DDB

= +25°C. Limits are 100% production tested at T

A

= 3.3V, C

IN4

= 0.1µF, TA = -40°C to +85°C,

REFBP

)

= +25NC,

A

MAX8982A/MAX8982X

BUCK1 RAMP-UP TRANSITION

V

BUCK1

NO LOAD

12.5mV/µs RAMP RATE

20µs/div

BUCK2 LOAD REGULATION

1.820

1.800

1.780

1.760

OUTPUT VOLTAGE (V)

1.740

L = 1.0µH, MURATA LQM2MPN1R0NG0

I

DCR = 85m

1.720

0 600

LOAD CURRENT (mA)

MAX8982A toc10

1.2V

0.6V

MAX8982A toc12

400200

V

BUCK1

V

BUCK2

I

BUCK2

BUCK1 RAMP-DOWN TRANSITION

I

= 1.2A

OUT

12.5mV/µs RAMP RATE

20µs/div

BUCK2 LOAD TRANSIENT

V

= 1.8V

OUT

40µs/div

MAX8982A toc11

MAX8982A toc13

1.2V

0.6V

AC-COUPLED

100mV/div

600mA

1mA

100

90

80

70

EFFICIENCY (%)

60

50

40

BUCK2 EFFICIENCY

vs. LOAD CURRENT

V

IN

V

= 4.1V

IN

V

= 5.5V

IN

100101 1000

LOAD CURRENT (mA)

= 4.5V

V

IN

= 5V

MAX8982A toc14

BUCK3 LOAD REGULATION

(MAX8982A ONLY)

3.300

L = 2.2µH, HITACHI METALS LTD

KSLI-252012AG-2R2

3.250

3.200

3.150

3.100

OUTPUT VOLTAGE (V)

3.050

3.000

0 600

DCR = 100m

I

LOAD CURRENT (mA)

MAX8982A toc15

500400300200100

21

Page 22

Power-Management ICs for

ICERA E400/E450 Platform

Typical Operating Characteristics (continued)

(MAX8982A: V

Circuits of Figures 2 and 3, unless otherwise noted. Typical values are at T

unless otherwise noted. Limits over the temperature range are guaranteed by design.

V

BUCK3

I

BUCK3

MAX8982A/MAX8982X

3.410

3.400

3.390

3.380

3.370

3.360

OUTPUT VOLTAGE (V)

3.350

3.340

3.330

IN1A

= V

= 5V, MAX8982X: V

IN1B

BUCK3 LOAD TRANSIENT

(MAX8982A ONLY)

20µs/div

V

OUT

C

OUT

MAX8982A toc16

= 3.2V

= 10µF

BUCK4 LOAD REGULATION

(MAX8982A ONLY)

L = TAIYO YUDEN NR3015T1R0N

I

DCR = 30m

0 600

LOAD CURRENT (mA)

500400100 200 300

= V

IN1A

AC-COUPLED

100mV/div

600mA

1mA

MAX8982A toc18

IN1B

= V

DDA

= V

= V

DDB

= +25°C. Limits are 100% production tested at T

A

= 3.3V, C

IN4

= 0.1µF, TA = -40°C to +85°C,

REFBP

)

BUCK3 EFFICIENCY

vs. LOAD CURRENT (MAX8982A ONLY)

100

EFFICIENCY (%)

V

= 4.1V

95

90

85

80

75

70

65

60

55

50

IN

V

= 5.5V

IN

1 1000

LOAD CURRENT (mA)

BUCK4 LOAD TRANSIENT (MAX8982A ONLY)

V

BUCK4

I

BUCK4

V

= 3.4V

OUT

1mA TO 1.5A

20µs/div

V

= 4.5V

IN

V

= 5V

IN

V

= 3.2V

OUT

10010

MAX8982A toc19

A

MAX8982A toc17

AC-COUPLED

50mV/div

1.5A

1mA

= +25NC,

22

BUCK4 EFFICIENCY vs. LOAD CURRENT

(MAX8982A ONLY)

100

90

80

70

60

50

EFFICIENCY (%)

40

30

20

10

1 10,000

LOAD CURRENT (mA)

VIN = 4.1V

VIN = 4.5V

VIN = 5V

VIN = 5.5V

BUCK4 SWITCHING FREQUENCY

vs. LOAD CURRENT (MAX8982A ONLY)

2.5

MAX8982A toc20

V

= 3.4V

OUT

100010010

2.0

1.5

1.0

SWITCHING FREQUENCY (MHz)

0.5

0

0 600

LOAD CURRENT (mA)

400200

MAX8982A toc21

Page 23

Power-Management ICs for

ICERA E400/E450 Platform

Typical Operating Characteristics (continued)

(MAX8982A: V

Circuits of Figures 2 and 3, unless otherwise noted. Typical values are at T

unless otherwise noted. Limits over the temperature range are guaranteed by design.

IN1A

= V

= 5V, MAX8982X: V

IN1B

IN1A

= V

IN1B

= V

DDA

= V

= V

DDB

= +25°C. Limits are 100% production tested at T

A

= 3.3V, C

IN4

= 0.1µF, TA = -40°C to +85°C,

REFBP

)

= +25NC,

A

MAX8982A/MAX8982X

BUCK4 SWITCHING FREQUENCY

vs. TEMPERATURE (MAX8982A ONLY)

2.20

2.15

2.10

2.05

2.00

1.95

1.90

SWITCHING FREQUENCY (MHz)

1.85

1.80

-40 85

TEMPERATURE (°C)

LDO3 LOAD REGULATION

2.820

2.815

2.810

2.805

2.800

OUTPUT VOLTAGE (V)

LDO1 LOAD REGULATION

2.705

2.704

MAX8982A toc22

2.703

2.702

2.701

2.700

OUTPUT VOLTAGE (V)

2.699

2.698

6035-15 10

2.697

0 300

LOAD CURRENT (mA)

25020050 100 150

1.812

1.810

1.808

MAX8982A toc23

1.806

1.804

1.802

1.800

1.798

OUTPUT VOLTAGE (V)

1.796

1.794

1.792

1.790

LDO2 LOAD REGULATION

0 150

LOAD CURRENT (mA)

10050

MAX8982A toc24

LDO4 LOAD REGULATION

0.903

MAX8982A toc25

0.902

OUTPUT VOLTAGE (V)

MAX8982A toc26

2.795

2.790

0 150

LOAD CURRENT (mA)

10050

LDO5 LOAD REGULATION

3.020

3.010

3.000

2.990

2.980

OUTPUT VOLTAGE (V)

2.970

2.960

0 150

LOAD CURRENT (mA)

10050

MAX8982A toc27

0.901

0 50

LOAD CURRENT (mA)

LDO6 LOAD REGULATION

2.720

2.715

2.710

2.705

2.700

OUTPUT VOLTAGE (V)

2.695

2.690

0 150

LOAD CURRENT (mA)

40302010

MAX8982A toc28

10050

23

Page 24

Power-Management ICs for

ICERA E400/E450 Platform

Typical Operating Characteristics (continued)

(MAX8982A: V

Circuits of Figures 2 and 3, unless otherwise noted. Typical values are at T

unless otherwise noted. Limits over the temperature range are guaranteed by design.

3.025

3.020

3.015

3.010

3.005

3.000

OUTPUT VOLTAGE (V)

2.995

2.990

2.985

MAX8982A/MAX8982X

0.902

IN1A

= V

= 5V, MAX8982X: V

IN1B

LDO7 LOAD REGULATION

0 100

LOAD CURRENT (mA)

806020 40

LDO9 LOAD REGULATION

IN1A

MAX8982A toc29

MAX8982A toc31

= V

IN1B

= V

DDA

= V

= V

DDB

= +25°C. Limits are 100% production tested at T

A

= 3.3V, C

IN4

= 0.1µF, TA = -40°C to +85°C,

REFBP

)

LDO8 LOAD REGULATION

(MAX8982A ONLY)

3.020

3.015

3.010

3.005

3.000

OUTPUT VOLTAGE (V)

2.995

2.990

2.985

0 100

LOAD CURRENT (mA)

80604020

LED CURRENT ACCURACY

vs. LED CURRENT SETTING

10

8

6

4

LUMEX SML-LX2832SISUGSBC

LED3

A

MAX8982A toc30

MAX8982A toc32

= +25NC,

24

OUTPUT VOLTAGE (V)

0.900

0 100

LOAD CURRENT (mA)

LED FLASH WAVEFORMS

I

LED2

I

LED3

1s/div

80604020

MAX8982A toc33

24mA

0A

24mA

0A

2

0

LED CURRENT ACCURACY (%)

-2

-4

0 25

LED CURRENT (mA)

OVERVOLTAGE PROTECTION

V

IN_

V

BUCK1

V

BUCK2

V

LDO1

400µs/div

LED2

2015105

MAX8982A toc34

5V/div

0V

1V/div

0V

1V/div

0V

2V/div

0V

Page 25

Power-Management ICs for

ICERA E400/E450 Platform

Pin Configurations

TOP VIEW

(BUMP ON BOTTOM)

1 2 3 4 5 6 7

MAX8982A

MAX8982A/MAX8982X

N32

A

kHz

B

OUT4 DR1 DR2 OUT8 VSIM

C

IN3 DR3

LX2

D

PGND2

E

F

PGND1

OUT9 GND

RESET IRQ

BUCK2

BUCK1

LX1 IN4 IN1A

DVS1 SDA

EN IN1B LX4

OUT5

WLP

REF

BP

OUT6 OUT2

SCL OUT1

PWR_

REQ

LX4

OUT3

V

DDB

BUCK3

BUCK4

PGND4 PGND4

V

LX3

PGND3

DDA

25

Page 26

Power-Management ICs for

ICERA E400/E450 Platform

Pin Configurations (continued)

TOP VIEW

(BUMP ON BOTTOM)

1 2 3 4 5 6 7

MAX8982X

N32

A

kHz

B

OUT4 DR1 DR2 DNC

C

IN3 DR3

OUT9 GND

RESET IRQ

MAX8982A/MAX8982X

LX2

D

PGND2 PGND3

E

F

PGND1

BUCK2

BUCK1

LX1 IN4 IN1A

DVS1 SDA

EN IN1B DNC DNC

REF

BP

OUT5

WLP

OUT6 OUT2

VSIM

SCL OUT1

PWR_

REQ

DNC

OUT3

V

DDB

DNC DNC

PGND4 PGND4

V

DDA

26

Page 27

Power-Management ICs for

ICERA E400/E450 Platform

Pin Description

MAX8982A/MAX8982X

PIN

GROUND

A3 GND GND Analog Ground

F1 PGND1 PGND1 Power Ground for BUCK1

E1 PGND2 PGND2 Power Ground for BUCK2

E7 PGND3 PGND3 Power Ground for BUCK3

F6, F7 PGND4 PGND4 Power Ground for BUCK4

INPUT SUPPLY

F4

E4 IN1B IN1B Input Supply to the IC. Connect IN1B to IN1A.

C1 IN3 IN3

F3

B7

B6

BUCK CONVERTERS

F2 LX1 LX1

D1 LX2 LX2

D7

E5, F5

E2 BUCK1 BUCK1 BUCK1 Output Feedback

D2 BUCK2 BUCK2 BUCK2 Output Feedback

D6

E6

MAX8982A MAX8982X

NAME

Input Supply to the IC. The operating voltage range for the MAX8982A is 4.1V to 5.5V.

IN1A —

— IN1A

IN4 —

— IN4 Connect IN4 to Both IN1A and IN1B

V

DDA

— V

V

DDB

— V

LX3 —

— DNC Do Not Connect

LX4 —

— DNC Do Not Connect

BUCK3 — BUCK3 Output Feedback

— DNC Do Not Connect

BUCK4 — BUCK4 Output Feedback

— DNC Do Not Connect

—

DDA

— Power Input for LDO3, LDO5, LDO6, and LDO7. Connect V

DDB

Connect three 330FF tantalum capacitors as close as possible to IN1A and IN1B.

Connect IN1A to IN1B.

Input Supply to the IC. The operating voltage range for the MAX8982X is 2.9V to 5.5V.

Bypass with a 22FF ceramic capacitor as close as possible to IN1A and IN1B. Connect

IN1A to IN1B.