Page 1

19-5331; Rev 1; 9/10

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

General Description

The MAX5974_ provide control for wide-input-voltage,

active-clamped, current-mode PWM, forward converters

in Power-over-Ethernet (PoE) powered device (PD) applications. The MAX5974A/MAX5974C are well-suited for

universal or telecom input range, while the MAX5974B/

MAX5974D also accommodate low input voltage down

to 10.5V.

The devices include several features to enhance supply

efficiency. The AUX driver recycles magnetizing current instead of wasting it in a dissipative clamp circuit.

Programmable dead time between the AUX and main

driver allows for zero-voltage switching (ZVS). Under lightload conditions, the devices reduce the switching frequency (frequency foldback) to reduce switching losses.

The MAX5974A/MAX5974B feature unique circuitry to

achieve output regulation without using an optocoupler,

while the MAX5974C/MAX5974D utilize the traditional

optocoupler feedback method. An internal error amplifier

with a 1% reference is very useful in nonisolated design,

eliminating the need for an external shunt regulator.

The devices feature a unique feed-forward maximum

duty-cycle clamp that makes the maximum clamp voltage during transient conditions independent of the line

voltage, allowing the use of a power MOSFET with lower

breakdown voltage. The programmable frequency dithering feature provides low-EMI, spread-spectrum operation.

The MAX5974_ are available in 16-pin TQFN-EP packages and are rated for operation over the -40°C to +85°C

temperature range.

Ordering Information

Features

S Peak Current-Mode Control, Active-Clamped

Forward PWM Controller

Regulation Without Optocoupler (MAX5974A/

S

MAX5974B)

Internal 1% Error Amplifier

S

100kHz to 600kHz Programmable Q8% Switching

S

Frequency, Synchronization Up to 1.2MHz

Programmable Frequency Dithering for Low-EMI,

S

Spread-Spectrum Operation

Programmable Dead Time, PWM Soft-Start,

S

Current Slope Compensation

Programmable Feed-Forward Maximum Duty-

S

Cycle Clamp, 80% Maximum Limit

Frequency Foldback for High-Efficiency Light-

S

Load Operation

Internal Bootstrap UVLO with Large Hysteresis

S

100µA (typ) Startup Supply Current

S

Fast Cycle-by-Cycle Peak Current-Limit, 35ns

S

Typical Propagation Delay

115ns Current-Sense Internal Leading-Edge

S

Blanking

Output Short-Circuit Protection with Hiccup Mode

S

Reverse Current Limit to Prevent Transformer

S

Saturation Due to Reverse Current

S

3mm x 3mm, Lead-Free, 16-Pin TQFN-EP

Applications

PoE IEEE® 802.3af/at Powered Devices

High-Power PD (Beyond the 802.3af/at Standard)

Active-Clamped Forward DC-DC Converters

IP Phones

Wireless Access Nodes

Security Cameras

MAX5974A/MAX5974B/MAX5974C/MAX5974D

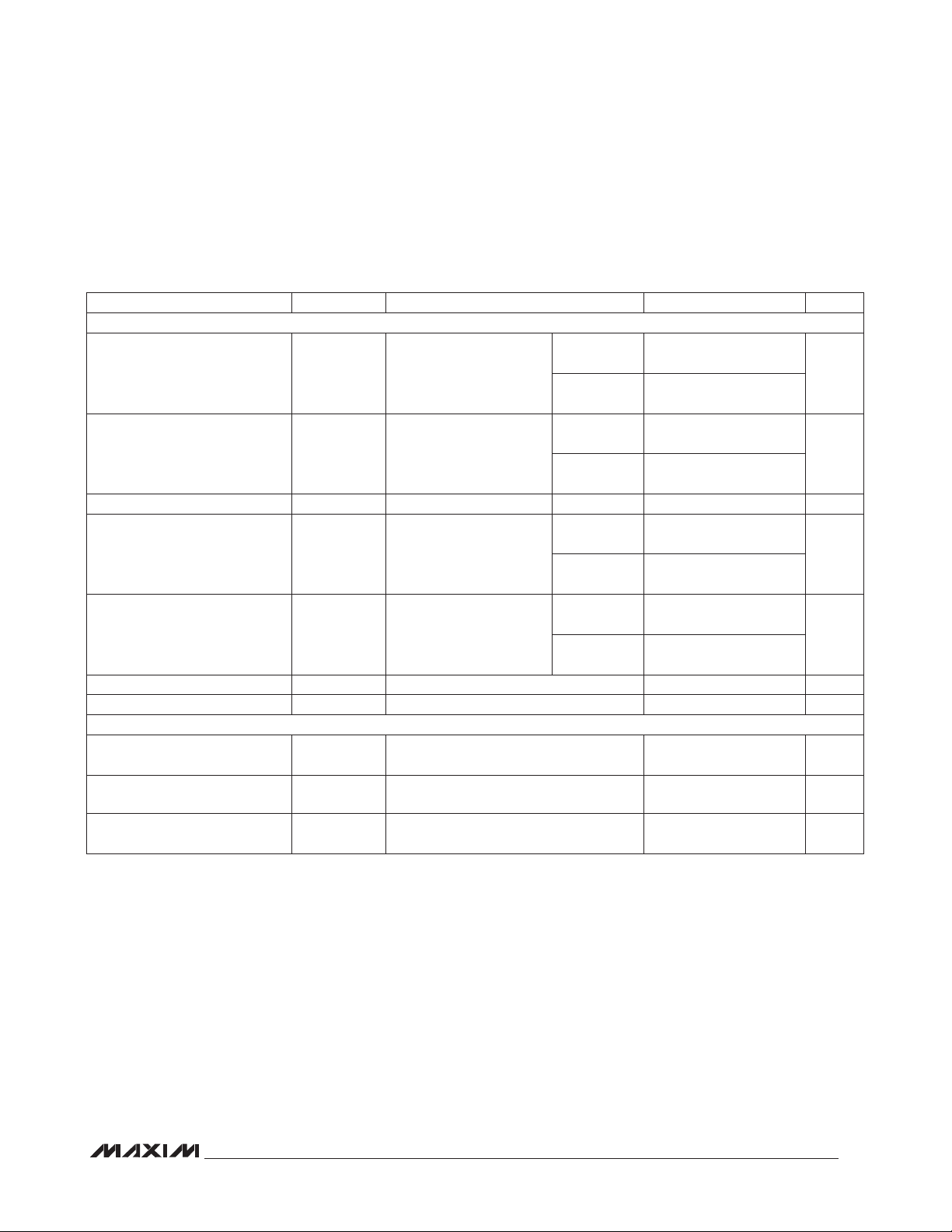

PART TOP MARK PIN-PACKAGE UVLO THRESHOLD (V) FEEDBACK MODE

MAX5974AETE+ +AHY 16 TQFN-EP* 20 Sample/Hold

MAX5974BETE+ +AHZ 16 TQFN-EP* 10 Sample/Hold

MAX5974CETE+ +AIA 16 TQFN-EP* 20 Continuously Connected

MAX5974DETE+ +AIB 16 TQFN-EP* 10 Continuously Connected

Note: All devices are specified over the -40°C to +85°C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

*EP = Exposed pad.

IEEE is a registered service mark of the Institute of Electrical and Electronics Engineers, Inc.

_______________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

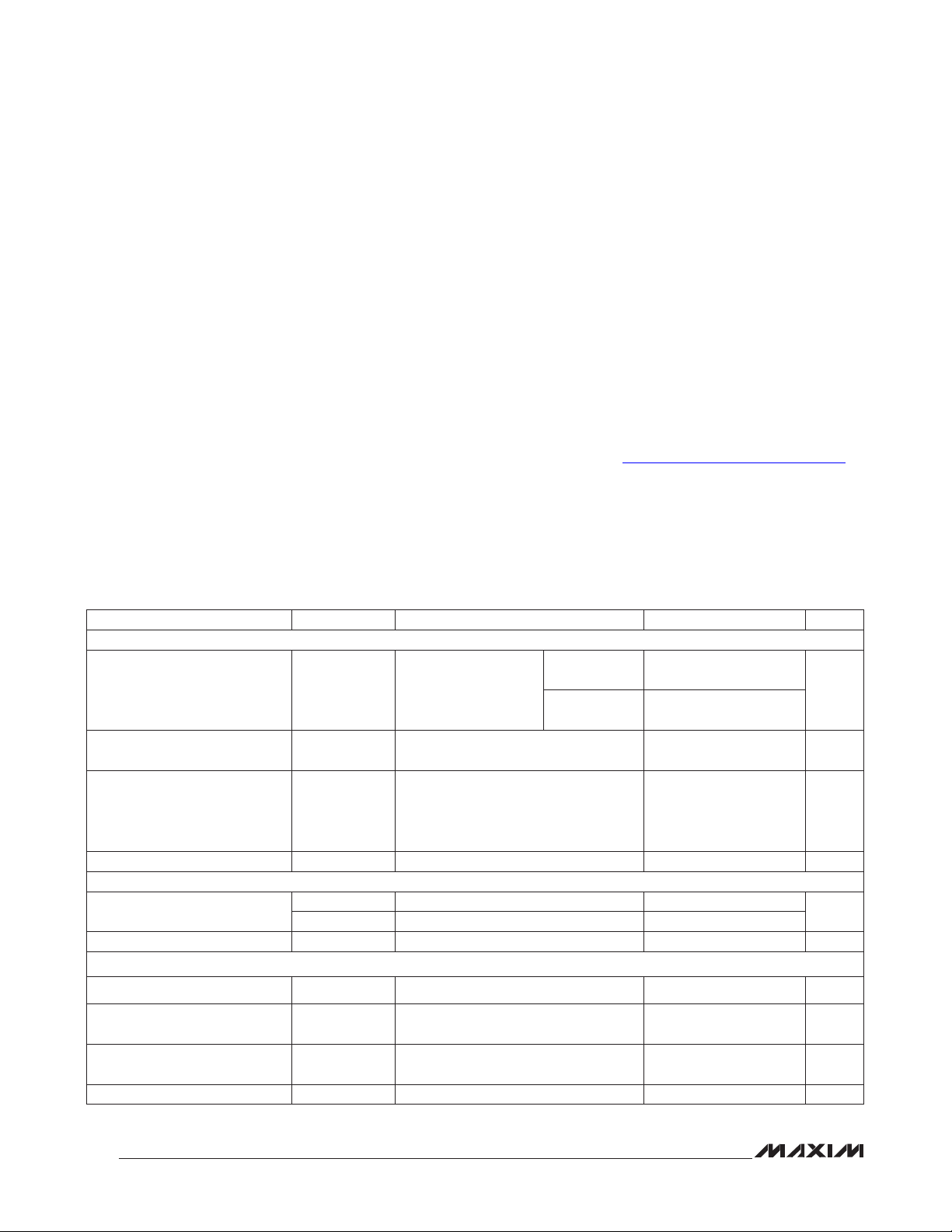

Page 2

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

ABSOLUTE MAXIMUM RATINGS

IN to GND ..............................................................-0.3V to +26V

EN, NDRV, AUXDRV to GND .....................-0.3V to (V

RT, DT, FFB, COMP, SS, DCLMP, DITHER/SYNC

to GND .................................................................-0.3V to +6V

FB to GND (MAX5974A/MAX5974B only) ..................-6V to +6V

FB to GND (MAX5974C/MAX5974D only) ..............-0.3V to +6V

CS, CSSC to GND ...................................................-0.8V to +6V

PGND to GND ......................................................-0.3V to +0.3V

Maximum Input/Output Current (continuous)

NDRV, AUXDRV ............................................................100mA

NDRV, AUXDRV (pulsed for less than 100ns) .................. Q1A

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-

layer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

+ 0.3V)

IN

ELECTRICAL CHARACTERISTICS

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = +2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, CIN = 1FF, TA = -40NC to +85NC,

GND

unless otherwise noted. Typical values are at T

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

UNDERVOLTAGE LOCKOUT/STARTUP (IN)

Bootstrap UVLO Wakeup Level V

Bootstrap UVLO Shutdown

Level

IN Supply Current in

Undervoltage Lockout

IN Supply Current After Startup I

ENABLE (EN)

Enable Threshold

Input Current I

MAX5974A/MAX5974B/MAX5974C/MAX5974D

OSCILLATOR (RT)

RT Bias Voltage V

NDRV Switching Frequency

Range

NDRV Switching Frequency

Accuracy

Maximum Duty Cycle D

V

I

= +25NC.) (Note 2)

A

INUVR

INUVF

START

C

V

ENR

V

ENF

EN

RT

f

SW

MAX

VIN rising

VIN falling 6.65 7 7.35 V

VIN = +18V (for MAX5974A/

MAX5974C);

V

= +9V (for MAX5974B/MAX5974D),

IN

when in bootstrap UVLO

VIN = +12V 1.8 3 mA

VEN rising 1.17 1.215 1.26

VEN falling 1.09 1.14 1.19

1

fSW = 250kHz 79 80 82 %

Continuous Power Dissipation (T

16-Pin TQFN (derate 20.8mW/NC above +70NC) .......1666mW

Junction-to-Case Thermal Resistance (B

16-Pin TQFN ...................................................................7NC/W

Junction-to-Ambient Thermal Resistance (B

16-Pin TQFN .................................................................48NC/W

Operating Temperature Range .......................... -40NC to +85NC

Maximum Junction Temperature .....................................+150NC

Storage Temperature Range ............................ -65NC to +150NC

Lead Temperature (soldering, 10s) ................................+300NC

Soldering Temperature (reflow) ......................................+260NC

= V

CS

MAX5974A/

MAX5974C

MAX5974B/

MAX5974D

CSSC

= V

DITHER/SYNC

= +70NC) (Note 1)

A

) (Note 1)

JC

) (Note 1)

JA

= V

= V

FFB

= V

FB

19.1 19.8 20.4

9.4 9.8 10.25

100 150

1.23 V

100 600 kHz

-8 +8 %

DCLMP

V

FA

V

FA

=

2

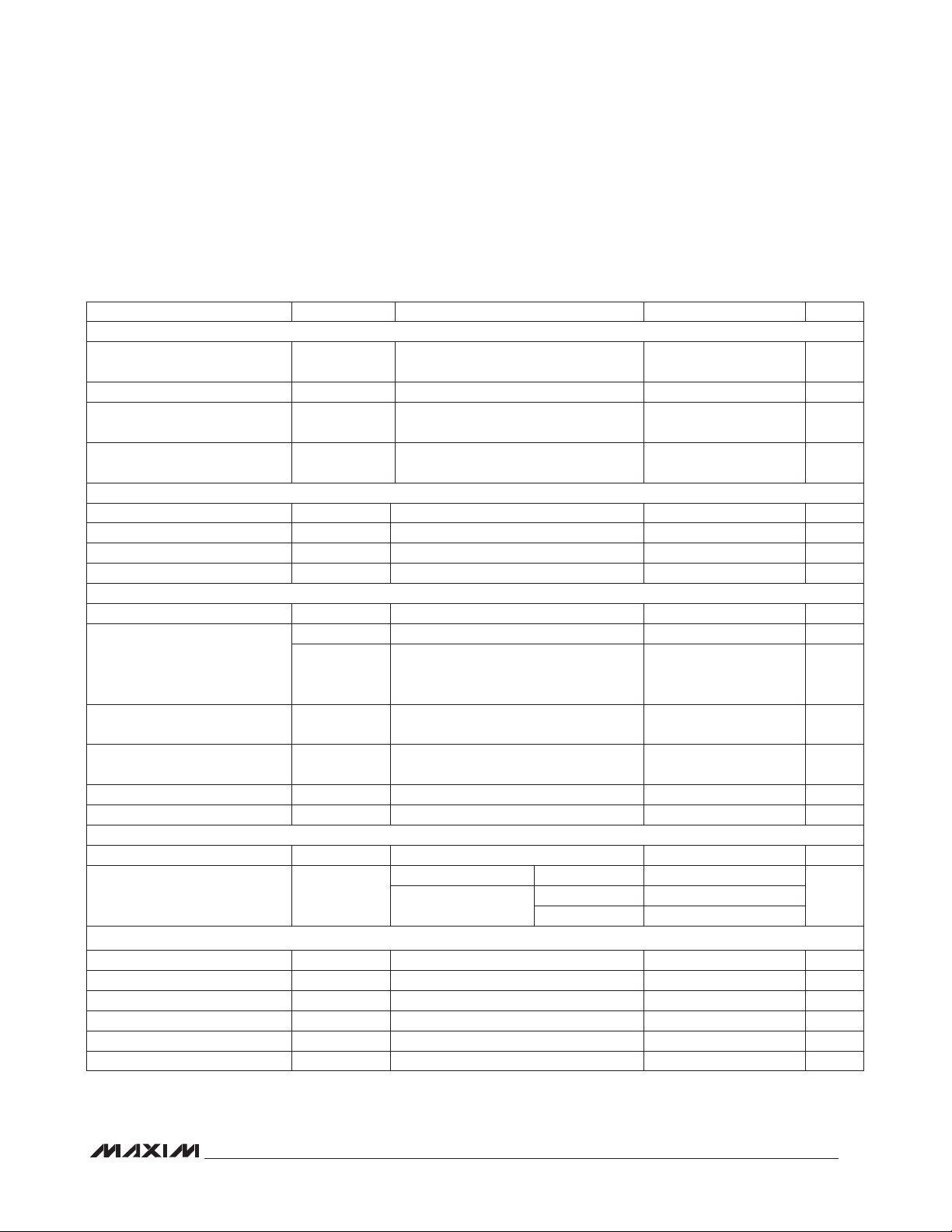

Page 3

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

ELECTRICAL CHARACTERISTICS (continued)

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = +2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, CIN = 1FF, TA = -40NC to +85NC,

GND

unless otherwise noted. Typical values are at T

= +25NC.) (Note 2)

A

CS

= V

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SYNCHRONIZATION (SYNC)

Synchronization Logic-High

Input

V

IH-SYNC

Synchronization Pulse Width 50 ns

Synchronization Frequency

Range

f

SYNCIN

Maximum Duty Cycle During

Synchronization

DITHERING RAMP GENERATOR (DITHER)

Charging Current V

Discharging Current V

= 0V 45 50 55

DITHER

= 2.2V 43 50 57

DITHER

Ramp’s High Trip Point 2 V

Ramp’s Low Trip Point 0.4 V

SOFT-START AND RESTART (SS)

Charging Current I

Discharging Current

Discharge Threshold to Disable

Hiccup and Restart

Minimum Restart Time During

Hiccup Mode

Normal Operating High Voltage V

Duty-Cycle Control Range V

SS-CH

I

SS-D

I

SS-DH

V

SS-DTH

t

RSTRT-MIN

SS-HI

SS-DMAX

VSS = 2V, normal shutdown 0.65 1.34 2 mA

(VEN < V

V

= 2V, hiccup mode discharge for

SS

t

RESTART

D

MAX

or VIN < V

ENF

(Note 3)

(typ) = (V

SS-DMAX

INUVF

/2.43V) 0 2 V

DUTY-CYCLE CLAMP (DCLMP)

DCLMP Input Current I

Duty-Cycle Control Range V

DCLMP

DCLMP-R

V

D

1 - (V

= 0 to 5V -100 0 +100 nA

DCLMP

V

DCLMP

MAX

(typ) =

DCLMP

2.43V)

/

V

DCLMP

V

DCLMP

NDRV DRIVER

Pulldown Impedance R

Pullup Impedance R

NDRV-N

NDRV-P

I

(sinking) = 100mA 1.9 3.4

NDRV

I

(sourcing) = 50mA 4.7 8.3

NDRV

Peak Sink Current 1 A

Peak Source Current 0.65 A

C

Fall Time t

Rise Time t

NDRV-F

NDRV-R

= 1nF 14 ns

NDRV

C

= 1nF 27 ns

NDRV

CSSC

= V

DITHER/SYNC

= V

FB

2.91 V

1.1 x

f

SW

D

MAX

x f

f

SW

9.5 10 10.5

),

1.6 2 2.4

0.15 V

1024

5 V

= 0.5V 73 75.4 77.5

= 1V 54 56 58

= 2V 14.7 16.5 18.3

= V

SYNC

FFB

2 x

f

SW

/

= V

DCLMP

kHz

%

FA

FA

FA

FA

Clock

Cycles

%

I

I

MAX5974A/MAX5974B/MAX5974C/MAX5974D

=

3

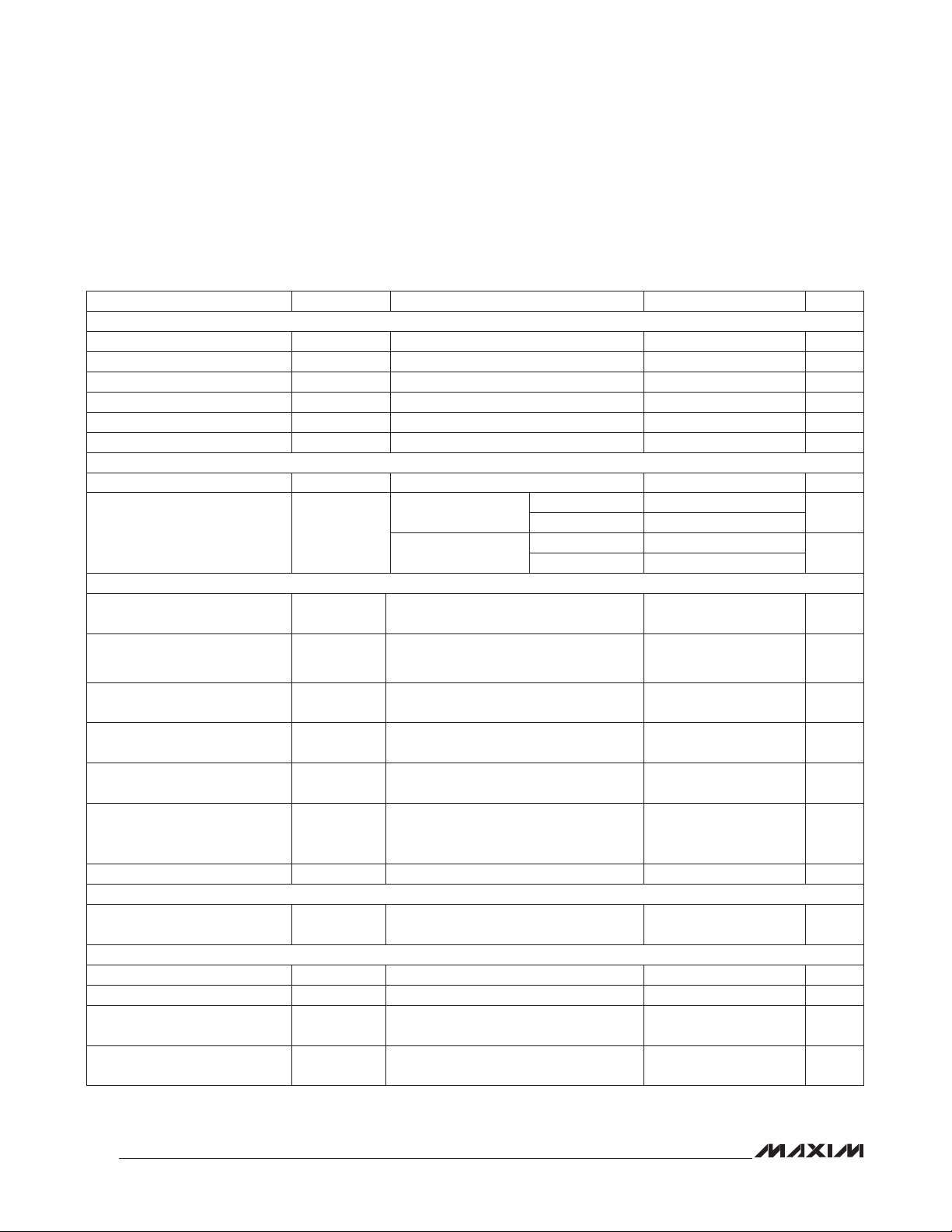

Page 4

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

ELECTRICAL CHARACTERISTICS (continued)

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = +2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, CIN = 1FF, TA = -40NC to +85NC,

GND

unless otherwise noted. Typical values are at T

= +25NC.) (Note 2)

A

CS

= V

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

AUXDRV DRIVER

Pulldown Impedance R

Pullup Impedance R

AUX-N

AUX-P

I

I

(sinking) = 50mA 4.3 7.7

AUXDRV

(sourcing) = 25mA 10.6 18.9

AUXDRV

Peak Sink Current 0.5 A

Peak Source Current 0.3 A

Fall Time t

Rise Time t

AUX-F

AUX-R

C

C

= 1nF 24 ns

AUXDRV

= 1nF 45 ns

AUXDRV

DEAD-TIME PROGRAMMING (DT)

DT Bias Voltage V

NDRV to AUXDRV Delay

(Dead Time)

DT

From NDRV falling

t

DT

to AUXDRV falling

AUXDRV rising to

NDRV rising

R

DT

R

DT

R

DT

R

DT

CURRENT-LIMIT COMPARATORS (CS)

Cycle-by-Cycle Peak

Current-Limit Threshold

V

CS-PEAK

= V

CSSC

= 10kI

= 100kI

= 10kI

= 100kI

= V

DITHER/SYNC

FB

= V

1.215 V

40

300 350 410

40

310 360 420

375 393 410 mV

FFB

= V

DCLMP

I

I

ns

ns

=

Cycle-by-Cycle Reverse

Current-Limit Threshold

Current-Sense Blanking Time

t

for Reverse Current Limit

Number of Consecutive Peak

Current-Limit Events to Hiccup

Current-Sense Leading-Edge

Blanking Time

Propagation Delay from

Comparator Input to NDRV

Minimum On-Time t

V

CS-REV

CS-BLANK-

REV

N

HICCUP

t

CS-BLANK

t

PDCS

ON-MIN

Turns AUXDRV off for the remaining

cycle if reverse current limit is exceeded

-118 -100 -88 mV

From AUXDRV falling edge 115 ns

8 Events

From NDRV rising edge 115 ns

From CS rising (10mV overdrive) to

NDRV falling (excluding leading-edge

35 ns

blanking)

100 150 200 ns

SLOPE COMPENSATION (CSSC)

Slope Compensation Current

Ramp Height

MAX5974A/MAX5974B/MAX5974C/MAX5974D

PWM COMPARATOR

Comparator Offset Voltage V

Current-Sense Gain A

Current-Sense Leading-Edge

Blanking Time

Comparator Propagation Delay t

PWM-OS

CS-PWM

t

CSSC-BLANK

PWM

Current ramp’s peak added to CSSC

input per switching cycle

V

- V

COMP

DV

COMP

/DV

CSSC

CSSC

(Note 4)

47 52 58

1.35 1.7 2 V

3.1 3.33 3.6 V/V

From NDRV rising edge 115 ns

Change in V

internal leading-edge blanking)

= 10mV (including

CSSC

150 ns

FA

4

Page 5

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

ELECTRICAL CHARACTERISTICS (continued)

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = +2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, CIN = 1FF, TA = -40NC to +85NC,

GND

unless otherwise noted. Typical values are at T

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

ERROR AMPLIFIER

FB Reference Voltage V

FB Input Bias Current I

Voltage Gain A

Transconductance g

Transconductance Bandwidth BW

Source Current VFB = 1V, V

Sink Current V

FREQUENCY FOLDBACK (FFB)

V

Gain

-to-FFB Comparator

CSAVG

= +25NC.) (Note 2)

A

REF

FB

EAMP

M

10 V/V

VFB when I

V

= 2.5V

COMP

VFB = 0 to 1.75V

Open loop (typical gain

= 1) -3dB frequency

= 1.75V, V

FB

COMP

COMP

COMP

= 0,

= V

CS

= 2.5V 300 375 455

= 1V 300 375 455

= V

CSSC

MAX5974A/

MAX5974B

MAX5974C/

MAX5974D

MAX5974A/

MAX5974B

MAX5974C/

MAX5974D

80 dB

MAX5974A/

MAX5974B

MAX5974C/

MAX5974D

MAX5974A/

MAX5974B

MAX5974C/

MAX5974D

DITHER/SYNC

1.202 1.215 1.227

-250 +250

-500 +100

= V

= V

FB

FFB

1.5 1.52 1.54

1.8 2.55 3.2

1.8 2.66 3.5

2

30

= V

DCLMP

V

nA

mS

MHz

FA

FA

MAX5974A/MAX5974B/MAX5974C/MAX5974D

=

FFB Bias Current I

NDRV Switching Frequency

During Foldback

Note 2: All devices are 100% production tested at T

Note 3: See the Output Short-Circuit Protection with Hiccup Mode section.

Note 4: The parameter is measured at the trip point of latch with V

DV

CSSC

< 0.25V.

FFB

f

SW-FB

V

= 0V, VCS = 0V (not in FFB mode) 26 30 33

FFB

fSW/2 kHz

= +25NC. Limits over temperature are guaranteed by design.

A

= 0V. Gain is defined as DV

FB

COMP

/DV

for 0.15V <

CSSC

FA

5

Page 6

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

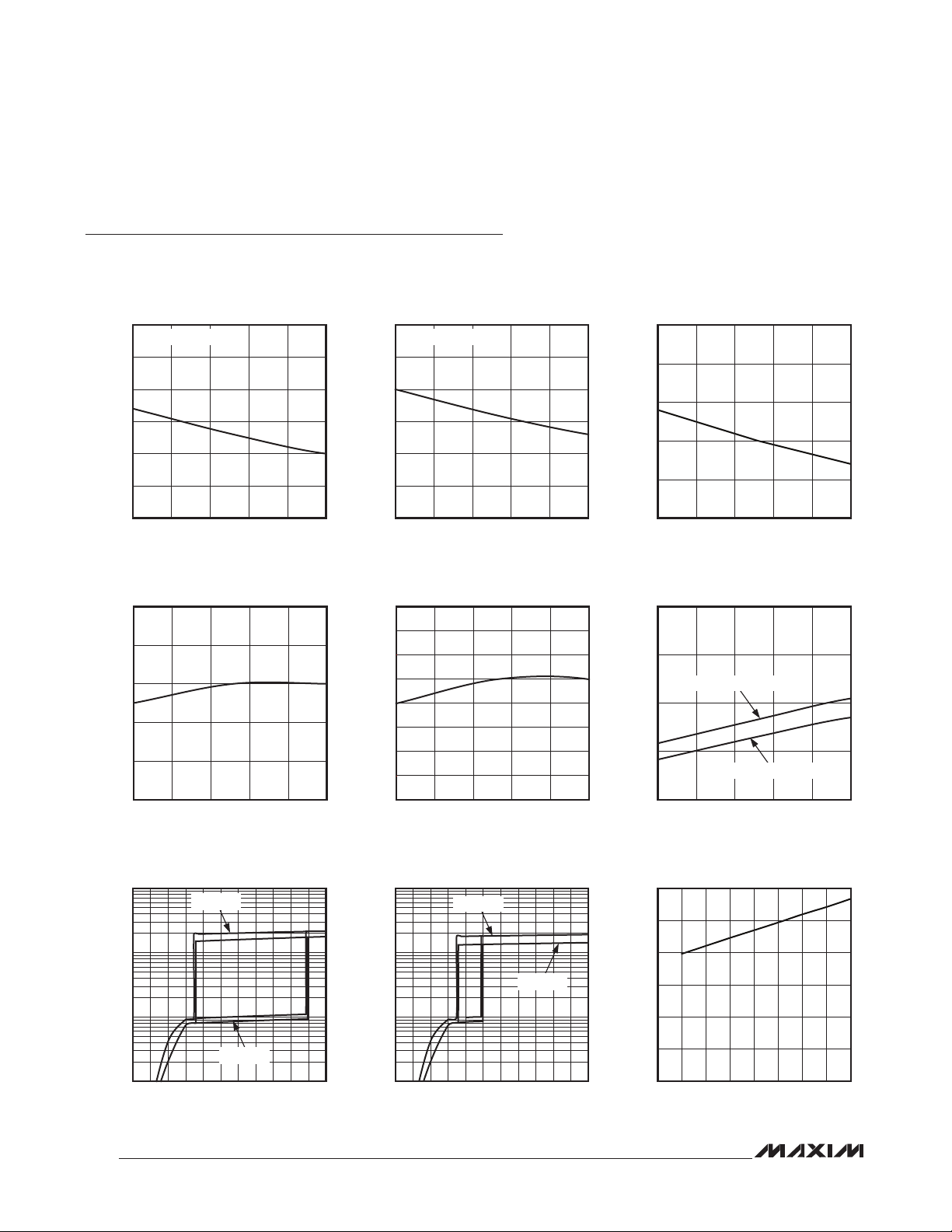

Typical Operating Characteristics

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = 2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, unless otherwise noted.)

GND

CS

= V

CSSC

= V

DITHER/SYNC

= V

FB

= V

FFB

= V

DCLMP

=

IN UVLO WAKE-UP LEVEL

vs. TEMPERATURE

20.1

MAX5974A/MAX5974C

20.0

19.9

19.8

19.7

IN UVLO WAKE-UP LEVEL (V)

19.6

19.5

-40 85

TEMPERATURE (°C)

EN RISING THRESHOLD

vs. TEMPERATURE

1.220

1.218

1.216

1.214

EN RISING THRESHOLD (V)

1.212

1.210

-40 85

TEMPERATURE (°C)

IN UVLO WAKE-UP LEVEL

vs. TEMPERATURE

10.1

MAX5974B/MAX5974D

10.0

MAX5974A/B/C/D toc01

9.9

9.8

9.7

IN UVLO WAKE-UP LEVEL (V)

9.6

603510-15

9.5

-40 85

TEMPERATURE (°C)

603510-15

7.3

7.2

MAX5974A/B/C/D toc02

7.1

7.0

IN UVLO SHUTDOWN LEVEL

6.9

6.8

EN FALLING THRESHOLD

vs. TEMEPRATURE

1.150

1.149

1.148

MAX5974A/B/C/D toc04

1.147

1.146

1.145

1.144

EN FALLING THRESHOLD (V)

1.143

603510-15

1.142

-40 85

TEMPERATURE (°C)

6035-15 10

140

120

MAX5974A/B/C/D toc05

100

UVLO CURRENT (µA)

80

60

IN UVLO SHUTDOWN LEVEL

vs. TEMPERATURE

-40 85

TEMPERATURE (°C)

603510-15

UVLO SHUTDOWN CURRENT

vs. TEMPERATURE

MAX5974A/MAX5974C

MAX5974B/MAX5974D

-40 85

TEMPERATURE (°C)

603510-15

MAX5974A/B/C/D toc03

MAX5974A/B/C/D toc06

SUPPLY CURRENT vs. SUPPLY VOLTAGE

(MAX5974A/MAX5974C)

10,000

1000

MAX5974A/MAX5974B/MAX5974C/MAX5974D

100

SUPPLY CURRENT (µA)

10

0 22

TA = +85°C

MAX5974A/B/C/D toc07

TA = -40°C

2018161412108642

SUPPLY VOLTAGE (V)

SUPPLY CURRENT vs. SUPPLY VOLTAGE

(MAX5974B/MAX5974D)

10,000

1000

100

SUPPLY CURRENT (µA)

10

0 22

TA = +85°C

SUPPLY VOLTAGE (V)

TA = -40°C

2018161412108642

2.4

2.0

MAX5974A/B/C/D toc08

1.6

1.2

0.8

SUPPLY CURRENT (mA)

0.4

0

SUPPLY CURRENT

vs. SWITCHING FREQUENCY

0 800

SWITCHING FREQUENCY (kHz)

6

MAX5974A/B/C/D toc09

700600500400300200100

Page 7

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

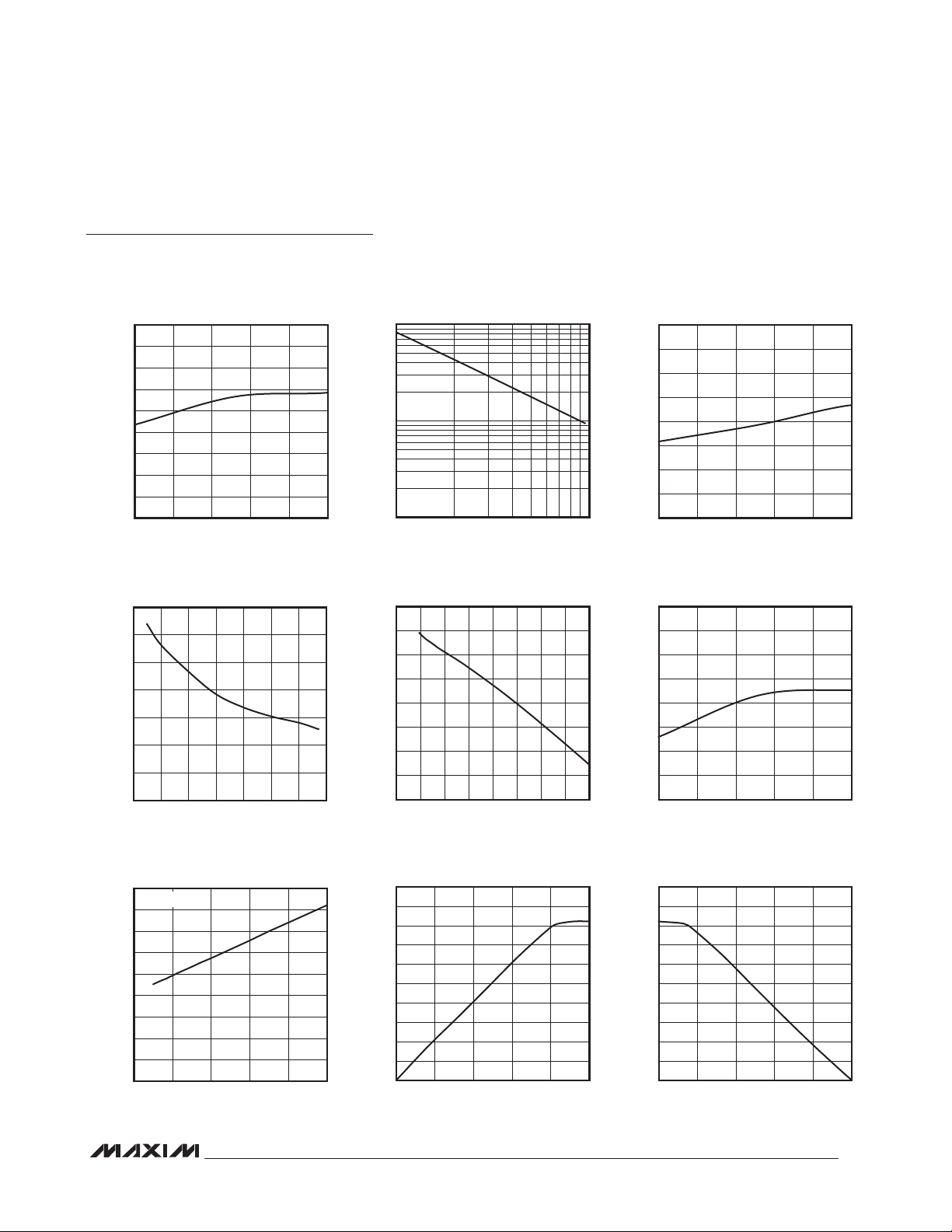

Typical Operating Characteristics (continued)

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = 2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, unless otherwise noted.)

GND

CS

= V

CSSC

= V

DITHER/SYNC

= V

FB

= V

FFB

= V

DCLMP

MAX5974A/MAX5974B/MAX5974C/MAX5974D

=

SOFT-START CHARGING CURRENT

vs. TEMPERATURE

10.06

10.05

10.04

10.03

10.02

10.01

10.00

9.99

SOFT-START CHARGING CURRENT (µA)

9.98

9.97

-40 85

TEMPERATURE (°C)

FREQUENCY DITHERING

vs. R

R

DITHER

DITHER

(kΩ)

14

12

10

8

6

4

FREQUENCY DITHERING (%)

2

0

300 1000

MAXIMUM DUTY CYCLE

vs. SYNC FREQUENCY

45

VSS = 0.5V

40

35

30

25

20

15

MAXIMUM DUTY CYCLE (%)

10

5

0

250 500

SYNC FREQUENCY (kHz)

SWITCHING FREQUENCY

vs. RRT VALUE

1000

MAX5974A/B/C/D toc10

100

SWITCHING FREQUENCY (kHz)

603510-15

10

RRT VALUE (kΩ)

10010

252

251

250

MAX5974A/B/C/D toc11

249

248

247

246

SWITCHING FREQUENCY (kHz)

245

244

MAXIMUM DUTY CYCLE

vs. SWITCHING FREQUENCY

900800700600500400

83

82

81

MAX5974A/B/C/D toc13

80

79

78

77

MAXIMUM DUTY CYCLE (%)

76

75

0 800

700600100 200 300 400 500

SWITCHING FREQUENCY (kHz)

81.0

80.9

80.8

MAX5974A/B/C/D toc14

80.7

80.6

80.5

80.4

MAXIMUM DUTY CYCLE (%)

80.3

80.2

MAXIMUM DUTY CYCLE

vs. V

VSS (V)

SS

2.01.51.00.5

100

90

80

MAX5974A/B/C/D toc17

70

60

50

40

30

MAXIMUM DUTY CYCLE (%)

20

10

0

100

90

80

MAX5974A/B/C/D toc16

70

60

50

40

30

MAXIMUM DUTY CYCLE (%)

20

10

0

450400350300

0 2.5

SWITCHING FREQUENCY

vs. TEMPERATURE

-40 85

TEMPERATURE (°C)

6035-15 10

MAXIMUM DUTY CYCLE

vs. TEMPERATURE

-40 85

TEMPERATURE (°C)

6035-15 10

MAXIMUM DUTY CYCLE

vs. V

DCLMP

0 2.5

V

DCLMP

2.01.51.00.5

(V)

MAX5974A/B/C/D toc12

MAX5974A/B/C/D toc15

MAX5974A/B/C/D toc18

7

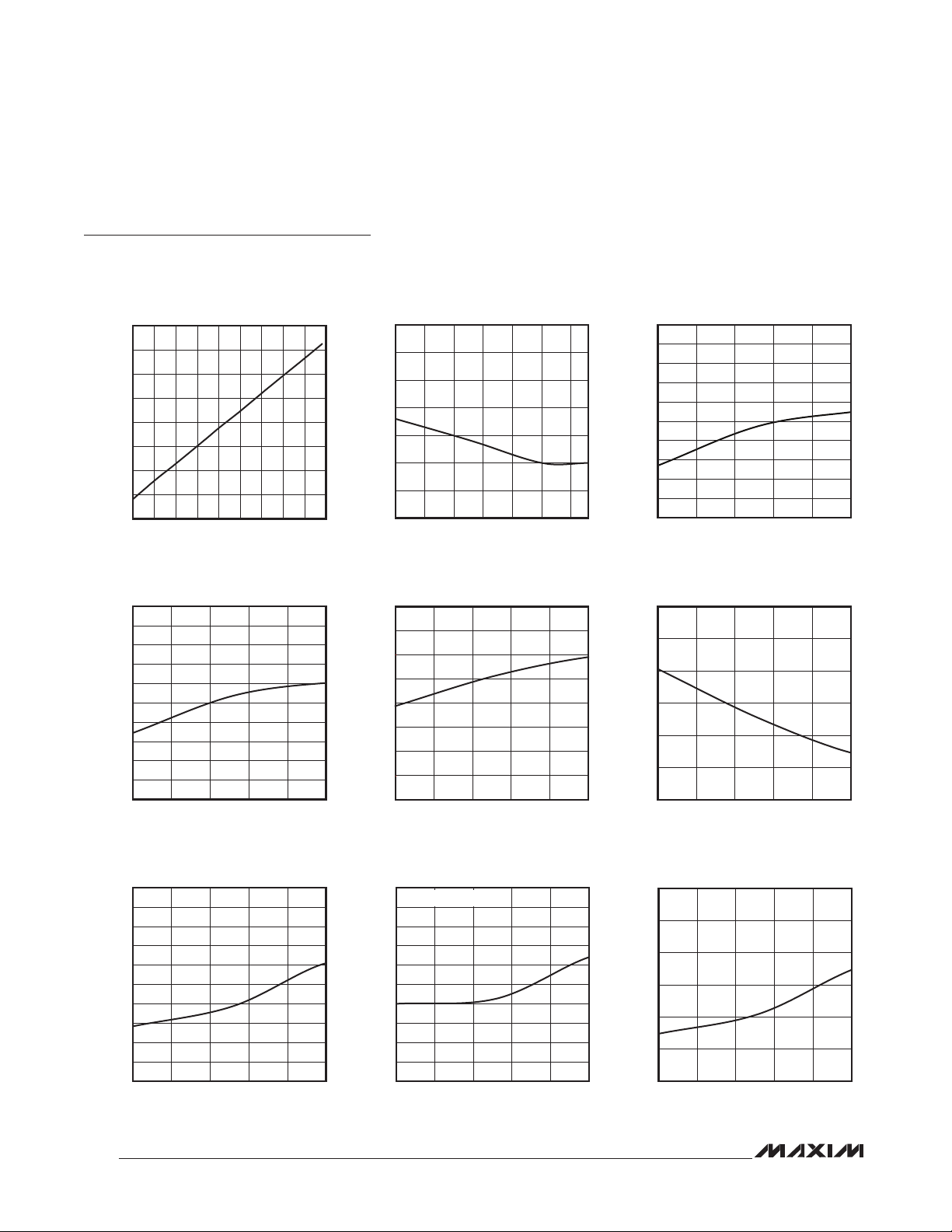

Page 8

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Typical Operating Characteristics (continued)

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = 2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, unless otherwise noted.)

GND

400

DEAD TIME vs. RDT VALUE

350

300

250

200

DEAD TIME (ns)

150

100

50

0

10 100

RDT VALUE (kΩ)

MAX5974A/B/C/D toc19

DEAD TIME (ns)

908020 30 40 6050 70

DEAD TIME vs. TEMPERATURE

102

100

98

96

94

92

90

88

-40

TEMPERATURE (°C)

CS

= V

CSSC

11085603510-15

= V

DITHER/SYNC

= V

PEAK CURRENT-LIMIT THRESHOLD

vs. TEMPERATURE

398

397

396

MAX5974A/B/C/D toc20

395

394

393

392

391

390

PEAK CURRENT-LIMIT THRESHOLD (mV)

389

388

-40 85

TEMPERATURE (°C)

FB

= V

FFB

= V

DCLMP

603510-15

=

MAX5974A/B/C/D toc21

REVERSE CURRENT-LIMIT THRESHOLD

vs. TEMPERATURE

-97

-98

-99

-100

-101

-102

-103

-104

-105

-106

REVERSE CURRENT-LIMIT THRESHOLD (mV)

-107

-40 85

TEMPERATURE (°C)

603510-15

MAX5974A/B/C/D toc22

SLOPE COMPENSATION CURRENT (mA)

CURRENT-SENSE GAIN

vs. TEMPERATURE

3.40

3.39

3.38

3.37

MAX5974A/MAX5974B/MAX5974C/MAX5974D

3.36

3.35

3.34

3.33

CURRENT-SENSE GAIN (V/V)

3.32

3.31

3.30

-40 85

TEMPERATURE (°C)

603510-15

MAX5974A/B/C/D toc25

FEEDBACK VOLTAGE (V)

SLOPE COMPENSATION CURRENT

vs. TEMPERATURE

54.0

53.5

53.0

52.5

52.0

51.5

51.0

50.5

50.0

-40 85

TEMPERATURE (°C)

FEEDBACK VOLTAGE

vs. TEMPERATURE

1.220

MAX5974C/MAX5974D

1.219

1.218

1.217

1.216

1.215

1.214

1.213

1.212

1.211

1.210

-40 85

TEMPERATURE (°C)

170

165

MAX5974A/B/C/D toc23

160

155

150

NDRV MINIMUM ON-TIME (ns)

145

6035-15 10

603510-15

140

1.522

1.521

MAX5974A/B/C/D toc26

1.520

1.519

1.518

FEEDBACK VOLTAGE (V)

1.517

1.516

NDRV MINIMUM ON-TIME

vs. TEMPERATURE

-40 85

TEMPERATURE (°C)

FEEDBACK VOLTAGE

vs. TEMPERATURE

-40 85

TEMPERATURE (°C)

MAX5974A/B/C/D toc24

603510-15

MAX5974A/B/C/D toc27

603510-15

8

Page 9

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Typical Operating Characteristics (continued)

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = 2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, unless otherwise noted.)

GND

CS

= V

CSSC

= V

DITHER/SYNC

= V

FB

= V

FFB

= V

DCLMP

MAX5974A/MAX5974B/MAX5974C/MAX5974D

=

TRANSCONDUCTANCE

vs. TEMPERATURE

3.0

2.9

2.8

2.7

2.6

2.5

2.4

2.3

TRANSCONDUCTANCE (mS)

2.2

2.1

2.0

-40 85

MAX5974C/MAX5974D

MAX5974A/MAX5974B

TEMPERATURE (°C)

ENABLE RESPONSE

603510-15

1ms/div

MAX5974A/B/C/D toc28

N (%)

MAX5974A/B/C/D toc31

MAX5974C

TRANSCONDUCTANCE HISTOGRAM

(MAX5974A/MAX5974B)

25

20

15

10

5

0

2.44

TRANSCONDUCTANCE (mS)

V

EN

2V/div

V

NDRV

20V/div

V

AUXDRV

20V/div

V

OUT

5V/div

25

20

MAX5974A/B/C/D toc29

15

N (%)

10

5

2.642.622.602.582.562.542.522.502.482.46

SHUTDOWN RESPONSE

0

MAX5974A/B/C/D toc32

4µs/div

TRANSCONDUCTANCE HISTOGRAM

(MAX5974C/MAX5974D)

2.56

TRANSCONDUCTANCE (mS)

V

EN

2V/div

V

NDRV

10V/div

V

AUXDRV

10V/div

V

OUT

5V/div

MAX5974A/B/C/D toc30

2.762.742.722.702.682.662.642.622.602.58

SHUTDOWN RESPONSE

100µs/div

MAX5974A/B/C/D toc33

V

EN

2V/div

V

NDRV

10V/div

V

AUXDRV

10V/div

V

OUT

5V/div

VSS RAMP RESPONSE

10µs/div

MAX5974A/B/C/D toc34

V

SS

2V/div

V

NDRV

10V/div

V

AUXDRV

10V/div

9

Page 10

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Typical Operating Characteristics (continued)

(VIN = 12V (for MAX5974A/MAX5974C, bring VIN up to 21V for startup), V

V

, VEN = 2V, NDRV = AUXDRV = SS = COMP = unconnected, RRT = 34.8kI, RDT = 25kI, unless otherwise noted.)

GND

V

RAMP RESPONSE

DCLMP

MAX5974A/B/C/D toc35

V

DCLMP

2V/div

NDRV 10% TO 90% RISE TIME

MAX5974A/B/C/D toc36

27.6ns

CS

= V

CSSC

= V

DITHER/SYNC

NDRV 90% TO 10% FALL TIME

0ns

= V

FB

= V

FFB

MAX5974A/B/C/D toc37

= V

DCLMP

=

10µs/div

AUXDRV 10% TO 90% RISE TIME

0ns

10ns/div

MAX5974A/B/C/D toc38

45.6ns

V

NDRV

10V/div

V

AUXDRV

10V/div

V

AUXDRV

2V/div

0ns

10ns/div

AUXDRV 90% TO 10% FALL TIME

0ns

10ns/div

MAX5974A/B/C/D toc39

21ns

V

NDRV

2V/div

V

AUXDRV

2V/div

13.8ns

10ns/div

PEAK NDRV CURRENT

PEAK SOURCE CURRENT

PEAK SINK CURRENT

200ns/div

MAX5974A/B/C/D toc40

V

NDRV

2V/div

I

NDRV

0.5A/div

PEAK AUXDRV CURRENT

MAX5974A/B/C/D toc41

PEAK SOURCE

CURRENT

SHORT-CIRCUIT BEHAVIOR

MAX5974A/B/C/D toc42

V

IN

MAX5974A/MAX5974B/MAX5974C/MAX5974D

I

AUXDRV

10

PEAK SINK CURRENT

400ns/div

0.2A/div

40ms/div

V

I

LX

NDRV

Page 11

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Pin Configuration

TOP VIEW

NDRV

PGND

AUXDRV

12 10 9

11

CS

MAX5974A/MAX5974B/MAX5974C/MAX5974D

FFB

CSSC

8

GND

7

FB

6

COMP

5

DCLMP

13

IN

14

15

16

SS

MAX5974A

MAX5974B

MAX5974C

MAX5974D

+

1 3EN4

2

SYNC

DITHER/

RT

DT

THIN QFN

EP

Pin Description

PIN NAME FUNCTION

from DT to GND to set the

DT

1 DT

2

DITHER/

SYNC

Dead-Time Programming Resistor Connection. Connect resistor R

desired dead time between the NDRV and AUXDRV signals. See the Dead Time section to calculate the resistor value for a particular dead time.

Frequency Dithering Programming or Synchronization Connection. For spread-spectrum frequency

operation, connect a capacitor from DITHER to GND and a resistor from DITHER to RT. To synchronize the internal oscillator to the externally applied frequency, connect DITHER/SYNC to the

synchronization pulse.

3 RT

4 FFB

5 COMP

Switching Frequency Programming Resistor Connection. Connect resistor R

from RT to GND to

RT

set the PWM switching frequency. See the Oscillator/Switching Frequency section to calculate the

resistor value for the desired oscillator frequency.

Frequency Foldback Threshold Programming Input. Connect a resistor from FFB to GND to set the

output average current threshold below which the converter folds back the switching frequency to

1/2 of its original value. Connect to GND to disable frequency foldback.

Transconductance Amplifier Output and PWM Comparator Input. COMP is level shifted down and

connected to the inverting input of the PWM comparator.

11

Page 12

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Pin Description (continued)

PIN NAME FUNCTION

6 FB Transconductance Amplifier Inverting Input

7 GND Signal Ground

8 CSSC

9 CS

10 PGND Power Ground. PGND is the return path for gate-driver switching currents.

11 NDRV Main Switch Gate-Driver Output

12 AUXDRV

13 IN

14 EN

Current Sense with Slope Compensation Input. A resistor connected from CSSC to CS programs the

amount of slope compensation. See the Programmable Slope Compensation section.

Current-Sense Input. Current-sense connection for average current sense and cycle-by-cycle current limit. Peak current-limit trip voltage is 400mV and reverse current-limit trip voltage is -100mV.

pMOS Active Clamp Switch Gate-Driver Output. AUXDRV can also be used to drive a pulse transformer for synchronous flyback application.

Converter Supply Input. IN has wide UVLO hysteresis, enabling the design of efficient power supplies. When the enable input EN is used to program a UVLO level for the power source, connect a

zener diode between IN and PGND to ensure that V

mum rating of 26V.

Enable Input. The gate drivers are disabled and the device is in a low-power UVLO mode when the

voltage on EN is below V

enable conditions. See the Enable Input section for more information about interfacing to EN.

. When the voltage on EN is above V

ENF

is always clamped below its absolute maxi-

IN

, the device checks for other

ENR

Feed-Forward Maximum Duty-Cycle Clamp Programming Input. Connect a resistive divider between

15 DCLMP

16 SS

— EP

the input supply voltage DCLMP and GND. The voltage at DCLMP sets the maximum duty cycle

(D

) of the converter inversely proportional to the input supply voltage, so that the MOSFET

MAX

remains protected during line transients.

Soft-Start Programming Capacitor Connection. Connect a capacitor from SS to GND to program the

soft-start period. This capacitor also determines hiccup mode current-limit restart time. A resistor

from SS to GND can also be used to set the D

Exposed Pad. Internally connected to GND. Connect to a large ground plane to maximize thermal

performance. Not intended as an electrical connection point.

below 75%.

MAX

MAX5974A/MAX5974B/MAX5974C/MAX5974D

12

Page 13

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Block Diagrams

MAX5974A/MAX5974B/MAX5974C/MAX5974D

SS16

10µA

VB

POK

-100mV

2mA

2µA

EVENTS

COUNT 8

COMP

LIM

LATCH

HICCUP

S

SET

Q

REVERSE I

CS9

115ns

BLANKING

< 150mV

SS

V

R

CLR

Q

CSSC8

SLOPE

COMPENSATION

VB

115ns

BLANKING

400mV

LIM

COMP

PEAK I

COMP5

VB

VB

PWM

COMP

1.52V

2 x R1

g

R1

FB6

M

MAX5974A

S/H

MAX5974B

IN13

= 20V (MAX5974A)

= 10V (MAX5974B)

LOW-POWER UVLO

INUVR

V

V

UVLO

THERMAL

SHUTDOWN

POK

INUVR

= 7V

INUVF

V

5V

1.23V

EN14

ENABLE

REGULATOR

VB

VC

CONTROL

DEAD-TIME

DRIVER

1A/-0.65A

11NDRV

DRIVER LOGIC

NDRV

PGND

LIMIT TURNS

LIM

REVERSE I

VC

OFF AUX IMMEDIATELY

AUXDRV

DEAD TIME

DRIVER

0.5A/-0.3A

12AUXDRV

PGND

NDRV

PULSE

BLANKING

POK

10X

CSAVG

V

SS

FFB COMP

OSCILLATOR

SYNC

1DT

3

RT

30µA/

< 80%

MAX

VB

20% < D

15

DCLMP

90µA

2V/400mV

50µA/

-50µA

VB

4

FFB

2

7GND

10PGND

SYNC

DITHER/

13

Page 14

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Block Diagrams (continued)

SS16

10µA

VB

POK

-100mV

2mA

2µA

EVENTS

COUNT 8

COMP

LIM

LATCH

HICCUP

S

SET

Q

REVERSE I

CS9

115ns

BLANKING

< 150mV

SS

V

R

CLR

Q

CSSC8

SLOPE

COMPENSATION

VB

115ns

BLANKING

400mV

LIM

COMP

PEAK I

COMP5

VB

VB

PWM

COMP

1.275V

2 x R1

g

R1

FB6

M

MAX5974C

MAX5974D

IN13

= 20V (MAX5974C)

LOW-POWER UVLO

INUVR

V

UVLO

THERMAL

SHUTDOWN

POK

= 7V

INUVF

V

= 10V (MAX5974D)

INUVR

V

1.23V

ENABLE

5V

REGULATOR

VB

EN14

NDRV

PULSE

BLANKING

LIMIT TURNS

LIM

DRIVER LOGIC

OFF AUX IMMEDIATELY

REVERSE I

VC

AUXDRV

DEAD TIME

DRIVER

0.5A/-0.3A

12AUXDRV

CONTROL

MAX5974A/MAX5974B/MAX5974C/MAX5974D

DEAD-TIME

NDRV

VC

DRIVER

1A/-0.65A

PGND

11NDRV

PGND

POK

10X

CSAVG

V

SS

FFB COMP

OSCILLATOR

SYNC

1DT

3

RT

30µA/

< 80%

MAX

VB

20% < D

15

DCLMP

90µA

2V/400mV

50µA/

-50µA

VB

4

FFB

2

7GND

10PGND

SYNC

DITHER/

14

Page 15

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Detailed Description

The MAX5974A/MAX5974B/MAX5974C/MAX5974D are

optimized for controlling a 25W to 50W active-clamped,

self-driven synchronous rectification forward converter

in continuous-conduction mode. The main switch gate

driver (NDRV) and the active-clamped switch driver

(AUXDRV) are sized to optimize efficiency for 25W

design. The features-rich devices are ideal for PoE IEEE

802.3af/at-powered devices.

The MAX5974A/MAX5974C offer a 20V bootstrap UVLO

wake-up level with a 13V wide hysteresis. The low

startup and operating currents allow the use of a smaller

storage capacitor at the input without compromising

startup and hold times. The MAX5974A/MAX5974C are

well-suited for universal input (rectified 85V AC to 265V

AC) or telecom (-36V DC to -72V DC) power supplies.

The MAX5974B/MAX5974D have a UVLO rising threshold

of 10V and can accommodate for low-input voltage (12V

DC to 24V DC) power sources such as wall adapters.

Power supplies designed with the MAX5974A/MAX5974C

use a high-value startup resistor, R

reservoir capacitor, C

Circuits). During this initial period, while the voltage is

less than the internal bootstrap UVLO threshold, the

device typically consumes only 100FA of quiescent current. This low startup current and the large bootstrap

UVLO hysteresis help to minimize the power dissipation

across R

voltage (265V AC).

Feed-forward maximum duty-cycle clamping detects changes in line conditions and adjusts the maximum duty cycle

accordingly to eliminate the clamp voltage’s (i.e., the main

power FET’s drain voltage) dependence on the input voltage.

For EMI-sensitive applications, the programmable frequency dithering feature allows up to Q10% variation in

the switching frequency. This spread-spectrum modulation technique spreads the energy of switching harmonics over a wider band while reducing their peaks, helping to meet stringent EMI goals.

The devices include a cycle-by-cycle current limit

that turns off the main and AUX drivers whenever the

internally set threshold of 400mV is exceeded. Eight

consecutive occurrences of current-limit events trigger

hiccup mode, which protects external components by

halting switching for a period of time (t

ing the overload current to dissipate in the load and

body diode of the synchronous rectifier before soft-start

is reattempted.

even at the high end of the universal AC input

IN

(see the Typical Application

IN

, that charges a

IN

) and allow-

RSTRT

The reverse current-limit feature of the devices turns

the AUX driver off for the remaining off period when

exceeds the -100mV threshold. This protects the

V

CS

transformer core from saturation due to excess reverse

current under some extreme transient conditions.

Current-Mode Control Loop

The advantages of current-mode control over voltagemode control are twofold. First, there is the feed-forward

characteristic brought on by the controller’s ability to adjust

for variations in the input voltage on a cycle-by-cycle basis.

Second, the stability requirements of the current-mode

controller are reduced to that of a single-pole system,

unlike the double pole in voltage-mode control.

The devices use a current-mode control loop where the

scaled output of the error amplifier (COMP) is compared

to a slope-compensated current-sense signal at CSSC.

Enable Input

The enable input EN is used to enable or disable the

device. Connect EN to IN for always enabled applications. Connecting EN to ground disables the device and

reduces current consumption to 150FA.

The enable input has an accurate threshold of 1.26V

(max). For applications that require a UVLO on the

power source, connect a resistive divider from the power

source to EN to GND as shown in Figure 1. A zener

diode between IN and PGND is required to prevent

IN from exceeding its absolute maximum rating of 26V

when the device is disabled. The zener diode should be

inactive below the maximum UVLO rising threshold voltage V

INUVR(MAX)

and 10.5V for the MAX5974B/MAX5974D). Design the

resistive divider by first selecting the value of R

on the order of 100kI. Then calculate R

where V

age and is equal to 1.26V and V

UVLO threshold for the power source, below which the

devices are disabled.

In the case where EN is externally controlled and UVLO

for the power source is unnecessary, connect EN to IN

and an open-drain or open-collector output as shown in

Figure 2. The digital output connected to EN should be

capable of withstanding IN’s absolute maximum voltage

of 24V.

EN(MAX)

(21V for the MAX5974A/MAX5974C

EN2

V

R R

EN2 EN1

is the maximum enable threshold volt-

V V=−

EN(MAX)

S(UVLO) EN(MAX)

S(UVLO)

is the desired

to be

EN1

as follows:

MAX5974A/MAX5974B/MAX5974C/MAX5974D

15

Page 16

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

V

S

The devices have an internal bootstrap UVLO that is very

Bootstrap Undervoltage Lockout

useful when designing high-voltage power supplies (see

the Block Diagrams). This allows the device to bootstrap

R

IN

IN

C

IN

R

EN1

MAX5974

itself during initial power-up. The MAX5974A/MAX5974C

soft-start when V

old of V

INUVR

exceeds the bootstrap UVLO thresh-

IN

(20V typ).

Because the MAX5974B/MAX5974D are designed for

use with low-voltage power sources such as wall adapters outputting 12V to 24V, they have a lower UVLO

wake-up threshold of 10V.

Startup Operation

DIGITAL

CONTROL

EN

R

EN2

N

The device starts up when the voltage at IN exceeds

20V (MAX5974A/MAX5974C) or 10V (MAX5974B/

MAX5974D) and the enable input voltage is greater than

1.26V.

During normal operation, the voltage at IN is normally derived from a tertiary winding of the transformer

(MAX5974C/MAX5974D). However, at startup there is

no energy being delivered through the transformer;

Figure 1. Programmable UVLO for the Power Source

V

S

hence, a special bootstrap sequence is required. In the

Typical Application Circuits, C

startup resistor, R

, to an intermediate voltage. Only

IN

100FA of the current supplied through R

charges through the

IN

IN

the ICs, the remaining input current charges C

reaches the bootstrap UVLO wake-up level. Once

V

IN

exceeds this level, NDRV begins switching the

V

R

IN

IN

n-channel MOSFET and transfers energy to the second-

IN

C

IN

MAX5974

ary and tertiary outputs. If the voltage on the tertiary

output builds to higher than 7V (the bootstrap UVLO

shutdown level), then startup has been accomplished

and sustained operation commences. If V

drops below

IN

7V before startup is complete, the device goes back to

low-current UVLO. In this case, increase the value of C

DIGITAL

CONTROL

EN

N

in order to store enough energy to allow for the voltage

at the tertiary winding to build up.

While the MAX5974A/MAX5974B derive their input voltage from the coupled inductor output during normal

operation, the startup behavior is similar to that of the

MAX5974A/MAX5974B/MAX5974C/MAX5974D

MAX5974C/MAX5974D.

Soft-Start

Figure 2. External Control of the Enable Input

A capacitor from SS to GND, CSS, programs the softstart time. V

controls the oscillator duty cycle during

SS

is used by

until

IN

IN

16

Page 17

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

startup to provide a slow and smooth increase of the

duty cycle to its steady-state value. Calculate the value

as follows:

of C

SS

I t

C

=

SS

where I

ing soft-start and t

A resistor can also be added from the SS pin to GND to

clamp VSS < 2V and, hence, program the maximum duty

cycle to be less than 80% (see the Duty-Cycle Clamping

section).

(10FA typ) is the current charging CSS dur-

SS-CH

is the programmed soft-start time.

SS

n-Channel MOSFET Gate Driver

The NDRV output drives an external n-channel MOSFET.

NDRV can source/sink in excess of 650mA/1000mA

peak current; therefore, select a MOSFET that yields

acceptable conduction and switching losses. The external MOSFET used must be able to withstand the maximum clamp voltage.

×

SS-CH SS

2V

p-Channel MOSFET Gate Driver

The AUXDRV output drives an external p-channel

MOSFET with the aid of a level shifter. The level shifter

, R

consists of C

Application Circuits. When AUXDRV is high, C

recharged through D5. When AUXDRV is low, the gate

of the p-channel MOSFET is pulled below the source by

the voltage stored on C

Add a zener diode between gate to source of the external n-channel and p-channel MOSFETs after the gate

resistors to protect V

maximum rating during transient condition (see the

Typical Application Circuits).

AUX

, and D5 as shown in the Typical

AUX

, turning on the pFET.

AUX

from rising above its absolute

GS

AUX

is

Dead Time

Dead time between the main and AUX output edges

allow ZVS to occur, minimizing conduction losses and

improving efficiency. The dead time (t

both leading and trailing edges of the main and AUX outputs as shown in Figure 3. Connect a resistor between

DT and GND to set t

400ns:

to any value between 40ns and

DT

) is applied to

DT

MAX5974A/MAX5974B/MAX5974C/MAX5974D

BLANKING, t

DEAD TIME, t

Figure 3. Dead Time Between AUXDRV and NDRV

BLK

NDRV

AUXDRV

DT

10k

R t

DT DT

Ω

= ×

40ns

17

Page 18

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Oscillator/Switching Frequency

The ICs’ switching frequency is programmable between

100kHz and 600kHz with a resistor R

connected

RT

between RT and GND. Use the following formula to

determine the appropriate value of R

erate the desired output-switching frequency (f

8.7 10

×

=

f

SW

where f

R

RT

is the desired switching frequency.

SW

needed to gen-

RT

9

SW

):

Peak Current Limit

The current-sense resistor (R

in the Typical

CS

Application Circuits), connected between the source

of the n-channel MOSFET and PGND, sets the current

limit. The current-limit comparator has a voltage trip level

(V

CS-PEAK

culate the value of R

where I

) of 400mV. Use the following equation to cal-

:

CS

400mV

RI=

CS

is the peak current in the primary side of

PRI

PRI

the transformer, which also flows through the MOSFET.

When the voltage produced by this current (through the

current-sense resistor) exceeds the current-limit comparator threshold, the MOSFET driver (NDRV) terminates

the current on-cycle, within 35ns (typ).

The devices implement 115ns of leading-edge blanking

to ignore leading-edge current spikes. These spikes

are caused by reflected secondary currents, currentdischarging capacitance at the FET’s drain, and gatecharging current. Use a small RC network for additional

filtering of the leading-edge spike on the sense waveform when needed. Set the corner frequency between

10MHz and 20MHz.

After the leading-edge blanking time, the device monitors V

for any breaches of the peak current limit of

CS

400mV. The duty cycle is terminated immediately when

exceeds 400mV.

V

CS

Reverse Current Limit

The devices protect the transformer against saturation

due to reverse current by monitoring the voltage across

while the AUX output is low and the p-channel FET

R

CS

is on.

Output Short-Circuit Protection

with Hiccup Mode

When the device detects eight consecutive peak currentlimit events, both NDRV and AUXDRV driver outputs are

turned off for a restart period, t

RSTRT

. After t

RSTRT

, the

device undergoes soft-start. The duration of the restart

period depends on the value of the capacitor at SS (C

During this period, C

rent of I

(2FA typ). Once its voltage reaches 0.15V,

SS-DH

is discharged with a pulldown cur-

SS

SS

).

the restart period ends and the device initiates a soft-start

sequence. An internal counter ensures that the minimum

restart period (t

RSTRT-MIN

time required for C

) is 1024 clock cycles when the

to discharge to 0.15V is less than

SS

1024 clock cycles. Figure 4 shows the behavior of the

device prior and during hiccup mode.

V

CS-PEAK

V

CSBL

(BLANKED CS

VOLTAGE)

MAX5974A/MAX5974B/MAX5974C/MAX5974D

SOFT-START

VOLTAGE,

V

SS

Figure 4. Hiccup Mode Timing Diagram

18

HICCUP

DISCHARGE WITH I

V

SS-HI

t

SS

(400mV)

SS-DH

t

RSTRT

V

SS-DTH

Page 19

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Frequency Foldback for High-Efficiency

Light-Load Operation

The frequency foldback threshold can be programmed

from 0 to 20% of the full load current using a resistor from

FFB to GND.

When V

CSAVG

falls below V

the switching frequency to 1/2 the original value to

reduce switching losses and increase the converter efficiency. Calculate the value of R

10 I R

× ×

LOAD(LIGHT) CS

=

where R

I

LOAD(LIGHT)

FFB

R

FFB

is the resistor between FFB and GND,

is the current at light-load conditions that

triggers frequency foldback, R

sense resistor connected between CS and PGND, and

is the current sourced from FFB to R

I

FFB

The maximum duty cycle is determined by the lowest

of three voltages: 2V, the voltage at SS (V

voltage (2.43V - V

DCLMP

calculated as:

D

MAX

where V

= minimum (2V, VSS, 2.43V - V

MIN

By connecting a resistor between SS and ground, the

voltage at SS can be made to be lower than 2V. V

calculated as follows:

V R I= ×

SS SS SS-CH

where RSS is the resistor connected between SS and

GND, and I

is the current sourced from SS to RSS

SS-CH

(10FA typ).

To set D

using supply voltage feed-forward, connect

MAX

a resistive divider between the supply voltage, DCLMP,

and GND as shown in the Typical Application Circuits.

This feed-forward duty-cycle clamp ensures that the

external n-channel MOSFET is not stressed during supply transients. V

is calculated as follows:

DCLMP

, the device folds back

FFB

as follows:

FFB

I

FFB

is the value of the

CS

(30FA typ).

FFB

Duty-Cycle Clamping

), and the

SS

). The maximum duty cycle is

V

MIN

=

2.43V

).

DCLMP

SS

is

SS

DCLMP

R

DCLMP2

DCLMP2

+

are the resistive divider

DCLMP1 DCLMP2

S

where R

V V

DCLMP S

DCLMP1

= ×

R R

and R

values shown in the Typical Application Circuits and V

is the input supply voltage.

Oscillator Synchronization

The internal oscillator can be synchronized to an external

clock by applying the clock to DITHER/SYNC directly. The

external clock frequency can be set anywhere between

1.1x to 2x the internal clock frequency.

Using an external clock increases the maximum duty

cycle by a factor equal to f

SYNC/fSW

. This factor should

be accounted for in setting the maximum duty cycle

using any of the methods described in the Duty-Cycle

Clamping section. The formula below shows how the

maximum duty cycle is affected by the external clock

frequency:

MIN

f

SYNC

SW

SYNC

is

V

= ×

2.43V f

where V

section, f

D

MAX

is described in the Duty-Cycle Clamping

MIN

is the switching frequency as set by the

SW

resistor connected between RT and GND, and f

the external clock frequency.

Frequency Dithering for Spread-

Spectrum Applications (Low EMI)

The switching frequency of the converter can be dithered in a range of Q10% by connecting a capacitor from

DITHER/SYNC to GND, and a resistor from DITHER to

RT as shown in the Typical Application Circuits. This

results in lower EMI.

A current source at DITHER/SYNC charges the capacitor C

it discharges C

to 2V at 50FA. Upon reaching this trip point,

DITHER

DITHER

to 0.4V at 50FA. The charging

and discharging of the capacitor generates a triangular

waveform on DITHER/SYNC with peak levels at 0.4V and

2V and a frequency that is equal to:

50 A

DITHER

µ

×

f

=

TRI

C 3.2V

MAX5974A/MAX5974B/MAX5974C/MAX5974D

19

Page 20

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Typically, f

R

DITHER

mines the amount of dither as follows:

should be set close to 1kHz. The resistor

TRI

connected from DITHER/SYNC to RT deter-

Applications Information

Startup Time Considerations

The bypass capacitor at IN, CIN, supplies current

%DITHER

4

= ×

3 R

RT

DITHER

R

where %DITHER is the amount of dither expressed as a

percentage of the switching frequency. Setting R

to 10 x R

generates Q10% dither.

RT

DITHER

Programmable Slope Compensation

The device generates a current ramp at CSSC such that

its peak is 50FA at 80% duty cycle of the oscillator. An

external resistor connected from CSSC to the CS then

converts this current ramp into programmable slopecompensation amplitude, which is added to the currentsense signal for stability of the peak current-mode

control loop. The ramp rate of the slope compensation

signal is given by:

R 50 A f

m

=

× µ ×

CSSC SW

80%

immediately after the devices wake up (see the Typical

Application Circuits). Large values of C

the startup time, but also supply gate charge for more

cycles during initial startup. If the value of C

small, V

enough time to switch and build up sufficient voltage

drops below 7V because NDRV does not have

IN

across the tertiary output (MAX5974C/MAX5974D) or

coupled inductor output (MAX5974A/MAX5974B), which

powers the device. The device goes back into UVLO

and does not start. Use a low-leakage capacitor for C

Typically, offline power supplies keep startup times to

less than 500ms even in low-line conditions (85V AC

input for universal offline or 36V DC for telecom applications). Size the startup resistor, R

, to supply both the

IN

maximum startup bias of the device (150FA) and the

charging current for C

within the desired 500ms time period. C

. CIN must be charged to 20V

IN

IN

enough charge to deliver current to the device for at

least the soft-start time (t

) set by CSS. To calculate the

SS

IN

approximate amount of capacitance required, use the

where m is the ramp rate of the slope-compensation

signal, R

is the value of the resistor connected

CSSC

between CSSC and CS used to program the ramp rate,

and f

is the switching frequency.

SW

Error Amplifier

following formula:

I Q f

=

G GTOT SW

(I I )(t )

+

IN

=

IN G SS

V

C

HYST

The MAX5974A/MAX5974B include an internal error

amplifier with a sample-and-hold input. The feedback

input of the MAX5974C/MAX5974D is continuously connected. The noninverting input of the error amplifier is

connected to the internal reference and feedback is

provided at the inverting input. High open-loop gain and

unity-gain bandwidth allow good closed-loop bandwidth

where I

after startup, Q

n-channel and p-channel FETs, f

ing frequency, V

(13V typ), and t

culated as follows:

is the ICs’ internal supply current (1.8mA)

IN

is the total gate charge for the

GTOT

is the ICs’ switch-

SW

is the bootstrap UVLO hysteresis

HYST

is the soft-start time. RIN is then cal-

SS

and transient response. Calculate the power-supply output voltage using the following equation:

R R

+

V V

= ×

MAX5974A/MAX5974B/MAX5974C/MAX5974D

OUT REF

FB1 FB2

R

FB2

where V

is the minimum input supply voltage for

S(MIN)

the application (36V for telecom), V

where V

and V

amplifier’s noninverting input is internally connected to

a soft-start circuit that gradually increases the reference

voltage during startup. This forces the output voltage to

come up in an orderly and well-defined manner under all

= 1.52V for the MAX5974A/MAX5974B

REF

= 1.215V for the MAX5974C/MAX5974D. The

REF

strap UVLO wake-up level (20V), and I

supply current at startup (150FA max).

Choose a higher value for R

above if a longer startup time can be tolerated in order

to minimize power loss on this resistor.

R

IN

V V

≅

−

S(MIN) INUVR

I

START

than the one calculated

IN

INUVR

START

is the boot-

load conditions.

increase

is too

IN

IN

must store

is the IN

.

20

Page 21

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Active Clamp Circuit

Traditional clamp circuits prevent transformer saturation

by channeling the magnetizing current (I

former onto a dissipative RC network. To improve efficiency, the active clamp circuit recycles I

magnetizing inductance and clamp capacitor. V

is given by:

V

=

S

−

1 D

where V

V

CLAMP

is the voltage of the power source and D is

S

the duty cycle. To select n-channel and p-channel FETs

with adequate breakdown voltages, use the maximum

value of V

CLAMP

. V

CLAMP(MAX)

occurs when the input

voltage is at its minimum and the duty cycle is at its

maximum. V

CLAMP(MAX-NORMAL)

during normal opera-

tion is therefore:

V

where V

source, N

and V

is the output voltage. The clamp capacitor,

O

CLAMP(MAX-NORMAL)

S(MIN)

is the minimum voltage of the power

is the primary to secondary turns ratio,

P/NS

=

−

1

N V

n-channel, and p-channel FETs must have breakdown

voltages exceeding this level.

If feed-forward maximum duty-cycle clamp is used then:

V

+

during feed-forward maxi-

Therefore, V

V

D 1

MAX-FF

V R

1

= − ×

2.43 R R

CLAMP(MAX-FF)

MIN

= = −

2.43 2.43

S DCLMP2

DCLMP1 DCLMP2

mum duty clamp is:

V

CLAMP(MAX-FF)

2.43 R R

× +

=

( )

=

1 D

−

DCLMP1 DCLMP2

R

DCLMP2

The AUX driver controls the p-channel FET through a

level shifter. The level shifter consists of an RC network

) of the trans-

M

between the

M

V

S(MIN)

×

N V

P O

×

S S(MIN)

DCLMP

V

S

MAX FF

−

CLAMP

(formed by C

AUX

and R

) and diode D5, as shown

AUX

in the Typical Application Circuits. Choose R

so that the time constant exceeds 100/fSW. Diode

C

AUX

D5 is a small-signal diode with a voltage rating exceeding 25V.

Additionally, C

should be chosen such that the

CLAMP

complex poles formed with magnetizing inductance

(L

MAG

) and C

are 2x to 4x away from the loop

CLAMP

bandwidth:

1-D

2 L C

π ×

MAG CLAMP

3 f

> ×

BW

Bias Circuit

Optocoupler Feedback (MAX5974C/MAX5974D)

An in-phase tertiary winding is needed to power the bias

circuit when using optocoupler feedback. The voltage

across the tertiary V

where V

is the output voltage and NT/NS is the turns

OUT

during the on-time is:

T

N

V VN= ×

T

OUT

T

S

ratio from the tertiary to the secondary winding. Select the

turns ratio so that V

is above the UVLO shutdown level

T

(7.5V max) by a margin determined by the holdup time

needed to “ride through” a brownout.

Coupled-Inductor Feedback (MAX5974A/MAX5974B)

When using coupled-inductor feedback, the power for

the devices can be taken from the coupled inductor during the off-time. The voltage across the coupled inductor, V

COUPLED

where V

, during the off-time is:

N

V VN= ×

COUPLED

is the output voltage and NC/NO is the

OUT

OUT

C

O

turns ratio from the coupled output to the main output

winding. Select the turns ratio so that V

COUPLED

above the UVLO shutdown level (7.5V max) by a margin

determined by the holdup time needed to “ride through”

a brownout.

This voltage appears at the input of the devices, less

a diode drop. An RC network consisting of R

C

is for damping the reverse recovery transients of

SNUB

diode D6.

AUX

SNUB

MAX5974A/MAX5974B/MAX5974C/MAX5974D

and

is

and

21

Page 22

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

During on-time, the coupled output is:

N N

V (V V )

COUPLED-ON OUT

where V

Care must be taken to ensure that the voltage at FB

(equal to V

resistive divider) is not more than 5V:

If this condition is not met, a signal diode should be

placed from GND (anode) to FB (cathode).

is the input supply voltage.

S

COUPLED-ON

V V 5V

= × <

FB-ON COUPLED-ON

attenuated by the feedback

S C

S

−= − ×

N N

P O

R

FB2

R R

( )

FB1 FB2

+

Layout Recommendations

Typically, there are two sources of noise emission in a

switching power supply: high di/dt loops and high dV/dt

surfaces. For example, traces that carry the drain current

often form high di/dt loops. Similarly, the heatsink of the

main MOSFET presents a dV/dt source; therefore, minimize the surface area of the MOSFET heatsink as much

as possible. Keep all PCB traces carrying switching currents as short as possible to minimize current loops. Use

a ground plane for best results.

For universal AC input design, follow all applicable

safety regulations. Offline power supplies can require

UL, VDE, and other similar agency approvals.

MAX5974A/MAX5974B/MAX5974C/MAX5974D

22

Page 23

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Typical Application Circuits

V

R

OPTO2

1kI

1%

S

36V TO 57V

C

BULK

33µF

R

DCLMP2

R

750I 1%

14.7kI 1%

10.0kI 1%

R

G1

121kI 1%

DCLMP1

I

30.1k

1%

C

SS

0.1µF

R

DT

16.9kI 1%

C

DITHER

10nF

R

RT

R

FFB

200kI 1%

R

IN

100kI

C

IN

1µF

25V

IN

EN

DCLMP

SS

DT

(OPTOCOUPLER

DITHER/

SYNC

RT

FFB

R

G2

FB

COMP

GND

MAX5974C

MAX5974D

FEEDBACK)

PGND

L1

3.3mH

AUXDRV

NDRV

CSSC

D1

N

T

D2

L2

6.8µH

D3

T1

N

P

R

GATE3

10I

C

AUX

47nF

499I 1%

CS

C

330pF

4.02kI 1%

18V

F

R

GATE1

N

S

10I

D4

N3

FDS3692

N

R

F

D5

R

CSSC

R

CS

0.2I

N

N1

5i412DP

R

GATE4

10I

18V

R

AUX

10kI

R

10I

GATE2

C

1%

U2

TLV4314AIDBVT-1.24V

OUT5

0.1µF

C

COMP1

2.2nF

R

4.02kI

1%

BIAS

R

2.00kI

COMP2

1%

C

OUT1COUT2COUT3COUT4

N2

N

5i412DP

IN

R

OPTO3

4.99kI

C

CLAMP

47nF

FOD817CSD

N4

P

IRF6217

1%

R

OPTO1

825I

U1

R

COMP2

499I

1%

C

COMP2

6.8pF

C

INT

0.1µF

5V, 5A

R

FB1

7.5kI

1%

R

FB2

2.49kI

1%

MAX5974A/MAX5974B/MAX5974C/MAX5974D

23

Page 24

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Typical Application Circuits (continued)

D6

R

FB1

18V

54.9kI 1%

TO FB

R

FB2

10kI 1%

L

COUPLED

N

C

N

N

C

CLAMP

47nF

O

N2

5i412DP

N4

IRF6217

R

GATE2

10I

N

N1

P

4 x 47µF

6.3V

C

OUT1COUT2COUT3COUT4

R

C

SNUB

V

S

36V TO 57V

C

BULK

33µF

63V

R

DCLMP1

30.1kI

1%

R

DCLMP2

750I 1%

C

SS

0.1µF

R

DT

16.9kI 1%

C

DITHER

10nF

R

RT

14.7kI 1%

R

FFB

10kI 1%

C

COMP

4.7nF

MAX5974A/MAX5974B/MAX5974C/MAX5974D

C

47nF

INT

R

2kI 1%

R

IN

100kI

C

IN

1µF

IN

EN

DCLMP

SS

25V

MAX5974A

T1

N

P

MAX5974B

DT

(COUPLED INDUCTOR

FEEDBACK)

DITHER/

SYNC

RT

FFB

FB

Z

COMP

GND

AUXDRV

PGND

NDRV

CSSC

R

GATE3

10I

18V

C

AUX

47nF

CS

499I 1%

C

F

330pF

R

CSSC

4.02kI 1%

SNUB

69.8I 1%

10pF

D3

R

N

R

F

GATE1

S

10I

D4

5i412DP

N3

FDS3692

N

R

GATE4

10I

R

AUX

D5

10kI

R

CS

0.2I

5V, 5A

C

OUT5

0.1µF

24

Page 25

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Typical Application Circuits (continued)

MAX5974A/MAX5974B/MAX5974C/MAX5974D

C

V

S

BULK

R

DCLMP2

C

DITHER

R

R

DCLMP1

R

DT

R

RT

FFB

C

SS

R

DITHER

R

IN

IN

EN

DCLMP

SS

DT

DITHER/

SYNC

RT

FFB

C

MAX5974C

MAX5974D

IN

AUXDRV

NDRV

L1

T1

N

R

C

CS

P

GATE3

18V

AUX

N

S

R

GATE1

D4

N

D1

N

T

D2

L2

D3

N3

R

GATE4

18V

R

GATE2

N

N2

N

N1

C

CLAMP

N4

P

C

OUT1COUT2COUT3COUT4

R

FB1

R

FB2

PGND

CSSC

R

CSSC

C

COMP

FB

COMP

R

z

GND

C

HF

Chip Information

PROCESS: BiCMOS

D5

R

AUX

R

CS

Package Information

For the latest package outline information and land patterns,

go to www.maxim-ic.com/packages. Note that a “+”, “#”, or

“-” in the package code indicates RoHS status only. Package

drawings may show a different suffix character, but the drawing

pertains to the package regardless of RoHS status.

PACKAGE

TYPE

16 TQFN-EP T1633+4

PACKAGE

CODE

OUTLINE

NO.

LAND

PATTERN NO.

21-0136 90-0031

25

Page 26

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

Revision History

REVISION

NUMBER

0 6/10 Initial release —

1 9/10

REVISION

DATE

DESCRIPTION

Introduced the MAX5974B/MAX5974D. Updated the Absolute Maximum

Ratings, Electrical Characteristics, Pin Description, the p-Channel MOSFET

Gate Driver, Frequency Foldback for High-Efficiency Light-Load Operation

sections, and Typical Application Circuits.

PAGES

CHANGED

1, 2, 3, 12, 15, 17,

19, 21, 23, 24, 25

MAX5974A/MAX5974B/MAX5974C/MAX5974D

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied.

Maxim reserves the right to change the circuitry and specifications without notice at any time.

26 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

©

2010 Maxim Integrated Products Maxim is a registered trademark of Maxim Integrated Products, Inc.

Loading...

Loading...