Page 1

General Description

The MAX3540 complete single-conversion television

tuner is designed for use in analog/digital terrestrial applications and digital set-top boxes. This television tuner

draws only 760mW of power from a +3.3V supply voltage.

The MAX3540 is designed to convert NTSC or ATSC signals in the 54MHz to 860MHz band to a 44MHz intermediate frequency (IF).

The MAX3540 includes a variable-gain low-noise amplifier (LNA), multiband tracking filters, a harmonic-rejection mixer, a low-noise IF amplifier, an IF power detector,

and a variable-gain IF amplifier. The MAX3540 also

includes fully monolithic VCOs and tank circuits as well

as a complete frequency synthesizer. This highly integrated design allows for low-power tuner-on-board

applications without the cost and power-dissipation

issues of dual-conversion tuner solutions.

The MAX3540 is specified for operation in the 0°C to

+85°C temperature range and is available in a leadless

48-pin flip-chip (fcLGA) package.

Applications

Televisions

Analog/Digital Terrestrial Receivers

Digital Set-Top Boxes

Cable Modems

VOIP Gateways

Features

♦ Low Power Consumption: 760mW (typ) from a

+3.3V Supply Voltage

♦ Integrated Tracking Filters

♦ ATSC A/74 Compliant

♦ 40dB Adjacent Channel Protection Ratio (ACPR)

♦ 4.4dB (typ) Low Noise Figure

♦ Small, 7mm x 7mm, fcLGA Leadless Package

♦ 256-QAM-Compatible Phase-Noise Performance

♦ IF Overload Detector Controls RF Variable-Gain

Amplifier

♦ 2-Wire I

2

C-Compatible Serial Control Interface

MAX3540

Complete Single-Conversion Television Tuner

________________________________________________________________

Maxim Integrated Products

1

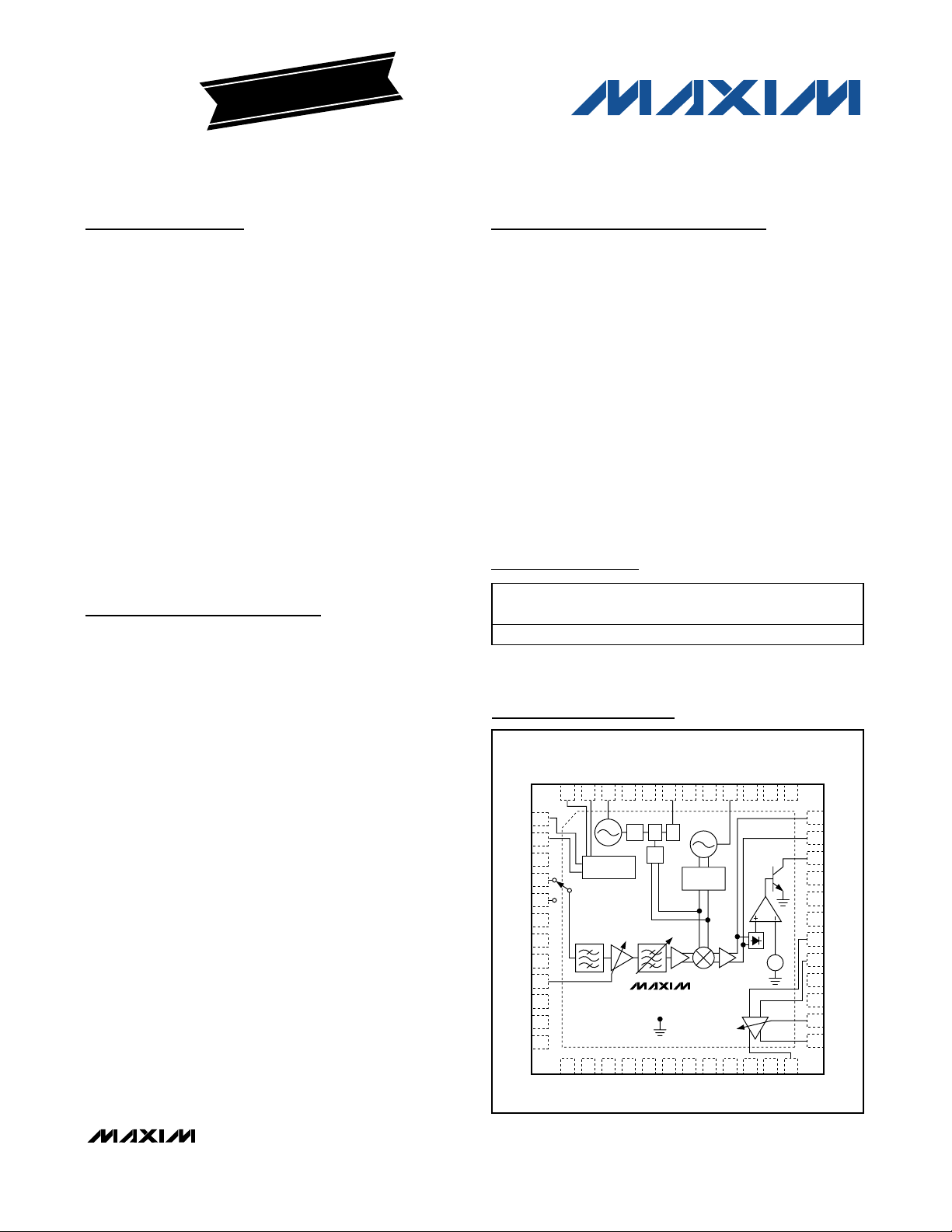

Pin Configuration

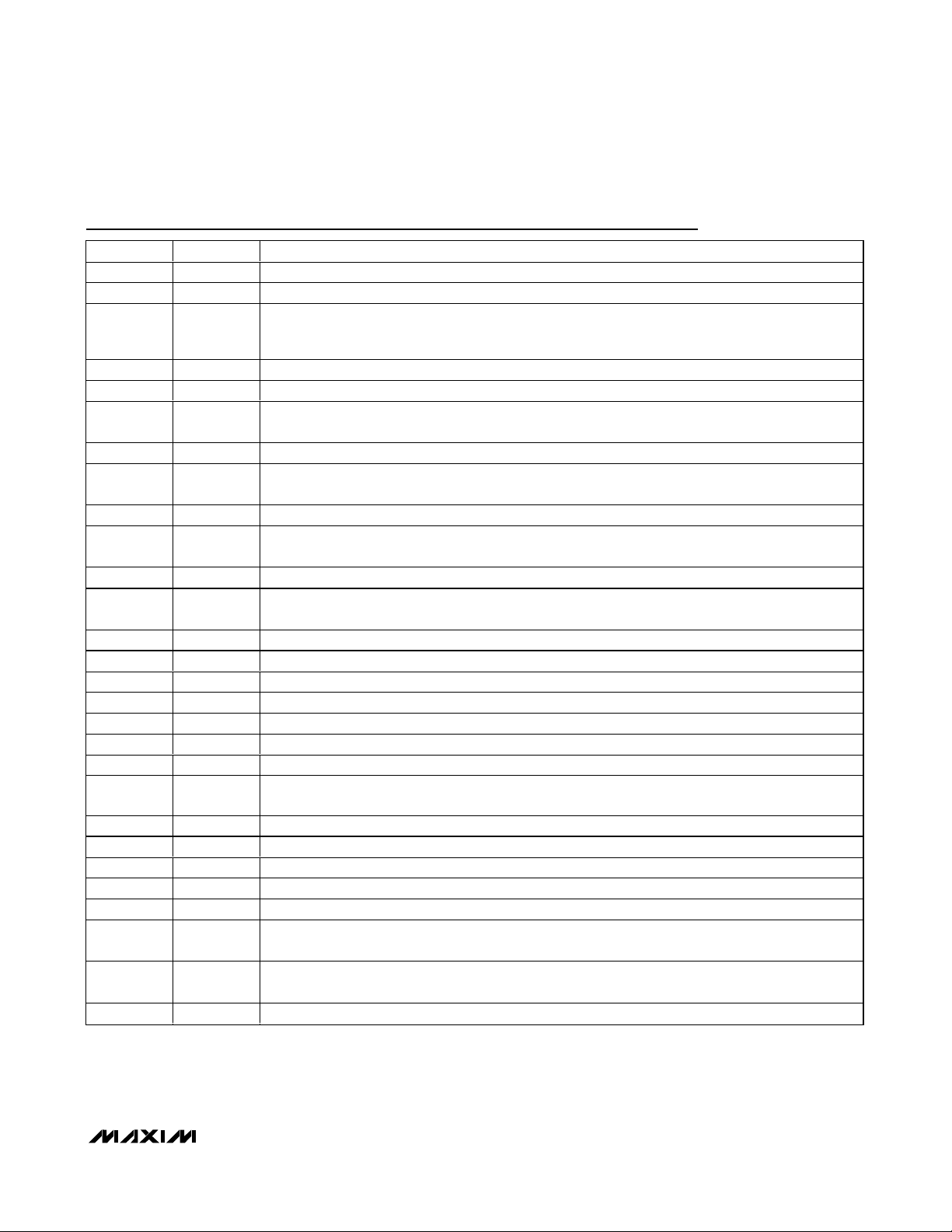

Ordering Information

19-0848; Rev 0; 10/07

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

*

EP = Exposed paddle.

EVALUATION KIT

AVAILABLE

PART

TEMP

RANGE

PINPACKAGE

PKG

CODE

MAX3540ULM#G42 0°C to +85°C 48 fcLGA-EP* L4877A-E

SCL

SDA

V

UHF_IN

VHF_IN

RFGND2

LEXT

RFGND3

RFAGC

V

GND

GND

GND

MUX

VCO

DIVIDER

GND

CC

V

GND

VTUNE

40414243 39 38 37464748

GND

XTALP

GND

÷

16 21201918 22 23 24151413

XTALN

4445

R

MAX3540

17

GND

VCCCP

PD CP

÷

N

EP

GND

ADDR2

ADDR1

+

1

2

3

CC

4

5

6

7

8

9

10

CC

11

12

GND

SERIAL

INTERFACE

GND

LDO

GND_TUNE

V

+

-

CC

V

GND

REF

CC

V

IFOUT2-

36

IFOUT1-

35

IFOUT1+

34

IFOVLD

33

V

CC

V

32

CC

31

GND

30

IFIN+

IFIN-

29

28

V

CC

27

GND

26

IFAGC

25

IFOUT2+

Page 2

MAX3540

Complete Single-Conversion Television Tuner

2 _______________________________________________________________________________________

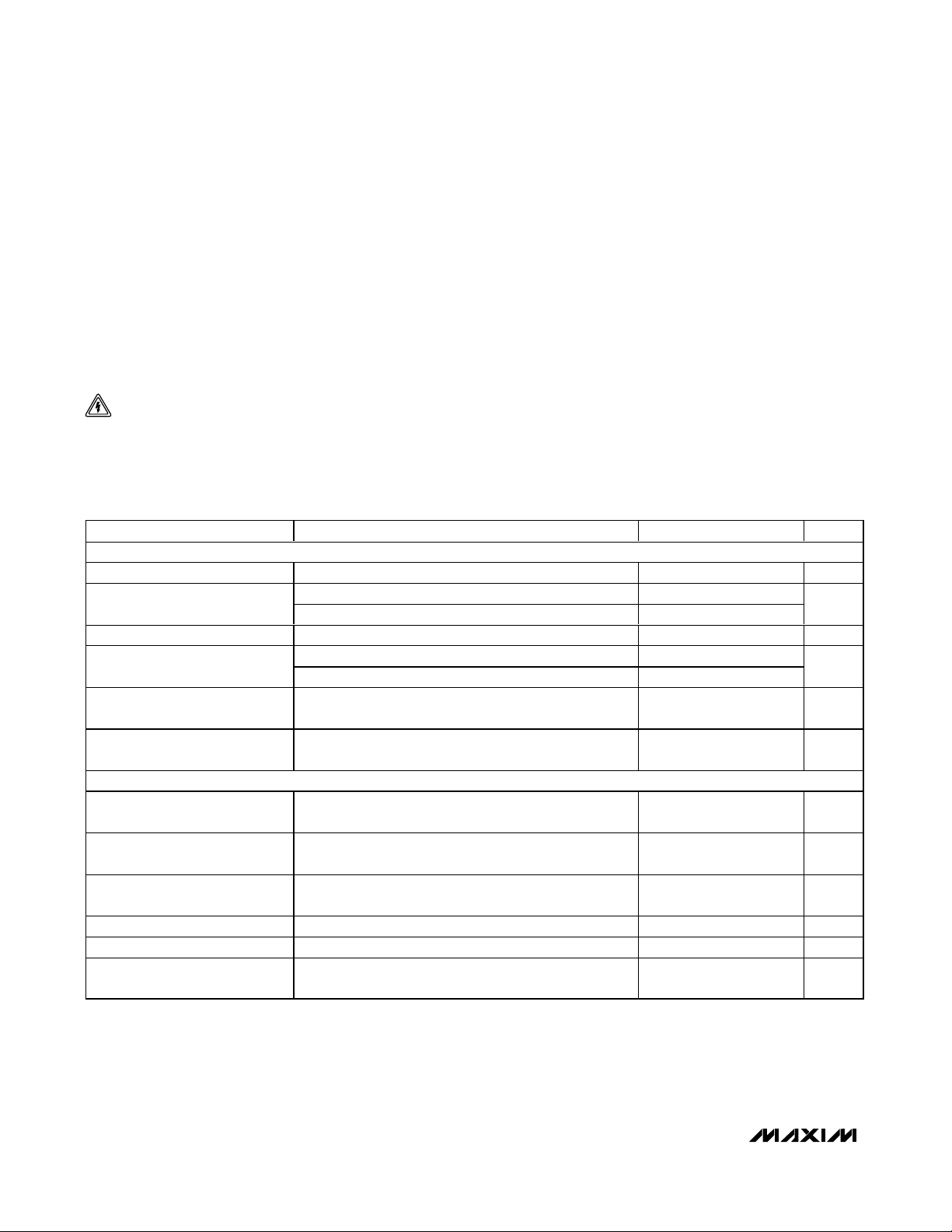

ABSOLUTE MAXIMUM RATINGS

DC ELECTRICAL CHARACTERISTICS

(MAX3540 Evaluation Kit, VCC= +3.1V to +3.5V, no RF signals at RF inputs, default register settings, V

RFAGC

= V

IFAGC

= +3V (minimum

attenuation), T

A

= 0°C to +85°C, unless otherwise noted. Typical values are at VCC= +3.3V, TA= +25°C, unless otherwise noted.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VCCto GND..............................................................-0.3V, +3.6V

RFIN, IFIN_, IFOUT1_, IFOUT2_, IFAGC, RFAGC,

VTUNE, LDO, MUX, CP, XTAL to GND ..-0.3V to (V

CC

+ 0.3V)

SDA, SCL, ADDR2, ADDR1 to GND......................-0.3V to +3.6V

IFOUT__ Short-Circuit Duration .....................................Indefinite

RF Input Power ...............................................................+10dBm

Continuous Power Dissipation (T

A

= +70°C)

48-Pin fcLGA (derate 25mW/°C above +70°C) ...............1.4W

Operating Temperature Range...............................0°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +165°C

Lead Temperature (soldering, 10s) .................................+240°C

CAUTION! ESD SENSITIVE DEVICE

SUPPLY VOLTAGE AND CURRENT

Supply Voltage +3.1 +3.5 V

Supply Current

RF and IF AG C Inp ut Bi as C ur r ent At +0.5V and +3V -50 +50 μA

RF and IF AGC Control Voltage

(Note 1)

Digital Input Logic-Level Low

Digital Input Logic-Level High

SERIAL INTERFACE

Input Logic-Level Low

Input Logic-Level High

Input Hysteresis

SDA, SCL Input Current -10 +10 μA

Output Logic-Level Low 3mA sink current 0.4 V

Output Logic-Level High

PARAMETER CONDITIONS MIN TYP MAX UNITS

Receive mode 240 275

Shutdown mode 5

Minimum attenuation +3

Maximum attenuation +0.5

0.7 x

V

CC

0.7 x

V

CC

V

CC

0.5

0.05 x

V

-

CC

0.3 x

V

CC

0.3 x

V

CC

mA

V

V

V

V

V

V

V

Page 3

MAX3540

Complete Single-Conversion Television Tuner

_______________________________________________________________________________________ 3

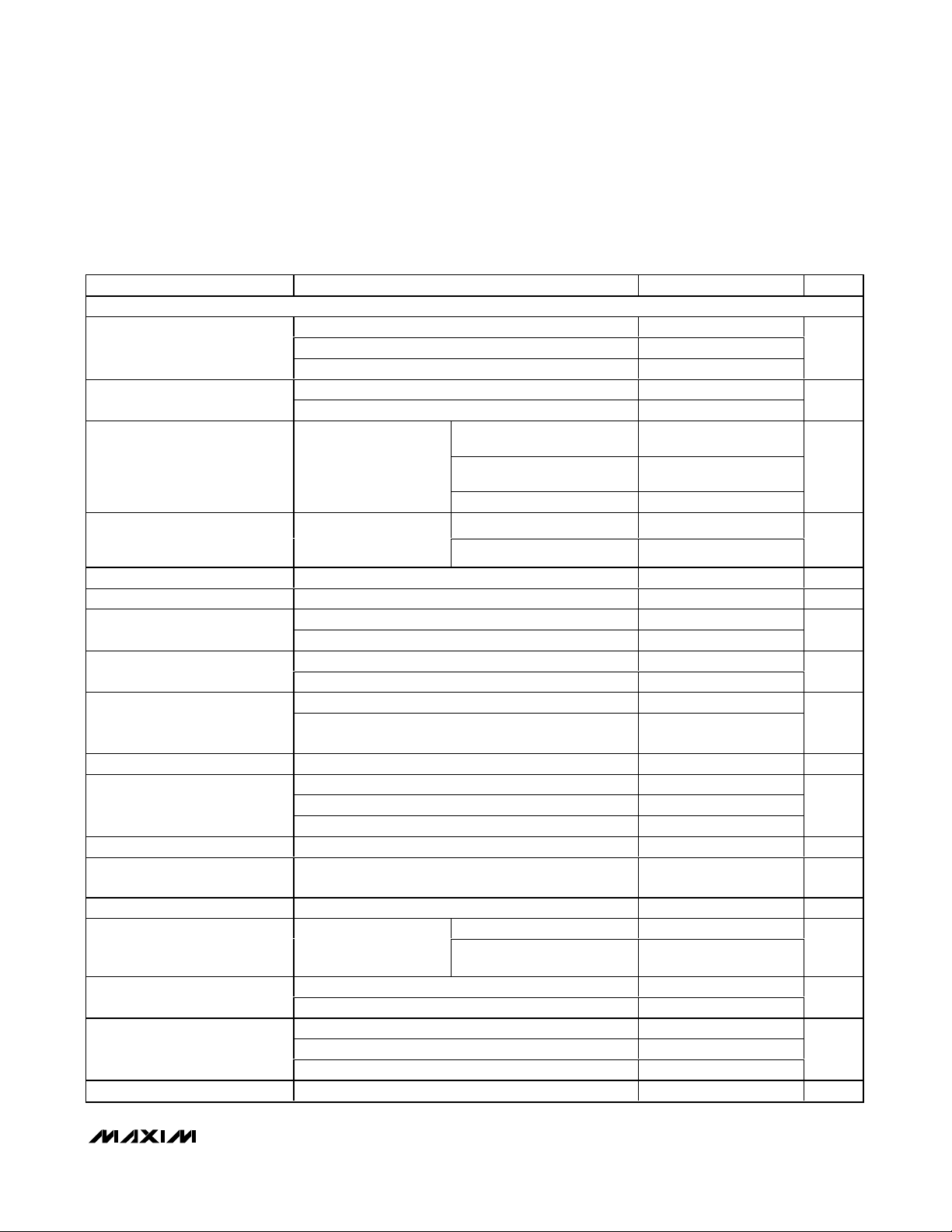

AC ELECTRICAL CHARACTERISTICS

(MAX3540 Evaluation Kit, VCC= +3.1V to +3.5V, 75Ω system impedance, default register settings, V

RFAGC

= V

IFAGC

= +3V (minimum

attenuation), T

A

= 0°C to +85°C, unless otherwise noted. Typical values are at VCC= +3.3V, TA= +25°C, unless otherwise noted.)

RF INPUT TO IFOUT1_ OUTPUT

Operating Frequency Range

(See Table 7)

Output Frequency

Voltage Gain

Operating Frequency Range

Input Return Loss Worst case, selected channel 8 dB

Noise Figure Maximum gain, V

Input IP2

(In-Band and Out-of-Band Tones)

Input IP3

(In-Band and Out-of-Band Tones)

Input P

Beats Within Output 0dBmV PIX carrier level (Note 1) -60 dBc

Gain Flatness 54MHz to 60MHz 1.5 dB

Isolation

Port-to-Port Isolation Isolation between RF input ports at 215MHz 30 dB

Image Rejection

Spurious Leakage at RF Input

Output Return Loss Balanced 50Ω load 9 dB

PARAMETER CONDITIONS MIN TYP MAX UNITS

VHF_IN, LPF enabled, INPT = 00 54 100

VHF_IN, LPF disabled, INPT = 01 100 300

UHF_IN, INPT = 10 300 860

Analog channel PIX carrier 45.75

Digital channel center frequency 44

Source impedance =

Ω, load impedance =

75

200

Ω

Gain specification met

across these frequency

bands

RFVGC

Maximum gain, V

RFVGC

Maximum gain, V

54MHz to 860MHz

Maximum gain, V

broadcast channels

M i ni m um g ai n, V

VHF_IN 54 300

UHF_IN 300 860

= 3V (Note 1) 4.4 dB

= 3V 15

= 3V,

RFAGC

= 3V,

RFAGC

= 0.5V -11

R FA GC

At 12.5dB of gain 29

Maximum gain, V

= 3V -13

RFVGC

At 12.5dB of gain 5 11

Maximum gain, V

1dB At 12.5dB of gain, CW tone at f

69 in UHF band

VHF_IN from 150MHz to 960MHz -60

VHF_IN from 960MHz to 1400MHz -40Beats, Converted to Output

UHF_IN from 600MHz to 1400MHz -40

5MHz to 50MHz, RF input to IF output, relative to desired

channel

Measured at 91.5MHz

above desired channel’s

center frequency

5MHz to 65MHz -40

65MHz to 878MHz -40

10kHz offset -85

100kHz offset, 1.5kHz loop bandwidth -105Phase Noise (Single-Sideband)

1MHz offset, 1.5kHz loop bandwidth -125

= 3V -24.5

RFVGC

- 36MHz, tested at Ch

C

54MHz to 860MHz 70

Broadcast channels,

T

= +25°C

A

28.0 34 45.5

66

34

-3

60 dBc

MHz

MHz

dB

MHz

dBm

dBm

dBm

dBc

P-P

dBc

dBmV

dBc/Hz

Page 4

MAX3540

Complete Single-Conversion Television Tuner

4 _______________________________________________________________________________________

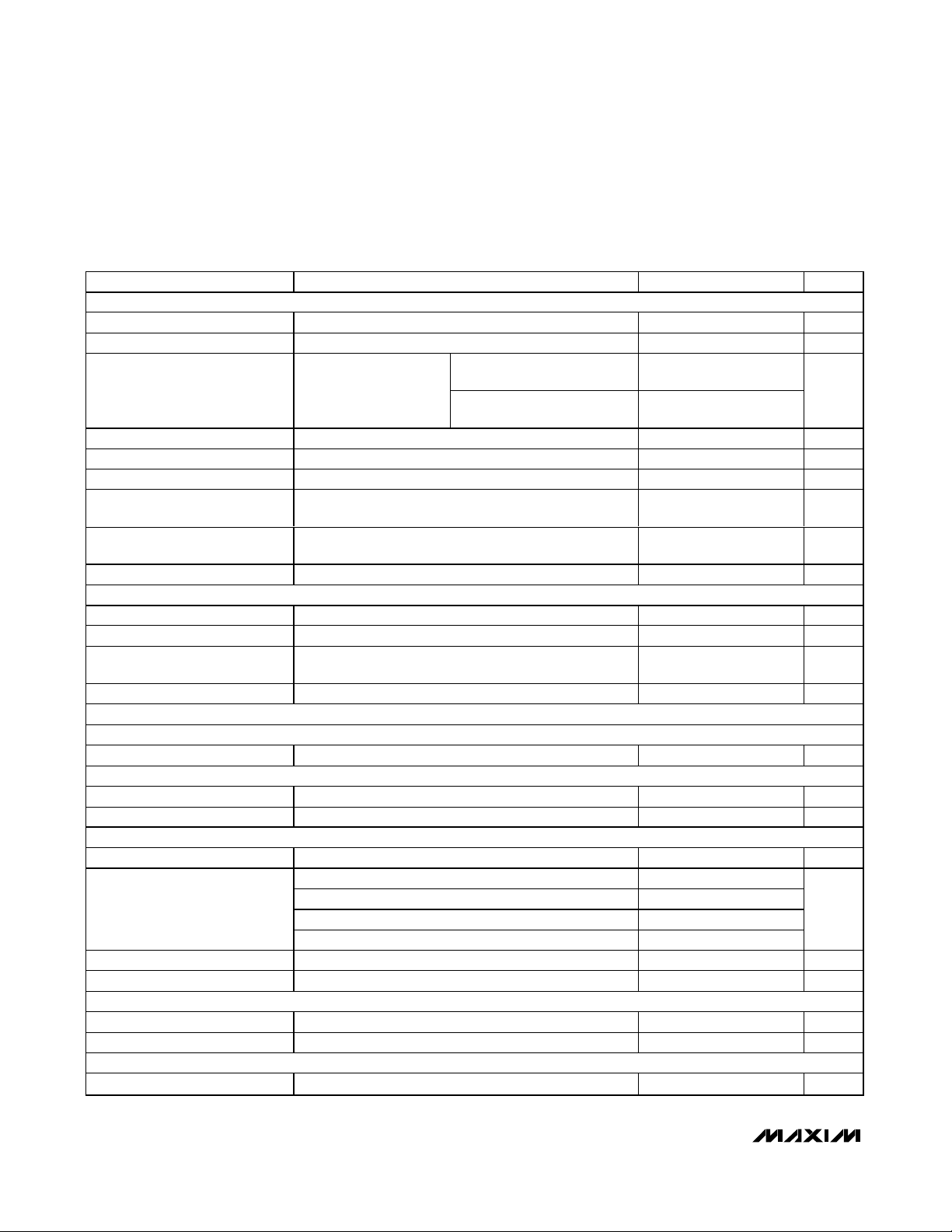

AC ELECTRICAL CHARACTERISTICS (continued)

(MAX3540 Evaluation Kit, VCC= +3.1V to +3.5V, 75Ω system impedance, default register settings, V

RFAGC

= V

IFAGC

= +3V (minimum

attenuation), T

A

= 0°C to +85°C, unless otherwise noted. Typical values are at VCC= +3.3V, TA= +25°C, unless otherwise noted.)

Note 1: Guaranteed by design and characterization.

IF VARIABLE-GAIN AMPLIFIER

Input Impedance Balanced 2000 Ω

Output Impedance Balanced (Note 1) 300 Ω

Passband Voltage Gain

Passband Gain Flatness 40MHz to 48MHz (Note 1) 1.2 dB

Output Voltage V

AGC Gain Slope V

Equivalent Input Voltage

Noise Density

Noise Figure Change vs.

Attenuation

IM3 V

IF OVERLOAD DETECTOR (see the IF Overload Detector section)

Output Overload Attack Point 0.7 V

Attack-Point Accuracy ±1 dB

Detector Output Voltage Range

Detector Gain 70 V/V

FREQUENCY SYNTHESIZER

REFERENCE OSCILLATOR

Frequency 4 MHz

DIVIDERS

RF N-Divider Ratio 256 32,767

RF R-Divider Ratio 8 127

LO PHASE DETECTOR AND CHARGE PUMP

Comparison Frequency 31.50 250.00 kHz

Charge-Pump Current

C har g e- P um p Thr ee- S tate C ur r ent ±5 nA

Charge-Pump Current Matching 5%

LOCAL OSCILLATOR (OSCILLATOR WITH NARROW BAND LOOP)

VCO Tuning Range Tank frequency 2160 4400 MHz

VCO Tuning Gain Tank oscillator gain 500 MHz/V

2-WIRE SERIAL INTERFACE

Clock Frequency 400 kHz

PARAMETER CONDITIONS MIN TYP MAX UNITS

Maximum gain setting,

= 3V

V

S our ce l oad = 300Ω ,

outp ut l oad = 300Ω

= 3V (Note 1) 2 V

IFAGC

= 3V to 0.5V (Note 1) 30 dB/V

IFAGC

At 44MHz, maximum gain, V

= 1.5V

OUT

Negative polarity, overload reduces V

(open collector, 0.3mA sink)

CP = 00 0.5

CP = 01 1

CP = 10 1.5

CP = 11 2

, 40dB < gain < 60dB (Note 1) -54 dBc

P-P

IFAGC

Minimum gain setting,

= 0.5V

V

IFAGC

= 3V (Note 1) 7.3 nV/√Hz

IFAGC

DET

54 56 65

0.5 3.0 V

< 0.35 dB/dB

dB

21

P-P

P-P

mA

Page 5

MAX3540

Pin Description

Complete Single-Conversion Television Tuner

_______________________________________________________________________________________ 5

PIN NAME FUNCTION

1 SCL 2-Wire Serial-Clock Interface. Requires a pullup resistor to VCC.

2 SDA 2-Wire Serial-Data Interface. Requires a pullup resistor to VCC.

3, 10, 23,

28, 32, 33,

37, 41, 44

4 UHF_IN UHF RF Input. Matched to 75Ω over the operating band. Requires a DC-blocking capacitor.

5 VHF_IN VHF RF Input. Matched to 75Ω over the operating band. Requires a DC-blocking capacitor.

6 RFGND2

7 LEXT RF VGA Supply Voltage. Connect through a 270nH pullup inductor to VCC.

8 RFGND3

9RFAGCRF AG C G ai n- C ontr ol V ol tag e. Accep ts a D C vol tag e fr om 0.5V ( m i ni m um g ai n) to 3V ( m axi m um g ai n) .

11–22,

27, 31

24 IFOUT2- Inver ti ng IF- V G A Outp ut. C onnect to the i np ut of an anti - al i asi ng fi l ter . Req ui r es a D C - b l ocki ng cap aci tor .

25 IFOUT2+

26 IFAGC IF AGC Gain-Control Voltage. Accepts a DC voltage from 0.5V (minimum gain) to 3V (maximum gain).

29 IFIN- Inverting IF-VGA Input. Connect to the output of an IF-SAW filter.

30 IFIN+ Noninverting IF-VGA Input. Connect to the output of an IF-SAW filter.

34 IFOVLD IF Power Detector Open-Collector Output. Requires a 10kΩ pullup resistor to VCC.

35 IFOUT1+ N oni nver ti ng IF- LN A Outp ut. Req ui r es a D C - b l ocki ng cap aci tor .

36 IFOUT1- Inverting IF-LNA Output. Requires a DC-blocking capacitor.

38 LDO VCO LDO Bypass. Bypass to ground with a 0.47μF capacitor.

39 GND_TUNE

40 VTUNE VCO Tuning Input. Connect to the PLL loop filter output.

42 MUX Test Output. Leave this pin unconnected during normal operation.

43 CP Charge-Pump Output. Connect to the PLL loop filter input.

45 XTALN Crystal Oscillator Feedback. See the Typical Application Circuit.

46 XTALP Crystal Input. Requires a DC-blocking capacitor.

47 ADDR1

48 ADDR2

EP EP Exposed Paddle. Solder evenly to the PCB ground plane for proper operation.

V

CC

GND Ground. Connect to the PCB’s ground plane.

Power-Supply Connections. Bypass each supply pin to ground with a 1000pF capacitor.

RF Ground. Bypass to the PCB’s ground plane with a 1000pF capacitor. Do not connect RFGND2

and RFGND3 together.

RF Ground. Bypass to the PCB’s ground plane with a 1000pF capacitor. Do not connect RFGND2

and RFGND3 together.

Noninverting IF-VGA Output. Connect to the input of an anti-aliasing filter. Requires a DC-blocking

capacitor.

VTUNE Ground Connection. Connect to the PCB ground plane. All loop filter component GND must

be connected to this pin (see the Typical Application Circuit).

2-Wire Serial-Interface Address Line 1. This pin along with ADDR2 sets the device address for the

2

C-compatible serial interface.

I

2-Wire Serial-Interface Address Line 2. This pin along with ADDR1 sets the device address for the

2

C-compatible serial interface.

I

Page 6

MAX3540

Complete Single-Conversion Television Tuner

6 _______________________________________________________________________________________

Detailed Description

Register Descriptions

The MAX3540 includes 11 programmable registers and

two read-only registers. The 11 programmable registers

include two N-divider registers, an R-divider register, a

VCO register, an RSSI/charge-pump/filter-select register, a control register, a shutdown register, and tracking-

filter control registers. These 11 programmable registers are also readable. The read-only registers include

a status register and a ROM table data register.

Recommended default bit settings are provided for

user convenience only and are not guaranteed. The

user must write all registers after power-up and no earlier than 100μs after power-up.

Table 1. Register Configuration

Table 2. N-DIV High Register (Address: 0000b)

REGISTER

NAME

N-DIV High Both 0x00 0 N14 N13 N12 N11 N10 N9 N8

N-DIV Low Both 0x01 N7 N6 N5 N4 N3 N2 N1 N0

R-DIV Both 0x02 0 R6 R5 R4 R3 R2 R1 R0

VCO Both 0x03 VCO4 VCO3 VCO2 VCO1 VCO0 LD VDIV1 V D IV 0

IFOVLD,

Charge

Pump, and

Filter Select

Control Both 0x05 0 0 0 0 SHDN_RF SHDN_IFAGC INPT1 IN P T0

Shutdown Both 0x06 S H D N _M IX 1 S H D N _M IX 0 S H D N _I F S H D N _P D S H D N _S Y N 0 0 0

Tracking

Filter Series

Cap

Tracking

Filter

Parallel Cap

Tracking

Filter ROM

Address

Reserved Both 0x0A X X X X X X X X

ROM Table

Data

Readback

Status Read 0x0C POR LD2 LD1 LD0 X X X X

R EA D /

W R I T E

Read 0x0B TFR7 TFR6 TFR5 TFR4 TFR3 TFR2 TFR1 TFR0

REGISTER

ADDRESS

Both 0x04 0 IFOVLD2 IFOVLD1 IFOVLD0 CP1 CP0 TF1 TF0

Both 0x07 TFS7 TFS6 TFS5 TFS4 TFS3 TFS2 TFS1 TFS0

Both 0x08 FLD 0 TFP5 TFP4 TFP3 TFP2 TFP1 TFP0

Both 0x09 0 0 0 0 TFA3 TFA2 TFA1 TFA0

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0

DATA BYTE

BIT NAME BIT LOCATION (0 = LSB)

RESERVED 7 0 Must be set to 0.

N[14:8] 6–0 001 0010

RECOMMENDED

DEFAULT

FUNCTION

Sets the most significant bits of the PLL integer divider (N). Default

integer divider value is N = 4688. N can range from 256 to 32,767.

Page 7

MAX3540

Complete Single-Conversion Television Tuner

_______________________________________________________________________________________ 7

Table 4. R-DIV Register (Address: 0010b)

Table 5. VCO Register (Address: 0011b)

Table 3. N-DIV Low Register (Address: 0001b)

BIT NAME BIT LOCATION (0 = LSB)

N[7:0] 7–0 0101 0000

RECOMMENDED

DEFAULT

FUNCTION

Sets the least significant bits of the PLL integer divider (N). Default

integer divider value is N = 4688. N can range from 256 to 32,767.

BIT NAME BIT LOCATION (0 = LSB)

RESERVED 7 0 Must be set to 0.

R[6:0] 6–0 100 0000

BIT NAME BIT LOCATION (0 = LSB)

VCO[4:3] 7, 6 01

VCO[2:0] 5, 4, 3 101

LD 2 1

VDIV[1:0] 1, 0 01

RECOMMENDED

DEFAULT

Sets the PLL reference div ider (R). Default reference divider value

is R = 64. R can range from 16 to 127.

RECOMMENDED

DEFAULT

VCO select. Selects one of three possible VCOs.

00 = VCOs shut down

01 = selects VCO1

10 = selects VCO2

11 = selects VCO3

VCO sub-band select. Selects one of eight possible VCO sub-bands.

000 = selects SB0

001 = selects SB1

010 = selects SB2

011 = selects SB3

100 = selects SB4

101 = selects SB5

110 = selects SB6

111 = selects SB7

Lock-detect enable.

0 = disabled

1 = enabled

VCO divider ratio select.

00 = sets V C O d i vi d er to 4

01 = sets V C O d i vi d er to 8

10 = sets VCO divider to 16

11 = sets VCO divider to 32

FUNCTION

FUNCTION

Page 8

MAX3540

Complete Single-Conversion Television Tuner

8 _______________________________________________________________________________________

Table 6. RSSI, Charge Pump, and Filter Select Register (Address: 0100b)

Table 7. Control Register (Address: 0101b)

BIT NAME BIT LOCATION (0 = LSB)

RESERVED 7 0 Must be set to 0.

IFO V LD [ 2:0] 6, 5, 4 000 Write content of ROM register OD[2:0] to this location.

CP[1:0] 3, 2 00

TF[1:0] 1, 0 00

BIT NAME BIT LOCATION (0 = LSB)

RESERVED 7–4 0000 Must be set to 0000.

SHDN_RF 3 0

SHDN_IFV

GA

INPT[1:0] 1, 0 00

2 1

RECOMMENDED

DEFAULT

RECOMMENDED

DEFAULT

FUNCTION

Selects the typical charge-pump current.

00 = 0.5mA

01 = 1mA

10 = 1.5mA

11 = 2mA

Selects the tracking filter band of operation.

00 = VHF low

01 = VHF high

10 = UHF

11 = factory use only

FUNCTION

RF shutdown.

0 = RF circuitry enabled

1 = RF circuitry disabled

IF VGA shutdown.

0 = IF VGA enab led

1 = IF VGA disabled

Select s the RF input.

00 = selects VHF_IN with LPF

01 = selects VHF_IN, no LPF

10 = select s UHF_IN

11 = factory use on l y

Page 9

MAX3540

Complete Single-Conversion Television Tuner

_______________________________________________________________________________________ 9

Table 8. Shutdown Register (Address: 0110b)

Table 9. Tracking-Filter Series Cap Register (Address: 0111b)

Table 10. Tracking-Filter Parallel Cap Register (Address: 1000b)

Table 11. Tracking-Filter ROM Address Register (Address: 1001b)

Table 12. Reserved Register (Address: 1010b)

*

See the RF Tracking Filter section.

BIT NAME BIT LOCATION (0 = LSB)

SHDN_MIX 7, 6 0

SHDN_IF 5 0

SHDN_PD 4 0

SHDN_SYN 3 0

RESERVED 2, 1, 0 000 Must be set to 000.

BIT NAME BIT LOCATION (0 = LSB)

TFS[7:0] 7–0 00000000* Programs series capacitor values in the tracking filter.

RECOMMENDED

DEFAULT

RECOMMENDED

DEFAULT

FUNCTION

Mixer shutdown.

00 = mixer enabled

01, 10 = factory use only

11 = mixer disabled

IF shutdown.

0 = IF section enabled

1 = IF section disabled

IF OVLD shutdown.

0 = power detector enabled

1 = power detector disabled

Frequency synthesizer shutdown.

0 = synthesizer enabled

1 = synthesizer disabled

FUNCTION

BIT NAME BIT LOCATION (0 = LSB)

FLD 7 0

Reserved 6 0 Must be set to 0.

TFP[5:0] 5–0 000000* Programs parallel capacitor values in the tracking filter.

BIT NAME BIT LOCATION (0 = LSB)

Reserved 7–4 0000 Must be set to 0000.

TFA[3:0] 3–0 0000* Address bits of the ROM register to be read.

BIT NAME BIT LOCATION (0 = LSB)

Reserved 7–0 N/A Reserved. Do not program these bits during normal operation.

RECOMMENDED

DEFAULT

RECOMMENDED

DEFAULT

RECOMMENDED

DEFAULT

FUNCTION

Filter load bit. A 0 to 1 transition of this bit forces the loading of the

ROM table data readback register.

FUNCTION

FUNCTION

Page 10

MAX3540

Complete Single-Conversion Television Tuner

10 ______________________________________________________________________________________

2-Wire Serial Interface

The MAX3540 uses a 2-wire I2C-compatible serial interface consisting of a serial-data line (SDA) and a serialclock line (SCL). SDA and SCL facilitate bidirectional

communication between the MAX3540 and the master at

clock frequencies up to 400kHz. The master initiates a

data transfer on the bus and generates the SCL signal to

permit data transfer. The MAX3540 behaves as a slave

device that transfers and receives data to and from the

master. Pull SDA and SCL high with external pullup

resistors (1kΩ or greater) for proper bus operation.

One bit is transferred during each SCL clock cycle. A

minimum of nine clock cycles is required to transfer a

byte in or out of the MAX3540 (8 data bits and an

ACK/NACK). The data on SDA must remain stable during

the high period of the SCL clock pulse. Changes in SDA

while SCL is high and stable are considered control signals (see the

START and STOP Conditions

section). Both

SDA and SCL remain high when the bus is not busy.

START and STOP Conditions

The master initiates a transmission with a START condition (S), which is a high-to-low transition on SDA while

SCL is high. The master terminates a transmission with

a STOP condition (P), which is a low-to-high transition

on SDA while SCL is high.

Acknowledge and Not-Acknowledge Conditions

Data transfers are framed with an acknowledge bit

(ACK) or a not-acknowledge bit (NACK). Both the master and the MAX3540 (slave) generate acknowledge

bits. To generate an acknowledge, the receiving device

must pull SDA low before the rising edge of the

acknowledge-related clock pulse (ninth pulse) and

keep it low during the high period of the clock pulse.

To generate a not-acknowledge condition, the receiver

allows SDA to be pulled high before the rising edge of

the acknowledge-related clock pulse, and leaves SDA

high during the high period of the clock pulse. Monitoring

the acknowledge bits allows for detection of unsuccessful

data transfers. An unsuccessful data transfer happens

if a receiving device is busy or if a system fault has

occurred. In the event of an unsuccessful data transfer,

the bus master must reattempt communication at a

later time.

Slave Address

The MAX3540 has a 7-bit slave address that must be

sent to the device following a START condition to initiate communication. The slave address is determined

by the state of the ADDR2 and ADDR1 pins and is

equal to 11000[ADDR2][ADDR1]. The 8th bit (R/W) following the 7-bit address determines whether a read or

write operation will occur. Table 15 shows the possible

address configurations.

Table 13. ROM Table Data Readback Register (Address: 1011b)

Table 14. Status Register (Address: 1100b)

Table 15. MAX3540 Address Configurations

*

See the RF Tracking Filter section.

BIT NAME BIT LOCATION (0 = LSB)

TFR[7:0] 7–0 00000000* Tracking-filter data bits read from the device’s ROM table.

BIT NAME BIT LOCATION (0 = LSB)

POR 7 0

LD[2:0] 6, 5, 4 000

Reserved 3–0 0000 Reserved.

RECOMMENDED

DEFAULT

RECOMMENDED

DEFAULT

Power-on reset.

0 = status register has been read

1 = power reset since last status register read

VCO tuning voltage indicators.

000 = PLL not in lock, tune to the next lowest sub-band

001–110 = PLL in lock

111 = PLL not in lock, tune to the next higher sub-band

ADDR2 ADDR1 WRITE ADDRESS READ ADDRESS

0 0 0xC0 0xC1

0 1 0xC2 0xC3

1 0 0xC4 0xC5

1 1 0xC6 0xC7

FUNCTION

FUNCTION

Page 11

MAX3540

Complete Single-Conversion Television Tuner

______________________________________________________________________________________ 11

The MAX3540 continuously awaits a START condition

followed by its slave address. When the device recognizes its slave address, it acknowledges by pulling the

SDA line low for one clock period. It is ready to accept

or send data depending on the R/W bit (Figure 1).

Write Cycle

When addressed with a write command, the MAX3540

allows the master to write to a single register or to multiple successive registers.

A write cycle begins with the bus master issuing a

START condition followed by the 7 slave address bits

and a write bit (R/W = 0). The MAX3540 issues an ACK

if the slave address byte is successfully received. The

bus master must then send to the slave the address of

the first register it wishes to write to. If the slave

acknowledges the address, the master can then write

one byte to the register at the specified address. Data

is written beginning with the most significant bit. The

MAX3540 again issues an ACK if the data is successfully written to the register. The master can continue to

write data to the successive internal registers with the

MAX3540 acknowledging each successful transfer, or it

can terminate transmission by issuing a STOP condition. The write cycle does not terminate until the master

issues a STOP condition.

Figure 2 illustrates an example in which registers 0

through 2 are written with 0x0E, 0xD8, and 0xE1,

respectively.

Read Cycle

A read cycle begins with the bus master issuing a

START condition followed by the seven slave address

bits and a write bit (R/W = 0). The MAX3540 issues an

ACK if the slave address byte is successfully received.

The master then sends the 8-bit address of the first register that it wishes to read. The MAX3540 then issues

another ACK. Next, the master must issue a START condition followed by the 7 slave address bits and a read

bit (R/W = 1). The MAX3540 issues an ACK if it successfully recognizes its address and begins sending data

from the specified register address starting with the

most significant bit (MSB). Data is clocked out of the

MAX3540 on the rising edge of SCL. On the 9th rising

edge of SCL, the master can issue an ACK and continue reading successive registers or it can issue a NACK

followed by a STOP condition to terminate transmission.

The read cycle does not terminate until the master

issues a STOP condition. Figure 3 illustrates an example

in which registers 0 and 1 are read back.

Figure 1. MAX3540 Slave Address Byte

Figure 2. Example: Write registers 0 through 2 with 0x0E, 0xD8, and 0xE1, respectively.

Figure 3. Example: Read data from registers 0 through 1.

SLAVE ADDRESS

S 11000ADDR2 ADDR1 R/W

SDA

SCL

NOTE: TIMING PARAMETERS CONFORM WITH I

WRITE DEVICE

START

START

ADDRESS

11000[ADDR2][ADDR1] 0 — 0x00 — 0x0E — 0xD8 — 0xE1 —

WRITE DEVICE

ADDRESS

110000[ADDR2][ADDR1] 0 — 0x00 —

123456789

2

C BUS SPECIFICATIONS.

R/W ACK

R/W ACK

WRITE REGISTER

ADDRESS

WRITE 1st REGISTER

ADDRESS

ACK

WRITE DATA TO

ACK

REGISTER 0x00

WRITE DEVICE

START

ADDRESS

110000[ADDR2][ADDR1] 1 — D7–D0 — D7–D0 —

ACK

WRITE DATA TO

REGISTER 0x01

R/W ACK

ACK

READ DATA

REG 0

WRITE DATA TO

REGISTER 0x02

READ DATA

ACK

ACK

REG 1

ACK

NACK

P

STOP

STOP

Page 12

MAX3540

Complete Single-Conversion Television Tuner

12 ______________________________________________________________________________________

Applications Information

RF Inputs

The MAX3540 features separate UHF and VHF inputs

that are matched to 75Ω. Both inputs require a DC-blocking capacitor. The input registers select the active inputs.

In addition, the input registers enable or disable the lowpass filter, which can be used when the VHF input is

selected. For 54MHz to 100MHz, select the VHF_IN with

the LPF filter enabled (INPT = 00). For 100MHz to

300MHz, select VHF_IN with LPF disabled (INPT = 01).

For 300MHz to 860MHz, select UHF_IN (INPT = 10).

RF Gain Control

The gain of the RF low-noise amplifier can be adjusted

over a typical 45dB range by the RFAGC pin. The

RFAGC input accepts a DC voltage from 0.5V to 3V,

with 3V providing maximum gain. This pin can be controlled with the IF power-detector output to form a

closed RF gain-control loop. See the

Closed-Loop RF

Gain Control

section for more information.

RF Tracking Filter

The MAX3540 includes a programmable tracking filter for

each band of operation to optimize rejection of out-ofband interference while minimizing insertion loss for the

desired received signal. VHF low, VHF high, or UHF tracking filter is selected by the TF register. The center fre-

quency of each tracking filter is selected by a switchedcapacitor array, which is programmed by the TFS[7:0]

bits in the Tracking-Filter Series Cap register and the

TFP[5:0] bits in the Tracking-Filter Parallel Cap register.

To accommodate part-to-part variations each part is factory-calibrated by Maxim. During calibration the y-intercept and slope for the series and parallel tracking

capacitor arrays is calculated and written into an internal

ROM table. The user must read the ROM table upon

power-up and store the data in local memory (8 bytes

total) to calculate the optimal TFS[7:0] and TFP[5:0] settings for each channel. Table 16 shows the address and

bits for each ROM table entry. See the

Interpolating

Tracking Filter Coefficients

section for more information

on how to calculate the required values.

Reading the ROM Table

Each ROM table entry must be read using a two-step

process. First, the address of the ROM bits to be read

must be programmed into the TFA[3:0] bits in the

Tracking Filter ROM Address register (Table 11).

Once the address has been programmed, the data

stored in that address is transferred to the TFR[7:0] bits

in the ROM Table Data Readback register (Table 13).

The ROM data at the specified address can then be

read from the TFR[7:0] bits and stored in the microprocessor’s local memory.

Table 16. ROM Table

DESCRIPTION ADDRESS

IFOVLD 0x0 OD2 OD1 OD0 X X X X X

VHF Low Series/

Parallel Y-Intercept

VHF High Series/

Parallel Y-Intercept

UHF Series/

Parallel Y-Intercept

VHF Low Series Slope 0x4 HS1[3] HS1[2] HS1[1] HS1[0] HP0[3] HP0[2] HP0[1] HP0[0]

VHF High Parallel Slope 0x5 HP1[3] HP1[2] HP1[1] HP1[0] US0[7] US0[6] US0[5] US0[4]

VHF Low Parallel Slope 0x6 US0[3] US0[2] US0[1] US0[0] US1[5] US1[4] US1[3] US1[2]

VHF High Parallel Slope 0x7 US1[1] US1[0] UP0[7] UP0[6] UP0[5] UP0[4] UP0[3] UP0[2]

UHF Parallel Slope 0x8 UP0[1] UP0[0] UP1[5] UP1[4] UP1[3] UP1[2] UP1[1] UP1[0]

0x1 LS0[5] LS0[4] LS0[3] LS0[2] LS0[1] LS0[0] LS1[3] LS1[2]

0x2 LS1[1] LS1[0] LP0[5] LP0[4] LP0[3] LP0[2] LP0[1] LP0[0]

0x3 LP1[3] LP1[2] LP1[1] LP1[0] HS0[3] HS0[2] HS0[1] HS0[0]

MSB LSB

DATA BYTE

D7 D6 D5 D4 D3 D2 D1 D0

Page 13

MAX3540

Complete Single-Conversion Television Tuner

______________________________________________________________________________________ 13

Interpolating Tracking Filter Coefficients

The TFS[7:0] and TFP[5:0] bits must be reprogrammed

for each channel frequency to optimize performance.

The optimal settings for each channel can be calculated

from the ROM table data using the equations below.

VHF LO filter:

VHF High filter:

UHF filter:

Where:

fRF= operating frequency in MHz

TFS = decimal value of the optimal TFS[7:0]

setting (Table 9) for the given operating frequency

TFP = decimal value of the optimal TFP[5:0] setting

(Table 10) for the given operating frequency

LS0, LS1, LP0, LP1, HS0, HS1, HP0, HP1, US0, US1,

UP0, and UP1 = the decimal values of the ROM

table coefficients (Table 16).

IF Overload Detector

The MAX3541 includes a broadband IF overload detector, which provides an indication of the total power present at the RF input. The overload-detector output

voltage is compared to a reference voltage and the difference is amplified. This error signal drives an opencollector transistor whose collector is connected to the

IFOVLD pin, causing the IFOVLD pin to sink current.

The nominal full-scale current sunk by the IFOVLD pin

is 300μA. The IFOVLD pin requires a 10kΩ pullup resistor to V

CC

.

The IF overload detector is calibrated at the factory to

attack at 0.6V

P-P

at IFOUT1. Upon power-up, the baseband processor must read OD[2:0] from the ROM table

and store it in the IFVOLD register.

Closed-Loop RF Gain Control

Closed-loop RF gain control can be implemented by

connecting the IFOVLD output to the RFAGC input.

Using a 10kΩ pullup resistor on the IFOVLD pin, as

shown in the

Typical Application Circuit

, results in a

nominal 0.5V to 3V control voltage range.

VCO and VCO Divider Selection

The MAX3540 frequency synthesizer includes three VCOs

and eight VCO sub-bands to guarantee a 2160MHz to

4400MHz VCO frequency range. The frequency synthesizer also features an additional VCO frequency divider,

which must be programmed to either 4, 8, 16, or 32

through the VDIV[1:0] bits in the VCO register based on

the channel being received. Table 5 describes how the

VDIV[1:0] bits should be programmed for each band of

operation.

To ensure PLL, lock the proper VCO and VCO sub-band

for the channel being received, which must be chosen by

iteratively selecting a VCO and VCO sub-band then reading the LD[2:0] bits to determine if the PLL is locked. Any

reading from 001 to 110 indicates the PLL is locked. If

LD[2:0] reads 000, the PLL is unlocked and the selected

VCO is at the bottom of its tuning range; a lower VCO subband must be selected. If LD[2:0] reads 111, the PLL is

unlocked and the selected VCO is at the top of its tuning

range; a higher VCO sub-band must be selected. The

VCO and VCO sub-band settings should be progressively

increased or decreased until the LD[2:0] reading falls in

the 001 to 110 range.

Due to overlap between VCO sub-band frequencies, it is

possible that multiple VCO settings can be used to tune to

the same channel frequency. System performance at a

given channel should be similar between the various possible VCO settings, so it is sufficient to select the first VCO

and VCO sub-band that provides lock.

Layout Considerations

The MAX3540 EV kit can serve as a guide for PCB layout.

Keep RF signal lines as short as possible to minimize

losses and radiation. Use controlled impedance on all

high-frequency traces. The exposed paddle must be soldered evenly to the board’s ground plane for proper

operation. Use abundant vias beneath the exposed paddle for maximum heat dissipation. Use abundant ground

vias between RF traces to minimize undesired coupling.

⎣

⎦

⎡

TFS 10 (2.4

=+×+−+××

TFP INT 10

=

LS0

⎢

⎣

⎡

[(1.6

⎢

⎢

⎢

0.6)

64

LP0

0.4)

+×+−+×(6 ))f 10 ]

64

(.85

LS1

16

LP1

16

2) f

2

RF 1

××

RF

⎤

-3

⎥

×

00

⎦

⎤

-3

⎥

⎥

⎥

⎤

-3

⎥

−

⎥

⎥

⎦

⎤

-3

⎥

−

⎥

⎥

⎦

⎤

-3

⎥

−

20

⎥

⎥

⎦

⎤

-3

⎥

⎥

⎥

⎦

TFS INT 10

=

TFP INT 10

=

TFS INT 10

TFP INT 10

=

⎡

⎢

⎢

⎢

⎣

⎡

⎢

⎢

⎢

⎣

=

⎡

⎢

⎢

⎢

⎣

HS0

⎡

⎢

⎢

⎢

⎣

[(2.8

[(1.6

[(3

[(1.6

0.8)

+×+−+×(.42 ×××

16

HP0

0.8)

+×+−+×(.15 00.6 ) f 10 ]

16

US0

)

++−+××(.26 f 10 ]

256

UP0

0.8)

+×+−+(.14

256

US1

64

HS1

16

HP1

16

UP1

6

0.8 )

44

0.8 )

0.8 ) f 10 ]

×××

f10]

RF

××

RF

×

RF

RF

20

10

−

10

Page 14

MAX3540

Complete Single-Conversion Television Tuner

14 ______________________________________________________________________________________

Typical Application Circuit

To minimize coupling between different sections of the

IC, the ideal power-supply layout is a star configuration, which has a large decoupling capacitor at the

central VCCnode. The VCCtraces branch out from this

node, with each trace going to separate VCCpins of

the MAX3540. Each VCCpin must have a bypass

capacitor with a low impedance to ground at the frequency of interest. Do not share ground vias among

multiple connections to the PCB ground plane.

22pF

ADDRESS1

V

CC

ADDRESS2

ADDR2

ADDR1

2.7kΩ2.7kΩ

SCL

SDA

V

UHF_IN

VHF_IN

RFGND2

LEXT

RFGND3

RFAGC

V

GND

GND

1

2

CC

3

4

5

6

7

8

9

CC

10

11

12

1000pF

IFOVLD

1000pF

SCLK

V

CC

SDATA

100Ω

1000pF

V

CC

1000pF

1000pF

V

CC

470nF

2.7Ω

0.1μF

100pF

XTALP

SERIAL

INTERFACE

1000pF

100pF

XTALN

÷

270Ω

CC

470pF

*

LDO

GND_TUNE

+

-

1000pF

47μF

V

CC

1000pF

1000pF

CC

V

IFOUT1-

36

IFOUT1+

35

IFOVLD

34

V

CC

33

V

CC

32

GND

31

V

REF

IFIN+

30

IFIN-

29

V

CC

28

GND

27

IFAGC

26

IFOUT2+

25

SAW

DRIVER

AMPLIFIER

V

CC

10kΩ

V

CC

1000pF

2.2pF

2.7kΩ

0.1μF

4700pF

R

1.3kΩ

**

0.033μF

VCCCP

4445

PD CP

÷

N

V

CC

1000pF

MUX

VCO

DIVIDER

V

*

CC

V

VTUNE

40414243 39 38 37464748

MAX3540

EP

680nH

IF-SAW

V

FILTER

IFAGC

0.1μF

IFOVLD

V

CC

1000pF

V

CC

1000pF

16 21201918 22 23 24151413

17

CC

GND

V

GND

CC

V

IFOUT2-

1000pF

ANTI-ALIASING

FILTER

*CONNECT TO COMMON GROUND POINT AT PIN 39.

GND

GND

GND

GND

GND

GND

GND

GND

IFOUT+

IFOUT-

Page 15

MAX3540

Complete Single-Conversion Television Tuner

______________________________________________________________________________________ 15

Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information

go to www.maxim-ic.com/packages

.)

48L LGA.EPS

Page 16

MAX3540

Complete Single-Conversion Television Tuner

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16

____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2007 Maxim Integrated Products is a registered trademark of Maxim Integrated Products, Inc.

Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information

go to www.maxim-ic.com/packages

.)

Loading...

Loading...