Page 1

General Description

The MAX1497/MAX1499 low-power, 3.5- and 4.5-digit,

analog-to-digital converters (ADCs) with integrated lightemitting diode (LED) drivers operate from a single 2.7V

to 5.25V power supply. They include an internal reference, a high-accuracy on-chip oscillator, and a multiplexed LED display driver. An internal charge pump

generates the negative supply needed to power the

integrated input buffers for single-supply operation. The

ADC is configurable for either a ±2V or ±200mV input

range and it outputs its conversion results to an LED

and/or to a microcontroller (µC). Microcontroller

communication is possible through an SPI™-/QSPI™/MICROWIRE™-compatible serial interface. The

MAX1497 is a 3.5-digit (±1999 count) device and the

MAX1499 is a 4.5-digit (±19,999 count) device.

The MAX1497/MAX1499 do not require external precision integrating capacitors, autozero capacitors, crystal

oscillators, charge pumps, or other circuitry required

with dual-slope ADCs (commonly used in panel meter

circuits).

These devices also feature on-chip buffers for the differential signal and reference inputs, allowing direct

interface with high-impedance signal sources. In addition, they use continuous internal offset-calibration and

offer >100dB rejection of 50Hz and 60Hz line noise.

Other features include data hold and peak detection,

overrange and underrange detection, and a user-programmable low-battery monitor.

The MAX1499 is available in a 32-pin, 7mm ✕7mm

TQFP package and the MAX1497 is available in 28-pin

SSOP and 28-pin PDIP packages. All devices in this

family operate over the -40°C to +85°C extended temperature range.

Applications

Digital Panel Meters

Hand-Held Meters

Digital Voltmeters

Digital Multimeters

Features

♦ High Resolution

MAX1499: 4.5 Digits (±19,999 Count)

MAX1497: 3.5 Digits (±1999 Count)

♦ Sigma-Delta ADC Architecture

No Integrating Capacitors Required

No Autozeroing Capacitors Required

>100dB of Simultaneous 50Hz and 60Hz

Rejection

♦ Operate from a Single 2.7V or 5.25V Supply

♦ Selectable Input Range of ±200mV or ±2V

♦ Selectable Voltage Reference: Internal 2.048V or

External

♦ Internal High-Accuracy Oscillator Needs No

External Components

♦ Automatic Offset Calibration

♦ Low Power (Exclude LED Driver Current)

Maximum 664µA Operating Current

Maximum 268µA Shutdown Current

♦ Small 32-Pin, 7mm x 7mm TQFP Package (4.5

Digits), 28-Pin SSOP Package (3.5 Digits)

♦ Also Available in a PDIP Package (3.5 Digits)

♦ Multiplexed LED Drivers

Resistor-Programmable Segment Current

♦ SPI-/QSPI-/MICROWIRE-Compatible Serial

Interface

♦ Extended Temperature Range (-40°C to +85°C)

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

________________________________________________________________ Maxim Integrated Products 1

Ordering Information

19-3054; Rev 1a; 2/04

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

PART

TEMP RANGE

PIN-

RESOLUTION

(DIGITS)

MAX1497EAI*

28 SSOP 3.5

MAX1497EPI

28 PDIP 3.5

MAX1499ECJ

32 TQFP 4.5

Pin Configurations appear at end of data sheet.

*Future product—contact factory for availability.

SPI/QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

PACKAGE

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

Page 2

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

AVDDto GND (MAX1499).........................................-0.3V to +6V

DV

DD

to GND (MAX1499) ........................................-0.3V to +6V

AIN+, AIN- to GND (MAX1499) ...........VNEG to (AV

DD

to +0.3V)

REF+, REF- to GND (MAX1499)......... VNEG to (AV

DD

to +0.3V)

LOWBATT to GND (MAX1499) ................-0.3V to (AV

DD

+ 0.3V)

CLK,

EOC, CS, DIN, SCLK,

DOUT to GND (MAX1499).......................-0.3V to (DV

DD

+ 0.3V)

VNEG to GND (MAX1499) .......................-2.6V to (AV

DD

+ 0.3V)

LED_EN to GND (MAX1499)....................-0.3V to (DV

DD

+ 0.3V)

ISET to GND (MAX1499)..........................-0.3V to (AV

DD

+ 0.3V)

V

DD

to GND (MAX1497)...........................................-0.3V to +6V

AIN+, AIN- to GND (MAX1497)..............VNEG to (V

DD

to +0.3V)

REF+, REF- to GND (MAX1497) ........... VNEG to (V

DD

to +0.3V)

CLK, EOC, CS, DIN, SCLK,

DOUT to GND (MAX1497)..........................-0.3V to (V

DD

+ 0.3V)

VNEG to GND (MAX1497)..........................-2.6V to (V

DD

+ 0.3V)

ISET to GND (MAX1497) ............................-0.3V to (V

DD

+ 0.3V)

VLED to GLED..........................................................-0.3V to +6V

GLED to GND........................................................-0.3V to +0.3V

SEG_ to GLED..........................................-0.3V to (VLED + 0.3V)

DIG_ to GLED ..........................................-0.3V to (VLED + 0.3V)

DIG_ Sink Current .............................................................300mA

DIG_ Source Current...........................................................50mA

SEG_ Sink Current ..............................................................50mA

SEG_ Source Current..........................................................50mA

Maximum Current Input into Any Other Pin ........................50mA

Continuous Power Dissipation (T

A

= +70°C)

32-Pin TQFP (derate 20.7mW/°C above +70°C).....1652.9mW

28-Pin SSOP (derate 9.5mW/°C above +70°C) ...........762mW

28-Pin PDIP (derate 14.3mW/°C above +70°C)......1142.9mW

Operating Temperature Range ...........................-40°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-60°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

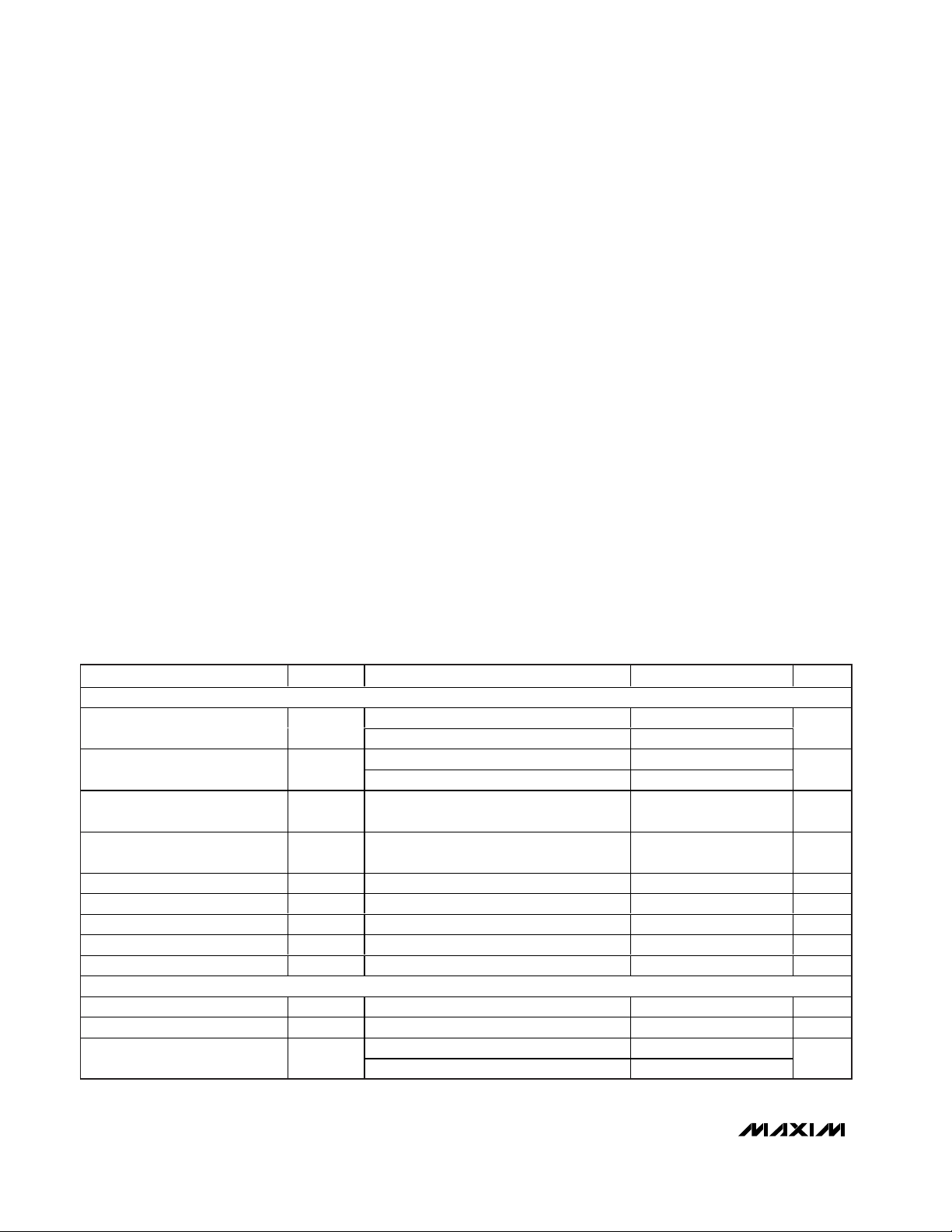

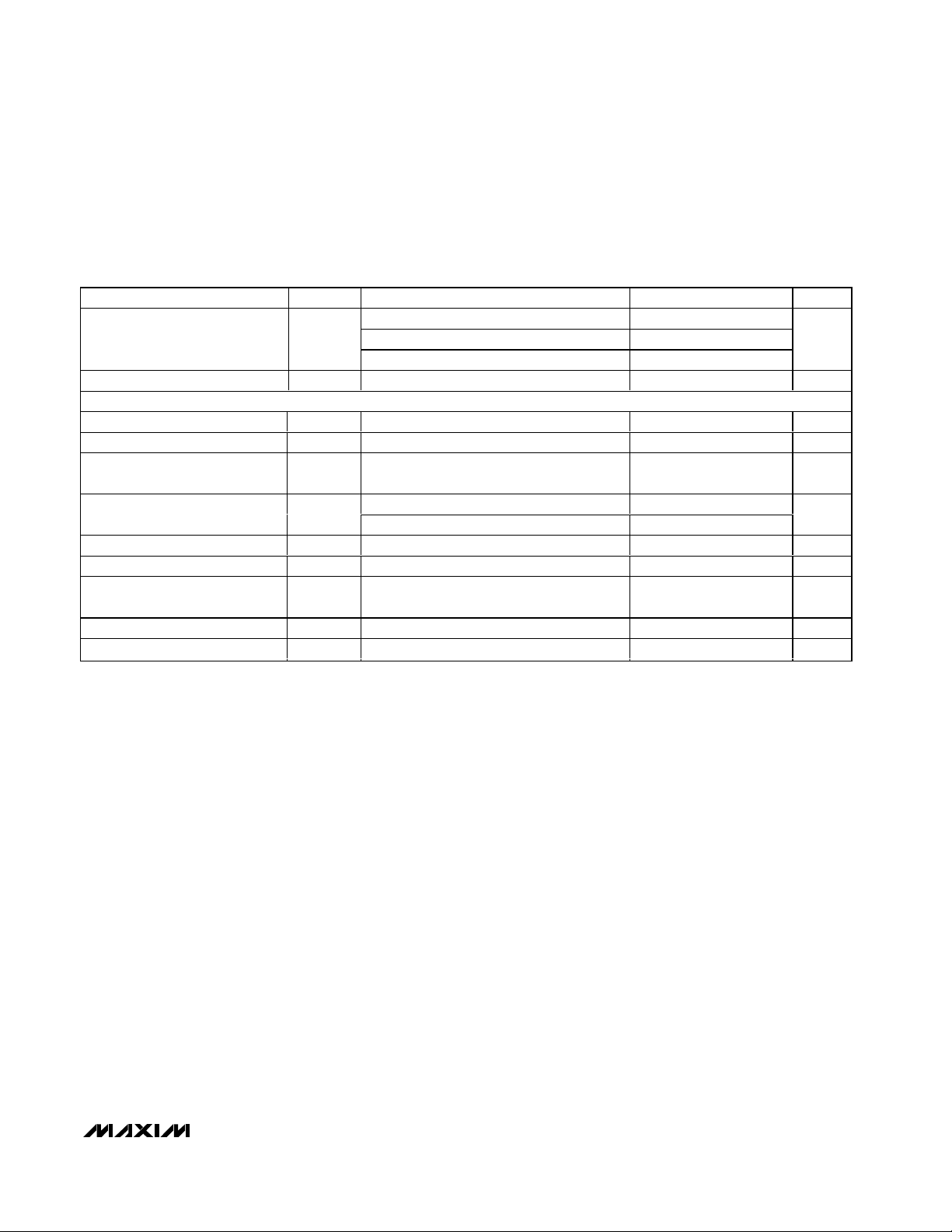

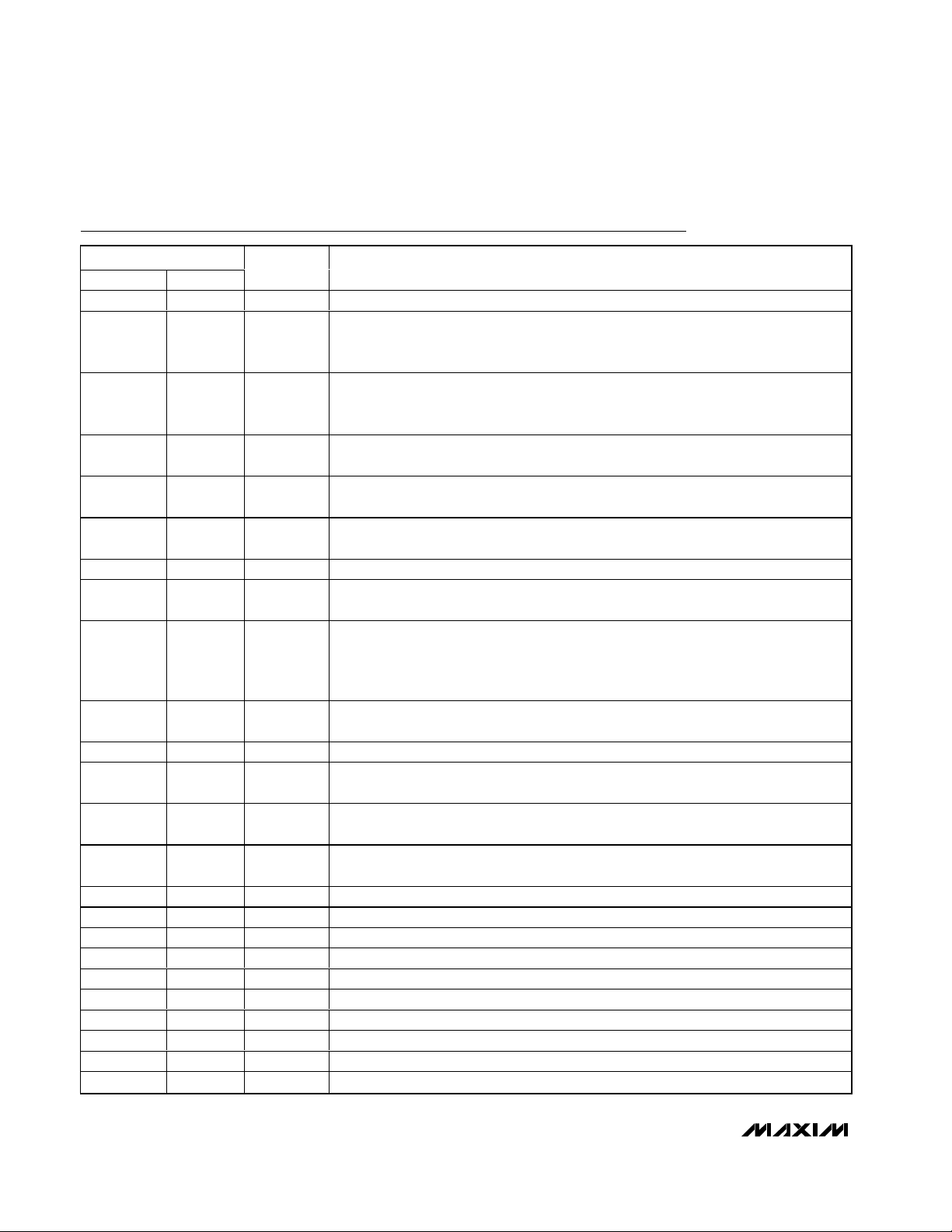

ELECTRICAL CHARACTERISTICS

(AVDD= DVDD= VDD= +2.7V to +5.25V, GND = 0, GLED = 0, V

LED

= +2.7V to +5.25V, V

REF+

- V

REF-

= 2.048V (external reference)

C

REF+

= C

REF-

= 0.1µF, C

VNEG

= 0.1µF. Internal clock mode, unless otherwise noted. All specifications are at TA= T

MIN

to T

MAX

.

Typical values are at T

A

= +25°C, unless otherwise noted.)

PARAMETER

CONDITIONS

UNITS

DC ACCURACY

MAX1499

Noise-Free Resolution

MAX1497

Count

2.000V range ±1

Integral Nonlinearity (Note 1) INL

200mV range ±1

Count

Range Change Ratio

(V

AIN+

- V

AIN-

= 0.100V) on 200mV range

(V

AIN+

- V

AIN-

= 0.100V) on 2.0V range

Ratio

Rollover Error

V

AIN+

- V

AIN-

= full scale

V

AIN-

- V

AIN+

= full scale

±1

Count

Output Noise 10

µV

P-P

Offset Error (Zero Input Reading)

Offset VIN = 0 (Note 2) -0 0

Reading

Gain Error (Note 3)

%FSR

Offset Drift (Zero Reading Drift) VIN = 0 (Note 4) 0.1

µV/°C

Gain Drift ±1

ppm/°C

INPUT CONVERSION RATE

External-Clock Frequency

MHz

External-Clock Duty Cycle 40 60 %

Internal clock 5

Conversion Rate

External clock, f

CLK

= 4.9152MHz 5

Hz

SYMBOL

MIN TYP MAX

-19,999 +19,999

-1999 +1999

10:1

-0.5 +0.5

4.9152

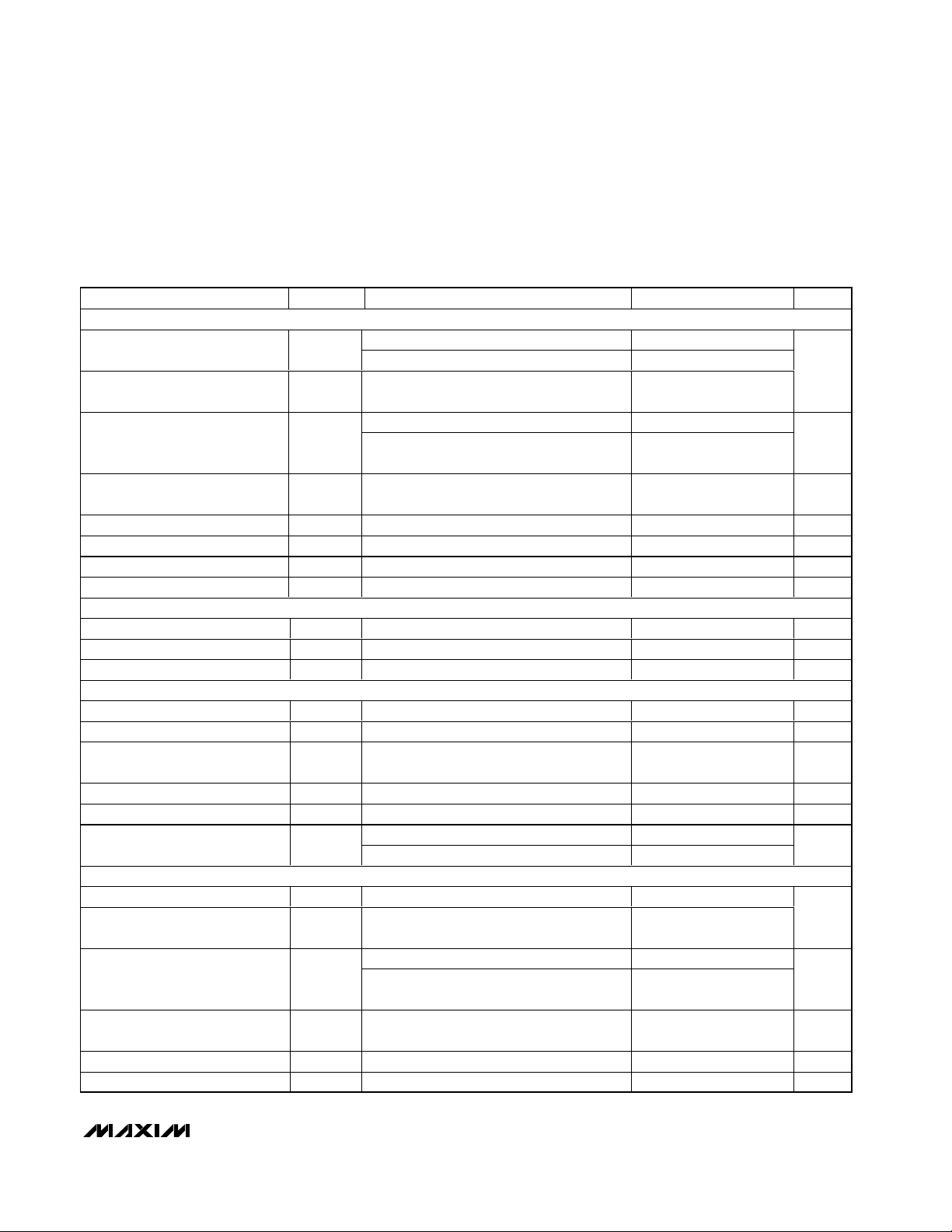

Page 3

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

_______________________________________________________________________________________ 3

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

ANALOG INPUTS (AIN+, AIN-) (bypass to GND with 0.1µF or greater capacitors)

RANGE bit = 0

AIN Input Voltage Range (Note 5)

RANGE bit = 1

AIN Absolute Input Voltage

Range to GND

V

Internal clock mode, 50Hz and 60Hz ±2%

Normal-Mode 50Hz and 60Hz

Rejection (Simultaneously)

External clock mode, 50Hz and 60Hz ±2%,

f

CLK

= 4.9152MHz

dB

Common-Mode 50Hz and 60Hz

Rejection (Simultaneously)

CMR

dB

Common-Mode Rejection CMR At DC

dB

Input Leakage Current 10 nA

Input Capacitance 10 pF

Average Dynamic Input Current

(Note 6) -20 +20 nA

LOW-BATTERY VOLTAGE MONITOR (LOWBATT) (MAX1499 only)

LOWBATT TripThreshold

V

LOWBATT Leakage Current 10 pA

Hysteresis 20 mV

INTERNAL REFERENCE (REF- = GND, INTREF bit = 1) (bypass REF+ to GND with a 4.7µF capacitor)

REF Output Voltage V

REF

AVDD = V

DD

= 5V

V

REF Output Short-Circuit Current

1mA

REF Output Temperature

Coefficient

AVDD = V

DD

= 5V 40

ppm/°C

Load Regulation I

SOURCE

= 0 to 300µA, I

SINK

= 0 to 30µA 6

mV/µA

Line Regulation 50

µV/V

0.1Hz to 10Hz 25

Noise Voltage

10Hz to 10kHz

µV

P-P

EXTERNAL REFERENCE (INTREF bit = 0) (bypass REF+ and REF- to GND with 0.1µF or greater capacitors)

REF Input Voltage Differential (V

REF+

- V

REF-

)

Absolute REF+, REF- Input

Voltage to GND

V

Internal clock mode, 50Hz and 60Hz ±2%

Normal-Mode 50Hz and 60Hz

Rejection (Simultaneously)

External clock mode, 50Hz and 60Hz ±2%,

f

CLK

= 4.9152MHz

dB

Common-Mode 50Hz and 60Hz

Rejection (Simultaneously)

CMR

dB

Common-Mode Rejection CMR At DC

dB

Input Leakage Current 10 nA

ELECTRICAL CHARACTERISTICS (continued)

(AVDD= DVDD= VDD= +2.7V to +5.25V, GND = 0, GLED = 0, V

LED

= +2.7V to +5.25V, V

REF+

- V

REF-

= 2.048V (external reference)

C

REF+

= C

REF-

= 0.1µF, C

VNEG

= 0.1µF. Internal clock mode, unless otherwise noted. All specifications are at TA= T

MIN

to T

MAX

.

Typical values are at T

A

= +25°C, unless otherwise noted.)

TC

VREF

For 50Hz and 60Hz ±2%, R

For 50Hz and 60Hz ±2%, R

SOURCE

SOURCE

< 10kΩ 150

< 10kΩ 150

-2.0 +2.0

-0.2 +0.2

-2.2 +2.2

100

120

100

2.048

2.007 2.048 2.089

400

2.048

-2.2 +2.2

100

120

100

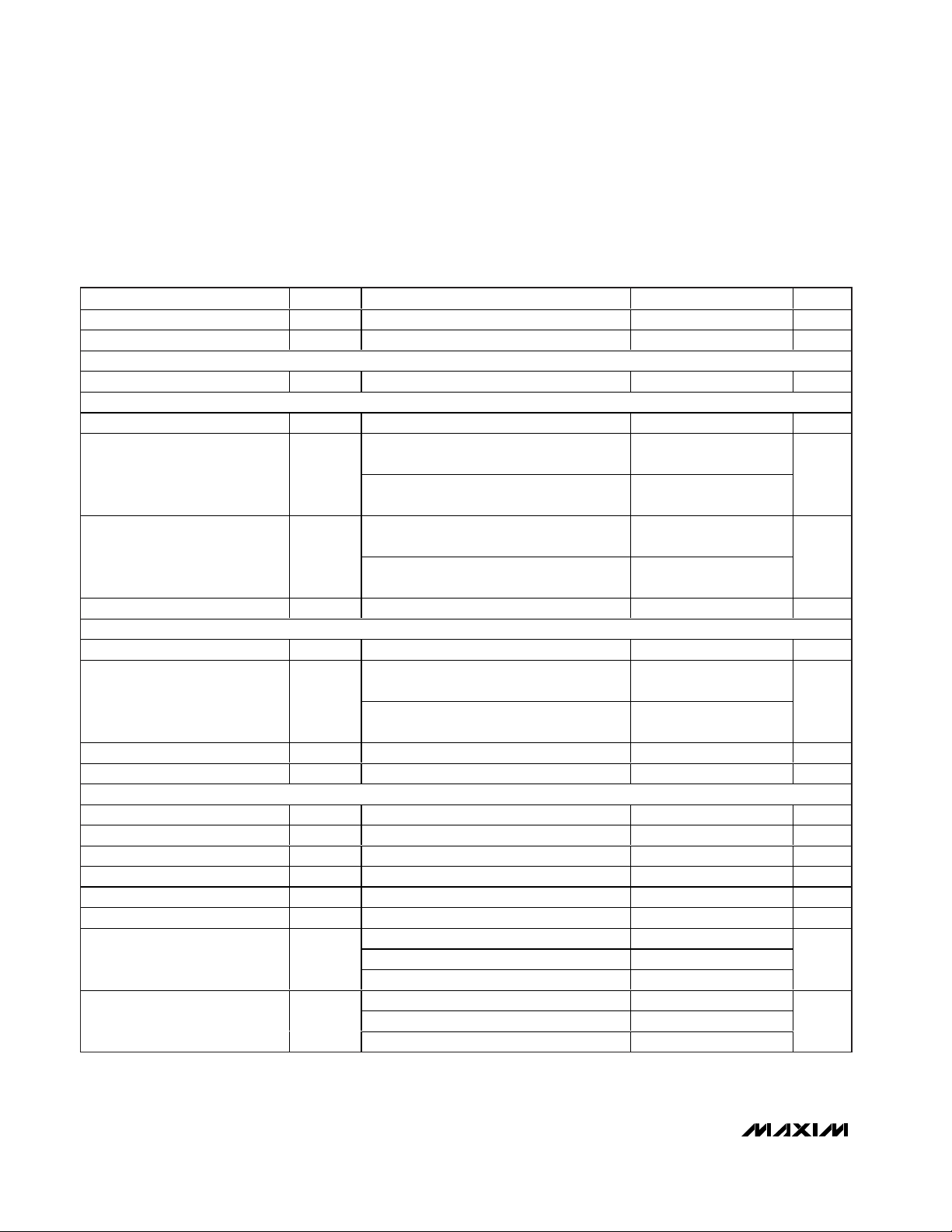

Page 4

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

4 _______________________________________________________________________________________

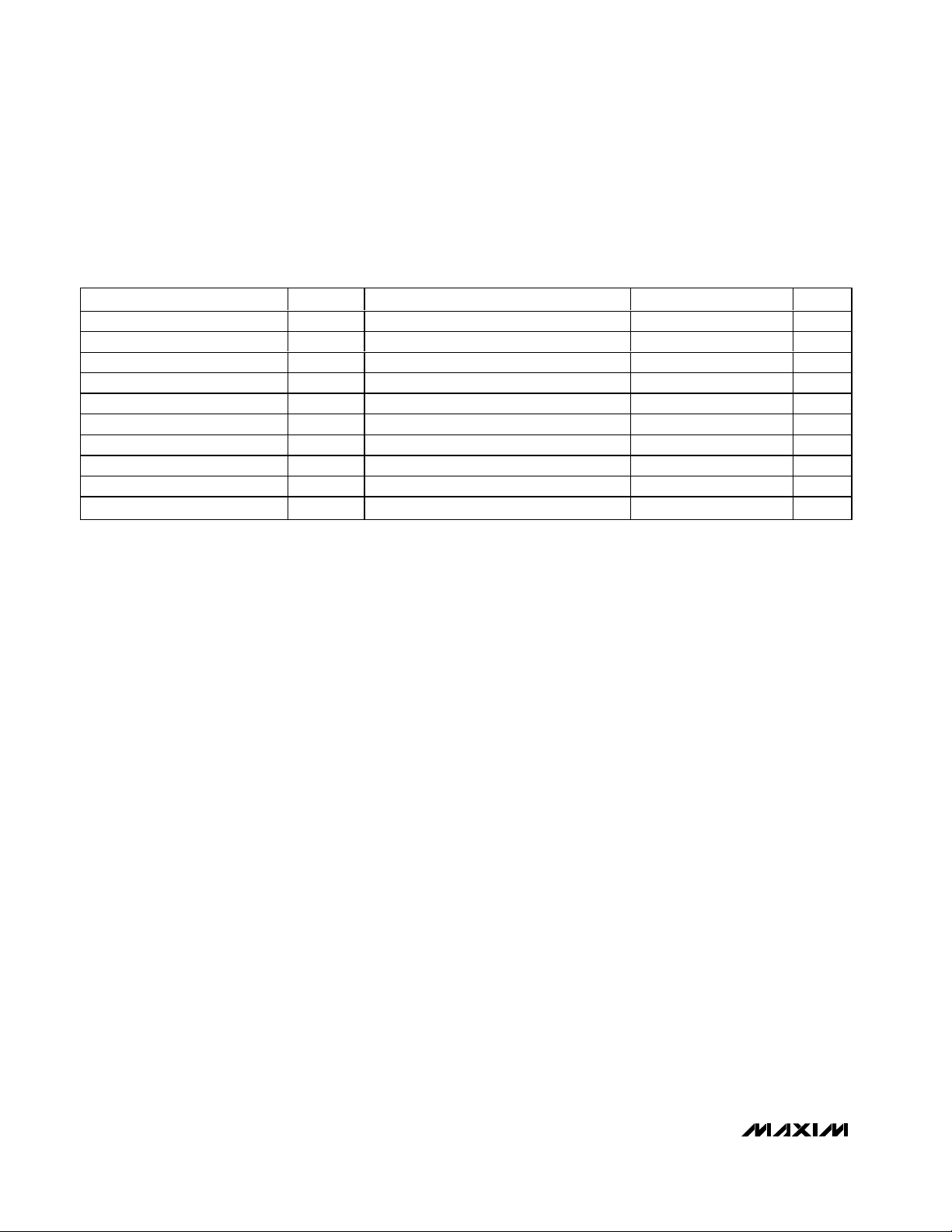

PARAMETER

CONDITIONS

UNITS

Input Capacitance 10 pF

Average Dynamic Input Current (Note 6) -20 +20 nA

CHARGE PUMP

Output Voltage VNEG C

VNEG

= 0.1µF

V

DIGITAL INPUTS (SCLK, DIN, CS, CLK)

Input Current I

IN

VIN = 0 or DVDD = V

DD

-10 +10 µA

MAX1499

0.3 x

Input Low Voltage V

INL

MAX1497

0.3 x

V

DD

V

MAX1499

0.7 x

Input High Voltage V

INH

MAX1497

0.7 x

V

Input Hysteresis V

HYS

DVDD = VDD = 3.0V

mV

DIGITAL OUTPUTS (DOUT, EOC)

Output Low Voltage V

OL

I

SINK

= 1mA 0.4 V

I

SOURCE

= 200µA, M AX 1499

0.8 x

Output High Voltage V

OH

I

SOURCE

= 200µA, M AX 1497

0.8 x

V

Tri-State Leakage Current I

L

DOUT only -1 +1 µA

Tri-State Output Capacitance C

OUT

DOUT only 15 pF

POWER SUPPLY (Note 10)

VDD Voltage V

DD

MAX1497

V

AVDD Voltage AV

DD

MAX1499

V

DVDD Voltage DV

DD

MAX1499

V

Power-Supply Rejection V

DD

PSRR (Note 7) 80 dB

Power-Supply Rejection AV

DD

(Note 7) 80 dB

Power-Supply Rejection DV

DD

(Note 7)

dB

VDD = 5.25V

744

VDD = 3.3V

663VDD Current (Notes 8, 9) I

VDD

Standby mode

325

µA

AVDD = 5.25V 640

AVDD = 3.3V 600

AVDD Current (Notes 8, 9) I

AVDD

Standby mode 305

µA

ELECTRICAL CHARACTERISTICS (continued)

(AVDD= DVDD= VDD= +2.7V to +5.25V, GND = 0, GLED = 0, V

LED

= +2.7V to +5.25V, V

REF+

- V

REF-

= 2.048V (external reference)

C

REF+

= C

REF-

= 0.1µF, C

VNEG

= 0.1µF. Internal clock mode, unless otherwise noted. All specifications are at TA= T

MIN

to T

MAX

.

Typical values are at T

A

= +25°C, unless otherwise noted.)

SYMBOL

MIN TYP MAX

-2.60 -2.42 -2.30

DV

DD

V

DD

200

DV

DD

V

DD

DV

DD

2.70 5.25

PSRR

PSRR

A

D

2.70 5.25

2.70 5.25

100

664

618

268

Page 5

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

_______________________________________________________________________________________ 5

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DVDD = 5V 320

DVDD = 3.3V 180DVDD Current (Notes 8, 9) I

DVDD

Standby mode 20

µA

LED Drivers Bias Current From AV

DD

or V

DD

µA

LED DRIVERS (Table 6)

LED Supply Voltage V

LED

V

LED Shutdown Supply Current I

SHDN

LED driver shutdown mode 10 µA

LED Supply Current I

LED

Seven segments and decimal point on,

R

ISET

= 25kΩ

mA

MAX1499

Display Scan Rate f

OSC

MAX1497

Hz

Segment Current Slew Rate

25

mA/µs

DIG_ Voltage Low V

DIG

I

DIG_

= 176mA

V

Segment Drive Source Current

Matching

∆I

SEG

±3 ±10 %

Segment Drive Source Current I

SEG

V

LED

- V

SEG

= 0.6V, R

ISET

= 25kΩ 16 20

mA

Interdigit Blanking Time 4µs

ELECTRICAL CHARACTERISTICS (continued)

(AVDD= DVDD= VDD= +2.7V to +5.25V, GND = 0, GLED = 0, V

LED

= +2.7V to +5.25V, V

REF+

- V

REF-

= 2.048V (external reference)

C

REF+

= C

REF-

= 0.1µF, C

VNEG

= 0.1µF. Internal clock mode, unless otherwise noted. All specifications are at TA= T

MIN

to T

MAX

.

Typical values are at T

A

= +25°C, unless otherwise noted.)

∆I

/∆t

SEG

120

2.70 5.25

176

512

640

0.178 0.300

25.5

Page 6

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

6 _______________________________________________________________________________________

TIMING CHARACTERISTICS (Notes 11, 12, Figure 8)

(AVDD= DVDD= VDD= +2.7V to +5.25V, GND = 0, GLED = 0, V

LED

= +2.7V to +5.25V, V

REF+

- V

REF-

= 2.048V (external reference)

C

REF+

= C

REF-

= 0.1µF, C

VNEG

= 0.1µF. Internal clock mode, unless otherwise noted. All specifications are at TA= T

MIN

to T

MAX

.

Typical values are at T

A

= +25°C, unless otherwise noted.)

PARAMETER

CONDITIONS

UNITS

SCLK Operating Frequency f

SCLK

0 4.2

MHz

SCLK Pulse-Width High t

CH

ns

SCLK Pulse-Width Low t

CL

ns

DIN to SCLK Setup t

DS

50 ns

DIN to SCLK Hold t

DH

0ns

CS Fall to SCLK Rise Setup t

CSS

50 ns

SCLK Rise to CS Rise Hold t

CSH

0ns

SCLK Fall to DOUT Valid t

DO

C

LOAD

= 50pF, Figures 13, 14

ns

CS Rise to DOUT Disable t

TR

C

LOAD

= 50pF, Figures 13, 14

ns

CS Fall to DOUT Enable t

DV

C

LOAD

= 50pF, Figures 13, 14

ns

Note 1: Integral nonlinearity is the deviation of the analog value at any code from its theoretical value after nulling the gain error and

offset error.

Note 2: Offset calibrated. See OFFSET_CAL1 and OFFSET_CAL2 (MAX1499 only) in the On-Chip Registers section.

Note 3: Offset nulled.

Note 4: Offset drift error is eliminated by recalibration at the new temperature.

Note 5: The input voltage range for the analog inputs is given with respect to the voltage on the negative input of the differential pair.

Note 6: V

AIN

+ or V

AIN

- = -2.2V to +2.2V. V

REF

+ or V

REF

- = -2.2V to +2.2V. All input structures are identical. Production tested on

AIN+ and REF+ only.

Note 7: Measured at DC by changing the power-supply voltage from 2.7V to 5.25V and measuring the effect on the conversion

error with external reference. PSRR at 50Hz and 60Hz exceeds 120dB with filter notches at 50Hz and 60Hz (Figure 2).

Note 8: CLK and SCLK are disabled.

Note 9: LED drivers are disabled.

Note 10: Power-supply currents are measured with all digital inputs at either GND, DV

DD

, or VDDand with the device in internal-clock mode.

Note 11: All input signals are specified with t

RISE

= t

FALL

= 5ns (10% to 90% of DVDD) and are timed from a voltage level of 50% of

DV

DD

, unless otherwise noted.

Note 12: See the serial-interface timing diagrams.

SYMBOL

MIN TYP MAX

100

100

120

120

120

Page 7

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

_______________________________________________________________________________________ 7

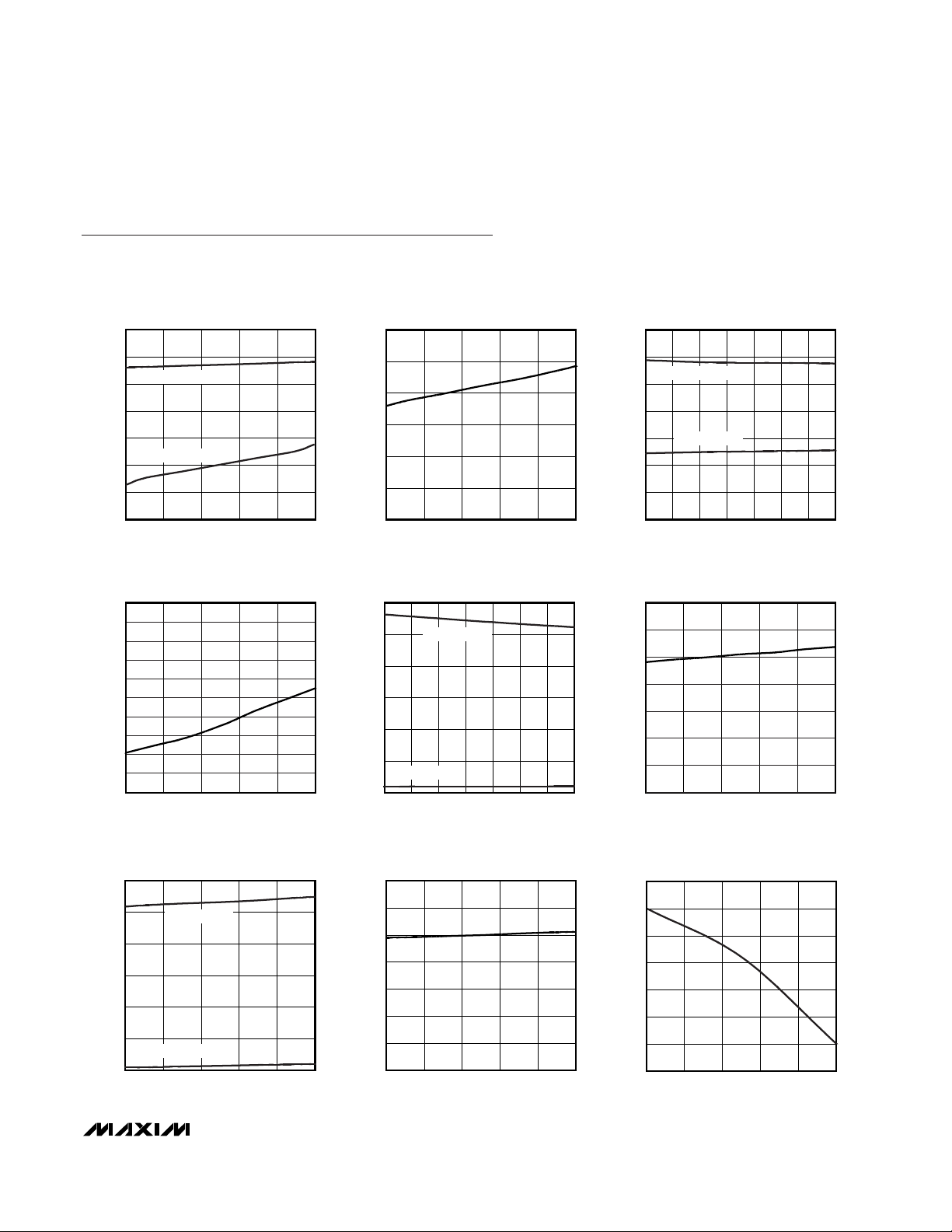

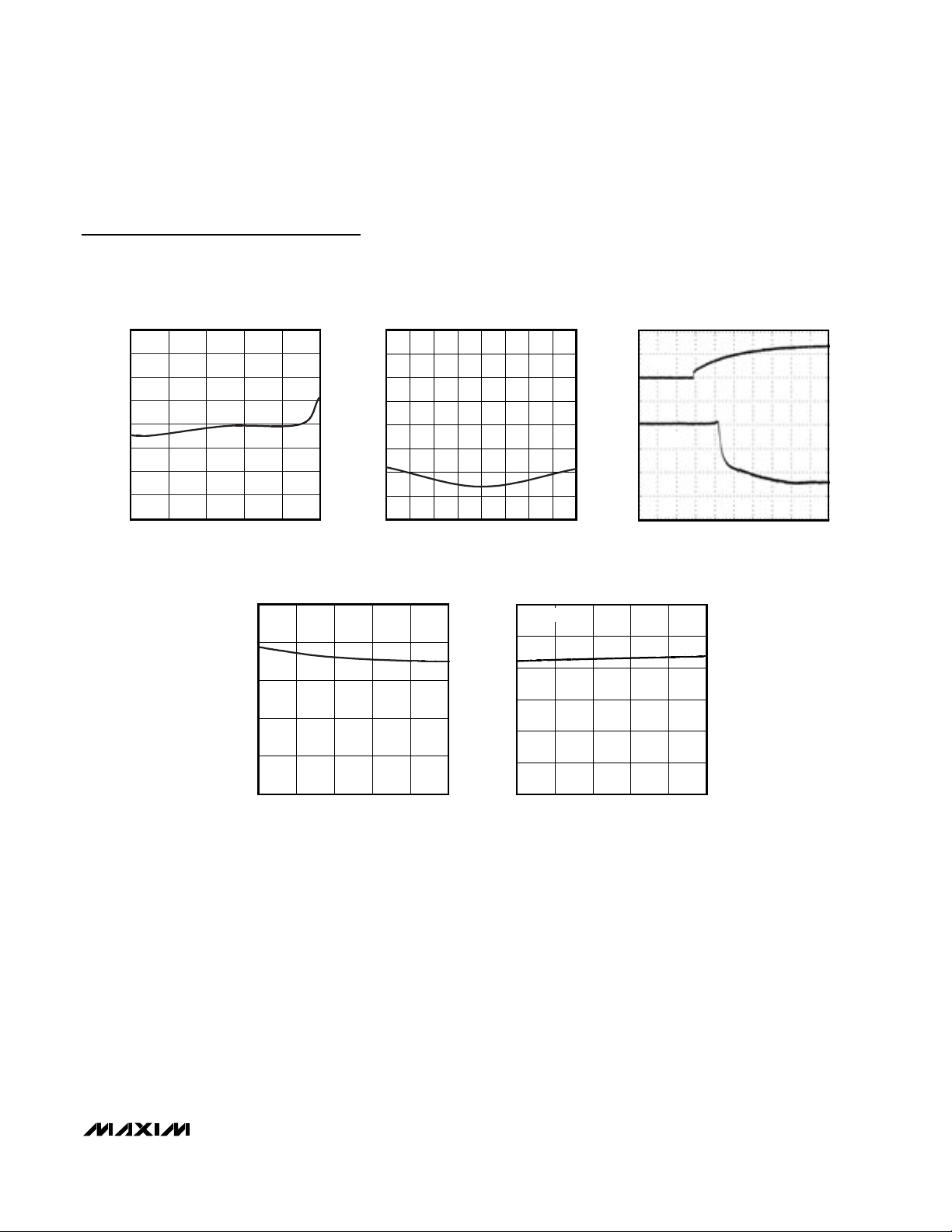

Typical Operating Characteristics

(AV

DD

= DVDD= VDD= +2.7V to +5.25V, V

LED

= +2.7V to +5.25V, GND = 0, GLED = 0, external reference mode, REF+ = 2.048V,

REF- = GND, C

REF+

= C

REF-

= 0.1µF, RANGE bit = 1, internal clock mode, C

VNEG

= 0.1µF. TA= +25°C, unless otherwise noted.)

SUPPLY CURRENT

vs. SUPPLY VOLTAGE (MAX1499)

MAX1497/99 toc01

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (µA)

4.754.253.753.25

100

200

300

400

500

600

700

0

2.75 5.25

ANALOG SUPPLY

DIGITAL SUPPLY

SUPPLY CURRENT

vs. SUPPLY VOLTAGE (MAX1497)

MAX1497/99 toc02

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (µA)

4.744.233.723.21

450

500

550

600

650

700

400

2.70 5.25

SUPPLY CURRENT

vs. TEMPERATURE (MAX1499)

MAX1497/99 toc03

TEMPERATURE (°C)

SUPPLY CURRENT (µA)

605040302010

100

200

300

400

500

600

700

0

070

ANALOG SUPPLY

DIGITAL SUPPLY

SUPPLY CURRENT

vs. TEMPERATURE (MAX1497)

MAX1497/99 toc04

TEMPERATURE (°C)

SUPPLY CURRENT (µA)

6035-15 10

610

640

630

620

650

660

670

680

690

700

600

-40 85

SHUTDOWN CURRENT

vs. TEMPERATURE (MAX1499)

MAX1497/99 toc05

TEMPERATURE (°C)

SHUTDOWN CURRENT (µA)

605040302010

50

100

150

200

250

300

0

070

ANALOG SUPPLY

DIGITAL SUPPLY

SHUTDOWN CURRENT

vs. SUPPLY VOLTAGE (MAX1499)

MAX1497/99 toc07

SUPPLY VOLTAGE (V)

SHUTDOWN CURRENT (µA)

4.754.253.753.25

50

100

150

200

250

300

0

2.75 5.25

ANALOG SUPPLY

DIGITAL SUPPLY

SHUTDOWN CURRENT

vs. SUPPLY VOLTAGE (MAX1497)

MAX1497/99 toc08

SUPPLY VOLTAGE (V)

SHUTDOWN CURRENT (µA)

4.744.233.723.21

50

150

100

200

250

300

350

0

2.70 5.25

MAX1499

OFFSET ERROR vs. SUPPLY VOLTAGE

MAX1497/99 toc09

SUPPLY VOLTAGE (V)

OFFSET ERROR (LSB)

4.754.253.753.25

-0.11

-0.06

-0.01

0.04

0.09

0.14

0.19

-0.16

2.75 5.25

SHUTDOWN CURRENT

vs. TEMPERATURE (MAX1497)

MAX1497/99 toc06

TEMPERATURE (°C)

SHUTDOWN CURRENT (µA)

6035-15 10

50

150

100

200

250

300

350

0

-40 85

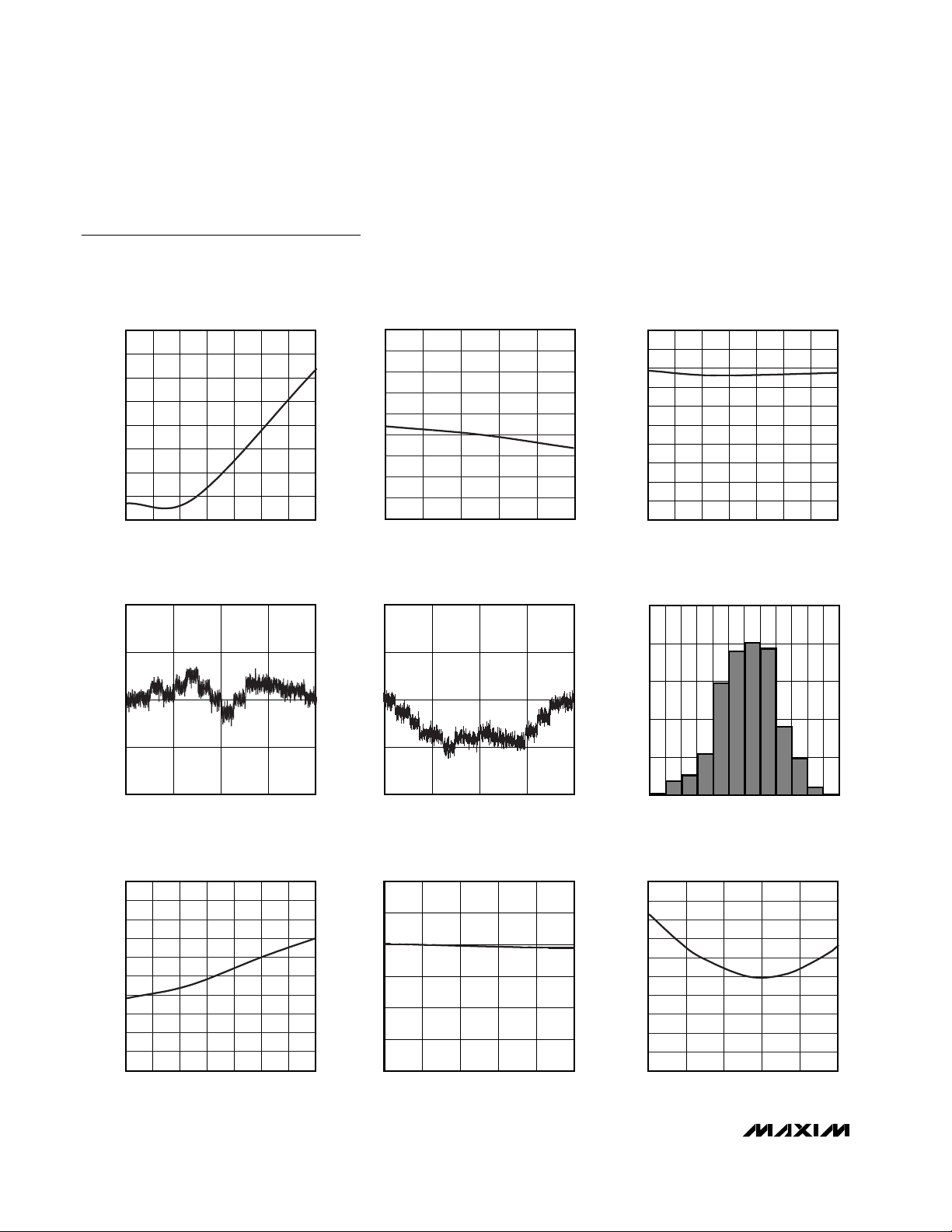

Page 8

INTERNAL REFERENCE VOLTAGE

vs. TEMPERATURE

MAX1497/99 toc16

TEMPERATURE (°C)

REFERENCE VOLTAGE (V)

605040302010

2.046

2.045

2.047

2.049

2.048

2.051

2.050

2.053

2.052

2.054

2.044

070

INTERNAL REFERENCE VOLTAGE

vs. ANALOG SUPPLY VOLTAGE

MAX1497/99 toc17

SUPPLY VOLTAGE (V)

REFERENCE VOLTAGE (V)

4.754.253.753.25

2.045

2.046

2.047

2.048

2.049

2.050

2.044

2.75 5.25

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

8 _______________________________________________________________________________________

Typical Operating Characteristics (continued)

(AV

DD

= DVDD= VDD= +2.7V to +5.25V, V

LED

= +2.7V to +5.25V, GND = 0, GLED = 0, external reference mode, REF+ = 2.048V,

REF- = GND, C

REF+

= C

REF-

= 0.1µF, RANGE bit = 1, internal clock mode, C

VNEG

= 0.1µF. TA= +25°C, unless otherwise noted.)

MAX1499

OFFSET ERROR vs. TEMPERATURE

MAX1497/99 toc10

TEMPERATURE (°C)

OFFSET ERROR (LSB)

605010 20 30 40

-0.1

0

0.1

0.2

0.3

0.4

0.5

0.6

-0.2

070

MAX1499

GAIN ERROR vs. SUPPLY VOLTAGE

MAX1497/99 toc11

SUPPLY VOLTAGE (V)

GAIN ERROR (% FULL SCALE)

4.754.253.25 3.75

-0.08

-0.04

-0.06

-0.02

0

0.02

0.04

0.06

0.08

-0.10

2.75 5.25

MAX1499

GAIN ERROR vs. TEMPERATURE

MAX1497/99 toc12

TEMPERATURE (°C)

GAIN ERROR (% FULL SCALE)

605030 402010

-0.09

-0.08

-0.07

-0.06

-0.05

-0.04

-0.03

-0.02

-0.01

0

-0.10

070

MAX1499

(±200mV INPUT RANGE) INL vs. OUTPUT CODE

MAX1497/99 toc13

OUTPUT CODE

INL (COUNTS)

10,0000-10,000

-0.5

0

0.5

1.0

-1.0

-20,000 20,000

MAX1499

(±2V INPUT RANGE) INL vs. OUTPUT CODE

MAX1497/99 toc14

OUTPUT CODE

INL (COUNTS)

10,0000-10,000

-0.5

0

0.5

1.0

-1.0

-20,000 20,000

NOISE DISTRIBUTION

MAX1497/99 toc15

NOISE (LSB)

PERCENTAGE OF UNITS (%)

0.80.70.60.50.40.30.20.10-0.1

5

10

15

20

25

0

-0.2

DATA OUTPUT RATE

vs. TEMPERATURE

MAX1497/99 toc18

TEMPERATURE (°C)

DATA OUTPUT RATE (Hz)

6035-15 10

4.92

4.98

4.96

4.94

5.00

5.02

5.04

5.06

5.08

5.10

4.90

-40 85

Page 9

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

_______________________________________________________________________________________ 9

Typical Operating Characteristics (continued)

(AV

DD

= DVDD= VDD= +2.7V to +5.25V, V

LED

= +2.7V to +5.25V, GND = 0, GLED = 0, external reference mode, REF+ = 2.048V,

REF- = GND, C

REF+

= C

REF-

= 0.1µF, RANGE bit = 1, internal clock mode, C

VNEG

= 0.1µF. TA= +25°C, unless otherwise noted.)

DATA OUTPUT RATE

vs. SUPPLY VOLTAGE

MAX1497/99 toc19

SUPPLY VOLTAGE (V)

DATA OUTPUT RATE (Hz)

4.744.233.21 3.72

4.995

4.990

4.985

5.000

5.005

5.010

5.015

5.020

4.980

2.70 5.25

OFFSET ERROR

vs. COMMON-MODE VOLTAGE

MAX1497/99 toc20

COMMON-MODE VOLTAGE (V)

OFFSET ERROR (LSB)

1.51.0-1.5 -1.0 -0.5 0 0.5

-0.15

-0.10

-0.05

0

0.05

0.10

0.15

0.20

-0.20

-2.0 2.0

SEGMENT CURRENT

vs. SUPPLY VOLTAGE

MAX1497/99 toc23

SUPPLY VOLTAGE (V)

SEGMENT CURRENT (µA)

4.744.233.723.21

5

10

15

20

25

30

0

2.70 5.25

R

ISET

= 25kΩ

V

NEG

STARTUP SCOPE SHOT

MAX1497/99 toc21

20ms/div

2V/div

1V/div

V

DD

V

NEG

CHARGE-PUMP OUTPUT VOLTAGE

vs. ANALOG SUPPLY VOLTAGE

MAX1497/99 toc22

SUPPLY VOLTAGE (V)

V

NEG

VOLTAGE (V)

4.754.253.753.25

-2.48

-2.46

-2.44

-2.42

-2.40

-2.50

2.75 5.25

Page 10

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

10 ______________________________________________________________________________________

Pin Description

PIN

MAX1497

NAME FUNCTION

131VNEG -2.5V Charge-Pump Voltage-Output. Connect a 0.1µF capacitor to GND.

232REF-

Negative Reference Voltage Input. For internal reference operation, connect REF- to

GND. For external reference operation, bypass REF- to GND with a 0.1µF capacitor and

set V

REF-

from -2.2V to +2.2V, provided V

REF+

> V

REF-

.

31REF+

Positive Reference Voltage Input. For internal reference operation, connect a 4.7µF

capacitor from REF+ to GND. For external reference operation, bypass REF+ to GND

with a 0.1µF capacitor and set V

REF+

from -2.2V to +2.2V, provided V

REF+

> V

REF-

.

42AIN+

Positive Analog Input. Positive side of fully differential analog input. Bypass AIN+ to GND

with a 0.1µF or greater capacitor.

53AIN-

Negative Analog Input. Negative side of fully differential analog input. Bypass AIN- to

GND with a 0.1µF or greater capacitor.

64I

SET

Segment Current Controller. Connect to ground through a resistor to set the segment

current. See Table 6 for segment current selection.

75GND Ground

8—V

DD

Analog and Digital Circuit Supply Voltage. Connect VDD to a +2.7V to +5.25V power

supply. Bypass V

DD

to GND with a 0.1µF and a 4.7µF capacitor.

98CLK

External Clock Input. When the EXTCLK register bit is set to one, CLK is the master clock

input (frequency = 4.9152MHz) for the modulator and the filter. When the EXTCLK

register bit is reset to zero, the internal clock is used. Connect CLK to GND or DV

DD

(MAX1499) or V

DD

(MAX1497) when the internal oscillator is used.

10 9 EOC

Active-Low End-of-Conversion Logic Output. A logic low at EOC indicates that a new

ADC result is available in the ADC result register.

11 10 CS Active-Low Chip Select Input. Forcing CS low activates the serial interface.

12 11 DIN

Serial Data Input. Data present at DIN is shifted into the internal registers in response to

a rising edge at SCLK when CS is low.

13 12 SCLK

Serial Clock Input. Apply an external clock to SCLK to facilitate communication through

the serial bus. SCLK may idle high or low.

14 13 DOUT

Serial Data Output. DOUT presets serial data in response to register queries. Data shifts

out on the falling edge of SCLK. DOUT goes high impedance when CS is high.

15 14 DIG0 Digit 0 Driver

16 15 DIG1 Digit 1 Driver

17 16 GLED Ground for LED-Display Segment Driver

18 17 DIG2 Digit 2 Driver

19 18 DIG3 Digit 3 Driver

20 20 SEGA Segment A Driver

21 21 SEGB Segment B Driver

22 22 SEGC Segment C Driver

23 23 SEGD Segment D Driver

24 24 SEGE Segment E Driver

MAX1499

Page 11

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 11

Detailed Description

The MAX1497/MAX1499 low-power, highly integrated

ADCs with LED drivers convert a ±2V differential input

voltage (one count is equal to 100µV for the MAX1499

and 1mV for the MAX1497) with a sigma-delta ADC and

output the result to an LED or µC. An additional

±200mV input range (one count is equal to 10µV for the

MAX1499 and 100µV for the MAX1497) is available to

measure small signals with increased resolution.

The devices operate from a single 2.7V to 5.25V power

supply and offer 3.5-digit (MAX1497) or 4.5-digit

(MAX1499) conversion results. An internal 2.048V reference, internal charge pump, and a high-accuracy onchip oscillator eliminate external components.

The MAX1497/MAX1499 interface with a µC using an

SPI-/QSPI-/MICROWIRE-compatible serial interface.

Data can either be sent directly to the display or to the

µC first for processing before being displayed.

The devices also feature on-chip buffers for the differential input signal and external reference inputs, allowing direct interface with high-impedance signal

sources. In addition, they use continuous internal offsetcalibration and offer >100dB of 50Hz and 60Hz line

noise rejection. Other features include data hold and

peak detection, overrange and underrange detection.

The MAX1499 also provides a low-battery monitor.

Analog Input Protection

Internal protection diodes limit the analog input range

from VNEG to (AVDD+ 0.3V) for the MAX1499, and

from VNEG to (VDDto 0.3V) for the MAX1497. If the

analog input exceeds this range, limit the input current

to 10mA.

Internal Analog Input/Reference Buffers

The MAX1497/MAX1499 analog input/reference buffers

allow the use of high-impedance signal sources. The

input buffers’ common-mode input range allows the analog inputs and the reference to range from -2.2V to +2.2V.

Modulator

The MAX1497/MAX1499 perform analog-to-digital conversions using a single-bit, 3rd-order, sigma-delta modulator. The sigma-delta modulator converts the input

signal into a digital pulse train whose average duty

cycle represents the digitized signal information. The

modulator quantizes the input signal at a much higher

sample rate than the bandwidth of the input.

The MAX1497/MAX1499 modulator provides 3rd-order

frequency shaping of the quantization noise resulting

from the single-bit quantizer. The modulator is fully differential for maximum signal-to-noise ratio and minimum susceptibility to power-supply noise. A single-bit

data stream is then presented to the digital filter to

remove the frequency-shaped quantization noise.

Pin Description (continued)

PIN

MAX1497

NAME FUNCTION

25 25 VLED

LED-Display Segment-Driver Supply. Connect to a +2.7V to +5.25V supply. Bypass with

a 0.1µF capacitor to GLED.

26 26 SEGF Segment F Driver

27 27 SEGG Segment G Driver

28 28 SEGDP Segment DP Driver

—6AV

DD

Analog Positive Supply Voltage. Connect AV

DD

to a +2.7V to +5.25V power supply.

Bypass AV

DD

to GND with a 0.1µF capacitor.

—7DV

DD

Digital Positive Supply Voltage. Connect DVDD to a +2.7V to +5.25V power supply.

Bypass DV

DD

to GND with a 0.1µF capacitor.

—19DIG4 Digit 4 Driver

—29LED_EN

Active-High LED Enable. The MAX1499 LED display driver turns off when LED_EN is

driven to logic low. The MAX1499 LED display driver turns on when LED_EN is driven to

logic high.

—30

Low-Battery Voltage Monitor. When the LOWBATT input voltage is lower than 2.048V, the

LOWBATT bit in the status register is set to one.

MAX1499

LOWBATT

Page 12

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

12 ______________________________________________________________________________________

Digital Filtering

The MAX1497/MAX1499 contain an on-chip digital lowpass filter that processes the data stream from the

modulator using a SINC4response:

The SINC

4

filter has a settling time of four output data

periods (4 x 200ms).

The MAX1497/MAX1499 have 25% overrange capabili-

ty built into the modulator and digital filter. The digital filter is optimized for the f

CLK

equal to 4.9152MHz. Other

clock frequencies can be used; however, 50Hz/60Hz

noise rejection decreases. The frequency response of the

SINC4filter is calculated as follows:

where N is the oversampling ratio, and f

m

= N x output

data rate = 5Hz.

Filter Characteristics

Figure 2 shows the filter frequency response. The

SINC4characteristic -3dB cutoff frequency is 0.228

times the first notch frequency (5Hz). The oversampling

ratio (OSR) for the MAX1497 is 128 and the OSR for the

MAX1499 is 1024.

The output data rate for the digital filter corresponds to

the positioning of the first notch of the filter’s frequency

response. The notches of the SINC4filter are repeated

at multiples of the first notch frequency. The SINC4filter

provides an attenuation of better than 100dB at these

notches. For example, 50Hz is equal to 10 times the

first notch frequency and 60Hz is equal to 12 times the

first notch frequency.

For large step changes at the input, allow a settling

time of 800ms before valid data is read.

Clock Modes

Configure the MAX1497/MAX1499 to use either the

internal oscillator or an externally applied clock to drive

the modulator and filter. Set the EXTCLK bit in the control register to zero to put the device in internal-clock

mode. Set the EXTCLK bit to one to put the device in

Hz

N

Z

Z

Hf

N

N

f

f

f

f

N

m

m

()

()

()

()

sin

sin

=

=

1

1

1

1

1

4

4

-

-

-

-

π

π

sin( )x

x

4

MAX1499

BINARY-TO-

BCD

CONVERTERS

ADC

LED

DRIVER

INPUT

BUFFERS

-2.5V

AIN+

AIN-

REF+

REF-

+2.5V

AV

DD

DV

DD

GLED

2.048V

BANDGAP

REFERENCE

OSCILLATOR

CLOCK

SCLK DIN DOUT

EOC

SEG1

SEGF

SEGDP

DIG0

DIG4

CLK

CS

SERIAL I/O AND CONTROL

+2.5V

2.048V

GND

A = 1.22

TO

CONTROL

CHARGE

PUMP

-2.5V

LOWBATTV

NEG

LED_EN

VLED

I

SET

Figure 1. MAX1499 Functional Diagram

Page 13

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 13

external-clock mode. When using the internal oscillator,

connect CLK to GND or DV

DD

for the MAX1499, or con-

nect CLK to V

DD

for the MAX1497. The MAX1497/

MAX1499 ideally operate with a 4.9152MHz clock to

achieve maximum rejection of 50Hz/60Hz commonmode, power-supply, and normal-mode noise.

Internal-Clock Mode

The MAX1497/MAX1499 contain an internal oscillator.

The power-up condition for the MAX1497/MAX1499 is

internal clock operation with the EXTCLK bit in the control register equal to zero. Using the internal oscillator

saves board space by removing the need for an external clock source.

External-Clock Mode

For external clock operation, set the EXTCLK bit in the

control register to one and drive CLK with a 4.9152MHz

clock source for best 50Hz/60Hz rejection ratio. Other

external clock frequencies allow for custom conversion

rates. A 2.4576MHz clock signal reduces the conversion rate and the LED update rate by a factor of two

while keeping good 50Hz/60Hz noise rejection. The

MAX1497/MAX1499 operate with an external clock

source of up to 5.05MHz.

Charge Pump

The MAX1497/MAX1499 contain an internal charge pump

to provide the negative supply voltage for the internal

analog input/reference buffers. The bipolar input range of

the analog input/reference buffers allows this device to

accept negative inputs with high source impedances.

Connect a 0.1µF capacitor from VNEG to GND.

LED Driver

The MAX1499 has a 4.5-digit common-cathode display

driver and the MAX1497 has a 3.5-digit common-cathode display driver. Figures 3 and 4 show the connection

schemes for a standard seven-segment LED display.

The LED update rate is 2.5Hz. The MAX1497/

MAX1499 automatically display the results of the ADC, if

desired (Table 1). The MAX1497/MAX1499 also allow

independent control of the LED driver through the serial

interface, allowing for data processing of the ADC result

before showing the result on the LED. Additionally, each

LED segment can be individually controlled (see the

LED segment-display register sections).

A

B

C

A AAA

D

DIGIT 4 DIGIT 3 DIGIT 2 DIGIT 1 DIGIT 0

D DDD

E

G

F

EEE

GGGG

F FFF

BBBB

CC CC

DP DP DP DP DP

Figure 3. Segment Connection for the MAX1499 (4.5 Digits)

A

B

AA A

D

DIGIT 3 DIGIT 2 DIGIT 1 DIGIT 0

DDD

E

G

F

EE

GGG

FFF

BBB

CC C

DP DP DP DP

C

Figure 4. Segment Connection for the MAX1497 (3.5 Digits)

SEG_SEL

SPI/ADC

HOLD

PEAK

DISPLAY VALUES

FORM

1XXX

LED segment

registers

01XX

LED display register

(user written)

001X

LED display register

0001Peak register

0000ADC result register

Table 1. LED Priority Table

X = Don’t care.

FREQUENCY (Hz)

GAIN (dB)

5040302010

-160

-120

-80

-40

0

-200

060

Figure 2. Frequency Response of the SINC4Filter (Notch at 60Hz)

Page 14

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

14 ______________________________________________________________________________________

Figure 5 shows a typical common-cathode configuration for two digits. In common-cathode configuration,

the cathodes of all LEDs in a digit are connected

together. Each segment driver of the MAX1497/

MAX1499 connects to its corresponding LEDs anodes.

For example, segment driver SEGA connects to all LED

segments designated as A. Similar configurations are

followed for other segment drivers.

The MAX1497/MAX1499 use a multiplexing scheme to

drive one digit at a time. The scan rate is fast enough to

make the digits appear to be lit. Figures 6 and 7 show

data timing diagrams for the MAX1497/MAX1499 where T

is the display scan period typically around 1/512Hz or

1.9531ms for the MAX1499 and 1/640Hz or 1.5625ms for

the MAX1497. TONin Figures 6 and 7 denotes the amount

of time each digit is on and is calculated as follows:

The MAX1497/MAX1499 allow for full decimal-point

control and feature leading-zero suppression. Use the

DPON, DPSET1, and DPSET2 bits in the control register

to set the value of the decimal point (Tables 2 and 3).

The MAX1497/MAX1499 overrange and underrange

display is shown in Table 4.

T

Tms

s MAX

T

Tms

s MAX

ON

ON

== =

== =

5

1 95312

5

390 60 1499

4

1 5625

4

390 60 1497

.

.( )

.

.( )

µ

µ

A

A

A

DIGIT 1 DIGIT 2

SEGDP

SEGG

SEGF

SEGE

SEGD

SEGC

SEGB

SEGA

DD

EE

GG

FF

BB

CC

DP DP

B C D E F G DP A B C D E F G DP

Figure 5. Two-Digit Common-Cathode Configuration

Table 2. Decimal-Point Control Table—MAX1499

DPON DPSET1 DPSET2 DISPLAY OUTPUT ZERO INPUT READING

00 0 18888 0

00 1 18888 0

01 0 18888 0

01 1 18888 0

10 0 1888.8 0.0

10 1 188.88 0.00

11 0 18.888 0.000

11 1 1.8888 0.0000

Table 3. Decimal-Point Control Table—MAX1497

DPON DPSET1 DPSET2 DISPLAY OUTPUT ZERO INPUT READING

X00 188.8 0.0

X01 18.88 0.00

X10 1888 0

X11 1.888 0.000

X = Don’t care.

Table 4. LED During Overrange and

Underrange Conditions

CONDITION MAX1497 MAX1499

Overrange 1--- 1----

Underrange -1--- -1----

Page 15

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 15

Leading-Zero Suppression

The MAX1497/MAX1499 include a leading-zero suppression circuitry to turn off unnecessary zeros. For

example, when DPSET1 and DPSET2 = [0,0], 0.0 is displayed instead of 000.0. This feature saves a substantial amount of power from being wasted.

Interdigit Blanking

The MAX1497/MAX1499 also include an interdigit

blanking circuitry. Without this feature, it is possible to

see a faint digit next to a digit that is completely on. The

interdigit blanking circuitry prevents bleeding over into

the next digit for a short period of time. The typical

interdigit blanking time is 4µs.

Reference

The MAX1497/MAX1499 reference sets the full-scale

range of the ADC transfer function. With a nominal

2.048V reference, the ADC full-scale range is ±2V with

the RANGE bit equal to zero. With the RANGE bit set to

one, the full-scale range is ±200mV. A decreased reference voltage decreases full-scale range (see the

Transfer Functions section).

The MAX1497/MAX1499 accept either an external reference or an internal reference. The INTREF bit selects

the reference mode (see the Control Register

(Read/Write) section).

For internal reference operation, set the INTREF bit to

one, connect REF- to GND, and bypass REF+ to GND

with a 4.7µF capacitor. The internal reference provides

a nominal 2.048V source between REF+ and GND. The

internal reference temperature coefficient is typically

40ppm/°C.

The default power-on state sets the MAX1497/

MAX1499 to use the external reference with the INTREF

bit cleared to zero. The external reference inputs, REF+

and REF-, are fully differential. For a valid external reference input, V

REF+

must be greater than V

REF-

. Bypass

REF+ and REF- with a 0.1µF or greater capacitor to

GND in external reference mode.

Figure 16 shows the MAX1497/MAX1499 operating with

an external single-ended reference. In this mode, REFis connected to GND and REF+ is driven with an external 2.048V reference. Bypass REF+ to GND with a

0.47µF capacitor.

143210432 04

T

T

ON

DIGIT 4 (MSD)

DIGIT 3

DIGIT 2

DIGIT 1

DIGIT 0 (LSD)

DATA

MSD LSD

Figure 6. LED Voltage Waveform—MAX1499

332103210 21

T

T

ON

DIGIT 3 (MSD)

DIGIT 2

DIGIT 1

DIGIT 0 (LSD)

DATA

MSD LSD

Figure 7. LED Voltage Waveform—MAX1497

Page 16

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

16 ______________________________________________________________________________________

Figure 15 shows the MAX1497/MAX1499 operating with

an external differential reference. In this mode, REF- is

connected to the top of the strain gauge and REF+ is

connected to the midpoint of the resistor-divider of

the supply.

Applications Information

Serial Interface

The SPI/QSPI/MICROWIRE serial interface consists of a

chip select (CS), a serial clock (SCLK), a data in (DIN),

a data out (DOUT), and an asynchronous EOC output.

EOC provides an asynchronous end-of-conversion signal with a period of 200ms (f

CLK

= 4.9152MHz). The

MAX1497 updates the data register when EOC goes

high. Data is valid in the ADC result registers when

EOC returns low. The serial interface provides access

to 12 on-chip registers, allowing control to all the power

modes and functional blocks. Table 5 lists the address

and read/write accessibility of all the registers.

A logic high on CS tri-states DOUT and causes the

MAX1497/MAX1499 to ignore any signals on SCLK and

DIN. To clock data in or out of the internal shift register,

drive CS low. SCLK synchronizes the data transfer. The

rising edge of SCLK clocks DIN into the shift register,

and the falling edge of SCLK clocks DOUT out of the

shift register. DIN and DOUT are transferred MSB first

(data is left justified). Figures 8–12 show the detailed

serial interface timing diagrams for the 8- and 16-bit

read/write operations.

All communication with the MAX1497/MAX1499 begins

with a command byte on DIN, where the first logic one

on DIN is recognized as the START bit (MSB) for the

command byte. The following seven clock cycles load

the command into a shift register. These 7 bits specify

which of the registers are accessed next, and whether

a read or write operation takes place. Transitions on the

serial clock after the command byte transfer, cause a

write or read from the device until the correct number of

CS

SCLK

DIN

DOUT

t

CSH

t

CL

t

DS

t

DH

t

DV

t

CH

t

DO

t

TR

t

CSH

t

CSS

Figure 8. Detailed Timing Diagram

SCLK

CS

DIN

DOUT

10RS4RS3 RS2 RS1 D7 D6 D5 D4 D3 D2 D1 D0D8D9RS0 x D15 D14 D13 D12 D11 D10

CONTROL BYTE DATA BYTE

Figure 9. Serial-Interface, 16-Bit, Write Timing Diagram

Page 17

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 17

SCLK

CS

DIN

DOUT

11RS4 RS3 RS2 RS1 RS0 x

D7 D6 D5 D4 D3 D2 D1 D0

CONTROL BYTE

DATA BYTE

Figure 12. Serial-Interface, 8-Bit, Read Timing Diagram

CS

SCLK

DIN

DOUT

10RS4 RS3 RS2 RS1 D7 D6 D5 D4 D3 D2 D1 D0RS0 x

CONTROL BYTE

DATA BYTE

Figure 10. Serial-Interface, 8-Bit, Write Timing Diagram

SCLK

CS

DIN

DOUT

11RS4 RS3 RS2 RS1 RS0 x

D7 D6 D5 D4 D3 D2 D1 D0D8D9D15 D14 D13 D12 D11 D10

CONTROL BYTE

DATA BYTE

Figure 11. Serial-Interface, 16-Bit, Read Timing Diagram

Page 18

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

18 ______________________________________________________________________________________

bits have been transferred (8 or 16). Once this has

occurred, the MAX1497/MAX1499 wait for the next

command byte. CS must not go high between data

transfers. If CS is toggled before the end of a write or

read operation, the device mode may be unknown.

Clock in 32 zeros to clear the device state and reset the

interface so it is ready to receive a new command byte.

On-Chip Registers

The MAX1497/MAX1499 contain 12 on-chip registers.

These registers configure the various functions of the

device and allow independent reading of the ADC

results and writing to the LED display. Table 5 lists the

address and size of each register.

The first of these registers is the status register. The 8bit status register contains the status flags for the ADC.

The second register is the 16-bit control register. This

register sets the LED display controls, range modes,

power-down modes, offset calibration, and the reset

register function (CLR). The third register is the 16-bit

overrange register, which sets the overrange limit of the

analog input. The fourth register is the 16-bit underrange register, which sets the underrange limit of the

analog input. Registers 5 through 7 contain the display

data for the individual segments of the LED. The eighth

register contains the custom offset value. The ninth register contains the 16 MSBs of the ADC conversion

result. The 10th register contains the LED data. The

11th register contains the peak analog input value. The

last register contains the lower four LSBs of the 20-bit

ADC conversion result.

REGISTER

N0.

ADDRESS

RS [4:0]

NAME WIDTH ACCESS

1 00000 Status register 8 Read only

2 00001 Control register 16 R/W

3 00010 Overrange register 16 R/W

4 00011 Underrange register 16 R/W

5 00100 LED segment-display register 1 16 R/W

6 00101 LED segment-display register 2 16 R/W

7 00110 LED segment-display register 3 8 R/W

8 00111 ADC custom offset register 16 R/W

9 01000 ADC result register 1 (16 MSBs) 16 Read only

10 01001 LED data register 16 R/W

11 01010 Peak register 16 Read only

12 10100 ADC result register 2 (4 LSBs) 8 Read only

—All other addresses Reserved — —

Table 5. Register Address Table

6kΩ

6kΩ

DOUT

DOUT

GND

GND

DV

DD

C

LOAD

50pF

C

LOAD

50pF

A) VOH TO HIGH-Z B) VOL TO HIGH-Z

Figure 13. Load Circuits for Disable Time

6kΩ

6kΩ

DOUT

DOUT

GND

GND

DV

DD

C

LOAD

50pF

C

LOAD

50pF

B) HIGH-Z TO VOH AND VOL TO V

OH

B) HIGH-Z TO VOL AND VOH TO V

OL

Figure 14. Load Circuits for Enable Time

Page 19

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 19

Default values: 00h

This register contains the status of the conversion

results.

SIGN: Latched negative-polarity indicator. Latches

high when the result is negative. Clears by reading the

status register, unless the condition remains true.

OVER: Overrange bit. Latches high if an overrange

condition occurs (the ADC result is larger than the

value in the overrange register). Clears by reading the

status register, unless the condition remains true.

UNDER: Underrange bit. Latches high if an underrange condition occurs (the ADC result is less than the

value in the underrange register). Clears by reading the

status register, unless the condition remains true.

LOW_BATT: Low-battery bit. Latches high if the voltage at the LOWBATT is lower than 2.048V (typ). Clears

by reading the status register, unless the condition

remains true. For the MAX1497, LOWBATT is not used

and the LOWBATT bit always returns to zero.

DRDY: Data ready bit. Latches high to indicate a completed conversion result with valid data. Read the ADC

result register to clear this bit.

Control and Status Registers

Command Byte (Write Only)

Status Register (Read Only)

MSB

LSB

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

START(1) R/W RS4 RS3 RS2 RS1 RS0 X

Control Register (Read/Write)

MSB

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

SPI/ADC EXTCLK INTREF DPON DPSET2 DPSET1 PD_DIG

PD_ANA

LSB

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

HOLD PEAK RANGE CLR SEG_SEL

OFFSET_

CAL2

ENABLE

START: Start bit. The first 1 clocked into the MAX1497/

MAX1499 is the first bit of the command byte.

(R/W): Read/Write. Set this bit to 1 to read from the

specified register. Set this bit to zero to write to the

selected register. Note that certain registers are read

only. Write commands to a read-only register are

ignored.

(RS4–RS0): Register address bits. RS4 to RS0 specify

which register is accessed.

X: Don’t care.

Default values: 0001h

This register is the primary control register for the

MAX1497/MAX1499. It is a 16-bit read/write register. It

is used to indicate the desired clock and reference

source. It sets the LED display controls, range modes,

power-down modes, offset calibration, and the reset

register function (CLR).

ENABLE: (default = 1) LED driver enable bit. When set to

1, the MAX1497/MAX1499 enables the LED display drivers. A 0 in this location disables the LED display drivers.

OFFSET_CAL2: (default = 0) Enhanced offset-calibration start bit (MAX1499, RANGE = 1). To achieve the

lowest possible offset in the ±200mV input range, per-

form an enhanced offset calibration by setting this bit to

MSB LSB

SIGN OVER UNDER LOW_BATT DRDY 0 0 0

OFFSET_CAL1

Page 20

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

20 ______________________________________________________________________________________

1. The calibration takes about nine cycles (1800ms).

After the calibration completes, set this bit to zero to

resume ADC conversions.

OFFSET_CAL1: (default = 0) Automatic offset calibration enable bit. When set to 1, the MAX1497/

MAX1499 disable automatic offset calibration. When this

bit is set to zero, automatic offset calibration is enabled.

SEG_SEL: (default = 0) SEG_SEL segment selection

bit. When set to 1, the LED segment drivers use the

LED segment registers to display individual segments

that can form letters or numbers or other information on

the display. The LED data register is not displayed.

Send the data first to the LED segment-display registers and then set this bit high.

CLR: (default = 0) Clear all registers bit. When set to 1,

all registers reset to their power-on reset states after CS

makes a low-to-high transition.

RANGE: (default = 0) Input range select bit. When set

to zero, the input voltage range is ±2V. When set to 1,

the input voltage range is ±200mV.

PEAK: (default = 0) Peak bit. When set to 1 (and the

HOLD bit is set to zero), the LED shows the result

stored in the peak register (see Table 6).

HOLD: (default = 0) Hold bit. When set to 1, the LED

register does not update from the ADC conversion

results and holds the last result on the LED. The

MAX1497/MAX1499 continue to perform conversions

during HOLD (Table 1).

PD_ANA: (default = 0) Power-down analog select bit.

When set to 1, the analog circuits (analog modulator

and ADC input buffers) go into the power-down mode.

When set to zero, the device is in full power-up mode.

PD_DIG: (default = 0) Power-down digital select bit.

When set to 1, the digital circuits (digital filter and LED

drivers) go into power-down mode. This also resets the

values of the internal SRAM in the digital filter to zeros.

When set to zero, the device returns to full power-up

mode. When powering down PD_DIG, power down the

LED segment drivers by clearing the ENABLE bit to zero.

DPSET[2:1]: (default = 00) Decimal-point selection bits

(Table 2 and 3).

DPON: (default = 0) Decimal-point enable bit (Tables 2

and 3).

INTREF: (default = 0) Reference select bit. For internal

reference operation, set INTREF to 1. For external reference operation, set INTREF to zero.

EXTCLK: (default = 0) External clock select bit. The

EXTCLK bit controls selection of the internal clock or an

external clock source. A 1 in this location selects the

signal at the CLK input as the clock source. A zero in

this location selects and powers up the internal clock

oscillator.

SPI/ADC: (default = 0) Display select bit. The SPI/ADC bit

controls selection of the data fed into LED data register. A

1 in this location selects SPI/QSPI/ MICROWIRE data

(user writes this data to the LED data register). A zero in

this location selects the ADC result register data, unless

hold or peak functions are active (Table 1).

Note: When changing any one of the following control

bits: OFFSET_CAL1, RANGE, PD_ANA, PD_DIG,

INTREF, and EXTCLK, wait 800ms before reading the

ADC results.

Overrange Register (Read/Write)

MSB

LSB

D15

D0

Default values: 7CF0h (for 3.5-digit, +1999)

4E1Fh (for 4.5-digit, +19,999)

The overrange register is a 16-bit read/write register

(D15 is the MSB). When the conversion result exceeds

the value in the overrange register, the OVER bit in the

status register latches to 1. The LED shows a 1 followed

by four dashes for the MAX1499 or a 1 followed by

three dashes for the MAX1497 (Table 4).

The data is represented in two’s complement format.

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1

Page 21

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 21

Default values: 8300h (for 3.5-digit, -2000)

B1E0h (for 4.5-digit, -20,000)

The underrange data register is 16-bit read/write register (D15 is the MSB). When the conversion result falls

below the value in the underrange register, the UNDR

bit in the status register sets to 1. The LED shows a -1

followed by four dashes for the MAX1499 or a -1 followed by three dashes for the MAX1497 (Table 4).

The data is represented in two’s complement format.

Default values: 0000h

Underrange Register (Read/Write)

MSB

LSB

D15

D0

LED Segment-Display Register 1 (Read/Write)

MSB

Bit 15 Bit 14 Bit 13 Bit 1 Bit 11 Bit 10 Bit 9 Bit 8

A1 G1 D1 F1 E1 DP2 X B0

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

C0 A0 G0 D0 F0 E0 DP1 0

LED segment-display register 1 is a 16-bit read/write

register. When the LED bit (in the control register) is set

to 1, the MAX1497/MAX1499 provide direct access to

individual LED segments. The bits in the LED segmentdisplay register determine if a segment is on or off.

Write a zero to turn on a segment and a 1 to turn off a

segment.

DP1: Segment DP driver bit of digit 1. The default value

turns on the LED segment.

E0: Segment E driver bit of digit 0. The default value

turns on the LED segment.

F0: Segment F driver bit of digit 0. The default value

turns on the LED segment.

D0: Segment D driver bit of digit 0. The default value

turns on the LED segment.

G0: Segment G driver bit of digit 0. The default value

turns on the LED segment.

A0: Segment A driver bit of digit 0. The default value

turns on the LED segment.

C0: Segment C driver bit of digit 0. The default value

turns on the LED segment.

B0: Segment B driver bit of digit 0. The default value

turns on the LED segment.

X: Don’t care.

DP2: Segment DP driver bit of digit 2. The default value

turns on the LED segment.

E1: Segment E driver bit of digit 1. The default value

turns on the LED segment.

F1: Segment F driver bit of digit 1. The default value

turns on the LED segment.

D1: Segment D driver bit of digit 1. The default value

turns on the LED segment.

G1: Segment G driver bit of digit 1. The default value

turns on the LED segment.

A1: Segment A driver bit of digit 1. The default value

turns on the LED segment.

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1

LSB

Page 22

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

22 ______________________________________________________________________________________

Default values: 0000h

LED segment-display register 2 is a 16-bit read/write

register. When the SEG_SEL bit (in the control register)

is set to 1, the MAX1497/MAX1499 provide direct

access to individual LED segments. The bits in the LED

segment-display register determine if a segment is on

or off. Write a zero to turn on a segment and a 1 to turn

off a segment.

C1: Segment C driver bit of digit 1. The default value

turns on the LED segment.

B1: Segment B driver bit of digit 1. The default value

turns on the LED segment.

MINUS: Segment minus driver bit. The default value

turns on the LED minus segment. Setting this bit to 1

enables the plus sign on the LED display.

DP3: Segment DP driver bit of digit 3. The default value

turns on the LED segment.

E2: Segment E driver bit of digit 2. The default value

turns on the LED segment.

F2: Segment F driver bit of digit 2. The default value

turns on the LED segment.

D2: Segment D driver bit of digit 2. The default value

turns on the LED segment.

G2: Segment G driver bit of digit 2. The default value

turns on the LED segment.

A2: Segment A driver bit of digit 2. The default value

turns on the LED segment.

C2: Segment C driver bit of digit 2. The default value

turns on the LED segment.

B2: Segment B driver bit of digit 2. The default value

turns on the LED segment.

DP4: Segment DP driver bit of digit 4. The default value

turns on the LED segment (MAX1499 only).

E3: Segment E driver bit of digit 3. The default value

turns on the LED segment (MAX1499 only).

F3: Segment F driver bit of digit 3. The default value

turns on the LED segment (MAX1499 only).

LED Segment-Display Register 2 (Read/Write)

MSB

Bit 15 Bit 14 Bit 13 Bit 1 Bit 11 Bit 10 Bit 9 Bit 8

F3 E3 DP4 MINUS B2 C2 A2 G2

LSB

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

D2 F2 E2 DP3 X B1 C1 0

LED Segment-Display Register 3 (Read/Write)

MSB

LSB

XXBC_ B3 C3 A3 G3 D3

Default values: 00h

LED segment-display register 3 is an 8-bit read/write

register. When the SEG_SEL bit (in the control register)

is set to 1, the MAX1497/MAX1499 provide direct

access to individual LED segments. The bits in the LED

segment-display register determine if a segment is on

or off. Write a zero to turn on a segment and a 1 to turn

off a segment.

D3: Segment D driver bit of digit 3. The default value

turns on the LED segment (MAX1499 only).

G3: Segment G driver bit of digit 3. The default value

turns on the LED segment (MAX1499 only).

A3: Segment A driver bit of digit 3. The default value

turns on the LED segment (MAX1499 only).

C3: Segment C driver bit of digit 3. The default value

turns on the LED segment (MAX1499 only).

B3: Segment B driver bit of digit 3. The default value

turns on the LED segment (MAX1499 only).

BC_: Segment B and C driver bit of digit 3 (3.5 digits)

or Digit 4 (4.5 digits). The default value turns on the

LED segment.

X: Don’t care.

Page 23

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 23

Default values: 0000h

In addition to automatic offset calibration, the

MAX1497/MAX1499 offer a user-defined custom offset

16-bit read/write register. The final result of the ADC

conversion is the input after autocalibration minus

the value in the custom offset. The custom offset value

is stored in this register. D15 is the MSB. The data is

represented in two’s complement format.

ADC Custom Offset-Calibration Register (Read/Write)

MSB

D15

ADC Result Register 1 (Read Only)

MSB

LSB

(MAX1497)

LSB

(MAX1499)

D15

D0

Default values: 0000h

ADC result register 1 is a 16-bit read-only register. This

register stores the 16 MSBs of the ADC result. The data

is represented in two’s complement format.

For the MAX1499, the data is 16-bit and D15 is the

MSB. For the MAX1497, the data is 12-bit, D15 is the

MSB, and D4 is the LSB.

Default values: 0000h

The LED data register is a 16-bit read/write register.

This register updates from ADC result register 1 or from

the serial interface by selecting the SPI/ADC bit in the

control register. The data is represented in two’s complement format.

For the MAX1499, the data is 16-bit and D15 is the

MSB. For the MAX1497, the data is 12-bit, D15 is the

MSB, and D4 is the LSB, followed by 4 trailing sub-bits.

LED Data Register (Read/Write)

MSB

LSB

(MAX1497)

LSB

(MAX1499)

D15

D0

ADC Result Register 2 (Read Only)

MSB LSB

D3 D2 D1 D0 0 0 0 0

Default values: 00h

ADC result register 2 is an 8-bit read-only register. This

register stores the 4 LSBs of the ADC result.

Use this result with the result in ADC result-register 1 to

form a 20-bit two’s complement conversion result.

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1

LSB

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1

Page 24

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

24 ______________________________________________________________________________________

PEAK Register (Read Only)

MSB

LSB

(MAX1497)

LSB

(MAX1499)

D15

D0

Default values: B1E0h

The peak data register is a 16-bit read only register. Set

the PEAK bit to 1 to enable the PEAK function. This register stores the peak value of the ADC conversion

result. First, the current ADC result is saved to the

PEAK register, then the new ADC conversion result is

compared to this value. If the new value is larger than

the value in the peak register, the MAX1497/MAX1499

save the new value to the peak register. If the new

value is less than the value in the peak register, the

value in the peak register remains unchanged. Set the

PEAK bit to zero to clear the value in the PEAK register.

The data is represented in two’s complement format.

For the MAX1499, the data is 16-bit and D15 is the MSB.

For the MAX1497, the data is 12-bit, D15 is the MSB,

and D4 is the LSB followed by 4 trailing sub-bits.

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1

Page 25

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

______________________________________________________________________________________ 25

Figure 16. Thermocouple Application with the MAX1497/MAX1499

Figure 15. Strain-Gauge Application with the MAX1497/MAX1499

MAX1497

MAX1499

AV

DD

DV

DD

DOUT

DIN

SCLK

4.7µF

0.1µF

0.1µF

0.1µF

0.1µF

0.1µF

ANALOG SUPPLY

FERRITE

BEAD

R

REF

R

R

ACTIVE

GAUGE

DUMMY

GAUGE

REF+

REF-

AIN+

AIN-

GND

EOC

CS

4.7µF

0.1µF

Power-On Reset

At power-on, the serial interface, logic LED drivers, digital filter, and modulator circuits reset. The registers

return to their default values. Allow time for the reference to settle before starting calibration.

Offset Calibration

The MAX1497/MAX1499 offer on-chip offset calibration.

The device offset calibrates during every conversion

when the OFFSET_CAL1 bit is zero in the control register. Enhanced offset calibration is only needed in the

MAX1499 when the RANGE bit = 1. It is performed on

demand by setting the OFFSET_CAL2 bit to 1.

Enhanced Offset Calibration

Enhanced offset calibration is a more accurate calibration method that is needed in the case of the ±200mV

range and 4.5-digit resolution. The MAX1499 performs

the enhanced calibration on demand by setting the

OFFSET_CAL2 bit to 1.

Power-Down Modes

The MAX1497/MAX1499 feature independent powerdown control of the analog and digital LED drivers circuitry. Writing a 1 to the PD_DIG and PD_ANA bits in

the control word, powers down the analog and digital

circuitry, reducing the supply current to 268µA (typ).

PD_DIG powers down the digital filter, while PD_ANA

powers down the analog modulator and ADC input

buffers. Writing a zero to the ENABLE bit in the control

word, powers down the LED drivers.

Peak

The MAX1497/MAX1499 feature peak detection circuitry. When activated (PEAK bit = 1), the devices display

only the highest voltage measured to the LED.

Hold

The MAX1497/MAX1499 feature data-hold circuitry.

When activated (HOLD bit = 1), the device displays the

current reading on the LED.

Low Battery

The MAX1499 features a low-battery detection input.

When the voltage at LOWBATT drops below 2.048V

(typ), the LOWBATT bit of the status register goes high.

Strain-Gauge Measurement

Connect the differential inputs of the MAX1497/MAX1499

to the bridge network of the strain gauge. In Figure 15,

the analog supply voltage powers the bridge network

and the MAX1497/MAX1499 along with the reference

voltage. The MAX1497/MAX1499 handle an analog input

voltage range of ±200mV and ±2V full scale. The analog/reference inputs of the parts allow the analog input

range to have an absolute value of anywhere between

-2.2V and +2.2V.

TEMP

SENSOR

THERMOCOUPLE

JUNCTION

+5V

MAX6062

0.1µF

+2.048V

0.47µF

AIN+

AIN-

REF+

REF-

GND

MAX1497

MAX1499

SPI

µC

Page 26

MAX1497/MAX1499

3.5- and 4.5-Digit, Single-Chip ADCs with LED

Drivers and µC Interface

26 ______________________________________________________________________________________

Thermocouple Measurement

Figure 16 shows a connection from a thermocouple to

the MAX1497/MAX1499. In this application, the

MAX1497/MAX1499 take advantage of the on-chip

input buffers that allow large source impedances on the

front end. The decoupling capacitors reduce noise

pickup from the thermocouple leads. To place the differential voltage from the thermocouple at a suitable

common-mode voltage, the AIN- input of the MAX1497/

MAX1499 is biased to GND. Use an external temperature sensor, such as the DS75, and a µC to perform

cold-junction temperature compensation.

Transfer Functions

Figures 17–20 show the transfer functions of the

MAX1497/MAX1499. The output data is stored in the

ADC data register in two’s complement.

The transfer function for the MAX1499 with AIN+ - AIN≥ 0, RANGE = 0 is:

COUNTS

VV

VV

AIN AIN

REF REF

. ,=

×

+

+

−

−

−

−

1 024 20 000

7CFh

7CFh

002h

001h

000h

FFFh

FFEh

FFDh

830h

<830h

-200mV

0

ANALOG INPUT VOLTAGE

+200mV

ADC RESULT

LED

1 - - -

1999

2

1

0

- 0

- 1

- 2

-1999

- 1 - - -

-100µV

100µV

Figure 19. MAX1497 Transfer Function, ±200mV Range

>7CFh

7CFh

002h

001h

000h

FFFh

FFEh

FFDh

830h

<830h

-2V

0

ANALOG INPUT VOLTAGE

+2V

ADC RESULT

LED

1 - - -

1999

2

1

0

- 0

- 1

- 2

-1999

- 1 - - -

-1mV

1mV

Figure 20. MAX1497 Transfer Function, ±2V Range

>4E1Fh

4E1Fh

0002h

0001h

0000h

FFFFh

FFFEh

FFFDh

B1E0h

<B1E0h

-2V

0

ANALOG INPUT VOLTAGE

+2V

ADC RESULT

LED

1 - - - -

19,999

2

1

0

- 0

- 1

- 2

-19,999

- 1 - - - -

-100µV

100µV

Figure 17. MAX1499 Transfer Function, ±2V Range

4E1Fh

4E1Fh

0002h

00001h

0000h

FFFFh

FFFEh

FFFDh

B1E0h

<B1E0h

-200mV

0

ANALOG INPUT VOLTAGE

+200mV

ADC RESULT

LED

1 - - - -

19,999

2

1

0

- 0

- 1

- 2

-19,999

- 1 - - - -

-10µV

10µV

Figure 18. MAX1499 Transfer Function, ±200mV Range

Page 27

The transfer function for the MAX1499 with AIN+ - AIN< 0, RANGE = 0 is:

The transfer function for the MAX1497 with AIN+ - AIN≥ 0, RANGE = 0 is:

The transfer function for the MAX1497 with AIN+ - AIN< 0, RANGE = 0 is:

The transfer function for the MAX1499 with AIN+ - AIN≥ 0, RANGE = 1 is:

The transfer function for the MAX1499 with AIN+ - AIN< 0, RANGE = 1 is:

The transfer function for the MAX1497 with AIN+ - AIN≥ 0, RANGE = 1 is:

The transfer function for the MAX1497 with AIN+ - AIN< 0, RANGE = 1 is:

Supplies, Layout, and Bypassing

Power up AVDD and DVDD (MAX1499) and VDD

(MAX1497) before applying an analog input and external reference voltage to the device. If this is not possible, limit the current into these inputs to 50mA. When

the analog and digital supplies come from the same

source, isolate the digital supply from the analog supply with a low-value resistor (10Ω) or ferrite bead. For

best performance, ground the MAX1497/MAX1499 to

the analog ground plane of the circuit board.

Avoid running digital lines under the device, because

they may couple noise onto the die. Run the analog

ground plane under the MAX1497/MAX1499 to minimize coupling of digital noise. Make the power-supply

lines to the MAX1497/MAX1499 as wide as possible to

provide low-impedance paths and reduce the effects of

glitches on the power-supply line.

Shield fast-switching signals, such as clocks, with digital

ground to avoid radiating noise to other sections of the

board. Avoid running clock signals near the analog

inputs. Avoid crossover of digital and analog signals.

Running traces that are on opposite sides of the board at