Page 1

General Description

The MAX1479 crystal-referenced phase-locked-loop

(PLL) VHF/UHF transmitter is designed to transmit ASK,

OOK, and FSK data in the 300MHz to 450MHz frequency

range. The MAX1479 supports data rates up to 100kbps

in ASK mode and 20kbps in FSK mode (both

Manchester coded). The device provides an adjustable

output power of more than +10dBm into a 50Ω load. The

crystal-based architecture of the MAX1479 eliminates

many of the common problems of SAW-based transmitters by providing greater modulation depth, faster frequency settling, higher tolerance of the transmit

frequency, and reduced temperature dependence.

These improvements enable better overall receiver performance when using the MAX1479 together with a

superheterodyne receiver such as the MAX1470,

MAX1471, MAX1473, or MAX7033.

The MAX1479 is available in a 16-pin thin QFN package (3mm x 3mm) and is specified for the automotive

temperature range from -40°C to +125°C.

Applications

Remote Keyless Entry

Tire Pressure Monitoring

Security Systems

Radio-Controlled Toys

Wireless Game Consoles

Wireless Computer Peripherals

Wireless Sensors

RF Remote Controls

Garage Door Openers

Features

♦ ETSI-Compliant EN300 220

♦ +2.1V to +3.6V Single-Supply Operation

♦ Supports ASK, OOK, and FSK Modulations

♦ Adjustable FSK Shift

♦ +10dBm Output Power into 50Ω Load

♦ Low Supply Current (6.7mA in ASK Mode,

and 10.5mA in FSK Mode)

♦ Uses Small Low-Cost Crystal

♦ Small 16-Pin Thin QFN Package

♦ Fast-On Oscillator—200µs Startup Time

♦ Programmable Clock Output

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

________________________________________________________________ Maxim Integrated Products 1

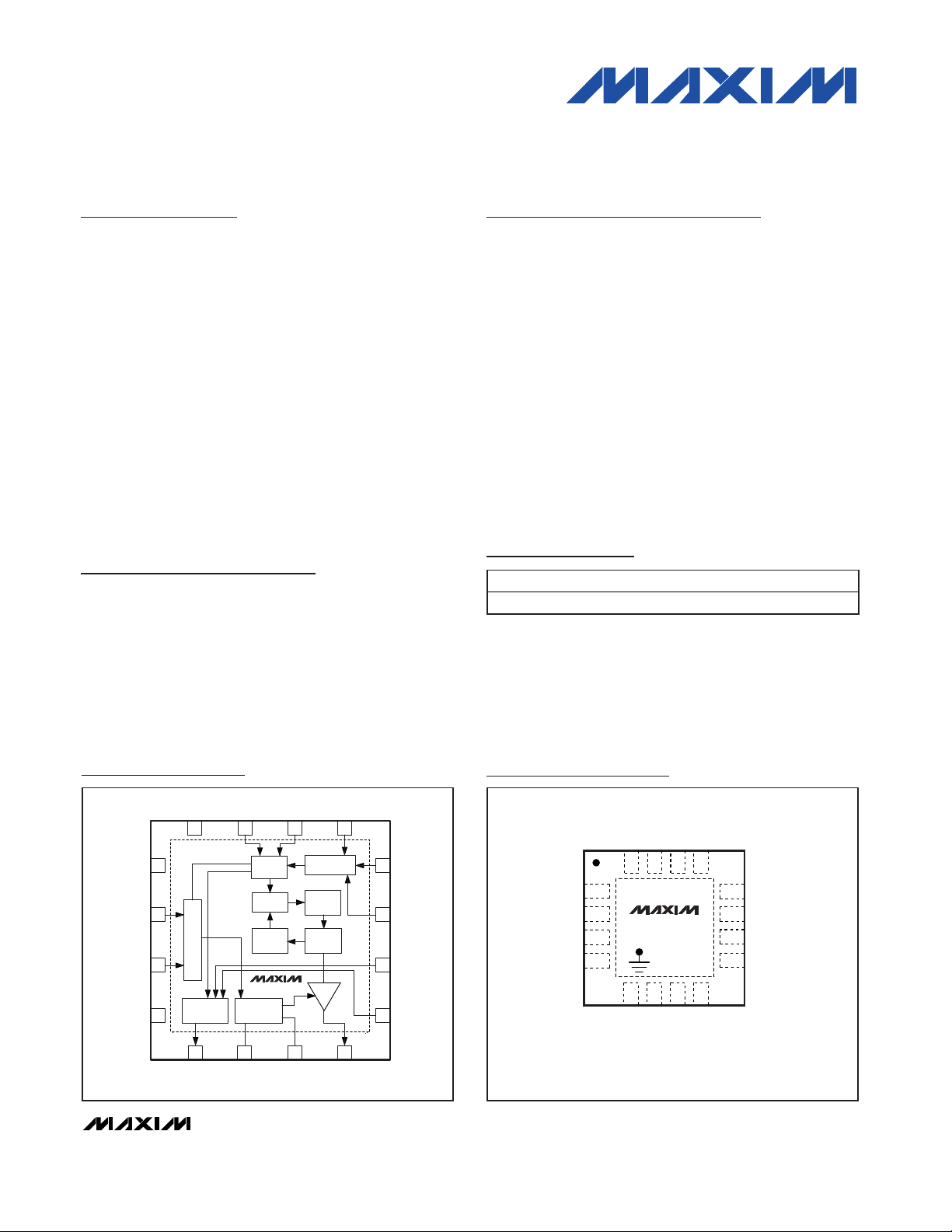

16 15 14 13

9

10

11

12

CLK0

CLK1

DEV0

DEV1

TOP VIEW

4

3

2

1

ENABLE

EP

DIN

MODE

V

DD

5678

V

DD_

PA

CLKOUT

PAOUT

ROUT

MAX1479

GND

XTAL2

XTAL1

DEV2

THIN QFN

(3mm x 3mm)

Pin Configuration

Ordering Information

MAX1479

ENABLE

DIN

MODE

V

DD

CLKOUT

V

DD_

PA

ROUT

PAOUT

CLK0

CLK1

DEV0

DEV1

DEV2

XTAL1

XTAL2

GND

CRYSTAL

DRIVER

4

3

2

1

5 6 7 8

9

10

11

12

13141516

CLOCK

DIVIDER

DIVIDE

BY 32

LOOP

FILTER

ASK

FSK

PA

ENVELOPE

SHAPING

DEVIATION

PD/CP

VCO

Functional Diagram

19-3353; Rev 0; 8/04

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

*EP = Exposed paddle.

PART TEMP RANGE PIN-PACKAGE

MAX1479ATE

16 Thin QFN-EP*

Typical Application Circuit appears at end of data sheet.

-40°C to +125°C

Page 2

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

2 _______________________________________________________________________________________

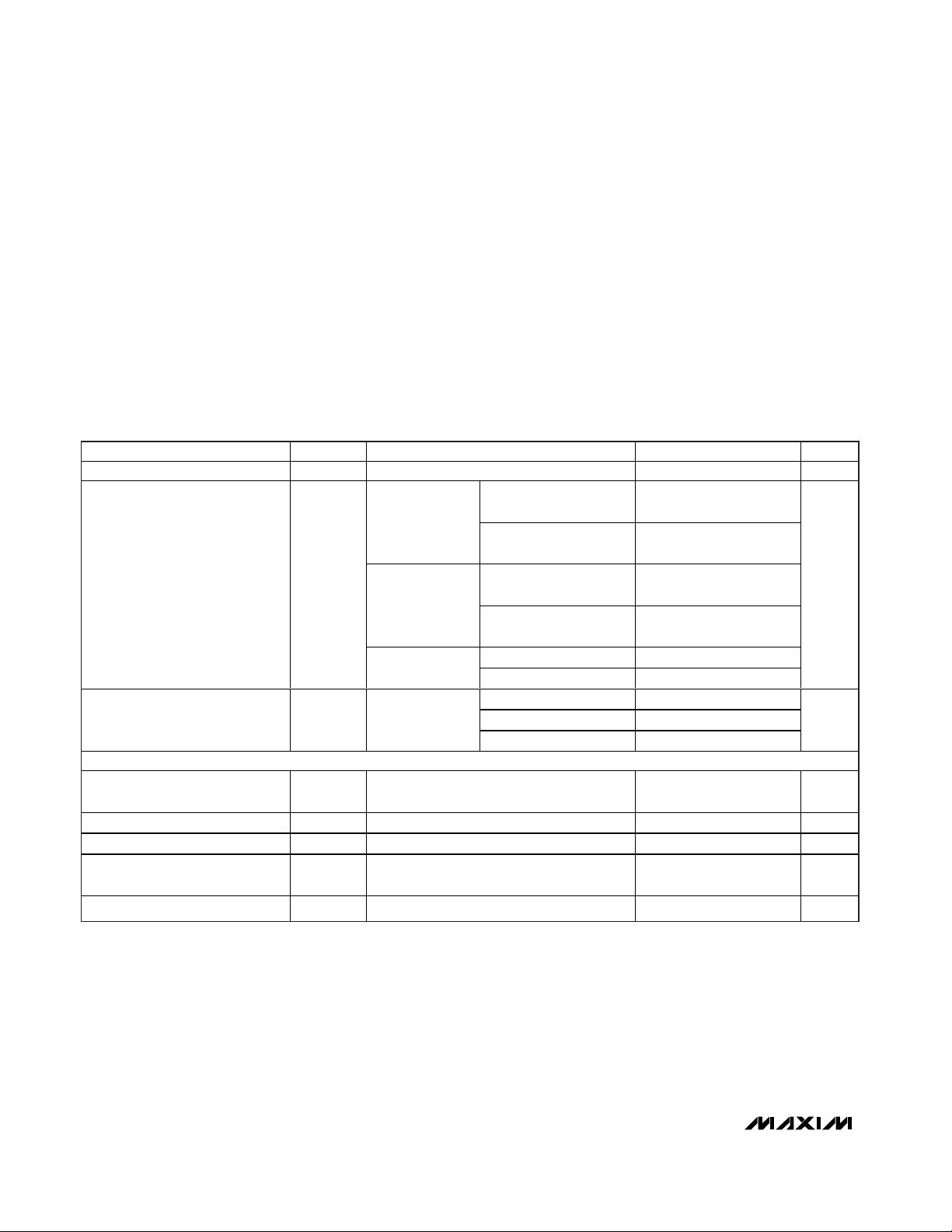

ABSOLUTE MAXIMUM RATINGS

DC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit, all RF inputs and outputs are referenced to 50Ω, VDD= +2.1V to +3.6V, V

ENABLE

= VDD, TA= -40°C to

+125°C, unless otherwise noted. Typical values are at V

DD

= +2.7V, TA= +25°C, unless otherwise noted.) (Note 1)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VDDto GND .............................................................-0.3V to +4V

All Other Pins to GND ................................-0.3V to (V

DD

+ 0.3V)

Continuous Power Dissipation (T

A

= +70°C)

16-Pin Thin QFN (derate 14.7mW/°C above +70°C) ...1176.5mW

Operating Temperature Range .........................-40°C to +125°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-60°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

PARAMETER

CONDITIONS

UNITS

Supply Voltage V

DD

2.1 3.6 V

fRF = 315MHz 2.9 4.3

PA off, V

DIN

at

0% duty cycle

(ASK or FSK)

(Note 2)

f

RF

= 433MHz 3.3 4.8

fRF = 315MHz 6.7

V

DIN

at 50% duty

cycle (ASK)

(Notes 3, 4)

f

RF

= 433MHz 7.3

fRF = 315MHz (Note 2)

Supply Current I

DD

V

DIN

at 100%

fRF = 433MHz (Note 4)

mA

TA = +25°C 0.2

TA < +85°C (Note 4)

300

Standby Current I

STDBYVENABLE

< V

IL

TA < +125°C (Note 2)

nA

DIGITAL INPUTS AND OUTPUTS

Data Input High V

IH

(Note 2)

V

DD

V

Data Input Low V

IL

(Note 2)

V

Maximum Input Current I

IN

20 µA

Output Voltage High V

OH

CLKOUT, load = 10kΩ || 10pF (Note 4)

V

DD

V

Output Voltage Low V

OL

CLKOUT, load = 10kΩ || 10pF (Note 4)

V

SYMBOL

MIN TYP MAX

10.7

duty cycle (FSK)

0.25

0.25

10.5 17.1

11.4 18.1

120

700 1600

11.4

0.25

0.25

Page 3

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

_______________________________________________________________________________________ 3

Note 1: Supply current, output power, and efficiency are greatly dependent on board layout and PAOUT match.

Note 2: 100% tested at T

A

= +125°C. Guaranteed by design and characterization over temperature.

Note 3: 50% duty cycle at 10kHz ASK data (Manchester coded).

Note 4: Guaranteed by design and characterization, not production tested.

Note 5: V

ENABLE

= VILto V

ENABLE

= VIH. f

OFFSET

is defined as the frequency deviation from the desired carrier frequency.

Note 6: Dependent on crystal and PC board trace capacitance.

Note 7: V

ENABLE

> VIH, V

DATA

> VIH, Efficiency = P

OUT

/ (VDDx IDD).

Note 8: Dependent on PC board trace capacitance.

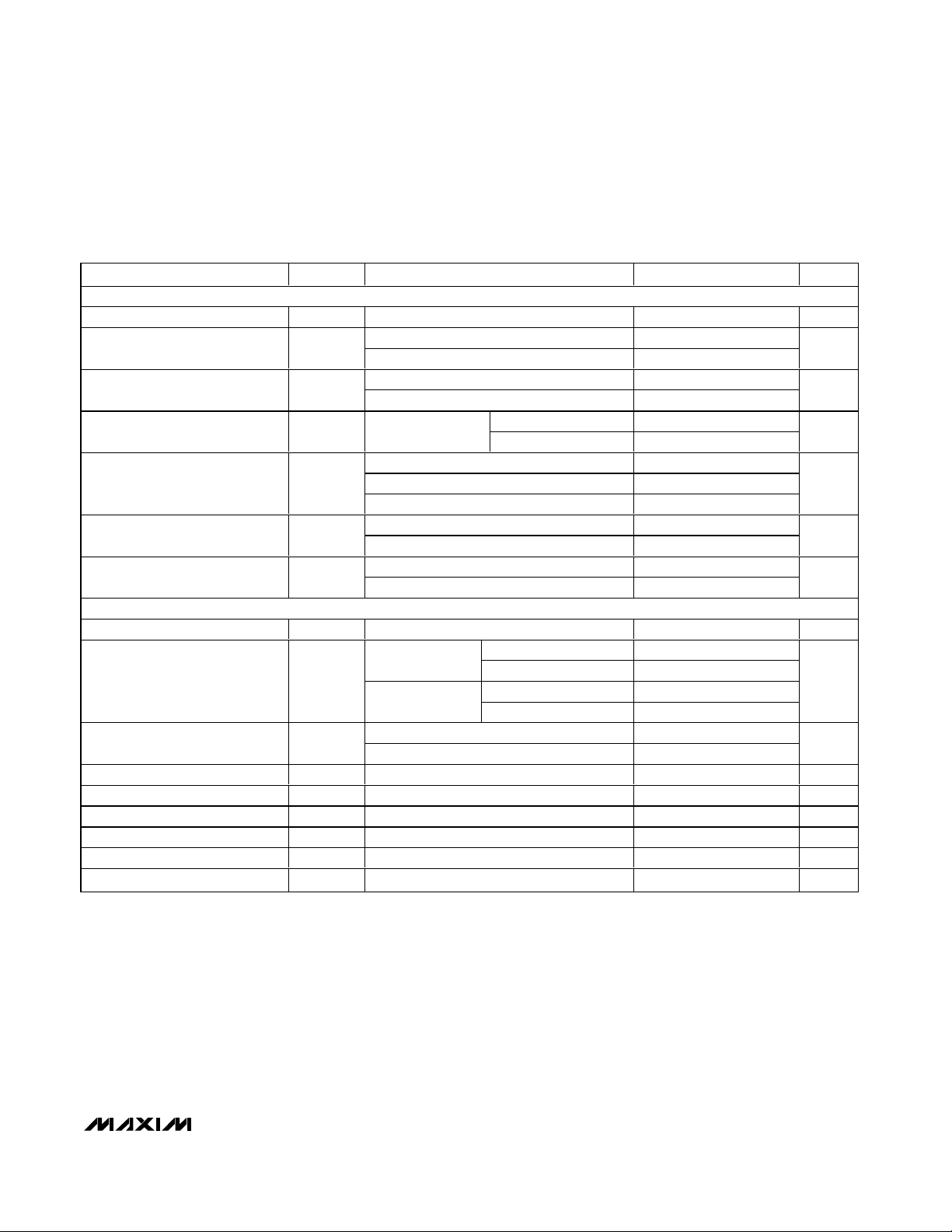

PARAMETER

CONDITIONS

SYSTEM PERFORMANCE

Frequency Range f

RF

(Note 2)

450

Settle to within 50kHz

Turn-On Time (Note 5) t

ON

Settle to within 5kHz

µs

ASK mode (Manchester coded)

Maximum Data Rate (Note 4)

FSK mode (Manchester coded) 20

fRF = 315MHz 55

Maximum FSK Frequency

Deviation

DEV[2:0] = 111

(Note 6)

f

RF

= 433MHz 80

kHz

TA = +25°C, VDD = +2.7V 6.8 10

TA = +125°C, VDD = +2.1V 2.7 5.3Output Power (Note 2) P

OUT

TA = -40°C, VDD = +3.6V

fRF = 315MHz 35

Transmit Efficiency with CW Tone

(Note 7)

f

RF

= 433MHz 34

%

fRF = 315MHz 27

Transmit Efficiency at 50% Duty

Cycle

f

RF

= 433MHz 25

%

PHASE-LOCKED-LOOP PERFORMANCE

VCO Gain K

VCO

f

OFFSET

= 100kHz -75

fRF = 315MHz

f

OFFSET

= 1MHz -98

f

OFFSET

= 100kHz -74

Phase Noise

f

RF

= 433MHz

f

OFFSET

= 1MHz -98

fRF = 315MHz -50

Maximum Carrier Harmonics

f

RF

= 433MHz -45

dBc

Reference Spur -40 dBc

Loop Bandwidth BW

kHz

Crystal Frequency Range f

XTAL

Crystal Tolerance 50

Crystal Load Capacitance C

LOAD

(Note 8) 4.5 pF

Clock Output Frequency

AC ELECTRICAL CHARACTERISTICS

(Typical Application Circuit, all RF inputs and outputs are referenced to 50Ω, VDD= +2.1V to +3.6V, V

ENABLE

= VDD, TA= -40°C to

+125°C, unless otherwise noted. Typical values are at V

DD

= +2.7V, TA= +25°C, unless otherwise noted.) (Note 1)

SYMBOL

D eter m i ned b y C LK0 and C LK1; see Tab l e 1 F

MIN TYP MAX UNITS

300

200

350

100

12.2 16.1

280 MHz/V

300

fRF/32 MHz

/ N MHz

XTAL

MHz

kbps

12.0

dBm

dBc/Hz

ppm

Page 4

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

4 _______________________________________________________________________________________

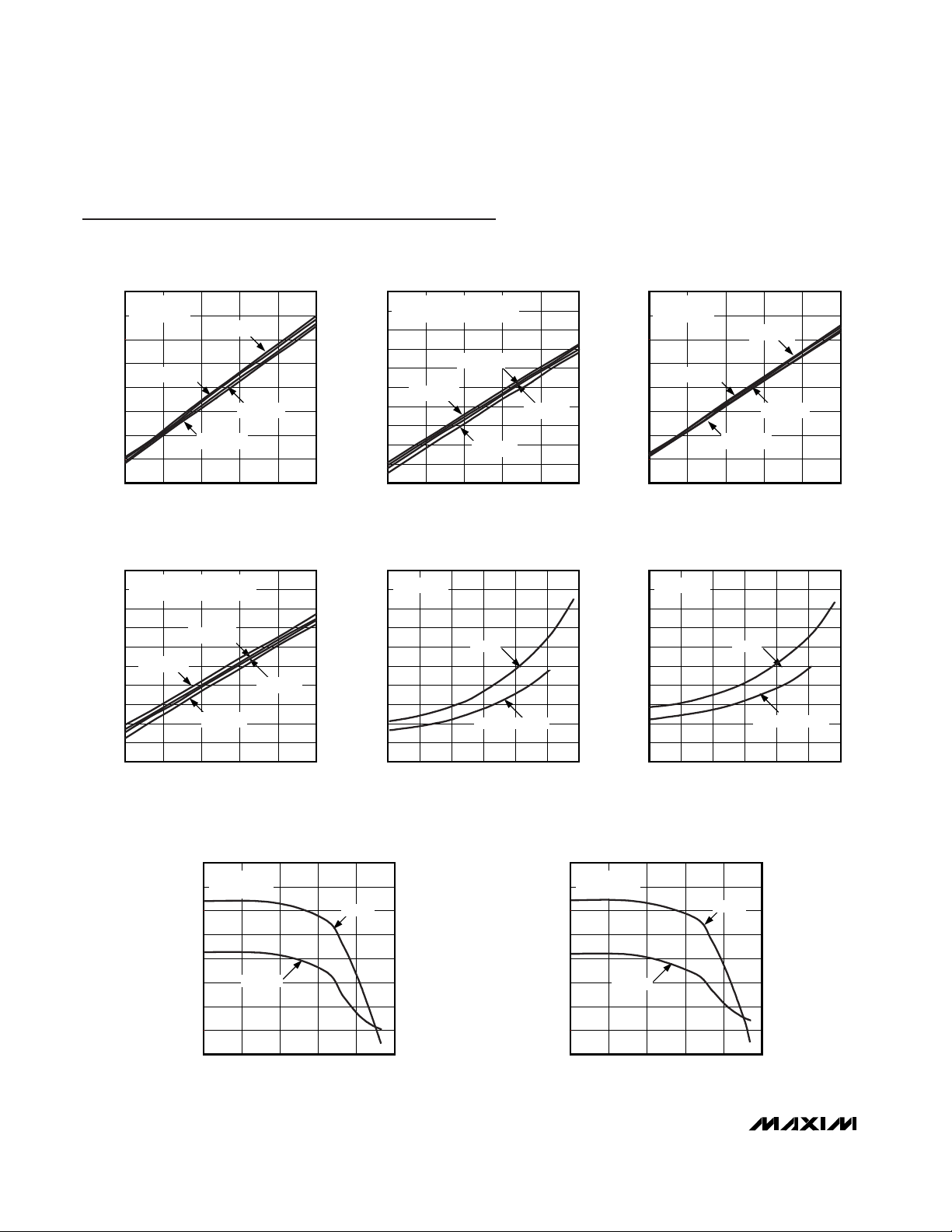

Typical Operating Characteristics

(Typical Application Circuit, VDD= +2.7V, TA = +25°C, unless otherwise noted.)

SUPPLY CURRENT vs. SUPPLY VOLTAGE

MAX1479 toc01

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (mA)

3.33.02.4 2.7

8

9

10

11

13

12

14

15

7

2.1 3.6

fRF = 315MHz

PA ON

TA = -40°C

TA = +25°C

TA = +125°C

TA = +85°C

3.33.02.72.4

5.5

6.0

6.5

7.0

7.5

8.0

8.5

9.0

9.5

10.0

5.0

2.1 3.6

SUPPLY CURRENT vs. SUPPLY VOLTAGE

MAX1479 toc02

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (mA)

fRF = 315MHz

PA 50% DUTY CYCLE AT 10kHz

TA = -40°C

TA = +25°C

TA = +125°C

TA = +85°C

SUPPLY CURRENT vs. SUPPLY VOLTAGE

MAX1479 toc03

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (mA)

3.33.02.4 2.7

8

9

10

11

13

12

14

15

7

2.1 3.6

fRF = 433MHz

PA ON

TA = -40°C

TA = +25°C

TA = +125°C

TA = +85°C

3.33.02.72.4

5.5

6.0

6.5

7.0

7.5

8.0

8.5

9.0

9.5

10.0

5.0

2.1 3.6

SUPPLY CURRENT vs. SUPPLY VOLTAGE

MAX1479 toc04

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (mA)

fRF = 433MHz

PA 50% DUTY CYCLE AT 10kHz

TA = -40°C

TA = +25°C

TA = +125°C

TA = +85°C

SUPPLY CURRENT vs. OUTPUT POWER

MAX1479 toc05

AVERAGE OUTPUT POWER (dBm)

SUPPLY CURRENT (mA)

62-2-6-10

3

4

5

6

7

8

9

10

11

12

2

-14 10

fRF = 315MHz

PA ON

50% DUTY CYCLE

SUPPLY CURRENT vs. OUTPUT POWER

MAX1479 toc06

AVERAGE OUTPUT POWER (dBm)

SUPPLY CURRENT (mA)

62-2-6-10

3

4

5

6

7

8

9

10

11

12

2

-14 10

fRF = 433MHz

PA ON

50% DUTY CYCLE

SUPPLY CURRENT AND OUTPUT POWER

vs. EXTERNAL RESISTOR

MAX1479 toc07

EXTERNAL RESISTOR (Ω)

SUPPLY CURRENT (mA)

OUTPUT POWER (dBm)

1k1001 10

4

6

8

10

14

12

16

18

2

-12

-8

-4

0

8

4

12

16

-16

0.1 10k

fRF = 315MHz

PA ON

POWER

CURRENT

SUPPLY CURRENT AND OUTPUT POWER

vs. EXTERNAL RESISTOR

MAX1479 toc08

EXTERNAL RESISTOR (Ω)

SUPPLY CURRENT (mA)

OUTPUT POWER (dBm)

1k1001 10

4

6

8

10

14

12

16

18

2

0.1 10k

fRF = 433MHz

PA ON

POWER

CURRENT

-12

-8

-4

0

8

4

12

16

-16

Page 5

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

_______________________________________________________________________________________ 5

OUTPUT POWER vs. SUPPLY VOLTAGE

MAX1479 toc10

SUPPLY VOLTAGE (V)

OUTPUT POWER (dBm)

3.33.02.72.4

6

8

10

12

14

16

4

2.1 3.6

fRF = 433MHz

PA ON

TA = +25°C

TA = +125°C

TA = +85°C

TA = -40°C

OUTPUT POWER vs. SUPPLY VOLTAGE

MAX1479 toc11

SUPPLY VOLTAGE (V)

OUTPUT POWER (dBm)

3.33.02.72.4

6

8

10

12

14

16

4

2.1 3.6

fRF = 315MHz

PA ON

ENVELOPE SHAPING

DISABLED

TA = +25°C

TA = +125°C

TA = +85°C

TA = -40°C

OUTPUT POWER vs. SUPPLY VOLTAGE

MAX1479 toc12

SUPPLY VOLTAGE (V)

OUTPUT POWER (dBm)

3.33.02.72.4

6

8

10

12

14

16

4

2.1 3.6

fRF = 433MHz

PA ON

ENVELOPE SHAPING

DISABLED

TA = +25°C

TA = +125°C

TA = +85°C

TA = -40°C

PHASE NOISE vs. OFFSET FREQUENCY

MAX1479 toc13

OFFSET FREQUENCY (Hz)

PHASE NOISE (dBc/Hz)

1M100k10k1k

-130

-120

-110

-100

-90

-80

-70

-60

-50

-40

-140

100 10M

fRF = 315MHz

fRF = 433MHz

CLOCK SPUR MAGNITUDE

vs. SUPPLY VOLTAGE

MAX1479 toc14

SUPPLY VOLTAGE (V)

CLKOUT SPUR MAGNITUDE (dBc)

3.33.02.72.4

-65

-60

-55

-50

-45

-40

-70

2.1 3.6

fRF = 315MHz

CLKOUT SPUR = f

RF

± f

CLKOUT

10pF LOAD CAPACITANCE

f

CLKOUT

= f

XTAL

/16

f

CLKOUT

= f

XTAL

/4

f

CLKOUT

= f

XTAL

/8

FREQUENCY STABILITY

vs. SUPPLY VOLTAGE

MAX1479 toc15

SUPPLY VOLTAGE (V)

FREQUENCY STABILITY (ppm)

3.33.02.72.4

-8

-6

-4

-2

0

2

4

6

8

10

-10

2.1 3.6

fRF = 315MHz

fRF = 433MHz

Typical Operating Characteristics (continued)

(Typical Application Circuit, VDD= +2.7V, TA = +25°C, unless otherwise noted.)

OUTPUT POWER vs. SUPPLY VOLTAGE

MAX1479 toc09

SUPPLY VOLTAGE (V)

OUTPUT POWER (dBm)

3.33.02.72.4

6

8

10

12

14

16

4

2.1 3.6

fRF = 315MHz

PA ON

TA = +25°C

TA = +125°C

TA = +85°C

TA = -40°C

Page 6

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

6 _______________________________________________________________________________________

Detailed Description

The MAX1479 is a highly integrated ASK/FSK transmitter operating over the 300MHz to 450MHz frequency

band. The device requires only a few external components to complete a transmitter solution. The MAX1479

includes a complete PLL and a highly efficient power

amplifier. The device can be set into a 0.2nA low-power

shutdown mode.

Shutdown Mode

ENABLE (pin 4) is internally pulled down with a 20µA

current source. If it is left unconnected or pulled low,

the MAX1479 goes into a low-power shutdown mode.

In this mode, the supply current drops to 0.2nA. When

ENABLE is high, the device is enabled and is ready for

transmission after 200µs (frequency settles to within

50kHz).

The 200µs turn-on time of the MAX1479 is mostly dominated by the crystal oscillator startup time. Once the

oscillator is running, the 300kHz PLL bandwidth allows

fast frequency recovery during power-amplifier toggling.

Mode Selection

MODE (pin 2) sets the MAX1479 in either ASK or FSK

mode. When MODE is set low, the device operates as

an ASK transmitter. If MODE is set high, the device

operates as an FSK transmitter. In the ASK mode, the

DIN pin controls the output of the power amplifier. A

logic low on DIN turns off the PA, and a logic high turns

on the PA. In the FSK mode, a logic low on the DIN pin

is represented by the low FSK frequency, and a logichigh input is represented by the high FSK frequency.

(The ASK carrier frequency and the lower FSK frequency are the same.) The deviation is proportional to the

crystal load impedance and pulling capacitance. The

maximum frequency deviation is 55kHz for f

RF

=

315MHz and 80kHz for f

RF

= 433MHz.

Pin Description

PIN

DESCRIPTION

1VDDSupply Voltage. Bypass to GND with a 10nF and 220pF capacitor as close to the pin as possible.

2

Mode Select. A logic low on MODE enables the device in ASK mode. A logic high on MODE enables the

device in FSK mode.

3DIN

Data Input. Power amplifier is on when DIN is high in ASK mode. Frequency is high when DIN is high in

FSK mode.

4

Standby/Power-Up Input. A logic low on ENABLE sets the device in standby mode.

5

Buffered Clock Output. Programmable through CLK0 and CLK1. See Table 1.

6

Power-Amplifier Supply Voltage. Bypass to GND with a 10nF and 220pF capacitor as close to the pin as

possible.

7ROUT

Envelope-Shaping Output. ROUT controls the power-amplifier envelope rise and fall. Bypass to GND with a

680pF and 220pF capacitor as close to the pin as possible.

8

Power-Amplifier Output. Requires a pullup inductor to the supply voltage, which can be part of the outputmatching network to an antenna.

9 CLK0 1st Clock Divider Setting. See Table 1.

10 CLK1 2nd Clock Divider Setting. See Table 1.

11 DEV0 1st FSK Frequency-Deviation Setting. See Table 2.

12 DEV1 2nd FSK Frequency-Deviation Setting. See Table 2.

13 DEV2 3rd FSK Frequency-Deviation Setting. See Table 2.

14

1st Crystal Input. fRF = 32 x f

XTAL

.

15

2nd Crystal Input. fRF = 32 x f

XTAL

.

16 GND Ground. Connect to system ground.

—EP

Exposed Ground Paddle. EP is the power amplifier’s ground. It must be connected to PC board through a

low-inductance path.

NAME

MODE

ENABLE

CLKOUT

V

DD_

PAOUT

XTAL1

XTAL2

PA

Page 7

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

_______________________________________________________________________________________ 7

Clock Output

The MAX1479 has a dedicated digital output pin for the

frequency-divided crystal clock signal. This is to be

used as the time base for a microprocessor. The frequency-division ratio is programmable through two digital input pins (CLK0, CLK1), and is defined in Table 1.

The clock output is designed to drive a 3.5MHz CMOS

rail-to-rail signal into a 10pF capacitive load.

Envelope-Shaping Resistor

The envelope-shaping resistor allows for a gentle turnon/turn-off of the PA in ASK mode. This results in a smaller spectral width of the modulated PA output signal.

Phase-Locked Loop

The PLL block contains a phase detector, charge

pump, integrated loop filter, VCO, asynchronous 32x

clock divider, and crystal oscillator. The PLL requires

no external components. The relationship between the

carrier and crystal frequency is given by:

f

XTAL

= fRF/ 32

Crystal Oscillator

The crystal oscillator in the MAX1479 is designed to

present a capacitance of approximately 3pF to ground

from the XTAL1 and XTAL2 pins in ASK mode. In most

cases, this corresponds to a 4.5pF load capacitance

applied to the external crystal when typical PC board

parasitics are added. In FSK mode, a percentage

(defined by bits DEV0 to DEV2) of the 3pF internal crystal oscillator capacitance is removed for a logic 1 on

the DIN pin to pull the transmit frequency. The frequency deviation is shown in Table 2. It is very important

to use a crystal with a load capacitance that is equal

to the capacitance of the MAX1479 crystal oscillator

plus PC board parasitics. If very large FSK frequency

deviations are desired, use a crystal with a larger

motional capacitance and/or reduce PC board parasitic

capacitances.

Power Amplifier

The PA of the MAX1479 is a high-efficiency, open-drain,

class-C amplifier. With a proper output-matching network, the PA can drive a wide range of impedances,

including small-loop PC board trace antennas and any

50Ω antennas. The output-matching network for a 50Ω

antenna is shown in the Typical Application Circuit. The

output-matching network suppresses the carrier harmonics and transforms the antenna impedance to an optimal

impedance at PAOUT (pin 8), which is about 250Ω.

When the output-matching network is properly tuned,

the power amplifier is highly efficient. The Typical

Application Circuit delivers +10dBm at a supply voltage of +2.7V, and draws a supply current of 6.7mA for

ASK/OOK operation (V

DIN

at 50% duty cycle) and

10.5mA for FSK operation. Thus, the overall efficiency

at 100% duty cycle is 35%. The efficiency of the power

amplifier itself is about 50%. An external resistor at

ROUT sets the output power.

Applications Information

Output Matching to 50Ω

When matched to a 50Ω system, the MAX1479 PA is

capable of delivering more than +10dBm of output

power at VDD= 2.7V. The output of the PA is an opendrain transistor that requires external impedance

matching and pullup inductance for proper biasing.

The pullup inductance from PAOUT to VDDserves three

main purposes: It forms a resonant tank circuit with the

capacitance of the PA output, provides biasing for the

PA, and becomes a high-frequency choke to reduce

the RF energy coupling into VDD. Maximum efficiency is

achieved when the PA drives a load of 250Ω. The recommended output-matching network topology is shown

in the Typical Application Circuit.

CLK1 CLK0 CLKOUT

00Logic 0

01f

XTAL

/ 4

10f

XTAL

/ 8

11f

XTAL

/ 16

Table 1. Clock Divider Settings

DEV2 DEV1 DEV0 DEVIATION

00 01/8 x max

00 11/4 x max

01 03/8 x max

01 11/2 x max

10 05/8 x max

10 13/4 x max

11 07/8 x max

11 1 Max

Table 2. Frequency-Deviation Settings

Page 8

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

8 _______________________________________________________________________________________

Output Matching to

PC Board Loop Antenna

In most applications, the MAX1479 power-amplifier output has to be impedance matched to a small-loop

antenna. The antenna is usually fabricated out of a copper trace on a PC board in a rectangular, circular, or

square pattern. The antenna has an impedance that

consists of a lossy component and a radiative component. To achieve high radiating efficiency, the radiative

component should be as high as possible, while minimizing the lossy component. In addition, the loop

antenna has an inherent loop inductance associated

with it (assuming the antenna is terminated to ground).

For example, in a typical application, the radiative

impedance is less than 0.5Ω, the lossy impedance is

less than 0.7Ω, and the inductance is approximately

50nH to 100nH.

The objective of the matching network is to match the

power-amplifier output to the impedance of the smallloop antenna. The matching components thus tune out

the loop inductance and transform the low radiative

and resistive parts of the antenna into the much higher

value of the PA output. This gives higher efficiency. The

low radiative and lossy components of the small-loop

antenna result in a higher Q matching network than the

50Ω network; thus, the harmonics are lower.

Layout Considerations

A properly designed PC board is an essential part of

any RF/microwave circuit. On the power-amplifier output, use controlled-impedance lines and keep them as

short as possible to minimize losses and radiation.

Keeping the traces short reduces parasitic inductance.

Generally, 1in of PC board trace adds about 20nH of

parasitic inductance. Parasitic inductance can have a

dramatic effect on the effective inductance. For example, a 0.5in trace connecting a 100nH inductor adds an

extra 10nH of inductance, or 10%.

To reduce the parasitic inductance, use wider traces

and a solid ground or power plane below the signal

traces. Using a solid ground plane can reduce the parasitic inductance from approximately 20nH/in to 7nH/in.

Also, use low-inductance connections to ground on all

GND pins and place decoupling capacitors close to all

VDDconnections.

Chip Information

TRANSISTOR COUNT: 2369

PROCESS: CMOS

COMPONENT

VALUE FOR

f

RF

= 433MHz

VALUE FOR

fRF = 315MHz

L1 22nH 27nH

L3 18nH 22nH

C1 6.8pF 15pF

C2 10pF 22pF

C3 10nF 10nF

C4 680pF 680pF

C6 6.8pF 15pF

C8 220pF 220pF

C10 10nF 10nF

C11 220pF 220pF

C12 220pF 220pF

C14 100pF 100pF

C15 100pF 100pF

Table 3. Component Values for Typical

Application Circuit

Page 9

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

_______________________________________________________________________________________ 9

MAX1479

ENABLE

DIN

MODE

V

DD

C10 C11

C15

C3

C8

C12 C4

L1

L3

C1

C2 C6

C14

V

CC

CLKOUT

V

DD_

PA

ROUT

PAOUT

CLK0

CLK1

DEV0

DEV1

DEV2

XTAL1

XTAL2

GND

CLOCK

OUTPUT

V

CC

RF

OUTPUT

CLOCKDIVIDER

INPUTS

FREQUENCYDEVIATION

INPUTS

MODE-SELECT

INPUT

DATA INPUT

ENABLE INPUT

CRYSTAL

DRIVER

4

3

2

1

5 6 7 8

9

10

11

12

13141516

CLOCK

DIVIDER

DIVIDE

BY 32

LOOP

FILTER

ASK

FSK

PA

ENVELOPE

SHAPING

DEVIATION

PD/CP

VCO

Typical Application Circuit

Page 10

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

10 ______________________________________________________________________________________

Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,

go to www.maxim-ic.com/packages

.)

12x16L QFN THIN.EPS

0.10 C 0.08 C

0.10 M C A B

D

D/2

E/2

E

A1

A2

A

E2

E2/2

L

k

e

(ND - 1) X e

(NE - 1) X e

D2

D2/2

b

L

e

L

C

L

e

C

L

L

C

L

C

E

1

2

21-0136

PACKAGE OUTLINE

12, 16L, THIN QFN, 3x3x0.8mm

Page 11

MAX1479

300MHz to 450MHz Low-Power,

Crystal-Based +10dBm ASK/FSK Transmitter

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________ 11

© 2004 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,

go to www.maxim-ic.com/packages

.)

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

EXPOSED PAD VARIATIONS

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED

WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE.

5. DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.20 mm AND 0.25 mm

FROM TERMINAL TIP.

6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

8. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220 REVISION C.

NOTES:

E

2

2

21-0136

PACKAGE OUTLINE

12, 16L, THIN QFN, 3x3x0.8mm

DOWN

BONDS

ALLOWED

Loading...

Loading...