Page 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

General Description

The MAX1385/MAX1386 set and control bias conditions

for dual RF LDMOS power devices found in cellular

base stations. Each device includes a high-side current-sense amplifier with programmable gains of 2, 10,

and 25 to monitor LDMOS drain current over the 20mA

to 5A range. Two external diode-connected transistors

monitor LDMOS temperatures while an internal temperature sensor measures the local die temperature of the

MAX1385/MAX1386. A 12-bit ADC converts the programmable-gain amplifier (PGA) outputs, external/internal temperature readings, and two auxiliary inputs.

The two gate-drive channels, each consisting of 8-bit

coarse and 10-bit fine DACs and a gate-drive amplifier,

generate a positive gate voltage to bias the LDMOS

devices. The MAX1385 includes a gate-drive amplifier

with a gain of 2 and the MAX1386 gate-drive amplifier

provides a gain of 4. The 8-bit coarse and 10-bit fine

DACs allow up to 18 bits of resolution. The MAX1385/

MAX1386 include autocalibration features to minimize

error over time, temperature, and supply voltage.

The MAX1385/MAX1386 feature an I2C/SPI™-compatible

serial interface. Both devices operate from a 4.75V to

5.25V analog supply (3.2mA supply current), a 2.7V to

5.25V digital supply (3.1mA supply current), and a 4.75V

to 11.0V gate-drive supply (4.5mA supply current). The

MAX1385/MAX1386 are available in a 48-pin thin QFN

package.

Applications

RF LDMOS Bias Control in Cellular Base Stations

Industrial Process Control

Features

♦ Integrated High-Side Drain Current-Sense PGA

with Gain of 2, 10, or 25

♦ ±0.5% Accuracy for Sense Voltage Between 75mV

and 250mV

♦ Full-Scale Sense Voltage of 100mV with Gain of 25

♦ Full-Scale Sense Voltage of 250mV with Gain of 10

♦ Common-Mode Range of 5V to 30V Drain Voltage

for LDMOS

♦ Adjustable Low Noise 0 to 5V, 0 to 10V Output

Gate-Bias Voltage Ranges with ±10mA Gate Drive

♦ Fast Clamp to 0V for LDMOS Protection

♦ 8-Bit DAC Control of Gate-Bias Voltage

♦ 10-Bit DAC Control of Gate-Bias Offset with

Temperature

♦ Internal Die Temperature Measurement

♦ External Temperature Measurement by Diode-

Connected Transistor (2N3904)

♦ Internal 12-Bit ADC Measurement of Temperature,

Current, and Voltages

♦ Selectable I

2

C-/SPI-Compatible Serial Interface

400kHz/1.7MHz/3.4MHz I

2

C-Compatible Control

for Settings and Data Measurement

16MHz SPI-Compatible Control for Settings

and Data Measurement

♦ Internal 2.5V Reference

♦ Three Address Inputs to Control Eight Devices in

I

2

C Mode

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

________________________________________________________________

Maxim Integrated Products

1

19-4456; Rev 0; 2/09

EVALUATION KIT

AVAILABLE

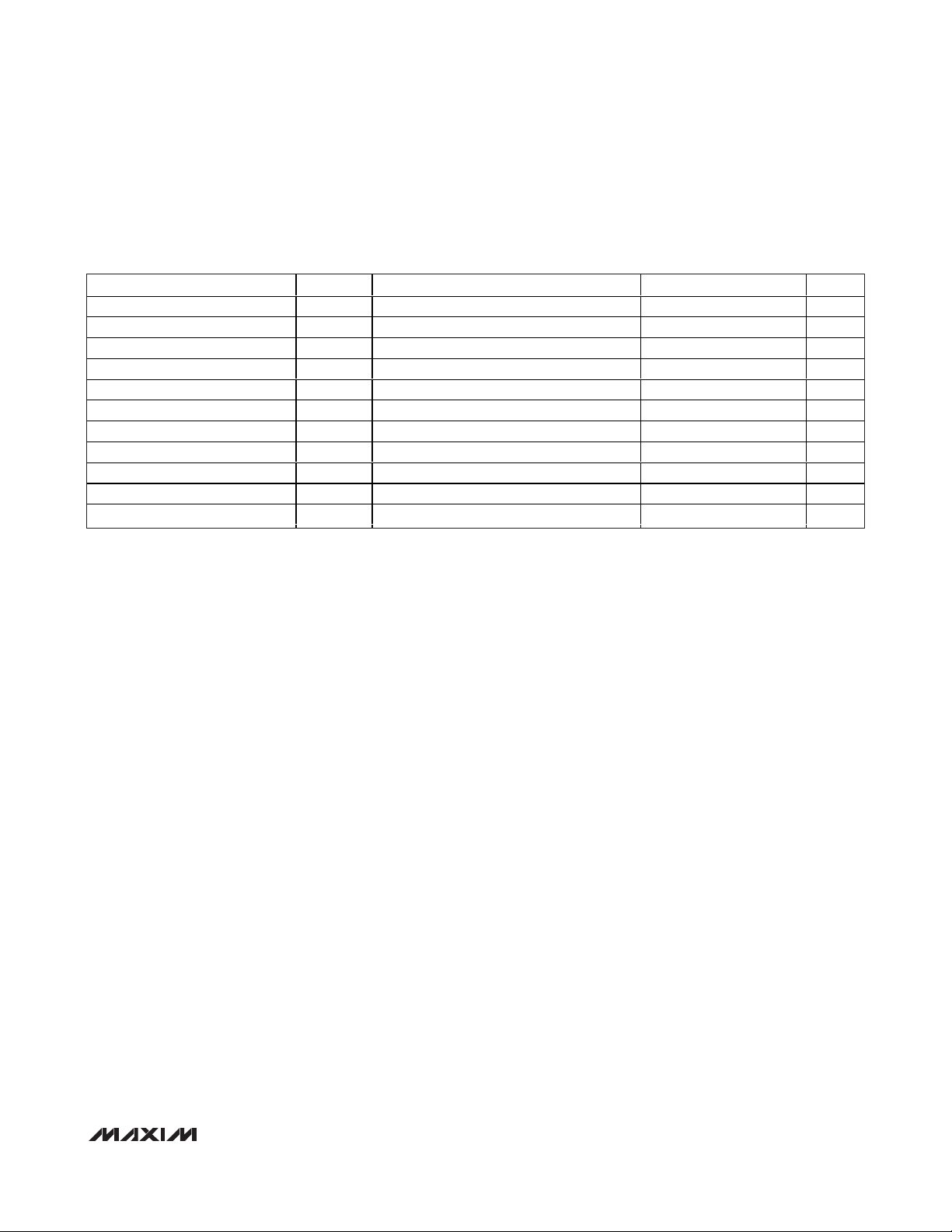

Ordering Information/Selector Guide

SPI is a trademark of Motorola, Inc.

*

EP = Exposed pad.

**

Future product—contact factory for availability.

+

Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration and Typical Operating Circuit (I

2

C Mode)

appear at end of data sheet.

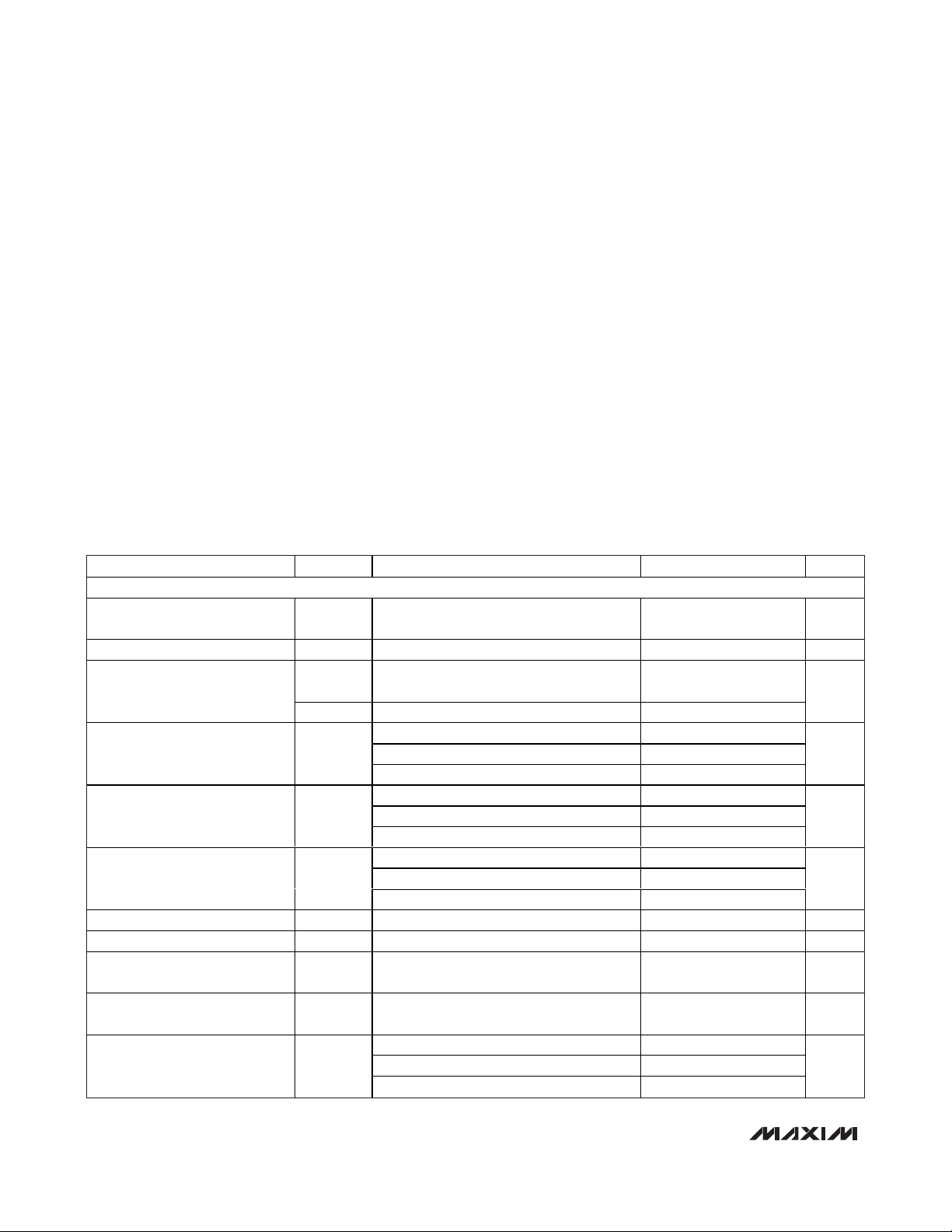

PART TEMP RANGE PIN-PACKAGE TEMP ERROR (°C) V

MAX1385AETM+** -40°C to +85°C 48 Thin QFN-EP* ±1 5

MAX1385BETM+ -40°C to +85°C 48 Thin QFN-EP* ±2 5

MAX1386AETM+** -40°C to +85°C 48 Thin QFN-EP* ±1 10

MAX1386BETM+** -40°C to +85°C 48 Thin QFN-EP* ±2 10

GATE

(V)

Page 2

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

AVDDto AGND .........................................................-0.3V to +6V

DV

DD

to DGND.........................................................-0.3V to +6V

AGND to DGND.....................................................-0.3V to +0.3V

CS1+, CS1-, CS2+, CS2- to GATEGND.................-0.3V to +32V

CS1- to CS1+, CS2- to CS2+ ...................................-6V to +0.3V

GATEV

DD

to GATEGND .........................................-0.3V to +12V

GATE1, GATE2 to GATEGND...........-0.3V to (GATEV

DD

+ 0.3V)

SAFE1, SAFE2 to GATEGND....................................-0.3V to +6V

GATEGND to AGND..............................................-0.3V to +0.3V

All Other Analog Inputs

to AGND ............-0.3V to the lower of +6V and (AV

DD

+ 0.3V)

Digital Inputs

to DGND ............-0.3V to the lower of +6V and (DV

DD

+ 0.3V)

SDA/DIN, SCL to DGND...........................................-0.3V to +6V

Digital Outputs to DGND .........................-0.3V to (DV

DD

+ 0.3V)

Maximum Continuous Current into Any Pin ........................50mA

Continuous Power Dissipation (T

A

= +70°C)

48-Pin, 7mm x 7mm, Thin QFN (derate 27.8 mW/°C

above +70°C).............................................................2222mW

Maximum Junction Temperature .....................................+150°C

Operating Temperature Range ...........................-40°C to +85°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

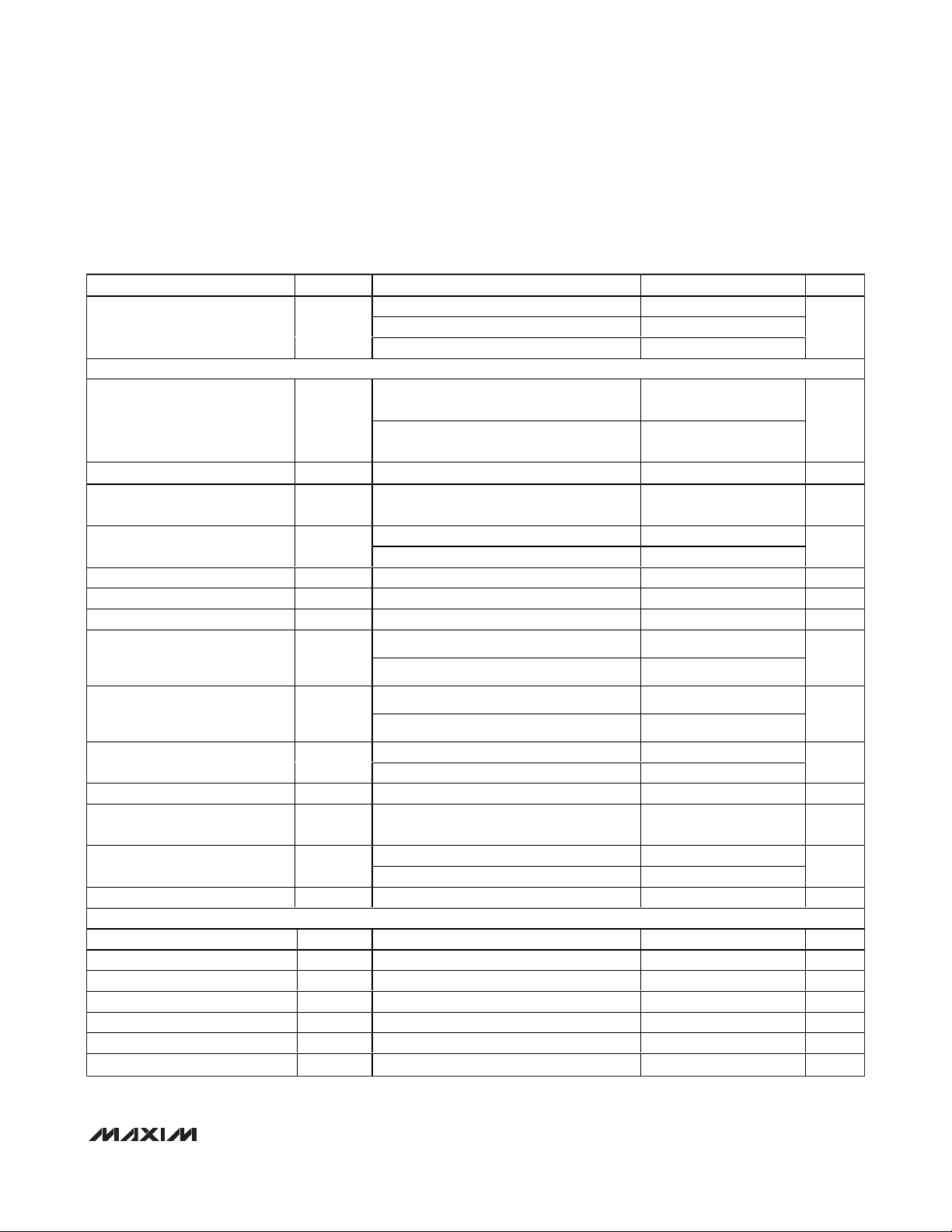

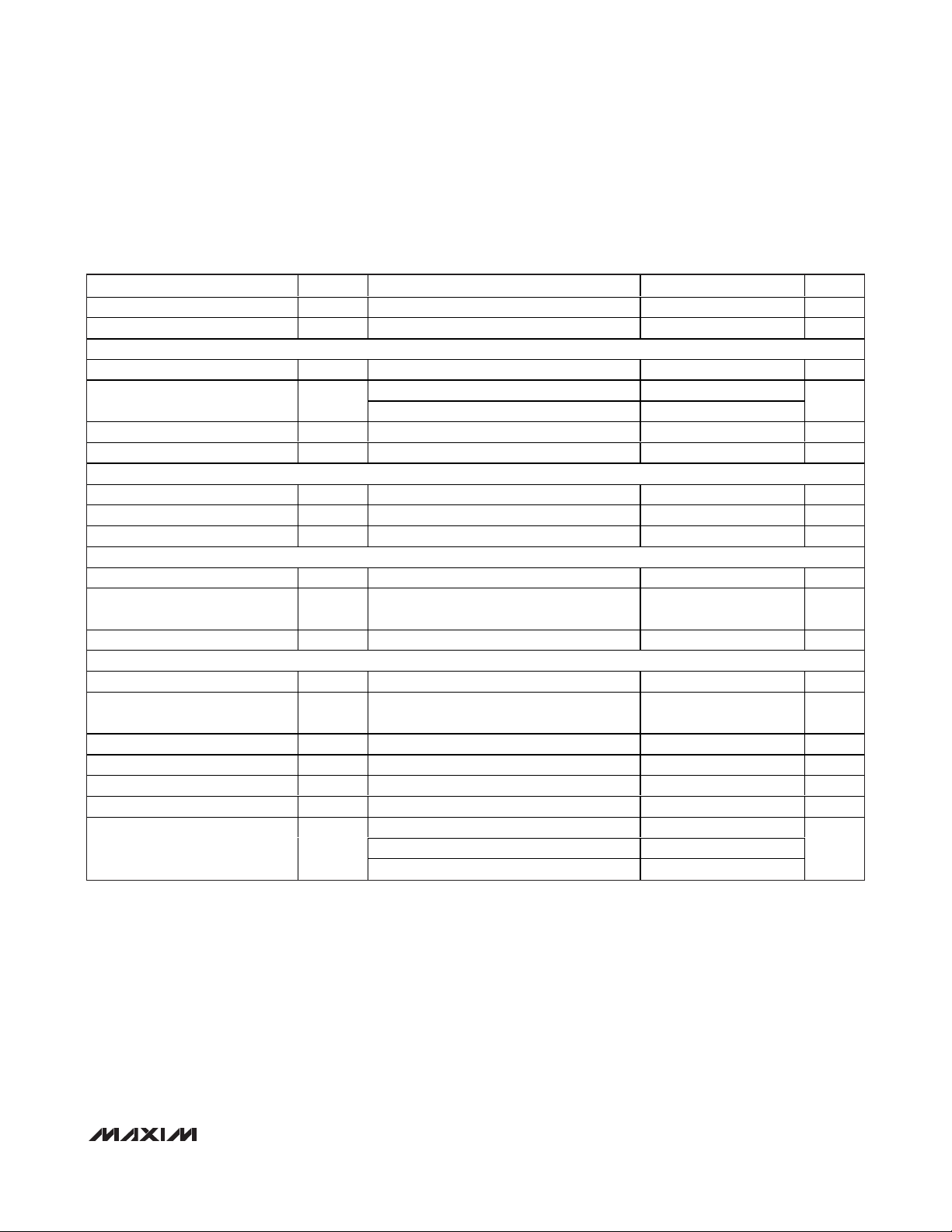

ELECTRICAL CHARACTERISTICS

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external V

REF-

DAC

= +2.5V, C

REF

= 0.1µF, unless otherwise noted. TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

HIGH-SIDE CURRENT SENSE WITH PGA

Common-Mode Input Voltage

Range

Common-Mode Rejection Ratio CMRR 11V < V

Input-Bias Current

Sense Voltage Range for

Accuracy of ±0.5% V

Sense Voltage Range for

Accuracy of ±2% V

Total PGAOUT Voltage Error V

PGAOUT Capacitive Load C

PGAOUT Settling Time t

Saturation Recovery Time

Sense-Amplifier Slew Rate

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

, V

V

CS+

CS-

V

SENSE

range

PGA gain = 25 0 100

=

PGA gain = 10 0 250Full-Scale Sense Voltage Range

PGA gain = 2 0 1250

PGA gain = 25 75 100

PGA gain = 10 75 250

PGA gain = 2 75 1250

PGA gain = 25 20 100

PGA gain = 10 20 250

PGA gain = 2 20 1250

SENSE

Settles to within ±0.5% of final value, RS =

50Ω, C

Settles to within ±0.5% accuracy; from

V

SENSE

Av

Av

Av

SENSE

SENSE

I

CS+

I

CS-

V

SENSE

VCS_+ -

VCS_-

PGAOUT

HSCS

CS+

< 100mV over the common-mode

= 75mV ±0.1 ±0.5 %

GATE

= 3 x full scale

= 2 0.5

PGA

= 10 2

PGA

= 25 2

PGA

< 30V 90 dB

= 15pF

530V

120 195

0.002 ±2

< 25 µs

< 45 µs

100 pF

µA

mV

mV

mV

V/µs

Page 3

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

_______________________________________________________________________________________ 3

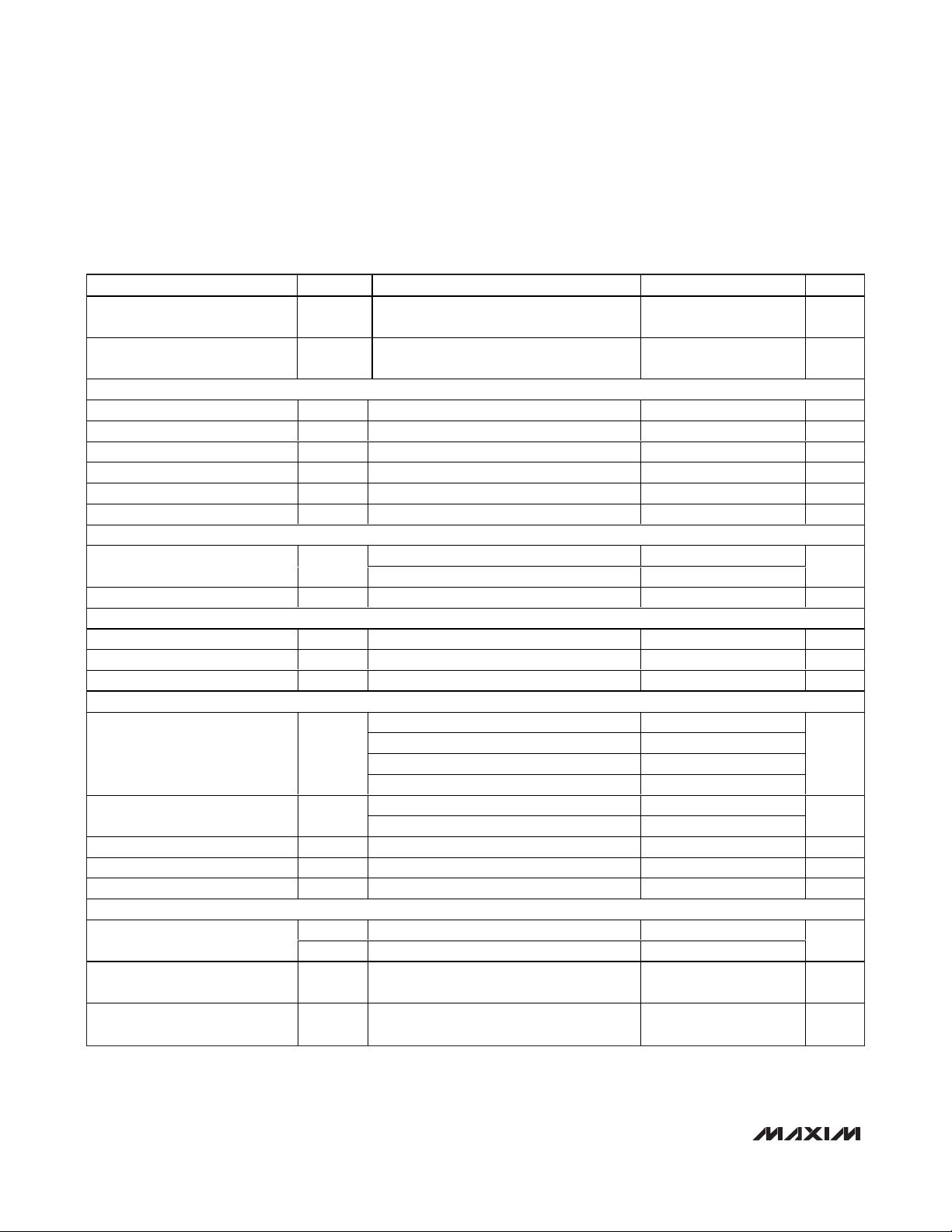

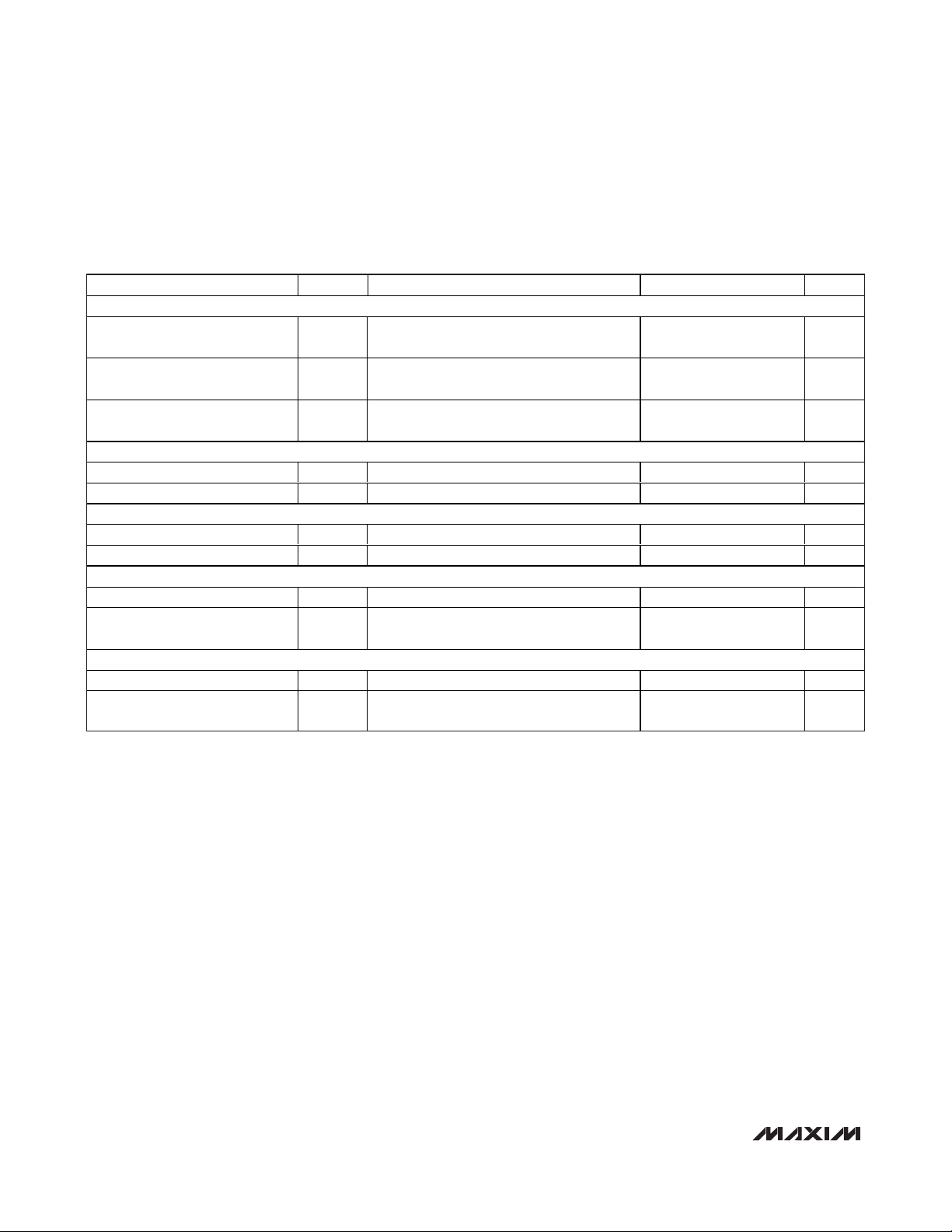

ELECTRICAL CHARACTERISTICS (continued)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external V

REF-

DAC

= +2.5V, C

REF

= 0.1µF, unless otherwise noted. TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

Sense-Amplifier Bandwidth

LDMOS GATE DRIVER (GAIN = 2 and 4)

Output Gate-Drive Voltage Range V

Output Impedance R

V

Settling Time t

GATE

Output Capacitive Load (Note 1) C

Noise RMS noise; 1kHz - 1MHz 250 nV/√Hz

V

GATE

Maximum Power-On Transient ±100 mV

Output Short-Circuit Current Limit I

Total Unadjusted Error

No Autocalibration and Offset

Removal (Note 2)

Total Adjusted Error

With Autocalibration and Offset

Removal

Drift

Clamp to Zero Delay 1µs

Output Safe Switch OnResistance

Amplifier Bandwidth

Amplifier Slew Rate 0.375 V/µs

MONITOR ADC DC ACCURACY

Resolution N

Differential Nonlinearity DNL

Integral Nonlinearity INL

Offset Error ±2 ±4 LSB

Gain Error (Note 5) ±2 ±4 LSB

Gain Temperature Coefficient ±0.4 ppm/°C

Offset Temperature Coefficient ±0.4 ppm/°C

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Av

= 2 900

PGA

Av

= 10 720

PGA

= 25 290

Av

PGA

I

= ±1mA 0.75

GATE

GATE

I

= ±10mA 1

GATE

GATE

GATE

GATE

TUE

TUE

R

OPSW

SC

ADC

Measured at DC 0.1 Ω

Settles to within ±0.5% of final value;

R

= 50Ω, C

SERIES

No series resistance, R

R

= 50Ω 0 25,000

SERIES

1s, sinking or sourcing ±25 mA

MAX1385, LOCODE = 128, HICODE = 180 ±6 ±20

MAX1386, LOCODE = 128, HICODE = 180 ±12 ±40

MAX1385, LOCODE = 128, HICODE = 180 ±1 ±8

MAX1386, LOCODE = 128, HICODE = 180 ±2 ±16

MAX1385, V

MAX1386, V

GATE_ clamped to AGND (Note 3) 500 Ω

MAX1385 300

MAX1386 150

ADC

(Note 4) ±0.6 ±2 LSB

ADC

GATE

GATE

= 15µF

GATE

= 0Ω 010

SERIES

> 1V ±15

> 1V ±30

12 Bits

GATEV

- 0.75

GATEV

- 1

10 ms

±0.5 ±2 LSB

kHz

DD

V

DD

nF

mV

mV

µV/°C

kHz

Page 4

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

4 _______________________________________________________________________________________

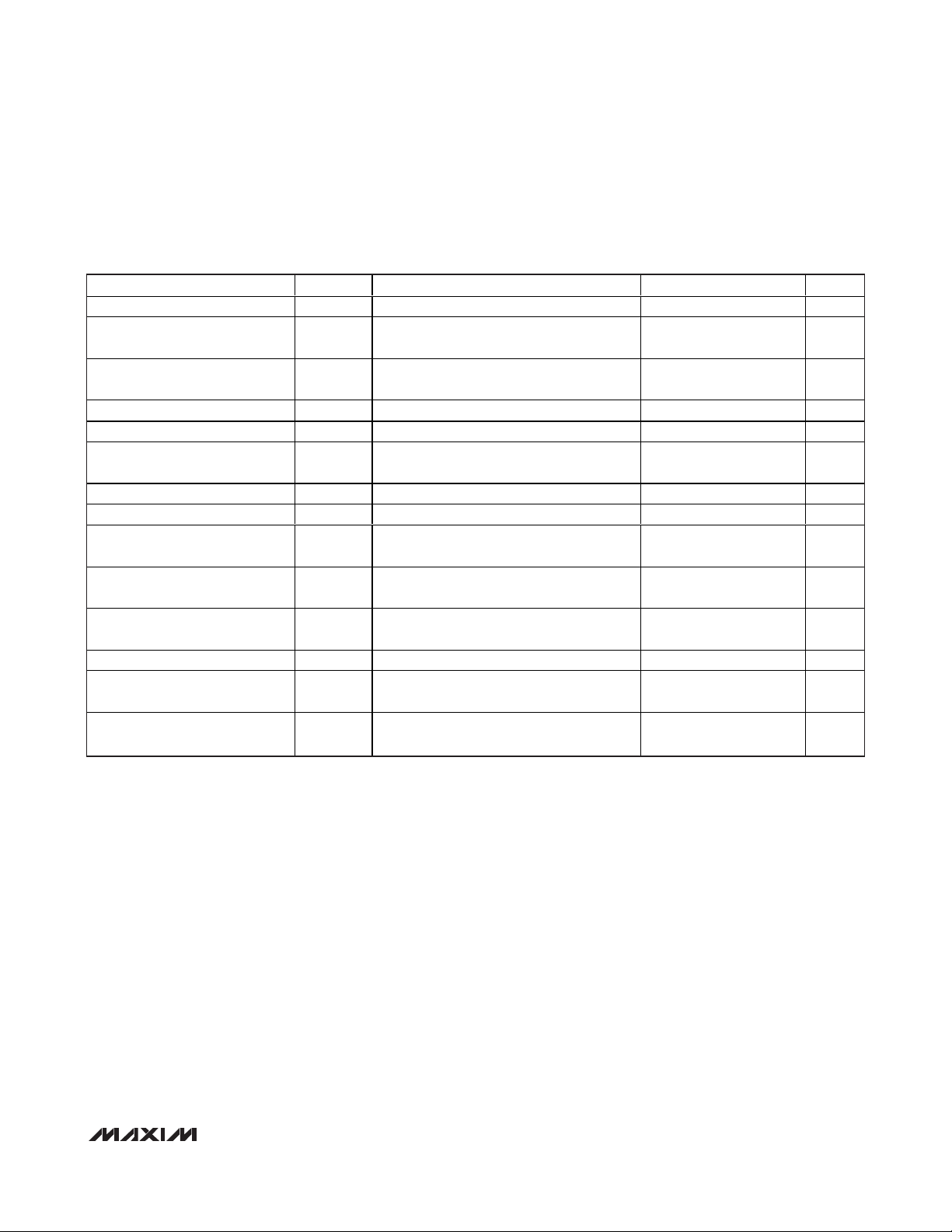

ELECTRICAL CHARACTERISTICS (continued)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external V

REF-

DAC

= +2.5V, C

REF

= 0.1µF, unless otherwise noted. TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

Channel-to-Channel Offset

Matching

Channel-to-Channel Gain

Matching

MONITOR ADC DYNAMIC ACCURACY (1kHz sine-wave input, 2.5V

Signal-to-Noise Plus Distortion SINAD 70 dB

Total Harmonic Distortion THD Up to the 5th harmonic -82 dB

Spurious-Free Dynamic Range SFDR 86 dB

Intermodulation Distortion IMD f

Full-Power Bandwidth -3dB point 10 MHz

Full-Linear Bandwidth S/(N + D) > 68dB 100 kHz

MONITOR ADC CONVERSION RATE

Power-Up Time t

Conversion Time t

MONITOR ADC ANALOG INPUT (ADCIN1, ADCIN2)

Input Range V

Input Leakage Current VIN = 0V and VIN = AV

Input Capacitance C

TEMPERATURE MEASUREMENTS

Internal Sensor Measurement

Error (Note 1)

External Sensor Measurement

Error (Notes 1, 7)

Temperature Resolution 1/8 °C/LSB

External Diode Drive 2.8 85 µA

Drive Current Ratio (Note 8) 16.5

INTERNAL REFERENCE

REFADC/REFDAC Output Voltage

REFADC/REFDAC Output

Temperature Coefficient

REFADC/REFDAC Output

Impedance

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

, up to 94.4ksps)

P-P

PU

CONV

ADCIN

ADCIN

V

REFADCTA

V

REFDACTA

TC

REFADC

TC

REFDAC

= 0.99kHz, f

IN1

External reference 0.8

Internal reference 70

Internally clocked 7.5 10 µs

Relative to AGND (Note 6) 0 V

MAX1385A/MAX1386A, TA = +25°C ±0.25

MAX1385A/MAX1386A, TA = T

MAX1385B/MAX1386B, TA = +25°C ±0.25

MAX1385B/MAX1386B, T

TA = +25°C ±0.4

T

= T

A

,

to T

MIN

= +25°C 2.494 2.500 2.506

= +25°C 2.494 2.500 2.506

= 1.02kHz 76 dB

IN2

DD

MAX

A

= T

MIN

MIN

to T

to T

MAX

MAX

-1.0 ±0.25 +1.0

-2.0 ±0.35 +2.0

-3 ±0.75 +3

±0.1 LSB

±0.1 LSB

REF

±0.01 ±1 µA

34 pF

±14 ppm/°C

6.5 kΩ

µs

V

°C

°C

V

Page 5

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

_______________________________________________________________________________________ 5

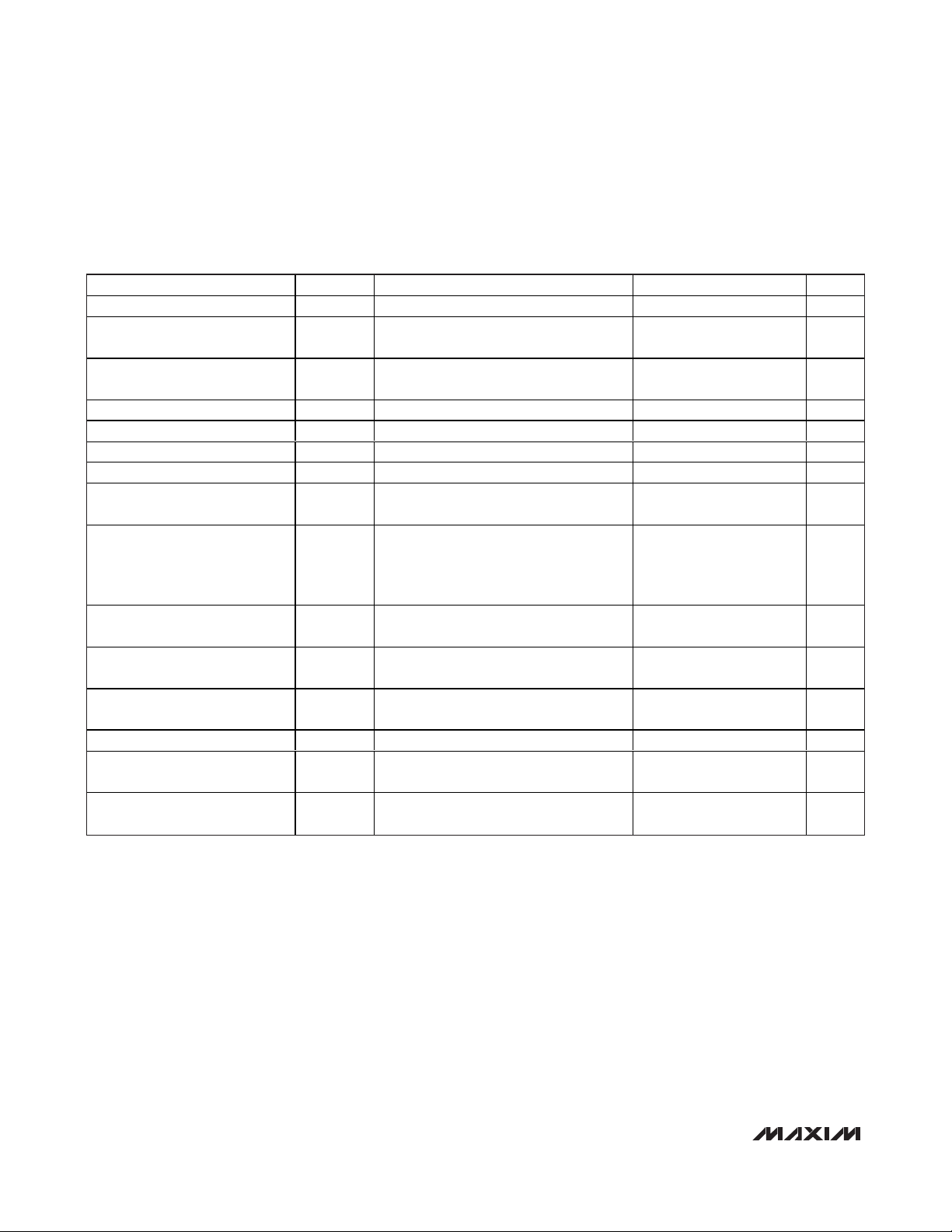

ELECTRICAL CHARACTERISTICS (continued)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external V

REF-

DAC

= +2.5V, C

REF

= 0.1µF, unless otherwise noted. TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

Capacitive Bypass at REF 270 nF

Power-Supply Rejection Ratio PSRR AVDD = +5V ±5% 70 dB

EXTERNAL REFERENCE

REFADC Input Voltage Range V

REFADC Input Current I

REFDAC Input Voltage Range V

REFDAC Input Current Static current when no DAC calibration 0.1 µA

GATE-DRIVER COARSE-DAC DC ACCURACY

Resolution N

Integral Nonlinearity INL

Differential Nonlinearity DNL

GATE-DRIVER FINE-DAC DC ACCURACY

Resolution N

Integral Nonlinearity INL

Differential Nonlinearity DNL

POWER SUPPLIES (Note 10)

Analog Supply Voltage AV

Digital Supply Voltage DV

Gate-Drive Supply Voltage V

Analog Supply Current I

Digital Supply Current I

GATEVDD Supply Current I

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

REFADC

REFADC

REFDAC

CDAC

CDAC

FDAC

GATEVDD

AVDD

DVDD

GATEVDD

Limited code test 1.0 AV

V

= 2.5V, f

REF

Acquisition/between conversions ±0.01 ±1

(Note 9) 0.5 2.5 V

Measured at GATE; fine DAC set at full scale ±0.15 ±1 LSB

Guaranteed monotonic ±0.05 ±0.5 LSB

CDAC

Measured at GATE; coarse DAC set at full

FDAC

scale

Guaranteed monotonic ±0.1 ±1 LSB

FDAC

DD

DD

AVDD = 5V 3.2 4 mA

DVDD = 2.7V to 5.25V 3.1 4.3 mA

I

AVDD

I

PD

DVDD

I

VDDGATE

= 174ksps 60 80

SAMPLE

8 Bits

10 Bits

4.75 5.25 V

2.7

4.75 11.00 V

3 4.5 7 mA

DD

±0.25 ±4 LSB

AV

DD

+ 0.3

0.1 2

0.1 2Shutdown Current (Note 11) I

0.1 2

V

µA

V

µA

Page 6

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

6 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external V

REF-

DAC

= +2.5V, C

REF

= 0.1µF, unless otherwise noted. TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

VIH AND VIL FOR SDA/DIN AND SCL IN I2C OPERATION ONLY

Input High Voltage V

Input Low Voltage V

Input Hysteresis V

VIH AND VIL FOR OPSAFE1 AND OPSAFE2

Input High Voltage V

Input Low Voltage V

VIH AND VIL FOR ALL OTHER DIGITAL INPUTS

Input High Voltage V

Input Low Voltage V

VOH AND VOL FOR A1/DOUT (SPI), SDA/DIN, ALARM

Output Low Voltage V

Output High Voltage V

VOH AND VOL FOR SAFE1, SAFE2, BUSY

Output Low Voltage V

Output High Voltage V

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

IH

IL

HYS

IH

IL

IH

IL

I

OL

OH

OL

OH

= 3mA 0.4 V

SINK

I

SOURCE

I

SINK

I

SOURCE

= 2mA

= 0.5mA 0.4 V

= 0.5mA

0.7 x

DV

DD

0.3 x

DV

DD

0.1 x

DV

DD

2.4 V

0.4 V

2.2 V

0.7 V

DV

DD

- 0.5

DV

DD

- 0.5

V

V

V

V

V

Page 7

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

_______________________________________________________________________________________ 7

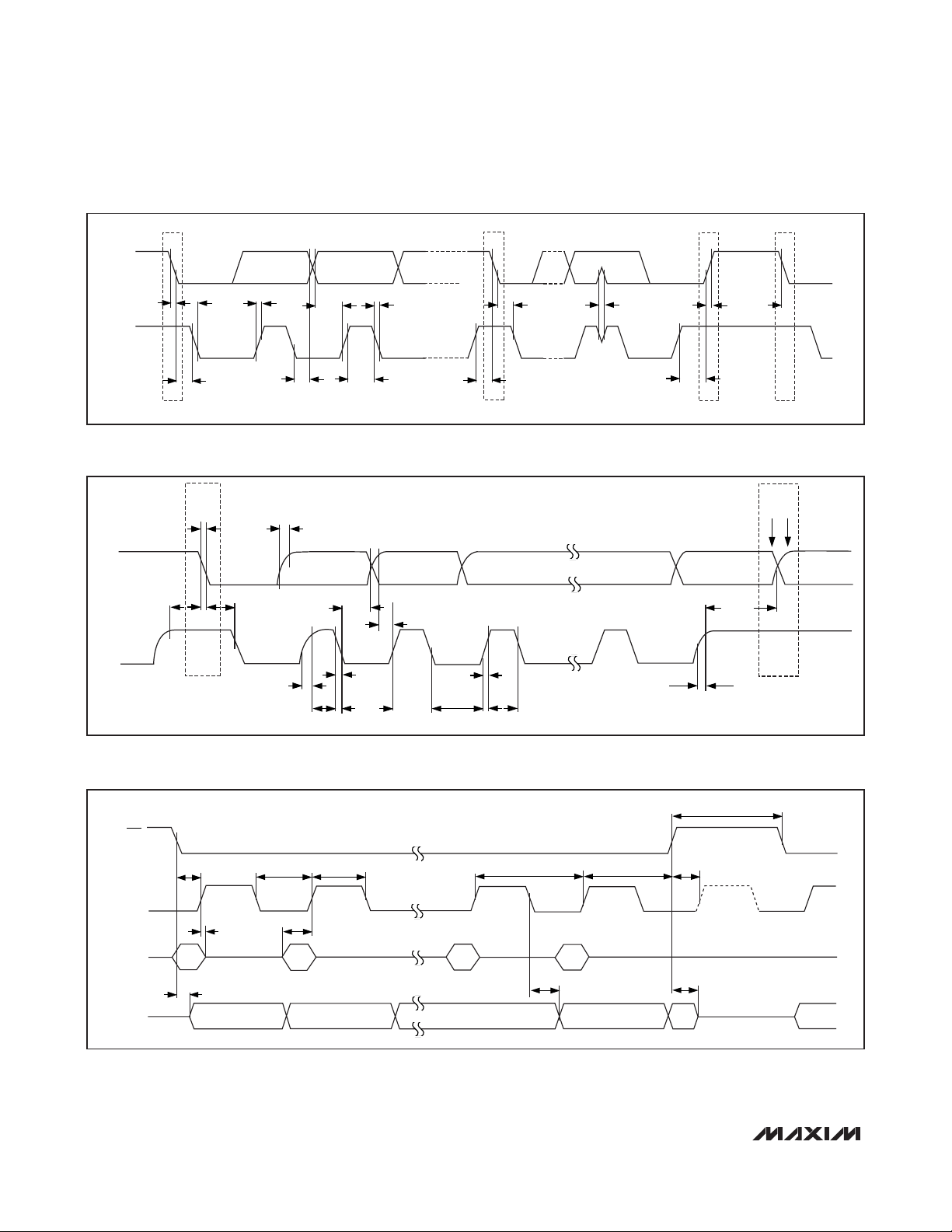

I2C SLOW-/FAST-MODE TIMING CHARACTERISTICS (Note 12, see Figure 1)

(GATEVDD= +5.5V for MAX1385, GATEVDD= +11V for MAX1386, AVDD= +5V, DVDD= 2.7V to 5.25V, external V

REFADC

= +2.5V,

external V

REFDAC

= +2.5V, C

REF

= 0.1µF, TA= -40°C to +85°C, unless otherwise noted).

Serial-Clock Frequency f

Bus Free Time Between STOP

and START Condition

Hold Time Repeated START

Condition

SCL Pulse-Width Low t

SCL Pulse-Width High t

Setup Time Repeated START

Condition

Data Hold Time t

Data Setup Time t

Rise Time of Both SDA and SCL

Signals, Receiving

Fall Time of Both SDA and SCL

Signals, Receiving

Fall Time of SDA Signal,

Transmitting

Setup Time for STOP Condition t

Capacitive Load for Each Bus

Line

Pulse Width of Spikes

Suppressed by the Input Filter

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SCL

t

BUF

t

HD;STA

LOW

HIGH

t

SU;STA

HD;DAT

SU;DAT

t

t

t

SU;STO

C

t

SP

After this period, the first clock pulse is

generated

(Note 13) 0 0.9 µs

(Note 14) 0 300 ns

R

(Note 14) 0 300 ns

F

(Notes 14, 15)

F

b

(Note 16) 0 50 ns

0 400 kHz

1.3 µs

0.6 µs

1.3 µs

0.6 µs

0.6 µs

100 ns

20 +

0.1C

b

0.6 µs

250 ns

400 pF

Page 8

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

8 _______________________________________________________________________________________

I2C HIGH-SPEED-MODE TIMING CHARACTERISTICS (Note 12, see Figure 2)

(GATEVDD= +5.5V for MAX1385, GATEVDD= +11V for MAX1386, AVDD= +5V, DVDD= 2.7V to 5.25V, external V

REFADC

= +2.5V,

external V

REFDAC

= +2.5V, C

REF

= 0.1µF, TA= -40°C to +85°C, unless otherwise noted).

Serial-Clock Frequency f

Setup Time Repeated START

Condition

Hold Time Repeated START

Condition

SCL Pulse-Width Low t

SCL Pulse-Width High t

Data Setup Time t

Data Hold Time t

Rise Time of SCL Signal,

Receiving

Rise Time of SCL Signal After a

Repeated START Condition and

After an Acknowledge Bit,

Receiving

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SCL

t

SU;STA

t

HD;STA

LOW

HIGH

SU;DAT

HD;DAT

t

RCL

t

RCL1

(Note 17) 0 70 ns

0 3.4 MHz

160 ns

160 ns

160 ns

60 ns

10 ns

10 40 ns

10 80 ns

Fall Time of SCL Signal,

Receiving

Rise Time of SDA Signal,

Receiving

Fall Time of SDA Signal,

Transmitting

Setup Time for STOP Condition t

Capacitive Load for Each Bus

Line

Pulse Width of Spikes That are

Suppressed by the Input Filter

t

FCL

t

RDA

t

FDA

SU;STO

C

b

t

SP

10 40 ns

10 80 ns

10 80 ns

160 ns

(Note 18) 100 pF

010ns

Page 9

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

_______________________________________________________________________________________ 9

Note 1: Guaranteed by design.

Note 2: Total unadjusted errors are for the entire gain drive channel including the 8- and 10-bit DACs and the gate driver. They are

all measured at the GATE1 and GATE2 outputs. Offset removal refers to presetting the drain current after a room temperature calibration by the user. This effectively removes the channel offset.

Note 3: During power-on reset, the output safe switch is closed. The output safe switch opens once both AV

DD

and DVDDsupply

voltages are established.

Note 4: Integral nonlinearity is the deviation of the analog value at any code from its theoretical value after the gain and offset errors

have been removed.

Note 5: Offset nulled.

Note 6: Absolute range for analog inputs is from 0 to AV

DD

.

Note 7: The MAX1385/MAX1386 and external sensor are at the same temperature. External sensor measurement error is tested with

a diode-connected 2N3904.

Note 8: The drive current ratio is defined as the large drive current divided by the small drive current in a temperature measure-

ment. See the

Temperature Measurements

section for further details.

Note 9: Guaranteed monotonicity. Accuracy might be degraded at lower V

REFDAC

.

Note 10: Supply current limits are valid only when digital inputs are at DV

DD

or DGND. Timing specifications are only guaranteed

when inputs are driven rail-to-rail.

Note 11: Shutdown supply currents are typically 0.1µA. Maximum specification is limited by automated test equipment.

Note 12: All timing specifications referred to V

IH

or VILlevels.

Note 13: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V

IL

of SCL) to bridge the unde-

fined region of SCL’s falling edge.

Note 14: C

b

= total capacitance of one bus line in pF; tRand tFare measured between 0.3 x DVDDand 0.7 x DVDD.

Note 15: For a device operating in an I

2

C-compatible system.

Note 16: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

Note 17: A device must provide a data hold time to bridge the undefined part between V

IH

and VILof the falling edge of the SCL signal.

An input circuit with a threshold as low as possible for the falling edge of the SCL signal minimizes this hold time.

Note 18: Cb = total capacitance of one bus line in pF. For bus loads between 100pF and 400pF, the timing parameters should be

linearly interpolated.

SPI TIMING CHARACTERISTICS (Note 12, See Figure 3)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= +5V, DVDD= 2.7V to 5.25V, external V

REFADC

=

+2.5V, external V

REFDAC

= +2.5V, C

REF

= 0.1µF, TA= -40°C to +85°C, unless otherwise noted.)

SCL Clock Period t

SCL High Time t

SCL Low Time t

DIN Setup Time t

DIN Hold Time t

SCL Fall to DOUT Transition t

CSB Fall to DOUT Enable t

CSB Rise to DOUT Disable t

CSB Rise or Fall to SCL Rise t

CSB Pulse-Width High t

Last Clock Rise to CSB Rise t

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

CP

CH

CL

DS

DH

DO

DV

TR

CSS

CSW

CSH

62.5 ns

25 ns

25 ns

10 ns

0ns

C

= 30pF 20 ns

LOAD

C

= 30pF 40 ns

LOAD

C

= 30pF (Note 12) 100 ns

LOAD

25 ns

100 ns

50 ns

Page 10

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

10 ______________________________________________________________________________________

Figure 1. I2C Slow-/Fast-Mode Timing Diagram

Figure 2. I2C High-Speed-Mode Timing Diagram

Figure 3. SPI Timing Diagram

SDA

t

t

R

t

HD;DAT

SU;DAT

t

HIGH

t

F

t

SU;STA

t

HD;STA

S

r

SCL

t

F

S

t

LOW

t

HD;STA

t

SP

t

SU;STO

t

r

t

BUF

P

S

Sr

t

t

FDA

RDA

SDA

t

SU;STA

t

HD;STA

t

HD;DAT

SCL

t

HIGH

t

FCL

t

LOW

t

RCL1

CSB

SCL

t

CSS

t

DH

t

CL

t

CH

t

DS

t

SU;DAT

t

LOW

t

RCL

t

HIGH

Sr

P

t

SU;STO

t

RCL1

t

CSW

t

t

CP

t

CSH

CSS

DIN

DOUT

D23

t

DV

D22

D1

D0

t

DO

D0D1

t

TR

Page 11

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 11

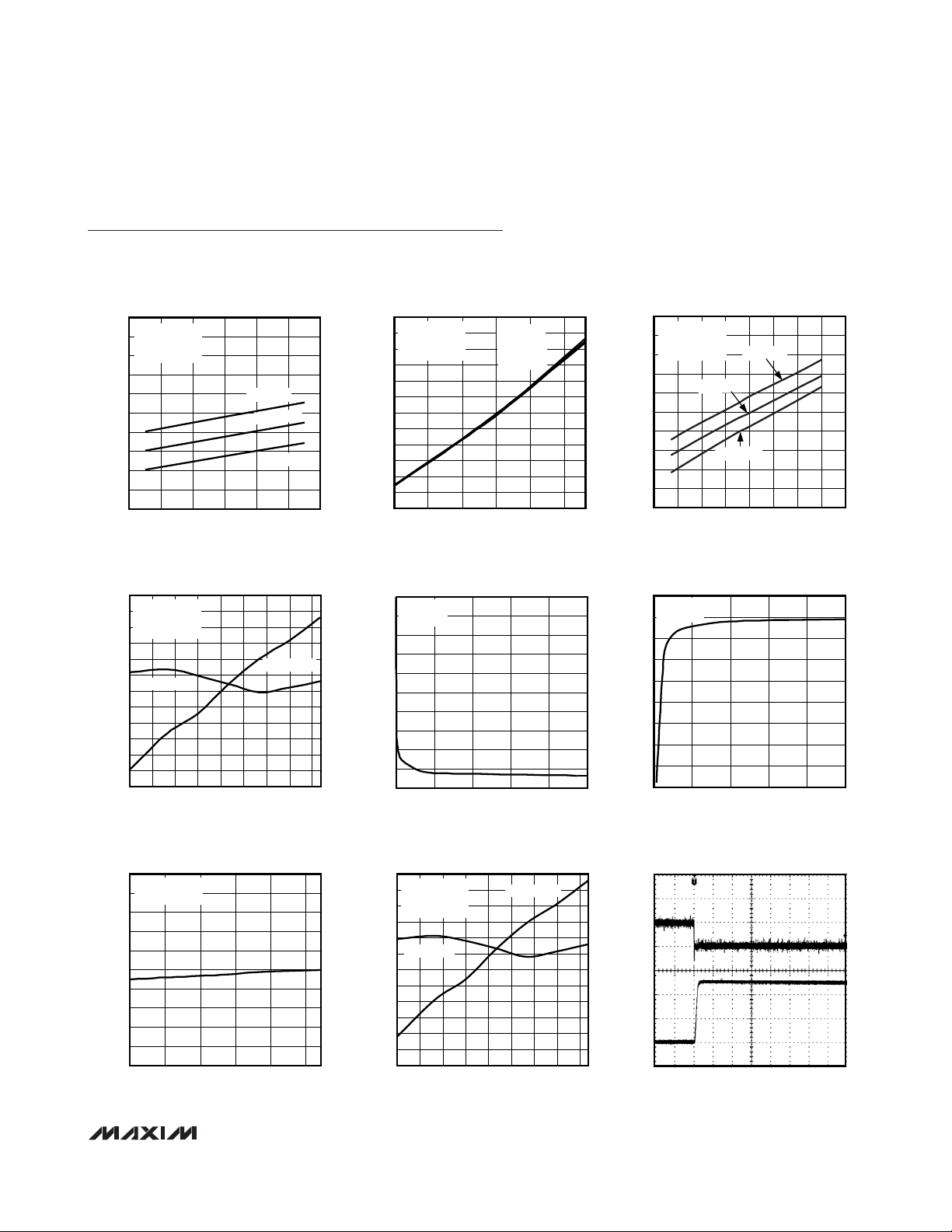

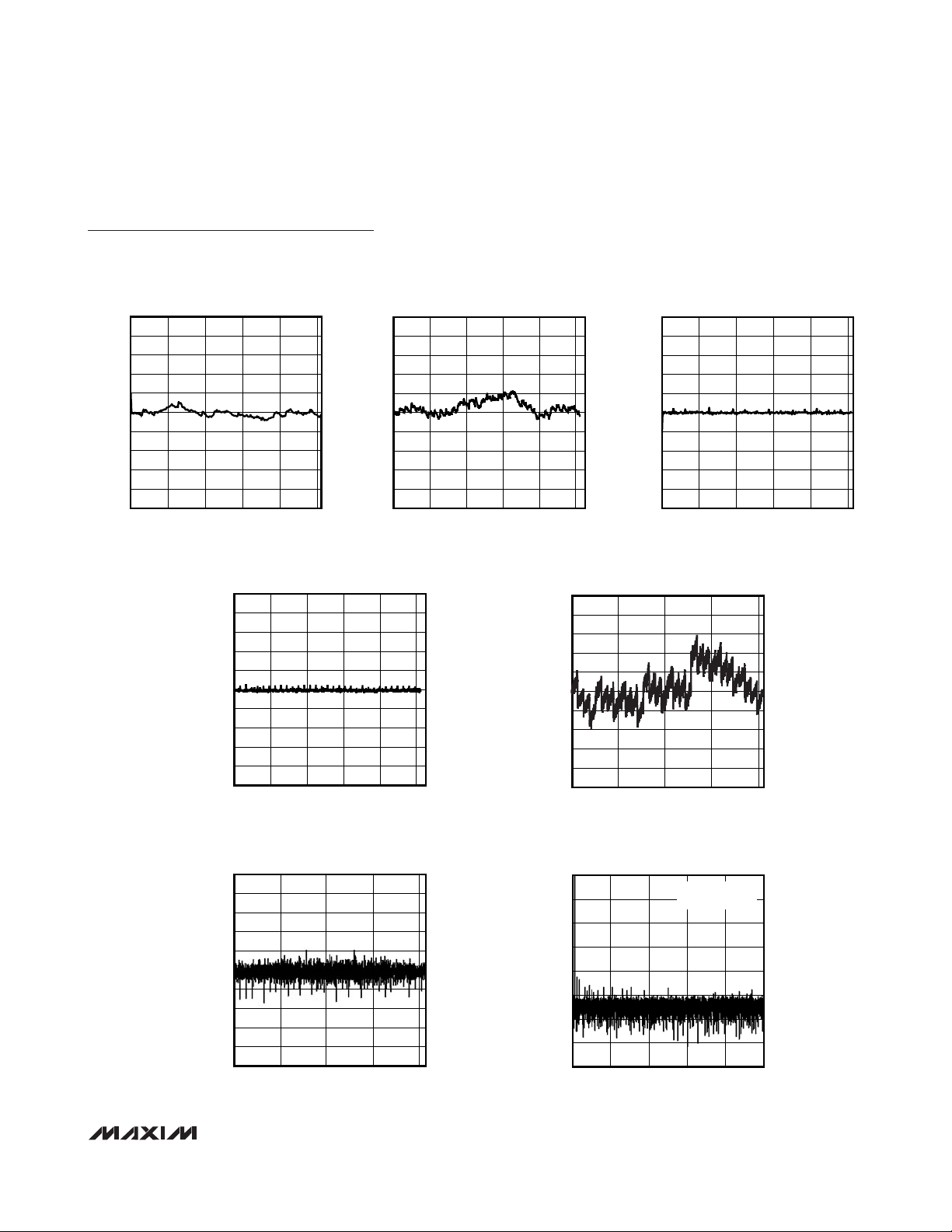

Typical Operating Characteristics

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external

V

REFDAC

= +2.5V, C

REF

= 0.1µF, TA= +25°C, unless otherwise noted.)

3.0

3.3

3.2

3.1

3.4

3.5

3.6

3.7

3.8

3.9

4.0

4.7 4.94.8 5.0 5.1 5.2 5.3

AVDD SUPPLY CURRENT

vs. AV

DD

VOLTAGE

MAX1385/86 toc01

AVDD (V)

I

AVDD

(mA)

Av

PGA

= 2

CMV = 12V

V

SENSE

= 100mV

TA = +85°C

TA = +25°C

TA = -40°C

DVDD SUPPLY CURRENT vs. DVDD VOLTAGE

MAX1385/86 toc02

DVDD (V)

I

DVDD

(mA)

5.24.74.23.73.2

1.25

1.50

1.75

2.00

2.25

2.50

2.75

3.00

3.25

3.50

3.75

4.00

1.00

2.7

Av

PGA

= 2

CMV = 12V

V

SENSE

= 100mV

TA = +25°C

TA = +85°C

TA = -40°C

GATEVDD SUPPLY CURRENT

vs. GATEV

DD

VOLTAGE

MAX1385/86 toc03

GATEVDD (V)

I

GATEVDD

(mA)

11108 96 75

4.1

4.2

4.3

4.4

4.5

4.6

4.7

4.8

4.9

5.0

4.0

412

Av

PGA

= 2

CMV = 12V

V

SENSE

= 100mV

TA = +85°C

TA = +25°C

TA = -40°C

TOTAL PGAOUT_ ERROR

vs. TEMPERATURE

MAX1385/86 toc04

TEMPERATURE (°C)

PGAOUT_ ERROR (%)

806535 50-10 5 20-25

-0.125

-0.100

-0.075

-0.050

-0.025

0

0.025

0.050

0.075

0.100

0.125

0.150

-0.150

-40

Av

PGA

= 2

CMV = 12V

V

SENSE

= 100mV

ACQUISITION

TRACKING

TOTAL PGAOUT_ ERROR vs. V

SENSE

MAX1385/86 toc05

V

SENSE

(mV)

PGAOUT_ ERROR (%)

1000750500250

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0.45

0.50

0

0 1250

Av

PGA

= 2

CMV = 12V

TOTAL PGAOUT_ ERROR vs. V

SENSE

MAX1385/86 toc06

V

SENSE

(mV)

PGAOUT_ ERROR (%)

80604020

-3.5

-3.0

-2.5

-2.0

-1.5

-1.0

-0.5

0

0.5

-4.0

0 100

Av

PGA

= 25

CMV = 12V

TOTAL PGAOUT_ ERROR

vs. COMMON-MODE VOLTAGE

MAX1385/86 toc07

COMMON-MODE VOLTAGE (V)

PGAOUT_ ERROR (%)

3025201510

0.01

0.02

0.03

0.04

0.05

0.06

0.07

0.08

0.09

0.10

0

5

Av

PGA

= 2

V

SENSE

= 100mV

PGAOUT_ OFFSET VOLTAGE

vs. TEMPERATURE

MAX1385/86 toc08

TEMPERATURE (°C)

OFFSET VOLTAGE (μV)

806535 50-10 5 20-25

-350

-300

-250

-200

-150

-100

-50

0

50

100

150

200

-400

-40

Av

PGA

= 2

CMV = 12V

V

SENSE

= 100mV

ACQUISITION

TRACKING

V

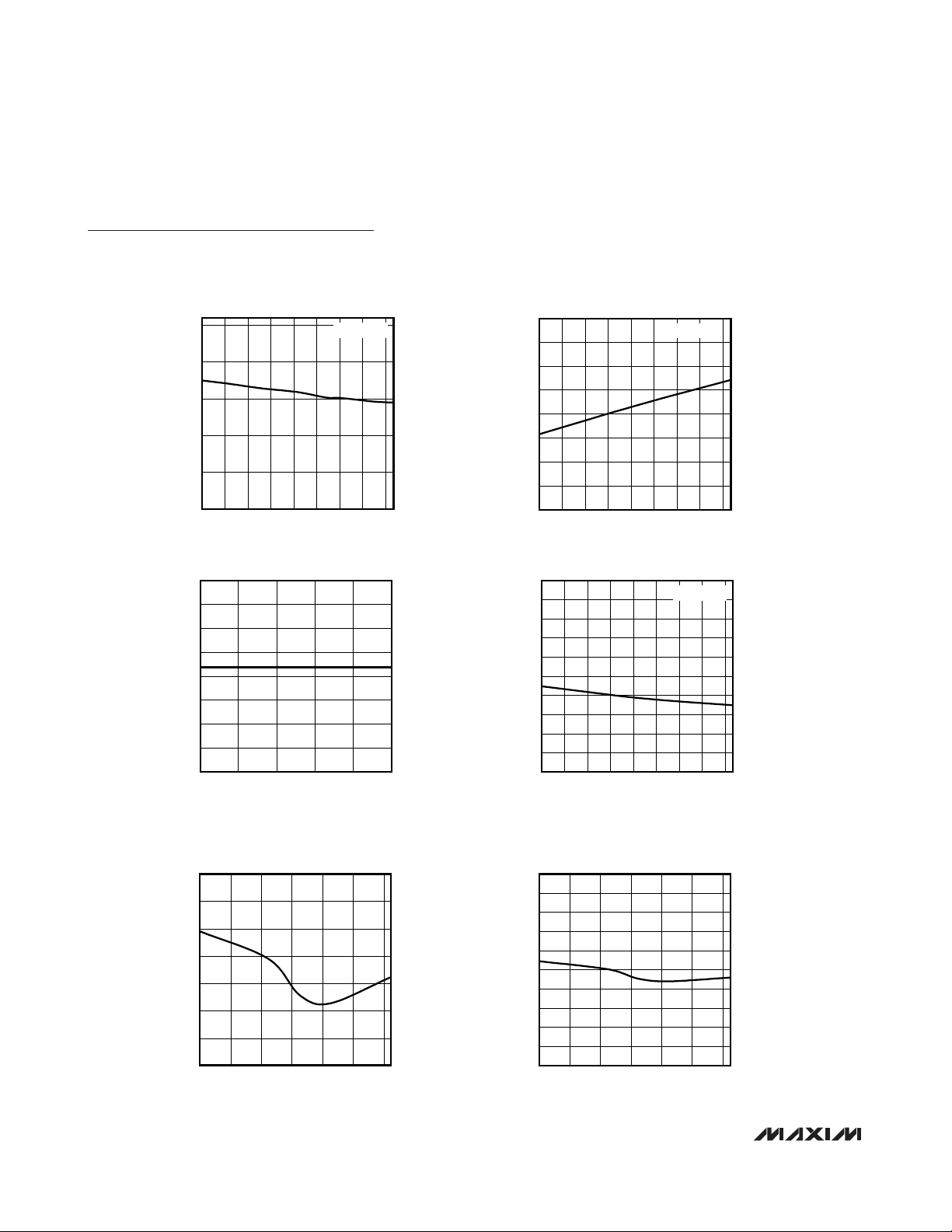

SENSE

TRANSIENT RESPONSE

MAX1385/86 toc09

100mV/div

1V/div

PGAOUT_

V

SENSE

10μs/div

Page 12

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

12 ______________________________________________________________________________________

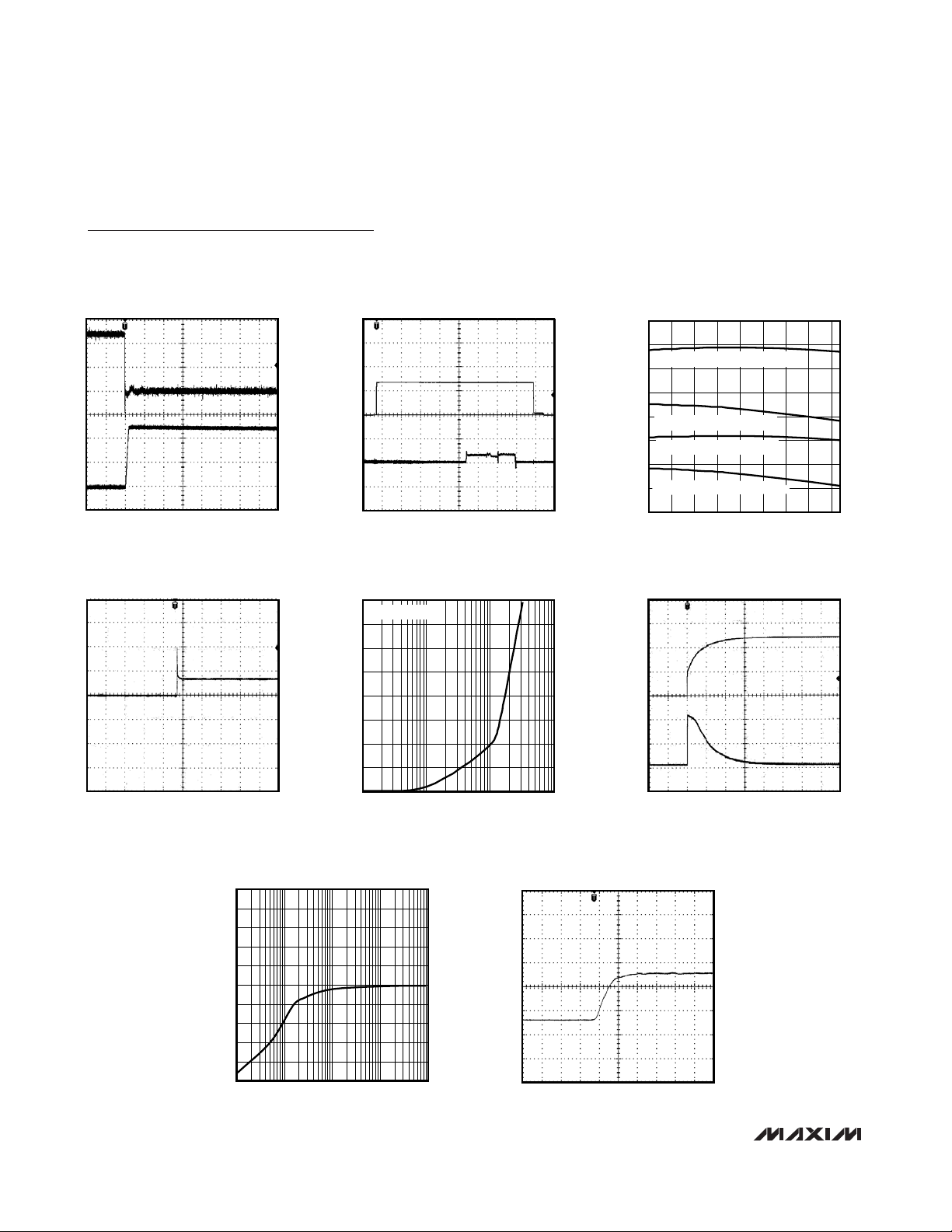

Typical Operating Characteristics (continued)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external

V

REFDAC

= +2.5V, C

REF

= 0.1µF, TA= +25°C, unless otherwise noted.)

PGAOUT_ 0mV TO 250mV

V

SENSE

TRANSIENT RESPONSE

MAX1385/86 toc10

V

SENSE

PGAOUT_

10µs/div

100mV/div

1V/div

PGAOUT_ PEDESTAL ERROR

DURING CALIBRATION

MAX1385/86 toc11

BUSY

PGAOUT_

20µs/div

2V/div

10mV/div

GATE_ OFFSET COMPENSATED

ERROR vs. TEMPERATURE

MAX1385/86 toc12

TEMPERATURE (°C)

ERROR VOLTAGE (mV)

8065-25 -10 5 3520 50

-7

-6

-5

-4

-3

-2

-1

0

-8

-40

L_ERROR, AUTOCALIBRATION

H_ERROR, AUTOCALIBRATION

L_ERROR, NO AUTOCALIBRATION

H_ERROR, NO AUTOCALIBRATION

V

GATE

vs. POWER-ON TIME

MAX1385/86 toc13

V

GATE_

400µs/div

50mV/div

CHARGE CURRENT vs. V

GATE

MAX1385/86 toc15

V

GATE_

1ms/div

I

GATE_

2V/div

20mA/div

GATE_ SETTLING TIME

vs. LOAD CAPACITANCE

MAX1385/86 toc14

LOAD CAPACITANCE (µF)

SETTLING TIME (ms)

101

2

4

6

8

10

12

14

16

0

0.1 100

R

SERIES

= 50

Ω

GATE_ VOLTAGE SWING

vs. LOAD RESISTANCE

MAX1385/86 toc16

LOAD RESISTANCE (Ω)

GATE_ VOLTAGE SWING (V)

10,0001000100

1

2

3

4

5

6

7

8

9

10

0

10 100,000

GLITCH ENERGY

MAX1385/86 toc17

1µs/div

10mV/div

Page 13

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 13

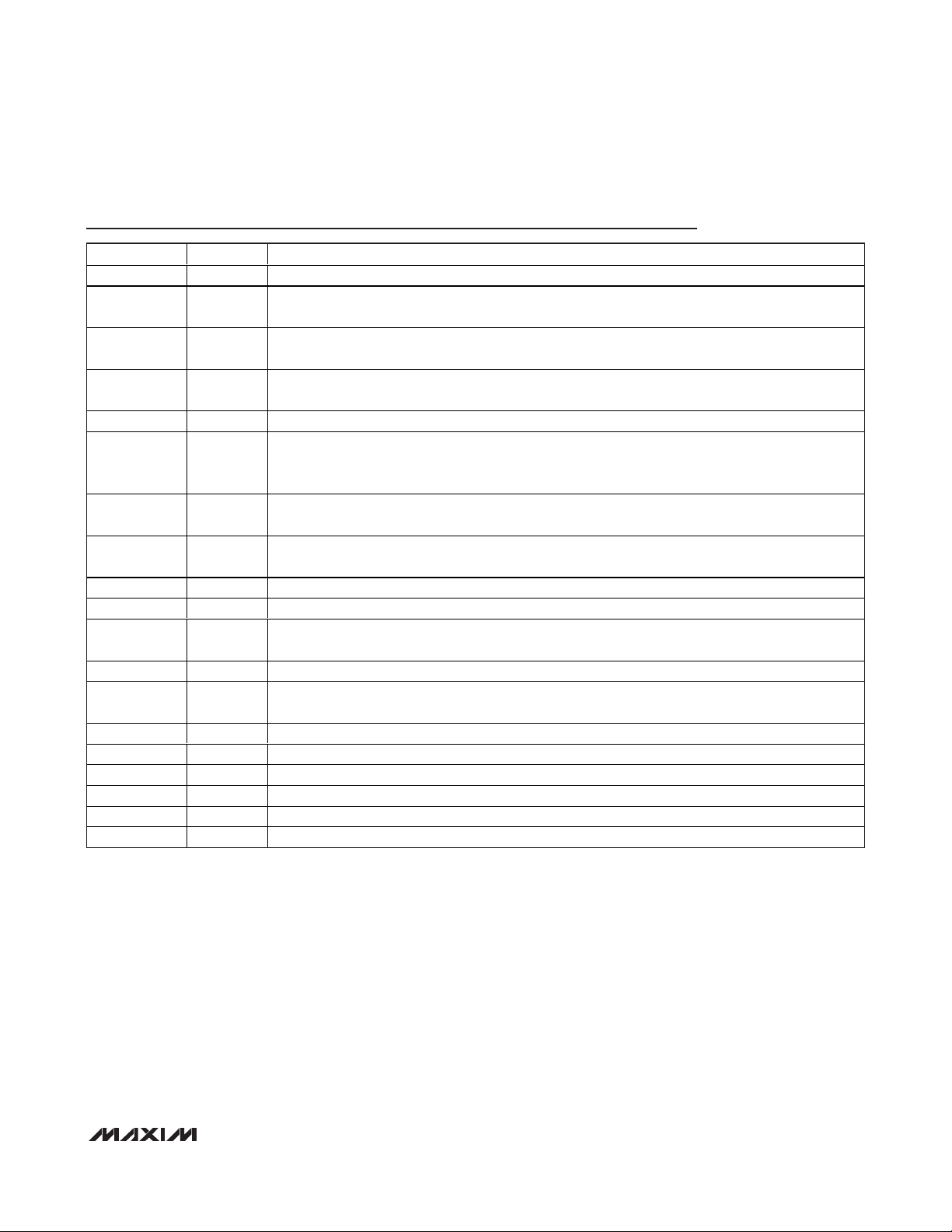

Typical Operating Characteristics (continued)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external

V

REFDAC

= +2.5V, C

REF

= 0.1µF, TA= +25°C, unless otherwise noted.)

-1.0

-0.4

-0.6

-0.8

-0.2

0

0.2

0.4

0.6

0.8

1.0

0 10050 150 200 250

INTEGRAL NONLINEARITY vs. DIGITAL

INPUT CODE (8-BIT COARSE DAC)

MAX1385/86 toc18

DIGITAL INPUT CODE

INL (LSB)

INTEGRAL NONLINEARITY vs. DIGITAL

INPUT CODE (10-BIT FINE DAC)

1.0

0.8

0.6

0.4

0.2

0

INL (LSB)

-0.2

-0.4

-0.6

-0.8

-1.0

0400200 600 800 1000

DIFFERENTIAL NONLINEARITY

vs. DIGITAL INPUT CODE (10-BIT FINE DAC)

1.0

0.8

0.6

0.4

0.2

0

DNL (LSB)

-0.2

-0.4

-0.6

-0.8

-1.0

0 400200 600 800 1000

DIGITAL INPUT CODE

DIGITAL INPUT CODE

MAX1385/86 toc21

DIFFERENTIAL NONLINEARITY

vs. DIGITAL INPUT CODE (8-BIT DAC)

1.0

0.8

MAX1385/86 toc19

0.6

0.4

0.2

0

DNL (LSB)

-0.2

-0.4

-0.6

-0.8

-1.0

0 10050 150 200 250

INTEGRAL NONLINEARITY

vs. DIGITAL OUTPUT CODE (ADC)

1.0

0.8

0.6

0.4

0.2

0

INL (LSB)

-0.2

-0.4

-0.6

-0.8

-1.0

0 20001000 3000 4000

DIGITAL OUTPUT CODE

DIGITAL INPUT CODE

MAX1385/86 toc22

MAX1385/86 toc20

DIFFERENTIAL NONLINEARITY

vs. DIGITAL OUTPUT CODE (ADC)

1.0

0.8

0.6

0.4

0.2

0

DNL (LSB)

-0.2

-0.4

-0.6

-0.8

-1.0

0 20001000 3000 4000

DIGITAL OUTPUT CODE

MAX1385/86 toc23

0

-20

-40

-60

-80

-100

AMPLITUDE (dB)

-120

-140

-160

0 5 10 15 20 25

FFT PLOT

fIN = 303Hz

f

SAMPLE

FREQUENCY (kHz)

= 49.15kHz

MAX1385/86 toc24

Page 14

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

14 ______________________________________________________________________________________

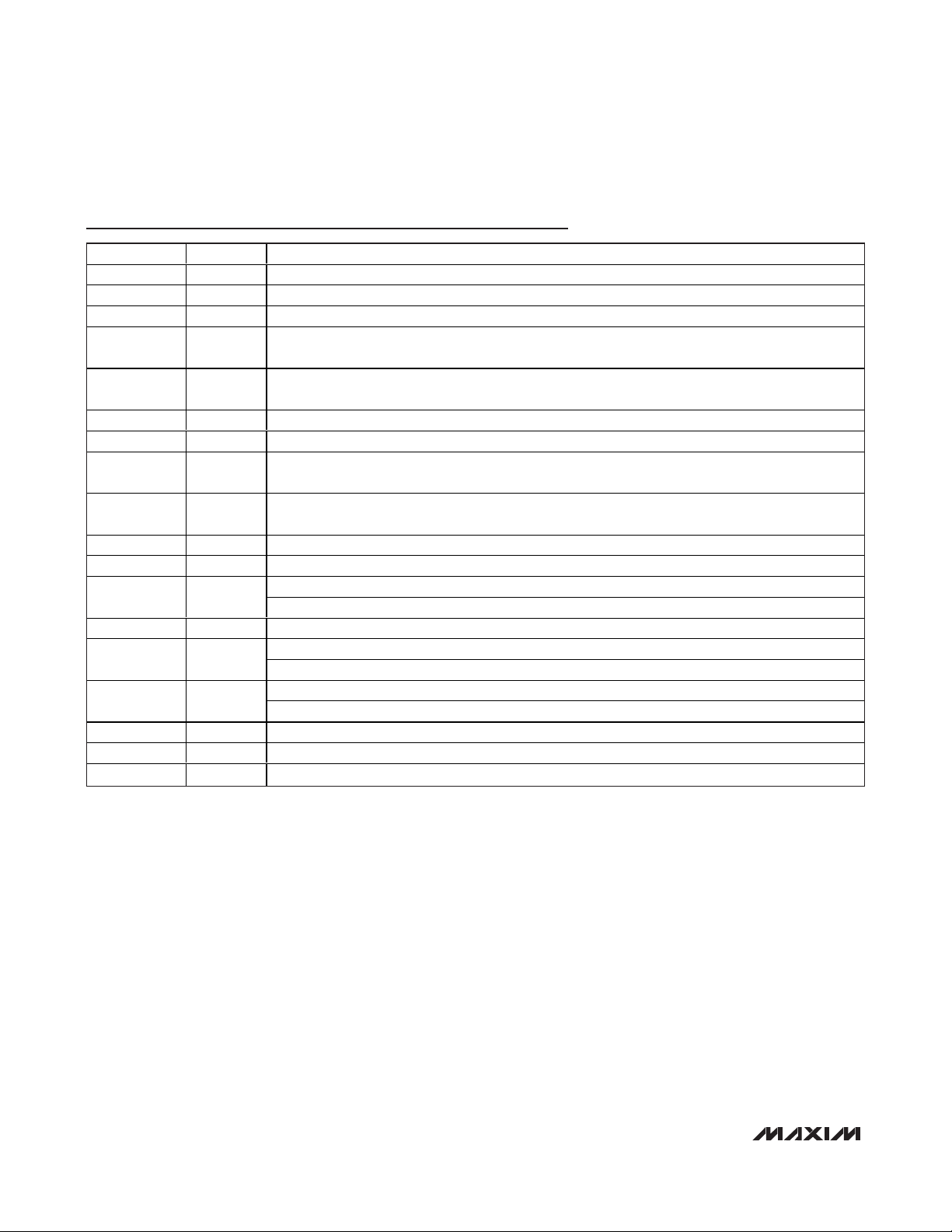

Typical Operating Characteristics (continued)

(GATEVDD= +5.5V for the MAX1385, GATEVDD= +11V for the MAX1386, AVDD= DVDD= +5V, external V

REFADC

= +2.5V, external

V

REFDAC

= +2.5V, C

REF

= 0.1µF, TA= +25°C, unless otherwise noted.)

2.484

2.489

2.494

2.499

2.504

2.509

-40 -10-25 5 20 35 50 65 80

INTERNAL REFERENCE

vs. TEMPERATURE

MAX1385/86 toc25

TEMPERATURE (°C)

REFERENCE VOLTAGE (V)

AVDD = 5V

-0.100

-0.050

-0.075

0.025

0

-0.025

0.075

0.050

0.100

-40 5 20-25 -10 35 50 65 80

ADC OFFSET ERROR vs. TEMPERATURE

MAX1385/86 toc26

TEMPERATURE (°C)

OFFSET ERROR (%)

AVDD = 5V

ADC OFFSET ERROR vs. AVDD VOLTAGE

0.100

0.075

0.050

0.025

0

-0.025

OFFSET ERROR (%)

-0.050

-0.075

-0.100

4.75 4.85 4.95 5.05 5.15 5.25

AVDD (V)

INTERNAL TEMPERATURE SENSOR

ERROR vs. TEMPERATURE

0

-0.2

-0.4

-0.6

-0.8

ERROR (°C)

-1.0

-1.2

-1.4

-40 0 20-20 40 60 80

TEMPERATURE (°C)

MAX1385/86 toc27

MAX1385/86 toc29

ADC GAIN ERROR vs. TEMPERATURE

0.05

0.04

0.03

0.02

0.01

0

-0.01

GAIN ERROR (%)

-0.02

-0.03

-0.04

-0.05

-40 -10 5 20-25 35 50 65 80

TEMPERATURE (°C)

EXTERNAL TEMPERATURE SENSOR

ERROR vs. TEMPERATURE

1.0

0.8

0.6

0.4

0.2

0

ERROR (°C)

-0.2

-0.4

-0.6

-0.8

-1.0

-40 0 20-20 40 60 80

TEMPERATURE (°C)

AVDD = 5V

MAX1385/86 toc28

MAX1385/86 toc30

Page 15

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 15

Pin Description

PIN NAME FUNCTION

1 DGND Digital Ground

2 SAFE1

3 A0/CSB

4 CNVST

5 SEL Mode Select. Connect SEL to DGND to select I2C mode. Connect SEL to DVDD to select SPI mode.

6 ALARM

7 SAFE2

8, 19, 25, 28,

35–39, 42, 46

9 REFDAC DAC Reference Input/Output

10 REFADC ADC Reference Input/Output

11 DXP1

12 DXN1 Diode Negative Input 1. Connect to cathode of temperature diode or the emitter of an npn transistor.

13 DXP2

14 DXN2 Diode Negative Input 2. Connect to cathode of temperature diode or the emitter of an npn transistor.

15 ADCIN1 ADC Input 1

16 ADCIN2 ADC Input 2

17 PGAOUT2 Programmable-Gain Amplifier Output 2

18 AV

20, 21, 22 AGND Analog Ground

N.C. No Connection. Not internally connected.

Safe Status Channel 1 Output. Programmable active-high or active-low. SAFE1 asserts when

programmed channel 1 temperature threshold or current threshold has been reached.

2

I

C-Compatible Address 0/ SPI-Compatible Chip Select. See the Digital Serial Interface section. In

SPI mode, drive A0/CSB low to select the device.

Active-Low Conversion-Start Input. Drive CNVST low to start a conversion (clock modes 01 and 11).

Connect CNVST to DV

Alarm Output. Program ALARM for comparator or interrupt output modes (see the Alarm Modes

section). Program ALARM to assert on any combination of channel temperature or current

thresholds.

Safe Status Channel 2 Output. Programmable active-high or active-low. SAFE2 asserts when

programmed channel 2 temperature threshold or current threshold has been reached.

Diode Positive Input 1. Connect to anode of temperature diode or the base and collector of an npn

transistor.

Diode Positive Input 2. Connect to anode of temperature diode or the base and collector of an npn

transistor.

Analog Power-Supply Input

DD

when initiating conversions through the serial interface (clock mode 00).

DD

Page 16

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

16 ______________________________________________________________________________________

Pin Description (continued)

PIN NAME FUNCTION

23 GATEGND Gate-Drive Amplifier Ground

24 GATEV

26 OPSAFE2 Operating Safe Channel 2 Input. Drive OPSAFE2 high to clamp GATE2 to AGND.

27 CS2+

29 CS2-

30 GATE2 Channel 2 Gate-Drive Amplifier Output

31 GATE1 Channel 1 Gate-Drive Amplifier Output

32 CS1-

33 CS1+

34 OPSAFE1 Operating Safe Channel 1 Input. Drive OPSAFE1 high to clamp GATE1 to AGND.

40 PGAOUT1 Programmable-Gain Amplifier Output 1

41 A2/N.C.

43 SCL Digital Serial Clock Input

44 SDA/DIN

45 A1/DOUT

47 BUSY Device Busy Output. See the BUSY Output section

48 DV

— EP Exposed Pad. Connect to AGND. Internally connected to analog ground.

DD

Gate-Drive Amplifier Supply Input

DD

Current-Sense Positive Input 2. CS2+ is the external sense resistor connection to the LDMOS 2

supply.

Current-Sense Negative Input 2. CS2- is the external sense resistor connection to the LDMOS 2

drain.

Current-Sense Negative Input 1. CS1- is the external sense resistor connection to the LDMOS 1

drain.

Current-Sense Positive Input 1. CS1+ is the external sense resistor connection to the LDMOS 1

supply.

I2C-Compatible Address 2. See the Digital Serial Interface section.

No Connection. Leave unconnected in SPI mode.

I2C-Compatible Serial Data Input/Output

SPI-Compatible Serial Data Input

I2C-Compatible Address 1. See the Digital Serial Interface section.

SPI-Compatible Serial Data Output

Digital Supply Input

Page 17

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 17

Functional Diagram

DV

DGND

SCL

SDA/DIN

A0/CSB

A1/DOUT

A2/N.C.

SAFE2

V

REFDAC

V

REFDAC

ALARM

PGA1

PGA2

DRV

10-BIT DAC

DRV

10-BIT DAC

SAFE1

DIGITAL

CURRENT AND

DD

SERIAL

INTERFACE

TEMPERATURE

COMPARATORS

PGA REGISTERS

REGISTER

SECTION

CHANNEL 1 DAC

REGISTERS

8-BIT HIGH CODE

8-BIT LOW CODE

10-BIT FINE

ADJUST CODE

CHANNEL 1 DAC

REGISTERS

8-BIT HIGH CODE

8-BIT LOW CODE

10-BIT FINE

ADJUST CODE

AV

DD

PGAOUT1

CS1+

CS1-

CS2-

CS2+

PGAOUT2

OPSAFE1

GATE1

GATEV

DD

GATEGND

OPSAFE2

GATE2

AGND

V

REFDAC

MEMORY

REFDAC

FIFO

2.5V

REF

REFADC

V

REFADC

MAX1385

MAX1386

12-BIT ADC

WITH T/H

CONVERSION AND

SCAN OSCILLATOR

AND CONTROL

CNVST

MUX

TEMP

SENSOR

PGAOUT1

PGAOUT2

EXTERNAL

TEMP

PROCESSING

ADCIN0

ADCIN1

DXP1

DXN1

DXP2

DXN2

Page 18

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

18 ______________________________________________________________________________________

Detailed Description

The MAX1385/MAX1386 set and control bias conditions

for dual RF LDMOS power devices found in cellular

base stations. Each device includes a high-side current-sense amplifier with programmable gains of 2, 10,

and 25 to monitor the LDMOS drain current over the

20mA to 5A range. Two external diode-connected transistors monitor the LDMOS temperatures while an internal temperature sensor measures the local die

temperature of the MAX1385/MAX1386. A 12-bit ADC

converts the programmable-gain amplifier (PGA) outputs, external/internal temperature readings, and two

auxiliary inputs.

The two gate-drive channels, each consisting of 8-bit

coarse and 10-bit fine DACs and a gate-drive amplifier,

generate a positive gate voltage to bias the LDMOS

devices. The MAX1385 includes a gate-drive amplifier

with a gain of 2 and the MAX1386 gate-drive amplifier

provides a gain of 4. The 8-bit coarse and 10-bit fine

DACs allow up to 18 bits of resolution. The MAX1385/

MAX1386 include autocalibration modes to minimize

error over time, temperature, and supply voltage.

The MAX1385/MAX1386 feature an I2C-/SPI-compatible

serial interface. Both devices operate from a 4.75V to

5.25V analog supply (3.2mA supply current), a 2.7V to

5.25V digital supply (3.1mA supply current), and a 4.75V

to 11.0V gate-drive supply (4.5mA supply current).

Power-On Reset

On power-up, the MAX1385/MAX1386 are in full powerdown mode (see the

SSHUT (Write)

section). To change

to normal power mode, write two commands to the

Software Shutdown register. The first command sets

FULLPD to 0 (other bits in the Software Shutdown register

are ignored). A second command is needed to activate

any internal blocks. The recommended sequence of commands to ensure reliable startup following the application

of power, is given in the

Appendix: Recommended

Power-Up Code Sequence

section.

ADC Description

The MAX1385/MAX1386 ADC uses a fully differential

successive approximation register (SAR) conversion

technique and on-chip track-and-hold (T/H) circuitry to

convert temperature and voltage signals into 12-bit digital results. The analog inputs accept single-ended

input signals. Single-ended signals are converted using

a unipolar transfer function. See the ADC transfer function of Figure 25 for more information.

The internal ADC block converts the results of the die

temperature, remote diode temperature readings,

PGAOUT1, PGAOUT2, ADCIN1, or ADCIN2 voltages

according to which bits are set in the ADC Conversion

register (see the

ADCCON (Write)

section). The results

of the conversions are written to FIFO memory. The

FIFO holds up to 15 words (each word is 16 bits) with

channel tags to indicate which channel the 12-bit data

comes from. The FIFO indicates an overflow condition

and an underflow condition (read of an empty FIFO) by

the Flag register (see the

RDFLAG (Read)

section) and

channel tags. The FIFO always stores the most recent

conversion results and allows the oldest data to be

overwritten. Read the latest result stored in the FIFO by

sending the appropriate read command byte (see the

FIFO (Read)

section).

Read the data stored in the FIFO through the FIFO

Read register. The

FIFO (Read)

section details which

channel is being read and whether the FIFO has overflowed.

Analog-to-Digital Conversion Scheduling

The MAX1385/MAX1386 ADC multiplexer scans selected inputs in the order shown in Table 1. The ADC multiplexer skips over the items that are not selected in the

Analog-to-Digital Conversion register. When writing a

conversion command before a conversion is complete,

the pending conversion may be canceled. In addition,

using the serial interface while the ADC is converting

may degrade the performance of the ADC.

ADC Clock Modes

The MAX1385/MAX1386 offer three different conversion/acquisition modes (known as clock modes) selectable through the Device Configuration register (see the

DCFIG (Read/Write)

section). Clock Mode 10 is

reserved and cannot be used. For conversion/acquisition examples and timing diagrams, see the

Applications Information

section.

If the analog-to-digital conversion requires the internal

reference (temperature measurement or voltage measurement with internal reference selected) and the reference has not been previously forced on, the device

inserts a worst-case delay of 81µs, for the reference to

settle, before commencing the analog-to-digital conversion. The reference remains powered up while there are

pending conversions. If the reference is not forced on,

it automatically powers down at the end of a scan or

when CONCONV in the Analog-to-Digital Conversion

register is set back to 0.

Page 19

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 19

Clock Mode 00

In clock mode 00, power-up, acquisition, conversion,

and power-down are all initiated by writing to the Analogto-Digital Conversion register and performed automatically using the internal oscillator. This is the default clock

mode. The ADC sets the BUSY output high, powers up,

scans all requested channels, stores the results in the

FIFO, and then powers down. After the scan is complete,

BUSY is pulled low and the results for all the commanded channels are available in the FIFO.

Clock Mode 01

In clock mode 01, power-up, acquisition, conversion,

and power-down are all initiated by setting CNVST low

for at least 40ns. Conversions are performed automatically using the internal oscillator. The ADC sets the

BUSY output high, powers up, scans all requested

channels, stores the results in the FIFO, and then powers down. After the scan is complete, BUSY is pulled

low and the results for all the commanded channels are

available in the FIFO.

Clock Mode 11

In clock mode 11, conversions are initiated one at a

time through CNVST in the order shown in Table 1 and

performed using the internal oscillator. In this mode, the

acquisition time is controlled by the time CNVST is

brought low. CNVST is resynchronized by the internal

oscillator, which means there is a one-clock-cycle

uncertainty (typically 320ns) in the exact sampling

instant. Different timing parameters apply depending

whether the conversion is temperature, voltage, using

the external reference, or using the internal reference.

For a temperature conversion, set CNVST low for at

least 40ns. The BUSY output goes high and the temperature conversion results are available after an additional 94µs (when BUSY goes low again). Thus, the

worst-case conversion time of the initial temperature

sensor scan (allowing the internal reference to settle) is

175µs. Subsequent temperature scans only take 85µs

worst case as the internal reference and temperature

sensor circuits are already powered.

For a voltage conversion while using an internal or

external reference, set CNVST low for at least 2µs but

less than 6.7µs. The BUSY output goes high and the

conversion results are available after an additional

7.5µs (typ) when BUSY goes low again.

Continuous conversion is not supported in this clock

mode (see the

ADCCON (Write)

section).

Changing Clock Modes During ADC Conversions

If a change is made to the clock mode in the Device

Configuration register while the ADC is already performing a conversion (or series of conversions), the following descriptions show how the MAX1385/MAX1386

respond:

• CKSEL = 00 and is then changed to another value

The ADC completes the already triggered series of

conversions and then goes idle. The BUSY output

remains high until the conversions are completed.

The MAX1385/MAX1386 then respond in accordance with the new CKSEL mode.

• CKSEL = 01 and is then changed to another value

If waiting for the initial external trigger, the

MAX1385/MAX1386 immediately exit clock mode

01, power down the ADC, and go idle. The BUSY

output stays low and waits for the external trigger. If

a conversion sequence has started, the ADC completes the requested conversions and then goes

idle. The BUSY output remains high until the conversions are completed. The MAX1385/MAX1386 then

respond in accordance with the new CKSEL mode.

• CKSEL = 11 and is then changed to another value

If waiting for an external trigger, the MAX1385/

MAX1386 immediately exit clock mode 11, power

down the ADC, and go idle. The BUSY output stays

low and waits for the external trigger.

Table 1. Order of ADC Conversion Scan

ORDER OF SCAN DESCRIPTION OF CONVERSION

1 Internal device temperature

2 External diode 1 temperature

3 PGAOUT1 for current sense

4 ADCIN1

5 External diode 2 temperature

6 PGAOUT2 for current sense

7 ADCIN2

Page 20

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

20 ______________________________________________________________________________________

Figure 4. Equivalent ADC Input Circuit

Analog Input Track and Hold

The equivalent circuit (Figure 4) shows the

MAX1385/MAX1386 ADC input architecture. In track

mode, a positive input capacitor is connected to

ADCIN_ and a negative input capacitor is connected to

AGND. After the T/H enters hold mode, the difference

between the sampled positive and negative input voltages is converted. The input capacitance charging rate

determines the time required for the T/H to acquire an

input signal. If the input signal’s source impedance is

high, the required acquisition time lengthens.

Any source impedance below 300Ω does not significantly affect the ADC’s AC performance. A high-imped-

ance source can be accommodated either by lengthening t

ACQ

or by placing a 1µF capacitor between the

positive input and AGND. The combination of the analog input source impedance and the capacitance at the

analog input creates an RC filter that limits the analoginput bandwidth.

Analog-Input Bandwidth

The ADC’s input-tracking circuitry has a 10MHz bandwidth to digitize high-speed transient events. Anti-alias

prefiltering of the input signals is necessary to avoid

high-frequency signals aliasing into the frequency band

of interest.

ADCIN_

CAPACITIVE DAC

CONTROL LOGIC

AGND

ADCIN_

AGND

TRACK MODE

HOLD/CONVERSION MODE

CAPACITIVE DAC

CONTROL LOGIC

Page 21

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 21

Analog-Input Protection

Internal ESD protection diodes clamp all analog inputs

to AVDDand AGND, allowing the inputs to swing from

AGND - 0.3V to AVDD+ 0.3V without damage. If an

analog input voltage exceeds the supplies, limit the

input current to 2mA.

DAC Description

The MAX1385/MAX1386 include two 8-bit and 10-bit

DAC blocks to independently control the voltage on

each LDMOS gate. Both 10-bit and 8-bit DACs can be

automatically calibrated to minimize output error over

time, temperature, and supply voltage. The 8-bit and

10-bit DACs have unipolar transfer functions and have

a relationship to the output voltage by the following

equation:

where LOCODE, HICODE, and FINECODE are the low

wiper (8 bits), high wiper (8 bits), and fine DAC (10 bits)

values written to the DAC by the user. LOCODE,

HICODE, and FINECODE represent the values in the

DAC input registers and may or may not be the actual

values in the DAC output registers depending whether

autocalibration is used or not (see the 8-Bit

Coarse-

DAC Adjustment

section). To find the actual voltage at

GATE_, multiply the V

DACOUT

result by 2 (MAX1385) or

4 (MAX1386). Due to the buffer amplifiers, the voltage

at GATE_ cannot be set below 100mV above AGND. It

is recommended that the LOCODE for DAC1 and DAC2

are set so that the minimum possible output at GATE_

is 200mV (MAX1385) and 400mV (MAX1386).

The DACs can be operated to produce an 18-bit

monotonic DAC with 12-bit (typ) INL. Write to either

HICODE or LOCODE in a leapfrog fashion, without

commanding autocalibration, to configure the 18-bit

monotonic DAC. When LOCODE > HICODE, invert the

value of FINECODE.

8-Bit Coarse-DAC Adjustment

Each DAC control block contains a resistor string with

wipers that serve as an 8-bit coarse DAC. Wipers are

set by writing to the appropriate DAC input registers

and/or using the Load DAC Control register (LDAC)

commands. The output of a coarse DAC is not updated

until the appropriate DAC output register(s) have been

set. See Figure 5 for the relationship between DAC

input registers, DAC output registers, and wipers.

DAC output registers are not directly accessible to the

user. Choose which input register to write to based on

whether automatic low or high calibration is desired, or

if updates to the output of the DAC need to be initiated

immediately. In the case of automatic low or high calibration, a correction code is added to or subtracted

from the 10-bit fine-DAC input register. Transfers from

the DAC input registers to DAC output registers can

occur immediately after a write to the appropriate DAC

input register or on a software command through the

Software LDAC register. See the

Register Descriptions

section for bit-level descriptions of these registers.

10-Bit Fine-DAC Adjustment

Each DAC control block contains a 10-bit fine DAC that

operates between the high and low wiper positions

from the 8-bit coarse DAC. The 10-bit fine DAC also

has an optional automatic calibration mode and can be

updated immediately or on a software-issued command

in the Software LDAC register. Writing to the appropriate fine-DAC input register determines whether automatic calibration is used and/or when the DAC is

updated. See Figure 6 for the relationship between

DAC input registers, DAC output registers, and the

Software LDAC register.

The fine-DAC output registers are not directly accessible. Choose which DAC input register to write to based

on whether automatic fine calibration is desired, or

whether updates to the output of the DAC need to be initiated immediately. In the case of automatic fine calibration, a correction code is added to or subtracted from

the input register code and transferred to the appropriate

fine-DAC output register. Transfers from a fine-DAC input

register to a fine-DAC output register can occur immediately after a write to the appropriate DAC input register or

on a software command through the Software LDAC register. See the

Register Descriptions

section for bit-level

detail of these registers.

V

DACOUT

V

REF REF

LOCODE

=× +× − ×

88 10

22 2

V

HICODE LOCODE

[]

FINECODE

Page 22

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

22 ______________________________________________________________________________________

Figure 6. Fine-DAC Register Diagram

Figure 5. Coarse-DAC Register Diagram

HIGH-CAL

COARSE DAC_ HIGH WIPER OUTPUT REGISTER

HIWIPE_ REGISTER

THRUHI_ REGISTER

THRULO_ REGISTER

INPUT REGISTERS

HCAL

V

DACREF

TO 10-BIT FINE DAC

LOWIPE_ REGISTER

LCAL

LOW-CAL

FROM 8-BIT COARSE DAC

LOAD DAC CONTROL REGISTER (LDAC)

FINE_ REGISTER

FINECAL_ REGISTER

COARSE DAC_ LOW WIPER OUTPUT REGISTER

LOAD DAC CONTROL REGISTER (LDAC)

FINE DAC_ OUTPUT REGISTER

10-BIT FINE

DAC

TO GATE-DRIVE BLOCK

FINECALTHRU_ REGISTER

INPUT REGISTERS

FINETHRU_ REGISTER

FROM 8-BIT COARSE DAC

FINE-CAL

Page 23

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 23

ADC/DAC References

The MAX1385/MAX1386 provide an internal low-noise

2.5V reference for the ADCs, DACs, and temperature

sensor. See the

Device Configuration Register

section

for information on configuring the device for external or

internal reference. Connect a voltage source to

REFADC in the 1V to AVDDrange when using an external ADC reference. Connect a voltage source to REFDAC in the 0.5V to 2.5V range when using an external

DAC reference. When using an external voltage reference, bypass the reference pin with a 0.1µF capacitor

to AGND.

The internal reference has a lowpass filter to reduce

noise. The device allows 60µs (typ) and 81µs (typ) worst

case for the reference to settle before permitting an analog-to-digital conversion. If reference mode 11 is selected, the required settling time is longer. In this case, the

user should set at least one of DAC1PD, DAC2PD, or

FBGON in the Software Shutdown register, any of which

forces the reference to be permanently powered up.

Temperature Measurements

The MAX1385/MAX1386 measure the internal die temperature and two external remote-diode temperature

sensors. Set up a temperature conversion by writing

to the Analog-to-Digital Conversion register (see the

ADCCON (Write)

section). Optionally program SAFE1

and SAFE2 outputs to depend on programmed temperature thresholds.

The MAX1385/MAX1386 can perform temperature measurements with an internal diode-connected transistor.

The diode bias current changes from 66µA to 4µA to

produce a temperature-dependent bias voltage difference. The second conversion result at 4µA is subtracted from the first at 66µA to calculate a digital value that

is proportional to the absolute temperature. The stored

data result is the aforementioned digital code minus an

offset to adjust from Kelvin to Celsius.

The reference voltage for the temperature measurements is always derived from the internal reference

source. Temperature results are in degrees Celsius

(two’s-complement form).

The temperature-sensing circuits power up for the first

temperature measurement in an analog-to-digital conversion scan. The temperature-sensing circuits remain

powered until the end of the scan to avoid a possible

67µs delay of internal reference power-up time for each

individual temperature channel. If the continuous convert bit CONCONV is set high and the current ADC

channel selection includes a temperature channel, the

temperature-sensor circuits remain powered up until

the CONCONV bit is set low.

The external temperature-sensor drive current ratio has

been optimized for a 2N3904 npn transistor with an ideality factor of 1.0065. The nonideality offset is removed

internally by a preset digital coefficient. Use of a transistor with a different ideality factor produces a proportionate difference in the absolute measured

temperature. More details on this topic and others related to using an external temperature sensor can be

found in Maxim Application Note 1057:

Compensating

for Ideality and Series Resistance Differences Between

Thermal Sense Diodes

and Application Note 1944:

Temperature Monitoring Using the MAX1253/MAX1254

and MAX1153/MAX1154

.

High-Side Current-Sense PGAs

The MAX1385/MAX1386 provide two high-side currentsense amplifiers with programmable gain. The currentsense amplifiers are unidirectional and provide a 5V to

30V input common-mode range. Both CS1+ and CS2+

must be within the specified common-mode range for

proper operation of each amplifier.

The sense amplifiers measure the load current, I

LOAD

,

through an external sense resistor, R

SENSE_

, between

the CS_+ and CS_- inputs. The full-scale sense voltage

range (V

SENSE_

= V

CS_

+ - V

CS_

-) depends on the pro-

grammed gain, Av

PGA_

(see the

DCFIG (Read/Write)

section). The sense amplifiers provide a voltage output

at PGAOUT_ according to the following equation:

These outputs are also routed to the internal 12-bit ADC

so that a digital representation of the amplified voltages

can be read through the FIFO.

The PGA scales the sensed voltages to fit the input

range of the ADC. Program the PGA with gains of 2, 10,

and 25 by setting the PGSET_ bits (see the

DCFIG

(Read/Write)

section). The input stages have nominal

input offset voltages of 0mV that can be adjusted by a

trim DAC (not shown in the

Functional Diagram

) over the

-3mV to +3mV range in 25µV steps. Autocalibration can

be used to control the trim DAC to minimize the effective

channel input offset voltage (see the

PGACAL (Write)

section). The PGA feedback network is referenced to

AGND.

ALARM Output

The state of ALARM is logically equivalent to the inclusive OR of SAFE1 and SAFE2. The exception to this

statement is when ALARM is configured for output interrupt mode (see the

Alarm Modes

section). When in output-interrupt mode, ALARM stays in its asserted state

until its associated flag is cleared by reading from the

VAvVV

PGAOUT PGA CS CS____

()=×+−−

Page 24

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

24 ______________________________________________________________________________________

Figure 7. Window-Threshold-Mode Diagram

Flag register. Configure ALARM for open-drain/pushpull and active-high/active-low by setting the respective

bits in the Hardware Alarm Configuration register.

SAFE1/SAFE2 Outputs

Set up the SAFE1 and SAFE2 outputs to allow WiredOR/AND-type logic functions or to create additional

interrupt-type signals to replace or supplement the

existing ALARM output. SAFE1 and SAFE2 do not have

any internal pullup/pulldown devices.

The SAFE1 and SAFE2 output buffers are CMOS-compatible, noninverting, output buffers capable of driving

to within 0.5V of either digital rail. The SAFE1 and

SAFE2 outputs power up as active-high CMOS outputs

with standard logic levels. Configure the SAFE1 and

SAFE2 outputs for open-drain or push-pull by setting

the appropriate bits in the Hardware Alarm

Configuration register. When configuring SAFE1 and

SAFE2 as open-drain outputs, an external pullup resistor is required.

BUSY Output

The BUSY output is forced high to show that the

MAX1385/MAX1386 are busy for a variety of reasons:

• The ADC is in the middle of a user-commanded con-

version cycle (but not in continuous convert mode)

• The ADC is in the middle of an internally triggered

conversion cycle (for a self-calibration measurement)

• The device is in the middle of DAC calibra-

tion calculations

• The device is in the middle of power-up initialization

• One of the PGA channels is undergoing self-calibration

The serial interface remains active regardless of the

state of the BUSY output. Wait until BUSY goes low to

read the current conversion data from the FIFO. When

BUSY is high as a result of an ADC conversion, do not

enter a second conversion command until BUSY has

gone low to indicate the previous conversion is complete. The rising edge of BUSY occurs on the next internal oscillator clock after the start of a new conversion

(either by CNVST or an interface command).

HIGHEST POSSIBLE THRESHOLD

VALUE (DEFAULT VALUE FOR HIGH

THRESHOLD REGISTER)

ALARM OUTPUT ASSERTED

WHEN MEASURED VALUE

RISES ABOVE THIS LEVEL

BUILT-IN 8 TO 64 LSBs

OF HYSTERESIS

RANGE OF VALUES THAT DO NOT CAUSE AN ALARM

BUILT-IN 8 TO 64 LSBs

OF HYSTERESIS

ALARM OUTPUT ASSERTED

WHEN MEASURED VALUE

FALLS BELOW THIS LEVEL

*ONLY WHEN ALARM IS CONFIGURED FOR OUTPUT-COMARATOR MODE.

WHEN IN OUTPUT-INTERRUPT MODE, FLAG REGISTER MUST BE READ

FOR ALARM TO BE DEASSERTED.

ALARM OUTPUT DEASSERTED

WHEN MEASURED VALUE FALLS

BELOW THIS LEVEL*

HIGH THRESHOLD

LOW THRESHOLD

ALARM OUTPUT DEASSERTED

WHEN MEASURED VALUE RISES

ABOVE THIS LEVEL*

LOWEST POSSIBLE THRESHOLD

VALUE (DEFAULT VALUE FOR HIGH

THRESHOLD REGISTER)

Page 25

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 25

In single-conversion mode (CKSEL = 11), the BUSY

signal remains high until the ADC has completed the

current conversion (not the entire scan, just the current

conversion), the data has been moved into the FIFO,

and the alarm limits for the channel have been checked

(if enabled). In multiple-conversion mode (CKSEL = 01

or CKSEL = 00), the BUSY signal remains high until all

channels have been scanned and the data from the

final channel has been moved into the FIFO and

checked for alarm limits (if enabled). In continuous-conversion mode (CONCONV = 1), the BUSY signal does

not go high as a result of ADC conversions; however,

BUSY does go high when CONCONV is removed and

remains high until the current scan is complete and the

ADC sequence halts.

After commanding any of the DAC autocalibration components, wait for BUSY to go low before setting OSCPD to 1.

Alarm Modes

The MAX1385/MAX1386 contain several programmable

modes for configuring outputs ALARM, SAFE1, and

SAFE2 behavior. Window-threshold mode allows SAFE_

to assert when the temperature/current is too high or

too low (outside the window). Hysteresis-threshold

mode allows SAFE_ to assert when the temperature/

current is too high, and then to deassert when the temperature/current falls back to an appropriate level.

ALARM asserts when SAFE1 and/or SAFE2 asserts.

Program ALARM for output-comparator mode to stay

asserted after an alarm condition until temperature/current levels are back below programmed thresholds.

Program ALARM for output-interrupt mode to stay

asserted after an alarm condition until the Flag register

is read.

Window-Threshold Mode

In window-threshold mode, ADC readings of

current/temperature are compared to the configured

current/temperature low/high thresholds that are programmed to cause an alarm condition. If an ADC reading falls out of the configured window and ALARM is

configured for output-comparator mode, ALARM

asserts until the current/temperature reading falls back

into the window (past the built-in hysteresis). If an ADC

reading falls out of the configured window and ALARM

is configured for output-interrupt mode, ALARM asserts

until the Flag register is read. Set the amount of built-in

hysteresis from 8 LSBs to 64 LSBs (see the

ALMSCFG

(Read/Write)

section). See Figures 7 and 8.

Figure 8. Window-Threshold-Mode Timing Diagram

MEASUREMENT VALUE

(TEMPERATURE OR CURRENT)

HIGH THRESHOLD

BUILT-IN HYSTERESIS

BUILT-IN HYSTERESIS

LOW THRESHOLD

ALARM OUTPUT

COMPARATOR MODE

OUTPUT-

(ACTIVE LOW)

OUTPUT-

INTERRUPT MODE

(ACTIVE LOW)

FLAG REGISTER

READ

FLAG REGISTER

READ

FLAG REGISTER

READ

TIME

TIME

Page 26

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

26 ______________________________________________________________________________________

Hysteresis-Threshold Mode

In hysteresis-threshold mode, ADC readings of

current/temperature are compared to the configured

current/temperature low/high thresholds that are programmed to cause an alarm condition. If an ADC reading exceeds its respective configured threshold and

ALARM is configured for output-comparator mode,

ALARM asserts until the current/temperature reading

falls back below its respective threshold. If an ADC

reading exceeds its respective configured threshold

and ALARM is configured for output-interrupt mode,

ALARM asserts until the Flag register is read. See

Figures 9 and 10.

Register Descriptions

Communicate with the MAX1385/MAX1386 through the

I2C/SPI-compatible serial interface. Complete read and

write operations consist of slave address bytes, command bytes, and data bytes. The following register

descriptions cover the contents of command bytes and

data bytes. See the

Digital Serial Interface

section for a

detailed description of how to construct full read and

write operations. All registers are volatile and are reset

to default states upon removal of power. These default

states are referred to as power-on reset (POR) states.

All accessible MAX1385/MAX1386 registers are shown

in Table 2.

TH1 and TH2 (Read/Write)

Write to Channel 1 and Channel 2 High Temperature

Threshold registers by sending the appropriate write

command byte followed by data bits D15–D0 (see Table

3). Bits D15–D12 are don’t care. Read channel 1 and

channel 2 high-temperature thresholds by sending the

appropriate read command byte. Channel 1 and

Channel 2 Temperature Threshold registers are compared to temperature readings from the remote diode

connected transistors. Temperature data is in two’s-complement format and the LSB corresponds to 1/8°C (see

Figure 26 for the Temperature Transfer Function).

TL1 and TL2 (Read/Write)

Write to Channel 1 and Channel 2 Low-TemperatureThreshold registers by sending the appropriate write

command byte followed by data bits D15–D0 (see Table

4). Bits D15–D12 are don’t care. Read channel 1 and

channel 2 low-temperature thresholds by sending the

appropriate read command. Channel 1 and Channel 2

Temperature Threshold registers are compared to temperature readings from the remote diode connected transistors. Temperature data is in two’s-complement format

and the LSB corresponds to 1/8°C (see Figure 26 for the

Temperature Transfer Function).

Figure 9. Hysteresis-Threshold-Mode Diagram

ALARM OUTPUT ASSERTED

WHEN MEASURED VALUE

RISES ABOVE THIS LEVEL

ALARM OUTPUT ASSERTED

WHEN MEASURED VALUE

FALLS BELOW THIS LEVEL

RANGE OF VALUES THAT DO NOT CAUSE AN ALARM

*ONLY WHEN ALARM IS CONFIGURED FOR OUTPUT-COMARATOR MODE.

WHEN IN OUTPUT-INTERRUPT MODE, FLAG REGISTER MUST BE READ

FOR ALARM TO BE DEASSERTED.

HIGHEST POSSIBLE THRESHOLD

VALUE (DEFAULT VALUE FOR HIGH

THRESHOLD REGISTER)

HIGH THRESHOLD

LOW THRESHOLD

LOWEST POSSIBLE THRESHOLD

VALUE (DEFAULT VALUE FOR LOW

THRESHOLD REGISTER)

Page 27

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

______________________________________________________________________________________ 27

Table 2. Register Listing (See

Appendix: Recommended Power-Up Code Sequence

section)

REGISTER DESCRIPTION MNEMONIC

Analog-to-Digital Conversion ADCCON 62 —

Channel 1 High-Current Threshold IH1 24 A4

Channel 1 High-Temperature Threshold TH1 20 A0

Channel 1 Low-Current Threshold IL1 26 A6

Channel 1 Low-Temperature Threshold TL1 22 A2

Channel 2 High-Current Threshold IH2 2C AC

Channel 2 High-Temperature Threshold TH2 28 A8

Channel 2 Low-Current Threshold IL2 2E AE

Channel 2 Low-Temperature Threshold TL2 2A AA

Coarse DAC1 High Wiper Input HIWIPE1 34 B4

Coarse DAC1 Low Wiper Input LOWIPE1 36 B6

Coarse DAC1 Write-Through High Wiper Input THRUHI1 74 B4

Coarse DAC1 Write-Through Low Wiper Input THRULO1 76 B6

Coarse DAC2 High Wiper Input HIWIPE2 3A BA

Coarse DAC2 Low Wiper Input LOWIPE2 3C BC

Coarse DAC2 Write-Through High Wiper Input THRUHI2 7A BA

Coarse DAC2 Write-Through Low Wiper Input THRULO2 7C BC

Device Configuration DCFIG 30 B0

FIFO Memory FIFO — 80

Fine DAC1 Input Read RDFINE1 — B8

Fine DAC1 Input Register with Autocalibration FINECAL1 38 —

Fine DAC1 Input Without Autocalibration FINE1 50 —

Fine DAC1 Write-Through Input with Autocalibration FINECALTHRU1 78 —

Fine DAC1 Write-Through Input Without Autocalibration FINETHRU1 52 —

Fine DAC2 Input Read RDFINE2 — BE

Fine DAC2 Input Register with Autocalibration FINECAL2 3E —

Fine DAC2 Input Without Autocalibration FINE2 54 —

Fine DAC2 Write-Through Input with Autocalibration FINECALTHRU2 7E —

Fine DAC2 Write-Through Input Without Autocalibration FINETHRU2 56 —

Flag RDFLAG — EA

Hardware Alarm Configuration ALMHCFG 60 E0

PGA Calibration Control PGACAL 4E —

Software Clear SCLR 68 —

Software LDAC LDAC 66 —

Software Shutdown SSHUT 64 —

Software Alarm Configuration ALMSCFG 32 B2

HEX COMMAND

WRITE READ

Page 28

MAX1385/MAX1386

Dual RF LDMOS Bias Controllers

with I2C/SPI Interface

28 ______________________________________________________________________________________

IH1 and IH2 (Read/Write)

Write to Channel 1 and Channel 2 High-CurrentThreshold registers by sending the appropriate write

command byte followed by data bits D15–D0 (see

Table 5). Bits D15–D12 are don’t care. Read channel 1

and channel 2 high-current thresholds by sending the

appropriate read command byte. Channel 1 and

Channel 2 Current-Threshold registers are compared to

ADC readings at PGAOUT1 and PGAOUT2. Use the

following equation to find the required threshold code

for a specified threshold current:

where I

DRAIN

is the current threshold in amperes,

R

SENSE

is the sense resistor, Av

PGA

is the voltage gain

of the PGA, V

REFADC

is the ADC reference voltage, and

I

THRESH

is the resulting threshold register value

in decimal.

IL1 and IL2 (Read/Write)

Write to Channel 1 and Channel 2 Low-CurrentThreshold registers by sending the appropriate write

command byte followed by data bits D15–D0 (see

Table 6). Bits D15–D12 are don’t care. Read channel 1

and channel 2 low-current thresholds by sending the

appropriate read command byte. Channel 1 and

Channel 2 Low-Current Threshold registers are compared to ADC readings at PGAOUT1 and PGAOUT2.

Figure 10. Hysteresis-Threshold-Mode Timing Diagram

Table 3. TH1 and TH2 (Read/Write)

X = Don’t care.

MEASUREMENT VALUE

(TEMPERATURE OR CURRENT)

HIGH THRESHOLD

LOW THRESHOLD

ALARM OUTPUT

COMPARATOR MODE