Page 1

General Description

The MAX1115/MAX1116 low-power, 8-bit, analog-todigital converters (ADCs) feature an internal track/hold

(T/H), voltage reference, VDDmonitor, clock, and serial

interface. The MAX1115 is specified from +2.7V to

+5.5V, and the MAX1116 is specified from +4.5V to

+5.5V. Both parts consume only 175µA at 100ksps.

The full-scale analog input range is determined by the

internal reference of +2.048V (MAX1115) or +4.096V

(MAX1116). The MAX1115/MAX1116 also feature

AutoShutdown™ power-down mode which reduces

power consumption to <1µA when the device is not in

use. The 3-wire serial interface directly connects to

SPI™, QSPI™, and MICROWIRE™ devices without

external logic. Conversions up to 100ksps are performed using an internal clock.

The MAX1115/MAX1116 are available in an 8-pin

SOT23 package with a footprint that is just 30% of an 8pin SO.

________________________Applications

Low-Power, Hand-Held Portable Devices

System Diagnostics

Battery-Powered Test Equipment

Receive Signal Strength Indicators

4mA to 20mA Powered Remote Data-Acquisition

Systems

Features

♦ Single Supply

+2.7V to +3.6V (MAX1115)

+4.5V to +5.5V (MAX1116)

♦ Input Voltage Range: 0 to V

REF

♦ Internal Track/Hold; 100kHz Sampling Rate

♦ Internal Reference

+2.048V (MAX1115)

+4.096V (MAX1116)

♦ SPI/QSPI/MICROWIRE-Compatible Serial Interface

♦ Small 8-Pin SOT23 Package

♦ Automatic Power-Down

♦ Low Power

175µA at 100ksps

18µA at +3V and 10ksps

1µA in Power-Down Mode

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

________________________________________________________________ Maxim Integrated Products 1

Pin Configuration

19-1822; Rev 0; 11/00

Ordering Information

AutoShutdown is a trademark of Maxim Integrated Products.

SPI/QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor, Corp.

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

PART TEMP. RANGE

MAX1115EKA -40°C to +85°C 8 SOT23 AADY

MAX1116EKA -40°C to +85°C 8 SOT23 AADX

PINPA CK A G E

TO P

M A RK

TOP VIEW

V

1

DD

CH0

2

MAX1115

3

MAX1116

4

SOT23

I.C.

GND

8

7

6

5

SCLK

DOUT

CONVST

I.C.

Page 2

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

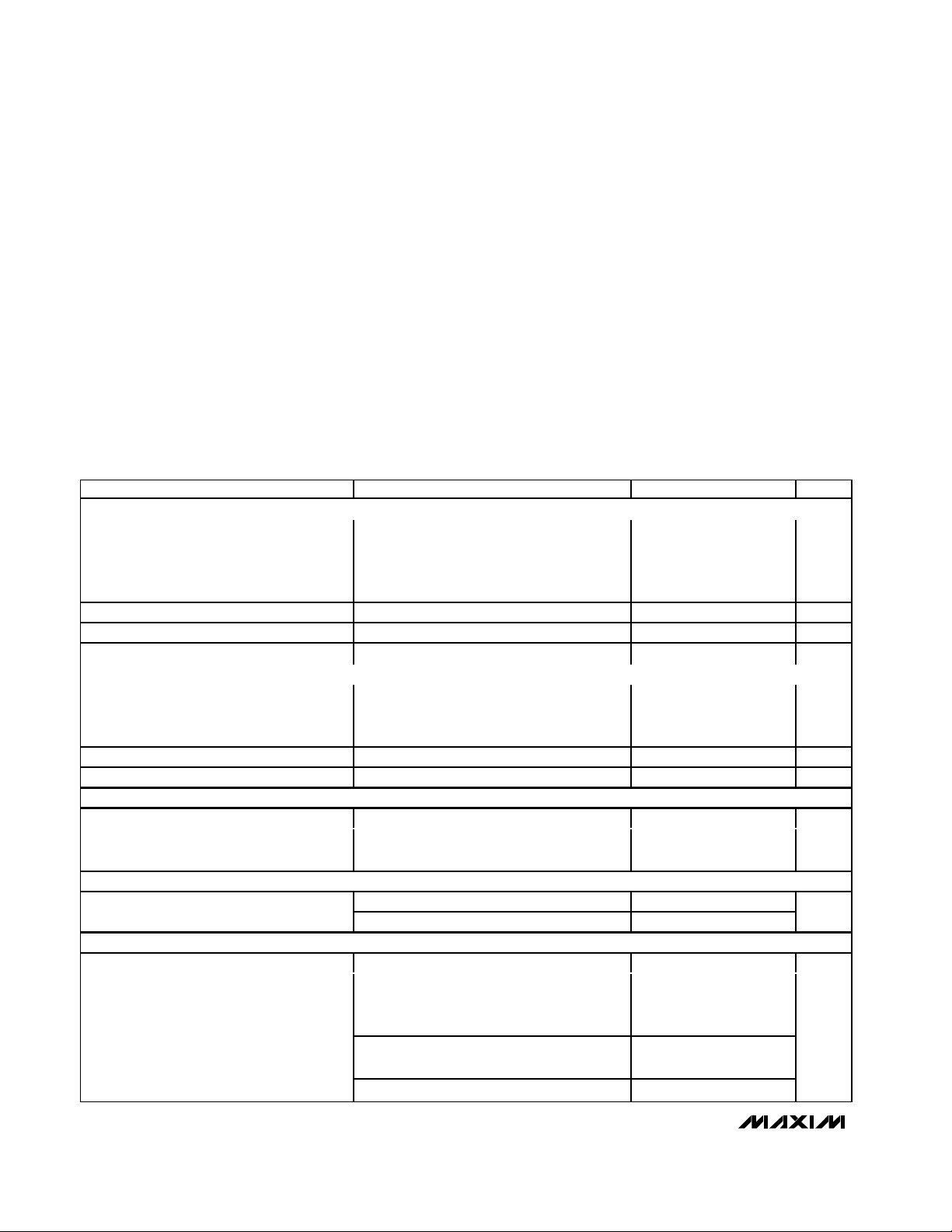

ELECTRICAL CHARACTERISTICS

(VDD= +2.7V to +3.6V (MAX1115), VDD= +4.5V to +5.5V (MAX1116), TA= T

MIN

to T

MAX

, unless otherwise noted.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VDDto GND...........................................................-0.3V to +6.0V

CH0 to GND ...............................................-0.3V to (V

DD

+ 0.3V)

Digital Output to GND ................................-0.3V to (V

DD

+ 0.3V)

Digital Input to GND ..............................................-0.3V to +6.0V

Maximum Current into Any Pin .........................................±50mA

Continuous Power Dissipation (T

A

= +70°C)

8-Pin SOT23 (derate 8.9mW/°C above +70°C)............714mW

Operating Temperature Range

MAX111_EKA ..................................................-40°C to + 85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-60°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DC ACCURACY

Resolution 8 bits

Relative Accuracy (Note 1) INL ±1 LSB

Differential Nonlinearity DNL ±1 LSB

Offset Error 0.5 LSB

Gain Error ±5

%FSR

Gain Temperature Coefficient 90

ppm/ °C

VDD/2 Sampling Error ±2 ±7%

DYNAMIC PERFORMANCE (25kHz sinewave input, VIN = V

REF(p-p

), f

SCLK

= 5MHz, f

SAMPLE

= 100ksps, RIN = 100Ω)

Signal-to-Noise Plus Distortion

SINAD

48 dB

Total Harmonic Distortion

(up to the 5th Harmonic)

THD -69 dB

Spurious-Free Dynamic Range SFDR 66 dB

Small-Signal Bandwidth f

-3dB

4

MHz

ANALOG INPUT

Input Voltage Range 0

V

REF

V

Input Leakage Current VCH = 0 or V

DD

±0.7

±10 µA

Input Capacitance C

IN

18 pF

INTERNAL REFERENCE

MAX1115

2.048

Voltage V

REF

MAX1116

4.096

V

POWER REQUIREMENTS

MAX1115 2.7 5.5

Supply Voltage V

DD

MAX1116 4.5 5.5

V

f

SAMPLE

= 10ksps 14 21

MAX1115

f

SAMPLE

= 100ksps 135 190

f

SAMPLE

= 10ksps 19 25

MAX1116

f

SAMPLE

= 100ksps 182 230

Supply Current (Note 2) I

DD

Shutdown 0.8 10

µA

Page 3

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

_______________________________________________________________________________________ 3

Note 1: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range and off-

set have been calibrated.

Note 2: Input = 0 with logic input levels of 0 and V

DD

.

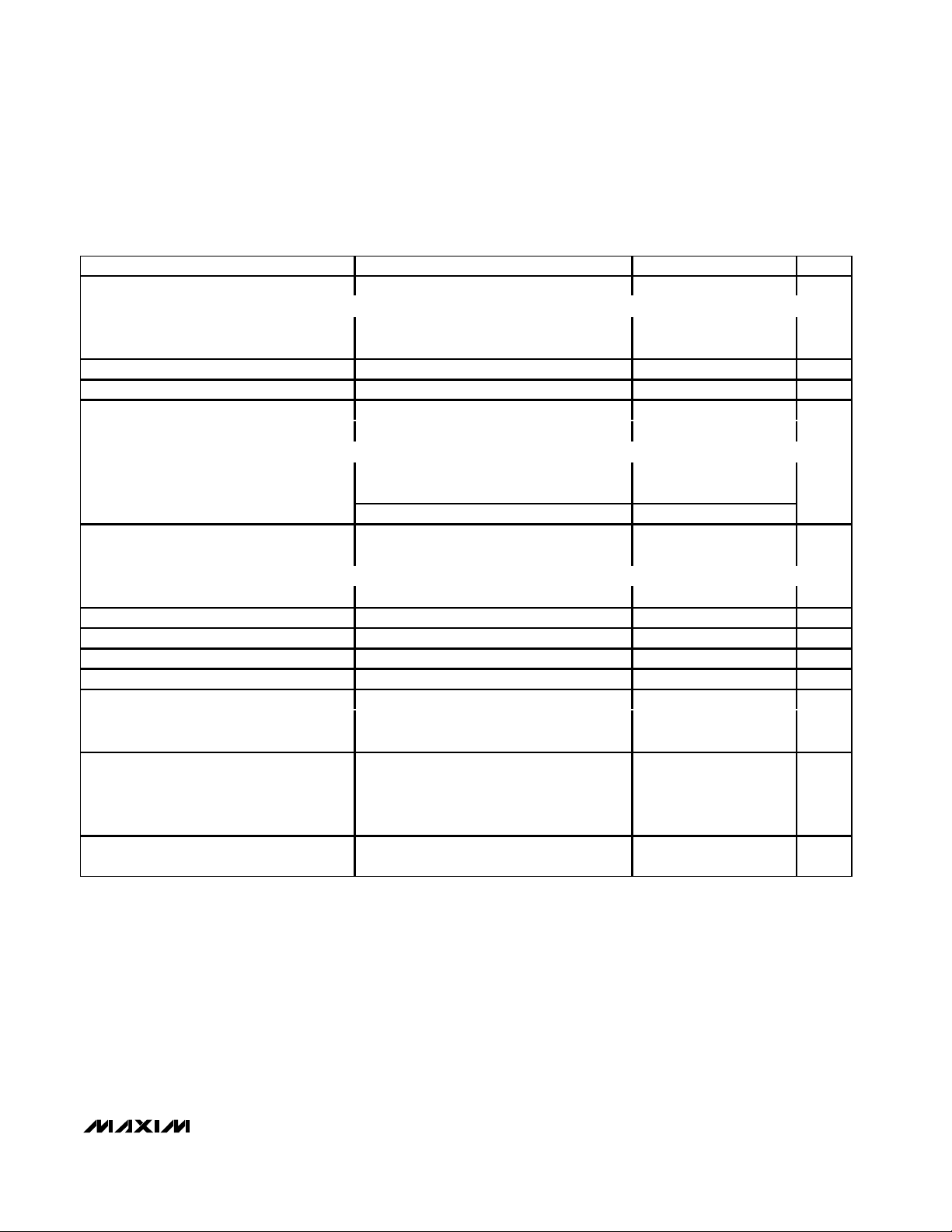

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Supply Rejection Ratio PSRR Full-scale or zero input

±0.5±1LSB/V

DIGITAL INPUTS (CNVST AND SCLK)

Input High Voltage V

IH

2V

Input Low Voltage V

IL

0.8 V

Input Hystersis

V

HYST

0.2 V

Input Current High I

IH

±10 µA

Input Current Low I

IL

±10 µA

Input Capacitance C

IN

2pF

DIGITAL OUTPUT (DOUT)

Output High Voltage V

OH

I

SOURCE

= 2mA VDD - 0.5 V

I

SINK

= 2mA 0.4

Output Low Voltage V

OL

I

SINK

= 4mA 0.8

V

Three-State Leakage Current I

L

±0.01

±10 µA

Three-State Output Capacitance

C

OUT

4pF

TIMING CHARACTERISTICS (Figures 6a–6d)

CNVST High Time t

csh

100

ns

CNVST Low Time t

csl

100

ns

Conversion Time t

conv

7.5 µs

Serial Clock High Time t

ch

75 ns

Serial Clock Low Time t

cl

75 ns

Serial Clock Period t

cp

200

ns

Falling of CNVST to DOUT

Active

t

csd

C

LOAD

= 100pF, Figure 1 100 ns

Serial Clock Falling Edge to

DOUT

t

cd

C

LOAD

= 100pF 10 100 ns

Serial Clock Rising Edge

To DOUT High-Z

t

chz

C

LOAD

= 100pF, Figure 2

100

500 ns

La st S er i al C l ock to N ex t C N V S T

( successi ve conver si ons on C H 0)

t

ccs

50 ns

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +2.7V to +3.6V (MAX1115), VDD= +4.5V to +5.5V (MAX1116), TA= T

MIN

to T

MAX

, unless otherwise noted.)

Page 4

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

4 _______________________________________________________________________________________

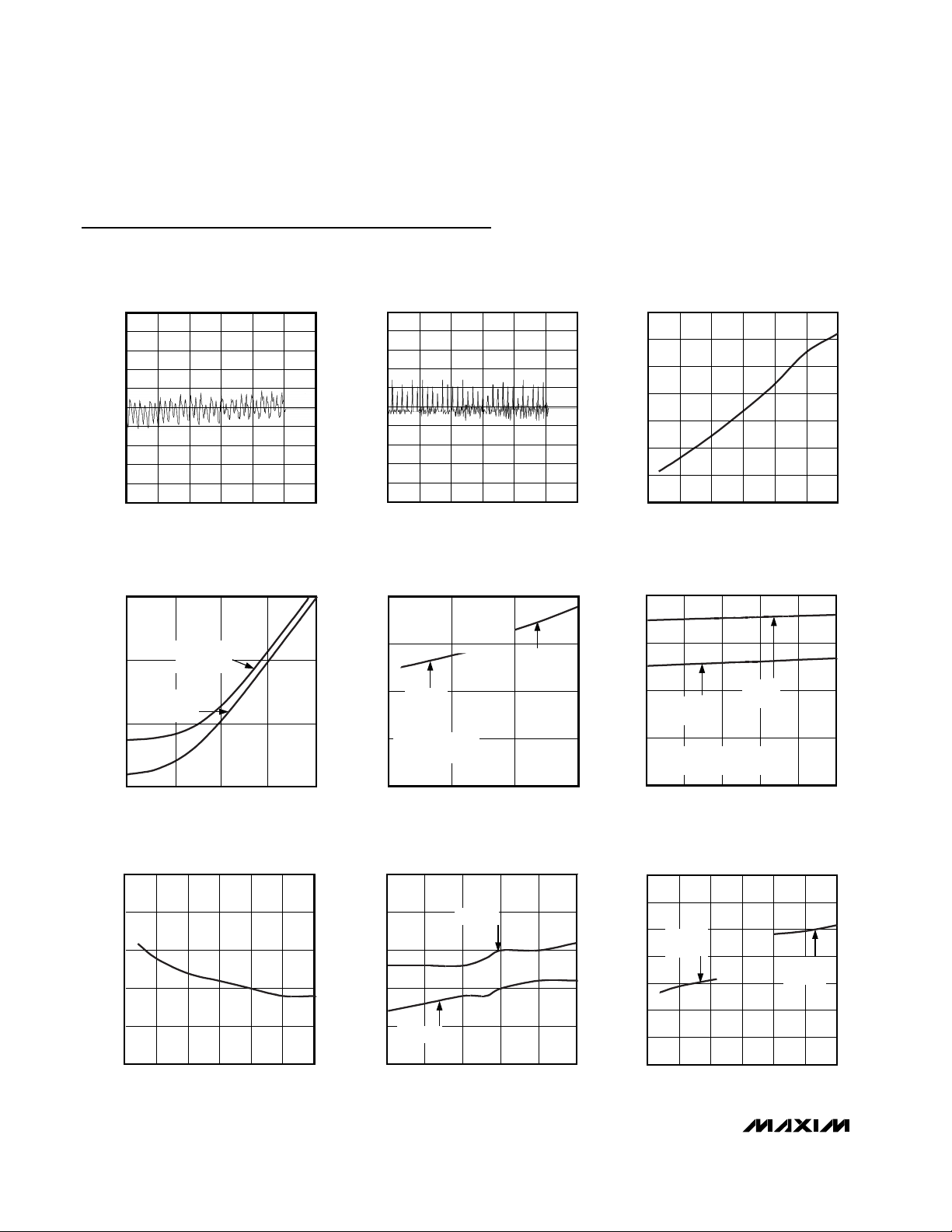

Typical Operating Characteristics

(VDD= +3V (MAX1115), VDD= +5V (MAX1116), f

scu

= 5MHz, f

sample

= 100ksps, C

LOAD

= 100pF, TA = +25°C, unless otherwise

noted.)

-1.0

-0.4

-0.6

-0.8

-0.2

0

0.2

0.4

0.6

0.8

1.0

0 10050 150 200 250 300

INTEGRAL NONLINEARITY

vs. OUTPUT CODE

MAX1115 toc01

OUTPUT CODE

INL (LSB)

-0.2

-0.4

-0.6

0

0.2

0.4

0.6

0.8

1.0

0 10050 150 200 250 300

DIFFERENTIAL NONLINEARITY

vs. OUTPUT CODE

MAX1115 toc02

OUTPUT CODE

DNL (LSB)

-0.8

-1.0

0

0.2

0.1

0.4

0.3

0.6

0.5

0.7

SHUTDOWN SUPPLY CURRENT

vs. SUPPLY VOLTAGE

MAX1115 toc03

SUPPLY VOLTAGE (V)

SHUTDOWN CURRENT (µA)

2.5

3.5

4.5

5.5

100.0

0

0.01 0.1 1 10 100

SUPPLY CURRENT vs.

CONVERSION RATE

1.0

MAX1115 toc04

CONVERSION (ksps)

SUPPLY CURRENT (µA)

10.0

MAX1116

V

DD

= +5V

MAX1115

V

DD

= +3V

0

50

100

150

200

2.5 3.5 4.5 5.5

SUPPLY CURRENT

vs. SUPPLY VOLTAGE

MAX1115 toc05

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (µA)

MAX1115

MAX1116

D

OUT

= 00000000

V

DD

= V

DIGITAL INPUTS

0

50

100

150

200

-40 -15 10 35 60 85

SUPPLY CURRENT

vs. TEMPERATURE

MAX1115 toc06

TEMPERATURE (°C)

SUPPLY CURRENT (µA)

D

OUT

= 00000000

V

DD

= V

REF

= V

DIGITAL INPUTS

MAX1115

V

DD

= +3V

MAX1116

V

DD

= +5V

5.0

5.2

5.3

5.1

5.4

5.5

2.5 3.5 4.5 5.5

CONVERSION TIME

vs. SUPPLY VOLTAGE

MAX1115 toc07

SUPPLY VOLTAGE (V)

CONVERSION TIME (µs)

MAX1115 toc08

5.0

5.2

5.3

5.1

5.4

5.5

-40 -15 10 35 60 85

CONVERSION TIME

vs. TEMPERATURE

TEMPERATURE (°C)

CONVERSION TIME (µs)

VDD = +3V

VDD = +5V

0

0.6

0.8

0.4

0.2

1.2

1.0

1.4

2.5 4.53.5 5.5

GAIN ERROR vs.

SUPPLY VOLTAGE

MAX1115 toc09

SUPPLY VOLTAGE (V)

GAIN ERROR (%FSR)

MAX1116

V

DD

= +5V

MAX1115

V

DD

= +3V

Page 5

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

_______________________________________________________________________________________ 5

Typical Operating Characteristics (continued)

(VDD= +3V (MAX1115), VDD= +5V (MAX1116), f

scu

= 5MHz, f

sample

= 100ksps, C

LOAD

= 100pF, TA = +25°C, unless otherwise

noted.)

2.0

1.5

1.0

0.5

0

-0.5

GAIN ERROR (%FSR)

-1.0

-1.5

-2.0

-40 603510-15 85

0.5

0.4

0.3

MAX1116

0.2

VDD = +3V

0.1

0

-0.1

OFFSET ERROR (LSB)

-0.2

-0.3

-0.4

-0.5

2.5 3.0 4.0 5.04.53.5 5.5

GAIN ERROR

vs. TEMPERATURE

MAX1116

= +5V

V

DD

TEMPERATURE (°C)

OFFSET ERROR vs.

SUPPLY VOLTAGE

SUPPLY VOLTAGE (V)

MAX1115

= +3V

V

DD

MAX1115

VDD = +3V

MAX1115 toc10

MAX1115 toc12

0

-20

-40

-60

AMPLITUDE (dB)

-80

-100

-120

0

0.5

0.4

0.3

0.2

0.1

0

-0.1

OFFSET ERROR (LSB)

-0.2

-0.3

-0.4

-0.5

-40 -15 603510 85

FFT PLOT

f

= 100kHz

SAMPLE

= 25.1kHz

f

IN

= 0.9xV

A

IN

20k

10k

ANALOG INPUT FREQUENCY (Hz)

30k

p-p

REF

40k 50k

MAX1115 toc11

OFFSET ERROR vs.

TEMPERATURE

MAX1116

VDD = +3V

TEMPERATURE (°C)

MAX1115

VDD = +5V

MAX1115 toc13

MAX1115

REFERENCE VOLTAGE

vs. NUMBER OF PIECES

21.0%

17.5%

14.0%

10.5%

7.0%

3.5%

0

1.982 2.008 2.0862.0602.034 2.112

REFERENCE VOLTAGE (V)

MAX1115 toc14

21.0%

17.5%

14.0%

10.5%

7.0%

3.5%

0

3.980 4.020 4.1404.1004.060 4.180

MAX1116

REFERENCE VOLTAGE

vs. NUMBER OF PIECES

MAX1115 toc15

REFERENCE VOLTAGE (V)

Page 6

MAX1115/MAX1116

Detailed Description

The MAX1115/MAX1116 ADCs use a successiveapproximation conversion technique and input

track/hold (T/H) circuitry to convert an analog signal to

an 8-bit digital output. The SPI/QSPI/MICROWIRE compatible interface directly connects to microprocessors

(µP’s) without additional circuitry (Figure 3).

Track/Hold

The input architecture of the ADC is illustrated in the

equivalent-input circuit shown in Figure 4 and is composed of the T/H, input multiplexer, input comparator,

switched capacitor DAC, and autozero rail.

The acquisition interval begins with the falling edge of

CNVST. During the acquisition interval, the analog input

(CH0) is connected to the hold capacitor (C

HOLD

).

Once the acquisition is complete, the T/H switch opens

and C

HOLD

is connected to GND, which retains the

charge on C

HOLD

as a sample of the signal at the ana-

log input.

Sufficiently low source impedance is required to ensure

an accurate sample. A source impedance of <1.5kΩ is

recommended for accurate sample settling. A 100pF

capacitor at the ADC inputs will also improve the accuracy of an input sample.

Conversion Process

The MAX1115/MAX1116 conversion process is internally timed. The total acquisition and conversion process

takes <7.5µs. Once an input sample has been

acquired, the comparator’s negative input is then connected to an autozero supply. Since the device

requires only a single supply, the negative input of the

comparator is set to equal VDD/2. The capacitive DAC

restores the positive input to VDD/2 within the limits of 8bit resolution. This action is equivalent to transferring a

charge QIN= 16pF ✕VINfrom C

HOLD

to the binaryweighted capacitive DAC, which forms a digital representation of the analog-input signal.

Single-Supply, Low-Power, Serial 8-Bit ADCs

6 _______________________________________________________________________________________

Pin Description

PIN NAME FUNCTION

1VDDPositive Supply Voltage

2 CH0 Analog Voltage Input

3, 5 I.C. Internally Connected. Connect to ground.

4 GND Ground

6 CNVST Convert/Start Input. CNVST initiates a power-up and starts a conversion on its falling edge.

7 DOUT

Serial Data Output. Data is clocked out on the falling edge of SCLK. DOUT goes low at the start of a

conversion and presents the MSB at the completion of a conversion. DOUT goes high impedance

once data has been fully clocked out.

8 SCLK Serial Clock. Used for clocking out data on DOUT.

Figure 1. Load Circuits for Enable Time

Figure 2. Load Circuits for Disable Time

V

DD

DOUT

3kΩ

GND

TO V

a) V

OL

OH

C

LOAD

DOUT

b) HIGH-Z TO VOL AND VOH to V

3kΩ

C

LOAD

GND

OL

DOUT

3kΩ

GND

a) V

TO High-Z b) VOL TO HIGH-Z

OH

C

LOAD

V

DD

DOUT

3kΩ

C

GND

LOAD

Page 7

Input Voltage Range

Internal protection diodes that clamp the analog input

to VDDand GND allow the input pin (CH0) to swing

from (GND - 0.3V) to (VDD+ 0.3V) without damage.

However, for accurate conversions, the inputs must not

exceed (VDD+ 50mV) or be less than (GND - 50mV).

Input Bandwidth

The ADC’s input tracking circuitry has a 4MHz smallsignal bandwidth, so it is possible to digitize highspeed transient events and measure periodic signals

with bandwidths exceeding the ADC’s sampling rate by

using undersampling techniques. Anti-alias filtering is

recommended to avoid high-frequency signals being

aliased into the frequency band of interest.

Serial Interface

The MAX1115/MAX1116 have a 3-wire serial interface.

The CNVST and SCLK inputs are used to control the

device, while the three-state DOUT pin is used to

access the conversion results.

The serial interface provides connection to microcontrollers (µCs) with SPI, QSPI, and MICROWIRE serial

interfaces at clock rates up to 5MHz. The interface supports either an idle high or low SCLK format. For SPI

and QSPI, set CPOL = CPHA = 0 or CPOL = CPHA = 1

in the SPI control registers of the µC. Figure 5 shows

the MAX1115/MAX1116 common serial-interface connections. See Figures 6a–6d for details on the serialinterface timing and protocol.

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

_______________________________________________________________________________________ 7

Figure 3. Typical Operating Circuit

Figure 4. Equivalent Input Circuit

Figure 5. Common Serial-Interface Connections

V

DD

ANALOG

INPUTS

CH0

MAX1115

V

GND

DD

0.1µF

1µF

V

DD

CPU

MAX1116

CONVST

SCLK

DOUT

I/O

SCK (SK)

MISO (SI)

GND

GND

CAPACITIVE DAC

C

CH0

V

DD

2

HOLD

16pF

HOLD

R

IN

6.5kΩ

TRACK

I/O

SCK

MISO

+3V

SS

a) SPI

CS

SCK

MISO

+3V

SS

b) QSPI

I/O

SK

SI

c) MICROWIRE

CONVST

SCLK

DOUT

MAX1115

MAX1116

CONVST

SCLK

DOUT

MAX1115

MAX1116

CONVST

SCLK

DOUT

MAX1115

MAX1116

COMPARATOR

AUTOZERO

RAIL

Page 8

MAX1115/MAX1116

Digital Inputs and Outputs

The MAX1115/MAX1116 perform conversions by using

an internal clock. This frees the µP from the burden of

running the SAR conversion clock, and allows the conversion results to be read back at the µP’s convenience

at any clock rate up to 5MHz.

The acquisition interval begins with the falling edge of

CNVST. CNVST can idle between conversions in either

a high or low state. If idled in a low state, CNVST must

be brought high for at least 50ns, then brought low to

initiate a conversion. To select V

DD

/2 for conversion,

the CNVST pin must be brought high and low for a second time (Figures 6c and 6d).

Single-Supply, Low-Power, Serial 8-Bit ADCs

8 _______________________________________________________________________________________

Figure 6a. Conversion and Interface Timing, Conversion on CH0 with SCLK Idle Low

Figure 6b. Conversion and Interface Timing, Conversion on CH0 with SCLK Idle High

ACTIVE POWER-DOWN MODE

t

CSH

CNVST

SCLK

DOUT

CH0

t

CONV

IDLE LOW IDLE LOW

t

csd

t

cd

D7 (MSB) D6 D5 D4 D3 D2 D1 D0

t

ch

t

cl

ACTIVE POWER-DOWN MODE

t

CSH

CNVST

SCLK

CH0

IDLE HIGH

t

CONV

t

ch

CH0

t

cp

t

cp

t

ccs

t

chz

CH0

t

ccs

IDLE HIGH

t

chz

DOUT

t

csd

t

cd

D7 (MSB) D6 D5 D4 D3 D2 D1 D0

t

cl

Page 9

After CNVST is brought low, allow 7.5µs for the conversion to be completed. While the internal conversion is in

progress, DOUT is low. The MSB is present at the

DOUT pin immediately after conversion is completed.

The conversion result is clocked out at the DOUT pin

and is coded in straight binary (Figure 7). Data is

clocked out at SCLK’s falling edge in MSB-first format

at rates up to 5MHz. Once all data bits are clocked out,

DOUT goes high impedance (100ns to 500ns after the

rising edge) of the eighth SCLK pulse.

SCLK is ignored during the conversion process. Only

after a conversion is complete will SCLK cause serial

data to be output. Falling edges on CNVST during an

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

_______________________________________________________________________________________ 9

Figure 6c. Conversion and Interface Timing, Conversion on VDD/ 2 with SCLK Idle Low

Figure 6d. Conversion and Interface Timing, Conversion on VDD/ 2 with SCLK Idle High

ACTIVE POWER-DOWN MODE

t

CSH

V

CH0

CNVST

SCLK

DOUT

DD

2

t

CONV

IDLE LOW IDLE LOW

t

csd

t

cd

D7 (MSB) D6 D5 D4 D3 D2 D1 D0

t

ch

t

cl

t

cp

ACTIVE POWER-DOWN MODE

t

CSH

t

CSL

V

CH0

t

ccs

t

chz

t

csl

DD

2

V

CH0

CNVST

SCLK

DOUT

DD

2

t

CONV

t

csd

t

cd

D7 (MSB) D6 D5 D4 D3 D2 D1 D0

t

ch

t

cl

t

cp

V

CH0

t

ccs

t

chz

DD

2

IDLE HIGHIDLE HIGH

Page 10

MAX1115/MAX1116

active conversion process interrupt the current conversion and cause the input multiplexer to switch to VDD/2.

To reinitiate a conversion on CH0, it is necessary to allow

for a conversion to be complete and all of the data to be

read out. Once a conversion has been completed, the

MAX1115/MAX1116 will go into Autoshutdown mode

(typically <1µA) until the next conversion is initiated.

Applications Information

Power-On Reset

When power is first applied, the MAX1115/MAX1116

are in AutoShutdown (typically <1µA). A conversion

can be started by toggling CNVST high to low.

Powering up the MAX1115/MAX1116 with CNVST low

will not start a conversion.

AutoShutdown and Supply Current

Requirements

The MAX1115/MAX1116 are designed to automatically

shutdown once a conversion is complete, without any

external control. An input sample and conversion

process will typically take 5µs to complete, during

which time the supply current to the analog sections of

the device are fully on. All analog circuitry is shutdown

after a conversion completes, which results in a supply

current of <1µA (see Shutdown Current vs. Supply Volt-

age plot in the Typical Operating Characteristics sec-

tion). The digital conversion result is maintained in a

static register and is available for access through the

serial interface at any time.

The power consumption consequence of this architecture is dramatic when relatively slow conversion rates

are needed. For example, at a conversion rate of

10ksps, the average supply current for the MAX1115 is

15µA, while at 1ksps it drops to 15µA. At 0.1 ksps it is

just 0.3µA, or a miniscule 1µW of power consumption

(see Average Supply Current vs. Conversion Rate plot

in the Typical Operating Characteristics sections).

Transfer Function

Figure 7 depicts the input/output transfer function.

Output coding is binary with a +2.048V reference,

1LSB = 8mV(VREF/256).

Layout, Grounding, and Bypassing

For best performance, board layout should ensure that

digital and analog signal lines are separated from each

other. Do not run analog and digital (especially clock)

lines parallel to one another or run digital lines underneath the ADC package.

Figure 8 shows the recommended system-ground connections. A single-point analog ground (star-ground

point) should be established at the ADC ground.

Connect all analog grounds to the star-ground. The

ground-return to the power supply for the star ground

should be low impedance and as short as possible for

noise-free operation.

High-frequency noise in the V

DD

power supply may

affect the comparator in the ADC. Bypass the supply to

the star ground with a 0.1µF capacitor close to the V

DD

pin of the MAX1115/MAX1116. Minimize capacitor lead

Single-Supply, Low-Power, Serial 8-Bit ADCs

10 ______________________________________________________________________________________

Figure 7. Input/Output Transfer Function

Figure 8. Power-Supply Connections

OUTPUT CODE

11111111

11111110

11111101

00000011

00000010

00000001

00000000

0

123

INPUT VOLTAGE (LSB)

FULL-SCALE

TRANSITION

FS = V

1LSB = V

256

FS - 1/2 LSB

REFIN

FS

REFIN

+ V

SYSTEM POWER SUPPLIES

GND

IN-

GND

IN-

1µF

0.1µF

MAX1115

MAX1116

10Ω

DD

DGNDV

DIGITAL

CIRCUITRY

+3V/+5V

V

DD

Page 11

lengths for best supply-noise rejection. If the power

supply is noisy, a 0.1µF capacitor in conjunction with a

10Ω series resistor can be connected to form a lowpass filter.

Chip Information

TRANSISTOR COUNT: 2000

PROCESS: BiCMOS

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

______________________________________________________________________________________ 11

Functional Diagram

SCLK

CNVST

CH0

INPUT

MULTIPLEXER

SPLIT

/2

V

DD

INPUT

TRACK

AND HOLD

INTERNAL

REFERENCE

2.096V

OR 4.096V

CONTROL

LOGIC AND

INTERNAL

OCSILLATOR

8-BIT

SAR

ADC

OUTPUT

SHIFT

REGISTER

MAX1115

MAX1116

DOUT

Page 12

MAX1115/MAX1116

Single-Supply, Low-Power, Serial 8-Bit ADCs

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 ____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2000 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

Package Information

SOT23, 8L.EPS

Loading...

Loading...