Page 1

PRST

P

P

E

P

Y

P

Y

P

P

P

L

PREQ

PGNT

P

R

P

R

PXAS

PXDS

P

T

J

T

K

L

W

L

LINT

LRDY

LCS

L

L

L

K

LBHE

K

)

www.maxim-ic.com

GENERAL DESCRIPTION

The DS3131 bit-synchronous (BoSS) HDLC

controller can handle up to 40 channels of highspeed, unchannelized, bit-synchronous HDLC.

The on-board DMA has been optimized for

maximum flexibility and PCI bus efficiency to

minimize host processor intervention in the data

path. Diagnostic loopbacks and an on-board

BERT remove the need for external components.

APPLICATIONS

Routers

xDSL Access Multiplexers (DSLAMs)

Clear-Channel (unchannelized) T1/E1

Clear-Channel (unchannelized) T3/E3

SONET/SDH Path Overhead Termination

High-Density V.35 Terminations

High-Speed Links such as HSSI

DEMO KIT AVAILABLE

DS3131 BoSS

40-Port, Unchannelized

Bit-Synchronous HDLC

FEATURES

40 Timing Independent Ports

40 Bidirectional HDLC Channels

Each Port Can Operate Up to 52Mbps

Up to 132Mbps Full-Duplex Throughput

On-Board Bit Error-Rate Tester (BERT)

Diagnostic Loopbacks in Both Directions

Local Bus Supports PCI Bridging

33MHz 32-Bit PCI Interface

Full Suite of Driver Code

Features continued on page 6.

ORDERING INFORMATION

PART TEMP RANGE PIN-PACKAGE

DS3131 0°C to +70°C

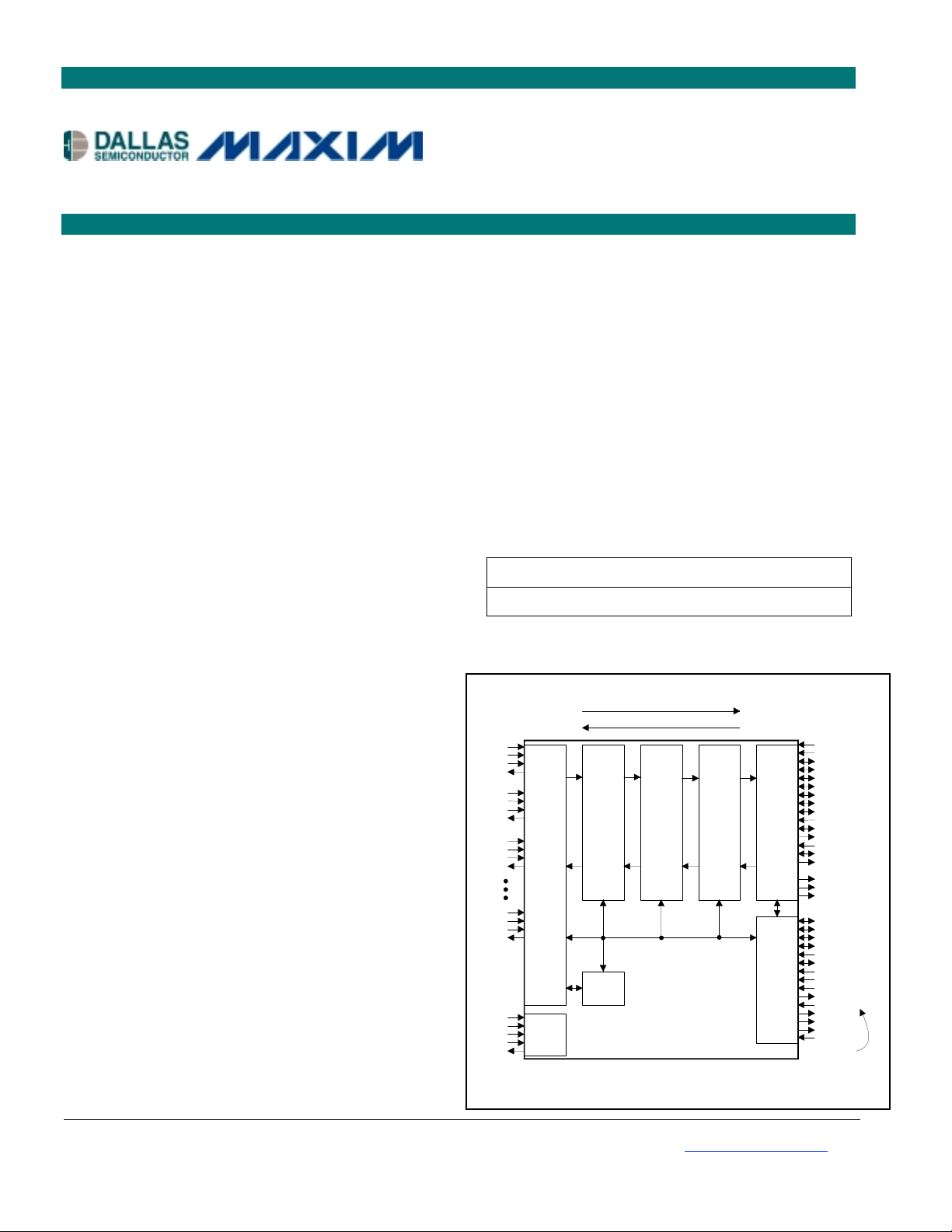

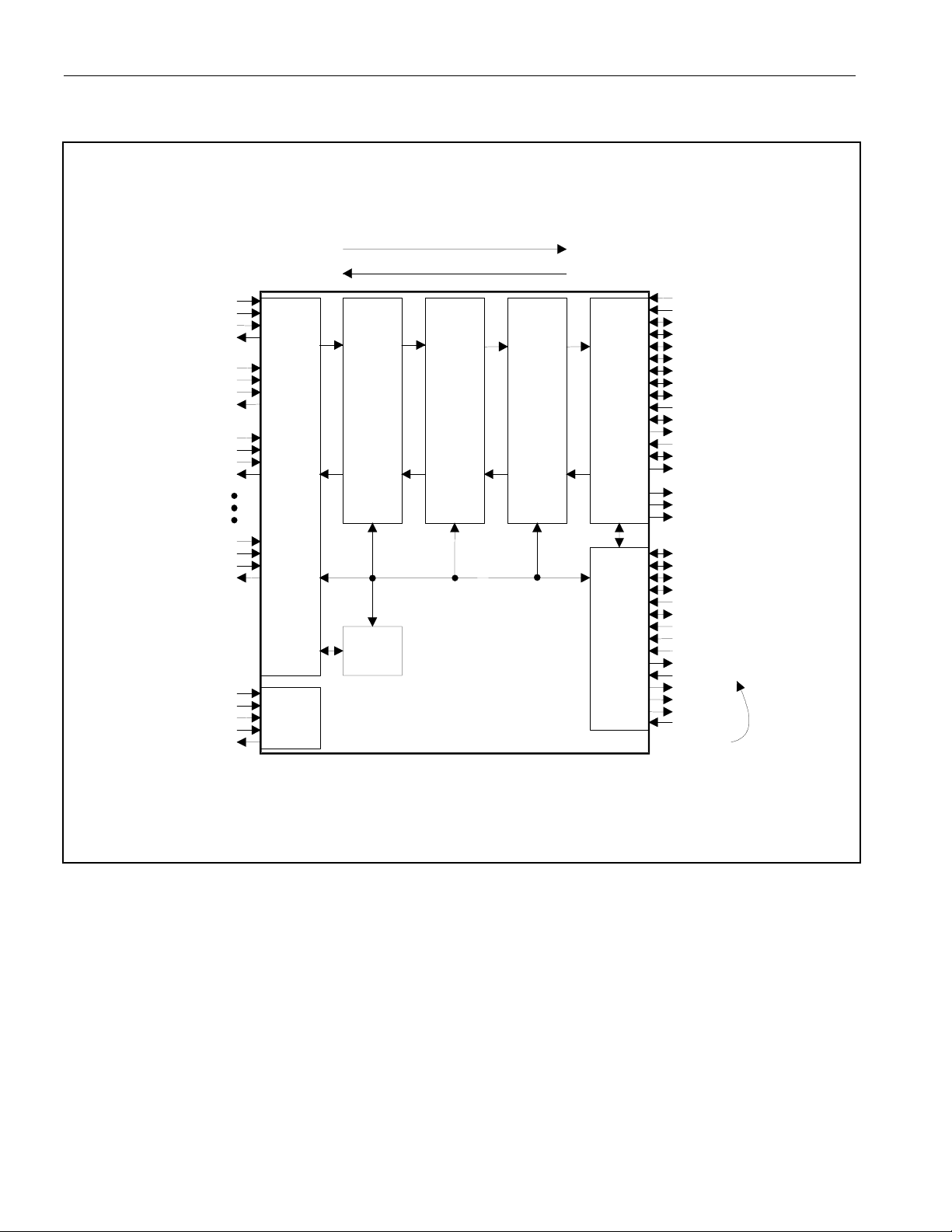

FUNCTIONAL DIAGRAM

RC39

RD39

TRS

JTDI

JTMS

JTCL

JTDO

RC0

RD0

TC0

TD0

RC1

RD1

TC1

TD1

RC2

RD2

TC2

TD2

TC39

TD39

LAYER 1 BLOCK (SECT. 6

JTAG TEST

ACCESS

(SECT. 12)

RECEIVE DIRECTION

TRANSMIT DIRECTION

40-BIT SYNCHRONOUS

HDLC CONTROLLERS (SECT. 7)

BERT

(SECT. 6)

FIFO BLOCK (SECT. 8)

INTERNAL CONTROL BUS

DS3131

272 PBGA

DMA BLOCK (SECT. 9)

PCI BLOCK (SECT. 10)

(SECT. 11)

LOCAL BUS BLOC

PIN NAMES IN ( )

ARE ACTIVE WHEN

THE DEVICE IS IN

THE MOT MODE

(i.e., LIM = 1).

PCLK

PAD[31:0]

CBE[3:0]

PPAR

FRAM

IRD

TRD

STO

PIDSEL

DEVSE

PER

SER

XBLAS

LA[19:0]

LD[15:0]

WR(LR/

RD(LDS)

LIM

LMS

LHOLD(

LHLDA(

BGAC

LCLK

LBPXS

BR)

BG)

)

Note: Some revisions of this dev ice may incorporate deviati ons from published specifications know n as errata. Multiple rev isions of any d evic e

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata

1 of 174 112002

.

Page 2

DS3131

TABLE OF CONTENTS

1. MAIN FEATURES .......................................................................................................................... 6

2. DETAILED DESCRIPTION.......................................................................................................... 7

3. SIGNAL DESCRIPTION..............................................................................................................14

3.1 OVERVIEW/SIGNAL LIST..........................................................................................................................14

3.2 SERIAL PORT INTERFACE SIGNAL DESCRIPTION.....................................................................................20

3.3 LOCAL BUS SIGNAL DESCRIPTION ..........................................................................................................20

3.4 JTAG SIGNAL DESCRIPTION ...................................................................................................................23

3.5 PCI BUS SIGNAL DESCRIPTION ...............................................................................................................24

3.6 PCI EXTENSION SIGNALS ........................................................................................................................26

3.7 SUPPLY AND TEST SIGNAL DESCRIPTION................................................................................................27

4. MEMORY MAP ............................................................................................................................ 28

4.1 INTRODUCTION ........................................................................................................................................28

4.2 GENERAL CONFIGURATION REGISTERS (0XX) ........................................................................................28

4.3 RECEIVE PORT REGISTERS (1XX) ............................................................................................................29

4.4 TRANSMIT PORT REGISTERS (2XX)..........................................................................................................30

4.5 RECEIVE HDLC CONTROL REGISTERS (3XX) .........................................................................................31

4.6 TRANSMIT HDLC CONTROL REGISTERS (4XX).......................................................................................32

4.7 BERT REGISTERS (5XX)..........................................................................................................................33

4.8 RECEIVE DMA REGISTERS (7XX)............................................................................................................33

4.9 TRANSMIT DMA REGISTERS (8XX).........................................................................................................34

4.10 FIFO REGISTERS (9XX)...........................................................................................................................34

4.11 PCI CONFIGURATION REGISTERS FOR FUNCTION 0 (PIDSEL/AXX) ......................................................35

4.12 PCI CONFIGURATION REGISTERS FOR FUNCTION 1 (PIDSEL/BXX).......................................................35

5. GENERAL DEVICE CONFIGURATION AND STATUS/INTERRUPT............................... 36

5.1 MASTER RESET AND ID REGISTER DESCRIPTION ...................................................................................36

5.2 MASTER CONFIGURATION REGISTER DESCRIPTION................................................................................37

5.3 STATUS AND INTERRUPT .........................................................................................................................39

5.3.1 General Description of Operation......................................................................................................39

5.3.2 Status and Interrupt Register Description...........................................................................................41

5.4 TEST REGISTER DESCRIPTION .................................................................................................................46

6. LAYER 1......................................................................................................................................... 47

6.1 GENERAL DESCRIPTION...........................................................................................................................47

6.2 PORT REGISTER DESCRIPTIONS ...............................................................................................................49

6.3 BERT.......................................................................................................................................................51

6.4 BERT REGISTER DESCRIPTION ...............................................................................................................52

7. HDLC .............................................................................................................................................. 59

7.1 GENERAL DESCRIPTION...........................................................................................................................59

7.2 HDLC OPERATION ..................................................................................................................................59

7.3 BIT-SYNCHRONOUS HDLC REGISTER DESCRIPTION ..............................................................................61

8. FIFO ................................................................................................................................................ 65

8.1 GENERAL DESCRIPTION AND EXAMPLE..................................................................................................65

8.1.1 Receive High Watermark....................................................................................................................67

8.1.2 Transmit Low Watermark....................................................................................................................67

8.2 FIFO REGISTER DESCRIPTION.................................................................................................................68

9. DMA ................................................................................................................................................ 74

9.1 INTRODUCTION ........................................................................................................................................74

9.2 RECEIVE SIDE ..........................................................................................................................................76

9.2.1 Overview .............................................................................................................................................76

9.2.2 Packet Descriptors..............................................................................................................................80

9.2.3 Free Queue..........................................................................................................................................82

2 of 174

Page 3

DS3131

9.2.4 Done Queue.........................................................................................................................................87

9.2.5 DMA Configuration RAM...................................................................................................................93

9.3 TRANSMIT SIDE........................................................................................................................................97

9.3.1 Overview .............................................................................................................................................97

9.3.2 Packet Descriptors............................................................................................................................105

9.3.3 Pending Queue..................................................................................................................................107

9.3.4 Done Queue.......................................................................................................................................111

9.3.5 DMA Configuration RAM.................................................................................................................116

10. PCI BUS ........................................................................................................................................ 121

10.1 GENERAL DESCRIPTION OF OPERATION................................................................................................121

10.1.1 PCI Read Cycle.................................................................................................................................122

10.1.2 PCI Write Cycle ................................................................................................................................123

10.1.3 PCI Bus Arbitration..........................................................................................................................124

10.1.4 PCI Initiator Abort............................................................................................................................124

10.1.5 PCI Target Retry...............................................................................................................................125

10.1.6 PCI Target Disconnect......................................................................................................................125

10.1.7 PCI Target Abort...............................................................................................................................126

10.1.8 PCI Fast Back-to-Back......................................................................................................................127

10.2 PCI CONFIGURATION REGISTER DESCRIPTION .....................................................................................128

10.2.1 Command Bits...................................................................................................................................129

10.2.2 Status Bits..........................................................................................................................................130

10.2.3 Command Bits...................................................................................................................................134

10.2.4 Status Bits..........................................................................................................................................135

11. LOCAL BUS................................................................................................................................. 138

11.1 GENERAL DESCRIPTION.........................................................................................................................138

11.1.1 PCI Bridge Mode ..............................................................................................................................141

11.1.2 Configuration Mode..........................................................................................................................143

11.2 LOCAL BUS BRIDGE MODE CONTROL REGISTER DESCRIPTION............................................................145

11.3 EXAMPLES OF BUS TIMING FOR LOCAL BUS PCI BRIDGE MODE OPERATION .....................................147

12. JTAG ............................................................................................................................................. 155

12.1 JTAG DESCRIPTION...............................................................................................................................155

12.2 TAP CONTROLLER STATE MACHINE DESCRIPTION..............................................................................156

12.3 INSTRUCTION REGISTER AND INSTRUCTIONS........................................................................................159

12.4 TEST REGISTERS....................................................................................................................................160

13. AC CHARACTERISTICS .......................................................................................................... 161

14. MECHANICAL DIMENSIONS................................................................................................. 169

14.1 272 PBGA PACKAGE.............................................................................................................................169

15. APPLICATIONS ......................................................................................................................... 170

15.1 T1/E1 AND T3/E3 APPLICATIONS..........................................................................................................170

15.2 DSL AND CABLE MODEM APPLICATIONS .............................................................................................173

15.3 SONET/SDH APPLICATIONS ................................................................................................................174

3 of 174

Page 4

DS3131

LIST OF FIGURES

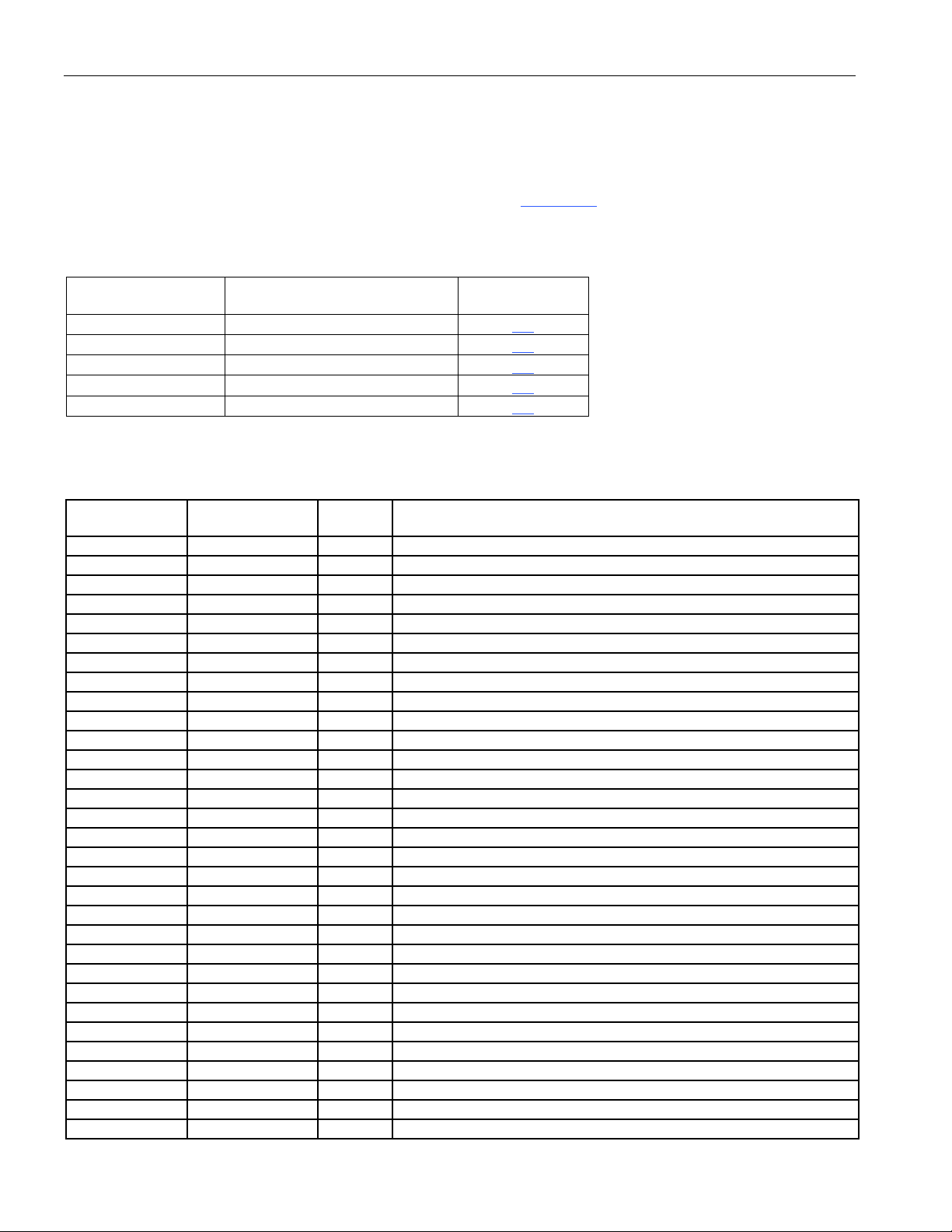

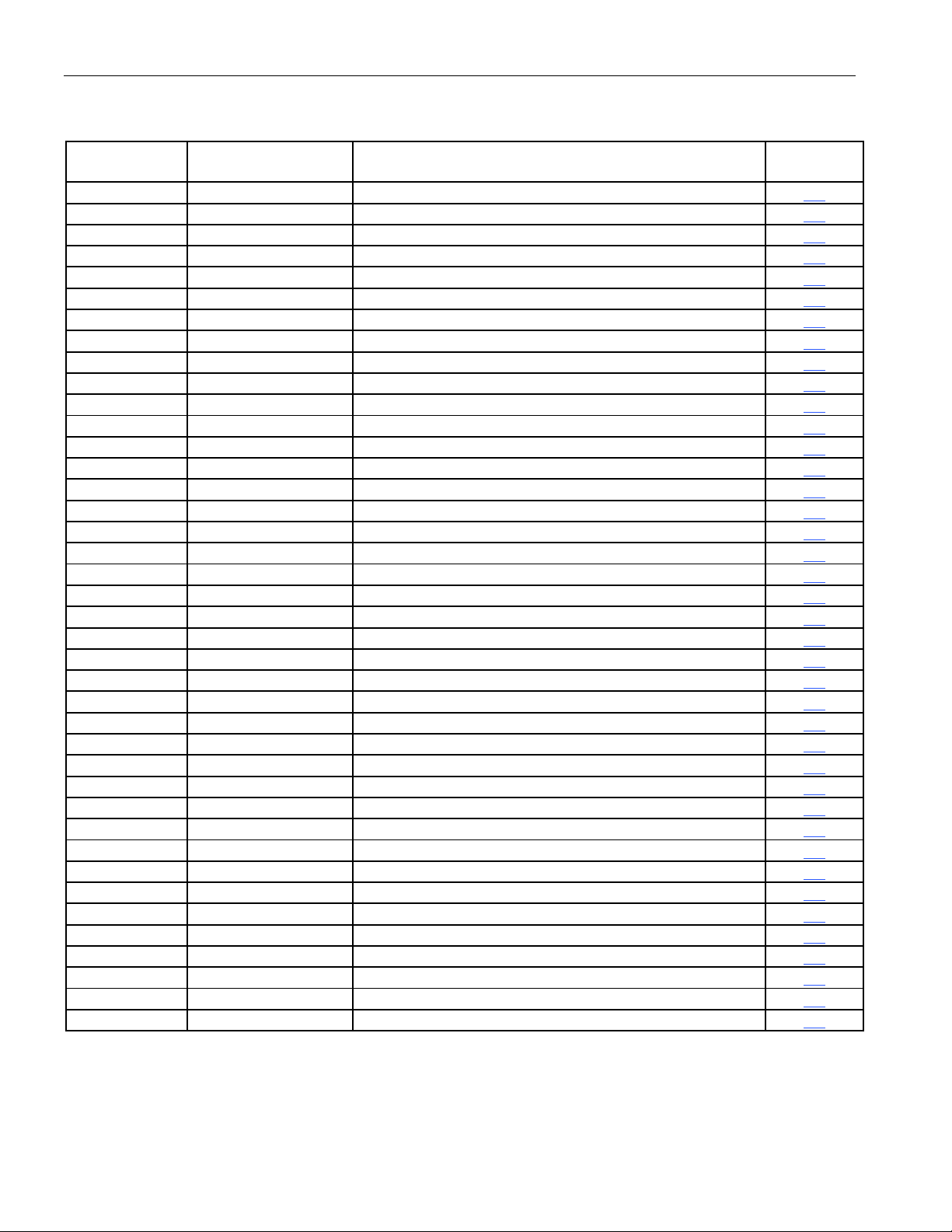

Figure 2-1. Block Diagram ........................................................................................................................10

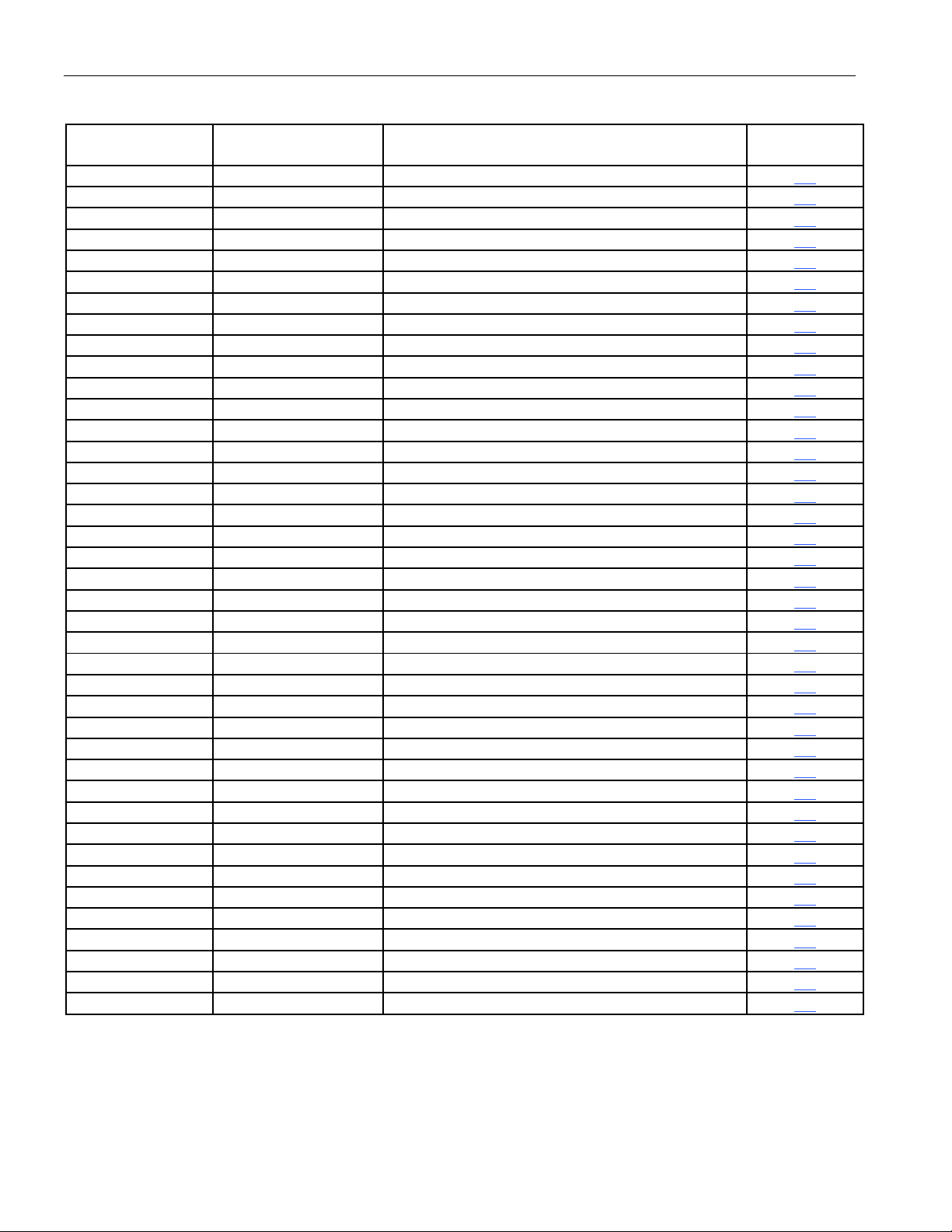

Figure 2-2. Configuration Options.............................................................................................................11

Figure 3-1. Signal Floorplan......................................................................................................................19

Figure 5-1. Status Register Block Diagram for SM...................................................................................40

Figure 6-1. Layer 1 Port Interface Block Diagram ....................................................................................48

Figure 6-2. BERT Mux Diagram...............................................................................................................51

Figure 6-3. BERT Register Set ..................................................................................................................52

Figure 8-1. FIFO Example.........................................................................................................................66

Figure 9-1. Receive DMA Operation.........................................................................................................78

Figure 9-2. Receive DMA Memory Organization.....................................................................................79

Figure 9-3. Receive Descriptor Example...................................................................................................80

Figure 9-4. Receive Packet Descriptors.....................................................................................................81

Figure 9-5. Receive Free-Queue Descriptor ..............................................................................................82

Figure 9-6. Receive Free-Queue Structure ................................................................................................84

Figure 9-7. Receive Done-Queue Descriptor.............................................................................................87

Figure 9-8. Receive Done-Queue Structure...............................................................................................89

Figure 9-9. Receive DMA Configuration RAM ........................................................................................93

Figure 9-10. Transmit DMA Operation.....................................................................................................99

Figure 9-11. Transmit DMA Memory Organization ...............................................................................100

Figure 9-12. Transmit DMA Packet Handling.........................................................................................101

Figure 9-13. Transmit DMA Priority Packet Handling ........................................................................... 102

Figure 9-14. Transmit DMA Error Recovery Algorithm.........................................................................104

Figure 9-15. Transmit Descriptor Example .............................................................................................105

Figure 9-16. Transmit Packet Descriptors ...............................................................................................106

Figure 9-17. Transmit Pending-Queue Descriptor...................................................................................107

Figure 9-18. Transmit Pending-Queue Structure.....................................................................................109

Figure 9-19. Transmit Done-Queue Descriptor .......................................................................................111

Figure 9-20. Transmit Done-Queue Structure .........................................................................................113

Figure 9-21. Transmit DMA Configuration RAM...................................................................................116

Figure 10-1. PCI Configuration Memory Map........................................................................................121

Figure 10-2. PCI Bus Read ......................................................................................................................122

Figure 10-3. PCI Bus Write .....................................................................................................................123

Figure 10-4. PCI Bus Arbitration Signaling Protocol..............................................................................124

Figure 10-5. PCI Initiator Abort ..............................................................................................................124

Figure 10-6. PCI Target Retry .................................................................................................................125

Figure 10-7. PCI Target Disconnect ........................................................................................................125

Figure 10-8. PCI Target Abort.................................................................................................................126

Figure 10-9. PCI Fast Back-to-Back........................................................................................................127

Figure 11-1. Bridge Mode........................................................................................................................ 139

Figure 11-2. Bridge Mode with Arbitration Enabled...............................................................................139

Figure 11-3. Configuration Mode............................................................................................................140

Figure 11-4. Local Bus Access Flowchart...............................................................................................144

Figure 11-5. 8-Bit Read Cycle.................................................................................................................147

Figure 11-6. 16-Bit Write Cycle ..............................................................................................................148

Figure 11-7. 8-Bit Read Cycle.................................................................................................................149

Figure 11-8. 16-Bit Write (Only Upper 8 Bits Active) Cycle .................................................................150

4 of 174

Page 5

DS3131

Figure 11-9. 8-Bit Read Cycle.................................................................................................................151

Figure 11-10. 8-Bit Write Cycle ..............................................................................................................152

Figure 11-11. 16-Bit Read Cycle.............................................................................................................153

Figure 11-12. 8-Bit Write Cycle ..............................................................................................................154

Figure 12-1. Block Diagram ....................................................................................................................155

Figure 12-2. TAP Controller State Machine............................................................................................156

Figure 13-1. Layer 1 Port AC Timing Diagram.......................................................................................162

Figure 13-2. Local Bus Bridge Mode (LMS = 0) AC Timing Diagram..................................................163

Figure 13-3. Local Bus Configuration Mode (LMS = 1) AC Timing Diagrams.....................................165

Figure 13-4. PCI Bus Interface AC Timing Diagram..............................................................................167

Figure 13-5. JTAG Test Port Interface AC Timing Diagram..................................................................168

Figure 15-1. 28 T1 Lines Demuxed from a T3 Line................................................................................170

Figure 15-2. Multiport T1 or E1 Application ..........................................................................................171

Figure 15-3. Unchannelized T3 or E3 Application..................................................................................172

Figure 15-4. DSLAM/Cable Modem Application...................................................................................173

Figure 15-5. SONET/SDH Overhead Termination Application..............................................................174

LIST OF TABLES

Table 1-A. Data Sheet Definitions...............................................................................................................7

Table 2-A. Restrictions ..............................................................................................................................12

Table 2-B. Initialization Steps ...................................................................................................................13

Table 2-C. Indirect Registers .....................................................................................................................13

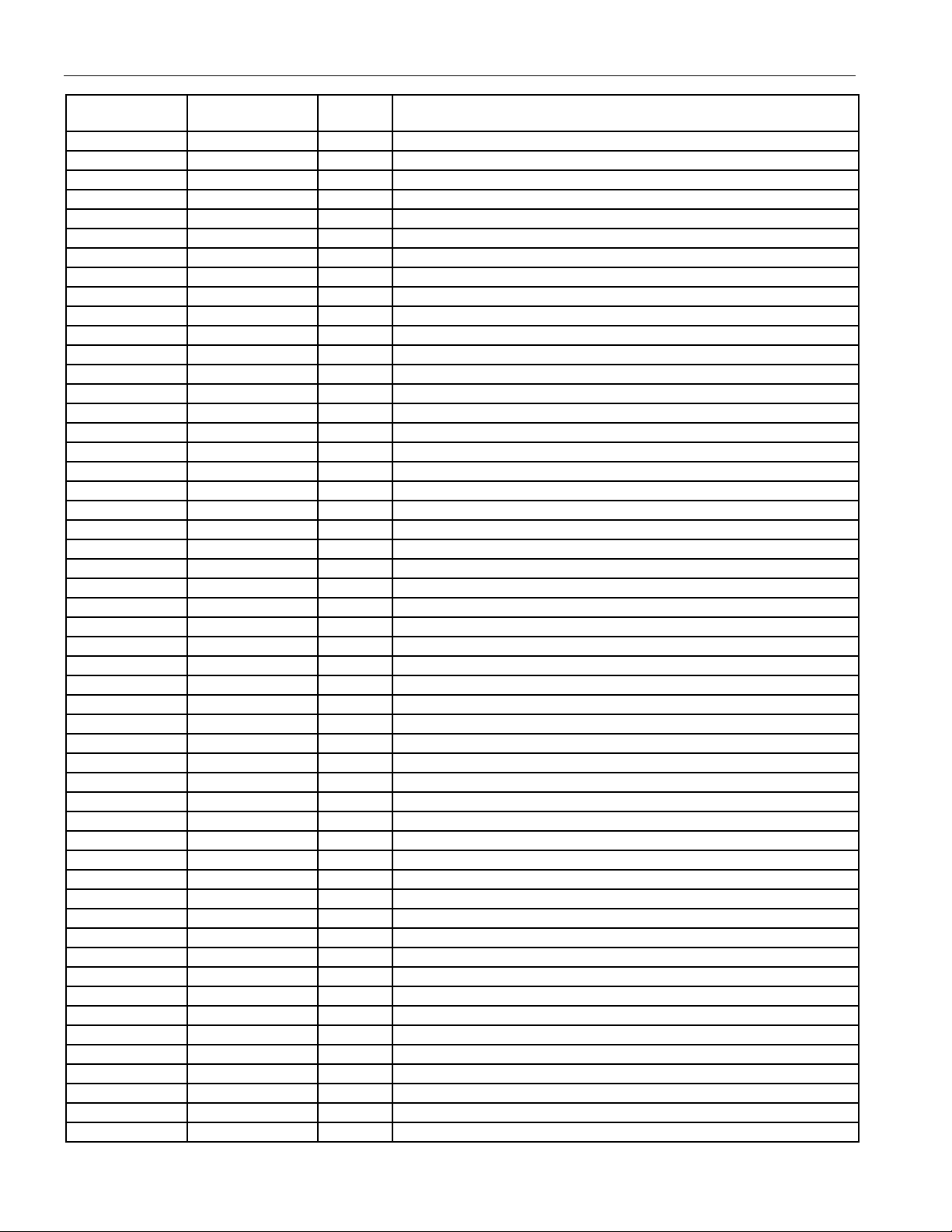

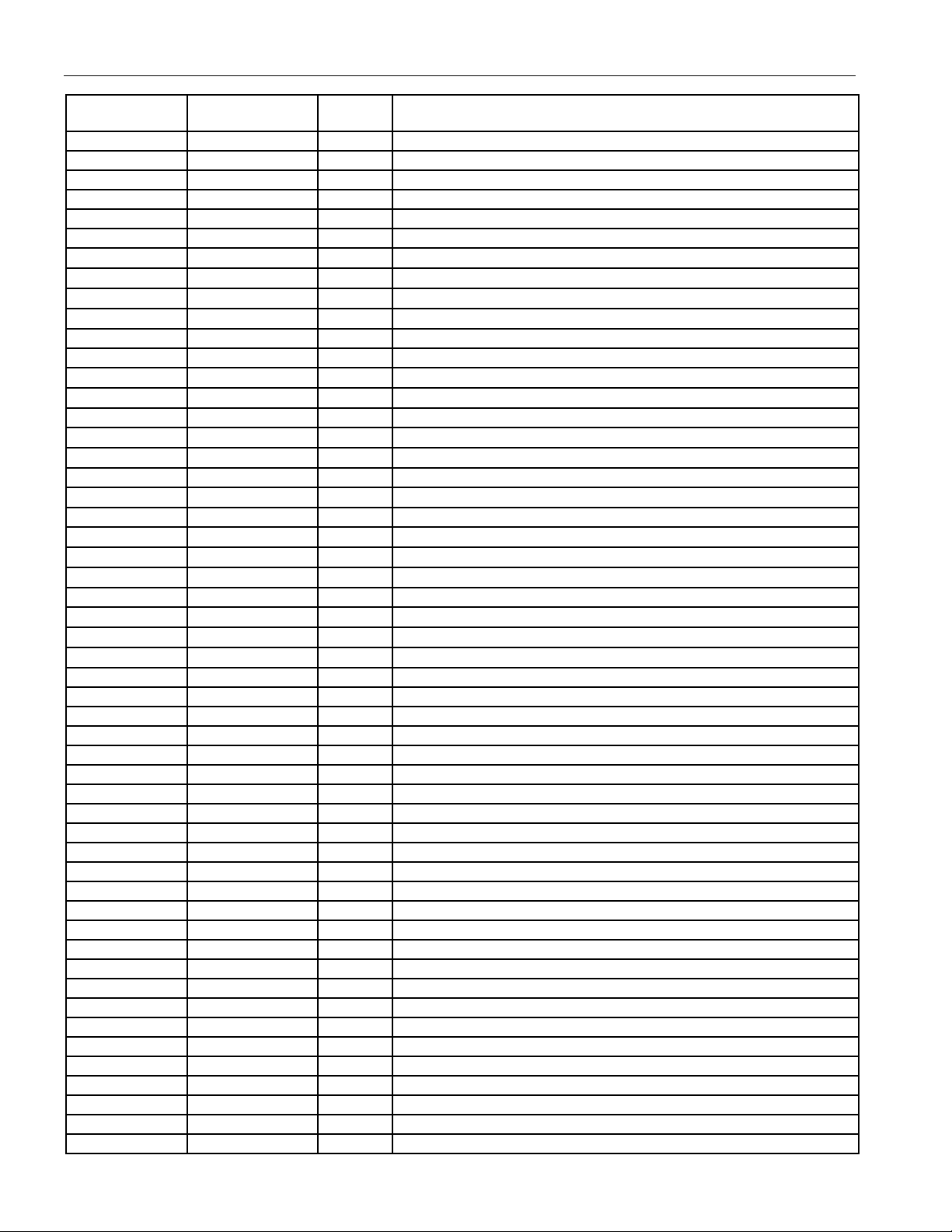

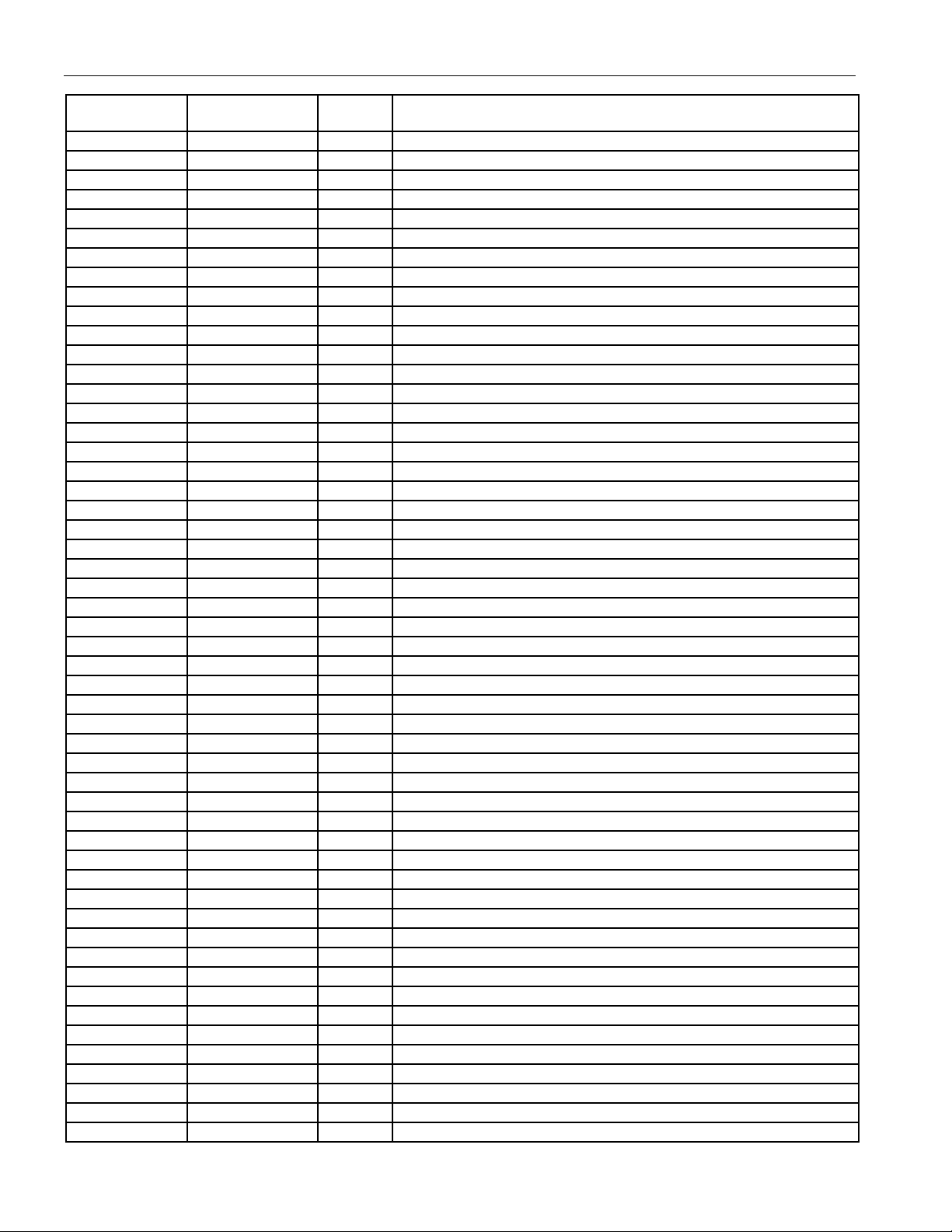

Table 3-A. Signal Description ...................................................................................................................14

Table 4-A. Memory Map Organization .....................................................................................................28

Table 6-A. HDLC Channel Assignment....................................................................................................47

Table 6-B. Port Configuration Options......................................................................................................47

Table 7-A. HDLC Channel Assignment....................................................................................................59

Table 7-B. Receive Bit-Synchronous HDLC Packet Processing Outcomes .............................................60

Table 7-C. Receive Bit-Synchronous HDLC Functions............................................................................ 60

Table 7-D. Transmit Bit-Synchronous HDLC Functions..........................................................................61

Table 8-A. FIFO Priority Algorithm Select...............................................................................................65

Table 9-A. DMA Registers to be Configured by the Host on Power-Up..................................................75

Table 9-B. Receive DMA Main Operational Areas...................................................................................77

Table 9-C. Receive Descriptor Address Storage .......................................................................................80

Table 9-D. Receive Free-Queue Read/Write Pointer Absolute Address Calculation................................83

Table 9-E. Receive Free-Queue Internal Address Storage ........................................................................83

Table 9-F. Receive Done-Queue Internal Address Storage.......................................................................88

Table 9-G. Transmit DMA Main Operational Areas.................................................................................97

Table 9-H. Done-Queue Error-Status Conditions....................................................................................103

Table 9-I. Transmit Descriptor Address Storage .....................................................................................105

Table 9-J. Transmit Pending-Queue Internal Address Storage................................................................108

Table 9-K. Transmit Done-Queue Internal Address Storage...................................................................112

Table 11-A. Local Bus Signals (LBPXS Floating or Connected High) ..................................................138

Table 11-B. Local Bus 8-Bit Width Address, LBHE Setting ..................................................................141

Table 11-C. Local Bus 16-Bit Width Address, LD, LBHE Setting.........................................................142

Table 12-A. Instruction Codes.................................................................................................................159

5 of 174

Page 6

DS3131

1. MAIN FEATURES

Layer 1

40 independent bit-synchronous physical ports

capable of speeds up to 52Mbps

Each port can be independently configured

Loopback in both directions (receive to transmit

and transmit to receive)

On-board BERT generation and detection

HDLC

40 independent full-duplex HDLC channels

132Mbps throughput in both the receive and

transmit directions with a 33MHz PCI clock

Transparent mode

Automatic flag detection and generation

Shared opening and closing flag

Interframe fill

Zero stuffing and destuffing

CRC16/32 checking and generation

Abort detection and generation

CRC error and long/short frame-error detection

Bit flip

Invert data

FIFO

Large 8kB receive and 8kB transmit buffers

maximize PCI bus efficiency

Small block size of 16 Bytes allows maximum

flexibility

Programmable low and high watermarks

Programmable HDLC channel priority setting

Governing Specifications

The DS3131 fully meets the following specifications:

•= ANSI (American National Standards Institute) T1.403-1995 Network-to-Customer Installation DS1 Metallic

Interface March 21, 1995

•= PCI Local Bus Specification V2.1 June 1, 1995

•= ITU Q.921 March 1993

•= ISO Standard 3309-1979 Data Communications–HDLC Procedures–Frame Structure

DMA

Efficient scatter-gather DMA minimizes PCI bus

accesses (same as the DS3134 Chateau)

Programmable small and large buffer sizes up to

8191 Bytes and algorithm select

Descriptor bursting to conserve PCI bus

bandwidth

Programmable packet-storage address offset

Identical receive and transmit descriptors

minimize host processing in store-and-

forward

Automatic channel disabling and enabling on

transmit errors

Receive packets are timestamped

Transmit packet priority setting

PCI Bus

32-bit, 33MHz

Version 2.1 Compliant; See t5 in the PCI Bus

AC Characteristics for a 1ns exception.

Note: This does not affect real- w orld

designs. DS3131 V

than the PCI specification, as detailed in the

first page of Section 13

Contains extension signals that allow adoption to

custom buses

Can burst up to 256 32-bit words to maximize

bus efficiency

is also slightly higher

IH

.

Local Bus

Can operate as a bridge from the PCI bus or a

configuration bus

Can arbitrate for the bus when in bridge mode

8 or 16 bits wide

Supports a 1MB address space when in bridge

mode

Supports Intel and Motorola bus timing

JTAG Test Access

3.3V low-power CMOS with 5V tolerant I/Os

272-pin plastic BGA package (27mm x 27mm)

6 of 174

Page 7

DS3131

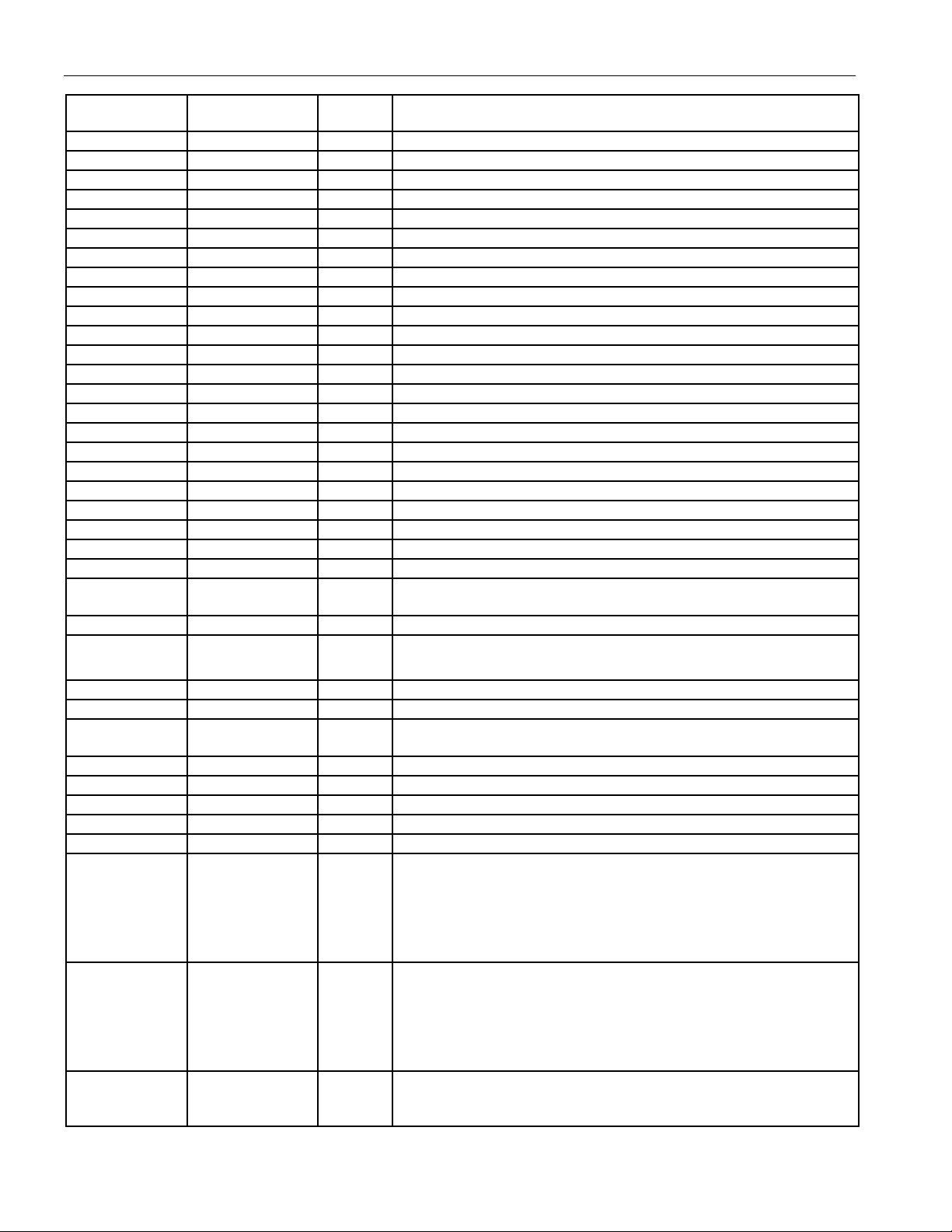

Table 1-A. Data Sheet Definitions

The following terms are used throughout this data sheet.

Note: The DS3131’s ports are numbered 0 t o 39; the HDLC channel s are numbered 1 to 40. HDLC Channel 1 is always associated wi th Port

0, HDLC Channel 2 with Port 1, and so on.

TERM DEFINITION

BERT Bit Error-Rate Tester

Descriptor A message passed back and forth between the DMA and the host

Dword Double word; a 32-bit data entity

DMA Direct Memory Access

FIFO First In, First Out. A temporary memory storage scheme.

HDLC High-Level Data-Link Control

Host The main controller that resides on the PCI Bus

n/a Not assigned

2. DETAILED DESCRIPTION

The DS3131 BoSS HDLC controller is based on Dallas Semiconductor’s DS3134 CHATEAU HDLC

controller. Both devices share the same DMA and FIFO structure as well as the same signal locations for

the local bus and the PCI bus. The primary difference between the two devices is in the Layer 1

functionality. The CHATEAU supports channelized T1/E1 whereas the BoSS does not. Therefore, the

Layer 1 functions in the CHATEAU that support channelized interfaces do not exist in the BoSS.

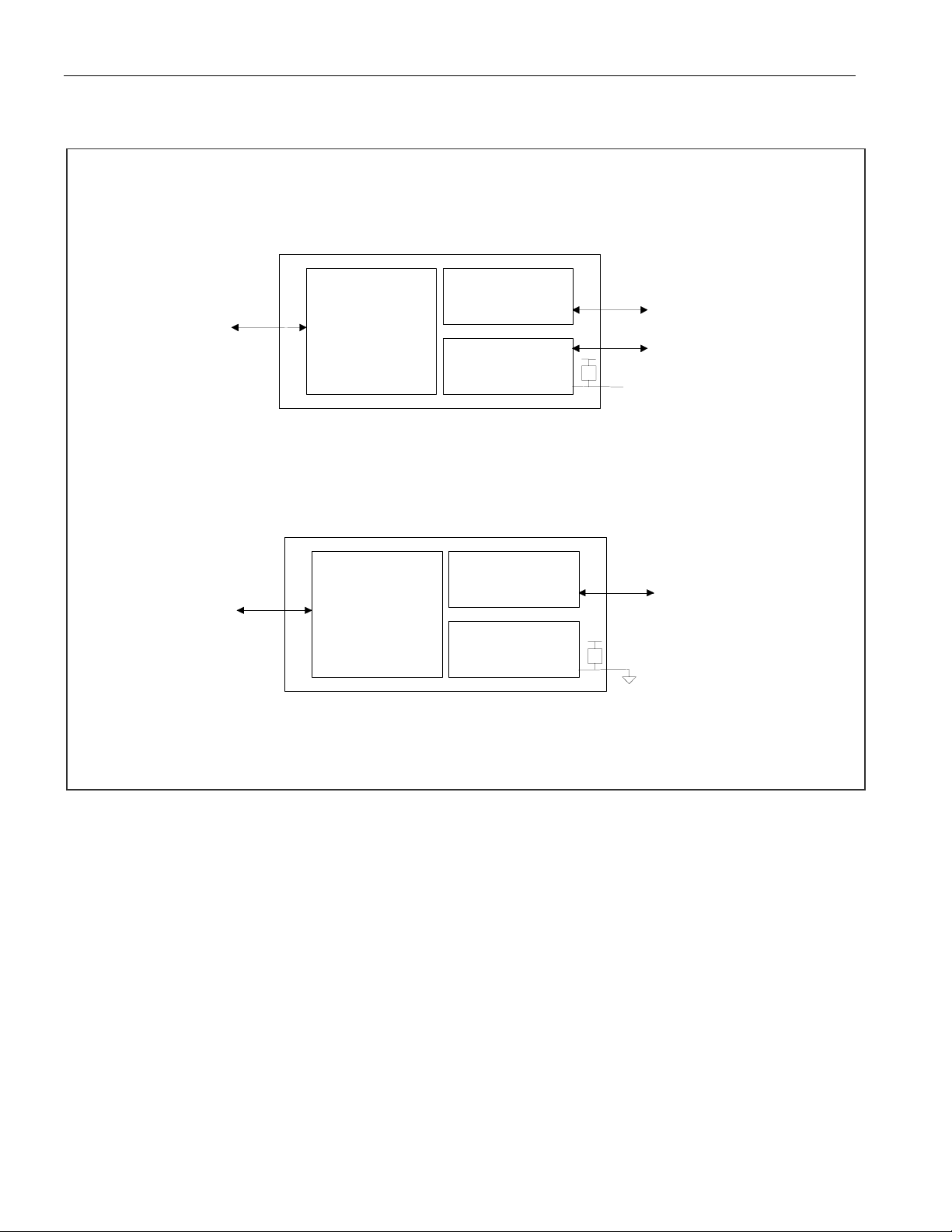

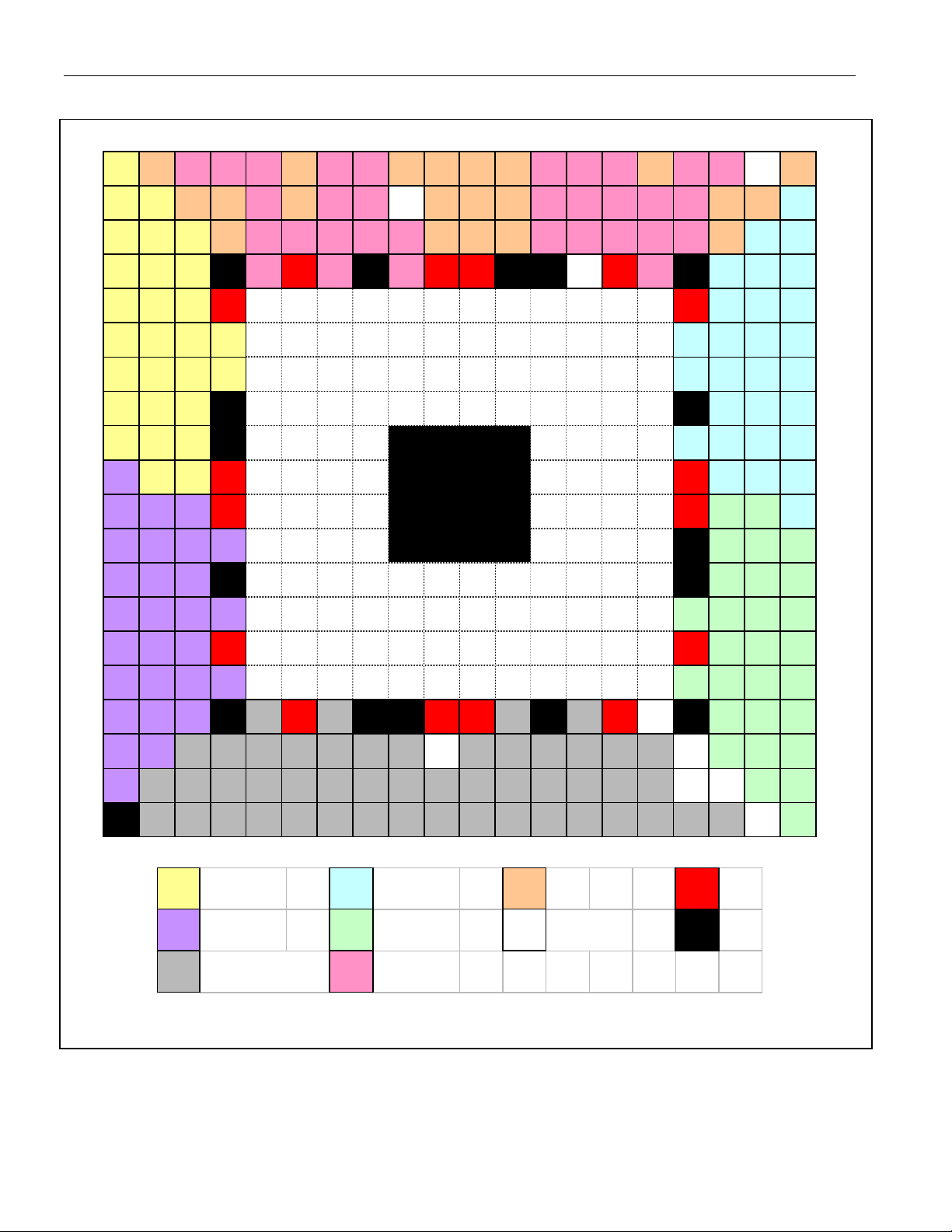

Figure 2-1 shows the major blocks of the device. The DS3131 can be operated in two configurations

depending on whether the local bus is enabled or not (Figure 2-2).

The Layer 1 block handles the physical input and output of serial data to and from the DS3131. The

DS3131 is capable of operating in a number of modes and can be used in many applications requiring

high-density and high-speed HDLC termination. Section 15 details a few common applications for the

DS3131. The Layer 1 block prepares the incoming data for the HDLC block and grooms data from the

HDLC block for transmission. The Layer 1 block interfaces directly to the BERT block. The BERT

block can generate and detect both pseudorandom and repeating bit patterns and is used to test and stress

data communication links. The BERT block is a global chip resource that can be assigned to an y one of

the 40 bit-synchronous ports.

The DS3131 BoSS is composed of 40 bit-synchronous HDLC controllers (one for each port) that are

each capable of operating at speeds up to 52Mbps. The bit-synchronous HDLC controllers also have

serial interfaces. The HDLC controllers perform all of the Layer 2 processing, which includes zero

stuffing and destuffing, flag generation and detection, CRC generation and checking, and abort

generation and checking.

In the receive path, the f ollowing process occurs. The HDLC controllers collect the incoming data and

then signal the FIFO that the controller has data to transfer. The 40 ports are priority decoded (Port 0 gets

the highest priority) for the data transfer from the HDLC controllers to the FIFO block. There is no

priority of transfer between the HDLC controllers and the FIFO because the DS3131 handles up to

132Mbps in both the receive and the transmit directions without any potential data loss because of

priority conflicts.

7 of 174

Page 8

DS3131

The FIFO transfers data from the HDLC engines into the FIFO and checks to see if the FIFO has filled to

beyond the programmable high watermark. If it has, the FIFO signals to the DMA that data is ready to be

burst read from the FIFO to the PCI bus. The FIFO block controls the DMA block and it tells the DMA

when to transfer data from the FIFO to the PCI bus. Since the DS3131 can handle multiple HDLC

channels, it is possible that at any one time, several HDLC channels may need to have data transferred

from the FIFO to the PCI bus. The FIFO determines which HDLC channel the DMA handles next

through a host configurable algorithm, which allows the selection to be either round robin or priority,

decoded (with HDLC channel 1 getting the highest priority). Depending on the application, the selection

of this algorithm can be quite important. The DS3131 cannot control when it is granted PCI bus access

and, if bus access is restricted, then the host may wish to prioritize which HDLC channels get top

priority access to the PCI bus when it is granted to the DS3131.

When the DMA transfers data from the FIFO to the PCI bus, it burst reads all available data in the FIFO

(even if the FIFO contains multiple HDLC packets) and tries to empty the FIFO. If an incoming HDLC

packet is not large enough to fill the FIFO to the high watermark, then the FIFO does not wait for more

data to enter. It signals the DMA that an end-of-frame (EOF) w as detected and that data is ready to be

transferred from the FIFO to the PCI bus.

In the transmit path, a very similar process occurs. As soon as an HDLC channel is enabled, the H DLC

(Layer 2) engines begin requesting data from the FIFO. Like the receive side, the 40 ports are priorit y

decoded with port 0 (HDLC channel #1) getting the highest priority. Therefore, if multiple ports are

requesting packet data, the FIFO first satisfies the requirements on all the enabled HDLC channels in the

lower numbered ports before moving to the higher numbered ports. Again, there is no potential data loss

as long as the transmit throughput maximum of 132Mbps is not exceeded. When the FIFO detects that an

HDLC engine needs data, it then transfers the data from the FIFO to the HDLC engines. If the FIFO

detects it is below the low watermark, it checks with the DMA to see if there is any data available for

that HDLC channel. The DMA knows if any data is available because the host on the PCI bus has

informed it of such through the pending-queue descriptor. When the DM A detects that data is avail able,

it informs the FIFO, which then decides which HDLC channel gets the highest priority to the DMA to

transfer data from the PCI bus into the FIFO. Again, since the DS3131 can handle multiple HDLC

channels, it is possible that at any one time, several HDLC channels may need the DMA to burst data

from the PCI bus into the FIFO. The FIFO determines which HDLC channel the DMA handles next

through a host-configurable algorithm, which allows the selection to be either round robin or priority

decoded (with HDLC channel 1 getting the highest priority).

When the DMA begins burst-writing data into the FIFO, it tries to completely fill the FIFO with HDLC

packet data even if it that means writing multiple packets. Once the FIFO detects that the DMA has filled

it to beyond the low watermark (or an EOF is reached), the FIFO begins transferring data to the HDLC

controller.

One of the DS3131’s unique attributes is the DMA’s structure. The DMA maintains maximum

flexibility, yet reduces the number of bus cycles required to transfer packet data. The DMA uses a

flexible scatter/gather technique, which all ows that packet data to be placed anywhere within the 32-bit

address space. The user has the option on the receive side of two different buffer siz es, which are called

“large” and “small” but that can be set to an y size up to 8191 Bytes. The user can choose to store the

incoming data in the large buffers, in the small buffers, or in the small buffers first, filling the large

buffers as needed. The varying buffer storage options allow the user to make the best use of available

memory and balance the trade-off between latency and bus utilization.

8 of 174

Page 9

DS3131

The DMA uses a set of descriptors to know where to store the incoming H D LC packet data and wh ere to

obtain HDLC packet data ready to be transmitted. The descriptors are fixed-size messages that are

handed back and forth from the DMA to the host. Since this descriptor transfer uses bus cycles, the

DMA has been structured to minimize the number of transfers required. For example, on the receive

side, the DMA obtains descriptors from the host to know where in the 32-bit address space to place the

incoming packet data. These descriptors are known as free-queue descriptors. When the DMA reads

these descriptors off the PCI bus, they provide all the information the DMA needs to store the incoming

data. Unlike other existing scatter/gather DMA arc hitectures, the DS3131 D MA does not need additional

bus cycles to determine where to place the data. Other DMA archite ctures tend to use pointers, which

require them to go back onto the bus to obtain more information and hence use more bus cycles.

Another technique the DMA uses to maximize bus utilization is burst reading and writing the

descriptors. The BoSS can be enabled to read and write the d escriptors in bu rsts of 8 or 1 6 instead o f one

at a time. Since there is fixed overhead associated with each bus transaction, the ability to burst read and

write descriptors allows the device to share the bus overhead among 8 or 16 descriptor transactions,

reducinga the total number of bus cycles needed.

The DMA can also burst up to 256 dwords (1024 Bytes) onto the PCI bus. This helps minimize bus

cycles by allowing the device to burst large amounts of data in a smaller number of bus transactions.

This reduces bus cycles by reducing the amount of fixed overhead placed on the bus.

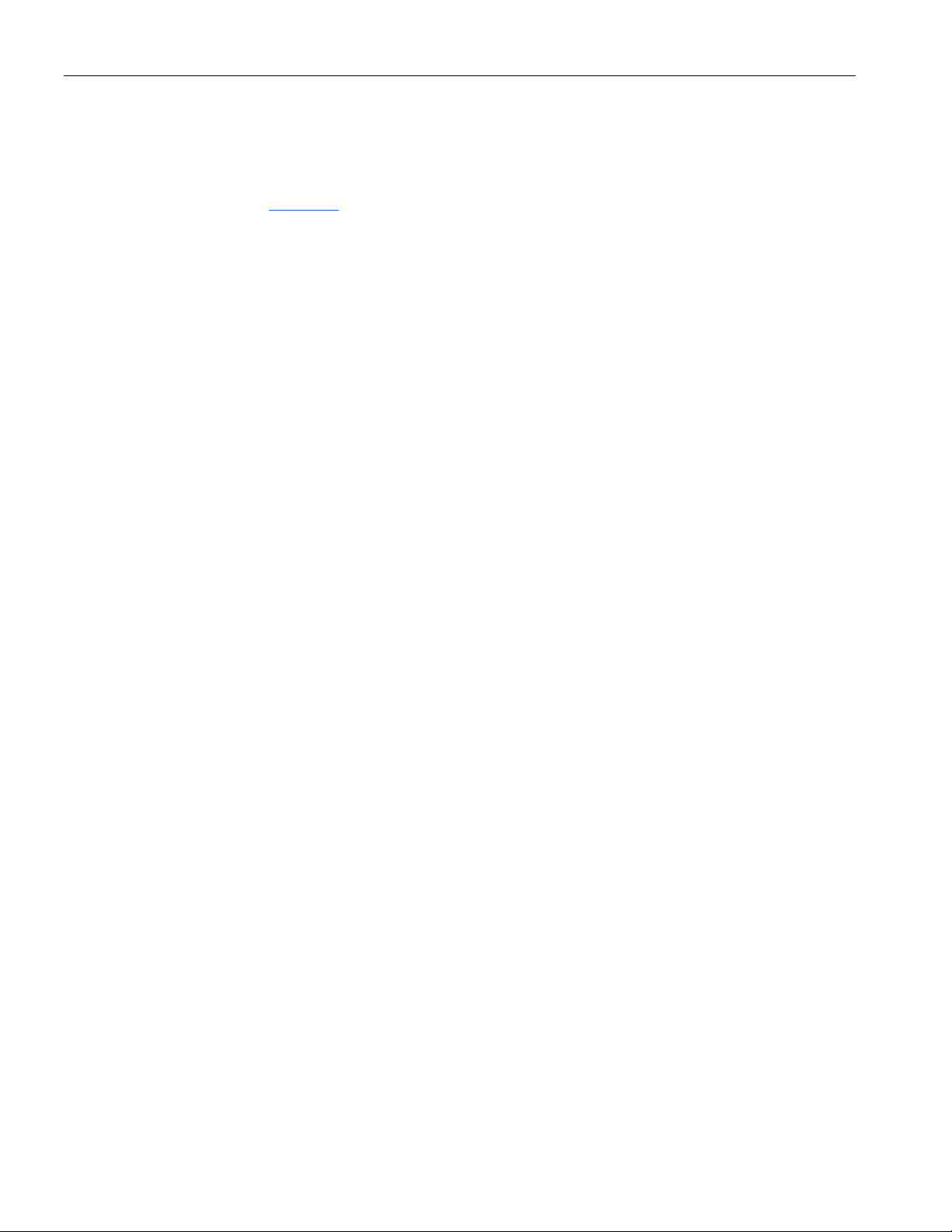

When the local bus is enabled, ports 28 to 39 (HDLC channels 29 to 40) are disabled to make room for

the signals needed by the local bus. The local bus block has two modes of operation. It can be us ed as a

bridge from the PCI bus, in which case it is a bus master. It can also be used as a confi guration bus, in

which case it is a bus slave. The bridge mode allows the host on the PCI bus to access the local bus. The

DS3131 maps data from the PCI bus to the local bus. In the configuration mode, the local bus is used

only to control and monitor the DS3131, while the HDLC packet data is still transferred to the host

through the PCI bus.

9 of 174

Page 10

Figure 2-1. Block Diagram

K

PRST

P

P

E

P

Y

P

Y

P

P

P

L

P

L

PREQ

PGNT

P

R

P

R

PXAS

PXDS

P

T

J

T

K

LWR

L

LINT

LRDY

LCS

R

G)L

K

K

A

LBHE

K

DS3131

RECEIVE DIRECTION

TRANSMIT DIRECTION

RC0

RD0

RC1

RD1

RC2

RD2

RC39

RD39

TC39

TD39

TRS

JTDI

JTMS

JTCL

JTDO

TC0

TD0

TC1

TD1

TC2

TD2

LAYER 1 BLOCK (SECT. 6)

JTAG

TEST

ACCESS

(SECT. 12)

CONTROLLERS (SECT. 7)

40-BIT SYNCHRONOUS HDLC

BERT

(SECT. 6)

FIFO BLOCK (SECT. 8)

DMA BLOCK (SECT. 9)

INTERNAL CONTROL BUS

DS3131

PCI BLOCK (SECT. 10)

(SECT. 11)

LOCAL BUS BLOC

PIN NAMES IN ( )

THE DEVICE IS IN

THE MOT MODE

(i.e., LIM = 1).

PCL

PAD[31:0]

CBE[3:0]

PPAR

FRAM

IRD

TRD

STO

IDSE

DEVSE

PER

SER

XBLAS

LA[19:0]

LD[15:0]

(LR/W)

RD(LDS)

LIM

LMS

LHOLD(LB

LHLDA(LB

LCL

LBPXS

)

BGAC

RE ACTIVE WHEN

10 of 174

Page 11

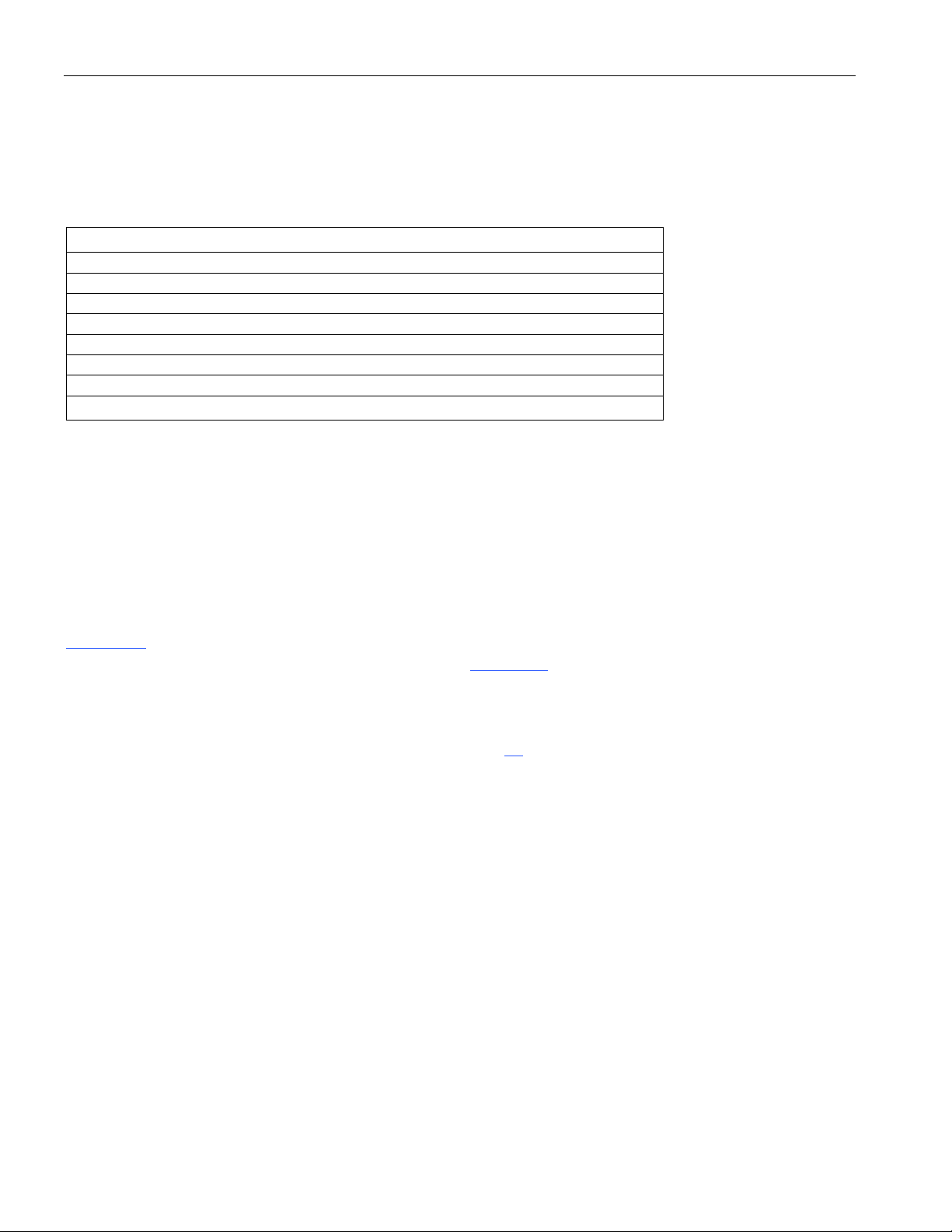

Figure 2-2. Configuration Options

28 Bit-Synchronous Ports/Local Bus Enabled (Default State)

DS3131

28 Serial

Interfaces

(Ports 0 to 27)

40 Serial

Interfaces

(Ports 0 to 39)

PCI Bus

28

Bit-Synchronous

HDLC Controllers

Local Bus

LBPXS

PU

Open-Circuited

40 Bit-Synchronous Ports/Local Bus Disabled

PCI Bus

40

Bit-Synchronous

HDLC Controllers

Local Bus

LBPXS

PU

11 of 174

Page 12

DS3131

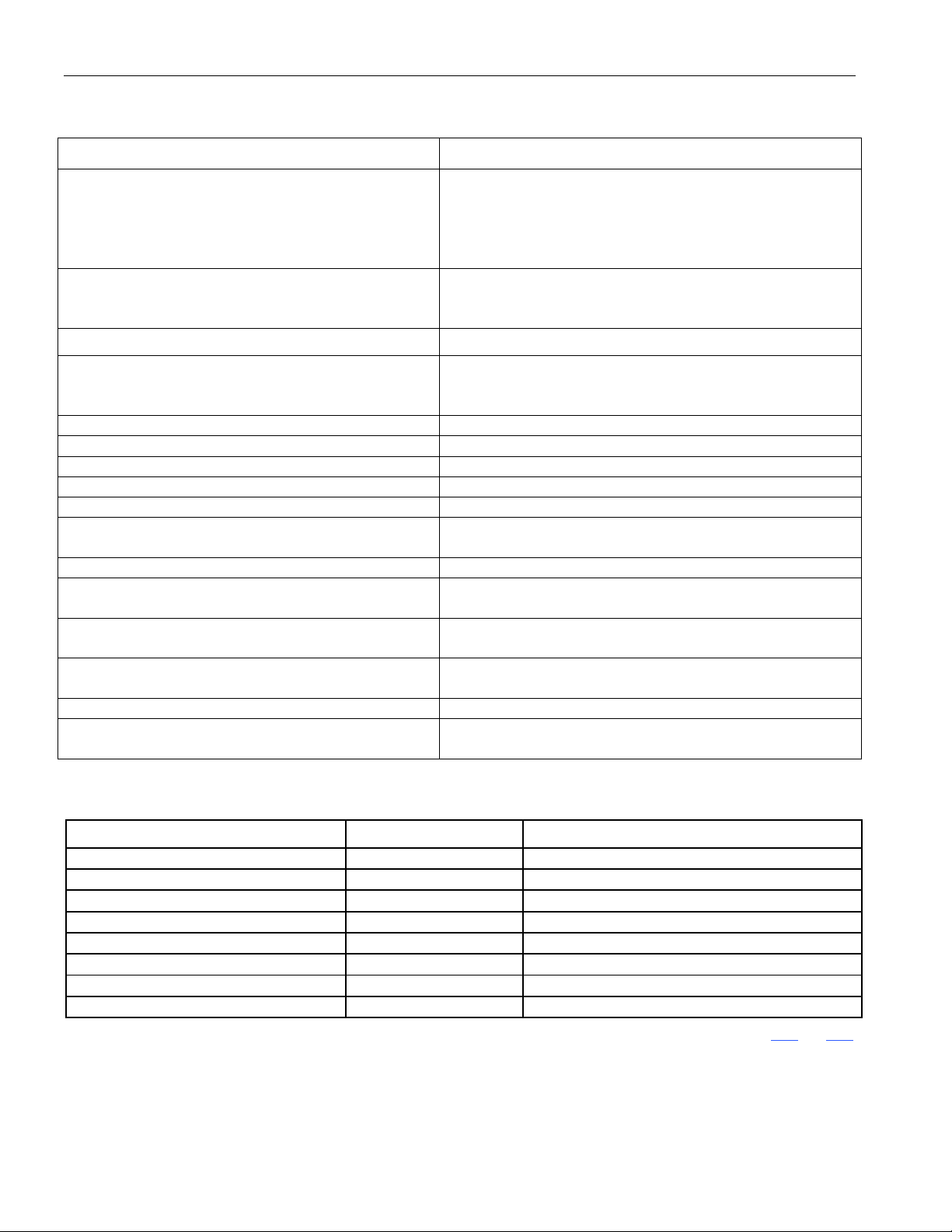

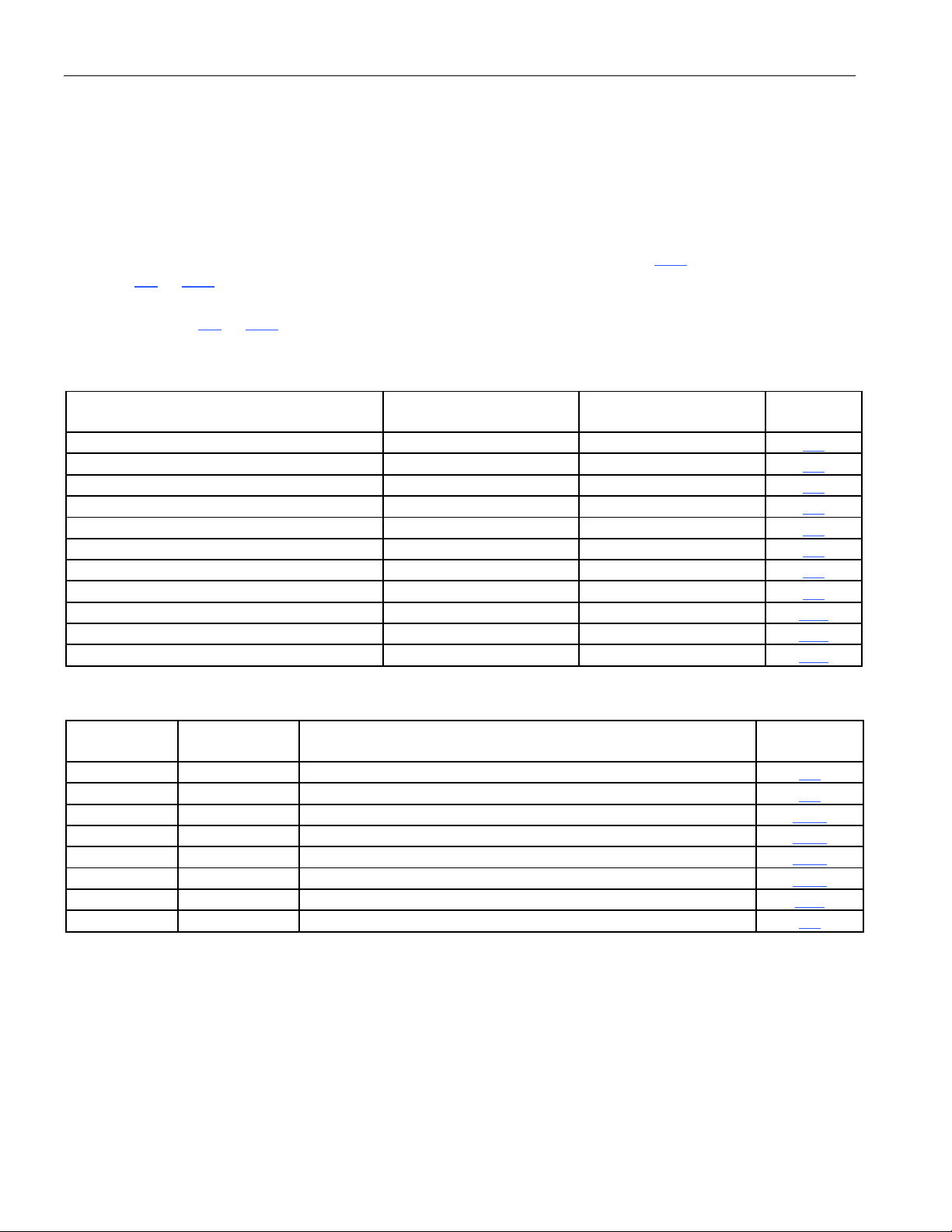

Restrictions

In creating the overall system architecture, the user must balance the port, throughput, and HDLC

channel restrictions of the DS3131. Table 2-A lists all of the upper-bound maximum restrictions.

Table 2-A. Restrictions

ITEM RESTRICTION

Port

Throughput

HDLC

Maximum of 40 physical ports

Maximum data rate of 52Mbps

Maximum receive: 132Mbps (Refer to Application Note 358: DS3134

PCI Bus Utilization.)

Maximum transmit: 132Mbps

Maximum of 40 channels

Internal Device Configuration Registers

All internal device configuration registers (with the exception of the PCI configuration registers, which

are 32-bit registers) are 16 bits wide and are not byte addressable. When the host on the PCI bus accesses

these registers, the particular combination of byte enables (i.e., PCBE signals) is not important, but at

least one of the byte enables must be asserted for a transaction to occur. All registers are read/write,

unless otherwise noted. Reserved bits should not be modified to allow for future upgrades to the d evice.

These bits should be treated as having no meaning and could be either 0 or 1 when read.

Initialization

On a system reset (which can be invoked b y either hardware a ction through the PRST signal or software

action through the RST control bit in the master reset and ID register), all of the internal device

configuration registers are set to 0 (0000h). The local bus bridge mode control register (LBBMC) is not

affected by a software-invoked system reset; it is forced to all zeros only by a hardware reset. The

internal registers that are access ed indirectl y (these are listed as “indirect r egisters” in the data sheet and

consist of the port DS0 configuration registers in the Layer 1 block, the DMA configuration RAMs, and

the FIFO registers) are not affe cted by a system reset, so they must be configured on power-up by the

host to a proper state.

By design, the DS3131 BoSS does not take control of the PCI bus upon power-up. All physical ports

start up by sending all ones (not the HDLC idle code), so the BoSS is idle upon power-up. Please note,

however, that the BoSS uses internal RAM to periodically store and retrieve the states of the internal

state machines. Because there are many such complex state machi nes and in terworkin g fun cti onal b l ocks

inside the BoSS, all internal registers must be initialized to a known state before any data packets can be

transmitted and received.

Table 2-B lists the steps required to initialize the DS3131. It is imperative that they are followed exactl y

in the order presented, or exactly as implemented in Dallas Semiconductor DS3131 driver code.

12 of 174

Page 13

DS3131

Table 2-B. Initialization Steps

INITIALIZATION STEP COMMENTS

1) System Reset System reset can be invoked by either hardware action

through the PRST signal (recommended) or software

action through the RST control bit in the master reset and

ID register. All configuration registers are set to 0 (0000h)

by system reset.

2) Configure LBBMC Register Please note that this register is not affected by the

software-invoked system reset. It is forced to all zeros only

by the hardware reset.

3) Configure PCI This is achieved by asserting the PIDSEL signal.

4) Disable Transmit and Receive DMA for each

Channel

Ensure the DMA is off on both the transmit and receive

sides through the channel-enable bit in the transmit and

receive RAM.

5) Configure Receive DMA Program the receive DMA configuration RAM.

6) Configure Receive FIFO Program the receive FIFO registers.

7) Configure Receive Layer 1 Program the receive port registers (RP[n]CR).

8) Configure Transmit DMA Program the transmit DMA configuration RAM.

9) Configure Transmit FIFO Program the transmit FIFO registers.

10) Configure Transmit Layer 2 Program the transmit HDLC port control registers

(TH[n]CR).

11) Configure Transmit Layer 1 Program the transmit port registers (TP[n]CR).

12) Configure Receive Layer 2 Program the receive HDLC port control registers

(RH[n]CR).

13) Enable Receive DMA for Each Channel Set the channel-enable bit in the receive DMA

configuration RAM for the channels in use.

14) Enable Transmit DMA for Each Channel Set the channel-enable bit in the transmit DMA

configuration RAM for the channels in use.

15) Configure Interrupts Optional,

16) Configure Master Control Register Set the RDE and TDE control bits in the master

configuration (MC) register .

Table 2-C. Indirect Registers

REGISTER NAME NUMBER OF INDIRECT REGISTERS

Receive DMA Configuration RDMAC 120 (three for each HDLC Channel)1

Transmit DMA Configuration TDMAC 240 (six for each HDLC Channel)1

Receive FIFO Starting Block Pointer RFSBP 40 (one for each HDLC Channel)

Receive FIFO Block Pointer RFBP 512 (one for each FIFO Block)

Receive FIFO High Watermark RFHWM 40 (one for each HDLC Channel)

Transmit FIFO Starting Block Pointer TFSBP 40 (one for each HDLC Channel)

Transmit FIFO Block Pointer TFBP 512 (one for each FIFO Block)

Transmit FIFO Low Watermark TFLWM 40 (one for each HDLC Channel)

1

On device initialization, the host needs only to write to one of the receive and one of the transmit DMA registers. See Sections 9.2.5 and 9.3.5

for details.

13 of 174

Page 14

DS3131

3. SIGNAL DESCRIPTION

3.1 Overview/Signal List

This section describes the input and output signals on the DS3131. Signal names follow a convention

that is shown in the Signal Naming Convention table below. Table 3-A

lists all of the signals, their signal

type, description, and pin location.

Signal Naming Convention

FIRST LETTER SIGNAL CATEGORY SECTION

R Receive Serial Port 3.2

T Transmit Serial Port 3.2

L Local Bus 3.3

J JTAG Test Port 3.4

LXXX–T/RXXX: Multiplexed local bus with extended ports controlled by LBPXS.

P PCI Bus 3.5

Table 3-A. Signal Description

PIN NAME TYPE FUNCTION

W20 TC0 I Transmit Serial Clock for Port 0

U19 TC1 I Transmit Serial Clock for Port 1

T17 TC2 I Transmit Serial Clock for Port 2

U20 TC3 I Transmit Serial Clock for Port 3

T19 TC4 I Transmit Serial Clock for Port 4

R18 TC5 I Transmit Serial Clock for Port 5

R19 TC6 I Transmit Serial Clock for Port 6

P18 TC7 I Transmit Serial Clock for Port 7

P20 TC8 I Transmit Serial Clock for Port 8

N19 TC9 I Transmit Serial Clock for Port 9

M17 TC10 I Transmit Serial Clock for Port 10

M19 TC11 I Transmit Serial Clock for Port 11

L19 TC12 I Transmit Serial Clock for Port 12

L20 TC13 I Transmit Serial Clock for Port 13

K19 TC14 I Transmit Serial Clock for Port 14

J20 TC15 I Transmit Serial Clock for Port 15

J18 TC16 I Transmit Serial Clock for Port 16

H19 TC17 I Transmit Serial Clock for Port 17

G20 TC18 I Transmit Serial Clock for Port 18

F20 TC19 I Transmit Serial Clock for Port 19

F19 TC20 I Transmit Serial Clock for Port 20

G17 TC21 I Transmit Serial Clock for Port 21

E19 TC22 I Transmit Serial Clock for Port 22

E18 TC23 I Transmit Serial Clock for Port 23

C20 TC24 I Transmit Serial Clock for Port 24

D18 TC25 I Transmit Serial Clock for Port 25

B20 TC26 I T ransmit Serial Clock for Port 26

B19 TC27 I T ransmit Serial Clock for Port 27

V19 TD0 O Transmit Serial Data for Port 0

U18 TD1 O Transmit Serial Data for Port 1

V20 TD2 O Transmit Serial Data for Port 2

14 of 174

Page 15

PIN NAME TYPE FUNCTION

T18 TD3 O Transmit Serial Data for Port 3

T20 TD4 O Transmit Serial Data for Port 4

P17 TD5 O Transmit Serial Data for Port 5

R20 TD6 O Transmit Serial Data for Port 6

P19 TD7 O Transmit Serial Data for Port 7

N18 TD8 O Transmit Serial Data for Port 8

N20 TD9 O Transmit Serial Data for Port 9

M18 TD10 O Transmit Serial Data for Port 10

M20 TD11 O Transmit Serial Data for Port 11

L18 TD12 O Transmit Serial Data for Port 12

K20 TD13 O Transmit Serial Data for Port 13

K18 TD14 O Transmit Serial Data for Port 14

J19 TD15 O Transmit Serial Data for Port 15

H20 TD16 O Transmit Serial Data for Port 16

H18 TD17 O Transmit Serial Data for Port 17

G19 TD18 O Transmit Serial Data for Port 18

G18 TD19 O Transmit Serial Data for Port 19

E20 TD20 O Transmit Serial Data for Port 20

F18 TD21 O Transmit Serial Data for Port 21

D20 TD22 O Transmit Serial Data for Port 22

D19 TD23 O Transmit Serial Data for Port 23

E17 TD24 O Transmit Serial Data for Port 24

C19 TD25 O Transmit Serial Data for Port 25

C18 TD26 O Transmit Serial Data for Port 26

A20 TD27 O Transmit Serial Data for Port 27

W9, U14, C10 N.C. — No Connect. Do not connect any signal to this pin.

V17 PAD0 I/O PCI Multiplexed Address and Data Bit 0

U16 PAD1 I/O PCI Multiplexed Address and Data Bit 1

Y18 PAD2 I/O PCI Multiplexed Address and Data Bit 2

W17 PAD3 I/O PCI Multiplexed Address and Data Bit 3

V16 PAD4 I/O PCI Multiplexed Address and Data Bit 4

Y17 PAD5 I/O PCI Multiplexed Address and Data Bit 5

W16 PAD6 I/O PCI Multiplexed Address and Data Bit 6

V15 PAD7 I/O PCI Multiplexed Address and Data Bit 7

W15 PAD8 I/O PCI Multiplexed Address and Data Bit 8

V14 PAD9 I/O PCI Multiplexed Address and Data Bit 9

Y15 P AD10 I/O PCI Multiplexed Address and Data Bit 10

W14 PAD11 I/O PCI Multiplexed Address and Data Bit 11

Y14 P AD12 I/O PCI Multiplexed Address and Data Bit 12

V13 P AD13 I/O PCI Multiplexed Address and Data Bit 13

W13 PAD14 I/O PCI Multiplexed Address and Data Bit 14

Y13 P AD15 I/O PCI Multiplexed Address and Data Bit 15

V9 PAD16 I/O PCI Multiplexed Address and Data Bit 16

U9 PAD17 I/O PCI Multiplexed Address and Data Bit 17

Y8 PAD18 I/O PCI Multiplexed Address and Data Bit 18

W8 PAD19 I/O PCI Multiplexed Address and Data Bit 19

V8 PAD20 I/O PCI Multiplexed Address and Data Bit 20

Y7 PAD21 I/O PCI Multiplexed Address and Data Bit 21

W7 PAD22 I/O PCI Multiplexed Address and Data Bit 22

V7 PAD23 I/O PCI Multiplexed Address and Data Bit 23

U7 PAD24 I/O PCI Multiplexed Address and Data Bit 24

V6 PAD25 I/O PCI Multiplexed Address and Data Bit 25

DS3131

15 of 174

Page 16

PIN NAME TYPE FUNCTION

Y5 PAD26 I/O PCI Multiplexed Address and Data Bit 26

W5 PAD27 I/O PCI Multiplexed Address and Data Bit 27

V5 PAD28 I/O PCI Multiplexed Address and Data Bit 28

Y4 PAD29 I/O PCI Multiplexed Address and Data Bit 29

Y3 PAD30 I/O PCI Multiplexed Address and Data Bit 30

U5 PAD31 I/O PCI Multiplexed Address and Data Bit 31

Y16

V12

Y9

W6

PCBE0

PCBE1

PCBE2

PCBE3

I/O

I/O

I/O

I/O

PCI Bus Command/Byte Enable Bit 0

PCI Bus Command/Byte Enable Bit 1

PCI Bus Command/Byte Enable Bit 2

PCI Bus Command/Byte Enable Bit 3

Y2 PCLK I PCI and System Clock. A 33MHz clock is applied here.

Y11

W10

W4

PDEVSEL

PFRAME

PGNT

I/O

I/O

I

PCI Device Select

PCI Cycle Frame

PCI Bus Grant

Y6 PIDSEL I P CI Initialization Device Sele ct

W18

V10

PINT

PIRDY

O

I/O

PCI Interrupt

PCI Initiator Ready

W12 PPAR I/O PCI Bus Parity

V11

V4

W3

Y12

W11

Y10

V18

Y20

W19

PPERR

PREQ

PRST

PSERR

PSTOP

PTRDY

PXAS

PXBLAST

PXDS

I/O

O

I

O

I/O

I/O

O

O

O

PCI Parity Error

PCI Bus Request

PCI Reset

PCI System Error

PCI Stop

PCI Target Ready

PCI Extension Signal: Address Strobe

PCI Extension Signal: Burst Last

PCI Extension Signal: Data Strobe

Y1 RC0 I Receive Serial Clock for Port 0

V3 RC1 I Receive Serial Clock for Port 1

V2 RC2 I Receive Serial Clock for Port 2

T4 RC3 I Receive Serial Clock for Port 3

U2 RC4 I Receive Serial Clock for Port 4

U1 RC5 I Receive Serial Clock for Port 5

R3 RC6 I Receive Serial Clock for Port 6

T1 RC7 I Receive Serial Clock for Port 7

P3 RC8 I Receive Serial Clock for Port 8

P2 RC9 I Receive Serial Clock for Port 9

N3 RC10 I Receive Serial Clock for Port 10

N1 RC11 I Receive Serial Clock for Port 11

M2 RC12 I Receive Serial Clock for Port 12

L3 RC13 I Receive Serial Clock for Port 13

L1 RC14 I Receive Serial Clock for Port 14

K3 RC15 I Receive Serial Clock for Port 15

J1 RC16 I Receive Serial Clock for Port 16

J3 RC17 I Receive Serial Clock for Port 17

H1 RC18 I Receive Serial Clock for Port 18

H3 RC19 I Receive Serial Clock for Port 19

G2 RC20 I Receive Serial Clock for Port 20

F1 RC21 I Receive Serial Clock for Port 21

G4 RC22 I Receive Serial Clock for Port 22

E1 RC23 I Receive Serial Clock for Port 23

E3 RC24 I Receive Serial Clock for Port 24

16 of 174

DS3131

Page 17

PIN NAME TYPE FUNCTION

C1 RC25 I Receive Serial Clock for Port 25

D3 RC26 I Receive Serial Clock for Port 26

C2 RC27 I Receive Serial Clock for Port 27

W2 RD0 I Receive Serial Data for Port 0

W1 RD1 I Receive Serial Data for Port 1

U3 RD2 I Receive Serial Data for Port 2

V1 RD3 I Receive Serial Data for Port 3

T3 RD4 I Receive Serial Data for Port 4

T2 RD5 I Receive Serial Data for Port 5

P4 RD6 I Receive Serial Data for Port 6

R2 RD7 I Receive Serial Data for Port 7

R1 RD8 I Receive Serial Data for Port 8

P1 RD9 I Receive Serial Data for Port 9

N2 RD10 I Receive Serial Data for Port 10

M3 RD11 I Receive Serial Data for Port 11

M1 RD12 I Receive Serial Data for Port 12

L2 RD13 I Receive Serial Data for Port 13

K1 RD14 I Receive Serial Data for Port 14

K2 RD15 I Receive Serial Data for Port 15

J2 RD16 I Receive Serial Data for Port 16

J4 RD17 I Receive Serial Data for Port 17

H2 RD18 I Receive Serial Data for Port 18

G1 RD19 I Receive Serial Data for Port 19

G3 RD20 I Receive Serial Data for Port 20

F2 RD21 I Receive Serial Data for Port 21

F3 RD22 I Receive Serial Data for Port 22

E2 RD23 I Receive Serial Data for Port 23

D1 RD24 I Receive Serial Data for Port 24

E4 RD25 I Receive Serial Data for Port 25

D2 RD26 I Receive Serial Data for Port 26

B1 RD27 I Receive Serial Data for Port 27

A19 JTMS I JTAG IEEE 1149.1 Test Mode Select

D16 JTDO O JTAG IEEE 1149.1 Test Serial-Data Output

B18 JTCLK I JTAG IEEE 1149.1 Test Serial Clock

B17 JTRST I JTAG IEEE 1149.1 Test Reset

C17 JTDI I JTAG IEEE 1149.1 Test Serial-Data Input

C8 LA0–RD37 I/O–I Local Bus Address Bit 0–Receive Serial Data for Port 37

A7 LA1–RC37 I/O–I Local Bus Address Bit 1–Receive Serial Clock for Port 37

B7 LA2–RD36 I/O–I Local Bus Address Bit 2–Receive Serial Data for Port 36

A6 LA3–RC36 I/O–I Local Bus Address Bit 3–Receive Serial Clock for Port 36

C7 LA4–RD35 I/O–I Local Bus Address Bit 4–Receive Serial Data for Port 35

B6 LA5–RC35 I/O–I Local Bus Address Bit 5–Receive Serial Clock for Port 35

A5 LA6–RD34 I/O–I Local Bus Address Bit 6–Receive Serial Data for Port 34

D7 LA7–RC34 I/O–I Local Bus Address Bit 7–Receive Serial Clock for Port 34

C6 LA8–RD33 I/O–I Local Bus Address Bit 8–Receive Serial Data for Port 33

B5 LA9–RC33 I/O–I Local Bus Address Bit 9–Receive Serial Clock for Port 33

A4 LA10–RD32 I/O–I Local Bus Address Bit 10–Receive Serial Data for Port 32

C5 LA11–RC32 I/O–I Local Bus Address Bit 11–Receive Serial Clock for Port 32

B4 LA12–RD31 I/O–I Local Bus Address Bit 12–Receive Serial Data for Port 31

A3 LA13–RC31 I/O–I Local Bus Address Bit 13–Receive Serial Clock for Port 31

D5 LA14–RD30 I/O–I Local Bus Address Bit 14–Receive Serial Data for Port 30

C4 LA15–RC30 I/O–I Local Bus Address Bit 15–Receive Serial Clock for Port 30

DS3131

17 of 174

Page 18

PIN NAME TYPE FUNCTION

B3 LA16–RD29 I/O–I Local Bus Address Bit 16–Receive Serial Data for Port 29

B2 LA17–RC29 I/O–I Local Bus Address Bit 17–Receive Serial Clock for Port 29

A2 LA18–RD28 I/O–I Local Bus Address Bit 18–Receive Serial Data for Port 28

C3 LA19–RC28 I/O–I Local Bus Address Bit 19–Receive Serial Clock for Port 28

A18 LD0–TC28 I/O–I Local Bus Data Bit 0–Transmit Serial Clock for Port 28

A17 LD1–TD28 I/O–O Local Bus Data Bit 1–Transmit Serial Data for Port 28

C16 LD2–TC29 I/O–I Local bus Data Bit 2–Transmit Serial Clock for Port 29

B16 LD3–TD29 I/O–O Local Bus Data Bit 3–Transmit Serial Data for Port 29

A16 LD4–TC30 I/O–I Local Bus Data Bit 4–Transmit Serial Clock for Port 30

C15 LD5–TD30 I/O–O Local Bus Data Bit 5–Transmit Serial Data for Port 30

D14 LD6–TC31 I/O–I Local Bus Data Bit 6–Transmit Serial Clock for Port 31

B15 LD7–TD31 I/O–O Local Bus Data Bit 7–Transmit Serial Data for Port 31

A15 LD8–TC32 I/O–I Local Bus Data Bit 8–Transmit Serial Clock for Port 32

C14 LD9–TD32 I/O–O Local Bus Data Bit 9–Transmit Serial Data for Port 32

B14 LD10–TC33 I/O–I Local Bus Data Bit 10–Transmit Serial Clock for Port 33

A14 LD11–TD33 I/O–O Local Bus Data Bit 11–Transmit Serial Data for Port 33

C13 LD12–TC34 I/O–I Local Bus Data Bit 12–Transmit Serial Clock for Port 34

B13 LD13–TD34 I/O–O Local Bus Data Bit 13–Transmit Serial Data for Port 34

A13 LD14–TC35 I/O–I Local Bus Data Bit 14-Transmit Serial Clock for Port 35

D12 LD15–TD35 I/O–O Local Bus Data Bit 15–Transmit Serial Data for Port 35

C9 LMS–RD39 I–I Local Bus Mode Select–Receive Serial Data for Port 39

B11 LBHE–TD37 O–O Local Bus Byte High Enable–Transmit Serial Data for Port 37

B10 LHOLD–TD39 O–O Local Bus Hold (Local Bus Request)–Transmit Serial Data for Port 39

A9 LWR–RC39 I/O–I

C12 LIM–TC36 I–I Local Bus Intel/Motorola Bus Select–Transmit Serial Clock for Port 36

C11 LHLDA–TC38 I–I

B12 LCLK–TD36 O–O Local Bus Clock–Transmit Serial Data for Port 36

A11 LBGACK–TD38 O–O Local Buses Grant Acknowledge–Transmit Serial Data for Port 38

A8 LRD–RD38 I/O–I

A12 LINT–TC37 I/O–I Local Bus Interrupt–Transmit Serial Clock for Port 37

A10 LRDY–TC39 I–I Local Bus PCI Bridge Ready–Transmit Serial Clock for Port 39

B9 LBPXS I Local Bus Port Extension Select. Leave open to enable local bus.

B8 LCS–RC38 I–I Local Bus Chip Select–Receive Serial Data for Port 38

Y19 TEST I Test. Factory test signals; leave open-circuited.

D6, D10, D11,

D15, F4, F17,

K4, K17, L4,

L17, R4, R17,

U6, U10, U11,

U15

A1, D4, D8, D9,

D13, D17, H4,

H17, J17, M4,

N4, N17, U4,

U8, U12, U13,

U17

J9–J12, K9–

K12, L9–L12,

M1, M9–11

VDD — Positive Suppl y, 3.3V (± 10%)

VSS — Ground

VSST — Ground and Thermal Dissipation Ball

Local Bus Write Enable (Local Bus Read/Write Select)–Receive Serial

Clock for Port 39

Local Bus Hold Acknowledge (Local Bus Grant)–Transmit Serial

Clock for Port 38

Local Bus Read Enable (Local Bus Data Strobe)–Receive Serial Data

for Port 38

DS3131

18 of 174

Page 19

Figure 3-1. Signal Floorplan

1234567891011121314151617181920

Y RC0 PCLK PAD30 PAD29 PAD26 PIDSEL PAD21 PAD18 PCBE2* PTRDY*

W RD1 RD0 PRST* PGNT* PAD27 PCBE3* PAD22 PAD19 NC

V RD3 RC2 RC1 PREQ* PAD28 PAD25 PAD23 PAD20 PAD16 PIRDY* PPERR* PCBE1* PAD13 PAD9 PAD7 PAD4 PAD0 PXAS* TD0 TD2 V

U RC5 RC4 RD2 VSS PAD31 VDD PAD24 VSS PAD17 VDD VDD VSS VSS NC VDD PAD1 VSS TD1 TC1 TC3 U

R RD8 RD7 RC6 VDD VDD TC5 TC6 TD6 R

T RC7 RD5 RD4 RC3 TC2 TD3 TC4 TD4 T

P RD9 RC9 RC8 RD6 TD5 TC7 TD7 TC8 P

N RC11 RD10 RC10 VSS VSS TD8 TC9 TD9 N

M RD12 RC12 RD11 VSS VSST VSST VSST VSST TC10 TD10 TC11 TD11 M

L RC14 RD13 RC13 VDD VSST VSST VSST VSST VDD TD12 TC12 TC13 L

K RD14 RD15 RC15 VDD VSST VSST VSST VSST VDD TD14 TC14 TD13 K

PDEV-

PSERR* PAD15 PAD12 PAD10 PCBE0* PAD5 PAD2 TEST

SEL*

P-

PSTOP* PPAR PAD14 PAD11 PAD8 PAD6 PAD3 PINT* PXDS* TC0 W

FRAME*

PXB-

LAST*

DS3131

Y

J RC16 RD16 RC17 RD17 VSST VSST VSST VSST VSS TC16 TD15 TC15 J

H RC18 RD18 RC19 VSS VSS TD17 TC17 TD16 H

G RD19 RC20 RD20 RC22 TC21 TD19 TD18 TC18 G

F RC21 RD21 RD22 VDD VDD TD21 TC20 TC19 F

E RC23 RD23 RC24 RD25 TD24 TC23 TC22 TD20 E

D RD24 RD26 RC26 VSS

LA17-

RC29

LA18RD28

LA19-

RC28

LA16RD29

LA13-

RC31

C RC25 RC27

BRD27

A VSS

1234567891011121314151617181920

LA14-

VDD LA7-RC34 VSS VSS VDD VDD

RD30

LA15-

LA11-

RC30

LA12-

RD31

LA10-

RD32

LA8-RD33 LA4-RD35 LA0-RD37 LMS-RD39 NC

RC32

LA9-RC33 LA5-RC35 LA2-RD36 LCS-RC38 LBPXS

LA6-RD34 LA3-RC36 LA1-RC37 LRD-RD38

LWRRC39

LHOLD-

TD39

LRDY-

TC39

LHLDA-

TC38

LBHE-

TD37

LBGAC-

TD38

LD15-

VSS LD6-TC31 VDD JTDO VSS TC25 TD23 TD22 D

TD35

LD12-

LIM-TC36

LCLK-

TD36

LINT-

TC37

LD9-TD32 LD5-TD30 LD2-TC29 JTDI TD26 TD25 TC24 C

TC34

LD13-

LD10-

TD34

LD14TC35

LD7-TD31 LD3-TD29 JTRST JTCLK TC27 TC26 B

TC33

LD11-

LD8-TC32 LD4-TC30 LD1-TD28 LD0-TC28 JTMS TD27 A

TD33

Receive Ports 0-13 Transmi t Port s 0-13 PCI other VDD

Receive Ports 14-27 Transmit Ports 14-27 JTAG, TEST, and NC VSS

Local B us and P orts 28-39 PCI address and data

19 of 174

Page 20

DS3131

3.2 Serial Port Interface Signal Description

Signal Name: RC0 to RC39

Signal Description: Receive Serial Clock

Signal Type: Input

Data can be clocked into the device either on rising edges (normal clock mode) or falling edges (inverted clock

mode) of RC. This is programmable on a per port basis. RC can operate at speeds from DC to 52MHz. Clock

gapping is acceptable. If not used, this signal should be wired low.

Signal Name: RD0 to RD39

Signal Description: Receive Serial Data

Signal Type: Input

Can be sampled either on the rising edge of RC (normal clock mode) or the falling edge of RC (inverted clock

mode). If not used, this signal should be wired low.

Signal Name: TC0 to TC39

Signal Description: Transmit Serial Clock

Signal Type: Input

Data is clocked out of the device at TD either on rising edges (normal clock mode) or falling edges (inverted clock

mode) of TC. This is programmable on a per port basis. TC can operate at speeds from DC to 52MHz. Clock

gapping is acceptable. If not used, this signal should be wired low.

Signal Name: TD0 to TD39

Signal Description: Transmit Serial Data

Signal Type: Output

Can be updated either on the rising edge of TC (normal clock mode) or the falling edge of TC (inverted clock

mode). TD can be forced either high or low by the TP[n]CR register. See Section 6.1

for details.

3.3 Local Bus Signal Description

Note: The signals listed in this section are only active when the local bus is enabled.

Signal Name: LMS

Signal Description: Local Bus Mode Select

Signal Type: Input

This signal should be connected low when the device operates with no local bus access or if the local bus is used

as a bridge from the PCI bus. This signal should be connected high if the local bus is to be used by an external host

to configure the device.

0 = local bus is in the PCI bridge mode (master)

1 = local bus is in the configuration mode (slave)

Signal Name: LIM

Signal Description: Local Bus Intel/Motorola Bus Select

Signal Type: Input

The signal determines whether the local bus operates in the Intel mode (LIM = 0) or the Motorola mode (LIM =

1). The signal names in parenthesis are operational when the device is in the Motorola mode.

0 = local bus is in the Intel mode

1 = local bus is in the Motorola mode

20 of 174

Page 21

DS3131

Signal Name: LBPXS

Signal Description: Local Bus or Port Extension Select

Signal Type: Input (with internal 10kΩ pullup)

This signal must be left open-circuited (or connected high) to activate and enable the local bus. When this signal is

connected low, the local bus is disabled and its signals are redefined to support 12 bit-synchronous HDLC

controllers on ports 28 to 39 (Table 3-A

).

0 = local bus disabled

1 (or open -ircuited) = local bus enabled

Signal Name: LD0 to LD15

Signal Description: Local Bus Nonmultiplexed Data Bus

Signal Type: Input/Output (three-state capable)

In PCI bridge mode (LMS = 0), data from/to the PCI bus can be transferred to/from these signals. When writing

data to the local bus, these signals are outputs and updated on the rising edge of LCLK. When reading data from

the local bus, these signals are inputs, which are sampled on the rising edge of LCLK. Depending on the assertion

of the PCI byte enables (PCBE0 to PCBE3) and the local bus-width (LBW) control bit in the local bus bridge

mode control register (LBBMC), this data bus uses all 16 bits (LD[ 15:0]) or just the lower 8 bits (LD[7:0]) or the

upper 8 bits (LD[15:8]). If the upper LD bits (LD[15:8]) are used, then the local bus high-enable signal (LBHE) is

asserted during the bus transaction. If the local bus is not currently involved in a bus transaction, all 16 signals are

three-stated. When reading data from the local bus, these signals are outputs that are updated on the rising edge of

LCLK. When writing data to the local bus, these signals become inputs, which are sampled on the rising edge of

LCLK. In configuration mode (LMS = 1), the external host configures the device and obtains real-time status

information about the device through these signals. Only the 16-bit bus width is allowed (i.e., byte addressing is

not available).

Signal Name: LA0 to LA19

Signal Description: Local Bus Nonmultiplexed Address Bus

Signal Type: Input/Output (three-state capable)

In the PCI bridge mode (LMS = 0), these signals are outputs that are asserted on the rising edge of LCLK to

indicate which address is written to or read from. If bus arbitration is enabled through the local bus arbitration

(LARBE) control bit in the LBBMC register, these signals are three-stated when the local bus is not currently

involved in a bus transaction and driven when a bus transaction is active. When bus arbitration is disabled, these

signals are always driven. These signals are sampled on the rising edge of LCLK to determine the internal device

configuration register that the external host wishes to access. In configuration mode (LMS = 1), these signals are

inputs and only the bottom 16 bits (LA[15:0]) are active; the upper four (LA[19:16]) are ignored and should be

connected low.

Signal Name: LWR

LWR (LR/WWWW)

LWRLWR

Signal Description: Local Bus Write Enable (Local Bus Read/Write Select)

Signal Type: Input/Output (three-state capable)

In the PCI bridge mode (LMS = 0), this output signal is asserted on the rising edge of LCLK. In Intel mode

(LIM = 0), it is asserted when data is to be written to the local bus. In Motorola mode (LIM = 1), this signal

determines whether a read or write is to occur. If bus arbitration is enabled through the LARBE control bit in the

LBBMC register, this signal is three-stated when the local bus is not currently involved in a bus transaction and

driven when a bus transaction is active. When bus arbitration is disabled, this signal is always driven. In

configuration mode (LMS = 1), this signal is sampled on the rising edge of LCLK. In Intel mode (LIM = 0), it

determines when data is to be written to the device. In Motorola mode (LIM = 1), this signal determines whether a

read or write is to occur.

21 of 174

Page 22

DS3131

Signal Name: LRD

LRD (LDS

LDS)

LRDLRD

LDSLDS

Signal Description: Local Bus Read Enable (Local Bus Data Strobe)

Signal Type: Input/Output (three-state capable)

In the PCI bridge mode (LMS = 0), this active-low output signal is asserted on the rising edge of LCLK. In Intel

mode (LIM = 0), it is asserted when data is to be read from the local bus. In Motorola mode (LIM = 1), the rising

edge is used to write data into the slave device. If bus arbitration is enabled through the LARBE control bit in the

LBBMC register, this signal is three-stated when the local bus is not currently involved in a bus transaction and

driven when a bus transaction is active. When bus arbitration is disabled, this signal is always driven. In

configuration mode (LMS = 1), this signal is an active-low input that is sampled on the rising edge of LCLK. In

Intel mode (LIM = 0), it determines when data is to be read from the device. In Motorola mode (LIM = 1), the

rising edge writes data into the device.

Signal Name: LINT

LINT

LINTLINT

Signal Description: Local Bus Interrupt

Signal Type: Input/Output (open drain)

In the PCI bridge mode (LMS = 0), this active-low signal is an input that is sampled on the rising edge of LCLK.

If asserted and unmasked, this signal causes an interrupt at the PCI bus through the PINTA signal. If not used in

PCI bridge mode, this signal should be connected high. In configuration mode (LMS = 1), this signal is an opendrain output that is forced low if one or more unmasked interrupt sources within the device is active. The signal

remains low until either the interrupt is serviced or masked.

Signal Name: LRDY

LRDY

LRDYLRDY

Signal Description: Local Bus PCI Bridge Ready (PCI Bridge Mode Only)

Signal Type: Input

This active-low signal is sampled on the rising edge of LCLK to determine when a bus transaction is complete.

This signal is only examined when a bus transaction is taking place. This signal is ignored when the local bus is in

configuration mode (LMS = 1) and should be connected high.

Signal Name: LHLDA (LBG

LBG)

LBGLBG

Signal Description: Local Bus Hold Acknowledge (Local Bus Grant) (PCI Bridge Mode Only)

Signal Type: Input

This input signal is sampled on the rising edge of LCLK to determine when the device has been granted access to

the bus. In Intel mode (LIM = 0), this is an active-high signal; in Motorola mode (LIM = 1) this is an active-low

signal. This signal is ignored and should be connected high when the local bus is in configuration mode

(LMS = 1). Also, in PCI bridge mode (LMS = 0), this signal should be wired deasserted when the local bus

arbitration is disabled through the LBBMC register.

Signal Name: LHOLD (LBR

LBR)

LBRLBR

Signal Description: Local Bus Hold (Local Bus Request) (PCI Bridge Mode Only)

Signal Type: Output

This signal is asserted when the DS3131 is attempting to control the local bus. In Intel mode (LIM = 0), this signal

is an active-high signal; in Motorola mode (LIM = 1) this signal is an active-low signal. It is deasserted

concurrently with LBGACK. This signal is three-stated when the local bus is in configuration mode (LMS = 1)

and also in PCI bridge mode (LMS = 0) when the local bus arbitration is disabled through the LBBMC register.

Signal Name: LBGACK

LBGACK

LBGACKLBGACK

Signal Description: Local Bus Grant Acknowledge (PCI Bridge Mode Only)

Signal Type: Output (three-state capable)

This active-low signal is asserted when the local bus hold-acknowledge/bus grant signal (LHLDA/LB G) has been

detected and continues its assertion for a programmable (32 to 1,048,576) number of LCLKs, based on the local

bus arbitration timer setting in the LBBMC register. This signal is three-stated when the local bus is in

configuration mode (LMS = 1).

22 of 174

Page 23

DS3131

Signal Name: LBHE

LBHE

LBHELBHE

Signal Description: Local Bus Byte-High Enable (PCI Bridge Mode Only)

Signal Type: Output (three-state capable)

This active-low output signal is asserted when all 16 bits of the data bus (LD[15:0]) are active. It remains high if

only the lower 8 bits (LD[7:0)] are active. If bus arbitration is enabled through the LARBE control bit in the

LBBMC register, this signal is three-stated when the local bus is not currently involved in a bus transaction and

driven when a bus transaction is active. When bus arbitration is disabled, this signal is always driven. This signal

remains in three-state when the local bus is not involved in a bus transaction and is in configuration mode

(LMS = 1).

Signal Name: LCLK

Signal Description: Local Bus Clock (PCI Bridge Mode Only)

Signal Type: Output (three-state capable)

This signal outputs a buffered version of the clock applied at the PCLK input. All local bus signals are generated

and sampled from this clock. This output is three-stated when the local bus is in configuration mode (LMS = 1). It

can be disabled in the PCI bridge mode through the LBBMC register.

Signal Name: LCS

LCS