Page 1

www.maxim-ic.com

GENERAL DESCRIPTION

The DS1500 is a full-function, year 2000-compliant

real-time clock/calendar (RTC) with an alarm,

watchdog timer, power-on reset, battery monitors,

256 bytes of on-board nonvolatile (NV) SRAM, NV

control for backing up an external SRAM, and a

32.768kHz output. User access to all registers within

the DS1500 is accomplished with a byte-wide

interface, as shown in Figure 7. The RTC registers

contain century, year, month, date, day, hours,

minutes, and seconds data in 24-hour binary-coded

decimal (BCD) format. Corrections for day of month

and leap year are made automatically.

APPLICATIONS

Remote Systems

Battery-Backed Systems

Telecom Switches

Office Equipment

Consumer Electronics

ORDERING INFORMATION

PART TEMP RANGE PIN-PACKAGE

DS1500YEN

DS1500WEN -40°C to +85°C 32 TSOP

Selector Guide appears at end of data sheet.

Typical Operating Circuit appears at end of data sheet.

-40°C to +85°C 32 TSOP

DS1500

Y2K Watchdog RTC with

Nonvolatile Control

FEATURES

§ BCD-Coded Century, Year, Month, Date, Day,

Hours, Minutes, and Seconds with Automatic

Leap-Year Compensation Valid Up to the Year

2100

§ Programmable Watchdog Timer and RTC Alarm

§ Century Register; Y2K-Compliant RTC

§ Automatic Battery Backup and Write Protection

to External SRAM

§ +5V Operation

§ Precision Power-On Reset

§ Power-Control Circuitry Supports System Power-

On from Date/Day/Time Alarm or Key Closure

§ 256 Bytes User NV RAM

§ Auxiliary Battery Input

§ Accuracy Better than ±1 Minute/Month at +25°C

§ Day-of-Week/Date Alarm Register

§ Battery Voltage-Level Indicator Flags

§ Industrial Temperature Range: -40°C to +85°C

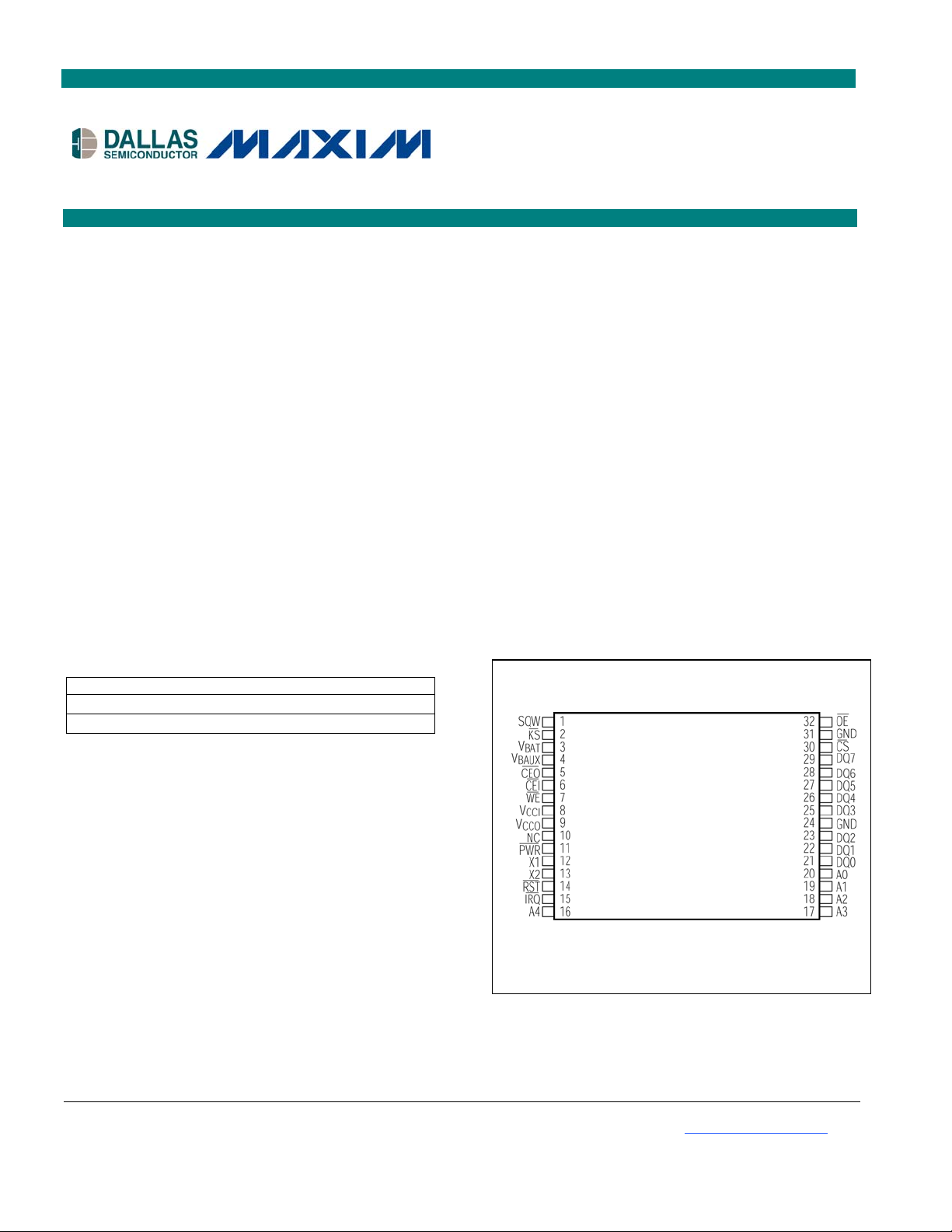

PIN CONFIGURATION

TOP VIEW

Dallas

Semiconductor

DS1500

TSOP

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata

1 of 19

REV: 030603

.

Page 2

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to Ground -0.5V to +6.0V

Operating Temperature Range

Storage Temperature Range

Soldering Temperature

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is

not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device.

See IPC/JEDEC J-STD-020A Specification

-40°C to +85°C (Note 1)

-55°C to +125°C

RECOMMENDED DC OPERATING CONDITIONS

(TA = -40°C to +85°C)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Power Supply Voltage (Note 2)

Logic 1 Voltage All Inputs (Note 2)

Pullup Voltage, IRQ, PWR, and RST Outputs

Logic 0 Voltage All Inputs (Note 2)

Battery Voltage (Note 2)

Auxiliary Battery Voltage (Note 2)

VCC

V

VPU

VIL

V

V

BAUX

IH

BAT

5V (Y) 4.5 5.0 5.5

3.3V (W) 3.0 3.3 3.6

+

V

V

CC

0.3

CC

0.3

+

Y 2.2

W 2.0

(Note 2) 5.5 V

Y -0.3 +0.8

W -0.3 +0.6

2.5 3.0 3.7 V

Y 2.5 3.0 5.3

W 2.5 3.0 3.7

V

V

V

V

DC ELECTRICAL CHARACTERISTICS

(V

< V

CCMIN

CCI

< V

, TA = -40°C to +85°C.)

CCMAX

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Active Supply Current (Note 3) ICC

TTL Standby Current (CS = VIH) I

CMOS Standby Current

(CS ³ V

- 0.2V)

CCI

I

CC1

CC2

Y 15

W 10

Y 5

W 4

Y 5

W 4

Input Leakage Current (Any Input) IIL -1 +1

Output Leakage Current (Any Output) IOL -1 +1

Output Logic 1 Voltage (I

Output Logic 0 Voltage (I

DQ0–7,

I

OUT

CEO I

= 5.0mA, IRQ,

OUT

= 7.0mA PWR, and RST)

Battery Low, Flag Trip Point (Note 2) V

Output Voltage (I

= 85mA ) (Note 5) V

CCO1

Power-Fail Voltage (Note 2) VPF

Battery Switchover Voltage VSO (Notes 2, 6)

Output Voltage (I

= 50µA) V

CCO2

Battery Leakage Current I

= -1.0mA) VOH (Note 2) 2.4 V

OUT

= 2.1mA,

OUT

V

(Note 2) 0.4 V

OL1

(Notes 2, 4) 0.4 V

V

OL2

Y 2.0

BLF

CCO1

W 1.9

Y

W

V

CCI

0.3

-

Y 4.20 4.50

W 2.75 2.97

V

BAT,

V

BAUX,

or V

PF

-

V

(Note 7)

CCO2

10 100 nA

LKG

BAT

0.3

V

V

2 of 19

mA

mA

mA

mA

mA

V

V

V

Page 3

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

DC ELECTRICAL CHARACTERISTICS

(VCC = 0V, TA = -40°C to +85°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Battery Current, BB32 = 0, EOSC = 0

Battery Current, BB32 = 0, EOSC = 1

V

Current BB32 = 1, SQW Open I

BAUX

BAT1

I

BAT2

BAUX

(Notes 8, 9)

(Notes 8, 9)

(Notes 8, 9) 2 µA

0.27 1.0 µA

0.01 0.1 µA

I

CRYSTAL SPECIFICATIONS*

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Nominal Frequency fO 32.768 kHz

Series Resistance ESR 45 kΩ

Load Capacitance CL 6 pF

*The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to Application Note 58: Crystal Considerations

for Dallas Real-Time Clocks for additional specifications.

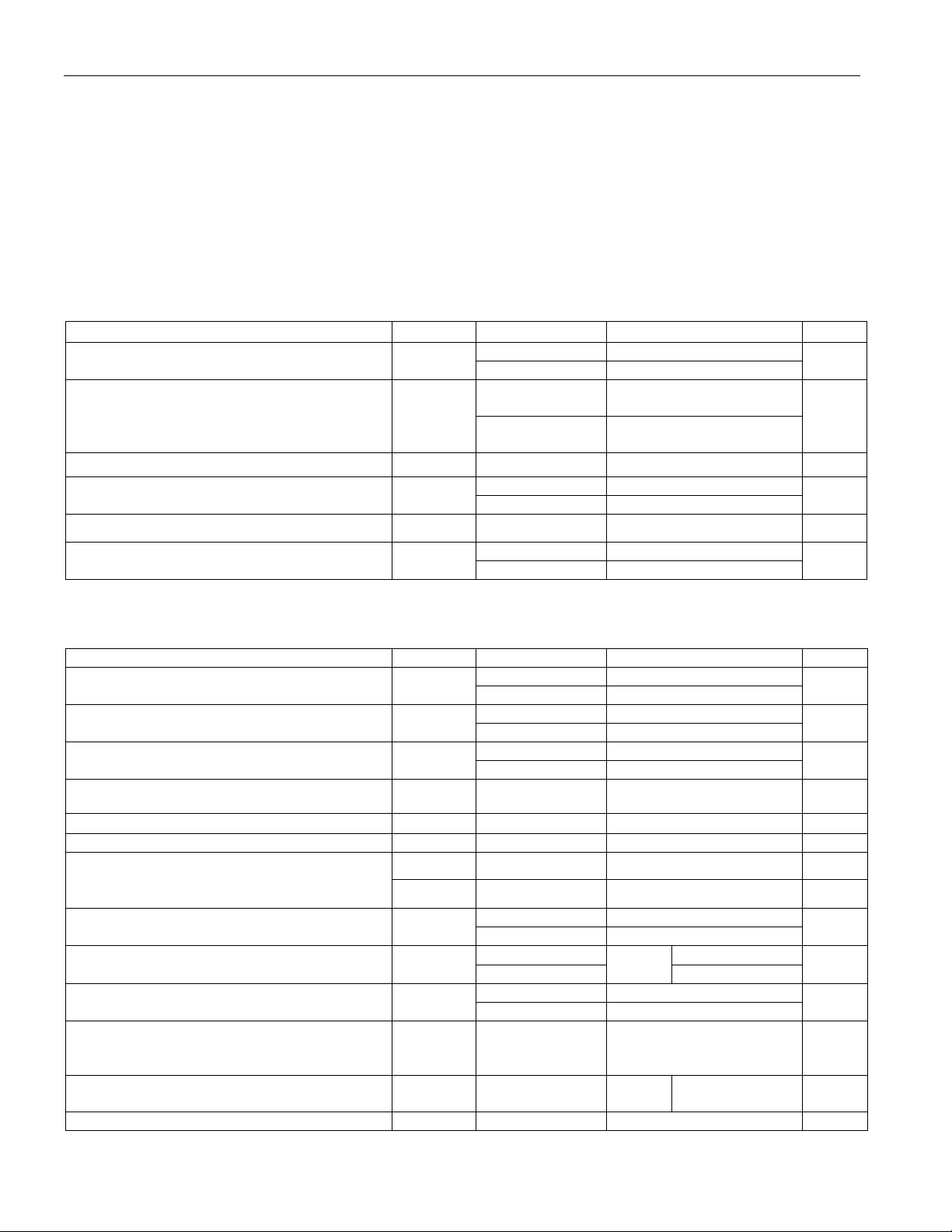

AC OPERATING CHARACTERISTICS

(V

= 5.0V ±10%, TA = -40°C to +85°C.)

CCI

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Read Cycle Time tRC

Address Access Time tAA

CS to DQ Low-Z

CS Access Time

CS Data Off Time

OE to DQ Low-Z (0°C to +85°C)

OE to DQ Low-Z (-40°C to 0°C)

OE Access Time

OE Data Off Time

Output Hold from Address tOH

Write Cycle Time

Address Setup Time

WE Pulse Width

CS Pulse Width

Data Setup Time

Data Hold Time

Address Hold Time

WE Data Off Time

Write Recovery Time

CEI to CEO Propagation Delay

Pulse Width, OE, WE, or CS High

Pulse Width, OE, WE, or CS Low

PW

PW

t

(Note 10)

(Note 10)

(Note 10)

(Note 10)

(Note 10)

t

t

t

t

t

t

CSL

CSA

CSZ

OEL

OEL

OEA

OEZ

70 ns

t

WC

0 ns

t

AS

t

50 ns

WEW

t

55 ns

CSW

30 ns

t

DS

t

5 ns

DH

0 ns

t

AH

t

(Note 10) 25 ns

WEZ

t

15 ns

WR

10 ns

t

CEPD

20 ns

HIGH

70 ns

LOW

70 ns

70 ns

5 ns

70 ns

25 ns

5 ns

2 ns

35 ns

25 ns

5 ns

3 of 19

Page 4

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

AC OPERATING CHARACTERISTICS (continued)

(V

= 3.3V ±10%, TA = -40°C to +85°C.)

CCI

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Read Cycle Time

Address Access Time

CS to DQ Low-Z

CS Access Time

CS Data Off Time

OE to DQ Low-Z (0°C to +85°C)

OE to DQ Low-Z (-40°C to 0°C)

OE Access Time

OE Data Off Time

Output Hold from Address

Write Cycle Time

Address Setup Time

WE Pulse Width

CS Pulse Width

Data Setup Time

Data Hold Time

Address Hold Time

WE Data Off Time

Write Recovery Time

CEI to CEO Propagation Delay

Pulse Width, OE, WE, or CS High

Pulse Width, OE, WE, or CS Low

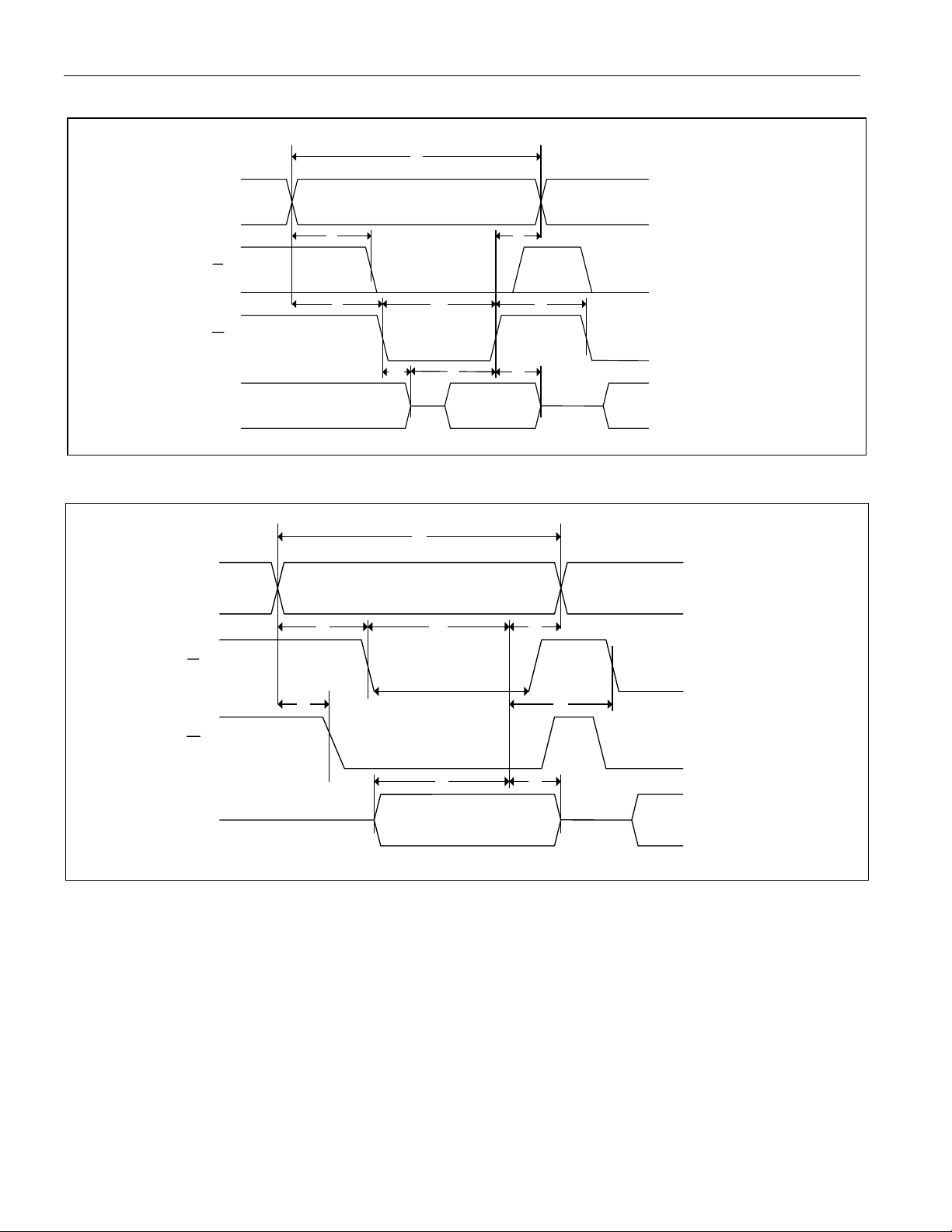

Figure 1. Read Cycle Timing

120 ns

t

RC

120 ns

t

AA

(Note 10) 5 ns

t

CSL

t

120 ns

CSA

t

(Note 10) 40 ns

CSZ

(Note 10) 5 ns

t

OEL

t

(Note 10) 2 ns

OEL

t

100 ns

OEA

t

(Note 10) 35 ns

OEZ

5 ns

t

OH

120 ns

t

WC

0 ns

t

AS

t

100 ns

WEW

t

110 ns

CSW

80 ns

t

DS

5 ns

t

DH

0 ns

t

AH

t

(Note 10) 40 ns

WEZ

15 ns

t

WR

t

10 ns

CEPD

PW

PW

40 ns

HIGH

100 ns

LOW

t

RC

A0-A4

t

CS

OE

DQ0-DQ7

t

AA

t

CSA

t

CSL

t

OEA

t

OEL

VALID

t

OEZ

OH

t

CSZ

4 of 19

Page 5

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

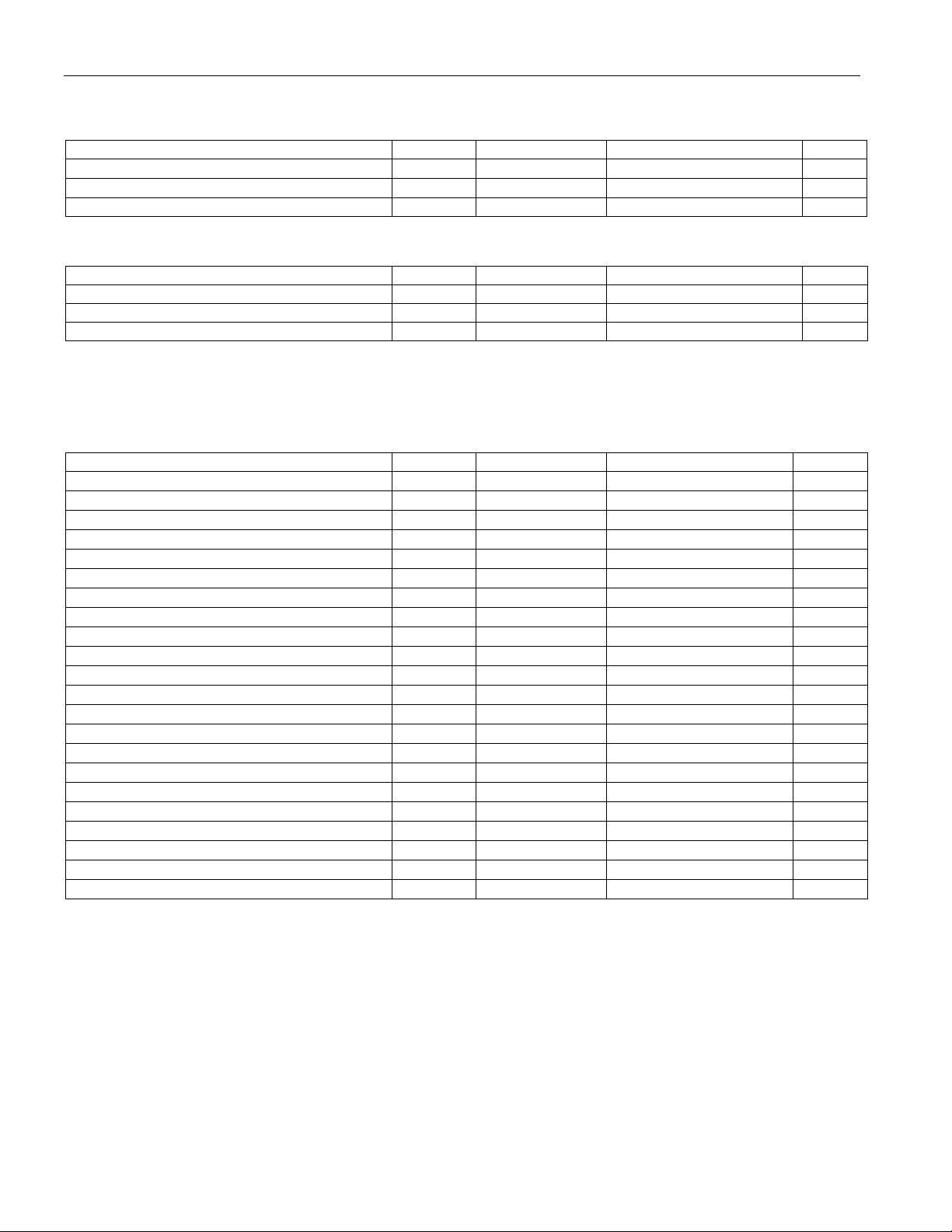

Figure 2. Write Cycle Timing, Write-Enable-Controlled

t

WC

A0-A4

VALID VALID

DATA INPUT

t

AH

t

DH

t

CS

WE

DQ0-DQ7

AS

t

AS

DATA OUTPUT DATA INPUT

t

WEW

t

WEZ

t

D

S

Figure 3. Write Cycle Timing, Chip-Select-Controlled

t

WR

A0-A4

CS

WE

DQ0-DQ7

t

WC

VALID VALID

t

AS

t

AS

t

CSW

t

DS

DATA INPU T

t

AH

t

WR

t

DH

DATA INPUT

5 of 19

Page 6

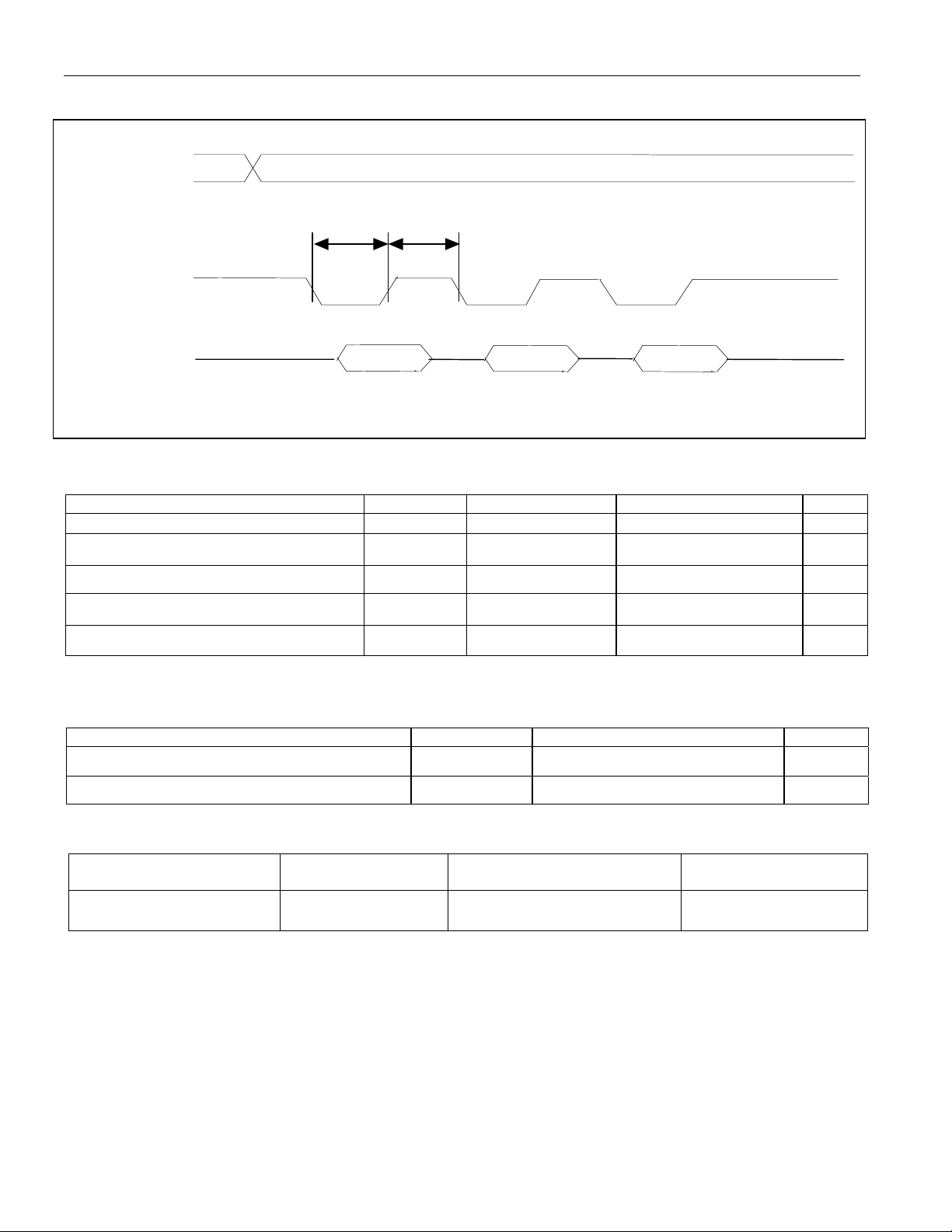

Figure 4. Burst Mode Timing Waveform

O

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

A0–A4

E, WE, OR CS

DQ0–DQ7

13h

LOW

PW

HIGH

PW

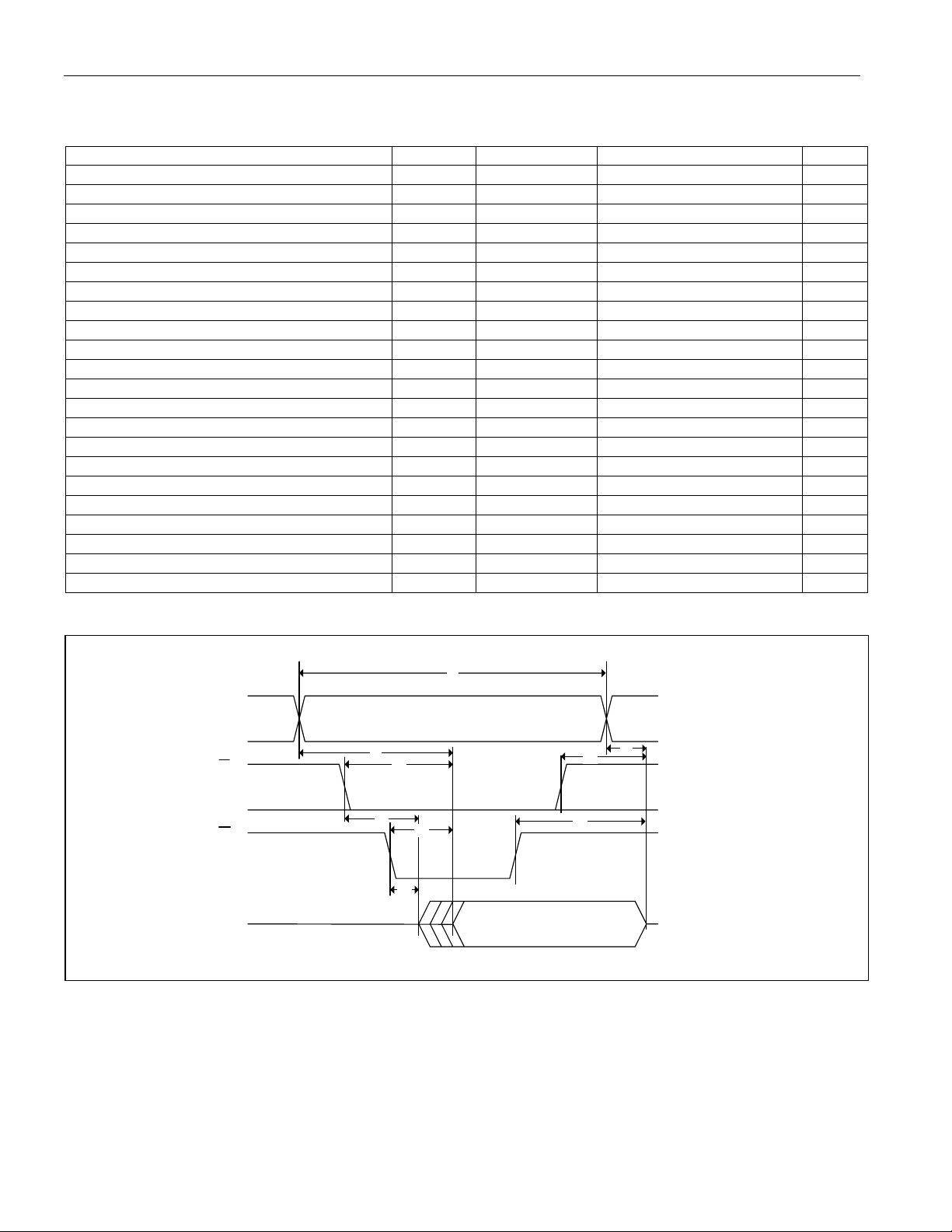

POWER-UP/DOWN CHARACTERISTICS (Figure 5)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

CS, CEI, or WE at V

V

Fall Time: V

CCI

V

Fall Time: V

CCI

V

Rise Time: V

CCI

PF(MAX)

PF(MIN)

PF(MIN)

VPF to RST High

t

t

REC

PF

FB

F

R

Before Power-Fail

IH

to V

t

PF(MIN)

to VSO t

to V

t

PF(MAX)

0

300

10

0

ms

ms

ms

ms

35 200 ms

CAPACITANCE

(TA = +25°C)

PARAMETER SYMBOL MIN TYP MAX UNITS

Capacitance on All Input Pins CIN 10 pF

10 pF

Capacitance on IRQ, PWR, RST, and DQ Pins

C

IO

AC TEST CONDITIONS

OUTPUT LOAD

(Y) 50pF + 1TTL Gate Input: 1.5V

(W) 25pF + 1 TTL Gate

INPUT PULSE

LEVELS

0V to 3.0V for

5V operation

TIMING MEASUREMENT

REFERENCE LEVELS

Output: 1.5V

6 of 19

INPUT PULSE RISE

AND FALL TIMES

5ns

Page 7

Figure 5. 5V Power-Up/Down Waveform Timing

R

V

PF(MAX)

V

PF(MIN)

V

V

CCI

SO

ST

t

F

t

PF

t

FB

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

t

R

t

t

DR

REC

INPUTS

OUTPUTS

Warning: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in batterybackup mode.

RECOGNIZED

VALID

DON'T CARE

HIGH-Z

RECOGNIZED

VALID

7 of 19

Page 8

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

WAKEUP/KICKSTART TIMING

(TA = +25°C) (Figure 6)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Kickstart-Input Pulse Width t

Wakeup/Kickstart Power-On Timeout t

Note: Time intervals shown above are referenced in Wakeup/Kickstart.

Figure 6. Wakeup/Kickstart Timing Diagram

2

KSPW

(Note 11) 2 s

POTO

ms

Note 1: Limits at -40°C are not production tested and are guaranteed by design.

Note 2: Voltage referenced to ground.

Note 3: Outputs are open.

Note 4: The IRQ, PWR, and RST outputs are open drain.

Note 5: Value for voltage and currents is from the V

Note 6: If V

is less than V

PF

is greater than V

or V

of V

BAT

BAUX

.

BAT

and V

BAT

and V

, the device power is switched from VCC to the greater of V

BAUX

, the device power is switched from VCC to the greater of V

BAUX

Note 7: Value for voltage and currents is from the V

Note 8: I

Note 9: V

BAT1

BAT

and I

or V

are specified with V

BAT2

current. Using a 32,768Hz crystal connected to X1 and X2.

BAUX

floating and do not include any RAM current.

CCO

input pin to the V

CCI

BAT

or V

input pin to the V

BAUX

CCO

pin.

CCO

pin.

BAT

BAT

or V

or V

when VCC drops below VPF. If VPF

BAUX

when VCC drops below the greater

BAUX

Note 10: These parameters are sampled with a 5pF load and are not 100% tested.

Note 11: Typical values are at +25°C, nominal (active) supply, unless otherwise noted.

Note 12: If the oscillator is not enabled, the startup time of the oscillator after V

is applied is added to the wakeup/kickstart timeout.

CCI

8 of 19

Page 9

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

PIN DESCRIPTION

PIN NAME FUNCTION

Square-Wave Output. When enabled, the SQW pin outputs a 32.768kHz square wave. If the square

1 SQW

2

3 V

4 V

5

6

7

8 V

9 V

KS

BAT

BAUX

CEO

CEI

WE

CC1

CC0

10 N.C. No Connect

11

PWR

12, 13 X1, X2

14

15

RST

IRQ

16–20 A4–A0 Address Inputs. Selects one of 17 register locations.

21–23,

25–29

DQ0–DQ7

24, 31 GND

30

32

*See “Conditions of Acceptability” at www.maxim-ic.com/TechSupport/QA/ntrl.htm.

CS

OE

wave (E32K) and battery-backup 32kHz (BB32) bits are enabled, power is provided by V

VCC is absent.

Kickstart Input. This pin is used to wake up a system from an external event, such as a key closure.

The KS pin is normally connected using a pullup resistor to V

connect to ground.

Battery input for any standard 3V lithium cell or other energy source. Battery voltage must be held

between 2.5V and 3.7V for proper operation. UL recognized to ensure against reverse charging

current when used with a lithium battery. If not used, connect to ground.*

Auxiliary battery input for any standard 3V lithium cell or other energy source. Battery voltage must

be held between 2.5V and 3.7V for proper operation. Provides backup power to the device, and

provides power for auxiliary functions. UL recognized to ensure against reverse charging current

when used with a lithium battery. If not used, connect to ground.*

Chip-Enable Output. Buffered chip-enable output signal for external SRAM switches high when V

falls below the power-fail point V

.

PF

Chip-Enable Input. Input for chip-enable signal for external SRAM.

Write-Enable Input. Active-low input that enables DQ0–DQ7 for data input to the device.

DC power is applied to the device on these pins. VCC is the positive terminal. When power is applied

within the normal limits, the device is fully accessible and data can be written and read. When V

drops below the normal limits, reads and writes are inhibited. As VCC drops below the battery

voltage, the RAM and timekeeping circuits are switched over to the battery.

Buffered V

mode.

output to external SRAM. Switches to either V

CC

Power-On Output (Open Drain). This output, if used, is normally connected to power-supply control

circuitry. This pin requires a pullup resistor connected to a positive supply to operate correctly.

Connections for a standard 32.768kHz quartz crystal. For greatest accuracy, the DS1500 must be

used with a crystal that has a specified load capacitance of either 6pF or 12.5pF. The crystal select

(CS) bit in control register B is used to select operation with a 6pF or 12.5pF crystal. The crystal is

attached directly to the X1 and X2 pins. There is no need for external capacitors or resistors. An

external 32.768kHz oscillator can also drive the DS1500. In this configuration, the X1 pin is

connected to the external oscillator signal and the X2 pin is floated. For more information about

crystal selection and crystal layout considerations, refer to Application Note 58: Crystal

Considerations with Dallas Real-Time Clocks. See Figure 8.

Reset Output (Open Drain). This output, if used, is normally connected to a microprocessor-reset

input. This pin requires a pullup resistor connected to a positive supply to operate correctly. When

RST is active, the device is not accessible.

Interrupt Output (Open Drain). This output, if used, is normally connected to a microprocessor

interrupt input. This pin requires a pullup resistor connected to a positive supply to operate correctly.

Data I/O pins for 8-bit parallel data transfer.

DC power is applied to the device on these pins. VCC is the positive terminal. When power is applied

within the normal limits, the device is fully accessible and data can be written and read. When V

drops below the normal limits, reads and writes are inhibited. As V

voltage, the RAM and timekeeping circuits are switched over to the battery.

Chip-Select Input. Active-low input to enable the device.

Output-Enable Input. Active-low input that enables DQ0–DQ7 for data output from the device

. If the KS function is not used,

BAUX

BAT

or V

when in data retention

BAUX

drops below the battery

CC

BAUX

when

CC

CC

CCI

9 of 19

Page 10

Figure 7. Block Diagram

R

P

C

KS C

CS WE O

I

X1

X2

32.768kHz CLOCK

OSCILLATOR

CLOCK ALARM AND WATCHDOG

V

BAT

V

BAT

V

BAUX

GND

EI

POWER CONTROL

WRITE PROTECTION,

AND POWER-ON

RESET

Figure 8. Typical Crystal Layout

LOCAL GROUND PLANE (LAYER 2)

COUNTDOWN

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

RQ

SQW

16 x 8

CLOCK AND CONTROL

REGISTERS

A0–A4

DQ0–DQ7

256 x 8

NV SRAM

E

Dallas

Semiconductor

DS1500

V

CCO

ST

WR

EO

X1

CRYSTAL

X2

GND

10 of 19

Page 11

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

DETAILED DESCRIPTION

The RTC registers are double buffered into an internal and external set. The user has direct access to the external

set. Clock/calendar updates to the external set of registers can be disabled and enabled to allow the user to access

static data. When the crystal oscillator is turned on, the internal set of registers are continuously updated; this

occurs regardless of external register settings to guarantee that accurate RTC information is always maintained.

The DS1500 contains its own power-fail circuitry that automatically deselects the device when the V

supply falls

CCI

below a power-fail trip point. This feature provides a high degree of data security during unpredictable system

operation caused by low V

Nonvolatile control of the external SRAM is analogous to that of the RTC registers. When V

power fail,

CEO is driven to an inactive level regardless of CEI. This write protection occurs when V

levels. An external SRAM can be made nonvolatile by using the V

CCI

and CEO pins.

CCO

slews down during a

CCI

is less than

CCI

the power-fail trip point.

The DS1500 has interrupt (

activity. The

IRQ interrupt or RST outputs can be invoked as the result of a time-of-day alarm, CPU watchdog

IRQ), power control (PWR), and reset (RST) outputs that can be used to control CPU

alarm, or a kickstart signal. The DS1500 power-control circuitry allows the system to be powered on by an external

stimulus, such as a keyboard or by a time and date (wakeup) alarm. The

or either of these events, and can be used to turn on an external power supply. The

PWR output pin can be triggered by one

PWR pin is under software

control, so that when a task is complete, the system power can then be shut down. The DS1500 power-on reset

can be used to detect a system power-down or failure and hold the CPU in a safe reset state until normal power

returns and stabilizes; the

RST output is used for this function.

The DS1500 is a clock/calendar chip with the features described above. An external crystal and battery are the

only components required to maintain time-of-day and memory status in the absence of power..

Table 1. RTC Operating Modes

V

V

CCI

VSO < V

V

< VSO < VPF

CCI

CCI

> VPF

< VPF X X X High-Z X Deselect CMOS Standby

CCI

CS OE WE

VIH

VIL

VIL VIL VIH D

VIL VIH VIH

X X X High-Z X Data Retention Battery Current

X X High-Z X Deselect Standby

X

VIL D

DQ0–DQ7 A0–A4 MODE POWER

A

IN

A

OUT

High-Z

IN

IN

AIN

Write Active

Read Active

Read Active

DATA READ MODE

The DS1500 is in read mode whenever CS (chip select) and OE (output enable) are low and WE (write enable) is

high. The device architecture allows ripple-through access to any valid address location. Valid data is available at

the DQ pins within t

times are satisfied. If

) or at output-enable access time (t

(t

CSA

OE. If the outputs are activated before t

inputs are changed while

(address access) after the last address input is stable, provided that CS and OE access

AA

CS or OE access times are not met, valid data is available at the latter of chip-enable access

). The state of the data input/output pins (DQ) is controlled by CS and

OEA

, the data lines are driven to an intermediate state until tAA. If the address

AA

CS and OE remain valid, output data remains valid for output-data hold time (t

) but then

OH

goes indeterminate until the next address access (Table 1).

DATA WRITE MODE

The DS1500 is in write mode whenever CS and WE are in their active state. The start of a write is referenced to the

latter occurring transition of

return inactive for a minimum of t

prior to the end of the write and remain valid for tDH afterward. In a typical application, the OE signal is high

t

DS

during a write cycle. However,

contention. If

OE is low prior to a high-to-low transition on WE, the data bus can become active with read data

defined by the address inputs. A low transition on

CS or WE. The addresses must be held valid throughout the cycle. CS or WE must

prior to the initiation of a subsequent read or write cycle. Data in must be valid

WR

OE can be active provided that care is taken with the data bus to avoid bus

WE then disables the outputs t

after WE goes active (Table 1).

WEZ

11 of 19

Page 12

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

DATA RETENTION MODE

The DS1500 is fully accessible and data can be written and read only when V

when V

falls below the power-fail point VPF (point at which write protection occurs) the internal clock registers

CCI

and SRAM are blocked from any access. While in the data retention mode, all inputs are don’t cares and outputs

go to a high-Z state, with the exception of V

CEO is forced high. If V

BAUX

when V

CCI

and V

switched from V

is less than V

PF

drops below VPF. If VPF is greater than V

CCI

to the larger of V

BAT

BAT

operation and SRAM data are maintained from the battery until V

square-wave and battery-backup 32kHz functions are enabled, V

, CEO, and with the possible exception of KS, PWR, SQW, and RST.

CCO

and V

and V

, the device power is switched from V

BAUX

BAUX

when V

CCI

and V

BAT

BAUX

drops below the larger of V

is returned to nominal levels (Table 1). If the

CC

always provides power for the square-wave

BAUX

output, when the device is in battery-backup mode. All control, data, and address signals must be no more than

0.3V above V

CCI

.

is greater than VPF. However,

CCI

to the greater of V

CCI

, the device power and V

and V

BAT

BAUX

are

CCO

. RTC

BAT

AUXILIARY BATTERY

The V

output features in the absence of V

no V

This auxiliary battery can be used as the primary backup power source for maintaining the clock/calendar and

external SRAM. This occurs if the V

a single battery with the auxiliary features enabled, then V

not to be used, it should be grounded.

input is provided to supply power from an auxiliary battery for the DS1500 kickstart and square-wave

BAUX

is applied to the device.

CCI

. This power source must be available to use these auxiliary features when

CCI

pin is at a lower voltage than V

BAT

BAUX

should be used and connected to V

. If the DS1500 is to be backed-up using

BAUX

BAT

. If V

BAUX

is

POWER-ON RESET

A temperature-compensated comparator circuit monitors the level of V

point, the

RST signal (open drain) is pulled low. When V

pulled low for a period of t

. The power-on reset function is independent of the RTC oscillator and therefore

REC

returns to nominal levels, the RST signal continues to be

CCI

operational whether or not the oscillator is enabled.

. When V

CCI

falls to the power-fail trip

CCI

TIME AND DATE OPERATION

The time and date information is obtained by reading the appropriate register bytes. Table 2 shows the RTC

registers. The time and date are set or initialized by writing the appropriate register bytes. The contents of the time

and date registers are in the binary-coded decimal (BCD) format. Hours are in 24-hour mode. The day-of-week

register increments at midnight. Values that correspond to the day of week are user-defined, but must be

sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in

undefined operation.

READING THE CLOCK

When reading the clock and calendar data, it is possible to access the registers while an update (once per second)

occurs. There are three ways to avoid using invalid time and date data.

The first method uses the transfer enable (TE) bit in the control B register. Transfers are halted when a 0 is written

to the TE bit. Setting TE to 0 halts updates to the user-accessible registers, while allowing the internal registers to

advance. After the registers are read, the TE bit should be written to 1. TE must be kept at 1 for at least 366µs to

ensure a user register update.

The time and date registers can be read and stored in temporary variables. The time and date registers are then

read again, and compared to the first values. If the values do not match, the time and date registers should be read

a third time and compared to the previous values. This should be done until two consecutive reads of the time and

date registers match. The TE bit should always be enabled when using this method for reading the time and date,.

The third method of reading the time and date uses the alarm function. The alarm can be configured to activate

once per second, and the time-of-day alarm-interrupt enable bit (TIE) is enabled. The TE bit should always be

enabled. When the

IRQ pin goes active, the time and date information does not change until the next update.

12 of 19

Page 13

DS1500 Y2KC Watchdog RTC with Nonvolatile Control

SETTING THE CLOCK

It is recommended to halt updates to the external set of double buffered RTC registers when writing to the clock.

The (TE) bit should be used as described above before loading the RTC registers with the desired RTC count (day,

date, and time) in 24-hour BCD format. Setting the (TE) bit to 1 transfers the new values written to the internal RTC

registers and allows normal operation to resume.

CLOCK ACCURACY

A standard 32.768kHz quartz crystal should be directly connected to the DS1500 X1 and X2 oscillator pins. The

crystal selected for use should have a specified load capacitance (C

) of either 6pF or 12.5pF, and the crystal

L

select (CS) bit set accordingly. For more information about crystal selection and crystal layout considerations, refer

to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks. An external 32.768kHz oscillator can

also drive the DS1500. To achieve low-power operation when using an external oscillator, it may be necessary to

connect the X1 pin to the external oscillator signal through a series connection consisting of a resistor and a

capacitor. A typical configuration consists of a 1.0M resistor in series with a 100pF ceramic capacitor. When using

an external oscillator the X2 pin must be left open. Accuracy of DS1510 is better than ±1min/month at +25°C.

Table 2. Register Map

ADDRESS

00H

01H

02H

03H

04H

05H

06H

07H

08H

09H

0AH

0BH

0CH

0DH

0EH

0FH

10H

11H

12H

13H

14H-1FH Reserved

0 = “0” and are read only.

B7 B6 B5 B4 B3 B2 B1 B0

0 10 Seconds Seconds Seconds 00–59

0 10 Minutes Minutes Minutes 00–59

0 0 10 Hours Hour Hours 00–23

0 0 0 0 0 Day Day 1–7

0 0 10 Date Date Date 01–31

EOSC E32K

10 CENTURY Century Century 00–39

AM1 10 Seconds Seconds Alarm Seconds 00–59

AM2 10 Minutes Minutes Alarm Minutes 00–59

AM3 0 10 Hours Hour Alarm Hours 00–23

AM4 Dy/Dt 10 Date Day/Date Alarm Day/Date 1–7/1–31

BLF1 BLF2 PRS PAB TDF KSF WDF IRQF Control A

TE CS BME TPE TIE KIE WDE WDS Control B

BB32 10 MO Month Month 01–12

10 YEAR Year Year 00–99

0.1 Second 0.01 Second Watchdog 00–99

10 Second Second Watchdog 00–99

Extended RAM Address RAM Address LSB 00–FF

DATA

Reserved

Reserved

Extended RAM Data RAM Data 00–FF

FUNCTION

BCD

RANGE

POWER-UP DEFAULT STATES

These bits are set upon power-up: EOSC = 0, E32K = 0, TIE = 0, KIE = 0, WDE = 0, and WDS = 0.

Note: Unless otherwise specified, the state of the control/RTC/SRAM bits in the DS1500 is not defined upon initial

power application; the DS1500 should be properly configured/defined during initial configuration.

USING THE CLOCK ALARM

The alarm settings and control reside within registers 08h to 0Bh (Table 2). The TIE bit and alarm mask bits AM1 to

AM4 must be set as described below for the

The alarm functions as long as at least one supply is at a valid level. Note that activating the

use of V

BAUX

.

IRQ or PWR outputs to be activated for a matched alarm condition.

PWR pin requires the

13 of 19

Page 14

DS1500 Y2K Watchdog RTC with Nonvolatile Control

The alarm can be programmed to activate on a specific day of the month, day of the week, or repeat every day,

hour, minute, or second. It can also be programmed to go off while the DS1500 is in the battery-backed state of

operation to serve as a system wakeup. Alarm mask bits AM1 to AM4 control the alarm mode. Table 3 shows the

possible settings. Configurations not listed in the table default to the once-per-second mode to notify the user of an

incorrect alarm setting. When the RTC register values match alarm register settings, the time-of-day/date alarm

flag TDF bit is set to 1. Once the TDF flag is set, the TIE bit enables the alarm to activate the

enables the alarm flag to activate the

PWR pin. The alarm functions on V

CC

, V

BAT

, and V

BAUX

IRQ pin. The TPE bit

.

Table 3. Alarm Mask Bits

DY/DT AM4 AM3 AM2 AM1 ALARM RATE

X 1 1 1 1 Once per second

X 1 1 1 0 When seconds match

X 1 1 0 0 When minutes and seconds match

X 1 0 0 0 When hours, minutes, and seconds match

0 0 0 0 0 When date, hours, minutes, and seconds match

1 0 0 0 0 When day, hours, minutes, and seconds match

CONTROL REGISTERS

The controls and status information for the DS1500 features are maintained in the following register bits.

Month Register (05h)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

EOSC E32K

EOSC, Oscillator Start/Stop Bit (05h Bit 7)

This bit when set to logic 0 starts the oscillator. When this bit is set to logic 1, the oscillator is stopped. This bit is

automatically set to logic 0 by the internal power-on reset when power is applied and V

voltage.

E32K, Enable 32.768kHz Output (05h Bit 6)

This bit, when written to 0, enables the 32.768 kHz oscillator frequency to be output on the SQW pin if the oscillator

is running. This bit is automatically set to logic 0 by the internal power-on reset when power is applied and V

rises above the power-fail voltage.

BB32, Battery Backup 32kHz Enable Bit (05h Bit 5)

When the BB32 bit is written to 1, it enables a 32kHz signal to be output on the SQW pin while the part is in

battery-backup mode, if voltage is applied to V

AM1 to AM4, Alarm Mask Bits (08H Bit 7; 09H Bit 7; 0AH Bit 7; 0BH Bit 7)

Bit 7 of registers 08h to 0Bh contains an alarm mask bit, AM1 to AM4. These bits, in conjunction with the TIE

described later, allow the

IRQ output to be activated for a matched-alarm condition. The alarm can be programmed

to activate on a specific day of the month, day of the week, or repeat every day, hour, minute, or second. Table 3

shows the possible settings for AM1 to AM4 and the resulting alarm rates. Configurations not listed in the table

default to the once-per-second mode to notify the user of an incorrect alarm setting.

DY/DT, Day/Date Bit (0BH Bit 6)

The DY/DT bit controls whether the alarm value stored in bits 0 to 5 of 0BH reflects the day of the week or the date

of the month. If DY/DT is written to a 0, the alarm is the result of a match with the date of the month. If DY/DT is

written to a 1, the alarm is the result of a match with the day of the week.

BB32 10 Month Month

rises above the power-fail

CC

BAUX.

CC

14 of 19

Page 15

DS1500 Y2K Watchdog RTC with Nonvolatile Control

Control A Register (0Eh)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

BLF1 BLF2 PRS PAB TDF KSF WDF IRQF

BLF1, Valid RAM and Time Bit 1 (0Eh Bit 7); BLF2, Valid RAM and Time Bit 2 (0Eh Bit 6)

These status bits give the condition of any batteries attached to the V

monitors the battery voltage of the backup-battery sources (V

the battery voltage on V

condition of V

with BLF2 reflecting V

BAT

BAT

and V

is less than V

BAUX

. If either bit is read as 1, the voltage on the respective pin is inadequate

BAUX

, otherwise BLF1 and BLF2 bits are 0. BLF1 reflects the

BLF

BAT

and V

or V

BAT

). The BLF1 and BLF2 bits are set to 1 if

BAUX

pins. The DS1500 constantly

BAUX

to maintain the RAM memory or clock functions. These bits are read only.

PRS, Reset Select Bit (0Eh Bit 5)

When set to 0, the

PWR pin is set high-Z when the DS1500 goes into power-fail. When set to 1, the PWR pin

remains active upon entering power-fail.

PAB, Power Active-Bar Control Bit (0Eh Bit 4)

When this bit is 0, the

PWR pin is in the active-low state. When this bit is 1, the PWR pin is in the high-impedance

state. The user can write this bit to 1 or 0. If either TDF AND TPE = 1 or KSF = 1, the PAB bit is cleared to 0. This

bit can be read or written.

TDF, Time-of-Day/Date Alarm Flag (0Eh Bit 3)

A 1 in the TDF bit indicates that the current time has matched the alarm time. If the TIE bit is also 1, the

IRQ pin

goes low and a 1 appears in the IRQF bit. This bit is cleared by reading the register or writing it to 0.

KSF, Kickstart Flag (0Eh Bit 2)

This bit is set to 1 when a kickstart condition occurs or when the user writes it to 1. If the KIE bit is also 1, the

IRQ

pin goes low and a 1 appears in the IRQF bit. This bit is cleared by reading the register or writing it to 0.

WDF, Watchdog Flag (0Eh Bit 1)

If the processor does not access the DS1500 with a write within the period specified in addresses 0CH and 0DH,

the WDF bit is set to 1. WDF is cleared by writing it to 0.

IRQF, Interrupt Request Flag (0Eh Bit 0)

The interrupt request flag (IRQF) bit is set to 1 when one or more of the following are true:

TDF = TIE = 1

KSF = KIE = 1

WDF = WDE = 1

i.e., IRQF = (TDF x TIE) + (KSF x KIE) + (WDF x WDE)

Any time the IRQF bit is 1, the

IRQ pin is driven low.

Clearing IRQ and Flags

The time-of-day/date alarm flag (TDF), watchdog flag (WDF), kickstart flag (KSF) and interrupt request flag (IRQF)

are cleared by reading the flag register (0EH). The address must be stable for a minimum of 15ns while

are active. After the address stable requirement has been met, either a change in address, a rising edge of

a rising edge of

CS causes the flags to be cleared. The IRQ pin goes inactive after the IRQF flag is cleared. TDF

and WDF can also be cleared by writing to 0.

CS and OE

OE, or

15 of 19

Page 16

DS1500 Y2K Watchdog RTC with Nonvolatile Control

Control B Register (0Fh)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

TE CS BME TPE TIE KIE WDE WDS

TE, Transfer Enable Bit (0Fh Bit 7)

When the TE bit is 1, the update transfer functions normally by advancing the counts once per second. When the

TE bit is written to 0, any update transfer is inhibited and the program can initialize the time and calendar bytes

without an update occurring in the midst of initializing. Read cycles can be executed in a similar manner. TE is a

read/write bit that is not modified by internal functions of the DS1500.

CS, Crystal Select Bit (0Fh Bit 6)

When CS is set to 0, the oscillator is configured for operation with a crystal that has a 6pF specified load

capacitance. When CS = 1, the oscillator is configured for a 12.5pF crystal. CS is disabled in the DS1510 module

and should be set to CS = 0.

BME, Burst-Mode Enable Bit (0Fh Bit 5)

The burst-mode enable bit allows the extended user RAM address registers to automatically increment for

consecutive reads and writes. When BME is set to 1, the automatic incrementing is enabled; when BME is set to 0,

the automatic incrementing is disabled.

TPE, Time-of-Day/Date Alarm Power-Enable Bit (0Fh Bit 4)

The wakeup feature is controlled through the TPE bit. When the TDF flag bit is set to 1, if TPE is 1, the

PWR pin is

driven active. Therefore, setting TPE to 1 enables the wakeup feature. Writing a 0 to TPE disables the wakeup

feature.

TIE, Time-of-Day/Date Alarm Interrupt-Enable Bit (0Fh Bit 3)

The TIE bit allows the TDF flag to assert an interrupt. When the TDF flag bit is set to 1, if TIE is 1, the IRQF flag bit

is set to 1. Writing a 0 to the TIE bit prevents the TDF flag from setting the IRQF flag.

KIE, Kickstart Enable-Interrupt Bit (0Fh Bit 2)

When V

KS pulsed low), causing the KSF bit to be set to 1. When V

(

is set to 1 while system power is applied, both

When KIE is cleared to a 0, the KSF bit has no effect on the

voltage is absent and KIE is set to 1, the PWR pin is driven active low when a kickstart condition occurs

CCI

is then applied, the IRQ pin is also driven low. If KIE

CCI

IRQ and PWR are driven low in response to KSF being set to 1.

PWR or IRQ pins.

WDE, Watchdog Enable Bit (0Fh Bit 1)

When WDE is set to 1, the watchdog function is enabled, and either the

IRQ or RST pin is pulled active based on

the state of the WDS and WDF bits. This bit is automatically cleared to logic 0 to by the internal power-on reset

when power is applied and V

rises above the power-fail voltage.

CC

WDS, Watchdog Steering Bit (0Fh Bit 0)

If WDS is 0 when the watchdog flag bit WDF is set to 1, the

1, the watchdog outputs a negative pulse on the

RST output. The WDE bit resets to 0 immediately after RST goes

active. This bit is automatically cleared to logic 0 to by the internal power-on reset when power is applied and V

IRQ pin is pulled low. If WDS is 1 when WDF is set to

CC

rises above the power-fail voltage.

CLOCK OSCILLATOR CONTROL

The clock oscillator can be stopped at any time. To increase the shelf life of a backup lithium-battery source, the

oscillator can be turned off to minimize current drain from the battery. The

EOSC bit is used to control the state of

the oscillator, and must be set to 0 for the oscillator to function.

USING THE WATCHDOG TIMER

The watchdog timer can be used to restart an out-of-control processor. The watchdog timer is user programmable

in 10ms intervals ranging from 0.01 seconds to 99.99 seconds. The user programs the watchdog timer by writing

the timeout value into the two BCD watchdog registers (address 0Ch and 0Dh). The watchdog reloads and restarts

whenever the watchdog times out. If either watchdog register is nonzero, a timeout sets the WDF bit to 1,

16 of 19

Page 17

DS1500 Y2K Watchdog RTC with Nonvolatile Control

regardless of the state of the watchdog enable (WDE) bit, to serve as an indication to the processor that a

watchdog timeout has occurred. The watchdog timer operates in two modes, repetitive and single-shot.

If WDE is 1 and the watchdog steering bit (WDS) is 0, the watchdog is in repetitive mode. When the watchdog

times out, both WDF and IRQF are set.

IRQ goes active and IRQF goes to 1. The watchdog timer is reloaded when

the processor performs a write of the watchdog registers and the timeout period restarts. Reading the control A

register clears the

IRQ flag.

If WDE and WDS are 1, the watchdog is in single-shot mode. When the watchdog times out,

period of t

. When RST goes inactive, WDE resets to 0. Writing a value of 00h to both watchdog registers

REC

RST goes active for a

disables the watchdog timer. The watchdog function is automatically disabled upon power-up by the power-on

reset setting WDE = 0 and WDS = 0. The watchdog registers are not initialized at power-up and should be

initialized by the user.

Note: The TE bit must be used to disable transfers when writing to the watchdog registers.

The following summarizes the configurations in which the watchdog can be used:

WDE = 0 and WDS = 0: WDF is set.

WDE = 0 and WDS = 1: WDF is set.

WDE = 1 and WDS = 0: WDF and IRQF are set, and the

WDE = 1 and WDS = 1: WDF is set, the

RST pin pulses low, and WDE resets to 0.

IRQ pin is pulled low.

WAKEUP/KICKSTART

The DS1500 incorporates a wakeup feature, which powers on at a predetermined date by activating the PWR

output pin. In addition, the kickstart feature allows the system to be powered up in response to a low-going

transition on the

upon such events as key closure, or a modem-ring-detects signal. To use either the wakeup or the kickstart

features, the DS1500 must have an auxiliary battery connected to the V

The wakeup feature is controlled through the time-of-day/date power-enable bit (TPE). Setting TPE to 1 enables

the wakeup feature. Transfers (TE) must be enabled for a wake up event to occur. Writing TPE to 0 disables the

wakeup feature. Similarly, the kickstart feature is controlled through the kickstart interrupt-enable bit (KIE).

If the wakeup feature is enabled, while the system is powered down (no V

the current day or date for a match condition with day/date alarm register (0Bh). With the day/date alarm register,

the hours, minutes, and seconds alarm bytes in the clock/calendar register map (02h, 01h, and 00h) are also

monitored. As a result, a wakeup occurs at the day or date and time specified by the day/date, hours, minutes, and

seconds alarm register values. This additional alarm occurs regardless of the programming of the TIE bit. When the

match condition occurs, the

supply, which provides V

this time, the time-of-day/date alarm flag is set, indicating that a wakeup condition has occurred.

If V

t

KSPW

is present, while VCC is low, the KS input pin is monitored for a low-going transition of minimum pulse width

BAUX

. When such a transition is detected, the PWR line is pulled low, as it is for a wakeup condition. Also at this

time, KSF is set, indicating that a kickstart condition has occurred. The

be allowed to float.

The timing associated with these functions is divided into five intervals, labeled 1 to 5 on the diagram.

The occurrence of either a kickstart or wakeup condition causes the

During Interval 1, if the supply voltage on the V

timeout period (t

or VPF in this time, then the PWR output pin is turned off and returns to its high-impedance level. In this event,

V

BAT

IRQ pin also remains tri-stated. The interrupt flag bit (either TDF or KSF) associated with the attempted power-

the

on sequence remains set until cleared by software during a subsequent system power-on.

KS pin, without operating voltage applied to the V

CCI

PWR pin is automatically driven low. This output can turn on the main system power

voltage to the DS1500 as well as the other major components in the system. Also, at

CCI

pin rises above the greater of V

CCI

) expires, then PWR remains at the active-low level. If V

POTO

pin. As a result, system power can be applied

pin, and the oscillator must be running.

BAUX

voltage), the clock/calendar monitors

CCI

KS input pin is always enabled and must not

PWR pin to be driven low, as described above.

or VPF before the power-on

BAT

does not rise above the greater of

CCI

17 of 19

Page 18

DS1500 Y2K Watchdog RTC with Nonvolatile Control

If V

is applied within the timeout period, then the system power-on sequence continues, as shown in Intervals 2

CCI

to 5 in the timing diagram. During Interval 2,

indicating that either TDF or KSF was set in initiating the power-on. In the diagram,

to the V

on. The

supply. Also at this time, the PAB bit is automatically cleared to 0 in response to a successful power-

BAUX

PWR line remains active as long as the PAB remains cleared to 0.

PWR remains active, and IRQ is driven to its active-low level,

KS is assumed to be pulled up

At the beginning of Interval 3, the system processor has begun code execution and clears the interrupt condition of

TDF and/or KSF by writing 0s to both of these control bits. As long as no other interrupt within the DS1500 is

pending, the

IRQ line is taken inactive once these bits are reset, and execution of the application software can

proceed. During this time, the wakeup and kickstart functions can be used to generate status and interrupts. TDF is

set in response to a day/date, hours, minutes, and seconds match condition. KSF is set in response to a low-going

transition on

response to enabled event. In addition, the other possible interrupt sources within the DS1500 can cause

driven low. While system power is applied, the on-chip logic always attempts to drive the

response to the enabled kickstart or wakeup condition. This is true even if

KS. If the associated interrupt-enable bit is set (TDE and/or KIE), then the IRQ line is driven low in

IRQ to be

PWR pin active in

PWR was previously inactive as the

result of power being applied by some means other than wakeup or kickstart.

The system can be powered down under software control by setting the PAB bit to 1. This causes the open-drain

PWR pin to be placed in a high-impedance state, as shown at the beginning of Interval 4 in the timing diagram. As

voltage decays, the IRQ output pin is placed in a high-impedance state when V

V

CCI

goes below VPF. If the

CCI

system is to be again powered on in response to a wakeup or kickstart, then both the TDF and KSF flags should be

cleared, and TPE and/or KIE should be enabled prior to setting the PAB bit.

During Interval 5, the system is fully powered down. Battery backup of the clock calendar and NV RAM is in effect

and

IRQ is tri-stated, and monitoring of wakeup and kickstart takes place. If PRS = 1, PWR stays active; otherwise,

if PRS = 0,

PWR is tri-stated.

SQUARE-WAVE OUTPUT

The square-wave output is enabled and disabled through the E32K bit. If the square wave is enabled (E32K = 0)

and the oscillator is running, then a 32.768kHz square wave is output on the SQW pin. If the battery-backup

32kHz-enable bit (BB32) is enabled, and voltage is applied to V

the SQW pin in the absence of V

CCI

.

, then the 32.768kHz square wave is output on

BAUX

BATTERY MONITOR

The DS1500 constantly monitors the battery voltage of the backup-battery sources (V

low flags BLF1 and BLF2 are set to 1 if the battery voltages on V

otherwise, BLF1 and BLF2 are 0. BLF1 monitors V

and BLF2 monitors V

BAT

and V

BAT

BAUX

BAUX

.

BAT

and V

). The battery

BAUX

are less than 2.5V (typical);

256 x 8 EXTENDED RAM

The DS1500 provides 256 x 8 of on-chip SRAM, which is controlled as nonvolatile storage sustained from a lithium

battery. On power-up, the RAM is taken out of write-protect status by an internal signal.

Two on-chip latch registers control access to the SRAM. One register is used to hold the SRAM address; the other

is used to hold read/write data. The SRAM address space is from 00h to FFh. The 8-bit address of the RAM

location to be accessed must be loaded into the extended RAM address register located at 10h. Data in the

addressed location can be read by performing a read operation from location 13h, or written to by performing a

write operation to location 13h. Data in any addressed location can be read or written repeatedly with changing the

address in location 10h.

To read or write consecutive extended RAM locations, a burst mode feature can be enabled to increment the

extended RAM address. To enable the burst mode feature, set the BME bit to 1. With burst mode enabled, write

the extended RAM starting address location to register 10h. Then read or write the extended RAM data from/to

register 13h. The extended RAM address locations are automatically incremented on the rising edge of

WE only when register 13h is being accessed (Figure 4). The address pointer wraps around after the last address

is accessed.

OE, CS,

18 of 19

Page 19

DS1500 Y2K Watchdog RTC with Nonvolatile Control

IRQ

R

KSPWR

C

WEOECEI

CEOC

SELECTOR GUIDE

PART

DS1500YEN

DS1500WEN 3.3 DS1500W N

NOMINAL

(V)

V

CC

TOP MARK

5 DS1500Y N

TYPICAL OPERATING CIRCUIT

V

V

CC

CC

RPU

CRYSTAL

V

CC

X2X1

RST

CPU

IRQ

ST

V

CCI

V

CCO

SQW

V

BAUX

A0–A4

DQ0–DQ7

Dallas

Semiconductor

DS1500

E

GND

GND

V

BAT

PACKAGE INFORMATION

(For the latest package outline information, go to www.maxim-ic.com/DallasPackInfo.)

V

CC

E

SRAM

19 of 19

Loading...

Loading...