Page 1

EDID EEPROM for DDC2TM monitor

01W145A

BU9882-

W/F-W/FV-W

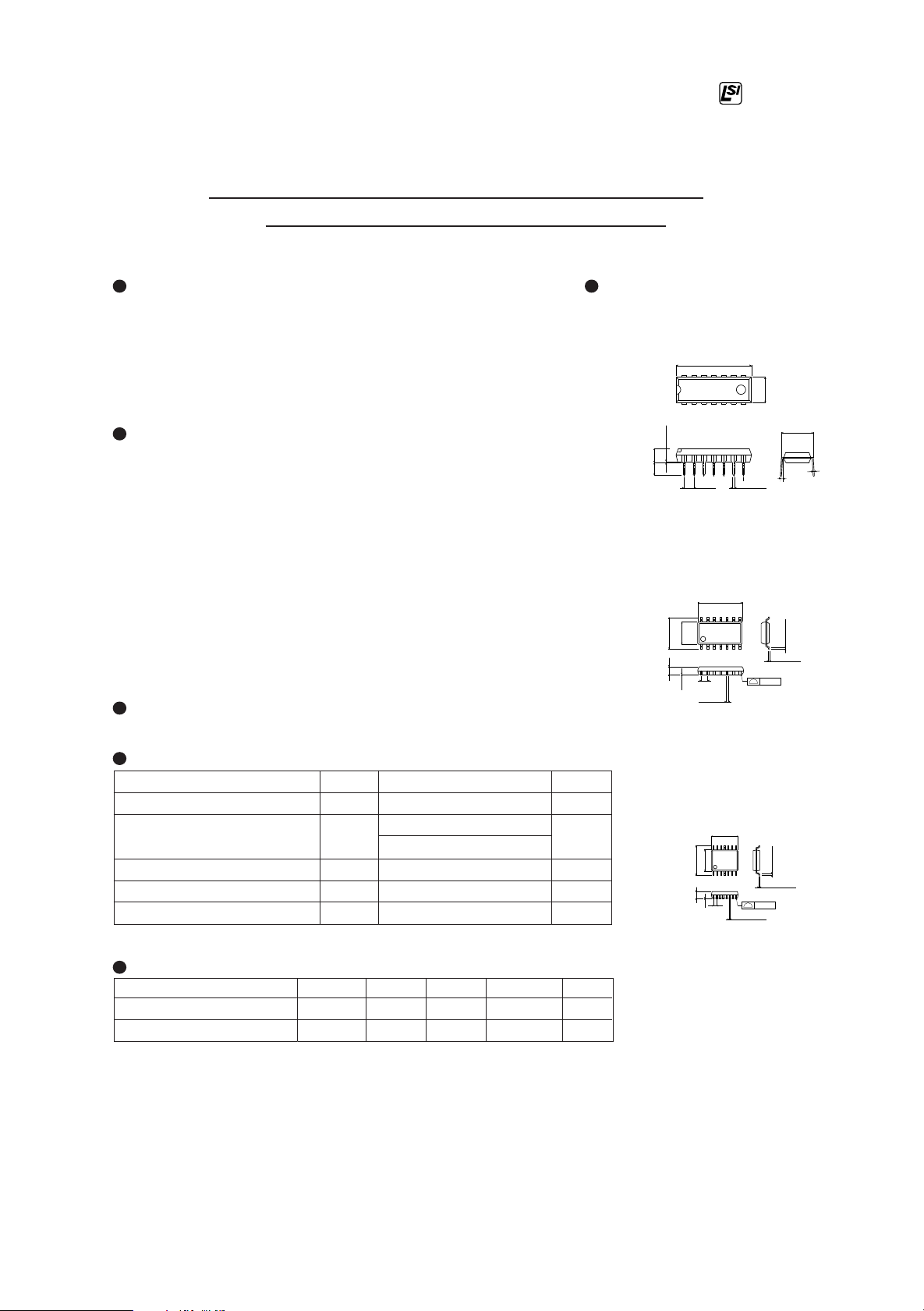

Description Dimension (Units : mm)

BU9882-W/F-W/FV-W is EEPROM for storing EDID

based on DDC2

TM

of PC monitor. Due to the independent

TM

BU9882-W

operating ports, and memory, this EEPROM can

simultaneously communicate with two personal computers.

19.4 ± 0.3

14 8

There is also a switch that connects the PC to CPU in the

monitor side, so that the PC can control the monitor.

Features

1)128word x 8bit x 2port configuration of 2kbit serial EEPROM

2) 2PC connection possible

3) 2port simultaneous read function when dual port used.

4) For DDC2

TM

5) Wide range of power supply voltage (2.5~5.5V)

0.51Min.

4.25 ± 0.3

3.2 ± 0.2

2.54

DIP14

6) Page write function (Max. 8Byte)

7) Low current consumption

Operating (5V) : 1.5mA (Typ.)

Stand by (5V) : 0.1µA (Typ.)

8) Inadvertent write protection function

Built-in noise filter to SCL, SDA pin

Write protection at low power supply voltage

9) High reliable Double-Cell system

BU9882F-W

14

6.2±0.3

4.4±0.2

1

1.5±0.1

1.27

0.11

0.4±0.1

8.7±0.2

Applications

CRT monitor, LCD monitor, LCD projector

SOP14

Absolute Maximum Ratings (Ta=25˚C)

Parameter Symbol

Supply Voltage

Power Dissipation

Operating Temperature Range

Storage Temperature Range

Terminal Voltage

∗1 Derating : 9.5mW/˚C for operation above Ta=25˚C ∗2 Derating : 4.5mW/˚C for operation above Ta=25˚C

∗3 Maximum: 6.8V

Vcc

Pd

Topr

Tstg

—

Limits

–0.3 ~

950 (DIP14)

450 (SOP14)

–40

~

–65

~

~

125

VCC+1.0 –0.3

6.5

85

Unit

BU9882FV-W

V

∗1

∗2

mW

˚C

˚C

∗3

V

5.0 ± 0.2

4.4 ± 0.2

6.4 ± 0.3

1

0.1

0.65

1.15 ± 0.1

SSOP-B14

Recommended Operating Conditions (Ta=25˚C)

Parameter

Supply Voltage 5.5 V

Input Voltage VCC+1.0 V

Symbol

VCC

VIN

Min. Max. Unit

2.5

0

Typ.

—

—

71

0.5 ± 0.1

8

7

8714

0.22 ± 0.1

6.5 ± 0.3

0.15±0.1

0.1

0.3Min.

0.15 ± 0.1

0.1

7.62

0° ~ 15°

0.3Min.

1

± 0.

0.3

November, 2001

Page 2

Electrical characteristics (Unless otherwise specified; Ta=–40 ~ 85˚C, Vcc=2.5 ~ 5.5V)

Symbol

"H" Input Voltage 1

"L" Input Voltage 1

"L" Input Voltage 2

"L" Output Voltage

Input Leak Current 1

Input Leak Current 2

Output Leak Current

Operating Current

Stand by current

∗ IOL at monitor mode (DDCENA=High) is sum of current flowed from Pull up resistance on SDA_MON side, and Pull up resistance on SDA_PC0/PC1 side.

VIH1

VIL1

VIL2

VOL1

ILI1

ILI2

ILO

ICC

ISB

Min.

2.0

—

—

—

–1

–1

–1

—

—

—

—

—

—

—

—

—

—

0.1

Max.

—

0.8

0.2VCC

0.4

1

50

1

3.0

5

Unit ConditionsTyp. Parameter

V

VCC≥4.0V

V

V

VCC<4.0V

SDA_PC0/1, IOL=3.0mA

V

µA

SCL_PC0/1, DDCENA,BANKSEL,VIN=0V~VCC+1.0V

µA

WPB

SDA_PC0/1,SCL/SDA_MON(DDCENA=GND),

µA

VOUT=0V~VCC+1.0V

fSCL=400kHz, VCC=5.5V

mA

∗

SCL/SDA_PC0/1=VCC

µA

SCL/SDA_MON=Hi—Z

DDCENA=WPB=BANKSEL=GND, DUALPCB=VCC

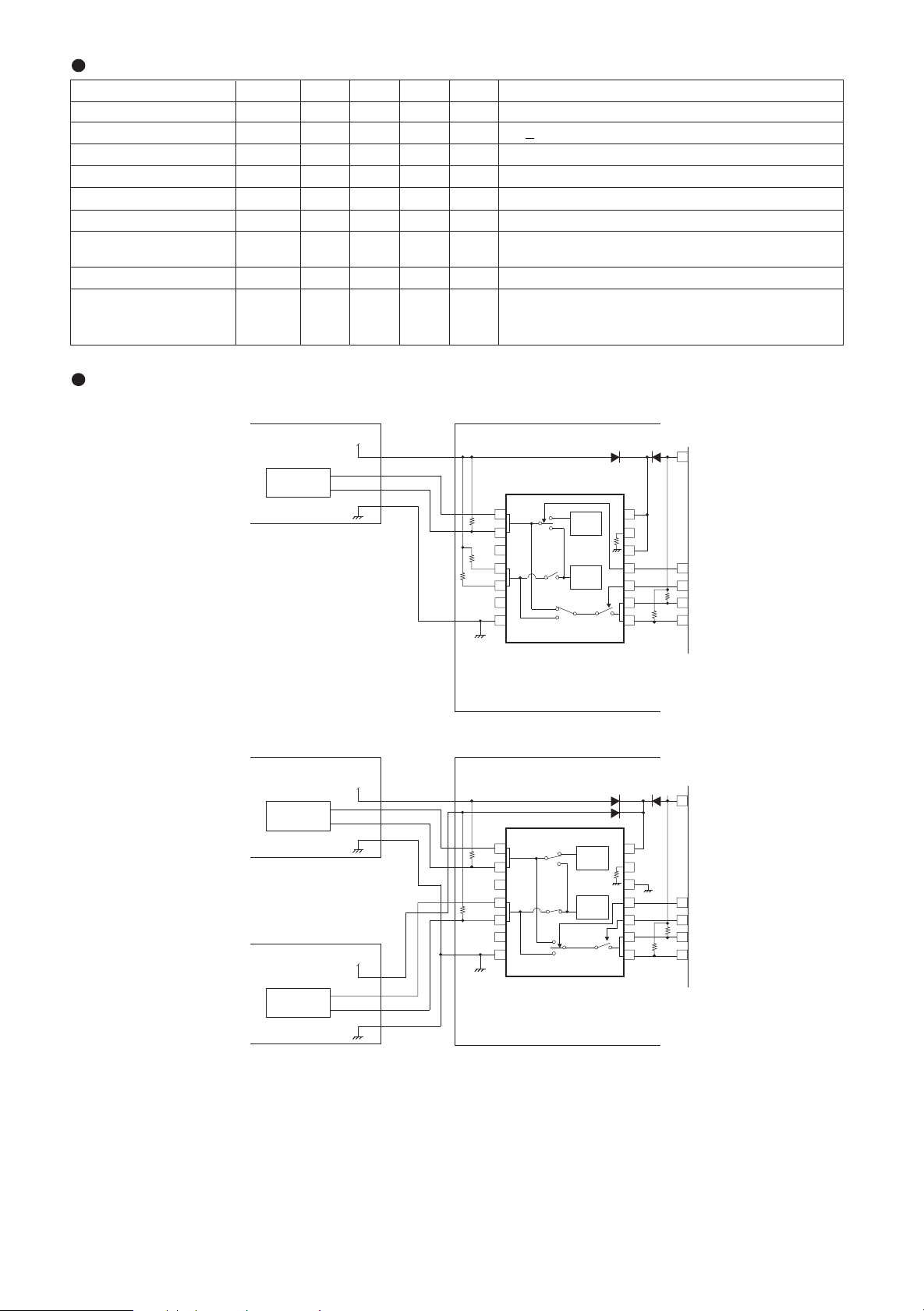

Application Circuit

< SINGLE Port >

PC 0 MONITOR

SCL

SDA

SCL_PCO

SDA_PCO

SCL_PC1

SDA_PC1

GND

1

2

NC

3

4

5

NC

6

7

BU9882-W/F-W/FV-W

BANK0

(1kbit)

BANK1

(1kbit)

VCC

14

WPB

13

DUALPCB

12

BANKSEL

11

DDCENA

10

SCL_MON

9

SDA_MON

8

VCC

CPU

< DUAL Port >

PC 0 MONITOR

SCL

SDA

PC 1

SCL

SDA

SCL_PCO

SDA_PCO

SCL_PC1

SDA_PC1

GND

1

2

NC

3

4

5

NC

6

7

BU9882-W/F-W/FV-W

BANK0

(1kbit)

BANK1

(1kbit)

VCC

14

WPB

13

DUALPCB

12

BANKSEL

11

DDCENA

10

SCL_MON

9

SDA_MON

8

VCC

CPU

Loading...

Loading...