Page 1

Features

• Utilizes the AVR

• AVR – High-performance and Low-power RISC Architecture

– 120 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

• Data and Non-volatile Program and Data Memories

– 2K Bytes of In-System Self Programmable Flash

Endurance 10,000 Write/Erase Cycles

– 128 Bytes In-System Programmable EEPROM

Endurance: 100,000 Write/Erase Cycles

– 128 Bytes Internal SRAM

– Programming Lock for Flash Program and EEPROM Da ta Security

• Peripheral Features

– One 8-bit Timer/Counter with Separate Prescaler

– One 16-bit Timer/Counter with Separate Prescaler,

Compare, Capture Modes and Two PWM Channels

– On-chip Analog Comparator

– Programmable Watchdog Timer with On-chip Oscillator

– USI – Universal Serial Interface

– Full Duplex UART

• Special Microcontroller Features

– debugWIRE On-chip Debugging

– In-System Programmable via SPI Port

– External and Internal Interrupt Sources

– Low-power Idle, Power-down, and Standby Modes

– Enhanced Power-on Reset Circuit

– Programmable Brown-out Detection Circuit

– Internal Calibrated Oscillator

• I/O and Packages

– 18 Programmable I/O Lines

– 20-pin PDIP, 20-pin SOIC, and 32-pin MLF

• Operating Voltages

– 1.8 - 5.5V (ATtiny2313)

• Speed Grades

– 0 - 16MHz (ATtiny2313). For Speed vs. VCC: See Figure 81 on page 180.

• Power Consumption Estimates

– Active Mode

1 MHz, 1.8V: 300 µA

32 kHz, 1.8V: 20 µA (including oscillator)

– Power-down Mode

0.5 µA at 1.8V

®

RISC Architecture

8-bit

Microcontroller

with 2K Bytes

In-System

Programmable

Flash

ATtiny2313

Preliminary

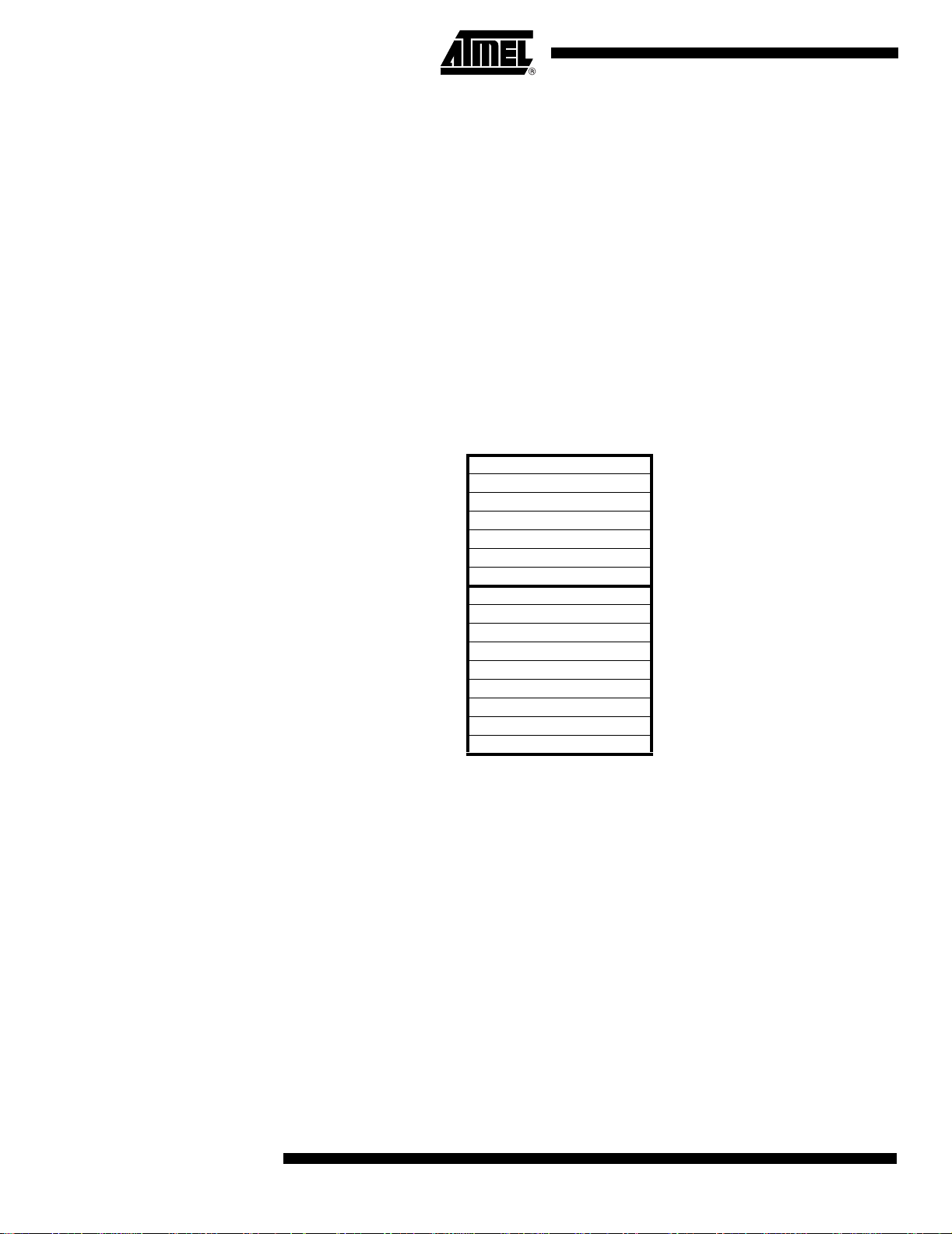

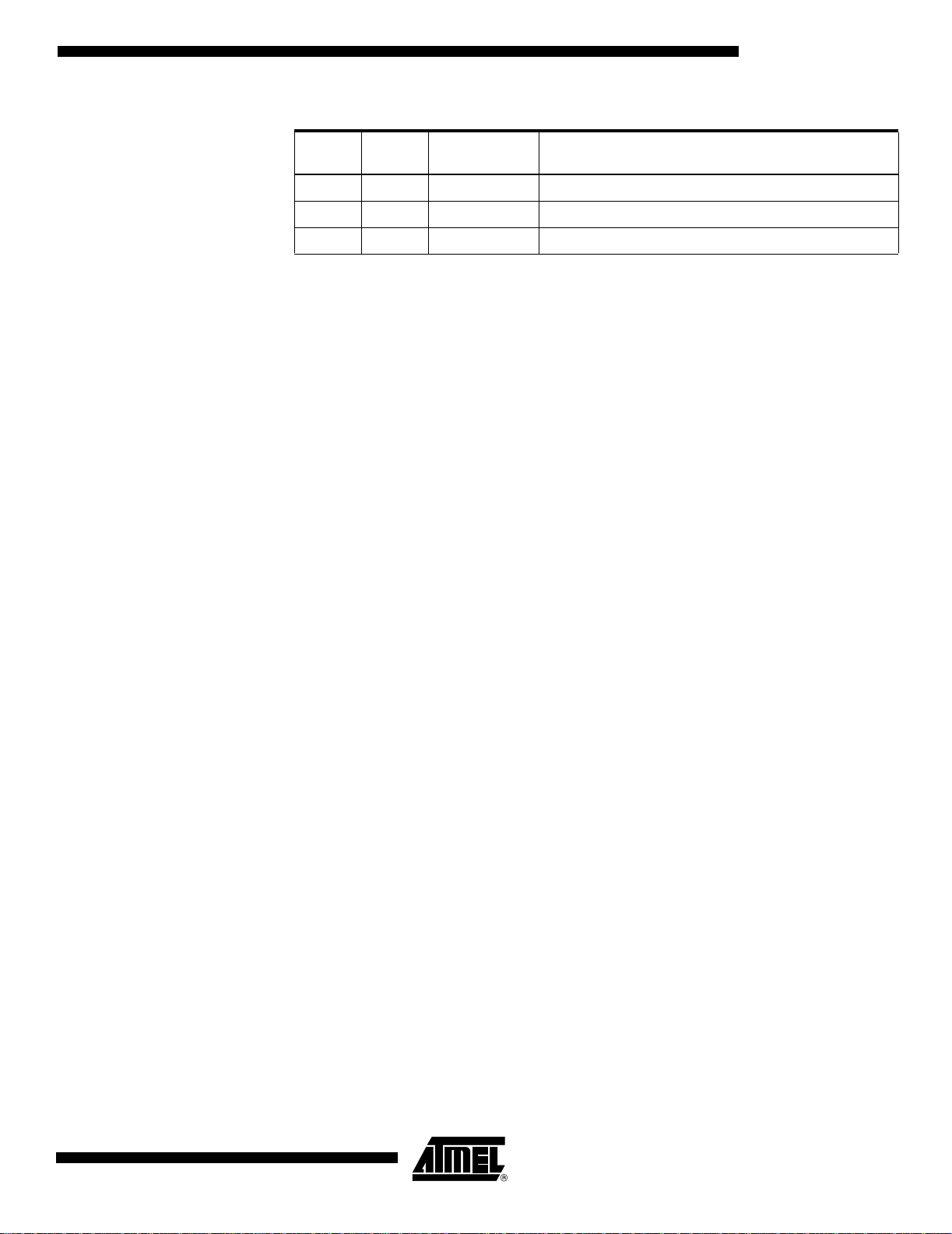

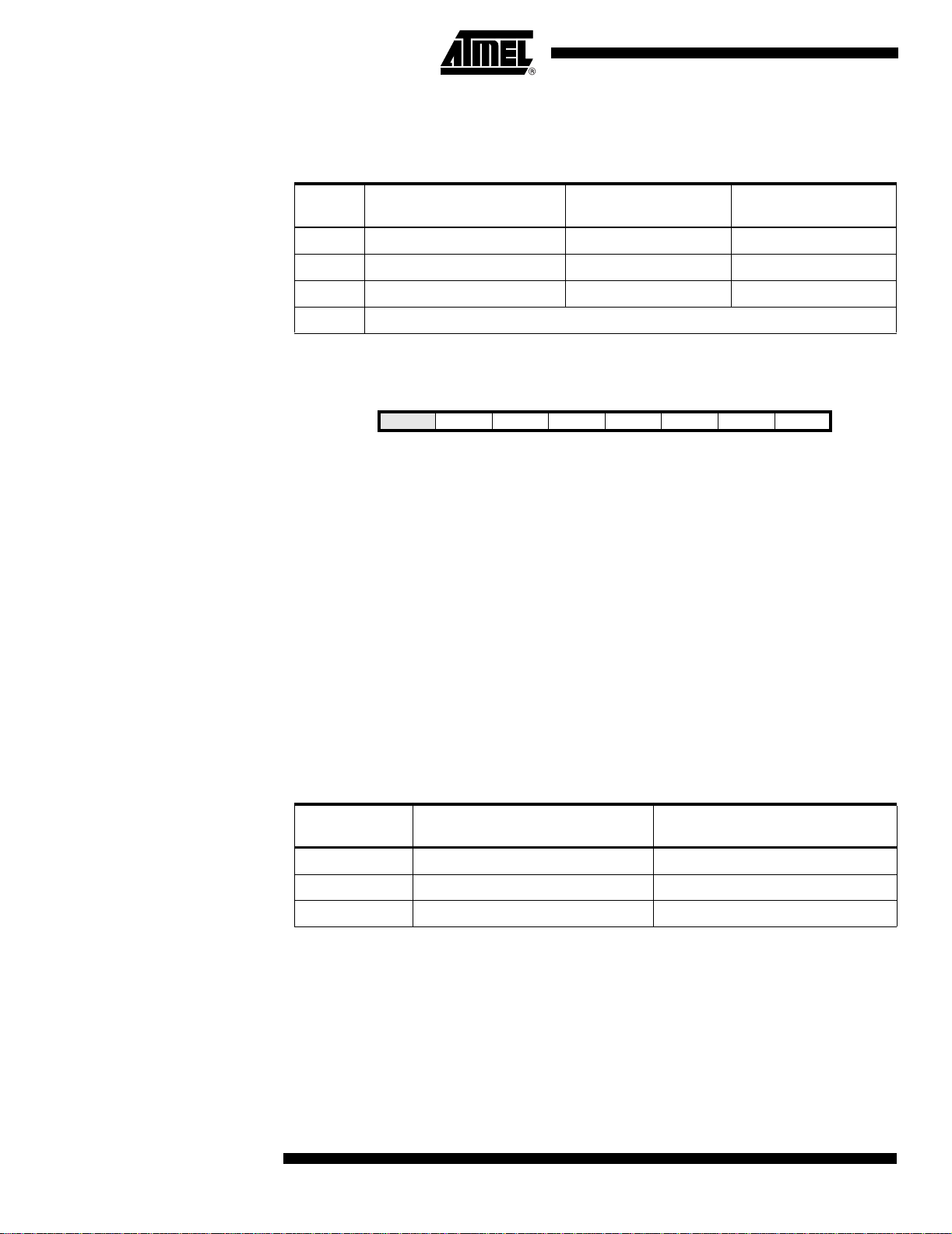

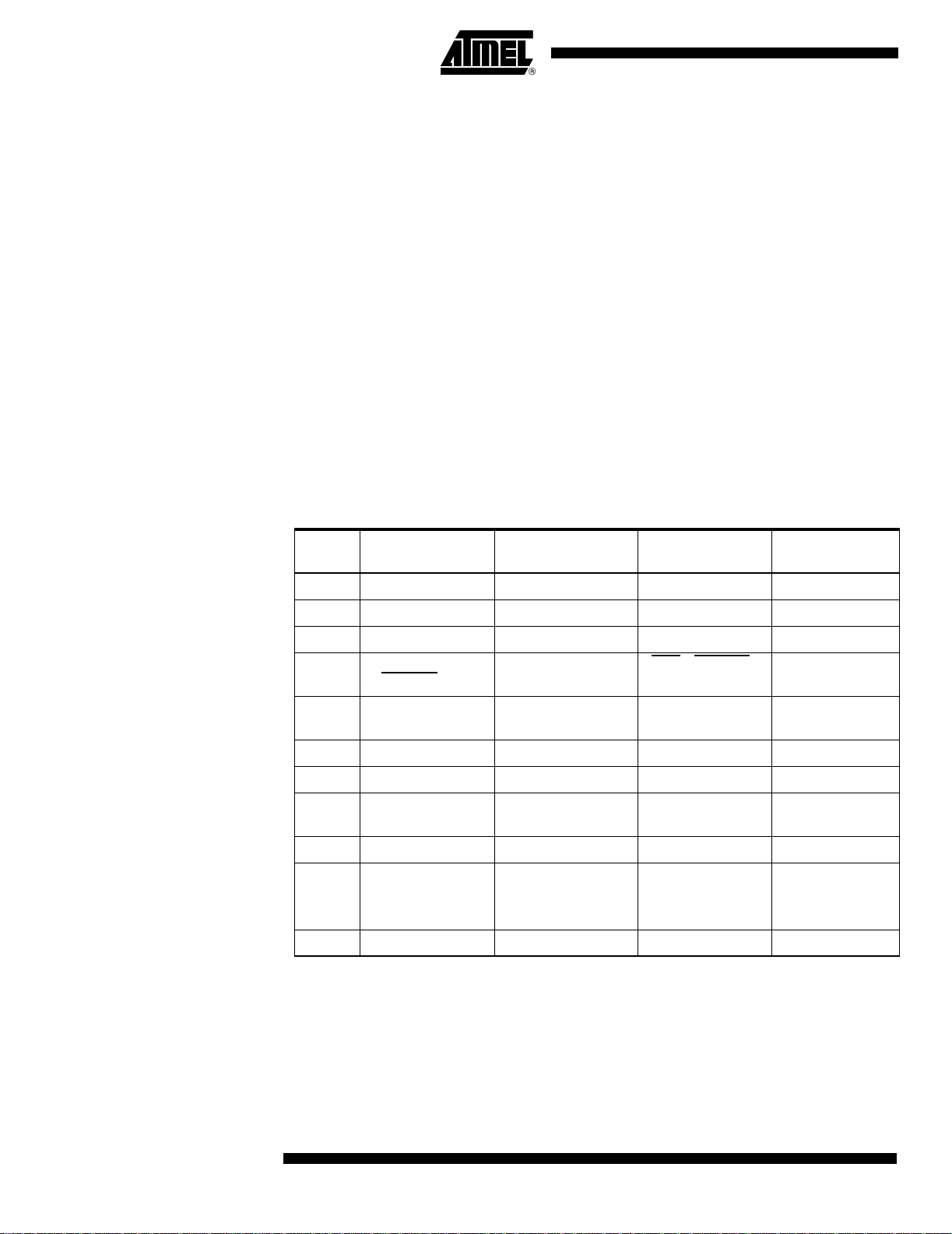

Pin Configurations

Figure 1. Pinout ATtiny2313

(RESET/dW)PA2

(RXD)PD0

(TXD)PD1

(XTAL2)PA1

(XTAL1)PA0

(CKOUT/XCK/INT0)PD2

(INT1)PD3

(OC0B/T1)PD5

(T0)PD4

GND

1

2

3

4

5

6

7

8

9

10

VCC

20

PB7(UCSK/SCK/PCINT7)

19

PB6(DO/PCINT6)

18

PB5(DI/SDA/PCINT5)

17

PB4(OC1B/PCINT4)

16

PB3(OC1A/PCINT3)

15

PB2(OC0A/PCINT2)

14

PB1(AIN1/PCINT1)

13

PB0(AIN0/PCINT0)

12

PD6(ICP)

11

2543A–AVR–0 8/ 0 3

Rev. 2543A– A VR –0 8/ 03

1

Page 2

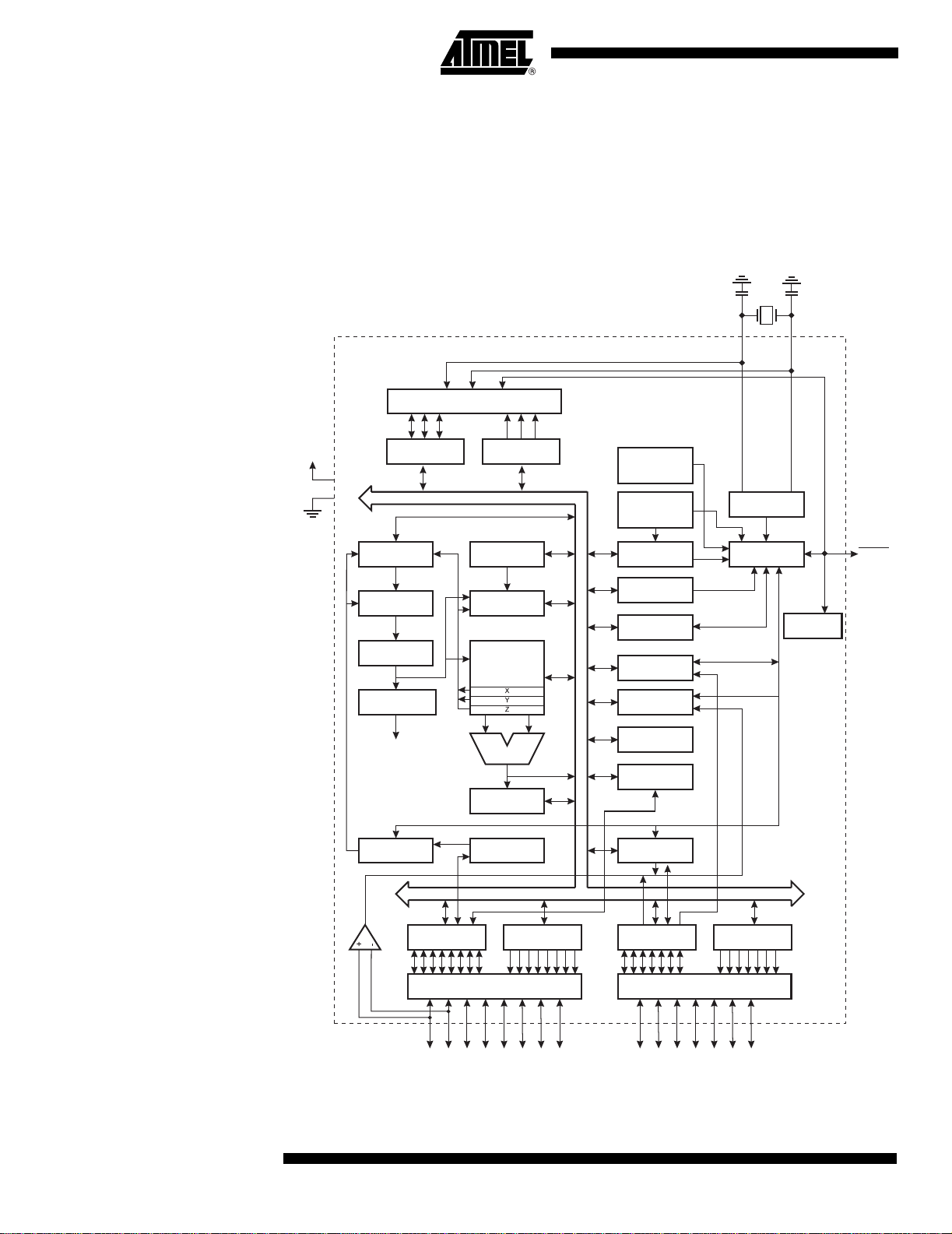

Overview The ATtiny2313 is a low-power CMOS 8-bit microcontroller based on the AVR

enhanced RISC architecture. By executing powerful instructions in a single clock cycle,

the ATtiny2313 achieves throughputs appr oaching 1 MIPS per MHz allowing the system

designer to optimize power consumption versus processing speed.

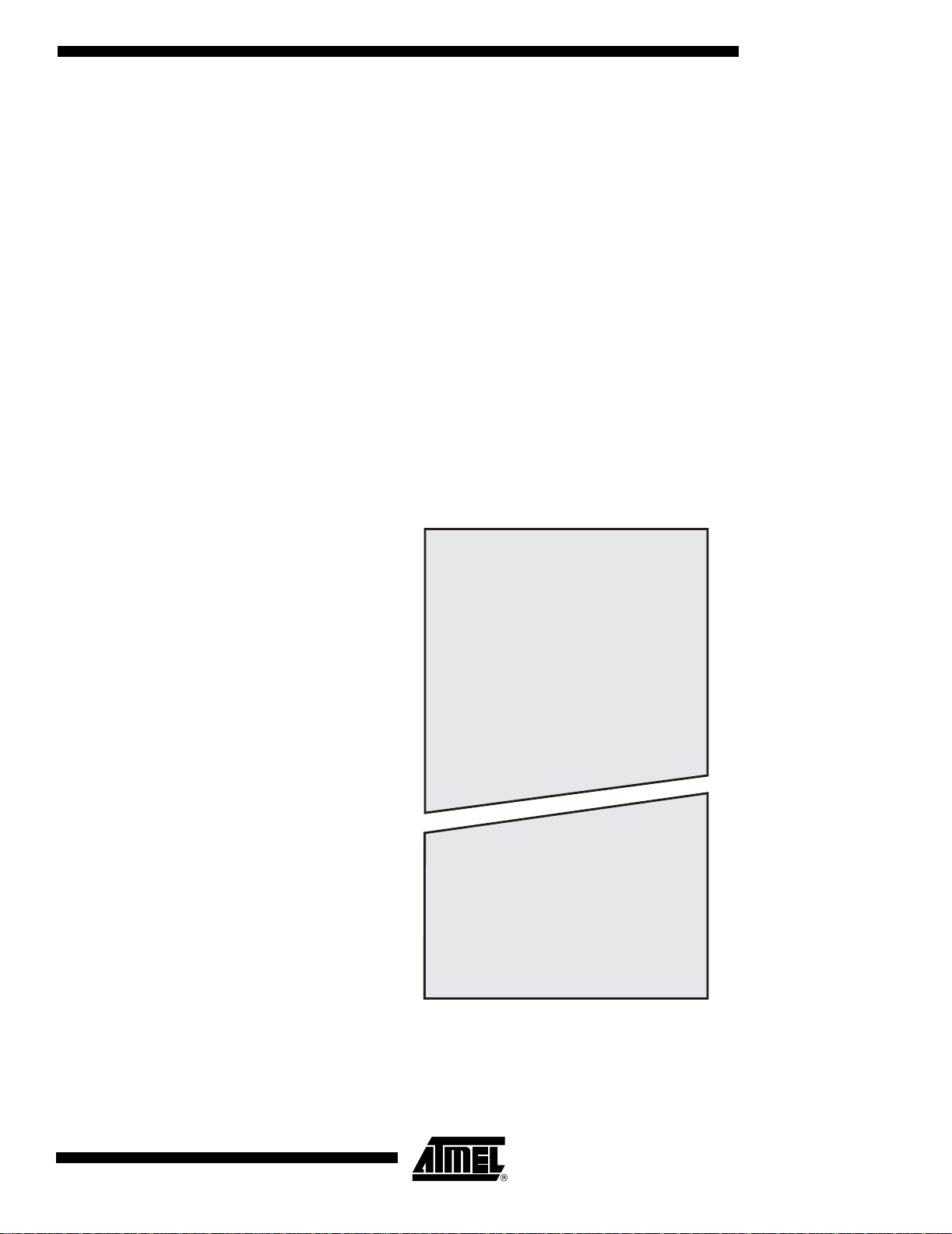

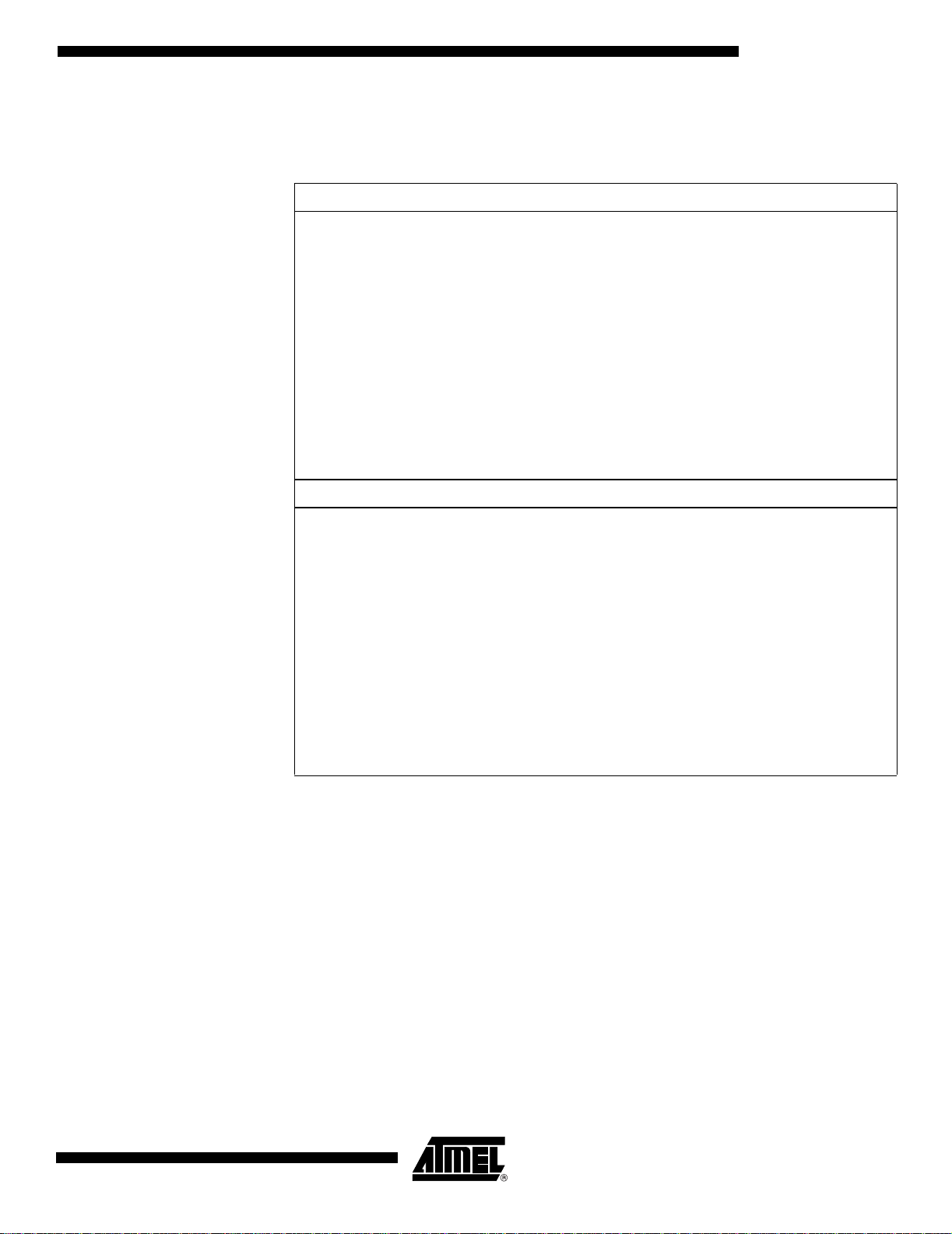

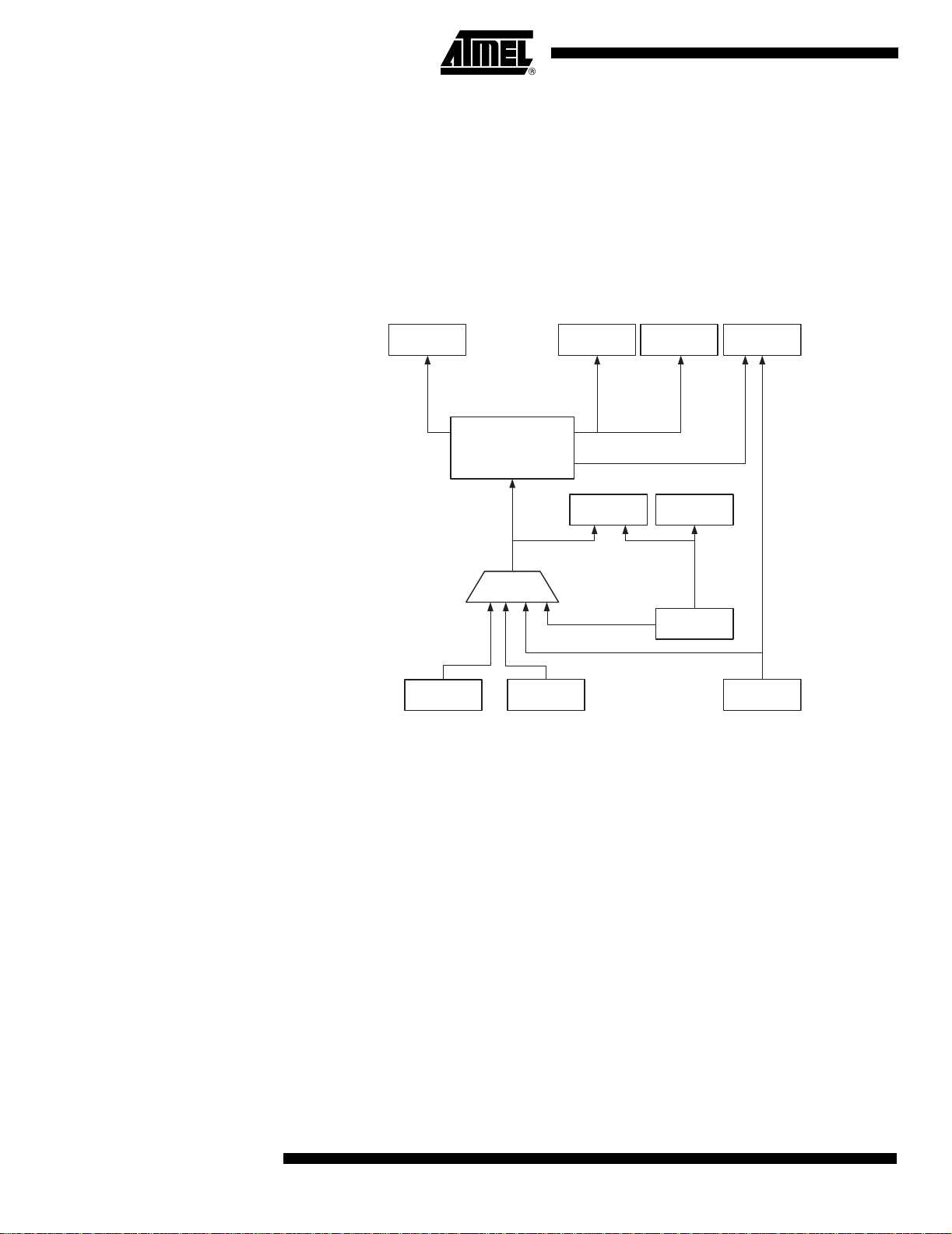

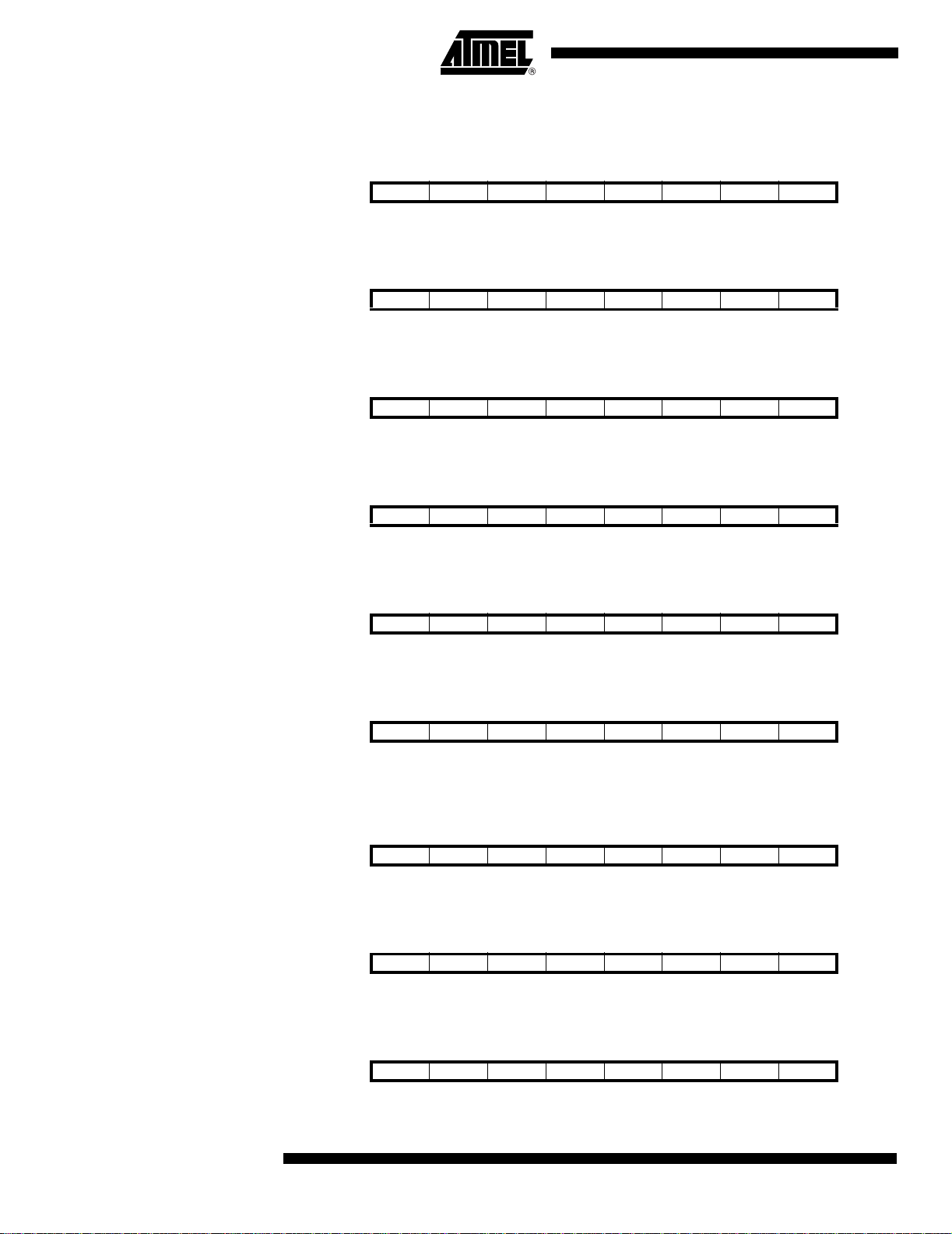

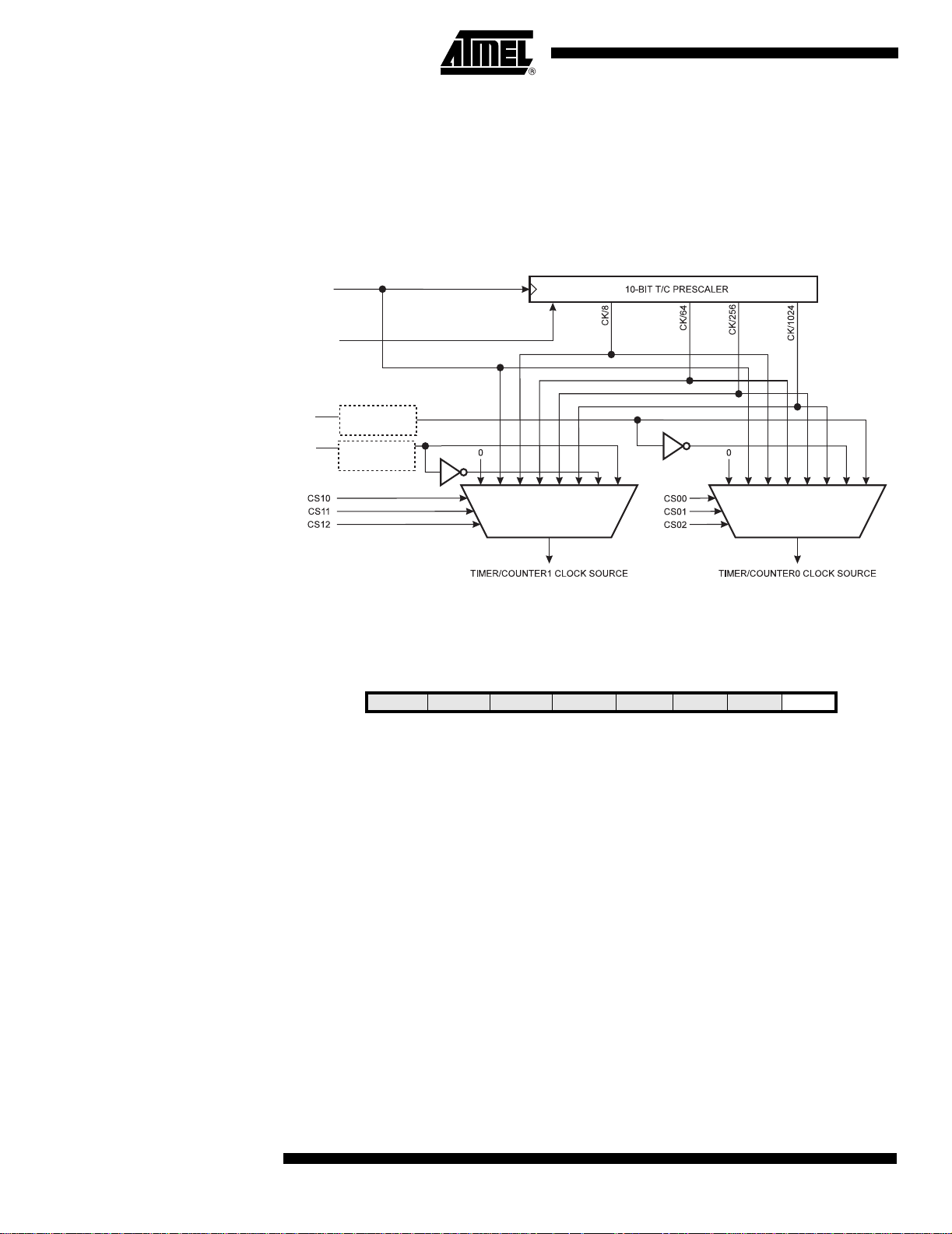

Block Diagram

Figure 2. Block Diagram

VCC

GND

DATA REGISTER

PORTA

PROGRAM

COUNTER

PROGRAM

FLASH

INSTRUCTION

REGISTER

INSTRUCTION

DECODER

CONTROL

LINES

PA0 - PA 2

PORTA DRIVERS

REG. PORTA

STACK

POINTER

SRAM

GENERAL

PURPOSE

REGISTER

ALU

STATUS

REGISTER

DATA DIR.

8-BIT DATA BUS

INTERNAL

CALIBRATED

OSCILLATOR

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

MCU CONTROL

REGISTER

MCU STATUS

REGISTER

TIMER/

COUNTERS

INTERRUPT

UNIT

EEPROM

USI

XTAL1

OSCILLATOR

TIMING AND

CONTROL

XTAL2

ON-CHIP

DEBUGGER

RESET

PROGRAMMING

LOGIC

DATA REGISTER

PORTB

ANALOG

COMPARATOR

2

ATtiny2313

SPI

REG. PORTB

PORTB DRIVERS

PB0 - PB7

DATA DIR.

USART

DATA REGISTER

PORTD

PORTD DRIVERS

PD0 - PD6

DATA DIR.

REG. PORTD

2543A–AVR–08/03

Page 3

ATtiny2313

The AVR core combines a ric h instr uctio n set wit h 32 general purpose worki ng regi sters .

All the 32 regi sters are dire ctly conn ected to the Arithm etic Logic U nit (A LU), all owing

two independent regist ers t o be acces sed i n one sing le inst ructi on execut ed in one clo ck

cycle. The resulting arc hitect ur e is more code eff icient whil e achievi ng throug hput s up to

ten times faster than conventional CISC microcontrollers.

The ATtiny2313 provides the fol lowing features: 2K bytes of In-System Programm able

Flash, 128 bytes EEPROM, 128 bytes SRAM, 18 general purpose I/O lines, 32 general

purpose wo rking re giste rs, a singl e-wire Inte rface f or O n-chip Debu ggi ng, two fle xible

Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, Universal Serial Int erface wi th Star t Condition Detector , a progra mmable

Watchdog Timer with internal Oscillator, and three sof tware sele ctable p ower savin g

modes. The Idle m ode stops the CPU whil e allowing the SRAM, Ti mer/Cou nters, and

interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt

or hardware reset. In Standby mode, the cryst al/resonator Oscillator is running while t he

rest of the devic e is sleeping . This allo ws very fast sta rt-up com bined with low-pow er

consumption.

The device is manufactured using Atmel’s high density non-volatile memory technology.

The On-chip ISP Flash allows the program memory to be reprogrammed In-System

through an SPI serial interface, or by a conventional non-volatile memory programmer.

By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATtiny2313 is a powerful microcontroller that provides a highly

flexible and cost effective solution to many embedded control applications.

The ATtiny2313 AVR is supported with a full suite of program and system development

tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits.

2543A–AVR–08/03

3

Page 4

Pin Descriptions

VCC Digital supply voltage. GND Ground. Port A (PA2..PA0) Port A is a 3-bit bi-directional I/O port with in ternal pull-up resistors (sel ected for each

bit). The Port A output buf fers have symmetrical drive char acteristics with both high sink

and source capability. As inputs, Por t A pins that are externally p ulled low w ill source

current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATtiny2313 as listed

on page 54.

Port B (PB7..PB0) Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port B output buf fers have symmetrical drive char acteristics with both high sink

and source capability. As inputs, Por t B pins that are externally p ulled low w ill source

current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATtiny2313 as listed

on page 54.

Port D (PD6..PD0) Port D is a 7-bit bi-direct ional I/O port w ith intern al pull-up resistor s (selected for each

bit). The Port D output buffers have symmetri cal drive character ist ics with both high sink

and source capability. As inputs, Port D pins that are externally pulled low will source

current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATtiny2313 as listed

on page 57.

RESET

XTAL1 Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL2 Output from the inverting Oscillator amplifier. XTAL2 is an alternate fun cti on for PA1.

About Code Examples

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table

15 on page 35. Shorter pulses are not guaranteed to generate a reset. The Reset Input

is an alternate function for PA2 and dW.

XTAL1 is an alternate function for PA0.

This documentation contai ns simpl e code examples that bri efly show how to use var ious

parts of the device. These cod e example s assume tha t the part speci fic header file is

included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please

confirm with the C compiler documentation for more details.

Disclaimer Typical values contained in this data sheet are based on simulations and characteriza-

tion of other AVR microcontrollers manufactured on the same process technology. Min

and Max values will be available after the device is characterized.

4

ATtiny2313

2543A–AVR–08/03

Page 5

ATtiny2313

AVR CPU Core

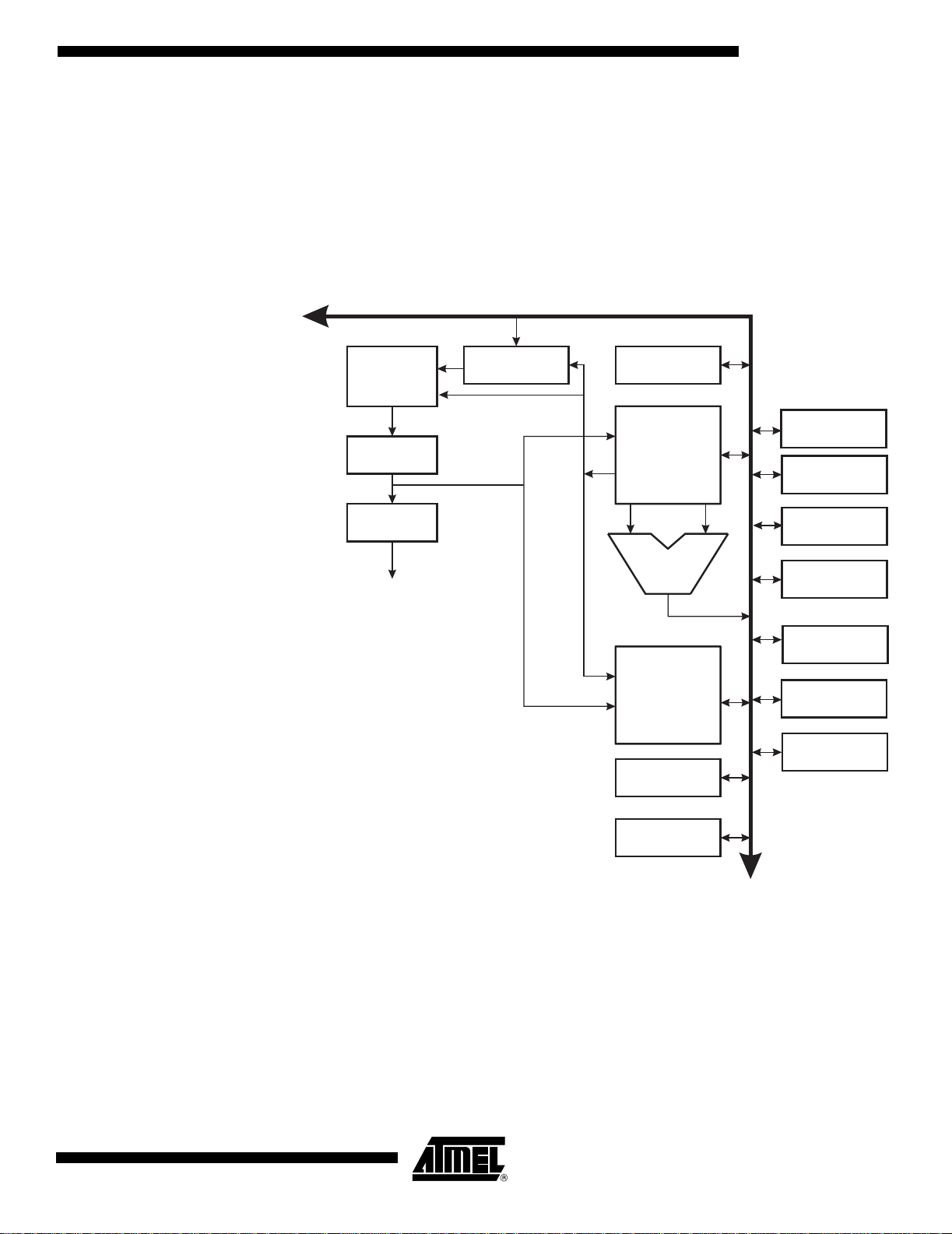

Introduction This section discusses the AV R core architecture in general. The main function of the

CPU core is to e nsu re corre ct program exec ution. The CP U mu st there fore b e abl e to

access memories, perform cal culations, control peripher als, and handle interrupts.

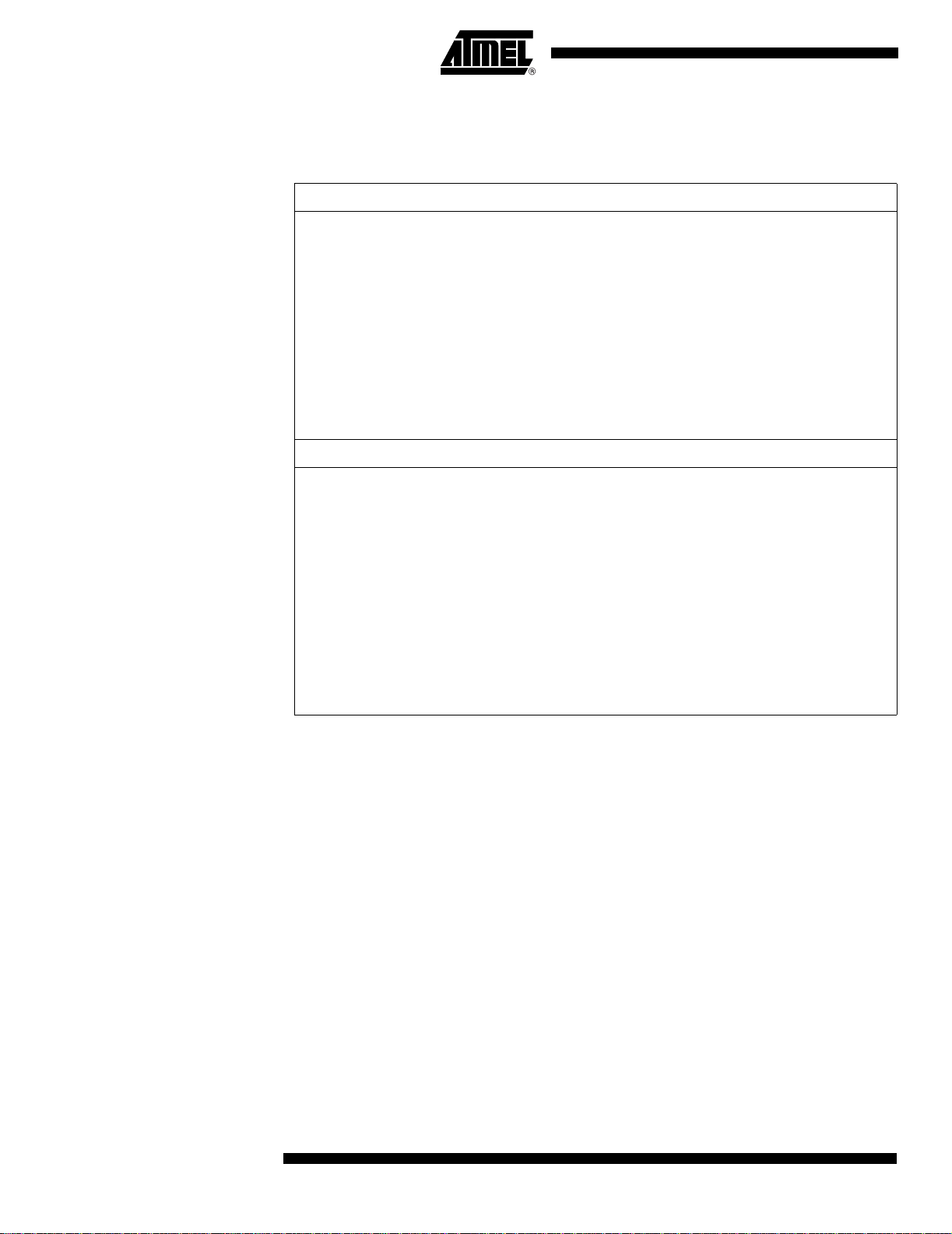

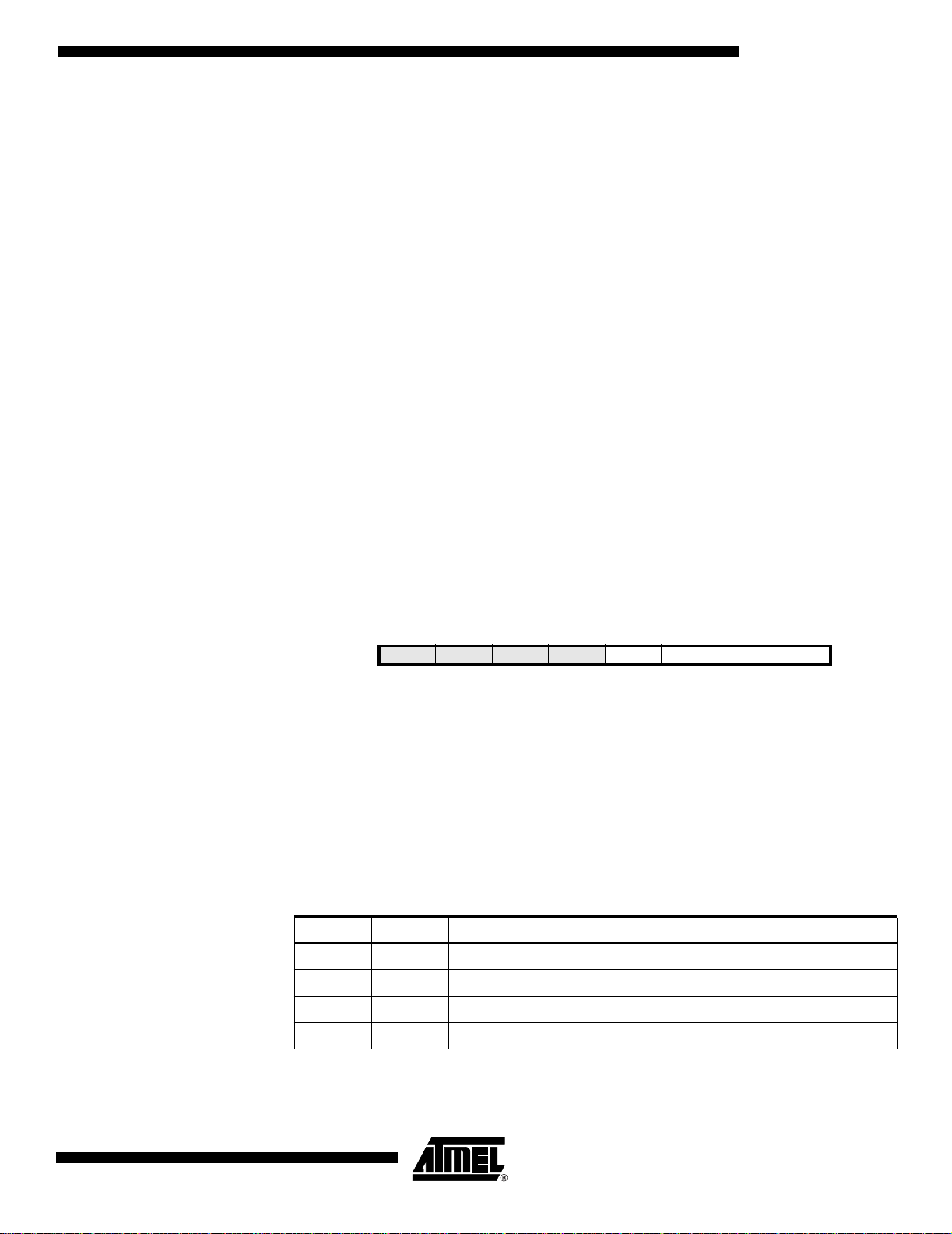

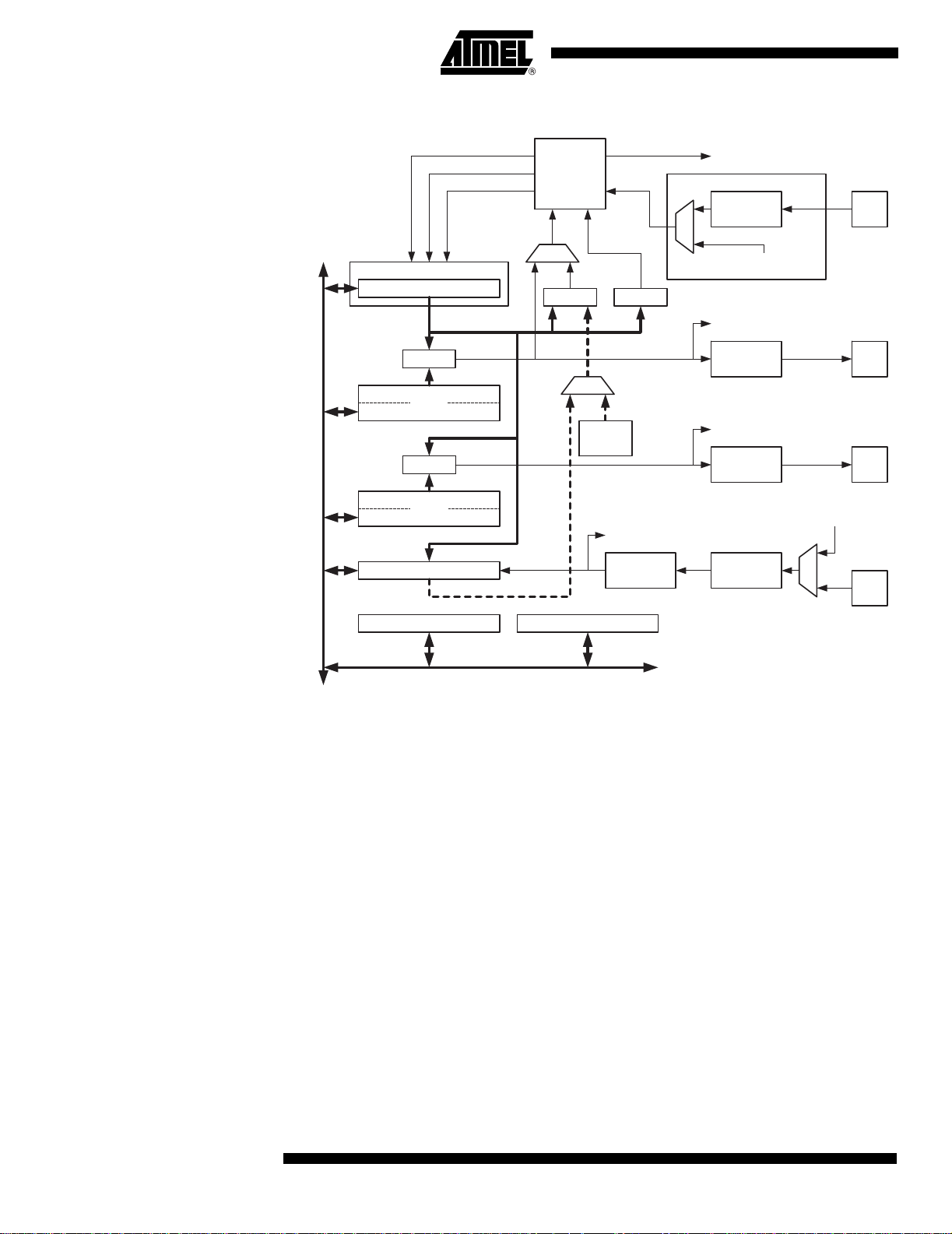

Architectual Overview Figure 3. Block Diagram of the AVR Architecture

Data Bus 8-bit

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Control Lines

Program

Counter

Direct Addressing

Status

and Control

32 x 8

General

Purpose

Registrers

ALU

Indirect Addressing

Data

SRAM

EEPROM

Interrupt

Unit

SPI

Unit

Watchdog

Timer

Analog

Comparator

I/O Module1

I/O Module 2

I/O Module n

2543A–AVR–08/03

I/O Lines

In order to maximize per formance and parallelism, the AVR uses a Harvard architecture

– with separate memories and buses for program and data. Instructions in the program

memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept

enables instructions to be executed in every clock cycle. The program memory is InSystem Reprogrammable Flash memory.

The fast-access Regist er File contains 32 x 8-bit general purpose working registers with

a single clock cycle a ccess time. This a llows single -cycle Arithmetic Logic Unit (ALU)

operation. In a typical AL U operation, two operands are out put from the Registe r File,

5

Page 6

the operation is executed, and the result is stored back in the Register File – in one

clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for

Data Space addressing – enabling efficient address calculations. One of the these

address pointers can also be used as an addres s pointer for look up ta bles in Flash program memory. These adde d function registers are the 1 6-bit X-, Y-, and Z-register,

described later in t his section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After

an arithmetic operation, the St atus Regist er is updat ed to reflect i nformation a bout the

result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions,

able to directly address the whole address space. Most AVR instructions have a single

16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

During interrupts and subroutine cal ls, the return address Program Counter (PC) is

stored on the Stack . Th e Stac k is effectiv ely al locat ed in t he general data SRAM , a nd

consequently the Stack size is only limited by the total SRAM size and the usage of the

SRAM. All user programs must initialize the SP in the Reset routine (bef ore subroutines

or interrupts are exe cuted). The S tack Pointer (SP ) is read/wri te accessible in the I/O

space. The data SRAM can easily be accessed through the five different addressing

modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

ALU – Arithmetic Logic Unit

A flexible inte rrupt modu le has its con trol regist ers in the I/O space with an additio nal

Global Interrupt Enabl e bit in the St atus Regis ter. All i nterr upts have a sep arat e Interrup t

Vector in the Interrupt Vector table. The interrupts have priority in accordance with their

Interrupt Vector pos ition. The lower the Interrupt Vect or address, the higher the priorit y.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control

Registers, and other I/O functions. The I/O Memory can be accessed directly, or as the

Data Space locations following thos e of the Regi ster File, 0x20 - 0x5F.

The high-performance AVR ALU operates in direct connection with all the 32 general

purpose worki ng register s. Withi n a single cl ock cycle, arithmet ic operat ions betw een

general purp ose regis ters or be tween a re giste r and an imme diate ar e ex ecuted . T he

ALU operations are divided i nto three main categories – ari thmet ic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier

supporting both signed/unsi gned m ultiplic ation and fractio nal format. See the “Ins truction Set” section for a detailed description.

6

ATtiny2313

2543A–AVR–08/03

Page 7

ATtiny2313

Status Register The Status Register contains information about the result of the most recently executed

arithmetic instruction. This information can be used for altering program flow in order to

perform conditi onal opera tions. Note that the Stat us Registe r is update d after all AL U

operations, as specified in the Instruction Set Reference. This will in many cases

remove the need for using the dedicated compare instructions, resulting in faster and

more compact code.

The Status Register is not a utomaticall y stored wh en ent ering an i nterrupt routine and

restored when returning from an interrupt. This must be handled by software.

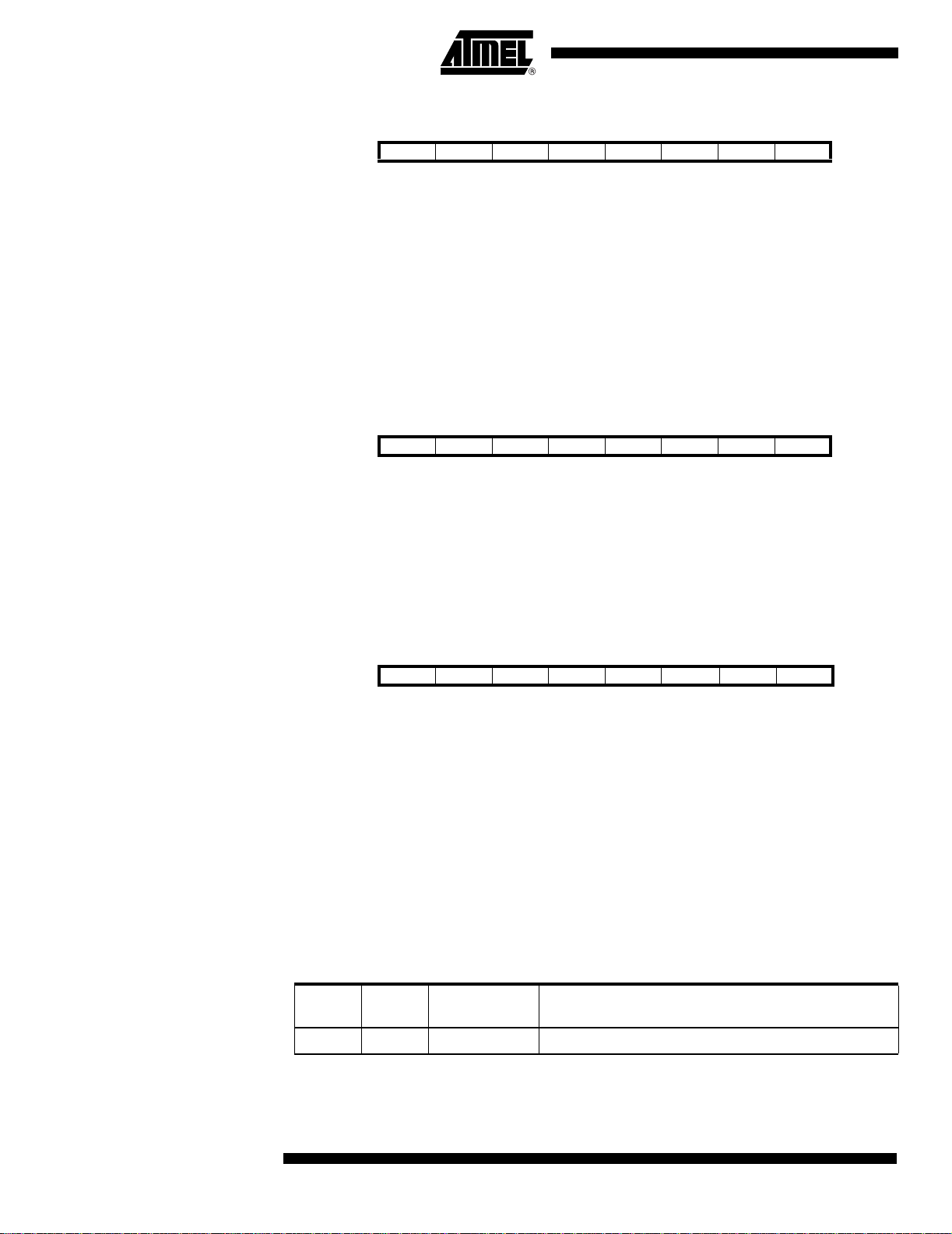

The AVR Status Register – SREG – is defined as:

Bit 76543210

I T H S V N Z C SREG

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bit 7 – I: Glob a l In te r ru p t En a b le

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global

Interrupt Enable Register is cleared, none of the interrupts are enabled independent of

the individual interrupt enable sett ings. The I-bit is cl eared by hardwar e after an in terrup t

has occurred, and is set by the RETI instruction to enable subsequent interrupts. The Ibit can also be set and cleared by the application with the SEI and CLI instructions, as

described in the instruction set reference.

• Bit 6 – T: Bit Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as sour ce or

destination for the operated bit. A bit from a register in the Reg ister File can be copied

into T by the BST instruction, and a bit i n T can be copied into a b it in a reg ister in the

Register File by the BLD instruct ion.

• Bit 5 – H: Half Car ry F la g

The Half Carry Flag H indicates a Half Carry in some arith metic opera tions. Half Carry Is

useful in BCD arithmetic. See the “Instru cti on Set Description” for detailed information.

• Bit 4 – S: Sign Bit, S = N

⊕ V

The S-bit is always an exclusive or between the negative flag N and the Two’s Complement Overflow Flag V. See the “Instruction Set Descr iption” for detailed information.

• Bit 3 – V: Two’s Complement Overflow Flag

The Two’s C omplem ent O verflow Fla g V s upports two’s compl eme nt a rithmet ics. S ee

the “Instruction Set Descr iption” for detailed information.

• Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See

the “Instruction Set Descr iption” for detailed information.

2543A–AVR–08/03

• Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result i n an arith metic or logic operation. S ee the

“Instruction Set Description” for detailed information.

7

Page 8

• Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information.

General Purpose Register File

The Register F ile is optim ized f or the A VR E nhanc ed RIS C in struction set. I n orde r to

achieve the required performance and flexibility, the following input/output schemes are

supported by the Register File:

• One 8-bit output operand and one 8-bit result input

• Two 8-bit output operands and one 8-bit result input

• Two 8-bit output operands and one 16-bit result input

• One 16-bit output operand and one 16-bit result input

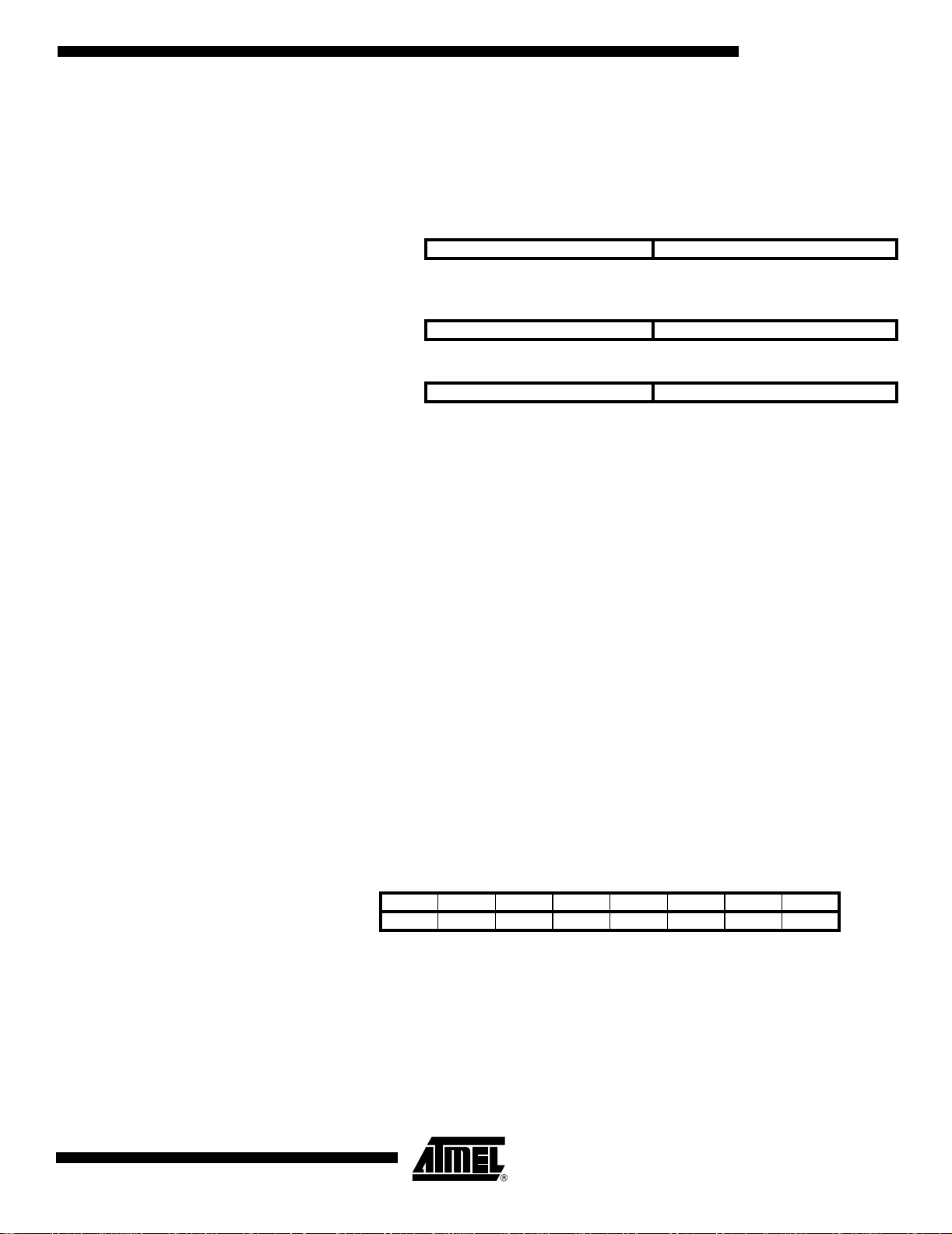

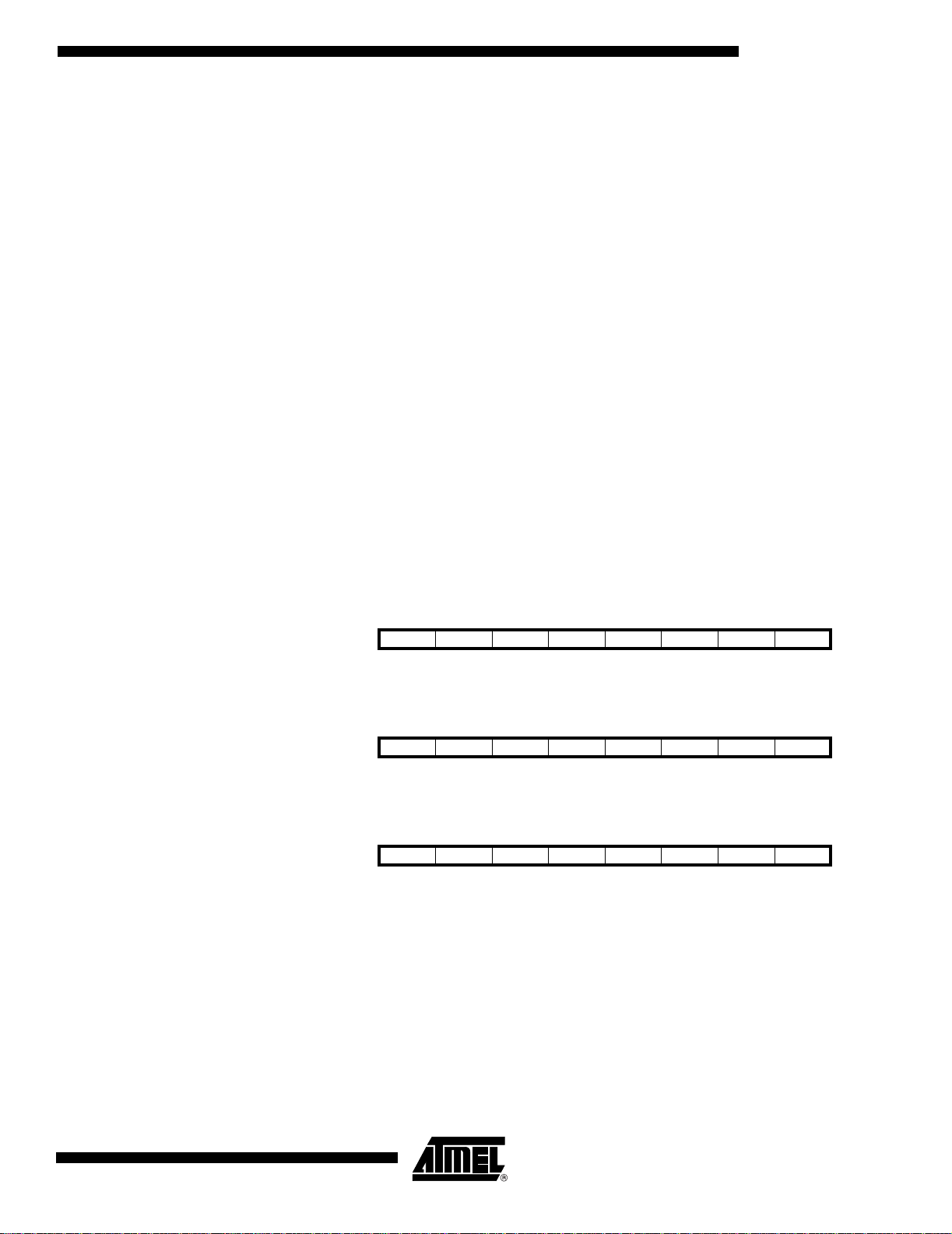

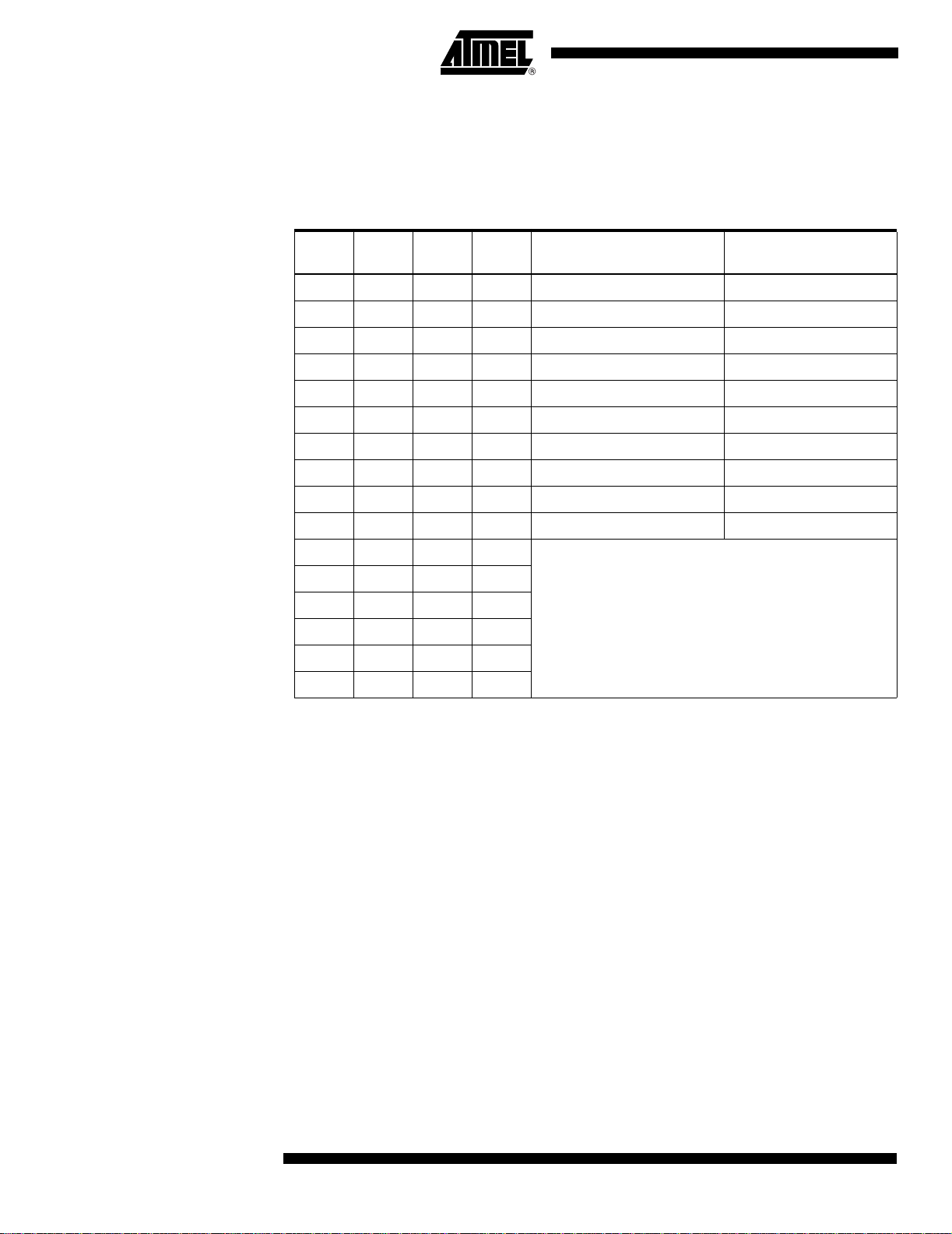

Figure 4 shows the structure of the 32 general purpose working registers in the CPU.

Figure 4. AVR CPU General Purpose Working Registers

70Addr.

R0 0x00

R1 0x01

R2 0x02

…

R13 0x0D

General R14 0x0E

Purpose R15 0x0F

Working R16 0x10

Registers R17 0x11

…

R26 0x1A X-register Low Byte

R27 0x1B X-register High Byte

R28 0x1C Y-register Low Byte

R29 0x1D Y-register High Byte

R30 0x1E Z-register Low Byte

R31 0x1F Z-register High Byte

Most of the instruction s operati ng on the Regist er File have di rec t access to al l regi sters ,

and most of them are single cycle instructions.

As shown in Figure 4, each register is also assigned a data memory address, mapping

them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, t his memory organizati on provides great

flexibility in acces s of the regi sters, as the X-, Y- and Z -pointe r registe rs can b e s et to

index any register in the file.

8

ATtiny2313

2543A–AVR–08/03

Page 9

ATtiny2313

The X-register, Y- regi ster, and Z-register

The registers R26..R31 have some added functions to their general purpose usage.

These registers are 16-bit address pointers for indirect addressing of the data space.

The three indirect address registers X, Y, and Z are defined as described in Figure 5.

Figure 5. The X-, Y-, and Z-registers

15 XH XL 0

X-register 7 0 7 0

R27 (0x1B) R26 (0x1A)

15 YH YL 0

Y-register 7 0 7 0

R29 (0x1D) R28 (0x1C)

15 ZH ZL 0

Z-register 7 0 7 0

R31 (0x1F) R30 (0x1E)

In the different addressi ng mode s these ad dress registe rs have f unctions as f ixed di splacement, autom atic increment, and aut omatic decreme nt (see the instruction set

reference for details).

Stack Pointer The Stack is mainly used for storing temp orary data, for storing l ocal variables and for

storing return addresses after interrupts and subroutine calls. The Stack Pointer Register always points to the top of the Stack. Note that the Stack is implemented as growing

from higher memory locati ons to lower mem ory locations. This implies that a Stack

PUSH command decreases the Stack Pointer.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Interrupt Stacks are located. This Stack space in the data SRAM must be defined by the

program before any subroutine calls are executed or interrupts are enabled. The Stack

Pointer must be set to point a bove 0x60. The Stack Poi nter is decremented by one

when data is pushed ont o the Stack with the PUSH instruction, and it is decremented by

two when the return address is pushed onto the Stack with subroutine call or interrupt.

The Stack Pointer is incremented by one when dat a is popped f rom the Stack with the

POP instruction, and it is incremented by two when data is popped from the Stack with

return from subroutine RET or return from interrupt RETI.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used i s implementation dependent. Note that the data space in some

implementations of the AVR architecture is so small that only SPL is needed. In this

case, the SPH Register will not be present.

Bit 1514131211109 8

––––––––SPH

SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 SPL

76543210

Read/WriteRRRRRRRR

R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

00000000

2543A–AVR–08/03

9

Page 10

Instruction Execution Timing

This section describes the gener al access timing conc epts for i nstruct ion execut ion. The

AVR CPU is driven by the CPU clock clk

, directly generated from the selected clock

CPU

source for the chip. No internal clock division is used.

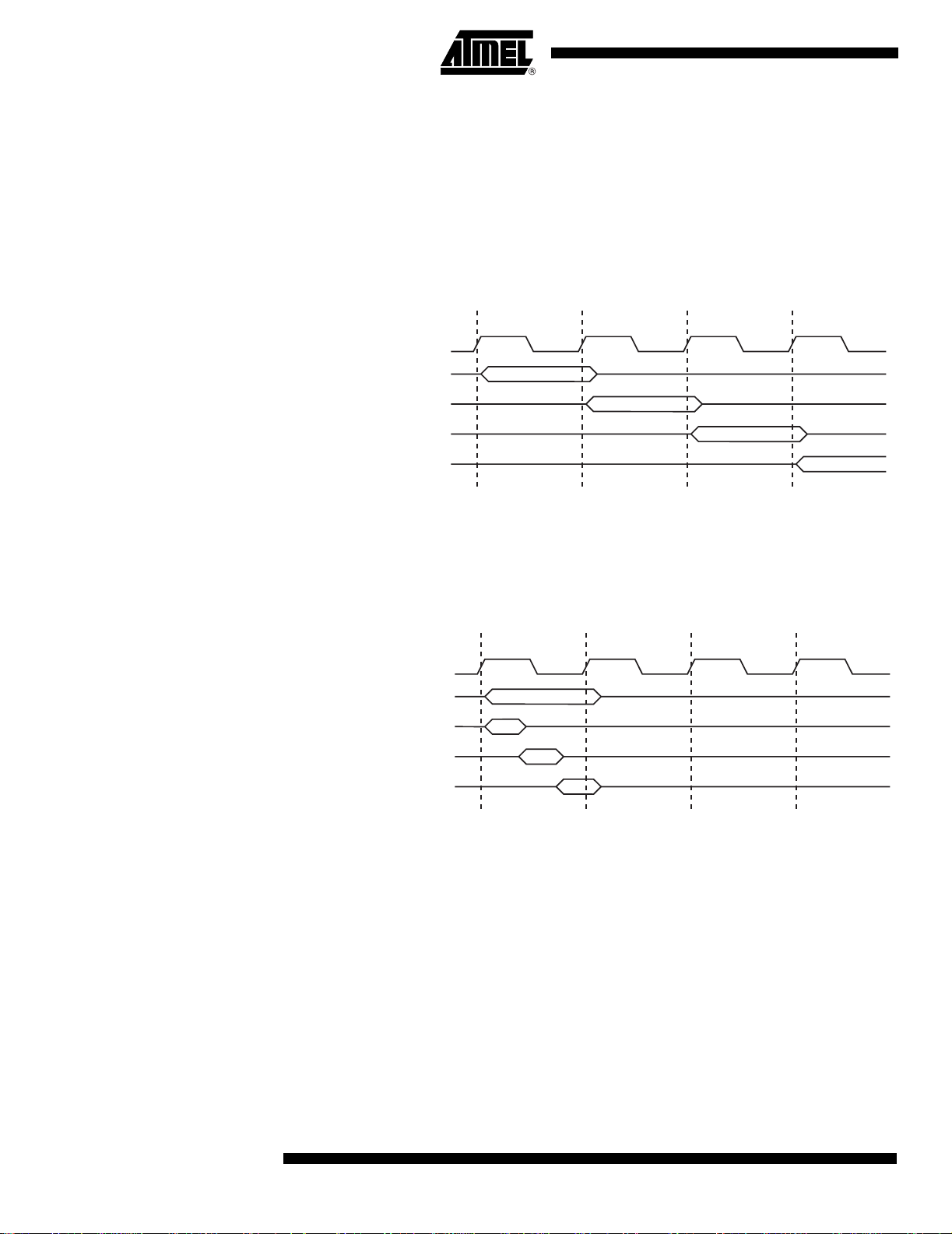

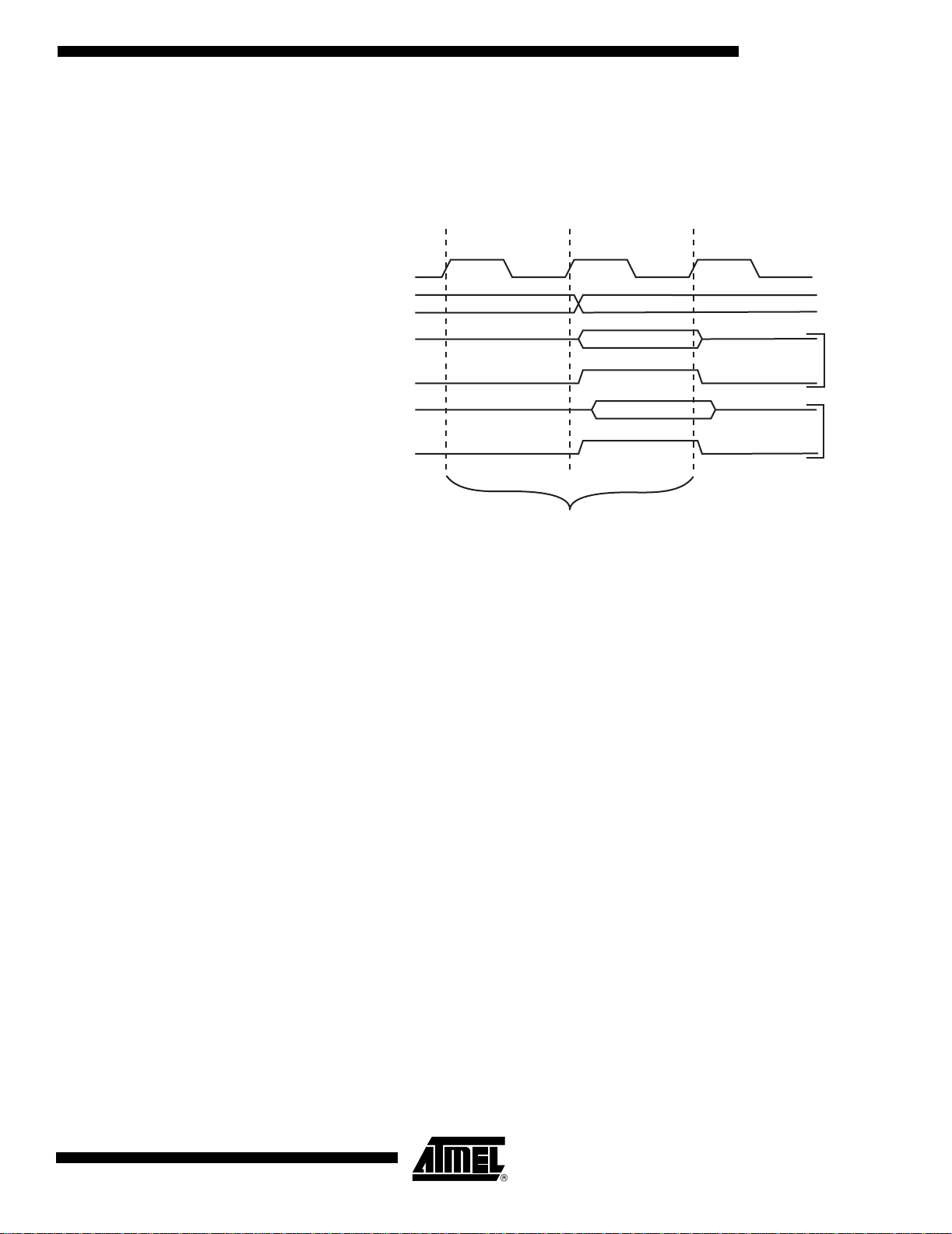

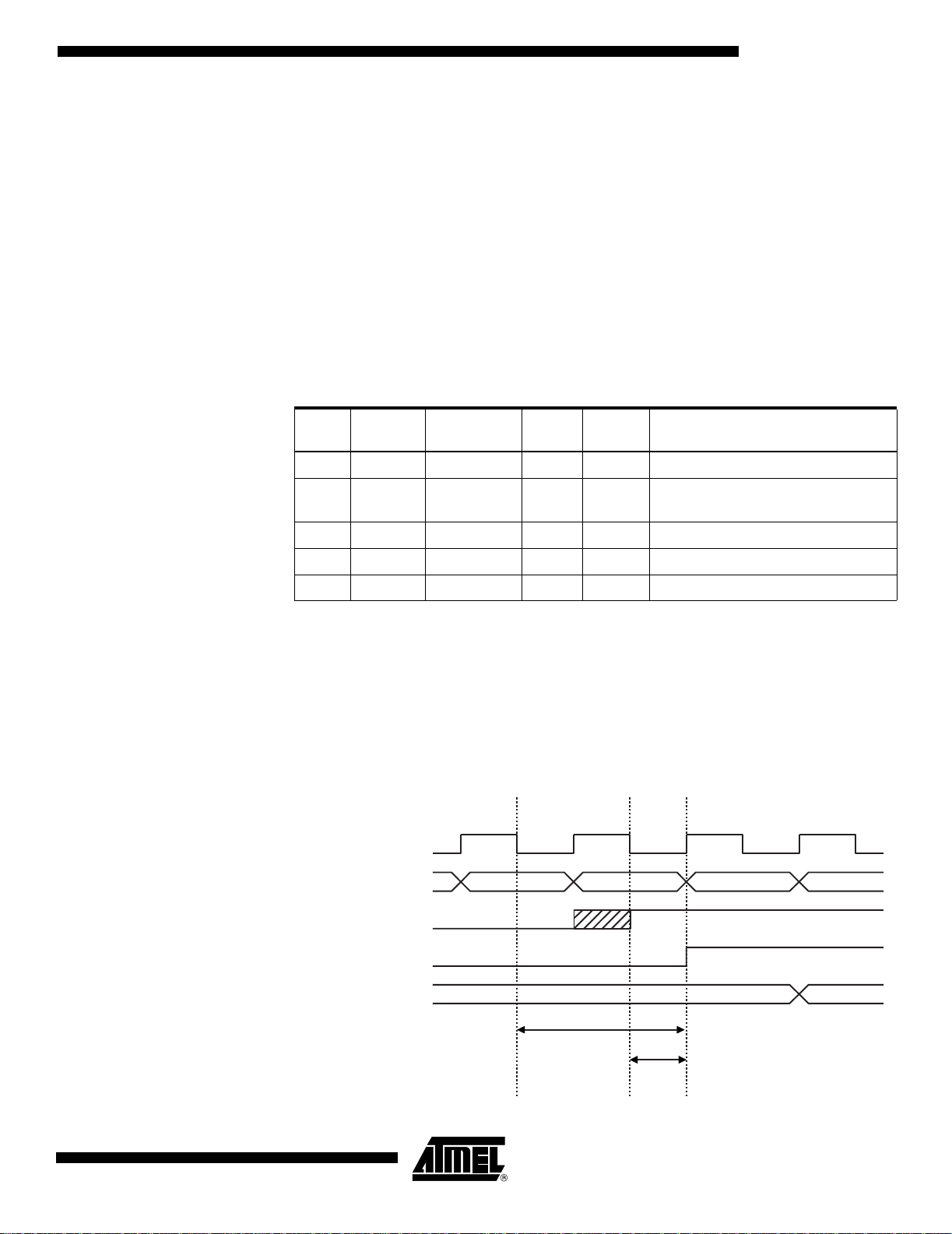

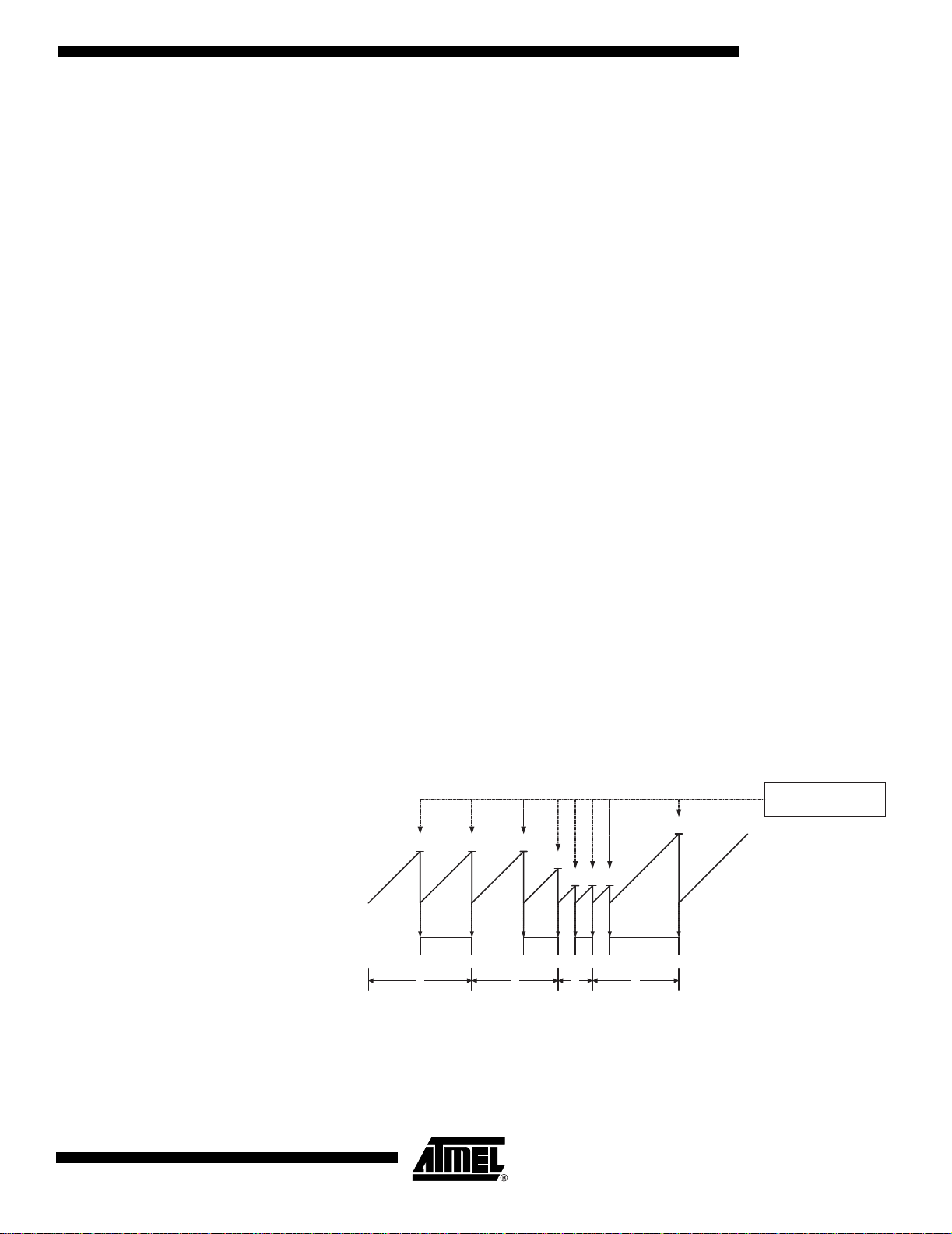

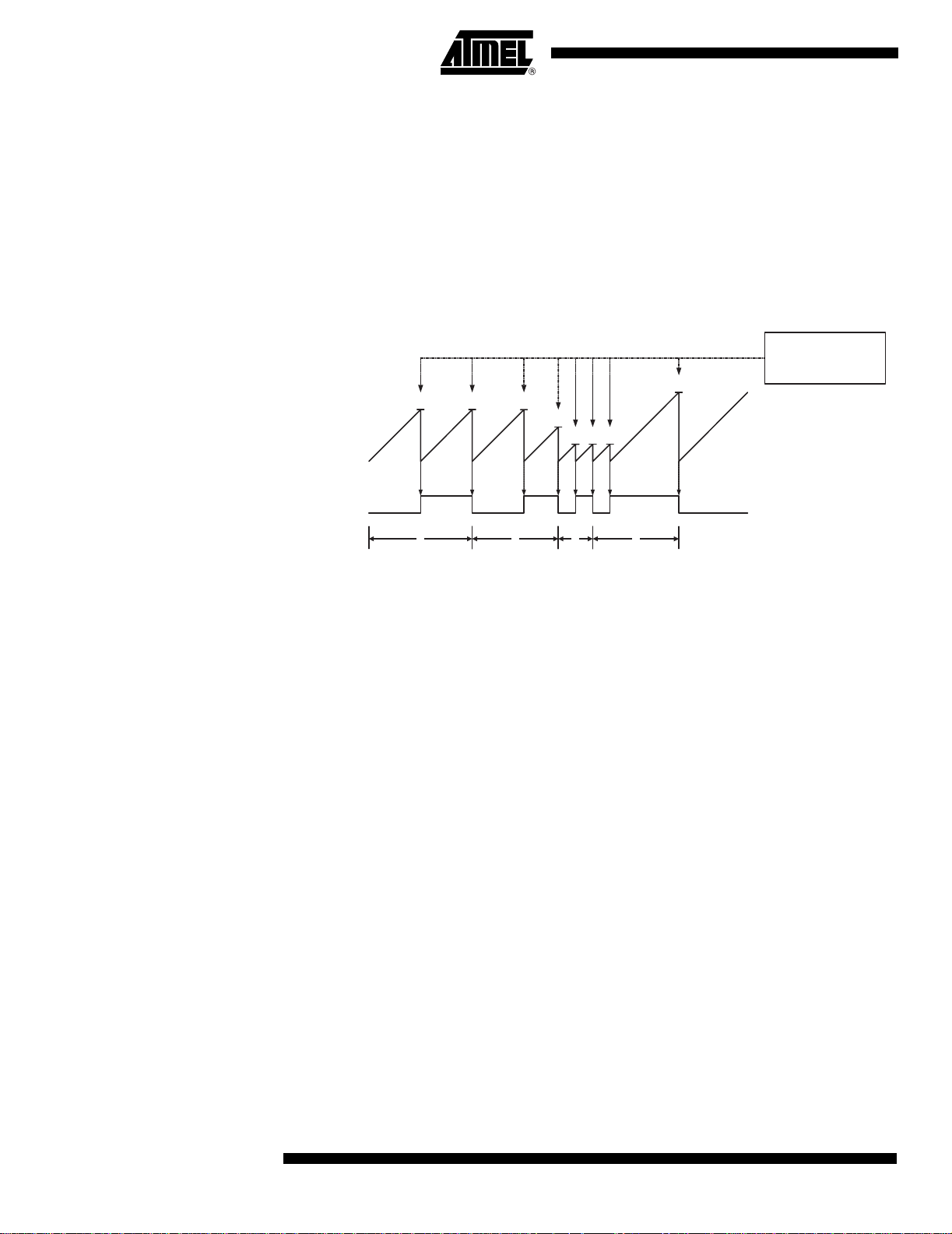

Figure 6 shows the parallel instructi on fetches and instruc tion exec utions enab led by the

Harvard architecture and the fast-access Register Fil e concept. This is the basic pipelining concept t o obtain up t o 1 M IPS p er MH z with t he co rrespondin g u nique res ults for

functions per cost, functions per clocks, and functions per power-unit.

Figure 6. The Parallel Instruc ti on Fetches and Instruction Executions

T1 T2 T3 T4

clk

CPU

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

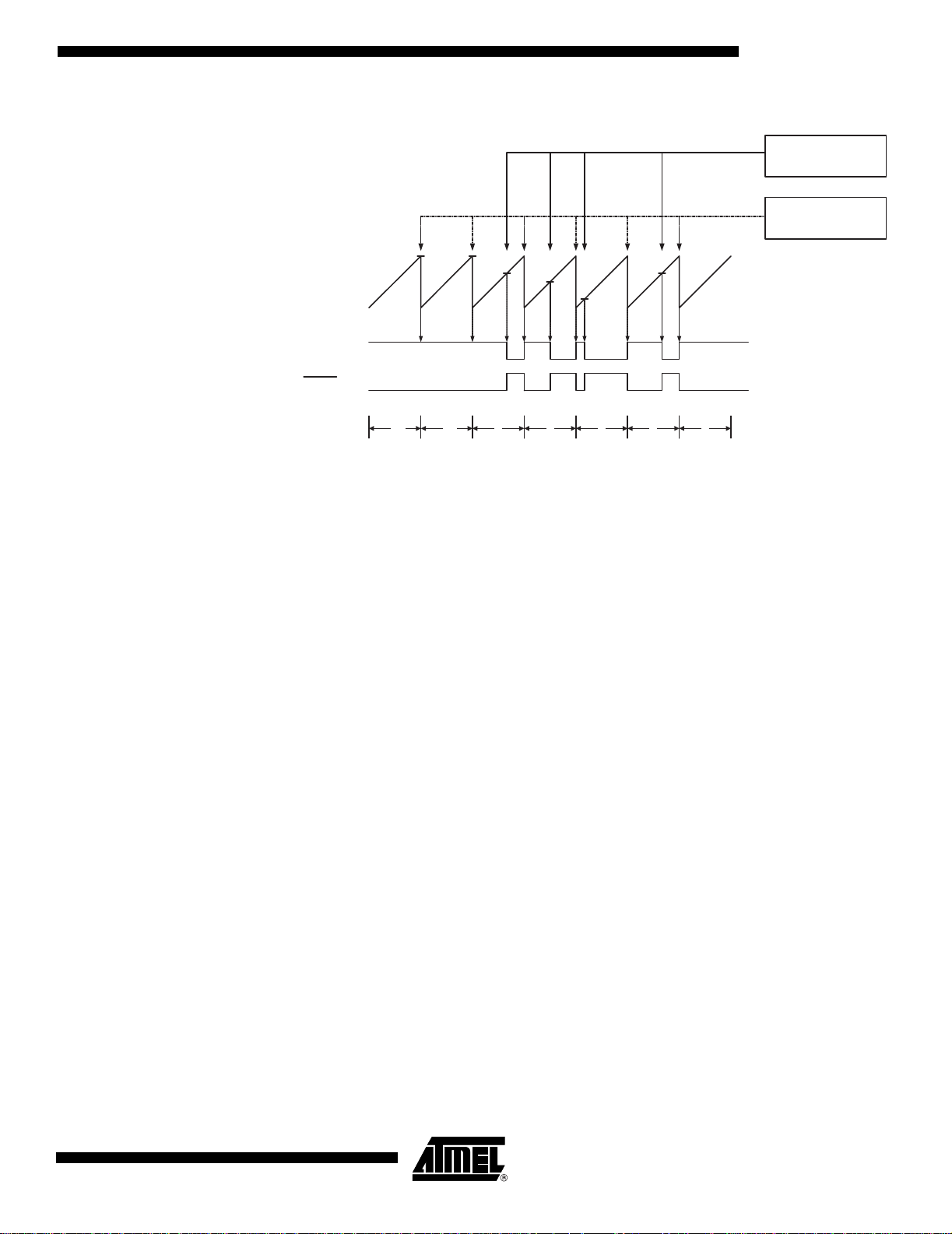

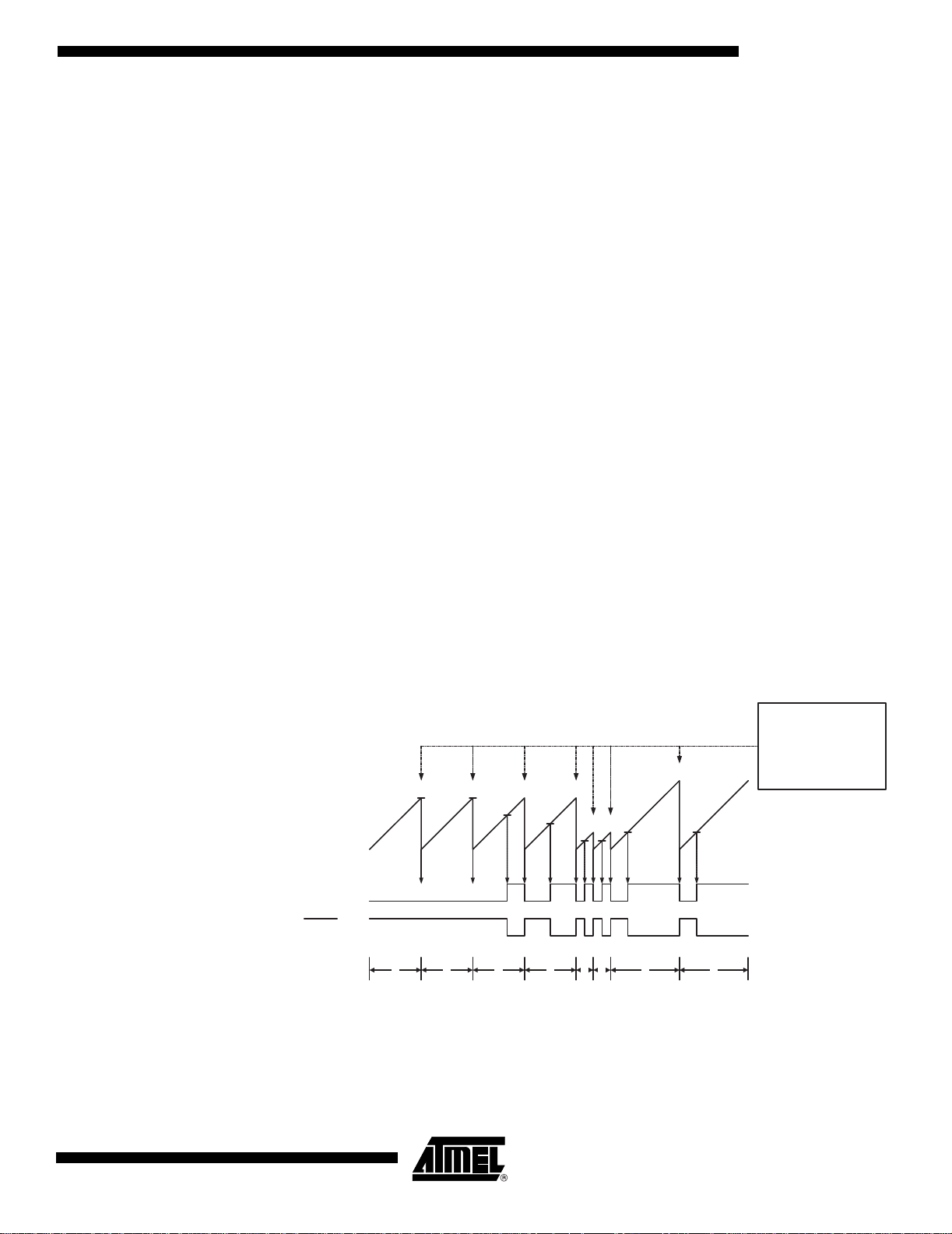

Figure 7 shows the internal timing concept for the Register File. In a single clock cycle

an ALU operation using two register operands is executed, and the result is stored back

to the destination regis ter.

Reset and Interrupt Handling

Figure 7. Single Cycle ALU Operation

T1 T2 T3 T4

clk

CPU

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

The AVR provides several different interrupt sources. These interrupts and the separate

Reset Vector each have a separate program vector in t he program memo ry space. Al l

interrupts are assigned indi vidual en able bits w hich must b e wr itten logic one together

with the Global Interrupt Enable bit in t he Status Register in order to enable the interrupt .

The lowest addresses in the p rogram memory spa ce are by def ault def ined as t he Rese t

and Interrupt Vectors. The complete list of vectors is shown in “Interrupts” on page 45.

The list also determines the priori ty levels of the different interrupts. The lower the

address the higher is the priority level. RESET has the highest priority, and next is INT0

– the External Inte rrupt Request 0. Ref er to “ Inter rupts” on page 45 for more i nformat ion .

When an interrupt occurs, the Global In terrupt Enab le I-bit is cleared and al l interrupts

are disabled. The user softw are ca n wri te logi c on e to the I-bit t o en able n este d int errupts. All enabled interrupts can then i nterrupt the current interrupt routine. The I-bit is

automatically set when a Return from Interrupt instruction – RETI – is executed.

10

ATtiny2313

2543A–AVR–08/03

Page 11

ATtiny2313

There are basicall y two types of inter rupts. The first type is triggered by an event that

sets the interrupt flag. For these interrupts, the P rogram Counter i s vectored to the

actual Interrupt Vector in order to execute the interrupt handling routine, and hardware

clears the corresponding interrupt flag. Interrupt flags can also be cleared by writing a

logic one to the flag bi t posi tion( s) to be c leared. If an i nterr upt condi tion oc curs whil e the

corresponding interru pt ena ble bit is cleared , the inte rrupt flag w ill be set an d rem embered until the interrupt is enabled, or the flag is cleared by software. Similarly, if one or

more interrupt conditions occur while the Global Interrupt Enable bit is cleared, the corresponding interrupt flag(s) will be set and remembered until th e Global Interrupt Enable

bit is set, and will then be executed by order of pri ority.

The second type of interrupts will trigger as long as the interrupt condition is present.

These interrupts do not necessarily have interrupt flags. If the interrupt condition disappears before the interrupt is enabled, the interrupt will not be tri ggered.

When the AVR exits from an interrupt, it will always return to the main pr ogram and execute one more instruction before any pending interrupt is served.

Note that the Status Register is not automatically stored when entering an interrupt routine, nor restored when returning from an interrupt routine. This must be handled by

software.

When using the CLI instruction to disable interrupts, the interrupts will be immediately

disabled. No interrupt wil l be executed after the CLI instruction, even if it occ urs simultaneously with the CLI instruction. The following example shows how this can be used to

avoid interrupts during the timed EEPROM write sequence..

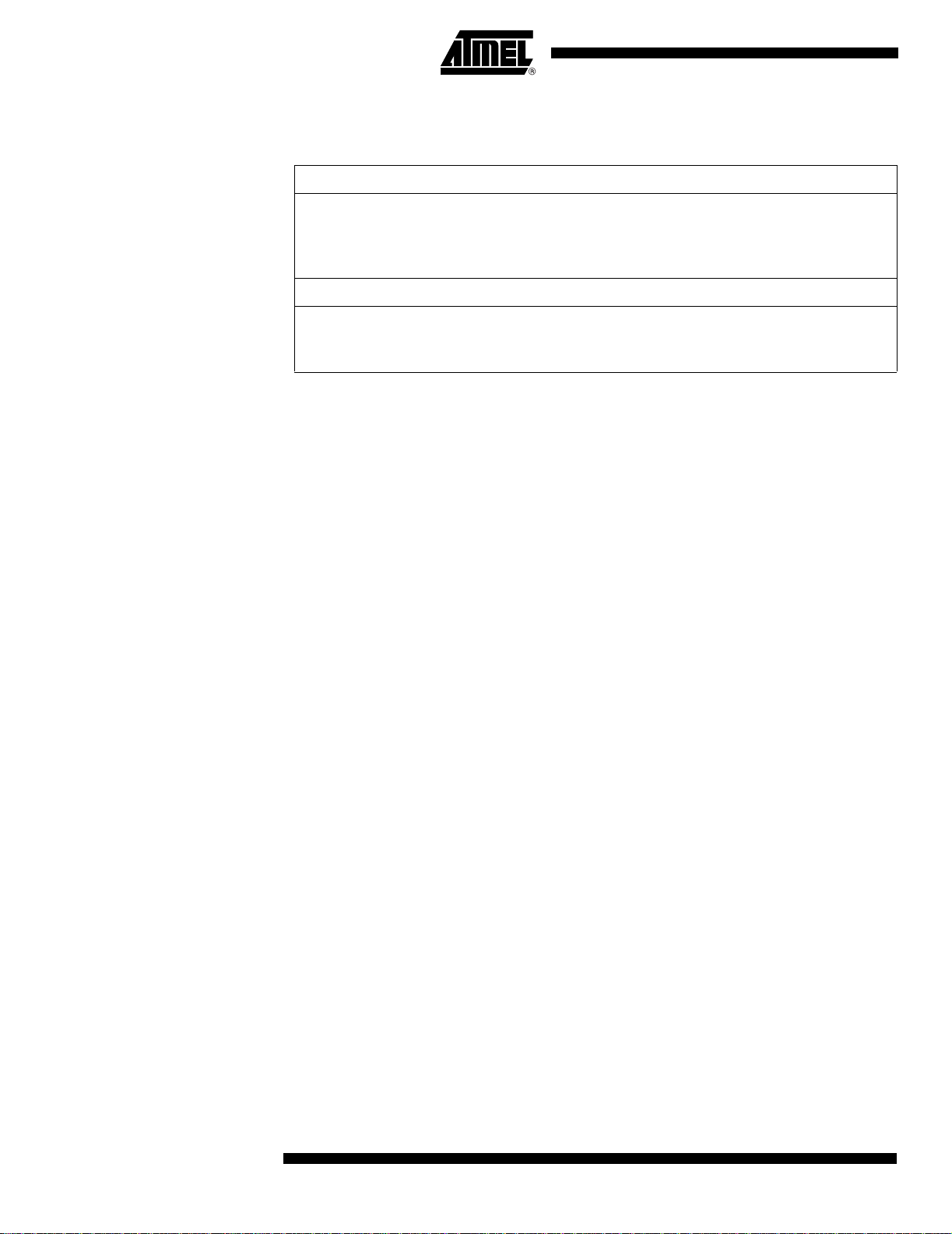

Assembly Code Example

in r16, SREG ; store SREG value

cli ; disable interrupts during timed sequence

sbi EECR, EEMWE ; start EEPROM write

sbi EECR, EEWE

out SREG, r16 ; restore SREG value (I-bit)

C Code Example

char cSREG;

cSREG = SREG; /* store SREG value */

/* disable interrupts during timed sequence */

_CLI();

EECR |= (1<<EEMWE); /* start EEPROM write */

EECR |= (1<<EEWE);

SREG = cSREG; /* restore SREG value (I-bit) */

2543A–AVR–08/03

11

Page 12

When using the SEI instruction to enable interrupts, the instruction following SEI will be

executed before any pending inter rupt s, as shown in this example.

Assembly Code Example

sei ; set Global Interrupt Enable

sleep ; enter sleep, waiting for interrupt

; note: will enter sleep before any pending

; interrupt(s)

C Code Example

_SEI(); /* set Global Interrupt Enable */

_SLEEP(); /* enter sleep, waiting for interrupt */

/* note: will enter sleep before any pending interrupt(s) */

Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles

minimum. After four clock cycles the program vector address for the actual interrupt

handling routine is executed. During this four clock cycle period, the Program Counter is

pushed onto the Stack. The vect or i s normall y a jum p to t he int errupt routin e, and thi s

jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle

instruction, this instruction is completed before the interrupt is served. If an interrupt

occurs when the MCU is in sleep mode, the interrupt execution response time is

increased by four clock cycles. This increase comes in additio n to the st art-up time from

the selected sleep mode.

A return from an interrupt handling routine takes four clock cycles. During these four

clock cycles, t he Program Counter (two bytes) is popped back from the St ack, the Stack

Pointer is incremented by two, and the I-bit in SREG is set.

12

ATtiny2313

2543A–AVR–08/03

Page 13

ATtiny2313

F

AVR ATtiny2313 Memories

In-System Reprogrammable Flash Program Memory

This section describes the different memories in the ATtiny2313. The AVR architecture

has two main memory spaces, the Data Memory and the Program Memory space. In

addition, the ATtiny2313 features an EEPROM Memory for data storage. All three memory spaces are linear and regular.

The ATtiny2313 contains 2K bytes On-chip In-System Reprogrammable Flash memory

for program storage. Since all AVR instr uctions are 16 or 32 bi ts wide, the Flash is organized as 1K x 16.

The Flash me mory has an endurance of at least 10 ,000 write/erase cycles. The

ATtiny2313 Program Counter (PC) is 10 bits wide, thus addressing the 1K program

memory locations. “Memory Programming” on page 160 contains a detailed description

on Flash data serial downloading using the SPI pins.

Constant tables can be allocated within the entire program memory address space (see

the LPM – Load Program Memory instruction description) .

Timing diagrams for instruction fetch and execution are presented in “Instruction Execution Timing” on page 10.

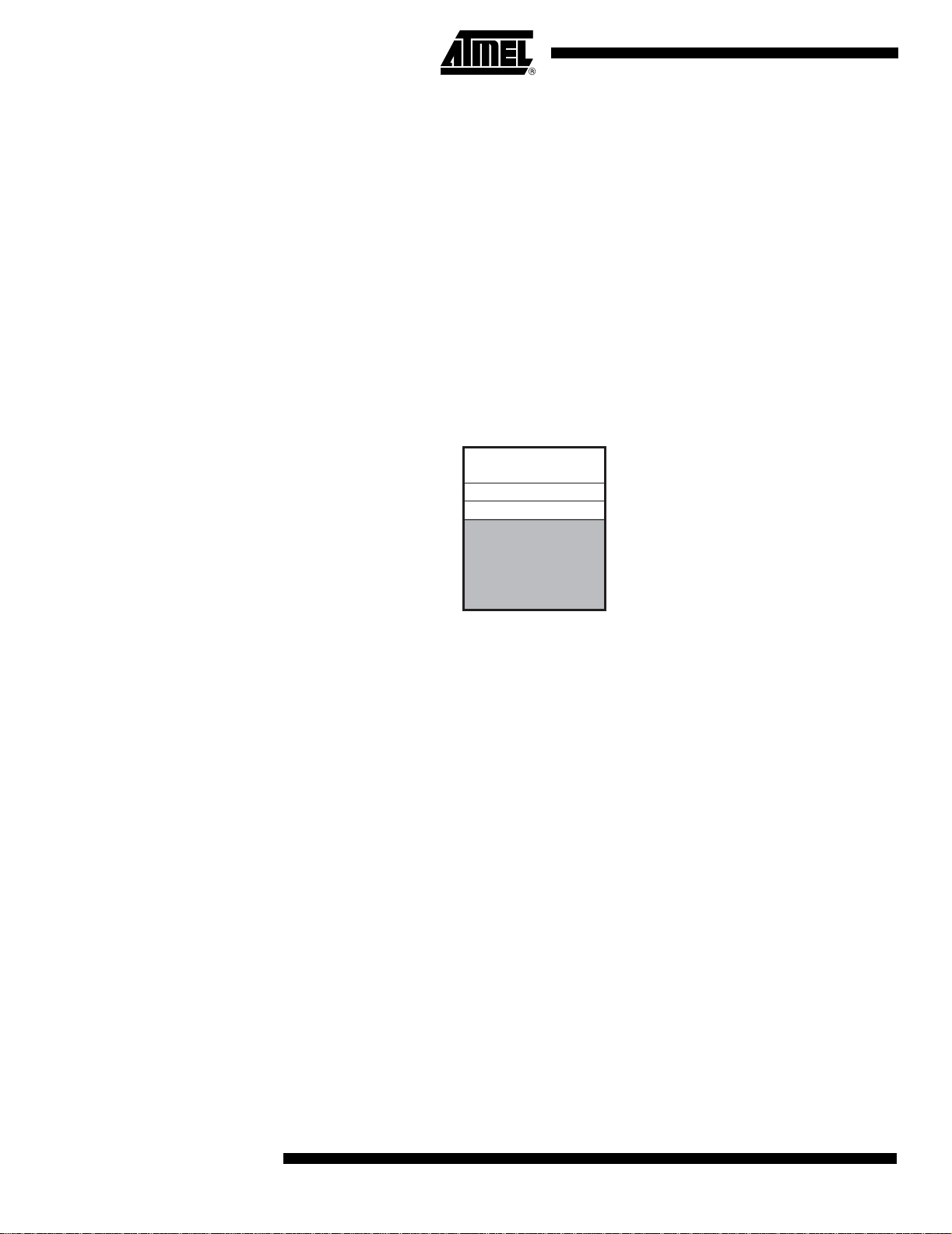

Figure 8. Program Memory Map

Program Memory

0x0000

0x03F

SRAM Data Memory Figure 9 shows how the ATtiny2313 SRAM Memory is organized.

The lower 224 data memory locations address bot h the Regi ster File, the I/O mem ory,

Extended I/O memo ry, and the internal data SR AM. The first 32 locations address the

2543A–AVR–08/03

13

Page 14

Register File, the next 64 location the standard I/O memory, and the next 128 locations

address the internal data SRAM.

The five dif ferent addressing modes for the data memory cover: Direct, Indire ct with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In

the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing rea ches the entire data space.

The Indirect with Displacement mode reaches 63 address locations from the base

address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-

increment, the address regis ter s X, Y, and Z are decremented or incremented.

The 32 general purpose working registers, 64 I/O Registers, and the 128 bytes of inter-

nal data SRAM in the ATtiny2313 are all accessible through all these addressing

modes. The Register File is described in “General Purpose Register File” on page 8.

Figure 9. Data Memory Map

Data Memory

32 Registers

64 I/O Registers

Internal SRAM

(128 x 8)

0x0000 - 0x001F

0x0020 - 0x005F

0x0060

0x00DF

14

ATtiny2313

2543A–AVR–08/03

Page 15

ATtiny2313

Data Memory Access Times This section describes the general access timing concepts for internal memory access.

The internal data SRAM access is performed in two clk

10.

Figure 10. On-chip Data SRAM Access Cycles

T1 T2 T3

clk

CPU

Address

Compute Address

Address valid

Data

cycles as described in Figure

CPU

WR

Write

Data

RD

Memory Access Instruction

Next Instruction

Read

EEPROM Data Memory The ATtiny2313 contains 128 bytes of data EEPROM memory. It is organized as a sep-

arate data space, in which single bytes can be read and written. The EEPROM has an

enduranc e of at lea st 100, 000 write /erase cycle s. The acc ess be tween th e EEPR OM

and the CPU is described in the following, specifying the EEPROM Address Registers,

the EEPROM Data Register, and the EEPROM Control Register. For a detailed description of Serial data downloading to the EEPROM, see page 173.

EEPROM Read/Write Access The EEPROM Access Registers are accessible in the I/O space.

The write access time for the EEPROM is given in Table 1. A self-timing function, however, lets the us er softw are detec t wh en the n ext b yte can be written. If the u ser code

contains instructions that write the EEPROM, some precautions must be taken. In

heavily filtered power suppl ies, V

causes the device for some period of time to run at a voltage lower than specified as

minimum for the clock frequency used. See “Preventing EEPROM Corruption” on page

20. for details on how to avoid problems in these situations.

is likely to rise or fall slowly on power-up/down. This

CC

2543A–AVR–08/03

In order to prevent unintenti onal EEPROM writes, a specific wr ite pro cedure must be f ollowed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is read, the CPU i s halted for four clock cycles before the next

instruction is execut ed. Wh en the E EPRO M is w ritten, the CPU is h alted fo r two cl ock

cycles before the next instr u ction is executed.

15

Page 16

The EEPROM Address Register

Bit 76543210

– EEAR6 EEAR5 EEAR4 EEAR3 EEAR2 EEAR1 EEAR0 EEAR

Read/Write R R/W R/W R/W R/W R/W R/W R/W

Initial Value 0 X X X X X X X

• Bit 7 – Res: Reserved Bit

This bit is reserved in the ATtiny2313 and will always read as zero.

• Bits 6..0 – EEAR6..0: EEPROM Address

The EEPROM Address Register – EEAR specify the EEPROM address in the 128 bytes

EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 127.

The initial value of EEAR is undefined. A proper value must be written before the

EEPROM may be accessed.

The EEPROM Data Register – EEDR

The EEPROM Control Register – EECR

Bit 76543210

MSB LSB EEDR

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bits 7..0 – EEDR7..0: EEPROM Data

For the EEPROM write operation, the EEDR Register contains the data to be written to

the EEPROM in the address given by the EEAR Register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by

EEAR.

Bit 76543210

– – EEPM1 EEPM0 EERIE EEMPE EEPE EERE EECR

Read/Write R R R/W R/W R/W R/W R/W R/W

Initial Value 0 0 X X 0 0 X 0

• Bits 7..6 – Res: Reserved Bits

These bits are reserved bits in t he ATtiny2313 and will always read as zero.

• Bits 5, 4 – EEPM1 and EEPM0: EEPROM Programming Mode Bits

The EEPROM Program ming mode bits setting def ines which prog ramming action that

will be triggered when writing EEPE. It is possible to program data in one atomic operation (erase the old value and program the new value) or to split the Erase and Write

operations in two differen t operations. T he Program ming times for the different m odes

are shown in Table 1. While EEPE is set, any write to EEPMn will be ignored. During

reset, the EEPMn bits will be reset to 0b00 unless the EEPROM is busy programming.

16

ATtiny2313

Table 1. EEPROM Mode Bits

Programming

EEPM1 EEPM0

0 0 3.4 ms Erase and Write in one operation (Atomic Operation)

Time Operation

2543A–AVR–08/03

Page 17

ATtiny2313

Table 1. EEPROM Mode Bits

Programming

EEPM1 EEPM0

0 1 1.8 ms Erase Only

1 0 1.8 ms Write Only

1 1 – Reserved for future use

• Bit 3 – EERIE: EEPROM Ready Interrupt Enable

Writing EERIE to one enables the EEPROM Ready Interrupt if the I-bit in SREG is set.

Writing EERIE to zero disables the interrupt. The EEPROM Ready Interrupt generates a

constant interrupt when Non-volatile memory is ready for programming.

• Bit 2 – EEMPE: EEPROM Master Program Enable

The EEMPE bit determines whether writing EEPE to one will have effect or not.

When EEMPE is set, setting EEPE within four clock cycles wi ll program the EEPROM at

the selected address. If EEMPE is zero, setting EEPE will have no effect. When EEMPE

has been written to one by software, hardware clears the bit to zero after four clock

cycles.

Time Operation

• Bit 1 – EEPE: EEPROM Program Enable

The EEPR OM P rog ram Enabl e S ignal EE PE is th e pr ogram ming enab le sign al t o the

EEPROM. When EEPE is written, the EEPROM will be programmed according to the

EEPMn bits setting. The EEMPE bit must be written to one before a logical one is written to EEPE, otherwis e no EEPROM write takes pl ace. When the write a ccess time has

elapsed, the EEP E bit is cleared by hardwa re. When EEPE has been set , the CPU is

halted for two cycles before the next instruction is executed.

• Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal – EERE – is the read strobe to the EEPROM. When

the correct address is set up in the EEAR Register, the EERE bit must be written to one

to trigger the EEPROM read. The EEPROM read access takes one instruction, and the

requested data is available immediately. When the EEPROM is read, the CPU is halted

for four cycles before the next instruction is executed. The user should poll the EEPE bit

before starting th e read operati on. If a write oper at ion is in progress, it i s ne ither possi ble

to read the EEPROM, nor to change the EEAR Register.

Atomic Byte Programming Using Atomic B yte Prog ramming is the si mplest mo de. When writin g a byte to the

EEPROM, the user must write the address into the EEAR Register and data into EEDR

Register. If the EEPMn bits are zero, writing EEPE (wi thin four cycles after EEMPE is

written) will trigger the erase/write operation. Both the erase and write cycle are done in

one operation and the total programming time is given in Table 1. The EEPE bit remains

set until the erase and write operations are completed. While the device is busy with

programming, it is not possible to do any other EEPROM operations.

Split Byte Programming It is possible to split the erase and wri te cycle in two d ifferent operations. Th is may be

useful if the system requires short access time for some limited period of time (typically

if the power supply voltage fal ls). In order to t ake advantage of this method, it is req uired

that the locations to be w ritten have be en eras ed before the write op eration. But si nce

the erase and write op erations are split, it is possi ble to do t he erase o perations w hen

the system allows doing time-cons uming operations (typically after Power-up).

17

2543A–AVR–08/03

Page 18

Erase To erase a byte, the address must be written to EEAR. If the EEPMn bits are 0b01, writ-

ing the EEPE (within four cycles after EEMPE is written) will trigger the erase operation

only (programming time is given in Table 1). The EEPE bit remai ns set until the erase

operation completes. While the device is busy programming, it is not possible to do any

other EEPROM operations.

Write To write a location, the user must write the address into EEAR and the data into EEDR.

If the EEPMn bits are 0b10, wri ti ng the EEPE (within four cycles after EEMPE is written)

will trigger the write operation only (programming time is give n in Table 1). The EE PE

bit remains set until the write o peration co mpletes . If the l ocation to be writ ten has not

been erased before write, the data that is stored must be considered as lost. While the

device is busy with programming, it is not possible to do any other EEPROM operations.

The calibrated Oscillator is used to time the EEPROM accesses. Make sure the Oscillator frequency is with in the requirements desc ribed in “Oscillator C alibration R egister –

OSCCAL” on page 26.

18

ATtiny2313

2543A–AVR–08/03

Page 19

ATtiny2313

The following code examples show one assembly and on e C function for writing to the

EEPROM. The examples assume t hat interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions.

Assembly Code Example

EEPROM_write:

; Wait for completion of previous write

sbic EECR,EEWE

rjmp EEPROM_write

; Set up address (r17) in address register

out EEAR, r17

; Write data (r16) to data register

out EEDR,r16

; Write logical one to EEMWE

sbi EECR,EEMW E

; Start eeprom wri te by setting EEWE

sbi EECR,EEWE

ret

C Code Example

void EEPROM_write(uns igned int uiAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEWE))

;

/* Set up address and data registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMWE */

EECR |= (1<<EEMWE);

/* Start eeprom write by setting EEWE */

EECR |= (1<<EEWE);

}

2543A–AVR–08/03

19

Page 20

The next code examples show assembly and C functions for reading the EEPROM. The

examples assume that interru pts are controlled so that no interrupts will occur during

execution of these functions.

Assembly Code Example

EEPROM_read:

; Wait for completion of previous write

sbic EECR,EEWE

rjmp EEPROM_read

; Set up address (r17) in address register

out EEAR, r17

; Start eeprom read by writing EERE

sbi EECR,EERE

; Read data from data register

in r16,EEDR

ret

C Code Example

unsigned char EEPROM_read(unsigned int uiAddress)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEWE))

;

/* Set up address reg ister */

EEAR = uiAddress;

/* Start eeprom read by writing EERE */

EECR |= (1<<EERE);

/* Return data from data register */

return EEDR;

}

Preventing EEPROM Corruption

20

ATtiny2313

During periods of low V

the EEPROM data can be corrupted because the supply volt-

CC,

age is too low for the CPU and the EEPROM to operate properly. These issues are the

same as for board level systems using EEPROM, and the same design solutions should

be applied.

An EEPROM data corruption can be caused by two situations wh en the voltage is too

low. First, a regular write sequence to t he EEPROM requires a minimum volt age to

operate correctly. Second ly, the CPU itself can execute ins tructions incorrectly , if the

supply voltage is too low.

EEPROM da ta corruption can easily be avoided by fol lowing this design

recommendation:

Keep the AVR RESET ac tive (low) during periods of insuf ficient power supp ly voltage.

This can be do ne by enab ling the i nternal B rown- out Detect or (BOD). If the de tection

level of the internal BOD does not match the needed detection level, an external low

reset Protecti on circ uit ca n be used. If a re set occurs w hile a write ope ration i s in

V

CC

progress, the write oper ation will be compl et ed provide d that the power supply voltage i s

sufficient.

2543A–AVR–08/03

Page 21

ATtiny2313

I/O Memory The I/O space definition of the ATtiny2313 is shown in “Register Summary” on page

198.

All ATtiny2313 I/Os and peripherals are place d in the I/O space. All I/O loc ations may be

accessed by the LD/LDS/LDD and ST/STS/STD instructions, transferring data between

the 32 general purpose working registers and the I/O space. I/O Registers within the

address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and

SBIC instructions. Refer to the instruction set section for more details. When using the

I/O specific c ommand s IN and OUT, t he I/O ad dresses 0x 00 - 0 x3F mus t be used.

When addressing I/O Registers as data space using LD and ST instructions, 0x20 must

be added to these addresses.

For compatibility wit h future devices, reserved bits should be writ ten to zero if accessed.

Reserved I/O memory addresses should never be written.

Some of the status flags a re cleared by writing a l ogical one to them. Note that, u nlike

most other AVRs, the CBI and SBI instructions wi ll only operate on the specified bit, and

can therefore be used on registers containing such status flags. The CBI and SBI

instructions work with registers 0x00 to 0x1F only.

The I/O and peripherals control registers are explained in later sections.

General Purpose I/O Registers The ATtiny2313 contains three General Purpose I/O Registers. These registers can be

used for storing any information, and they are particularly useful for storing global variables and status flags. General Purpose I/O Registers within the address range 0x00 0x1F are directly bit-accessible using the SBI, CBI, SBIS, and SBIC instructions.

General Purpose I/O Register 2 – GPIOR2

Bit 76543210

MSB LSB GPIOR2

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

General Purpose I/O Register 1 – GPIOR1

Bit 76543210

MSB LSB GPIOR1

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

General Purpose I/O Register 0 – GPIOR0

Bit 76543210

MSB LSB GPIOR0

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

2543A–AVR–08/03

21

Page 22

System Clock and Clock Options

Clock Systems and their Distribution

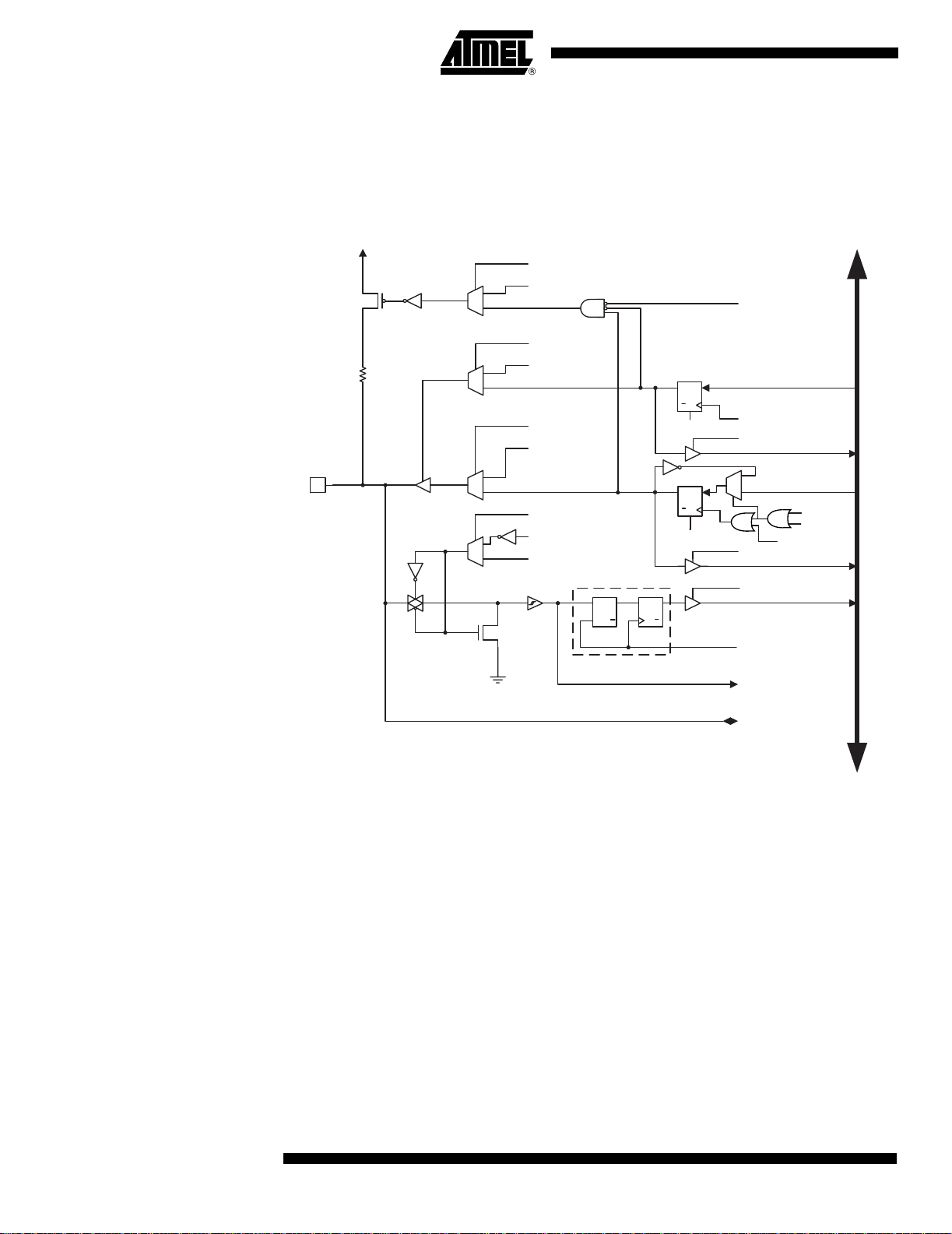

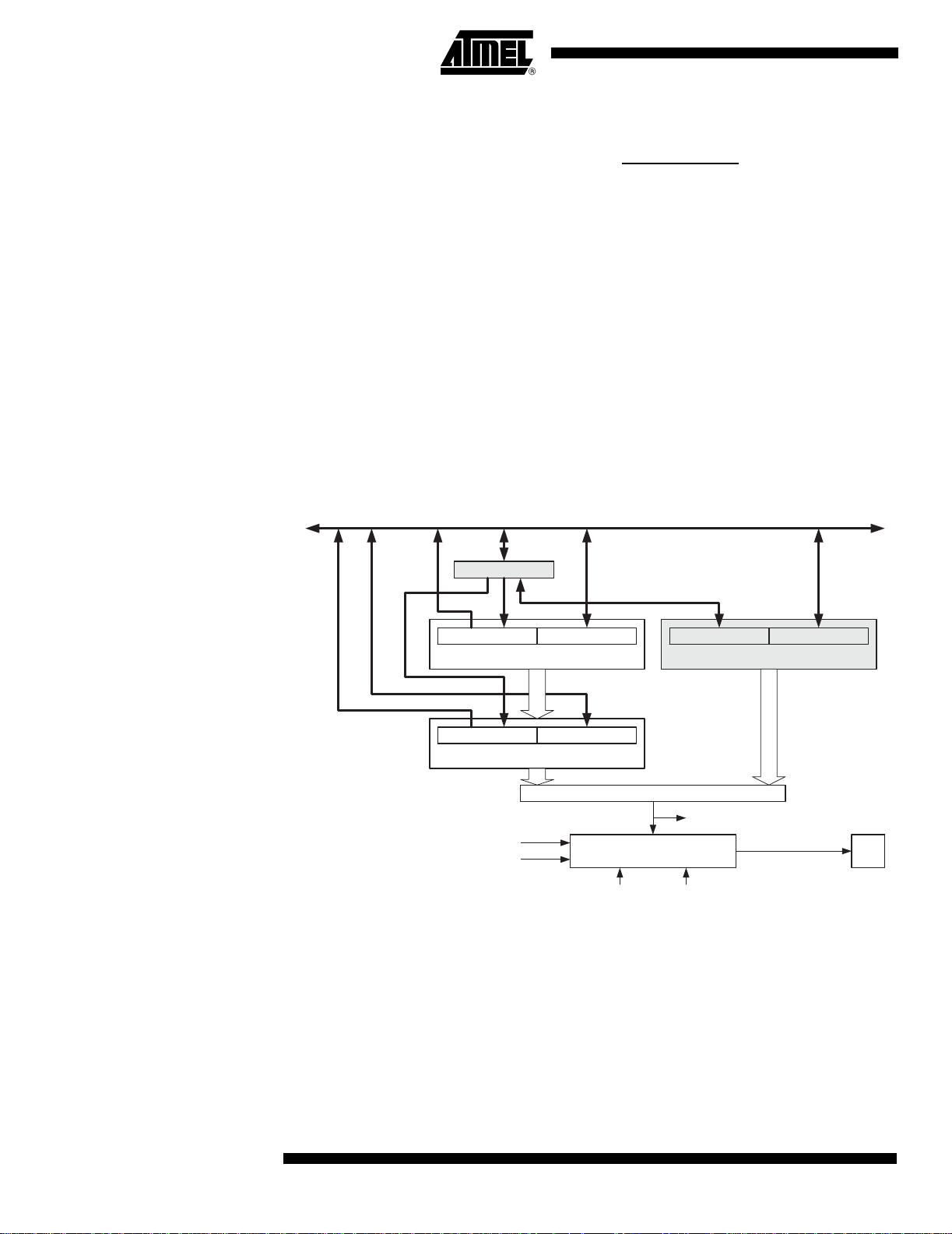

Figure 11 presen ts the princip al clo ck system s in the AV R and the ir distributi on. All of

the clocks need not be active at a given time. In order to redu ce power consump tion, the

clocks to modules not being used can be halted by using different sleep modes, as

described in “Power Management and Sleep Modes” on page 30. The clock systems

are detailed below.

Figure 11. Clock Distribution

General I/O

Modules

clk

CPU Core RAM

I/O

AVR Clock

Control Unit

Source clock

Clock

Multiplexer

clk

CPU

clk

FLASH

Reset Logic

Watchdog Timer

Watchdog clock

Watchdog

Oscillator

Flash and

EEPROM

CPU Clock – clk

I/O Clock – clk

I/O

Flash Clock – clk

CPU

FLASH

External Clock

Crystal

Oscillator

Calibrated RC

Oscillator

The CPU clock is routed to parts of the system concerned with operation of the AVR

core. Examples of such module s are the General Purpose Reg ister File, the Stat us Register and the data memory holding the Stack Pointer. Halting the CPU clock inhibits the

core from performing general operations and calculations.

The I/O clock is used by the majority of the I/O modules, like Timer/Counters, and

USART. The I/O clock is also used by the External Interrupt module, but note that some

external inter rupts are d etected by as ynchrono us logic, al lowing suc h interrup ts to be

detected even if the I/O clock i s halted . Also note that start conditi on detect ion in the USI

module is carried out asynchronously when clk

is halted, enabling USI start condition

I/O

detection in all sleep modes.

The Flash clock controls operation of the Flash interface. The Flash clock is usually

active simultaneously with th e CPU clock.

22

ATtiny2313

2543A–AVR–08/03

Page 23

ATtiny2313

Clock Sources The device has the following clock source options, selectable by Flash Fuse bits as

shown below. The clock from the selected source is input to the A VR cl ock gene rator,

and routed to the appropriate module s.

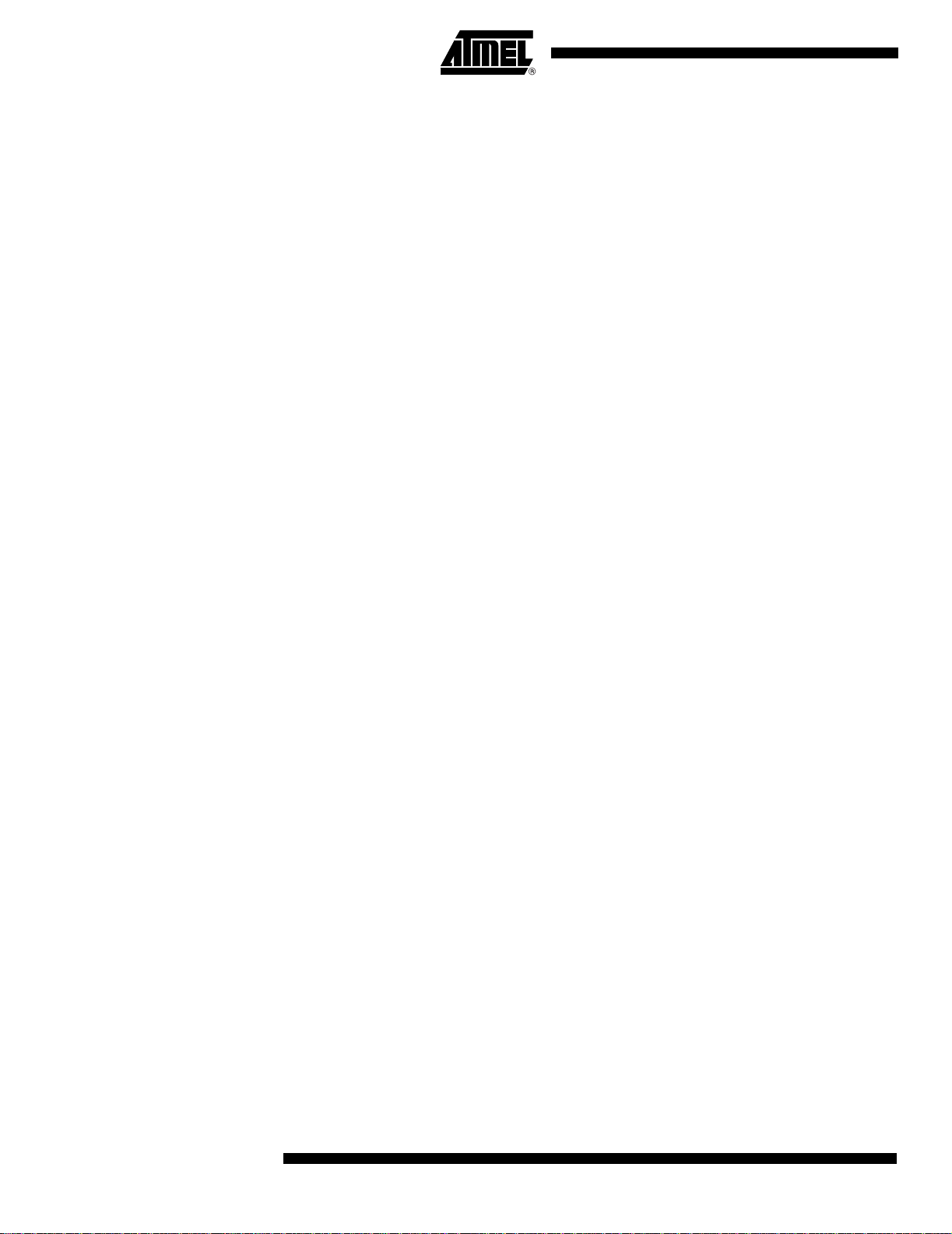

Table 2. Device Clocking Select

Device Clocking Option CKSEL3..0

External Clock 0000 - 0001

Calibrated Internal RC Oscillator 4MHz 0010 - 0011

Calibrated internal RC Oscillator 8MHz 0100 - 0101

Watchdog Oscillator 128kHz 0110 - 0111

External Crystal/Ceramic Resonator 1000 - 1111

Note: 1. For all fuses “1” means unprogrammed while “0” means programmed.

(1)

The various choices for each clocki ng optio n is given i n the followi ng secti ons. When the

CPU wakes up from Power-down, the sel ected clock source is us ed to time the start-up,

ensuring stable Oscillator operation before instruction execution starts. When the CPU

starts from reset, there is an additional delay allowing the power to reach a stable level

before commenci ng n ormal op eration . Th e Wa tchdog Os cillator i s used for timing this

real-time part of the start-up time. The number of WDT Oscillator cycles used for each

time-out is shown in Table 3. The freque ncy of the Watchdog Oscillator is voltage

dependent as shown in “ATt iny2313 Ty pic al Charac teris tics – Preli minary Dat a” on page

181.

Table 3. Number of Watchdog Oscillator Cycles

Typ Time-out (VCC = 5.0V) Typ Time-out (VCC = 3.0V) Number of Cycles

4.1 ms 4.3 ms 4K (4,096)

65 ms 69 ms 64K (65,536)

Default Clock Source The device is shipped with CKSEL = “0010”, SUT = “10”, and CKDIV8 programmed.

The default clock source setting is t he Internal R C Oscillator wit h longest start-up t ime

and an initial system clock prescaling of 8. This defaul t settin g ensur es that all user s can

make their desired clock source setting using an In-System or Parallel programmer.

2543A–AVR–08/03

23

Page 24

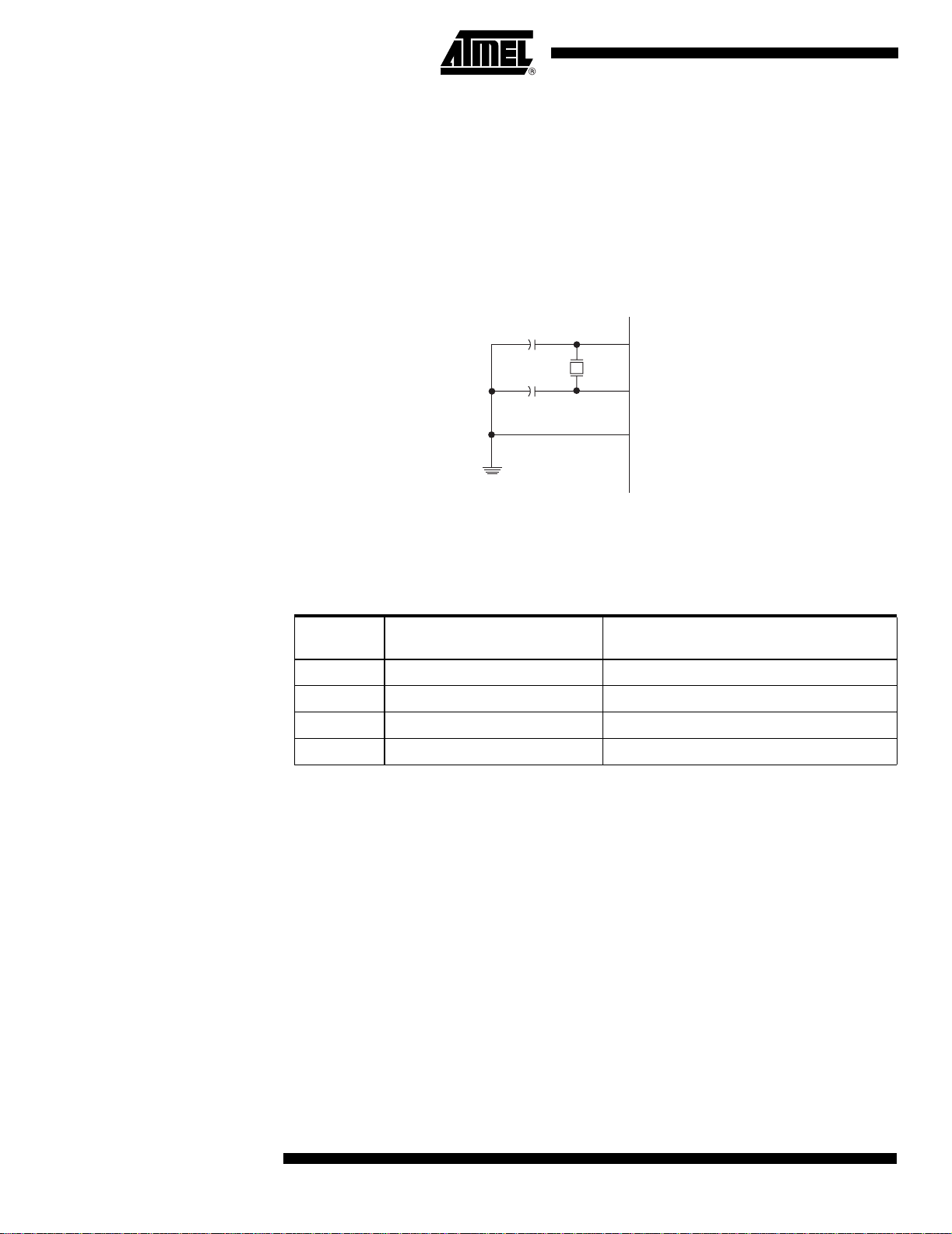

Crystal Oscillator XTAL1 and XTAL2 are input and o utput , respectively, of an inverting amplifier which can

be configured for use as an On-chip Osc illator, as shown i n F igure 12. Either a quartz

crystal or a ceramic resonator may be used.

C1 and C2 should always be equal for both crystals and resonators. The optimal value

of the capacitors depends on the crystal or resonator in use, the amount of stray capacitance, and the electromagnetic noise of the environment. Some initial guidelines for

choosing capacitors for use with crystals are given in Table 4. For ceramic resonators,

the capacitor values given by the manufacturer should be used.

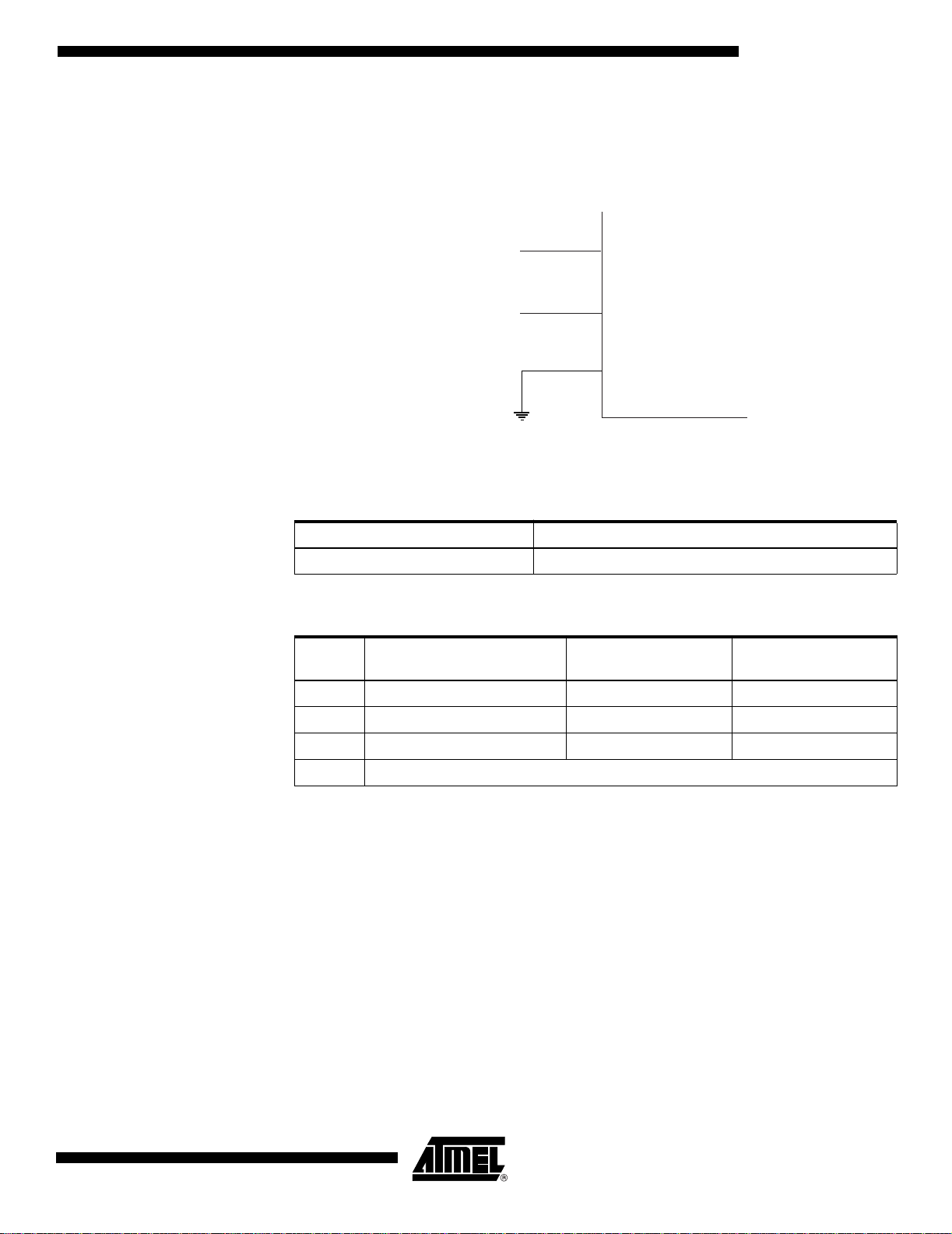

Figure 12. Crystal Oscillator Connections

C2

C1

XTAL2

XTAL1

GND

The Oscillator can operate in three different modes, each optimized for a specific frequency range. The operating mode is selected by the fuses CKSEL3..1 as shown in

Table 4.

Table 4. Crystal Oscillator Operating Modes

CKSEL3..1 Frequency Range

(2)

100

101 0.9 - 3.0 12 - 22

110 3.0 - 8.0 12 - 22

111 8.0 - 12 - 22

Notes: 1. The frequency ranges are preliminary values. Actual values are TBD.

2. This option should not be used with crystals, only with ceramic resonators.

0.4 - 0.9 –

(1)

(MHz)

Recommended Range for Capacitors C1

and C2 for Use with Crystals (pF)

24

The CKSEL0 Fuse together with the SUT1..0 Fuses select the start-up times as shown

in Table 5.

ATtiny2313

2543A–AVR–08/03

Page 25

Table 5. Start-up Times for the Crystal Oscillator Clock Selection

ATtiny2313

Start-up Time from

Power-down and

CKSEL0 SUT1..0

0 00 258 CK

0 01 258 CK

010 1K CK

011 1K CK

100 1K CK

1

1

1

Notes: 1. These options should only be used when not operating close to the maximum fre-

01 16K CK 14CK Crystal Oscillator, BOD

10 16K CK 14CK + 4.1 ms Crystal Oscillator, fast

11 16K CK 14CK + 65 ms Crystal Oscillator,

quency of the device, and only if frequency stability at start-up is not important for the

application. These options are not suitable for crystals.

2. These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating

close to the maximum frequency of the device, and if frequency stability at start-up is

not important for the application.

Power-save

(1)

(1)

(2)

(2)

(2)

Additional Delay

from Reset

(VCC = 5.0V) Recommended Usage

14CK + 4.1 ms Ceramic resonator, fast

rising power

14CK + 65 ms Ceramic resonator,

slowly rising power

14CK Ceramic resonator,

BOD enabled

14CK + 4.1 ms Ceramic resonator, fast

rising power

14CK + 65 ms Ceramic resonator,

slowly rising power

enabled

rising power

slowly rising power

Calibrated Internal RC Oscillator

The calibrated internal R C Oscillator provides a f ixed 8.0 MH z clock. T he frequ ency is

nominal value at 3V and 25°C. I f 8 MHz frequency exc eeds the specif ication of the

device (depends on V

), the CKDIV8 Fuse must be programmed in order to divide the

CC

internal frequency by 8 during start-up. The device is shipped with the CKDIV8 Fuse

programmed. This clock may b e selected a s the system clock by p rogramming the

CKSEL Fuses as sho wn in T able 6. If selected, it will o perate with no external com ponents. During reset, hardware loads the calibration byte into the OSCCAL Register and

thereby automaticall y calibrates the RC Oscillat or. At 3V and 25°C, this cal ibr ation gives

a frequency within ± 1% of the nom inal fr equency. When th is Osc illator is u sed as t he

chip clock, the Watchdog Oscillator will still be used for the Watchdog Timer and for the

Reset Time-out. For more information on the pre-programmed calibration value, see the

section “Calibration Byte” on page 162.

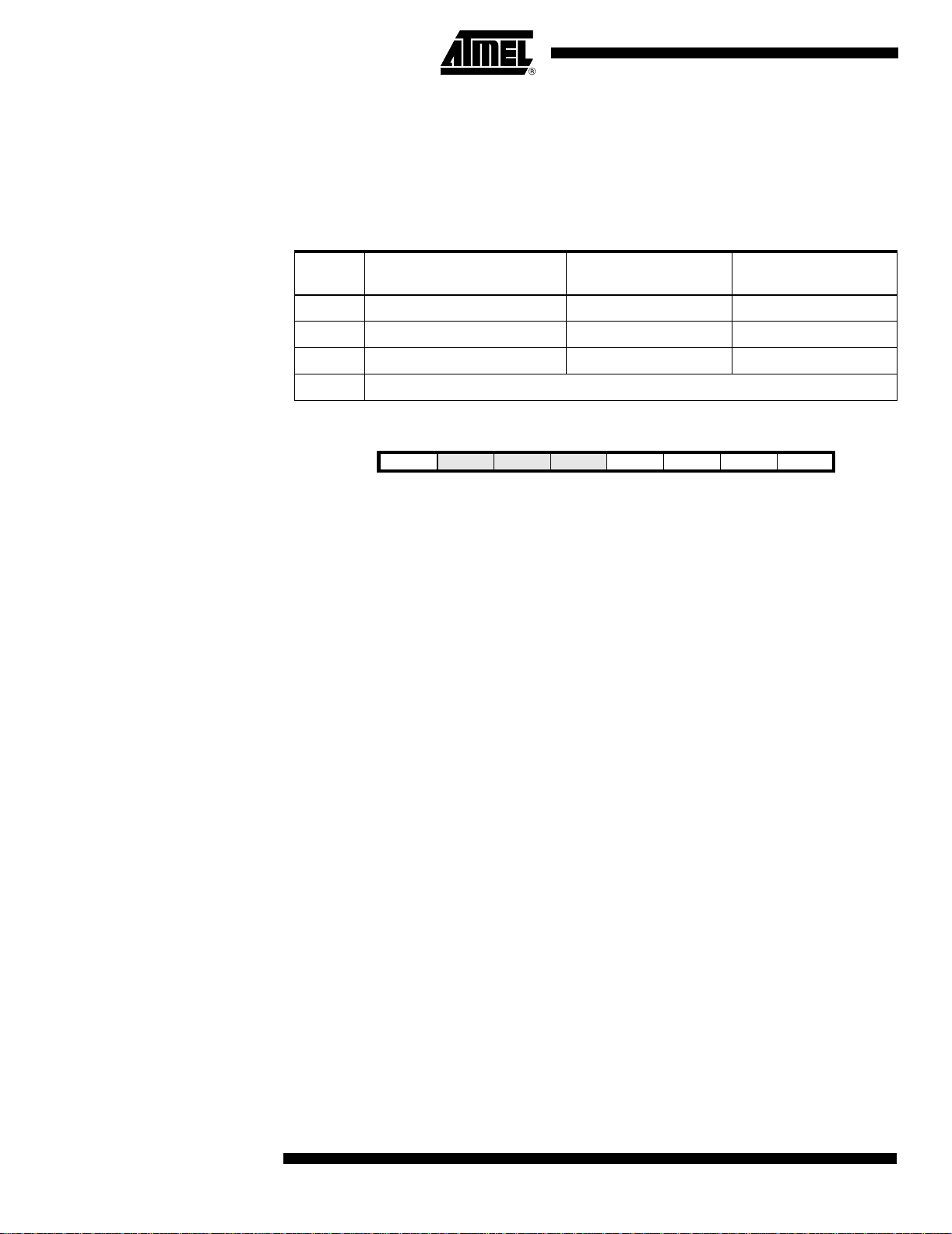

Table 6. Internal Calibrated RC Oscillator Operati ng Mo des

CKSEL3..0 Nominal Frequency

0010 - 0011 4.0 MHz

0100 - 0101 8.0 MHz

Note: 1. The device is shipped with this option selected.

(1)

2543A–AVR–08/03

25

Page 26

When this Oscilla tor is sele cted, sta rt-up times are determ ined by the SUT Fuse s as

shown in Table 7.

Table 7. Start-up times for the internal calibrated RC Oscillator clock selection

Oscillator Calibrat ion Register – OSCCAL

Start-up Time from Power-

SUT1..0

00 6 CK 14CK BOD enabled

01 6 CK 14CK + 4.1 ms Fast rising power

(1)

10

11 Reserved

Note: 1. The device is shipped with this option selected.

Bit 76543210

Read/Write R R/W R/W R/W R/W R/W R/W R/W

Initial Value Device Specific C a libra tion Value

down and Power-save

6 CK 14CK + 65 ms Slowly rising power

– CAL6 CAL5 CAL4 CAL3 CAL 2 CAL1 CAL0 OSCCAL

Additional Del ay from

Reset (VCC = 5.0V) Recommended Usage

• Bits 6..0 – CAL6..0: Oscillator Calibration Value

Writing the calibration byte to this address will trim the internal Oscillator to remove process variations from the Oscillator frequency. This is done automatically during Chip

Reset. When OSCCAL is zero, the lowest avai lable frequency is chosen. Writing nonzero values to this register will increase the frequency of the internal Oscillator. Writing

0x7F to the register gives the hi ghest availab le frequency . The calibrated Os cillator is

used to time EEPRO M and Fla sh acc ess. If EEPRO M or Flas h is writt en, do no t calibrate to more than 10% above the nominal fre quency. Ot herwise, th e EEPROM or Flash

write may fail. Note that the Oscillator is intended for calibration to 8.0/4.0 MHz. Tuning

to other values is not guaranteed, as indi cated in Table 8.

Avoid changing the c ali bration value in large steps when calibrating the Calibrated Inter nal RC Oscillator to ensure stable operation of the MCU. A variation in frequency of

more than 2% from one cycle to the ne xt can l ead to unpr edicat ble behavi or. Cha nges in

OSCCAL should not exceed 0x20 for each calibration.

Table 8. Internal RC Oscillator Frequency Range.

OSCCAL

Value

0x00 50% 100%

0x3F 75% 150%

0x7F 100% 200%

Min Frequency in Percentage of

Nominal Frequency

Max Frequency in Percentage of

Nominal Frequency

26

ATtiny2313

2543A–AVR–08/03

Page 27

ATtiny2313

External Clock To drive the device from an external clock source, XTAL1 should be driven as shown in

Figure 13. To run the de vice on an exte rnal clock, the CK SEL Fuses must be programmed to “0000”.

Figure 13. External Clock Drive Configuration

NC

EXTERNAL

CLOCK

SIGNAL

XTAL2

XTAL1

GND

When this clock source is selected, start-up times are determined by the SUT Fuses as

shown in Table 10.

Table 9. Crystal Oscillator Clock Frequency

CKSEL3..0 Frequency Range

0000 - 0001 0 - 16 MHz

Table 10. Start-up Times for the External Clock Selection

Start-up Time from Power-

SUT1..0

00 6 CK 14CK BOD enabled

01 6 CK 14CK + 4.1 ms Fast rising power

10 6 CK 14CK + 65 ms Slowly rising power

down and Power-save

Addition al Delay fr om

Reset (VCC = 5.0V) Recommended Usage

2543A–AVR–08/03

11 Reserved

When applying an external clock, it is required to avoid sudden changes in the applied

clock frequency to ensure stable operation of the MCU. A variation in frequency of more

than 2% from one clock cycle to the next can lead to unpredictable behavior. It is

required to ensu re that th e MCU is kept in Reset during such changes in the clock

frequency.

Note that the Sy stem Cl ock Presc aler can be us ed to imp lement ru n-time changes of

the internal clock frequ ency while still ensuring stable operation.

27

Page 28

128 kHz Internal Oscillator

The 128 kHz Internal Oscillator is a low power Oscillator providi ng a clock of 128 kHz.

The frequenc y is no minal at 3 V and 25°C . Th is clock may be se lected as th e syste m

clock by programming the CKSEL Fuses to “0110 - 0111”.

When this clock source is selected, start-up times are determined by the SUT Fuses as

shown in Table 11.

Table 11. Start-up Times for the 128 kHz Internal Oscillator

Clock Prescale Register – CLKPR

Start-up Time from Power-

SUT1..0

00 6 CK 14CK BOD enabled

01 6 CK 14CK + 4 ms Fast rising power

10 6 CK 14CK + 64 ms Slowly rising power

11 Reserved

Bit 76543210

Read/Write R/W R R R R/W R/W R/W R/W

Initial Value 0 0 0 0 See Bit Description

down and Power-save

CLKPCE – – – CLKPS3 CLKPS2 CLKPS1 CLKPS0 CLKPR

Addition al Delay fr om

Reset Recommended Usage

• Bit 7 – CLKPCE: Clock Prescaler Change Enable

The CLKPCE bit must be written to logic one to enable change of the CLKPS bits. The

CLKPCE bit is only u pdated wh en the other bits in C LKPR a re simu ltanio sly writte n to

zero. CLKPCE is cleared by hardware four cycles after it is written or when CLKPS bits

are written. Rewriting t he CLKPCE bit wit hin this ti me-out per iod does nei ther ext end the

time-out period, nor clear the CLKPCE bit.

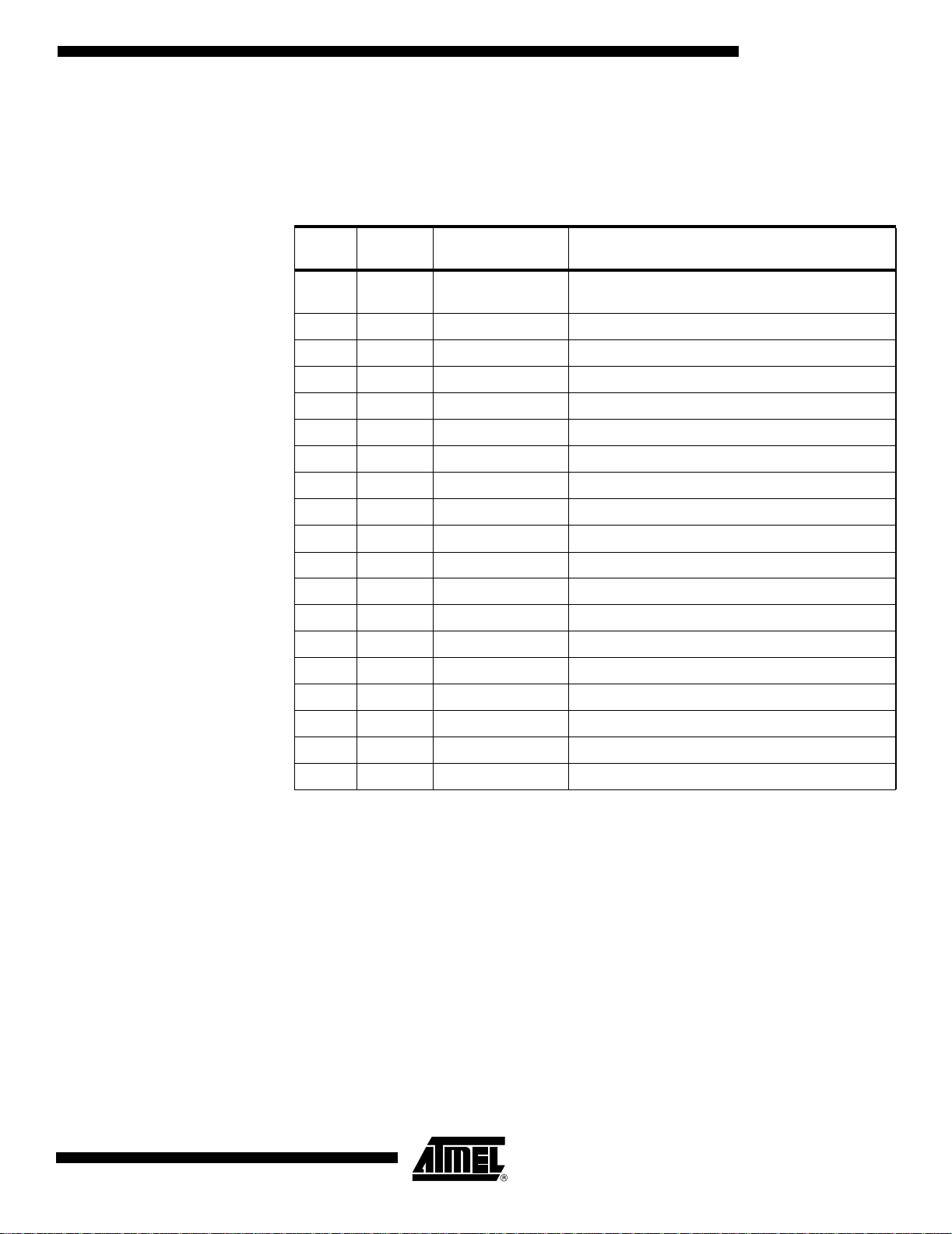

• Bits 3..0 – CLKPS3..0: Clock Prescaler Select Bits 3 - 0

These bits define the division factor between the selected clock source and the internal

system clock. These bits can be written run-time to vary the clock frequency to suit the

application requirements. As the divider divides the master clock input to the MCU, the

speed of all synchronous peripherals is reduced when a division factor is used. The division factors are given in Table 12.

28

To avoid uni ntenti onal ch ang es of c lock freque ncy, a spec ial wr ite pr ocedure must be

followed to change the CLKPS bits:

1. Write the Clock Prescaler Change Enable (CLKPCE) bit to one and all other bits

in CLKPR to zero.

2. Within four cycles, write the desired value to CLKPS while writing a zero to

CLKPCE.

Interrupts must be disabled when changing prescaler setting to make sure the write procedure is not interrupted.

The CKDIV8 Fu se determi nes the initia l value of the CLK PS bits. If CKDIV8 is unp rogrammed, the CLKPS bits will be reset to “0000”. If CKDIV8 is programmed , CLKPS bits

are reset to “ 0011”, giving a divisi on factor of 8 at start up. This feat ure should be used i f

the selected c lock sou rce has a highe r frequen cy tha n the maxi mum freq uency of the

device at the present operating conditions. Note that any value can be written to the

CLKPS bits reg ardless of the CKD IV8 Fuse setting. T he Applic ation softwa re must

ensure that a sufficient division factor is chosen if the selcted clock source has a higher

ATtiny2313

2543A–AVR–08/03

Page 29

ATtiny2313

frequency than the maximum frequency of the device at the present operating conditions. The device is shipped with the CKDIV8 Fuse programmed.

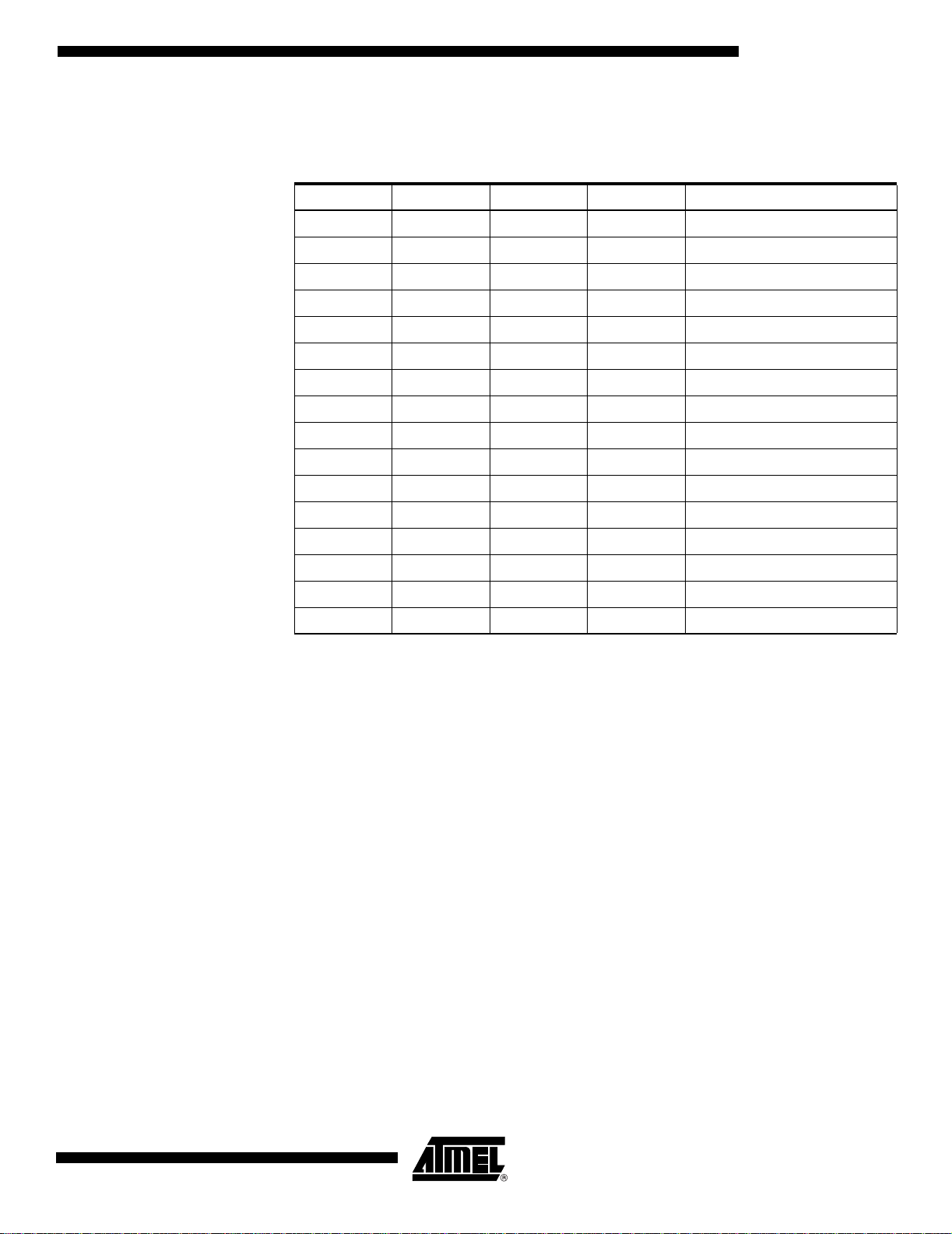

Table 12. Clock Prescaler Select

CLKPS3 CLKPS2 CLKPS1 CLKPS0 Clock Division Factor

0000 1

0001 2

0010 4

0011 8

0100 16

0101 32

0110 64

0111 128

1000 256

1 0 0 1 Reserved

1 0 1 0 Reserved

1 0 1 1 Reserved

1 1 0 0 Reserved

1 1 0 1 Reserved

1 1 1 0 Reserved

1 1 1 1 Reserved

2543A–AVR–08/03

29

Page 30

Power Management and Sleep Mo des

Sleep modes enable the application to shut down unused modules in the MCU, thereby

saving power. The AVR provides various sleep modes allowing the user to tailor the

power consumption to the application’s requirements.

To enter any of the three sleep modes, the SE bit in SMCR must be written to logic one

and a SLEEP instruction must be executed. The SM1 and SM0 bits in the MCUCR Register select which sleep mode (Idle, Power-down, or Standby) will be activated by the

SLEEP instruction. See Table 13 for a summary. If an e nabled interrupt occurs while the

MCU is in a sleep mode, the MCU wakes up. The MCU is then halted for four cycles in

addition to the start -up time, executes the inter rupt routine, and resumes exec ution from

the instruction f ollowin g SLEEP. T he conte nts of the regist er file and SRAM are un altered when the device wakes up from sleep. If a reset occurs during sleep mode, the

MCU wakes up and executes from the Reset Vector.

Figure 11 on page 22 presents the different clock systems in the ATtiny2313, and their

distribution. The figure is helpful in selecting an appropriate sleep mode.

MCU Control Register – MCUCR

The Sleep Mode Control Register contai ns control bits for power management.

Bit 76543210

PUD SM1 SE SM0 ISC11 ISC10 ISC01 ISC00 MCU CR

Read/Write R R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bits 6, 4 – SM1..0: Sleep Mode Select Bits 1 and 0

These bits select between the five available sleep modes as shown in Table 13.

Table 13. Sleep Mode Select

SM1 SM0 Sleep Mode

00Idle

0 1 Power-down

1 1 Power-down

1 0 Standby

Note: 1. Standby mode is only recommended for use with external crystals or resonators.

• Bit 5 – SE: Sleep Enable

The SE bit must be written to lo gic one t o make the MCU enter the sle ep mode when the

SLEEP instruction is executed. To avoi d the MCU entering the sleep mode unl ess it is

the programmer’s purpose, it is recommended to write the Sleep Enable (SE) bit to one

just before the execution of the SLEEP instruction and to clear it immediately after waking up.

30

ATtiny2313

2543A–AVR–08/03

Page 31

ATtiny2313

Idle Mode When the SM1..0 bits are written to 00, the SLEEP instruction makes the MCU enter

Idle mode, stopping the CPU but allowing the UART, Analog Comparator, ADC, USI,

Timer/Counters, Watchdog, and the interrupt system to continue operating. T his sleep

mode basically halts clk

CPU

and clk

Idle mode enables the MCU to wake up from external triggered interrupts as well as

internal ones like the Timer Overflow and UART Transmit Complete interrupts. If wakeup from the Analog Comparator interrupt is not required, the Analog Comparator can be

powered down by setting the ACD bit in the Analog Comparat or Control and Status

Register – ACSR. This will reduce power consumpti on in I dle mode.

Power-down Mode When the SM1..0 bits are written to 01 or 11, the SLEEP in struction make s the MCU

enter Power-down mode . In this mode, t he external Osc illator is stopped, while the

external interrupts , the USI start conditi on detect ion, and the Watchd og continue operat ing (if enabled). Only an External Reset, a Watchdog Reset, a Brown-out Reset, USI

start condition i nterru pt, an ext ern al leve l int err upt on INT0, or a pin change int err upt can

wake up the MCU. This sleep mode basical ly halts all generated clock s, al lowing operation of asynchronous modules only.

Note that if a level triggered interrupt is used for wake-up f rom Power-down mode, the

changed level must be held for some time to wake up the MCU. Refer to “External Inter rupts” on page 61 for details.

, while allowing the other clocks to run.

FLASH

When waking up from Power-down mode, there is a delay from the wake -up con dition

occurs until the wake-up becomes effective. This allows the clock to restart and become

stable after having been stopp ed. The wake-u p p eriod is defined b y th e same CKS EL

Fuses that define the Reset Time-out period, as described in “Clock Sources” on page

23.

Standby Mode When the SM1..0 bits are 10 and an external crystal/resonator clock option is selected,

the SLEEP instruction ma kes the MCU enter Stan dby mode. This mode i s identical to

Power-down with the exception that the Oscillator is kept running. From Standby mode,

the device wakes up in six clock cycles.

Table 14. Active Clock Domains and Wake-up Sources in the Different Sleep Modes.

Active Clock Domains Oscillators Wake-up Sources

CPU

Sleep Mode

Idle XXXXXX

Power-down X

Standby

Notes: 1. Only recommended with external crystal or resonator selected as clock source.

(1)

2. For INT0, only level interrupt.

clk

FLASH

clk

IO

clk

Enabled

XX

INT0, INT1 and

Pin Change

(2)

(2)

X

X

USI Start Condition

SPM/EEPROM Ready

Other I/O

2543A–AVR–08/03

31

Page 32

Minimizing Power Consumption

Analog Comparator When entering Idle mode, the Analog Comparator should be disabled if not used. In

Brown-out Detector If the Brown-out Det ector is not needed by the application, this module should be turned

Internal Voltage Reference The I nternal Voltage Reference will be enabl ed when needed by the Brown-out Detec-

There are several issues to consider when trying to minimize the power consumption in

an AVR controlled system. In general, sleep modes should be used as much as possible, and the slee p mode shoul d be se lected s o that as few a s p ossible of the devi ce’s

functions are op erating. A ll function s no t needed shoul d be d isabled. In part icular, the

following modules may need special consideration when trying to achieve the lowest

possible power consumption.

other slee p modes , the Anal og Com parato r is automa tical ly disab led. Ho wever, if the

Analog Comparator is set up to use the Internal Voltage Reference as input, the Analog

Comparator should be disabled in all sleep modes. Otherwise, the Internal Voltage Reference will be enabled, independent of sleep mode. Refer to “Analog Compara tor” on

page 151 for details on how to configure the Analog Comparator.

off. If the Brown-out Detector is enabled by the BODLEVEL Fuses, it will be enabled in

all sleep m odes, and h enc e, al ways consum e po wer. In t he d eeper slee p mo des, t his

will contribute significantly to the total current consumption. Refer to “Brown-out Detection” on page 36 for details on how to configure the Brown-out Detector.

tion or the Analog Comparator. If these modules are disabled as described in the

sections above, the internal voltage reference will be disabled and it will not be consuming power. When turned on again , the user must allow the reference to st art up before

the output is used. If the reference is kept on in sleep mode, the output can be used

immediately. Refer to “Internal Voltage Reference” on page 39 for details on the start-up

time.

Watchdog Timer If the Watchdog Timer is not needed in the application, the module should be turned off.

If the Watchdog Timer is enab led, it will be ena bled in all sleep modes, and hence,

always consume power. In the deeper sleep mo des, this will contribute significant ly to

the total curr ent consumption. Refer to “Interrupts” on page 45 for details on how to configure the Watchdog Timer.

32

ATtiny2313

2543A–AVR–08/03

Page 33

ATtiny2313

Port Pins When entering a sleep mode, all port pins should be configured to use minimum power.

The most important is then to ensure that no pins drive resistive loads. In sleep modes

where the I/O clock (clk

This ensures that no power is co nsumed b y the input logic w hen not needed . In som e

cases, the input logic is needed for detecting wake-up conditions, and it will then be

enabled. Refer to the section “Digital Input Enable and Sleep Modes” on page 51 for

details on which pins are enabled. If the input buffer is enabl ed and the input signal is

left floating or have an analog signal level close to V

sive power.

For analog input pins, the digital input buffer should be disabled at all times. An analog

signal level close to V

mode. Digital input buffers can be disabled by writing to the Digital Input Disable Registers (DIDR). Refer to “Digital Input Disable Register – DIDR” on page 152.

) is stopped, the inp ut buffers of the de vice will b e disa bled.

I/O

/2, the input buffer will use exces-

CC

/2 on an input pi n can cause signif icant curren t eve n in act ive

CC

2543A–AVR–08/03

33

Page 34

System Control and

]

Reset

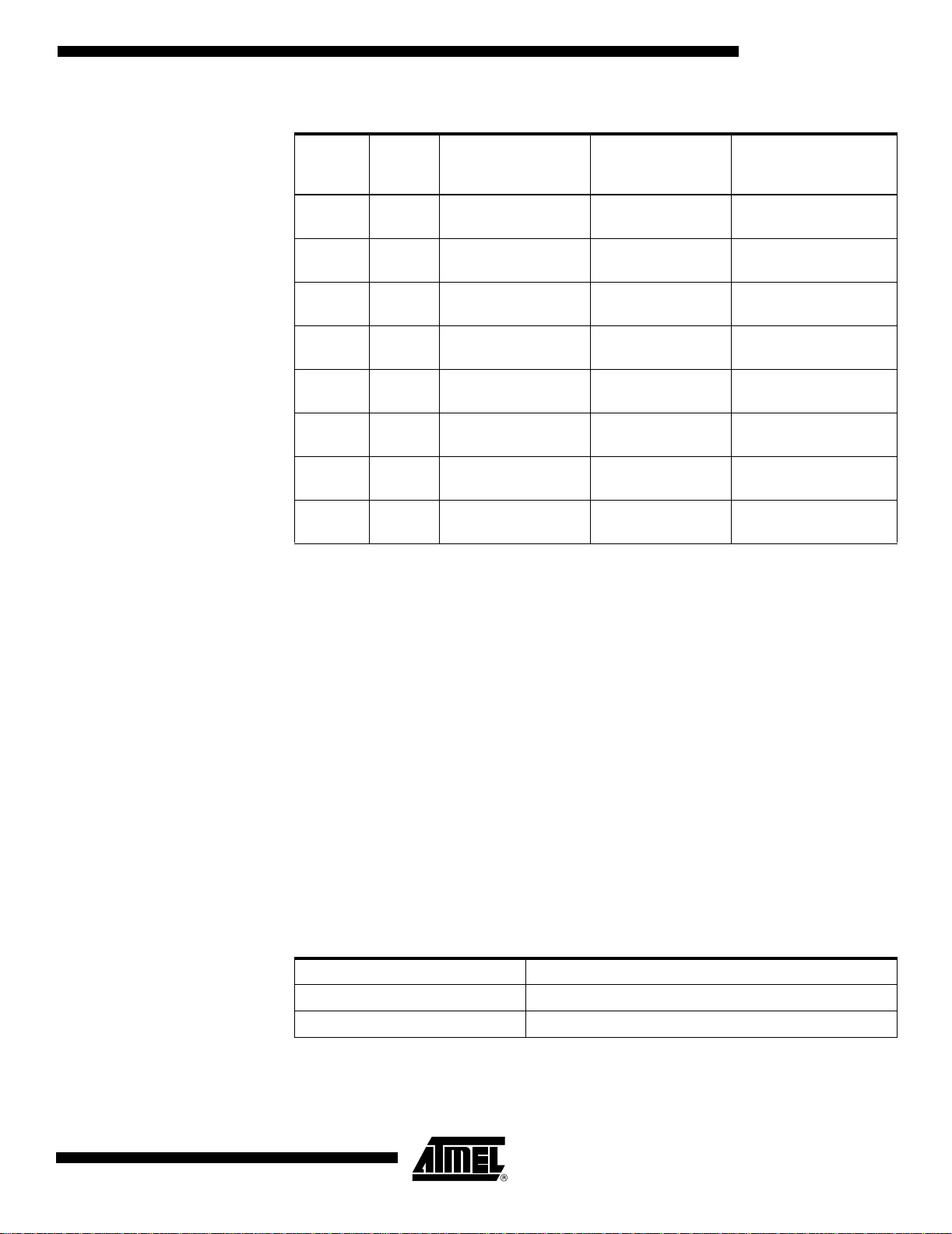

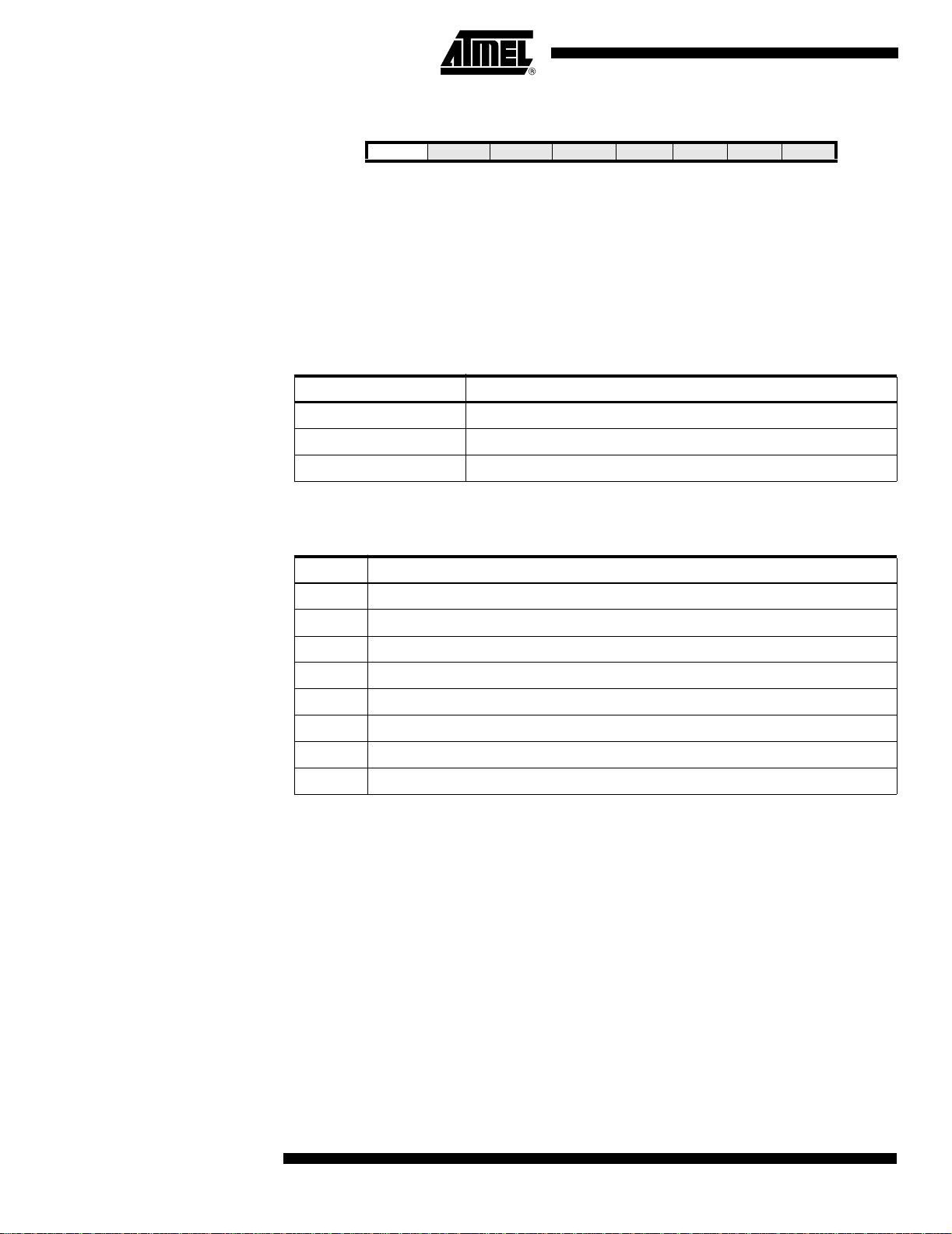

Resetting the AVR During reset, all I/O Registers are set to their initial values, and the program starts exe-

cution from the Reset Vector. The instruction placed at the Reset Vector must be an

RJMP – Relative Jump – instruction to the reset handling routine. If the program never

enables an interrupt source, the Interrupt Vectors are not used, and regular program

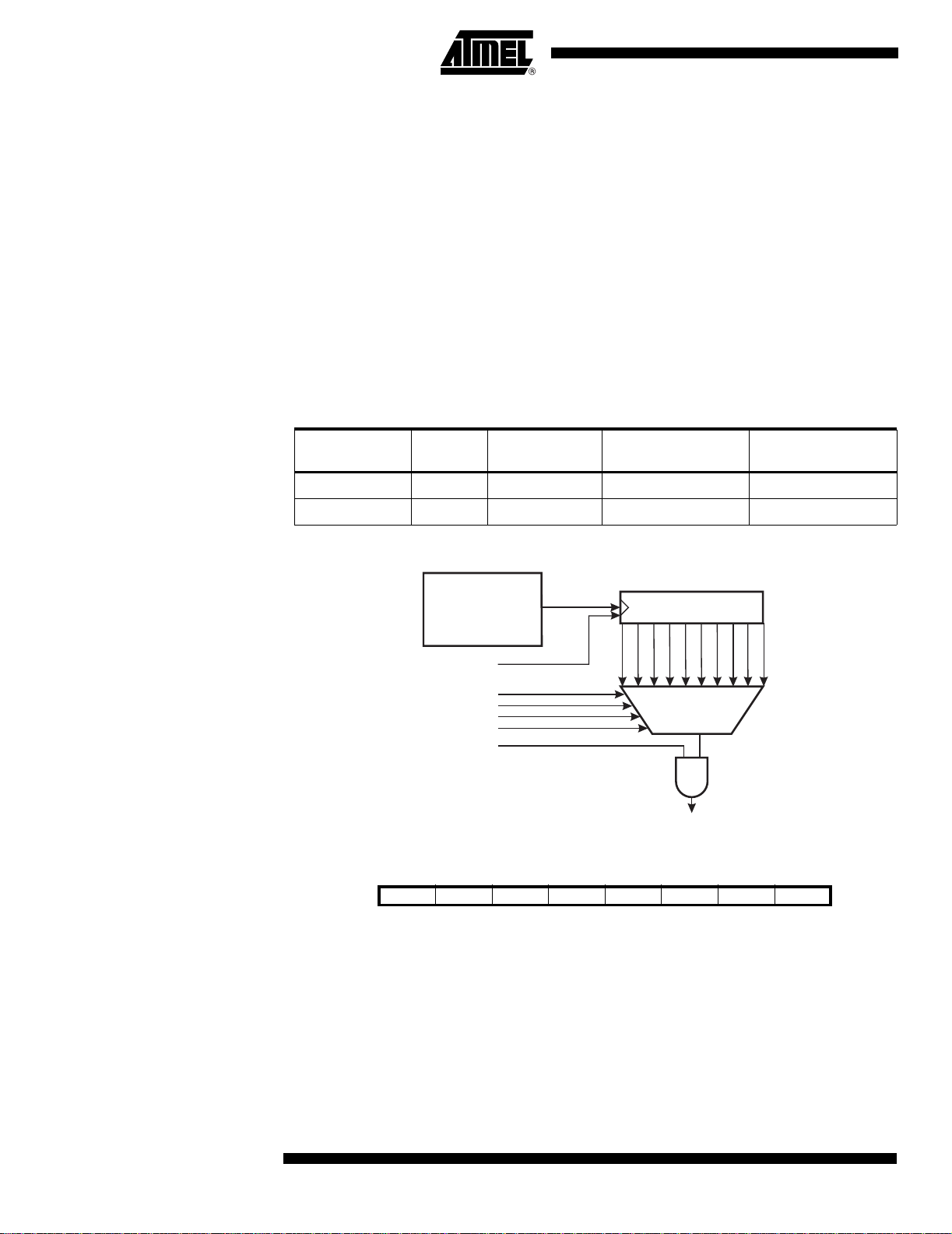

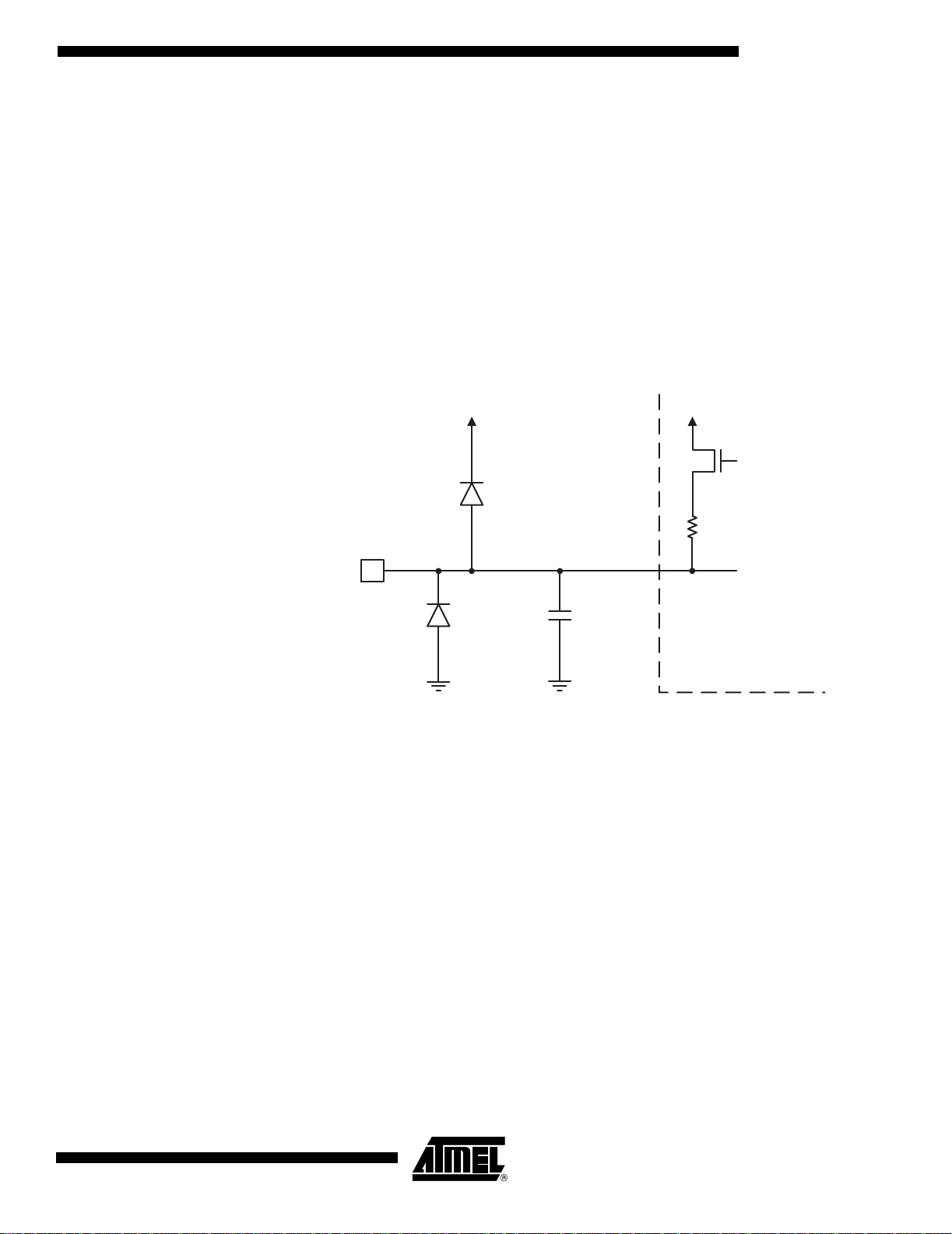

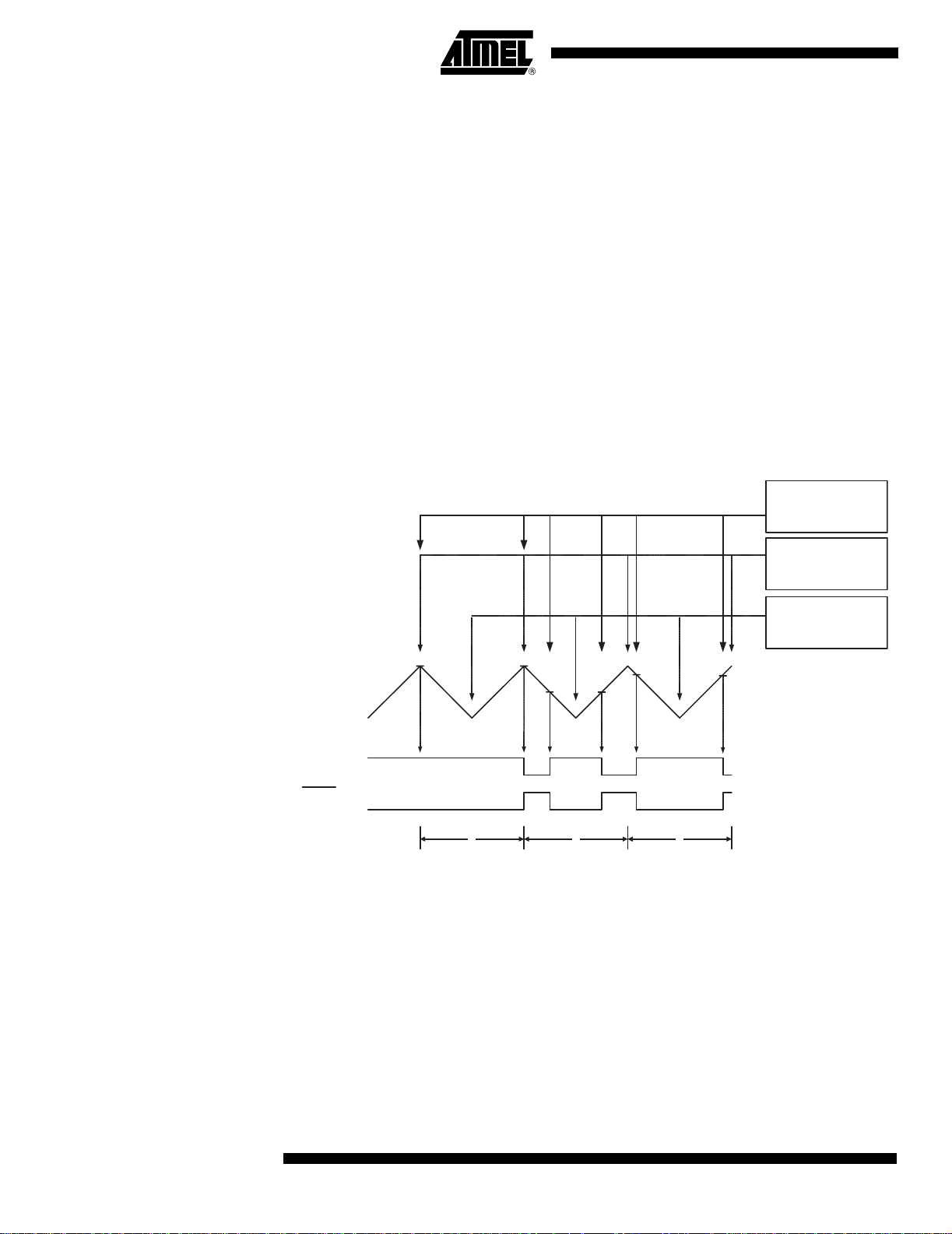

code can be placed at these locations. The circuit diagram in Figure 14 shows the reset

logic. Table 15 defines the electrical parameters of the reset circuitry.

The I/O ports of the AVR are immediately reset to their initial state when a reset source

goes active. This does not require any clock source to be running.

After all reset sources have gone inactive, a delay counter is invoked, stretching the

internal reset. This allows the power to reach a stable level before normal operation

starts. The time-out period of the delay counter is defined by the user through the SUT

and CKSEL Fuses. The different selections for the delay period are presented in “Clock

Sources” on page 23.

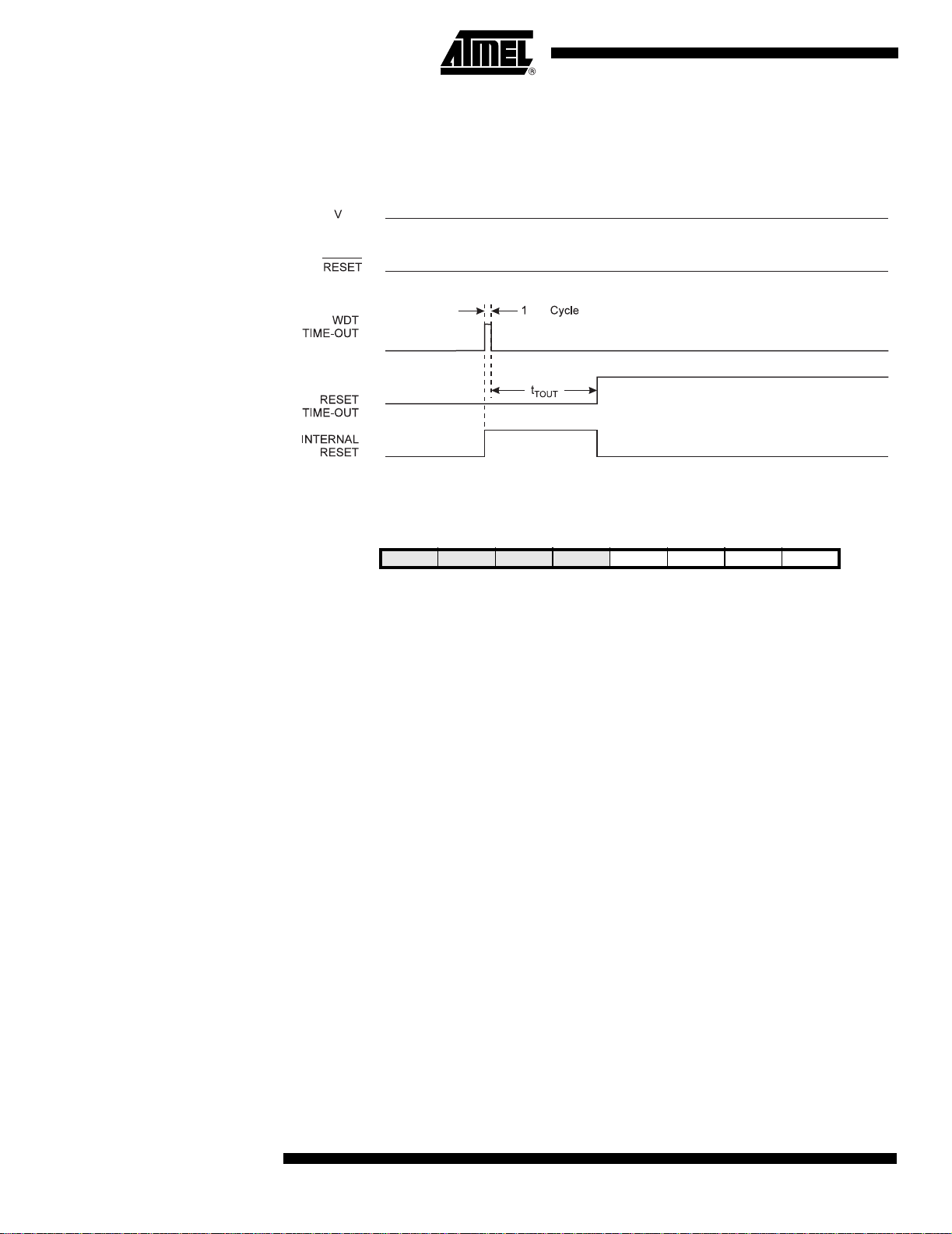

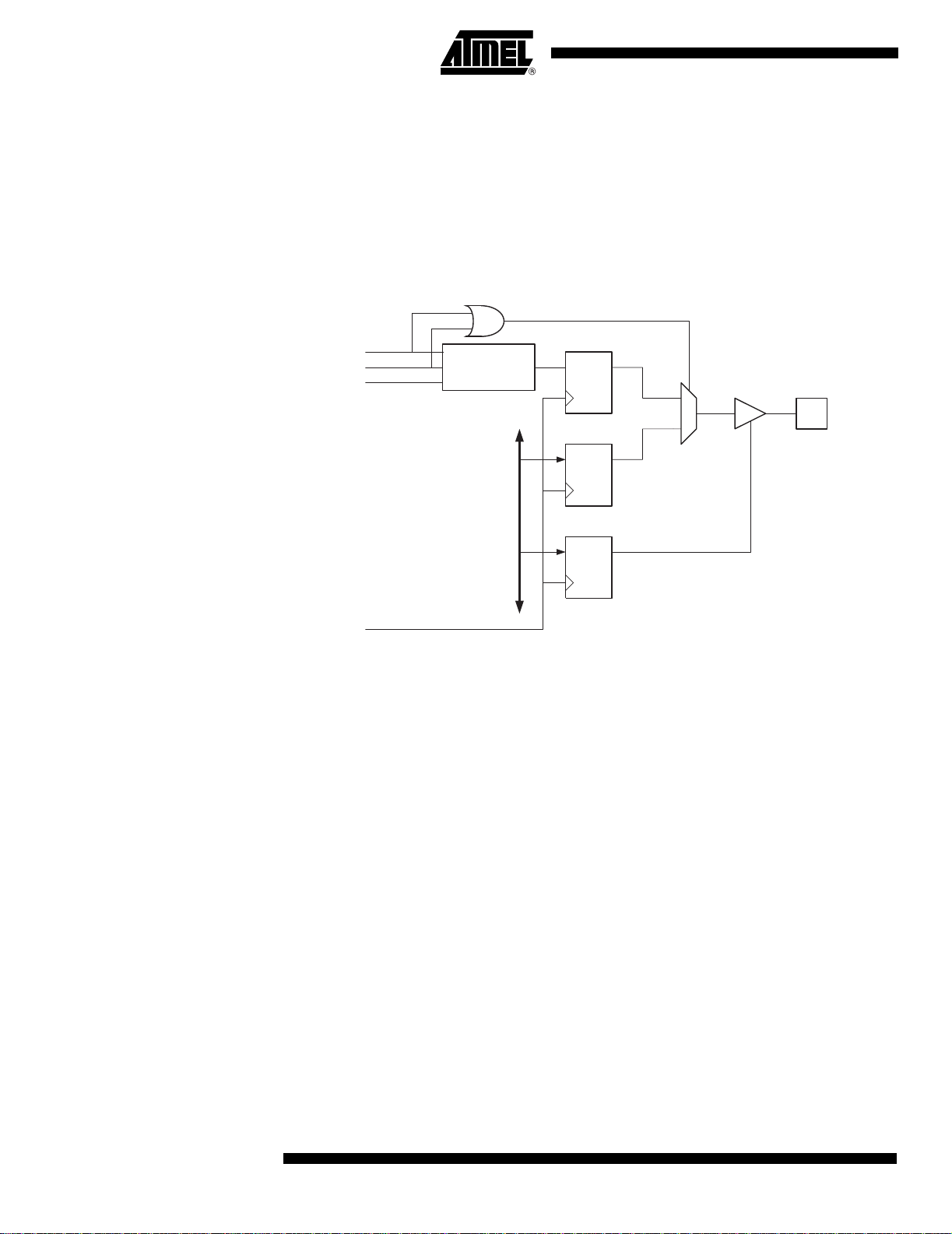

Reset Sources The ATtiny2313 has four sources of reset:

• Power-on Reset. The MCU is reset when the supply voltage is below the Power- on

Reset threshold (V

• External Reset. The MCU is reset when a low level is present on the RESET

longer than the minimum pulse length.

• Watchdog Reset. The MCU is reset when the Watchdog Timer period expires, the

Watchdog is enabled, and Watchdog Interrupt is disabled.

• Brown-out Reset. The MCU is reset when the supply voltage V

Brown-out Reset threshold (V

POT

).

pin for

is below the

) and the Brown-out Detector is enabled.

BOT

CC

Figure 14. Reset Logic

BODLEVEL [2..0]

Pull-up Resistor

SPIKE

FILTER

Power-on Reset

Circuit

Brown-out

Reset Circuit

Watchdog

Oscillator

Clock

Generator

CKSEL[3:0]

SUT[1:0

DATA BUS

MCU Status

Register (MCUSR)

BORF

PORF

CK

WDRF

EXTRF

Delay Counters

TIMEOUT

34

ATtiny2313

2543A–AVR–08/03

Page 35

ATtiny2313

Table 15. Reset Characteristics

(1)

Symbol Parameter Condition Min Typ Max Units

Power-on Reset

Threshold Voltage

TA = -40 - 85°C1.2 V

(rising)

V

V

t

RST

POT

RST

Power-on Reset

Threshold Voltage

(2)

(falling)

RESET Pin Threshold

Voltage

Minimum pulse width on

RESET Pin

TA = -40 - 85°C1.1 V

VCC = 3V 0.2 V

CC

0.85 V

CC

V

VCC = 3V 900 ns

Notes: 1. Values are guidelines only. Actual values are TBD.

2. The Power-on Reset will not work unless the supply voltage has been below V

POT

(falling)

Power-on Reset A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detec-

tion level i s defined in Table 15. Th e POR is a ctivated w heneve r V

is below the

CC

detection level. The POR circuit can be used to trigger the start-up Reset, as well as to

detect a failure in supply volt age.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines

how long the device is kept in RESET after V

again, without any delay, when V

decreases below the detection level.

CC

rise. The RESET signal is activated

CC

Figure 15. MCU Start-up, RESET

V

V

CC

RESET

TIME-OUT

INTERNAL

RESET

POT

V

RST

t

TOUT

Tied to V

CC

2543A–AVR–08/03

35

Page 36

Figure 16. MCU Start-up, RESET Extended Externally

V

V

CC

RESET

TIME-OUT

INTERNAL

RESET

POT

V

RST

t

TOUT

External Reset An External Reset is generated by a low level on the RESET

pin. Reset pulses longer

than the minimum pulse width (see T able 15) will generate a rese t, even if the clock is

not running. Shorter pulses are not guarante ed to generate a reset. When the applied

signal reaches the Reset Threshold Voltage – V

counter starts the MCU after the Time-out period – t

– on its positive edge, the delay

RST

TOUT –

has expired.

Figure 17. External Reset During Operation

CC

Brown-out Detection ATtin y2313 ha s an On-chi p Brown-o ut Detecti on (BOD) cir cuit for mo nitoring the V

level during operation by comparing it to a fixed trigge r level. The trigger level for the

BOD can be selected by the BODLEVEL Fuses. The trigger level has a hysteresis to

ensure spike free Brown-out Detection. The hysteresis on the detection level should be

interpreted as V

BOT+

= V

Table 16. BODLEVEL Fuse Coding

BOT

+ V

HYST

/2 and V

(1)

BOT-

= V

BOT

- V

HYST

/2.

CC

36

ATtiny2313

BODLEVEL 2..0 Fuses Min V

111 BOD Disabled

110 1.8

100 4.3

BOT

Typ V

BOT

Max V

BOT

Units

2543A–AVR–08/03

V101 2.7

Page 37

ATtiny2313

Table 16. BODLEVEL Fuse Coding

BODLEVEL 2..0 Fuses Min V

(1)

BOT

Typ V

BOT

Max V

BOT

Units

011

010

Reserved

001

000

Note: 1. V

may be below nominal minimum operating voltage for some devices. For

BOT

devices where this is the case, the device is tested down to VCC = V

BOT

durin g the

production test. This guarantees that a Brown-Out Reset will occur before VCC drops

to a voltage where correct operation of the microcontroller is no longer guaranteed.

The test is performed using BODLEVEL = 110 for ATtiny2313V and

BODLEVEL = 101 for ATtiny2313L.

Table 17. Brown-out Characteristics

Symbol Parameter Min Typ Max Units

V

HYST

t

BOD

When the BOD is enabled, and VCC decreases to a value below the trigger level (V

Brown-out Detector Hysteresis 50 mV

Min Pulse Width on Brown-out Reset 2 ns

BOT-

in Figure 18), the Brown-out Reset is immediat ely activated. When VCC increases above

the trigger level (V

out period t

has expired.

TOUT

The BOD circuit will only detect a drop in V

for longer than t

BOD

in Figure 18), the delay cou nter starts the M CU after t he Time-

BOT+

if the voltage stays below the trigger level

CC

given in Table 15.

Figure 18. Brown-out Reset During Operation

V

CC

RESET

TIME-OUT

INTERNAL

RESET

V

BOT-

V

BOT+

t