Page 1

Features

• High-performance, Low-power AVR

• RISC Architecture

– 130 Powerful Instructions – Most Single Clock Cycle Execution

– 32x8GeneralPurposeWorkingRegisters

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-chip 2-cycle Multiplier

• Nonvolatile Program and Data Memories

– 8K Bytes of In-System Self-programmable Flash

Endurance: 1,000 Write/Erase Cycles

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

– 512 Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

– 512 Bytes Internal SRAM

– Up to 64K Bytes Optional External Memory Space

– Programming Lock for Software Security

• Peripheral Features

– One 8-bit Timer/Counter with Separate Prescaler and Compare Mode

– One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture

Mode

– Three PWM Channels

– Programmable Serial USART

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator

– On-chip Analog Comparator

• Special Microcontroller Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Three Sleep Modes: Idle, Power-down and Standby

• I/O and Packages

– 35 Programmable I/O Lines

– 40-pin PDIP, 44-lead TQFP, 44-lead PLCC, and 44-pad MLF

• Operating Voltages

– 2.7 - 5.5V for ATmega8515L

– 4.5 - 5.5V for ATmega8515

• Speed Grades

– 0 - 8 MHz for ATmega8515L

– 0 - 16 MHz for ATmega8515

®

8-bit Microcontroller

8-bit

Microcontroller

with 8K Bytes

In-System

Programmable

Flash

ATmega8515

ATmega8515L

Preliminary

Rev. 2512A–AVR–04/02

1

Page 2

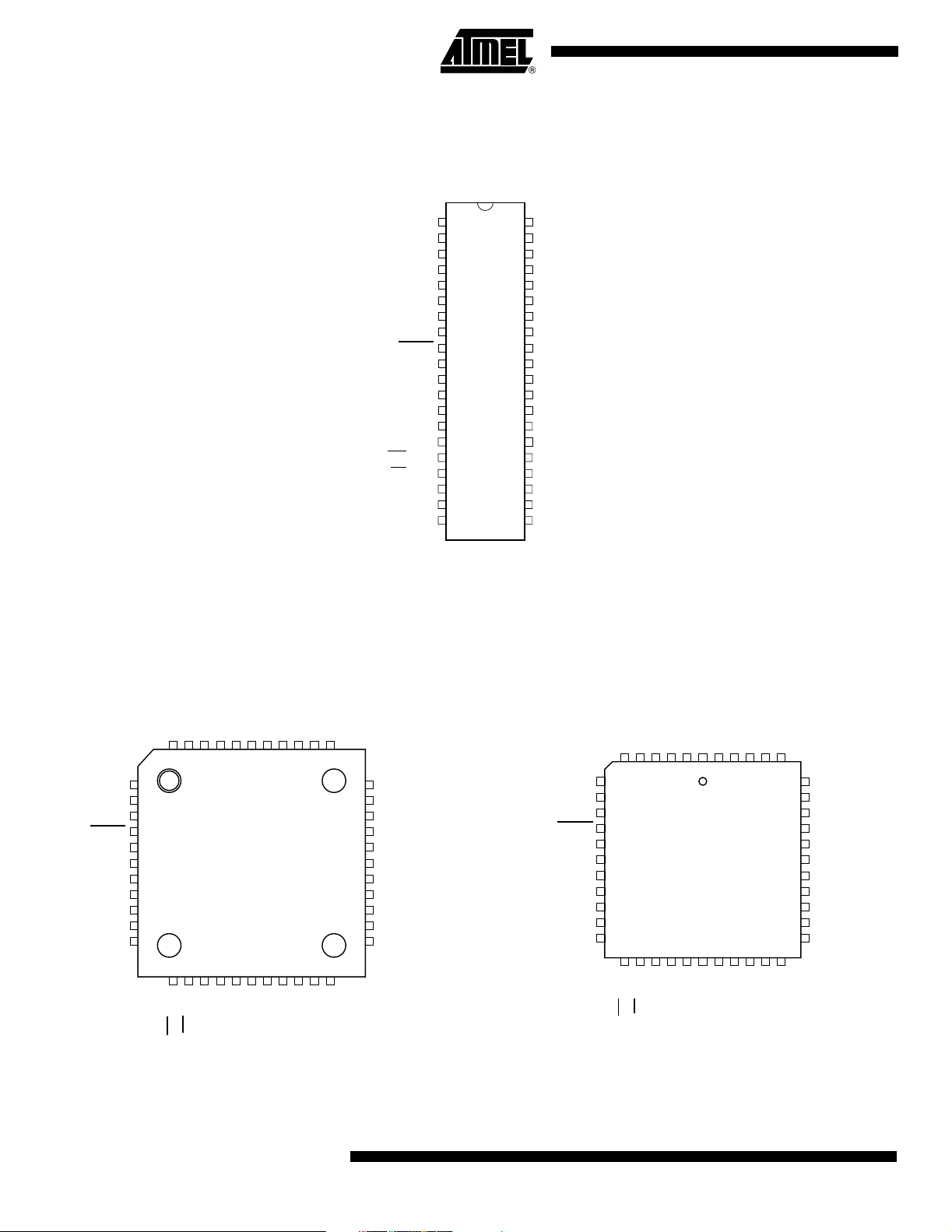

Pin Configurations

Figure 1. Pinout ATmega8515

PDIP

TQFP/MLF

(OC0/T0) PB0

(T1) PB1

(AIN0) PB2

(AIN1) PB3

(SS) PB4

(MOSI) PB5

(MISO) PB6

(SCK) PB7

RESET

(RXD) PD0

(TDX) PD1

(INT0) PD2

(INT1) PD3

(XCK) PD4

(OC1A) PD5

(WR) PD6

(RD) PD7

XTAL2

XTAL1

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

VCC

39

PA0 (AD0)

38

PA1 (AD1)

37

PA2 (AD2)

36

PA3 (AD3)

35

PA4 (AD4)

34

PA5 (AD5)

33

PA6 (AD6)

32

PA7 (AD7)

31

PE0 (ICP/INT2)

30

PE1 (ALE)

29

PE2 (OC1B)

28

PC7 (A15)

27

PC6 (A14)

26

PC5 (A13)

25

PC4 (A12)

24

PC3 (A11)

23

PC2 (A10)

22

PC1 (A9)

21

PC0 (A8)

PLCC

(MOSI) PB5

(MISO) PB6

(SCK) PB7

RESET

(RXD) PD0

(TXD) PD1

(INT0) PD2

(INT1) PD3

(XCK) PD4

(OC1A) PD5

2

PB4 (SS)

PB3 (AIN1)

PB2 (AIN0)

PB1 (T1)

PB0 (OC0/T0)

NC*

VCC

4443424140393837363534

1

2

3

4

5

6

NC*

7

8

9

10

11

1213141516171819202122

NC*

GND

XTAL2

(RD) PD7

(WR) PD6

XTAL1

(A8) PC0

ATmega8515(L)

PA0 (AD0)

PA1 (AD1)

PA2 (AD2)

(A9) PC1

(A10) PC2

(A11) PC3

PA3 (AD3)

33

32

31

30

29

28

27

26

25

24

23

(A12) PC4

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PE0 (ICP/INT2)

NC*

PE1 (ALE)

PE2 (OC1B)

PC7 (A15)

PC6 (A14)

PC5 (A13)

* NC= Do not connect

(May be used in future devices)

(MOSI) PB5

(MISO) PB6

(SCK) PB7

RESET

(RXD) PD0

NC*

(TXD) PD1

(INT0) PD2

(INT1) PD3

(XCK) PD4

(OC1A) PD5

PB4 (SS)

PB3 (AIN1)

PB2 (AIN0)

PB1 (T1)

PB0 (OC0/T0)

NC*

VCC

PA0 (AD0)

65432

7

8

9

10

11

12

13

14

15

16

17

1819202122232425262728

XTAL2

(RD) PD7

(WR) PD6

GND

XTAL1

1

4443424140

NC*

(A8) PC0

(A9) PC1

PA1 (AD1)

PA2 (AD2)

PA3 (AD3)

39

38

37

36

35

34

33

32

31

30

29

(A10) PC2

(A11) PC3

(A12) PC4

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PE0 (ICP/INT2)

NC*

PE1 (ALE)

PE2 (OC1B)

PC7 (A15)

PC6 (A14)

PC5 (A13)

2512A–AVR–04/02

Page 3

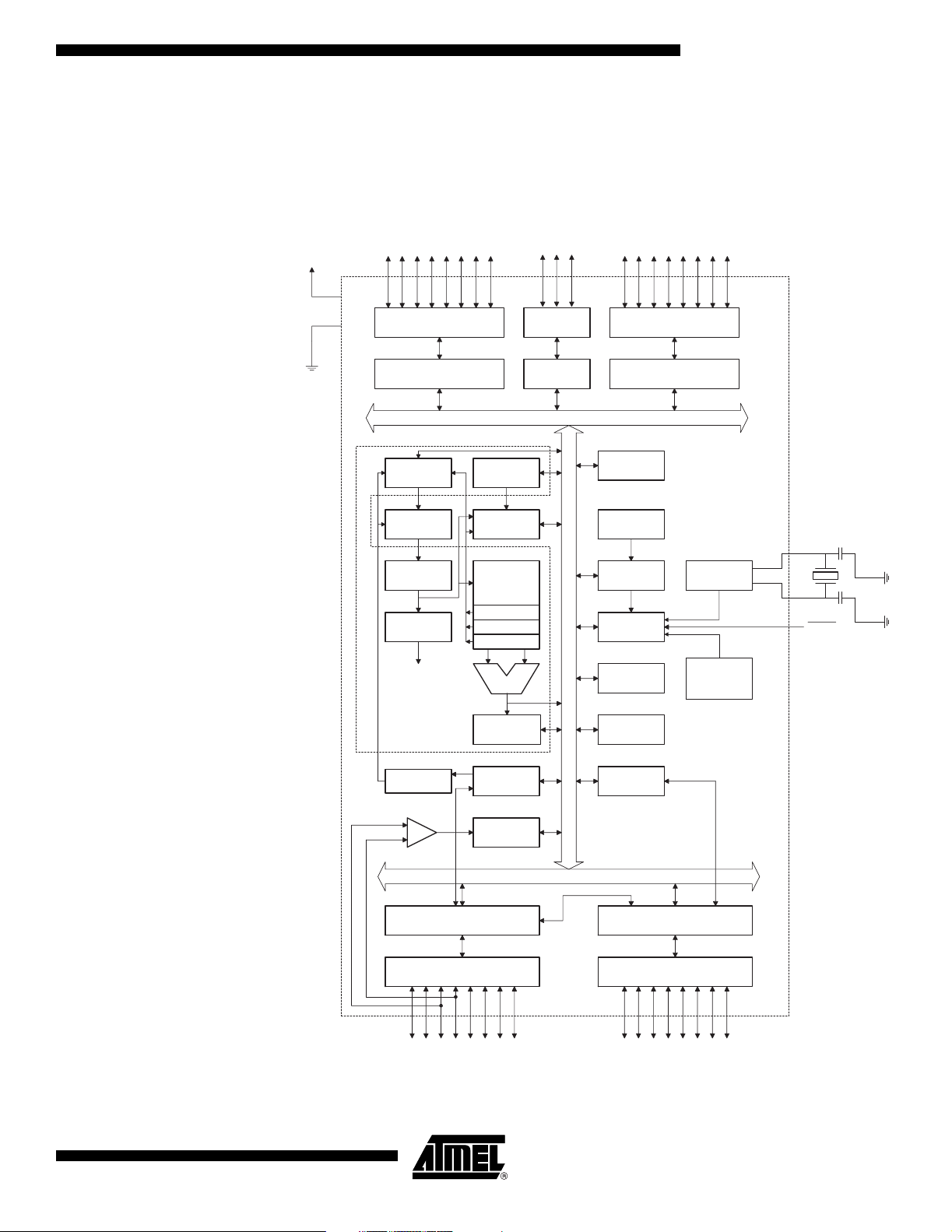

ATmega8515(L)

Overview The ATmega8515 is a low-powerCMOS8-bit microcontrollerbas ed on theAVR

enhanced RISC architecture. By executing powerful instructions in a single clock cycle,

the ATmega8515 achieves throughputs approaching 1 MIPSperMHzallowing the sys-

tem designer to optimize powerconsumption versusprocessing speed.

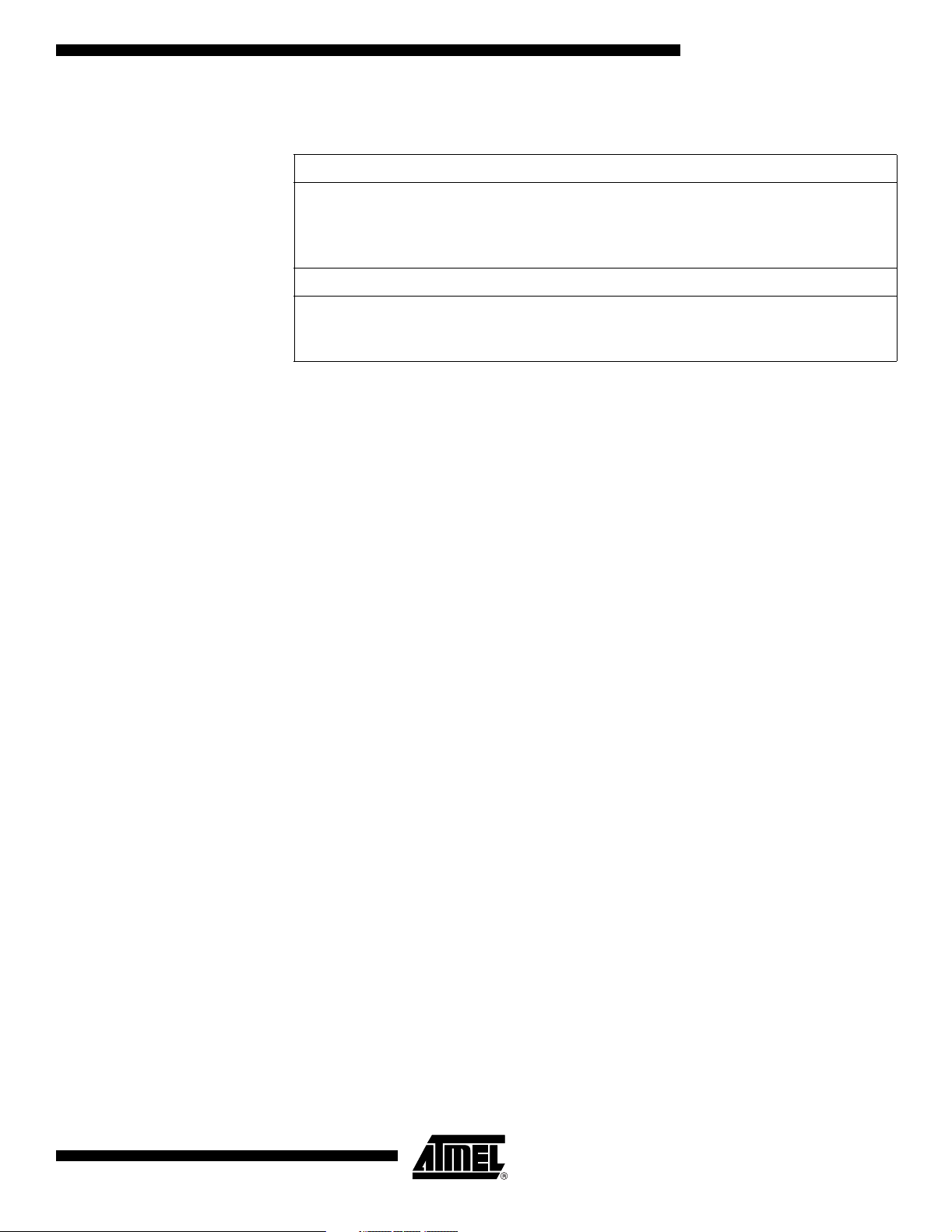

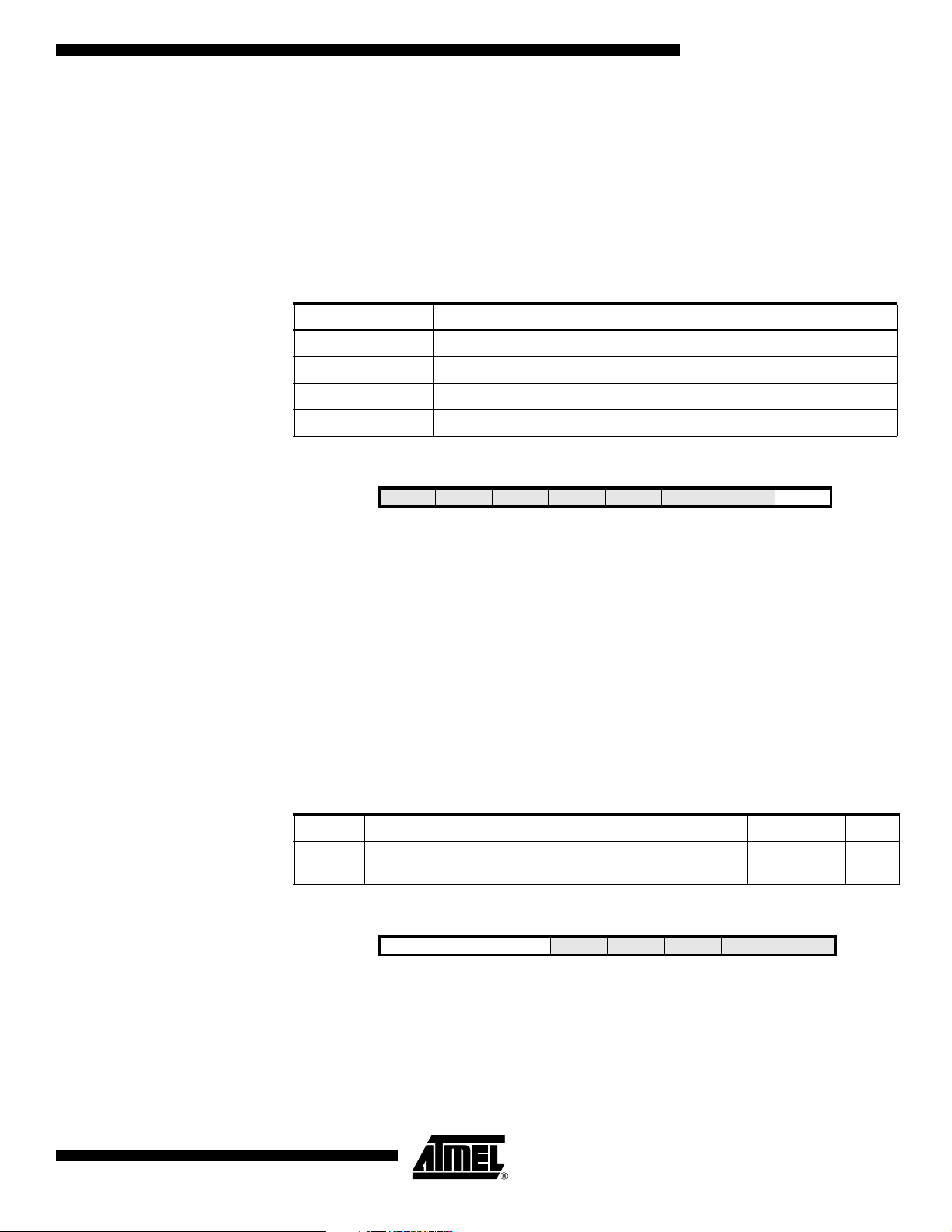

Block Diagram Figure 2. Block Diagram

VCC

PA0 - PA7 PC0 - PC7

PORTA DRIVERS/BUFFERS

PE0 - PE2

PORTE

DRIVERS/

BUFFERS

PORTC DRIVERS/BUFFERS

GND

PORTA DIGITAL INTERFACE

PROGRAM

COUNTER

PROGRAM

FLASH

INSTRUCTION

REGISTER

INSTRUCTION

DECODER

CONTROL

LINES

AVR CPU

PROGRAMMING

LOGIC

STACK

POINTER

SRAM

GENERAL

PURPOSE

REGISTERS

X

Y

Z

ALU

STATUS

REGISTER

SPI

PORTE

DIGITAL

INTERFACE

PORTC DIGITAL INTERFACE

TIMERS/

COUNTERS

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

MCU CTRL.

& TIMING

INTERRUPT

UNIT

EEPROM

USART

OSCILLATOR

INTERNAL

CALIBRATED

OSCILLATOR

XTAL1

XTAL2

RESET

2512A–AVR–04/02

+

-

PORTB DIGITAL INTERFACE

PORTB DRIVERS/BUFFERS

COMP.

INTERFACE

PORTD DIGITAL INTERFACE

PORTD DRIVERS/BUFFERS

PD0 - PD7PB0 - PB7

3

Page 4

TheAVRcore combines a rich instruction set with32 generalpurpose working registers.

All the 32 registers are directly connected to theArithmeticLogicUnit (ALU), allowing

twoindependent registers to beaccessed in one singleinstruction executed in one clock

cycle. The resulting architectureis more codeefficient whileachieving throughputs up to

ten timesfaster than conventionalCISCmicrocontrollers.

The ATmega8515 provides the following features: 8Kbytes ofIn-System Programmable

Flash with Read-While-Write capabilities, 512 bytesEEPROM, 512 bytesSRAM, an

External memory interface,35generalpurpose I/Olines, 32generalpurpose working

registers, two flexibleTimer/Counters withcomparemodes, Internal andExternal inter-

rupts, a Serial Programmable USART, a programmable Watchdog Timerwith internal

Oscillator, a SPIserialport, and three software selectable powersaving modes.The Idle

mode stops the CPUwhileallowing the SRAM, Timer/Counters, SPIport, andInterrupt

system to continue functioning. ThePower-downmode saves the Registercontentsbut

freezes the Oscillator, disabling all otherchipfunctions until thenextinterruptorhard-

ware reset. In Standby mode, the crystal/resonatorOscillator isrunning whilethe restof

th e deviceissleeping. This allows very fast start -upcombinedwithlow-power

consumption.

The deviceis manufactured using Atmel’shighdensity nonvolatilememory technology.

The On-chipISP Flash allows the program memory to be reprogrammedIn-System

through an SPIserial interface,bya conventional nonvolatilememory programmer, or

by an On-chipBoot program running on the AVR core. The boot program can useany

interfacetodownload theapplication program in theApplication Flash memory. Soft-

wareinthe Boot Flash section will continue to run whiletheApplication Flash section is

updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU

withIn-System Self-programmable Flash onamonolithicchip, theAtmel ATmega8515

is a powerful microcontroller that provides a highly flexibleandcosteffective solution to

many embeddedcontrol applications.

The ATmega8515 issupportedwith a full suite ofprogram andsystem development

tools including:CCompilers, Macroassemblers, Program debugger/simulators, In-cir-

cuit Emulators, andEvaluation kits.

Disclaimer Typical valuescontained in thisdata sheet are based on simulations andcharacteriza-

tion of other AVR microcontrollers manufactured on the same process technology. Min

andMax valueswill beavailableafter the deviceischaracterized.

AT90S4414/8515 and ATmega8515 Compatibility

AT90S4414/8515 Compatibility Mode

The ATmega8515 provides all the features of theAT90S4414/8515. Inaddition,several

newfeature s a readded .The ATmega8515 isba ckward comp atible with

AT90S4414/8515 in most cases. However, some incompatibilitiesbetween thetwo

microcontrollers exist. To solve thisproblem, an AT90S4414/8515 compatibility mode

can be selectedbyprogramming the S8515CFuse. ATmega8515 is 100%pin compatible with AT90S4414/8515, andcan replacetheAT90S4414/8515 on current printed

circuit boards. However, the location ofFuse bits and theelectricalcharacteristics differs between thetwo devices.

Programming the S8515CFuse will change the following functionality:

•Thetimedsequence forchanging the Watchdog Time-out period isdisabled. See

“TimedSequencesforChanging the Configuration of the Watchdog Timer”onpage

50 fordetails.

•The double buffering of the USART receive registers isdisabled. See “AVR USART

vs. AVR UART – Compatibility”onpage 133 fordetails.

•PORTE(2:1)will be set as output, and PORTE0 will be set as input.

4

ATmega8515(L)

2512A–AVR–04/02

Page 5

ATmega8515(L)

Pin Descriptions

VCC Digitalsupply voltage.

GND Ground.

Port A (PA7..PA0) PortAis an 8-bit bi-directionalI/Oport with internalpull-upresistors (selectedfor each

bit).ThePort A output buffers have symmetricaldrive characteristics withbothhighsink

andsource capability. When pins PA0toPA7 areused as inputs and areexternally

pulledlow, theywill source current if theinternalpull-upresistors areactivated.ThePort

A pins aretri-statedwhen a reset condition becomes active, even if the clock is not

running.

PortAalso serves the functions of variousspecialfeatures of the ATmega8515 aslisted

on page 64.

Port B (PB7..PB0) Port B is an 8-bit bi-directionalI/Oport with internalpull-upresistors (selectedfor each

bit).ThePort B output buffers have symmetricaldrive characteristics withbothhighsink

andsource capability.As inputs, Port Bpins that areexternally pulledlowwill source

current if the pull-upresistors areactivated.ThePort Bpins aretri-statedwhen a reset

condition becomes active, even if the clock is not running.

Port B also serves the functions of variousspecialfeatures of the ATmega8515 aslisted

on page 64.

Port C (PC7..PC0) Port C is an 8-bit bi-directionalI/Oport with internalpull-upresistors (selectedfor each

bit).ThePort C output buffers have symmetricaldrive characteristics withbothhighsink

andsource capability.As inputs, Port Cpins that areexternally pulledlowwill source

current if the pull-upresistors areactivated.ThePort Cpins aretri-statedwhen a reset

condition becomes active, even if the clock is not running.

Port D (PD7..PD0) Port D is an 8-bit bi-directionalI/Oport with internalpull-upresistors (selectedfor each

bit).ThePort D output buffers have symmetricaldrive characteristics withbothhighsink

andsource capability.As inputs, Port Dpins that areexternally pulledlowwill source

current if the pull-upresistors areactivated.ThePort Dpins aretri-statedwhen a reset

condition becomes active, even if the clock is not running.

Port D also serves the functions of variousspecialfeatures of the ATmega8515 aslisted

on page 69.

Port E(PE2..PE0) Port E is an 3-bit bi-directionalI/Oport with internalpull-upresistors (selectedfor each

bit).ThePort E output buffers have symmetricaldrive characteristics withbothhighsink

andsource capability.As inputs, Port Epins that areexternally pulledlowwill source

current if the pull-upresistors areactivated.ThePort Epins aretri-statedwhen a reset

condition becomes active, even if the clock is not running.

Port E also serves the functions of variousspecialfeatures of the ATmega8515 aslisted

on page 71.

RESET

XTA L1 Input to theinverting Oscillator amplifier and input to theinternalclock operating circuit.

XTA L2 Output from theinverting Oscillator amplifier.

2512A–AVR–04/02

Reset input. A lowlevel on thispin forlonger than the minimum pulse lengthwill gener-

ate a reset, even if the clock is not running. Theminimumpulse length is given in Table

18 on page 43. Shorterpulses are not guaranteed to generate a reset.

5

Page 6

About Code Examples

Thisdocumentation containssimple codeexamples that briefly showhow to usevarious

parts of the device. These codeexamples assume that the part specificheaderfileis

includedbefore compilation. Beawarethat not all C Compiler vendors include bit defini-

tions in the headerfiles and interrupt handling in C iscompilerdependent. Please

confirm with the CCompilerdocumentation for more details.

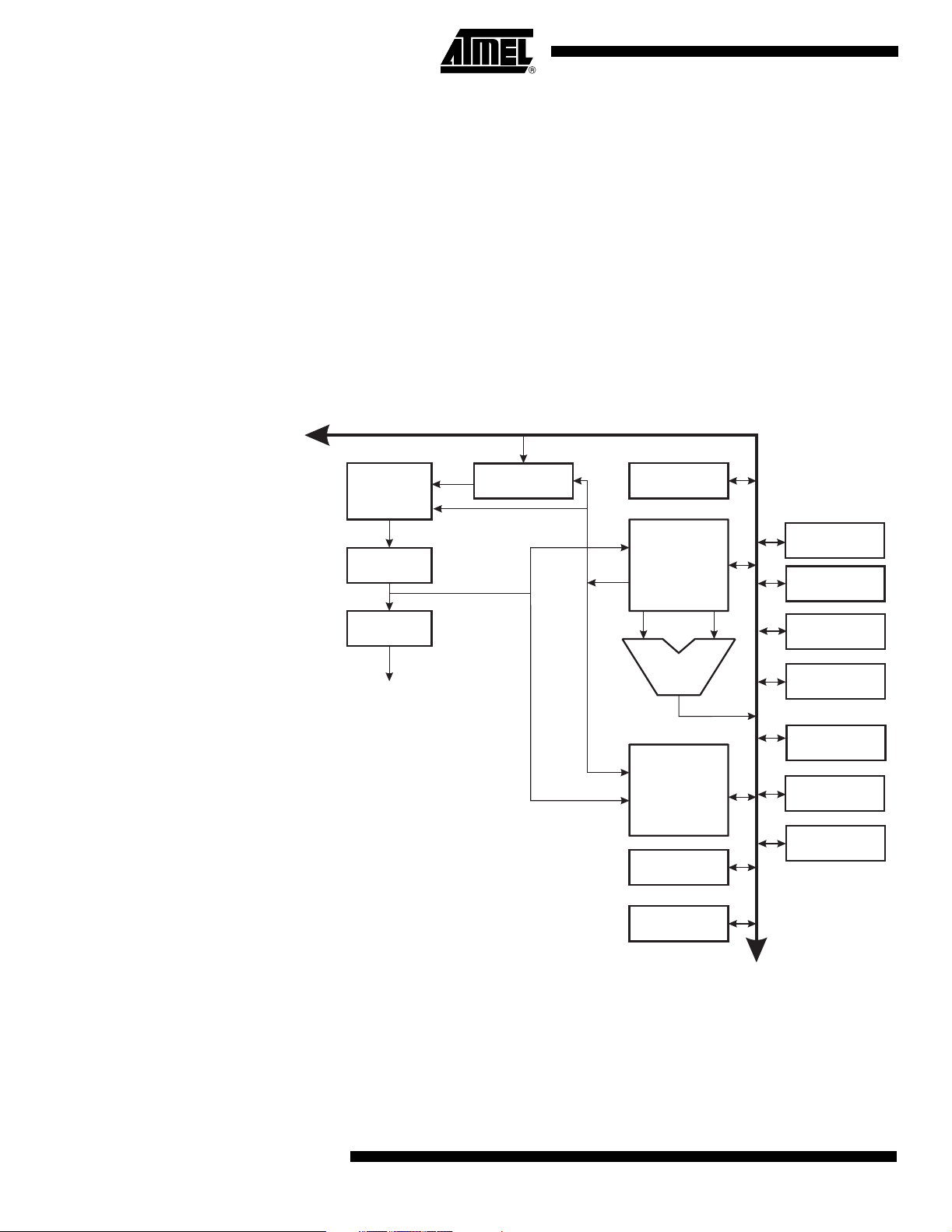

AVR CPU Cor e

Introduction Thissection discusses the AVR corearchitectureingeneral.Themainfunction of the

CPUcoreis to ensure correct program execution. The CPU musttherefore beableto

access memories, perform calculations, controlperipherals, andhandleinterrupts.

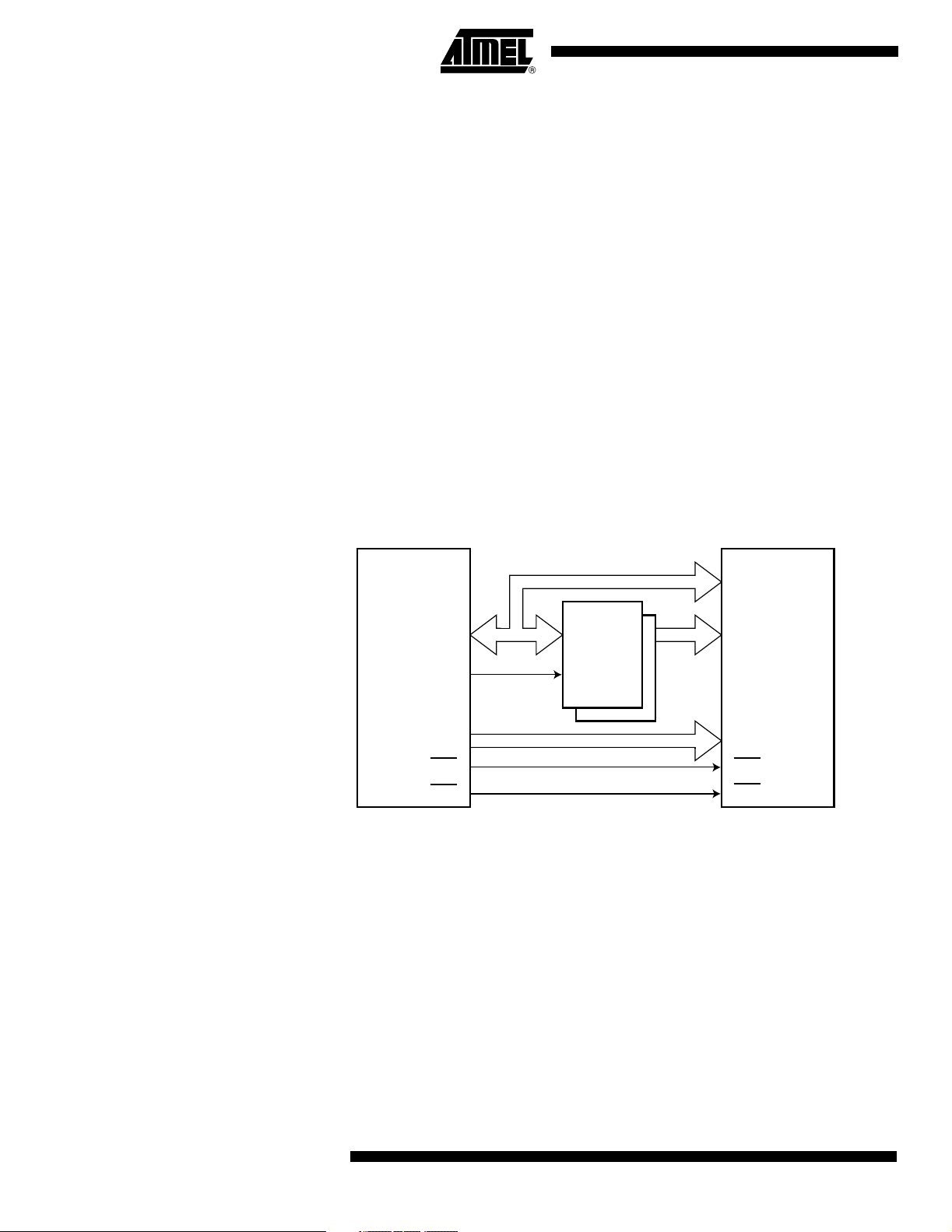

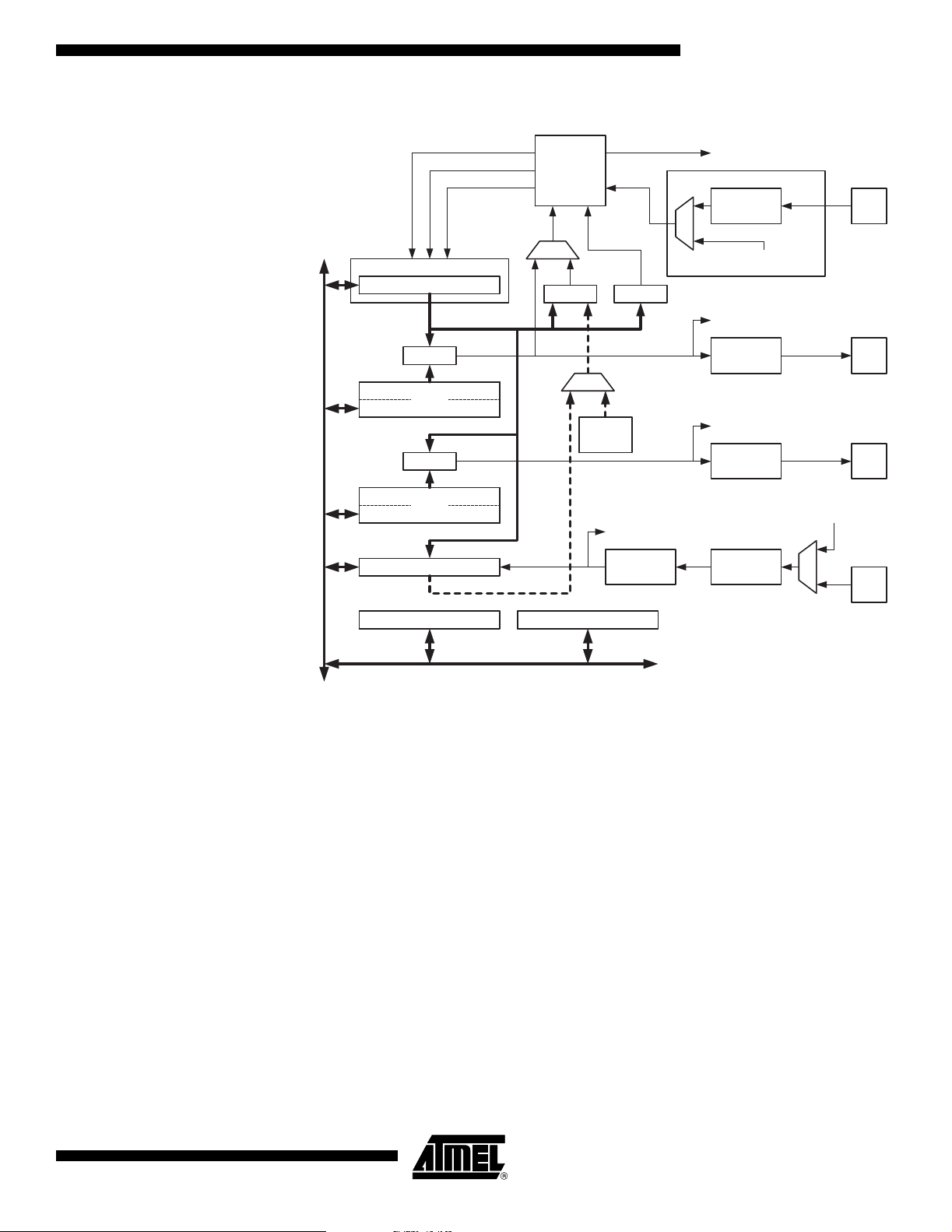

Architectural Overview Figure 3. Block Diagram of theAVRArchitecture

Data Bus 8-bit

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Control Lines

Program

Counter

Direct Addressing

Indirect Addressing

Status

and Control

32x8

General

Purpose

Registrers

ALU

Data

SRAM

EEPROM

Interrupt

Unit

SPI

Unit

Watchdog

Timer

Analog

Comparator

I/O Module1

I/O Module 2

I/O Module n

I/O Lines

Inorder to maximize performanceandparallelism, the AVR uses a Harvard architecture

– withseparate memories andbusesforprogram anddata. Instructions in the program

memory areexecutedwith a single levelpipelining. Whileoneinstruction isbeing exe-

cuted, thenextinstruction ispre-fetchedfrom the program memory.Thisconcept

enables instructions to beexecuted in every clock cycle. The program memory isIn-

System reprogrammable Flash memory.

6

ATmega8515(L)

2512A–AVR–04/02

Page 7

ATmega8515(L)

The fast-access RegisterFile contains32 x 8-bit generalpurpose working registers with

a single clock cycleaccess time. This allows single-cycleArithmeticLogicUnit (ALU)

operation. Inatypical ALU operation, twooperands areoutput from theRegisterFile,

theoperation is executed, and the resultisstoredback in the RegisterFile – in one

clock cycle.

Six of the 32 registers can beused as three 16-bit indirectaddress registerpointers for

Data Spaceaddressing – enabling efficient address calculations. One of thethese

address pointers can also beused as an address pointerforlook up tables in Flash pro-

gram memory.Theseaddedfunction registers arethe16-bit X-, Y-, andZ-register,

describedlater in thissection.

TheALU supports arithmetic andlogic operationsbetween registers orbetween a con-

stant and a register. Single register operationscan also beexecuted in theALU.After

an arithmetic operation, the Status Register is updated to reflectinformation about the

resultof theoperation.

Program flow isprovidedbyconditional and unconditionaljump andcall instructions,

abletodirectly address the wholeaddress space. Most AVR instructionshave a single

16-bit word format. Every program memory address contains a16- or32-bit instruction.

Program Flash memory spaceisdivided in two sections, the Boot Program section and

theApplication Program section. Bothsectionshave dedicatedLock bitsforwrite and

read/write protection. The SPM instruction that writes into theApplication Flash memory

section must resideinthe Boot Program section.

ALU – Arithmetic Logic Unit

During interrupts andsubroutine calls, the returnaddress program counter(PC) is

stored on the Stack.The Stack is effectively allocated in thegeneraldata SRAM, and

consequently the stack sizeis only limitedbythetotalSRAMsizeand theusage of the

SRAM.All userprograms mustinitializethe SPinthe reset routine (before subroutines

or interrupts areexecuted).The Stack PointerSPisread/write accessibleinthe I/O

space. The data SRAMcan easily beaccessed through the five different addressing

modessupported in the AVR architecture.

Thememory spaces in theAVRarchitectureareall linear andregular memory maps.

A flexibleinterruptmodule has itscontrolregisters in the I/Ospace with an additional

GlobalInterrupt Enable bit in the Status Register.All interruptshave a separate interrupt

vector in the InterruptVector table. Theinterruptshave priority in accordance with their

InterruptVectorposition. The lower the InterruptVector address, the higher the priority.

The I/O memory space contains64addressesforCPUperipheralfunctions asControl

Registers, SPI, and otherI/Ofunctions.The I/OMemory can beaccesseddirectly, or as

the Data Space locationsfollowing thoseof the RegisterFile,$20 -$5F.

The high-performance AVR ALU operates in direct connection with all the 32general

purpose working registers. Within a single clock cycle, arithmetic operationsbetween

generalpurpose registers orbetween a register and an immediate areexecuted.The

ALU operations are divided into three main categories –arithmetic, logical, andbit-func-

tions. Some implementations of thearchitecturealso provideapowerful multiplier

supporting bothsigned/unsigned multiplication andfractionalformat. See the“Instruc-

tion Set” section for a detaileddescription.

2512A–AVR–04/02

7

Page 8

Status Register The Status Registercontains information about the resultof themost recently executed

arithmetic instruction. This information can beusedfor altering program flow in order to

perform conditional operations. Note that the statusregister is updated after all ALU

operations, asspecified in the Instruction Set Reference. Thiswill in manycases

remove theneedfor using the dedicatedcompareinstructions, resulting in faster and

more compact code.

The statusregister is not automatically storedwhen enteringaninterrupt routine and

restoredwhen returning from an interrupt. This must be handledbysoftware.

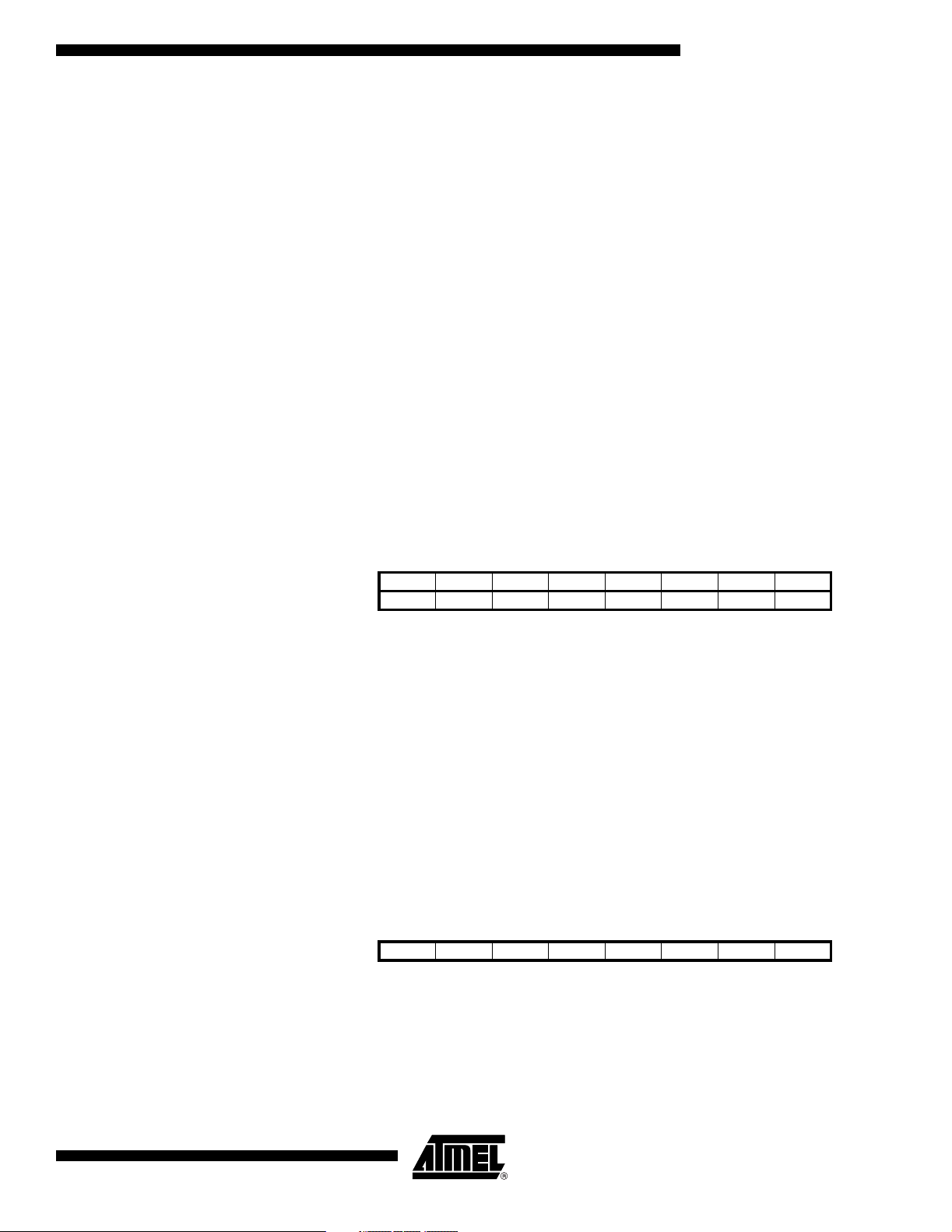

TheAVRstatusregister – SREG –isdefined as:

Bit 76543 210

I THSVNZ CSREG

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bit 7 – I: Global Interrupt Enable

The GlobalInterrupt Enable bit must be set for theinterrupts to be enabled.Theindivid-

ual interrupt enable control is then performed in separate controlregisters. If theglobal

interruptenable register iscleared, none of theinterrupts areenabled independent of

theindividual interrupt enable settings.The I-bit isclearedbyhardwareafter an interrupt

has occurred, and isset by theRETI instruction to enable subsequent interrupts.The I-

bit can also be set andclearedbytheapplication with the SEI andCLIinstructions, as

described in theinstruction set reference.

• Bit 6 – T: Bit Copy Storage

The Bit Copy instructionsBLD(Bit LoaD) andBST (Bit STore) usetheT-bit assourceor

destination for theoperatedbit. A bit from a register in theRegisterFile can be copied

into T by the BSTinstruction, and a bit in T can be copied into a bit in a register in the

RegisterFile by the BLD instruction.

• Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a half carry in some arithmetic operations. Half Carry is

useful in BCD arithmetic. See the“Instruction Set Description” fordetailed information.

• Bit 4 – S: Sign Bit, S = N

⊕ V

The S-bit is always an exclusive orbetween the negative flag N and thetwo’scomple-

ment overflowflag V. See the“Instruction Set Description” fordetailed information.

• Bit 3 – V: Two’s Complement Overflow Flag

TheTwo’sComplement OverflowFlag V supports two’scomplement arithmetics. See

the“Instruction Set Description” fordetailed information.

• Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative resultinanarithmetic orlogic operation. See

the“Instruction Set Description” fordetailed information.

•Bit1–Z: Zero Flag

The Zero Flag Z indicates a zero resultinanarithmetic orlogic operation. See the

“Instruction Set Description” fordetailed information.

8

ATmega8515(L)

2512A–AVR–04/02

Page 9

ATmega8515(L)

• Bit0–C:CarryFlag

The Carry Flag C indicates a carry in an arithmetic orlogic operation. See the“Instruc-

tion Set Description” fordetailed information.

General Purpose Register File

TheRegisterFileis optimizedfor the AVR Enhanced RISC instruction set. Inorder to

achieve the requiredperformanceandflexibility, the following input/output schemes are

supportedbythe RegisterFile:

• One 8-bit output operand and one 8-bit resultinput

•Two8-bit output operands and one 8-bit resultinput

•Two8-bit output operands and one 16-bit resultinput

• One 16-bit output operand and one 16-bit resultinput

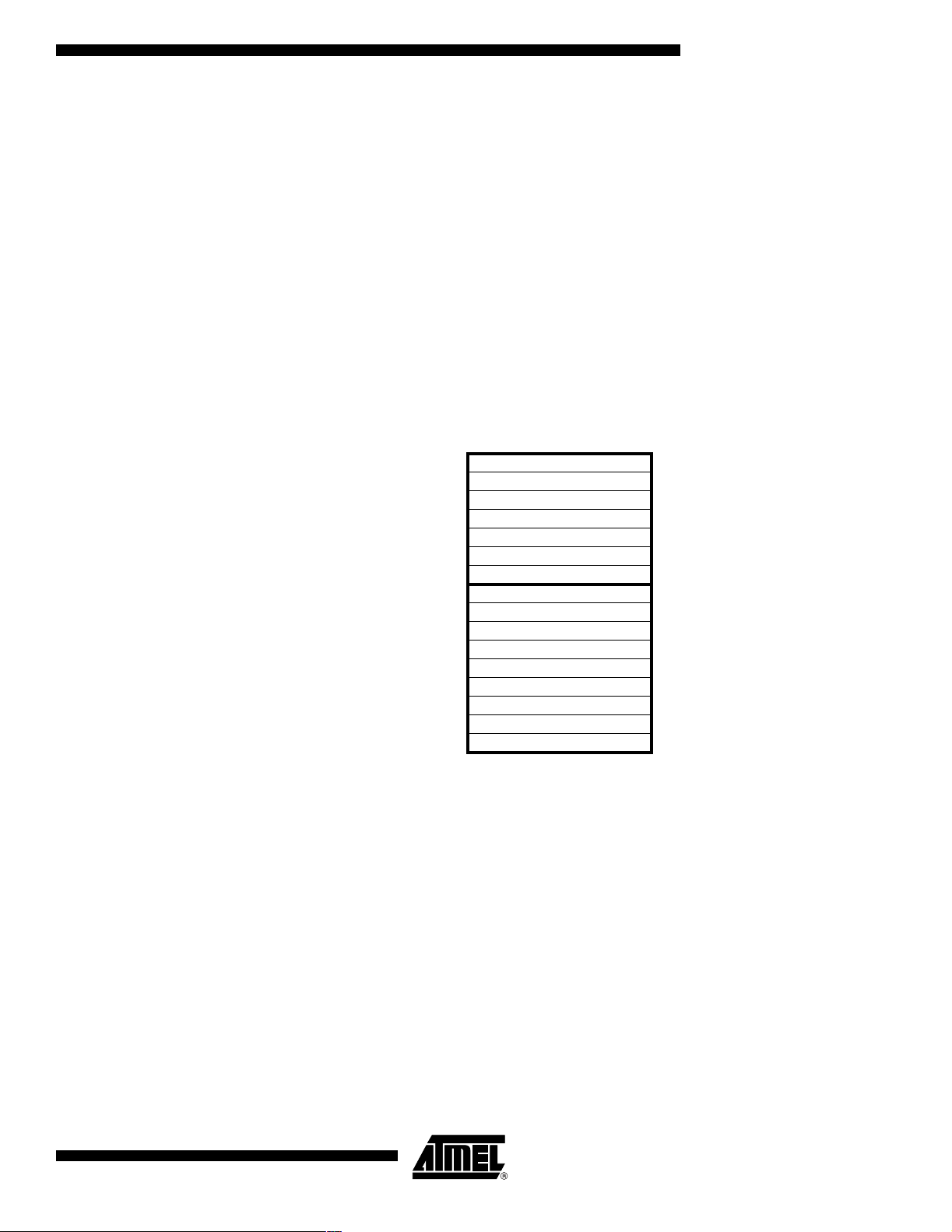

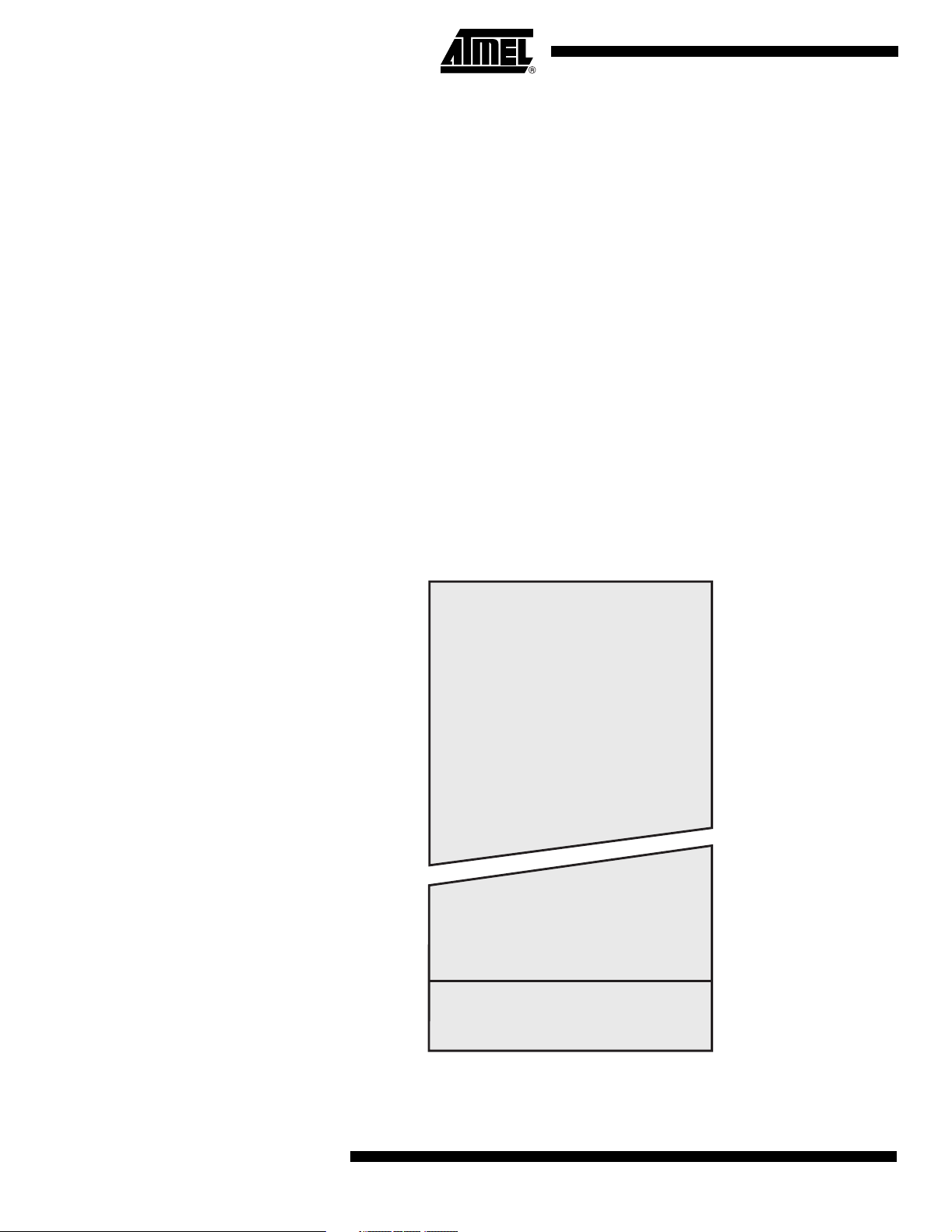

Figure4shows the structureof the 32 generalpurpose working registers in the CPU.

Figure 4. AVR CPUGeneral Purpose Working Registers

7 0Addr.

R0 $00

R1 $01

R2 $02

…

R13$0D

General R14 $0E

PurposeR15$0F

Working R16$10

Registers R17$11

…

R26$1A X-registerLowByte

R27$1BX-registerHighByte

R28 $1CY-registerLowByte

R29$1DY-registerHighByte

R30 $1EZ-registerLowByte

R31 $1FZ-registerHighByte

2512A–AVR–04/02

Mostof theinstructions operatingonthe RegisterFile have directaccess to all registers,

and mostof them are single cycleinstructions.

AsshowninFigure4, each register is alsoassigned a data memory address, mapping

them directly into the first 32 locations of theuserData Space. Although not being phys-

ically implemented asSRAMloc ations, this memory organization provides great

flexibility in access of the registers, as the X-, Y-, andZ-pointer Registers can be set to

index anyregister in the file.

9

Page 10

The X-register, Y-register, and Z-register

The registers R26..R31 have some addedfunctions to their generalpurposeusage.

These registers are16-bit address pointers for indirectaddressing of the Data Space.

Thethree indirectaddress registers X, Y, andZare defined asdescribed in Figure5.

Figure 5. The X-, Y-, andZ-registers

15 XH XL 0

X-register 7 0 7 0

R27($1B) R26($1A)

15 YH YL 0

Y-register 7 0 7 0

R29($1D) R28 ($1C)

15 ZH ZL 0

Z-register 7 0 7 0

R31 ($1F) R30 ($1E)

Inthe different addressing modes theseaddress registers have functions asfixeddis-

placement, automatic increment, and automaticdecrement (see the Instruction Set

reference fordetails).

Stack Pointer The Stack is mainly usedforstoring temporary data,forstoring local variables andfor

storing returnaddresses after interrupts andsubroutine calls.The Stack Pointer Regis-

ter always points to thetop of the stack. Note that the Stack is implemented as growing

from higher memory locations to lower memory locations.This implies that a stack

PUSH commanddecreases the Stack Pointer.

The Stack Pointerpoints to the data SRAMstack area wherethe Subroutine andInter-

rupt Stacks are located.ThisStack spaceinthe data SRAM must be definedbythe

program beforeanysubroutine calls areexecuted or interrupts areenabled.The Stack

Pointer must be set to point above $60. The Stack Pointer isdecrementedbyone when

data ispushed onto the Stack with thePUSH instruction, and it isdecrementedbytwo

when the returnaddress ispushed onto the Stack withsubroutine call or interrupt. The

Stack Pointer is incrementedbyone when data ispoppedfrom the Stack with thePOP

instruction, and it is incrementedbytwo when address ispoppedfrom the Stack with

return from subroutine RETorreturn from interruptRETI.

The AVR Stack Pointer is implemented as two8-bit registers in the I/Ospace. The num-

ber ofbits actually used is implementation dependent. Note that the data spaceinsome

implementations of theAVRarchitectureisso small that only SPL is needed. Inthis

case, the SPH Registerwill not be present.

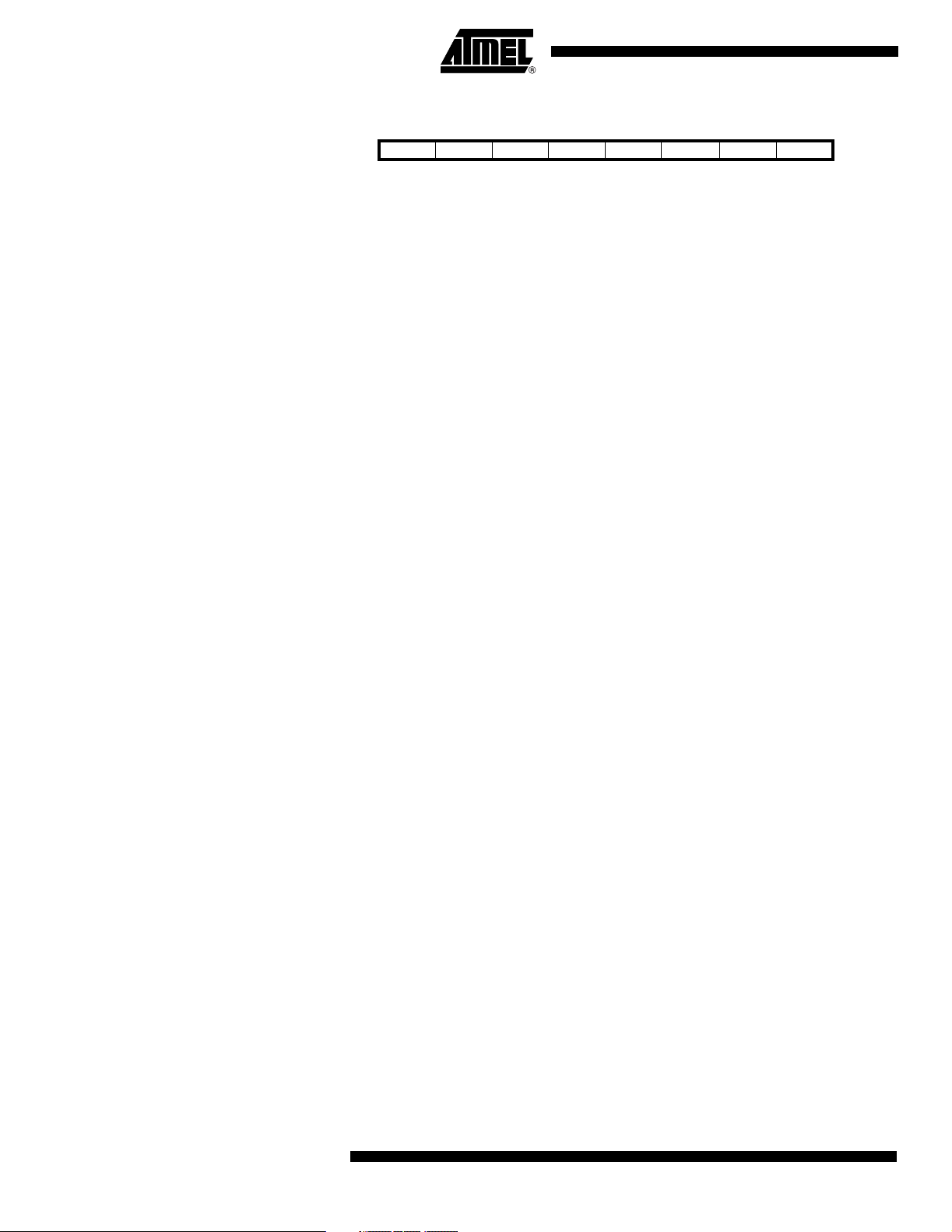

Bit 15 14 13 12 11 10 9 8

SP15 SP14 SP13 SP12 SP11 SP10 SP9 SP8 SPH

SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 SPL

76543 210

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

00000000

10

ATmega8515(L)

2512A–AVR–04/02

Page 11

ATmega8515(L)

Instruction Execution Timing

Thissection describes the general access timing conceptsfor instruction execution. The

AVR CPU isdriven by the CPUclock clk

,directly generatedfrom the selectedclock

CPU

source for the chip. Nointernalclock division is used.

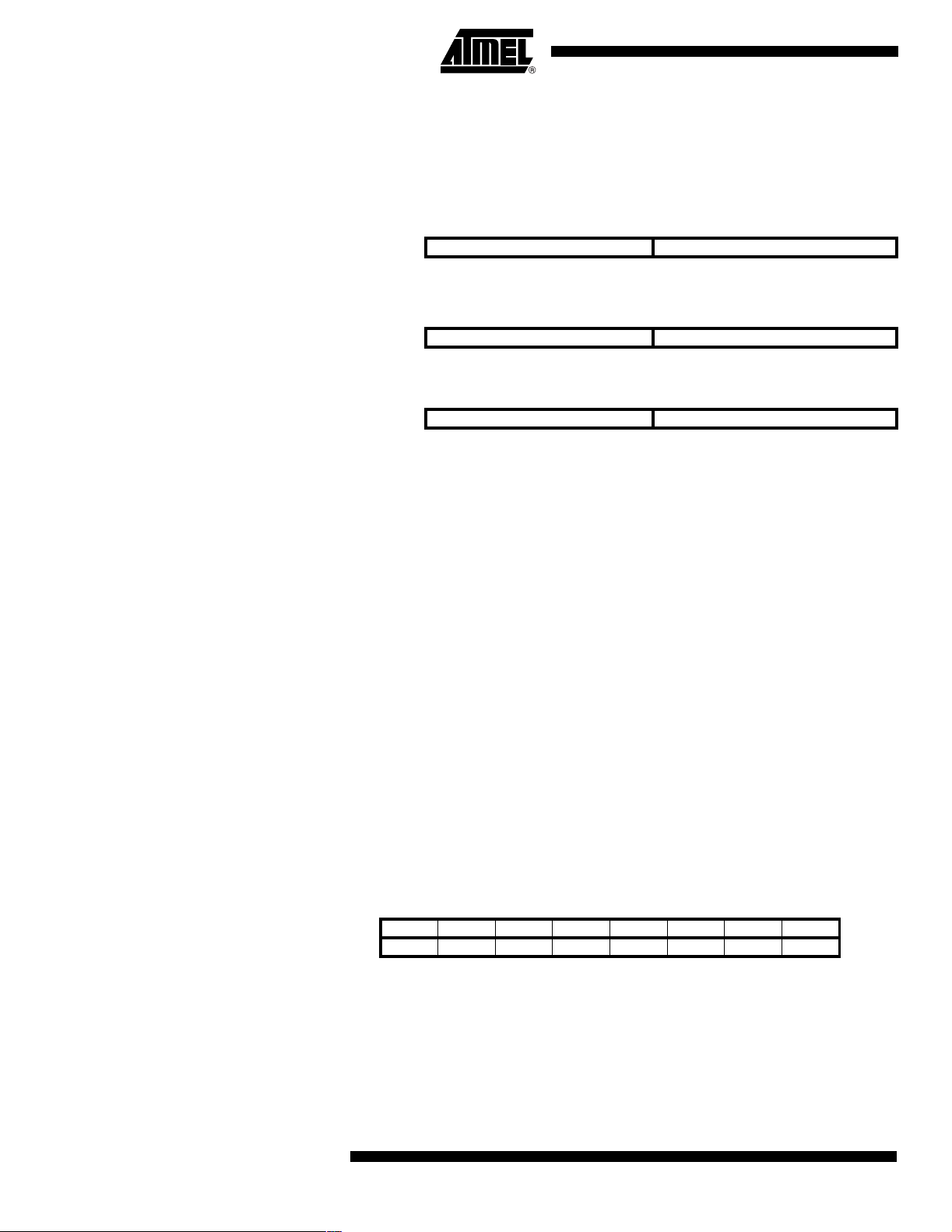

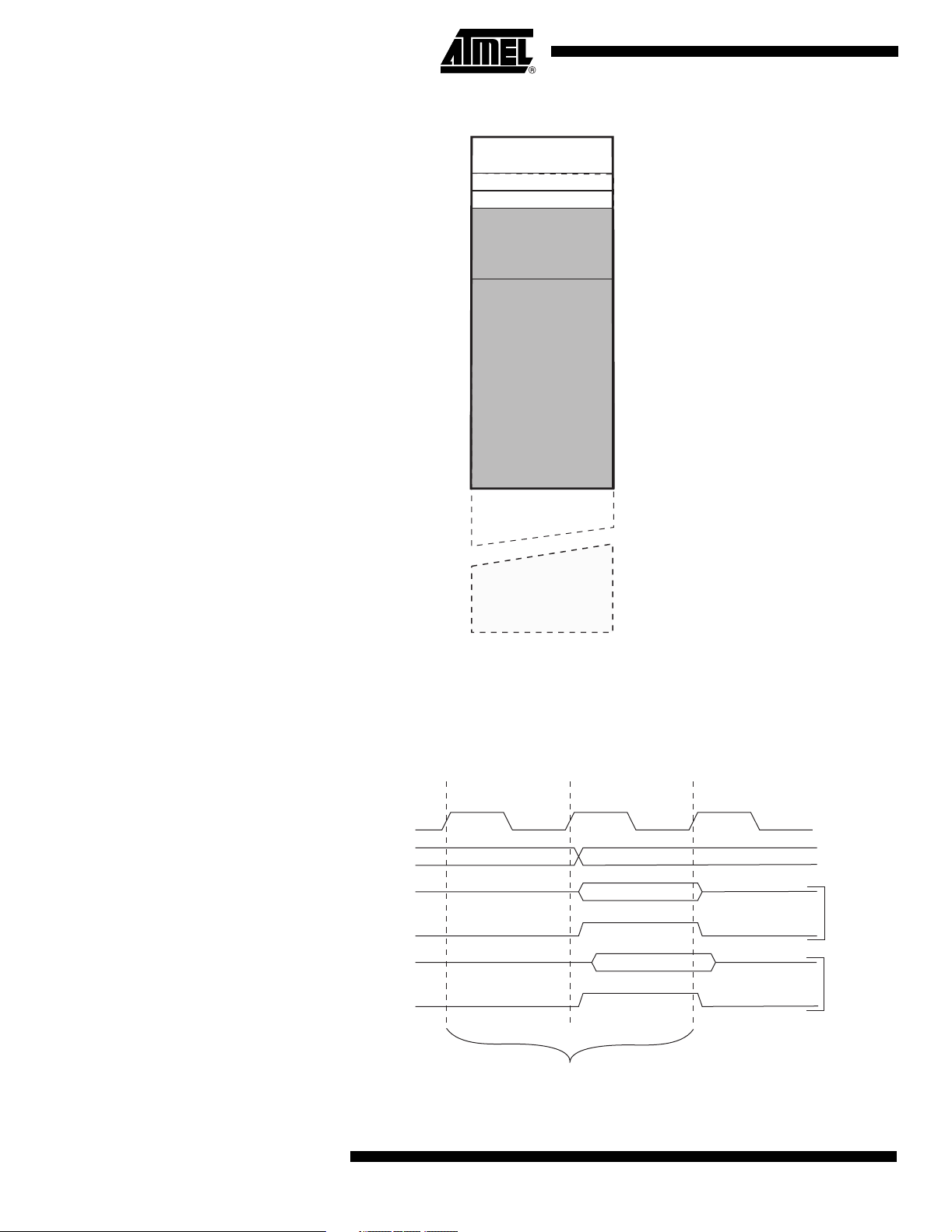

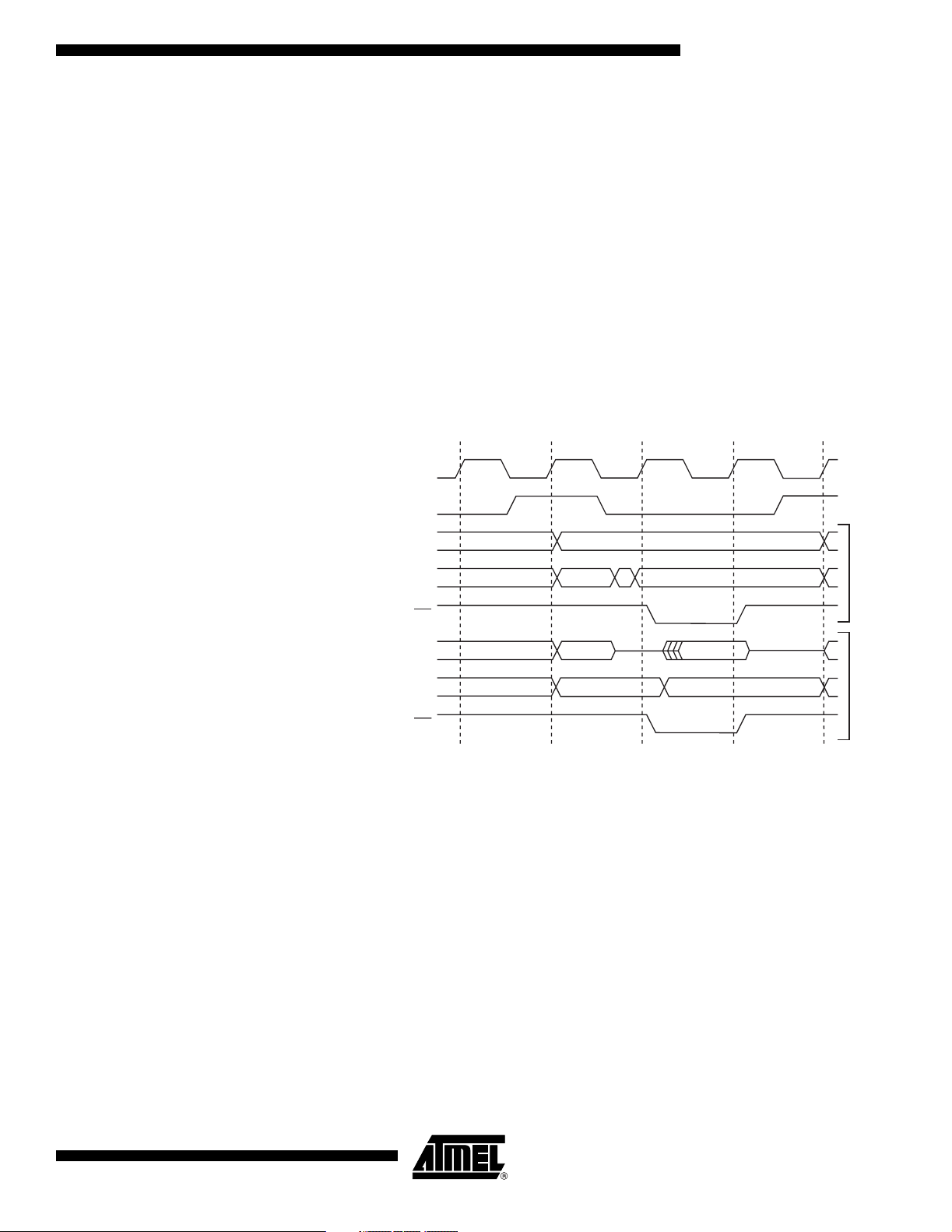

Figure 6shows the parallel instruction fetches and instruction executions enabledbythe

Harvard architectureand the fast-access Registerfile concept. This is the basicpipelin-

ing concepttoobtain up to 1 MIPSperMHzwith the corresponding unique resultsfor

functionspercost,functionsperclocks, andfunctionsperpower-unit.

Figure 6. TheParallelInstruction Fetches andInstruction Executions

T1 T2 T3 T4

clk

CPU

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

Figure 7shows theinternal timing concept for the Registerfile. Inasingle clock cyclean

ALU operation using two register operands is executed, and the resultisstoredback to

the destination register.

Reset and Interrupt Handling

Figure 7. Single CycleALU Operation

T1 T2 T3 T4

clk

CPU

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

The AVR providesseveraldifferent interrupt sources.Theseinterrupts and the separate

Reset Vector each have a separate program vector in the program memory space. All

interrupts areassigned individual enable bitswhich must be written logic one together

with the GlobalInterrupt Enable bit in the Status Register in order to enabletheinterrupt.

Dependingonthe program counter value, interrupts maybe automatically disabled

when Boot Lock bitsBLB02 orBLB12 are programmed.Thisfeatureimprovessoftware

security. See the section “Memory Programming” on page 175 fordetails.

The lowestaddresses in the program memory spaceare by default defined as theReset

andInterruptVectors.The complete listof vectors isshownin“Interrupts”onpage 51.

The listalso determines the prioritylevels of the different interrupts.The lower the

address the higher is the prioritylevel.RESET has the highest priority, and nextisINT0

–the ExternalInterruptRequest0.The InterruptVectors can bemoved to the startof

the Boot Flash section by setting the IVSEL bit in the GeneralInterrupt Control Register

(GICR).Refer to “Interrupts”onpage 51 for moreinformation. TheReset Vectorcan

2512A–AVR–04/02

11

Page 12

also bemoved to the startof the Boot Flash section by programming the BOOTRST

Fuse,see “Boot LoaderSupport–Read-While-Write Self-Programming” on page 162.

When an interruptoccurs, the GlobalInterrupt Enable I-bit iscleared and all interrupts

are disabled.Theusersoftware can write logic one to the I-bit to enablenested inter-

rupts.All enabled interruptscan then interruptthe current interrupt routine. The I-bit is

automatically set whenaReturn from Interruptinstruction – RETI –is executed.

Thereare basically twotypes of interrupts.The firsttypeis triggeredbyan event that

sets theinterrupt flag. For theseinterrupts, theProgram Counter is vectored to the

actualInterruptVector in order to execute theinterrupt handling routine, andhardware

clears the corresponding interrupt flag. Interrupt flagscan also be clearedbywriting a

logic one to the flag bit position(s) to be cleared. If an interrupt condition occurs whilethe

corresponding Interrupt Enable bit iscleared, theinterrupt flag will be set andremembered until theinterruptis enabled, or the flag isclearedbysoftware. Similarly, if one or

moreinterrupt conditions occurwhilethe GlobalInterrupt Enable bit iscleared, the corresponding interrupt flag(s) will be set andremembered until the GlobalInterrupt Enable

bit isset, andwill then beexecutedbyorder ofpriority.

The second typeof interruptswill trigger aslong as theinterrupt condition ispresent.

Theseinterruptsdo not necessarily have interrupt flags. If theinterrupt condition disap-

pears beforetheinterruptis enabled, theinterrupt will not betriggered.

When the AVR exitsfrom an interrupt, it will always returntothemainprogram and exe-

cute one moreinstruction beforeanypending interruptisserved.

Note that the Status Register is not automatically storedwhen enteringaninterrupt rou-

tine, norrestoredwhen returning from an interrupt routine. This must be handledby

software.

When using the CLI instruction to disableinterrupts, theinterruptswill be immediately

disabled. Nointerrupt will beexecuted after the CLI instruction, even if it occurs simulta-

neously with the CLI instruction. The following example shows how thiscan beused to

avoid interruptsduring thetimedEEPROM write sequence..

Assembly Code Example

in r16, SREG

cli ; disable interrupts during timed sequence

sbi EECR, EEMWE

sbi EECR, EEWE

out SREG, r16

; store SREG value

; start EEPROM write

; restore SREG value (I-bit)

CCode Example

char cSREG;

cSREG = SREG;

/*

disable interrupts during timed sequence */

_CLI();

EECR |= (1<<EEMWE);

EECR |= (1<<EEWE);

SREG = cSREG;

/* store SREG value */

/* start EEPROM write */

/* restore SREG value (I-bit) */

12

ATmega8515(L)

2512A–AVR–04/02

Page 13

ATmega8515(L)

When using the SEI instruction to enableinterrupts, theinstruction following SEI will be

executedbeforeanypending interrupts, asshowninthis example.

Assembly Code Example

sei

; set global interrupt enable

sleep

; enter sleep, waiting for interrupt

; note: will enter sleep before any pending

; interrupt(s)

CCode Example

_SEI();

_SLEEP();

/* note: will enter sleep before any pending interrupt(s) */

Interrupt Response Time Theinterruptexecution response for all theenabled AVR interrupts isfourclock cycles

minimum. Afterfourclock cycles theProgram Vector address for theactual interrupt

handling routine is executed. During thisfourclock cycle period, theProgram Counter is

pushed onto the Stack.TheVector is normally a jump to theinterrupt routine, and this

jump takes three clock cycles. If an interruptoccurs during execution of amulti-cycle

instruction, this instruction iscompletedbeforetheinterruptisserved. If an interrupt

occurs when the MCU is in sleep mode, theinterruptexecution responsetimeis

increasedbyfourclock cycles.This increase comes in addition to the start-up time from

the selectedsleep mode.

/* set global interrupt enable */

/* enter sleep, waiting for interrupt */

A return from an interrupt handling routine takesfourclock cycles. During these four

clock cycles, theProgram Counter(two bytes) ispoppedback from the Stack, the Stack

Pointer is incrementedbytwo, and the I-bit in SREG isset.

2512A–AVR–04/02

13

Page 14

AVR ATmega8515 Memories

Thissection describes the different memories in the ATmega8515. The AVR architec-

ture has twomainmemory spaces, the Data Memory and theProgram Memory space.

Inaddition, the ATmega8515 features an EEPROM Memory fordata storage. All three

memory spaces are linear andregular.

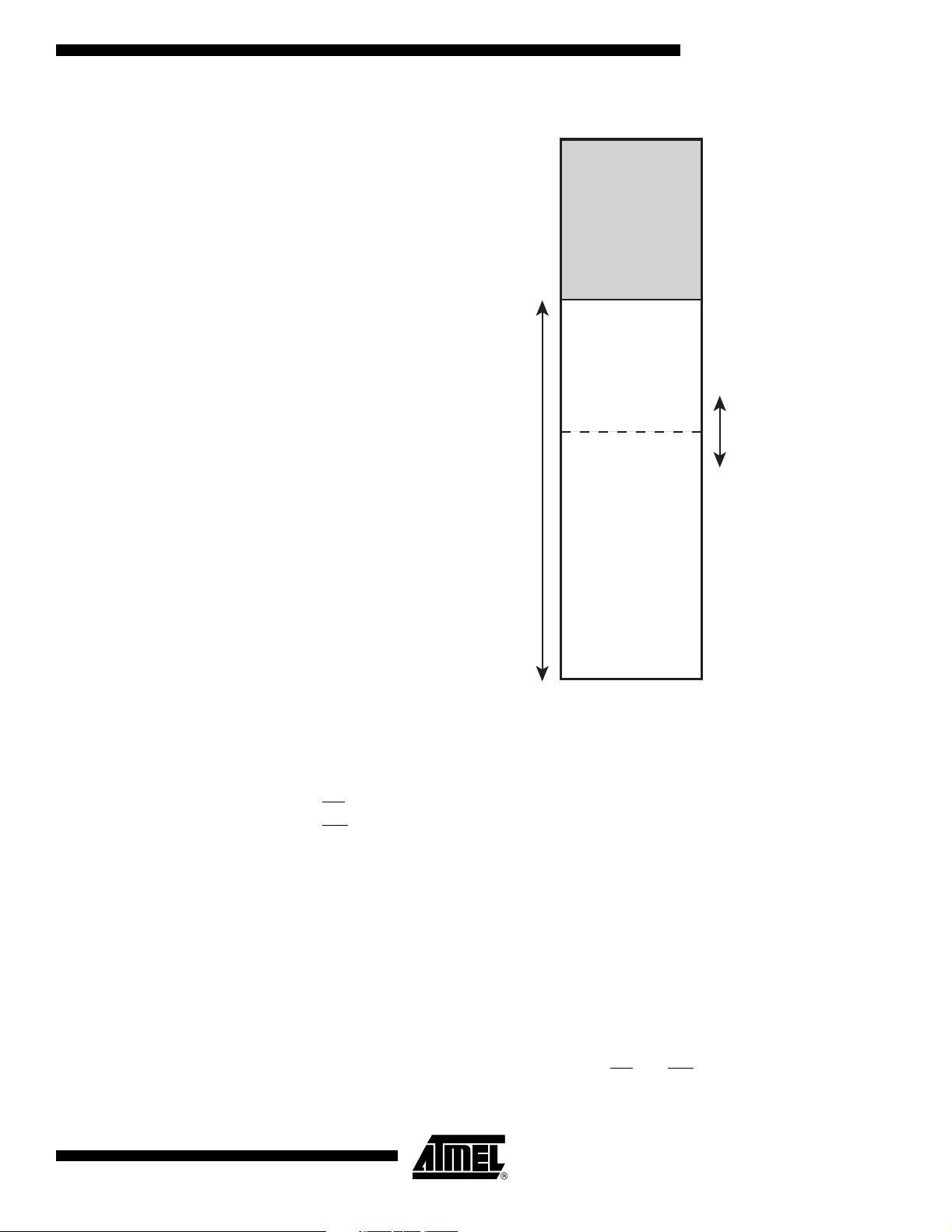

In-System Reprogrammable Flash Program Memory

The ATmega8515 contains 8KbytesOn-chipIn-System Reprogrammable Flash memory forprogram storage. Sinceall AVR instructions are16 or32 bitswide, the Flash is

organized as 4Kx16. Forsoftware security, the Flash Program memory spaceis

divided into two sections, Boot Program section and Application Program section.

The Flash memory has an enduranceof at least1,000 write/erase cycles.Th e

ATmega8515 Program Counter(PC) is 12 bitswide, thus addressing the4Kprogram

memory locations.Theoperation ofBoot Program section and associatedBoot Lock

bitsforsoftware protection are described in detail in “Boot LoaderSupport–Read-

While-Write Self-Programming” on page 162. “Memory Programming” on page 175 con-

tains a detaileddescription on Flash data serialdownloading using the SPIpins.

Constant tablescan beallocatedwithin the entireProgram memory address space,see

the LPM – Load Program Memory instruction description.

Timing diagramsfor instruction fetch and execution are presented in “Instruction Execu-

tion Timing” on page 11.

Figure 8. Program Memory Map

$000

Application Flash Section

Boot Flash Section

$FFF

14

ATmega8515(L)

2512A–AVR–04/02

Page 15

ATmega8515(L)

SRAM Data Memory Figure 9shows how the ATmega8515 SRAMMemory is organized.

The lower608 Data Memory locations address theRegisterFile, the I/OMemory, and

theinternaldata SRAM.The first 96 locations address the RegisterFileandI/OMemory, and thenext 512 locations address theinternaldata SRAM.

An optional externaldata SRAMcan beusedwith the ATmega8515. ThisSRAMwill

occupy an area in the remaining address locations in the 64K address space. This area

starts at theaddress following theinternalSRAM.TheRegisterfile,I/O, ExtendedI/O

andInternalSRAM occupies the lowest 608 bytes in normal mode,so when using 64KB

(65536 bytes) ofExternalMemory, 64928 Bytes ofExternalMemory areavailable. See

“ExternalMemory Interface” on page 22 fordetails on how to takeadvantage of the

external memory map.

When theaddresses accessing the SRAM memory spaceexceeds theinternaldata

memory locations, theexternaldata SRAM is accessed using the same instructions as

for theinternaldata memory access. When theinternaldata memories areaccessed,

the read andwrite strobe pins(PD7 and PD6) areinactive during the wholeaccess

cycle. ExternalSRAM operation is enabledbysetting the SREbit in the MCUCR

register.

Accessing externalSRAM takes one additionalclock cycle perbyte compared to access

of theinternalSRAM.This means that the commands LD, ST,LDS,STS, LDD, STD,

PUSH, and POPtakeoneadditionalclock cycle. If the Stack isplaced in external

SRAM, interrupts, subroutine calls andreturns takethree clock cycles extra becausethe

two-byte program counter ispushed andpopped, and external memory access does not

takeadvantage of theinternalpipe-line memory access. When externalSRAM interface

is usedwithwait-state, one-byte external access takes two, three, orfour additional

clock cyclesfor one, two, and three wait-statesrespectively. Interrupts, subroutine calls

andreturnswill needfive,seven, or nine clock cycles morethan specified in theinstruction set manualfor one, two, and three wait-states.

The five different addressing modesfor the data memory cover: Direct,Indirect withDisplacement,Indirect,Indirect with Pre-decrement, andIndirect with Post-increment. In

the Registerfile,registers R26 to R31 featuretheindirectaddressing pointerregisters.

The directaddressing reaches theentire data space.

The Indirect withDisplacement mode reaches63address locationsfrom the base

address given by the Y- orZ-register.

When using register indirectaddressing modeswith automaticpre-decrement andpost-

increment, theaddress registers X, Y, andZare decremented or incremented.

The 32 generalpurpose working registers, 64 I/Oregisters, and the 512 bytes of internal

data SRAM in the ATmega8515 areall accessiblethrough all theseaddressing modes.

The Registerfileisdescribed in “General Purpose RegisterFile” on page 9.

2512A–AVR–04/02

15

Page 16

Figure 9. Data Memory Map

Data Memory

32 Registers

64 I/O Registers

Internal SRAM

(512 x 8)

External SRAM

(0 - 64K x 8)

$0000 - $001F

$0020 - $005F

$0060

$025F

$0260

$FFFF

Data Memory Access Times Thissection describes the general access timing conceptsfor internal memory access.

Theinternaldata SRAM access isperformed in two clk

cycles asdescribed in Figure

CPU

10.

Figure 10. On-chipData SRAM Access Cycles

T1 T2 T3

clk

CPU

Address

Compute Address

Address Valid

Data

WR

Write

Data

RD

Memory Access Instruction

Next Instruction

Read

16

ATmega8515(L)

2512A–AVR–04/02

Page 17

ATmega8515(L)

EEPROM Data Memory The ATmega8515 contains 512 bytes ofdata EEPROM memory. Itis organized as a

separate data space, in which single bytescan be read andwritten. The EEPROM has

an enduranceof at least100,000 write/erase cycles.Theaccess between the EEPROM

and the CPU isdescribed in the following,specifying the EEPROM Address Registers,

the EEPROM Data Register, and the EEPROM Control Register.

For a detaileddescription ofSPIdata downloading to the EEPROM, see page 189.

EEPROM Read/Write Access The EEPROM Access Registers areaccessibleinthe I/Ospace.

The write access time for the EEPROM is given in Table1.Aself-timing function,how-

ever, lets theusersoftware detect when thenext byte can be written. If theusercode

contains instructions that write the EEPROM, some precautions must betaken. In

heavily filteredpowersupplies, V

causes the device forsome period of time to run at a voltage lower than specified as

minimum for the clock frequency used. See “Preventing EEPROM Corruption” on page

21. fordetails on how to avoidproblems in these situations.

Inorder to prevent unintentionalEEPROM writes, a specificwrite proceduremust be fol-

lowed.Refer to the description of the EEPROM Control Registerfordetails on this.

When the EEPROM isread, the CPU ishaltedforfourclock cyclesbeforethenext

instruction is executed. When the EEPROM iswritten, the CPU ishaltedfor two clock

cyclesbeforethenextinstruction is executed.

islikely to riseorfall slowly on Power-up/down. This

CC

The EEPROM Address Register – EEARH and EEARL

The EEPROM Data Register – EEDR

Bit 15 14 13 12 11 10 9 8

–––––––EEAR8EEARH

EEAR7 EEAR6 EEAR5 EEAR4 EEAR3 EEAR2 EEAR1 EEAR0 EEARL

76543 210

Read/WriteRRRRRRRR/W

R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value0000000X

XXXXXXXX

• Bits 15..9 – Res: Reserved Bits

These bits are reservedbits in the ATmega8515 andwill always read aszero.

• Bits 8..0 – EEAR8..0: EEPROM Address

The EEPROM Address Registers – EEARH andEEARL – specify the EEPROM

address in the512bytesEEPROM space. The EEPROM data bytes areaddressedlin-

early between0and 511. Theinitial value ofEEAR is undefined.Aproper value must be

written beforethe EEPROM maybeaccessed.

Bit 76543 210

MSB LSB EEDR

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

2512A–AVR–04/02

• Bits 7..0 – EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR Registercontains the data to be written to

the EEPROM in theaddress given by the EEAR Register. For the EEPROM read oper-

ation, the EEDR contains the data read out from the EEPROM at theaddress given by

EEAR.

17

Page 18

The EEPROM Control Register –EECR

Bit 76543 210

––––EERIEEEMWEEEWEEEREEECR

Read/WriteRRRRR/W R/W R/W R/W

Initial Value00000 0X 0

• Bits 7..4 – Res: Reserved Bits

These bits are reservedbits in the ATmega8515 andwill always read aszero.

• Bit 3 – EERIE: EEPROM Ready Interrupt Enable

Writing EERIE to one enables the EEPROM Ready Interruptif the I-bit in SREG isset.

Writing EERIE to zero disables theinterrupt. The EEPROM Ready interrupt generates a

constant interrupt when EEWE iscleared.

• Bit 2 – EEMWE: EEPROM Master Write Enable

The EEMWE bit determineswhethersetting EEWE to one causes the EEPROM to be

written. When EEMWE isset,setting EEWE within fourclock cycleswill write data to the

EEPROM at the selected address If EEMWE iszero,setting EEWE will have no effect.

When EEMWE hasbeen written to one by software,hardware clears the bit to zeroafter

fourclock cycles. See the description of the EEWE bit for an EEPROM write procedure.

• Bit 1 – EEWE: EEPROM Write Enable

The EEPROM Write Enable SignalEEWEis the write strobetothe EEPROM. When

address anddata are correctly set up, the EEWE bit must be written to one to write the

value into the EEPROM.The EEMWE bit must be written to one beforealogical one is

written to EEWE, otherwisenoEEPROM write takesplace. The following procedure

should be followedwhen writing the EEPROM (theorder ofsteps 3 and 4is not

essential):

1. Wait untilEEWEbecomeszero.

2. Wait untilSPMEN in SPMCR becomeszero.

3. Write newEEPROM address to EEAR (optional).

4. Write newEEPROM data to EEDR (optional).

5. Write a logical one to the EEMWE bit while writing a zerotoEEWE in EECR.

6. Within fourclock cycles aftersetting EEMWE, write a logical one to EEWE.

18

The EEPROM can not be programmedduring a CPUwritetothe Flash memory.The

softwaremust check that the Flash programming iscompletedbefore initiating a new

EEPROM write. Step 2is only relevant if the software contains a Boot Loader allowing

the CPU to program the Flash. If the Flash is neverbeing updatedbythe CPU, step 2

can be omitted. See “Boot LoaderSupport–Read-While-Write Self-Programming” on

page 162 fordetails about boot programming.

Caution: An interrupt between step 5andstep6will makethe write cycle fail, sincethe

EEPROM MasterWrite Enable will time-out. If an interrupt routine accessing the

EEPROM is interrupting anotherEEPROM access, the EEAR or EEDR Registerwill be

modified, causing theinterruptedEEPROM access to fail. Itisrecommended to have

theglobal interrupt flag clearedduring all the steps to avoid these problems.

When the write access time has elapsed, the EEWE bit isclearedbyhardware. The

usersoftware can poll thisbit andwait for a zero before writing thenext byte. When

EEWE hasbeen set, the CPU ishaltedfor two cyclesbeforethenextinstruction is

executed.

ATmega8515(L)

2512A–AVR–04/02

Page 19

ATmega8515(L)

• Bit 0 – EERE: EEPROM Read Enable

The EEPROM ReadEnable SignalEERE is the readstrobetothe EEPROM. When the

correctaddress isset up in the EEAR Register, the EEREbit must be written to a logic

one to trigger the EEPROM read.The EEPROM read access takes one instruction, and

the requesteddata is availableimmediately. When the EEPROM isread, the CPU is

haltedforfourcyclesbeforethenextinstruction is executed.

Theusershould poll the EEWE bit before starting the read operation. If a write operation

is in progress, it is neitherpossibletoread the EEPROM, nor to change the EEAR

Register.

The calibratedOscillator is used to time the EEPROM accesses.Table1lists thetypical

programming time forEEPROM access from the CPU.

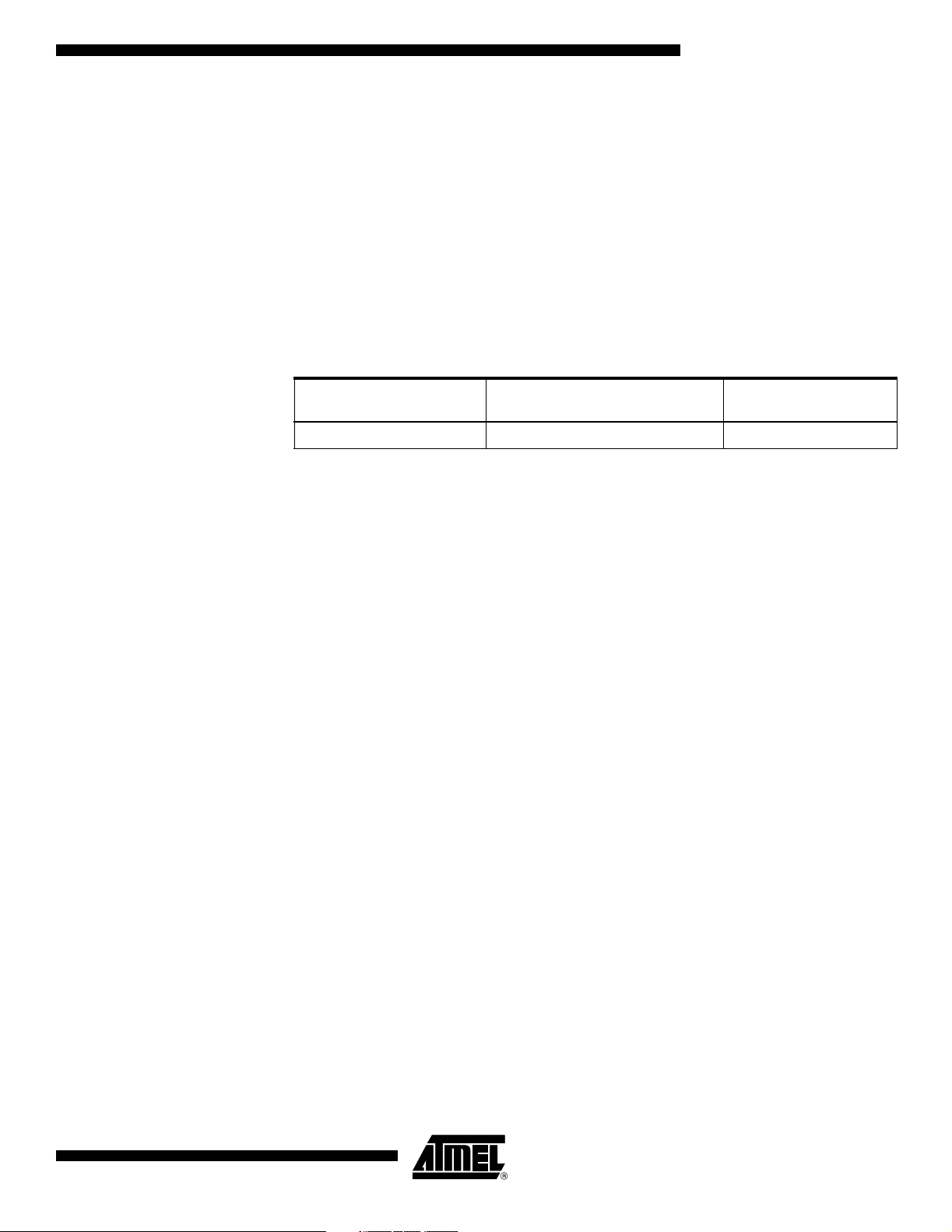

Table 1. EEPROM Programming Time

Number of Calibrated RC

Symbol

EEPROM Write (from CPU) 8448 8.5 ms

Note: 1. Uses 1 MHz clock, independent of CKSEL Fuse settings.

Oscillator Cycles

(1)

Typ Programming Time

2512A–AVR–04/02

19

Page 20

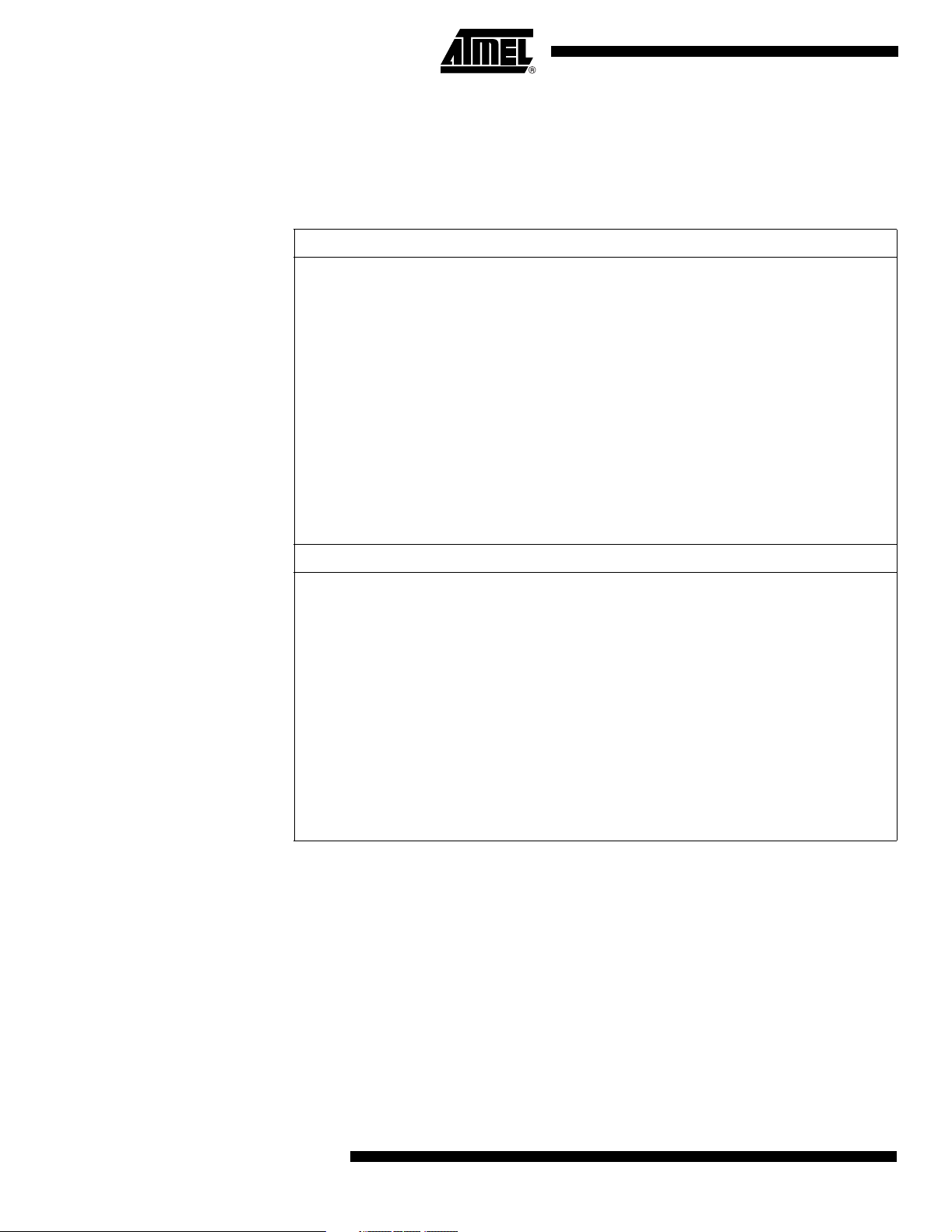

The following codeexamplesshow one assembly and one Cfunction forwriting to the

EEPROM.Theexamples assume that interrupts are controlled(e.g.,bydisabling inter-

rupts globally) sothat no interruptswill occurduring execution of these functions.The

examples alsoassume that no Flash Boot Loader ispresent in the software. If such

codeispresent, the EEPROM write function mustalso wait for any ongoing SPMcom-

mand to finish.

Assembly Code Example

EEPROM_write:

; Wait for completion of previous write

sbic EECR,EEWE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to data register

out EEDR,r16

; Write logical one to EEMWE

sbi EECR,EEMWE

; Start eeprom write by setting EEWE

sbi EECR,EEWE

ret

CCode Example

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

{

Wait for completion of previous write

/*

while(EECR & (1<<EEWE))

;

/* Set up address and data registers */

EEAR = uiAddress;

EEDR = ucData;

Write logical one to EEMWE */

/*

EECR |= (1<<EEMWE);

/* Start eeprom write by setting EEWE */

EECR |= (1<<EEWE);

}

*/

20

ATmega8515(L)

2512A–AVR–04/02

Page 21

ATmega8515(L)

Thenext codeexamplesshow assembly andCfunctionsforreading the EEPROM.The

examples assume that interrupts are controlledsothat no interruptswill occurduring

execution of these functions.

Assembly Code Example

EEPROM_read:

; Wait for completion of previous write

sbic EECR,EEWE

rjmp EEPROM_read

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Start eeprom read by writing EERE

sbi EECR,EERE

; Read data from data register

in r16,EEDR

ret

CCode Example

unsigned char EEPROM_read(unsigned int uiAddress)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEWE))

;

/* Set up address register */

EEAR = uiAddress;

Start eeprom read by writing EERE */

/*

EECR |= (1<<EERE);

/* Return data from data register */

return EEDR;

}

Preventing EEPROM Corruption

2512A–AVR–04/02

During periods oflow V

, the EEPROM data can be corruptedbecausethe supply volt-

CC

age is too lowfor the CPU and the EEPROM to operate properly.Theseissues arethe

same asforboard levelsystems using EEPROM, and the same design solutionsshould

beapplied.

An EEPROM data corruption can be causedbytwo situationswhen thevoltage is too

low. First, a regularwrite sequencetothe EEPROM requires aminimumvoltage to

operate correctly. Secondly, the CPU itself can execute instructions incorrectly, if the

supply voltage is too low.

EEPROM data c o rruption c an easi ly beavoid edbyfo llo wing th isdes ign

recommendation:

Keep the AVR RESETactive (low) during periods of insufficient powersupply volt-

age. Thiscan be done by enabling theinternalBrown-out Detector(BOD). If the

detection level of theinternalBODdoes not match theneededdetection level, an

externallow V

Reset Protection circuit can beused. If aReset occurs whilea

CC

write operation is in progress, the write operation will be completedprovided that the

powersupply voltage issufficient.

21

Page 22

I/O Memory The I/Ospace definition of the ATmega8515 isshown in “RegisterSummary”onpage

209.

All ATmega8515 I/Os andperipherals are placed in the I/Ospace. The I/Olocations are

accessedbythe IN andOUTinstructions, transferring data between the 32 generalpur-

pose working registers and the I/Ospace. I/O Registers within theaddress range $00 -

$1F are directly bit-accessibleusing the SBI andCBIinstructions. Inthese registers, the

value ofsingle bitscan be checkedbyusing the SBIS andSBICinstructions.Refer to

theinstruction set section for more details. When using the I/Ospecificcommands IN

andOUT, the I/O addresses$00 -$3Fmust beused. When addressing I/O Registers as

data spaceusing LD andSTinstructions, $20 must beadded to theseaddresses.

Forcompatibilitywithfuture devices, reservedbitsshould be written to zeroif accessed.

ReservedI/O memory addressesshould neverbe written.

Some of the statusflags are clearedbywriting a logical one to them. Note that the CBI

and SBI instructionswill operate on all bits in the I/O Register, writing a one back into

anyflag read asset, thusclearing the flag. The CBI andSBIinstructionswork withreg-

isters $00 to $1F only.

The I/O andperipherals controlregisters areexplained in latersections.

External Memory Interface

Overview When theeXternalMEMory (XMEM) is enabled, address space outsidetheinternal

With all the features the ExternalMemory Interface provides, it iswell suited to operate

as an interfacetomemory devicessuch as externalSRAM andFlash, andperipherals

such as LCD-display, A/D, andD/A. Themainfeatures are:

•

Four Different Wait State Settings (Including No wait State)

• Independent Wait State Setting for Different External Memory Sectors (Configurable

Sector Size)

• The Number of Bits Dedicated to Address High Byte is Selectable

• Bus Keepers on Data Lines to Minimize Current Consumption (Optional)

SRAMbecomes availableusing the dedicated external memory pins(see Figure1on

page 2, Table26 on page 63, Table 32onpage 67, and Table 38onpage 71).The

memory configuration isshowninFigure11.

22

ATmega8515(L)

2512A–AVR–04/02

Page 23

Figure 11. ExternalMemory withSectorSelect

Internal Memory

Lower Sector

SRW01

SRW00

ATmega8515(L)

0x0000

0x25F

0x260

SRL[2..0]

Using the External Memory Interface

External Memory

(0-64K x 8)

Theinterface consists of:

•AD7:0:Multiplexedlow-order address bus anddata bus

•A15:8:High-order address bus(configurable number ofbits)

•ALE: Address latch enable

•RD

• WR

The controlbitsfor the ExternalMemory Interfaceare located in three registers, the

MCU Control Register – MCUCR, the ExtendedMCUControl Register – EMCUCR, and

the SpecialFunction IO Register – SFIOR.

: Readstrobe

:Write strobe

Upper Sector

SRW11

SRW10

0xFFFF

2512A–AVR–04/02

When the XMEM interfaceis enabled, it will overridethe settings in the data direction

registers correspondingtothe portsdedicated to theinterface. Fordetails about thisport

override,see thealternate functions in section “I/O Ports”onpage 56.The XMEM inter-

face will auto-detect whether an access is internal or external. If theaccess is external,

the XMEM interface will output address, data, and the controlsignals on the ports

according to Figure13(thisfigure shows the wave formswithout wait states). When

ALE goesfrom high to low, thereis avalid address on AD7:0. ALE islowduring a data

transfer. When the XMEM interfaceis enabled, alsoaninternal access will causeactivity on address-, data-, and ALE ports, but theRD

internal access. When the ExternalMemory Interfaceisdisabled, thenormalpin and

andWR strobeswill not toggle during

23

Page 24

data direction settings areused. Note that when the XMEM interfaceisdisabled, the

address spaceabove theinternalSRAMboundary is not mapped into theinternal

SRAM. Figure12illustrateshow to connectanexternalSRAM to the AVR using an octal

latch (typically “74x573”or equivalent)which is transparent when G ishigh.

Address Latch Requirements Due to the high-speed operation of the XRAM interface, theaddress latch must be

selectedwithcare for system frequencies above 8 MHz @ 4V and 4 MHz @ 2.7V.

When operating at conditions above these frequencies, thetypical old style 74HC series

latch becomes inadequate. Theexternal memory interfaceisdesigned in complianceto

the 74AHC serieslatch. However, most latchescan beused aslong theycomply with

themaintimingparameters.Themainparameters for theaddress latch are:

• D to Qpropagation delay(t

• Data setup time before Glow(t

• Data (address) hold time afterGlow(

Theexternal memory interfaceisdesigned to guaranty minimum address hold time after

G is assertedlow of t

201).The D to Qpropagation delay(t

ing theaccess time requirement of theexternalcomponent. The data setup time before

Glow(t

(dependent on the capacitive load).

Figure 12. ExternalSRAMConnected to the AVR

) mustnotexceed address valid to ALE low(t

su

= 5ns(refer to t

h

pd

)

)

su

)

th

LAXX_LD/tLLAXX_ST

) must betaken into consideration when calculat-

pd

in Table 99 to Table106 on page

) minus PCB wiring delay

AVLLC

D[7:0]

AD7:0

ALE

DQ

G

A[7:0]

SRAM

AVR

A15:8

RD

WR

Pull-up and Bus Keeper The pull-upresistors on theAD7:0 ports maybeactivated if the corresponding Port reg-

ister iswritten to one. To reduce powerconsumption in sleep mode, it isrecommended

to disablethe pull-ups by writing thePort register to zero before entering sleep.

The XMEM interfacealso provides a buskeeper on theAD7:0 lines.The buskeeper

can be disabled and enabled in softwareasdescribed in “SpecialFunction IO Register –

SFIOR” on page 29. When enabled, the buskeeperwill keep the previous value on the

AD7:0 buswhilethese lines aretri-statedbythe XMEM interface.

If neitherbus-keeper norpull-ups are enabled, the XMEM interface will leave theAD7:0

tri-statedduring a read access until thenextRAM access (internal or external) appears.

A[15:8]

RD

WR

Timing External memory deviceshave various timing requirements. To meet these require-

ments, the ATmega8515 XMEM interface providesfourdifferent wait states asshownin

Table 3. Itis important to consider thetimingspecification of theexternal memory

device before selecting the wait state. Themostimportant parameters aretheaccess

24

ATmega8515(L)

2512A–AVR–04/02

Page 25

ATmega8515(L)

time for theexternal memory in conjunction with the set-upreq uirement of the

ATmega8515. Theaccess time for theexternal memory isdefined to bethetimefrom

receiving the chipselect/address until the data of this address actually isdriven on the

bus.Theaccess time cannot exceed thetimefrom theALE pulseis assertedlow until

data must be stable during a readsequence (t

106 on page 201).The different wait states are set up in software. As an additionalfeature, it ispossibletodividetheexternal memory spaceintwo sectors with individualwait

state settings.This makes it possibletoconnecttwo different memory deviceswithdif-

ferent timing requirements to the same XMEM interface. ForXMEMinterface timing

details, please refer to Figure89 to Figure 92, and Table 99 to Table106.

Note that the XMEM interfaceis asynchronous and that the waveforms in the figures

below are related to theinternal system clock.The skewbetween the Internal andExter-

nalclock (XTAL1) is not guaranteed(it variesbetween devices, temperature, andsupply

voltage). Consequently, the XMEM interfaceis not suitedforsynchronous operation.

LLRL

+ t

RLRH

- t

in Table 99 to Table

DVRH

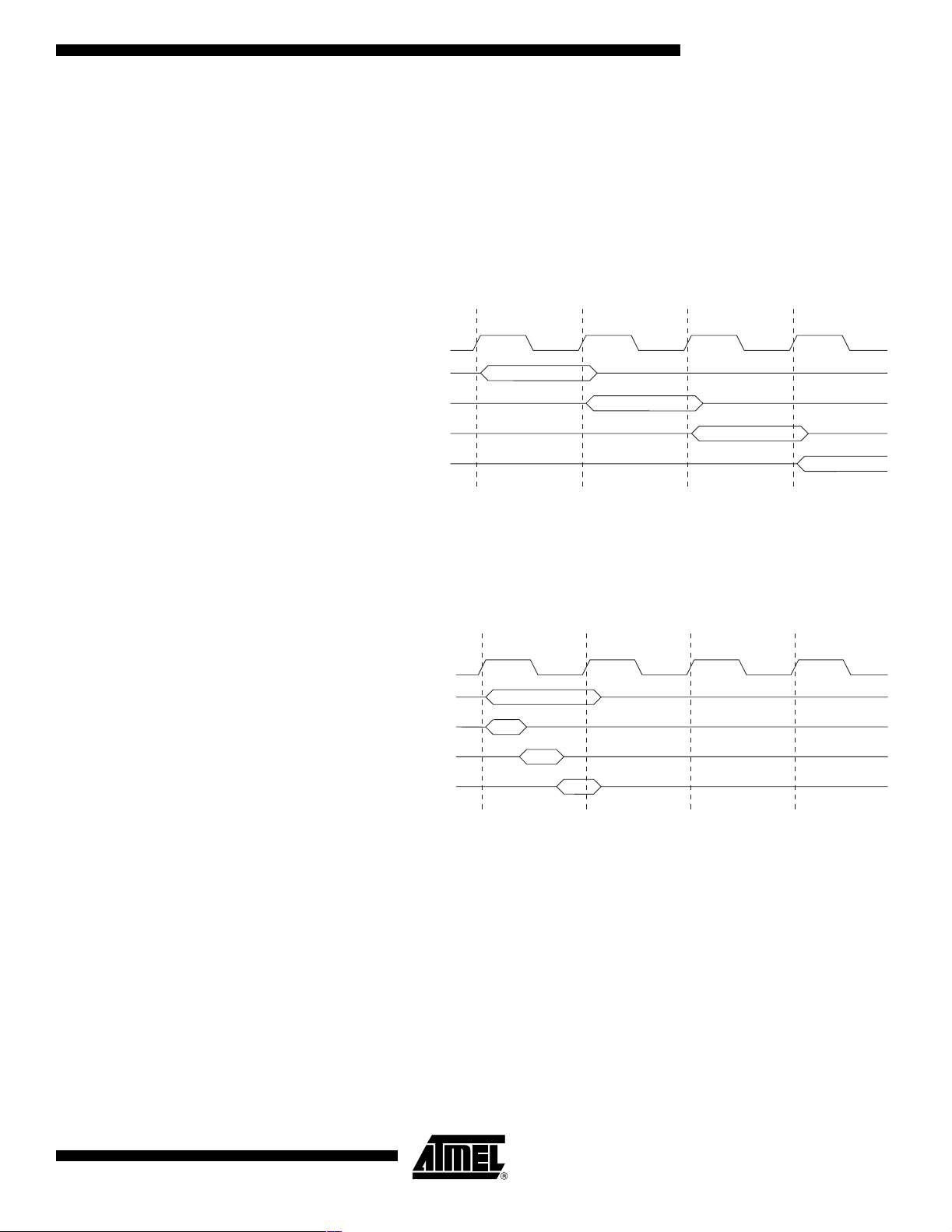

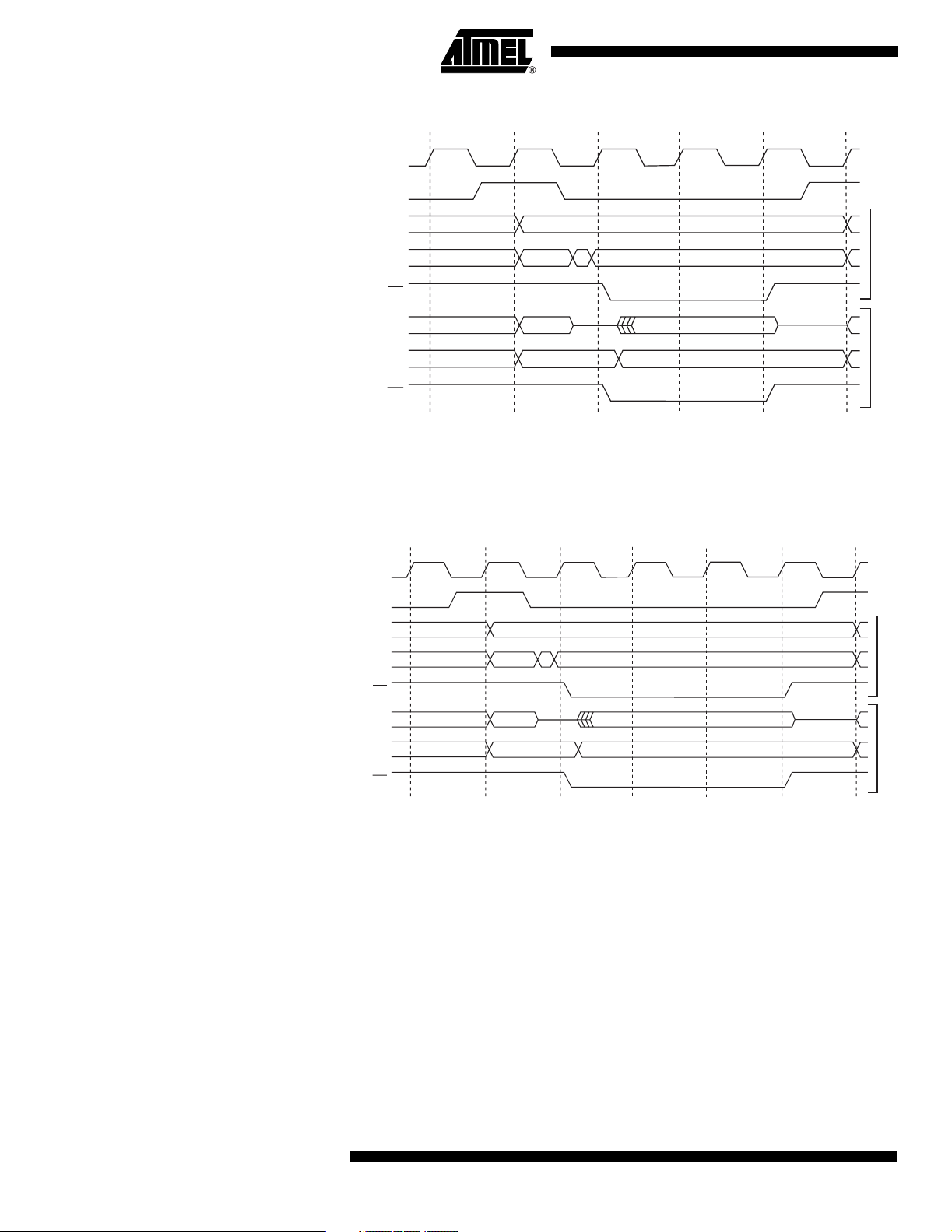

Figure 13. ExternalData Memory Cycle swithout Wait State (SRW n1 = 0and

SRWn0 = 0)

System Clock (CLK

(1)

CPU

ALE

A15:8

DA7:0

WR

DA7:0 (XMBK = 0)

DA7:0 (XMBK = 1)

RD

T1 T2 T3

)

AddressPrev. Addr.

Address DataPrev. Data XX

DataPrev. Data Address

DataPrev. Data Address

T4

Write

Read

Note: 1. SRWn1 =SRW11 (uppersector) orSRW01 (lowersector), SRWn0 =SRW10 (upper

sector) orSRW00 (lowersector)

TheALE pulseinperiod T4 is only present if thenextinstruction accesses theRAM

(internal or external).

2512A–AVR–04/02

25

Page 26

Figure 14. ExternalData Memory CycleswithSRWn1 = 0andSRWn0 = 1

System Clock (CLK

CPU

ALE

T1 T2 T3

)

T4

(1)

T5

A15:8

DA7:0

WR

DA7:0 (XMBK = 0)

DA7:0 (XMBK = 1)

RD

Address DataPrev. Data XX

AddressPrev. Addr.

DataPrev. Data Address

DataPrev. Data Address

Note: 1. SRWn1 =SRW11 (uppersector) orSRW01 (lowersector), SRWn0 =SRW10 (upper

sector) orSRW00 (lowersector)

TheALE pulseinperiod T5 is only present if thenextinstruction accesses theRAM

(internal or external).

Figure 15. ExternalData Memory CycleswithSRWn1 = 1andSRWn0 = 0

System Clock (CLK

CPU

ALE

A15:8

DA7:0

T1 T2 T3

)

AddressPrev. Addr.

Address DataPrev. Data XX

T4 T5

(1)

T6

Write

Read

Write

WR

DA7:0 (XMBK = 0)

DA7:0 (XMBK = 1)

RD

DataPrev. Data Address

DataPrev. Data Address

Note: 1. SRWn1 =SRW11 (uppersector) orSRW01 (lowersector), SRWn0 =SRW10 (upper

sector) orSRW00 (lowersector)

TheALE pulseinperiod T6 is only present if thenextinstruction accesses theRAM

(internal or external).

Read

26

ATmega8515(L)

2512A–AVR–04/02

Page 27

ATmega8515(L)

XMEM Register Description

MCU Control Register – MCUCR

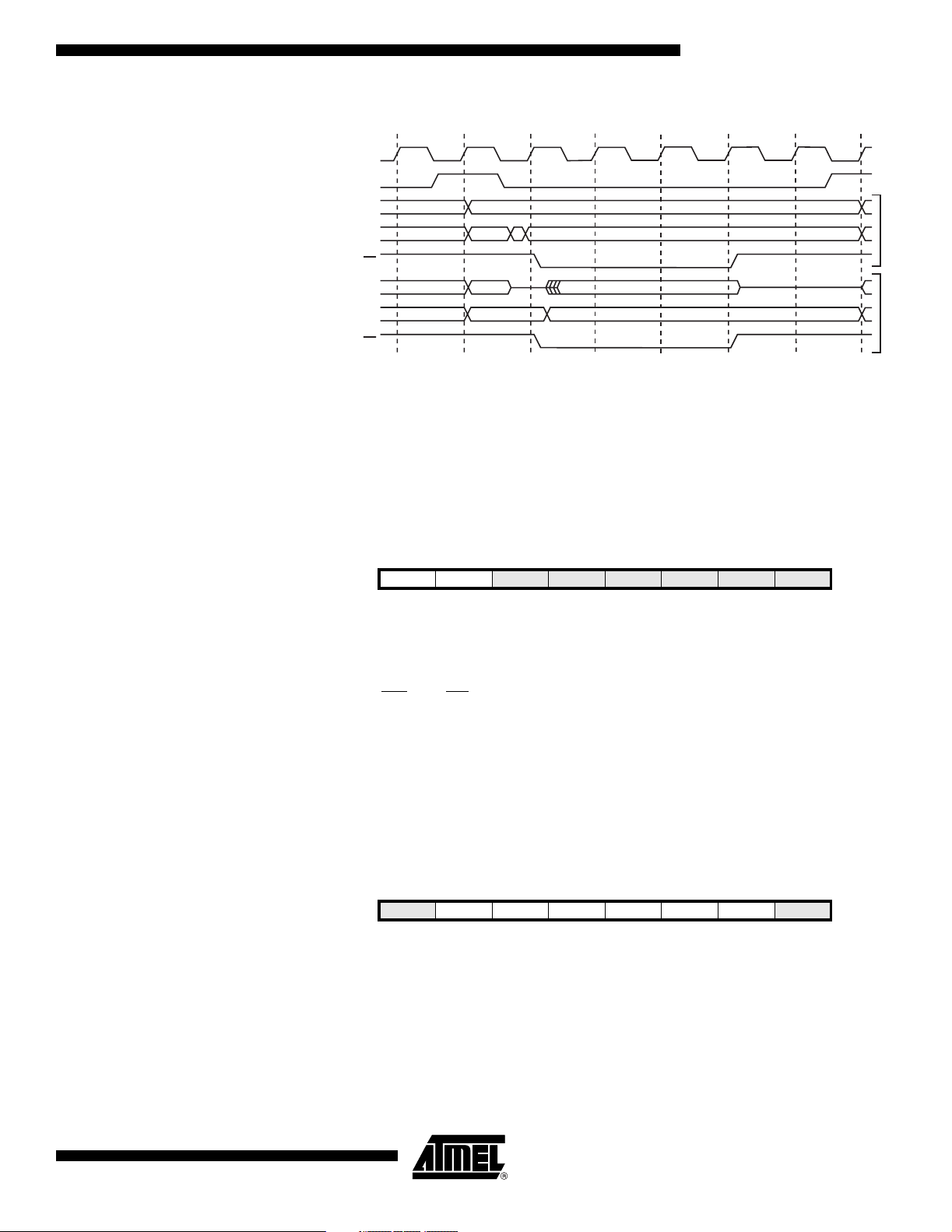

Figure 16. ExternalData Memory CycleswithSRWn1 = 1andSRWn0 = 1

System Clock (CLK

DA7:0 (XMBK = 0)

DA7:0 (XMBK = 1)

CPU

ALE

A15:8

DA7:0

WR

)

T1 T2 T3

AddressPrev. Addr.

Address DataPrev. Data XX

DataPrev. Data Address

DataPrev. Data Address

RD

T4 T5 T6

(1)

T7

Note: 1. SRWn1 =SRW11 (uppersector) orSRW01 (lowersector), SRWn0 =SRW10 (upper

sector) orSRW00 (lowersector)

TheALE pulseinperiod T7 is only present if thenextinstruction accesses theRAM

(internal or external).

Bit 76543 210

SRE SRW10

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

SE SM1 ISC11 ISC10 ISC01 ISC00 MCUCR

Write

Read

Extended MCU Control Register – EMCUCR

• Bit 7 – SRE: External SRAM/XMEM Enable

Writing SRE to one enables the ExternalMemory Interface.The pin functions AD7:0,

A15:8, ALE, WR

, and RD areactivated as thealternate pin functions.The SREbit over-

rides anypin direction settings in the respective Data Direction Registers. Writing SRE

to zero,disables the ExternalMemory Interfaceand thenormalpin anddata direction

settings areused.

• Bit 6 – SRW10: Wait State Select Bit

For a detaileddescription,see common description for the SRWn bitsbelow (EMCUCR

description).

Bit 76543 210

SM0 SRL2 SRL1 SRL0 SRW01 SRW00 SRW11 ISC2 EMCUCR

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bit 6..4 – SRL2, SRL1, SRL0: Wait State Sector Limit

Itispossibletoconfigure different wait statesfordifferent external memory addresses.

The ExternalMemory address space can be divided in two sectors that have separate

wait state bits.The SRL2,SRL1, andSRL0 bitsselectthe splitting of these sectors, see

Table2andFigure11.By default, the SRL2,SRL1, andSRL0 bits are set to zeroand

theentire ExternalMemory address spaceis treated as one sector. When the entire

2512A–AVR–04/02

27

Page 28

SRAM address spaceisconfigured as one sector, the wait states are configuredbythe

SRW11 andSRW10 bits.

Table 2. SectorLimitswithDifferent Settings ofSRL2..0

SRL2 SRL1 SRL0 Sector Limits

000

001

010

011

100

101

110

111

Lowersector=N/A

Uppersector=0x0260 - 0xFFFF

Lowersector=0x0260 - 0x1FFF

Uppersector=0x2000 - 0xFFFF

Lowersector=0x0260 - 0x3FFF

Uppersector=0x4000 - 0xFFFF

Lowersector=0x0260 - 0x5FFF

Uppersector=0x6000 - 0xFFFF

Lowersector=0x0260 - 0x7FFF

Uppersector=0x8000 - 0xFFFF

Lowersector=0x0260 - 0x9FFF

Uppersector=0xA000 - 0xFFFF

Lowersector=0x0260 - 0xBFFF

Uppersector=0xC000 - 0xFFFF

Lowersector=0x0260 - 0xDFFF

Uppersector=0xE000 - 0xFFFF

• Bit 1 and Bit 6 MCUCR – SRW11, SRW10: Wait State Select Bits for Upper

Sector

The SRW11 andSRW10 bitscontrol thenumber ofwait statesfor theuppersector of

the ExternalMemory address space,see Table 3.

• Bit 3..2 – SRW01, SRW00: Wait State Select Bits for Lower Sector

The SRW01 andSRW00 bitscontrol thenumber ofwait statesfor the lowersector of

the ExternalMemory address space,see Table 3.

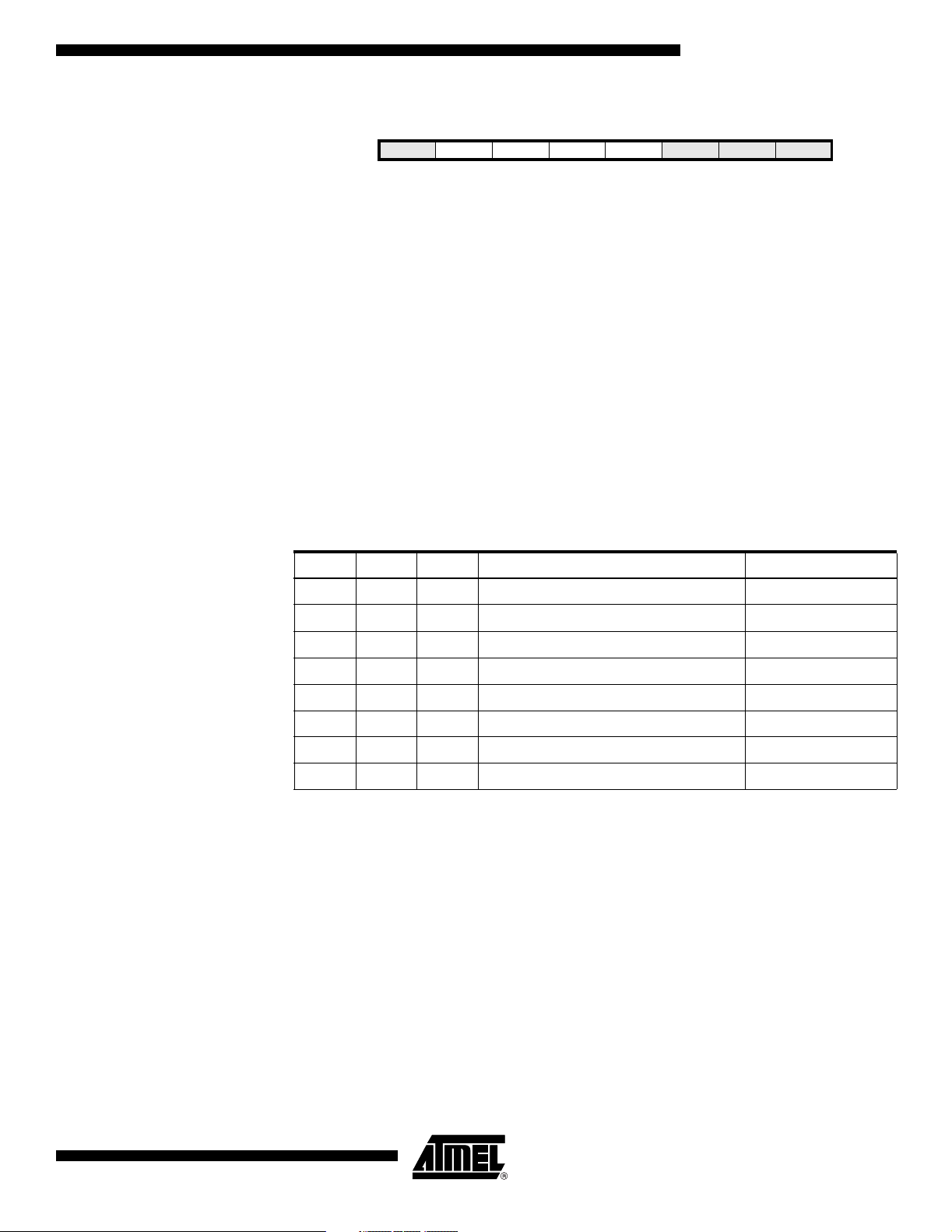

Table 3. Wait States

SRWn1 SRWn0 Wait States

00No wait states.

01Wait one cycle during read/write strobe.

10Wait two cyclesduring read/write strobe.

11

Note: 1. n = 0or 1 (lower/uppersector).

Forfurtherdetails of thetimingandwait states of the ExternalMemory Interface,see

Figure13 to Figure16how the setting of the SRWbits affects the timing.

(1)

Wait two cyclesduring read/write andwait one cycle before driving out

new address.

28

ATmega8515(L)

2512A–AVR–04/02

Page 29

ATmega8515(L)

Special Function IO Register – SFIOR

Bit 76543 210

– XMBK XMM2 XMM1 XMM0 PUD – PSR10 SFIOR

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value000000 00

•Bit6–XMBK: External Memory Bus Keeper Enable

Writing XMBK to one enables the BusKeeper on theAD7:0 lines. When the BusKeeper

is enabled, AD7:0 will keep the last driven value on the lines even if the XMEM interface

has tri-stated the lines. Writing XMBK to zero disables the BusKeeper. XMBK is not

qualifiedwithSRE, soevenif the XMEM interfaceisdisabled, the BusKeepers are still

activated aslong asXMBKis one.

• Bit 6..3 – XMM2, XMM1, XMM0: External Memory High Mask

When the ExternalMemory is enabled, all Port Cpins areusedfor the high address

byte by default. If the full 60KB address spaceis not required to access the External

Memory, some, or all, Port Cpinscan be releasedfor normal PortPinfunction as

described in Table4.Asdescribed in “Using all 64KB Locations ofExternalMemory”on

page 30, it ispossibletousethe XMMn bits to access all 64KB locations of the External

Memory.

Table 4. Port C Pins Released asNormal PortPinswhen the ExternalMemory is

Enabled

XMM2 XMM1 XMM0 # Bits for External Memory Address Released Port Pins

0008(Full 60 KB space)None

0017 PC7

0106 PC7 - PC6

0115 PC7 - PC5

1004 PC7 - PC4

1013 PC7 - PC3

1102 PC7 - PC2

111NoAddress HighbitsFull Port C

2512A–AVR–04/02

29

Page 30

Using all 64KB Locations of External Memory

Sincethe ExternalMemory is mapped after the InternalMemory asshowninFigure11,

only 60KB ofExternalMemory is available by default (address space0x0000 to 0x025F

isreservedforInternalMemory). However, it ispossibletotakeadvantage of the entire

ExternalMemory by masking the higher address bits to zero. Thiscan be done by using

the XMMn bits andcontrolbysoftwarethemost significant bits of theaddress. By setting Port C to output 0x00, andreleasing themost significant bitsfor normal PortPin

operation, the Memory Interface will address 0x0000 - 0x1FFF. See codeexample

below.

Assembly Code Example

; OFFSET is defined to 0x2000 to ensure

; external memory access

; Configure Port C (address high byte) to

; output 0x00 when the pins are released

; for normal Port Pin operation

ldi r16, 0xFF

out DDRC, r16

ldi r16, 0x00

out PORTC, r16

; release PC7:5

ldi r16, (1<<XMM1)|(1<<XMM0)

out SFIOR, r16

; write 0xAA to address 0x0001 of external

; memory

ldi r16, 0xaa

sts 0x0001+OFFSET, r16

; re-enable PC7:5 for external memory

ldi r16, (0<<XMM1)|(0<<XMM0)

out SFIOR, r16

; store 0x55 to address (OFFSET + 1) of

; external memory

ldi r16, 0x55

sts 0x0001+OFFSET, r16

CCode Example

#define OFFSET 0x2000

(1)

(1)

30

void XRAM_example(void)

{

unsigned char *p = (unsigned char *) (OFFSET + 1);

DDRC = 0xFF;

PORTC = 0x00;

SFIOR = (1<<XMM1) | (1<<XMM0);

*p = 0xaa;

SFIOR = 0x00;

*p = 0x55;

}

Note: 1. Theexample codeassumes that the part specificheaderfileis included.

Caremust beexercised using this option as mostof thememory is masked away.

ATmega8515(L)

2512A–AVR–04/02

Page 31

System Clock and Clock Options

ATmega8515(L)

Clock Systems and their Distribution

Figure17presents the principalclock systems in the AVR and theirdistribution. All of

the clocks need not beactive at a given time. Inorder to reduce powerconsumption, the

clocks to modules not being usedcan be haltedbyusing different sleep modes, as

described in “PowerManagement andSleepModes”onpage 38. The clock systems

are detailedbelow.

Figure 17. Clock Distribution

General I/O

Modules

clk

I/O

AVR Clock

Control Unit

CPU Core RAM

clk

CPU

clk

FLASH

Reset Logic

Watchdog Timer

Flash and

EEPROM

CPU Clock – clk

I/O Clock – clk

I/O

CPU

External RC

Oscillator

Source clock

Clock

Multiplexer

External Clock

Crystal

Oscillator

Watchdog clock

Watchdog

Low-frequency

Crystal Oscillator

Oscillator

Calibrated RC

Oscillator

The CPUclock isrouted to parts of the system concernedwith operation of theAVR

core. Examples ofsuch modules arethe General PurposeRegisterFile, the Status Reg-

ister, and the data memory holding the Stack Pointer. Halting the CPUclock inhibits the

core from performing general operations andcalculations.

The I/Oclock is usedbythemajority of the I/O modules, likeTimer/Counters, SPI, and

USART. The I/Oclock is alsousedbythe ExternalInterruptmodule,but note that some

external interrupts are detectedbyasynchronouslogic, allowing such interrupts to be

detected even if the I/Oclock ishalted.

2512A–AVR–04/02

31

Page 32

Flash Clock – clk

FLASH

The Flash clock controls operation of the Flash interface. The Flash clock is usually

active simultaneously with the CPUclock.

Clock Sources The device has the following clock sourceoptions, selectable by Flash Fuse bits as

shown below.The clock from the selectedsourceis input to the AVR clock generator,

androuted to theappropriate modules.

Table 5. Device Clocking OptionsSelect

Device Clocking Option CKSEL3..0

ExternalCrystal/Ceramic Resonator 1111 - 1010

ExternalLow-frequency Crystal 1001

External RCOscillator 1000 - 0101

CalibratedInternal RCOscillator 0100 - 0001

ExternalClock 0000

Note: 1. For all fuses “1” means unprogrammedwhile“0”meansprogrammed.

(1)

Thevariouschoicesfor each clocking option is giveninthe following sections. When the

CPUwakes upfrom Power-downor Power-save, the selectedclock sourceis used to

time the start-up, ensuring stable Oscillator operation beforeinstruction execution starts.

When the CPUstartsfrom Reset, thereis as an additionaldelay allowing the power to

reach a stable levelbefore commencing normal operation. The Watchdog Oscillator is

usedfor timing thisreal-time partof the start-up time. Thenumber ofWDT Oscillator

cycles usedfor each time-out isshowninTable 6.The frequency of the Watchdog Oscillator is voltage dependent asshown in “ATmega8515 TypicalCharacteri stics –

Preliminary Data” on page 204. The deviceisshippedwith CKSEL = “0001” and

SUT = “10” (1 MHz Internal RCOscillator, slowly rising power).

Table 6. Number ofWatchdog Oscillator Cycles

Typ Time-out (VCC= 5.0V) Typ Time-out (VCC= 3.0V) Number of Cycles

4.1 ms 4.3 ms 4K(4,096)

65ms69ms64K65,536)

Crystal Oscillator XTAL1andXTAL2areinput and output,respectively, of an inverting amplifierwhich can

be configuredfor useas an On-chipOscillator, asshowninFigure18.Either a quartz

crystal or a ceramicresonator maybeused.The CKOPT Fuse selectsbetween two different oscillator amplifier modes. When CKOPT isprogrammed, the Oscillator output

will oscillate will a full rail-to-railswingontheoutput. This modeissuitable when operatinginavery noisy environment orwhen theoutput from XTAL2 drives a secondclock

buffer.This mode has a wide frequency range. When CKOPT is unprogrammed, the

Oscillatorhas a smaller output swing. Thisreducespowerconsumption considerably.

This mode has a limitedfrequency range and it can not beused to drive otherclock

buffers.

Forresonators, themaximum frequency is 8 MHz withCKOPT unprogrammed and

16MHzwithCKOPT programmed. C1andC2 should always beequalforbothcrystals

andresonators.Theoptimal value of the capacitors depends on the crystal orresonator

in use, theamountofstraycapacitance, and theelectromagnetic noiseof theenviron-

ment. Some initial guidelinesforchoosing capacitors for use withcrystals aregivenin

Table 7. Forceramicresonators, the capacitor values given by the manufacturershould

beused.

32

ATmega8515(L)

2512A–AVR–04/02

Page 33

Figure 18. CrystalOscillatorConnections

ATmega8515(L)

C2

C1

XTAL2

XTAL1

GND

The Oscillatorcan operateinthree different modes, each optimizedfor a specificfre-

quency range. Theoperating modeisselectedbythe fuses CKSEL3..1 asshownin

Table 7.

Table 7. CrystalOscillatorOperating Modes

Frequency Range

CKOPT CKSEL3..1

1 101

1 110 0.9-3.0 12 - 22

1 111 3.0 - 8.0 12 - 22

0101, 110, 111 1.0 - 12 - 22

Notes: 1. The frequency ranges are preliminary values.Actual values areTBD.

2. This option should not beusedwithcrystals, only withceramicresonators.

(2)

(MHz)

0.4 - 0.9 –

(1)

Recommended Range for Capacitors

C1 and C2 for Use with Crystals (pF)

The CKSEL0 Fuse togetherwith the SUT1..0 fusesselectthe start-up times asshownin

Table8.

Table 8. Start-up Timesfor the CrystalOscillatorClock Selection

Start-up Time

CKSEL0 SUT1..0

0 00 258 CK

0 01 258 CK

010 1KCK

011 1KCK

100 1KCK

101 16K CK – Crystal oscillator,

110 16K CK 4.1 msCrystal oscillator, fast

111 16K CK 65msCrystal oscillator,

from Power-down

(1)

(1)

(2)

(2)

(2)

Additional Delay from

Reset (VCC= 5.0V)

4.1 msCeramicresonator,

65msCeramicresonator,

– Ceramicresonator,

4.1 msCeramicresonator,

65msCeramicresonator,

Recommended

Usage

fast rising power

slowly rising power

BOD enabled

fast rising power

slowly rising power

BOD enabled

rising power

slowly rising power

2512A–AVR–04/02

33

Page 34

Notes: 1. Theseoptionsshould only beusedwhen not operating closetothemaximum fre-

quency of the device, and only iffrequency stability at start-up is not important for the

application. Theseoptions are not suitable forcrystals.

2. Theseoptions are intendedfor use withceramicresonators andwill ensure fre-

quency stability at start-up.Theycan also beusedwithcrystals when not operating

closetothemaximum frequency of the device, and iffrequency stability at start-up is

not important for theapplication.

Low-frequency Crystal Oscillator

To usea32.768 kHz watch crystal as the clock source for the device, the Low-frequency CrystalOscillator must be selectedbysetting the CKSEL Fuses to “1001”. The

crystalshould be connected asshowninFigure18.By programming the CKOPT Fuse,

theusercan enableinternalcapacitors on XTAL1andXTAL2, thereby removing the

needfor externalcapacitors.Theinternalcapacitors have a nominal value of36pF.

When thisOscillator isselected, start-up times are determinedbythe SUT Fuses as

showninTable 9.

Table 9. Start-up Timesfor the Low-frequency CrystalOscillatorClock Selection

Start-up Time

SUT1..0

00 1KCK

01 1KCK

10 32KCK 65msStable frequency at start-up

11 Reserved

Note: 1. Theseoptionsshould only beused iffrequency stability at start-up is not important

from Power-down

(1)

(1)

for theapplication.

Additional Delay from

Reset (VCC= 5.0V) Recommended Usage

4.1 msFast rising power orBOD

enabled

65msSlowly rising power

34

ATmega8515(L)

2512A–AVR–04/02

Page 35

ATmega8515(L)

External RC Oscillator For timing insensitive applications, theexternal RCconfiguration showninFigure19

can beused.The frequency isroughly estimatedbytheequation f=1/(3RC). Cshould

beatleast22pF. By programming the CKOPT Fuse, theusercan enableaninternal

36 pF capacitorbetween XTAL1and GND, thereby removing the needfor an external

capacitor.

Figure 19. External RCConfiguration

V

CC

R

NC

XTAL2

XTAL1

C

GND

The Oscillatorcan operate in fourdifferent modes, each optimizedfor a specificfre-

quency range. Theoperating modeisselectedbythe fuses CKSEL3..0 asshownin

Table 10.

Table 10. External RCOscillatorOperating Modes

CKSEL3..0 Frequency Range (MHz)

0101 - 0.9

0110 0.9-3.0

0111 3.0 - 8.0

1000 8.0 - 12.0

When thisOscillator isselected, start-up times are determinedbythe SUT Fuses as

showninTable 11.

2512A–AVR–04/02

Table 11. Start-up Timesfor the External RCOscillatorClock Selection

Start-up Time

SUT1..0

00 18 CK – BOD enabled

01 18 CK 4.1 msFast rising power

10 18 CK 65msSlowly rising power

11 6CK

Note: 1. This option should not beusedwhen operating closetothemaximum frequency of

from Power-down

(1)

the device.

Additional Delay from

Reset (VCC= 5.0V) Recommended Usage

4.1 msFast rising power orBOD

enabled

35

Page 36

Calibrated Internal RC Oscillator

The calibrated internal RCOscillatorprovides a fixed 1.0, 2.0, 4.0, or 8.0 MHz clock.All

frequencies are nominal values at 5V and 25°C.Thisclock maybe selected as the sys-

tem clock by programming the CKSEL Fuses asshowninTable12.If selected, it will

operate with no externalcomponents.The CKOPT Fuse should always beunprogrammedwhen using thisclock option. During reset,hardware loads the calibration byte

into the OSCCAL Register and thereby automatically calibrates theRCOscillator.At5V,

25°C, and 1.0 MHz Oscillatorfrequency selected, thiscalibration gives a frequency

within ± 1% of the nominalfrequency. When thisOscillator is used as the chipclock, the

Watchdog Oscillatorwill still beusedfor the Watchdog Timer andfor theReset Time-

out. For moreinformation on the pre-programmedcalibration value,see the section

“Calibration Byte” on page 177.

Table 12. InternalCalibrated RCOscillatorOperating Modes

CKSEL3..0 Nominal Frequency (MHz)

(1)

0001

0010 2.0

0011 4.0

0100 8.0

Note: 1. The deviceisshippedwith this option selected.

1.0

When thisOscillator isselected, start-up times are determinedbythe SUT Fuses as

showninTable13. XTAL1andXTAL2 should be leftunconnected(NC).

Oscillator Calibration Register – OSCCAL