Page 1

Features

• Utilizes the AVR

• AVR - High-performance and Low-power RISC Architecture

– 120/121 Powerful Instructions - Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers + Peripheral Control Registers

– Up to 6 MIPS Throughput at 6 MHz

• Data and Nonvolatile Program Memory

– 64K/128K Bytes of In-System Programmable Flash

Endurance: 1,000 Write/Erase Cycles

– 4K Bytes Internal SRAM

– 2K/4K Bytes of In-System Programmable EEPROM

Endurance: 100,000 Write/Erase Cycles

– Programming Lock for Flash Program and EEPROM Data Security

– SPI Interface for In-System Programming

• Peripheral Features

– On-chip Analog Comparator

– Programmable Watchdog Timer with On-chip Oscillator

– Programmable Serial UART

– Master/Slave SPI Serial Interface

– Real Time Counter (RTC) with Separate Oscillator

– Two 8-bit Timer/Counters with Separate Prescaler and PWM

– Expanded 16-bit Timer/Counter system, with Separate Prescaler,

Compare, Capture Modes and Dual 8-, 9-, or 10-bit PWM

– Programmable Watchdog Timer with On-chip Oscillator

– 8-channel, 10-bit ADC

• Special Microcontroller Features

– Low-power Idle, Power Save and Power Down Modes

– Software Selectable Clock Frequency

– External and Internal Interrupt Sources

• Specifications

– Low-power, High-speed CMOS Process Technology

– Fully Static Operation

• Power Consumption at 4 MHz, 3V, 25°C

– Active: 5.5 mA

– Idle Mode: 1.6 mA

– Power Down Mode: < 1 µA

• I/O and Packages

– 32 Programmable I/O Lines, 8 Output Lines, 8 Input Lines

– 64-pin TQFP

• Operating Voltages

– 2.7 - 3.6V (ATmega603L and ATmega103L)

– 4.0 - 5.5V (ATmega603 and ATmega103)

• Speed Grades

– 0 - 4 MHz (ATmega603L and ATmega103L)

– 0 - 6 MHz (ATmega603 and ATmega103)

®

RISC Architecture

8-bit

Microcontroller

with 64K/128K

Bytes In-System

Programmable

Flash

ATmega603

ATmega603L

ATmega103

ATmega103L

Preliminary

Rev. 0945D–06/99

1

Page 2

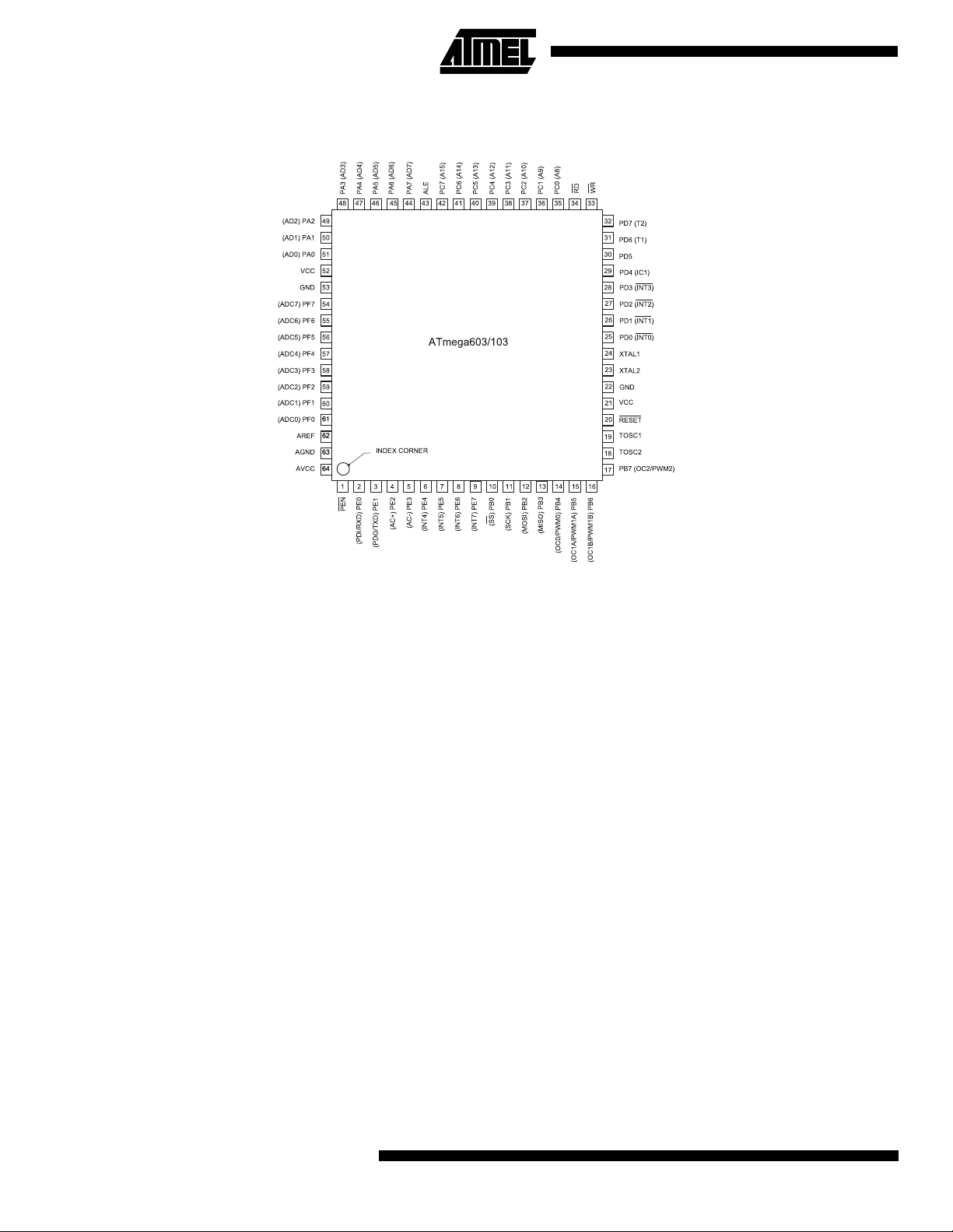

Pin Configuration

TQFP

Description

The ATmega603/103 is a low-power CM OS 8-bit microc ontroller based on the AVR RISC architectur e. By executing

powerful instructions in a single clock cycle, the ATmega603/103 achieves throughputs approaching 1 MIPS per MHz

allowing the system designer to optimize power consumption versus processing speed.

The AVR core is based on an enhanced RISC architecture that combines a rich instruction set wi th 32 general purpose

working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent

registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code

efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega603/103 provides the following features: 64K/128K bytes of In-system Programmable Flash, 2K/4K bytes

EEPROM, 4K by tes S RAM, 32 g eneral pur pose I/O li nes, 8 In put l ines , 8 Ou tput l ines , 32 genera l pur pos e work ing registers, Real Time Counter (RTC), 4 flexible timer/counters with compare modes and PWM, UART, programmable Watchdog

Timer with internal oscillator, an SPI serial port and three software selectable power saving modes. The Idle Mode stops

the CPU while allowing the SRAM, timer/counters, SPI port and interrupt system to continue functioning. The Power Down

mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Power Sav e m ode , the tim er osci ll ato r con tin ues to ru n, al lo win g the us er to m ai ntai n a tim er base while the

rest of the device is sleeping.

The device is manu factured using At mel’s hig h-densi ty nonv olatile m emory technolog y. The on-c hip ISP Flas h allow s the

program memory to be reprogrammed in-system through a serial interface or by a conventional nonvolatile memory programmer. By combining an 8-bit RISC CPU with a large array of ISP Flash on a monolithic chip, the Atmel ATmega603/103

is a powerful mi crocontroller that provides a highly flex ible and cos t effective sol ution to many e mbedded contr ol

applications.

The ATmega603/103 AVR is supported with a full suite of program and system development tools including: C compilers,

macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

2

ATmega603/103

Page 3

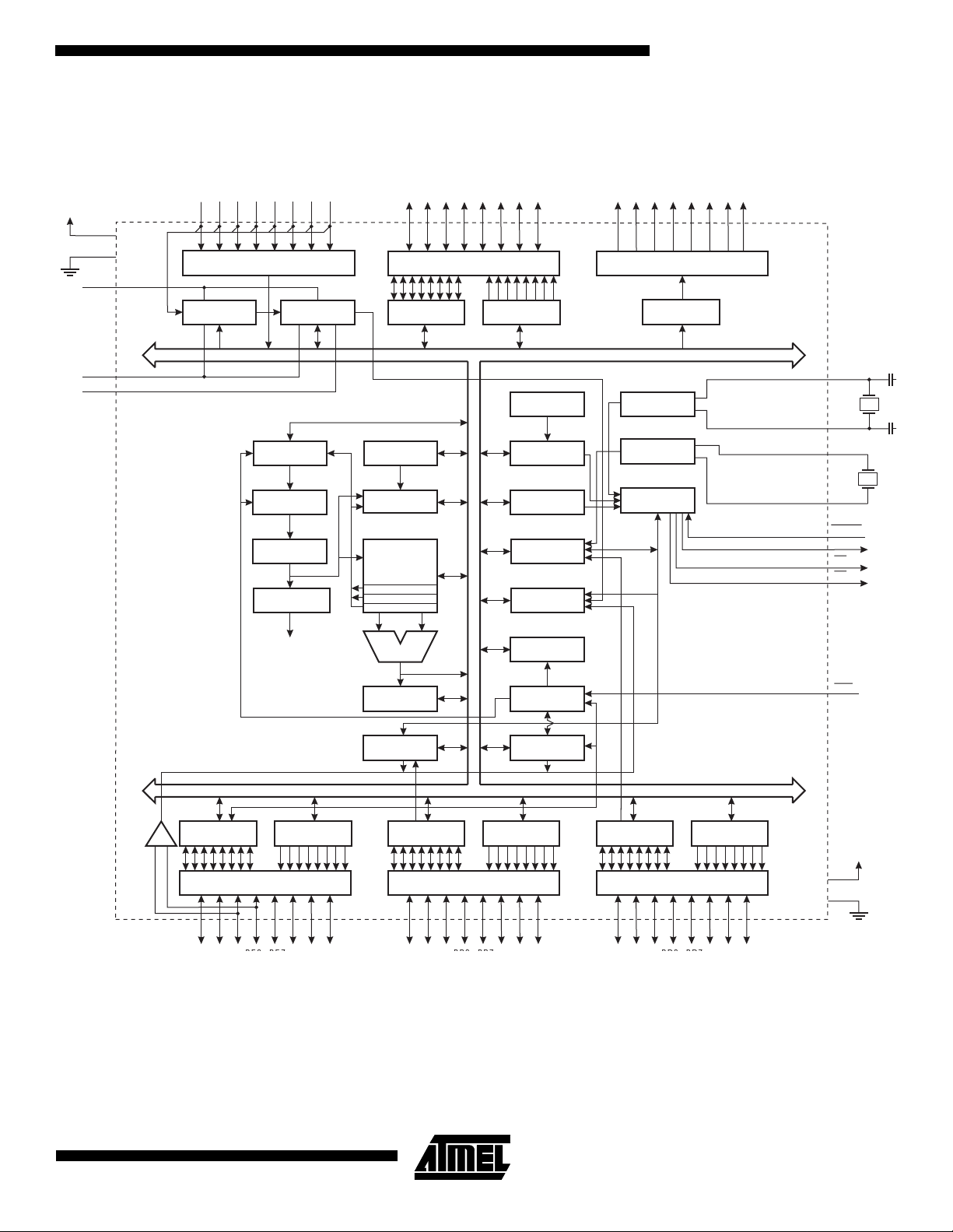

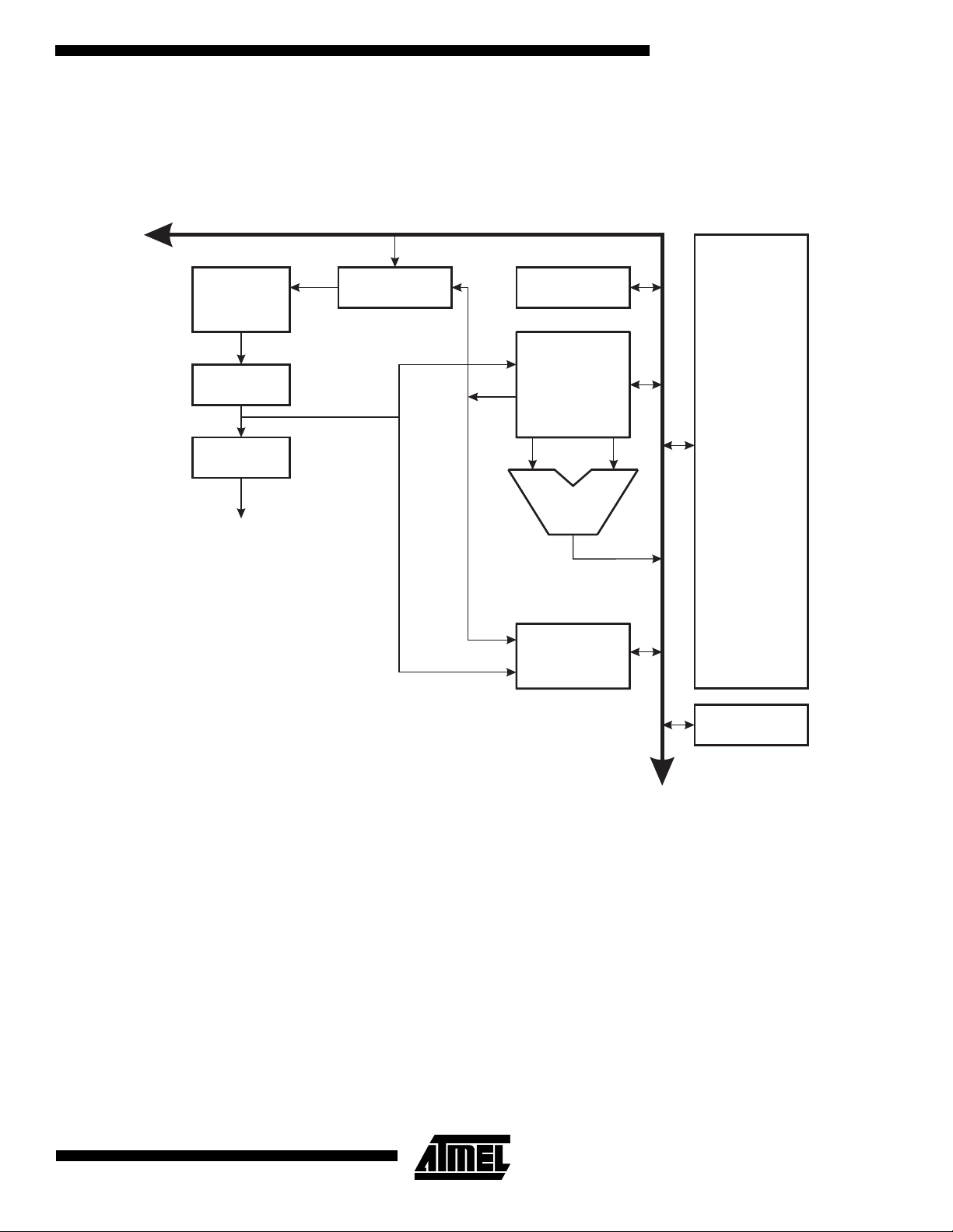

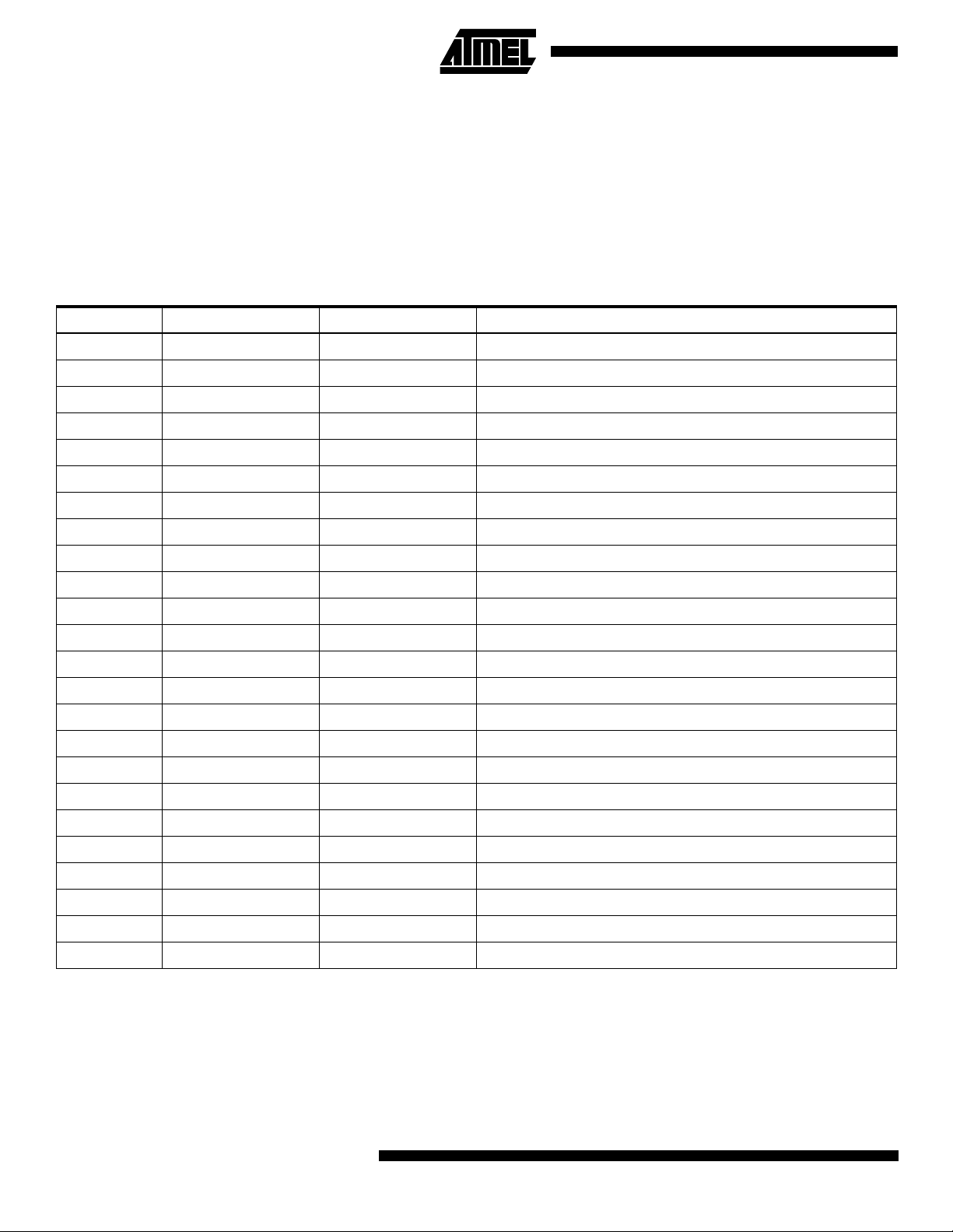

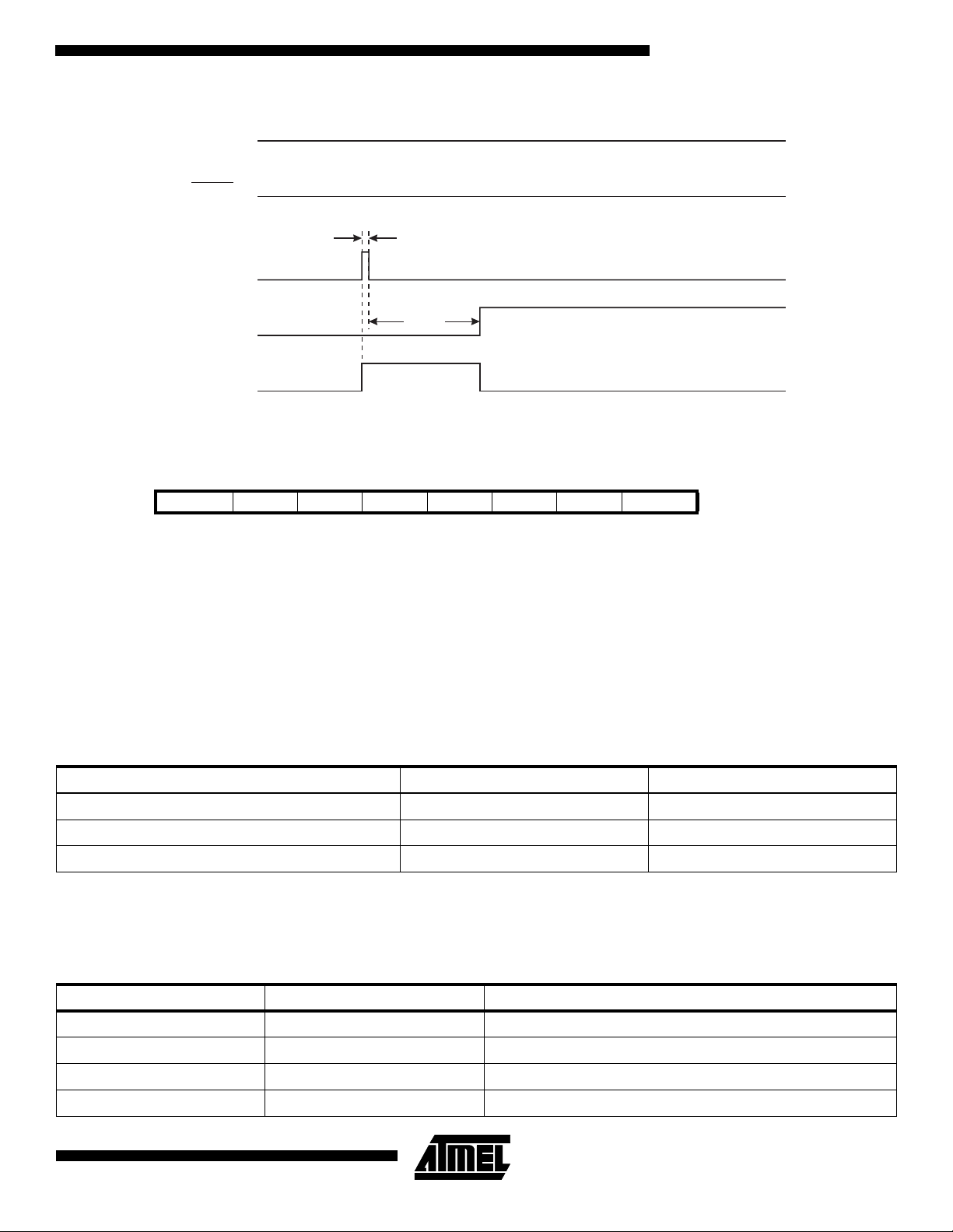

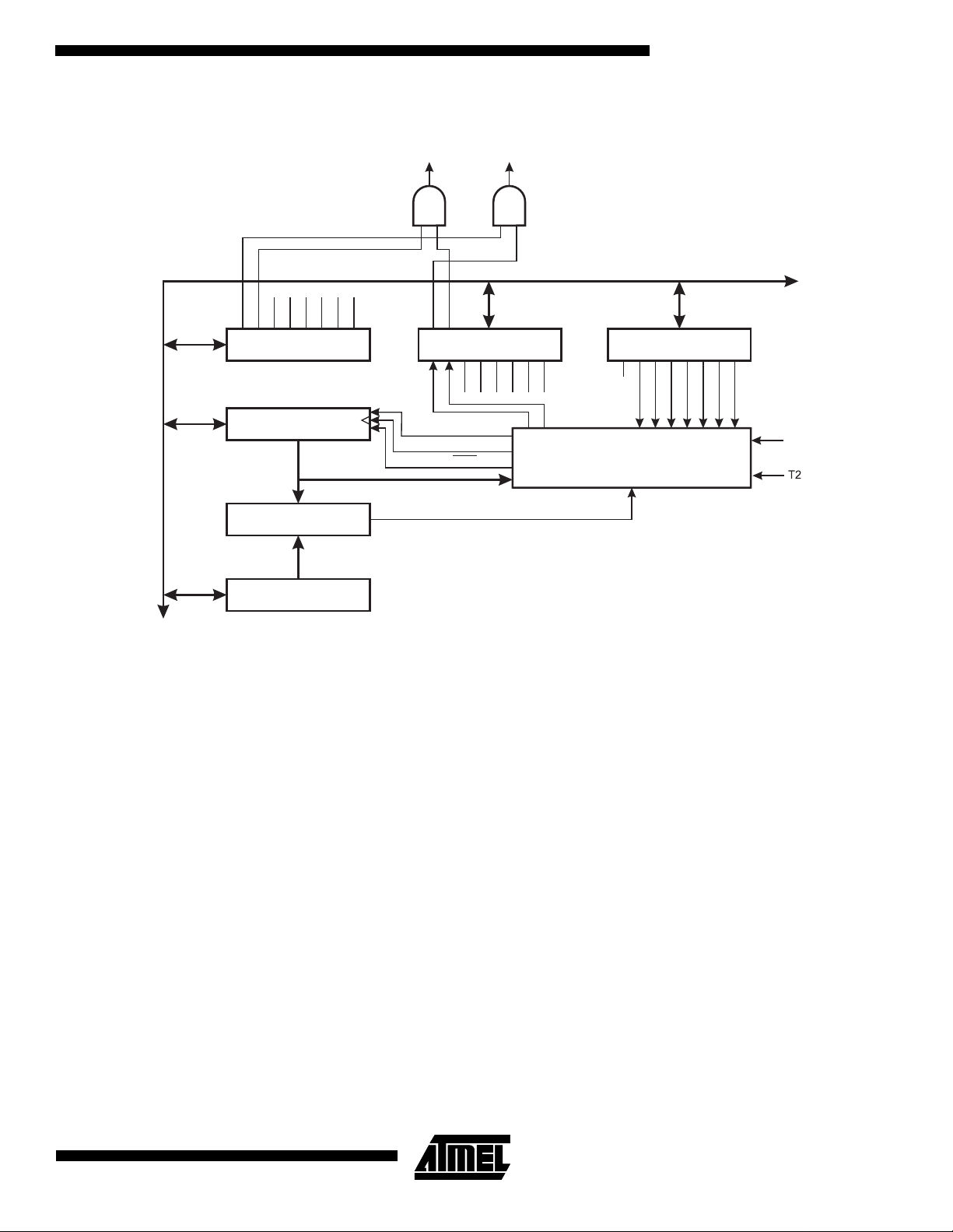

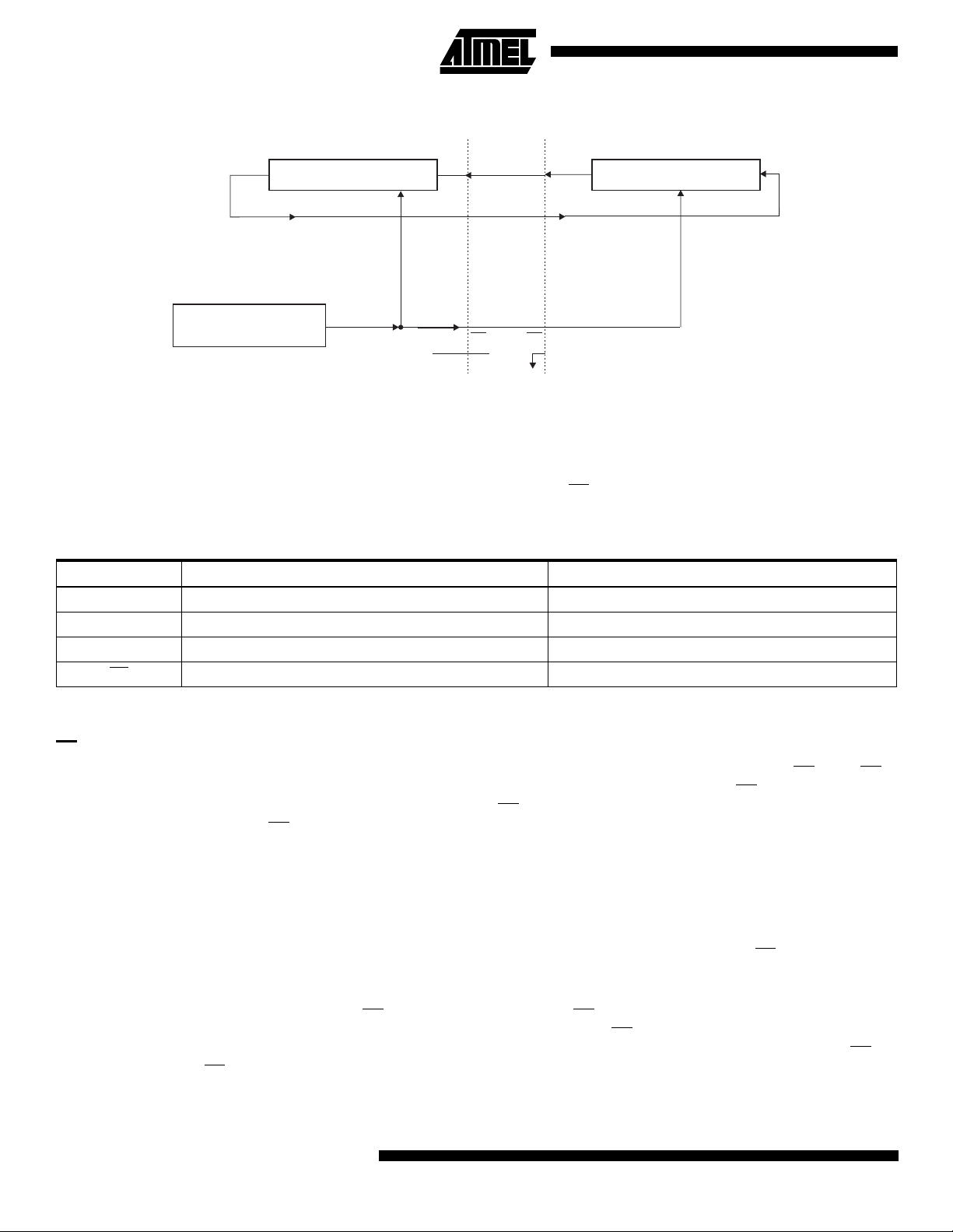

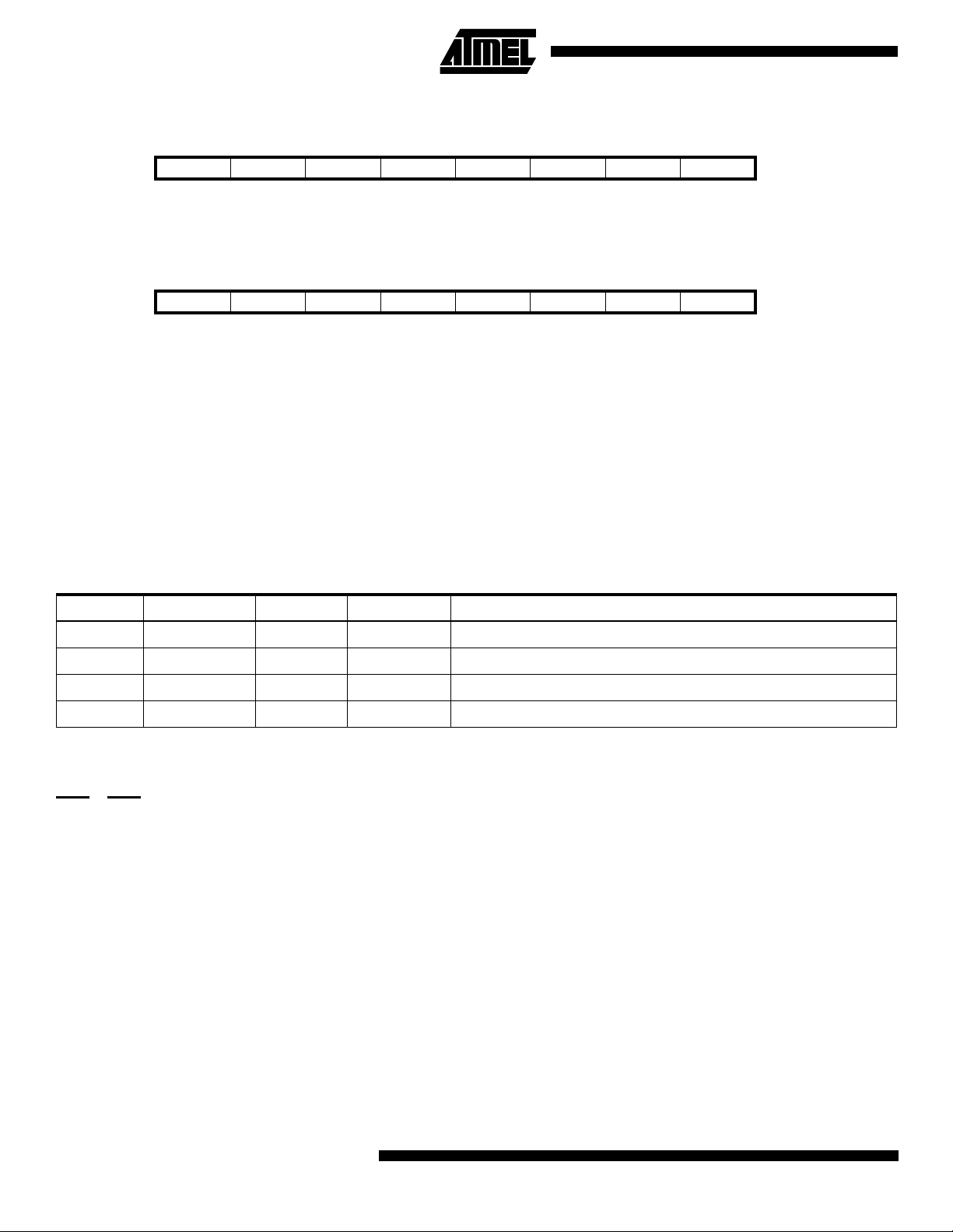

Block Diagram

Figure 1. The ATmega603/103 Block Diagram

VCC

GND

AVCC

PORTF BUFFERS

ANALOG MUX ADC

PORTA DRIVER/BUFFERS

DATA REGISTER

PORTA

DATA DIR.

REG. PORTA

8-BIT DATA BUS

ATmega603/103

PORTC DRIVERS

DATA REGISTER

PORTC

AGND

AREF

PROGRAM

COUNTER

PROGRAM

FLASH

INSTRUCTION

REGISTER

INSTRUCTION

DECODER

CONTROL

LINES

STACK

POINTER

SRAM

GENERAL

PURPOSE

REGISTERS

X

Y

Z

ALU

STATUS

REGISTER

SPI

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

MCU CONTROL

REGISTER

TIMER/

COUNTERS

INTERRUPT

UNIT

EEPROM

PROGRAMMING

LOGIC

UART

OSCILLATOR

OSCILLATOR

TIMING AND

CONTROL

XTAL1

XTAL1

TOSC2

TOSC1

RESET

ALE

WR

RD

PEN

ANALOG

COMPARATOR

DATA REGISTER

+

-

PORTE

DATA DIR.

REG. PORTE

DATA REGISTER

PORTB

PORTB DRIVER/BUFFERSPORTE DRIVER/BUFFERS

DATA DIR.

REG. PORTB

DATA REGISTER

PORTD

PORTD DRIVER/BUFFERS

DATA DIR.

REG. PORTD

VCC

GND

3

Page 4

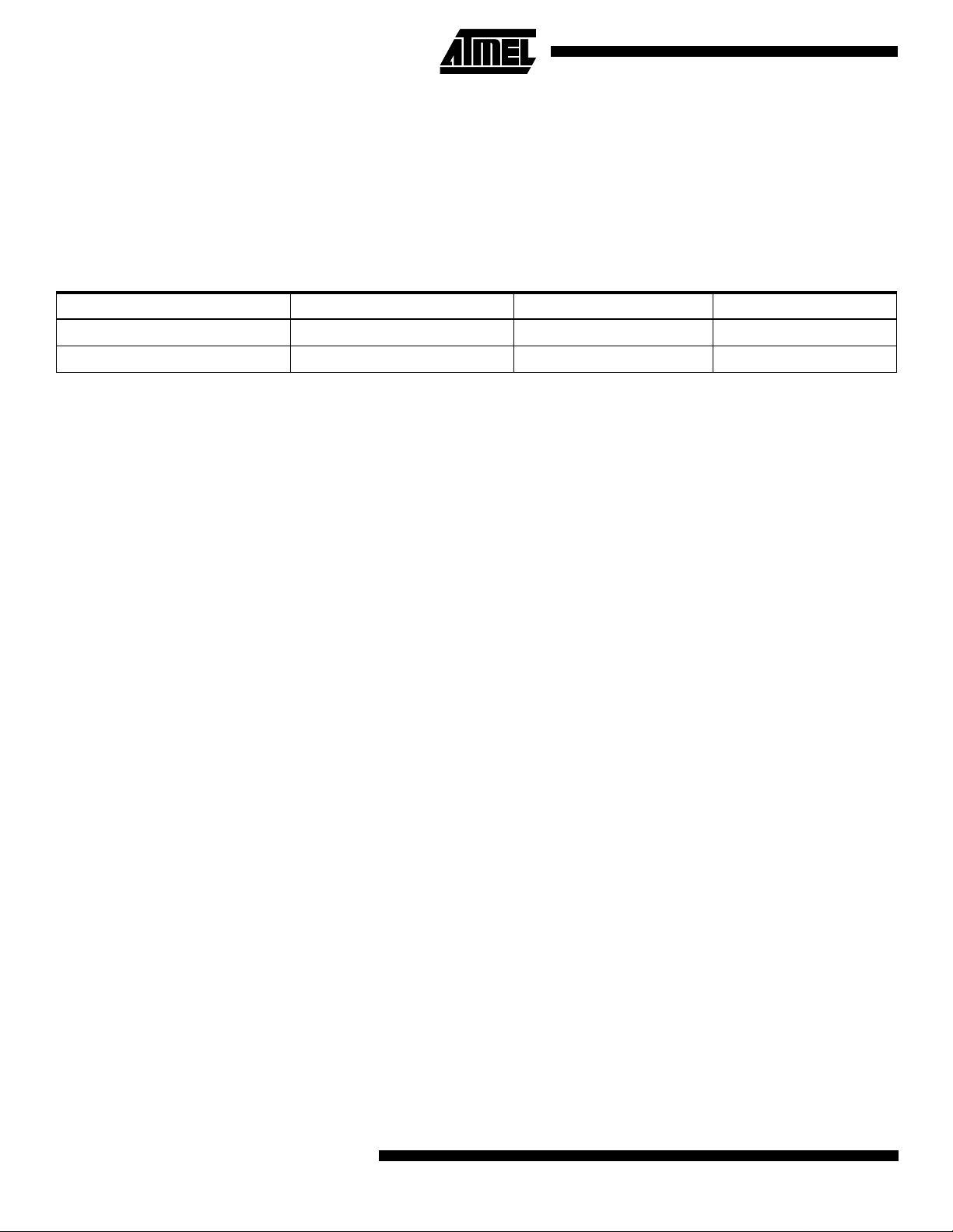

Comparison Between ATmega603 and ATmega103

The ATmega603 has 64K bytes of In-System Programmable Flash, 2K bytes of EEPROM, and 4K bytes of internal SRAM.

The ATmega603 does not have the ELPM instruction.

The ATmega103 has 128K bytes of In-System Programmable Flash, 4K bytes of EEPROM, and 4K bytes of internal

SRAM. The ATmega103 has the ELPM instruction, necessary to reach the upper half of the F lash memory for constant

table lookup.

Table 1 summarizes the different memory sizes for the two devices.

Table 1. Memory Size Summary

Part Flash EEPROM SRAM

ATmega603 64K bytes 2K bytes 4K bytes

ATmega103 128K bytes 4K bytes 4K bytes

Pin Descriptions

VCC

Supply voltage

GND

Ground

Port A (PA7..PA0)

Port A is an 8-bit bi-directional I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The Port A

output buffers can si nk 20 mA and can dr ive LED disp lays direc tly. When pins PA 0 to PA7 are used as inputs and ar e

externally pulled low, they will source current if the internal pull-up resistors are activated.

Port A serves as Multiplexed Address/Data bus when using external SRAM.

The port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B (PB7..PB0)

Port B is an 8-bi t bi -dir ec ti ona l I/O p or t wi th in ter nal pull-up resistors. The Po rt B ou tput bu ffer s can si nk 2 0 m A. A s inp uts ,

Port B pins that are externally pulled low, will source current if the pull-up resistors are activated.

Port B also serves the functions of various special features.

The port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port C (PC7..PC0)

Port C is an 8-bit Output port. The Port C output buffers can sink 20 mA.

Port C also serves as Address output when using external SRAM.

Since Port C is an output only port, the port C pins are not tri-stated when a reset condition becomes active.

Port D (PD7..PD0)

Port D is an 8-bit bi-di r ectio nal I/O port with internal pull-up resi st or s. The P or t D ou tput buff er s can si nk 20 m A. A s inp uts ,

Port D pins that are externally pulled low will source current if the pull-up resistors are activated.

Port D also serves the functions of various special features.

The port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

4

ATmega603/103

Page 5

ATmega603/103

Port E (PE7..PE0)

Port E is an 8-bi t bi - direc ti ona l I/O p or t wi th in ter nal p ull -up resistors. The Po rt E ou tput bu ffer s c an si nk 2 0 m A. A s inp uts,

Port E pins that are externally pulled low will source current if the pull-up resistors are activated.

Port E also serves the functions of various special features.

The port E pins are tri-stated when a reset condition becomes active, even if the clock is not running

Port F (PF7..PF0)

Port F is an 8-bit Input port. Port F also serves as the analog inputs for the ADC.

RESET

Reset input. An exter nal res et is gen erate d by a lo w le vel on the RESET pin. Res et p ul ses l on ger th an 5 0 n s w ill g ener a te

a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.

XT AL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

XT AL2

Output from the inverting oscillator amplifier

TOSC1

Input to the inverting Timer/Counter oscillator amplifier

TOSC2

Output from the inverting Timer/Counter oscillator amplifier

WR

External SRAM Write Strobe.

RD

External SRAM Read Strobe.

ALE

ALE is the Address Latch Enable used when the Exter nal Memory is enabled. The ALE strobe is used to latc h the loworder address (8 bits) into an address latch during the first access cycle, and the AD0-7 pins are used for data during the

second access cycle.

AVCC

This is the supply voltage to the A /D Con verte r. It sho ul d be exter na lly c onn ec ted to V

for details on operation of the ADC.

AREF

This is the analog reference input for the ADC converter. For ADC operations, a voltage in the range AGND to AVCC must

be applied to this pin.

AGND

If the board has a separate ana log ground plane, this pin should be con nec ted to thi s gro und pla ne. Ot he rwis e, c onn ec t to

GND.

via a low-pass filter. See page 66

CC

PEN

This is a programming ena ble pin for the low-v oltage serial program ming mo de. By holdin g this pin low during a power -on

reset, the device will enter the serial programming mode. PEN

has no function during normal operation.

5

Page 6

Clock Options

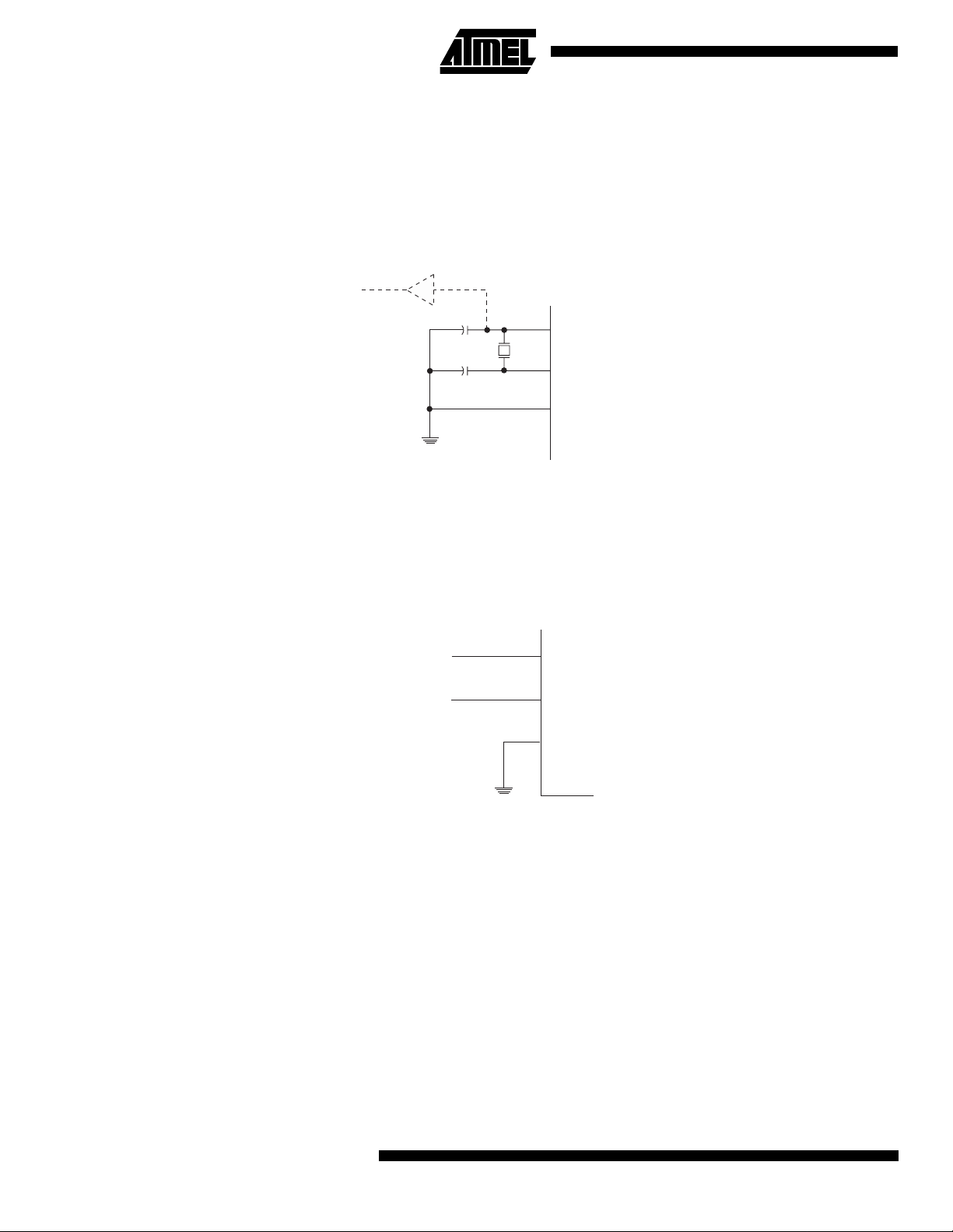

Crystal Oscillator

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an onchip oscillator, as shown in Figure 2. Either a quartz crystal or a ceramic resonator may be used.

Figure 2. Oscillator Conn ec tion s

MAX 1 HC BUFFER

HC

C2

C1

Note: When using the MCU Oscillator as a clock for an external device, an HC buffer should be connected as indicated in the figure.

XTAL2

XTAL1

GND

External Clock

To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in

Figure 3.

Figure 3. External Clock Drive Configuration

NC

EXTERNAL

OSCILLATOR

SIGNAL

XTAL2

XTAL1

GND

Timer Oscillator

For the Timer Oscillator pins, TOSC1 and TOSC2, the crystal is connected directly between the pins. No external capacitors are needed. The os ci ll ator is o pti miz ed fo r us e with a 32 ,768 Hz watc h cr ysta l. A n e xte rnal c lo ck s ig nal a pplied to this

pin goes through the same amplifier having a bandwidth of 256 kHz. The external clock signal should therefore be in the

range 0 Hz - 256 kHz.

6

ATmega603/103

Page 7

Architectural Overview

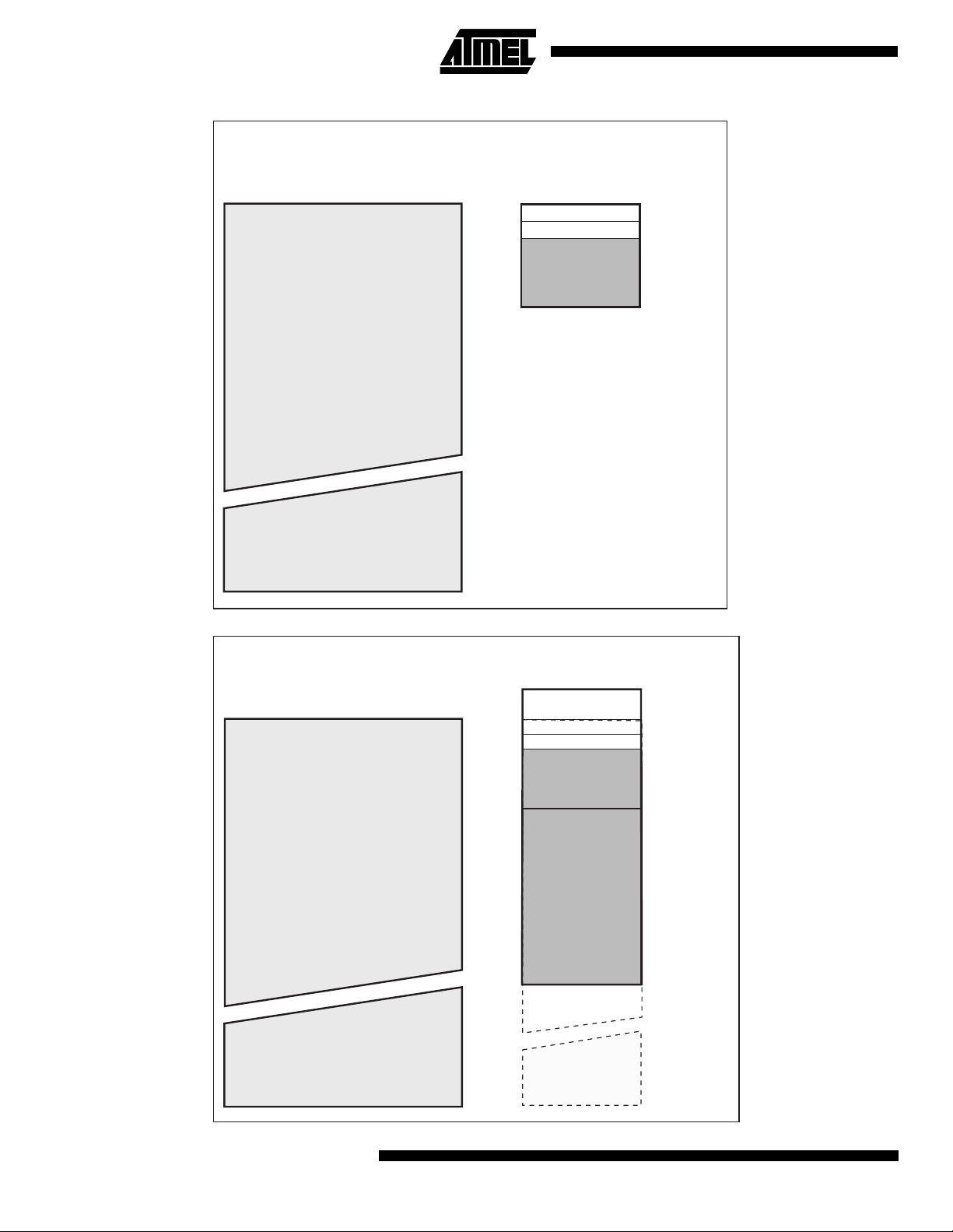

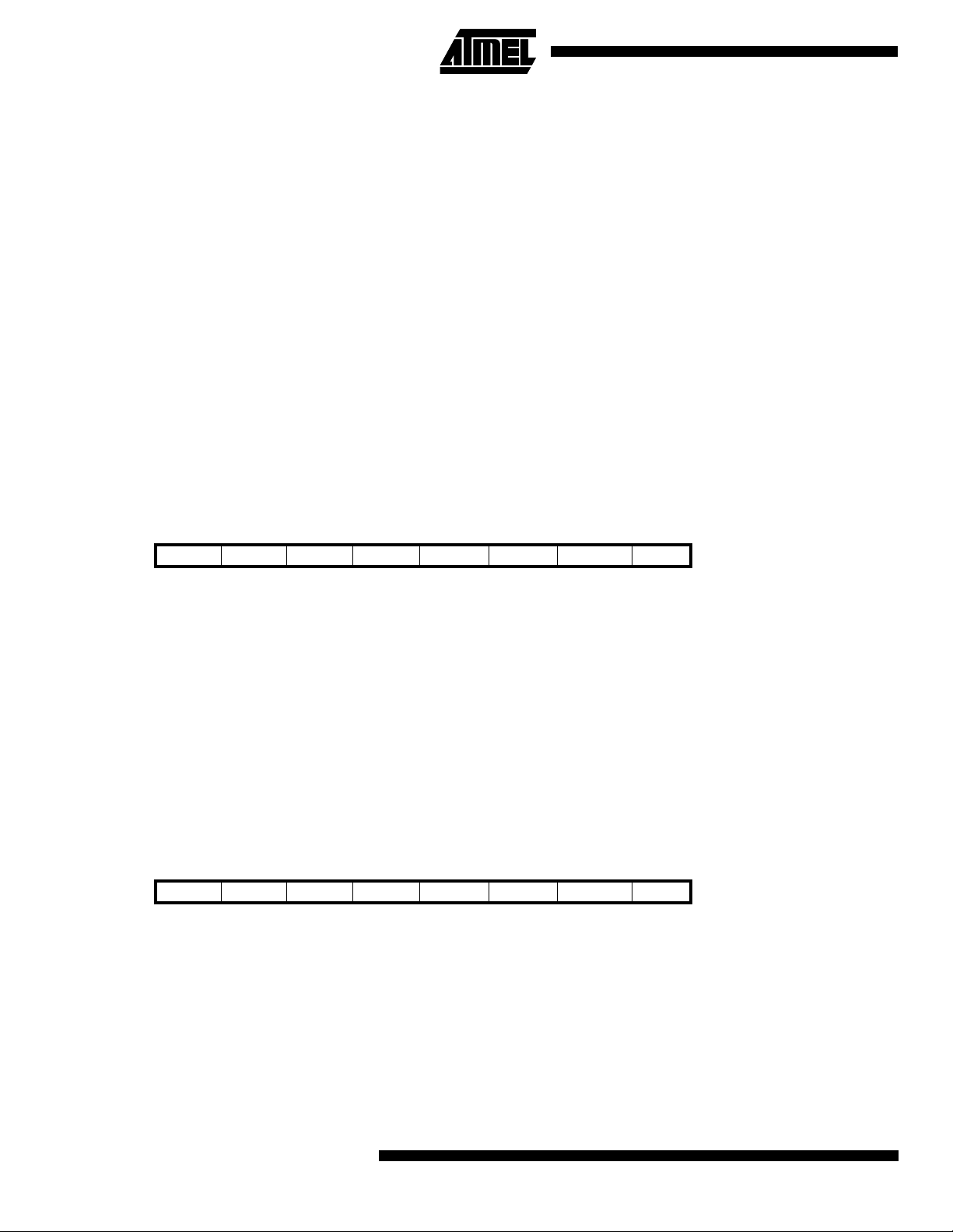

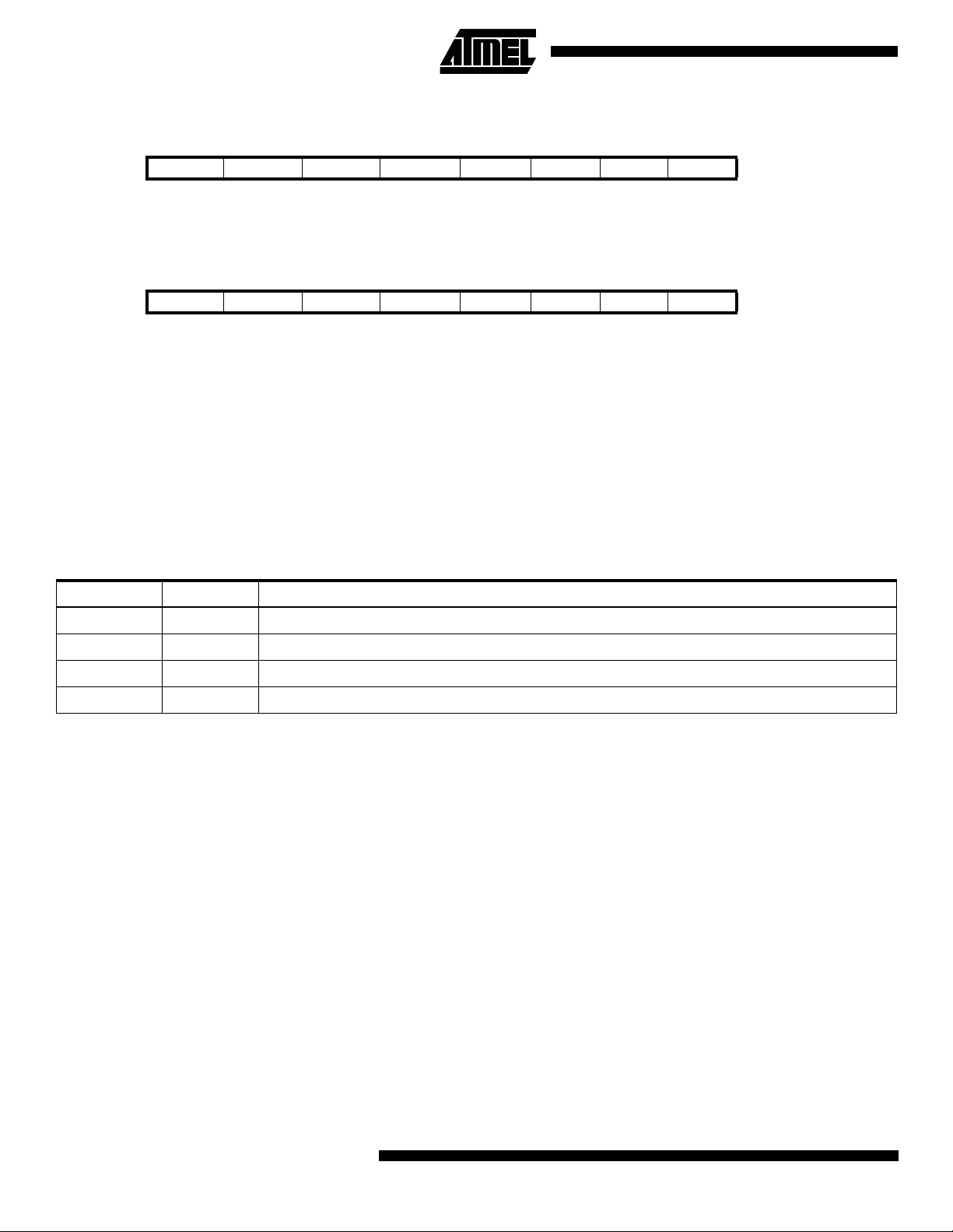

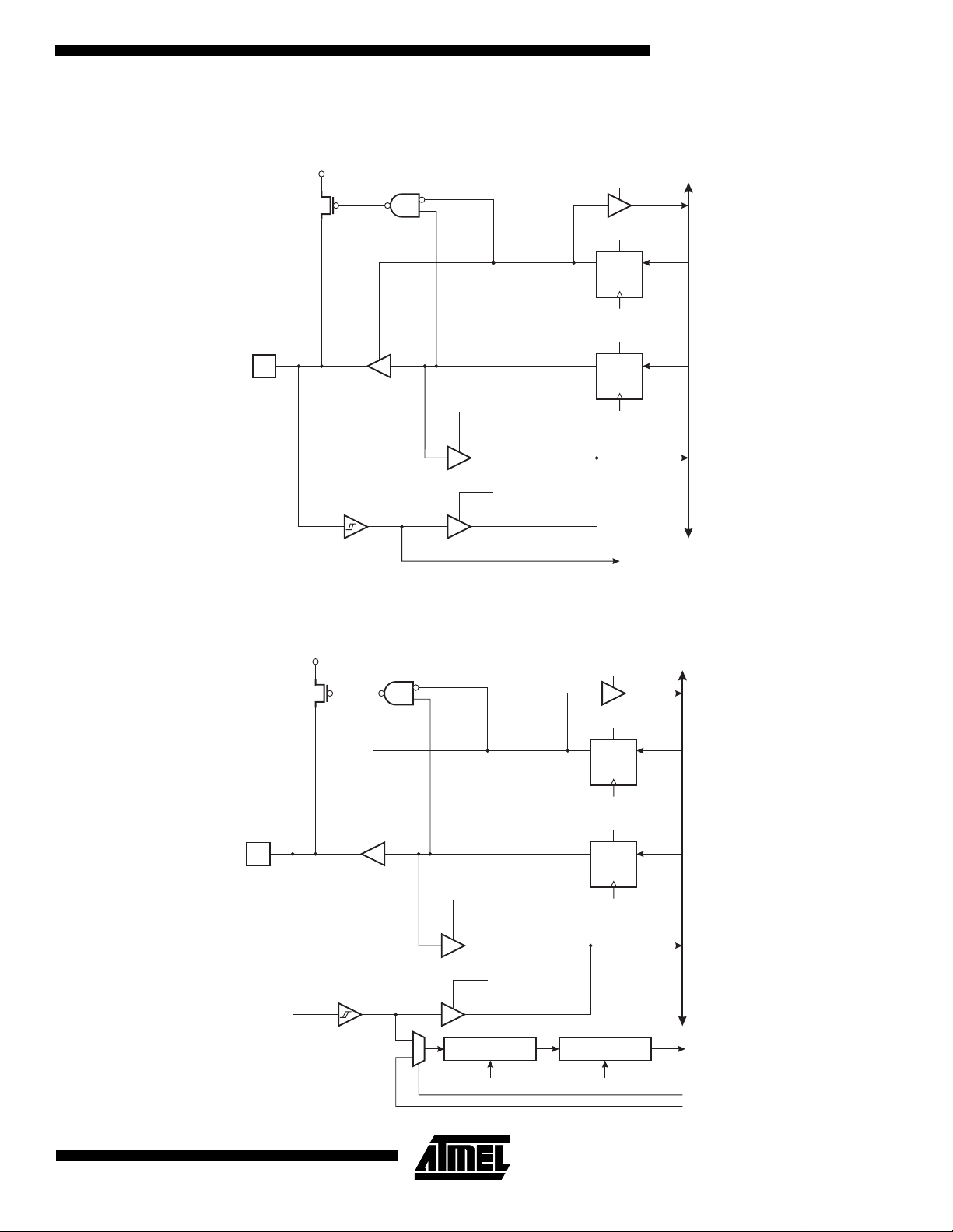

Figure 4. The ATmega603/103 AVR RISC Architecture

AVR ATmega603/103 Architecture

ATmega603/103

Data Bus 8-bit

32K/64K x 16

Program

Memory

Instruction

Register

Instruction

Decoder

Control Lines

Program

Counter

DirectAddressing

Status

and Test

32 x 8

General

Purpose

Registers

Peripherals

ALU

IndirectAddressing

4K x 8

Data

SRAM

2K/4K x 8

EEPROM

The AVR uses a Harvard architecture concept - with separate memories and buses for program and data. The program

memory is accesses with a single level pipeline. While one instruction is being executed, the next instruction is pre-fetched

from the program me mor y. This co nc ept enables instructio ns to be executed in ever y cl ock cycle. The program me mor y is

in-system programmable Flash memory. With a few exceptions, AVR instructions have a single 16-bit word format,

meaning that every program memory address contains a single 16-bit instruction.

During interrupts and subroutine c alls, the ret urn address program counter (PC) is stor ed on the st ack. The stac k is

effectively allocated in the general data SRAM, and consequently the sta ck siz e i s onl y limi ted by the total SRAM si z e an d

the usage of the SRAM. All user programs must initialize the SP in the reset routine (before subroutines or interrupts are

executed). The 16-bit stack pointer SP is read/write accessible in the I/O space.

The 4000 bytes da ta SRAM can be easily ac cessed th rough the f ive dif ferent ad dressing modes sup ported in t he AVR

architecture.

7

Page 8

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status

register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the

program memory. Th e diffe rent in terrupts have priority in a ccordan ce wit h thei r interr upt vect or pos ition. T he lo wer th e

interrupt vector address, the higher the priority.

The memory spaces in the AVR architecture are all linear and regular memory maps.

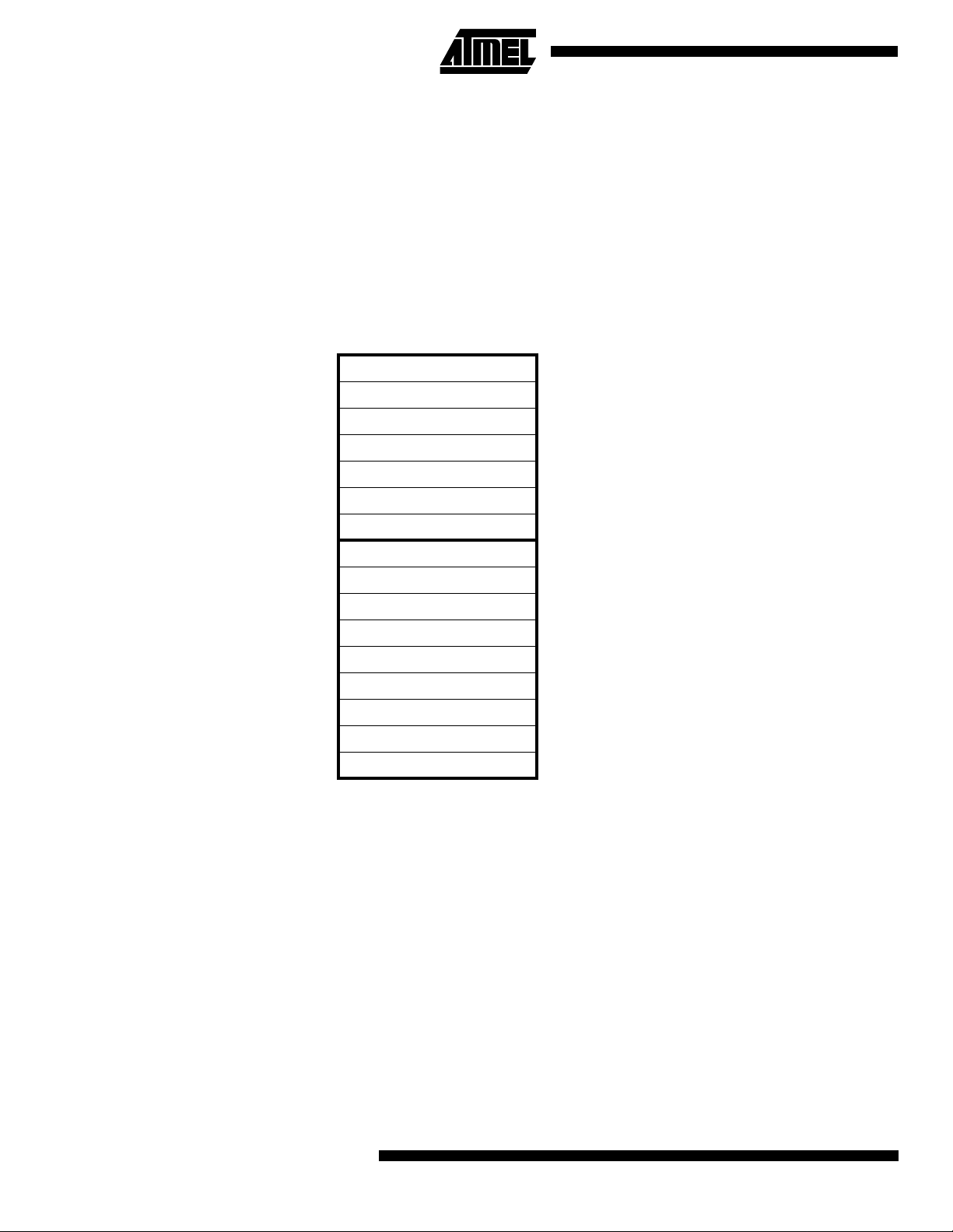

General Purpose Register File

Figure 5 shows the structure of the 32 general purpose working registers in the CPU.

Figure 5. AVR CPU General Purpose Working Registers

7 0 Addr.

R0 $00

R1 $01

R2 $02

. . .

R13 $0D

General R14 $0E

Purpose R15 $0F

Working R16 $10

Registers R17 $11

. . .

R26 $1A X-register low byte

R27 $1B X-register high byte

R28 $1C Y-register low byte

R29 $1D Y-register high byte

R30 $1E Z-register low byte

R31 $1F Z-register high byte

All the register opera ting instructi ons in the instructio n set have direct and single cycle access to all registe rs. The only

exception is the five consta nt arithme tic and logic in struction s SBCI, SUBI, CPI, ANDI and ORI betwe en a constan t and a

register and the LDI i nstruc tion f or load imm ediate consta nt data . Th ese ins tructi ons a pply to the s econ d hal f of t he regi sters in the register file - R16..R31. The general SBC, SUB, CP, AND and OR and all other operations between two registers

or on a single register apply to the entire register file.

As shown in Figure 5, each register is als o assigned a data memory addr ess, mapping them directly into the first 32

locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization

provides great flexibility in access of the registers, as the X,Y and Z registers can be set to index any register in the file.

The 4K bytes of SRAM available for general data are implemented as addresses $0060 to $0FFF.

8

ATmega603/103

Page 9

ATmega603/103

X-register, Y-register and Z-register

The registers R26..R 31 ha ve some a dded funct ions to th eir general pur pose us age. These regis ters a re a ddress poi nters

for indirect addressing of the SRAM. The three indirect address registers X, Y and Z are defined as:

Figure 6. X, Y and Z Registers

15 0

X - register 7 0 7 0

R27 ($1B) R26 ($1A)

15 0

Y - register 7 0 7 0

R29 ($1D) R28 ($1C)

15 0

Z - register 7 0 7 0

R31 ($1F) R30 ($1E)

In the different addr essing modes these addres s re gisters have fu nctio ns as fixed displ acement, automat ic i ncremen t and

decrement (see the descriptions for the different instructions).

ALU - Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a

single clock cy cl e, AL U operations between r egis ter s in the re gis te r f il e ar e exec uted . The ALU operations are div i ded in to

three main categories - arithmetic, logical and bit-functions.

ISP Flash Program Memory

The ATmega603/103 contains 64K/128K bytes on-chip In-system Programmable Flash memory for program storage.

Since all instructio ns are single or dou ble 16-bit word s, the Flash is orga nized as 64K x 16. The Flash memory has an

endurance of at least 1000 write/erase cycles.

Constant tables can be allocated in the entire program memory space (see the LPM - Load Program Memory and ELPM

Extended Load Program Memory instruction descriptions).

SRAM Data Memory

The ATmega603/103 supports two different configurations for the SRAM data memory as listed in the following table:

Table 2. Memory Configurations

Configuration Internal SRAM Data Memory External SRAM Data Memory

A 4000 None

B 4000 up to 64K

Note: When using 64K of External SRAM, 60K will be available.

9

Page 10

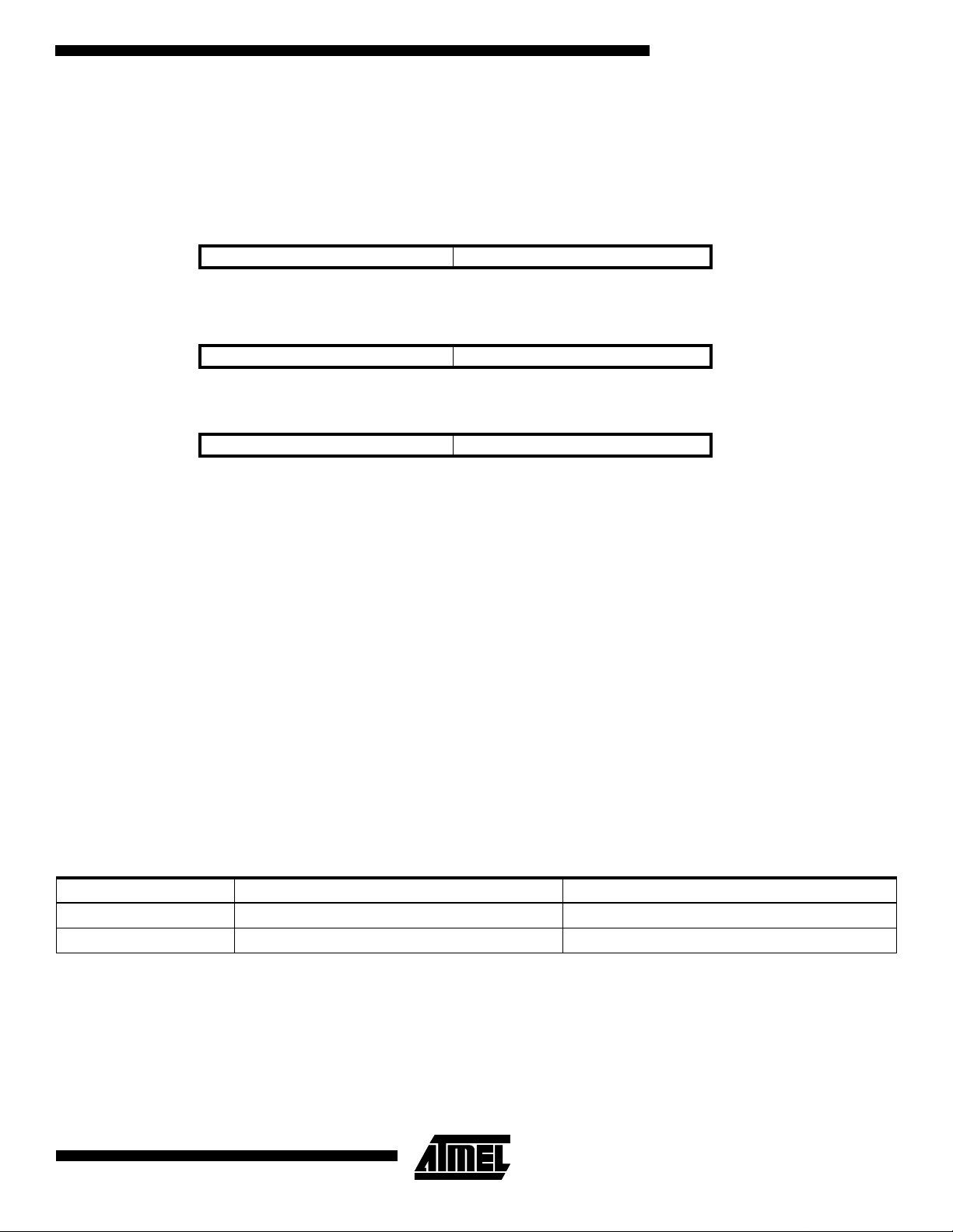

Figure 7. Memory Configurations

Memory Configuration A

Program Flash

(32K/64K x 16)

$0000

Data MemoryProgram Memory

32 Registers

64 I/O Registers

Internal SRAM

(4000 x 8)

$0000 - $001F

$0020 - $005F

$0060

$0FFF

Memory Configuration B

Program Memory

Program Flash

(32K/64K x 16)

$7FFF/$FFFF

$0000

Data Memory

32 Registers

64 I/O Registers

Internal SRAM

(4000 x 8)

External SRAM

(0 - 64K x 8)

$0000 - $001F

$0020 - $005F

$0060

$0FFF

$1000

10

ATmega603/103

$7FFF/

$FFFF

$FFFF

Page 11

ATmega603/103

The 4096 first Data Memory locations address both the Register file, the I/O Memory and the internal data SRAM. The first

96 locations address the register file and I/O memory, and the next 4000 locations address the internal data SRAM.

An optional external data SRAM can be used with the ATmega603/103. This SRAM will occupy an area in the remaining

address locations in the 64K ad dr ess s pa ce . Thi s a rea s tarts at t he a ddr es s fol lowing the internal SRAM. If a 64K ex terna l

SRAM is used, 4K of the external memory is lost as the addresses are occupied by internal memory.

When the addresses accessing the SRAM memory space exceeds the internal data memory locations, the external data

SRAM is accesse d using t he sam e ins tructio ns as for the inter nal da ta memo ry acces s. W hen the internal data m emor ies

are accessed, the read and write strobe pins (RD

operation is enabled by setting the SRE bit in the MCUCR register.

Accessing external SRAM takes one additional clock cycle per byte compared to access of the internal SRAM. This means

that the commands LD, ST, LDS, STS, PUSH and POP take one additional clock cycle. If the stack is placed in external

SRAM, interrupts, subroutine call s and returns take two clock cycles extra because the two- byte program counter is

pushed and popped. When external SRAM interface is used with wait state, two additional clock cycles is used per byte.

This has the following e ffec t: Da ta tran sfer instructions take two extr a cl oc k cy c les, wh er eas in terr upt, su br outine c al ls an d

returns will need four clock cycles more than specified in the instruction set manual.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with

Pre-Decrement and Indirect with Post-Increment. In the register file, registers R26 to R31 feature the indirect addressing

pointer registers.

The Indirect with Displacement mode features a 63 address locations reach from the base address given by the Y or

Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X,

Y and Z are decremented and incremented.

The entire data addres s sp ac e in cl ud ing the 32 gene ra l p ur pose wor ki ng regis te rs an d th e 64 I/O r egi s ters ar e al l ac cess ible through all these addressing modes. See the next section for a detailed description of the different addressing modes.

and WR) are inactive during the whole acce ss cycle. Ex ternal SRA M

Program and Data Addressing Modes

The ATmega603/103 AV R RISC microco ntroller supports po werful and effi cient addressing modes for acc ess to the

program memory (Flash) and data memory ( SRAM, Register File and I/O M emory). This se ction descr ibes the different

addressing modes suppor ted by the AVR a rchitectur e. In the f igures, OP means the o peration code par t of th e ins tructio n

word. To simplify, not all figures show the exact location of the addressing bits.

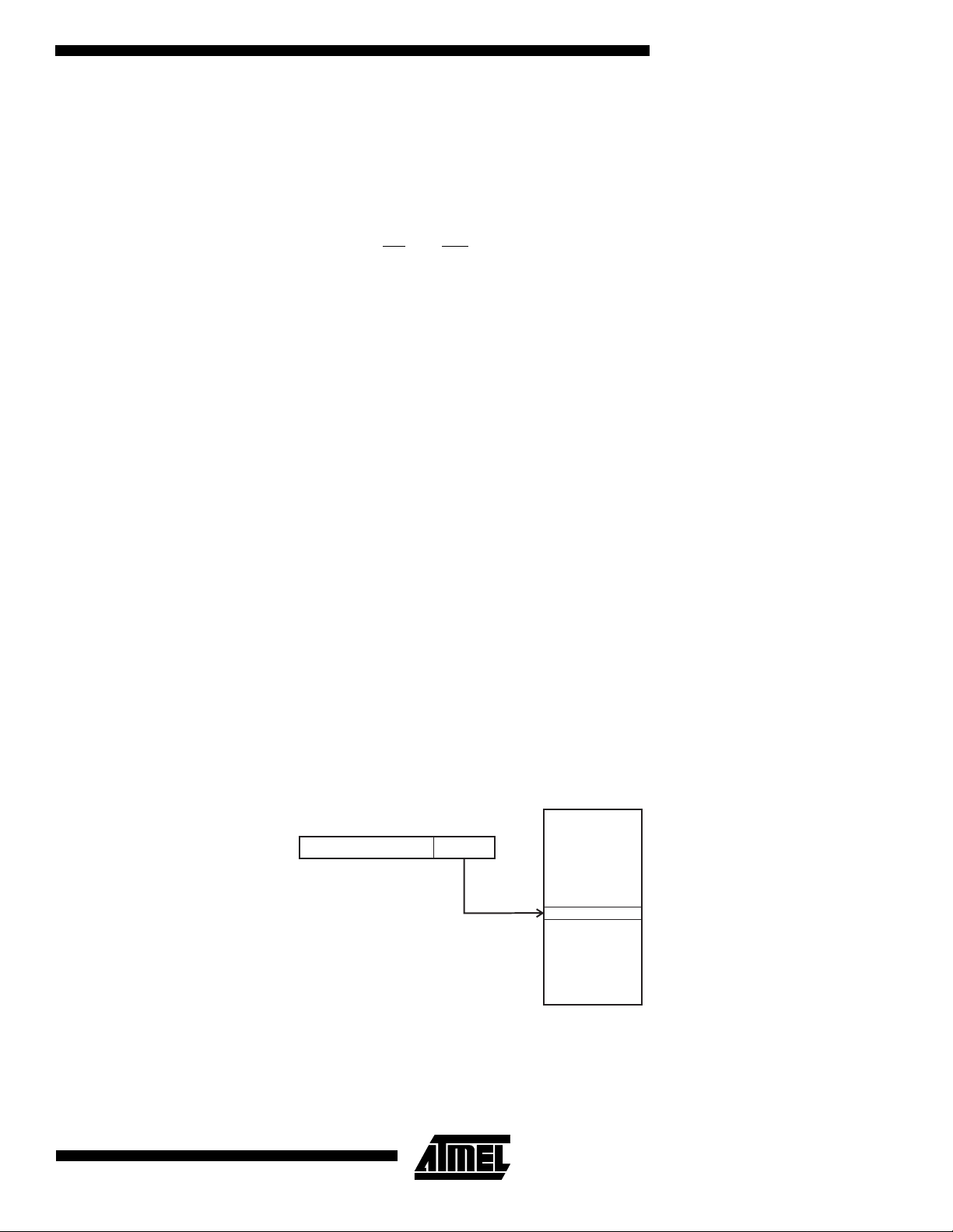

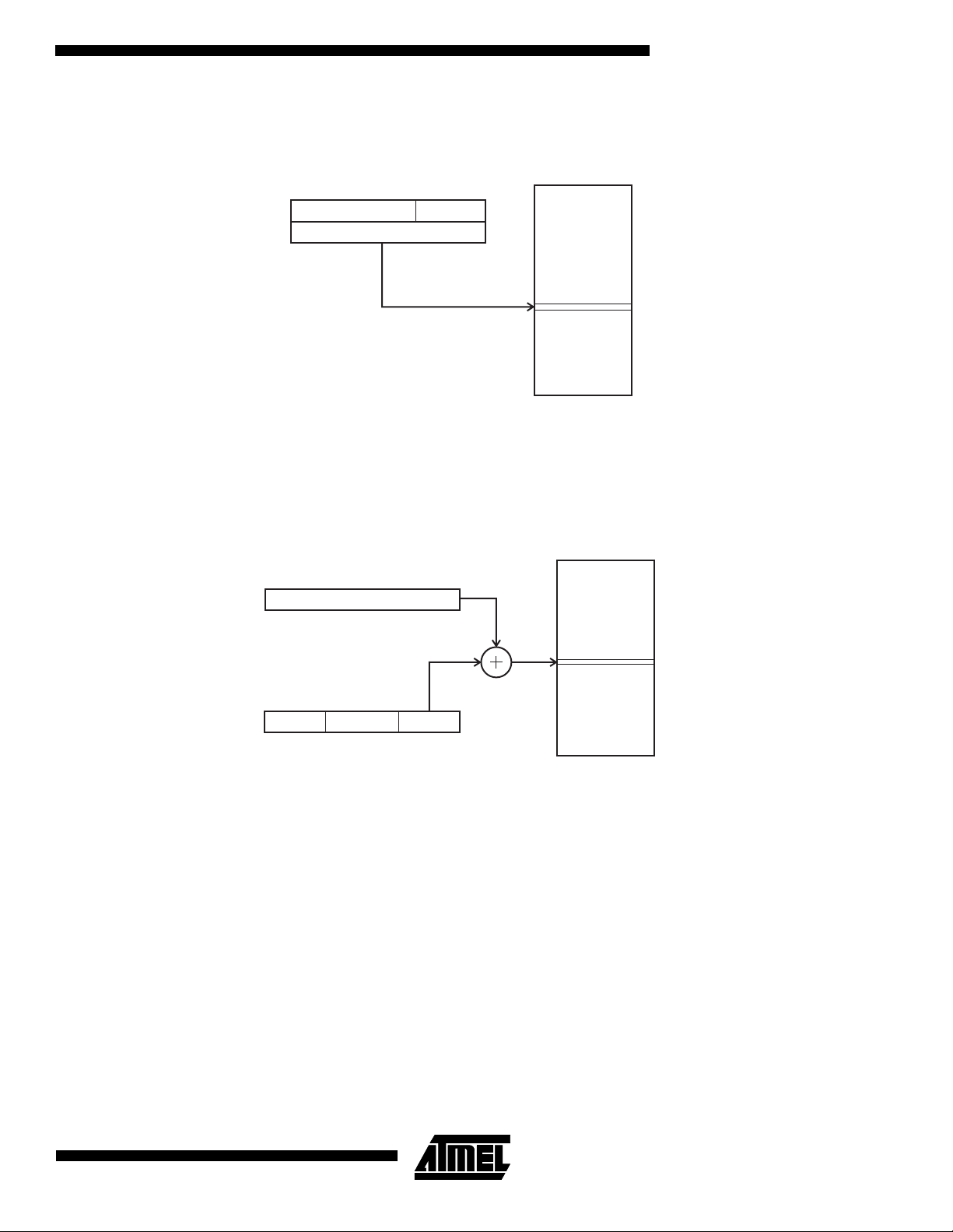

Register Direct, Single Register Rd

Figure 8. Direct Single Register Addressing

15

The operand is contained in register d (Rd).

REGISTER FILE

04

OP d

0

d

31

11

Page 12

Register Direct, Two Registers Rd and Rr

Figure 9. Direct Register Addressing, Two Registers

15

REGISTER FILE

0459

OP dr

0

d

r

31

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

I/O Direct

Figure 10. I/O Direct Addressing

15

OP P

n

I/O MEMORY

05

0

63

Operand address is contained in 6 bits of the instruction word. n is the destination or source register address.

12

ATmega603/103

Page 13

ATmega603/103

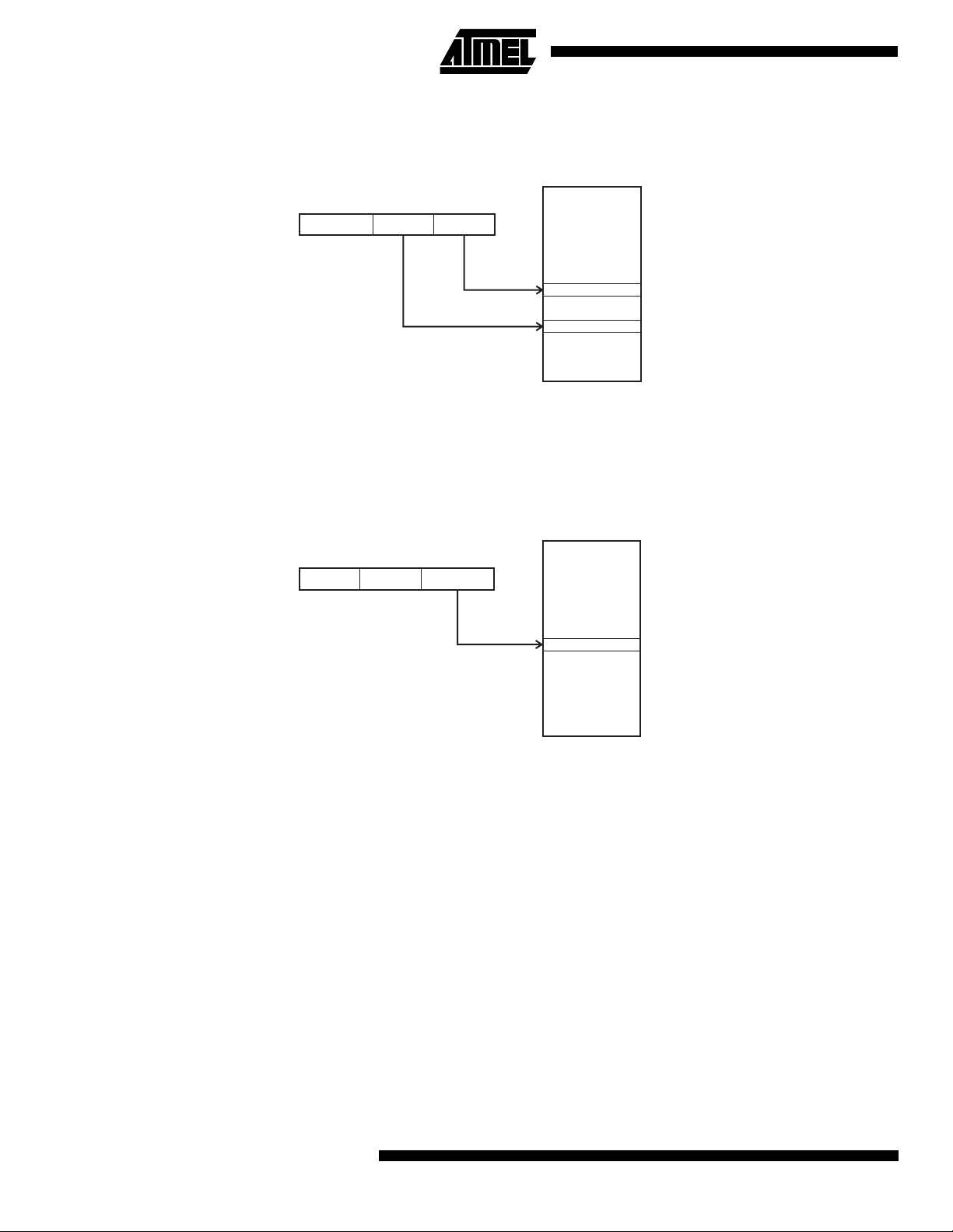

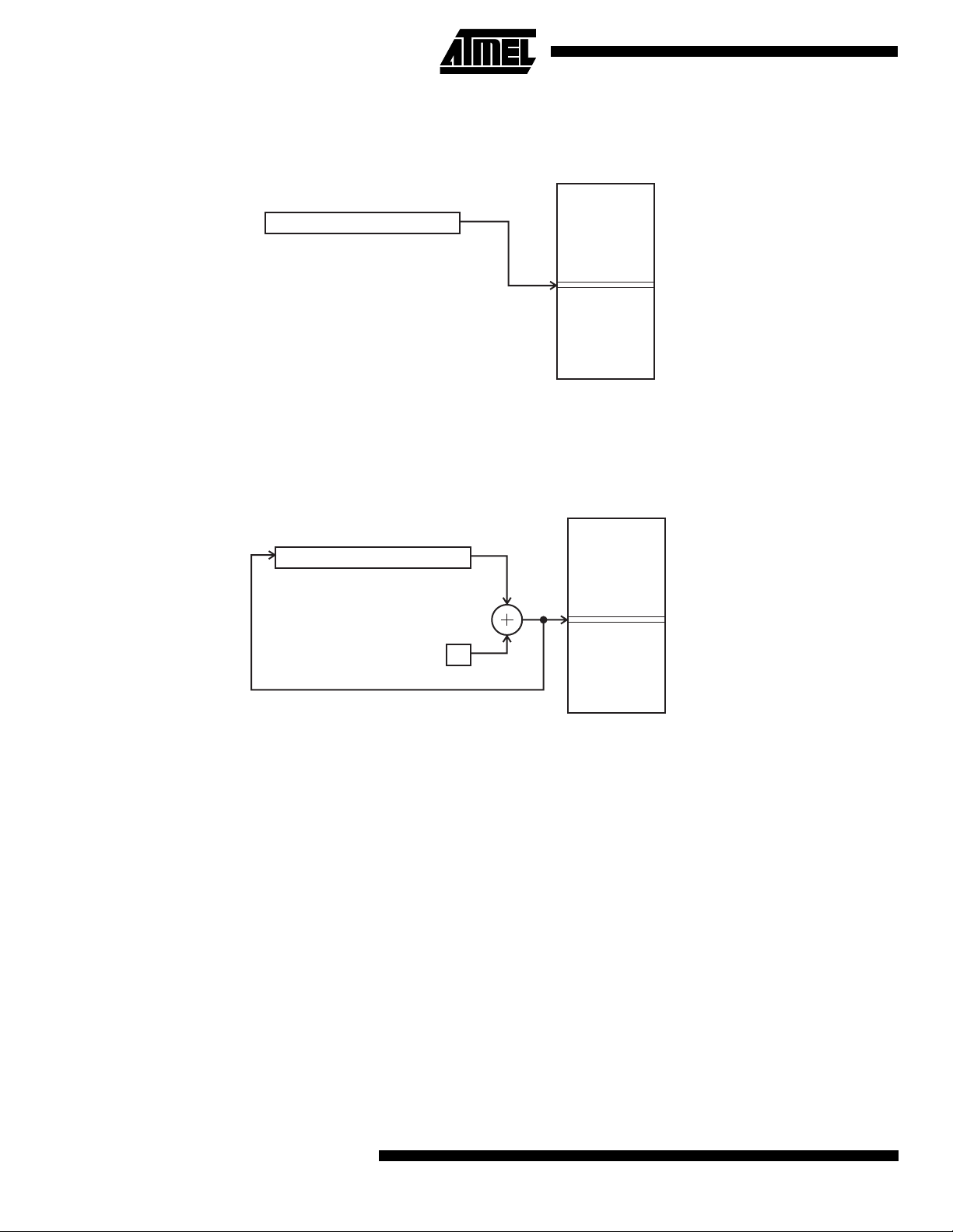

Data Direct

Figure 11. Direct Data Addressing

31

OP Rr/Rd

15 0

20 19

16 LSBs

16

Data Space

A 16-bit Data Address is contained in the 1 6 LSBs of a two-word instruction. Rd/Rr s pecify the destination or source

register.

Data Indirect with Displacement

$0000

$FFFF

Figure 12. Data Indirect with Displacement

15

Y OR Z - REGISTER

15

OP an

Data Space

0

05610

$0000

$FFFF

Operand address is the re sult of the Y or Z-register contents added to the address contained in 6 bits of the in struction

word.

13

Page 14

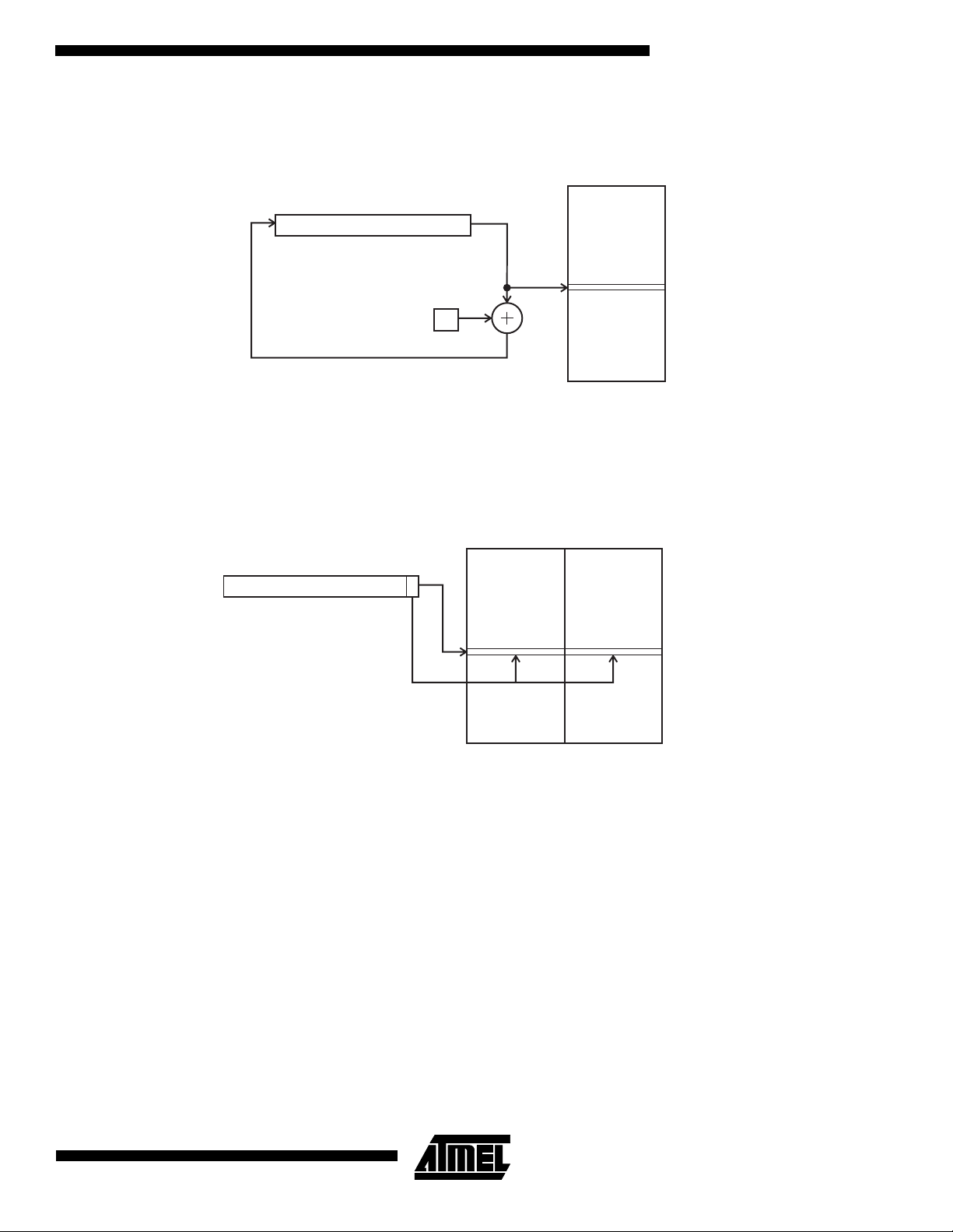

Data Indirect

Figure 13. Data Indirect Addressing

015

X, Y OR Z - REGISTER

Operand address is the contents of the X, Y or the Z-register.

Data Indirect With Pre-Decrement

Figure 14. Data Indirect Addressing with Pre-Decrement

015

X, Y OR Z - REGISTER

Data Space

Data Space

$0000

$FFFF

$0000

-1

$FFFF

The X, Y or the Z- regi ste r i s dec r eme nte d b efor e th e o peration. Operand addr es s is the decremented con tent s of the X, Y

or the Z-register.

14

ATmega603/103

Page 15

ATmega603/103

Data Indirect With Post-Increment

Figure 15. Data Indirect Addressing with Post-Increment

Data Space

015

X, Y OR Z - REGISTER

1

The X, Y or the Z-r egister is incr emen ted a fter the ope rati on. O perand addr ess is t he c onten t of the X , Y or t he Z-r egister

prior to incrementing.

Constant Addressing Using the LPM and ELPM Instructions

$0000

$FFFF

Figure 16. Code Memory Constant Addressing

PROGRAM MEMORY

0115

Z - REGISTER

$0000

$7FFF/$FFFF

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 32K), LSB selects low

byte if cleared (LSB = 0) or high byte if set (LSB = 1). If ELPM is used, LSB of the RAM Page Z register - RAMPZ is used to

select low or high memory page (RAMPZ0 = 0: Low Page, RAMPZ0 = 1: High Page). ELPM does not apply to the

ATmega603.

15

Page 16

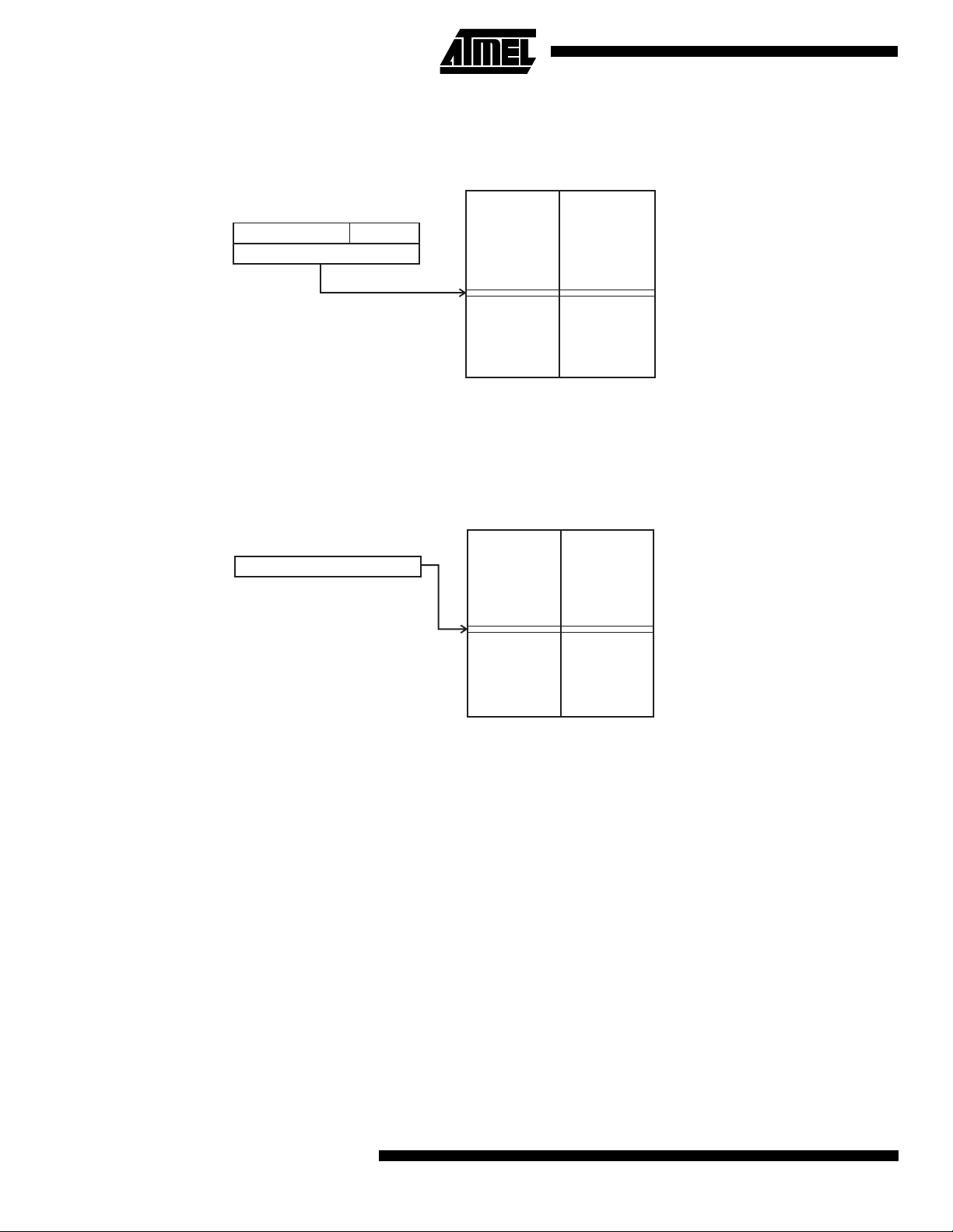

Direct Program Address, JMP and CALL

Figure 17. Direct Program Memory Addressing

PROGRAM MEMORY

31

OP

15 0

21 20

16 LSBs

16

Program execution continues at the address immediate in the instruction words.

Indirect Program Addressing, IJMP and ICALL

Figure 18. Indirect Program Memory Addressing

PROGRAM MEMORY

015

Z - REGISTER

$0000

$7FFF/$FFFF

$0000

$7FFF/$FFFF

Program execution continues at address contained by the Z-register (i.e. the PC is loaded with the contents of the

Z-register).

16

ATmega603/103

Page 17

Relative Program Addressing, RJMP and RCALL

Figure 19. Relative Program Memory Addressing

15

PC

0

PROGRAM MEMORY

ATmega603/103

$0000

15

1112

OP k

Program execution continues at address PC + k + 1. The relative address k is -2048 to 2047.

0

$7FFF/$FFFF

EEPROM Data Memory

The EEPROM memory is organized as a separate data space, in which single bytes can be read and written. The

EEPROM has an endura nce of at leas t 100,000 wr ite/erase cy cles. The access betwe en the EEPROM and the CPU is

described on pa ge 52 specif ying th e EEPR OM a ddress r egiste r, the EEPROM data r egister , and t he EEP ROM co ntrol

register.

Memory Access Times and Instruction Execution Timing

This section describes the general access timing concepts for instruction execution and internal memory access.

The AVR CPU is driven b y the S yste m Clock Ø, di rectly gener ated from the ex ternal c lock c rystal for the c hip. No interna l

clock division is used.

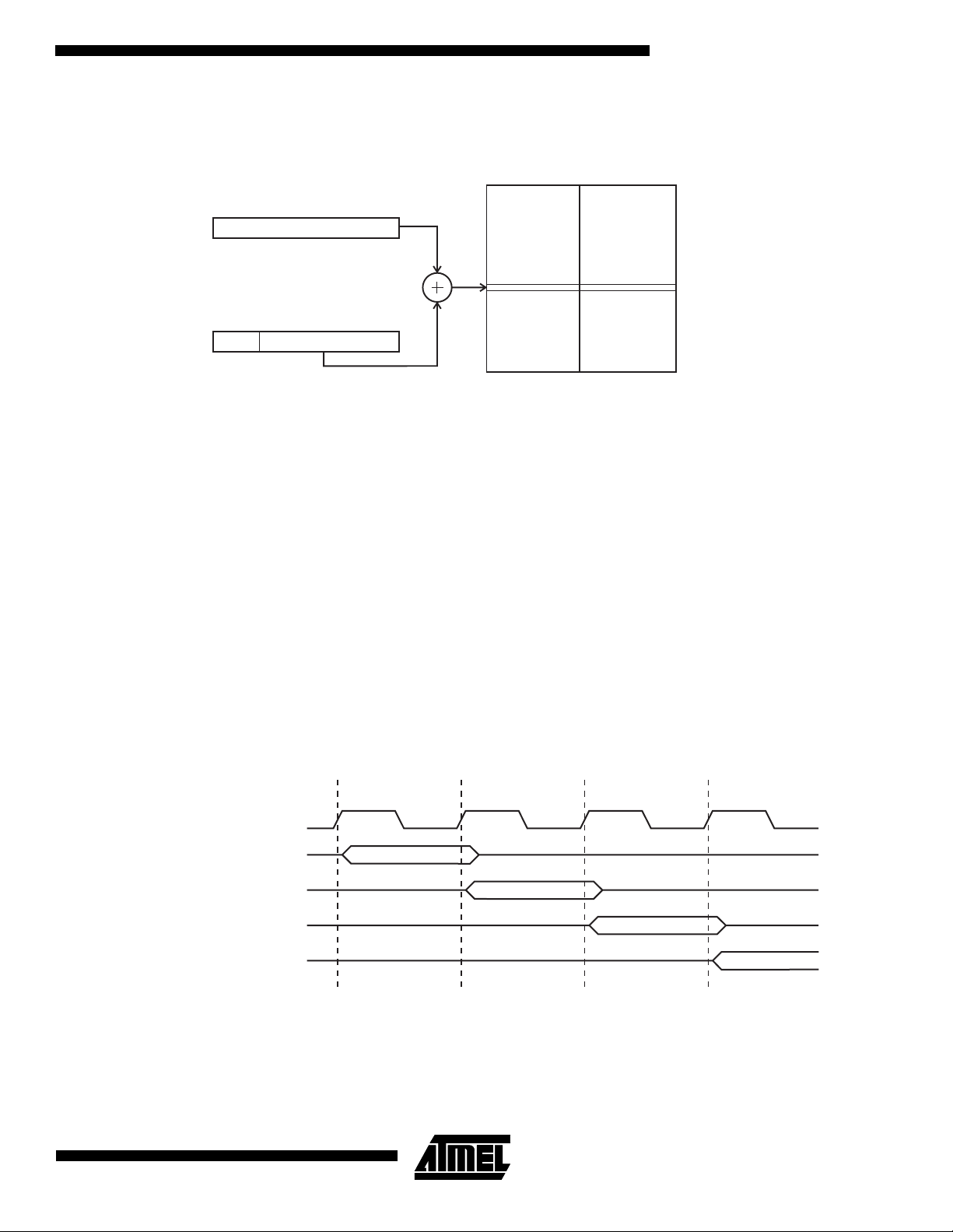

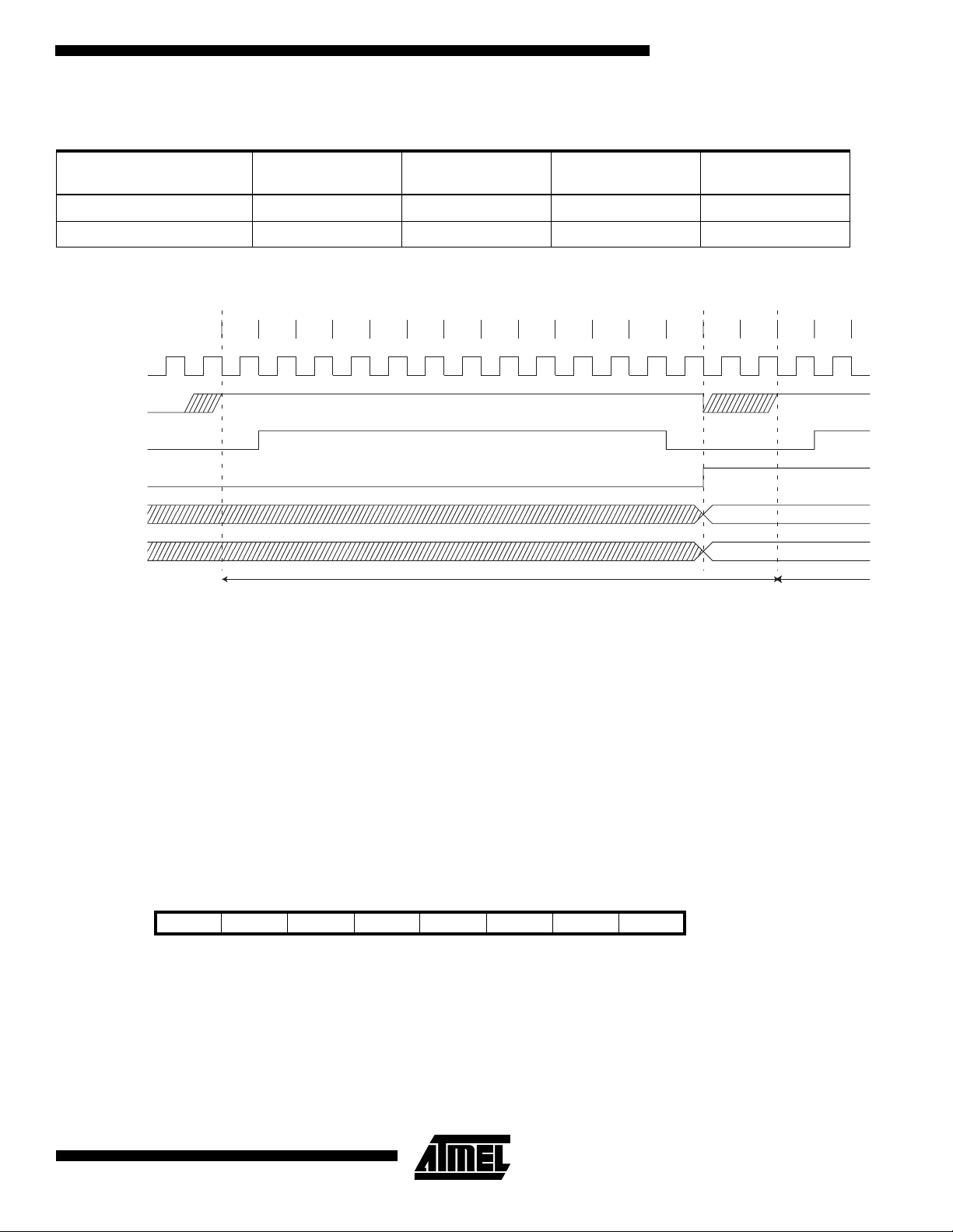

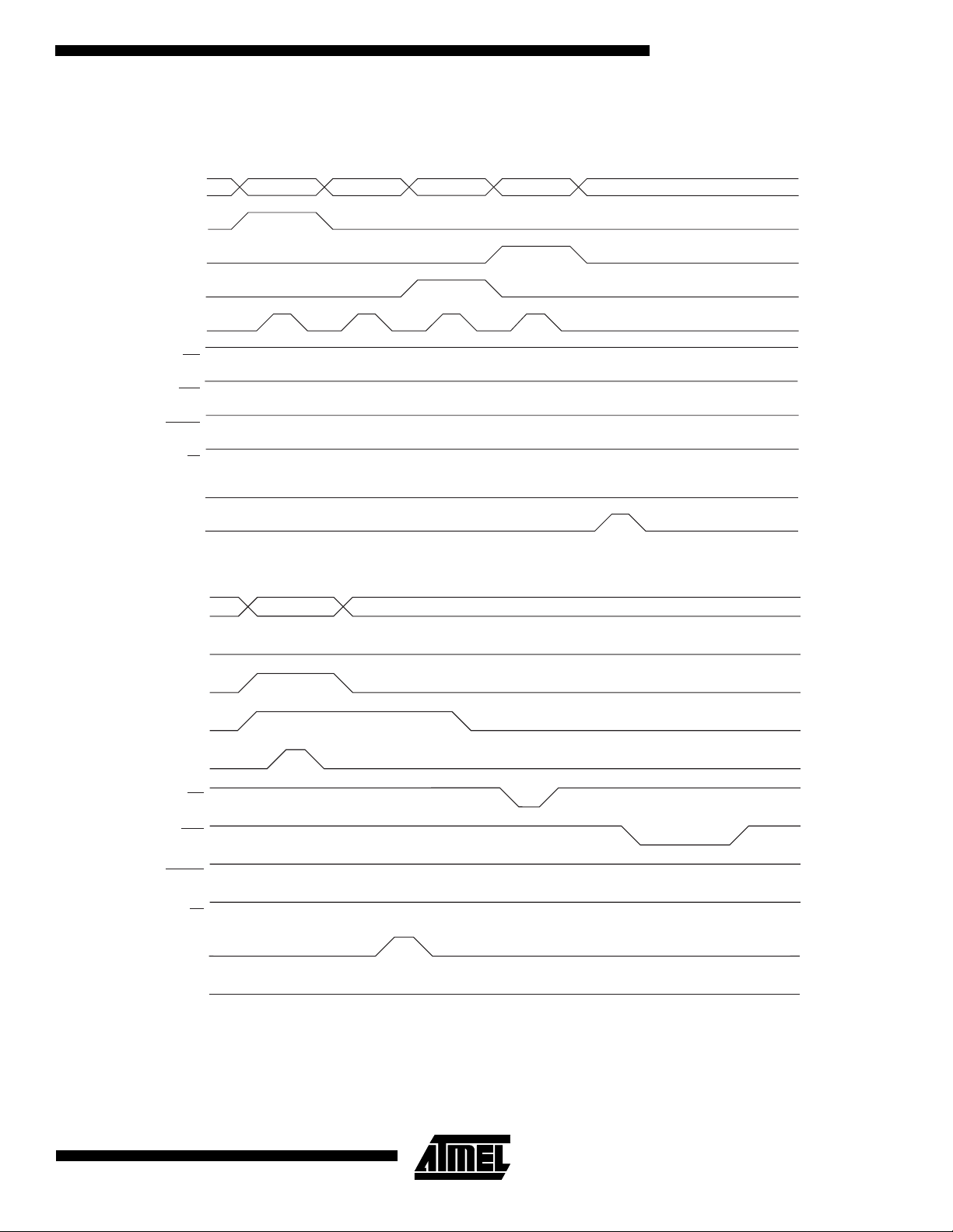

Figure 20 shows the parallel instructio n fetches and instructio n executions enabl ed by the Harvard architec ture and the

fast-access register file concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding

unique results for functions per cost, functions per clocks, and functions per power-unit.

Figure 20. The Parallel Instruction Fetches and Instruction Executions

T1 T2 T3 T4

System Clock Ø

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

Figure 21 shows the internal timing concept for the register file. In a single clock cycle an ALU operation using two register

operands is executed, and the result is stored back to the destination register.

17

Page 18

Figure 21. Single Cycle ALU Operation

T1 T2 T3 T4

System Clock Ø

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

The internal data SRAM access is performed in two System Clock cycles as described in Figure 22.

Figure 22. On-Chip Data SRAM Access Cycles

T1 T2 T3 T4

System Clock Ø

Address

Prev. Address

Address

Data

WR

Data

RD

See “Interface to external SRAM” on page 72 for a description of the access to the external SRAM.

Read Write

18

ATmega603/103

Page 19

I/O Memory

The I/O space definition of the ATmega603/103 is shown in the following table:

Table 3. ATmega603/103 I/O Space

I/O Address (SRAM Address) Name Function

$3F ($5F) SREG Status REGister

$3E ($5E) SPH Stack Pointer High

$3D ($5D) SPL Stack Pointer Low

$3C ($5C) XDIV XT AL Divi de Control Regi ster

$3B ($5B) RAMPZ RAM Page Z Select Register

$3A ($5A) EICR External Interrupt Control Register

$39 ($59) EIMSK External Interrupt MaSK register

$38 ($58) EIFR External Interrupt Flag Register

$37 ($57) TIMSK Timer/Counter Interrupt MaSK register

$36 ($56) TIFR Timer/Counter Interrupt Flag register

$35 ($55) MCUCR MCU General Control Register

ATmega603/103

$34 ($54) MCUSR MCU Status Register

$33 ($53) TCCR0 Timer/Counter0 Control Register

$32 ($52) TCNT0 Timer/Counter0 (8-bit)

$31 ($51) OCR0 Timer/Counter0 Output Compare Register

$30 ($50) ASSR Asynchronous Mode Status Register

$2F ($4F) TCCR1A Timer/Counter1 Control Register A

$2E ($4E) TCCR1B Timer/Counter1 Control Register B

$2D ($4D) TCNT1H Timer/Counter1 High Byte

$2C ($4C) TCNT1L Timer/Counter1 Low Byte

$2B ($4B) OCR1AH Timer/Counter1 Output Compare Register A High Byte

$2A ($4A) OCR1AL Timer/Counter1 Output Compare Register A Low Byte

$29 ($49) OCR1BH Timer/Counter1 Output Compare Register B High Byte

$28 ($48) OCR1BL Timer/Counter1 Output Compare Register B Low Byte

$27 ($47) ICR1H Timer/Counter1 Input Capture Register High Byte

$26 ($46) ICR1L Timer/Counter1 Input Capture Register Low Byte

$25 ($45) TCCR2 Timer/Counter2 Control Register

$24 ($44) TCNT2 Timer/Counter2 (8-bit)

$23 ($43) OCR2 Timer/Counter2 Output Compare Register

$21 ($41) WDTCR Watchdog Timer Control Register

$1F ($3F) EEARH EEPROM Address Register High

$1E ($3E) EEARL EERPOM Address Register Low

$1D ($3D) EEDR EEPROM Data Register

$1C ($3C) EECR EEPROM Control Register

19

Page 20

Table 3. ATmega603/103 I/O Space (Continued)

I/O Address (SRAM Address) Name Function

$1B ($3B) PORTA Data Register, Port A

$1A ($3A) DDRA Data Direction Register, Port A

$19 ($39) PINA Input Pins, Port A

$18 ($38) PORTB Data Register, Port B

$17 ($37) DDRB Data Direction Register, Port B

$16 ($36) PINB Input Pins, Port B

$15 ($35) PORTC Data Register, Port C

$12 ($32) PORTD Data Register, Port D

$11 ($31) DDRD Data Direction Register, Port D

$10 ($30) PIND Input Pins, Port D

$0F ($2F) SPDR SPI I/O Data Register

$0E ($2E) SPSR SPI Status Register

$0D ($2D) SPCR SPI Control Register

$0C ($2C) UDR UART I/O Data Register

$0B ($2B) USR UART Status Register

$0A ($2A) UCR UART Control Register

$09 ($29) UBRR UART Baud Rate Register

$08 ($28) ACSR Analog Comparator Control and Status Register

$07 ($27) ADMUX ADC Multiplexer Select Register

$06 ($26) ADCSR ADC Control and Status Register

$05 ($25) ADCH ADC Data Register High

$04 ($24) ADCL ADC Data Register Low

$03 ($23) PORTE Data Register, Port E

$02 ($22) DDRE Data Direction Register, Port E

$01 ($21) PINE Input Pins, Port E

$00 ($20) PINF Input Pins, Port F

Note: Reserved and unused locations are not shown in the table

All the different ATmega603/103 I/Os and peripherals are placed in the I/O space. The different I/O locations are directly

accessed by the IN and OUT ins truct ions transf erring data be tween the 32 ge neral purp ose workin g register s and the I/O

space. I/O registers within the address range $00 - $1F are directly bit-accessible using the SBI and CBI instructions. In

these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction

set chapter for more details. When using the I/O specific instructions IN, OUT, the I/O register address $00 - $3F are used.

When addressing I/O registers as SRAM, $20 must be added to this address. All I/O r egister addresses throughout this

document are shown with the SRAM address in parentheses.

For compatibility with future devices, res er ve d b its s hou ld be wr itte n t o z er o i f a cces s ed. Res erve d I/ O mem or y add re ss es

should never be written.

Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on

all bits in the I/O regi ster , writing a one ba ck in to any flag read as s et, thus cl earing t he f lag. The C BI and SB I instr ucti ons

work with registers $00 to $1F only.

20

ATmega603/103

Page 21

ATmega603/103

The different I/O and peripherals control registers are explained in the following sections.

Status Register - SREG

The AVR status register - SREG - at I/O space location $3F ($5F) is defined as:

Bit 76543210

$3F ($5F) I T H S V N Z C SREG

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value00000000

•

Bit 7 - I: Global Interrupt Enable

The global interr upt e nable bit must be set (one ) for the i nterrup ts to be e nable d. The indi vidu al in terrup t enab le c ontrol is

then performed in s eparate con trol regi sters. If the globa l inte rru pt ena ble r egist er is clear ed (zero ), non e of the i nter rupts

are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has

occurred, and is set by the RETI instruction to enable subsequent interrupts.

Bit 6 - T: Bit Copy Storage

•

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T bit as source and destination for the operated bit. A

bit from a register in the regi ste r file can be copied into T by the BST instru ct ion , and a bit i n T can be c opi ed i nto a bit in a

register in the register file by the BLD instruction.

Bit 5 - H: Half Carry Flag

•

The half carry flag H indicates a half carry in some arithmetic operations. See the Instruction Set Description for detailed

information.

Bit 4 - S: Sign Bit, S = N ⊕ V

•

The S-bit is always an exclusive or between the negative flag N and the two’s complement overflow flag V. See the Instruc-

tion Set Description for detailed information.

Bit 3 - V: Two’s Complement Overflow Flag

•

The two’s complement overflow flag V supports two’s complement arithmetics. See the Instruction Set Description for

detailed information.

Bit 2 - N: Negative Flag

•

The negative flag N indicates a negative result from an arithmetical or logical operation. See the Instruction Set Description

for detailed information.

Bit 1 - Z: Zero Flag

•

The zero flag Z indi cates a zero r esult from an arithmetic al or logical operation. See the Instru ction Se t Descriptio n for

detailed information.

Bit 0 - C: Carry Flag

•

The carry flag C indicates a carry in an ari thmetical or logical opera tion. See the Instruction Se t Description for detailed

information.

Note that the status register is not automatically stored when entering an interrupt routine and restored when returning from

an interrupt routine. This must be handled by software.

Stack Pointer - SP

The general AVR 16-bit Stack Poin ter is effecti vely built up of two 8- bit registe rs in the I/O s pace loca tions $3E ($5E ) and

$3D ($5D). As the ATmega603/103 supports up to 64 kB memory, all 16-bits are used.

Bit 151413121110 9 8

$3E ($5E) SP15 SP14 SP13 SP12 SP11 SP10 SP9 SP8 SPH

$3D ($5D) SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 SPL

76543210

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

Initial value00000000

00000000

21

Page 22

The Stack Pointe r poin ts to the da ta SRA M st ack a rea where t he Subrou tine and I nte rrupt Stac ks are lo cated . Th is Sta ck

space in the d ata SRAM m ust be defi ned by the p rogram befor e any su broutine cal ls are execu ted or in terrupts are

enabled. The stack pointer must be set to point above $60. The Stack Pointer is decremented by one when data is pushed

onto the Stack with the PUSH instruction, and it is decremented by two when an address is pushed onto the Stack with

subroutine calls and interrupts. The Stack Pointer is incremented by one when data is popped from the Stack with the POP

instruction, and it is incremente d by two when an address i s popped from the Stac k with return from subr outine RET or

return from interrupt RETI.

RAM Page Z Select Register - RAMPZ

Bit 7654321 0

$3B ($5B) - - - - - - - RAMPZ0 RAMPZ

Read/WriteRRRRRRRR/W

Initial value0000000 0

The RAMPZ register is normally used to select which 64K RAM Page is accessed by the Z pointer. As the ATmega603/103

does not support more than 64K of SRAM memory , this regi ster is use d only to se lect whi ch page in the program memo ry

is accessed when the ELPM instruction is used. The different settings of the RAMPZ0 bit have the following effects:

RAMPZ0 = 0: Program memory address $0000- $7FFF (lower 64K bytes) is accessed by ELPM

RAMPZ0 = 1: Program memory address $8000- $FFFF (higher 64K bytes) is accessed by ELPM

Note that LPM is not affected by the RAMPZ setting.

The ATmega603 does not contain the RAMPZ register, and it does not have the ELPM instruction. The ordinary LPM

instruction can reach the entire program memory in the ATmega603.

MCU Control Register - MCUCR

The MCU Control Register contains control bits for general MCU functions.

Bit 7654321 0

$35 ($55) SRE SRW SE SM1 SM0 - - - MCUCR

Read/Write R/W R/W R/W R/W R/W R R R

Initial value0000000 0

•

Bit 7 - SRE: External SRAM Enable

When the SRE bit is set (one), the externa l data SRAM is enabl ed, and the pin func tions AD0- 7 (Port A), and A8-15 (P ort

C) are activated as the al ternate pin functions. Then the SRE b it ove r rides a ny pi n d ir ecti on s et tin gs in the respective da ta

direction registers. When the SRE bit is cleared (zero), the external data SRAM is disabled, and the normal pin and data

direction settings are used.

Bit 6 - SRW: External SRAM Wait State

•

When the SRW bit is set ( one ), a one cycle wait state is ins ert ed in the ex terna l d ata SRA M a cces s c ycle . W hen the SRW

bit is cleared (zero), the external data SRAM access is executed with a three-cycle scheme. See Figure 51.External

SRAM Access Cycle without wait states73 and Figure 52.External SRAM Access Cycle with wait state74.

Bit 5 - SE: Sleep Enable

•

The SE bit must be set (one) to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the

MCU entering the sleep mode unless it is the programmers purpose, it is recommended to set the Sleep Enable SE bit just

before the execution of the SLEEP instruction.

22

ATmega603/103

Page 23

ATmega603/103

•

Bits 4,3 - SM1/SM0: Sleep Mode Select bits 1 and 0

This bit selects between the three available sleep modes as shown in the following table:

Table 4. Sleep Mode Select

SM1 SM0 Sleep Mode

0 0 Idle Mode

01Reserved

1 0 Power Down

1 1 Power Save

Bits 2..0 - Res: Reserved bits

•

These bits are reserved bits in the ATmega603/103 and always read zero.

XTAL Divide Control Register - XDIV

The XTAL Divide Contr ol Reg ister is used to di vide the X TAL cl ock fr equenc y by a numbe r in the rang e 1 - 129. This f eature can be used to decrease power consumption when the requirement for processing power is low.

Bit 7 654321 0

$3C ($5C) XDIVEN XDIV6 XDIV5 XDIV4 XDIV3 XDIV2 XDIV1 XDIV0 XDIV

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value0 000000 0

Bit 7 - XDIVEN: XTAL Divide Enable

•

When the XDIVEN bit is set (one), the clock frequency of the CPU and all peripherals is divided by the factor defined by the

setting of XDIV6 - XDIV0. This bit can be set and cleared run-time to vary the clock frequency as suitable to the application.

Bits 6..0 - XDIV6..XDIV0: XTAL Divide Select Bits 6 - 0

•

These bits define the division factor that applies when the XDIVEN bit is set (one). If the value of these bits is denoted d,

f

the following formula defines the resulting CPU clock frequency

f

CLK

clk

XTAL

------------------ -=

129 d–

:

The value of these bits can only be ch ange d when XDIV EN i s ze ro. Whe n XDIVEN is set to one, the value written si multaneously into XDIV6..XDIV0 is taken as the division factor. When XDIVEN is cleared to zero, the value written

simultaneously into XDIV6..XDIV0 is rejected. As the divider divides the master clock input to the MCU, the speed of all

peripherals is reduced when a division factor is used.

23

Page 24

Reset and Interrupt Handling

The ATmega603/103 provides 23 different interrupt sources. These interrupts and the separate reset vector each have a

separate program vector in the program memory space. All interrupts are assigned individual enable bits which must be set

(one) together with the I-bit in the status register in order to enable the interrupt.

The lowest addresses i n the pro gram memory s pace are aut omatically defined a s the Reset an d Interru pt vectors. The

complete list of vectors is shown in Table 5. The list also determines the priority levels of the different interrupts. The lower

the address the higher is the priority level. RESET has the highest priority, and next is INT0 - the External Interrupt Request

0 etc.

Table 5. Reset and Interrupt Vectors

Vector No. Program Address Source Interrupt Definition

1 $0000 RESET Hardware Pin, Power-on Reset and Watchdog Reset

2 $0002 INT0 External Interrupt Request 0

3 $0004 INT1 External Interrupt Request 1

4 $0006 INT2 External Interrupt Request 2

5 $0008 INT3 External Interrupt Request 3

6 $000A INT4 External Interrupt Request 4

7 $000C INT5 External Interrupt Request 5

8 $000E INT6 External Interrupt Request 6

9 $0010 INT7 External Interrupt Request 7

10 $0012 TIMER2 COMP Timer/Counter2 Compare Match

11 $0014 TIMER2 OVF Timer/Counter2 Overflow

12 $0016 TIMER1 CAPT Timer/Counter1 Capture Event

13 $0018 TIMER1 COMPA Timer/Counter1 Compare Match A

14 $001A TIMER1 COMPB Timer/Counter1 Compare Match B

15 $001C TIMER1 OVF Timer/Counter1 Overflow

16 $001E TIMER0 COMP Timer/Counter0 Compare Match

17 $0020 TIMER0 OVF Timer/Counter0 Overflow

18 $0022 SPI, STC SPI Serial Transfer Complete

19 $0024 UART, RX UART, Rx Complete

20 $0026 UART, UDRE UART Data Register Empty

21 $0028 UART, TX UART, Tx Complete

22 $002A ADC ADC Conversion Complete

23 $002C EE READY EEPROM Ready

24 $002E ANALOG COMP Analog Comparator

24

ATmega603/103

Page 25

The most typical program setup for the Reset and Interrupt Vector Addresses are:

Address Labels Code Comments

$0000 jmp RESET ; Reset Handler

$0002 jmp EXT_INT0 ; IRQ0 Handler

$0004 jmp EXT_INT1 ; IRQ1 Handler

$0006 jmp EXT_INT2 ; IRQ2 Handler

$0008 jmp EXT_INT3 ; IRQ3 Handler

$000A jmp EXT_INT4 ; IRQ4 Handler

$000C jmp EXT_INT5 ; IRQ5 Handler

$000E jmp EXT_INT6 ; IRQ6 Handler

$0010 jmp EXT_INT7 ; IRQ7 Handler

$0012 jmp TIM2_COMP ; Timer2 Compare Handler

$0014 jmp TIM2_OVF ; Timer2 Overflow Handler

$0016 jmp TIM1_CAPT ; Timer1 Capture Handler

$0018 jmp TIM1_COMPA ; Timer1 CompareA Handler

$001A jmp TIM1_COMPB ; Timer1 CompareB Handler

$001C jmp TIM1_OVF ; Timer1 Overflow Handler

$001E jmp TIM0_COMP ; Timer0 Compare Handler

$0020 jmp TIM0_OVF ; Timer0 Overflow Handler

$0022 jmp SPI_STC ; SPI Transfer Complete Handler

$0024 jmp UART_RXC ; UART RX Complete Handler

$0026 jmp UART_DRE ; UDR Empty Handler

$0028 jmp UART_TXC ; UART TX Complete Handler

$002A jmp ADC ; ADC Conversion Complete Handler

$002C jmp EE_RDY ; EEPROM Ready Handler

$002E jmp ANA_COMP ; Analog Comparator Handler

;

$0030 MAIN: ldi r16, high(RAMEND); Main program start

$0031 out SPH,r16

$0032 ldi r16, low(RAMEND)

$0033 out SPL,r16

$0034 <instr> xxx

... ... ... ...

ATmega603/103

Reset Sources

The ATmega603/103 has three sources of reset:

• Power-On Reset. The MCU is reset when the supply voltage is below the power-on reset threshold (V

• External Reset. The MCU is reset when a low level is present on the RESET

pin for more than 50 ns.

POT

).

• Watchdog Reset. The MCU is reset when the Watchdog timer period expires and the Watchdog is enabled.

During reset, all I/O registers except the MCU Status register are then set to their initial values, and the program starts exe-

cution from address $0000. The instruction placed in address $0000 must be a JMP - absolute jump instruction to the reset

handling routine. If the program never enables an interrupt source, the interrupt vectors are not used, and regular program

code can be placed at these locations. The circuit diagram in Figure 23 shows the reset logic. Table 6 defines the timing

and electrical parameters of the reset circuitry.

25

Page 26

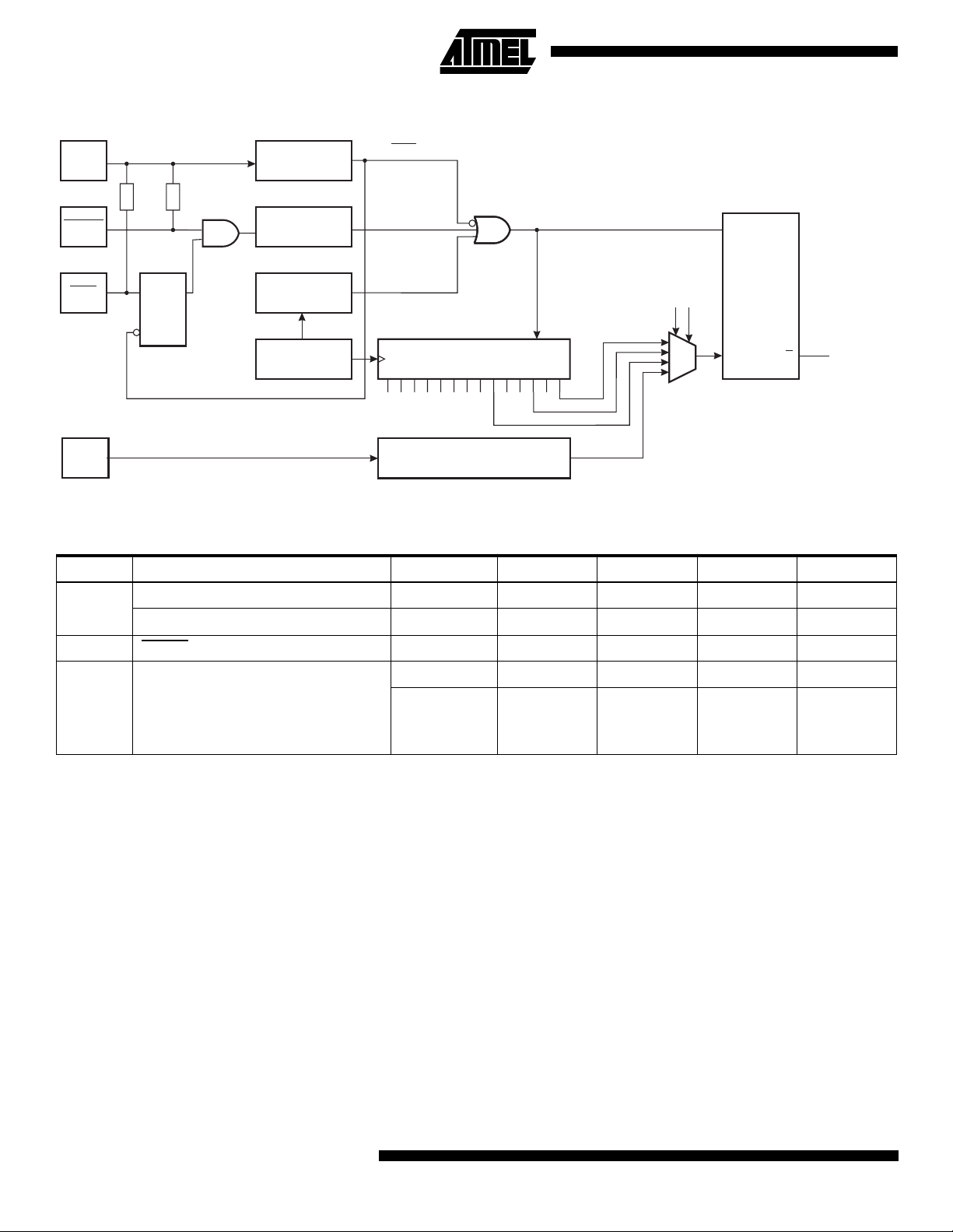

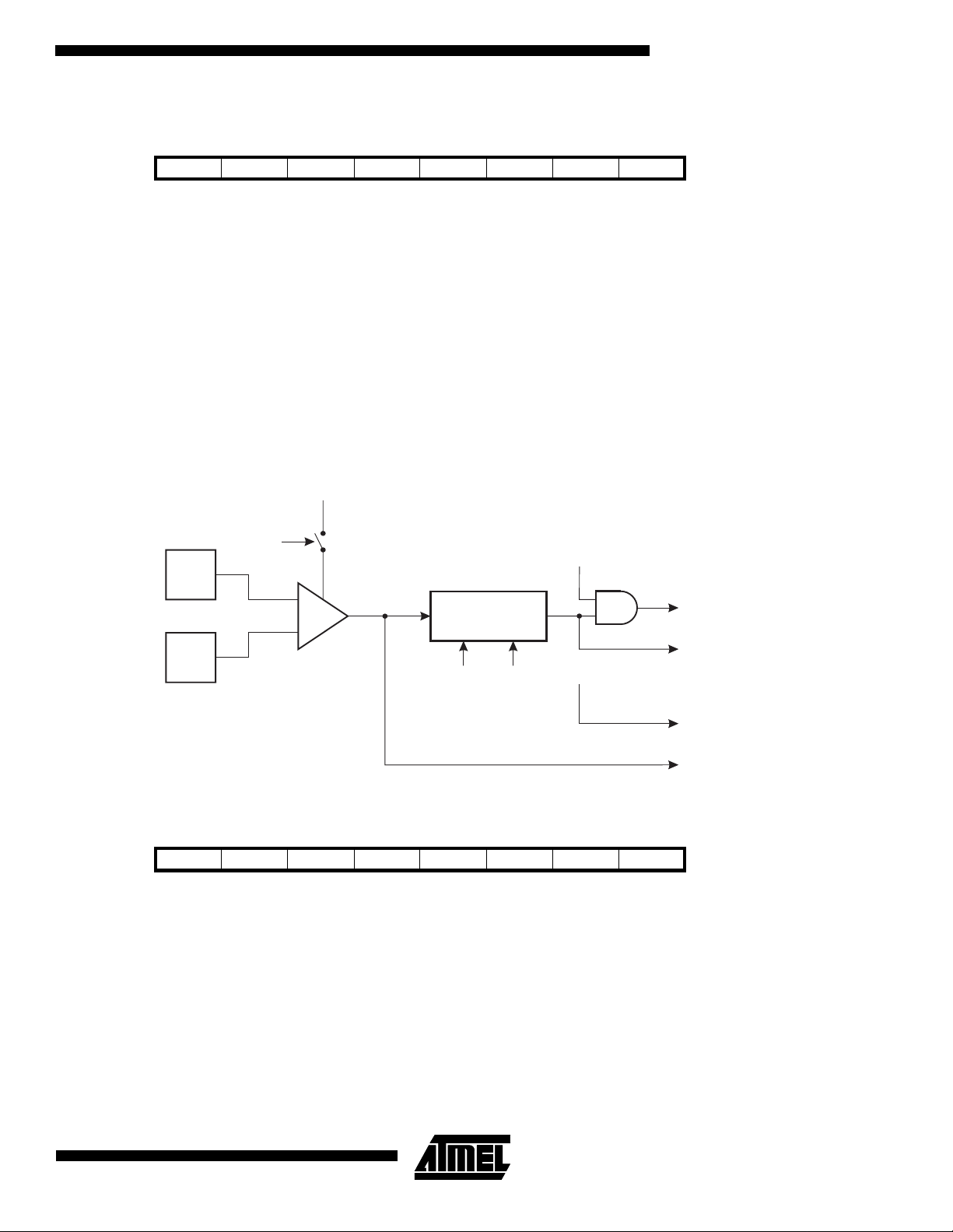

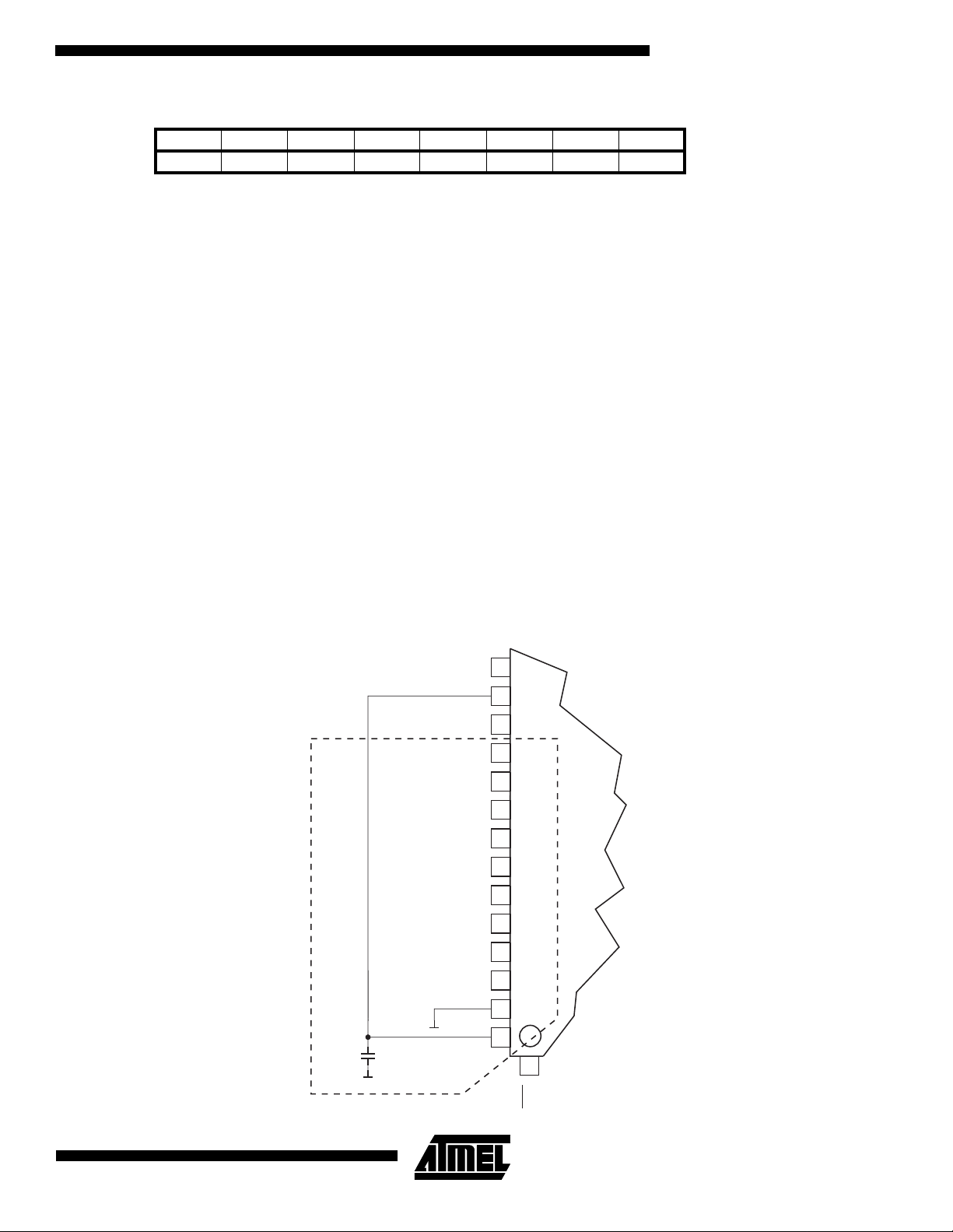

Figure 23. Reset Logic

VCC

RESET

PEN D Q

XTAL1

10-50K

E

100-500K

Power-On Reset

Circuit

Reset Circuit

Watchdog

Timer

On-Chip

RC-Oscillator

POR

14-Stage Ripple Counter

Q8 Q11 Q13

Delay Unit

COUNTER RESET

SUT0

SUT1

QS

R

Q

Table 6. Reset Characteristics (VCC = 5V)

Symbol Parameter Condition Min Typ Max Units

Power-On Reset Threshold (rising) 1.0 1.4 1.8 V

(1)

V

POT

Power-On Reset Threshold (falling) 0.4 0.6 0.8 V

INTERNAL

RESET

V

RST

RESET Pin Threshold Voltage VCC/2 V

SUT = 00 5 CPU cycles

T

TOUT

Reset Delay Time-Out Period

SUT = 01

SUT = 10

SUT = 11

0.4

3.2

12.8

Note: 1. The Power-On Reset will not work unless the supply voltage has been below V

0.5

4.0

16.0

POT

(falling)

0.6

4.8

19.2

ms

26

ATmega603/103

Page 27

ATmega603/103

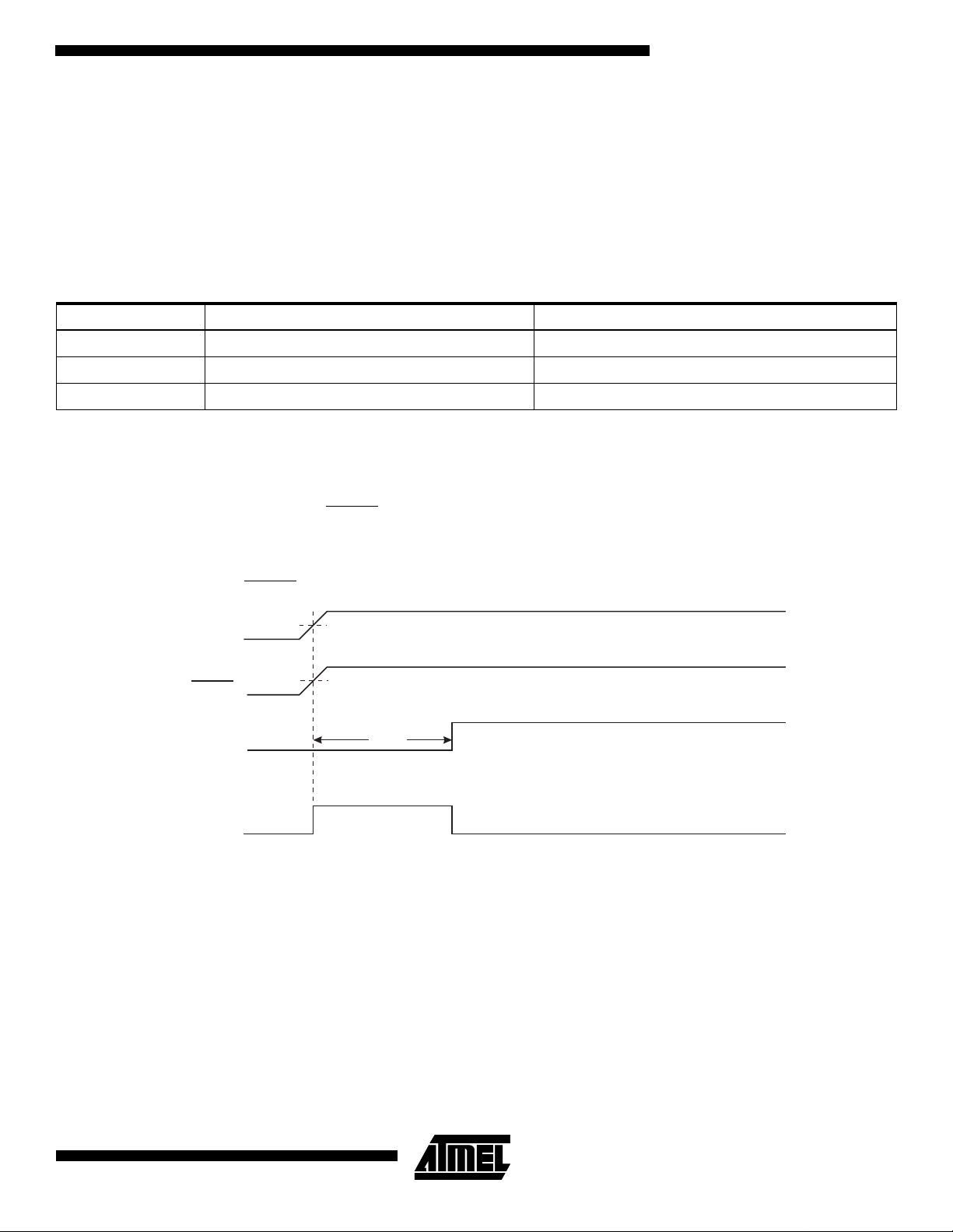

Power-On Reset

A Power-On Reset (POR ) circuit ensures tha t the device is reset from power-on. As s hown in Figure 23, an inter nal timer

clocked from the Watchd og timer oscillator prevents the MCU from st arting until after a cer tain period after V

reached the Power-O n Th resh old v ol tage - V

, regardless of the VCC rise time (see Fi gure 24) . The Fu se bits SUT1 and

POT

SUT0 is used to select start-up time as indicated in Table 6. A “0” in the table indicates that the fuse is programmed.

The user can select the start-up time according to typical oscillator start-up time. The number of WDT oscillator cycles used

for each time-out ex cept for S UT = 00 is sho wn in Tabl e 7. The f requency of the w atchdo g osc illator is volta ge depe ndent

as shown in “Typical characteristics” on page 110.

Table 7. Number of watchdog oscillator cycles

SUT 1/0 Time-out at VCC = 5V Number of WDT cycles

01 0.5 ms 512

10 4.0 ms 4K

11 16.0 ms 16K

The setting SUT 1/0 = 00 starts the MCU after 5 CPU clock cycles, and can be used when an external clock signal is

applied to the XTAL1 pin. This setting does not use the WDT oscillator, and enables very fast start-up from the sleep

modes power down or power save if the clock si gnal is pr esent du ring sleep. For details, r efer to the prog ramming speci fication starting on page 92.

If the built-in start-up delay is sufficient, RESET

ing the pin low for a period after V

has been applied, the Power-On Reset period can be extended. Refer to Figure 25 for

CC

can be connected to VCC directly or via an external pull-up resistor. By hold-

a timing example on this.

CC

has

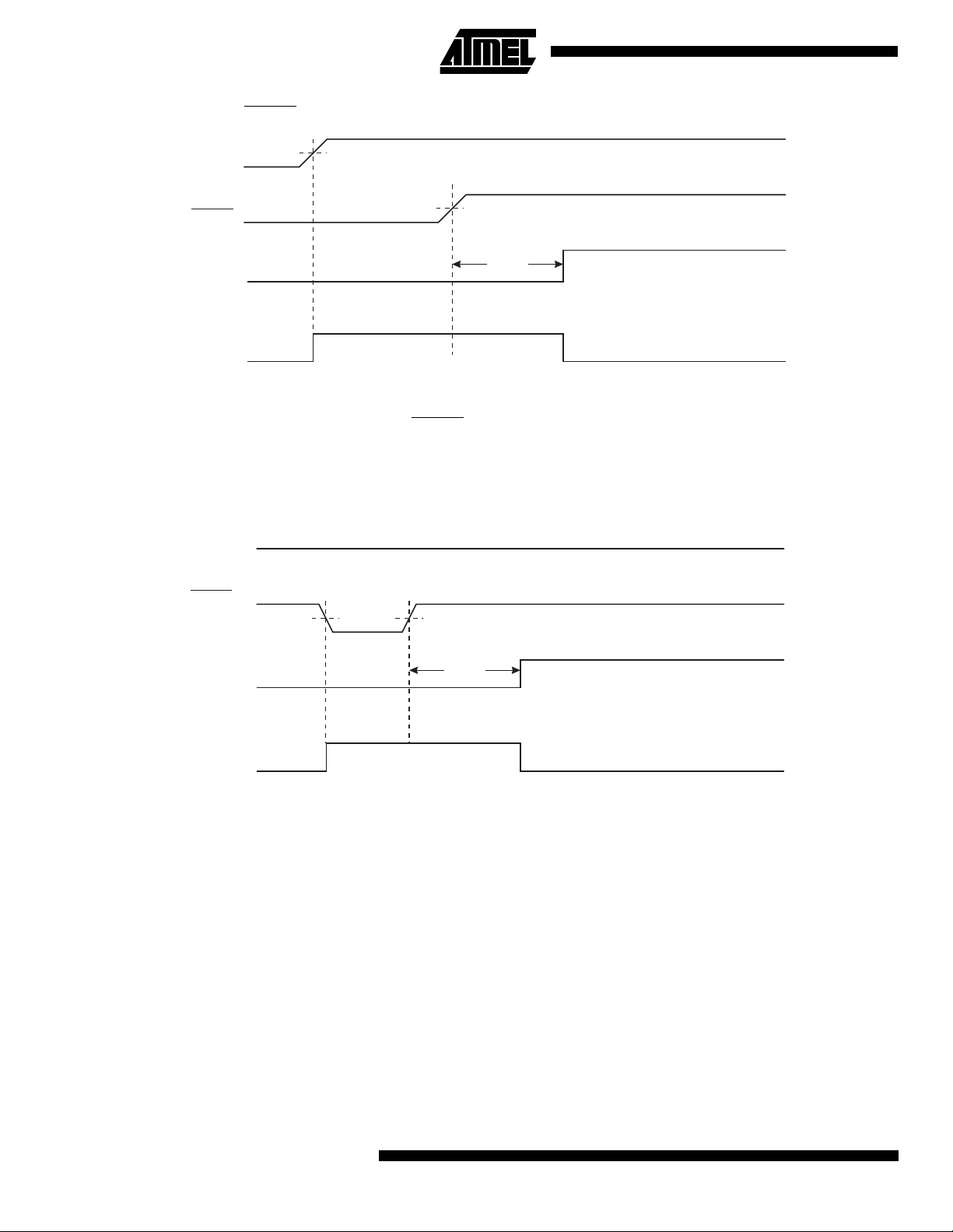

Figure 24. MCU Start-Up, RESET

VCC

RESET

TIME-OUT

INTERNAL

RESET

Tied to VCC.

V

POT

V

RST

t

TOUT

27

Page 28

Figure 25. MCU Start-Up, RESET

VCC

RESET

TIME-OUT

INTERNAL

RESET

Controlled Externally

V

POT

V

RST

t

TOUT

External Reset

An external reset is generated by a low level on the RESET

pin. Reset pulses longer than 50 ns will generate a reset, even

if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the ap plied signal reaches the

Reset Thresh old Vo ltage - V

- on its positive edge, the delay timer starts the MCU after the Time-out period t

RST

TOUT

has

expired.

Figure 26. External Reset During Operation

VCC

RESET

V

RST

t

TIME-OUT

INTERNAL

RESET

TOUT

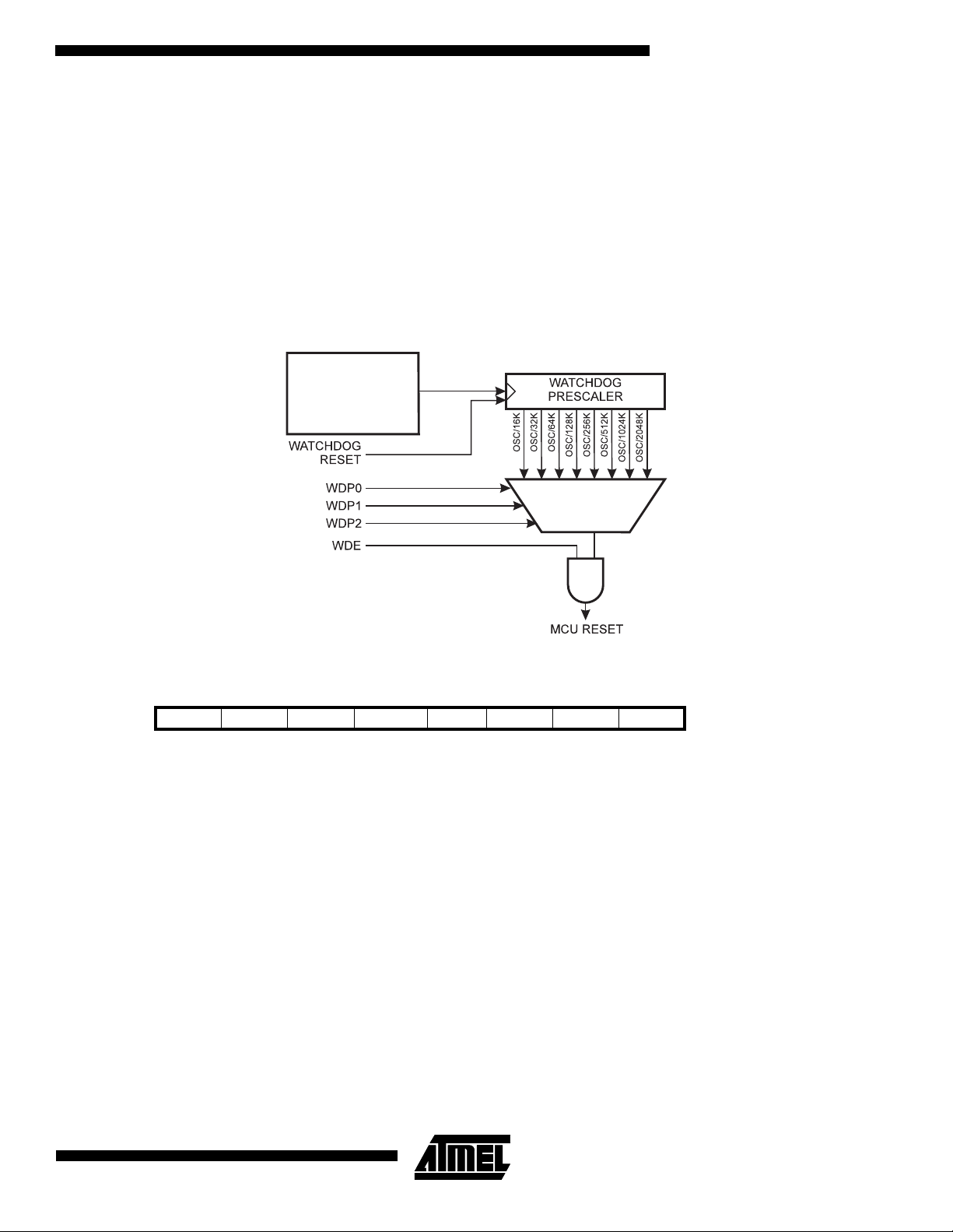

Watchdog Reset

When the Watchdo g tim es out, i t will generate a sh ort rese t pulse o f 1 XT AL cyc le durati on. On the falli ng edge of this

pulse, the delay timer starts counting the Time-out period t

. Refer to page 51 for details on operation of the Watchdog.

TOUT

28

ATmega603/103

Page 29

Figure 27. Watchdog Reset During Operation

VCC

RESET

ATmega603/103

WDT

TIME-OUT

RESET

TIME-OUT

INTERNAL

RESET

1 XTAL Cycle

t

TOUT

MCU Status Register - MCUSR

The MCU Status Register provides information on which reset source caused an MCU reset.

Bit 7 654321 0

$34 ($54) - - - - - - EXTRF PORF MCUSR

Read/WriteR RRRRRR/WR/W

Initial value 0 0 0 0 0 0 See bit description

•

Bits 7..2 - Res: Reserved Bits

These bits are reserved bits in the ATmega603/103 and always read as zero.

Bit 1 - EXTRF: External Reset Flag

•

After a power-on reset, this bit is undefined (X). It will be set by an external reset. A watchdog reset will leave this bit

unchanged.

Bit 0 - PORF: Power-on Reset Flag

•

This bit is set by a power-on reset. A watchdog reset or an external reset will leave this bit unchanged.

To summarize, the following table shows the value of these two bits after the three modes of reset:

Table 8. PORF and EXTRF Values after Reset

Reset Source EXTRF PORF

Power-on Reset undefined 1

External Reset 1 unchanged

Watchdog Reset unchanged unchanged

To make use of these bi ts to ident ify a reset conditio n, the us er softwa re should clear bot h the PORF an d EXTRF bits as

early as possible in the program. Checking the PORF and EXTRF values is done before the bits are cleared. If the bit is

cleared before an external or watchdog reset occurs, the source of reset can be found by using the following truth table:

Table 9. Reset Source Identification

EXTRF PORF Reset Source

0 0 Watchdog Reset

0 1 Power-on Reset

1 0 External Reset

1 1 Power-on Reset

29

Page 30

Interrupt Handling

The ATmega603/103 has two dedicated 8-bit Interrupt Mask control registers; EIMSK - External Interrupt Mask register and

TIMSK - Timer/Counter Interrupt Mask register. In addition, other enable and mask bits can be found in the peripheral

control registers.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user software can set (one) the I-bit to enable nested interrupts. The I-bit is set (one) when a Return from Interrupt instruction - RETI

- is executed.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hard-

ware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a

logic one to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the interrupt flag will be set

and remembered until the interrupt is enabled, or the flag is cleared by software.

If one or more interrupt conditi ons occu r when the global interrupt ena ble bit is clea red (zero), th e correspondi ng interrup t

flag(s) will be set and remembered until the global interrupt enable bit is set (one), and will be executed by order of priority.

Note that external level interrupt does not have a flag, and will only be remembered for as long as the interrupt condition is

active.

Note that the status register is not automatically stored when entering an interrupt routine and restored when returning from

an interrupt routine. This must be handled by software.

External Interrupt Mask Register - EIMSK

Bit 7654 3 2 10

$39 ($59) INT7 INT6 INT5 INT4 INT3 INT2 INT1 INT0 EIMSK

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

•

Bits 7..4 - INT7 - INT4: External Interrupt Request 7-4 Enable

When an INT7- INT4 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the corresponding external pin

interrupt is enabled. The Inter rupt Sens e Control bits in th e Externa l Interru pt Contro l Register - EICR defin es whethe r the

external interrupt is acti vated on risi ng or f allin g edge or l evel s ensed . Activ ity on a ny of these pins wi ll trig ger a n inte rrupt

request even if the pin is enabled as an output. This provides a way of generating a software interrupt.

Bits 3..0 - INT3 - INT0: External Interrupt Request 3-0 Enable

•

When an INT3 - INT0 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the corresponding external pin

interrupt is enabled . The ex tern al in terrupts are al ways lo w lev el trig gered inter rupts. Activi ty on any o f thes e pin s will trigger an interrupt request even if the pin is enabl ed as an output. This p rovides a way of ge nerating a so ftware interru pt.

When enabled, a level triggered interrupt will generate an interrupt request as long as the pin is held low.

External Interrupt Flag Register - EIFR

Bit 7654 3 2 10

$38 ($58) INTF7 INTF6 INTF5 INTF4 - - - - EIFR

Read/Write R/W R/W R/W R/W R R R R

Initial value 0 0 0 0 0 0 0 0

Bits 7..4 - INTF7 - INTF4: External Interrupt 7-4 Flags

•

When an event on the INT7 - INT4 pins triggers an interrupt request, the corresponding interrupt flag, INTF7 - INTF4

becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INT7 - INT4 in EIMSK, are set (one), the

MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag is

cleared by writing a logical one to it.

Bits 3..0 - Res: Reserved Bits

•

These bits are reserved bits in the ATmega603/103 and always read as zero.

30

ATmega603/103

Page 31

ATmega603/103

External Interrupt Control Register - EICR

Bit 7654 3 2 1 0

$3A ($5A) ISC71 ISC70 ISC61 ISC60 ISC51 ISC50 ISC41 ISC40 EICR

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

•

Bits 7..0 - ISCX1, ISCX0: External Interrupt 7-4 Sense Control bits

The External Interrupts 7 - 4 a re ac tiva ted by the external pins INT7 - INT4 if the SREG I- fla g an d th e c orr es pon din g i nte rrupt mask in the EIMSK is set. The level and edges on the external pins that activate the interrupts are defined in the

following table:

Table 10. Interrupt Sense Control

ISCX1 ISCX0 Description

0 0 The low level of INTX generates an interrupt request.

01Reserved

1 0 The falling edge of INTX generates an interrupt request.

1 1 The rising edge of INTX generates an interrupt request.

Note: X = 7, 6, 5 or 4.

When changing the ISC X1 /ISCX 0 bit s, the int errup t m us t be di sa ble d b y cle ari ng its Interrupt Enable bit in the GIM SK Re gis ter.

Otherwise an interrupt can occur when the bits are changed.

The value on the INTX pin is sampled before detecting edges. If edge interrupt is selected, pulses that last longer than one

CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt.

clock frequency c an be lowe r than the X TAL frequency if the XTAL divider is enabled.

If low level inte rrupt i s se lected , the

low level must be held until the completion of the currently executing instruction to generate an interrupt.

Observe that CPU

If enabled, a level

triggered interrupt will generate an interrupt request as long as the pin is held low.

Timer/Counter Interrupt Mask Register - TIMSK

Bit 7 6 5 4 3 2 1 0

$37 ($57) OCIE2 TOIE2 TICIE1 OCIE1A OCIE1B TOIE1 OCIE0 TOIE0 TIMSK

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

•

Bit 7 - OCIE2: Timer/Counter2 Output Compare Interrupt Enable

When the OCIE2 bit is set (on e) and the I- bi t in the S tatus Reg ister is set ( one ), th e Tim er/Cou nter 2 Co mpa re Match i nte rrupt is enabled. The correspo nding in terrupt ( at vector $0012) is executed i f a Compar e match in Tim er/Cou nter2 oc curs,

i.e., when the OCF2 bit is set in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 6 - TOIE2: Timer/Counter2 Overflow Interrupt Enable

•

When the TOIE2 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is

enabled. The corresponding interrup t (at vector $001 4) is exec uted if an over flow in Time r/Coun ter2 occu rs, i.e., when the

TOV2 bit is set in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 5 - TICIE1: Timer/Counter1 Input Capture Interrupt Enable

•

When the TICIE1 bit is set (one) a nd the I-bit in the Statu s Register is set (one), th e Timer/Co unter1 Input Capt ure Event

Interrupt is enabled. The corresponding interrupt (at vector $0016) is executed if a capture-triggering event occurs on pin

29, PD4(IC1), i.e., when the ICF1 bit is set in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 4 - OCE1A: Timer/Counter1 Output CompareA Match Interrupt Enable

•

When the OCIE1A bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareA Match

interrupt is enabled. The corresponding interrupt (at vector $0018) is executed if a CompareA match i n Timer/Counter1

occurs, i.e., when the OCF1A bit is set in the Timer/Counter Interrupt Flag Register - TIFR.

31

Page 32

•

Bit 3 - OCIE1B: Timer/Counter1 Output CompareB Match Interrupt Enable

When the OCIE1B bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 CompareB Match

interrupt is enabled. The corresponding interrupt (at vector $001A) is executed if a Compare B match in Timer/Counter1

occurs, i.e., when the OCF1B bit is set in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 2 - TOIE1: Timer/Counter1 Overflow Interrupt Enable

•

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter1 Overflow interrupt is

enabled. The correspondin g in ter rupt ( at v ector $001 C) is executed if an overflow in Timer/Cou nter 1 occur s, i.e. , w hen th e

TOV1 bit is set in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 1 - OCIE0: Timer/Counter0 Output Compare Interrupt Enable

•

When the OCIE0 bit is set (on e) and the I- bi t in the S tatus Reg ister is set ( one ), th e Tim er/Cou nter 0 Co mpa re Match i nte r-

rupt is enabled . The corre spon ding in terr upt (a t vec tor $0 01E) is exec uted i f a Compar e m atch in Time r/Coun ter0 occurs ,

i.e., when the OCF0 bit is set in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 0 - TOIE0: Timer/Counter0 Overflow Interrupt Enable

•

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is

enabled. The corresponding interrup t (at vector $002 0) is exec uted if an over flow in Time r/Coun ter0 occu rs, i.e., when the

TOV0 bit is set in the Timer/Counter Interrupt Flag Register - TIFR

Timer/Counter Interrupt Flag Register - TIFR

Bit 7 6 5 4 3 2 1 0

$36 ($56) OCF2 TOV2 ICF1 OCF1A OCF1B TOV1 OCF0 TOV0 TIFR

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

Bit 7 - OCF2: Output Compare Flag 2:

•

The OCF2 bit is set (o ne) wh en c om par e m atch o cc urs be tween Tim er /Cou nter 2 and the data in O CR2 - O ut put Comp ar e

Register 2. OCF2 is c le ared by hardware when executi ng the c orr es pon ding i nte rrup t handling vector. Altern ati vely , O CF2

is cleared by writing a l ogic one to the flag. W hen the I-bit in SRE G, and OCIE2 (T imer/Counter2 Compare Interru pt

Enable), and the OCF2 are set (one), the Timer/Counter2 Output Compare Interrupt is executed.

Bit 6 - TOV2: Timer/Counter2 Overflow Flag

•

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared by hardware when executing the

corresponding interrupt handling vector. Alternatively, TOV2 is cleared by writing a logic one to the flag. When the I-bit in

SREG, and TOIE2 (T imer/Counter 1 Overflow Inter rupt Enable ), and TOV2 ar e set (one), the Ti mer/Counter 2 Overflow

Interrupt is executed. In PWM mode, this bit is set when Timer/Counter2 advances from $00.

Bit 5 - ICF1: Input Capture Flag 1

•

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the

input capture register - ICR1. ICF1 is cleared by har dware when executi ng the corresp onding interrupt han dling vector.

Alternatively, ICF1 is cleared by writing a logic one to the flag. When the SREG I-bit, and TICIE1 (Timer/Counter1 Input

Capture Interrupt Enable), and ICF1 are set (one), the Timer/Counter1 Capture Interrupt is executed.

Bit 4 - OCF1A: Output Compare Flag 1A

•

The OCF1A bit is set (one) when compare match oc curs between the Time r/Counter1 and the data in OCR1A - Output

Compare Register 1A. OCF1A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1A (Timer/Counter1 Compare

Interrupt Enable), and the OCF1A are set (one), the Timer/Counter1 Compare A match Interrupt is executed.

Bit 3 - OCF1B: Output Compare Flag 1B

•

The OCF1B bit is set (one) when compare match oc curs between the Time r/Counter1 and the data in OCR1B - Output

Compare Register 1B. OCF1B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1B is cleared by writing a logic one to the flag.. When the I-bit in SREG, and OCIE1B (Timer/Counter1 Compare

match Interrupt Enable), and the OCF1B are set (one), the Timer/Counter1 Compare B match Interrupt is executed.

32

ATmega603/103

Page 33

ATmega603/103

•

Bit 2 - TOV1: Timer/Counter1 Overflow Flag

The TOV1 is set (one) when an overflow occu rs i n Tim er /Co unte r1 . TOV1 is c lea red b y h ar dwa re when ex ec uti ng the co rresponding int errupt hand ling vecto r. Alterna tively, TOV 1 is clear ed by writin g a logic one to th e flag. Whe n the I-bit in

SREG, and TOIE1 (T imer/Counter 1 Overflow Inter rupt Enable ), and TOV1 ar e set (one), the Ti mer/Counter 1 Overflow

Interrupt is executed. In PWM mode, this bit is set when Timer/Counter1 advances from $0000.

Bit 1 - OCF0: Output Compare Flag 0

•

The OCF0 bit is set (o ne) wh en c om par e m atch o cc urs be tween Tim er /Cou nter 0 and the data in O CR0 - O ut put Comp ar e

Register 0. OCF0 is c le ared by hardware when executi ng the c orr es pon ding i nte rrup t handling vector. Altern ati vely , O CF0

is cleared by writing a l ogic one to the flag. W hen the I-bit in SRE G, and OCIE0 (T imer/Counter2 Compare Interru pt

Enable), and the OCF0 are set (one), the Timer/Counter0 Output Compare Interrupt is executed.

Bit 0 - TOV0: Timer/Counter0 Overflow Flag

•

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the

corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG Ibit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt

is executed. In PWM mode, this bit is set when Timer/Counter0 advances from $00.

Interrupt Response Time

The interrupt execution res ponse for all the enabl ed AVR interrupts is 4 cloc k cycles minim um. 4 clock cycles after the

interrupt flag h as been set , the pro gram ve ctor addre ss for the actual interru pt handl ing routi ne is exec uted. Du ring this 4

clock cycle period, the Program Counter (2 bytes) is pushed onto the Stack, and the Stack Pointer is decremented by 2.

The vector is nor ma ll y a jum p t o t he interrupt routine, and th is j ump ta kes 3 clock cyc les . If a n i nte rrupt occurs during ex ecution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes 4 clock cycles. During these 4 clock

cycles, the Program Counter (2 bytes) is popped back from the Stack, and the Stack Pointer is incremented by 2. When the

AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending

interrupt is served.

Sleep Modes

To enter any of the three sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed.

The SM1 and SM0 bits in the MCUCR register select which sleep mode (Idle, Power Down, or Power Save) will be activated by the SLEEP instruction, see Table 4.

If an enabled interrup t occurs while the MCU is in a sleep mod e, the MCU awakes , executes the i nterrupt rout ine, and

resumes execution from the instruction following SLEEP. The contents of the register file, SRAM, and I/O memory are unaltered. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset vector

Idle Mode

When the SM1/SM0 bits are set to 00, the SLEEP i nstructi on makes the MCU enter th e Idle Mode, sto pping the CPU but

allowing SPI, UART, Analog Comparator, ADC, Timer/Counters, Watchdog and the interrupt system to continue operating.

This enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and

UART Receive Complete interrupts. If wake-up from the Analog Comparator interrupt is not required, the analog comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status register - ACSR. This will

reduce power co nsumption in Id le Mode. When t he MCU wa kes up from Idle mode , the CPU starts p rogram e xecution

immediately.

33

Page 34

Power Down Mode

When the SM1/SM0 bit s are set to 10, the S LEEP in struct ion mak es the M CU enter the P ower Do wn Mode. In this mod e,

the external oscillator is stopped, while the external interrupts and the Watchdog (if enabled) continue operating. Only an

external reset, a watchdog reset (if enabled), or an external level interrupt can wake up the MCU.

Note that if a level triggered interrupt is used fo r wake-up from P ower Down Mode, the changed level mu st be held for

some time to wake up the MCU. This makes the MCU le ss sensi tive to noi se. The c hanged level is sampled twi ce by the

watchdog oscillator cl ock, a nd if the inp ut ha s the requi red level d uring this time , the MCU wi ll wa ke u p. The period of th e

watchdog oscillator is 1 us (nominal) at 5.0V and 25C. The frequency of the watchdog oscillator is voltage dependent as

shown in section “Typical char acteristics” on page 110.

When waking up from Powe r Down Mode, ther e is a delay fro m the wake-up conditio n occurs un til the wake-u p becomes

effective. This a llows the clo ck to res tart a nd bec ome stab le aft er ha ving been s topped . The wak e-up pe riod is defi ned by

the same SUT fuses that define the r ese t tim e-out period. The wake-up period is equa l to the cl ock re se t per iod, as sho wn

in Table 6.

If the wake-up condition disappears before the MCU wakes up and starts to execute, e.g. a low level on is not held long

enough, the interrupt causing the wake-up will not be executed.

Power Save Mode

When the SM1/SM0 bits are 11, the SLEEP instruction makes the MCU enter the Power Save Mode. This mode is identical

to Power Down, with one exception:

If Timer/Counter0 is clocked as y nch ronou sl y , i.e. th e AS 0 bi t in ASS R is s et, Tim er/Co unte r0 will run dur in g sl ee p. In add ition to the Power Down wa ke-up s ources, the device ca n also wa ke up fro m either Time r Overflow o r Output Compare

event from Timer/Counter0 i f the corr espon ding Tim er/Counter 0 interr upt enab le bits ar e set in TIMSK. To en sure that th e

part executes the Interrupt routine when waking up, also set the global interrupt enable bit in SREG.

When waking up from Power Save Mode by an exter nal interrupt, 2 i nstruction cy cles are exec uted before the inte rrupt

flags are updated. When waking up by the asynchronous timer, 3 instruction cycles are executed before the flags are

updated. During these cycles, the processor executes instructions, but the interrupt condition is not readable, and the

interrupt routine has not started yet .

Timer/Counters

The ATmega603/103 pr ovid es th re e g ene ral purpose Timer/Counter s - t wo 8-bit T/Cs and one 16 -b it T/C. Ti me r/C ount er 0

can optionally be asynchronously clocked from an external oscillator. This oscillator is optimized for use with a 32.768 kHz

crystal, enabling use of Timer/Counter0 as a Real Time Clock (RTC). Timer/Counter0 has its own prescaler.

Timer/Counters 1 and 2 have ind ivid ual pres caling se lecti on from the same 10- bit pres cali ng timer. Thes e Timer/Co unters

can either be used as a timer with an internal clock timebase or as a counter with an external pin connection which triggers

the count ing.

34

ATmega603/103

Page 35

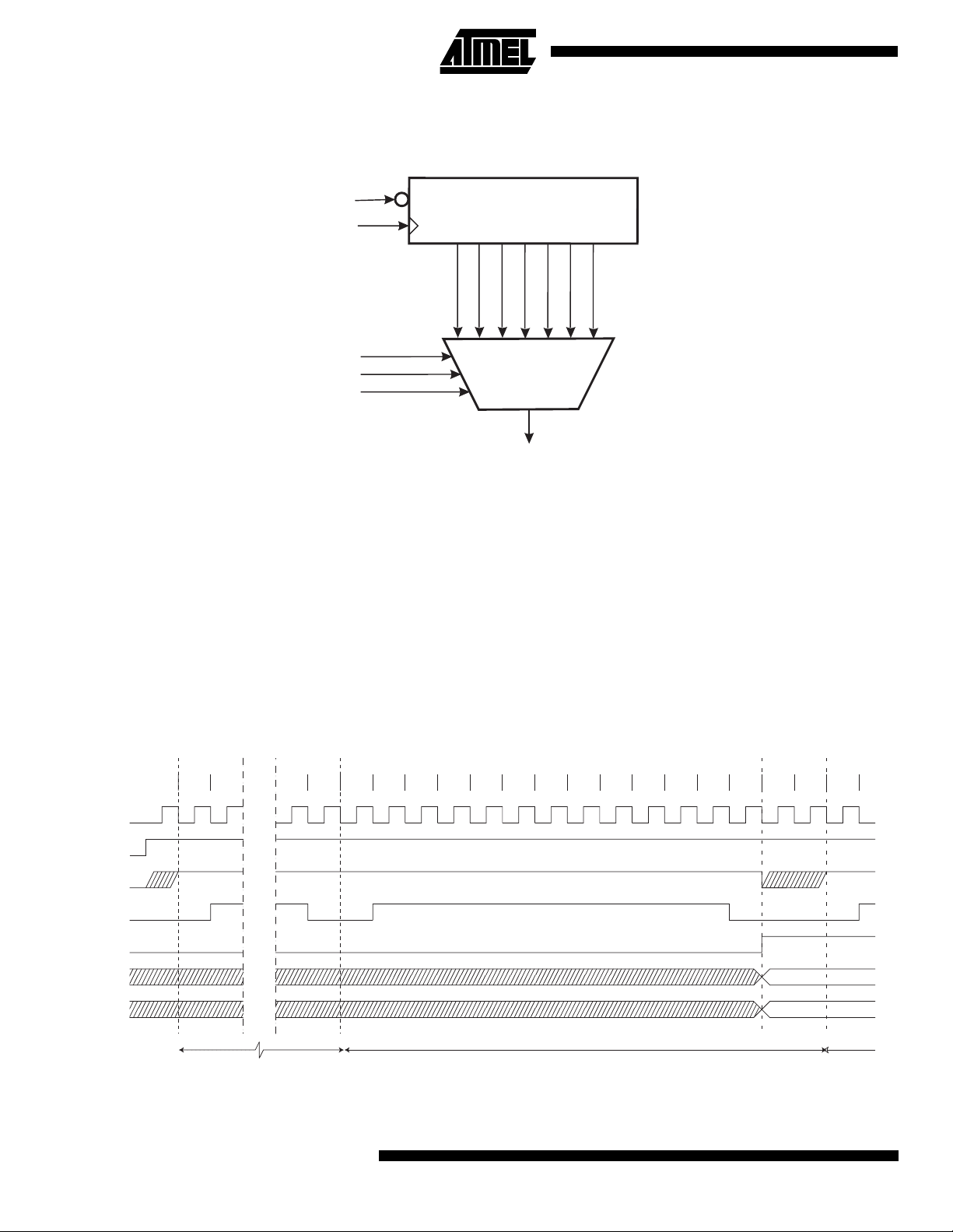

Timer/Counter Prescalers

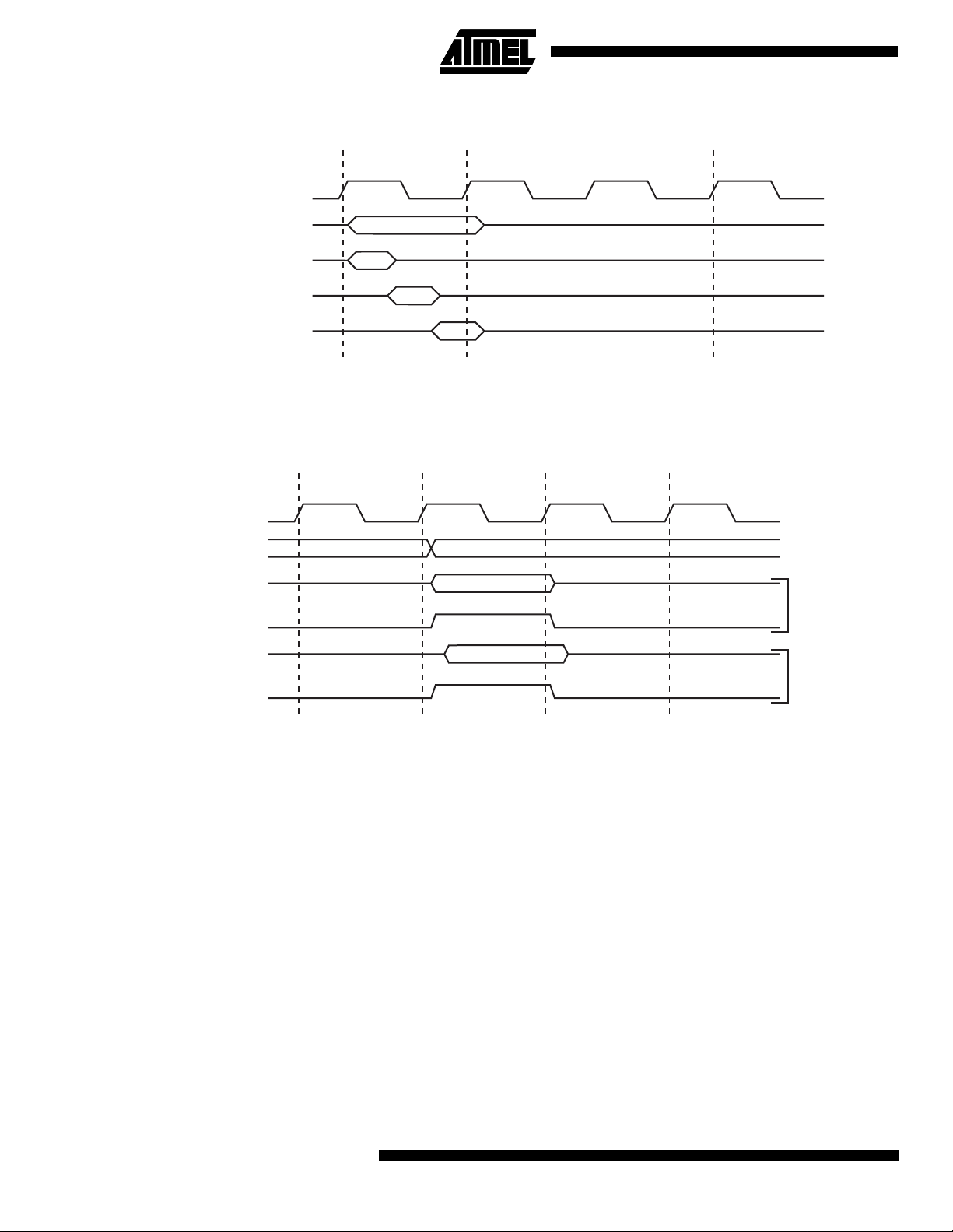

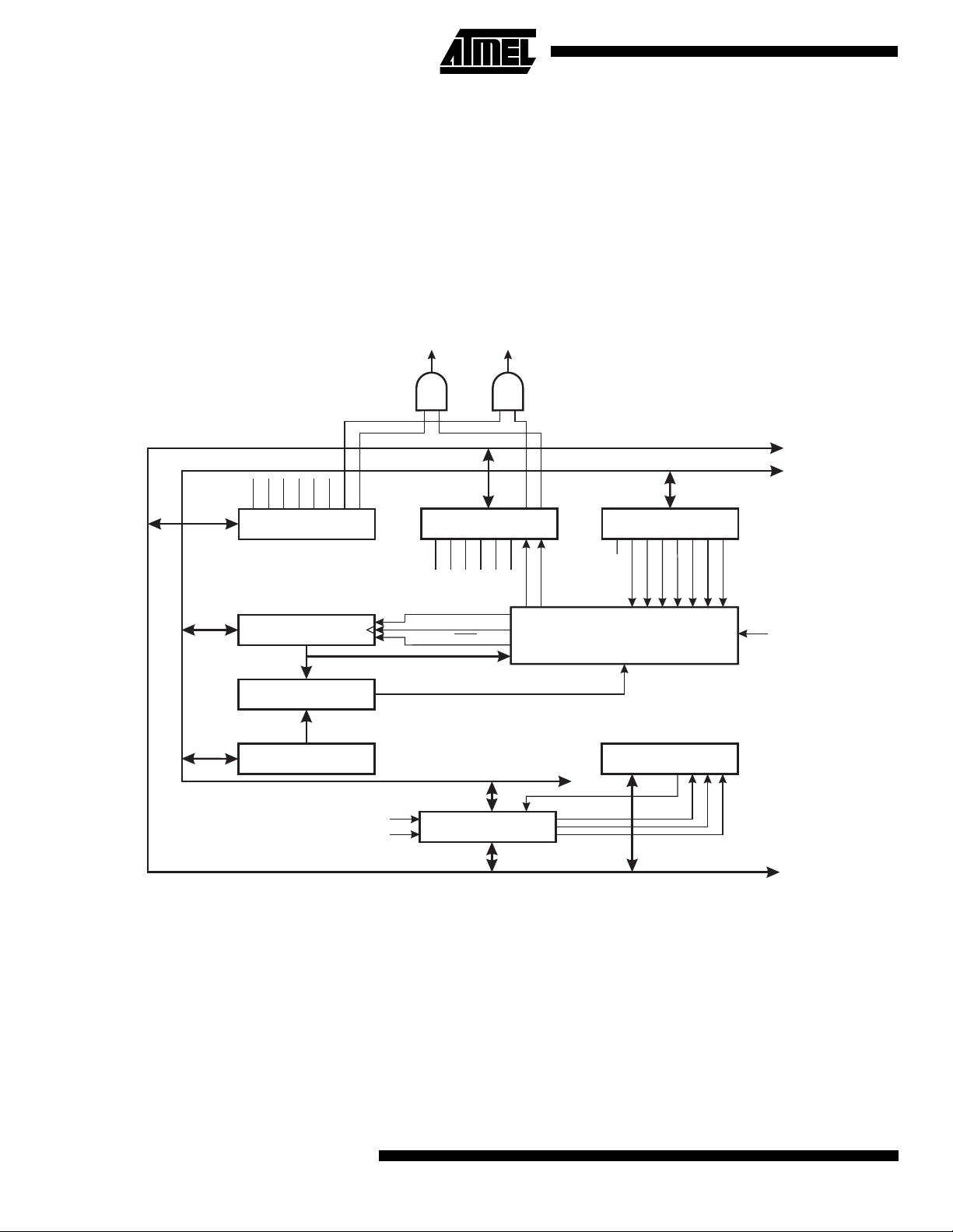

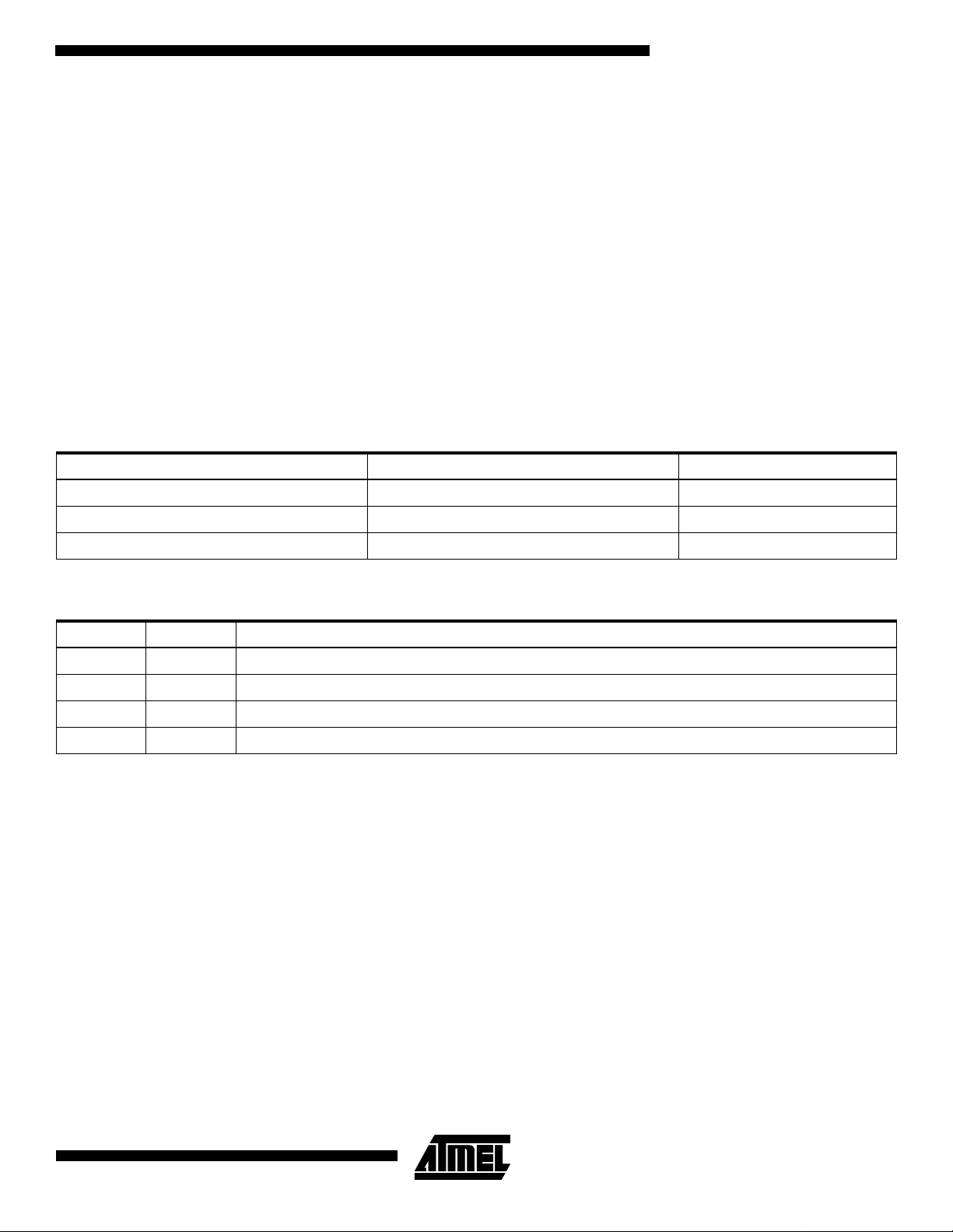

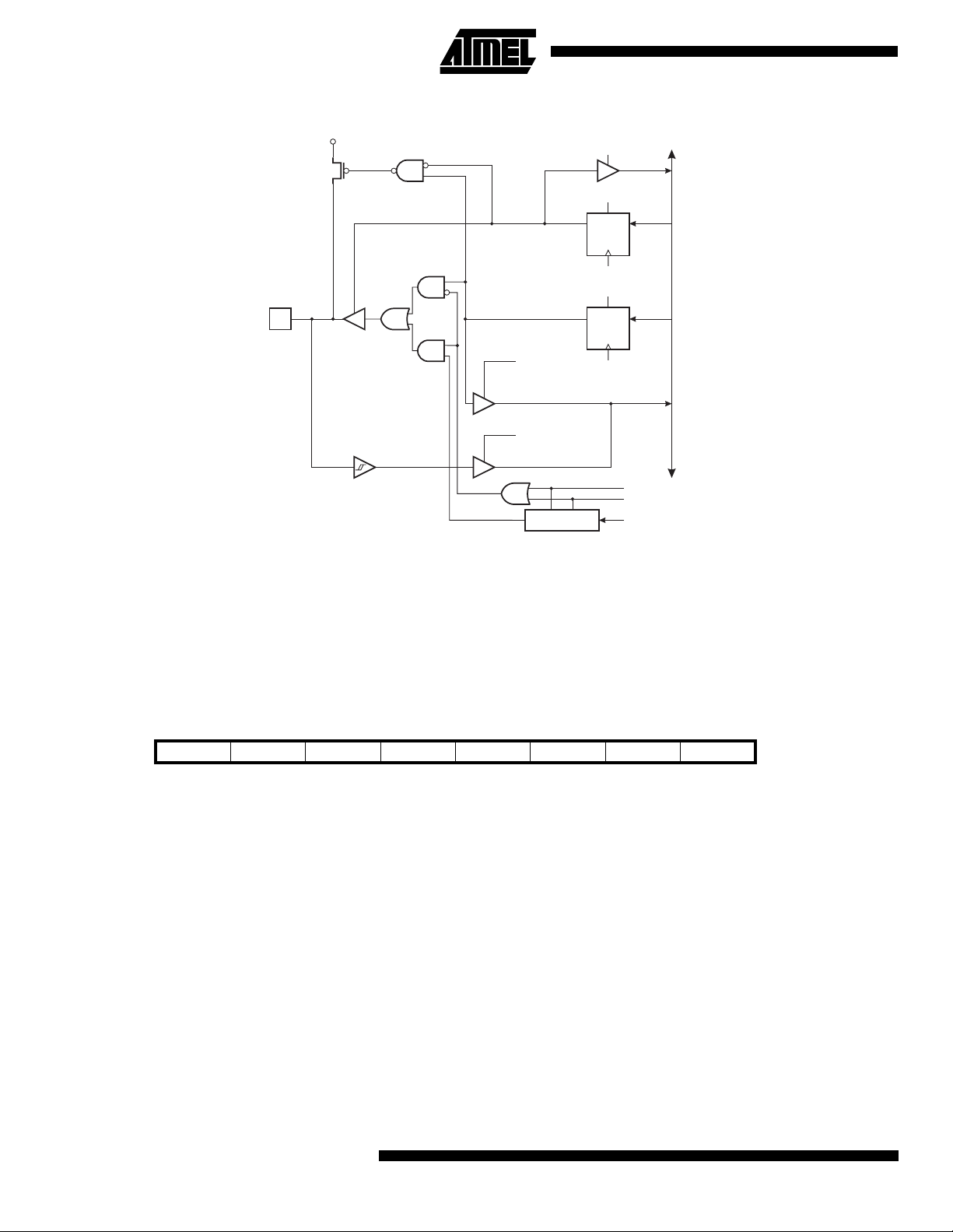

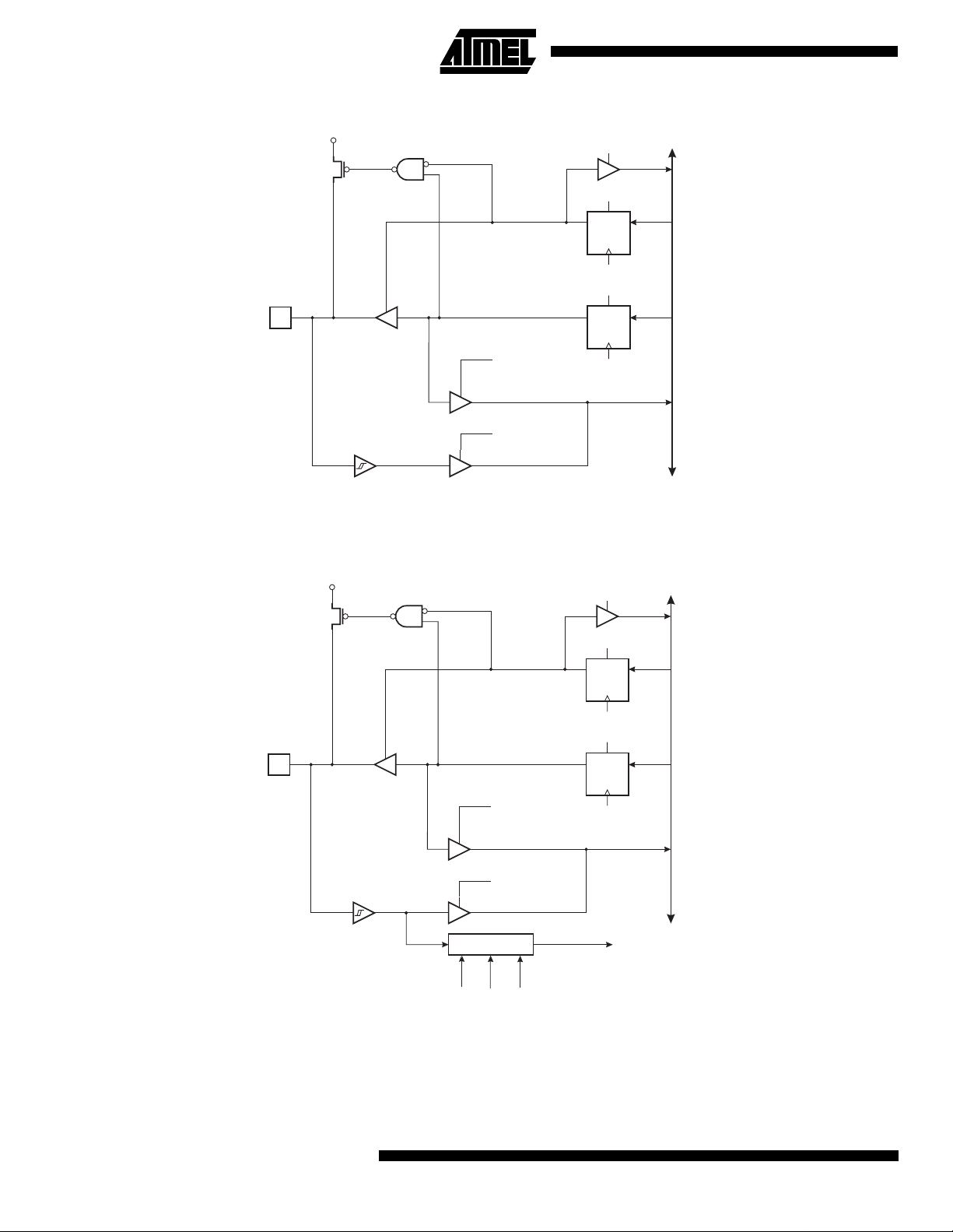

Figure 28. Prescaler for Timer/Counter 1 and Timer/Counter2

ATmega603/103

CK

T1

T2

CS20

CS21

CS22

0

TIMER/COUNTER2 CLOCK SOURCE

TCK2

10-BIT T/C PRESCALER

CK/8

CS10

CS11

CS12

CK/64

CK/256

0

TIMER/COUNTER1 CLOCK SOURCE

CK/1024

TCK1

For Timer/Counters 1 and 2, the four different prescaled selections are: CK/8, CK/64, CK/256 and CK/1024 where CK is

the CPU clock. Observe that CPU clock frequency can be lower than the XTAL frequency if the XTAL divider is enabled. For

Timer/Counters 1 and 2, added selections as CK, external source and stop, can be selected as clock sources.

Figure 29. The Timer/Counter0 Prescaler

CK

TOSC1

AS0

CS00

CS01

CS02

PCK0

10-BIT T/C PRESCALER

PCK0/8

TIMER/COUNTER0 CLOCK SOURCE

PCK0

PCK0/32

PCK0/64

PCK0/128

PCK0/256

PCK0/1024

35

Page 36

The clock source for Timer/Counter0 prescaler is named PCK0. PCK0 is by default connected to the main system clock

CK. Observe that CPU clock frequency can be lower than the XTAL frequency if the XTAL divider is enabled. By setting the

AS0 bit in ASSR , Timer/Counter 0 p rescaler is asy nchronously clo cked from the TOS C1 pin. This en ables use of

Timer/Counter0 as a Real Time Clock (RTC). A crystal can be connected between the TOSC1 and TOSC2 pins to serve as

an independent clock source for Timer/Counter0. This oscillator is optimized for use with a 32.768 kHz crystal.

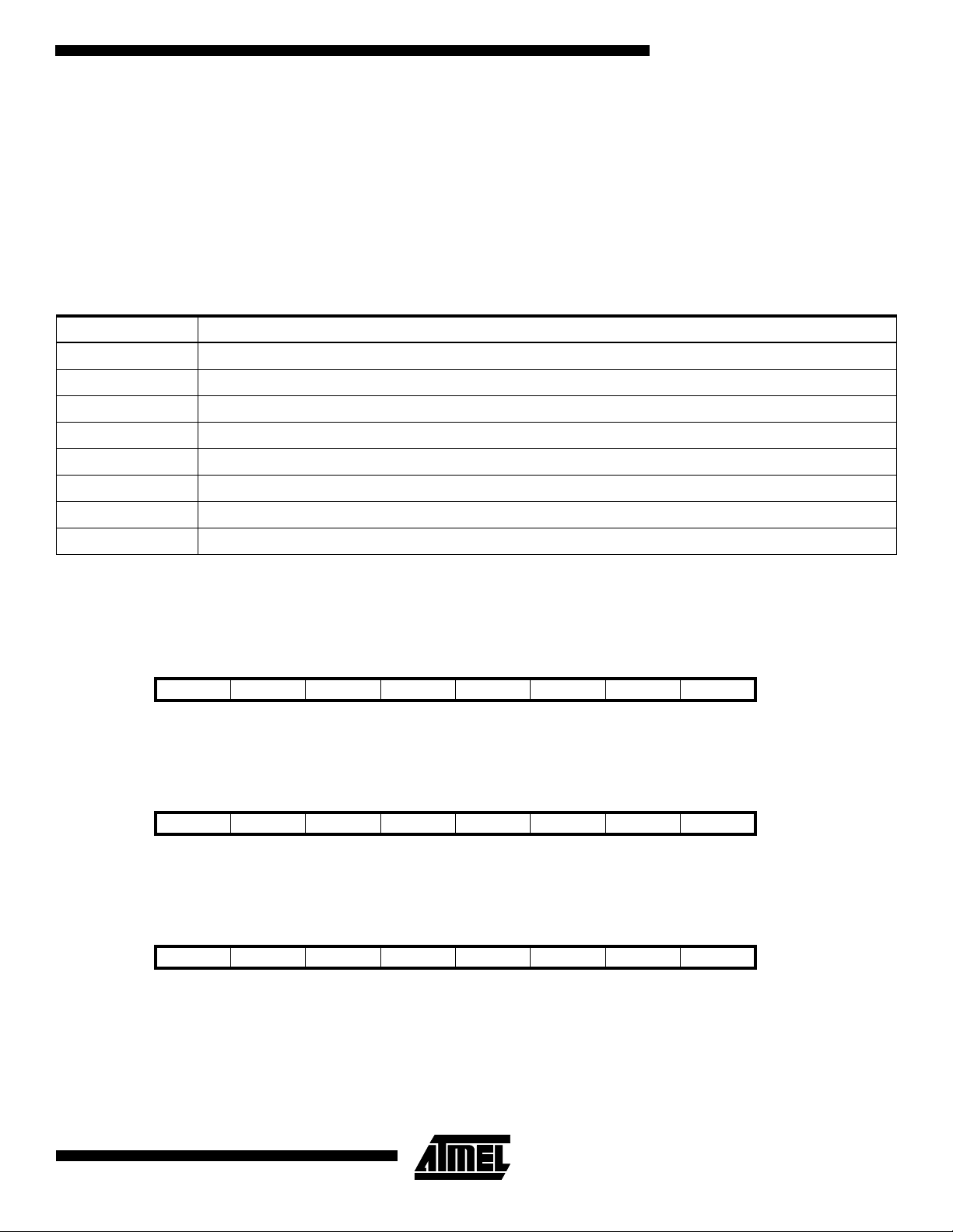

8-bit Timer/Counters T/C0 and T/C2

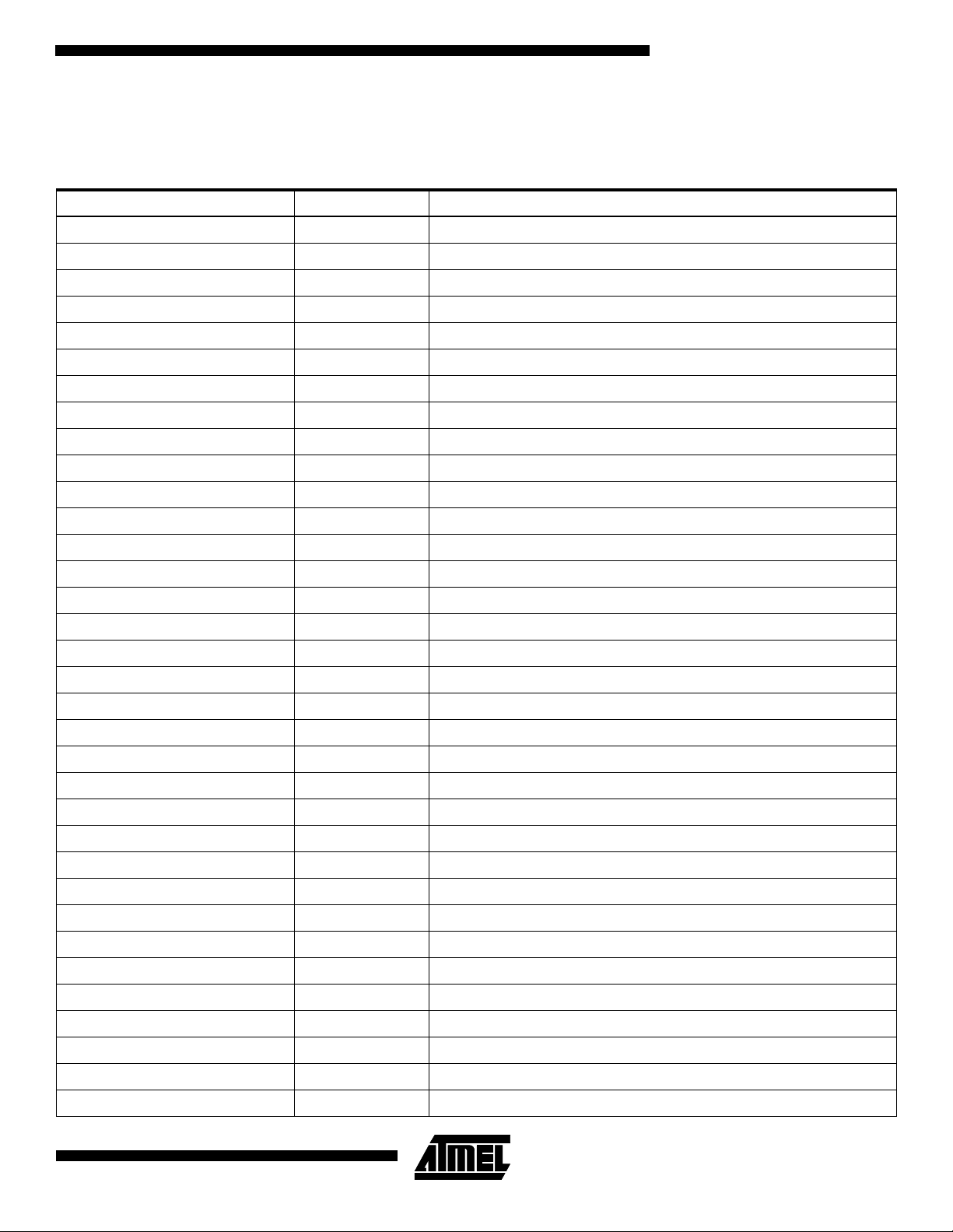

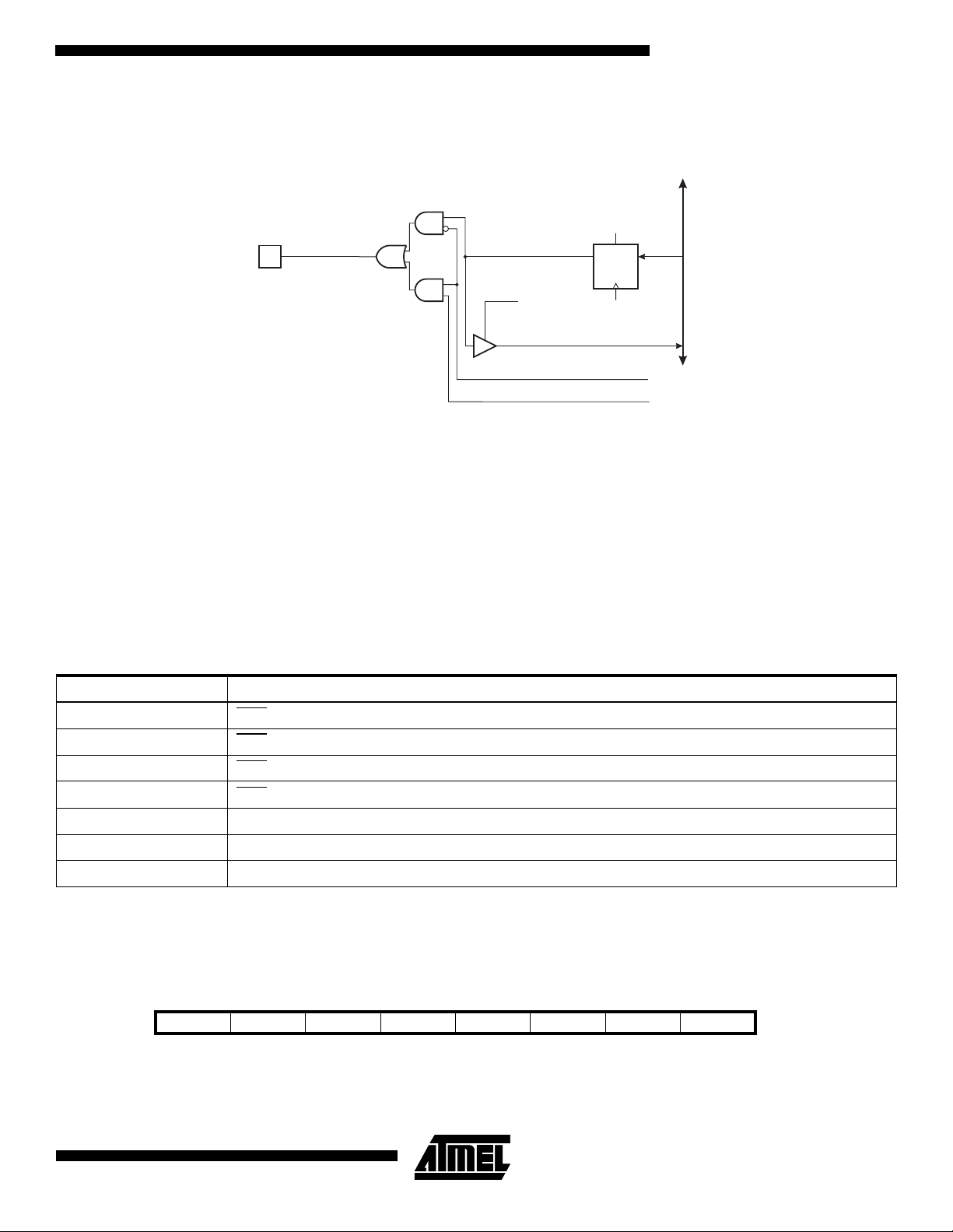

Figure 30 shows the block diagram for Timer/Counter0.

Figure 30. Timer/Counter0 Block Diagram

8-BIT DATA BUS

8-BIT ASYNCH T/C0 DATA BUS

OCIE1B

TOIE2

TICIE1

OCIE1A

OCIE2

TIMER INT. MASK

REGISTER (TIMSK)

7

TIMER/COUNTER0

(TCNT0)

7

8-BIT COMPARATOR

7

OUTPUT COMPARE

REGISTER0 (OCR0)

TOIE1

OCIE0

TOIE0

0

0

0

TCK0

CK

T/C0 OVER-

FLOW IRQ

TIMER INT. FLAG

REGISTER (TIFR)

TOV2

OCF2

T/C CLEAR

T/C CLK SOURCE

UP/DOWN

T/C0 COMPARE

MATCH IRQ

ICF1

OCF2B

OCF2A

SYNCH UNIT

OCF0

TOV0

T/C0 CONTROL

REGISTER (TCCR0)

CS02

CS01

CS00

CTC0

PWM0

COM01

TOV0

TOV1

OCF0

CONTROL

LOGIC

COM00

ASYNCH. STATUS

REGISTER (ASSR)

AS0

TC0UB

OCR0UB

PCK0

ICR0UB

36

ATmega603/103

Page 37

Figure 31. Timer/Counter2 Block Diagram

OCIE1B

TICIE1

(TCNT2)

OCIE1A

TOIE1

OCIE0

OCIE2

TOIE2

TIMER INT. MASK

REGISTER (TIMSK)

8-BIT DATA BUS

7

TIMER/COUNTER2

7

8-BIT COMPARATOR

TOIE0

0

0

T/C2 OVER-

FLOW IRQ

OCF2

TOV2

TIMER INT. FLAG

REGISTER (TIFR)

TOV2

OCF2

T/C CLEAR

T/C CLK SOURCE

UP/DOWN

T/C2 COMPARE

MATCH IRQ

ICF1

OCF2B

OCF2A

TOV1

OCF0

ATmega603/103

T/C2 CONTROL

REGISTER (TCCR2)

CS21

CS20

CS22

COM20

COM21

CTC2

CK

T2

TOV0

PWM2

CONTROL

LOGIC

7

OUTPUT COMPARE

REGISTER2 (OCR2)

0

Note: Figure 31 shows the block diagram for Timer/Counter2.

The 8-bit Timer/Cou nter0 can sele ct clock sourc e from PCK0 or pres caled PCK0 . The 8-bit Timer /Counter2 can s elect

clock source from CK, prescaled CK, or an external pin. Both Timer/Counters can be stopped as described in the specification for the Timer/Counter Control Registers - TCCR0 and TCCR2.

The different status flags (overflow, compare match and capture event) are found in the Timer/Counter Interrupt Flag Register - TIFR. Control signals are found in the Timer/Counter Control Registers - TCCR0 and TCCR2. The interrupt

enable/disable settings are found in the Timer/Counter Interrupt Mask Register - TIMSK.

When Timer/Counter2 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To

assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one

internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counters feature a high resolution and a high accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities m ake these un its useful for lower speed function s or exact ti ming functions wi th

infrequent actions.

Both Timer/Counters support two Output Compare functions using the Output Compare Registers - OCR0 and OCR2 as

the data source to be compared to the Timer/Counter contents. The Output Compare functions include optional clearing of

the counter on compare match, and action on the O utput Compare Pins - PB4( OC0/PWM0) and PB7(OC2/PW M2) - on

compare match.

Timer/Counter0 and 2 can also be used as 8-bit Pulse Width Modulators. In this mode the Timer/Counter and the output

compare register serve as a glitch-free, stand-alone PWM with centered pulses. Refer to page 40 for a detailed description

on this function.

37

Page 38

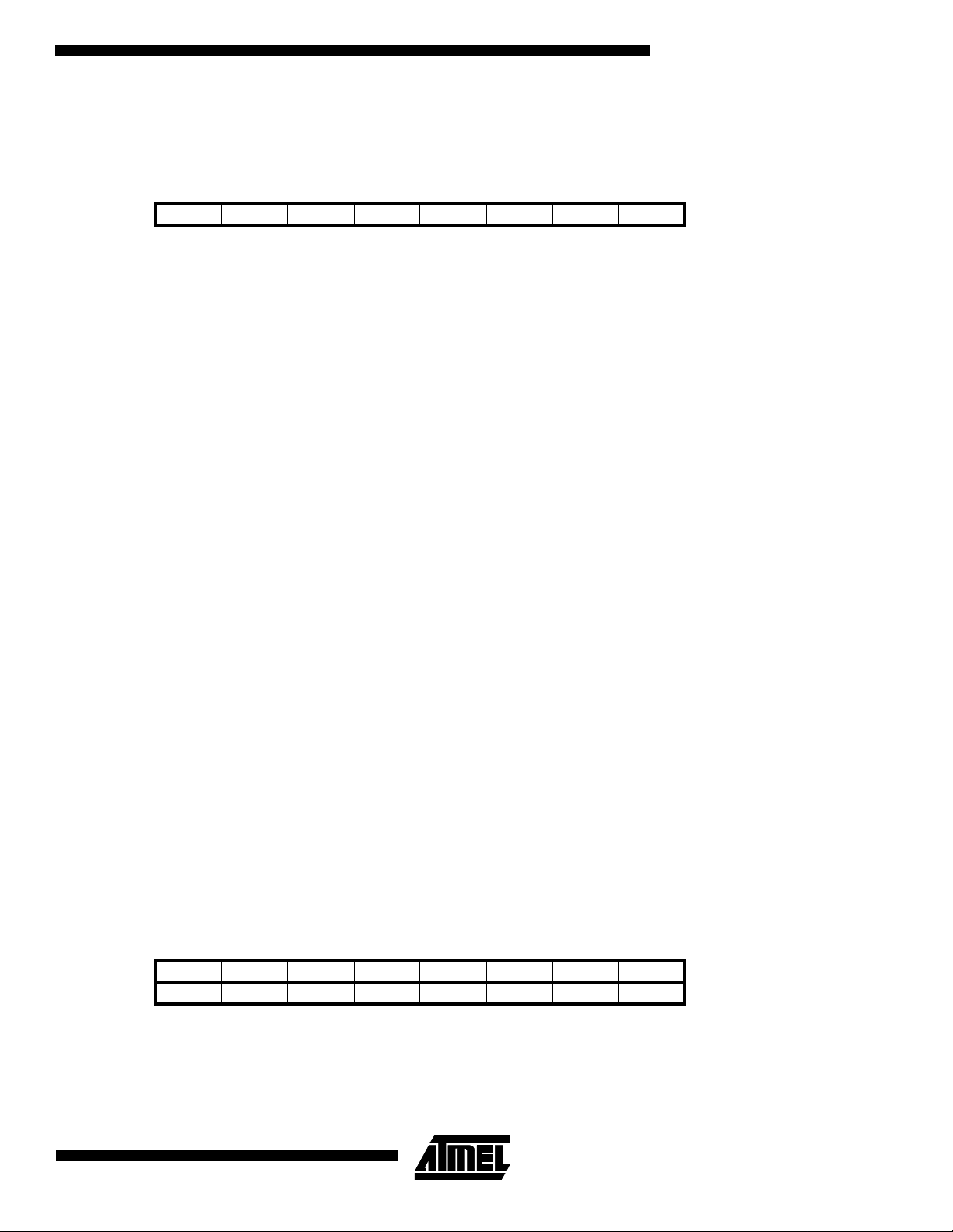

Timer/Counter0 Control Register - TCCR0

Bit 7 6 5 4 3 2 1 0

33 ($53) - PWM0 COM01 COM00 CTC0 CS02 CS01 CS00 TCCR0

Read/Write R R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

Timer/Counter2 Control Register - TCCR2

Bit 7 6 5 4 3 2 1 0

$25 ($45) - PWM2 COM21 COM20 CTC2 CS22 CS21 CS20 TCCR2

Read/Write R R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

•

Bit 7 - Res: Reserved Bit

This bit is a reserved bit in the ATmega603/103 and always reads as zero.

Bit 6 - PWM0 / PWM2: Pulse Width Modulator Enable

•

When set (one) this bit enables PWM mode for Timer/Counter0 or Timer/Counter2. This mode is described on page 40.