Page 1

Features

• Configurations:

– Can be configured as a combination of touchscreen, sliders/wheels and keys, with

Adjacent Key Suppression

• QField

™

Touchscreen:

– Two-touch capable with independent XY tracking for one or two concurrent

touches in real time, with touch size reporting

– Up to eight-inch diagonal screen size supported

– 1024 x 1024 resolution

• Discrete Keys:

– Up to 32 (subject to other configurations)

• QSlide

™

/QWheel™:

– Configurable up to four independent sliders/wheels

• Linearity:

– Screen design dependent but typically better than ±1 percent

• Filtering:

– Advanced digital filtering (user configurable)

• Response Times:

– Sub 15 ms possible, depending on filter settings

• Technolo g y:

– Patented charge-transfer (transverse mode)

• Panel Thickness:

– Glass up to 5 mm, screen size dependent

– Plastic up to 3 mm, screen size dependent

• Channel Sensitivity:

– Individually settable via simple commands over serial interface

• Interface:

2

C-compatible slave mode, 100 kHz or 400 kHz with 2.7V or greater Vdd

–I

• Power:

– 1.8V to 5.5V (2.7V to 5.5V in high speed mode)

• Packages:

– 32-pin 5 x 5mm MLF RoHS compliant

• Signal Processing:

– Self-calibration, auto drift compensation, noise filtering, Adjacent Key

Suppression technology

™

(AKS™) technology between groups

QTwo™ 10-bit

Touchscreen

Controller

AT42QT5320

Summary

Note: This is a summary document. A

complete document is available under

NDA. For more information contact

www.atmel.com/touchscreen.

9509AS–AT42–10/08

Page 2

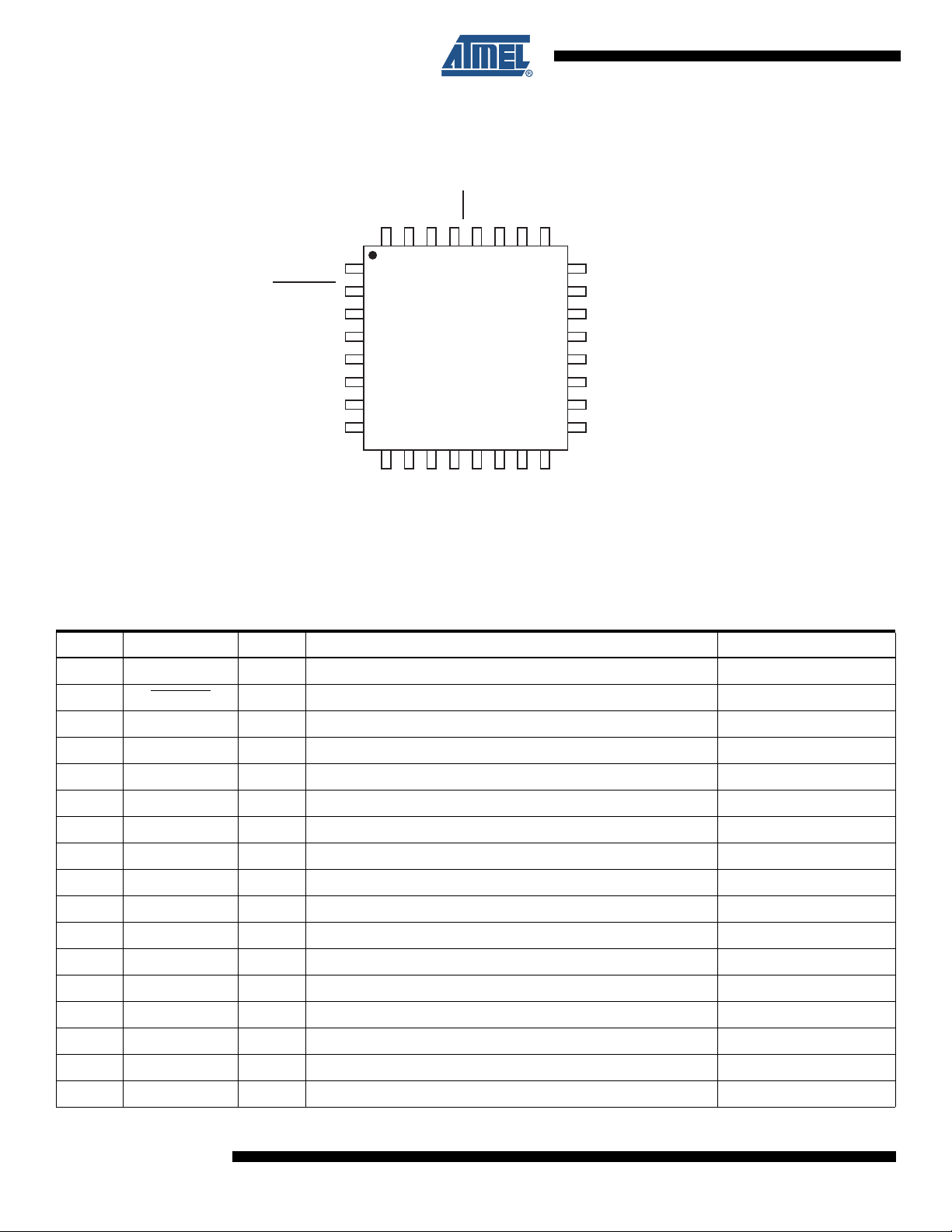

1. Pinout and Schematic

Y2A

Y1A

Y0A

RST

SCL

SDA

Y3B

Y2B

TRIGGER

VREF

SMPX0X1X2X3

X4

Y3A

CHANGE

Vss

Vdd

Vss

Vdd

X6

X7 X5

Vdd

Vdd

Vss

A0

Y0B

Y1B

1

2

3

4

5

6

7

817

18

19

20

21

22

23

24

32

31

30

29

282726

25

9

10

11

16

15

14

13

12

QT5320

FORCE_S

1.1 Pinout Configuration

1.2 Pin Descriptions

Table 1-1. Pin Listing

Pin Name Type Comments If Unused, Connect To...

1 Y3A I Y line connection Leave open

2 CHANGE OD State change notification –

3 Vss P Supply ground –

4 Vdd P Power –

5 Vss P Supply ground –

6 Vdd P Power –

7 X6 O X matrix drive line Leave open

8 X7 O X matrix drive line Leave open

9 TRIGGER I Trigger input (active low) Vdd or Vss

10 Vref I Supply ground –

11 SMP O Sample output. –

12 X0 O X matrix drive line Leave open

13 X1 O X matrix drive line Leave open

14 X2 O X matrix drive line Leave open

15 X3 O X matrix drive line Leave open

16 X4 O X matrix drive line Leave open

17 X5 O X matrix drive line Leave open

2

QT5320

9509AS–AT42–10/08

Page 3

QT5320

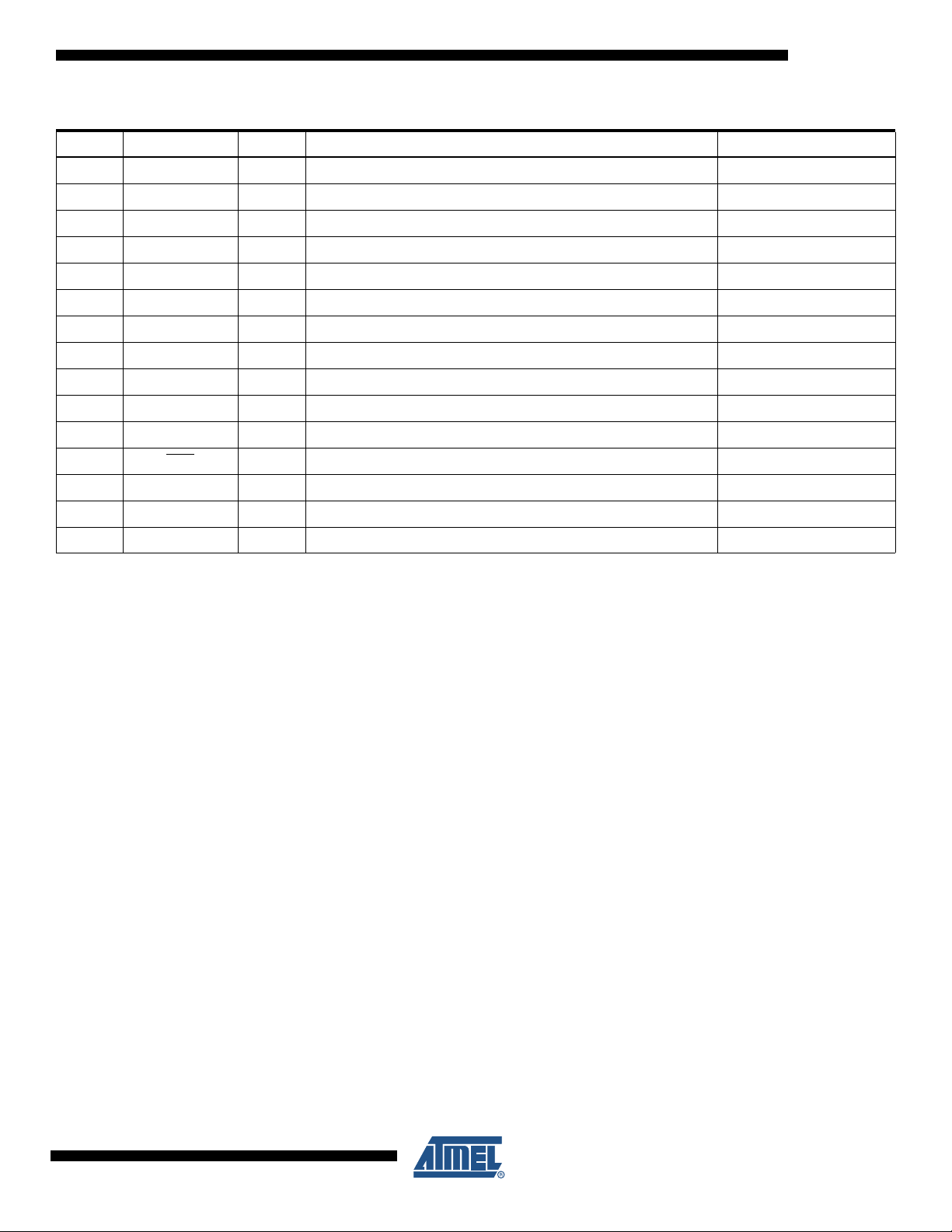

Table 1-1. Pin Listing

Pin Name Type Comments If Unused, Connect To...

18 Vdd P Power –

19 FORCE_S I Force sensor input Vdd or Vss

20 Vdd P Power –

21 Vss P Supply ground –

22 A0 I I2C-compatible address select –

23 Y0B I Y line connection Leave open

24 Y1B I Y line connection Leave open

25 Y2B I Y line connection Leave open

26 Y3B I Y line connection Leave open

27 SDA OD Serial Interface Data –

28 SCL OD Serial Interface Clock –

29 RST

30 Y0A I Y line connection Leave open

I Reset low; has internal 30k - 60k pull-up Leave open or Vdd

31 Y1A I Y line connection Leave open

32 Y2A I Y line connection Leave open

9509AS–AT42–10/08

3

Page 4

1.3 Schematic

Rp

Rp Rp

Ry3

Ry2

Ry1

Ry0

Rs2 Rs0

SCL

SDA

Creg

VREG

Rx7

Cs3

Cs2

Cs1

Cs0

Rx1

Rx4

VDD

Rs3 Rs1

Rx3

Rx2

Rx6

Rx0

Rx5

Vunreg

VDD

VDD

MATRIXYSCANIN

ADDRESS SELECT

FORCE SENSOR

CHANGE

Creg

TRIGGER

I2C

QT5320

Follow regulator manufacturer's recommended values

for input and output bypass capacitors (Creg).

Add two 100nF capacitors: one close to pins 4 and 6,

and another close to pins 18 and 20.

MATRIX X DRIVE

NOTES:

1) The central pad on the underside of the chip

is a Vss pin and should be connected to ground.

Do not put any other tracks underneath

the body of the chip.

2) It is important to place all Cs, Rs, Rx and Ry

components physically near to the chip.

3) Leave YnA, YnB unconnected if not used.

Figure 1-1. Typical Circuit

Suggested regulator manufacturers:

• Torex (XC6215 series)

• Seiko (S817 series)

• BCDSemi (AP2121 series)

4

QT5320

9509AS–AT42–10/08

Page 5

2. Overview of the QT5320

2.1 Introduction

The QT5320 is a versatile capacitive touchscreen controller, able to support a diagonal

touchscreen of up to 8 inches. The IC supports Two Touch

of devices from Atmel

The QT5320 uses Atmel's patented QMatrix

excellent moisture tolerance, fast acquisition and outstanding ground load immunity.

A unique feature of the QT5320 is that it allows a choice to be made as to how many of the

capacitive measurement channels form part of a touchscreen, and which ones form discrete

keys or sliders.

This controller offers unrivalled flexibility to create touchscreens, sliders and keys. The device can

report two touches on a touchscreen making it suitable for next generation touch interfaces.

Concurrent use of a touchscreen plus keys or sliders is also possible.

By treating all capacitive channels equally during measurement, and then applying additional signal

processing, the device allows the channels to be used as part of a touchscreen, or part of one or more

sliders, or as discrete touch keys.

QT5320

™

®

.

™

capacitive sensing technique, which offers

operation, part of the QTwo™ family

Touchscreens can be created that are of arbitrary channel length and width. Channels not used in the

touchscreen can either be turned into sliders or keys. There are some constraints on the starting

channels for touchscreens and sliders, but these have no practical impact for most applications.

The controller also has the ability to save a Y line when configuring a touchscreen, reusing it in the

touchscreen pattern at the two edges. This saved Y line can then be used to create extra objects like

a slider or multiple keys, while allowing the touchscreen to be sized as though it was “one Y line

larger”. In this “wrapped Y line” mode Two Touch processing cannot be used.

See Figure 2-1 for configuration examples.

9509AS–AT42–10/08

5

Page 6

Figure 2-1. Example Touchscreen Configurations

Y

X

QT5320

Y3

Y2

Y1

Y0

X0 X1 X2 X3 X4 X5 X6 X7

Y

X

Y3

Y2

Y1

Y0

X0 X1 X2 X3 X4 X5 X6 X7

QT5320

= slider

= touchscreen

= key

= disabled

Object Color Code

6

QT5320

9509AS–AT42–10/08

Page 7

3. Revision History

Revision No. History

Revision AS – October 2008 Initial release for chip revision 5.0

QT5320

9509AS–AT42–10/08

7

Page 8

Headquarters International

Atmel Corporation

2325 Orchard Parkway

San Jose, CA 95131

USA

Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

Atmel Asia

Unit 01-05 & 16, 19/F

BEA Tower, Millennium City 5

418 Kwun Tong Road

Kwun Tong

Kowloon

Hong Kong

Tel: (852) 2245-6100

Fax: (852) 2722-1369

Touch Technology Division

1 Mitchell Point

Ensign Way

Hamble

Southampton

Hampshire SO31 4RF

United Kingdom

Tel: (44) 23-8056-5600

Fax: (44) 23-8045-3939

Product Contact

Web Site

www.atmel.com

Atmel Europe

Le Krebs

8, Rue Jean-Pierre Timbaud

BP 309

78054 Saint-Quentin-enYvelines Cedex

France

Tel: (33) 1-30-60-70-00

Fax: (33) 1-30-60-71-11

Technical Support

touch@atmel.com

Atmel Japan

9F, Tonetsu Shinkawa Bldg.

1-24-8 Shinkawa

Chuo-ku, Tokyo 104-0033

Japan

Tel: (81) 3-3523-3551

Fax: (81) 3-3523-7581

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any

intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND

CONDITIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR

STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL,

PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR

LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY

OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the

right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information

contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are

not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel®, Atmel logo and combinations thereof, and others are registered trademarks, Adjacent

Key Suppression

™

, AKS™, QField™, QMatrix™, QTouch™, QSlide™, QWheel™, Tw o To u c h™, QTwo™ and others are trademarks of Atmel

Corporation or its subsidiaries. Other terms and product names may be registered trademarks or trademarks of others.

9509AS–AT42–10/08

Loading...

Loading...