Page 1

Features

5

6

7

8

9

10

11

12

13

29

28

27

26

25

24

23

22

21

A6

A5

A4

A3

A2

A1

A0

NC

I/O0

A8

A9

A11

NC

OE

A10

CE

I/O7

I/O6

432

1

323130

14151617181920

I/O1

I/O2

GND

DC

I/O3

I/O4

I/O5

A7

A12

A14DCVCCWEA13

• Fast Read Access Time – 150 ns

• Automatic Page Write Operation

– Internal Address and Data Latches for 64 Bytes

– Internal Control Timer

• Fast Write Cycle Times

– Page Write Cycle Time: 3 ms or 10 ms Maximum

– 1 to 64-byte Page Write Operation

• Low Power Dissipation

– 50 mA Active Current

– 200 µA CMOS Standby Current

• Hardware and Software Data Protection

• DATA Polling for End of Write Detection

• High Reliability CMOS Technology

– Endurance: 104 or 105 Cycles

– Data Retention: 10 Years

• Single 5V ± 10% Supply

• CMOS and TTL Compatible Inputs and Outputs

• JEDEC Approved Byte-wide Pinout

• Full Military, Commercial, and Industrial Temperature Ranges

Description

The AT28C256 is a high-performance electrically erasable and programmable read

only memory. Its 256K of memory is organized as 32,768 words by 8 bits. Manufactured with Atmel’s advanced nonvolatile CMOS technology, the device offers access

times to 150 ns with power dissipation of just 440 mW. When the device is deselected,

the CMOS standby current is less than 200 µA.

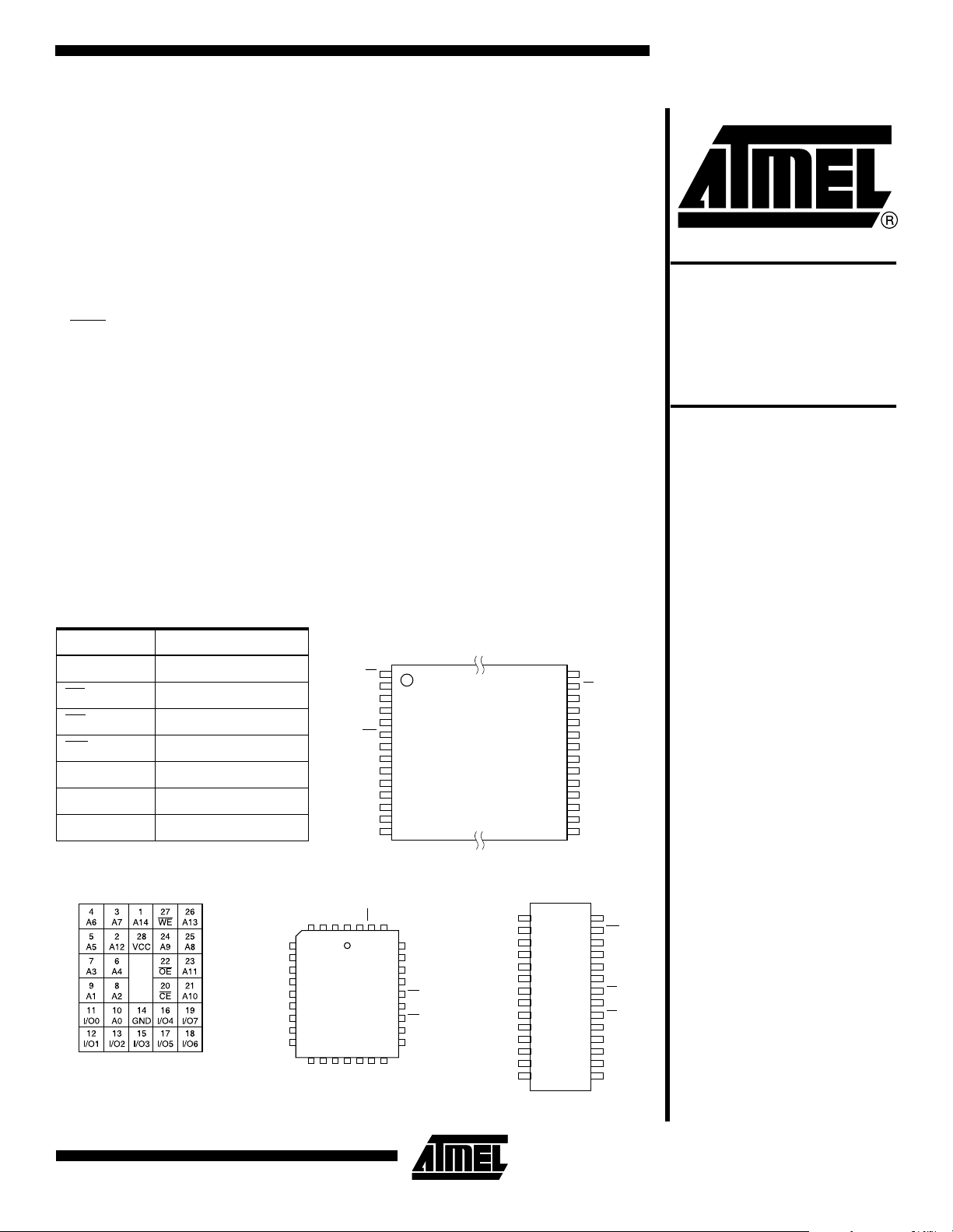

Pin Configurations

Pin Name Function

TSOP

Top V ie w

(continued)

256K (32K x 8)

Paged Parallel

EEPROM

AT28C256

A0 - A14 Addresses

CE

OE

WE

Chip Enable

Output Enable

Write Enable

I/O0 - I/O7 Data Inputs/Outputs

NC No Connect

DC Don’t Connect

PGA

Top V ie w

1

OE

2

A11

3

A9

4

A8

5

A13

6

WE

7

VCC

8

A14

9

A12

10

A7

11

A6

12

A5

13

A4

14

A3

LCC, PLCC

Top V i e w

Note: PLCC package pins 1 and

17 are DON’T CONNECT.

28

A10

27

CE

26

I/O7

25

I/O6

24

I/O5

23

I/O4

22

I/O3

21

GND

20

I/O2

19

I/O1

18

I/O0

17

A0

16

A1

15

A2

CERDIP, PDIP, FLATPACK,

SOIC — Top V ie w

1

28

A14

A12

I/O0

I/O1

I/O2

GND

2

3

A7

4

A6

5

A5

6

A4

7

A3

8

A2

9

A1

10

A0

11

12

13

14

VCC

27

WE

26

A13

25

A8

24

A9

23

A11

22

OE

21

A10

20

CE

19

I/O7

18

I/O6

17

I/O5

16

I/O4

15

I/O3

Rev. 0006H–12/99

1

Page 2

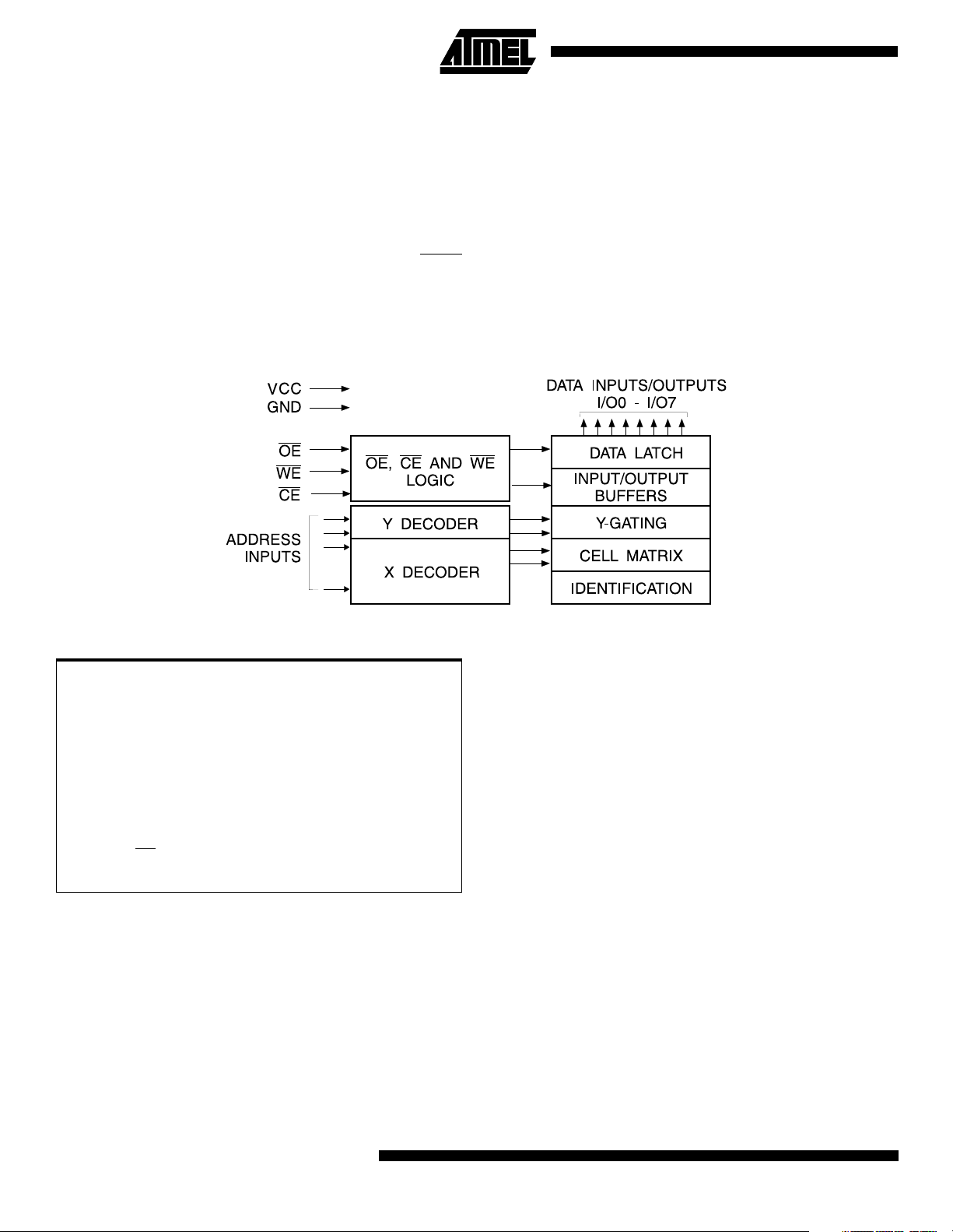

The AT28C256 is accessed like a Static RAM for the read

or write cycle without the need for external components.

The device contains a 64-byte page register to allow writing

of up to 64 bytes simultaneously. During a write cycle, the

addresses and 1 to 64 bytes of data are internally latched,

freeing the address and data bus for other operations.

Following the initiation of a write cycle, the device will automatically write the latched data using an internal control

timer. The end of a write cycle can be detected by DATA

Polling of I/O7. Once the end of a write cycle has been

detected a new access for a read or write can begin.

Block Diagram

Atmel’s 28C256 has additional features to ensure high

quality and manufacturability. The device utilizes internal

error correction for extended endurance and improved data

retention characteristics. An optional software data protection mechanism is available to guard against inadvertent

writes. The device also includes an extra 64 bytes of

EEPROM for device identification or tracking.

Absolute Maximum Ratings*

Temperature under Bias ................................ -55°C to +125°C

Storage Temperature ..................................... -65°C to +150°C

All Input Voltages

(including NC Pins)

with Respect to Ground...................................-0.6V to +6.25V

All Output Voltages

with Respect to Ground.............................-0.6V to V

Voltage on OE

with Respect to Ground...................................-0.6V to +13.5V

and A9

+ 0.6V

CC

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions for extended periods may affect

device reliability

2

AT28C256

Page 3

AT28C256

Device Operation

READ: The AT28C256 is accessed like a Static RAM.

When CE

at the memory location determined by the address pins is

asserted on the outputs. The outputs are put in the high

impedance state when either CE

line control gives designers flexibility in preventing bus contention in their system.

BYTE WRITE: A low pulse on the WE

or WE low (respectively) and OE high initiates a write cycle.

The address is latched on the falling edge of CE

whichever occurs last. The data is latched by the first rising

edge of CE

will automatically time itself to completion. Once a programming operation has been initiated and for the duration

of t

operation.

PAGE WRITE: The page write operation of the AT28C256

allows 1 to 64 bytes of data to be written into the device

during a single internal programming period. A page write

operation is initiated in the same manner as a byte write;

the first byte written can then be followed by 1 to 63 additional bytes. Each successive byte must be written within

150 µs (t

exceeded the AT28C256 will cease accepting data and

commence the internal programming operation. All bytes

during a page write operation must reside on the same

page as defined by the state of the A6 - A14 inputs. For

each WE

tion, A6 - A14 must be the same.

The A0 to A5 inputs are used to specify which bytes within

the page are to be written. The bytes may be loaded in any

order and may be altered within the same load period. Only

bytes which are specified for writing will be written; unnecessary cycling of other bytes within the page does not

occur.

DATA

indicate the end of a write cycle. During a byte or page

write cycle an attempted read of the last byte written will

result in the complement of the written data to be presented

on I/O

data is valid on all outputs, and the next write cycle may

begin. DATA

cycle.

TOGGLE BIT: In addition to DATA

provides another method for determining the end of a write

cycle. During the write operation, successive attempts to

read data from the device will result in I/O

between one and zero. Once the write has completed, I/O

will stop toggling and valid data will be read. Reading the

toggle bit may begin at any time during the write cycle.

DATA PROTECTION: If precautions are not taken, inadvertent writes may occur during transitions of the host

and OE are low and WE is high, the data stored

or OE is high. This dual-

or CE input with CE

or WE,

or WE. Once a byte write has been started it

, a read operation will effectively be a polling

WC

) of the previous byte. If the t

BLC

BLC

limit is

high to low transition during the page write opera-

POLLING: The AT28C256 features DATA Polling to

. Once the write cycle has been completed, true

7

Polling may begin at anytime during the write

Polling the AT28C256

toggling

6

system power supply. Atmel has incorporated both hardware and software features that will protect the memory

against inadvertent writes.

HARDWARE PROTECTION: Hardware features protect

against inadvertent writes to the AT28C256 in the following

ways: (a) V

write function is inhibited; (b) V

V

has reached 3.8V the device will automatically time out

CC

sense – if VCC is below 3.8V (typical) the

CC

power-on delay – once

CC

5 ms (typical) before allowing a write; (c) write inhibit –

holding any one of OE

low, CE high or WE high inhibits

write cycles; and (d) noise filter – pulses of less than 15 ns

(typical) on the WE

or CE inputs will not initiate a write

cycle.

SOFTWARE DATA PROTECTION: A software controlled

data protection feature has been implemented on the

AT28C256. When enabled, the software data protection

(SDP), will prevent inadvertent writes. The SDP feature

may be enabled or disabled by the user; the AT28C256 is

shipped from Atmel with SDP disabled.

SDP is enabled by the host system issuing a series of three

write commands; three specific bytes of data are written to

three specific addresses (refer to “Software Data Protection” algorithm). After writing the 3-byte command

sequence and after t

the entire AT28C256 will be pro-

WC

tected against inadvertent write operations. It should be

noted, that once protected the host may still perform a byte

or page write to the AT28C256. This is done by preceding

the data to be written by the same 3-byte command

sequence used to enable SDP.

Once set, SDP will remain active unless the disable command sequence is issued. Power transitions do not disable

SDP and SDP will protect the AT28C256 during power-up

and power-down conditions. All command sequences must

conform to the page write timing specifications. The data in

the enable and disable command sequences is not written

to the device and the memory addresses used in the

sequence may be written with data in either a byte or page

write operation.

After setting SDP, any attempt to write to the device without

the 3-byte command sequence will start the internal write

timers. No data will be written to the device; however, for

the duration of t

, read operations will effectively be poll-

WC

ing operations.

DEVICE IDENTIFICATION: An extra 64 bytes of EEPROM

memory are available to the user for device identification.

By raising A9 to 12V ± 0.5V and using address locations

7FC0H to 7FFFH the additional bytes may be written to or

read from in the same manner as the regular memory

array.

6

OPTIONAL CHIP ERASE MODE: The entire device can

be erased using a 6-byte software code. Please see “Soft-

ware Chip Erase” application note for details.

3

Page 4

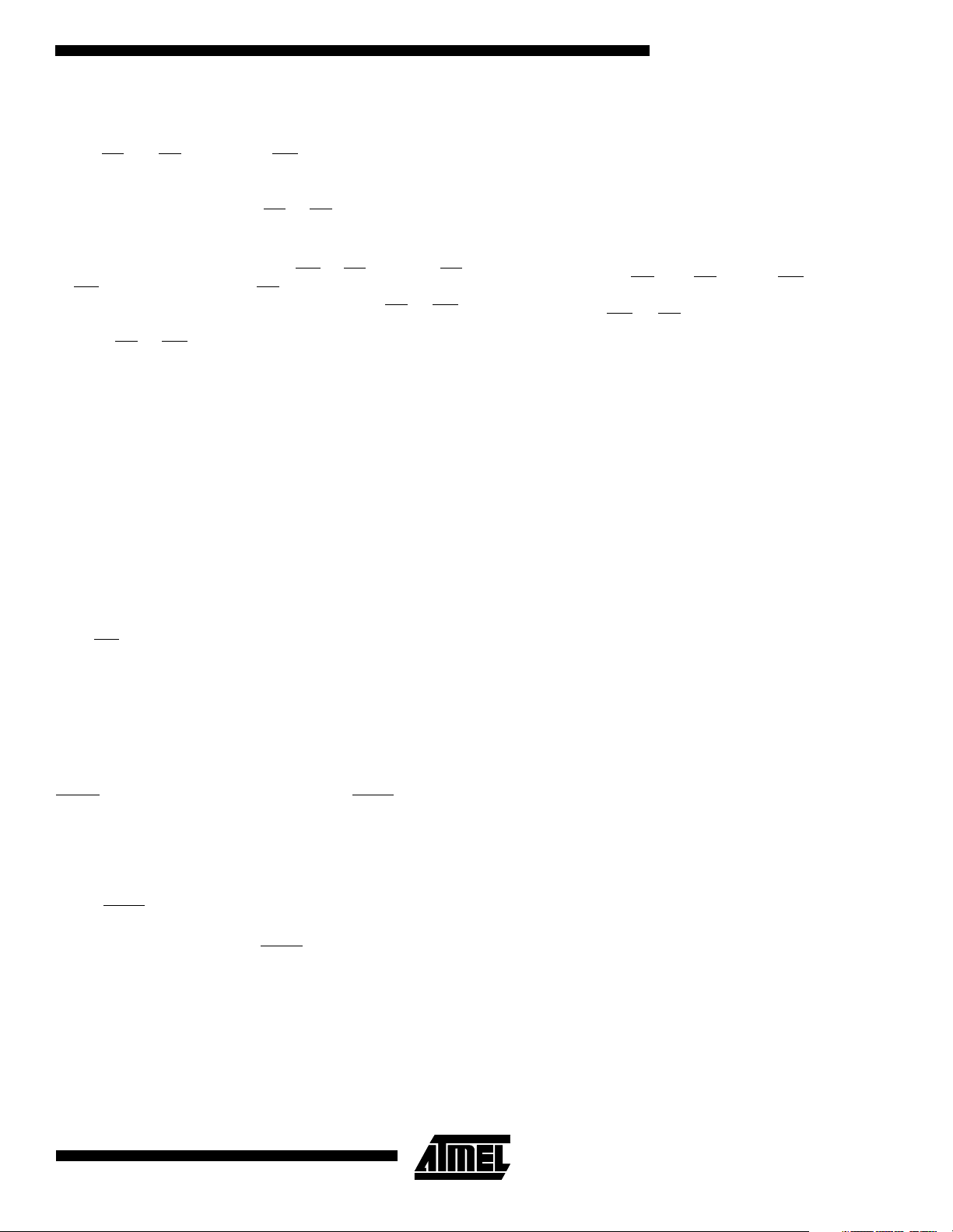

DC and AC Operating Range

AT28C256-15 AT28C256-20 AT28C256-25 AT28C256-35

Com. 0°C - 70°C0°C - 70°C0°C - 70°C

Operating

Temperature (Case)

Ind. -40°C - 85°C-40°C - 85°C-40°C - 85°C

Mil. -55°C - 125°C-55°C - 125°C-55°C - 125°C-55°C - 125°C

V

Power Supply 5V ± 10% 5V ± 10% 5V ± 10% 5V ± 10%

CC

Operating Modes

Mode CE OE WE I/O

Read V

(2)

Write

Standby/Write Inhibit V

IL

V

IL

IH

Write Inhibit X X V

Write Inhibit X V

Output Disable X V

Chip Erase V

IL

V

IL

V

IH

(1)

X

IL

IH

(3)

V

H

V

IH

V

IL

D

OUT

D

X High Z

IH

X

X High Z

V

IL

High Z

IN

Notes: 1. X can be VIL or VIH.

2. Refer to AC programming waveforms.

= 12.0V ± 0.5V.

3. V

H

DC Characteristics

Symbol Parameter Condition Min Max Units

I

I

I

I

I

V

V

V

V

LI

LO

SB1

SB2

CC

IL

IH

OL

OH

Input Load Current VIN = 0V to VCC + 1V 10 µA

Output Leakage Current V

= 0V to V

I/O

CC

10 µA

Com., Ind. 200 µA

VCC Standby Current CMOS CE = V

- 0.3V to VCC + 1V

CC

Mil. 300 µA

VCC Standby Current TTL CE = 2.0V to VCC + 1V 3 mA

V

Active Current f = 5 MHz; I

CC

= 0 mA 50 mA

OUT

Input Low Voltage 0.8 V

Input High Voltage 2.0 V

Output Low Voltage IOL = 2.1 mA 0.45 V

Output High Voltage IOH = -400 µA 2.4 V

4

AT28C256

Page 5

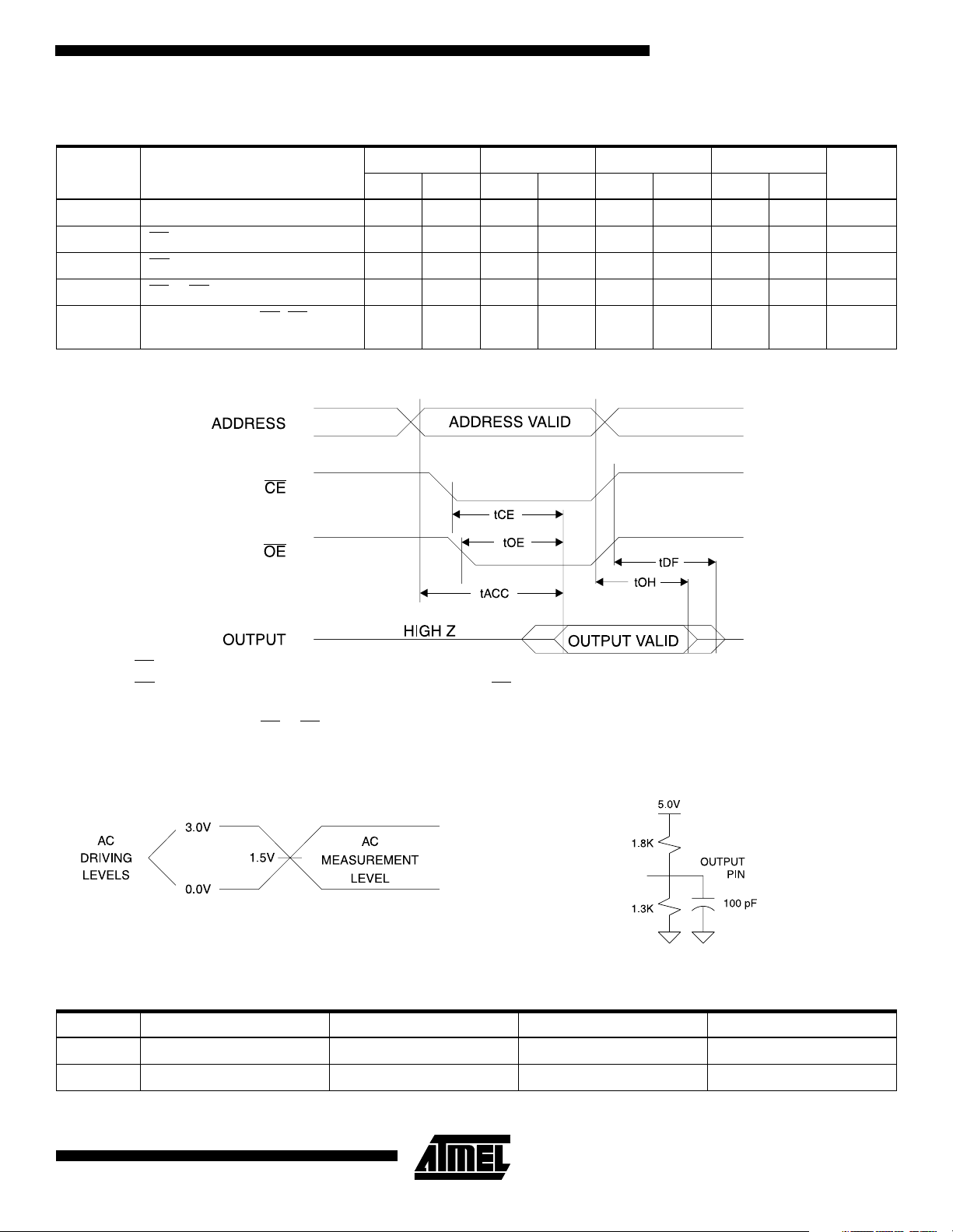

AC Read Characteristics

tR, tF < 5 ns

Symbol Parameter

AT28C256

AT28C256-15 AT28C256-20 AT28C256-25 AT28C256-35

UnitsMin Max Min Max Min Max Min Max

t

t

t

t

t

ACC

CE

OE

DF

OH

(1)

(2)

(3)(4)

Address to Output Delay 150 200 250 350 ns

CE to Output Delay 150 200 250 350 ns

OE to Output Delay 0 70 0 80 0 100 0 100 ns

CE or OE to Output Float 050055060070 ns

Output Hold from OE, CE or

Address, whichever occurred first

AC Read Waveforms

0000 ns

(1)(2)(3)(4)

Notes: 1. CE may be delayed up to t

2. OE may be delayed up to tCE - tOE after the falling edge of CE without impact on tCE or by t

without impact on t

is specified from OE or CE whichever occurs first (CL = 5 pF).

3. t

DF

ACC

.

- tCE after the address transition without impact on t

ACC

ACC

.

- tOE after an address change

ACC

4. This parameter is characterized and is not 100% tested.

Input Test Waveforms and

Output Test Load

Measurement Level

Pin Capacitance

f = 1 MHz, T = 25°C

Symbol Typ Max Units Conditions

C

IN

C

OUT

Note: 1. This parameter is characterized and is not 100% tested.

(1)

46pFV

812pFV

IN

OUT

= 0V

= 0V

5

Page 6

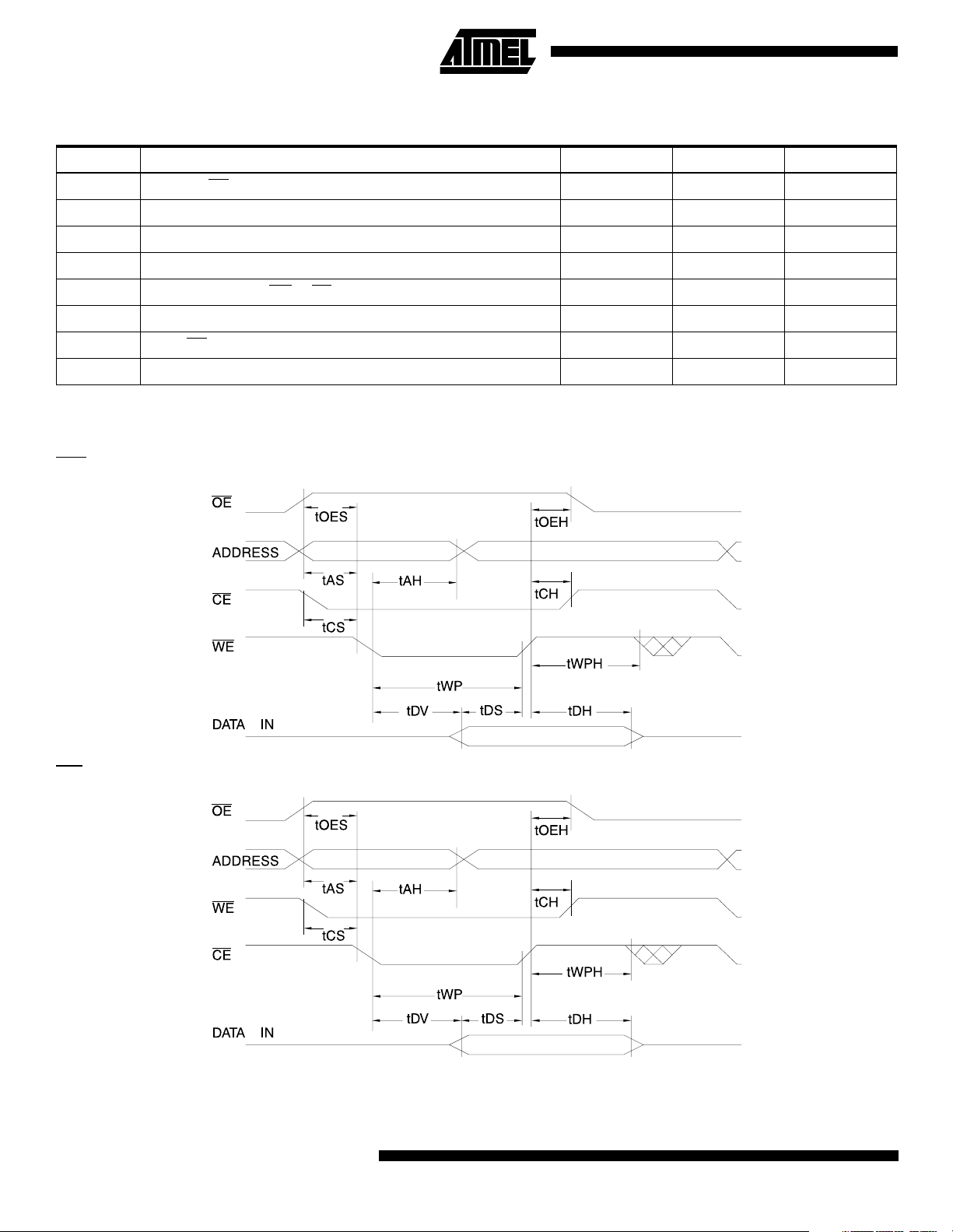

AC Write Characteristics

Symbol Parameter Min Max Units

t

AS

t

AH

t

CS

t

CH

t

WP

t

DS

tDH, t

t

DV

, t

OES

OEH

Address, OE Setup Time 0 ns

Address Hold Time 50 ns

Chip Select Setup Time 0 ns

Chip Select Hold Time 0 ns

Write Pulse Width (WE or CE) 100 ns

Data Setup Time 50 ns

Data, OE Hold Time 0 ns

Time to Data Valid NR

(1)

Note: 1. NR = No Restriction

AC Write Waveforms

WE Controlled

CE Controlled

6

AT28C256

Page 7

AT28C256

tS = tH = 5 µsec (min.)

tW = 10 msec (min.)

VH = 12.0V ± 0.5V

Page Mode Characteristics

Symbol Parameter Min Max Units

t

WC

Write Cycle Time (option available)

AT28C256 10 ms

AT28C256F 3 ms

t

AS

t

AH

t

DS

t

DH

t

WP

t

BLC

t

WPH

Address Setup Time 0 ns

Address Hold Time 50 ns

Data Setup Time 50 ns

Data Hold Time 0 ns

Write Pulse Width 100 ns

Byte Load Cycle Time 150 µs

Write Pulse Width High 50 ns

Page Mode Write Waveforms

(1)(2)

Notes: 1. A6 through A14 must specify the same page address during each high to low transition of WE (or CE).

2. OE must be high only when WE and CE are both low.

Chip Erase Waveforms

7

Page 8

Software Data Protection

Enable Algorithm

LOAD DATA AA

ADDRESS 5555

(1)

TO

Software Data Protection

Disable Algorithm

LOAD DATA AA

ADDRESS 5555

(1)

TO

LOAD DATA 55

TO

ADDRESS 2AAA

LOAD DATA A0

TO

ADDRESS 5555

LOAD DATA XX

TO

ANY ADDRESS

LOAD LAST BYTE

TO

LAST ADDRESS

WRITES ENABLED

(4)

ENTER DATA

PROTECT STATE

(2)

Notes for software program code:

1. Data Format: I/O7 - I/O0 (Hex);

Address Format: A14 - A0 (Hex).

2. Write Protect state will be activated at end of

write even if no other data is loaded.

3. Write Protect state will be deactivated at end of

write period even if no other data is loaded.

4. 1 to 64 bytes of data are loaded.

LOAD DATA 55

TO

ADDRESS 2AAA

LOAD DATA 80

TO

ADDRESS 5555

LOAD DATA AA

TO

ADDRESS 5555

LOAD DATA 55

TO

ADDRESS 2AAA

LOAD DATA 20

TO

ADDRESS 5555

LOAD DATA XX

TO

ANY ADDRESS

LOAD LAST BYTE

TO

LAST ADDRESS

EXIT DATA

PROTECT STATE

(4)

(3)

Software Protected Write Cycle Waveforms

(1)(2)

Notes: 1. A6 through A14 must specify the same page address during each high to low transition of WE (or CE) after the software

code has been entered.

2. OE

8

must be high only when WE and CE are both low.

AT28C256

Page 9

AT28C256

Data Polling Characteristics

Symbol Parameter Min Typ Max Units

t

DH

t

OEH

t

OE

t

WR

Notes: 1. These parameters are characterized and not 100% tested.

Data Hold Time 0 ns

OE Hold Time 0 ns

OE to Output Delay

Write Recovery Time 0 ns

2. See “AC Read Characteristics”.

(2)

(1)

Data Polling Waveforms

ns

Toggle Bit Characteristics

Symbol Parameter Min Typ Max Units

t

DH

t

OEH

t

OE

t

OEHP

t

WR

Notes: 1. These parameters are characterized and not 100% tested.

Data Hold Time 10 ns

OE Hold Time 10 ns

OE to Output Delay

OE High Pulse 150 ns

Write Recovery Time 0 ns

2. See “AC Read Characteristics”.

(2)

Toggle Bit Waveforms

(1)

(1)(2)(3)

ns

Notes: 1. Toggling either OE or CE or both OE and CE will operate toggle bit.

2. Beginning and ending state of I/O6 will vary.

3. Any address location may be used but the address should not vary.

9

Page 10

10

AT28C256

Page 11

AT28C256

Ordering Information

I

t

ACC

(ns)

150 50 0.2 AT28C256(E,F)-15JC

200 50 0.2 AT28C256(E,F)-20JC

(mA)

CC

50 0.3 AT28C256(E,F)-15DM/883

50 0.3 AT28C256(E,F)-20DM/883

(2)

Ordering Code Package Operation RangeActive Standby

AT28C256(E,F)-15PC

AT28C256(E,F)-15SC

AT28C256(E,F)-15TC

AT28C256(E,F)-15JI

AT28C256(E,F)-15PI

AT28C256(E,F)-15SI

AT28C256(E,F)-15TI

AT28C256(E,F)-15FM/883

AT28C256(E,F)-15LM/883

AT28C256(E,F)-15UM/883

AT28C256(E,F)-20PC

AT28C256(E,F)-20SC

AT28C256(E,F)-20TC

AT28C256(E,F)-20JI

AT28C256(E,F)-20PI

AT28C256(E,F)-20SI

AT28C256(E,F)-20TI

AT28C256(E,F)-20FM/883

AT28C256(E,F)-20LM/883

AT28C256(E,F)-20UM/883

32J

28P6

28S

28T

32J

28P6

28S

28T

28D6

28F

32L

28U

32J

28P6

28S

28T

32J

28P6

28S

28T

28D6

28F

32L

28U

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Package Type

28D6 28-lead, 0.600" Wide, Non-windowed, Ceramic Dual Inline Package (Cerdip)

28F 28-lead, Non-windowed, Ceramic Bottom-brazed Flat Package (Flatpack)

32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)

32L 32-pad, Non-windowed, Ceramic Leadless Chip Carrier (LCC)

28P6 28-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)

28S 28-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)

28T 28-lead, Plastic Thin Small Outline Package (TSOP)

28U 28-pin, Ceramic Pin Grid Array (PGA)

W Die

Options

Blank Standard Device: Endurance = 10K Write Cycles; Write Time = 10 ms

E High Endurance Option: Endurance = 100K Write Cycles

F Fast Write Option: Write Time = 3 ms

11

Page 12

Ordering Information

I

t

ACC

(ns)

250 50 0.2 AT28C256(E,F)-25JC

(3)

150

(mA)

CC

50 0.3 AT28C256(E,F)-25DM/883

50 0.35 5962-88525 16 UX

(2)

Ordering Code Package Operation RangeActive Standby

AT28C256(E,F)-25PC

AT28C256-W

AT28C256(E,F)-25JI

AT28C256(E,F)-25PI

AT28C256(E,F)-25FM/883

AT28C256(E,F)-25LM/883

AT28C256(E,F)-25UM/883

AT28C256(E,F)-35UM/883

5962-88525 16 XX

5962-88525 16 YX

5962-88525 16 ZX

5962-88525 15 UX

5962-88525 15 XX

5962-88525 15 YX

5962-88525 15 ZX

5962-88525 14 UX

5962-88525 14 XX

5962-88525 14 YX

5962-88525 14 ZX

32J

28P6

DIE

32J

28P6

28D6

28F

32L

28U

28U

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Package Type

28D6 28-lead, 0.600" Wide, Non-windowed, Ceramic Dual Inline Package (Cerdip)

28F 28-lead, Non-windowed, Ceramic Bottom-brazed Flat Package (Flatpack)

32J 32-lead, Plastic J-leaded Chip Carrier (PLCC)

32L 32-pad, Non-windowed, Ceramic Leadless Chip Carrier (LCC)

28P6 28-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)

28U 28-pin, Ceramic Pin Grid Array (PGA)

W Die

Options

Blank Standard Device: Endurance = 10K Write Cycles; Write Time = 10 ms

E High Endurance Option: Endurance = 100K Write Cycles

F Fast Write Option: Write Time = 3 ms

12

AT28C256

Page 13

AT28C256

Ordering Information

I

t

ACC

(ns)

150

200

250

(3)

(3)

(3)

(mA)

CC

50 0.35 5962-88525 08 UX

50 0.35 5962-88525 12 UX

50 0.35 5962-88525 04 UX

50 0.35 5962-88525 13 UX

(2)

Ordering Code Package Operation RangeActive Standby

5962-88525 08 XX

5962-88525 08 YX

5962-88525 08 ZX

5962-88525 07 UX

5962-88525 07 XX

5962-88525 07 YX

5962-88525 07 ZX

5962-88525 06 UX

5962-88525 06 XX

5962-88525 06 YX

5962-88525 06 ZX

5962-88525 12 XX

5962-88525 12 YX

5962-88525 12 ZX

5962-88525 04 XX

5962-88525 04 YX

5962-88525 04 ZX

5962-88525 13 XX

5962-88525 13 YX

5962-88525 13 ZX

5962-88525 11 UX

5962-88525 11 XX

5962-88525 11 YX

5962-88525 11 ZX

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Class B, Fully Compliant

(-55°C to 125°C)

Package Type

28D6 28-lead, 0.600" Wide, Non-windowed, Ceramic Dual Inline Package (Cerdip)

28F 28-lead, Non-windowed, Ceramic Bottom-brazed Flat Package (Flatpack)

32L 32-pad, Non-windowed, Ceramic Leadless Chip Carrier (LCC)

28U 28-pin, Ceramic Pin Grid Array (PGA)

W Die

Options

Blank Standard Device: Endurance = 10K Write Cycles; Write Time = 10 ms

E High Endurance Option: Endurance = 100K Write Cycles

F Fast Write Option: Write Time = 3 ms

13

Page 14

Ordering Information

I

t

ACC

(ns)

250 50 0.35 5962-88525 05 UX

300 50 0.35 5962-88525 10 UX

350 50 0.35 5962-88525 09 UX

Notes: 1. Electrical specifications for these speeds are defined by Standard Microcircuit Drawing 5962-88525.

2. See “Valid Part Numbers” table below.

3. SMD specifies Software Data Protection feature for device type, although Atmel product supplied to every device type in the

SMD is 100% tested for this feature.

(mA)

CC

50 0.35 5962-88525 02 UX

50 0.35 5962-88525 01 UX

(2)

Ordering Code Package Operation RangeActive Standby

5962-88525 05 XX

5962-88525 05 YX

5962-88525 05 ZX

5962-88525 03 UX

5962-88525 03 XX

5962-88525 03 YX

5962-88525 03 ZX

5962-88525 10 XX

5962-88525 10 YX

5962-88525 10 ZX

5962-88525 02 XX

5962-88525 02 YX

5962-88525 02 ZX

5962-88525 09 XX

5962-88525 09 YX

5962-88525 09 ZX

5962-88525 01 XX

5962-88525 01 YX

5962-88525 01 ZX

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

28U

28D6

32L

28F

Class B, Fully Compliant

(-55°C to 125°C)

Class B, Fully Compliant

(-55°C to 125°C)

Class B, Fully Compliant

(-55°C to 125°C)

Class B, Fully Compliant

(-55°C to 125°C)

Class B, Fully Compliant

(-55°C to 125°C)

Class B, Fully Compliant

(-55°C to 125°C)

Military/883C

Military/883C

Military/883C

Military/883C

Military/883C

Military/883C

Package Type

28D6 28-lead, 0.600" Wide, Non-windowed, Ceramic Dual Inline Package (Cerdip)

28F 28-lead, Non-windowed, Ceramic Bottom-brazed Flat Package (Flatpack)

32L 32-pad, Non-windowed, Ceramic Leadless Chip Carrier (LCC)

28U 28-pin, Ceramic Pin Grid Array (PGA)

W Die

Options

Blank Standard Device: Endurance = 10K Write Cycles; Write Time = 10 ms

E High Endurance Option: Endurance = 100K Write Cycles

F Fast Write Option: Write Time = 3 ms

14

AT28C256

Page 15

AT28C256

Valid Part Numbers

The following table lists standard Atmel products that can be ordered.

Device Numbers Speed Package and Temperature Combinations

AT28C256 15 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256E 15 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256F 15 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256 20 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256E 20 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256F 20 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256 25 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256E 25 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256F 25 JC, JI, PC, PI, SC, SI, TC, TI, DM/883, FM/883, LM/883, UM/883

AT28C256 – W

Die Products

Reference Section: Parallel EEPROM Die Products

15

Page 16

Packaging Information

28D6, 28-lead, 0.600" Wide, Non-windowed Ceramic

Dual Inline Package (Cerdip)

Dimensions in Inches and (Millimeters)

MIL-STD-1835 D-10 CONFIG A

1.49(37.9)

.225(5.72)

SEATING

PLANE

.200(5.08)

.125(3.18)

MAX

.110(2.79)

.090(2.29)

.015(.381)

.008(.203)

1.44(36.6)

1.300(33.02) REF

.065(1.65)

.045(1.14)

.620(15.7)

.590(15.0)

PIN

1

.610(15.5)

.510(13.0)

.023(.584)

.014(.356)

0

REF

15

.700(17.8) MAX

.098(2.49)

MAX

.005(.127)

MIN

.060(1.52)

.015(.381)

28F, 28-lead, Non-windowed, Ceramic Bottombrazed Flat Package (Flatpack)

Dimensions in Inches and (Millimeters)

MIL-STD-1835 F-12 CONFIG B

PIN #1 ID

.728(18.5)

.712(18.1)

.416(10.6)

.384(9.75)

.006(.152)

.004(.102)

.077(1.96)

.043(1.09)

.286(7.26)

.274(6.96)

.370(9.40)

.250(6.35)

.019(.483)

.015(.381)

.050(1.27) BSC

.045(1.14) MAX

.119(3.02)

.087(2.21)

.045(1.14)

.026(.660)

32J, 32-lead, Plastic J-leaded Chip Carrier (PLCC)

Dimensions in Inches and (Millimeters)

JEDEC STANDARD MS-016 AE

.045(1.14) X 45˚

.032(.813)

.026(.660)

.050(1.27) TYP

PIN NO. 1

IDENTIFY

.553(14.0)

.547(13.9)

.300(7.62) REF

.430(10.9)

.390(9.90)

.453(11.5)

.447(11.4)

.495(12.6)

.485(12.3)

.025(.635) X 30˚ - 45˚

.595(15.1)

.585(14.9)

AT CONTACT

POINTS

.022(.559) X 45˚ MAX (3X)

.012(.305)

.008(.203)

.530(13.5)

.490(12.4)

.021(.533)

.013(.330)

.030(.762)

.015(.381)

.095(2.41)

.060(1.52)

.140(3.56)

.120(3.05)

32L, 32-pad, Non-windowed, Ceramic Leadless Chip

Carrier (LCC)

Dimensions in Inches and (Millimeters)

MIL-STD-1835 C-12

16

AT28C256

Page 17

Packaging Information

AT28C256

28P6, 28-lead, 0.600" Wide, Plastic Dual Inline

Package (PDIP)

Dimensions in Inches and (Millimeters)

JEDEC STANDARD MS-011 AB

1.47(37.3)

.220(5.59)

SEATING

PLANE

.161(4.09)

.125(3.18)

MAX

.110(2.79)

.090(2.29)

.012(.305)

.008(.203)

1.44(36.6)

1.300(33.02) REF

.065(1.65)

.041(1.04)

.630(16.0)

.590(15.0)

.690(17.5)

.610(15.5)

PIN

1

.566(14.4)

.530(13.5)

.090(2.29)

.005(.127)

.065(1.65)

.015(.381)

.022(.559)

.014(.356)

0

REF

15

28S, 28-lead, 0.300" Wide, Plastic Gull Wing Small

Outline (SOIC)

Dimensions in Inches and (Millimeters)

MAX

MIN

28T, 28-lead, Plastic Thin Small Outline Package

(TSOP)

Dimensions in Millimeters and (Inches)*

INDEX

MARK

AREA

0.55 (0.022)

BSC

0

REF

5

7.15 (0.281)

REF

8.10 (0.319)

7.90 (0.311)

0.20 (0.008)

0.10 (0.004)

0.70 (0.028)

0.30 (0.012)

11.9 (0.469)

11.7 (0.461)

0.27 (0.011)

0.18 (0.007)

13.7 (0.539)

13.1 (0.516)

1.25 (0.049)

1.05 (0.041)

0.20 (0.008)

0.15 (0.006)

*Controlling dimension: millimeters

28U, 28-pin, Ceramic Pin Grid Array (PGA)

Dimensions in Inches and (Millimeters)

17

Page 18

Atmel Headquarters Atmel Operations

Corporate Headquarters

2325 Orchard Parkway

San Jose, CA 95131

TEL (408) 441-0311

FAX (408) 487-2600

Europe

Atmel U.K., Ltd.

Coliseum Business Centre

Riverside Way

Camberley, Surrey GU15 3YL

England

TEL (44) 1276-686-677

FAX (44) 1276-686-697

Asia

Atmel Asia, Ltd.

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimhatsui

East Kowloon

Hong Kong

TEL (852) 2721-9778

FAX (852) 2722-1369

Japan

Atmel Japan K.K.

9F, Tonetsu Shinkawa Bldg.

1-24-8 Shinkawa

Chuo-ku, Tokyo 104-0033

Japan

TEL (81) 3-3523-3551

FAX (81) 3-3523-7581

Atmel Colorado Springs

1150 E. Cheyenne Mtn. Blvd.

Colorado Springs, CO 80906

TEL (719) 576-3300

FAX (719) 540-1759

Atmel Rousset

Zone Industrielle

13106 Rousset Cedex

France

TEL (33) 4-4253-6000

FAX (33) 4-4253-6001

Fax-on-Demand

North America:

1-(800) 292-8635

International:

1-(408) 441-0732

e-mail

literature@atmel.com

Web Site

http://www.atmel.com

BBS

1-(408) 436-4309

© Atmel Corporation 1999.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for

any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without

notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are

not authorized for use as critical components in life support devices or systems.

®

Marks bearing

Terms and product names in this document may be trademarks of others.

and/or ™ are registered trademarks and trademarks of Atmel Corporation.

Printed on recycled paper.

0006H–12/99/xM

Loading...

Loading...