Page 1

APLUS INTEGRATED CIRCUITS INC. APC5860

APC5860 DE-COMPRESSION VOICE IC

1. CHIP FEATURES.

z DUAL OPERATION FREQUENCIES:

- 32.768 KHZ & 0.5 SECOND TIMER INTERRUPT.

- BUILT-IN PLL CIRCUIT TO GENERATE SYSTEM CLOCK MAX 20MHZ.

z BUILT-IN 2KBYTES(1K*16) RAM.

z ADDRESS UP TO 8MBYTE(4M*16) RAM OR ROM OR “ROM AND RAM”

BUILT-IN 16KBYTE(8K*16) PROGRAM ROM AND 1M BYTE(512K*16) DATA ROM

z BUILT-IN DECOMPRESSION ENGINE

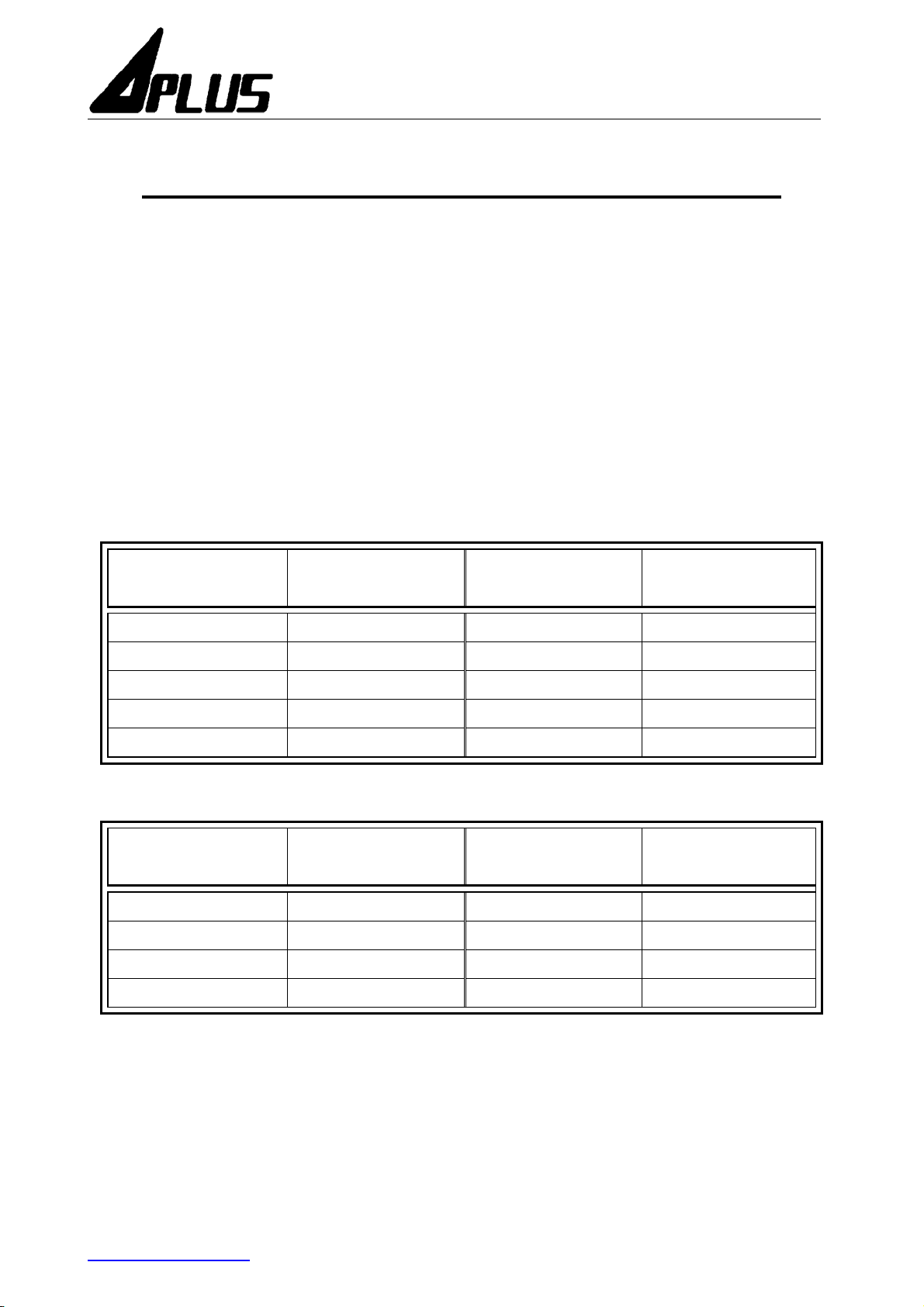

THE VOICE AND MUSIC DE-COMPRESSION RATE IS AS THE FOLLOWS:

- 3.6KBIT/SEC - 4.8KBIT/SEC - 6.0KBIT/SEC - 7.2KBIT/SEC - 8.4KBIT/SEC - 9.6KBIT/SEC -

10.8KBIT/SEC - 12.0 KBIT/SEC - 13.2 KBIT/SEC - 14.4 KBIT/SEC

DE-COMPRESSION

RATE

VOICE DURATION

DE-COMPRESSION

RATE

VOICE DURATION

3.6 K BIT/SEC 37.93 min. 9.6 K BIT/SEC 14.22 min.

4.8 K BIT/SEC 28.44 min. 10.8 K BIT/SEC 12.64 min.

6.0 K BIT/SEC 22.76 min. 12.0 K BIT/SEC 11.38 min.

7.2 K BIT/SEC 18.96 min. 13.2 K BIT/SEC 10.34 min.

8.4 K BIT/SEC 16.25 min. 14.4 K BIT/SEC 9.48 min.

THE MUSIC DE-COMPRESSION RATE IS AS THE FOLLOWS:

DE-COMPRESSION

RATE

10 K BIT/SEC

12 K BIT/SEC

14 K BIT/SEC

16 K BIT/SEC

VOICE DURATION

13.65 min.

11.38 min.

9.75 min.

8.53 min.

DE-COMPRESSION

RATE

18 K BIT/SEC

20 K BIT/SEC

22 K BIT/SEC

24 K BIT/SEC

VOICE DURATION

7.59 min.

6.83 min.

6.21 min.

5.69 min.

z BUILT-IN 12 BITS D/A, 8 BITS ADC.

z I/O PORTS

16 I/O PINS FOR PORT A.

12 OUTPUT FOR PORT B.

16 I/O PINS FOR PORT C.

www.aplusinc.com.tw TEL : 886-2-2782-9266

1

Page 2

APLUS INTEGRATED CIRCUITS INC. APC5860

z TWO 16BITS TIMERS : TIMER_A AND TIMER_B.

z WATCHDOG TIMER.

z SLEEP MODE : CRYSTAL & SYSTEM

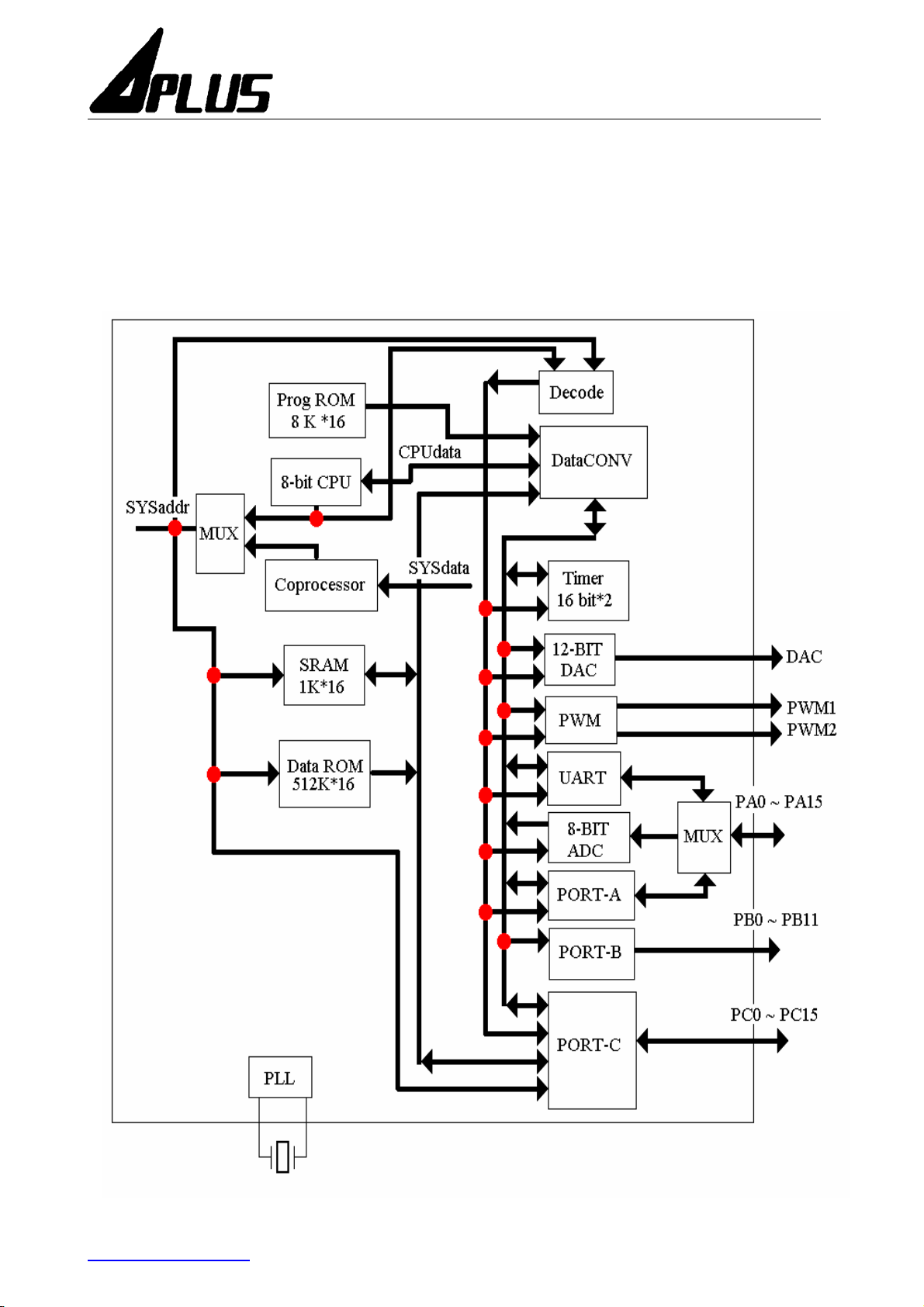

2. BLOCK DIAGRAM.

www.aplusinc.com.tw TEL : 886-2-2782-9266

2

Page 3

APLUS INTEGRATED CIRCUITS INC. APC5860

.

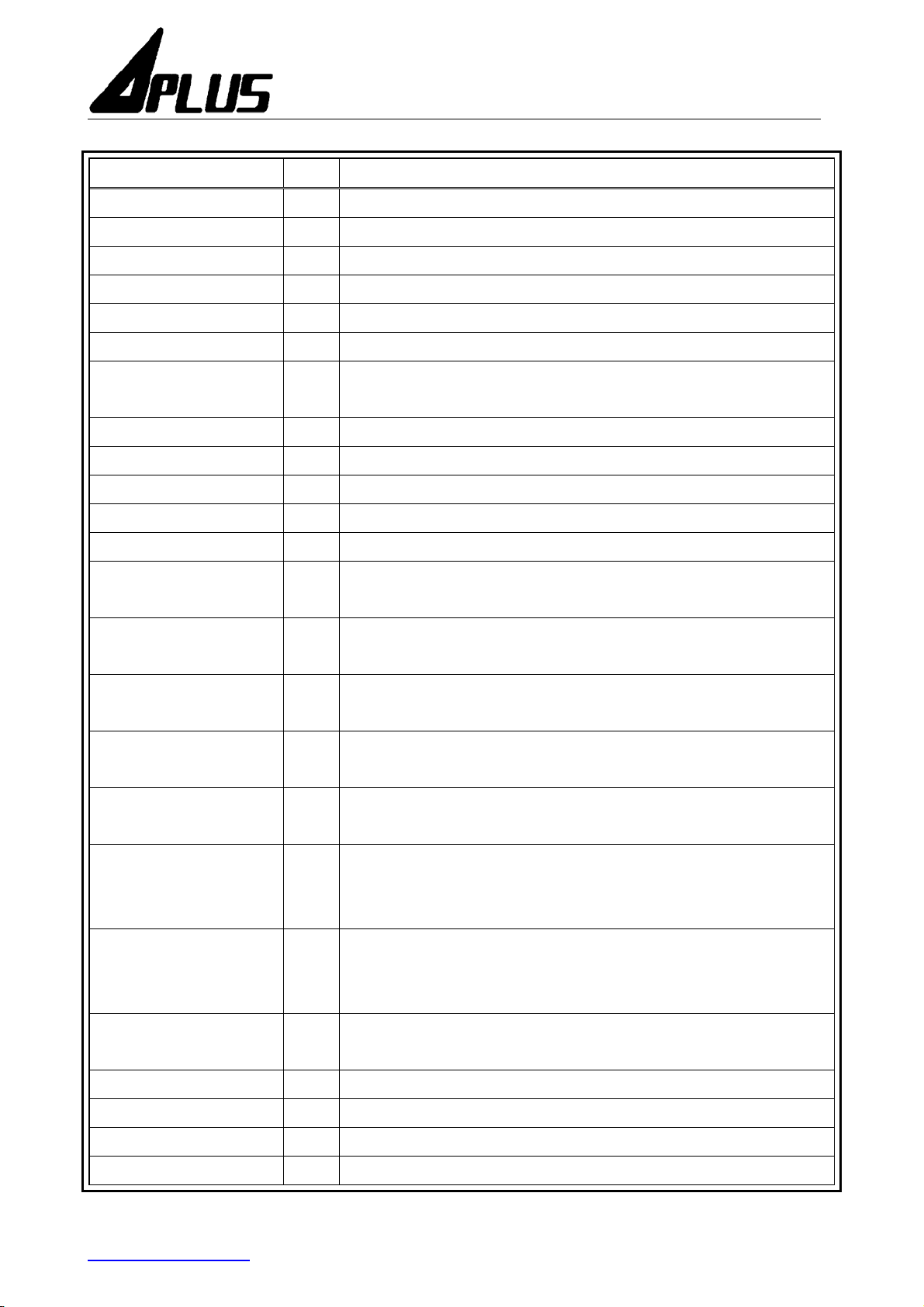

2. PIN DESCRIPTION :

PIN NAME I/O DESCRIPTION

RESET I RESET INPUT. ACTIVE LOW.

PWM1,PWM2 O PWM OUTPUT.

DAC O OUTPUT FROM D/A CONVERTER.

XOSC1 I CRYSTAL OSCILLATOR INPUT PIN.

XOSC2 O CRYSTAL OSCILLATOR OUTPUT PIN.

CAP I CAPACITOR FOR PLL CIRCUIT.

PA0-PA7 I/O

PA8-PA12 IO I/O PORT_A PIN 8 TO 12, INTERNAL PULL HIGH.

PA13/ADC I/O I/O PORT_A PIN 13 OR ANALOG SIGNAL INPUT, INTERNAL PULL LOW.

PA14 I/O I/O PORT_A PIN 14, INTERNAL PULL HIGH.

PA15 I/O I/O PORT_A PIN 15, INTERNAL PULL HIGH.

PB0-PB5/BANK3-BANK8

O PORT_B OR EXTERNAL MEMORY BANK SELECT

PB6/EMEMRD O

PB7/EXTRAM O

PB8/EMEMWRL I/O

PB9/EXTIRQ I/O

PB10/EMEMWRH O

I/O PORT_A PIN 0 TO 7. ALSO AS EXTERNAL INTERRUPT

SOURCE.(FALL EDGE TRIGGER), INTERNAL PULL HIGH.

PORT_B PIN 6 OR EXTERNAL RAM READ

(ACTIVE LOW).

PORT_B PIN 7 OR EXTERNAL RAM SELECT PIN

(ACTIVE LOW)

Port_b pin 8 or External RAM low byte write(Active Low),

Input,at reset cycle, output at normal cycle, internal pull high.

Port_b pin 9 or External IRQ input pin(rise edge trigger),

Inputat reset cycle, output at normal cycle, internal pull low.

Port_b pin 10 or External RAM high byte write(Active Low)

,Input at reset cycle, output at normal cycle, Internal pull low

PORT_B PIN 11 ROM SELECT OR EXTERNAL ROM CHIP SELECT

PB11/EXTROMCS I/O

ACTIVE LOW), INPUT AT RESET CYCLE, OUTPUT AT NORMAL

OPERATION CYCLE

, INTERNAL PULL HIGH.

EMEMAD: External memory Address/Data

PC/EMEMAD

If it is address then EMEMA0~EMEMA12 is A1~A13.

I/O

EMEMA13~EMEMA15 is BANK0~BANK2.

External memory address latch enable. Input at reset cycle,

ALE O

output at normal operation cycle, internal pull high.

VDD1-VDD4 I DIGITAL POWER INPUT.

GND1-GND4 I DIGITAL GROUND.

PLLVDD,PLLGND I POWER AND GROUND FOR PLL CIRCUIT.

DACVDD,DACGND I POWER AND GROUND FOR DAC CIRCUIT.

www.aplusinc.com.tw TEL : 886-2-2782-9266

3

Page 4

APLUS INTEGRATED CIRCUITS INC. APC5860

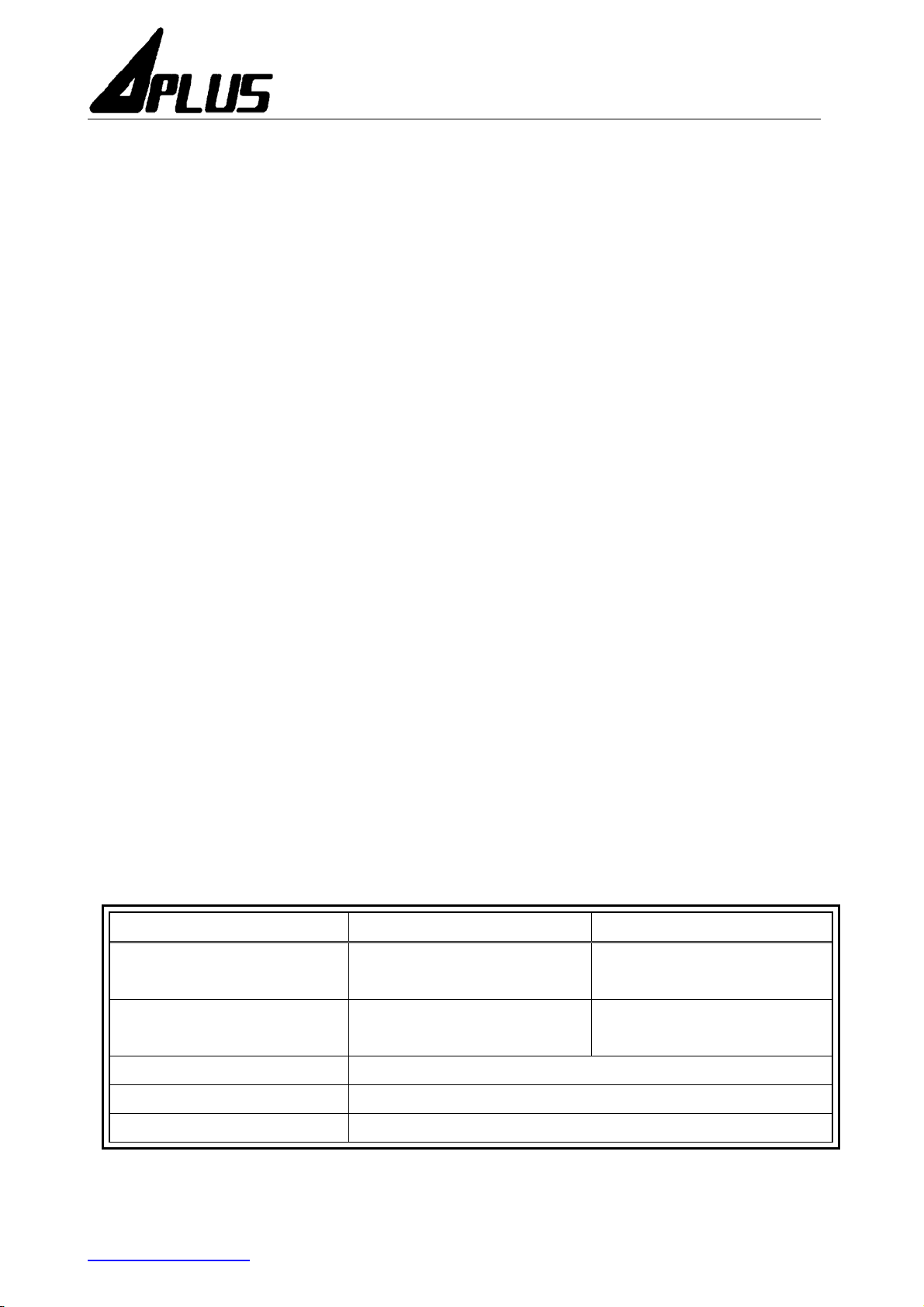

4. ADDRESS ARRANGEMENT :

1) RAM :

0000-07FF : INTERNAL RAM, 1KX16.

0000-1FFF : EXTERNAL NON-BANK RAM(EXTRAMCS=1), 4KX16.

2) ROM :

z 4000-7FFF : DATA AREA FOR BANK SELECT, 8KX16 EACH,

MAX. TO 64MBIT BANK ROM OR BANK RAM.

z C000-FFFF : FOR SYSTEM PROGRAM OR USER PROGRAM, 8KX16.

z FFF0, FFF1 : COPROCESSOR OK IRQ VECTOR.

z FFF2, FFF3 : ADC IRQ VECTOR.

z FFF4, FFF5 : NOT USE

z FFF6, FFF7 : TIMER IRQ(FIX_TIMER IRQ OR TIMER_A IRQ) VECTOR.

z FFF8, FFF9 : PA[7:0] IRQ VECTOR.

z FFFA, FFFB : TIMER_B NMI VECTOR.

z FFFC, FFFD : RES VECTOR.

z FFFE, FFFF : EXT IRQ VECTOR.

PRIORITY IS ARRANGED AS RES, NMI, OK_INT, ADC_INT, TIMER_INT,PA_INT,

AND EXT_IRQ.

MEMORY MAPPING ( INTERNAL ROM )

www.aplusinc.com.tw TEL : 886-2-2782-9266

4

Page 5

APLUS INTEGRATED CIRCUITS INC. APC5860

MEMORY MAPPING ( EXTTERNAL ROM )

3) Others :

z 3FE0 System Flag. Read only. :

3FE0

BIT - 0 NO USE NO USE

0 1

BIT - 1 NO USE NO USE

BIT - 2 ADC NO ERROR. ADC ERROR.

TIMER_A INT FLAG

TIMER IRQ TIMER_A INT FLAG

BIT - 3

www.aplusinc.com.tw TEL : 886-2-2782-9266

1 1 ……….. TIMER_A INT

1 0 ………. FIX_TIMER INT

1 X ………. NO TIMER INT

5

Page 6

APLUS INTEGRATED CIRCUITS INC. APC5860

.

BIT - 4 NO USE

BIT - 5 OK FLAG(COPROCESSOR OK)

BIT - 6 COPROCESSOR CARRY.

BIT - 7 TONE0 OR TONE1 ENABLE.

z 3FE0 System control 0. Write only. :

3FE0

BIT - 0 MUST 0 = PA14,PA15 ARE IO PINS(DEFAULT).

BIT - 1 PB9 IS IO PIN(DEFAULT). PB9 IS EXTIRQ PIN.

BIT - 2 PB7 IS IO PIN(DEFAULT). PB7 IS EXTRAMCS.

ADC DISABLE, PA13 IS IO

BIT - 3

PIN

(DEFAULT).

BIT - 4 NO USE(MUST 0)

BIT - 5 NO USE(MUST 0)

BIT - 6 PWM DISABLE(DEFAULT). PWM ENABLE.

BIT - 7 DAC DISABLE(DEFAULT). DAC ENABLE.

z 3FE1 System Control 1. Write only.

3FE1

TIMER A CLOCK SELECT

BIT - 0

32.768K HZ.(DEFAULT)

BIT - 1 NO USE(MUST 0)

0 1

ADC ENABLE, PA13 IS ADC PIN.

0 1

TIMER A CLOCK SELECT SYSTEM

CLOCK

.

BIT - 2 TIMER A DISABLE.(DEFAULT) TIMER A ENABLE.

BIT - 3 TIMER B DISABLE.(DEFAULT) TIMER B ENABLE.

TIMER A INTERRUPT

BIT - 4

DISABLE

BIT - 5 TIMER B NMI DISABLE.(DEFAULT)TIMER B NMI ENABLE.

SYSTEM CLOCK = PLL

BIT - 6

CLOCK

(DEFAULT).

BIT - 7 WATCHDOG TIMER DISABLE.

z 3FE2 System control 2. Write only.

3FE2

=1 Æ ENTRY STAND-BY MODE. IN STAND-BY MODE, HOLD CPU

BIT - 0

THE NMI AND IRQ WILL WAKE UP THE CPU.

.(DEFAULT)

TIMER A INTERRUPT ENABLE.

SYSTEM CLOCK = 32768HZ.

WATCHDOG TIMER

ENABLE

.(DEFAULT)

0 1

www.aplusinc.com.tw TEL : 886-2-2782-9266

6

Page 7

APLUS INTEGRATED CIRCUITS INC. APC5860

T

=1 Æ ENTRY SLEEP MODE. IN SLEEP MODE , THE BOTH OF MAIN

SYSTEM CLOCK AND

32768HZ WILL BESTOPPED, SO ALL

BIT - 1

FUNCTION ARE STOPPED AND ONLY EXTERNAL INTERRUP

CAN WAKE UP THIS CHIP

00 : SYSTEM CLOCK = FXOSC/2 X 256(4.19MHZ)(DEFAULT).

BIT – 3 ~ 2

01 : SYSTEM CLOCK = FXOSC/2 X 512(8.38MHZ)

10 : SYSTEM CLOCK = FXOSC/2 X 768(12.58MHZ)

0XXX : FIX-TIMER DISABLE.

1000 : FIX-TIMER = 64HZ.

1001 : FIX-TIMER = 32HZ.

1010 : FIX-TIMER = 16HZ.

BIT- 7 ~ 4

1011 : FIX-TIMER = 8HZ.

1100 : FIX-TIMER = 4HZ.

1101 : FIX-TIMER = 2HZ.

1110 : FIX-TIMER = 1HZ.

1111 : FIX-TIMER = 0.5HZ

z 3FE3 : PORT_A[7..0] INTERRUPT ENABLE REGISTER. WRITE ONLY.

AN ‘0’ IN THIS REGISTER WILL SET THE INTERRUPT FUNCTION OF THE CORRESPONDING PIN

OF

PORT_A TO BE ENABLED. THE DEFAULT VALUE FOR EACH BIT IS ‘1’.

z 3FE4 : PORT_A[7..0] DATA REGISTER. READ AND WRITE.

z 3FE5 : PORT_A[7..0] DIRECTION REGISTER. WRITE ONLY.

AN ‘1’ IN THIS REGISTER WILL SET THE CORRESPONDING PIN OF PORT_A TO BE OUTPUT.

THE DEFAULT VALUE FOR EACH BIT IS ZERO.

z 3FE6: PORT_B[7..0] DATA REGISTER. WRITE ONLY.

z 3FE7 : CLEAR WATCHDOG TIMER. WRITE ONLY.

THE WATCHDOG TIMER RESET WILL HAPPEN IF THE PROGRAMMER DO NOT CLEAR THE

WATCHDOG TIMER BEFORE WATCHDOG TIMER TIME-OUT.

z 3FE8 VOICE CHANNEL 0 LOW BYTE. WRITE ONLY.

BIT 2-0 : RESERVED.

BIT 3: NO USE (MUST 0)

BIT 7-4: = VOICE CHANNEL 0 LOW NIBBLE BYTE.

www.aplusinc.com.tw TEL : 886-2-2782-9266

7

Page 8

APLUS INTEGRATED CIRCUITS INC. APC5860

z 3FE9 : VOICE CHANNEL 0 HIGH BYTE. WRITE ONLY.

THE RESOLUTION OF VOICE CHANNEL 0 IS 12 BITS($3FE9,$3FE8 BIT7_4).

z 3FEA : BANK REGISTER FOR COPROCESSOR. WRITE ONLY.

z 3FEB : BANK REGISTER MSB BIT FOR COPROCESSOR. WRITE ONLY.

BANK REGISTER IS 9 BITS REGISTER($3FEB BIT0, $3FEA BIT7-0). THE MEMORY RANGE OF

BANK IS FROM $4000 TO $7FFF.

BIT 7-1 : RESERVED.

z 3FEC,3FED : TIMER A DATA OR TONE0 GENERATOR. READ AND WRITE. AFTER TIMER_A BE

ENABLED, THE TIMER WILL START TO COUNT DOWN. WHEN TIMER COUNTS TO ZERO, THE

TIMER WILL COUNT FROM THE INITIAL VALUE AND TIMER_A IRQ WILL BE HAPPEN.

THE TIME ELAPSE = (($3FED,$3FEC)+1) / (TIMER A INPUT CLOCK).

z 3FEE : TIMER B LOW BYTE DATA. READ AND WRITE.

z 3FEF : TIMER B HIGH BYTE DATA. READ AND WRITE.

AFTER TIMER_B BE ENABLED, THE TIMER WILL START TO COUNT DOWN. WHEN TIMER

COUNTS TO ZERO,THE TIMER WILL COUNT FROM THE INITIAL VALUE AND TIMER_B NMI WILL

BE HAPPEN.

THE TIME ELAPSE = (($3FEF,$3FEE)+1) / (TIMER B INPUT CLOCK).

z 3FF0 : PORT_A[15..8] DIRECTION REGISTER. WRITE ONLY.

AN ‘1’ IN THIS REGISTER WILL SET THE CORRESPONDING PIN OF PORT_A TO BE OUTPUT.

THE DEFAULT VALUE FOR EACH BIT IS ZERO.

z 3FF1 : PORT_A[15..8] DATA REGISTER. READ AND WRITE.

z 3FF2: PORT_B[11..8] DATA REGISTER. WRITE ONLY.

BIT 3-0: PORT_B PIN 11 TO PIN 8.

BIT 7-4 : RESERVED.

z 3FF4 : BANK REGISTER FOR CPU. WRITE ONLY.

z 3FF5 : BANK REGISTER MSB BIT FOR CPU. WRITE ONLY.

BANK REGISTER IS 9 BITS REGISTER($3FF5 BIT0, $3FF4 BIT7-0).

THE MEMORY RANGE OF BANK IS FROM $4000 TO $7FFF.

www.aplusinc.com.tw TEL : 886-2-2782-9266

8

Page 9

APLUS INTEGRATED CIRCUITS INC. APC5860

BIT 1: RESERVED.

BIT 2: = 1 VOICE0 BUFFER BE TRANSFERRED TO DAC PORT DIRECTLY.(DEFAULT)

= 0 VOICE0 BUFFER WILL BE TRANSFERRED TO DAC PORT WHEN TIMER_B NMI HAPPEN.

BIT 7-3 : RESERVED.

z 3FF6 : PORT_C[7..0] DATA REGISTER. READ AND WRITE.

z 3FF7 : PORT_C[15..8] DATA REGISTER. READ AND WRITE.

z 3FF8: PORT_C[7..0] DIRECTION REGISTER. WRITE ONLY.

AN ‘1’ IN THIS REGISTER WILL SET THE CORRESPONDING PIN OF PORT_C TO BE OUTPUT.

THE DEFAULT VALUE FOR EACH BIT IS ZERO.

z 3FF9: PORT_C[15..8] DIRECTION REGISTER. WRITE ONLY.

AN ‘1’ IN THIS REGISTER WILL SET THE CORRESPONDING PIN OF PORT_C TO BE OUTPUT.

THE DEFAULT VALUE FOR EACH BIT IS ZERO.

z 3FFA :ADC REGISTER. READ ONLY.

WHEN THE TIMER B NMI OCCURS, THE A/D CONVERSION PROCESS STARTS AND THE S/H

CIRCUIT STOP SAMPLING AND BEGIN HOLDING IT UNTIL THE ADC PROCESS IS FINISHED.

THE ADC INT WILL GENERATE WHEN ADC PROCESS IS FINISHED.

z 3FFB,3FFC :….NO USE

z 3FFD : ……NO USE

z 3FFE: VOICE CHANNEL 1 LOW BYTE AND SYSTEM CONTROL 3. WRITE ONLY.

3FFE

0 1

SEPARATE MODE FOR DAC

BIT - 0

OUTPUT

(DEFAULT)

MIX MODE FOR DAC OUTPUT.

SEPARATE MODE FOR PWM

BIT - 1

OUTPUT

(DEFAULT)

MIX MODE FOR PWM OUTPUT

BIT - 2 NO USE(MUST 0)

BIT - 3 NO USE (MUST 0)

BIT – 7 ~ 4 VOICE CHANNEL 1 LOW NIBBLE BYTE.

www.aplusinc.com.tw TEL : 886-2-2782-9266

9

Page 10

APLUS INTEGRATED CIRCUITS INC. APC5860

z 3FFF : VOICE CHANNEL 1 HIGH BYTE. WRITE ONLY.

THE RESOLUTION OF VOICE CHANNEL 1 IS 12 BITS($3FFF,$3FFE BIT7_4). THIS REGISTER

WILL BE TRANSFERRED TO PWM PORT WHILE TIMER_B NMI HAPPEN IN SEPARATE MODE.

www.aplusinc.com.tw TEL : 886-2-2782-9266

10

Loading...

Loading...