Page 1

INTEGRATED CIRCUITS INC.--APC58120

APC58120 --- COMPRESS VOICE IC

1. Introduction :

APC58120 is a speech-melody chip. APC58120 provides one 10-bit DA

converter and one PWM driving speaker directly. But only one function

can be active at the same time. Besides, a general voice and music

decompression rate provided in the embedded decompression engine is

14.4k bit/sec for maximum and 3.6k bit/sec for minimum, while a

high-quality music decompression rate given in the engine is 24k bit/sec

for maximum and 10k bit/sec for minimum.

2. Features :

Power supply 2.4V~3.6V(For 2 battery application)

8k x 24bit instruction ROM

16M x 1 bit Data ROM

Built-in 1K x16 bit RAM

Built-in RC 32K oscillator

8 bit Timer x 3

1 Fix Timer x1

Watchdog Timer

10 bit DAC x1

10 bit PWM x1

16 bit Port A x1

8 bit Port B x1

8-level stacks of program counter

24-bit instructions

16-bit data bus

5 interrupt Timer_ A, Timer_ B, Timer_ C, Timer_ D, PA_INT

www.aplusinc.com.tw Page / 18 VER1.0

1

Page 2

INTEGRATED CIRCUITS INC.--APC58120

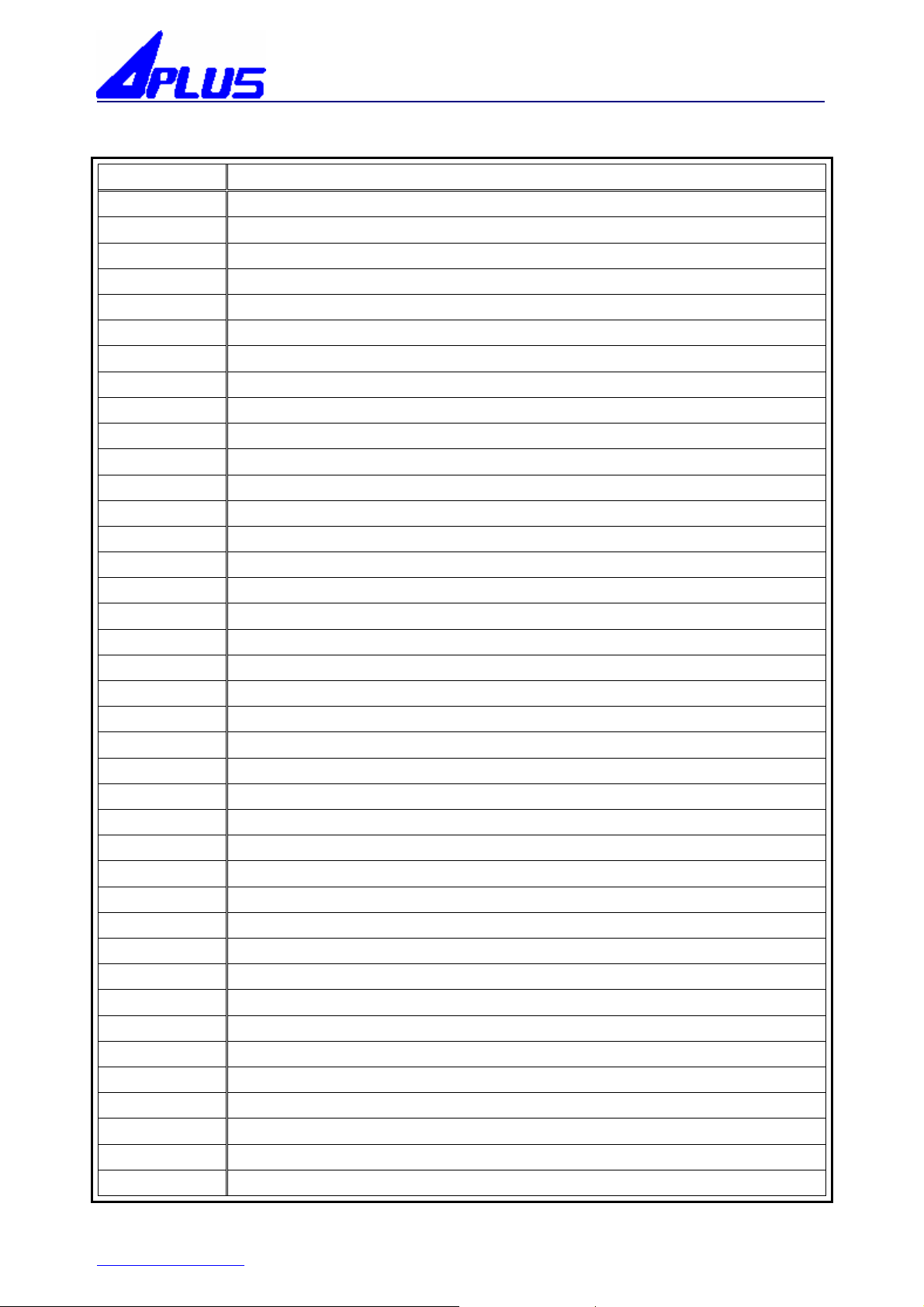

3. Memory mapping :

Address Register

00h INDirect addressing register ( IND0 )

01h Memory Index Register (MIR0)

02h INDirect addressing register ( IND1 )

03h Memory Index Register (MIR1)

04h Program register(PC)

05h Status Flag Register ( SFR )

06h Timer_A

07h Timer_B

08h Timer_C

09h Timer_D

0Ah TCA register

0Bh TCB register

0Ch TCC register

0Dh TCD register

0Eh Port A data Register ( RPA )

0Fh Port A Control register CPA

10h Port B data Register ( RPB )

11h Port B Control register CPB

12h Watchdog Timer Control Register

13h Interrupt Flag Register(IFR)

14h PLL Control register

15h PortA Interrupt control register

16h PortA Pull High register

17h PortB Pull High register

18h PortA Pull Down register

19h PortB Pull Down register

1Ah PortA edge Control register

1Bh Table Pointer Register High Word

1Ch Table Pointer Register Low Word

1Dh Data Pointer Register High Word

1Eh Data Pointer Register Low Word

1Fh M1

20h M0

21h C1

22h C0

23h Other register

24h PIR register

25h PLLSEL register

30H~3FFH RAM

www.aplusinc.com.tw Page / 18 VER1.0

2

Page 3

INTEGRATED CIRCUITS INC.--APC58120

y

4. Pin assignment :

mbol I/O Description

S

IN I 32K Oscillator resistor input

IO_VSS I Ground for IO PAD

CORE_VSS I Ground for CORE LOGIC

CORE_VDD I Power for CORE LOGIC

IO_VDD I Power for IO PAD

PA0~PA15 I/O I/O port

PB0~PB7 I/O I/O port

IO_VDD I Power for IO PAD

CORE_VDD I Power for CORE LOGIC

CORE_VSS I Ground for CORE LOGIC

IO_VSS I Ground for IO PAD

OSC1 I Crystal input

OSC2 O Crystal Output

TESTMODE I For test only

ERSTB I Chip Reset

XT_RC_SEL I Crystal or 32K oscillator select

DAC_VDD I Power for DAC

DAC_VSS I Ground for DAC

DACO O DAC output

PWMVDD I PWM VDD

PWM1O O PWM Output 1

PWMVSS I PWM VSS

PWM2O O PWM Output 2

PWMVDD I PWM VDD

ANA_VDD I Power for Analog Circuit

ANA_VSS I Ground for Analog Circuit

PLLCAP I PLL CAP input

www.aplusinc.com.tw Page / 18 VER1.0

3

Page 4

INTEGRATED CIRCUITS INC.--APC58120

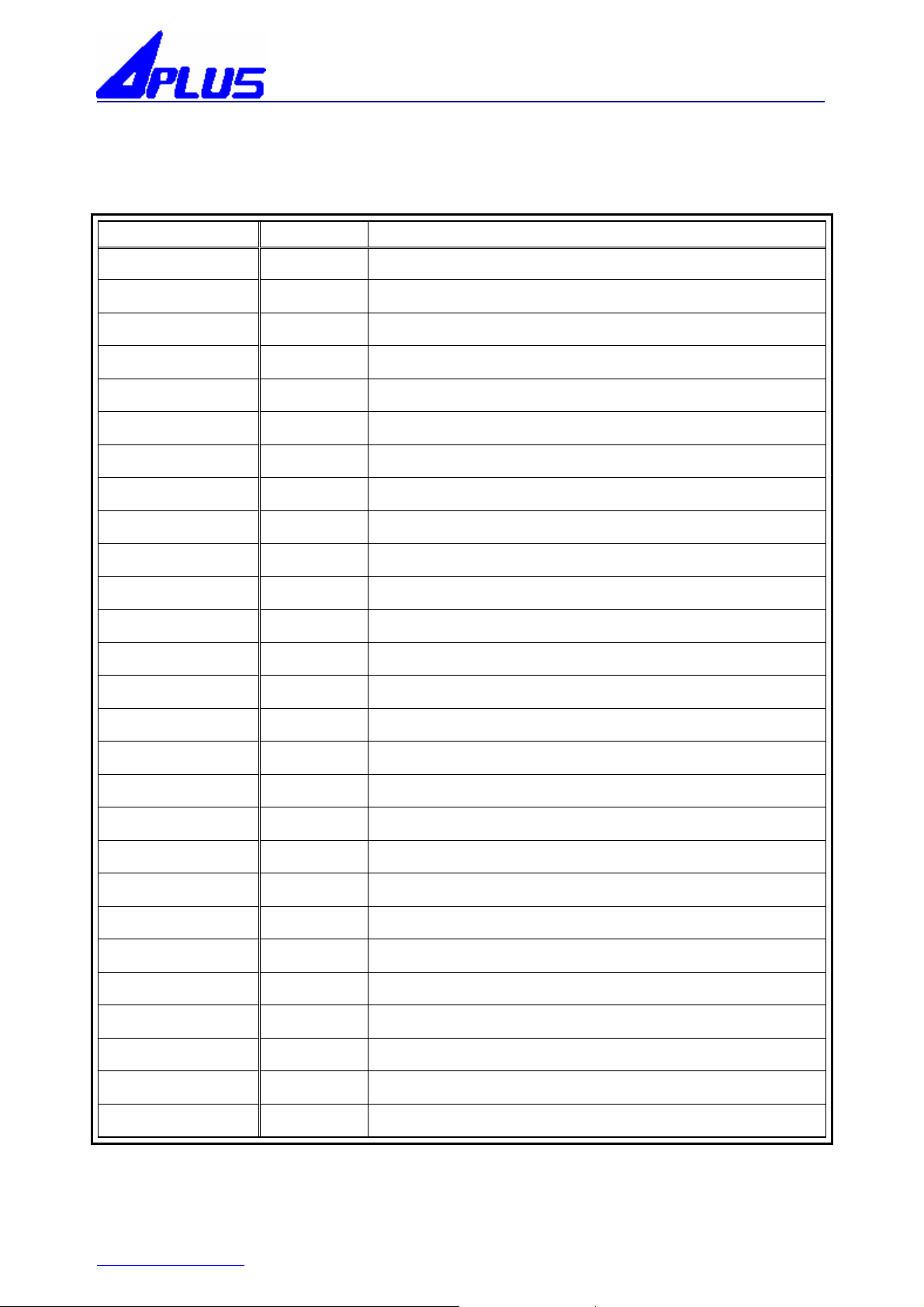

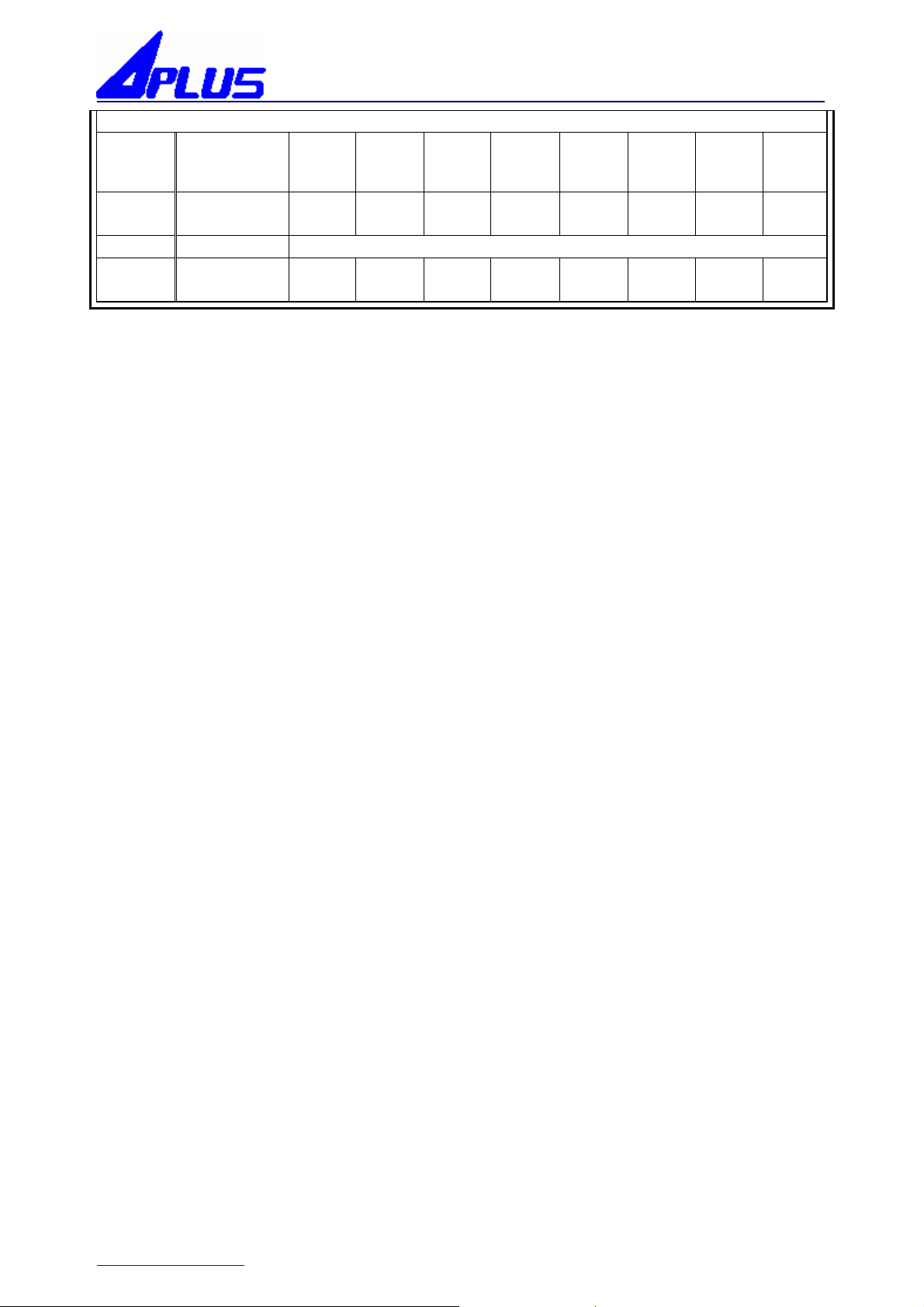

5.Function Control Registers:

Address Name

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

21h

22h

IND0[9:0]

MIR0[9:0]

IND1[9:0]

MIR1[9:0]

PC

SFR[7:0]

Timer_A

Timer_B

Timer_C

Timer_D

TCA[7:0]

TCB[7:0]

TCC[7:0]

TCD[7:0]

RPA[15:0]

CPA[15:0]

RPB[7:0]

CPB[7:0]

WTC[7:0]

IFR[7:0]

IFR[15:8]

PLLC[5:0]

IPA[7:0]

PHA

PHB

PDA

PDB

PADC

TDPTRH[16]

TDPTRL

DPTRH

DPTRL

M1

M0

C1

C0

Bit15/

Bit7

Bit14/

Bit6

Bit13/

Bit5

Bit12/

Bit4

Bit11/

Bit3

Bit10/

Bit2

Bit9/

Bit1

Bit8/

Bit0

Use contents of MIR0 to address data memory

(not a physical register)

Indirect data memory address pointer 0

Use contents of MIR1 to address data memory

(not a physical register)

Indirect data memory address pointer 1

Program Counter register

Ponrst WT SP Z AC C

8 bits of real timer clock/counter

8 bits of real timer clock/counter

8 bits of real timer clock/counter

Fix Timer

TAEI TAEN

TBEI TBEN

TCEI TCEN

TACK

SEL

TBCK

SEL

TCCK

SEL

TAPRE

EN

TBPRE

EN

TCPRE

EN

TAPS2 TAPS1 TAPS0

TBPS2 TBPS1 TBPS0

TCPS2 TCPS1 TCPS0

TDEI TDEN TDPS2 TDPS1 TDPS0

Port A data Register

Port A Control register

Port B data Register

Port B Control register

PortA7

_F

PortA6

_F

PortA5

_F

PortA4

PWMEN DACE

_F

Timer_

DF

PortA3

_F

N

WTPS

C2

Timer_

CF

PortA2

_F

PLLEN

WTPS

C1

Timer_

BF

PortA1

_F

PLLCl

ksel1

WTPS

C0

Timer_

AF

PortA0

_F

PLLCl

ksel0

PortA Interrupt control register

PortA Pull High register

PortB Pull High register

PortA Pull Down register

PortB Pull Down register

PortA Edge Control register

Table Pointer Register High Word

Table Pointer Register Low Word

Data Pointer Register High Word

Data Pointer Register Low Word

Result of multiplier high word

Result of multiplier Low word

Channel 1 register

Channel 0 register

www.aplusinc.com.tw Page / 18 VER1.0

4

Page 5

INTEGRATED CIRCUITS INC.--APC58120

23h[7:0]

23h[11:8]

24h

25h

OTH

OTH

PIR

PLLSEL

TMRB

OVPA

SSEN

C1ALP

ASSEN

pwmdo

usel

TMRA

OVPA

SSEN

REG1 REG2

C0ALP

ASSEN

Pre Index Register

LVDSEL LVDE N Config

_wtc1

PWMD

atasel

DACD

atasel

MIX1s

el

pllbypa

sssel

PLLsel

6. Special registers :

1)00H [9:0] <IND0> Indirect address register 0{RW}

Description:

Not serving as a physical register,the register is used as an indirect address register.

Reading or writing this address will have access to the register of the address

defined by 01H(MIR0).

2)01H [9:0] <MIR0> Memory Index register 0{RW}

[9:0] indicate that this register used in the indirect addressing mode defines which

register will be select during the instruction to read/write 00H

3)02H [9:0] <IND1> Indirect address register 1{RW}

Description:

Not serving as a physical register,the register is used as an indirect address register.

Reading or writing this address will have access to the register of the

address defined by 03H(MIR1).

4)03H [9:0] <MIR1> Memory Index register 1{RW}

[9:0] indicate that this register used in the indirect addressing mode defines

which register will be select during the instruction to read/write 02H

5) 04H <PC> Program Counter register

6)05H [5:0] <SFR> Status Flag register

<C> Carry Flag

<AC>Auxiliary Flag

<Z> Zero Flag

<SP> Sleep Flag

<WT> Watchdog Flag

<Ponrst> ponrst Flag

7)06H [15:0] <Timer_ A> Timer/Counter A register {RW}

8)07H [15:0] <Timer_ B> Timer/Counter B register {RW}

9)08H [15:0] <Timer_ C> Timer/Counter C register {RW}

10)09H [15:0] <Timer_ D> Fix Timer

Config

_wtc0

MIX0s

el

www.aplusinc.com.tw Page / 18 VER1.0

5

Page 6

INTEGRATED CIRCUITS INC.--APC58120

11)0AH [7:0] <TCA> Timer/Counter A Control register{RW}

[2:0] < TAPS2, TAPS1, TAPS0> Timer prescaler bit

TAPS2 TAPS1 TAPS0 rate

0 0 0 1:2

0 0 1 1:4

0 1 0 1:8

0 1 1 1:16

1 0 0 1:32

1 0 1 1:64

1 1 0 1:128

1 1 1 1:256

[4] <TAPREEN>

0:Timer A Prescaler Disable Prescale Rate 1:1

1:Timer A Prescaler Enable(default)

[5] <TACKSEL>

0: select system clock(default)

1: select crystal clock(32768)

[6]< TAEN> Timer/Counter Enable control

0: Timer/Counter disable(default)

1: Timer/Counter enable

[7]<TAEI> Timer/Counter Interrupt Enable control

0: Timer/Counter interrupt disable(default)

1: Timer/Counter interrupt enable

12)0BH [7:0] <TCB> Timer/Counter B Control register{RW}

[2:0] < TBPS2, TBPS1, TBPS0> Timer prescaler bit

TBS2 TBS1 TBS0 rate

0 0 0 1:2

0 0 1 1:4

0 1 0 1:8

0 1 1 1:16

1 0 0 1:32

1 0 1 1:64

1 1 0 1:128

1 1 1 1:256

[4] <TBPREEN>

0:Timer B Prescaler Disable Prescale Rate 1:1

1:Timer BPrescaler Enable(default)

[5] <TBCKSEL>

0: select system clock(default)

1: select crystal clock(32768)

[6]< TBEN> Timer/Couner Enable control

0: Timer/Counter disable(default)

1: Timer/Counter enable

[7]<TBEI> Timer/Counter Interrupt Enable control

0: Timer/Counter interrupt disable(default)

1: Timer/Counter interrupt enable

www.aplusinc.com.tw Page / 18 VER1.0

6

Page 7

INTEGRATED CIRCUITS INC.--APC58120

13) 0CH [7:0] <TCC> Timer/Counter C Control register{RW}

[2:0] < TCPS2, TCPS1, TCPS0> Timer prescaler bit

TCS2 TCS1 TCS0 rate

0 0 0 1:2

0 0 1 1:4

0 1 0 1:8

0 1 1 1:16

1 0 0 1:32

1 0 1 1:64

1 1 0 1:128

1 1 1 1:256

[4] <TCPREEN>

0:Timer C Prescaler Disable Prescale Rate 1:1

1:Timer C Prescaler Enable(default)

[5] <TCCKSEL>

0: select system clock(default)

1: select crystal clock(32768)

[6]< TCEN> Timer/Counter Enable control

0: Timer/Counter disable(default)

1: Timer/Counter enable

[7]<TCEI> Timer/Counter Interrupt Enable control

0: Timer/Counter interrupt disable(default)

1: Timer/Counter interrupt enable

14) 0DH [7:0] <TCD> Timer/Counter D Control register{RW}

[2:0] < TDPS2, TDPS1, TDPS0> Timer prescaler bit

TDS2 TDS1 TDS0 rate

0 0 0 0.5Hz

0 0 1 1Hz

0 1 0 2Hz

0 1 1 4Hz

1 0 0 8Hz

1 0 1 16Hz

1 1 0 32Hz

1 1 1 64Hz

[6]< TDEN> Timer/Counter Enable control

0: Timer/Counter disable(default)

1: Timer/Counter enable

[7]<TDEI> Timer/Counter Interrupt Enable control

0: Timer/Counter interrupt disable(default)

1: Timer/Counter interrupt enable

15) 0EH [15:0] <RPA> Port A data Register{RW}

www.aplusinc.com.tw Page / 18 VER1.0

7

Page 8

INTEGRATED CIRCUITS INC.--APC58120

16) 0FH [15:0] <CPA> Port A Control register{RW}

0: output

1: input(default)

17) 10H [7:0] <RPB> Port B data Register{RW}

18) 11H [7:0] <CPB> Port B Control register{RW}

0: output

1: input(default)

19) 12H [2:0] <WTC> Watchdog control register{RW}

[2:0] < WTPSC2,WTPSC1,WTPSC0>

WTPSC2 WTPSC1 WTPSC0 rate

0 0 0 1:1

0 0 1 1:2

0 1 0 1:4

0 1 1 1:8

1 0 0 1:16

1 0 1 1:32

1 1 0 1:64

1 1 1 1:128

WTPSC2 WTPSC1 WTPSC0 Rate

0 0 0 22ms

0 0 1 44ms

0 1 0 88ms

0 1 1 176ms

1 0 0 352ms

1 0 1 704ms

1 1 0 1408ms

1 1 1 2816ms

20) 13H <IFR> Interrupt Flag register{RW}

[0]< Timer_ AF> Timer/Counter A Flag register

[1]< Timer_ BF> Timer/Counter B Flag register

[2]< Timer_ CF> Timer/Counter C Flag register

[3]< Timer_ DF> Timer/Counter D Flag register

[8] < PortA0F> Port A Flag register

[9] < PortA1F> Port A Flag register

[10] < PortA2F> Port A Flag register

[11] < PortA3F> Port A Flag register

[12] < PortA4F> Port A Flag register

[13] < PortA5F> Port A Flag register

[15] < PortA7F> Port A Flag register

www.aplusinc.com.tw Page / 18 VER1.0

8

Page 9

INTEGRATED CIRCUITS INC.--APC58120

21) 14H <PLLC> PLL Control register

[1:0] < PLLClksel1, PLLClksel0>

0 0 24Mhz(default)

0 1 32Mhz

1 0 40Mhz

1 1 48MHz

[2] <PLLEN>

0: disable

1: enable (default)

[3] <DACEN> DAC enable register

0:disable (default)

1:enable

[4] <PWMEN> PWM enable register

0:disable (default)

1:enable

22) 15H [7:0] <IPA> Port A Interrupt control register {RW}

0: disable Port A Interrupt(default)

1:enable Port A Interrupt

23) 16H [15:0] <PHA> Port A Pull High register {RW}

0: Not pull high (default)

1 : pull high

24) 17H [7:0] <PHB> Port B Pull High register {RW}

0: Not pull high (default)

1 : pull high

25) 18H [15:0] <PDA> Port A Pull Down register {RW}

0: Not pull down (default)

1 : pull down

26) 19H [7:0] <PDB> Port B Pull Down register {RW}

0: Not pull down (default)

1 : pull down

27) 1AH [15:0] <PADC>Port A Edge Control register{RW}

[7:0] Port A interrupt happen when positive edge occur

[15:8] Port A interrupt happen when negative edge occur

28) 1BH <TDPTRH> Table Pointer Register High Word {RW}

29) 1CH <TDPTRL> Table Pointer Register Low Word {RW}

30) 1DH [15:0] <DPTRH> Data Pointer Register High Word {RW}

31) 1EH [15:0] <DPTRL> Data Pointer Register Low Word {RW}

32) 1FH [15:0] <M1> Result of multiplier high word {RW}

33) 20H [15:0] <M0> Result of multiplier low word {RW}

34) 21H [15:6] <C1> Channel 1 data register {RW}

www.aplusinc.com.tw Page / 18 VER1.0

9

Page 10

INTEGRATED CIRCUITS INC.--APC58120

35) 22H [15:6] <C0> Channel 0 data register {RW}

36) 23H [11:0] OTH OTHER register

[1:0] <CONFIG_wtc1,CONFIG_wtc0>

x0 for watchdog timer disabled all the time

01 for watchdog timer disabled during sleep or stand-by mode

11 for watchdog timer enabled all the time (default)

[2]<LVDEN> Low Voltage reset enable

0 : disable(default)

1 : enable

[3]<LVDSEL> Low Voltage reset voltage select

0 : Lower 1.4~1.8V(default)

1 : Higher 2.1~2.8V

[4]<C0ALPASSEN> C0 register Pass to temp0 register {see figure 1}

0:whether pass controlled by Timer A (default)

1:always pass

[5]< TMRAOVPASSEN > Timer A overflow signal pass enable

0:disable (default)

1:enable

[6]<C1PASSEN> C1 register Pass to temp1 register {see figure 1}

0:whether pass controlled by Timer B (default)

1:always pass

[7]<TMRBOVPASSEN>Timer B overflow signal pass enable

0:disable (default)

1:enable

[8]<MIX0sel> select channel 0 data or mixed data

0:select channel 0 Data (default)

1: select Mix Data

[9]<MIX1sel> select channel 1 data or mixed data

0:select channel 0 Data(default)

1: select Mix Data

[10]<DACDatasel> DAC select MUX0 data or MUX1 data

0:select MUX0 Data(default)

1: select MUX1 Data

[11]<PWMDatasel> PWM select MUX0 data or MUX1 data

0:select MUX0 Data(default)

1: select MUX1 Data

[13:12] REG[1:0]

They are unused

[14] pwmdousel

0:select 1’s order modulator

1:select 2’s order modulator(default)

37) 24H[10:0] Pre Index Register

38) 25H[0]

[0] <PLLsel>

0: System Clock = PLL(default)

1: System Clock = 32768Hz

[1]< pllbypasssel>

0: select 1/2 PLL clock(default)

1: select PLL clock

www.aplusinc.com.tw Page / 18 VER1.0

10

Page 11

INTEGRATED CIRCUITS INC.--APC58120

7. Special Register Condition :

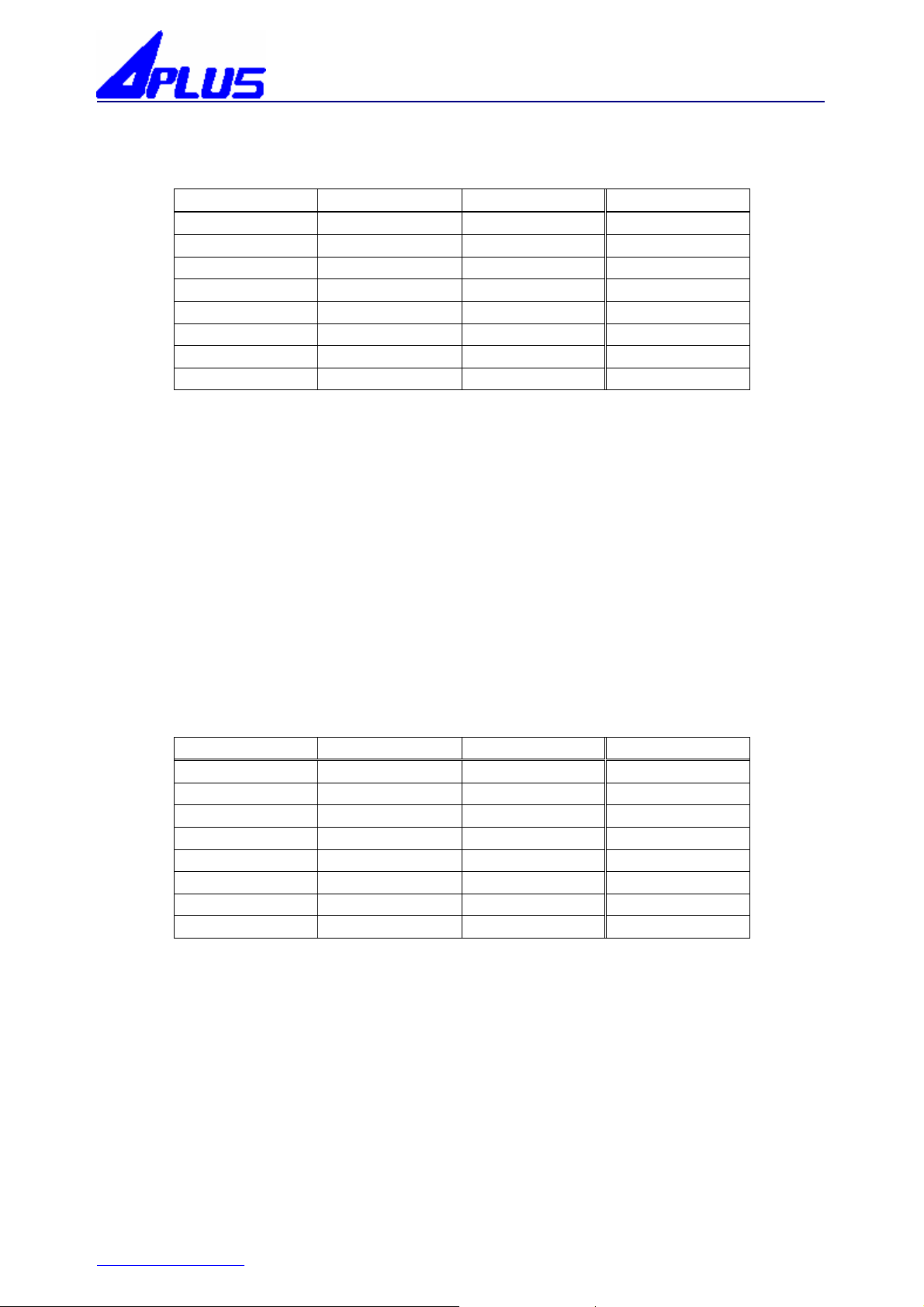

Registers Power-on/External Reset Watchdog reset

01H(MIR0)

03H(MIR1)

04H(PC)

05H(SFR)

06H(TIMER_A)

07H(TIMER_B)

08H(TIMER_C)

09H(TIMER_D)

0AH(TCA)

0BH(TCB)

0CH(TCC)

0DH(TCD)

0EH(RPA)

0FH(CPA)

10H(RPB)

11H(CPB)

12H(WTC)

13H(IFR)

14H(PLLC)

15H(IPA)

16H(PHA)

17H(PHB)

18H(PDA)

19H(PDB)

1AH(PADC)

1BH(TDPTRH)

1CH(TDPTRL)

1DH(DPTRH)

1EH(DPTRL)

1FH(M1)

20H(M0)

21H(C1)

22H(C0)

23H(OTH)

24H(PIR)

25H(PLLSEL)

xxxx xxxx xxxx xxxx uuuu uuuu uuuu uuuu

xxxx xxxx xxxx xxxx uuuu uuuu uuuu uuuu

0000 0000 0000 0000 0000 0000 0000 0000

---- ---- --11 1xxx ---- ---- --u0 1uuu

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

---- ---- ---- ---- ---- ---- ---- ----

---- ---- 0001 -111 ---- ---- 0001 -111

---- ---- 0001 -111 ---- ---- 0001 -111

---- ---- 0001 -111 ---- ---- 0001 -111

---- ---- 00-- -111 ---- ---- 00-- -111

xxxx xxxx xxxx xxxx uuuu uuuu uuuu uuuu

1111 1111 1111 1111 1111 1111 1111 1111

xxxx xxxx xxxx xxxx uuuu uuuu uuuu uuuu

---- ---- 1111 1111 ---- ---- 1111 1111

---- ---- ---- -111 ---- ---- ---- -111

0000 0000 ---- 0000 0000 0000 ---- 0000

---- ---- ---0 0100 ---- ---- ---0 0100

---- ---- 0000 0000 ---- ---- 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

---- ---- 0000 0000 ---- ---- 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

---- ---- ---- ---0 ---- ---- ---- ---0

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 0000 0000 0000 0000 0000 0000

0000 0000 00-- ---- 0000 0000 00-- ---0000 0000 00-- ---- 0000 0000 00-- ----

---- 1000 0000 0011 ---- 1000 0000 0011

0000 0000 0000 0000 0000 0000 0000 0000

---- ---- ---- --00 ---- ---- ---- --00

x:unknown

u:unchanged

?:conditional

red color means only controlled by power on reset

www.aplusinc.com.tw Page / 18 VER1.0

11

Page 12

INTEGRATED CIRCUITS INC.--APC58120

8. Figure 1 MIX system :

www.aplusinc.com.tw Page / 18 VER1.0

12

Page 13

INTEGRATED CIRCUITS INC.--APC58120

d

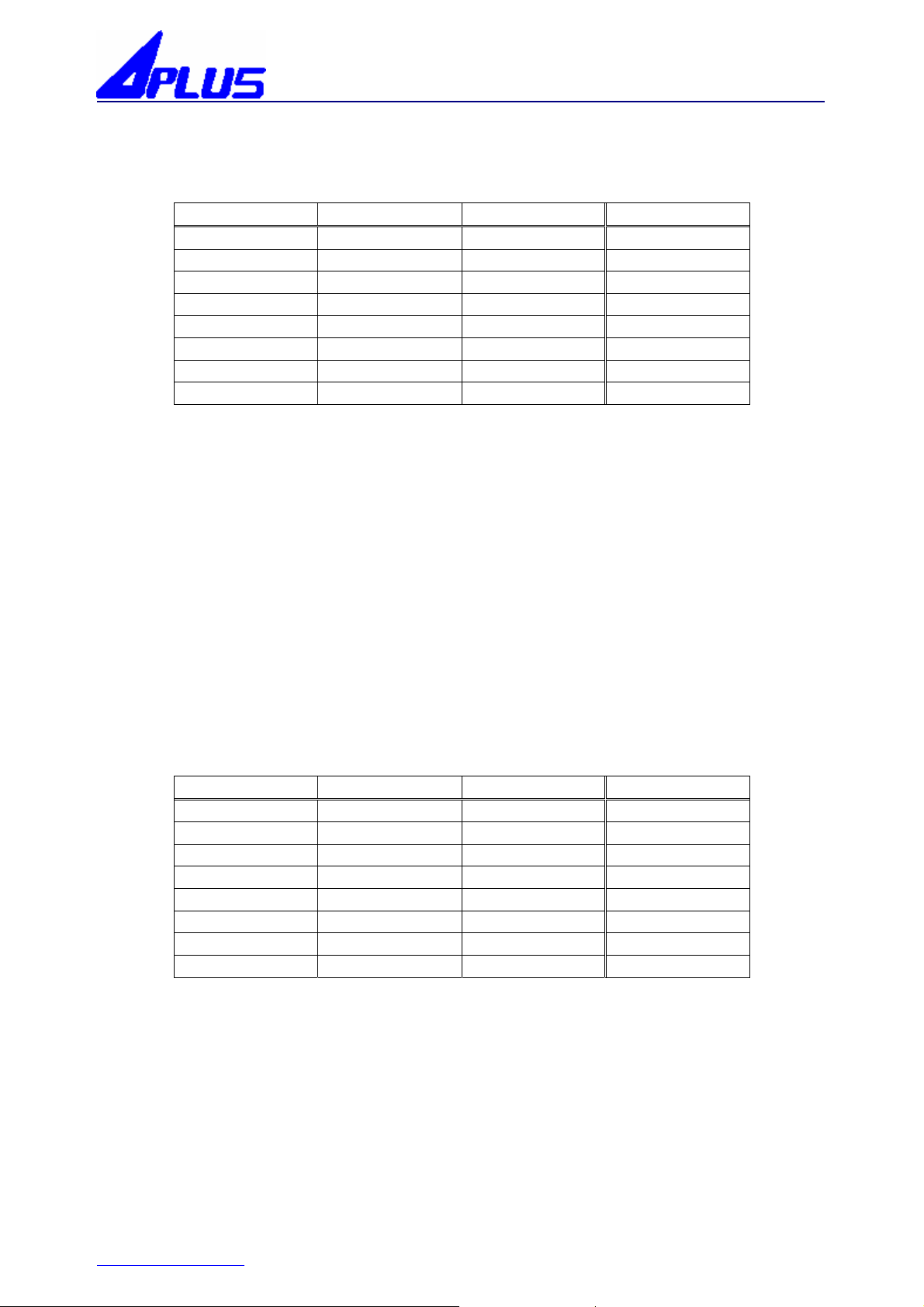

9. Instruction Set :

Binary Code Syntax Operation Status Affecte

00000000

0000000000000000

00001111 11111110

000nnnnn

00001111

11111111 000nnnnn

00001111

11111110 001nnnnn

00001111 11111111

001nnnnn

00001111

11111111 11110110

00001111

11111111 11110111

00001111

11111111 11111000

00001111

11111111 11111001

00001111

11111111 11111010

00001111 11111111

11111011

00001111 11111111

11110100

00001111 11111111

11110101

00001111 11111111

11111100

00001111 11111111

11111101

00001111

11111111 11111110

00001111

11111111 11111111

00010000

iiiiiiii iiiiiiii

00010001

rrrrrrrr rrrrrrrr

NOP

SHLM n

SHRM n

SHSLM n

SHSRM n

CLRWT

STDBY

SLEEP

RET

RETI

SKIPA

TLBDA

TLBPA

TLDDA

TLDPA

LDDA

LDPA

MULIA i

MULAR r

None None

SLM M1M0 n bit→M1M0

sign →M1M0[31]

0 →M1M0[n-1:0]

SRM M1M0 n bit→M1M0

sign →M1M0[31]

sign →M1M0[31:31-n]

SLM M1M0 n bit→M1M0

{SATURATION}

sign →M1M0[31]

0 →M1M0[n-1:0]

SRM M1M0 n bit→M1M0

{SATURATION}

sign →M1M0[31]

sign→M1M0[31:31-n]

0→WT

Stop Clock SP=0

Stop OSC SP=0

Stack→PC

Stack→PC

PC+A →PC

(TDPTR[31:0])(Byte mode)→A

(TDPTR[31:0])(Byte mode)→A

tdptr+=1

(TDPTR[31:0])→A

(TDPTR[31:0])→A,tdptr+=1

(DPTR[31:0])→A

(DPTR[31:0])→A,dptr+=1

i*A→M1M0

r*A →M1M0

None

None

None

None

None

None

None

Z

Z

Z

Z

Z

Z

None

None

www.aplusinc.com.tw Page / 18 VER1.0

13

Page 14

INTEGRATED CIRCUITS INC.--APC58120

00010010

rrrrrrrr rrrrrrrr

00010011

rrrrrrrr rrrrrrrr

00010100

rrrrrrrr rrrrrrrr

00010101

rrrrrrrr rrrrrrrr

00010110

rrrrrrrr rrrrrrrr

00010111

iiiiiiii iiiiiiii

00011000

rrrrrrrr rrrrrrrr

0001101d

rrrrrrrr rrrrrrrr

0001110d

rrrrrrrr rrrrrrrr

0010dnnn

nrrrrrrr rrrrrrrr

0011dnnn

nrrrrrrr rrrrrrrr

0100dnnn

nrrrrrrr rrrrrrrr

0101dnnn

nrrrrrrr rrrrrrrr

1000bbbb

rrrrrrrr rrrrrrrr

1001bbbb

rrrrrrrr rrrrrrrr

1010bbbb

rrrrrrrr rrrrrrrr

1011bbbb

rrrrrrrr rrrrrrrr

1100000d

rrrrrrrr rrrrrrrr

1100001d

rrrrrrrr rrrrrrrr

1100010d

rrrrrrrr rrrrrrrr

1100011d

rrrrrrrr rrrrrrrr

1100100d

rrrrrrrr rrrrrrrr

1100101d

rrrrrrrr rrrrrrrr

1100110d

MULSAR r

CMPAR r

STAR r

CLRR r

MULMR

MULMI

STARO

LDR r,d

LDRO r,d

SSHL r,n,d

SSHR r,n,d

SHL r,n,d

SHR r,n,d

BCR r,b

BSR r,b

BTRSC r,b

BTRSS r,b

ADDAR r,d

ADCAR r,d

SUBAR r,d

SBCAR r,d

IORAR r,d

XORAR r,d

ANDAR r,d

r*A →M1M0{SATURATION}

r-A C,Z

A→r

0→r

r*M1M0 ->M1M0 None

i*M1M0 ->M1M0 None

r A → (r+PIR)

r → d

(r+PIR) → d

r SHL n →d

sign →r[15]

0 →r[n-1:0]

r SHR n →d

sign→r[15]

sign→r[15:15-n]

r SHL n ->d

0 →r[n-1:0]

r SHR n ->d

0 →r[15:16-n]

0 →r[b]

1 →r[b]

Skip if r[b]=0 None

Skip if r[b]=1

r+A →d

r+A+C →d

r-A →d

r-A-/C →A

r .OR. A →d

r .XOR.A →d

r .AND.A →d

None

None

Z

Z

Z

None

None

None

None

None

None

None

C,AC,Z

C,AC,Z

C,AC,Z

C,AC,Z

Z

Z

Z

www.aplusinc.com.tw Page / 18 VER1.0

14

Page 15

rrrrrrrr rrrrrrrr

1100111d

rrrrrrrr rrrrrrrr

1101000d

rrrrrrrr rrrrrrrr

1101001d

rrrrrrrr rrrrrrrr

1101010d

rrrrrrrr rrrrrrrr

1101011d

rrrrrrrr rrrrrrrr

1101100d

rrrrrrrr rrrrrrrr

1101101d

rrrrrrrr rrrrrrrr

1101110d

rrrrrrrr rrrrrrrr

1101111d

rrrrrrrr rrrrrrrr

11100010

rrrrrrrr rrrrrrrr

11101100

iiiiiiii iiiiiiii

11101101

iiiiiiii iiiiiiii

11110010

iiiiiiii iiiiiiii

11110100

iiiiiiii iiiiiiii

11110101

iiiiiiii iiiiiiii

11110110

iiiiiiii iiiiiiii

11110111

iiiiiiii iiiiiiii

11111000

iiiiiiii iiiiiiii

11111001

iiiiiiii iiiiiiii

11111010

iiiiiiii iiiiiiii

11111011

iiiiiiii iiiiiiii

11111100

iiiiiiii iiiiiiii

11111101

iiiiiiii iiiiiiii

11111110

iiiiiiii iiiiiiii

INTEGRATED CIRCUITS INC.--APC58120

COMR r,d

ADDSAR

r,d

ADCSAR

r,d

SUBSAR

r,d

SBCSAR

r,d

DECR r,d

DRSZ r,d

INCR r,d

IRSZ r,d

XCHAR r

CALL i

JUMP i

LDIA i

ADDSIA i

ADCSIA i

SUBSIA i

SBCSIA i

ADDIA i

ADCIA i

SUBIA i

SBCIA i

CMPIA i

IORIA i

XORIA i

/R →d

r+A →d{SATURATION}

r+A+C →d{SATURATION}

r-A →d{SATURATION}

r-A-/C→d{SATURATION}

r-1 →d

r-1 →d,skip if Zero

r+1 →d

r+1 →d,skip if Zero

r <-> A None

PC →stack,i →PC

i →PC

i →A

i+A →A{SATURATION}

i+A+C→A{SATURATION}

i-A→A{SATURATION}

i-A-/C→A{SATURATION}

i+A →A

i+A+C →A

i-A →A

i-A-/C→A

i-A C,Z

i .OR. A →A

i .XOR.A →A

Z

C,AC,Z

C,AC,Z

C,AC,Z

C,AC,Z

Z

None

Z

None

None

None

None

C,AC,Z

C,AC,Z

C,AC,Z

C,AC,Z

C,AC,Z

C,AC,Z

C,AC,Z

C,AC,Z

Z

Z

www.aplusinc.com.tw Page / 18 VER1.0

15

Page 16

INTEGRATED CIRCUITS INC.--APC58120

11111111

iiiiiiii iiiiiiii

Notes to syntax:

r: General register address

A: Accumulator

b: Bit position

n: Number

i: Immediate data

d: Destination

'1' General register

'0' Accumulator

Z: Zero flag

C: Carry flag

AC: Auxiliary

SP: Sleep flag

Reg: General register

WT: watchdog timer

OR.: Inclusive

XOR.: Exclusive

/: Complement

M1M0 : M1 & M0 register

ANDIA i

i .AND.A →A

Z

10. DAC & PWM :

PWM:A 10-bit PWM is built in APC58120.The PWM can drive speaker directly.

DAC: A 10-bit current mode DA converter is built in APC58120.The input data and

the mapping current are as follows.

Input data(Code) Current (mA)

0 0

1 3/1024

2 3*2/1024

3 3*3/1024

4 3*4/1204

……. ……

1024 3*1024/1024 = 3

11. Electrical Parameter :

DC Characteristic

Test Condition: VDD = 2.4V – 3.6V (3.3V), TA (max) = 75°C

Parameter Symbol

Operating Voltage VDD 2.4 3.6 V

Operating Current IDD 3.35 mA VDD = 3.3V

Power down Current IDWN 7.85 uA VDD = 3.3V

Specification

Min Max Unit

Test Condition

www.aplusinc.com.tw Page / 18 VER1.0

16

Page 17

INTEGRATED CIRCUITS INC.--APC58120

AC Characteristic

Conditions at: Ta = 0 ~ 75°C, VDD = 3.3V, VSS = 0V

Name Symbol Conditions Min. Typ. Max. Unit

PLL Oscillator

Frequency

Fcry 32 Mhz

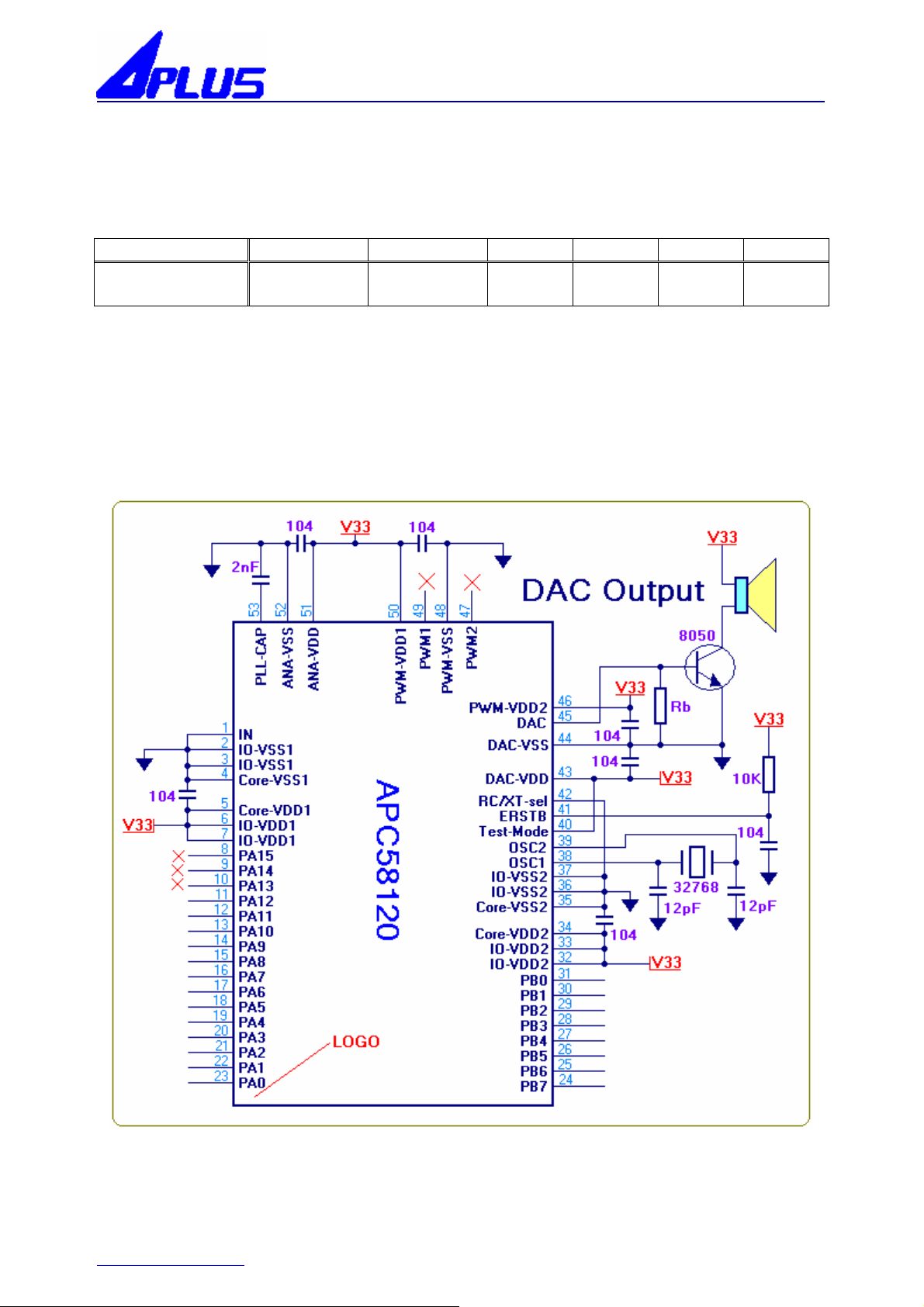

12. APPLICATION CIRCUIT :

DAC Output application :

www.aplusinc.com.tw Page / 18 VER1.0

17

Page 18

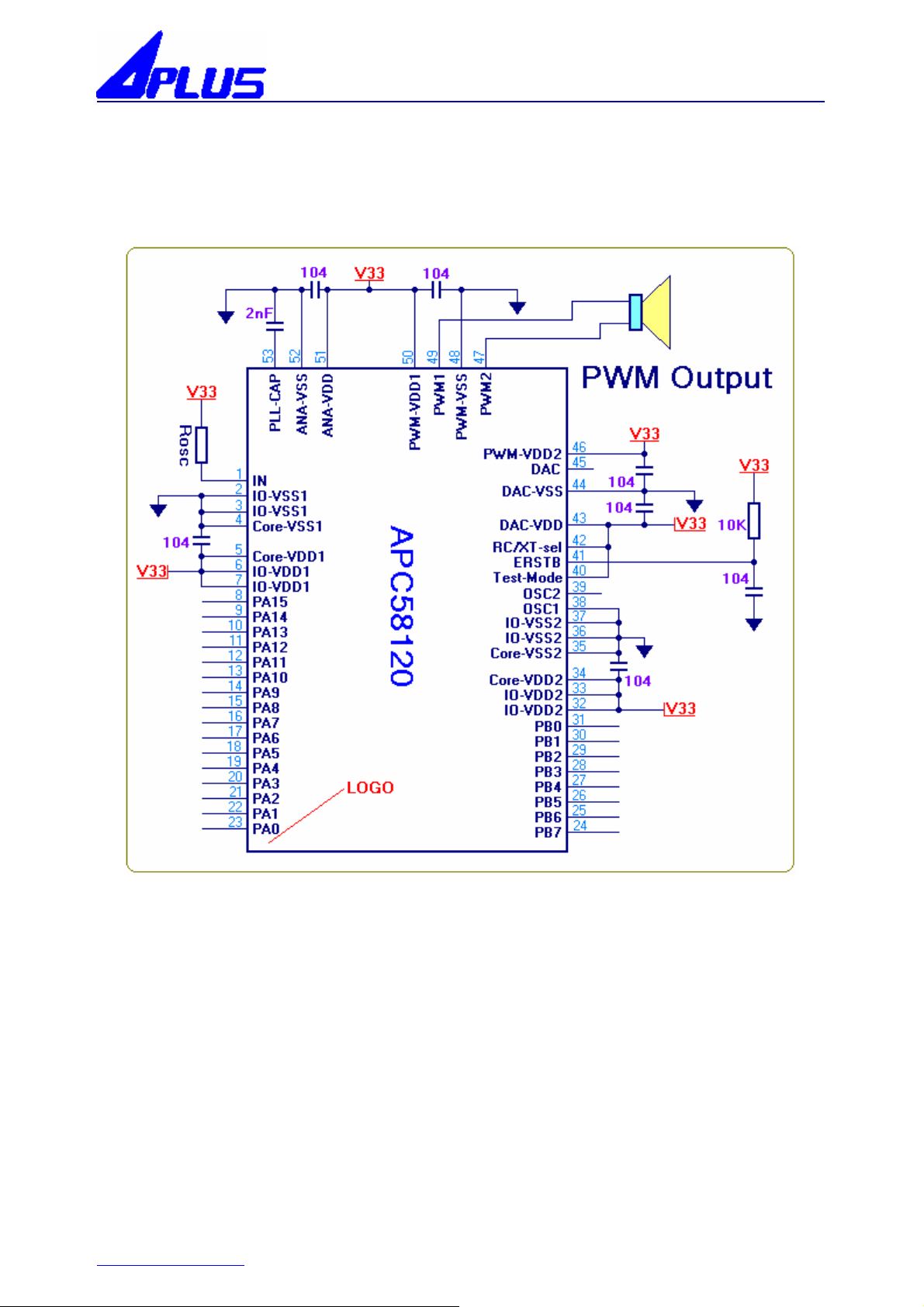

INTEGRATED CIRCUITS INC.--APC58120

PWM Output application :

www.aplusinc.com.tw Page / 18 VER1.0

18

Loading...

Loading...