Page 1

Integrated Circuits Inc. aP89341/170/085

APLUS MAKE YOUR PRODUCTION A-PLUS

VOICE OTP IC

aP89341 – 341sec

aP89170 – 170sec

aP89085 – 85sec

APLUS INTEGRATED CIRCUITS INC.

Address:

3 F-10, No. 32, Sec. 1, Chenggung Rd., Taipei,

Taiwan 115, R.O.C.

(115)台北市南港區成功路一段 32 號 3樓之 10.

TEL: 886-2-2782-9266

FAX: 886-2-2782-9255

WEBSITE : http: //www.aplusinc.com.tw

Sales E-mail:

sales@aplusinc.com.tw

Support E-mail:

service@aplusinc.com.tw

Page 2

Integrated Circuits Inc. aP89341/170/085

FEATURES

• Standard CMOS process.

• Embedded 8M/4M/2M EPROM.

• 341/170/85 sec Voice Length at 6KHz sampling and 4-bit ADPCM compression.

• Maximum 254 voice groups.

• Combination of voice blocks to extend playback duration.

• 7680 table entries are available for voice block combinations.

• User selectable PCM or ADPCM data compression

• Three triggering modes are available (controlled by M1 and M0 input pins):

- Key Trigger Mode (M1=0, M0=0) - S1 ~ S8 to trigger up to 32 voice groups; SBT

to trigger up to 254 voice groups sequentially.

- CPU Parallel Trigger Mode (M1=0, M0=1) – S[8:1] services as 8-bits address to

trigger up to 254 voice groups with SBT goes HIGH to strobe the address bits.

- CPU Serial Command Mode (M1=1, M0=0) – user commands are clocked serially

into the chip which enable user to fully control the operation of the chip.

• Voice Group Trigger Options: Edge / Level; Hold / Un-hold; Retrigger / Non-retrigger.

• Whole Chip Options: Ramp / No-ramp; Output Options; Long / Short debounce time.

• Optional 16ms or 65us (@ 8KHz sampling rate) selectable debounce time

• RST pin set to HIGH to stop the playback at once

• Three user programmable outputs for STOP pulse, BUSY signal and flashing LED.

• Built-in oscillator to control sampling frequency with an external resistor

• 2.2V – 3.6V single power supply and < 5uA low stand-by current

• PWM Vout1 and Vout2 drive speaker directly

• D/A COUT pin drives speaker through an external BJT

• Development System support voice compilation.

DESCRIPTION

aP89341/170/085 series high performance Voice OTP is fabricated with Standard CMOS process with

embedded 8M/4M/2M bits EPROM. It can store up to 341/170/85 sec voice message with 4-bit

ADPCM compression at 6KHz sampling rate. 8-bit PCM is also available as user selectable option.

Three trigger modes, simple Key trigger mode, Parallel CPU trigger mode and CPU serial command

mode, facilitate different user interface. User selectable triggering and output signal options provide

maximum flexibility to various applications. Built-in resistor controlled oscillator, 8-bit current mode

D/A output and PWM direct speaker driving output minimize the number of external components. PC

controlled programmer and developing software are available.

Ver 2.1 1 Aug 24, 2006

Page 3

Integrated Circuits Inc. aP89341/170/085

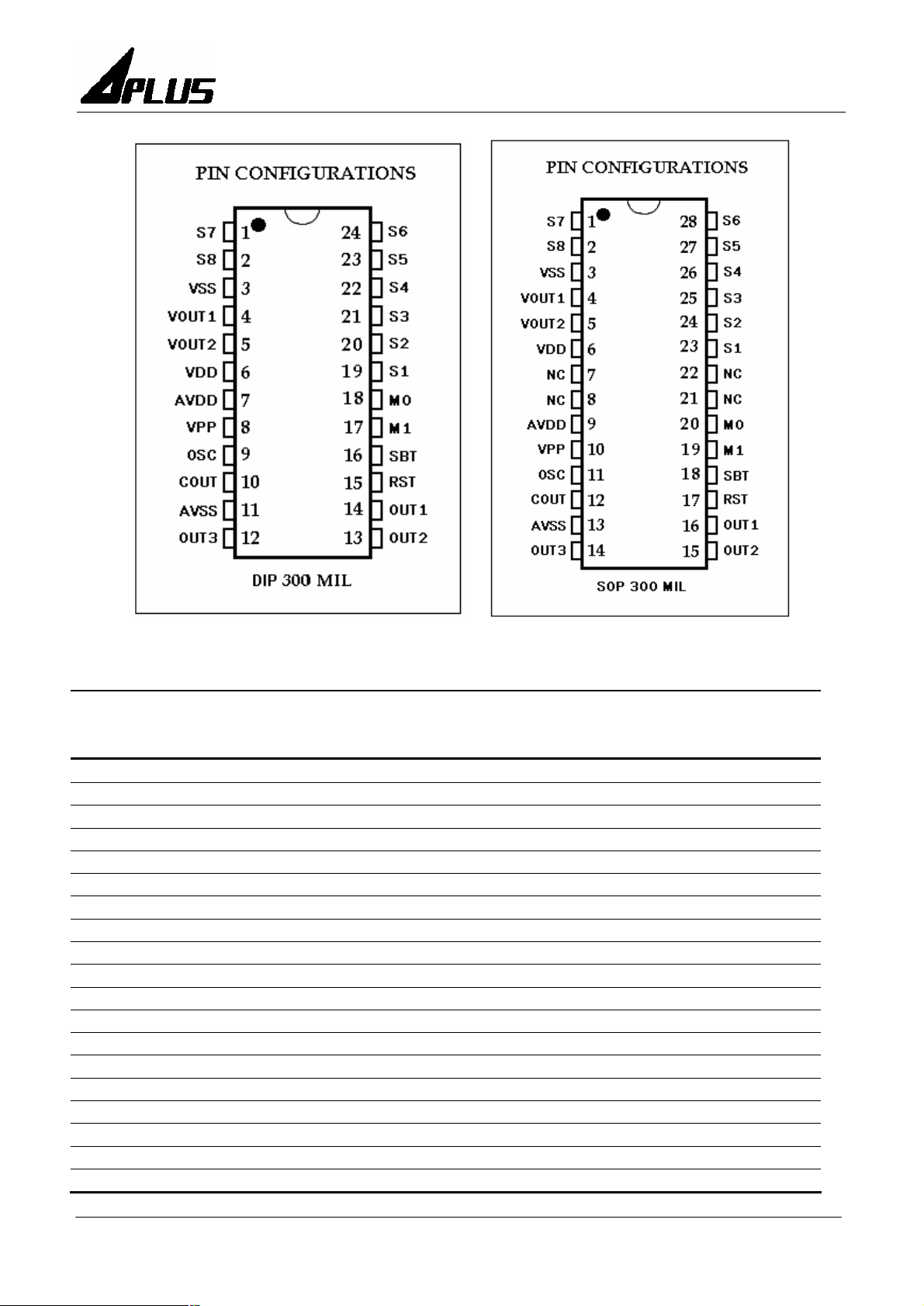

PIN NAMES

PIN

(24-pin)

1 S7 IO6 Trigger pin (I/O pin with internal pull-down)

2 S8 IO7 Trigger pin (I/O pin with internal pull-down)

3 VSS VSS Ground

4 VOUT1 - PWM output to drive speaker directly

5 VOUT2 - PWM output to drive speaker directly

6 VDD VDD Supply voltage

7 AVDD AVDD Analog supply voltage

8 VPP VPP Supply voltage for OTP programming

9 OSC ACLK Oscillator input

10 COUT - D/A current output

11 AVSS AVSS Analog ground

12 OUT3 - Programmable output (I/O pin)

13 OUT2 SIO Programmable output (I/O pin)

14 OUT1 OEB Programmable output (I/O pin)

15 RST DCLK Reset pin (input pin with internal pull-down)

16 SBT PGM Trigger pin (I/O pin with internal pull-down)

17 M1 M1 Mode select pin 1 (input with internal pull-down)

18 M0 M0 Mode select pin 0 (input with internal pull-down)

19 ~ 24 S1~S6 IO0~IO6 Trigger input (I/O pin with internal pull-down)

Playback

Mode

OTP

Program

Mode

Description

Ver 2.1 2 Aug 24, 2006

Page 4

Integrated Circuits Inc. aP89341/170/085

PIN DESCRIPTIONS

S1 ~ S8

Input Trigger Pins:

- In Key Trigger Mode, S1 to S8 is used to trigger the first 32 out of the total 254 Voice Groups .

- In CPU Parallel Command Mode, S1 to S8 serve as Voice Group address inputs for 254 Voice

Groups with S1 as LSB and S8 as MSB.

- In CPU Serial Command Mode, S1 is Chip Select (SC) pin to initiate the command input. S2 is

the Serial Clock (SCK) pin which clocks the input command and data bits into the chip. S3 is the

Data In (DI) pin in which command and data bits are shifted input into the chip.

- In OTP Programming Mode, S1 to S8 are used as data I/O pins.

SBT

Input Trigger Pin:

- In Key Trigger Mode, this pin is trigger pin to trigger the playback of Voice Groups one by one

sequentially.

- In CPU Parallel Command Mode, this pin is used as address strobe to latch the Voice Group

address input at S1 to S8 and starts the voice playback.

- In OTP Programming Mode, this pin is used as PGM signal.

VDD and AVDD

Power Supply Pins: These two pins must be connected together to the positive power supply.

VSS and AVSS

Power Ground Pins: These two pins must be connected to the power ground.

M0 and M1

Operating Mode Setting Pins:

- M1=0, M0=0 set the chip into Key Trigger Mode

- M1=0, M0=1 set the chip into CPU Parallel Command Mode

- M1=1, M0=0 set the chip into CPU Serial Command Mode

- M1=1, M0=1 set the chip into OTP Programming Mode

VOUT1 and VOUT2

Digital PWM output pins which can drive speaker and buzzer directly for voice playback.

OSC

During voice playback, an external resistor is connect between this pin and the VDD pin to set the

sampling frequency. In OTP Programming Mode, this is the ACLK input signal.

VPP

During voice playback, this pin must be connected together with VDD to the positive power supply

voltage. In OTP Programming Mode, this pin is connected to a separate 6.5V power supply voltage

for EPROM programming.

OUT1, OUT2 and OUT3

- In Key Trigger Mode and CPU Parallel Command Mode, these pins are user programmable pins

for the STOP pulse, BUSY and LED signals.

- In CPU Serial Command Mode, OUT1, OUT2 and OUT3 are fixed as BUSY, POUT and FULL

status output which tell the status of the chip operation. POUT can be further configurable to

BUSYB, 8K, 4K, 2K, 1K, 16Hz, 1M and EMPTY (or FULLB).

- During OTP programming, OUT1 serves as OEB while OUT2 serves as SIO (serial data IO).

COUT

Analog 8-bit current mode D/A output for voice playback

RST

Chip reset in playback mode or DCLK pin in OTP programming mode.

Ver 2.1 3 Aug 24, 2006

Page 5

Integrated Circuits Inc. aP89341/170/085

VOICE SECTION COMBINATIONS

Voice files created by the PC base developing system are stored in the built-in EPROM of the

aP89341/170/085 chip as a number of fixed length Voice Blocks. Voice Blocks are then selected and

grouped into Voice Groups for playback. Up to 254 Voice Groups are allowed. A Voice Block Table

is used to store the information of combinations of Voice Blocks and then group them together to form

Voice Group.

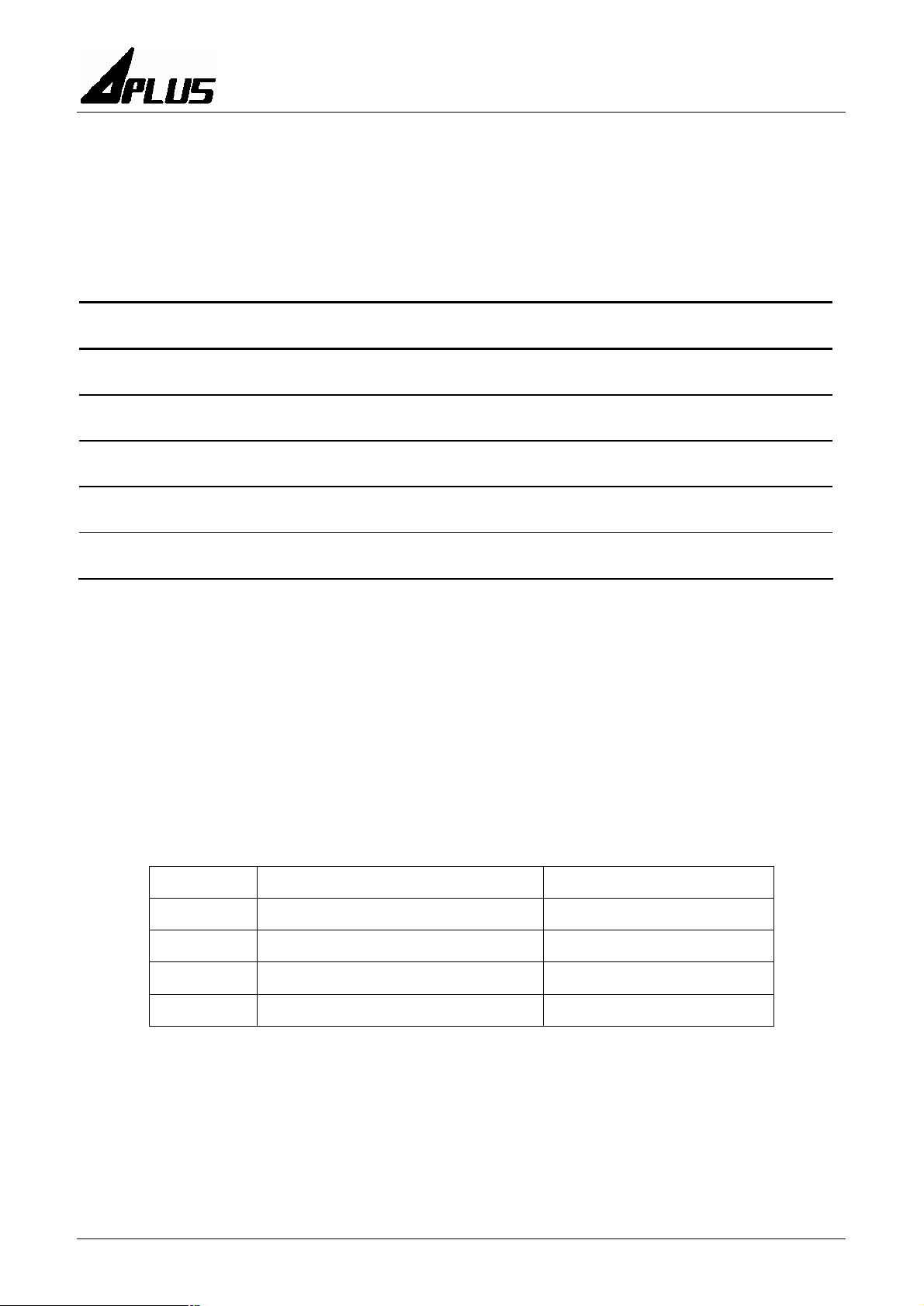

Chip aP89341 aP89170 aP89085

Memory size 8M bits 4M bits 2M bits

Max no. of Voice Block 2016 992 480

Max. no. of Voice Group 254 254 254

No of Voice Table entries 7680 7680 7680

Voice Length

(@ 6KHz 4-bit ADPCM)

Example of Voice Block Combination

Assume here we have three voice files, they are “How are You?”, Sound Effect and Music. Each of

the voice file is divided into a number of fixed length Voice Block and stored into the memory.

Voice File 1 - “How are You?” is stored in Voice Block B0 to B12.

Voice File 2 - Sound Effect is stored in Voice Block B13 to B15.

Voice File 3 - Music is Voice Block B16 to B40.

Voice Blocks are grouped together using Voice Table to form Voice Group for playback:

Group no. Voice Group contents Voice Table Entries

Group 1 “How are You?” B0 … B12

Group 2 Sound Effect + “How are You?” B13 … B15 + B0 … B12

Group 3 “How are You?” + Music B0 … B12 + B16 … B40

341 sec 170 sec 85 sec

Group 4 Music B16 … B40

Voice Data Compression

Voice File data is stored in the on-chip EPROM as either 4-bit ADPCM or 8-bit PCM format. Voice

data stored as 4-bit ADPCM provides 2:1 data compression which can save 50% of memory space.

On the other hand, voice data are stored as 8-bit PCM format means no data compression is employed

but voice playback quality will be better.

Ver 2.1 4 Aug 24, 2006

Page 6

Integrated Circuits Inc. aP89341/170/085

Programmable Options

In Key Trigger Mode (M1=0; M0=0) and CPU Parallel Trigger Mode (M1=0; M0=1), user can select

different trigger functions and output signals to be sent out from the pins OUT1, OUT2 and OUT3.

Options that affect all Voice Group playback are called Whole Chip Options. Options that only affect

the playback of individual Voice Group are called Group Options.

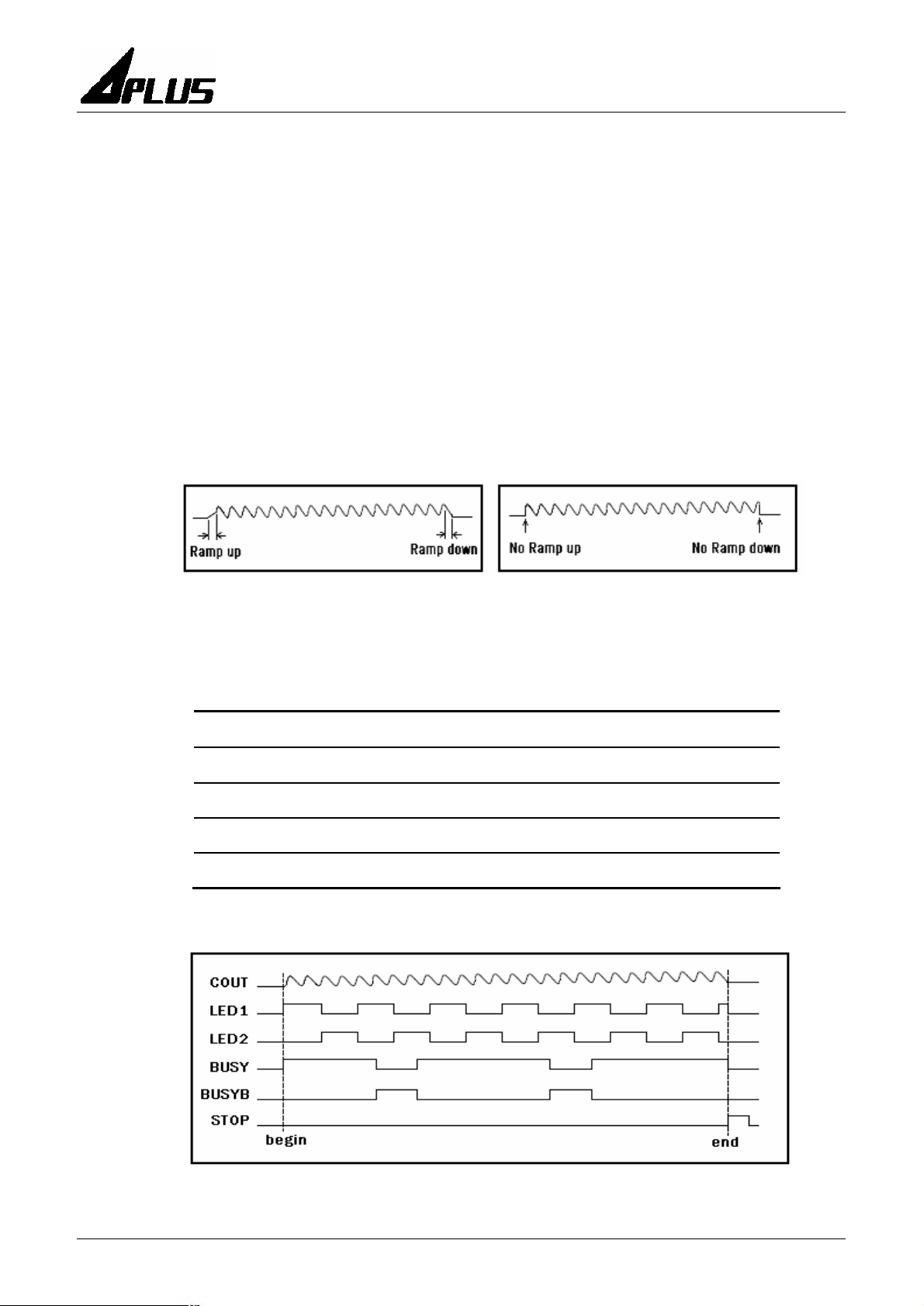

Whole Chip Options

• Long (16ms) or short (65us) debounce time at 8KHz sampling rate.

• Ramp-up-down enable or disable:

When COUT is used for playback, Ramp-up-down should be enabled. This function eliminates

the ‘POP’ noise at the begin and end of voice playback.

When VOUT1 and VOUT2 are used to drive speaker directly, Ramp-up-down should be

disabled.

Fig. 1 Ramp-up-down Enable Fig.2 Ramp-up-down Disable

• Output Options:

This option sets up the three output pins OUT1, OUT2 and OUT3 to send out different signals

during voice playback. Four settings are allowed:

Option 1 LED1 LED2 BUSY

Option 2 STOP LED1 LED2

Option 3 LED1 BUSY STOP

Option 4 LED1 BUSY BUSYB

Note: BUSY can be set or reset associated with each Voice Block. Stop plus must be set to

enable in order to have STOP plus to come out at the end of playback.

OUT1 OUT2 OUT3

Fig. 3 Output waveforms

Ver 2.1 5 Aug 24, 2006

Page 7

Integrated Circuits Inc. aP89341/170/085

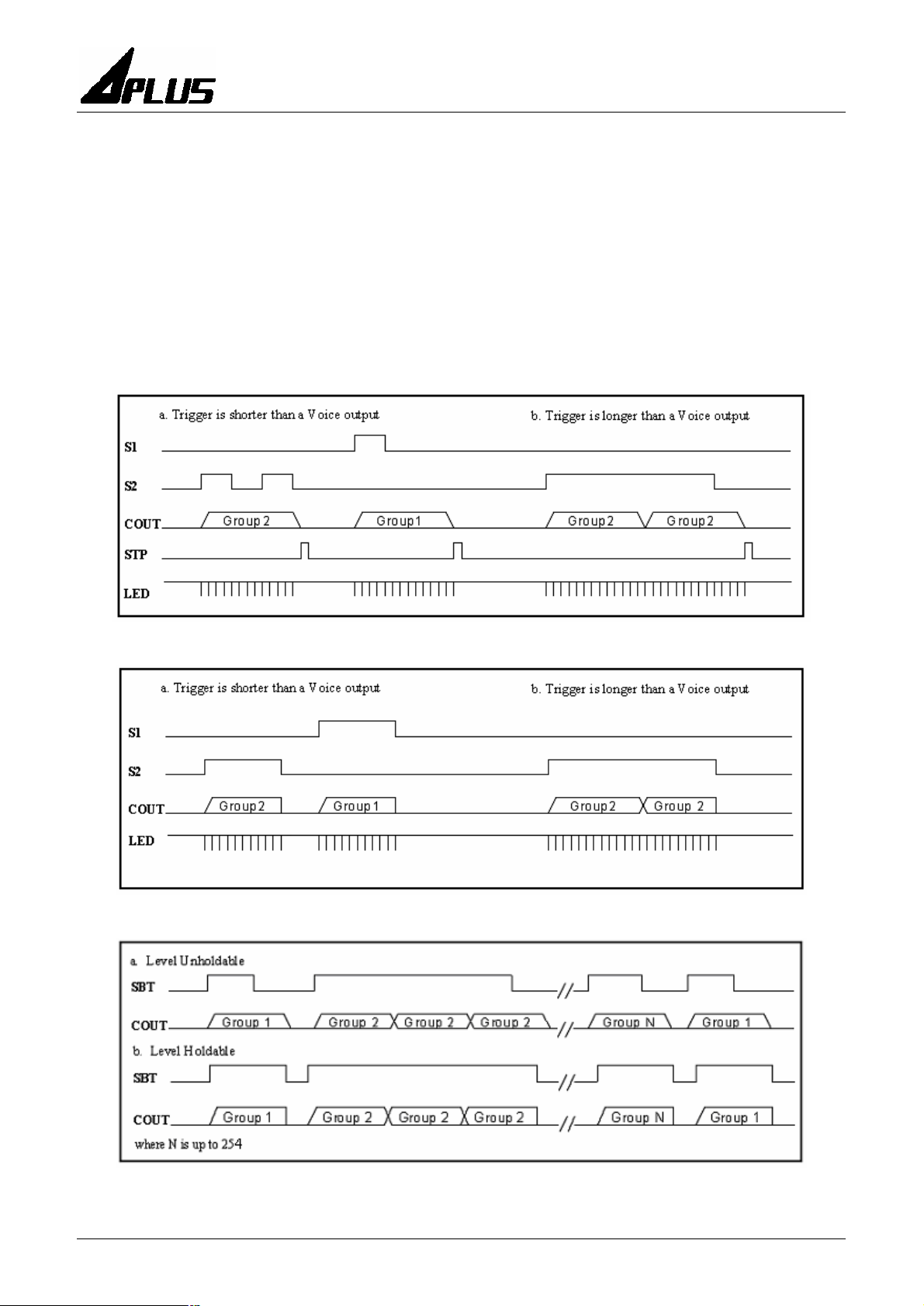

Group Options

User selectable options that affect each individual group are called Group Options. They are:

• Edge or Level trigger

• Unholdable or Holdable trigger

• Re-triggerable or non-retriggerable

• Stop pulse disable or enable

Fig. 4 to Fig. 9 show the voice playback with different combination of triggering mode and the

relationship between outputs and voice playback.

Fig. 4 Level, Unholdable, Non-retriggerable

Fig. 5 Level Holdable

Fig. 6 SBT sequential trigger with Level Holdable and Unholdable

Ver 2.1 6 Aug 24, 2006

Page 8

Integrated Circuits Inc. aP89341/170/085

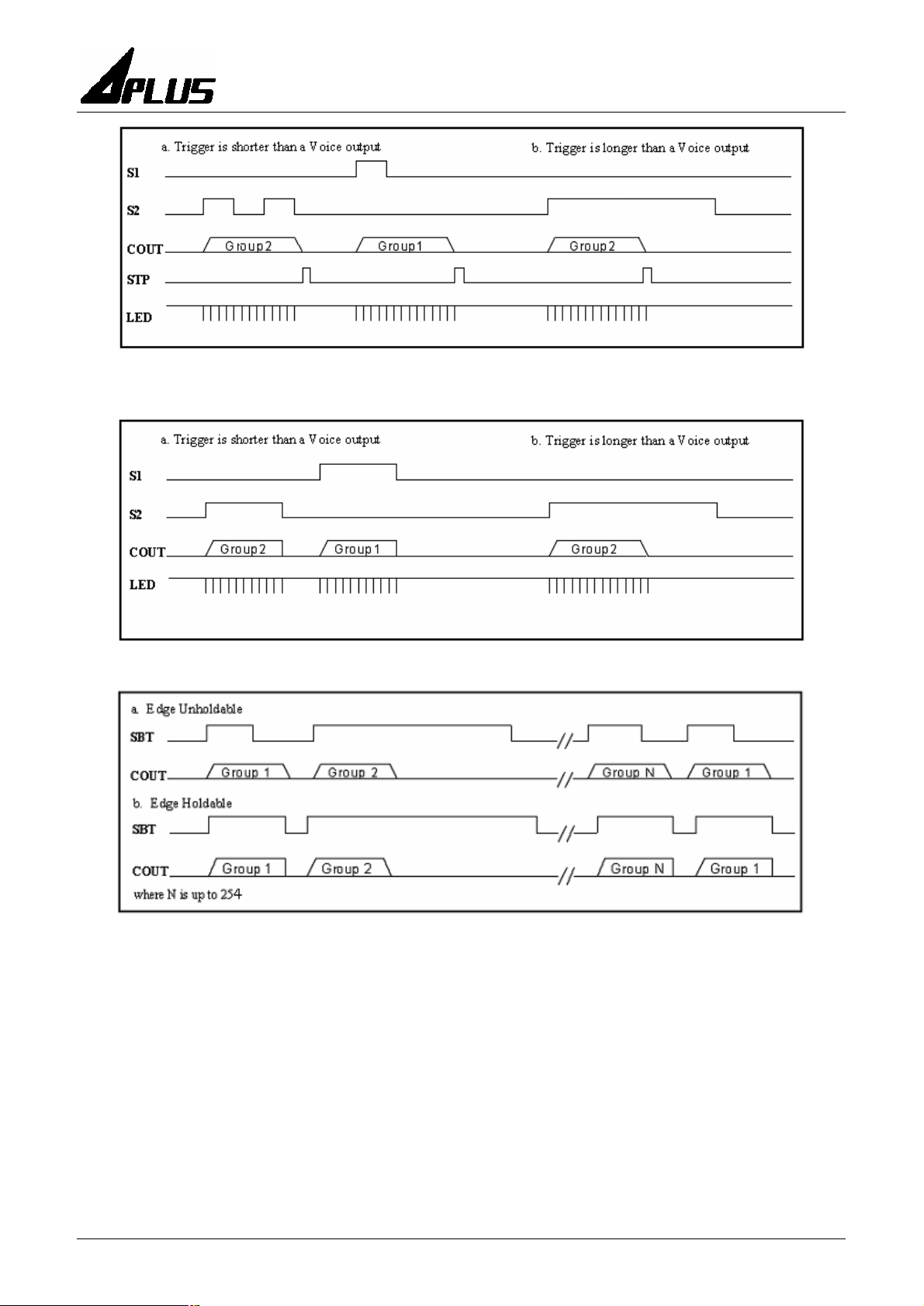

Fig. 7 Edge, Unholdable, Non-retrigger

Fig. 8 Edge, Holdable

Fig. 9 SBT sequential trigger with Edge Holdable and Unholdable

TRIGGER MODES

There are three trigger modes available for aP89341/170/085 series which are determined by setting

M1 and M2 pins to logic HIGH or LOW.

• Key Trigger Mode (M1=0; M0=0);

• CPU Parallel Trigger Mode (M1=0; M0=1);

• CPU Serial Command Mode (M1=1; M0=0);

Ver 2.1 7 Aug 24, 2006

Page 9

Integrated Circuits Inc. aP89341/170/085

Key Trigger Mode (M1=0, M0=0)

With this trigger mode, the beginning 32 Voice Groups are triggered by setting S1 to S8 to HIHG or

LOW in different combinations. Each Voice Group can have its only independent trigger options (See

Fig. 4, 5, 7 and 8 for trigger options definition).

A maximum of 254 Voice Groups are available. The 33rd to 254th Voice Groups can only be

triggered one by one sequentially with the SBT key (See Fig. 6 and 9).

The setting of S1 to S8 for triggering the 1st to the 32nd Voice Groups are as follow:

Voice

Group

1 HIGH NC NC NC NC NC NC NC

2 NC HIGH NC NC NC NC NC NC

3 NC NC HIGH NC NC NC NC NC

4 NC NC NC HIGH NC NC NC NC

5 NC NC NC NC HIGH NC NC NC

6 NC NC NC NC NC HIGH NC NC

7 NC NC NC NC NC NC HIGH NC

8 NC NC NC NC NC NC NC HIGH

9 HIGH HIGH NC NC NC NC NC NC

10 NC HIGH HIGH NC NC NC NC NC

11 NC NC HIGH HIGH NC NC NC NC

12 NC NC NC HIGH HIGH NC NC NC

13 NC NC NC NC HIGH HIGH NC NC

14 NC NC NC NC NC HIGH HIGH NC

15 NC NC NC NC NC NC HIGH HIGH

16 HIGH NC NC NC NC NC NC HIGH

17 HIGH HIGH HIGH NC NC NC NC NC

18 NC HIGH HIGH HIGH NC NC NC NC

19 NC NC HIGH HIGH HIGH NC NC NC

20 NC NC NC HIGH HIGH HIGH NC NC

21 NC NC NC NC HIGH HIGH HIGH NC

22 NC NC NC NC NC HIGH HIGH HIGH

23 HIGH NC NC NC NC NC HIGH HIGH

24 HIGH HIGH NC NC NC NC NC HIGH

25 HIGH HIGH HIGH HIGH NC NC NC NC

26 NC HIGH HIGH HIGH HIGH NC NC NC

27 NC NC HIGH HIGH HIGH HIGH NC NC

28 NC NC NC HIGH HIGH HIGH HIGH NC

29 NC NC NC NC HIGH HIGH HIGH HIGH

30 HIGH NC NC NC NC HIGH HIGH HIGH

31 HIGH HIGH NC NC NC NC HIGH HIGH

32 HIGH HIGH HIGH NC NC NC NC HIGH

Note: NC represents open or no connection

S1 S2 S3 S4 S5 S6 S7 S8

Ver 2.1 8 Aug 24, 2006

Page 10

Integrated Circuits Inc. aP89341/170/085

CPU Parallel Trigger Mode (M1=0, M0=1)

In this mode, S8 to S1 serve as 8-bit addresses input for 254 Voice Groups with S8 represents the

MSB and S1 represents LSB. After Group address is set and ready, setting the SBT input pin to HIGH

will trigger the corresponding Voice Group to playback.

Trigger options defined in Fig. 4, 5, 7 and 8 are valid for this mode.

Fig. 10 CPU Parallel Trigger Mode

Note that SBT pin cannot be used as Single Button Sequential trigger in this mode. In stead, it acts as

a Strobe input to clock-in the Voice Group address set at S8 to S1 into the chip.

Voice Groups are represented in Binary address format. For example:

S[8:1] = 0000 0000 (00hex) for Voice Group #1

S[8:1] = 0000 0001 (01hex) for Voice Group #2

• • •

S[8:1] = 0000 1000 (08 hex) for Voice Group #9

• • •

S[8:1] = 1000 1000 (88 hex) for Voice Group #137

• • •

S[8:1] = 1111 1101 (FD hex) for Voice Group #254

CPU Serial Command Mode (M1=1, M0=0)

This trigger mode is specially designed for simple CPU interface. The aP89341/170/085 is controlled

by command sent to it from the host CPU. S1 to S3 are used to input command word into the chip

while OUT1 to OUT3 as output from the chip to the host CPU for feedback response.

• S1 acts as CS (Chip Select) to initiate the command word input

• S2 acts as SCK (Serial Clock) to clock-in the command word at rising edge.

• S3 acts as DI (Data-In) to input the command bits.

• OUT1 acts as BUSY to indicate the chip is in busy state.

• OUT2 acts as POUT to output user selected information.

• OUT3 acts as FULL signal to indicate the Voice Group address buffer is full.

Command input into the chip may contains 8-bit or 16-bit data. The first 8-bit data is command bits

while the second 8-bit data (if any) is the Voice Group address data. Table 1 summarize the available

commands and their functions.

Ver 2.1 9 Aug 24, 2006

Page 11

Integrated Circuits Inc. aP89341/170/085

Command D7 D6 D5 D4 D3 D2 D1 D0

PUP1 (C5h) 1 1 0 0 0 1 0 1

PUP2 (8Dh) 1 0 0 0 1 1 0 1

PDN1

(E1h)

PDN2

(A9h)

PLAY

(55h)

STATUS

(E3h)

PAUSE

(39h)

RESUME

(1Dh)

PREFETCH

(71h)

1 1 1 0 0 0 0 1

1 0 1 0 1 0 0 1

0 1 0 1 0 1 0 1

G7 G6 G5 G4 G3 G2 G1 G0

1 1 1 0 0 0 1 1 Set output status for OUT2 pin

0 0 0 1 0 G2 G1 G0

0 0 1 1 1 0 0 1

0 0 0 1 1 1 0 1

0 1 1 1 0 0 0 1

G7 G6 G5 G4 G3 G2 G1 G0

Description

Power up the chip with NO ramp-up (suitable

for VOUT direct drive)

Power up the chip WITH ramp-up (suitable for

COUT transistor drive)

Power down the chip with NO ramp-down

(suitable for VOUT direct drive)

Power down the chip WITH ramp-down

(suitable for COUT transistor drive)

Playback the specified Voice Group

immediately

Voice Group address

(G7=MSB; G0=LSB)

OUT2 = BUSYB (000), 8K (001), 4K, 2K, 1K,

16Hz, 1M, EMPTY (FULLB)

Pause the playback and hold at current COUT

value

Resume playback from the previous COUT

value

Pre-load Voice Group address into buffer for

next playback

Voice Group address

(G7=MSB; G0=LSB)

• Power up with RAMP-UP (PU2-C5H) or without RAMP-UP (PU1-8DH)

Fig. 11 Power-up command timing

1. PU1 (C5H) will power-up the chip and set the COUT to 80H immediately and stay

there.

2. PU2 (8DH) will Ramp-up chip and ramp-up COUT from 00H to 80H and stay there.

3. Power-up will start after 350us (at 6KHz sampling rate).

4. Voice will be playback immediately after PU1 / PU2 completes if the section buffer

is filled with the PREFETCH command before power-up.

5. OUT1 (BUSY) will output logic HIGH during Ramp-up operation.

6. PDN2 (Power-down with ramp-down) will be executed correctly only if PU2 is

executed before.

Ver 2.1 10 Aug 24, 2006

Page 12

Integrated Circuits Inc. aP89341/170/085

• Power-down with RAMP-DOWN (PD2-A9H) or without RAMP-DOWN (PD1-E1H)

Fig. 12 Power-down commands timing

1. PDN1 will power-down the chip and set the COUT data to 00H immediately.

2. PDN2 will power-down the chip by Ramp-down the COUT from its current value to 00H.

3. Power-down will start after 350us (at 6KHz sampling rate).

4. The OUT1 pin (BUSY) will output logic HIGH during Ramp-down operation.

5. PDN2 (Power-down with ramp-down) will be executed correctly only if PU2 is

executed before.

• Playback Voice Group (PLAY-55H)

Fig. 13 Playback command timing

1. The 8-bit Voice Group address, G[0:7] follow immediately the 8-bit PLAY command.

2. Once the 16-bit command and address are clocked into the chip, the new voice group

address is loaded into the address buffer immediately and the voice group will be played

accordingly.

3. The OUT1 pin (BUSY) will stay at logic HIGH when the new voice group is played.

• Set OUT2 pin status (STATUS-E3H)

Fig. 14 Setup the status of programmable output pin, OUT2

Ver 2.1 11 Aug 24, 2006

Page 13

Integrated Circuits Inc. aP89341/170/085

1. Signal output from the pin, OUT2, is defined by G[3:0], as below:

G[3:0] OUT2 G[3:0] OUT2

000 BUSYB 100 1KHz

001 8KHz 101 16Hz

010 4KHz 110 1MHz

011 2KHz 111 FULLB

2. If the STATUS is not executed, default value of OUT2 is the internal Reset signal.

3. BUSYB is the logical inversion of BUSY.

4. EMPTY (or FULLB) is the logical inversion of FULL.

5. Only the 1MHz clock will not be stopped by the PAUSE command.

• Pause and Resume (PLAUS-39H; RESUME-1DH)

Fig. 15 Pause and Resume command timing

6. In Pause state, VOUT1 and VOUT2 will stay at logic LOW while the COUT will stay at

the current D/A data level (i.e. COUT is kept outputting an DC current). When Resume,

the COUT data will continue at the current D/A data level.

7. The Pause state will be released by PDN1, PDN2, PLAY and RESUME commands.

• Prefetch Voice Group Address (PREFETCH-71H)

Fig. 16 Prefetch next Voice Group timing

1. The PREFETCH command pre-load the next Voice Group Address into the address buffer.

2. The OUT3 output (FULL) will become logic HIHG once the Group Address is successfully

loaded.

3. The Voice Group will be played once the playing of the current Voice Group is finished.

4. The FULL signal will become logic LOW once the Voice Group is played and the address

buffer is released and ready for next PREFECT action.

5. Using the PREFECT make sure there is no gap between each Voice Group.

Ver 2.1 12 Aug 24, 2006

Page 14

Integrated Circuits Inc. aP89341/170/085

BLOCK DIAGRAM

Fig. 17 Block Diagram

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Unit

VDD - VSS -0.5 ~ +3.8 V

VIN V

V

V

OUT

T (Operating):

DIP

SOP

T (Junction) -40 ~ +125

T (Storage) -55 ~ +125

- 0.3<VIN<V

SS

SS <VOUT<VDD

-10 ~ +70

-40 ~ +85

+ 0.3 V

DD

V

℃

℃

℃

Ver 2.1 13 Aug 24, 2006

Page 15

Integrated Circuits Inc. aP89341/170/085

DC CHARACTERISTICS ( T

Symbol Parameter Min. Typ. Max.

VDD Operating Voltage 2.2 3.0 3.6 V

ISB Standby current

IOP Operating current

VIH "H" Input Voltage 2.5 3.0 3.5 V VDD=3.0V

VIL "L" Input Voltage -0.3 0 0.5 V VDD=3.0V

IOL V

IOH V

ICO C

IOH O/P high Current

IOL O/P low Current

low O/P Current

OUT

high O/P Current

OUT

O/P Current

OUT

= 0 to 70℃, VDD = 3.3V, VSS = 0V )

A

Unit Condition

1 5 μA

120

-65

-3

-8

8

15 mA

mA

mA

mA

mA

mA

I/O open

I/O open

Vout=0.3V

Vout=2.5V

V

VOH=2.5V

VOL=0.3V

COUT

=1.0V

∆F/F

Frequency Stability -5

Fosc(3.4V) - Fosc(2.7V)

+5 % Fosc(3V)

Ver 2.1 14 Aug 24, 2006

Page 16

Integrated Circuits Inc. aP89341/170/085

tBH

TIMING WAVEFORMS

KEY Trigger Mode

tKD

S1~S8, SBT

COUT

tSTPD

STOP

BUSY

tBD

CPU Parallel Mode

Addr.

S1~S8

SBT

tAS

tSBTW

CPU Serial Command Mode

tCS

S1(CS)

S3(DI)

S2(SCK)

COUT

BUSY

FULL

tDH

tDS

tAH

tSCKW

tSCKC

Fig. 18 Timing Waveform

tSTPW

tBH

tCH

tCOUTD

tBD

tFD

Ver 2.1 15 Aug 24, 2006

Page 17

Integrated Circuits Inc. aP89341/170/085

AC CHARACTERISTICS ( T

= 0 to 70℃, VDD = 3.3V, VSS = 0V, 8KHz sampling )

A

Symbol Parameter Min. Typ. Max.

tKD Key trigger debounce time (long) 16

tKD Key trigger debounce time (long) –

retrigger option

tKD Key trigger debounce time (short) 65

tKD Key trigger debounce time (short) –

retrigger option

t

t

tBD BUSY signal output delay time

tBH BUSY signal output hold time

STOP pulse output delay time

STPD

STOP pulse width

STPW

24

200

64

100

Unit Note

ms

ms

μs

μs

256 μs

100 ns

ms

ns

1,2

1,2

1,2

1,2

1

tAS Address set-up time 100

tAH Address hold time 100

t

SBTW

t

SBTW

tCS Chip select set-up time 100

tCH Chip select hold time 100

tDS Data-in set-up time 100

tDH Data-in hold time 100

t

SCKW

t

SCKC

t

COUTD

SBT stroke pulse width (long) 16

SBT stroke pulse width (short) 65

Serial clock pulse width 1

Serial clock cycle time 2

COUT output delay time

256 μs

ns

ns

ms

μs

ns

ns

ns

ns

μs

μs

1,2

1,2

tFD FULL signal output delay time

t

LED flash frequency

LEDC

100

3

ns

Hz

3

Notes :

1. This parameter is inversely proportional to the sampling frequency.

2. The long or short debounce time is selectable as whole chip option during Voice Files Compiling.

3. This parameter is proportional to the sampling frequency.

Ver 2.1 16 Aug 24, 2006

Page 18

Integrated Circuits Inc. aP89341/170/085

OSCILLATOR RESISTANCE TABLE

Sampling Frequency

R

OSC

KHz KOhm

4.90

5.26

5.88

300

290

280

6.09 270 110 13.33

6.33 260 100 14.51

6.67 250 91 15.63

6.85 240 82 16.95

7.14 230 75 18.18

7.46 220 68 19.23

7.70 210 62 20.83

8.06 200 56 22.22

8.47 190 51 23.81

8.93 180 43 25.00

9.26 170

9.80 160

10.42 150

Note: The data in the above tables are within 3% accuracy and measured at VDD = 3.0V. Oscillator frequency is

subjected to IC lot to lot variation.

R

OSC

KOhm KHz

Sampling Frequency

140 11.00

130 11.76

120 12.50

Ver 2.1 17 Aug 24, 2006

Page 19

Integrated Circuits Inc. aP89341/170/085

S1 S2 S3 S8

•

•

•

•

•

•

S1 S2 S3 S8

• •

•

•

•

•

TYPICAL APPLICATIONS

Key Trigger Mode

0.01uF

0.1uF

8Ω

Speaker

VDD, AVDD,VPP

ROSC

RST

OSC

COUT

8050D

390Ω

3.3V

SBT

VOUT1

VOUT2

OUT1

8 / 16Ω

Speaker

VSS, AVSS

Fig. 22 Using 3.3V Battery

4.5V

HT7335

ROSC

Output driving of HT LDO:

HT7136 (30mA, 3.6V)

HT7133 (30mA, 3.3V)

HT7536 (100mA, 3.6V)

HT7335 (250mA, 3.5V)

Fig. 23 Using 4.5V Battery

0.01uF

VDD, AVDD,VPP

RST

OSC

SBT

VSS, AVSS

COUT

VOUT1

VOUT2

OUT1

10uF

8 / 16Ω

Speaker

8Ω

Speaker

8050D

Ver 2.1 18 Aug 24, 2006

Page 20

Integrated Circuits Inc. aP89341/170/085

S8

S1 S2 S3

• •

•

•

•

•

•

•

•

CPU Parallel Mode

VIN=+5V

HT7335

VOUT=+3.5V

ROSC

0.01uF

VDD, AVDD,VPP

10uF

8Ω

Speaker

MCU

Addr[0]

Addr[1]

Addr[2]

Addr[7]

I[0..2]

Rin

Rin = 860KΩ x (VIN-VOUT) / VIN

Fig. 24 5V CPU Control with COUT

3

RST

OSC

OUT[1..3]

VSS, AVSS

COUT

8050D

Ver 2.1 19 Aug 24, 2006

Page 21

Integrated Circuits Inc. aP89341/170/085

DI

2 7

8 6

5 4

+ + - -

3

CPU Serial Command Mode

VIN=+5V

VOUT=+3.5V

HT7335

0.01uF

10uF

ROSC

CS

SCK

MCU

Rin

BUSY

FULL

Rin = 860KΩ x (VIN-VOUT) / VIN

Fig. 25 5V CPU Control with TDA Power Amplifier

VDD, AVDD,VPP

RST

OSC

S1 (CS)

S2 (SCK)

S3 (DI)

OUT1

OUT3

VSS, AVSS

COUT

10uF

33Ω

10KΩ

10u

0.01uF

TDA2822M

Vcc

Gnd

8Ω

Speaker

1

0.1u

0.1u

4.7Ω

4.7Ω

Ver 2.1 20 Aug 24, 2006

Page 22

Integrated Circuits Inc. aP89341/170/085

BONDING PAD DIAGRAMS

aP89341

Notes:

1. Two VPP pads should be connected to the Positive Power Supply during voice playback.

2. VDD and AVDD should be connected to the Positive Power Supply.

3. VSS and AVSS should be connected to the Power GND.

4. Substrate should be connected to the Power GND.

Ver 2.1 21 Aug 24, 2006

Page 23

Integrated Circuits Inc. aP89341/170/085

aP89170

aP89085

Notes:

5. VPP and VSL pads should be connected to the Positive Power Supply during voice playback.

6. VDD and AVDD should be connected to the Positive Power Supply.

7. VSS and AVSS should be connected to the Power GND.

8. Substrate should be connected to the Power GND.

Ver 2.1 22 Aug 24, 2006

Page 24

Integrated Circuits Inc. aP89341/170/085

PACKAGES DIMENSION OUTLINES

24-Pin 300mil P-DIP Package

28-Pin 300mil SOP Package

Ver 2.1 23 Aug 24, 2006

Loading...

Loading...