Page 1

ADC1001 10-Bit mP Compatible A/D Converter

ADC1001 10-Bit mP Compatible A/D Converter

December 1994

General Description

The ADC1001 is a CMOS, 10-bit successive approximation

A/D converter. The 20-pin ADC1001 is pin compatible with

the ADC0801 8-bit A/D family. The 10-bit data word is read

in two 8-bit bytes, formatted left justified and high byte first.

The six least significant bits of the second byte are set to

zero, as is proper for a 16-bit word.

Differential inputs provide low frequency input common

mode rejection and allow offsetting the analog range of the

converter. In addition, the reference input can be adjusted

enabling the conversion of reduced analog ranges with 10bit resolution.

Features

Y

ADC1001 is pin compatible with ADC0801 series 8-bit

A/D converters

Y

Compatible with NSC800 and 8080 mP derivativesÐno

interfacing logic needed

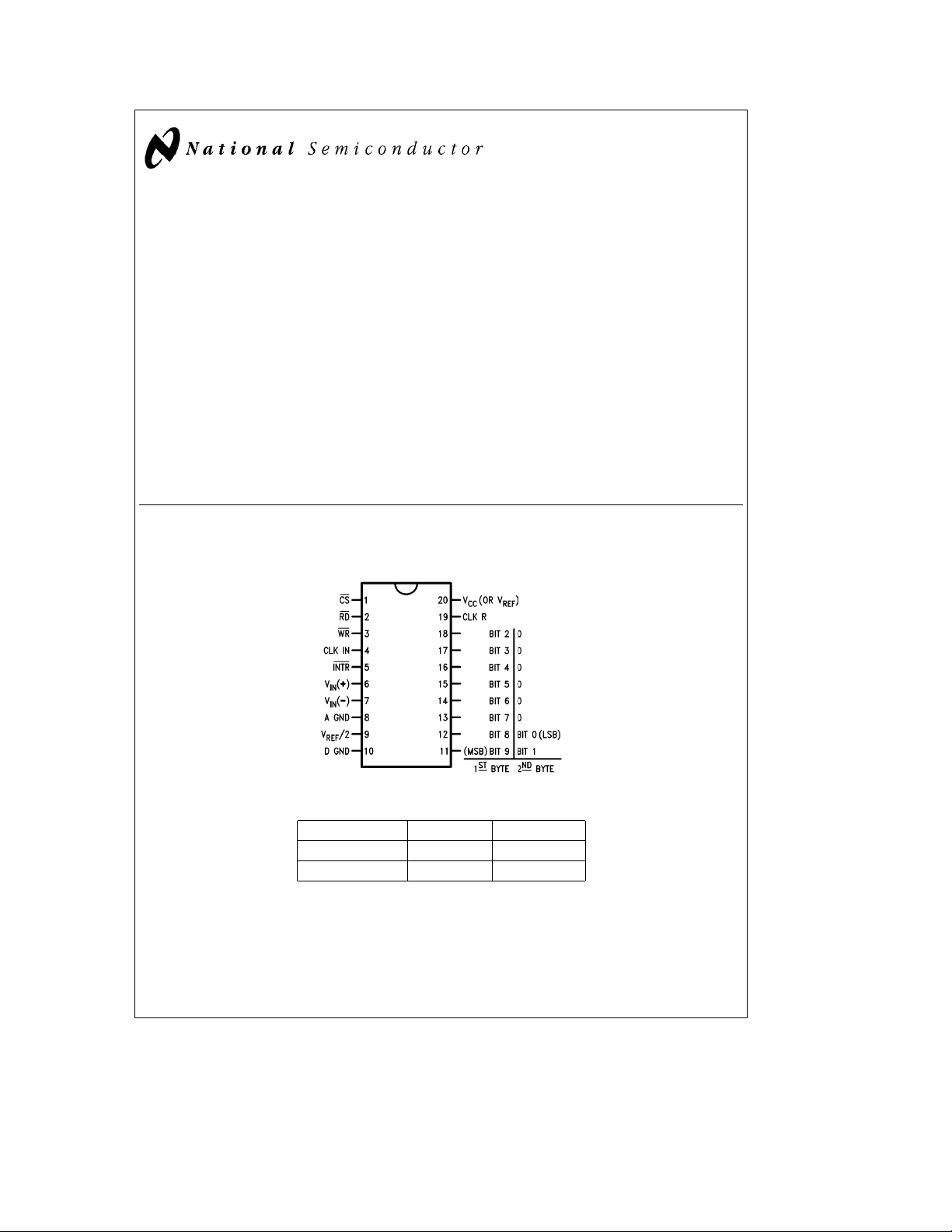

Connection Diagram

ADC1001 (for an 8-bit data bus)

Dual-In-Line Package

Y

Easily interfaced to 6800 mP derivatives with minimal

external logic

Y

Differential analog voltage inputs

Y

Logic inputs and outputs meet both MOS and TTL voltage level specifications

Y

Works with 2.5V (LM336) voltage reference

Y

On-chip clock generator

Y

0V to 5V analog input voltage range with single 5V supply

Y

Operates ratiometrically or with 5 VDC, 2.5 VDC, or analog span adjusted voltage reference

Y

0.3×standard width 20-pin DIP package

Key Specifications

Y

Resolution 10 bits

Y

Linearity error

Y

Conversion time 200mS

g

1 LSB

Top View

TL/H/5675– 11

Ordering Information

Temperature Range 0§Ctoa70§Cb40§Ctoa85§C

Order Number ADC1001CCJ-1 ADC1001CCJ

Package Outline J20A J20A

TRI-STATEÉis a registered trademark of National Semiconductor Corp.

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

TL/H/5675

Page 2

Absolute Maximum Ratings (Notes1&2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (V

Logic Control Inputs

Voltage at Other Inputs and Outputs

Storage Temperature Range

Package Dissipation at T

Lead Temp. (Soldering, 10 seconds) 300§C

ESD Susceptibility (Note 10) 800V

) (Note 3) 6.5V

CC

e

25§C 875 mW

A

b

b

0.3V to (V

b

65§Ctoa150§C

0.3V toa18V

CC

a

0.3V)

Operating Conditions (Notes1&2)

Temperature Range T

ADC1001CCJ

ADC1001CCJ-1 0§CsT

Range of V

CC

s

MIN

b

40§CsT

4.5 VDCto 6.3 V

s

T

T

A

MAX

s

a

85§C

A

s

a

70§C

A

DC

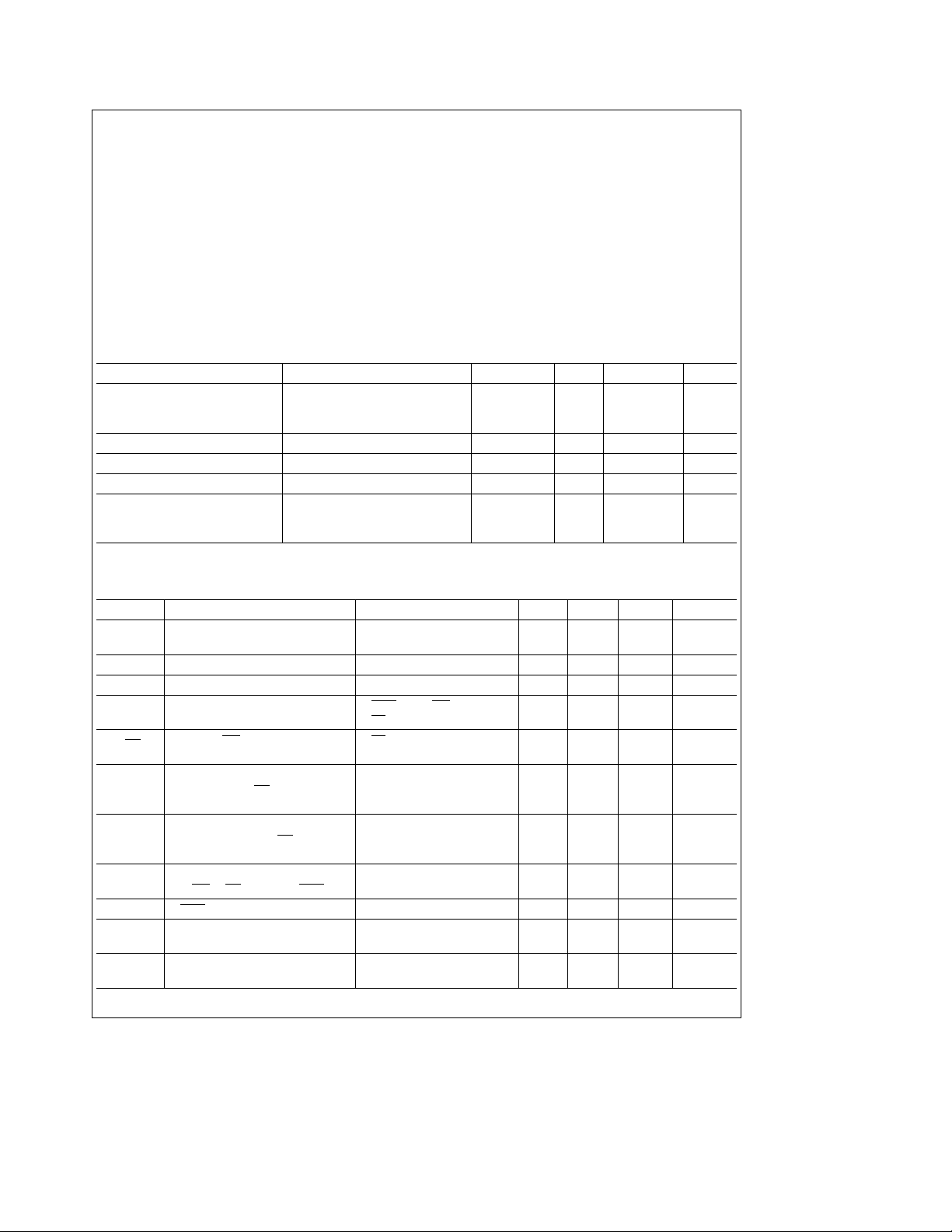

Converter Characteristics

s

Converter Specifications: V

CC

e

5VDC,V

/2e2.500 VDC,T

REF

MIN

s

T

T

A

MAX

and f

e

410 kHz unless otherwise specified.

CLK

Parameter Conditions MIn Typ Max Units

Linearity Error

Zero Error

Full-Scale Error

g

1 LSB

g

2 LSB

g

2 LSB

Total Ladder Resistance (Note 9) Input Resistance at Pin 9 2.2 4.8 KX

Analog Input Voltage Range (Note 4) V(a)orV(b) GNDb0.05 V

DC Common-Mode Error Over Analog Input Voltage Range

e

Power Supply Sensitivity V

CC

Allowed V

Voltage Range (Note 4)

g

5V

DC

(a) and VIN(b)

IN

5% Over

g

(/8 LSB

g

(/8 LSB

CC

a

0.05 V

DC

AC Electrical Characteristics

Timing Specifications: V

e

5VDCand T

CC

Symbol Parameter Conditions MIn Typ Max Units

T

f

c

CLK

Conversion Time (Note 5) 80 90 1/f

Clock Frequency (Note 8) 100 1260 kHz

Clock Duty Cycle 40 60 %

CR Conversion Rate In Free-Running INTR tied to WR with 4600 conv/s

Mode CSe0VDC,f

t

W(WR)L

t

ACC

Width of WR Input (Start Pulse CSe0VDC(Note 6) 150 ns

Width)

Access Time (Delay from C

Falling Edge of RD

to Output

Data Valid)

t1H,t

TRI-STATEÉControl (Delay C

0H

from Rising Edge of RD

Hi-Z State) Circuits)

tWI,t

t

1rs

C

IN

C

OUT

Delay from Falling Edge 300 450 ns

RI

of WR

or RD to Reset of INTR

INTR to 1st Read Set-Up Time 550 400 ns

Input Capacitance of Logic 5 7.5 pF

Control Inputs

TRI-STATE Output 5 7.5 pF

Capacitance (Data Buffers)

e

25§C unless otherwise specified.

A

e

f

410 kHz 195 220 ms

CLK

e

410 kHz

CLK

e

100 pF 170 300 ns

L

e

10 pF, R

to (See TRI-STATE Test

L

e

10k 125 200 ns

L

CLK

2

Page 3

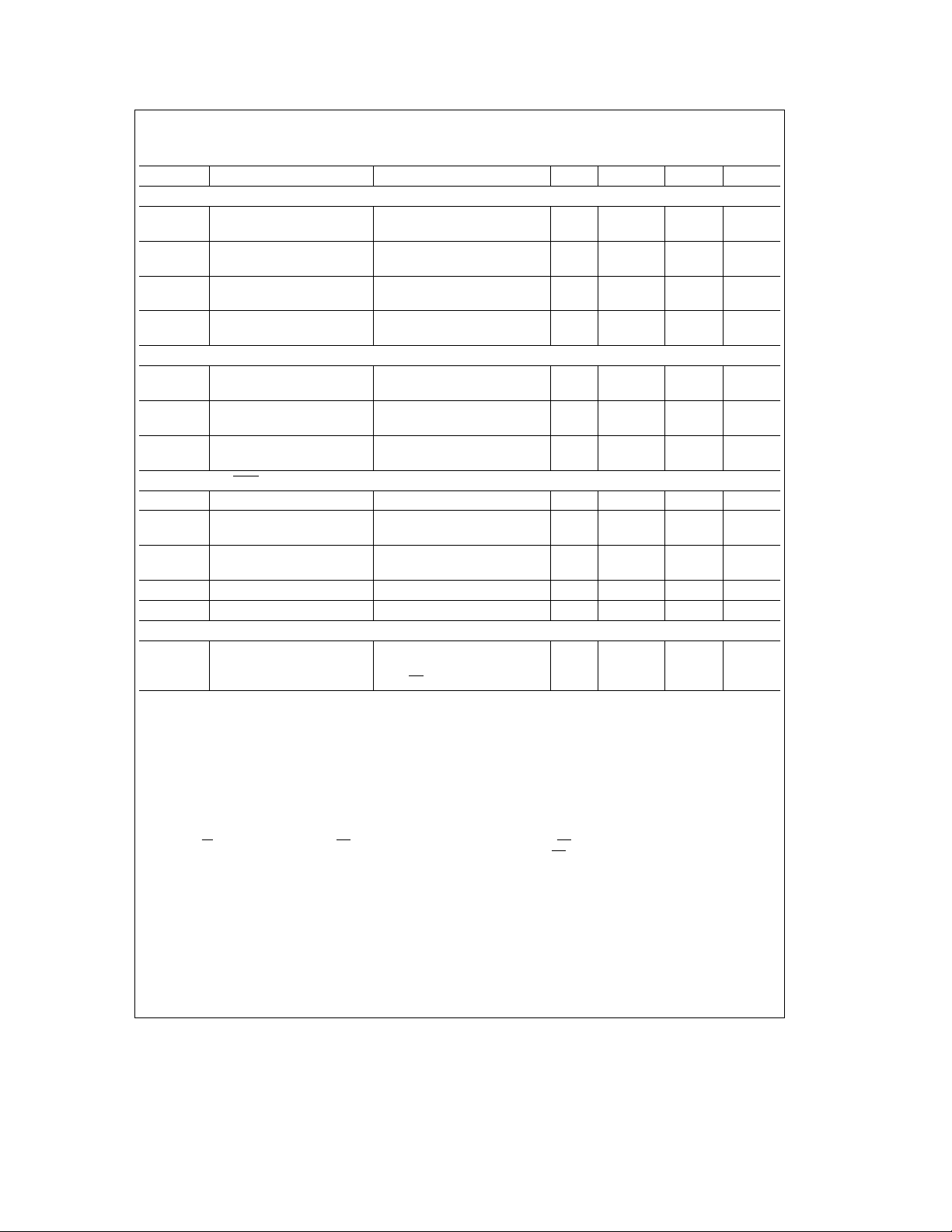

DC Electrical Characteristics

s

The following specifications apply for V

e

5VDCand T

CC

Symbol Parameter Conditions MIn Typ Max Units

CONTROL INPUTS[Note: CLK IN is the input of a Schmitt trigger circuit and is therefore specified separately

VIN(1) Logical ‘‘1’’ Input Voltage V

(Except CLK IN)

VIN(0) Logical ‘‘0’’ Input Voltage V

(Except CLK IN)

IIN(1) Logical ‘‘1’’ Input Current V

(All Inputs)

IIN(0) Logical ‘‘0’’ input Current V

(All Inputs)

CC

CC

IN

IN

e

e

e

e

5.25 V

4.75 V

5V

0V

CLOCK IN

a

V

T

b

V

T

V

H

CLK IN Positive Going 2.7 3.1 3.5 V

Threshold Voltage

CLK IN Negative Going 1.5 1.8 2.1 V

Threshold Voltage

CLK IN Hysteresis 0.6 1.3 2.0 V

a)b

(V

T

b

(V

)

T

OUTPUTS AND INTR

V

(0) Logical ‘‘0’’ Output Voltage I

OUT

V

(1) Logical ‘‘1’’ Output Voltage I

OUT

I

OUT

I

SOURCE

I

SINK

TRI-STATE Disabled Output V

Leakage (All Data Buffers) V

e

1.6 mA, V

OUT

eb

360 mA, V

O

eb

I

10 mA, V

O

e

OUT

e

OUT

V

Short to GND, T

OUT

V

Short to VCC,T

OUT

POWER SUPPLY

I

CC

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified. The separate A GND point should always be wired to the D GND.

Note 3: A zener diode exists, internally, from V

Note 4: For V

conduct for analog input voltages one diode drop below ground or one diode drop greater than the V

as high level analog inputs (5V) can cause this input diode to conductÐespecially at elevated temperatures, and cause errors for analog inputs near fullscale. The

spec allows 50 mV forward bias of either diode. This means that as long as the analog V

code will be correct. To achieve an absolute 0 V

variations, initial tolerance and loading.

Note 5: With an asynchronous start pulse, up to 8 clock periods may be required before the internal clock phases are proper to start the conversion process. The

start request is internally latched, see

Note 6: The CS

the converter in a reset mode and the start of conversion is initiated by the low to high transition of the WR

Note 7: All typical values are for T

Note 8: Accuracy is guaranteed at f

Note 9: The V

of these two equal resistors.

Note 10: Human body model, 100 pF discharged through a 1.5 kX resistor.

Supply Current (Includes f

Ladder Current) V

to GND and has a typical breakdown voltage of 7 VDC.

(b)tVIN(a) the digital output code will be all zeros. Two on-chip diodes are tied to each analog input (see Block Diagram) which will forward

IN

input is assumed to bracket the WR strobe input and therefore timing is dependent on the WR pulse width. An arbitrarily wide pulse width will hold

A

pin is the center point of a two resistor divider (each resistor is 2.4kX) connected from VCCto ground. Total ladder input resistance is the sum

REF/2

CC

to5VDCinput voltage range will therefore require a minimum supply voltage of 4.950 VDCover temperature

DC

Figure 1

.

e

25§C.

e

410 kHz. At higher clock frequencies accuracy can degrade.

CLK

e

CLK

REF

and CS

410 kHz,

/2eNC, T

s

T

T

MIN

, unless otherwise specified.

A

MAX

]

DC

DC

DC

DC

e

4.75 V

CC

e

4.75 V

CC

e

4.75 V

CC

0.4 V

DC

5V

DC

A

e

1 2.5 5.0 mA

DC

e

25§C 4.5 6 mA

A

e

25§C 9.0 16 mA

A

e

25§C

does not exceed the supply voltage by more than 50 mV, the output

IN

2.0 15 V

0.8 V

0.005 1 mA

b

b

1

DC

2.4 V

DC

4.5 V

0.005 mA

0.4 V

0.1

b

100 mA

0.1 3 mA

supply. Be careful, during testing at low VCClevels (4.5V),

CC

pulse (see Timing Diagrams).

DC

DC

DC

DC

DC

DC

DC

DC

DC

DC

DC

DC

DC

DC

3

Page 4

Typical Performance Characteristics

Delay From Falling Edge of

Logic Input Threshold

Voltage vs Supply Voltage

RD

to Output Data Valid

vs Load Capacitance

Output Current vs

Temperature

CLK IN Schmitt Trip Levels

vs Supply Voltage

TRI-STATE Test Circuits and Waveforms

TL/H/5675– 3

TL/H/5675– 5

4

t1H,C

t

t0H,C

t

TL/H/5675– 2

e

10 pF

L

e

20 ns

r

e

10 pF

L

e

20 ns

r

TL/H/5675– 4

TL/H/5675– 6

Page 5

Timing Diagrams

TL/H/5675– 7

Output Enable and Reset INTR

Note: All timing is measured from the 50% voltage points.

BYTE SEQUENCING FOR THE 20-PIN ADC1001

Byte 8-Bit Data Bus Connection

Order

MSB

1st Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2

2nd Bit 1 Bit 0 0 0 0 0 0 0

TL/H/5675– 8

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

LSB

5

Page 6

Functional Description

The ADC1001 uses an advanced potentiometric resistive

ladder network. The analog inputs, as well as the taps of

this ladder network, are switched into a weighted capacitor

array. The output of this capacitor array is the input to a

sampled data comparator. This comparator allows the successive approximation logic to match the analog difference

input voltage[V

The most significant bit is tested first and after 10 comparisons (80 clock cycles) a digital 10-bit binary code (all

e

‘‘1’’s

full-scale) is transferred to an output latch and then

an interrupt is asserted (INTR

sition). The device may be operated in the free-running

mode by connecting INTR

ensure start-up under all possible conditions, an external

WR

pulse is required during the first power-up cycle. A conversion in process can be interrupted by issuing a second

start command.

On the high-to-low transition of the WR

SAR latches and the shift register stages are reset. As long

as the CS

main in a reset state.

periods after at least one of these inputs makes a low-tohigh transition.

A functional diagram of the A/D converter is shown in

ure 1

. All of the inputs and outputs are shown and the major

logic control paths are drawn in heavier weight lines.

The conversion is initialized by taking CS

neously low. This sets the start flip-flop (F/F) and the resulting ‘‘1’’ level resets the 8-bit shift register, resets the Interrupt (INTR) F/F and inputs a ‘‘1’’ to the D flop, F/F1, which

is at the input end of the 10-bit shift register. Internal clock

signals then transfer this ‘‘1’’ to the Q output of F/F1. The

AND gate, G1, combines this ‘‘1’’ output with a clock signal

to provide a reset signal to the start F/F. If the set signal is

no longer present (either WR

reset and the 10-bit shift register then can have the ‘‘1’’

(a)bVIN(b)]to taps on the R network.

IN

makes a high-to-low tran-

to the WR inut with CSe0. To

input the internal

input and WR input remain low, the A/D will re-

Conversion will start from 1 to 8 clock

Fig-

and WR simulta-

or CS is a ‘‘1’’) the start F/F is

clocked in, which allows the conversion process to continue. If the set signal were to still be present, this reset pulse

would have no effect and the 10-bit shift register would continue to be held in the reset mode. This logic therefore allows for wide CS

and WR signals and the converter will start

after at least one of these signals returns high and the internal clocks again provide a reset signal for the start F/F.

After the ‘‘1’’ is clocked through the 10-bit shift register

(which completes the SAR search) it causes the new digital

word to transfer to the TRI-STATE output latches. When

this XFER signal makes a high-to-low transition the one

shot fires, setting the INTR F/F. An inverting buffer then

supplies the INTR

output signal.

Note that this SET control of the INTR F/F remains low for

aproximately 400 ns. If the data output is continuously enabled (CS

and RD both held low), the INTR output will still

signal the end of the conversion (by a high-to-low transition), because the SET

input can control the Q output of

the INTR F/F even though the RESET input is constantly at

a ‘‘1’’ level. This INTR

duration of the SET

output will therefore stay low for the

signal.

When data is to be read, the combination of both CS and

RD

being low will cause the INTR F/F to be reset and the

TRI-STATE output latches will be enabled.

Zero and Full-Scale Adjustment

Zero error can be adjusted as shown in

forced to

a

2.5 mV (a(/2 LSB) and the potentiometer is

Figure 2

.VIN(a)is

adjusted until the digital output code changes from 00 0000

0000 to 00 0000 0001.

Full-scale is adjusted as shown in

input. With V

less 1(/2 LSBs (V

the digital output code changes from 11 1111 1110 to 11

(a) forced to the desired full-scale voltage

IN

b

1(/2 LSBs), V

FS

Figure 3

, with the V

/2 is adjusted until

REF

REF

1111 1111.

/2

NOTE: VIN(b) should be biased so

t

b

(b)

that V

wiper is set at most negative

voltage position.

0.05V when potentiometer

IN

FIGURE 2. Zero Adjust Circuit

TL/H/5675– 9

TL/H/5675– 10

FIGURE 3. Full-Scale Adjust

6

Page 7

Typical Application

Block Diagram

TL/H/5675– 1

Note 1: CS shown twice for clarity. TL/H/5675– 13

Note 2: SAReSuccessive Approximation Register. FIGURE 1

7

Page 8

Physical Dimensions inches (millimeters)

Cavity Dual-In-Line Package (J) (Side Brazed)

Order Number ADC1001CCJ or ADC1001CCJ-1

ADC1001 10-Bit mP Compatible A/D Converter

NS Package Number J20A

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant support device or system whose failure to perform can

into the body, or (b) support or sustain life, and whose be reasonably expected to cause the failure of the life

failure to perform, when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can effectiveness.

be reasonably expected to result in a significant injury

to the user.

National Semiconductor National Semiconductor National Semiconductor National Semiconductor

Corporation Europe Hong Kong Ltd. Japan Ltd.

1111 West Bardin Road Fax: (

Arlington, TX 76017 Email: cnjwge@tevm2.nsc.com Ocean Centre, 5 Canton Rd. Fax: 81-043-299-2408

Tel: 1(800) 272-9959 Deutsch Tel: (

Fax: 1(800) 737-7018 English Tel: (

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Fran3ais Tel: (

Italiano Tel: (

a

49) 0-180-530 85 86 13th Floor, Straight Block, Tel: 81-043-299-2309

a

49) 0-180-530 85 85 Tsimshatsui, Kowloon

a

49) 0-180-532 78 32 Hong Kong

a

49) 0-180-532 93 58 Tel: (852) 2737-1600

a

49) 0-180-534 16 80 Fax: (852) 2736-9960

Loading...

Loading...