Page 1

71M6541D/71M6541F/71M6542F

Energy Meter ICs

A Maxim Integrated Product s Brand

MPU

RTC

TIMERS

IAP

VA

IBP

XIN

XOUT

RX

TX

TX

RX

COM0...5

V3P3A V3P3SYS

VBAT

VBAT_RTC

SEG

GNDA GNDD

SEG/DIO

DIO

ICE

LINE

NEUTRAL

LOAD

8888.8888

PULSES,

DIO

IR

AMR

POWER FAULT

COMPARATOR

MODUL-

ATOR

SERIAL PORTS

OSCILLATOR/

PLL

MUX and ADC

LCD DRIVER

DIO, PULSES

COMPUTE

ENGINE

FLASH

MEMORY

RAM

32 kHz

REGULATOR

Shunt

POWER SUPPLY

TERIDIAN

71M6541D/F

TEMPERATURE

SENSOR

VREF

BATTERY

PWR MODE

CONTROL

WAKE-UP

NEUTRAL

I2C or µWire

EEPROM

IAN

IBN

RTC

BATTERY

V3P3D

BATTERY

MONITOR

SPI INTERFACE

HOST

LCD DISPLAY

Resistor Divider

Pulse

Transformer

TERIDIAN

71M6xx1

Shunt

LINE

LINE

Note:

This system is referenced to LINE

11/5/2010

19-5376; Rev 1.1; 4/11

Single Conv ert er Technology is a regis t er ed trade ma rk of Maxim Integrated

April 2011

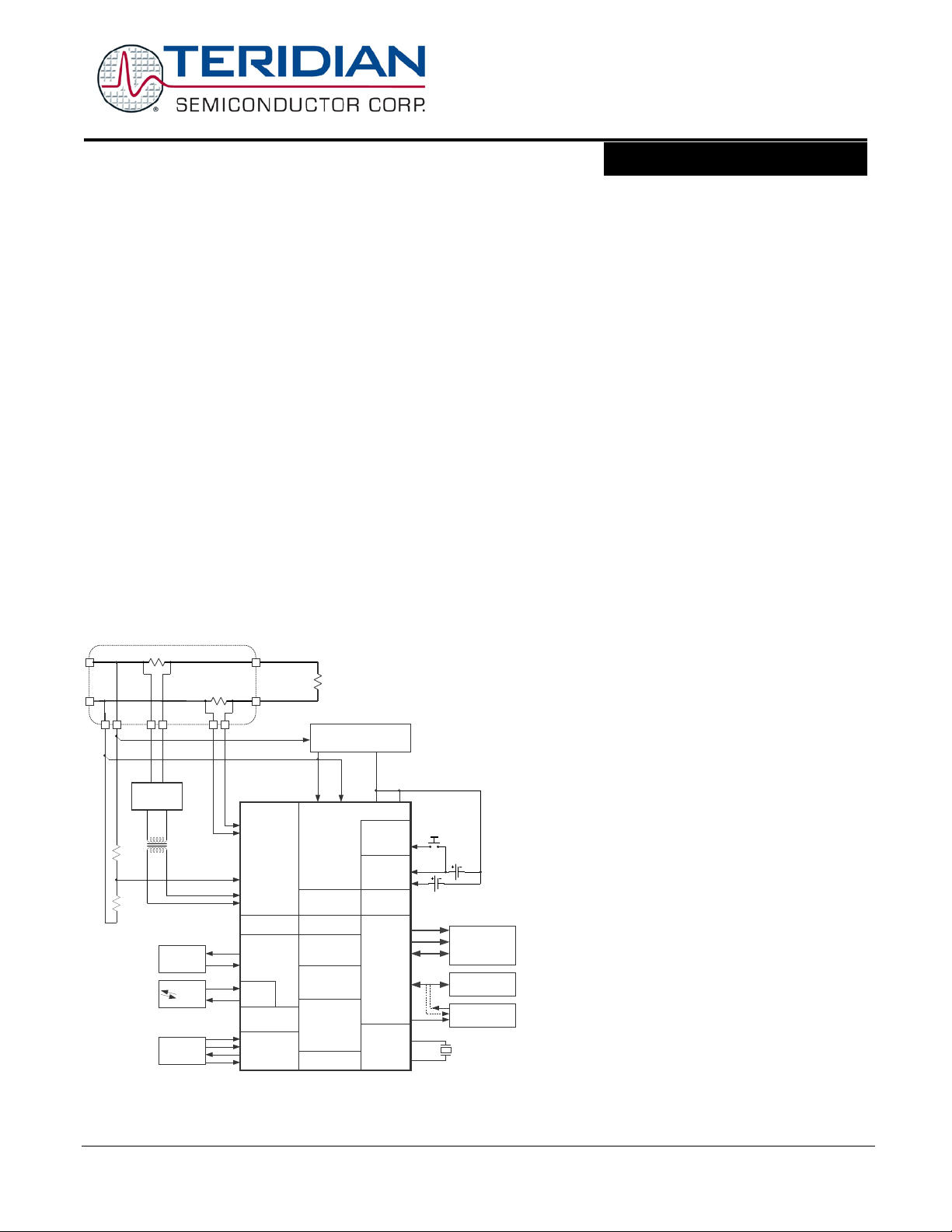

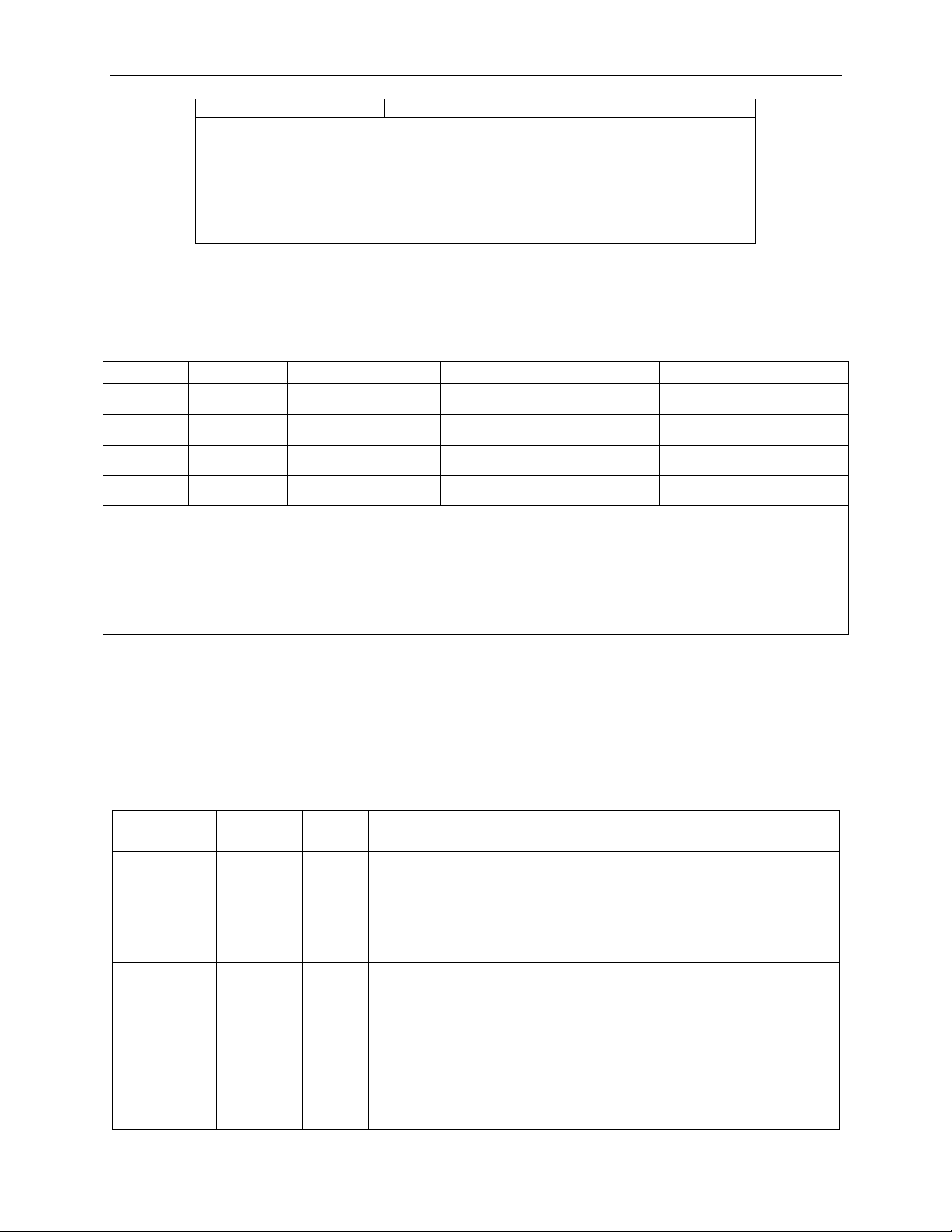

GENERAL DESCRIPTION

The 71M6541D/71M6541F/71M6542F are Teridian’s 4t h-generation

single-phase m etering SoC s with a 5 MHz 8051 -compatible MPU core,

low-power RTC wi th digital temperat ure compensation, fl ash memory,

and LCD driver. Our Single Converter Technology® with a 22-bit deltasigma ADC, three or four analog inputs, digital temperature compensation, precision voltage reference, and a 32-bit computation

engine (CE) supports a wide range of metering applications with

very few external components.

The 71M6541D/71M6541F/71M6542F support optional interfaces to

the Teridian 71M6x01 series of isolated sensors, w hich offer BOM

cost reduction, immunity to magnetic tamper, and enhanced

reliability. Other features include an SPI™ interface, advanced

power management, ultra-low-power operat ion in active and battery

modes, 3/5KB shared RAM and 32/64K B of flash mem ory that can be

programmed in the field with code and/or data during meter

operation and the ability to drive up to six LCD segments per SEG

driver pin. High processing and sampling rates combined with

differential inputs offer a powerful metering platform for residential

meters.

A complete array of code development tools, demonstration code,

and reference designs enable rapid development and certification of

meters t hat meet all ANSI and IEC electric ity metering standards

worldwide.

Products, Inc.

SPI is a trademark of Mot orol a, Inc.

MICROWIRE i s a trademark of N at ional Semiconduct or Corp.

v1.1 © 2008–2011 Teridian Semiconductor Corporation 1

D ATA SHEET

FEATURES

• 0.1% Accuracy Over 2000:1 Current Range

• Exceeds IEC 62053/ANSI C12.20 Standards

• Two Current Sensor Inputs with Selectable

Differential Mode

• Selectable Gain of 1 or 8 for One Current Input

to Support Shunts

• High-Speed Wh/VARh Pulse Outputs with

Programmable Width

• 32KB Flash, 3KB RAM (71M6541D)

• 64KB Flash, 5KB RAM (71M6541F/42F)

• Up to Four Pulse Outputs with Pulse Count

• Four-Quadrant Metering

• Digital Temperature Compensation:

- Metrology Compensation

- Accurate RTC for TOU Functions with

Automatic Temperature Compensation

for Crystal in All Power Modes

• Independent 32-Bit Compute Engine

• 46-64Hz Line Frequency Range with the Same

Calibration

• Phase Compensation (±10°)

• Three Battery-Backup Modes:

- Brownout Mode (BRN)

- LCD Mode (LCD)

- Sleep Mode (SLP)

• Wake-Up on Pin Events and Wake-On Timer

• 1µA in Sleep Mode

• Flash Security

• In-System Program Update

• 8-Bit MPU (80515), Up to 5 MIPS

• Full-Speed MPU Clock in Brownout Mode

• LCD Drive r:

- Up to 6 Commons/Up to 56 Pins

• 5V LCD Driver with DAC

• Up to 51 Multifunction DIO Pins

• Hardware Watchdog Timer (WDT)

• I2C/MICROWIRE™ EEPROM Interface

• SPI In terface with Flash Program Capability

• Two UARTs for IR and AMR

• IR LED Driver with Modulation

• Industrial Temperature Range

• 64-Pin (71M6541D/71M6541F) and 100-pin

(71M6542F) Lead(Pb)-Free LQFP Package

Page 2

Table of Contents

1 Introduction ................................................................................................................................. 10

2 Hardware Descript io n .................................................................................................................. 11

2.1 Hardware Overview............................................................................................................... 11

2.2 Analog Front End (AFE) ........................................................................................................ 12

2.2.1 Signal Input Pins ....................................................................................................... 14

2.2.2 Input Multiplexer ........................................................................................................ 15

2.2.3 Delay Compensation ................................................................................................. 19

2.2.4 ADC Pre-Amplifier ..................................................................................................... 20

2.2.5 A/D Converter (ADC) ................................................................................................. 20

2.2.6 FIR Filter ................................................................................................................... 20

2.2.7 Voltage Refer enc es ................................................................................................... 20

2.2.8 71M6x01 Isolated Sensor Interface (Remote Sensor I nterface) .................................. 22

2.3 Digital Computation Engine (CE) ........................................................................................... 24

2.3.1 CE Program Memory ................................................................................................. 24

2.3.2 CE Data Memory ....................................................................................................... 24

2.3.3 CE Communicati on with t he MPU .............................................................................. 25

2.3.4 Meter Equations ........................................................................................................ 25

2.3.5 Real-Time Monitor (RTM) .......................................................................................... 25

2.3.6 Pulse Generators ...................................................................................................... 27

2.3.7 CE Functional Ov erview ............................................................................................ 28

2.4 80515 MPU Core .................................................................................................................. 31

2.4.1 Memory Organization and Addressing ....................................................................... 31

2.4.2 Special Function Registers (SFRs) ............................................................................ 33

2.4.3 Generic 80515 Speci al Function Registers ................................................................ 34

2.4.4 Instructi on S et ........................................................................................................... 36

2.4.5 UARTs ...................................................................................................................... 36

2.4.6 Timers and Counters ................................................................................................. 39

2.4.7 WD Timer (Software Watchdog Timer) ...................................................................... 40

2.4.8 Interrupts ................................................................................................................... 40

2.5 On-Chip Resources............................................................................................................... 48

2.5.1 Physical Memory ....................................................................................................... 48

2.5.2 Oscillator ................................................................................................................... 50

2.5.3 PLL and Internal Cl ocks............................................................................................. 50

2.5.4 Real-Time Clock (RTC) ............................................................................................. 51

2.5.5 71M654x Temperature Sensor .................................................................................. 56

2.5.6 71M654x Battery Monitor ........................................................................................... 57

2.5.7 UART and Optical Int erfac e ....................................................................................... 58

2.5.8 Digital I/O and LCD Segment Drivers ......................................................................... 59

2.5.9 EEPROM Interface .................................................................................................... 70

2.5.10 SPI Slave Port ........................................................................................................... 73

2.5.11 Hardware Watchdog Timer ........................................................................................ 78

2.5.12 Test Ports (TMUXOUT and TMUX2OUT Pins)........................................................... 78

3 Functional Description ................................................................................................................ 80

3.1 Theory of Operation .............................................................................................................. 80

3.2 Battery Modes ....................................................................................................................... 81

3.2.1 BRN Mode ................................................................................................................ 83

3.2.2 LCD Mode ................................................................................................................. 83

3.2.3 SLP Mode ................................................................................................................. 84

2 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 3

3.3 Fault and Reset Behavi or ...................................................................................................... 85

3.3.1 Events at Power-Down .............................................................................................. 85

3.3.2 IC Behavior at Low Batt er y Volt age ........................................................................... 86

3.3.3 Reset Sequence ........................................................................................................ 86

3.3.4 Watchdog Timer Reset .............................................................................................. 86

3.4 Wake Up Behavior ................................................................................................................ 87

3.4.1 Wake on Hardware Event s ........................................................................................ 87

3.4.2 Wake on Timer .......................................................................................................... 90

3.5 Data Flow and MPU/CE Communic ation ............................................................................... 91

4 Application Information ............................................................................................................... 92

4.1 Connecting 5 V Devic es ........................................................................................................ 92

4.2 Direct Connection of Sensors ................................................................................................ 92

4.3 71M6541D/F Using Local Sensors ........................................................................................ 93

4.4 71M6541D/F Using 71M6x01and Current Shunts .................................................................. 94

4.5 71M6542F Using Local S ensors ............................................................................................ 95

4.6 71M6542F Using 71M6x 01 and Cur r ent Shunts .................................................................... 96

4.7 Metrology Tem per ature Compensation .................................................................................. 97

4.7.1 Voltage Reference Precision ..................................................................................... 97

4.7.2 Temperature Coefficients for the 71M654x ................................................................ 97

4.7.3 Temperature Compensation for VREF with Local Sensors ......................................... 98

4.7.4 Temperature Compensation for VREF with Remote Sensor ....................................... 99

4.8 Connecting I2C EEPROMs .................................................................................................. 100

4.9 Connecting Thr ee-Wire EEPROMs ..................................................................................... 101

4.10 UART0 (TX/RX) .................................................................................................................. 101

4.11 Optical Int erfac e ( UA RT1) ................................................................................................... 101

4.12 Connecting the Reset Pi n .................................................................................................... 102

4.13 Connecting the Emulator Port Pins ...................................................................................... 102

4.14 Flash Programming ............................................................................................................. 104

4.14.1 Flash Programming via the ICE Port ........................................................................ 104

4.14.2 Flash Programming via the SPI Port ........................................................................ 104

4.15 MPU Firmware Librar y ........................................................................................................ 104

4.16 Crystal Oscill ator ................................................................................................................. 104

4.17 Meter Calibration ................................................................................................................. 104

5 Firmware Interface ..................................................................................................................... 105

5.1 I/O RAM Map –Functional Order ......................................................................................... 105

5.2 I/O RAM Map – Alphabetical Order ..................................................................................... 111

5.3 CE Interface Descri ption ..................................................................................................... 125

5.3.1 CE Program ............................................................................................................ 125

5.3.2 CE Data Format ...................................................................................................... 125

5.3.3 Constants ................................................................................................................ 125

5.3.4 Environment ............................................................................................................ 126

5.3.5 CE Calculations ....................................................................................................... 126

5.3.6 CE Front End Data (Raw Data)................................................................................ 127

5.3.7 FCE Status and Control ........................................................................................... 127

5.3.8 CE Transfer Variables ............................................................................................. 129

5.3.9 Pulse Generation..................................................................................................... 132

5.3.10 Other CE Parameters .............................................................................................. 134

5.3.11 CE Calibration Paramet er s ...................................................................................... 135

5.3.12 CE Flow Diagrams .................................................................................................. 136

6 Electrical Specifications ............................................................................................................ 138

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 3

Page 4

6.1 Absolute Maximum Ratings ................................................................................................. 138

6.2 Recommended External Com ponents ................................................................................. 139

6.3 Recommended Operating Conditions .................................................................................. 139

6.4 Performance Specifications ................................................................................................. 140

6.4.1 Input Logic Lev els ................................................................................................... 140

6.4.2 Output Logic Levels ................................................................................................. 140

6.4.3 Battery Monitor ........................................................................................................ 141

6.4.4 Temperature Monitor ............................................................................................... 141

6.4.5 Supply Current ........................................................................................................ 142

6.4.6 V3P3D Switch ......................................................................................................... 143

6.4.7 Internal Power Faul t Compar ators ........................................................................... 143

6.4.8 2.5 V Voltage Regul ator – System Power ................................................................ 143

6.4.9 2.5 V Voltage Regul ator – Batt er y Power ................................................................. 144

6.4.10 Crystal Oscillator ..................................................................................................... 144

6.4.11 Phase-Locked Loop (PLL) ....................................................................................... 144

6.4.12 LCD Drivers ............................................................................................................ 145

6.4.13 VLCD Generator...................................................................................................... 146

6.4.14 VREF ...................................................................................................................... 148

6.4.15 ADC Converter ........................................................................................................ 149

6.4.16 Pre-Amplifier for IAP-IAN ......................................................................................... 150

6.5 Timing Specifications .......................................................................................................... 151

6.5.1 Flash Memory ......................................................................................................... 151

6.5.2 SPI Slave ................................................................................................................ 151

6.5.3 EEPROM Interface .................................................................................................. 151

6.5.4 RESET Pin .............................................................................................................. 151

6.5.5 RTC ........................................................................................................................ 152

6.6 Package Outline Drawings .................................................................................................. 153

6.6.1 64-Pin LQFP Outline Pac k age Dr awing ................................................................... 153

6.6.2 100-Pin LQFP Package Outline Drawing ................................................................. 154

6.7 Pinout Diagrams ................................................................................................................. 155

6.7.1 71M6541D/F LQFP-64 Package Pinout ................................................................... 155

6.7.2 71M6542F LQFP-100 Package Pi nout..................................................................... 156

6.8 Pin Descripti ons .................................................................................................................. 157

6.8.1 Power and Ground Pins........................................................................................... 157

6.8.2 Analog Pins ............................................................................................................. 158

6.8.3 Digital Pins .............................................................................................................. 159

6.8.4 I/O Equivalent Circ uits ............................................................................................. 161

7 Ordering Information ................................................................................................................. 162

7.1 71M6541D/F and 71M6542F ............................................................................................... 162

8 Related Informati on ................................................................................................................... 162

9 Contact Information ................................................................................................................... 162

Appendix A: Acronyms ..................................................................................................................... 163

Appendix B: Revision Hi story ........................................................................................................... 164

4 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 5

Figures

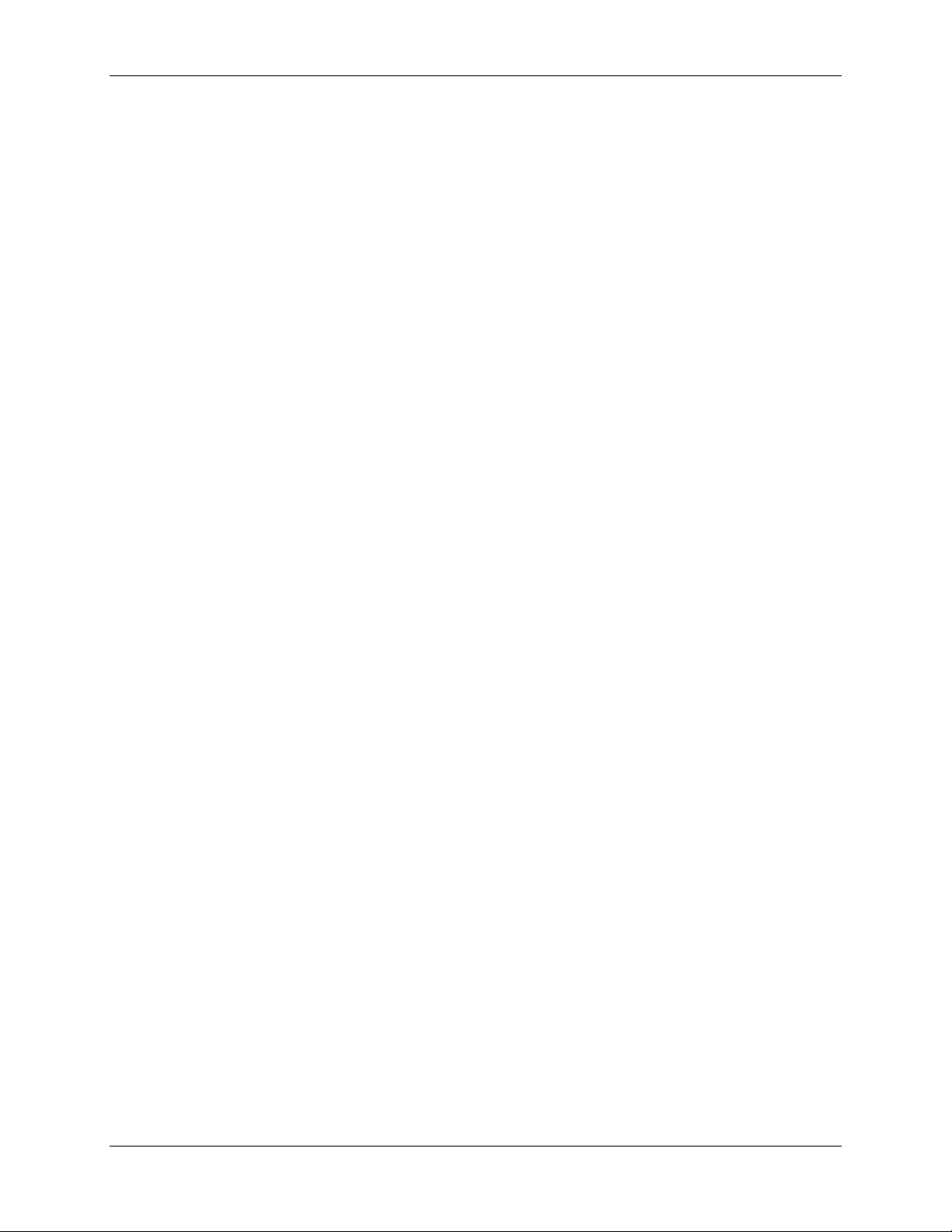

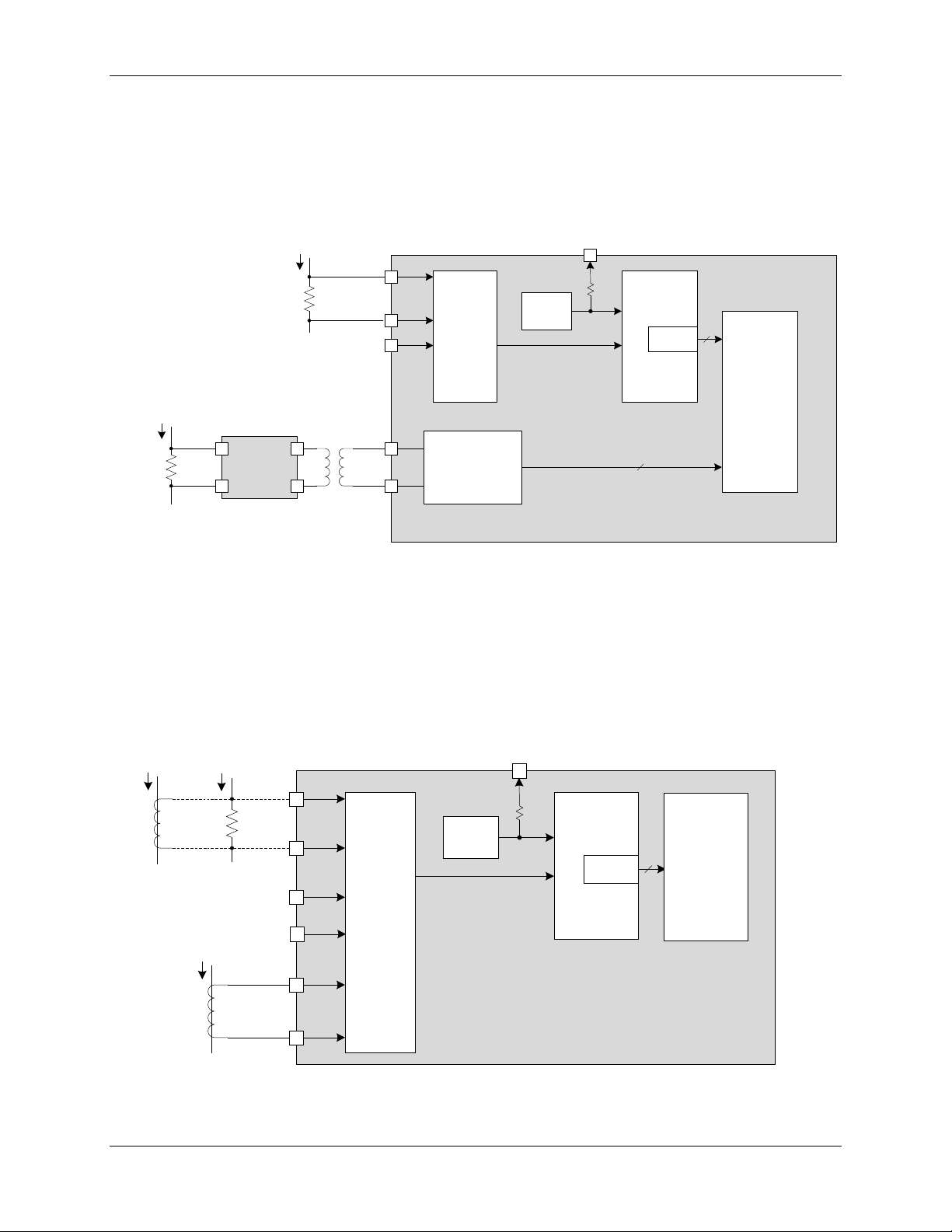

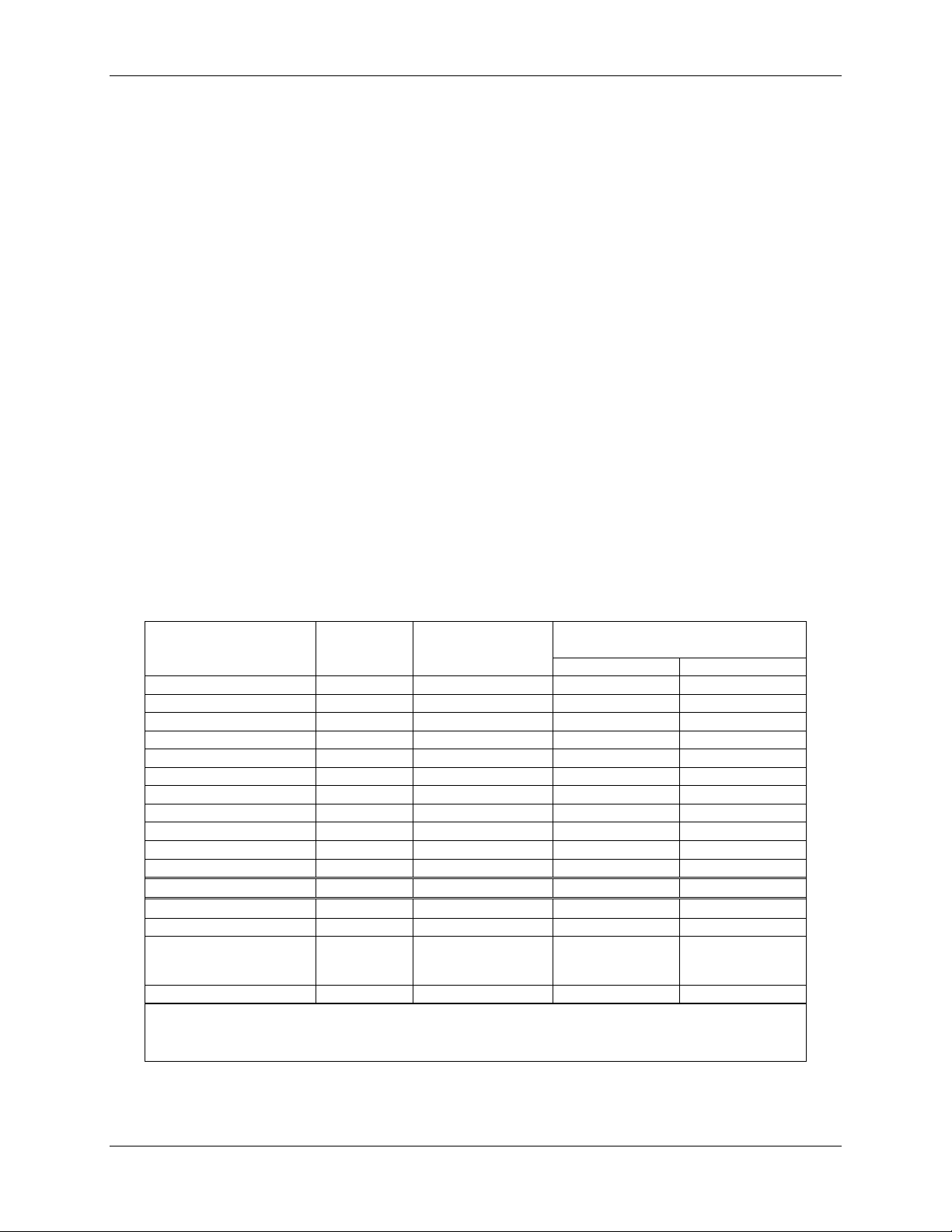

Figure 1: IC Functi onal Bl oc k Di agr am ..................................................................................................... 9

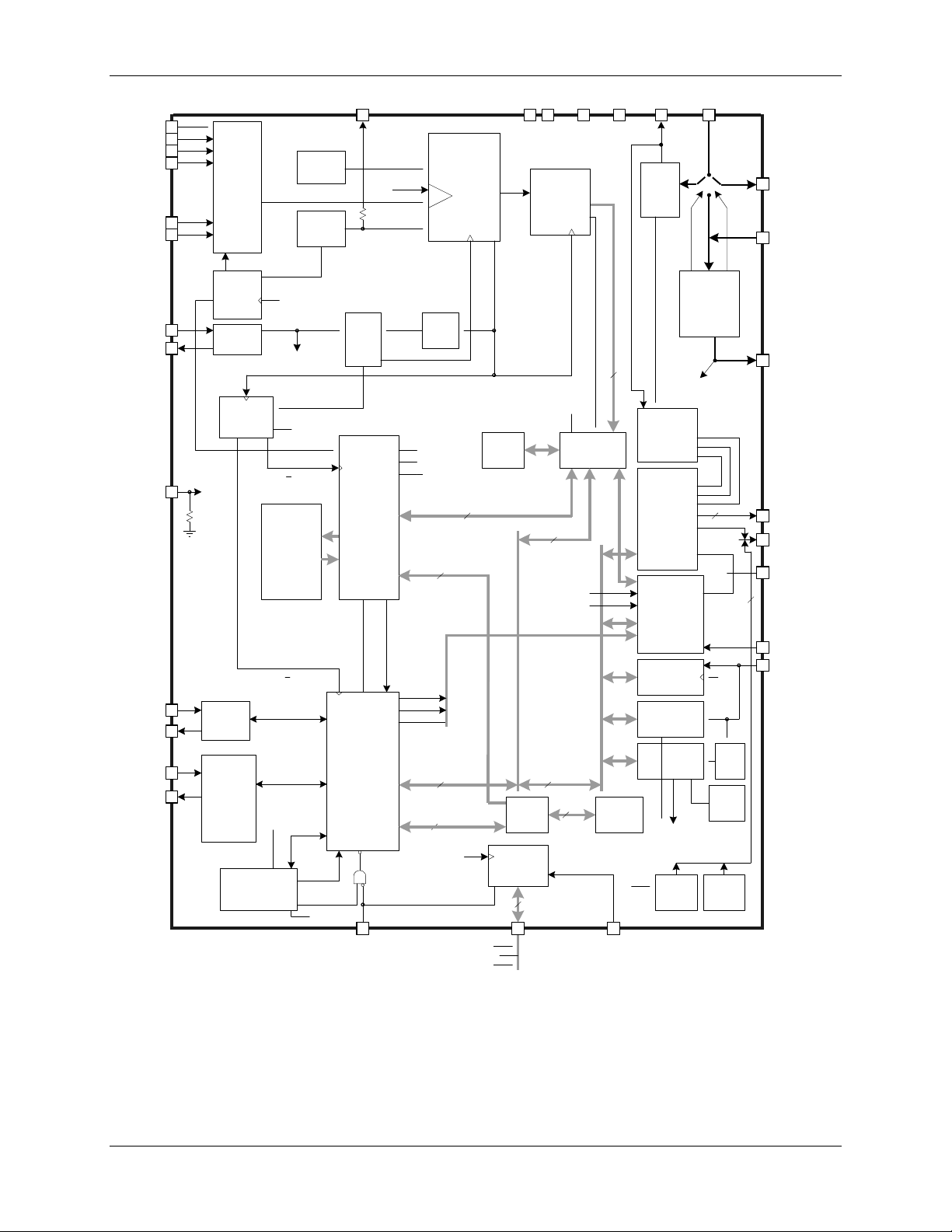

Figure 2. 71M6541D/F AFE Bl oc k Di agr am (Local S ensors) .................................................................. 12

Figure 3. 71M6541D/F AFE Bl oc k Di agr am with 71M 6x01 ..................................................................... 13

Figure 4. 71M6542F AFE Block Diagr am ( Loc al S ensors) ...................................................................... 13

Figure 5. 71M6542F AFE Block Diagr am with 71M6x01 ......................................................................... 14

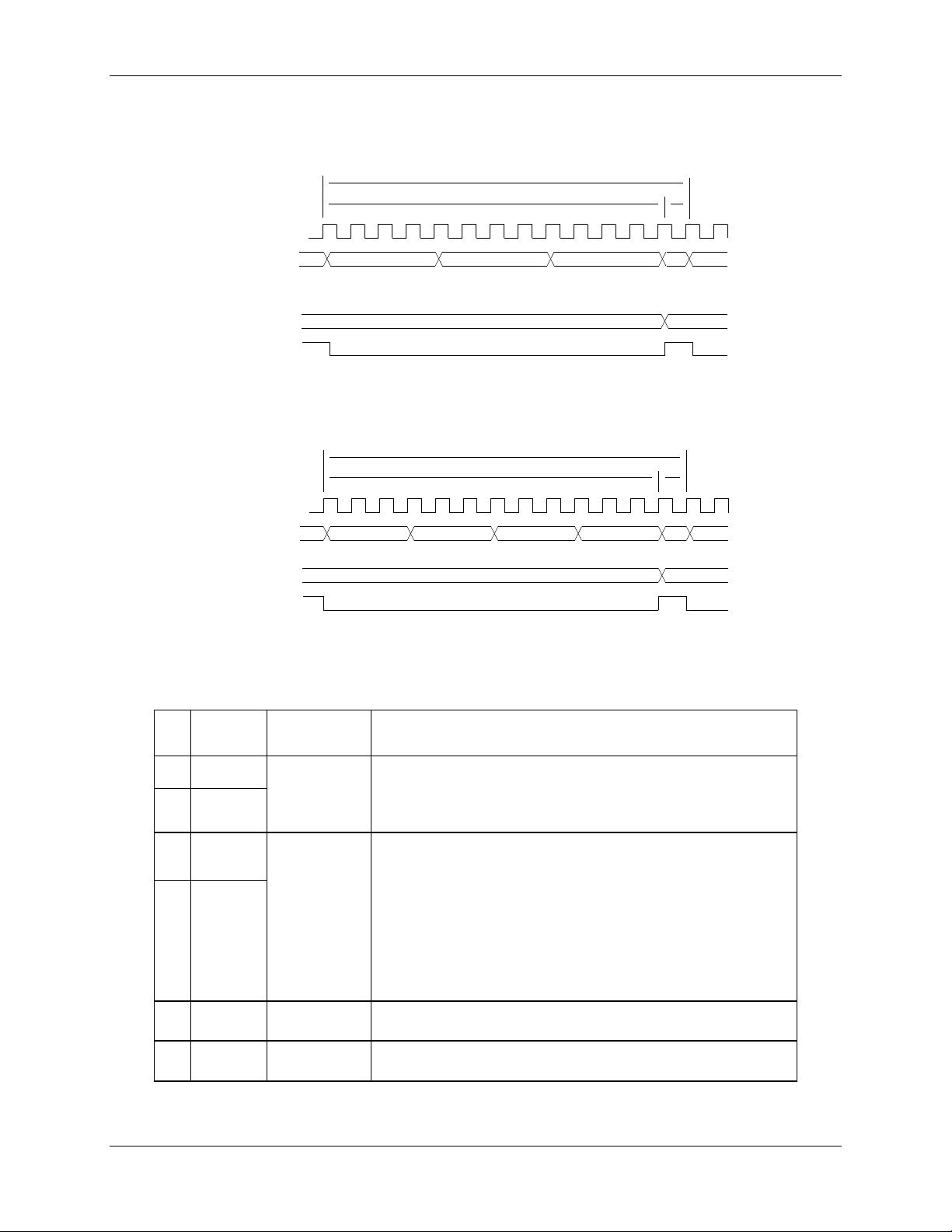

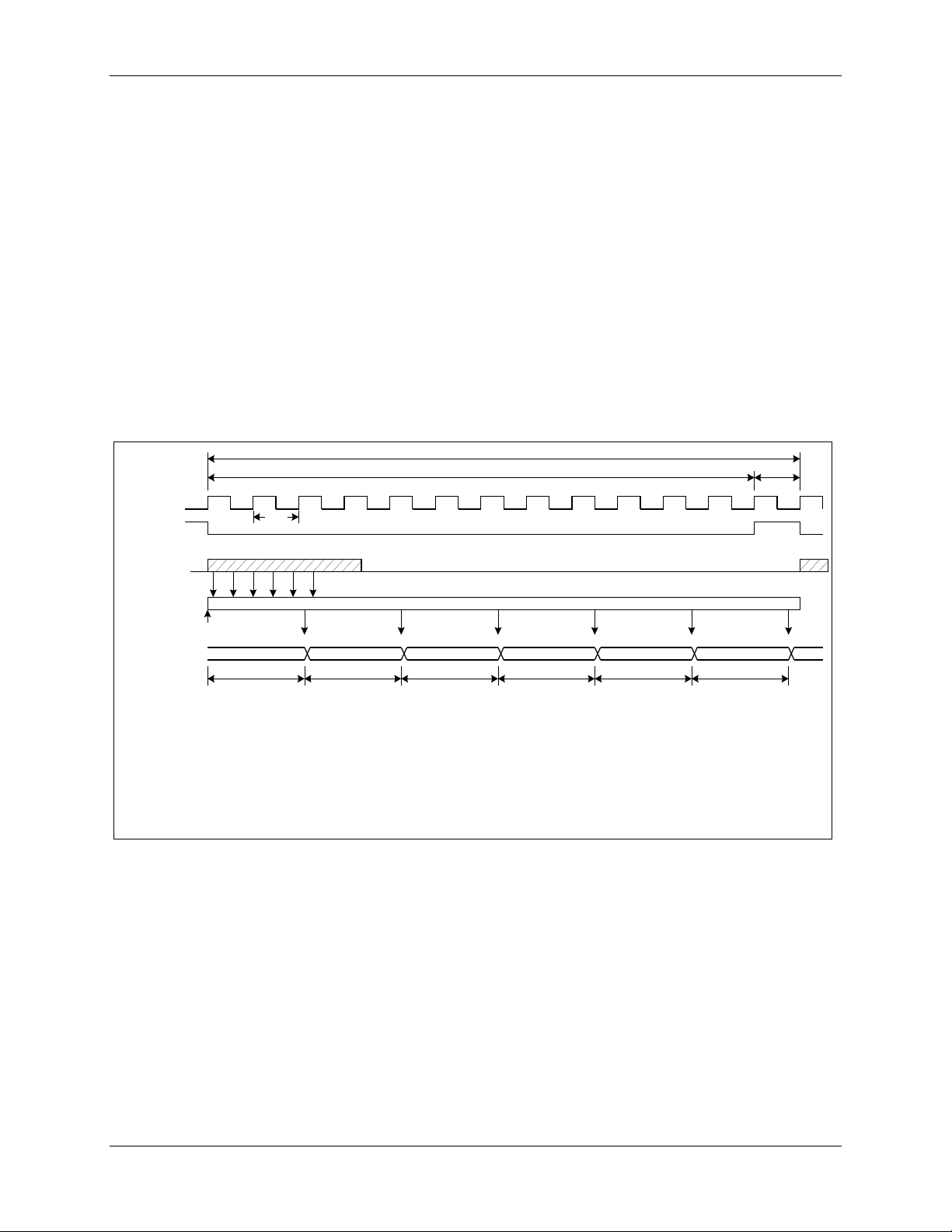

Figure 6: States in a Multiplexer Frame (MUX_DIV[3:0] = 3) .................................................................. 17

Figure 7: States in a Multiplexer Fram e (MUX_DIV[3:0] = 4) .................................................................. 17

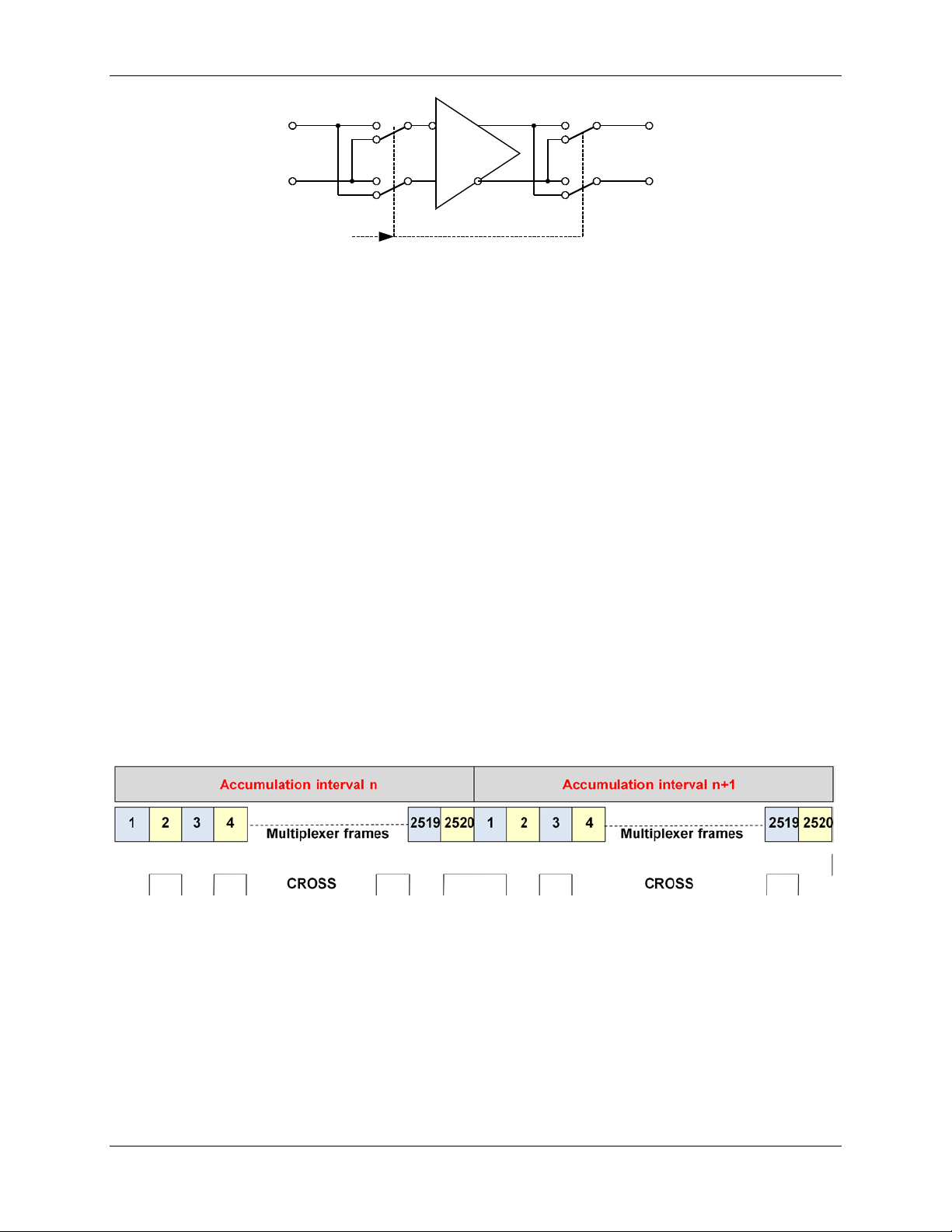

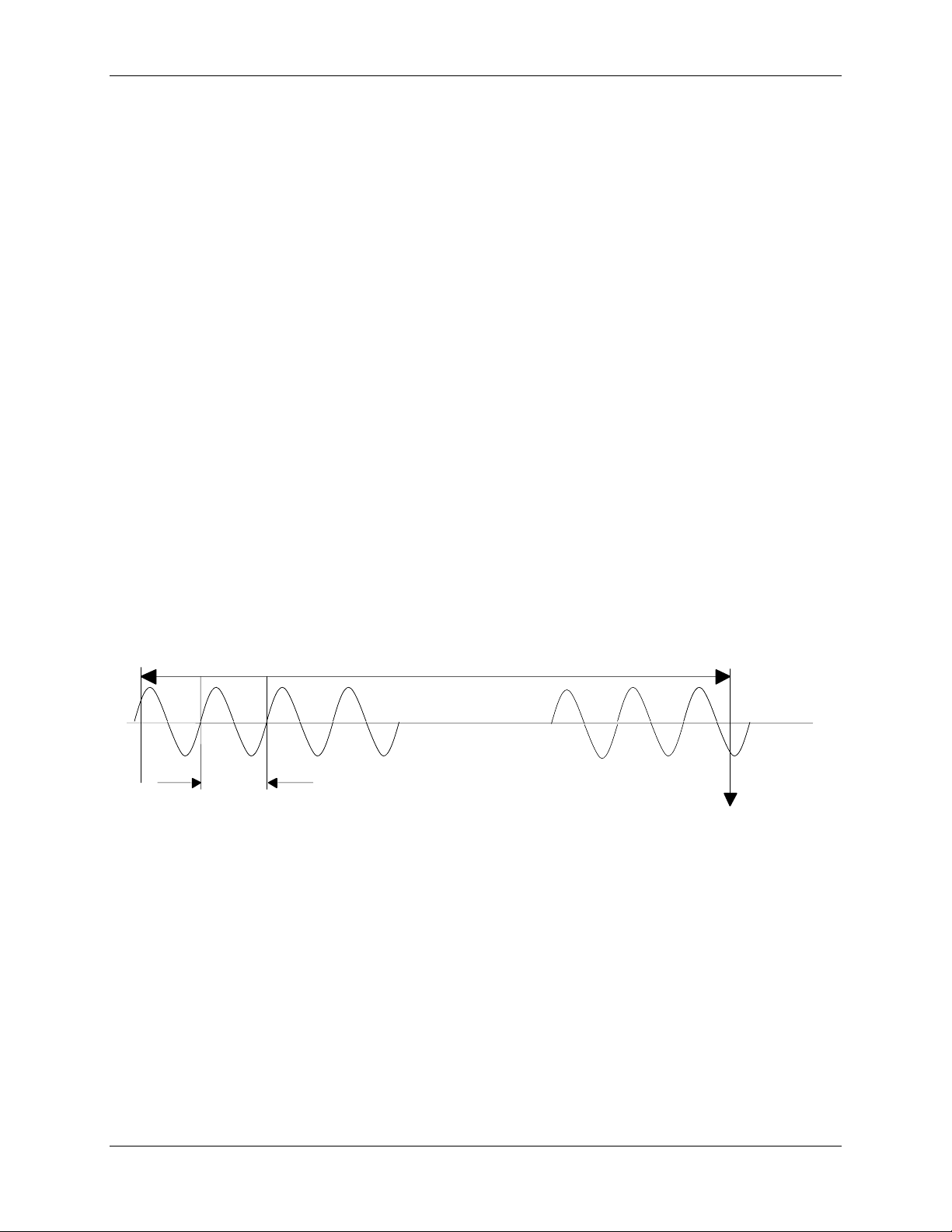

Figure 8: General Topology of a Chopped Amplifier ............................................................................... 21

Figure 9: CROSS Signal wit h CHOP_E = 00 ........................................................................................... 21

Figure 10: RTM Timing .......................................................................................................................... 26

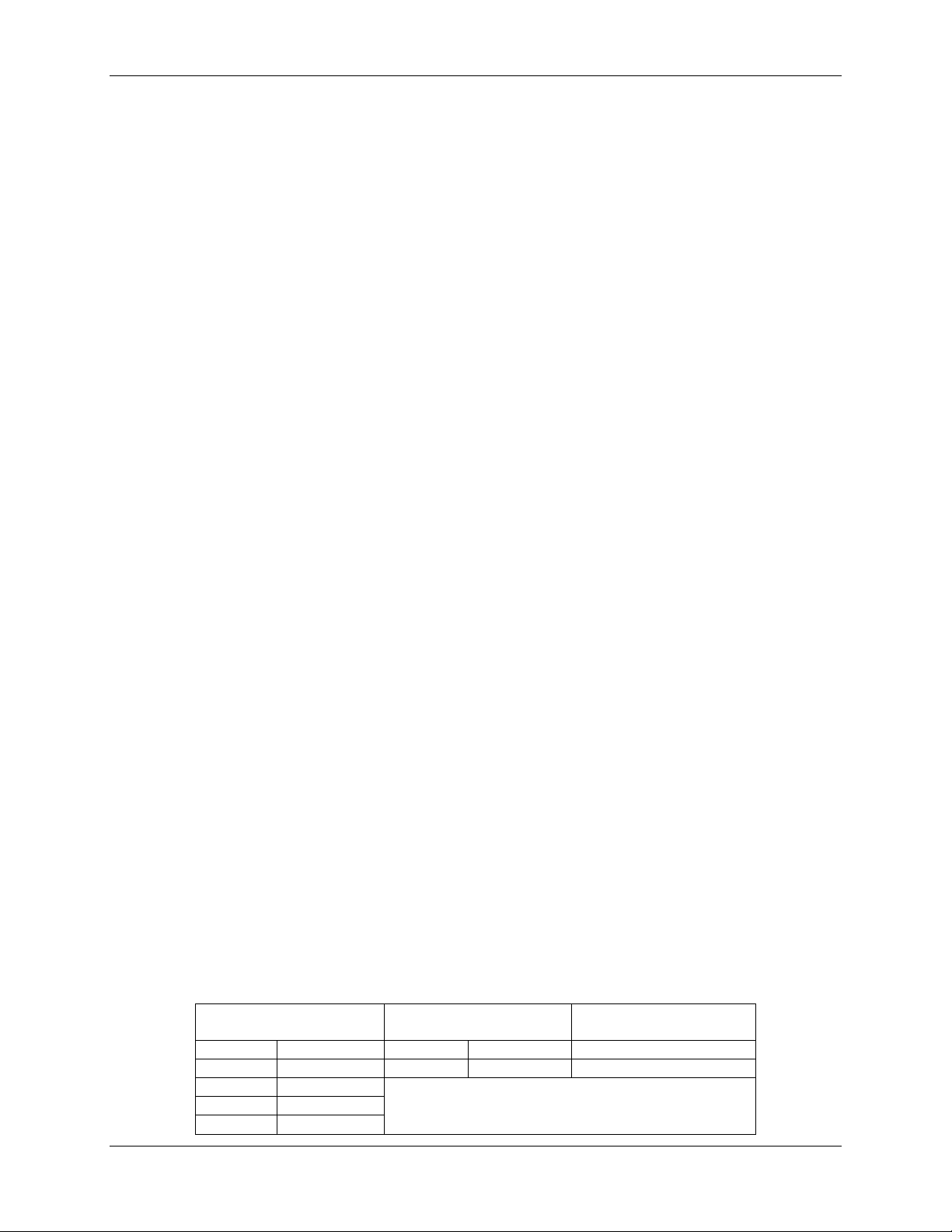

Figure 11: Timing r elationship between ADC MUX, CE, and RTM Serial Transfer .................................. 26

Figure 12. Pulse Generat or FI FO Timing ............................................................................................... 28

Figure 13: Accum ulation Interval ............................................................................................................ 29

Figure 14: Samples from Multiplexer Cycle (MUX_DIV[3:0] = 3) ............................................................. 30

Figure 15: Samples from Multiplexer Cycle (MUX_DIV[3:0] = 4) ............................................................. 30

Figure 16: Interrupt Structure ................................................................................................................. 47

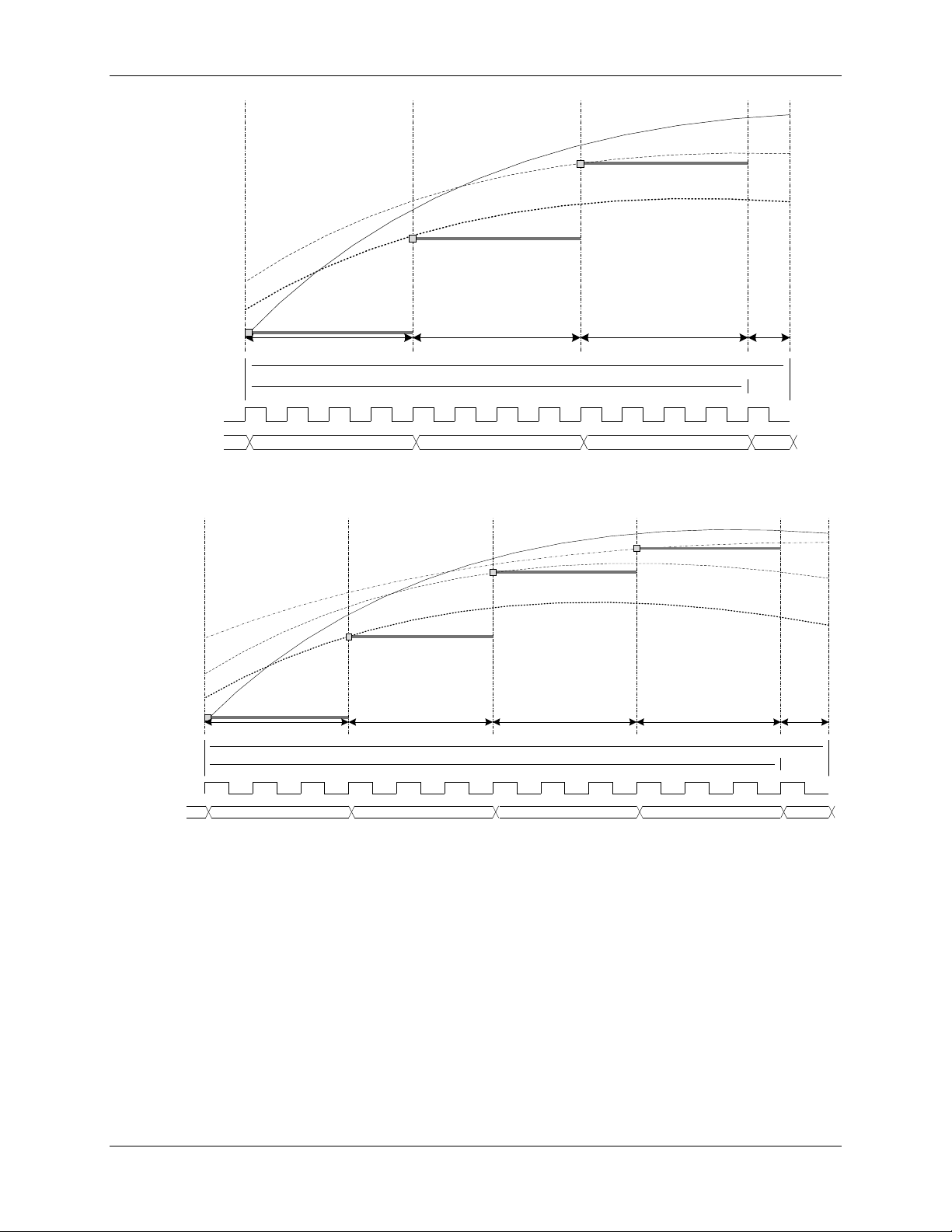

Figure 17: Autom atic Temper ature Compensation ................................................................................. 54

Figure 18: Optical I nterface .................................................................................................................... 58

Figure 19: Optical I nterface (UART1) ..................................................................................................... 59

Figure 20: Connecting an External Load to DIO Pins ............................................................................. 60

Figure 21: LCD Waveform s ................................................................................................................... 68

Figure 22: 3-wire Interface. Write Command, HiZ=0. ............................................................................. 72

Figure 23: 3-wire Interface. Write Command, HiZ=1 .............................................................................. 72

Figure 24: 3-wire Interface. Read Command. ........................................................................................ 72

Figure 25: 3-Wire Int erfac e. Write Command when CNT=0 ................................................................... 73

Figure 26: 3-wire Interface. Write Command when HiZ=1 and WFR=1. ................................................. 73

Figure 27: SPI Slave Port - Typical Multi-Byte Read and Write operations .............................................. 75

Figure 28: Voltage, Current, Momentary and Accumulated Ener gy ......................................................... 80

Figure 29: Operation Modes State Diagram ........................................................................................... 81

Figure 30: MPU/CE Data Flow ............................................................................................................... 91

Figure 31: Resistive Voltage Divider (Voltage Sensi ng) .......................................................................... 92

Figure 32. CT with Single-Ended Input Connection (Current S ensing) .................................................... 92

Figure 33: CT with Differential Input Connection ( Cur r ent Sensi ng) ........................................................ 92

Figure 34: Diff er ential Resistive Shunt Connecti ons (Curr ent Sensing) ................................................... 92

Figure 35. 71M6541D/F with Local Sensors ........................................................................................... 93

Figure 36: 71M6541D/F with 71M6x01 isolated Sensor .......................................................................... 94

Figure 37: 71M6542F with Local Sensors .............................................................................................. 95

Figure 38: 71M6542F with 71M6x01 Isolated Sensor ............................................................................. 96

Figure 39: I2C EEPROM Connection .................................................................................................... 100

Figure 40: Connections for UART0 ...................................................................................................... 101

Figure 41: Connection for Optical Components .................................................................................... 102

Figure 42: External Components for the RE SE T P in: Pu s h-Button (Left), Production Circuit (Right) ......... 102

Figure 43: External Components for the Emulator Int erface ................................................................. 103

Figure 44: CE Data Flow: Multi plexer and ADC .................................................................................... 136

Figure 45: CE Data Flow: Scaling, Gain Control, Intermediate Variables .............................................. 136

Figure 46: CE Data Flow: Squaring and Summation Stages ................................................................. 137

Figure 51: 64-pin LQFP Pac k age Outli ne ............................................................................................. 153

Figure 52: 100-pin LQF P Pack age Outli ne ........................................................................................... 154

Figure 53: Pinout for the 71M6541D/F (LQFP-64 Package) ................................................................. 155

Figure 54: Pinout for the 71M6542F (LQFP-100 Package) ................................................................... 156

Figure 55: I/O Equivalent Circuits ......................................................................................................... 161

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 5

Page 6

Tables

Table 1. Required CE Code and Set tings for Local Sensors ................................................................... 15

Table 2. Required CE Code and Set tings for 71M6x01 isolated Sensor ................................................. 15

Table 3: ADC Input Configur ation ......................................................................................................... 17

Table 4: Multiplexer and A DC Configuration Bits ................................................................................... 19

Table 5. RCMD[4:0] Bits ........................................................................................................................ 22

Table 6: Remote Interfac e Read Commands ........................................................................................ 23

Table 7: I/O RAM Control Bits for I sol ated Sensor ................................................................................. 23

Table 8: Inputs Selected in Multiplexer Cycles ....................................................................................... 25

Table 9: CKMPU Clock Frequencies ...................................................................................................... 31

Table 10: Memory Map .......................................................................................................................... 32

Table 11: Inter nal Data Memory Map ..................................................................................................... 33

Table 12: Special Func tion Register Map ............................................................................................... 33

Table 13: Generic 80515 SFRs - Locati on and Reset V alues ................................................................. 34

Table 14: PSW Bit Functions (SFR 0xD0) ................................................................................................. 35

Table 15: Port Register s (SE GDIO0-15) ................................................................................................ 36

Table 16: Stretch M em ory Cycl e Widt h .................................................................................................. 36

Table 18: Baud Rate Generat ion............................................................................................................ 37

Table 19: UART Modes ......................................................................................................................... 37

Table 20: The S0CON (UART0) Register (SFR 0x98) ............................................................................. 38

Table 21: The S1CON (UART1) Register (SFR 0x9B ) ............................................................................. 38

Table 22: PCON Register Bi t Description (SFR 0x87) ............................................................................ 39

Table 23: Timers/Counters Mode Descripti on ........................................................................................ 39

Table 24: Allowed Timer /Counter Mode Combinations ........................................................................... 39

Table 25: TMOD Regi ster Bit Description (SFR 0x89) ............................................................................ 40

Table 26: The TCON Register Bit Functions (SF R 0x 88) ........................................................................ 40

Table 27: The IEN0 Bit Functions (SFR 0xA8) ........................................................................................ 41

Table 28: The IEN1 Bit Functions (SFR 0xB8) ........................................................................................ 41

Table 29: The IEN2 Bit Func tions (SFR 0x9A) ........................................................................................ 42

Table 30: TCON Bit Functi ons (SFR 0x88) ............................................................................................. 42

Table 31: The T2CON Bit F unctions (SFR 0xC8) ................................................................................... 42

Table 32: The IRCON Bit F unc tions (SFR 0xC0) .................................................................................... 42

Table 33: External MPU Interrupts ......................................................................................................... 44

Table 34: Interrupt Enable and Flag Bits ............................................................................................... 44

Table 35: Inter r upt Pri ori ty Level Groups ................................................................................................ 45

Table 36: Inter r upt Pri ori ty Levels .......................................................................................................... 45

Table 37: Inter r upt Pri ori ty Registers (IP0 and IP1) ................................................................................. 45

Table 38: Inter r upt Polling Sequence ..................................................................................................... 46

Table 39: Inter r upt Vector s .................................................................................................................... 46

Table 40: Flash Memory Access ............................................................................................................ 48

Table 41: Flash Securit y ........................................................................................................................ 49

Table 42: Clock System Summ ar y ......................................................................................................... 51

Table 43: RTC Control Regi ster s ........................................................................................................... 52

Table 44: I/O RAM Registers for RTC Temperature Compensati on ........................................................ 53

Table 45: NV RAM Temperature Table Structure ................................................................................... 54

Table 46: I/O RAM Registers for RTC Interrupts .................................................................................... 55

Table 47: I/O RAM Registers for Temperature and Battery Measurement .............................................. 56

Table 48: Selectable Resources using the DIO_Rn[2:0] Bits................................................................... 59

Table 49: Data/Dir ec tion Registers for SEGDIO0 to SEGDIO14 (71M6541D/F)...................................... 61

Table 50: Data/Dir ec tion Registers for SEGDIO19 to SEGDIO 27 ( 71M 6541D/F).................................... 62

Table 51: Data/Dir ec tion Registers for SEGDIO36-39 to SEGDIO44 -45 (71M6541D/F) .......................... 62

Table 52: Data/Dir ec tion Registers for SEGDIO51 and SEG DIO 55 ( 71M 6541D/F) ................................. 62

Table 53: Data/Dir ec tion Registers for SEGDIO0 to SEGDIO15 (71M6542F) ......................................... 63

6 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 7

Table 54: Data/Dir ec tion Registers for SEGDIO16 to SEGDIO 31 ( 71M 6542F) ....................................... 64

Table 55: Data/Dir ec tion Registers for SEGDIO32 to SEGDIO45 ( 71M 6542F) ....................................... 64

Table 56: Data/Dir ec tion Registers for SEGDIO51 to SEGDIO 55 ( 71M 6542F) ....................................... 64

Table 57: LCD_VMODE[1:0] Configurations .......................................................................................... 65

Table 58: LCD Configurations ............................................................................................................... 67

Table 59: 71M6541D/F LCD Data Registers for SEG46 to SEG50 ......................................................... 69

Table 60: 71M6542F LCD Dat a Register s for SEG46 to SEG50 ............................................................ 70

Table 61: EECTRL Bits for 2-pin Interface ............................................................................................... 71

Table 62: EECTRL B its for the 3-wir e Interface ....................................................................................... 71

Table 63: SPI Transacti on Fields ........................................................................................................... 74

Table 64: SPI Command Sequenc es ..................................................................................................... 75

Table 65: SPI Register s ......................................................................................................................... 76

Table 66: TMUX[5:0] Selections ............................................................................................................ 79

Table 67: TMUX2[4:0] Selections ........................................................................................................... 79

Table 68: Avail able Cir c uit Functions ..................................................................................................... 82

Table 69: VSTAT[2:0] (SFR 0xF9[2:0]) .................................................................................................... 85

Table 70: Wake Enables and Flag Bi ts .................................................................................................. 87

Table 71: Wake Bits .............................................................................................................................. 89

Table 72: Clear Event s for WAKE fl ags .................................................................................................. 90

Table 73: GAIN_ADJn Com pensation Channels .................................................................................... 98

Table 74: GAIN_ADJn Com pensation Channels .................................................................................. 100

Table 75: I/O RAM Map – Functional Order , Basi c Configuration ......................................................... 105

Table 76: I/O RAM Map – Functional Order ......................................................................................... 107

Table 77: I/O RAM Map – Functional Order ......................................................................................... 111

Table 78. Standard CE Codes ............................................................................................................. 125

Table 79: CE EQU Equations and Element Input Mapping ................................................................... 126

Table 80: CE Raw Data Access Locati ons ........................................................................................... 127

Table 81: CESTATUS Register .............................................................................................................. 127

Table 82: CESTATUS (CE RAM 0x80) Bit Definitions .............................................................................. 128

Table 83: CECONFIG Register ............................................................................................................. 128

Table 84: CECONFIG (CE RAM 0x20) Bit Definit ions ............................................................................. 128

Table 85: Sag Threshold and Gain Adjust Control ................................................................................ 129

Table 86: CE Transfer Variables (with Local Sensors).......................................................................... 130

Table 87: CE Transfer Variables (with Remote Sensor) ....................................................................... 130

Table 88: CE Energy Measurem ent Variables (with Local S ensors) ..................................................... 131

Table 89: CE Energy Measurem ent Variables (with Remote Sensor) ................................................... 131

Table 90: Other Transf er V ari ables ...................................................................................................... 132

Table 91: CE Pulse Generati on P ar am eters......................................................................................... 132

Table 92: CE Parameters for Noise Suppres si on and Code V er si on..................................................... 134

Table 93: CE Calibration Parameters ................................................................................................... 135

Table 94: Absolute M aximum Ratings .................................................................................................. 138

Table 95: Recommended Ex ternal Components .................................................................................. 139

Table 96: Recommended O per ating Conditions ................................................................................... 139

Table 97: Input Logic Lev els ................................................................................................................ 140

Table 98: Output Logic Levels ............................................................................................................. 140

Table 99 : Battery Monit or Performance Specifications (TEMP_BAT= 1) ................................................ 141

Table 100. Temperature Monitor .......................................................................................................... 141

Table 101: Supply Current Performance Specifications ........................................................................ 142

Table 102: V3P3D Swit c h Perf ormance Specifications ......................................................................... 143

Table 103. Inter nal P ower Fault Comparator Specifications ................................................................. 143

Table 104: 2.5 V Voltage Regulator Performance Specif ications .......................................................... 143

Table 105: Low-Power Voltage Regulator Performanc e Specif ic ations ................................................. 144

Table 106: Crystal Oscill ator Performance Specifications ..................................................................... 144

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 7

Page 8

Table 107: PLL Perf ormance S pecifications ......................................................................................... 144

Table 108: LCD Driv er Performance Specifications .............................................................................. 145

Table 109: LCD Driv er Performance Specifications .............................................................................. 146

Table 110: VREF Perf ormance S pecifications ...................................................................................... 148

Table 111. ADC Convert er Performance Specifications ....................................................................... 149

Table 112: Pre-Amplifier Performance Specifications ........................................................................... 150

Table 113: Flash Memory Timing Specifications .................................................................................. 151

Table 114. SPI Slave Timing Specifications ......................................................................................... 151

Table 115: EEPROM Interface Timing ................................................................................................. 151

Table 116: RESET Pin Timing ............................................................................................................. 151

Table 117: RTC Range for Date........................................................................................................... 152

Table 118: Power and Ground Pins ..................................................................................................... 157

Table 119: Analog Pins ........................................................................................................................ 158

Table 120: Digit al Pi ns ......................................................................................................................... 159

8 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 9

IAP

MUX

and

PREAMP

XIN

XOUT

VREF

CKADC

CE

32-bit Compute

Engine

MPU

(80515)

CE CONTROL

OPT_RX/

SEGDIO55

OPT_TX/

SEGDIO51/

WPULSE/

VARPULSE

RESET

VBIAS

EMULATOR

PORT

3

CE_BUSY

OPTICAL

INTERFACE

UART0

TX

RX

XFER BUSY

6

COM0..5

VLC2

LCD DRIVER

CEDATA

0x000...0x2FF

PROG

0x000...0x3FF

DATA

0x0000...0xFFFF

PROGRAM

0x0000...0xFFFF

0x0000…

0xFFFF

DIGITAL I/O

CONFIGURATION

RAM

(I/O RAM)

0x2000...0x20FF

I/O RAM

MEMORY SHARE

0x0000...0x13FF

16

8

RTCLK

RTCLK (32KHz)

MUX_SYNC

CKCE

CKMPU

CK32

32

8

8

8

POWER FAULT

DETECTION

4.9 MHZ

< 4.9MHz

4.9 MHz

GNDD

V3P3A

V3P3D

VBAT

Voltage

Regulator

2.5V to logic

VDD

32KHz

MPU_RSTZ

FAULTZ

WAKE

CONFIGURATION

PARAMETERS

GNDA

VBIAS

2/15/2011

CROSS

CLOCK GEN

Oscillator

32 KHz

CK32

MCK

PLL

VREF

DIV

ADC

MUX CTRL

STRT

MUX

MUX

CKFIR

RTM

SEGDIO Pins

WPULSE

VARPULSE

WPULSE

VARPULSE

TEST

TEST

MODE

VLC1

VLC0

< 4.9MHz

CKMPU_2x

CKMPU_2x

SDCK

SDOUT

SDIN

E_RXTX/SEG48

E_TCLK/SEG49

E_RST/SEG50

FLASH

64/32 KB

V3P3A

FIR

EEPROM

INTERFACE

CK_4X

LCD_GEN

PB

RTC

VBIAS

MEMORY

SHARE

16

E_RXTX

E_TCLK

E_RST(Open Drain)

ICE_E

∆ Σ

AD CONVERTER

+

-

VREF

V3P3SYS

TEST MUX

VLCD

VLCD

Voltage

Boost

MPU RAM

3/5 KB

22

SPI

VSTAT

VBAT_RTC

IAN

IBP

IBN

VA

VB*

SEG Pins

2

TEST MUX

2

Non-Volatile

CONFIGURATION

RAM

BAT

TEST

TEMP

SENSOR

RTM

* 71M6542 only

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 9

Figure 1: IC Functional Block Diagram

Page 10

1 Introduction

This data sheet covers the 71M6541D (32KB) , 71M6541F (64KB) and 71M6542F (64KB) fourth

generation Teri dian energy measurement S oCs. The t erm “71M 654x ” is used when discus si ng a dev ice

feature or behavior that is applicable to all three part numbers. The appropriate part num ber is i ndic ated

when a device feature or behav ior is being discussed that appl ies only to a specific part number. This

data sheet also cover s basic details about the companion 71M6x01 isolated c ur r ent sensor device. For

more complete information on the 71M6x01 sensors, r efer to the 71M6xxx Data Sheet.

This document covers the use of the 71M654x with local ly connected sensors as well when it is used in

conjunction wit h the 71M6x01 isolated current sensor. T he 71M 654x and 71M6x01 chipset make it

possible to use one non-isol ated and one isolated shunt cur r ent sensor t o c r eate single-phase and twophase energy meters using i nexpensive shunt resistors , while achieving unprecedented performance with

this type of sensor technology . The 71M654x SoCs also support confi gur ations involving one loc ally

connected shunt and one locally connected Curr ent Transformer ( CT), or two CTs.

To facilitat e doc um ent navigation, hyperlink s are often used to reference figures, tables and section

headings that are l oc at ed in other par ts of the document. All hyperlinks i n this document are highlight ed in

blue. Hyperlinks are used extensively to inc r ease the level of detail and clarity pr ov ided within each

section by refer enci ng other relevant parts of the document. To further facilitate document navigation, t his

document is published as a PDF docum ent with bookmarks enabled.

The reader is also encouraged to obt ain and review the documents listed in 8 Related Information on

page 162 of this document.

10 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 11

2 Hardware Description

2.1 Hardware Overview

The Teridian 71M6541D/F and 71M6542F single-chip energy meter ICs integrate all primary functional

blocks required to implement a solid-state residential electricity meter. Included on the chip are:

• An analog front end (AFE) feat uri ng a 22-bit second-order sigma-delta ADC

• An independent 32-bi t digital computation engi ne ( CE) to implement DSP functions

• An 8051-compatible microprocessor (MPU) whic h ex ecutes one i nstr uc tion per clock cycle (80515)

• A precision voltage reference (VREF)

• A temperature sensor for digital temperature c om pensation:

- Metrology digital temperature compensation (MPU)

- Automatic RTC digital temper ature compensation operational in all power states

• LCD drivers

• RAM and Flash memory

• A real time clock (RTC)

• A variety of I/O pins

• A power failure interr upt

• A zero-crossing interrupt

• Selectable cur r ent sensor interfaces for loc ally -c onnec ted sensors as well as isolated sensors (i .e.,

using the 71M6x01 companion IC with a shunt resistor sensor)

• Resistive Shunt and Cur r ent Transformers are supported

Resistive Shunts and Current Transformers (CT) current sensors are supported. Resistive shunt curr ent

sensors may be connected directly to the 71M654x device or i sol ated using a companion 71M6x01

isolator IC in order to implement a variety of single-phase / split-phase (71M6541D/F) or two-phase

(71M6542F) metering configurations. An inexpensive, small size pulse transformer is used to isolate the

71M6x01 isolated sensor from the 71M654x. The 71M654x performs digital communications bidirectionally with the 71M6x01 and also provi des power t o the 71M6x01 through the isolating pulse

transformer. Isolated (remote) shunt current sensors ar e c onnec ted to the differenti al input of the

71M6x01. Included on t he 71M6x01 companion isolat or chip are:

• Digital isol ation communications interface

• An analog front end (AFE)

• A precision voltage reference (VREF)

• A temperature sensor (for digital temperature compensation)

• A fully diff er ential shunt resistor sensor input

• A pre-amplifier to optimize shunt current sensor perform anc e

• Isolated power circ uitry obtains dc power fr om pul ses sent by the 71M654x

In a typical application, the 32-bit compute engine (CE) of the 71M654x sequentially processes the samples

from the voltage inputs on analog input pins and from the external 71M6x01 isolated sensors and pe r forms

calculations to measure ac tive energy (Wh) and reactive energy (VA Rh) , as well as A

quadrant metering. These measurements are then ac cessed by the M P U, processed further and output

using the peripheral dev ices available to the MPU.

In addition to ad vanced measurement func t ions , the c loc k func tion allows the 71M6541D/F and 71M6542F

to record time-of-use (TOU) metering information for multi-rate applications and to time-stamp tamper or

other events. Measurements can be displayed on 3.3 V LCDs commonly used in low-temperature

environments. An on-chip charge pum p is available to drive 5 V LCDs. Flexible mapping of LCD display

segments facilitate integration of existing custom LCDs. Design trade-off bet ween the number of LCD

segments and DIO pins can be im plem ented in software to accommodat e various requi r ements.

2

h, and V2h for four-

In addition to the temperature-trimmed ultra-precisi on vol tage reference, the on-chip digital temperatur e

compensation mechanism includes a temperature sensor and associated controls for correction of unwanted

temperature effects on measurement and RTC accuracy, e.g., to meet the requirements of ANSI and IEC

standards. Temperature-dependent ext ernal components such as crystal oscillator, resistive sh unts, current

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 11

Page 12

∆Σ ADC

CONVERTER

VREF

MUX

VREF

VREF

VADC

22

FIR

IBP

IAP

VADC10 (VA)

IAN

IBN

71M6541D/F

CE RAM

*IN = Optional Neutral Current

Local

Shunt

IN*

CT

I

LINE

or

CT

11/5/2010

I

LINE

transformer s (CT s) and their corresponding signal conditioning ci rcuit s can be char ac terized and their

correcti on factors can be programmed to produce electricity meters with exc eptional accuracy over the

industrial t e mper ature ran ge.

One of the two internal UARTs is adapted to support an Infrared L ED with internal drive and s ens e con figuration

and can als o function as a stan dard UART. The optical output can be modulated at 38 kHz. This flexibility

makes it possible t o im plem ent AM R meter s with an IR int erface. A block diagram of the IC is shown in

Figure 1.

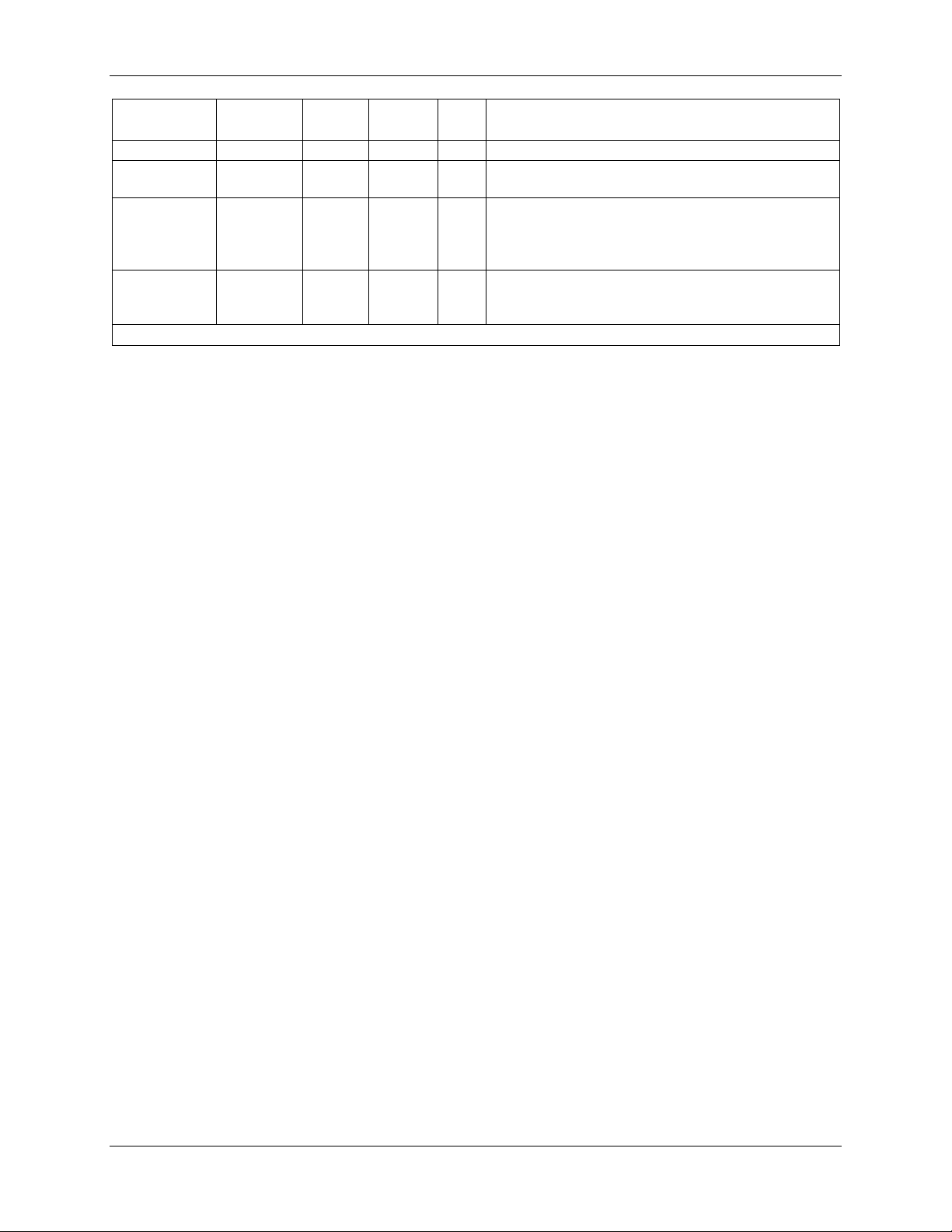

2.2 Analog Front End (AFE)

The AFE functions as a data acquisition system, controlled by the MPU. When used with locally

connected sensors, as seen i n Figure 2, the analog input signal s (IAP-IAN, VA and IBP-IBN) are

multiplexed to the ADC input and sampled by the ADC. The ADC output is decimated by the FIR filter

and stored in CE RAM where it can be accessed and proces sed by t he CE .

See Figure 6 for the m ultiplexer sequence correspondi ng to Figure 2. See Figure 35 for the meter

configurati on c or r espondi ng to Figure 2.

Figure 2. 71M6541D/F AFE Block Diagram (Local Sensors)

12 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 13

∆Σ ADC

CONVERTER

VREF

MUX

VREF

VREF

VADC

22

FIR

IBP

IAP

VADC10 (VA)

IAN

IBN

71M6541D/F

CE RAM

71M6x01

SP

SN

INP

INN

Remote

Shunt

IN*

Digital

Isolation

Interface

Local

Shunt

I

LINE

22

11/5/2010

* IN = Optional Neutral Current

∆Σ ADC

CONVERTER

VREF

MUX

VREF

VREF

VADC

22

FIR

IBP

IAP

VADC10 (VA)

IAN

IBN

71M6542F

CE RAM

Local

Shunt

IB

CT

IA

or

CT

11/5/2010

IA

VADC9 (VB)

Figure 3 shows the 71M6541D/F multiplexer interface with one local and one remote resistive shunt

sensor. As seen in Figure 3, when a remote isolated shunt sensor is connected via the 71M6x01, the

samples associated with this current channel are not routed to the multipl ex er, and ar e instead

transferred digitally to the 71M6541D/F via the digital isol ation interface and are dir ectly stored in CE

RAM.

See Figure 6 for the m ultiplexer timing sequence correspondi ng to Figure 3. See Figure 36 for the meter

configurati ons corr espondi ng to Figure 3.

Figure 3. 71M6541D/F AFE Block Diagram with 71M6x01

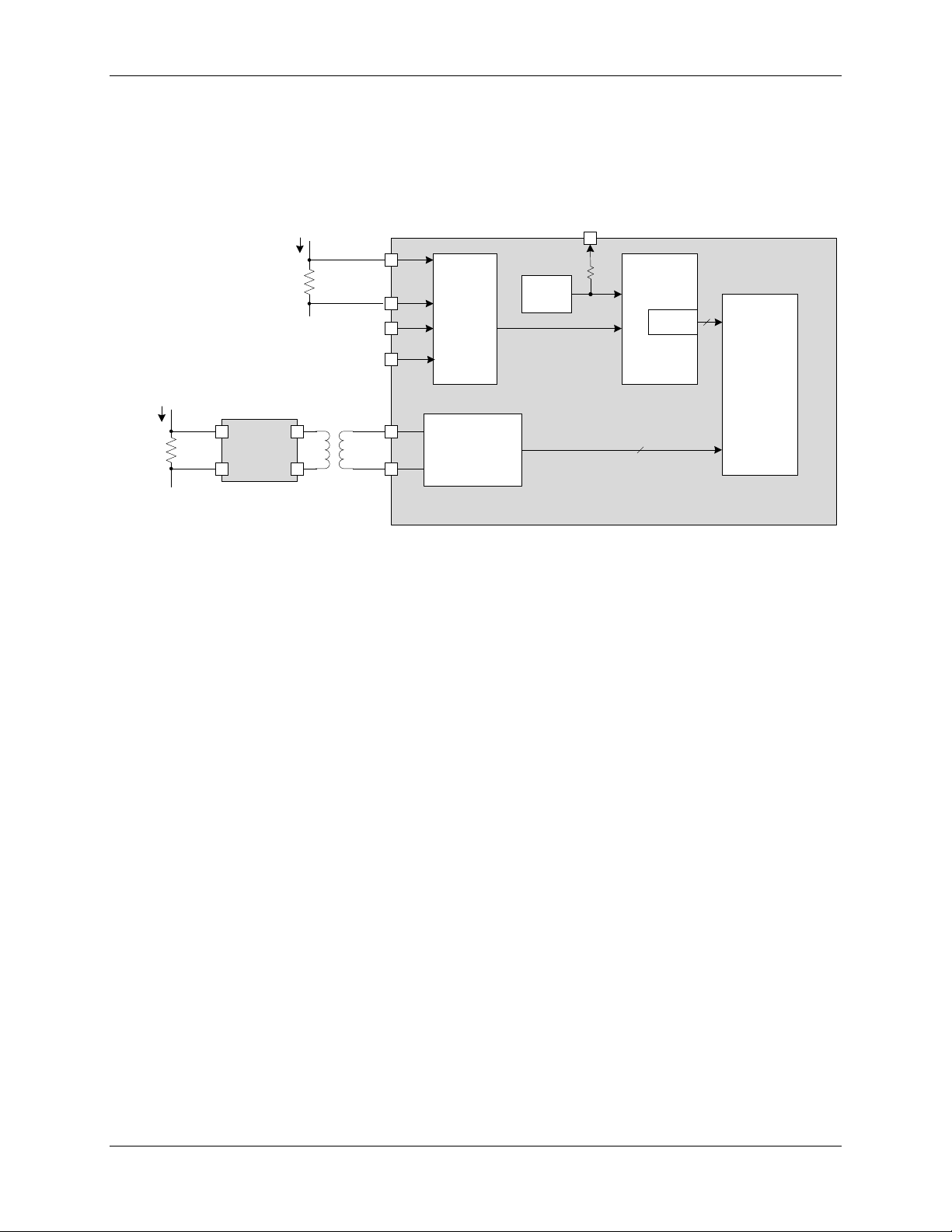

Figure 4 shows the 71M6542F AFE with locally connected sensors. The anal og input signals (IAP-IAN,

VA, IBP-IBN and VB) are multiplexed t o the ADC input and sampl ed by the ADC. The ADC out put is

decimated by the FIR filt er and stor ed in CE RAM where it can be accessed and processed by the CE.

See Figure 7 for the multiplexer timing sequence corresponding to Figure 4. See Figure 37 for the meter

configurati on c or r espondi ng to Figure 4.

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 13

Figure 4. 71M6542F AFE Block Diagram (Local Sensors)

Page 14

∆Σ ADC

CONVERTER

VREF

MUX

VREF

VREF

VADC

22

FIR

IBP

VADC9 (VB)

IAP

VADC10 (VA)

IAN

IBN

71M6542F

CE RAM

71M6x01

SP

SN

INP

INN

Remote

Shunt

IB

Digital

Isolation

Interface

Local

Shunt

IA

22

11/5/2010

Figure 5 shows t he 71M6542F multiplexer interface with one l oc al and one r em ote resistive shunt sensor.

As seen in Figure 5, when a remote isolat ed shunt sen sor is connected via the 71M6x01, the samples

associated with t his curr ent channel are not routed to the multi plex er , and are instead transferred digitally

to the 71M6542F via the digit al isolation interface and are di r ectly stored in CE RAM.

See Figure 6 for the multiplexer timing sequence corresponding to Figure 5. See Figure 38 for the meter

configurati ons corr espondi ng to Figure 5.

Figure 5. 71M6542F AFE Block Diagram with 71M6x01

2.2.1 Signal Input Pins

The 71M6541D/F f eatures five ADC inputs. The 71M6542F feat ur es six A DC input s.

IAP-IAN and IBP-IBN are intended for use as current sensor inputs. These four current sensor inputs can be

configured as four s ingle-ended inputs, or can be paired to form two differential inputs. For best

performance , it is reco m men ded to con figure the cu rrent sensor inputs as diffe ren tial inputs (i.e., IAP-IAN

and IBP-IBN). The first differential input (IAP-IAN) features a pre-amplif ier with a selectable gain of 1 or 8,

and is intended for dire c t conne ction to a shunt res istor sensor , and can also be us ed with a Cur ren t

Transformer (CT). The remaining differential pair (i.e., IBP-IBN) may be used with CTs, or may be enabled

to interface to a r emote 71M6x01 isolated current senso r providing isol ation for a sh unt resist or sensor using

a low cost pulse transformer.

The remaining input in the 71M6541D/F (VA) is single-ended, and is intended for sensing the line voltage in

a single-phase meter application using Equation 0 or 1 (see 2.3.4 Meter Equati ons on page 25). The

71M6542F features an additional single-ended voltage s ens ing input (VB) to su pport bi-phase applicat ions

using Equation 2. These s ingle-ended inputs are referenced to the V3 P3A pin.

All analog si gnal input pins measure voltage. In th e c ase of sh unt cur rent sensors, currents are sensed as a

voltage drop in the shunt resistor sens or . Referring to Figure 3, shunt sensors can be conne c ted dire c t ly to

the 71M654x (re ferre d to as a ‘loc al’ shunt sensor) or connec te d via an isolated 71M6x01 (referred to as a

‘remote’ shunt sensor). In the case of Cur ren t Transformers (CT), the current is measur ed as a voltage

across a bur den resistor that is connected to the secondary winding of the CT. Meanwhile, line voltages are

sensed through resistive voltage dividers. The VA and VB pins (VB is available in the 71M6542F only) are

single-ended and their c ommon return is the V3P3A pin.

Pins IAP-IAN can be programmed individually to be differential or single-ended as determined by the

DIFFA_E (I/O RAM 0x210C[4]) control bit. However, for most appli c ations, IAP-IAN are c onfigured as a

differential input to work wit h a shunt or CT directly interfaced to the IAP-IAN differential input with the

appropriate external signal conditioning components (see 4.2 Direct Connec tion of Sensors on page 92).

The performance of t he IAP-IAN pins can be enhanced by enabling a pr e-amplifier with a fixed gain of 8,

using the I/O RAM contr ol bit PRE_E (I/O RAM 0x2704[5]). When PRE_E = 1, IAP-IAN become the inputs

to the 8x pre-amplifi er, and the output of this amplifier is supplied to the multiplexer. The 8x amplification

14 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 15

71M6542F

(hex)

Eq. 0 or 1

Eq. 2

FIR_LEN[1:0]

210C[2:1] 1 1

2

ADC_DIV

2200[5] 1 1

0

PLL_FAST

2200[4] 1 1

1

MUX_DIV[3:0]

2100[7:4] 3 3

4

MUX0_SEL[3:0]

2105[3:0] 0 0

0

MUX1_SEL[3:0]

2105[7:4] A A

A

MUX2_SEL[3:0]

2104[3:0] 2 2

2

MUX3_SEL[3:0]

2104[7:4] 1 1

9

RMT_E

2709[3] 0 0

0

DIFFA_E

210C[4] 1 1 1 DIFFB_E

210C[5] 1 1

1

EQU[2:0]

2106[7:5]

0 or 1

0 or 1

2

CE Code

--

CE41A01

CE41A01

CE41A04

Equations

--

0 or 1

0 or 1

2

--

1 Shunt and 1 CT

2 CTs

1 Shunt and 1 CT

2 CTs

1 Shunt and 1 CT

2 CTs

Applicable Figure

--

Figure 2

Figure 4

Figure 4

during initialization.

is useful when current sensor s with low sensitivit y, such as shunt r esi stor s, ar e used. With PRE_E set, the

IAP-IAN input signal am plitude is restricted t o 31.25 mV peak.

For the 71M 654x application utilizing two shunt resistor s ens o rs (Figure 3), the IAP-IAN pins are configured

for differential mode to interface to a local shunt by setting the DIFFA_E control bit. Meanwhile , the IBP-IBN

pins are re-configured as digital balanced pair to communicate with a Teridian 71M6x01 Isolated Sensor

interface by setting t he RMT_E control bit (I/O RAM 0x2709[3]). The 71M6x01 communicates with the

71M654x using a bi-directional digital data stream through an isolating low -cost pulse transformer. The

71M654x also supplies power to the 71 M6 x01 through the isola ting transformer. This type of interface is

further described at the end of this chapter (see 2.2.8 71M6x01 Isolated Sensor Interface (Remote Sensor

Interface)).

For use with Current Transformers (CTs), as shown in Figure 2, the RMT_E control bit is reset, so that the

IBP-IBN pins are c onfigured as local analog inputs. The IAP-IAN pins cannot be configured as a remote

sensor interf ac e.

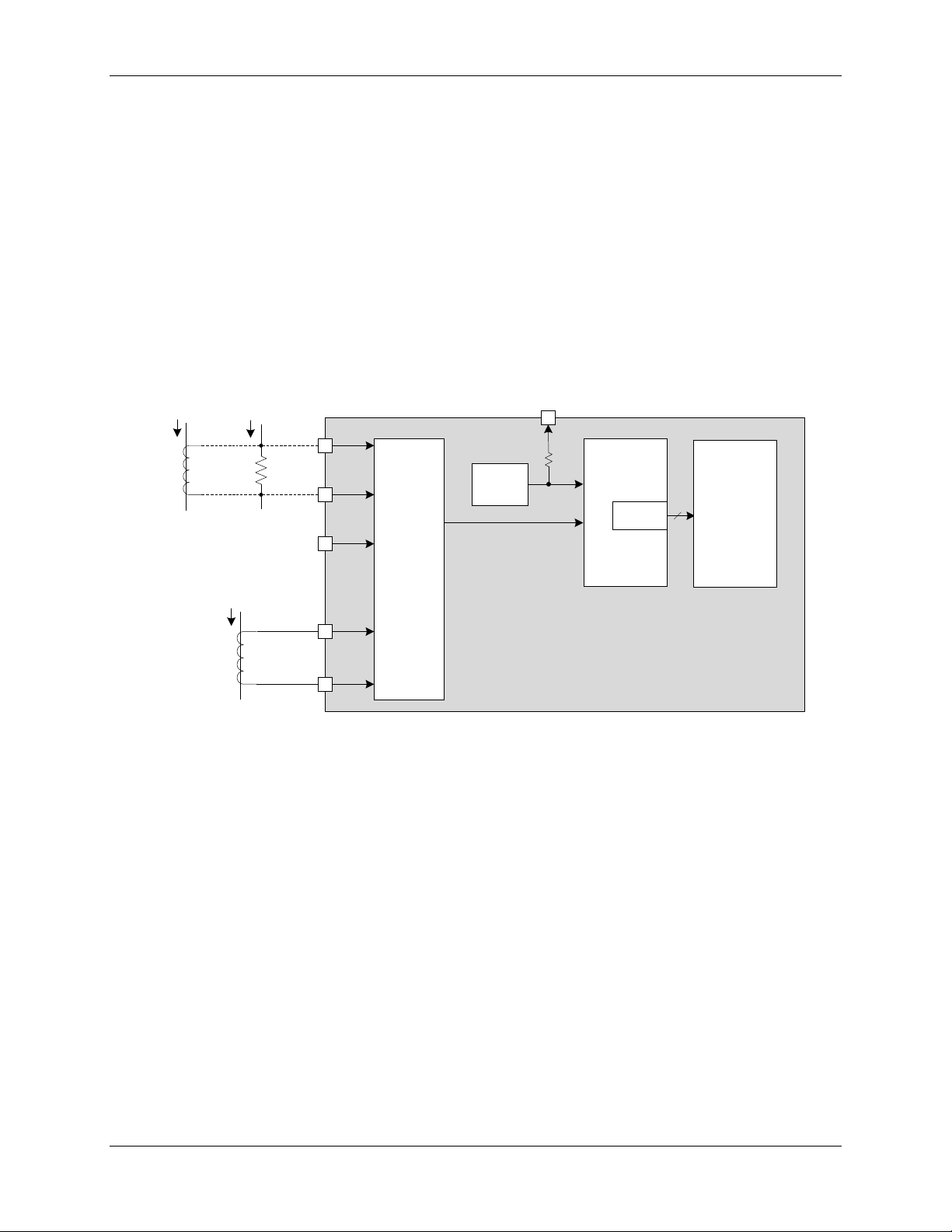

2.2.2 Input Mu lt ip le x e r

When operating with local sensors, the input multiplexer sequentially applies the input signals from the analog

input pins to the input of the ADC (see Figure 2 and Figure 4). One complete sampling sequence is called a

multiplexer frame. The multiplexer of the 71M6541D/F can selec t up to three input signals (IAP-IAN, VA, and

IBP-IBN) per multiplexer frame as controlled by the I/O RAM control field MUX_DIV[3:0] (I/O RAM

0x2100[7:4]) (see Figure 6). T he multiplex er of t he 71M65 42F add s the VB signal to achiev e a total of

four inputs (see Figure 7). T he mult iplex er al way s sta rts at state 1 an d pro ceed s unt i l as many s tat e s

as determined by MUX_DIV[3:0] have been conv er ted.

The 71M65 41D/ F an d 71M 65 42F ea ch re qui r e a uni que CE c ode that is written f or the spec ific

appli c ation. M oreover, each CE code r equire s specific AFE and MUX settings in or der to function

properly. Table 1 prov ides the CE code and settings corresponding to the local sensor c onfigurations

shown in Figure 2 and Figure 4. Table 2 pr ov ides the CE code and sett ings corresponding to the

local/remote sensor configuration utilizing the 71M6x01 as shown in Figure 3 and Figure 5.

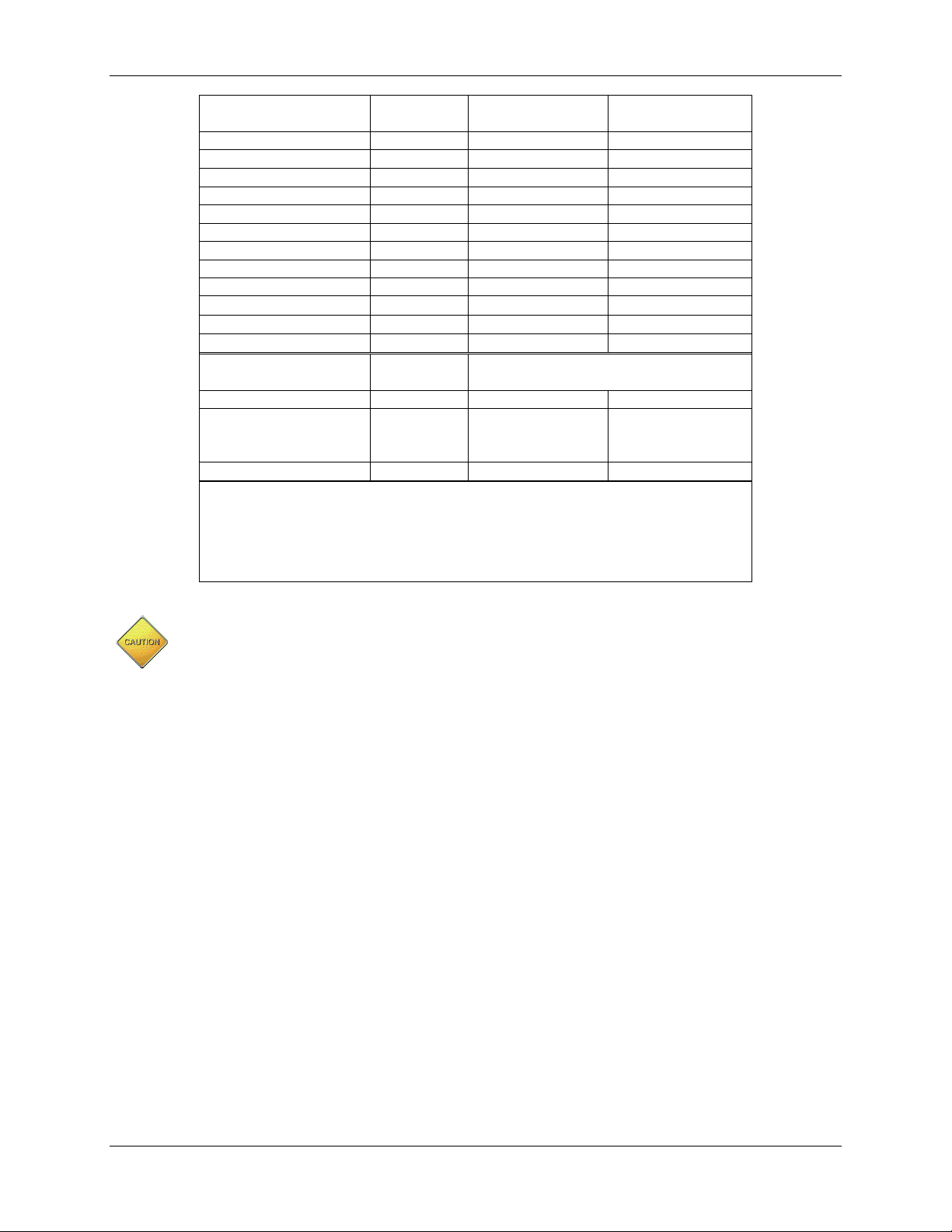

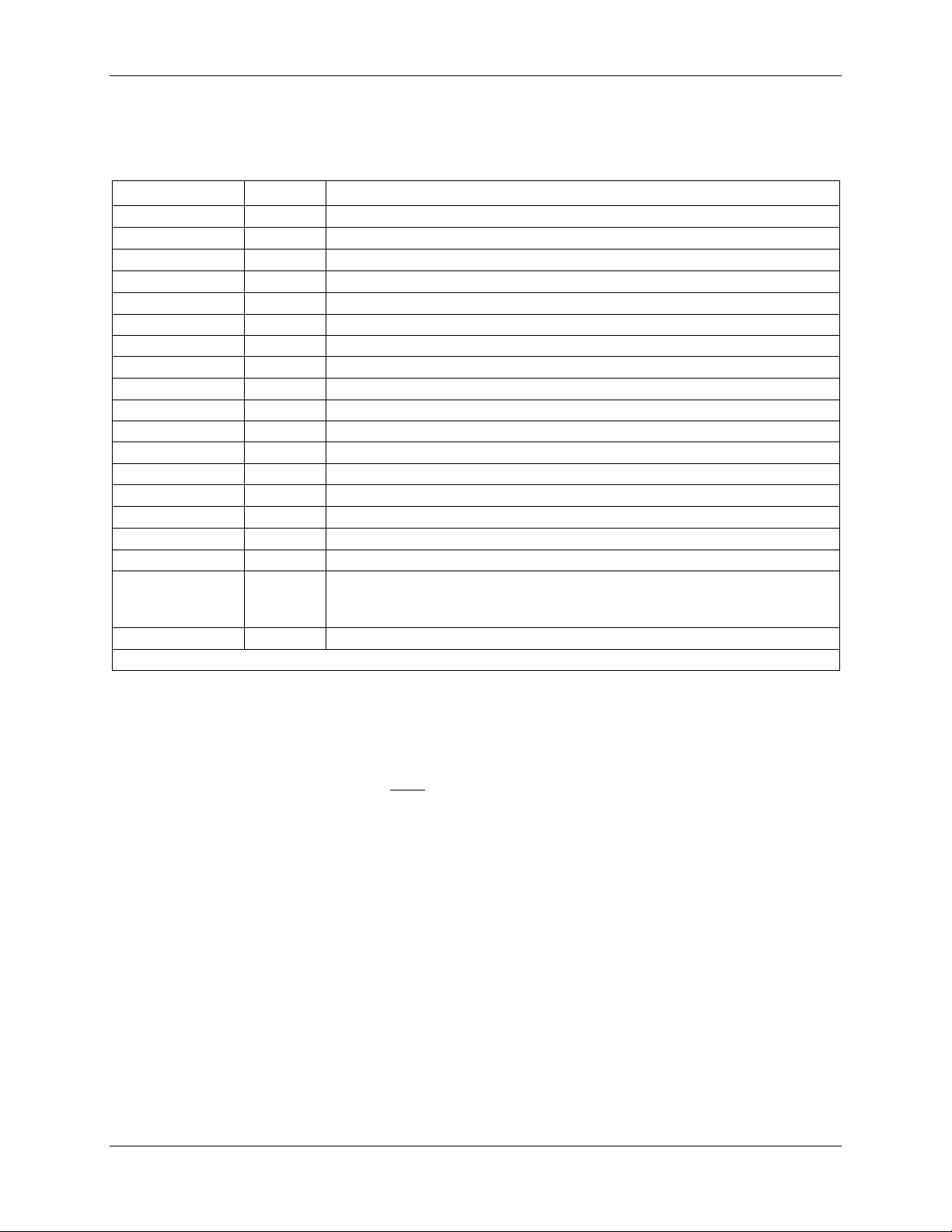

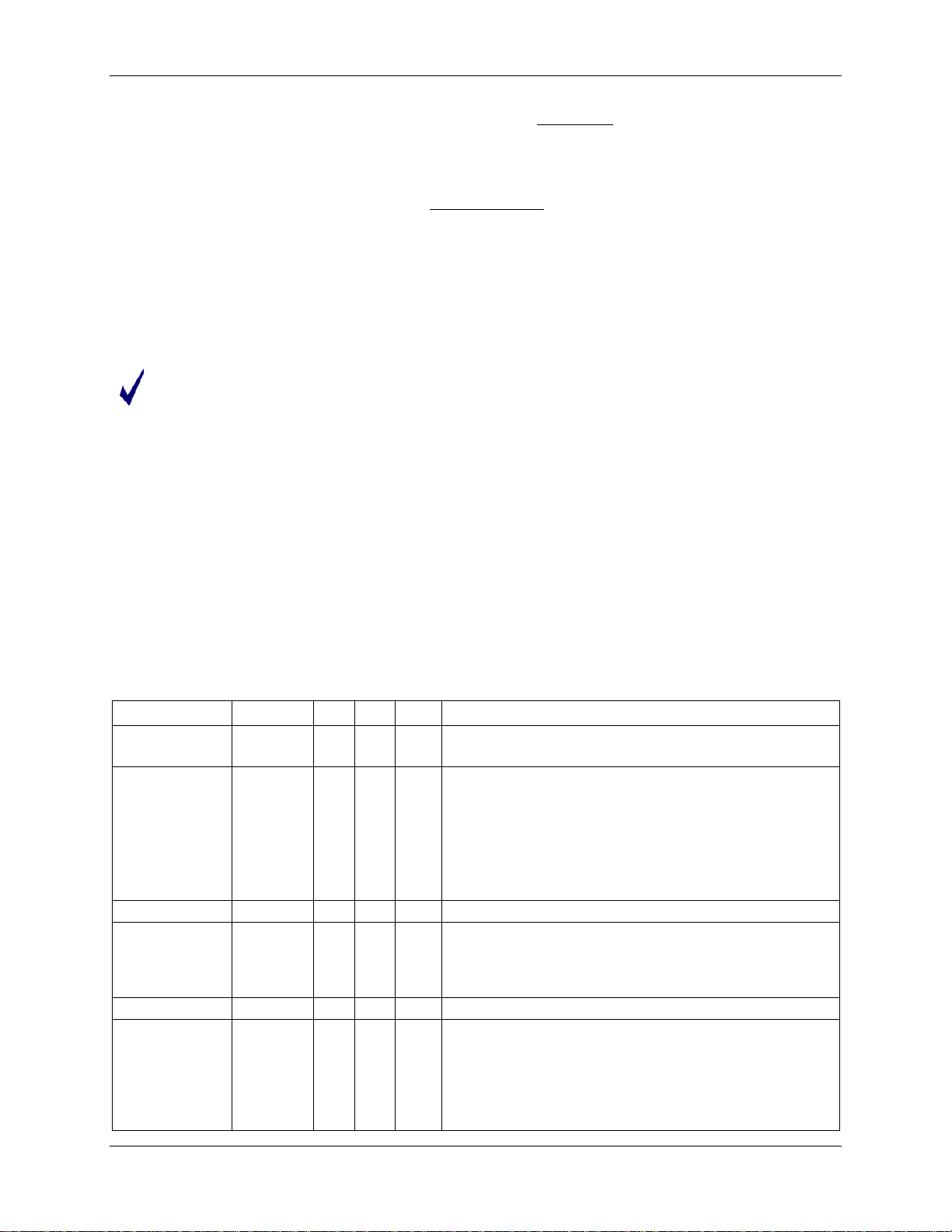

Table 1. Required CE Code and Settings for Lo cal Senso rs

I/O RAM

Mnemonic

Current Sensor Types

Notes:

TERIDIAN updates the CE code periodically. Please contact your local TERIDIAN representative to obtain the latest

CE code and the associated settings. The configuration presented in this table is set by the MPU demonstration code

I/O RAM

Location

71M6541D/E

(hex)

or

or

or

Table 2. Required CE Code and Settings for 71M6x01 isol at ed Sensor

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 15

Page 16

I/O RAM

Mnemonic

I/O RAM

Location

71M6541D/E

(hex)

71M6542F

(hex)

FIR_LEN[1:0]

210C[2:1] 1 1

ADC_DIV

2200[5] 1 1

PLL_FAST

2200[4] 1 1

MUX_DIV[3:0]

2100[7:4] 3 3

MUX0_SEL[3:0]

2105[3:0] 0 0

MUX1_SEL[3:0]

2105[7:4] A A

MUX2_SEL[3:0]1

2104[3:0] 1 9

MUX3_SEL[3:0]1

2104[7:4] 1 1

RMT_E

2709[3] 1 1

DIFFA_E

210C[4] 1 1

DIFFB_E

210C[5] 0 0

EQU[2:0]

2106[7:5]

0 or 1

0, 1 or 2

CE41B0162012

CE41B0166013

Equations

--

0, 1

0, 1 and 2

1 Local Shunt

1 Remote Shunt

1 Local Shunt

1 Remote Shunt

Applicable Figure

--

Figure 3

Figure 5

is set by th e MPU d em ons trati on c od e dur i ng in it i al iz ation.

CE Code --

Current Sensor Type --

Notes:

1. Although not used, set to 1 (the sample data is ignored by the CE)

2. 71M654x with 71M6201 remote sensor (200 Amps)

3. 71M654x with 71M6601 remote sensor (60 Amps)

TERIDIAN updates the CE code periodically. Please contact your local TERIDIAN representative

to obtain the latest CE code and the associated settings. The configuration presented in this table

and

and

Using settings for the I/ O RAM Mnemoni cs listed in Table 1 and Table 2 that do not match

those required by the corresponding CE co de being u sed results in unde sira bl e si de ef f ect s

and must not b e selected by the MPU. Consult your lo c al TERIDIAN repre se ntati ve to obtain

the correct CE co de and AFE / MU X s et t i ng s correspo nding to the application.

For a basic single-phase application, the IAP-IAN current input is configured for differential mode,

whereas the VA pin is single-ended and is typically connected to the phase voltage via a resistor divider.

The IBP-IBN differential input may be optionally used to s ens e the Neutral current. This configuration

implies that t he m ultiplexer applies a total of three inputs to the ADC. For this confi gur ation, the

multiplexer sequence is as shown in Figure 6. In this configuration IAP-IAN, IBP-IBN and VA are

sampled, the ext r a conversi on time slot (i.e., slot 2) is the optional Neutral curr ent, and the physical

current sensor for the Neutral current measurement m ay be omit ted if not required.

For a standard single-phase appl ication with tamper sensor in the neutral path, two current inputs can be

configured for differential mode, using the pin pair s IAP-IAN and IBP-IBN. This means that the multiplexer

applies a total of three inputs to the ADC. In this application, the system design may use two locally

connected current sensors via IAP-IAN and IBP-IBN, as show n in Figure 2, and configured as differential

inputs. Alternately, the IAP-IAN pin pair is con fig ure d as a diffe ren tial input and connected to a local current

shunt, and IBP-IBN is configured to connect to an isolated 71M6x01 isolated sensor (i.e., RMT_E = 1), as

shown in Figure 3. The VA pin is typically connected to the phase voltage via resistor div iders. For this

configuration, the multiplexer frame is also as sho wn in Figure 6 and time slot 2 is unused and ignored by

the CE, as the samples correspondi ng to the remote sensor (IBP-IBN) do not pass through the

multiplexer and are stored directly in CE RAM. The remote current sensor channel is sampled during t he

second half of the multiplexer frame and its timing rel ationship to the VA voltage is precisel y k nown so

that delay compensation can be properly applied.

The 71M6542F adds the ability to sample a second phase voltage (applied at the VB pin), which makes it

suitable for met er s with two voltage and two current sensors, such as m eters implementing Equation 2 for

dual-phase operation (P = VA*IA+VB*IB). Figure 7 shows the multiplexer sequence when four input s are

processed with l oc ally c onnec ted sensors, as shown in Figure 3. When using one loc al and one r em ote

senso r (Figure 5), the multiplexer sequence is also as shown in Figure 7.

16 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 17

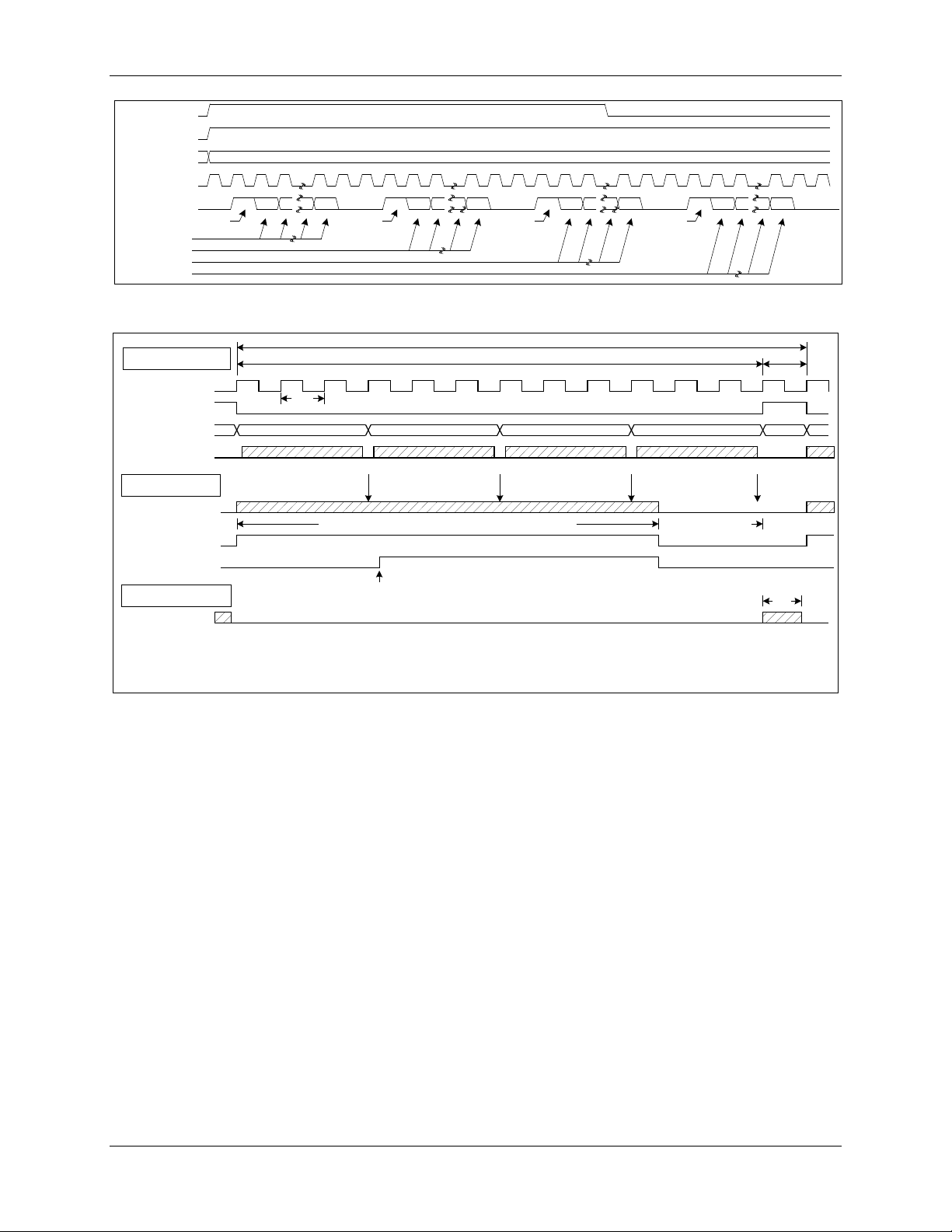

CK32

MUX STATE

00 1 2

MUX_DIV[3:0] = 3 Conversions

Settle

Multiplexer Frame

S

CROSS

MUX_SYNC

0S

11/5/2010

Fig. 2: IA VA IB

Fig. 3: IA VA Not Used

Fig. 5: IA VA VB

CK32

MUX STATE

0 1 2 3

MUX_DIV = 4 Conversions

Settle

Multiplexer Frame

S

CROSS

MUX_SYNC

0S

11/5/2010

Fig. 4: IA VA IB VB

disturbed.

For both multiplex er sequences sho wn in Figure 6 and Figure 7, the frame dur ation is 13 CK32 cycles

(where CK32 = 32768 Hz), t her ef or e, the resulting sample rate is 32768 Hz / 13 = 2520.6 Hz.

Table 3 summarizes the various AFE input configurations.

Figure 6: States in a Multipl exer Frame (MUX_DIV[3:0] = 3)

Figure 7: States in a Multipl exer Frame (MUX_DIV[3:0] = 4)

Table 3: ADC Input Configuration

Pin

ADC

Channel

IAP ADC0

IAN ADC1

Required

Setting

DIFFA_E = 1

Comment

Differential mode must be selected with DIFFA_E = 1 (I/O

RAM 0x21 0C[4]). The ADC results are stored i n CE RAM

location ADC0 (CE RAM 0x0), and ADC1 (CE RAM 0x1) is not

For locally connected sensors (Figure 2 and Figure 4), the

IBP ADC2

differential input must be enabled by setting DIFFB_E (I/O

RAM 0x21 0C[5].

IBN ADC3

DIFFB_E = 1

or

RMT_E = 1

For the r emote connected sensor (Figure 3 and Figure 5)

with a remote shunt sensor, RMT_E (I/O RAM 0x2709[3])

must be set.

In both cases , the ADC results are stored in RA M loca tion

ADC2 (CE R AM 0x2 ), and ADC3 (CE RAM 0x3 ) is not

disturbed.

VA ADC10 --

VB ADC9 --

Multiplexer adv anc e, FIR initiation and chopping of the ADC reference voltage (using the internal CROSS

signal, see 2.2.7 Voltage References) are cont r olled by the internal MUX_CTRL circuit. Additionally,

v1.1 © 2008–2011 Teridian Semiconductor Cor por ation 17

Single-ended mode only . The ADC resul t is stored in RAM

location ADC10 (CE RAM 0xA).

Single-ended mode only ( 71M 6542F only). The ADC result

is stored in RAM location ADC9 (CE RAM 0x9).

Page 18

MUX_CTRL launches each pass of the CE through its code. Conceptually, MUX_CTRL is clocked by

CK32, the 32768 Hz clock from the PLL block. The behavior of the MUX_CTRL circuit is governed by:

• CHOP_E[1:0] (I/O RAM 0x2106[3:2])

• MUX_DIV[3:0] (I/O RAM 0x2100[7:4])

• FIR_LEN[1:0] (I/O RAM 0x210C[2:1])

• ADC_DIV (I/O RAM 0x2200[5])

The duration of each multiplexer state depends on the number of ADC sampl es processed by the FI R as

determined by the FIR_LEN[1:0] (I/O RAM 0x210C[2:1] control field. Each multiplexer state starts on the

rising edge of CK32, t he 32-kHz clock.

It is recomm ended that MUX_DIV[3:0] (I/O RAM 0x220 0[ 2:0]) be s et to zero whi le cha nging the ADC

confi guration. Although not required, it minimizes system transients that might be caused by momentary

shorts between the AD C inpu ts, especially when changing the DIFFn_E control bits (I/O RAM 0x210C[5:4]).

After the configuration bits are set, MUX_DIV[3:0] should be set to the required value.

Additionall y , t he ADC can be configured to operate at ½ rate (32768*75=2.46MHz). In this mode, the

bias current to the ADC am plifiers is reduced and overall system power i s reduced. The ADC_DIV (I/O

RAM 0x2200[5]) bit selects full speed or half speed. At half speed, if FIR_LEN[1:0] is set to 01 (288),

each conversion requir es 4 XTAL cy cl es, r esul ting in a 2520Hz sample rate when MUX_DIV[3:0] = 3.

Note that in order to work with these power-reduci ng se ttings, a corresponding CE c ode is required.

The duration of each time sl ot in CK32 cycles depends on FIR_LEN[1:0], ADC_DIV and PLL_FAST:

Time_Slot _Dur ation (PLL_FAST = 1) = (FIR_LEN[1:0]+1) * (ADC_DIV+1)

Time_Slot _Dur ation (PLL_FAST = 0) = 3*(FIR_LEN[1:0]+1) * (ADC_DIV+1)

The duration of a multiplexer frame in CK32 cycles is:

MUX_Frame_Durati on = 3-2*PLL_FAST + Time_Slot_Duration * MUX_DIV[3:0]

The duration of a multiplexer frame in CK_FIR c ycle s is:

MUX frame duration (CK_FI R c ycles) =

[3-2*PLL_FAST + Time_Slot_Dur ation * MUX_DIV] * (48+PLL_FAST*102)

The ADC conversion sequence is progr ammable through the MUXx_SEL control fields (I/O RAM 0x2100

to 0x2105). As stated above, there are three ADC time slots in the 71M6541D/F and four ADC time slots

in the 71M6542F, as set by MUX_DIV[3:0] (I/O RAM 0x2100[7:4]). In the expression MUXx_SEL[3:0] = n, ‘x’

refers to the multiplexer frame time slot number and n refers to the desired ADC input number or ADC handle

(i.e., ADC0 to ADC10, or simply 0 to 10 decimal). Thus, there are a total of 11 valid ADC handles in the

71M654x devices. For example, if MUX0_SEL[3:0] = 0, then ADC0, corresponding to the sample from the

IAP-IAN input (configured as a differential input), is positioned in the multiplexer frame during time slot 0. See

Table 1 and Table 2 f or the appropriate MUXx_SEL[3:0] settings and other settings applic able to a

particular CE code.

Note that whe n the remote s ensor interface is enabled, and even though th e samples corresponding to

the remote sensor current (IBP-IBN) do not pass t hrough the mul tiplexer, the MUX2_SEL[3:0] and

MUX3_SEL[3:0] control fields must be written wit h a v alid ADC handle that is not being used. Typically,

ADC1 is used for this purp ose (see Table 2). I n this manne r , the ADC1 handle, whic h is not used i n the

71M6541D/F or 71M65 42F, i s used a s a place holder in the multiplex er fram e, in order to gener ate th e

correct multiplexer frame sequence and the correct s ampl e r ate. The re sul ti n g sampl e dat a st or ed in

CE RAM 0x1 is undefined and is ignored by the CE code. Meanwhile, the digital isol ation interface t akes

care of automatically storin g the sample s for the remote interfac e current (IBP-IBN) in CE RAM 0x2.

Delay compensati on and other functions in the CE code require the settings for MUX_DIV[3:0],

MUXx_SEL[3:0], RMT_E, FIR_LEN[1:0], ADC_DIV and PLL_FAST to be fixed for a given CE code.

Refer to Table 1 and Table 2 for the settings that are applicable to the 71M6541D/F and

71M6542F.

18 © 2008–2011 Teridian Semiconductor Corporati on v1.1

Page 19

MUX5_SEL[3:0]

MUX6_SEL[3:0]

2102[3:0]

Selects the ADC input conver ted during time slot 6.

2102[7:0]

Selects the ADC input conver ted during time slot 7.

MUX9_SEL[3:0]