Datasheet QL82SD-4PT280C, QL82SD-4PT280I, QL82SD-4PT280M, QL82SD-5PB516C, QL82SD-5PB516M Datasheet (QUICK LOGIC)

...

© 2002 QuickLogic Corporation

•

•

•

•

•

•

• • • • • •

Preliminary

1

www.quicklogic.com

Device Highlights

LVDS SERDES Basic Features

• 10 High Speed Bus LVDS Serial Links—

bandwidth up to 5 Gbps

• Eight Independent Bus LVDS serial

transceivers with operating speeds to 632

Mbps per channel

• Two Independent Bus LVDS clock serial

transceivers with operating speeds to

400 MHz per channel

• Integrated clock and data recovery (CDR)

with no external analog components

required

• CDR bypass for applications with external

clock source

• Programmable serial to parallel

configuration

• 10-bit data width—with

• clock recovery

• 4-bit, 7-bit and 8-bit data widths—

with external clock

• 1-bit asynchronous level conversion

• Fast Lock and Random (auto) Lock capable

• Lock signal feedback

• I/O support for LVTTL, LVCMOS, PCI,

GTL+, SSTL2, SSTL3, LVDS, LVPECL

• Low Power/Independent power-down

mode for each SERDES channel

• IEEE1149.1 JTAG Support &

boundary scan

• Operation over PCB or backplane traces, or

across twisted pair cabling up to 25 m

• Point-to-Point, Multi-Point, and Multi-Drop

Support

• Pre-Emphasis Control on each LVDS

Channel Link

Extended Features

The following can be implemented into the

programmable logic:

• UTOPIA Level 2, 16-bit wide System

interface (up to 50 MHz) with parity support

for ATM applications

• UTOPIA Level 3 compatible 8-bit wide

system Interface (up to 100 MHz) with parity

support for ATM applications

• CSIX-L1 32-bit switch fabric interface (up to

100 MHz)

• Supports Generic 8,16,32-bit

microprocessor bus interface for

configuration, control and status monitoring

• Supports Generic 32, 64-bit peripheral bus

interface for bridging functions

Flexible Programmable Logic

• 2,016 Programmable Logic Cells

• 536 K System Gates

• Muxed architecture; non-volatile technology

• Completely customizable for any digital

application

Dual Port SRAM Blocks

• 36 Dual Port SRAM Blocks

• Configurable array sizes (by 2, 4, 9, 18)

• < 3 ns access times, FIFO capable of over

300 MHz

• Configurable as RAM or FIFO

QL82SD Device Data Sheet

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

2

Programmable I/O

• Up to 252 Programmable I/O pins

• High performance Enhanced I/O (EIO): Less than 3 ns Tco

• Programmable Slew Rate Control

• Programmable I/O Standards

• LVTTL, LVCMOS, PCI, GTL+, SSTL2, and SSTL3, LVDS, LVPECL

• Four Independent I/O Banks

• Three Register Configuration: Input, Output, OE

Embedded Computational Unit (ECU) Blocks

• Integrated multiply, add, and accumulate function

• 18 distributed MAC blocks

• 8 × 8 multiply (sign & unsigned)

• 16-bit carry add

Advanced Clock Network

• Nine Global Clock Networks consisting of:

• one dedicated

• eight programmable

• Eight I/O (high drive) networks: two I/Os per bank

• Ten Quad-Net Networks—five per quadrant

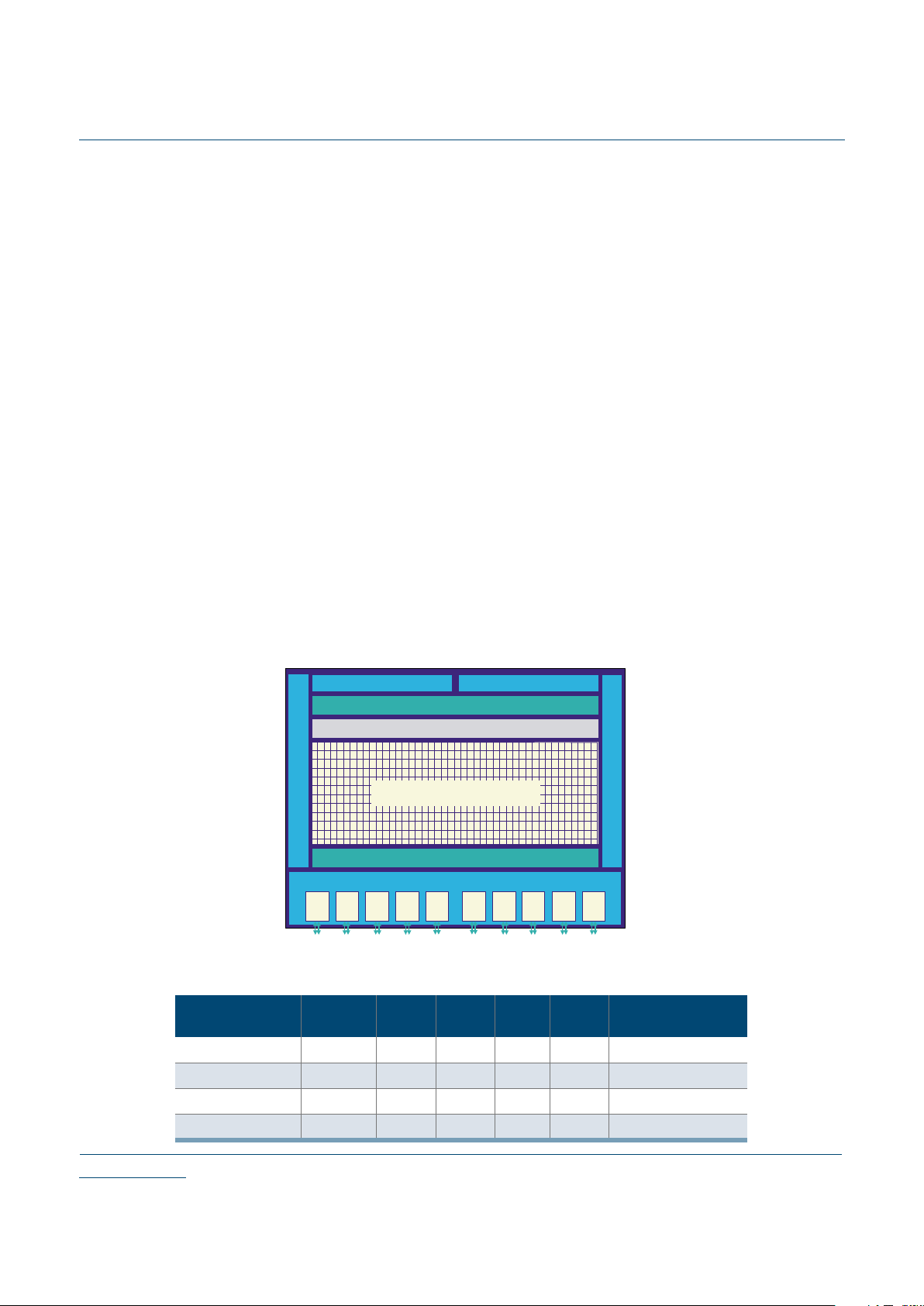

Figure 1: QL82SD Device Block Diagram

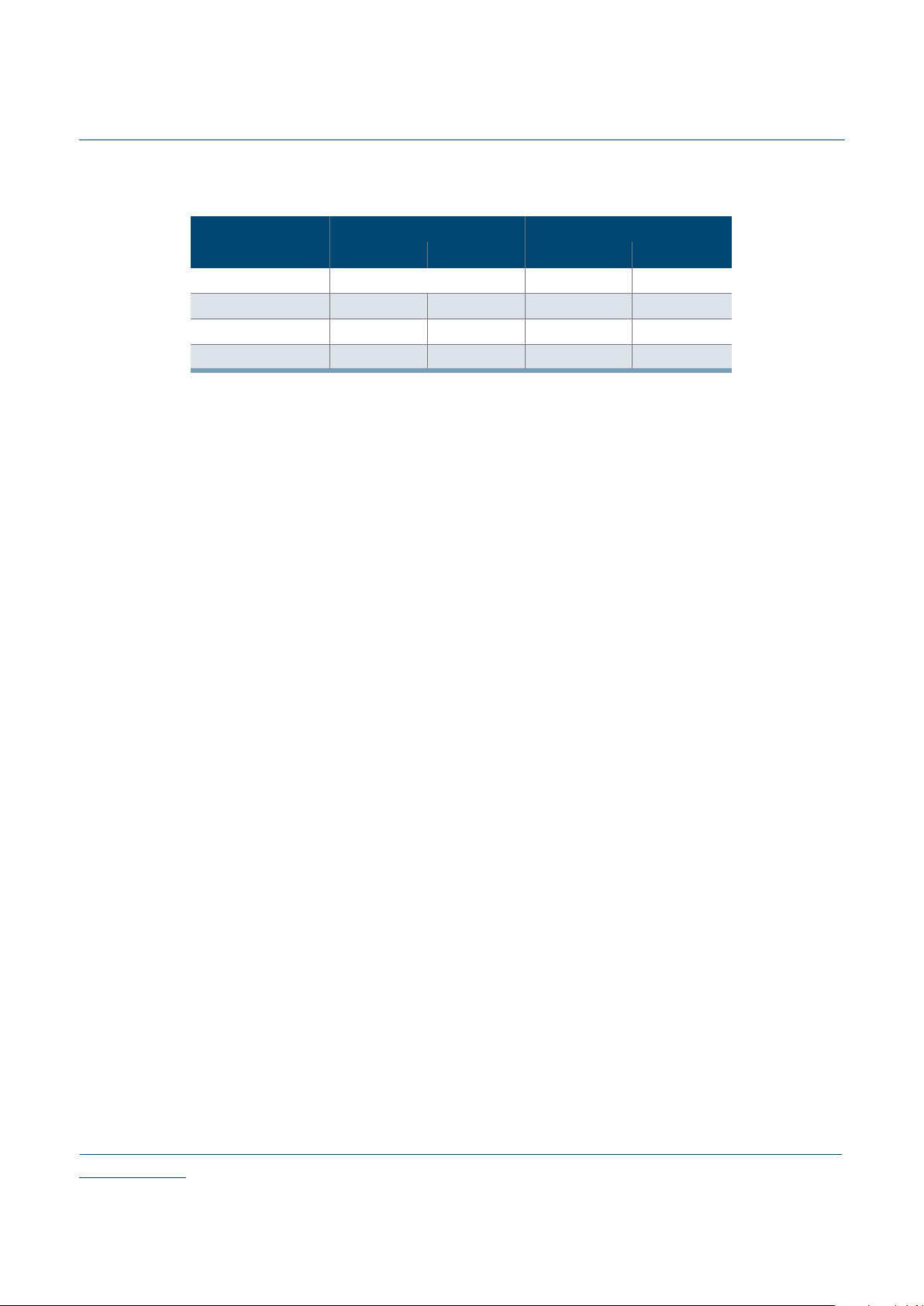

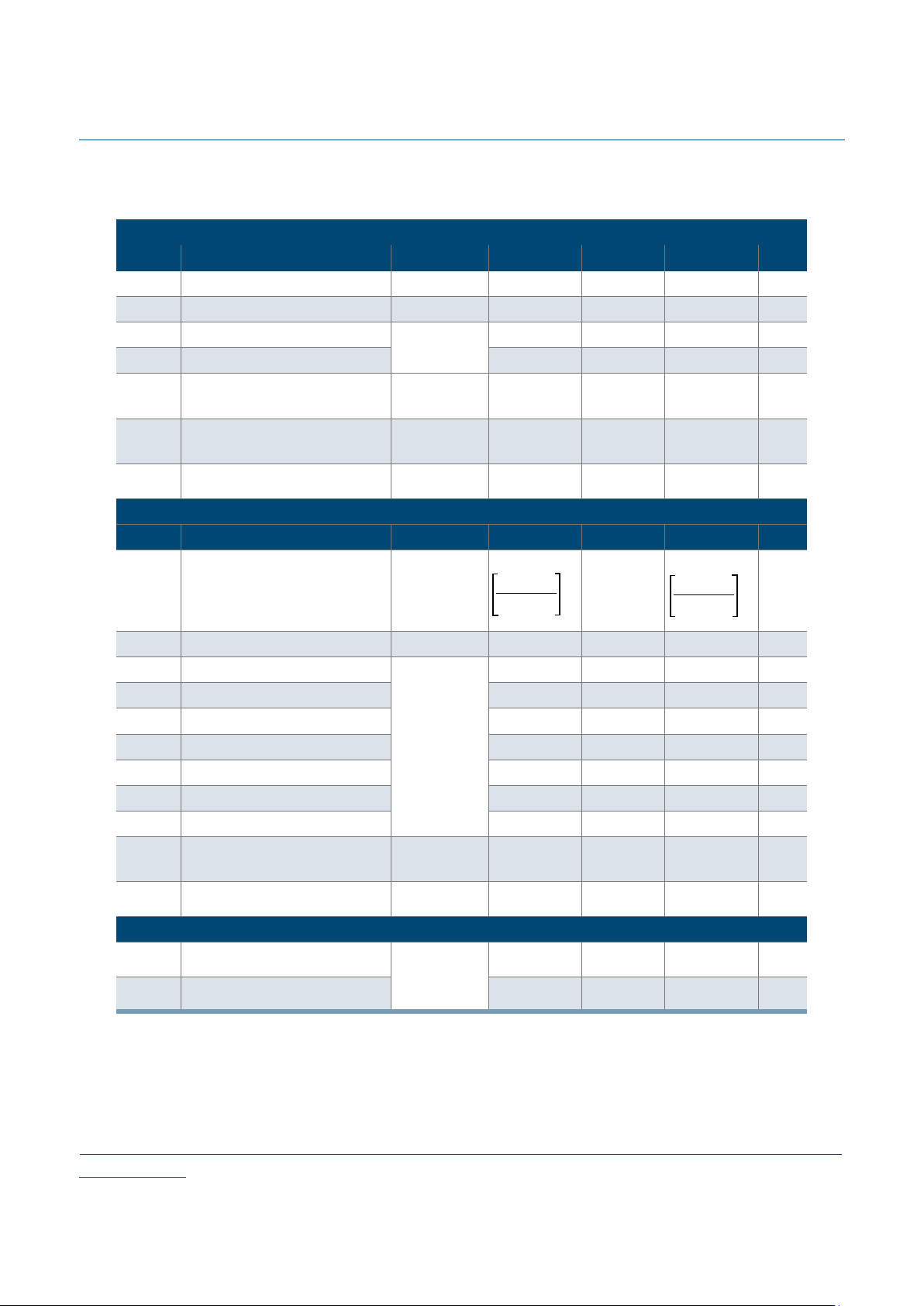

Table 1: QL82SD Device Table

Customer Part #

SERDES

Data

LV DS

Clocks

SRAM

Blocks

Logic

Cells

ECU

Blocks

Programmable I/O

QL82SD-PQ208 4 2 36 2016 18 75

QL82SD-PT280 8 2 36 2016 18 121

QL82SD-PS484 8 2 36 2016 18 209

QL82SD-PB516 8 2 36 2016 18 252

RAM Blocks

Embedded Computational Units (ECUs)

RAM Blocks

IO Block IO Block

IO Block

2016 Logic Cells

CLKB

CH7

CH6

CH5

CH4

CH3

CH2

CH1

CH0

CLKA

LVDS/SERDES IO Block

IO Block

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

3

www.quicklogic.com

General Description

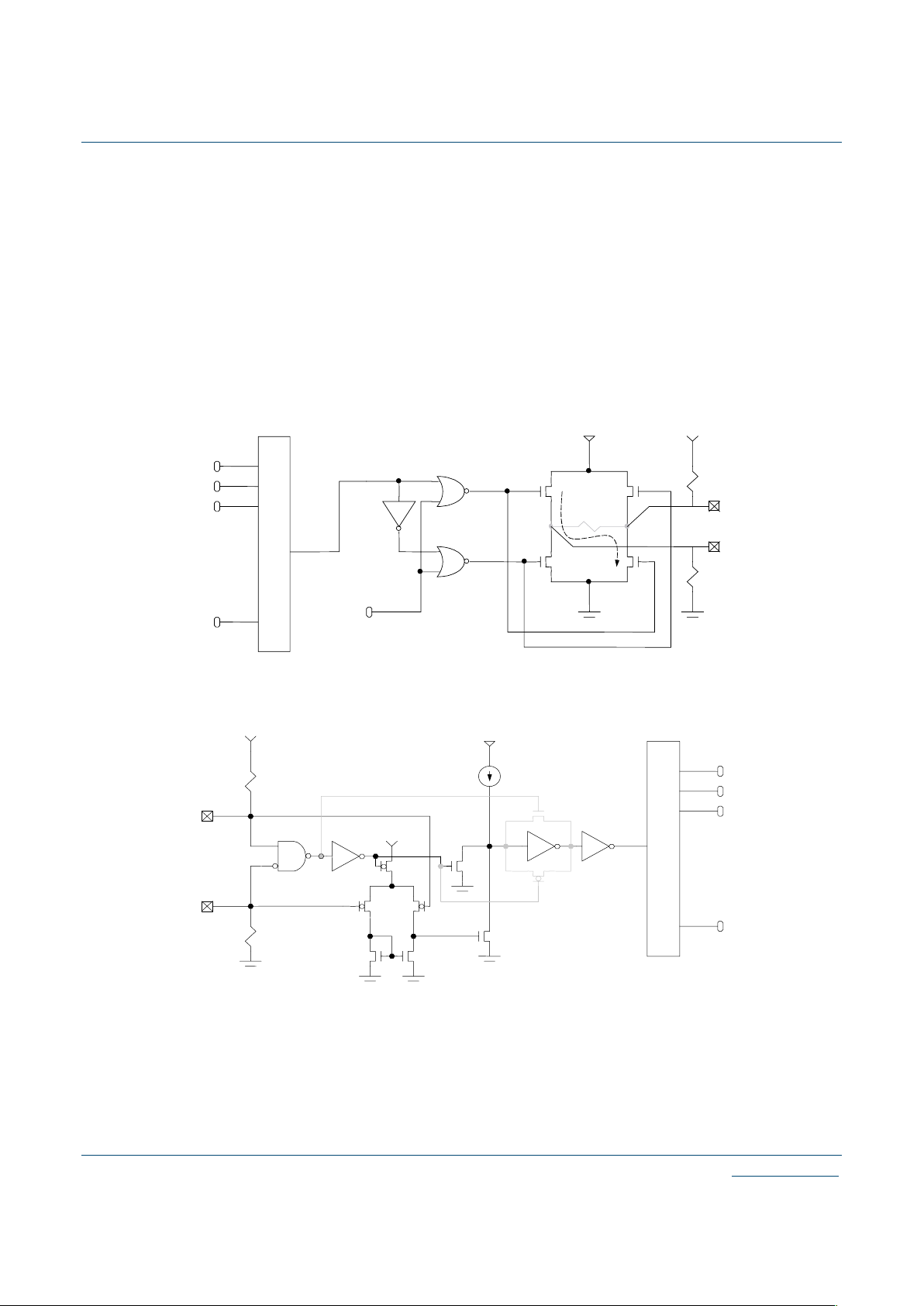

LVDS SERDES Transmitter and Receiver

A QuickSD LVDS SERDES device in serializer mode takes a parallel data bus and a separate

clock and converts them into a serial data stream. In deserializer mode, it takes a serial data

stream and converts it to a configurable bit wide parallel data bus and separate clock. The

reduced number of I/O board traces and cable connectors saves on cost and significantly

simplifies design. Skew and timing issues are significantly reduced and performance is

enhanced.

Figure 2 and Figure 3 illustrate the block diagrams of the QuickSD device

transmitter and receiver.

Figure 2: LVDS SERDES Transmitter Block Diagram

Figure 3: LVDS SERDES Receiver Block Diagram

RL = 2 7

Ω

- 100ΩVo +

Vo -

IL = 8-12 mA

Do +

Do -

300k

300k

/E nabl e

Parallel to Serial

.

.

.

.

txd [9:0]

TTL_Din

Din +

Din -

300k W

300k W

VCM = 0.2 V - 2.2 V

Serial to Parallel

.

.

.

.

FPGA

rxd [9:0]

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

4

LVDS SERDES Applications

The QuickSD device is designed to address the need for high-speed serial communications.

It maintains the features of standard discrete SERDES devices, but integrates these features

with customizable logic to allow for the highest degree of flexibility, performance, and

integration at the lowest cost. The QuickSD device is designed to support both transmit and

receive requirements in a single chip. The device can support multiple channels in a variety

of modes (with or without clock recovery,) a variety of translation widths (1:1 to 1:10), as

well as a range of frequencies. These capabilities make this device ideal in applications where

the performance is critical and customization is required.

The QuickSD device targets three applications: on-board, board-to-board (via common

backplane), and box-to-box (via common cable).

Software Support

The turnkey QuickWorks package from QuickLogic provides the most complete ESP and

FPGA software solution from design entry to logic synthesis, to place and route, and to

simulation. The package provides a solution for designers who use third-party tools from

Cadence, Mentor, OrCAD, Synopsys, Viewlogic, Veribest and other third-party tools for

design entry, synthesis, or simulation. A power calculator is also provided for SERDES power

consumption.

To speed up the QuickSD design process, QuickLogic includes a SERDES Wizard in its

QuickWorks package. This wizard simplifies the process of configuring the multi-channel

SERDES core into each of its modes. For details on the SERDES Wizard, please refer to "The

QL82SD Quickstart Design Guide". To find this guide go to the QuickSD device

documentation Web page at

http://www.quicklogic.com/home.asp?PageID=315&sMenuID=199#Order.

Process Data

QuickSD is fabricated on a 0.25 µ, five-layer metal CMOS process. The core voltage is

2.5 Volt V

CC

supply and 3.3 V tolerant I/O with the addition of 3.3 Volt V

CCIO

. QuickSD is

available in commercial and industrial temperature grades.

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

5

www.quicklogic.com

Ordering Information

Maximum Ratings and Operating Range

Table 2: Absolute Maximum Electrical Ratings

VCC Voltage -0.3 V to 4 V

Bus LVDS Driver

Output Voltage

-0.3 V to +2.8 V

LVCMOS/LVTTL

Input Voltage

-0.3 V to (V

CC

+ 0.3 V)

Bus LVDS Output Short

Circuit Duration

10 mS

LVCMOS/LVTTL

Output Voltage

-0.3 V to (V

CC

+ 0.3 V) ESD Rating HBM 2 kV

Bus LVDS Receiver

Input Voltage

-0.3 V to +2.8 V

Table 3: Absolute Maximum Thermal Ratings

Junction Temperature +150°C

Lead Temperature

(Soldering, 4 seconds)

+260°C

Storage Temperature -65°C to +150°C

Thermal and Power

Dissipation

Characteristics

See the following table

Table 4: Thermal and Power Dissipation Characteristics

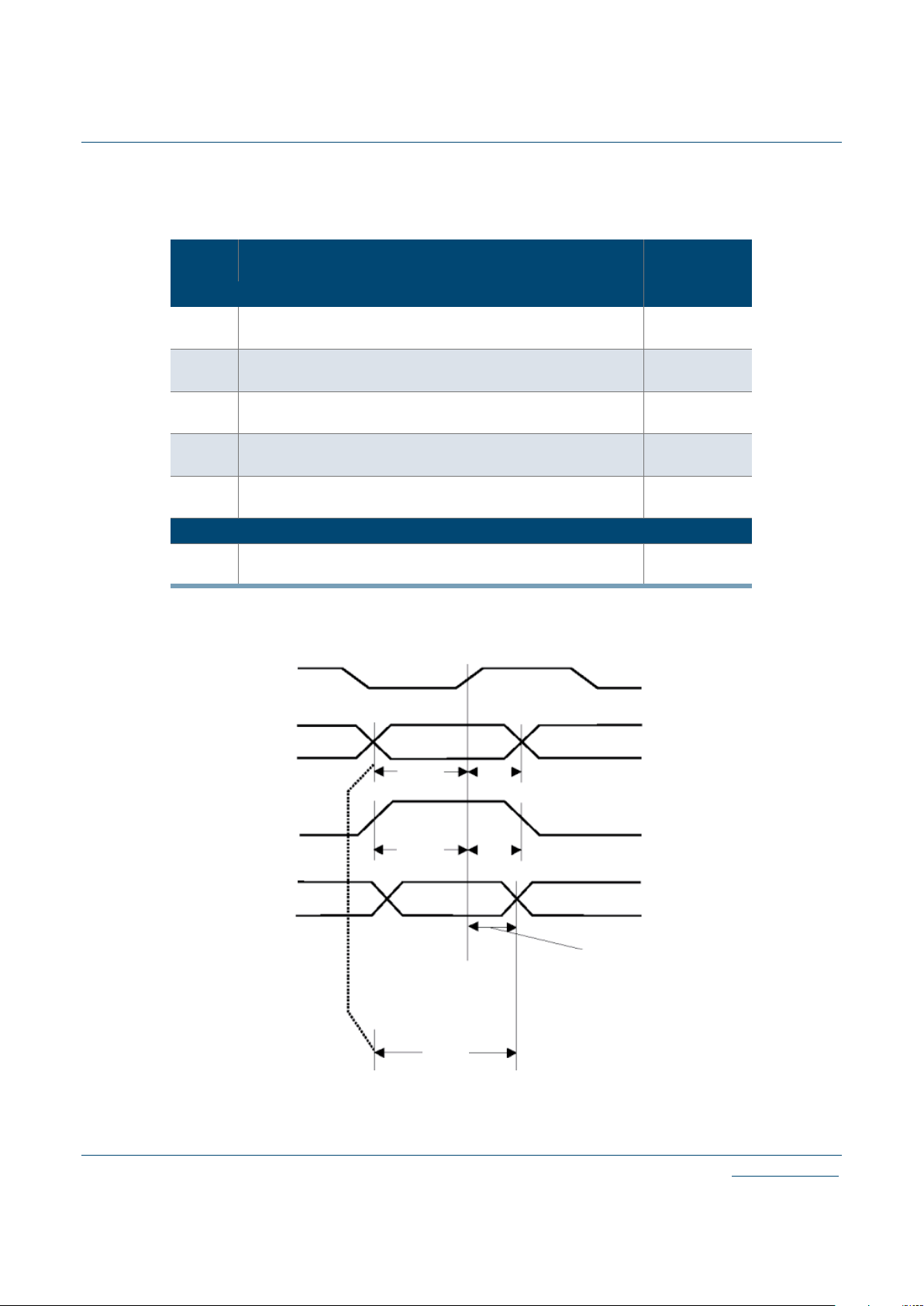

Package 0ja (*C/W vs. Airflow 0jc (*C/W)

Estimated Maximum

Power Dissipation (W)

0.0 0.5 1.0 2.0

PQ208 26.0 24.5 23.0 22.0 11.0 1.65

QL 82SD - 4 PB516 C

QuickLogic device

QuickSD device

part number

Speed Grade

4 = Quick

5 = Fast

6 = Faste r

7 = Faste st

Package Code

PQ208 = 208-pin FPBGA

PT280 = 280-pin BGA (1.0mm)

PS484 = 484-pin BGA (1.0mm)

PB516 = 516-pin BGA (1.27mm)

Operating Range

C = Commercial

I = Industrial

M = Military

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

6

Electrical Specifications - LVDS SERDES

LVDS SERDES Transceiver Capability (Speed)

General Test Conditions

All tests are done for the 484-pin BGA package (1.00 mm pitch). The tests are set up so

that an LVDS SERDES channel of a QL82SD transmits, and the other LVDS SERDES

channel of the same device (or another QL82SD device) receives. All results are given as

worst cases over commercial temperature, VCC, and process, with PLLVCC = 2.5 V unless

otherwise specified.

If the QL82SD device is used only for transmit or receive, but not both simultaneously, the

performance can be significantly better, and, in many cases, exceeds 1 Gb/s per channel.

NOTE:

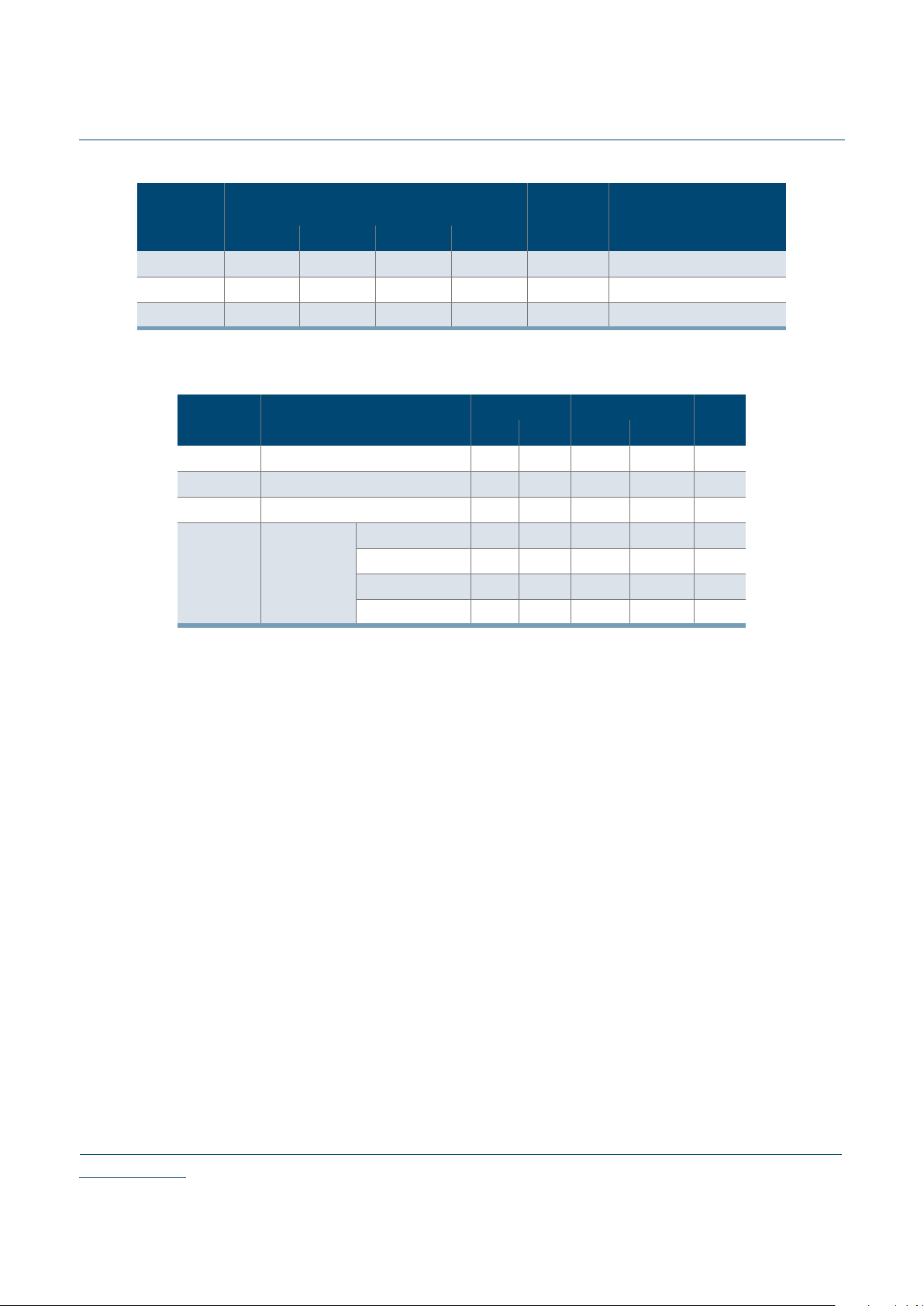

All data are in Mb/s. Low/High frequencey refers to internal SERDES PLL lock

range (see

Table 29 on page 31 for more information).

PT280 18.5 17.0 15.5 14.0 7.0 2.24

PS484 28.0 26.0 25.0 23.0 9.0 2.42

PB516 20.0 19.0 17.5 16.0 7.0 2.51

Table 5: Operating Ranges

Symbol Parameter Industrial Commercial Unit

Min Max Min Max

Vcc Supply Voltage 2.3 2.7 2.3 2.7 V

Vccio I/O Input Tolerance Voltage 2.3 3.6 2.3 3.6 V

T

A

Ambient Temperature -40 85 0 70 °C

K Delay Factor

-4 Speed Grade 0.43 2.16 0.47 2.11 n/a

-5 Speed Grade 0.43 1.80 0.46 1.76 n/a

-6 Speed Grade 0.43 1.26 0.46 1.23 n/a

-7 Speed Grade 0.43 1.14 0.46 1.11 n/a

Table 4: Thermal and Power Dissipation Characteristics

Package 0ja (*C/W vs. Airflow 0jc (*C/W)

Estimated Maximum

Power Dissipation (W)

0.0 0.5 1.0 2.0

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

7

www.quicklogic.com

Cable - Normal Operation

NOTE:

Test Conditions: Up to 3-meter Category 5 Cable without any compensation.

Cable - High Speed Operation

NOTE:

Test Conditions: Up to 9" Category 5 Cable, and reference design in the

programmable fabric portion of the device for internal skew compensation for channel link

modes.

Backplane - Normal Operation

NOTE:

Test Conditions: Up to 18" point-to-point backplane without any compensation.

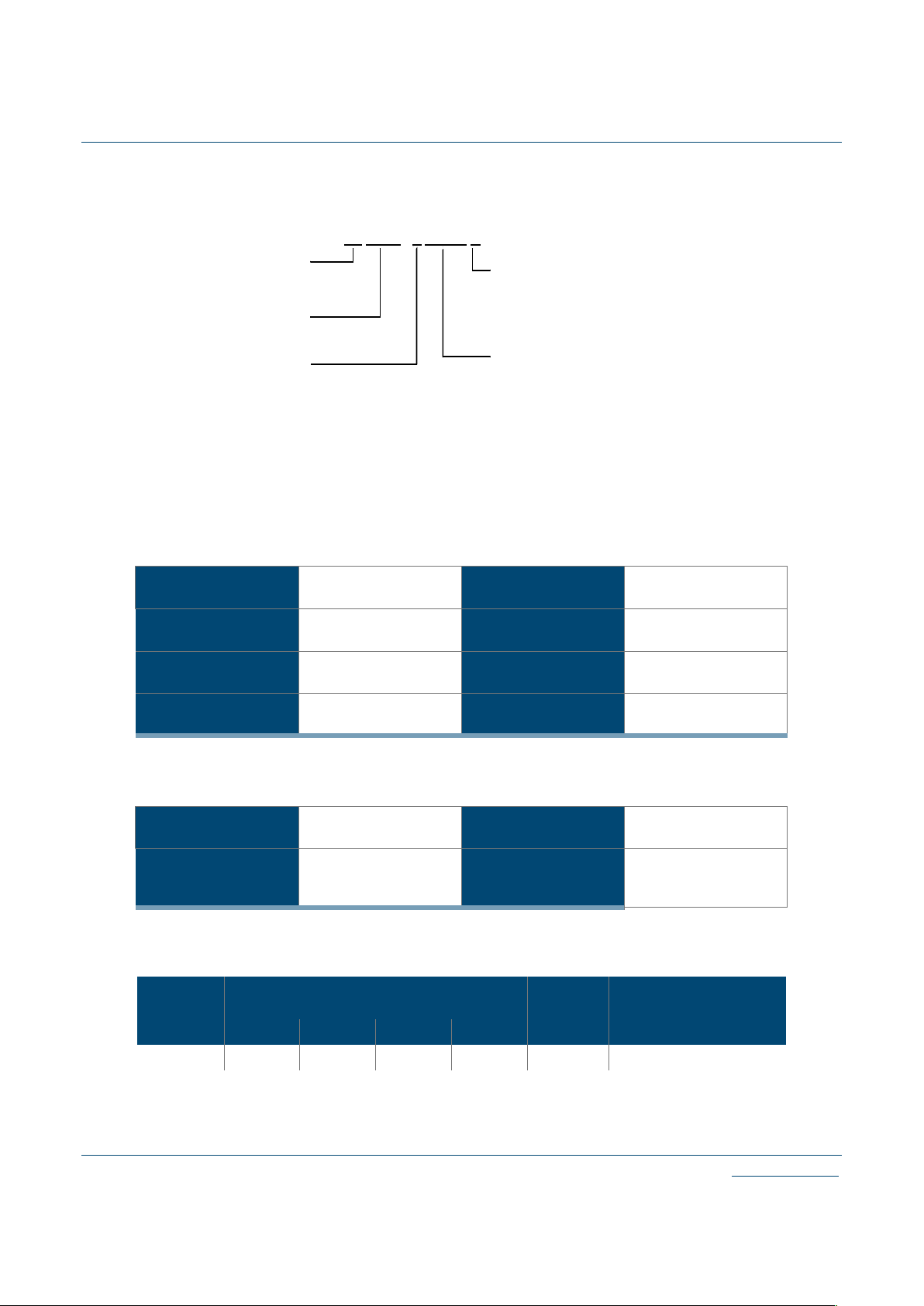

Table 6: Cable - Normal

Low Frequency High Frequency

Modes Min Max Min Max

10:1 Mode Not Available 250 350

8:1 112 360 224 368

7:1 112 322 224 364

4:1 112 348 224 304

Table 7: Cable - High Speed Operation

Low Frequency High Frequency

Modes Min Max Min Max

10:1 Mode Not Available 250 350

8:1 112 480 224 552

7:1 112 462 224 504

4:1 112 456 224 500

Table 8: Backplane - Normal Operation

Low Frequency High Frequency

Modes Min Max Min Max

10:1 Mode Not Available 250 350

8:1 112 320 224 376

7:1 112 315 224 385

4:1 112 384 224 384

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

8

Backplane - High Speed Operation

NOTE:

Test Conditions: Up to 18" point-to-point backplane, and reference design in the

programmable fabric portion of the device for internal skew compensation for channel link

modes.

1:1 Mode (Asynchronous Level Conversion)

Up to 9" cable: 0 to 500 Mbps

Up to 18" point-to-point backplane: 0 to 700 Mbps

All numbers are for LVDS channel performance only, and do not include the programmable

fabric’s ability to support high data rates.

Table 9: Backplane - High Speed Operation

Low Frequency High Frequency

Modes Min Max Min Max

10:1 Mode Not Available 250 350

8:1 112 632 224 632

7:1 112 630 224 630

4:1 112 628 224 628

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

9

www.quicklogic.com

Bus LVDS DC Specifications

Over the operating range, RxVcc = 3.0 V to 3.6 V.

NOTE:

Apply to pad_ChX_p/n, pad_ClkX_p/n

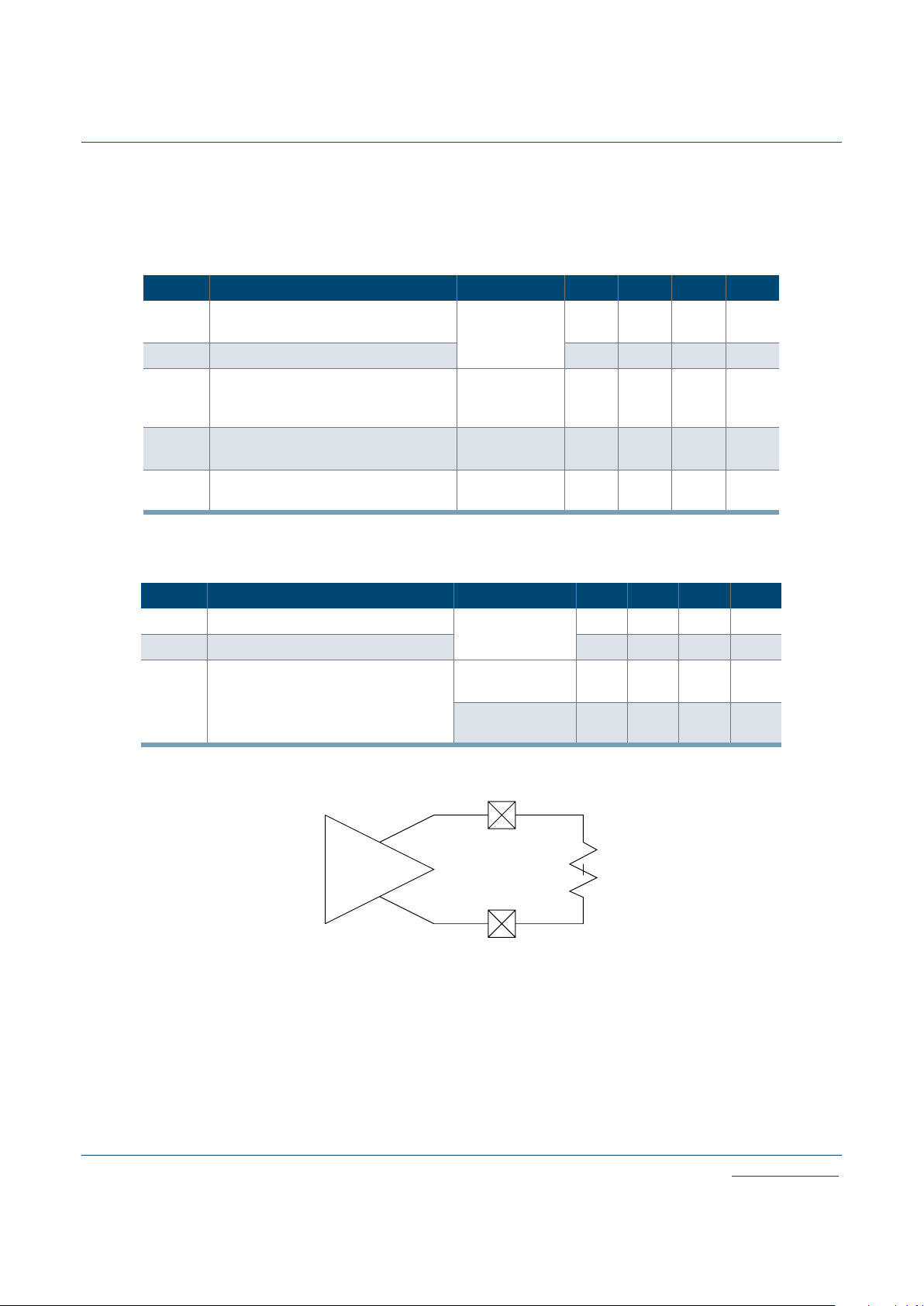

Figure 4: Output Differential Voltage

Table 10: Serializer / Transmitter

Symbol Parameter Conditions Min Typ Max Units

V

OD

Output Differential Voltage,

pad_ChX_p - Pad_ChX_n

Figure 4

Figure 5

R

L

= 27Ω

240 325 420 mV

V

OS

Offset Voltage 0.90 1.10 1.30 V

I

OS

Output Short Circuit Current

D

O

= 0 V,

D

IN

+ H,

EN + OE + V

CC

20 25 35 mA

I

OZ

Tri-State Output Current

DO = 0 V/VCC,

EN = 0

-25 ±10 25 µA

I

OX

Power-Off Output Current

V

CC

- 0 V,

D

O

= 0 V/V

CC

-25 ±10 25 µA

Table 11: Deserializer / Receiver

Symbol Parameter Conditions Min Typ Max Units

V

TH

Differential Threshold High Voltage

Figure 6

V

CM

= 1.1 V

n/a 35 50 mV

V

TL

Differential Threshold Low Voltage -50 -35 n/a mV

I

IN

Input Current

V

IN

= 0 V,

V

CC

= 0 V / 3.6 V

-25±825µA

VIN = 2.4 V,

V

CC

= 0 V / 3.6 V

-25 ±8 25 µA

D out +

D out -

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

10

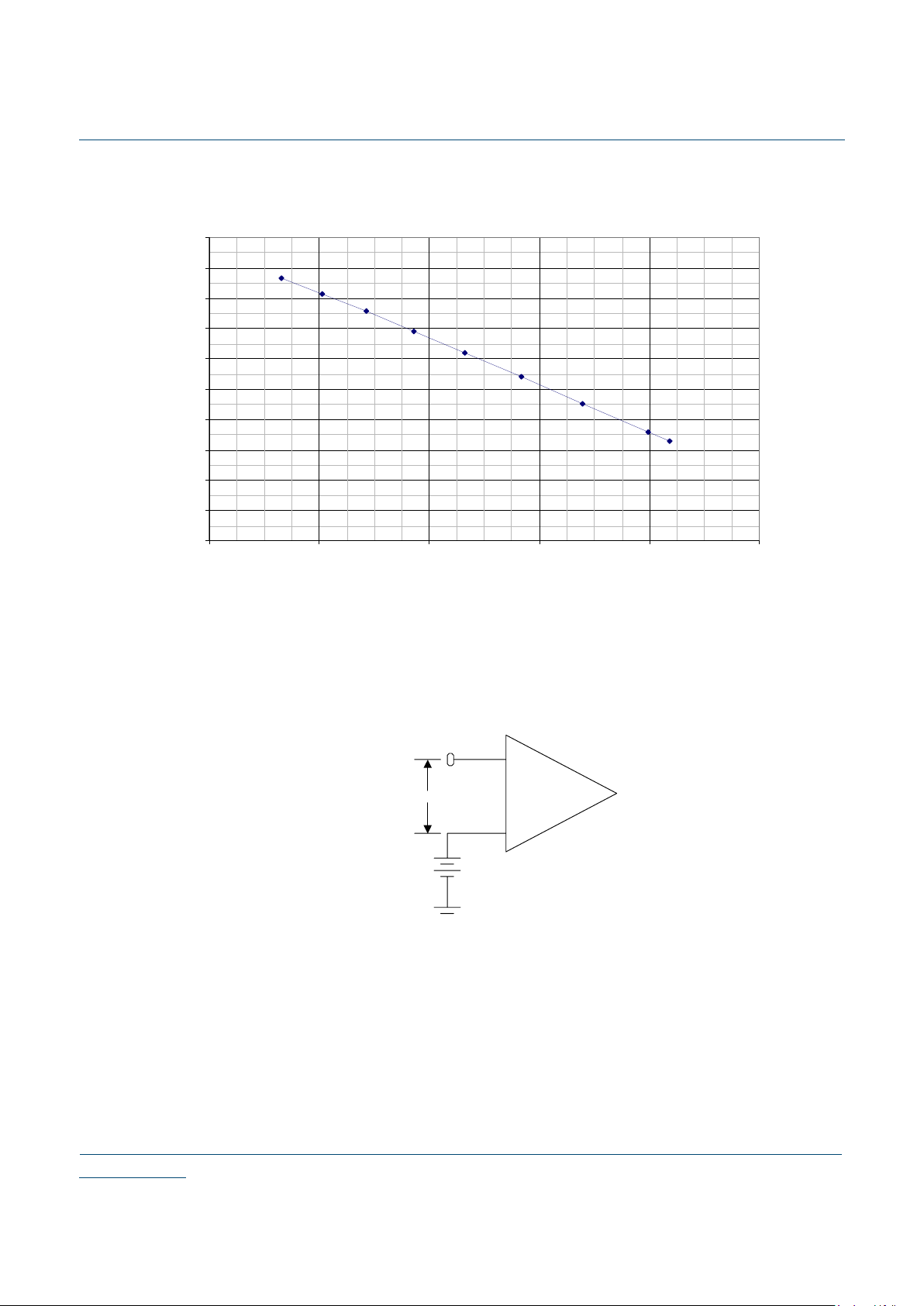

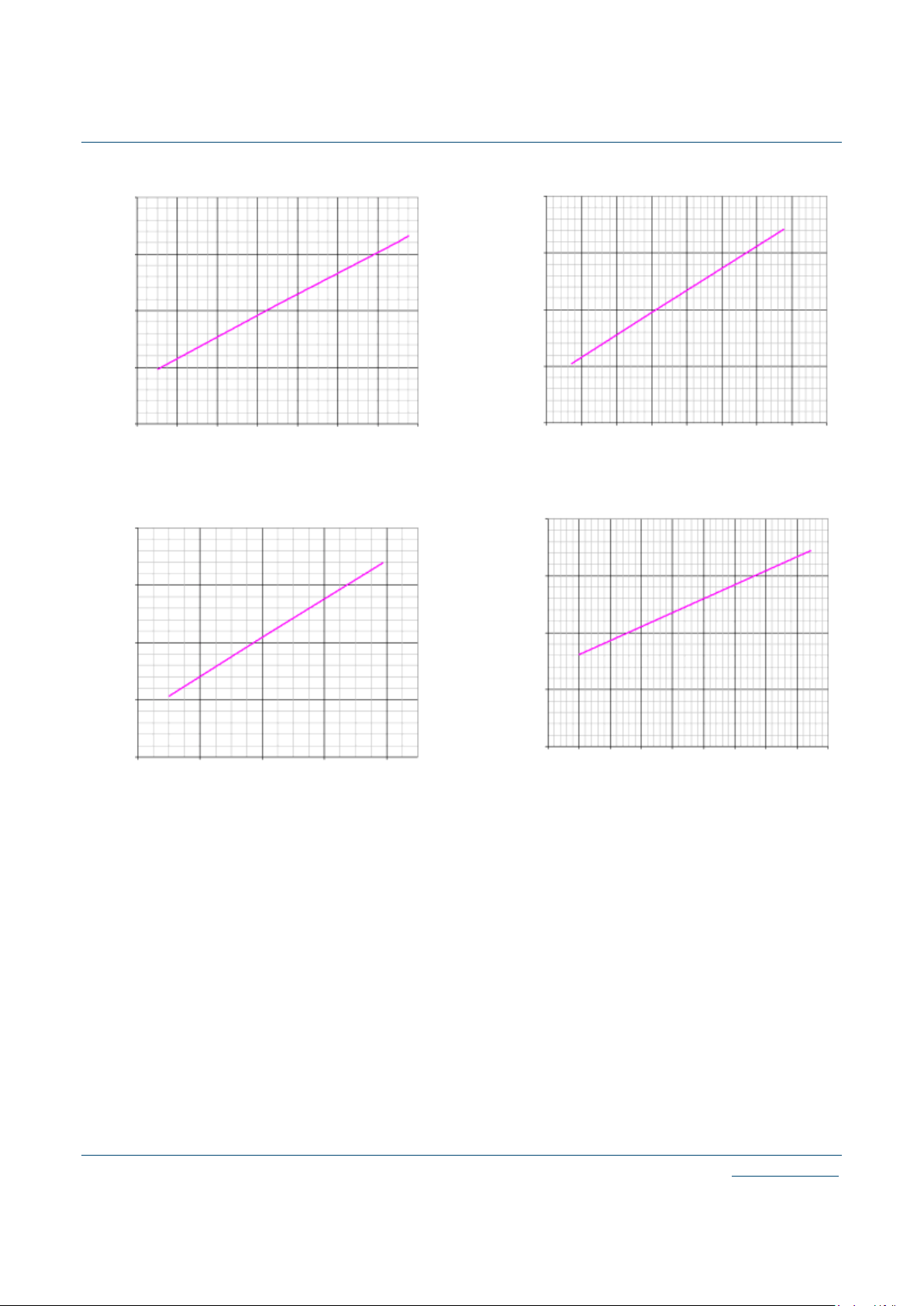

Figure 5: Output Differential Voltage for Different Loads

Figure 6: Differential Threshold Voltages

82SD BLVDS output Vod vs Iod

0.00

0.10

0.20

0.30

0.40

0.50

0.60

0.70

0.80

0.90

1.00

8 9 10 11 12 13

Iod ( m A )

Vod ( v )

100

Ω

60

Ω

27

Ω

40

Ω

80

Ω

VCM

VTH/ VTL

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

11

www.quicklogic.com

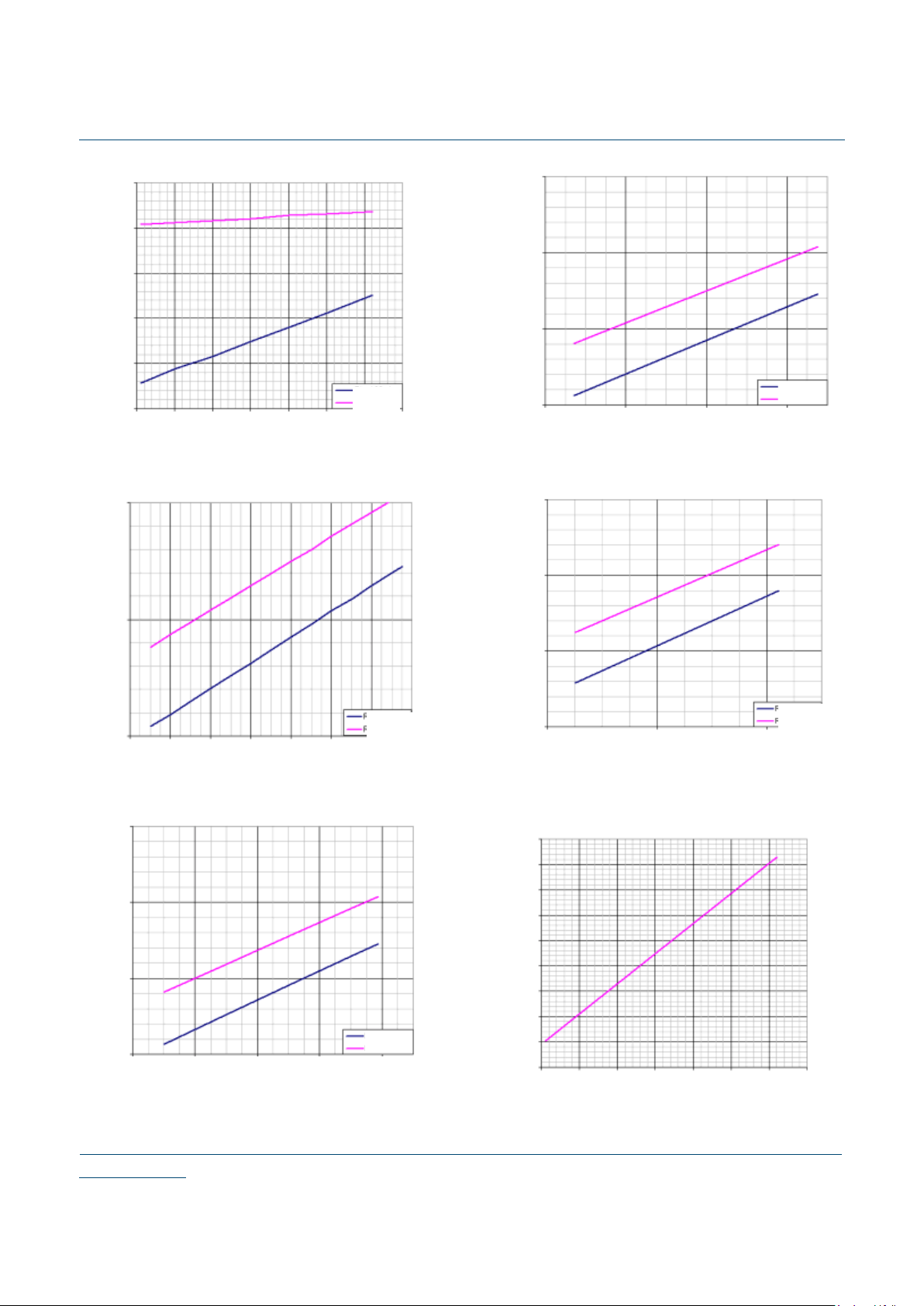

Supply Current per Channel

NOTE:

More accurate supply current/power consumption numbers specific to your

application should be calculated using the power calculator supplied with QuickLogic’s

QuickWorks software package.

Table 12: Serializer / Transmitter

Symbol Parameter Conditions Min Typ Max Units

I

CCT

Serializer Supply Current CL =10 pF

Figure 7 1:1 Mode Figure 7 mA

Figure 8 4:1 Mode Figure 8 mA

Figure 9 7:1 Mode Figure 9 mA

Figure 12 8:1 Mode Figure 12 mA

Figure 11

10:1 Mode

Data/Clock

Figure 11 mA

I

CCTX

Serializer Supply Current

Powerdown

EN = 0 1 10 µA

Table 13: Deserializer / Receiver

Symbol Parameter Conditions Min Typ Max Units

I

CCR

Serializer Supply Current CL = 10 pF

Figure 13 1:1 Mode Figure 13 mA

Figure 14 4:1 Mode Figure 14 mA

Figure 15 7:1 Mode Figure 15 mA

Figure 13 8:1 Mode Figure 13 mA

Figure 14

10:1 Mode

Data/Clock

Figure 14 mA

I

CCRX

Serializer Supply Current

Powerdown

EN = 0 1 10 µA

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

12

Figure 7: Data/Clock Channel, 1:1 Transmit Mode

Figure 8: Data/Clock Channel, 4:1 Transmit Mode

Figure 9: Data/Clock Channel, 7:1 Transmit Mode

Figure 10: Data/Clock Channel, 8:1 Transmit Mode

Figure 11: Data/Clock Channel,10:1 Transmit Mode

Figure 12: Data/Clock Channel, 1:1 Receive Mode

S

upply Current at VccTx = 2.5

V

ICCT (mA)

Clock Frequency(MHz)

0

9

10

11

12

13

0 100 200 300 400 500 600 700

Rt=100ohm

Rt= 27ohm

Supply Current at VccTx = 2.5 V

ICCT (mA)

Clock Frequency(MHz)

10

15

20

20 40 60 80 100 120 140 160

Rt=100ohm

Rt= 27ohm

Supply Current at VccTx = 2.5V

ICCT (mA)

Clock Frequency(MHz)

10

10 30 50 70 90

Rt=100ohm

Rt= 27ohm

15

20

25

Supply Current at VccTx = 2.5 V

ICCT (mA)

10

20 40 60

15

20

25

Rt=100ohm

Rt= 27ohm

Clock Frequency(MHz)

Supply Current at VCCRX = 3.3 V V

CC

= 2.5 V

ICCR (mA)

Clock Frequency (MHz)

2

0 100 200 300 400 500 600 700

4

6

8

10

12

14

16

18

20

S

upply Current at VccTx = 2.5

V

ICCT (mA)

Clock Frequency(MHz)

10

10 30 50 70

Rt=100ohm

Rt= 27ohm

15

20

25

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

13

www.quicklogic.com

Figure 13: Data/Clock Channel, 4:1 Receive Mode

Figure 14: Data/Clock Channel, 7:1 Receive Mode

Figure 15: Data/Clock Channel, 8:1 Receive Mode

Figure 16: Data/Clock Channel, 10:1 Receive Mode

ICCR (mA)

Clock Frequency (MHz)

5

20 40 60 80 100 120 140 160

15

20

25

Supply Current at V

CCRX

= 3.3 V, V

CC

= 2.5 V

10

ICCR (mA)

Clock Frequency (MHz)

S

upply Current at VCCRX = 3.3 V, V

CC

= 2.5 V

0

10 30 50 70 90

20

10

5

15

ICCR (mA)

Clock Frequency (MHz)

10 20 30 40 50 60 70 80 90

5

S

upply Current at

VCCR

X

= 3.3 V,

V

CC

= 2.5

V

20

15

10

0

ICCR (mA)

Clock Frequency (MHz)

S

upply Current at

VCCR

X

= 3.3 V,

V

CC

= 2.5

V

0

10

15

20

5

20 25 30 35 40 45 50 55 60 70

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

14

SERDES Timing Requirements

NOTE:

Both Table 14 and Tabl e 15 refer to CDR (10:1) Mode for ChX_txclk and

Channel Link (8:1, 7:1, 4:1) Mode for ClkX_txclk

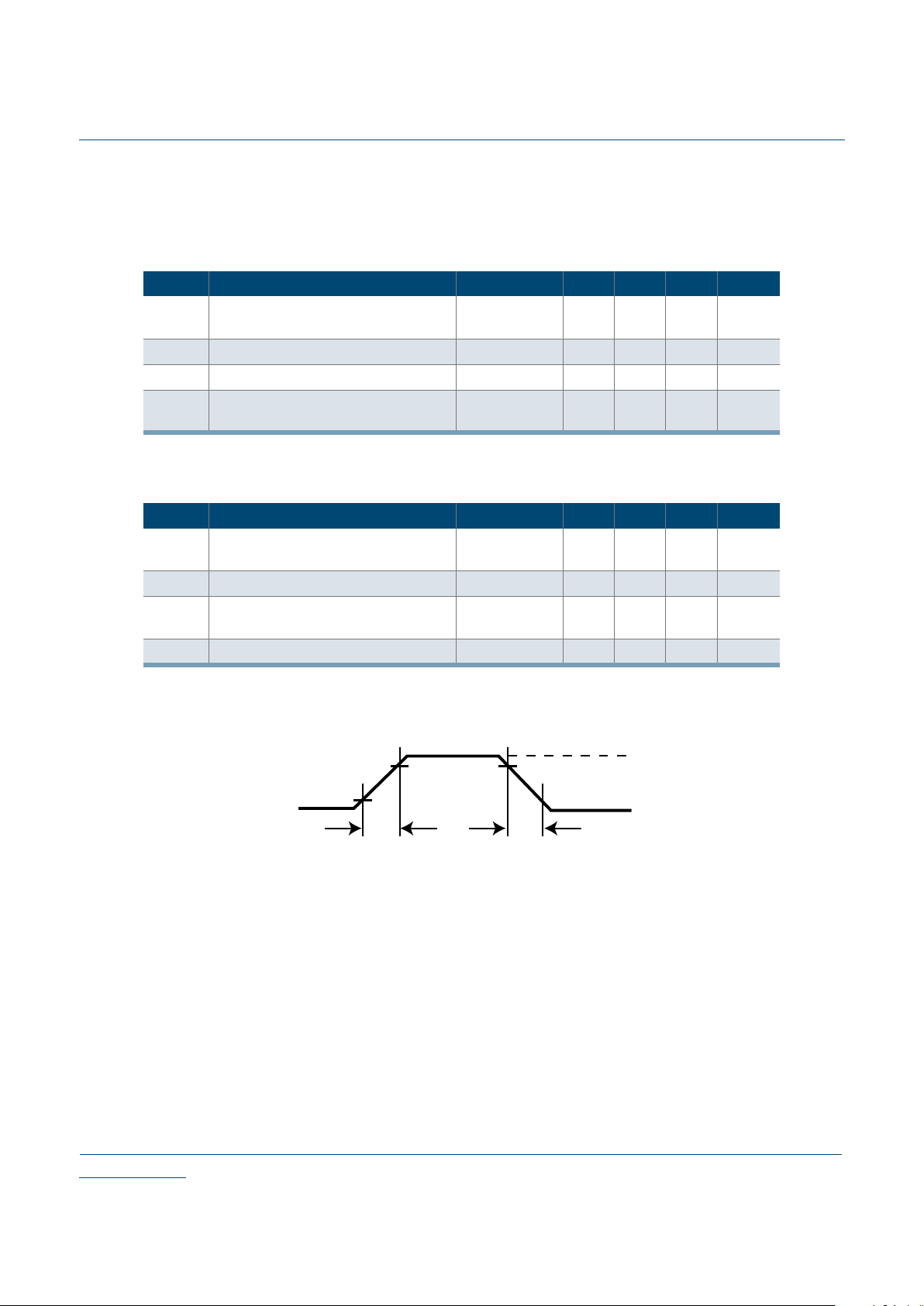

Figure 17: Serializer Transmit Clock / Deserializer Reference Clock Transition Times

Table 14: Serializer / Transmitter Transmit Clock

Symbol Parameter Conditions Min Ty p Max Units

t

TCP

Transmit Clock Period

Mode

Dependent

n/a T n/a nS

t

TDC

Transmit Clock Duty Cycle 45 50 55 %

t

CLKT

Transmit Clock Input Transition Time Figure 17 1 n/a n/a V/nS

t

JIT

Transmit Clock Input Jitter n/a n/a 150.0

pS

(RMS)

Table 15: Deserializer / Receiver Transmit Clock

Symbol Parameter Conditions Min Ty p Max Units

t

RFCP

Reference Clock Period

Mode

Dependent

n/a T n/a nS

t

RFDC

Reference Clock Duty Cycle 40 50 60 %

t

RFCP/tTCP

Ratio of Reference Clock to

Transmit Clock

0.4 0.5 0.6 n/a

t

RFTT

Reference Clock Transition Time Figure 17 1 n/a n/a V/nS

90%

90%

10%

10%

txclk

tclkT/tRFTT tclkT/tRFTT

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

15

www.quicklogic.com

SERDES Switching Characteristics - Serializer/Transmitter]

Table 16: Serializer/Transmitter Switching Characteristics

CDR (10:1) Mode

Symbol Parameter Conditions Min Typ Max Units

t

HZD

pad_ChX_p/n High to Tri-State Delay

Figure 18

1.9 2.2 2.5 nS

t

LZD

pad_ChX_p/n Low to Tri-State Delay 1.9 2.0 2.2 nS

t

ZHD

pad_ChX_p/n Tri-State to High Delay 1.9 2.4 3.0 nS

t

ZLD

pad_ChX_p/n Tri-State to Low Delay 2.0 2.3 2.8 nS

t

DIS

ChX_txd[9:0] Setup to ChX_txclk

Figure 19

2.6 3.2 nS

t

DIH

ChX_txd[9:0] Hold from ChX_txclk 2.1 2.7 nS

t

PLD

Serializer PLL Lock Time Figure 20 90 uS

Channel Link (8:1, 7:1, 4:1) Mode

Symbol Parameter Conditions Min Typ Max Units

t

HZD

pad_ChX_p/n High to Tri-State Delay

Figure 18

1.9 2.2 2.5 nS

t

LZD

pad_ChX_p/n Low to Tri-State Delay 1.9 2.0 2.2 nS

t

ZHD

pad_ChX_p/n Tri-State to High Delay 1.9 2.4 3.0 nS

t

ZLD

pad_ChX_p/n Tri-State to Low Delay 2.0 2.3 2.8 nS

t

DIS

ChX_txd[N-1:0] Setup to ChX_txclk

Figure 21

2.6 3.2 nS

t

DIH

ChX_txd[N-1:0] Hold from ChX_txclk 2.1 2.7 nS

t

SD

Serializer Delay 1.7 nS

t

SCP

Serial Transmit Clock Period T/mode nS

t

TXD[N-1]

Transmitter Output Pulse Position for

Bit [N-1]

[N-1] x t

SCP

+ 1.1 [N-1] x t

SCP

+ 1.5 nS

t

PLD

Serializer PLL Lock Time Figure 20 90 uS

Asynchronous Level Conversion (1:1) Mode

t

HZD

pad_ChX_p/n High to Tri-State Delay

Figure 18

1.9 2.2 2.5 nS

t

LZD

pad_ChX_p/n Low to Tri-State Delay 1.9 2.0 2.2 nS

t

ZHD

pad_ChX_p/n Tri-State to High Delay 1.9 2.4 3.0 nS

t

ZLD

pad_ChX_p/n Tri-State to Low Delay 2.0 2.3 2.8 nS

t

ASD

Asynchronous Serializer Delay -

Data Channel

Figure 22

1.8 nS

t

ASC

Asynchronous Serializer Delay -

Channel Clock

1.7 nS

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

16

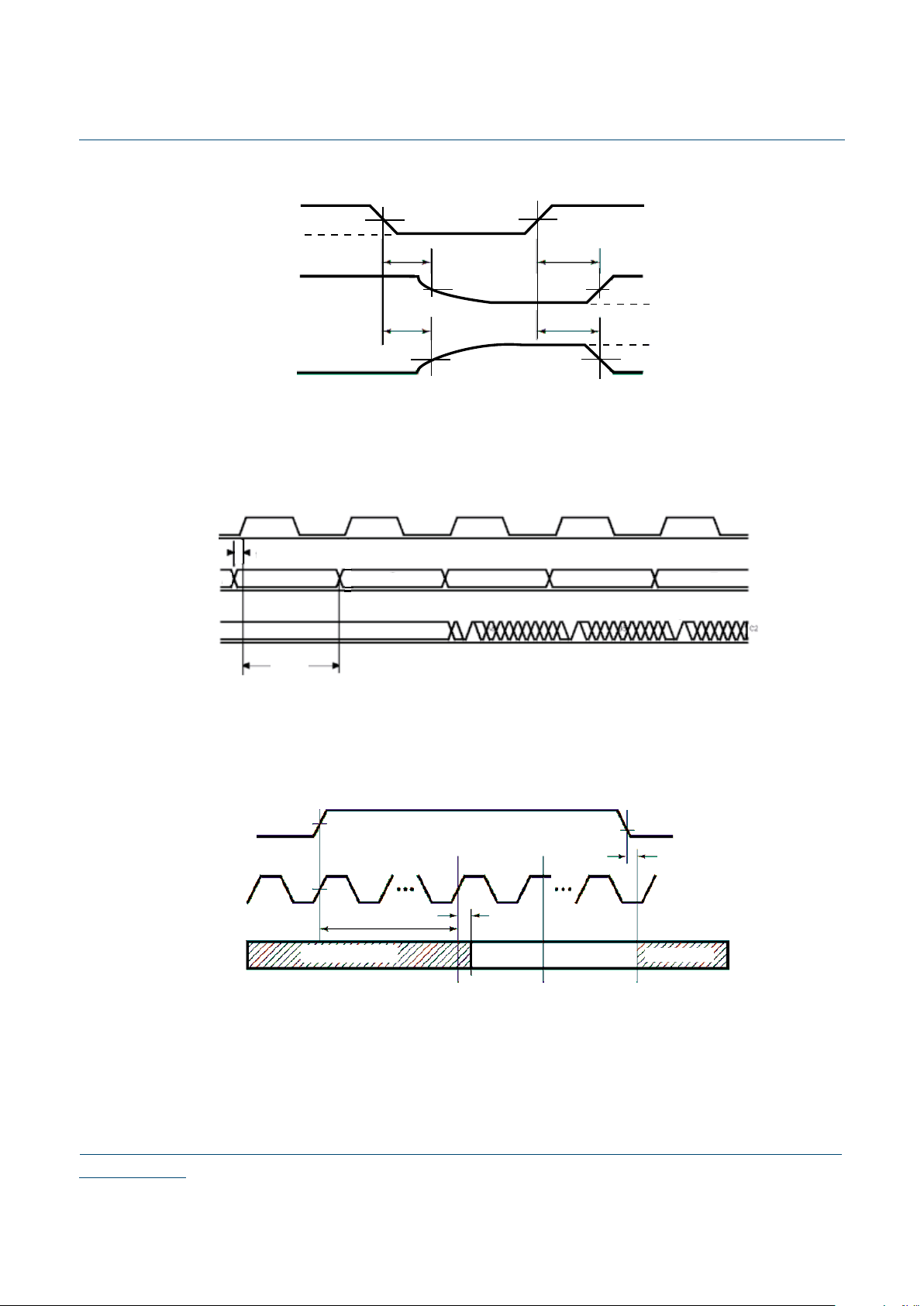

Figure 18: Serializer Delays to Tri-State

Figure 19: 10:1 Mode Serializer Transmit with Embedded Clock

Figure 20: Serializer PLL Times

3V

0V

V

V

0H

0L

EN

Pad_p/n

t

LZD

t

HZD

t

ZHD

t

ZLD

50%

1.1V

50%

50%

50%

1.5V1.5V

1.1V

Ch0_txclk

Ch0_txd[9:0]

A

B

C

D

E

DIS

DIH

t

t

F

Pad_Ch0_p/n

t

ZHD

or

t

ZLD

0.8V

t

HZD

or

t

LZD

TRI-STATE

Output Active

TRI-STATE

txclk

Pad_p/n

ENABLE

2.0V

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

17

www.quicklogic.com

Figure 21: Channel Link Mode Serializer Transmit (Using 8:1 Mode as Example)

Figure 22: 1:1 Mode Asynchronous Level Conversion Mode Serializer Delays

[bit3][bit2][bit1][bit0][bit7][bit6][bit5][bit4]

Pad_ClkX _p/n

Pad_ ChX _p/n

TXD

[4]

[5]

[6]

[7]

[0]

ChX _txd [7:0]

ChX_txclk

Note: [N-1]

physical

positi ons wrt

Pad_ClkX_p/n while

Pad_ChX_p/n bit[n]

bit positions wrt

ChX

_txd [7:0].

tt

t

t

TXD

t

TXD

t

TXD

t

TXD

t

TXD

t

DIS

DIH

SD

denotes

refers to

bit

logical

Ch0_txd [0]

Pad_Ch0_p/n

ClkA_txclk

Pad_ClkA_p/n

t

ASD

t

ASC

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

18

SERDES Switching Characteristics - Deserializer/Receiver

a. These values include the delay resulting from application of internal compensation for data/clock skew.

Table 17: Deserializer / Receiver Switch Characteristics

CDR (10:1) Mode

Symbol Parameter Conditions Min Typ Max Units

t

RCP

ChX_rxclk Period 28.5 T 40.0 nS

t

RDC

ChX_rxclk Duty Cycle 45 50 55 %

t

DD

Deserializer Delay

Figure 23

2

× t

RCP

+ 1.5 2 × t

RCP

+ 2.5 2 × t

RCP

+ 3.5 nS

t

RXPD

ChX_rxclk to ChX_rxd[9..0] 1.5 2.5 3.5 nS

t

DSR1

Deserializer PLL Lock Time

from powered-down state

Figure 24: 25 MHz

Figure 24: 50 MHz

5

8

uS

uS

t

DSR2

Deserializer PLL Lock Time from SYNCPAT

Figure : 25 MHz

Figure : 50 MHz

1

0.75

uS

uS

t

DJIT

Pad_ChX_p/n Jitter

25 MHz

50 MHz

±350

±200

pS

pS

Channel Link (8:1, 7:1, 4:1) Mode

Symbol Parameter Conditions Min Typ Max Units

t

RCP

ChX_rxclk Period T nS

t

RDC

ChX_rxclk Duty Cycle 45 50 55 %

t

DD

Deserializer Delay

Figure 26

2

× t

RCP

+ 1.5 2 × t

RCP

+ 2.5 2 × t

RCP

+ 3.5 nS

t

RXPD

ChX_rxclk to ChX_rxd[N-1..0] 1.5 2.5 3.5 nS

t

RXDS

Pad_ChX_p/n Setup to Strobe Position 150 200 pS

t

RXDH

Pad_ChX_p/n Hold to Strobe Position 150 200 pS

t

SCD

Pad_ClkX_p/n to Serial Clock Delay

a

0.6 0.8 1 nS

t

SCP

Serial Clock Period T/mode nS

t

RXD[N-1]

Receiver Input Strobe Position for Bit [N-1] [N-1]

× t

SCP

+ 1.1 [N-1] × t

SCP

+ 2.4 nS

t

DSR1

Deserializer PLL Lock Time from

powered-down state

Figure 24: 25 MHz

Figure 24: 50 MHz

5

8

uS

uS

t

DJIT

Pad_ChX_p/n Jitter

25 MHz

50 MHz

±300

±150

pS

pS

Asynchronous Level Conversion (1:1) Mode

t

ADD

Asynchronous Deserializer Delay -

Data Channel

Figure 27

1.7 nS

t

ADC

Asynchronous Serializer Delay -

Channel Clock

a

0.6 0.8 1 nS

LVDS Link

Frequency

Compression

Mode

-1

Mode Dependent

LVDS Link

Frequency

Compression

Mode

-1

Mode Dependent

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

19

www.quicklogic.com

Figure 23: 10:1 Mode Deserializer Receive with Embedded Clock

Figure 24: Deserializer PLL Lock Time from Power Down

Figure 25: 10:1 Mode Deserializer PLL Lock Time from SYNCPAT

RXPD

DD

t

A

B

Ch0_txclk

Ch0_rxd[9:0]

Ch0_rxclk

pad_Ch0_p/n

t

2.0V

Enable

Chx_txclk

Pad_Chx_p/n

Chx_lock

Chx-rxd

[N-1,0]

Chx_rxclk

OE

t

ZHLK

DSR1

t

SYNC patterns

ZHR or

ZLR

t

t

Data

t

HZR ortLZR

SYNC Symbol or DIN0-9

1.5V

0.8V

Enable

Chx_txclk

Pad_Chx_p/n

Chx_lock

Chx-rxd

[N-1,0]

Chx_rxclk

OE

VCC

DSR2

t

SYNC patterns

Data

ZLR

t

t

ZHR or

SYNC Symbol or DIN0-9

t

HZR ortLZR

0.0V

0.8V

1.2V

1.0V

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

20

Figure 26: Channel Link Mode Deserializer Receive (Using 8:1 Mode as Example)

Figure 27: 1:1 Mode Asynchronous Level Conversion Mode Deserializer Delays

SERDES Bit Error Rate

The following table indicates the SERDES bit error rate at TA = 25° C and

PLLVcc = 2.5 V unless otherwise specified.

Table 18: Serializer/Deserializer Bit Error Rate

Modes Bit Error Rate

10:1 < 1 x 10

-12

8:1 < 1 x 10

-12

7:1 < 1 x 10

-12

4:1 < 1 x 10

-12

[bit3] [bit2] [bit1] [bit0] [bit7] [bit6] [bit5] [bit4]

Pad_Clkx

_p/n

Pad_Chx_p/n

SerialClock

(Internal)

RXD [ 1] max

[0] max

[1] min

[0] min

Chx_rxclk

Chx_rxd [7:0]

Note:

[N-1] denotes

physical strobe positions

wrt Pad_ClkX_p/n

while

Pad_ChX_p/n bit[n] refers

logical bit positions

wrt

ChX

_

rxd

[7:0].

t

t

t

RXD

t

RXD

t

RXD

t

t

t

t

RCP

SCP

SCD

Strobe

RXDS

RXDH

t

t

RXPD

DD

RXD

t

to

Ch0_txd [0]

Pad_Ch0_p/n

ClkA_txclk

Pad_ClkA_p/n

t

ASD

t

ASC

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

21

www.quicklogic.com

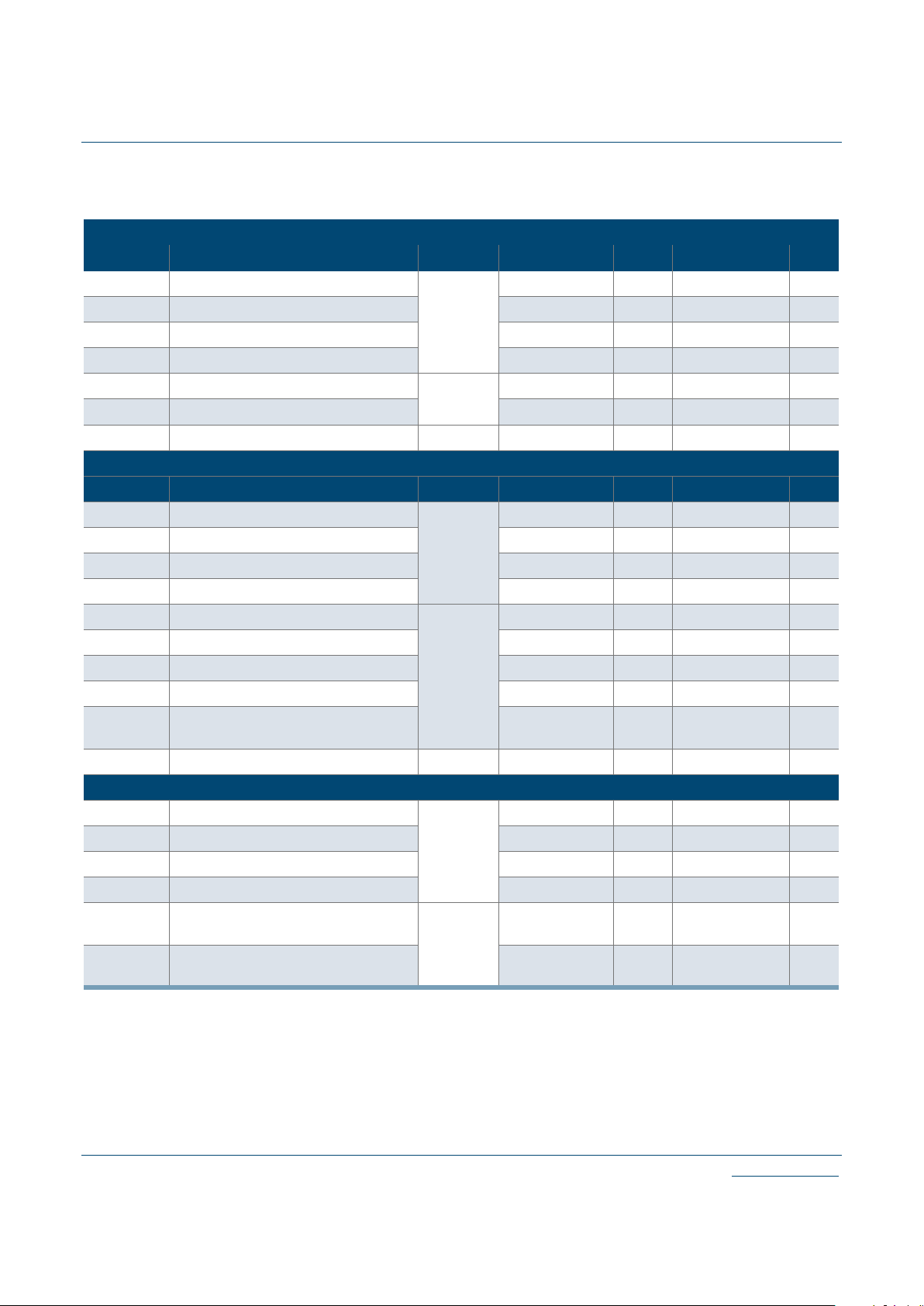

Electrical Specification - Programmable Fabric

DC Characteristics

DC Input/Output Levels

NOTE:

The above table gives the programmable logic timing model for the QuickSD device.

The programmable logic includes the following major elements: Super Logic (Flip-Flop and

Combinational Circuit), Clock, and I/O.

Table 19: DC Characteristics

Symbol Parameter Conditions Min Max Units

I

I

I or I/O Input Leakage Current VI = V

CCIO

or GND -10 10 µA

I

OZ

3-State Output Leakage Current VI = V

CCIO

or GND -10 10 µA

C

I

Input Capacitance

a

a. Capacitance is sample tested only. Clock pins are 12 pF maximum.

8pF

I

OS

Output Short Circuit Current

b

b. Only one output at a time. Duration should not exceed 30 seconds.

Vo = GND -15 -180 mA

V

o

= V

CC

40 210 mA

I

CC

D.C. Supply Current

c

c. For -4/-5/-6/-7 commercial grade devices only. Maximum ICC is 3 mA for all industrial grade devices.

VI,Vo =V

CCIO

or GND 0.50 (typ) 2 mA

I

CCIO

D.C. Supply Current on V

CCIO

02mA

I

REF

D.C. Supply Current on V

REF

-10 10 µA

I

PD

Pad Pull-down (programmable) V

CCIO

= 3.6 V 150 µA

Table 20: DC Input/Output Levels

V

REF

V

IL

V

IH

V

OL

V

OH

I

OLIOH

V

MINVMAXVMIN

V

MAX

V

MIN

V

MAX

V

MAX

V

MIN

mA mA

LVTTL n/a n/a

-0.3 0.8 2.0 V

CCIO

- 0.3 0.40 2.40 2.0 -2.0

LVCMOS2 n/a n/a -0.3 0.7 1.7 V

CCIO

- 0.3 0.70 1.70 2.0 -2.0

GTL+ 0.88 1.12 -0.3 V

REF

- 2.0 V

REF

+ 2.0 V

CCIO

- 0.3 0.60 n/a 40 n/a

PCI n/a n/a -0.3 0.30 × V

CC

0.50 × VCCV

CCIO

- 0.5 0.10 × V

CC

0.90 × V

CC

1.5 -0.5

SSTL2 1.15 1.35

-0.3 V

REF

- 0.18 V

REF

+ 0.18 V

CCIO

+ 0.3 0.74 1.76 7.6 -7.6

SSTL3 1.30 1.70 -0.3 V

REF

- 0.20 V

REF

+ 2.0 V

CCIO

+ 0.3 1.10 1.90 8.0 -8.0

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

22

Super Logic (Flip-Flop and Combinational Circuit) AC Characteristics at

VCC = 2.5 V, TA = 25o C (K = 1)

Figure 28: Super Logic Cell Flip-Flop Structure

Figure 29: Combinational Delay for Logic Cell

Table 21: Logic Cells

Symbol Parameter Condition

Propagation delay (ns)

Fanout = 1

t

PD

Combinational Delay

a

a. Stated timing for worst case Propagation Delay over process variation at VCC = 2.5 V and

TA = 25 °C. Multiply by the appropriate Delay Factor, K, for speed grade, voltage and temperature

settings as specified in the operating range.

Figure 29 0.257

t

SU

Setup Time

b

b. These limits are derived from a representative selection of the slowest paths through the logic cell

including typical net delays. Worst case delay values for specific paths should be determined from

timing analysis of your particular design.

Figure 30

0.22

t

H

Hold Time 0

t

CLK

Clock to Q Delay Figure 31 0.255

t

CWHI

Clock High Time

Figure 32

0.46

t

CWLO

Clock Low Time 0.46

t

SET

Set Delay

Figure 33

0.18

t

RESET

Reset Delay 0.09

t

SW

Set Width 0.30

t

RW

Reset Width 0.30

reset

clk

d

set

q

tPD

input

output

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

23

www.quicklogic.com

Figure 30: Setup and Hold Time for Flip-Flop

Figure 31: Delay from Clock Input to Flip-Flop Q Output

Figure 32: Clock High and Low Time for Flip-Flop

Figure 33: Timing Requirements for Flip-Flop SET and RESET

tSU

tH

Input (d)

clk

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

24

Clock AC Characteristics at VCC = 2.5 V, TA = 25 oC (K = 1)

Figure 34: Clock Structure

I/O AC Characteristics at VCC = 2.5 V, TA = 25 oC (K = 1)

Figure 35: I/O Structure

Table 22: Clock Performance

Clock Performance

Global Dedicated

Logic Cells 1.51 ns 1.59 ns

I/Os 2.06 ns 1.73 ns

Skew 0.55 ns 0.14 ns

Table 23: Input Register Cell

Symbol

Input Register Cell Only

Parameter Propagation Delay (ns)

t

PGCK

Global clock pin delay to quad net 1.34

t

BGCK

Global clock buffer delay (quad net to flip

flop)

0.56

programmable clock

Hardware Clock

Global Clock Buffer

Global Clock

PGCK

BGCK

t

t

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

25

www.quicklogic.com

Figure 36: Input Register Cell

Table 24: Input Register Cell

Symbol

Input Register Cell Only

Parameter

Propagation

Delay (ns)

t

ISU

Input Register Setup Time: the amount of time the synchronous

input of the flip flop must be stable before the active clock edge.

3.12

t

IH

Input Register Hold Time: the amount of time the synchronous input

of the flip flop must be stable after the active clock edge.

0

t

ICLK

Input Register Clock to Q: the amount of time taken by the flip flop

to output after the active clock edge.

1.08

t

IRST

Input Register Reset Delay: the amount of time between when the

flip flop is “reset” (low) and when Q is consequently “reset” (low).

0.99

t

IESU

Input Register Clock Enable Setup Time: the amount of time

“enable” must be stable before the active clock edge.

0.37

t

IEH

Input Register Clock Enable Hold Time: the amount of time “enable”

must be stable after the active clock edge.

0

PAD

E

R

Q

D

+

-

TIN, TINI

TISU

TICLK

tSID

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

26

Table 25: Standard Input Delays

Figure 37: Input Register Timing

Figure 38: Output Register Cell

Symbol Parameter

Propagation

delay (ns)

Standard

Input Delays

To get the total input delay and this delay to tISU

t

SID (LVTTL)

LVTTL input delay: Low Voltage TTL for 3.3 V applications 0.34

t

SID (LVCMOS2)

LVCMOS2 input delay: Low Voltage CMOS for 2.5 V and

lower applications

0.42

t

SID (GTL+)

GTL+ input delay: Gunning Transceiver Logic 0.68

t

SID (SSTL3)

SSTL3 input delay: Stub Series Terminated Logic for 3.3 V 0.55

t

SID (SSTL2)

SSTL2 input delay: Stub Series Terminated Logic for 2.5V 0.607

R

CLK

D

Q

tISU

tIH

tICLK

tIESU

tIEH

tIRST

E

PAD

OUTPUT

REGISTER

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

27

www.quicklogic.com

Table 26: Output Register Cell

Figure 39: Output Register Cell Timing

Electrical Specification - RAM Block

Figure 40: RAM Module

Symbol Parameter Propagation delay (ns)

Output Register Cell Only

t

OUTLH

Output Delay low to high (10% of H) 0.40

t

OUTHL

Output Delay high to low (90% of H) 0.55

t

PZH

Output Delay tri-state to high (10% of Z) 2.94

t

PZL

Output Delay tri-state to low (90% of Z) 2.34

t

PHZ

Output Delay high to tri-State 3.07

t

PLZ

Output Delay low to tri-State 2.53

t

CO

Clock to out delay 3.15 (fast slew) 10.2(slow slew)

L

H

L

H

tOUTLH

tOUTHL

L

H

Z

tPZH

L

H

Z

tPZL

L

H

Z

tPLZ

L

H

Z

tPHZ

WA

WD

WE

WCLK

RE

RCLK

RA

RD

[9:0]

[17:0]

[9:0]

[17:0]

MODE ASY NCRD

[1:0]

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

28

RAM Cell Synchronous Write Timing

Table 27: RAM Cell Synchronous Write Timing

Figure 41: RAM Cell Synchronous Write Timing

Symbol Parameter

Propagation

delay (ns)

t

SWA

WA setup time to WCLK: the amount of time the WRITE ADDRESS

must be stable before the active edge of the WRITE CLOCK

0.675

t

HWA

WA hold time to WCLK: the amount of time the WRITE ADDRESS

must be stable after the active edge of the WRITE CLOCK

0

t

SWD

WD setup time to WCLK: the amount of time the WRITE DATA must

be stable before the active edge of the WRITE CLOCK

0.654

t

HWD

WD hold time to WCLK: the amount of time the WRITE DATA must

be stable after the active edge of the WRITE CLOCK

0

t

SWE

WE setup time to WCLK: the amount of time the WRITE ENABLE

must be stable before the active edge of the WRITE CLOCK

0.623

t

HWE

WE hold time to WCLK: the amount of time the WRITE ENABLE must

be stable after the active edge of the WRITE CLOCK

0

t

WCRD

WCLK to RD (WA=RA): the amount of time between the active WRITE

CLOCK edge and the time when the data is available at RD

4.38

tSWA

tSWD

tSWE

tHWA

tHWD

tHWE

tWCRD

old data

new data

WCLK

WA

WD

WE

RD

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

29

www.quicklogic.com

RAM Cell Read Timing

Table 28: RAM Cell Synchronous and Asynchronous Read Timing

Figure 42: RAM Cell Synchronous and Asynchronous Read Timing

Symbol Parameter

Propagation

delay (ns)

RAM Cell Synchronous Read Timing

t

SRA

RA setup time to RCLK: the amount of time the READ ADDRESS

must be stable before the active edge of the READ CLOCK

0.686

t

HRA

RA hold time to RCLK: the amount of time the READ ADDRESS

must be stable after the active edge of the READ CLOCK

0

t

SRE

RE setup time to WCLK: the amount of time the READ ENABLE

must be stable before the active edge of the READ CLOCK

0.243

t

HRE

RE hold time to WCLK: the amount of time the READ ENABLE

must be stable after the active edge of the READ CLOCK

0

t

RCRD

RCLK to RD: the amount of time between the active READ CLOCK

edge and the time when the data is available at RD

4.38

RAM Cell Asynchronous Read Timing

r

PDRD

RA to RD: amount of time between when the READ ADDRESS is

input and when the DATA is output

2.06

RE

RD

RCLK

RA

TSRA THRA

TSRE

THRE

OLD data NEW data

TRCRD

RPDRD

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

30

LVDS SERDES Description

LVDS SERDES Applications

The QL82SD device in the QuickLogic QuickSD ESP (Embedded Standard Product) device

family provides a completely integrated configurable Serializer/Deserializer interface solution

combined with 536 K system gates of customizable logic. This device provides a means to

receive and transmit high-speed serial data and implement any proprietary high-speed serial

link.

The QL82SD device is a high performance serializer/deserializer chip. It can be combined

with FIFO buffer memory to build a complete serial link. The need for external FIFOs can be

eliminated by configuring the available internal RAM as two 256 x 36 FIFOs.

The embedded SERDES core is a full duplex design with a serialization section for

transmission and a deserialization section for reception. The transmitter and receiver can be

configured for level conversion (1:1), signals that transmit a clock signal with the data

(1:4, 1:7, 1:8), or applications that require clock recovery (1:10).

The embedded SERDES core has a system interface that emulates a synchronous FIFO for

ease of use. FIFOs allow maximum sustained performance of 600 MB/s running a full duplex

link. Their function is to handle the asynchronous interface between the bus data rate and

the different serial data rates, and handle phase and frequency differences inherent in serial

links. Internal FIFOs of 256

×××× 36 or 512 ×××× 16 can be cascaded with external FIFOs to

expand the buffering to the desired size.

The QL82SD is a versatile part that allows the system designer to create proprietary or

standardized serial links by taking advantage of some, or all, of the embedded features. It has

a number of useful features for system designers of proprietary links with additions of

embedded computational units and customizable I/O.

LVDS SERDES Block Functional Description

The QuickSD SERDES consists of a physical layer for high-speed serial communications,

handling all data translations, clocking and timing. The core is made up of eight data

channels and two channel clocks. These blocks contain the circuitry necessary for all the data

muxing and de-muxing, clock multiplication and division, clock and data phase alignment,

and clock recovery and encoding. The core can be configured to support systems that

transmit a separate clock signal or that have the clock embedded into the data stream and

require clock recovery.

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

31

www.quicklogic.com

LVDS SERDES Data Channel Configuration

A representation of the SERDES data channel is shown in Figure 43. The device consists of

eight identical data channels.

Figure 43: SERDES Channel 0

Each SERDES data channel can be operated independently. The data channels are

transceivers, so they can either send or receive data on the serial LVDS wire pair. The

direction of transfer is selected with the ChX_oe pin. If this pin is high, the channel is in

transmit mode, if this pin is low, the channel is in receive mode.

The data channel can be configured to deal with different parallel data widths and clocking

mechanisms,

Table 2 9 shows the settings for the ChX_mode[3:0] pins and the modes that

they refer to.

For the Channel Clock A/B modes, see

“LVDS SERDES Channel Clock Configuration” on

page 32

for more details. If the data channel is not needed, then it can be powered down (to

reduce overall device power) by tying the ChX_en signal low. This signal must be held high

for normal operation.

For a detailed description of how to use the various modes of the data channel to transmit

and receive data, see

“LVDS SERDES Transmit and Receive Operation” on page 33.

Table 29: ChX_mode[3:0]

ChX_mode[3] Description

bit [3]

Low Frequency (1), High Frequency (0)

Determines high or low frequency lock range for internal SERDES PLL.

When this bit is set to ‘1’, the low frequency range is selected.

When this bit is set to ‘0’, the high frequency range is selected.

bit [2]

In 10:1 mode, this bit must be set to ‘0’.

In channel clock mode, the pin setting does not matter.

bit [1] Embedded clock mode (0), channel-clock (1)

bit [0] CLKA (1), CLKB (0) channel clock select

Ch0_rst

Ch0_lock

Ch0_en

Ch0_oe

Ch0_pre_emp

Ch0_mode[3:0]

Ch0_sync

Ch0_txclk

Ch0_rxclk

Ch0_txd[9:0]

Ch0_rxd[9:0]

pad_Ch0-p

pad_Ch0_n

SERDES

Channel 0

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

32

LVDS SERDES Channel Clock Configuration

There are two SERDES channel clocks within the core. Figure 44 shows a representation of

the channel clock. Each channel clock is identical.

Figure 44: SERDES CLK A

Each of the two SERDES channel clocks can be configured independently. They can be

configured to act as the transmit or receive clock for up to 8 SERDES data channels (for serial

links where the clock is provided as a separate LVDS wire pair). Alternatively, the channel

clock can be configured as a simple bi-directional IO pin, where the internal signals are

CMOS, but the external pin is LVDS. In such a case, the I/O will act simply as a level

converter.

Since the channel clock may act as a transmit or receive clock (or as an input or output signal

in data mode), the direction of the channel clock must be selected with the ClkX_oe pin. If

this pin is high, then the channel clock is transmitting a clock (or acting as an output signal

in data mode). If this pin is low, then the channel clock is receiving a clock (or acting as an

input signal in data mode).

When the channel clocks are used to act as the transmit or receive clock for one or more

data channels, then four modes are available, using the CLKx_MODE[1:0] input.

Table 30

shows these modes.

When a channel clock is configured with ClkX_MODE[1:0] equal to 01, 10, or 11, then any

of the data channels can be configured to use that channel clock as its clock, by setting the

data channel's ChX_MODE inputs to point to the correct channel clock. See the

Section ,

“LVDS SERDES Data Channel Configuration,” on page 31

for more information.

When the channel clock is configured with ClkX_MODE[1:0] equal to 00, the channel clock

becomes a simple LVDS-to-CMOS level converter.

When ClkX_oe is high, the channel clock will be configured as an output, in which the data

supplied on the ClkX_txclk pin is converted to LVDS and comes out on the pad_ClkX_p and

pad_ClkX_n external LDVS signals asynchronously.

When ClkX_oe is low, the channel clock is configured as an LVDS input, in which the LVDS

signal on pad_ClkX_p and pad_ClkX_n is converted to CMOS levels and enters the device

on the ClkX_rxclk pin.

Table 30: ClkX_mode[1:0]

ClkX_mode[1:0] Mode

00 1:1 mode (no PLL)

01 4:1 mode

10 7:1 mode

11 8:1 mode

ClkA_oe

ClkA_rxclk

ClkA_pre_emp

ClkA_en

ClkA_mode[1:0]

ClkA_txclk

pad_ClkA_p

pad_ClkA_n

SERDES

CLKA

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

33

www.quicklogic.com

Any data channel ca n also b e config ured as a level t r anslat or. Thi s is done by setting that data

channel's ChX_mode[3:0] input to point to a channel clock (A or B) which has also been

configured in level translator mode.

LVDS SERDES Transmit and Receive Operation

The SERDES core can transmit and receive serial data across LVDS wires in many different

formats. This section describes each of the various transmit and receive formats.

Transmit 10-bit Data With Embedded Clock

The waveform in Figure 19, illustrates how 10-bit data can be transmitted serially on the

differential LVDS outputs.

NOTE:

The pad_ChX_p and pad_ChX_n outputs in the diagram are representing the data

changes which occur on a pair of LVDS signals.

When the SERDES is in 10-bit mode, no separate clock signal is needed, since the clock is

embedded within the serial data stream. In

Figure 19, you will notice that at t

DIS

the rising

edge of ChX_txclk registers the 10-bit data value B within the SERDES core. After about one

clock period of ChX_txclk, the serialized data begins to appear on the LVDS outputs

(pad_ChX_p and pad_ChX_n) in the following sequence:

1. First, a logic 1 is transmitted, which is the start bit, and part of the data used to transmit

the clock.

2. Then each of the 10 bits of the data value B is transmitted in sequence.

3. Finally, a logic 0 is transmitted, which is the stop bit (MSB first). This stop bit is the

remaining part of the embedded clock.

NOTE:

By using a stop bit value of 0 and a start bit value of 1, there is always a guaranteed

0 to 1 transition in the bitstream (the end of one frame and the beginning of the next).

Because of this, the receiver is able to recover the embedded clock from the serial bit stream.

The pertinent timing parameters shown in

Figure 19 are:

• t

DIS

is the setup time needed for the ChX_txd bus relative to the ChX_txclk clock

• t

DIH

is the hold time for the ChX_txd relative to the ChX_txclk clock

Receive 10-bit Data With Embedded Clock

In 10-bit mode, the clock is embedded in the serial data stream on the pad_ChX_p and

pad_ChX_n LVDS signal (shown in

Figure 23) as one signal, but actually is a pair of

differential signals). When using the SERDES data channel in 10-bit receive mode, a

reference clock is needed which matches the parallel clock rate of the transmitter (shown in

Figure 23 as ChX_txclk). There is no timing phase relationship between the reference clock

and the received parallel clock (ChX_rxclk), but the two clocks will have the same frequency.

NOTE:

The serial data bits are transmitted with a 0 as a stop bit and a 1 as a start bit, and.

The SERDES block recovers the clock from this data stream, as shown with the ChX_rxclk

waveform (

Figure 23). The parallel 10-bit data is also recovered and timed appropriately with

the recovered clock.

The pertinent timing parameters shown in

Figure 23 are:

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

34

•

t

DD

is the delay from the rising edge of the start bit in the serial bitstream to the rising

edge of the recovered parallel clock

• t

RXPD

is the propagation delay time provided for the recovered data with respect to the

recovered clock.

Transmit 8-bit Data With Channel Clock

When the SERDES is in 8-bit mode, it must be configured to use a channel clock. The

waveforms shown in

Figure 21 show the parallel transmit clock provided by the user to the

clock channel (ClkX_txclk), and the converted channel clock on the LVDS outputs of the

channel clock (pad_ClkX_p and pad_ClkX_n).

NOTE:

The output of the channel clock has the same period as the parallel transmit clock.

This is done to frame the serial data transmitted on the pad_ChX_p and pad_ChX_n pins.

The LVDS channel clock (pad_ClkX_p and pad_ClkX_n) is multiplied up by the receiver to

capture each bit of the transmitted data.

The 8-bit data is converted to a simple serial bit stream.

The pertinent timing parameters shown in

Figure 21 are:

• t

DIS

is the setup time needed on the parallel transmit data (ChX_txd[7:0] with respect to

the parallel transmit clock (ClkX_txclk)

• t

DIH

is the hold time needed on the parallel transmit data (ChX_txd[7:0] with respect to

the parallel transmit clock (ClkX_txclk)

• t

SD

is the clock delay between the rising edge of the parallel transmit clock to the rising

edge of the LVDS channel clock

• t

TXD[N-1]

is the serial data physical bit position with respect to the LVDS channel clock.

NOTE:

t

TXD[N-1]

denotes physical bit positions wrt pad_ClkX_p/n while pad_ChX_p/n bit[n]

refers to logical bit positions wrt ChX_txd[7:0].

Receive 8-bit Data With Channel Clock

The SERDES in 8-bit receive mode receives serial data on the pad_ChX_p and pad_ChX_n

LVDS input, and a clock on the pad_ClkX_p and pad_ClkX_n LVDS input (see

Figure 26 ).

The LVDS input clock is multiplied by 8 within the SERDES core to capture the 8 bits of data

from the pad_ChX_p and pad_ChX_n serial bitstream. The parallelized data goes out on the

ChX_rxd internal 8-bit bus, and the re-timed parallel clock goes out on the ClkX_rxclk pin.

The pertinent timing parameters shown in this diagram are:

• t

DD

is the delay between the first bit of the serial data showing up in the serial bit stream

and the rising edge of the retimed parallel clock corresponding to the same data frame

• t

RXPD

is the propagation delay time provided for the recovered data with respect to the

recovered clock

• t

RXDS

is the setup time needed for the serial data on the pad_ChX_p and pad_ChX_n

LVDS inputs to the rising edge of the internal serial clock strobe

• t

RXDH

is the hold time needed for the serial data on the pad_ChX_p and pad_ChX_n

LVDS inputs relative to the internal serial clock strobe

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

35

www.quicklogic.com

• t

SCD

is the delay between the rising edge of the LVDS channel clock and the first rising

edge of the multiplied internal serial clock corresponding to the same data frame.

• t

RXD[N-1]

is the internal clock strobe positions with respect to the rising edge of the LVDS

channel clock

NOTE:

t

RXD[N-1]

denotes physical strobe positions with respect to pad ClkX_p/n while

pad_ChX_p/n bit[n] refers to logical bit positions with respect to ChX_rxd[7:0]

Asynchronous Level Conversion Mode for the Data Channel and

Channel Clock

When the SERDES data channel ChX_mode[3:0] pins are set to use a channel clock which

is in level translator mode, then that data channel is also in level translator mode. In level

translator mode, the data channel only converts the internal CMOS signal to LVDS (for

output mode), or vice versa for input mode.

When the data channel or channel clock is in this asynchronous signal translation mode, and

configured as outputs (ChX_oe or ClkX_oe high) the output mode waveforms in

Figure 22

apply.

When the data channel or channel clock is in this asynchronous signal translation mode, and

configured as inputs (ChX_oe or ClkX_oe low) the input mode waveforms in

Figure 27 apply.

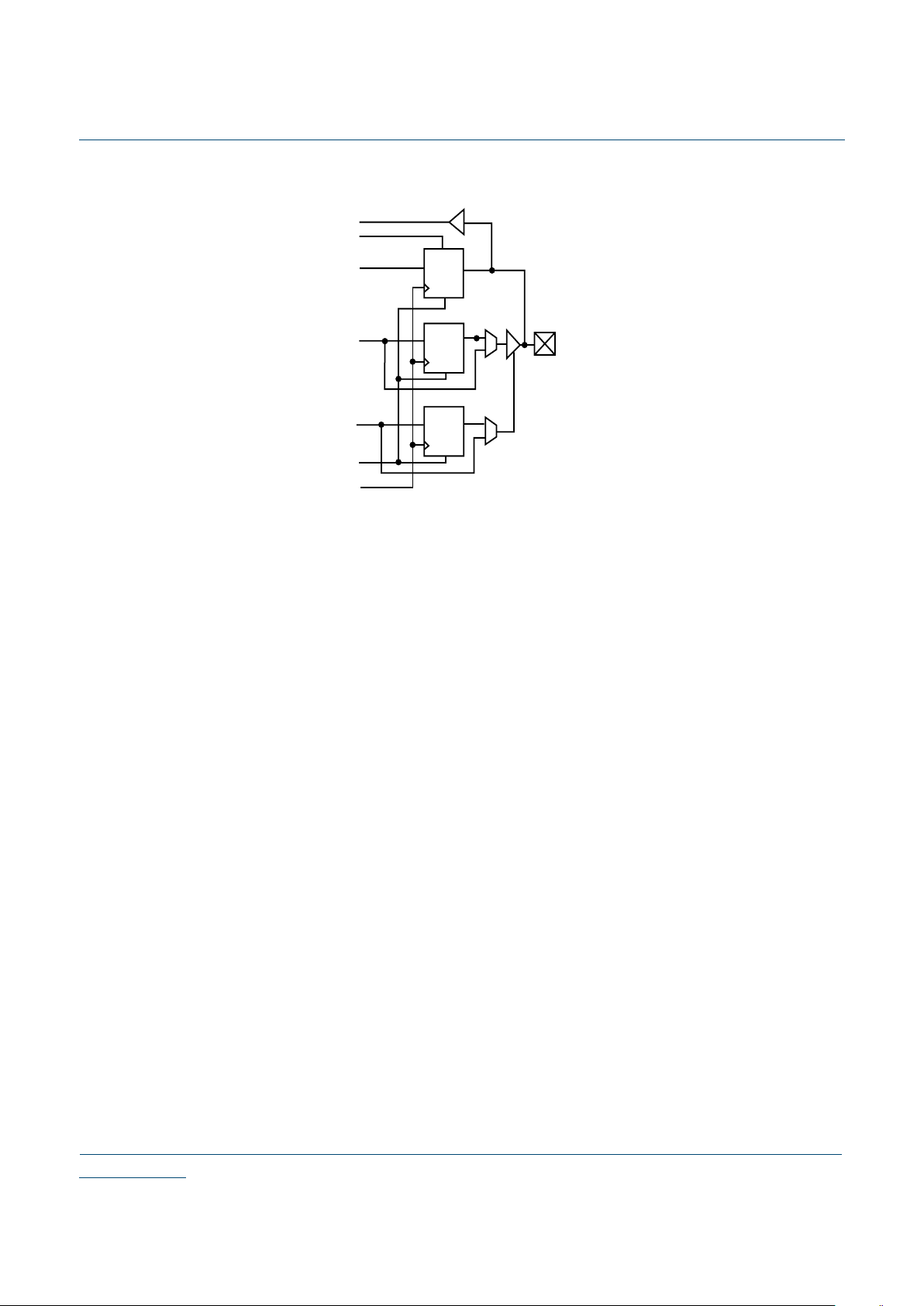

Programmable Fabric Description

The QuickSD device features an enhanced Super Logic Cell with an additional D flip-flop

register and associated control logic. This advanced architectural approach addresses today's

highly register intensive designs.

The QuickSD logic Supercell structure, shown in

Figure 45, is similar to the .35 mm

QuickLogic logic cell with the addition of a second register. Both registers share CLK, SET

and RESET inputs. The second register has a two-to-one multiplexer controlling its input.

This register can be loaded from the NZ output or directly from a dedicated input.

NOTE:

The input "PP" is not an "input" in the classical sense. It can only be tied high or low

using default links only and is used to select which path "NZ" or "PS" is used as an input to

the register. All other inputs can be connected not only to "tiehi" and "tielo" but to multiple

routing channels as well.

The complete logic cell consists of two 6-input AND gates, four two-input AND gates, seven

two-to-one multiplexers, and two D flip-flops with asynchronous SET and RESET controls.

The cell has a fan-in of 30 (including register control lines) and fits a wide range of functions

with up to 17 simultaneous inputs. It has six outputs, of which four are combinatorial and

two are registered. The high logic capacity and fan-in of the logic cell accommodate many

user functions with a single level of logic delay while other architectures require two or more

levels of delay.

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

36

Figure 45: SERDES Logic Cell

RAM Block Description

General Description

The QuickSD device includes multiple dual-port 2,304-bit RAM modules for implementing

RAM and FIFO functions. Each module is user-configurable into four different block

organizations. Modules can also be cascaded horizontally to increase their effective width or

vertically to increase their effective depth as shown in the following figure. The RAM can also

be configured as a modified Harvard Architecture, similar to those found in DSPs.

Figure 46: SERDES 2,304-bit RAM Module

QS

A1

A2

A3

A4

A5

A6

OS

OP

B1

B2

C1

C2

MP

MS

D1

D2

E1

E2

NP

NS

F1

F2

F3

F4

F5

F6

PS

PP

QC

QR

AZ

OZ

QZ

NZ

Q2Z

FZ

MODE [1:0]

WA [9:0]

WD [17:0]

WE

WCLK

RCLK

ASYNCRD

RA [9:0]

RD [17:0]

RE

2,304-bit Module

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

37

www.quicklogic.com

There are 36 RAM blocks within the QuickSD device, for a total of 82.9 Kbits of RAM. Using

two "mode" pins, designers can configure each module into 128 x 18 (Mode 0), 256 x 9

(Mode 1), 512 x 4 (Mode 2), or 1024 x 2 blocks (Mode 3). The blocks are also easily

cascadable to increase their effective width and/or depth. See

Figure 47 for cascaded RAM

modules.

Figure 47: Cascaded RAM Modules

The RAM modules are dual-port, with completely independent READ and WRITE ports and

separate READ and WRITE clocks. The READ ports support asynchronous and synchronous

operation, while the WRITE ports support synchronous operation. Each port has 18 data

lines and 10 address lines, allowing word lengths of up to 18 bits and address spaces of up

to 1,024 words. Depending on the mode selected, however, some higher order data or

address lines may not be used.

The Write Enable (WE) line acts as a clock enable for synchronous write operation.

The Read Enable (RE) acts as a clock enable for synchronous READ operation (ASYNCRD

input low), or as a flow-through enable for asynchronous READ operation (ASYNCRD input

high).

Designers can cascade multiple RAM modules to increase the depth or width allowed in

single modules by connecting corresponding address lines together and dividing the words

between modules.

A similar technique can be used to create depths greater than 512 words. In this case address

signals higher than the ninth bit are encoded onto the write enable (WE) input for WRITE

operations. The READ data outputs are multiplexed together using encoded higher READ

address bits for the multiplexer SELECT signals.

The RAM blocks can be loaded with data generated internally (typically for RAM or FIFO

functions). The RAM achieve 155 MHz performance for the lowest speed grade devices

when using multiple blocks cascaded together.

Multiple Accessing of Memories

The extremely fast RAM can be used in designs that require multiple memory accessing. The

RAM achieves 280 MHz performance for the fastest speed grade and 155 MHz

performance for the lowest speed grade devices when using multiple blocks cascaded

together. Write through of DATA is also possible with the QuickLogic RAM.

WDATA

WADDR

WDATA

RDATA

RADDR

RDATA

RAM

Module

(2304 bits)

RAM

Module

(2304 bits)

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

38

ECU Block Description

ECU Block General Description

Traditional Programmable Logic architectures do not implement arithmetic functions

efficiently or effectively. These functions require high logic cell usage while garnering only

moderate performance results. By embedding a dynamically reconfigurable computational

unit, the QuickSD device can address various arithmetic functions efficiently and effectively

providing for a robust DSP platform—this approach offers greater performance than

traditional programmable logic implementations. The ECU block is ideal for complex DSP,

filtering, and algorithmic functions. The QuickSD device architecture will allow functionality

above and beyond that achievable using DSP processors or programmable logic devices. The

embedded block is implemented at the transistor level with the following block diagram.

Figure 48: SERDES ECU Block Diagram

ECU Mode Select

The ECU block can be configured for eight arithmetic functions via an instruction as shown

in

Tabl e 31 . The modes for the ECU block are Dynamically Re-programmable through the

Instruction Set Sequencer.

Table 31: Instruction Set Sequencer

Instruction Set Operation

0 0 0 Multiply

0 0 1 Multiply - Add

0 1 0 Accumulate

0 1 1 Add

1 0 0 Multiply (registered)

a

a. A[15:0] set to zero.

1 0 1 Multiply - Add (registered)

1 1 0 Multiply Accumulate

1 1 1 Add (registered)

Abus

16

Xbus

8

Ybus

8

Ibus

3

Sign

1

Rbus

17

88

16 16

Multiply Add Register

Sequencer Memory Logic Cell

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

39

www.quicklogic.com

Clock Networks Description

Global Clocks

In the QuickSD device, there are nine global clock networks: one is dedicated and eight are

programmable . Global clocks can drive logic cell, I/O, ECU blocks and RAM registers in the

device. Five global clocks will have access to a Quad Net (local clock network) connection

with a programmable connection to the register inputs.

Figure 49 gives the global clock

methodology

Figure 49: Global Clock

Quad-Net Network

There are five Quad-Net local clock networks in each quadrant for a total of 20 in a device.

Each Quad-Net is local to a quadrant. Quad-Net is multiplexed with the clock buffer before

driving the column clock buffers.

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

40

Dedicated Clock

There is one dedicated clock in QuickSD devices. It connects to the clock input of the

SuperCell, I/O, and RAM registers through a hardwired connection and is multiplexed with

the programmable clock input. There are four inversions from pad to register inputs and the

dedicated clock takes on the same configuration as the global clock. The dedicated clock

provides a fast global network with low skew. You can select either the dedicated clock or the

programmable clock;

Figure 50 gives the dedicated clock circuitry within the logic cell.

Figure 50: Dedicated Clock Circuitry

The performance of the dedicated clock is given in Table 3 2

Table 32: Dedicated Clock Performance

Clock Performance

TT, 25C, 2.5 V Global Dedicated

Macro (rear) 1.51 1.59

I/O (far) 2.06 1.73

Skew 0.55 0.14

Programmable clock

Hard-wired clock

CLK

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

41

www.quicklogic.com

I/O Cell Structure

I/O Cell Structure General Description

The QuickSD device features a variety of distinct I/O pins to maximize performance,

functionality, and flexibility with bi-directional I/O pins and input-only pins. All input and I/O

pins are 2.5 V and 3.3 V tolerant and comply with the specific I/O standard selected. The

outputs swing from Vss to VCCIO (0 V to 3.3 V ± 10%). The VCCIO pins must be tied to

a 3.3 V supply to provide 3.3 V compliance.

If 3.3 V compliance is not required, then these pins must be tied to the 2.5 V supply.

Table 33 summarizes the I/O specifications that are supported.

As designs become more complex and requirements more stringent, varying I/O standards

are developing for specific applications. I/O standards for processors, memories and various

bus applications have become common place and a requirement for many systems. In

addition, I/O timing has become a greater issue with specific requirements for setup, hold,

clock to out, and switching times.

The QuickSD device has addressed these changing system requirements. The QuickSD

device includes a completely new I/O cell which consists of programmable I/Os as well as a

new cell structure consisting of three registers: input, output and output enable. The QuickSD

device offers banks of programmable I/O that addresses many of the new bus standards that

are popular today. In addition, the input register addresses the setup time, the output register

addresses clock-to-out time, and the OE register addresses the switching time from high

impedance to a given value.

Figure 51 shows the QuickSD device I/O cell.

Table 33: Supported I/O Specifications

/O Standard Reference Voltage Output Voltage Application

LVTTL n/a 3.3 general purpose

LVCMOS2 n/a 2.5 general purpose

PCI n/a 3.3 PCI bus applications

GTL+ 1 n/a high speed bus - Pentium Pro

SSTL3 1.5 3.3 memory bus - Hitachi, IBM

SSTL2 1.25 2.5 memory bus - Hitachi, IBM

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

42

Figure 51: QuickSD I/O Cell

The bi-directional I/O pin options can be programmed for input, output, or bi-directional

operation. Each bi-directional I/O pin is associated with an I/O cell which features an

input/feedback register, an input buffer, output/feedback register, three-state output buffer,

an output enable register, and two 2-to-1 multiplexers.

For input functions, I/O pins can provide combinatorial

registered data or both options

simultaneously to the logic array. For combinatorial input operation, data is routed from I/O

pins through the input buffer to the array logic. For registered input operation, I/O pins drive

the D input of input cell registers, allowing data to be captured with fast set-up times without

consuming internal logic cell resources.

For output functions, I/O pins can receive combinatorial or registered data from the logic

array. For combinatorial output operation, data is routed from the logic array through a

multiplexer to the I/O pin. For registered output operation, the array logic drives the D input

of the output cell register which in turn drives the I/O pin through a multiplexer. The

multiplexer allows either a combinatorial or a registered signal to be driven to the I/O pin.

The three-state output buffer controls the flow of data from the array logic to the I/O pin and

allows the I/O pin to act as an input and/or output. The buffer's output enable can be

individually controlled by a logic cell array or any pin (through the regular routing resources),

or bank-controlled through one of the global networks.

The signal can also be either combinatorial or registered. This is identical to that of the flow

for the output cell. For combinatorial control operation, data is routed from the logic array

through a multiplexer to the three-state control. For registered control operation, the array

logic drives the D input of the OE cell register which in turn drives the three-state control

through a multiplexer. The multiplexer allows either a combinatorial or a registered signal to

be driven to the three-state control.

For output functions, I/O pins can be individually configured for active HIGH, active LOW,

or open-drain inverting operation. In the active HIGH and active LOW modes, the pins of

all devices are fully 3.3 V compliant.

E

Q

R

D

E

D

R

Q

PA D

E

D

R

Q

+

-

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

43

www.quicklogic.com

When I/O pins are unused, the OE controls can be permanently disabled, allowing the output

cell register to be used for registered feedback into the logic array.

I/O cell registers are controlled by clock, clock enable, and reset signals, which can come

from the regular routing resources, from one of the global networks, or from two input pins

per bank of I/O's. The CLK and RESET signals share a common line, while the clock enables

for each register can be independently controlled. Additionally, the output and enable

registers will increase a device's register count. The addition of an output register will also

decrease the TCO. Since the output register does not need to drive the routing, the length

of the output path is also reduced.

Extra registers add more inputs and outputs to the I/O structure. Extra routing resources are

added to connect the I/O structure to the other parts of the device.

I/O interface support is programmable on a per bank basis. There are 4 I/O banks per chip.

Users can not mix a 2.5 volt I/O with 3.3 volt I/O on the same I/O bank.

Figure 52 illustrates

the multiple I/O bank configurations.

Figure 52: Multiple I/O Bank Configurations

Each I/O bank is independent of other I/O banks and each I/O bank has its own V

CCIO

and

V

REF

supplies. A mixture of different I/O standards can be used on the device; however, there

is a limitation as to which I/O standards can be supported within a given bank. Differential

I/O can be shared with non differential I/O. There can only be one V

REF

and one V

CCIO

per

bank.

Programmable Slew Rate

Each I/O has programmable slew rate capability. The rate is programmable to one of two

slew rates: either fast or slow. The slower rate can be used to reduce ground bounce noise.

The slow slew rate is 1 V/ns under typical conditions. The fast slew rate is 2.8 V/ns

Table 34: 3.3 V Slew Rate

VCCIO = 3.3 V Fast Slew Slow Slew

Rising Edge 2.8 V/nS 1.0 V/vS

Falling Edge 2.86 V/nS 1.0 V/nS

VCCIO 0 VREF 0

I/O Bank 0

I/O Bank 1

VCCIO 1

VREF 1

I/O Bank 2

VCCIO 2VREF 2

I/O Bank 3

VCCIO 3

VREF 3

www.quicklogic.com

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary

44

.

NOTE:

Condition: 2.5 V, 25 °C

Programmable Weak-Pull

Programmable weak pull-down resistors are available on each I/O. I/O Weak Pull-Down

eliminates the need for an external pull-down resistor for used I/O. The spec for pull-down

current is a maximum of 150 uA under a worst case condition.

-148 uA @ 3.6 V, -55 °C,

- 69 uA@ 2.5 V, 25 °C. Figure 53 illustrates the weak pull-down circuit.

Figure 53: I/O Weak Pull-Down Circuit

I/O Control and Local Hi-Drives

Each bank of I/Os has two input-only pins that can be programmed to drive the RST, CLK,

and EN inputs of I/O's in that bank. These input-only pins also double up as high-drive inputs

to a quadrant. Both as an I/O control or high-drive, these buffers can be driven by the

internal logic. The I/O control network and local high-drive performance is indicated in

Tabl e 36 .

Table 35: 2.5 V Slew Rate

VCCIO = 2.5 V Fast Slew Slow Slew

Rising Edge 1.7 V/nS 0.6 V/vS

Falling Edge 1.9 V/nS 0.6 V/nS

Table 36: I/O Control Network/ Local Hi-Drive Performance

TT, 25C, 2.5V From Pad From Array

I/O (slow) 1.00 ns 1.14 ns

I/O (fast) 0.63 ns 0.78 ns

Skew 0.37 ns 0.36 ns

I/O

Register 1

PAD

© 2002 QuickLogic Corporation

•

•

•

•

•

•

QL82SD Device Data Sheet Rev C

Preliminary