QUICK LOGIC QL2009-0PB256C, QL2009-0PB256I, QL2009-0PF144C, QL2009-0PF144I, QL2009-0PQ208C Datasheet

...

QL2009

3.3V and 5.0V pASIC 2 FPGA

Combining Speed, Density, Low Cost and Flexibility

Rev. C

pASIC 2

HIGHLIGHTS

… 9,000

usable ASIC gates,

225 I/O pins

QL2009

Block Diagram

Ultimate Verilog/VHDL Silicon Solution

-Abundant, high-speed interconnect eliminates manual routing

-Flexible logic cell provides high efficiency and performance

-Design tools produce fast, efficient Verilog/VHDL synthesis

Speed, Density, Low Cost and Flexibility in One Device

-16-bit counter speeds exceeding 200 MHz

-9,000 usable ASIC gates, 16,000 usable PLD gates, 225 I/Os

-3-layer metal ViaLink process for small die sizes

-100% routable and pin-out maintainable

Advanced Logic Cell and I/O Capabilities

-Complex functions (up to 16 inputs) in a single logic cell

-High synthesis gate utilization from logic cell fragments

-Full IEEE Standard JTAG boundary scan capability

-Individually-controlled input/feedback registers and OEs on all I/O pins

Other Important Family Features

-3.3V and 5.0V operation with low standby power

-I/O pin-compatibility between different devices in the same packages

-PCI compliant (at 5.0V), full speed 33 MHz implementations

-High design security provided by security fuses

3

pASIC 2

672

Logic

Cells

3-35

QL2009

PRODUCT

SUMMARY

FEATURES

The QL2009 is a 9,000 usable ASIC gate,16,000 usable PLD gate member of

the pASIC 2 family of FPGAs. pASIC 2 FPGAs employ a unique combination

of architecture, technology, and software tools to provide high speed, high

usable density, low price, and flexibility in the same devices. The flexibility

and speed make pASIC 2 devices an efficient and high performance silicon

solution for designs described using HDLs such as Verilog and VHDL, as well

as schematics.

The QL2009 contains 672 logic cells. With 225 maximum I/Os, the QL2009

is available in 144-pin TQFP, 208-PQFP, and 256-pin PBGA packages.

Software support for the complete pASIC families, including the QL2009, is

available through three basic packages. The turnkey QuickWorks package

provides the most complete FPGA software solution from design entry to logic

synthesis (by Synplicity, Inc.), to place and route, to simulation. The

QuickToolsTM and QuickChipTM packages provide a solution for designers

who use Cadence, Mentor, Synopsys, Viewlogic, Veribest, or other third-party

tools for design entry, synthesis, or simulation.

Total of 225 I/O Pins

- 217 bidirectional input/output pins, PCI-compliant at 5.0V

in -1/-2 speed grades

- 4 high-drive input-only pins

- 4 high-drive input/distributed network pins

Four Low-Skew (less than 0.5ns) Distributed Networks

- Two array networks available to logic cell flip-flop clock, set, and

reset - each driven by an input-only pin

- Two global clock/control networks available to F1 logic input, and

logic cell flip-flop clock, set, reset; input and I/O register clock, reset,

enable; and output enable controls - each driven by an input-only pin, or

any input or I/O pin, or any logic cell output or I/O cell feedback

High Performance

- Input + logic cell + output delays under 6 ns

- Datapath speeds exceeding 225 MHz

- Counter speeds over 200 MHz

3-36

QL2009

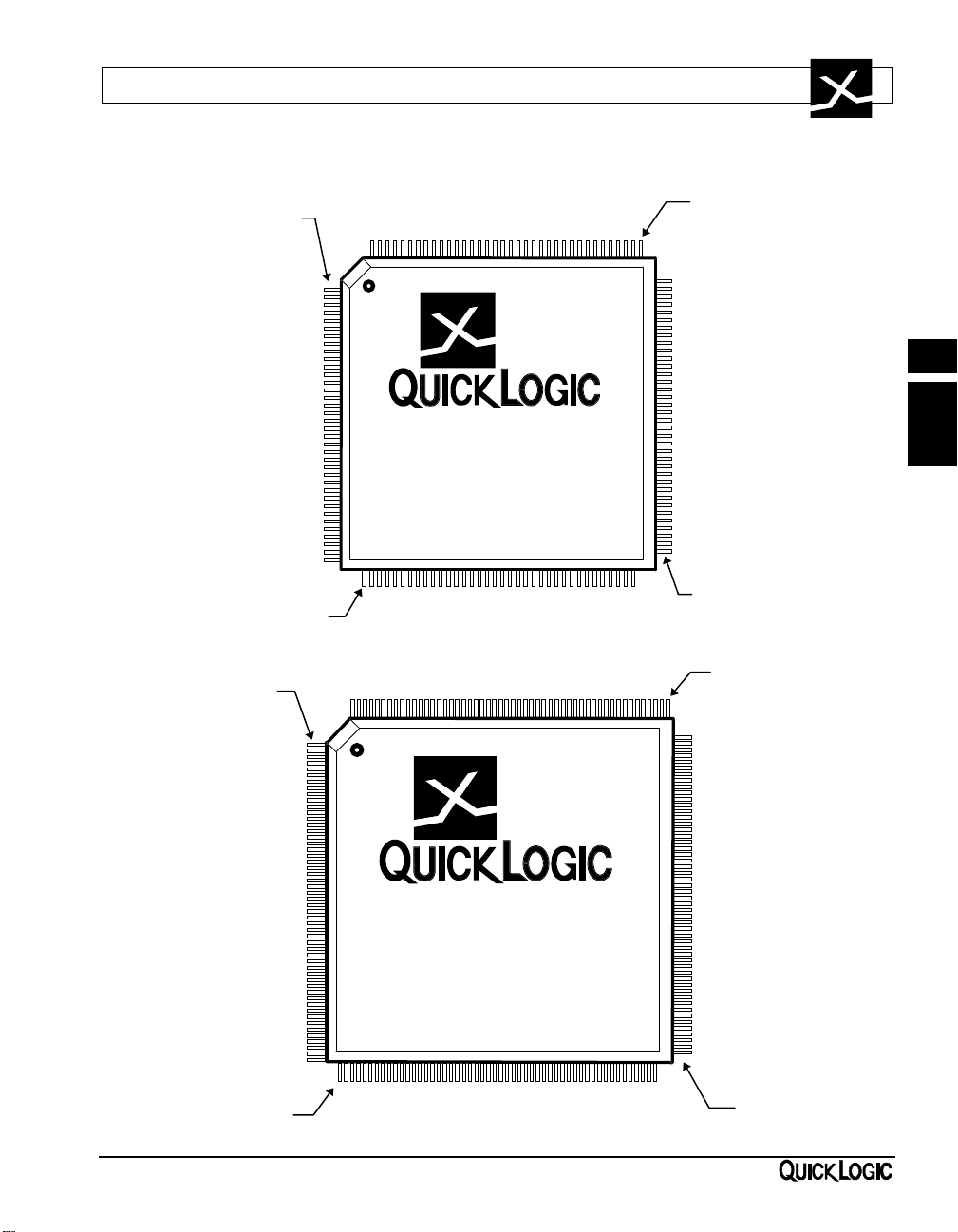

PIN # 1

PINOUT DIAGRAMS

PIN # 109

144-PIN TQFP

3

pASIC 2

pASIC

QL2009-1PF144C

PIN # 37

PIN # 1

PIN # 53

208-PIN PQFP

PIN # 73

PIN # 157

pASIC

QL2009-1PQ208C

PIN # 105

3-37

QL2009

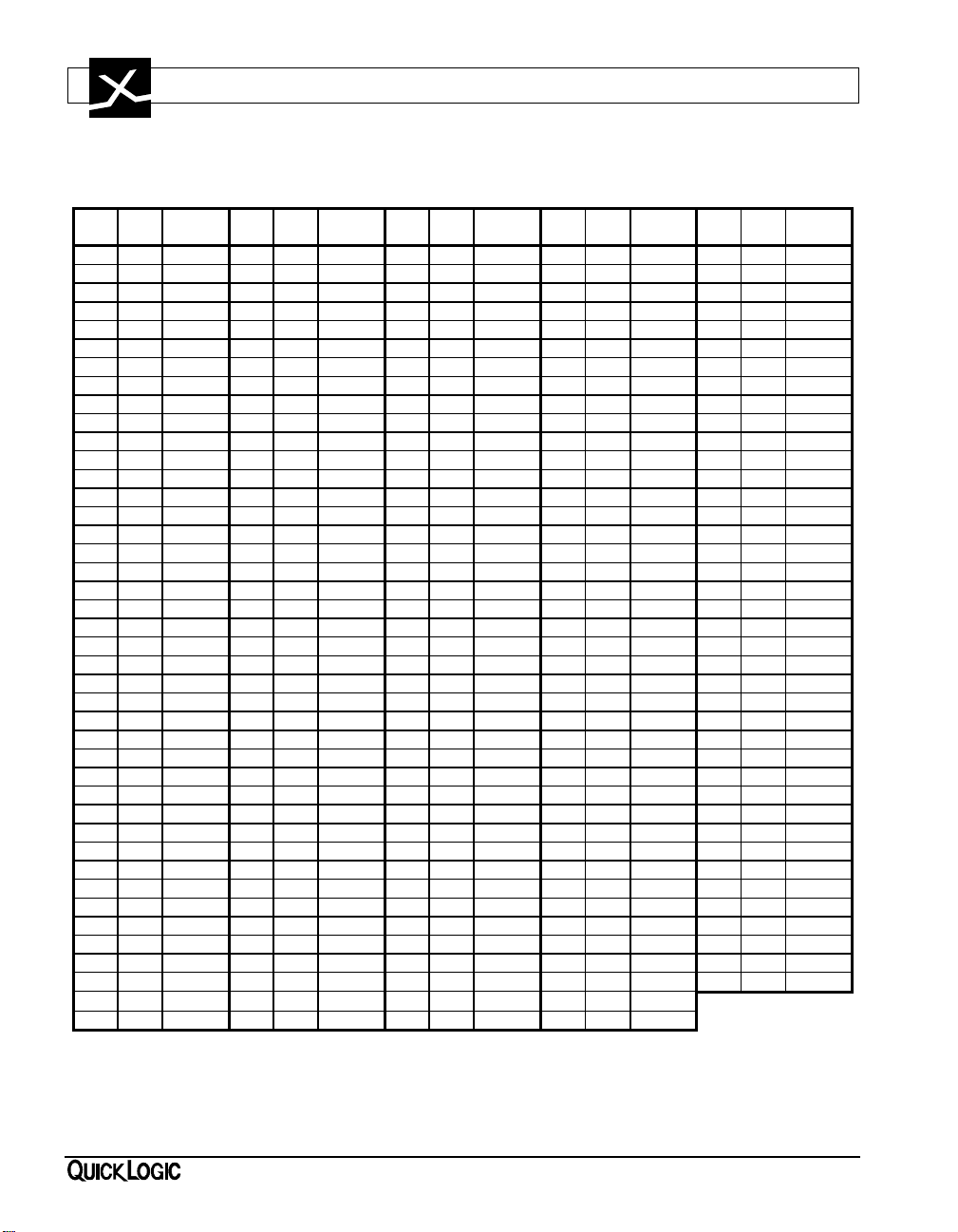

PQFP 208 and TQFP 144 Pinout Table

208 144 Function 208 144 Function 208 144 Function 208 144 Function 208 144 Function

PQFP TQFP PQFP TQFP PQFP TQFP PQFP TQFP PQFP TQFP

1 NC I/O 43 30 GND 85 60 I/O 127 87 GND 169 117 I/O

2 1 I/O 44 31 I/O 86 61 I/O 128 88 I/O 170 118 I/O

3 2 I/O 45 NC I/O 87 NC I/O 129 89 I 171 119 I/O

4 3 I/O 46 32 I/O 88 62 I/O 130 90 ACLK / I 172 120 I/O

5 NC I/O 47 NC I/O 89 63 I/O 131 91 VCC 173 NC I/O

6 4 I/O 48 33 I/O 90 NC I/O 132 92 I 174 NC I/O

7 5 I/O 49 NC I/O 91 NC I/O 133 93 GCLK / I 175 121 I/O

8 NC I/O 50 34 I/O 92 64 I/O 134 94 VCC 176 NC I/O

9 6 I/O 51 35 I/O 93 NC I/O 135 95 I/O 177 122 GND

10 7 VCC 52 36 I/O 94 65 I/O 136 NC I/O 178 123 I/O

11 NC I/O 53 37 I/O 95 66 GND 137 96 I/O 179 124 I/O

12 NC GND 54 38 TDI 96 67 I/O 138 NC I/O 180 NC I/O

13 8 I/O 55 39 I/O 97 NC VCC 139 97 I/O 181 125 I/O

14 NC I/O 56 NC I/O 98 NC I/O 140 98 I/O 182 126 GND

15 9 I/O 57 40 I/O 99 68 I/O 141 NC I/O 183 127 I/O

16 NC I/O 58 NC I/O 100 69 I/O 142 99 I/O 184 128 I/O

17 10 I/O 59 NC GND 101 NC I/O 143 NC I/O 185 129 I/O

18 11 I/O 60 41 I/O 102 70 I/O 144 100 I/O 186 NC I/O

19 12 I/O 61 42 VCC 103 71 TRSTB 145 NC VCC 187 130 VCC

20 13 I/O 62 43 I/O 104 72 TMS 146 101 I/O 188 131 I/O

21 NC I/O 63 NC I/O 105 NC I/O 147 102 GND 189 132 I/O

22 14 I/O 64 44 I/O 106 73 I/O 148 103 I/O 190 NC I/O

23 15 GND 65 45 I/O 107 NC I/O 149 104 I/O 191 133 I/O

24 16 I/O 66 NC I/O 108 74 I/O 150 NC I/O 192 134 I/O

25 17 I 67 46 I/O 109 75 I/O 151 105 I/O 193 NC I/O

26 18 ACLK / I 68 47 I/O 110 76 I/O 152 106 I/O 194 135 I/O

27 19 VCC 69 48 I/O 111 77 I/O 153 NC I/O 195 136 I/O

28 20 I 70 NC I/O 112 NC I/O 154 107 I/O 196 NC I/O

29 21 GCLK / I 71 49 I/O 113 78 I/O 155 NC I/O 197 137 I/O

30 22 VCC 72 NC I/O 114 79 VCC 156 108 I/O 198 NC I/O

31 23 I/O 73 50 GND 115 80 I/O 157 109 TCK 199 138 GND

32 NC I/O 74 51 I/O 116 NC GND 158 110 STM 200 139 I/O

33 24 I/O 75 52 I/O 117 81 I/O 159 111 I/O 201 NC VCC

34 NC I/O 76 NC I/O 118 82 I/O 160 NC I/O 202 140 I/O

35 25 I/O 77 53 I/O 119 NC I/O 161 112 I/O 203 NC I/O

36 NC I/O 78 54 GND 120 83 I/O 162 113 I/O 204 141 I/O

37 26 I/O 79 55 I/O 121 NC I/O 163 NC GND 205 142 I/O

38 27 I/O 80 56 I/O 122 84 I/O 164 NC I/O 206 NC I/O

39 28 I/O 81 NC I/O 123 85 I/O 165 114 VCC 207 143 TDO

40 NC I/O 82 57 I/O 124 NC I/O 166 115 I/O 208 144 I/O

41 NC VCC 83 58 VCC 125 86 I/O 167 116 I/O

42 29 I/O 84 59 I/O 126 NC I/O 168 NC I/O

3-38

Loading...

Loading...