Page 1

Q200

Series™

Intelligent Disk Drives

Technical Reference Manual

For Q250, Q280

Disk Drives

Page 2

Q200

SERIES

tm

INTELLIGENT DISK DRIVES

Q250jQ280

DISK

DRIVES

Technical

Publication

Reference

No.

REV

A

Manual

81-45528

Page 3

PREFACE

This

the

technicians

integrating

Quantum

products

or

Additional

following~manuals:

Publication

Quantum

Quantum

ANSI

Quantum

Representative,

spare

Publication

manual

Q250

contains

and

and

them

reserves

without

improvements

information

No.

81-45233

81-45416

X3.131-1986

publications

parts.

No

Q280

engineers

the

in

or

81-45528

rigid

into

incurring

units

may

technical

disk

evaluating

systems.

right

to

any

previously

on

the

Title

Q250/Q280

Q200

Small

may

be

Series

Computer

be

ordered

Rev.

reference

drives.

make

changes

obligation

Q250

Disk

and

Drives.

Programmer's

System

requested

from

KL587

UL/CSA/VDE

information

Information

or

maintaining

to

sold

or

Q280

Interface

from

Quantum

and/or

incorporate

shipped.

is

given

OEM

Manual

Manual

your

Quantum

in

describing

is

intended

the

drives,

improvements

such

in

the

(SCSI)

Sales

the

same

manner

for

or

to

its

changes

as

CSA

certification

VDE

Model

material

Q250

and

shipment.

~arranty

and

representative.

Quantum

The

and

u.S.

service

product

is

the

Patents

Copyright

Q200

AIRLOCK

Printed

Series

is

in

UL

recognition

certification

and

Q280

workmanship

The

warranty

further

center

described

subject

are

1987

Quantum

and

a

registered

DisCache

U.S.A.

granted

disk

details

All

requests

herein

of

allowed

expected

granted

under

granted

WARRANTY

drives

for

a

period

includes

can

for

in

your

area.

PATENTS

is

pending

to

issue

Corporation.

are

trademarks

trademark

under

File

per

are

warranted

parts

be

obtained

service

covered

in

All

of

Quantum

Nos.

File

of

one

and

by

patent

1987.

rights

of

File

No.

LR496896-8

No.

11342-3250-1002

against

year

labor.

from

should

u.S.

be

Patent

applications

reserved.

Quantum

Corporation.

E78016

and

defects

from

your

This

date

is

Quantum

directed

No.

Corporation.

LR496896-11

in

of

a

limited

sales

to

the

4,538,193,

from

which

ii

Page 4

PREFACE

TAB

L E o F

CON

TEN

T S

. .

ii

SECTION

1.1

1.2

Features

Logic

SECTION

2.1

Head

2.1.1

2.1.2

2.1.3

2.1.4

2.1.S

2.1.6

2.1.7

2.2

Drive

2.2.

2.2.2

2.2.3

2.2.4

2.2.S

2.2.6

2.2.7

2.2.8

2.3

PCB

2.3.1

2.3.2

2.3.3

2.3.4

2.3.S

2.3.6

2.3.7

2.3.8

2.3.9

2.3.10

2.4

2.S

2.6

Power-Up

Read

write

1.

INTRODUCTION .

. . . . . .

Conventions

2.

PRINCIPLES

Disk

Assembly

Base

Disk

Rotary

Headstack

Automatic

DC

Drive

Air

Electronics.

1

Disk

Simplified

SCSI

SCSI

SCSI

Power

Shorting

Flex

Functional

Power-On-Reset

Motor

Electronic

S080

Servo

Actuator

Read/Write

FYLO

DICEY

Microprocessor

Sequence/Recalibration.

Command

Command

..

casting

Stack

Assembly.

positioner

Assembly.

Actuator

Motor.

Filtration.

Format

Explanation--Block

Bus

Physical

Bus

Signal

Bus

Timing.

Requirements.

Plug

Circuit

Elements.

Control

Return

SCSI

Bus

Control,

Positioning

Circuit.

Timing

Data

Controller

Controller

Sequence.

Sequence.

OF

OPERATION

(HDA)

. . . . . .

Assembly.

..

. . .

. . . .

Assembly

(Actuator)

. . . . . . . . . .

Lock

(AIRLOCK)

. . . . .

...

.

..

. .

.

..............

. . . . . . . . .

Interface.

Descriptions

.

..

. . .

Options.

............

......

..

.

....................

.

..

(POR)

and

Circuit

Spring.

Controller.

AMC

and

...............

Servo

.

Warm

. . .

. . .

AGC.

circuit.

. . . . . . . . . . . .

IC,

and

IC.

and

EPROM

. . . . . . . .

.

..

.

..

..

.........

.........

.........

..

Diagram

......

...........

...........

Reset

..

. . .

.

..

xtal

........

.........

.

..........

...........

. . .

. . . . . . . .

. . . . . . . .

.

......

.

......

.......

.......

.......

.......

.

......

. .

........

.

.....

......

..

.

.....

..

..

Oscillators

..

......

.

.

1-1

1-1

1-2

2-1

2-1

2-1

2-2

2-2

2-2

2-2

2-2

2-3

2-4

2-4

2-4

2-8

2-10

2-11

2-14

2-16

2-19

2-19

2-19

2-20

2-21

2-21

2-23

2-27

2-27

2-29

2-30

2-32

2-32

2-33

2-33

SECTION

3.

ENGINEERING

DRAWINGS

.

iii

3-1

.

Page 5

SECTION

4.

APPLICATIONS . .

. . . . . .

4-1

4.1

4.2

4.3

Special

4.1.1

4.1.2

Errors

4 • 2 • 1

4.2.2

4.2.3

4.2.4

Grounding,

SECTION

5.1

5.2

5.3

5.4

5.5

Maintenance

Level

Level

Connector

PCB

5.5.1

5.5.2

5.5.3

SECTION

6.1

6.2

Spare

Reference

Considerations.

-REQ/-ACK

Hints

and

Errors.

Allocating

Creating

Updating

5.

MAINTENANCE.

1

Maintenance.

2

Maintenance.

Waveforms

Special

Techniques

Test

6.

PARTS

Parts

Handshake.

for

Software

Media

Defects.

. . . . . . . . . . . . . .

Replacement

the

the

Electrostatic

Precautions.

Maintenance.

and

Techniques.

Test

and

Connector

LISTS

List

Parts

...

....

List(s)

. . . . .

Driver

writers

. . . . . . . .

Sectors.

Defect

Drive

Lists.

Using

the

Discharges,

. .

. . . . . . . . .

. . . . . . . . .

. . .

. . . .

..

. . . . . . . .

Equipment

Waveform

J5

Signals.

...............

Descriptions

.

.

..

..

..

.

. . . . . .

Defect

and

Lists

EMI

..

..

............

.

.........

........

. . . . . .

.

......

...

.......

.....

. .

.

.....

..

..

....

.

....

.

...

...

...

..

. •

.•

..

. .

4-1

4-1

4-3

4-5

4 - 5

4-6

4-8

4-9

4-10

5-1

5-1

5-1

5-2

5-2

5-2

5-2

5-3

5-4

6-1

6-1

6-2

iv

Page 6

LIS

T

o F

FIG

U

RES

2-1

2-2

2-3

2-4

2-5

2-6

2-7

2-8

2-9

2-10

2-11

2-12

2-13

2-14

2-15

2-16

2-17

3-1

3-2

3-3

3-4

3-5

3-6

3-7

3-8

3-9

3-10

3-11

3-12

4-1

4-2

4-3

4-4

4-5

Exploded

Inside

Disk

Electronics

J1

SCSI

SCSI

Drive

General

Connector

5080

5080

Servo

Read

DICEY

Power-Up

Read

write

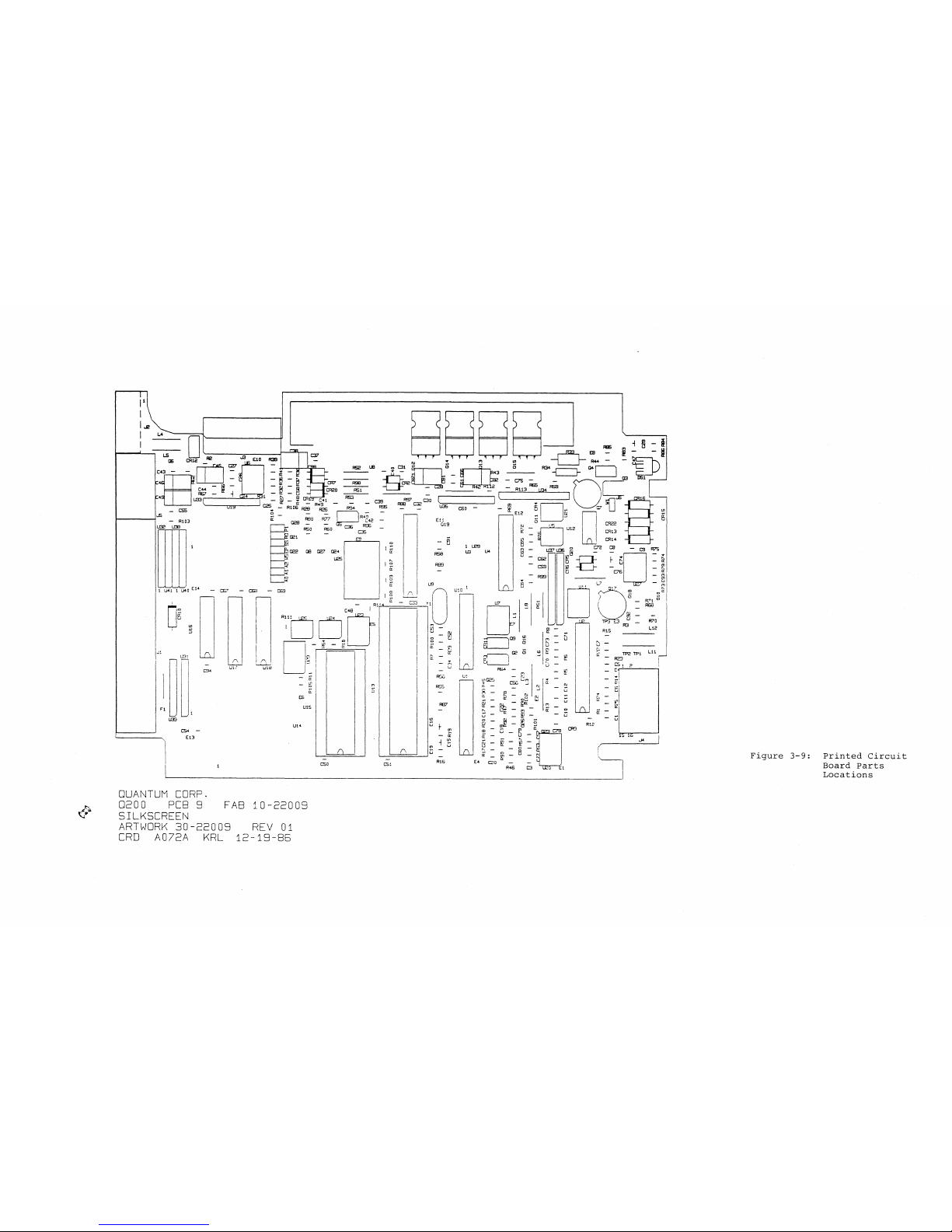

Printed

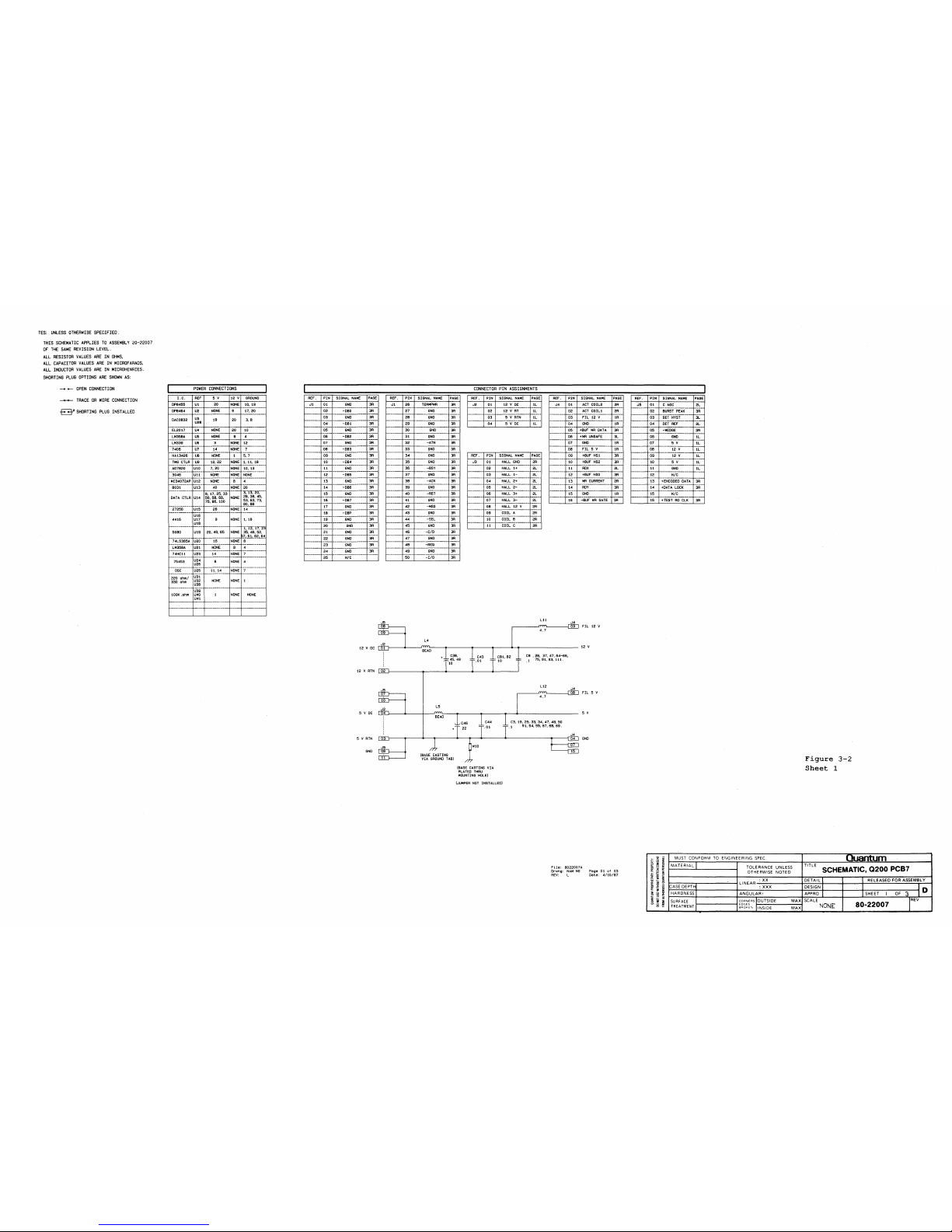

Schematic,

Schematic,

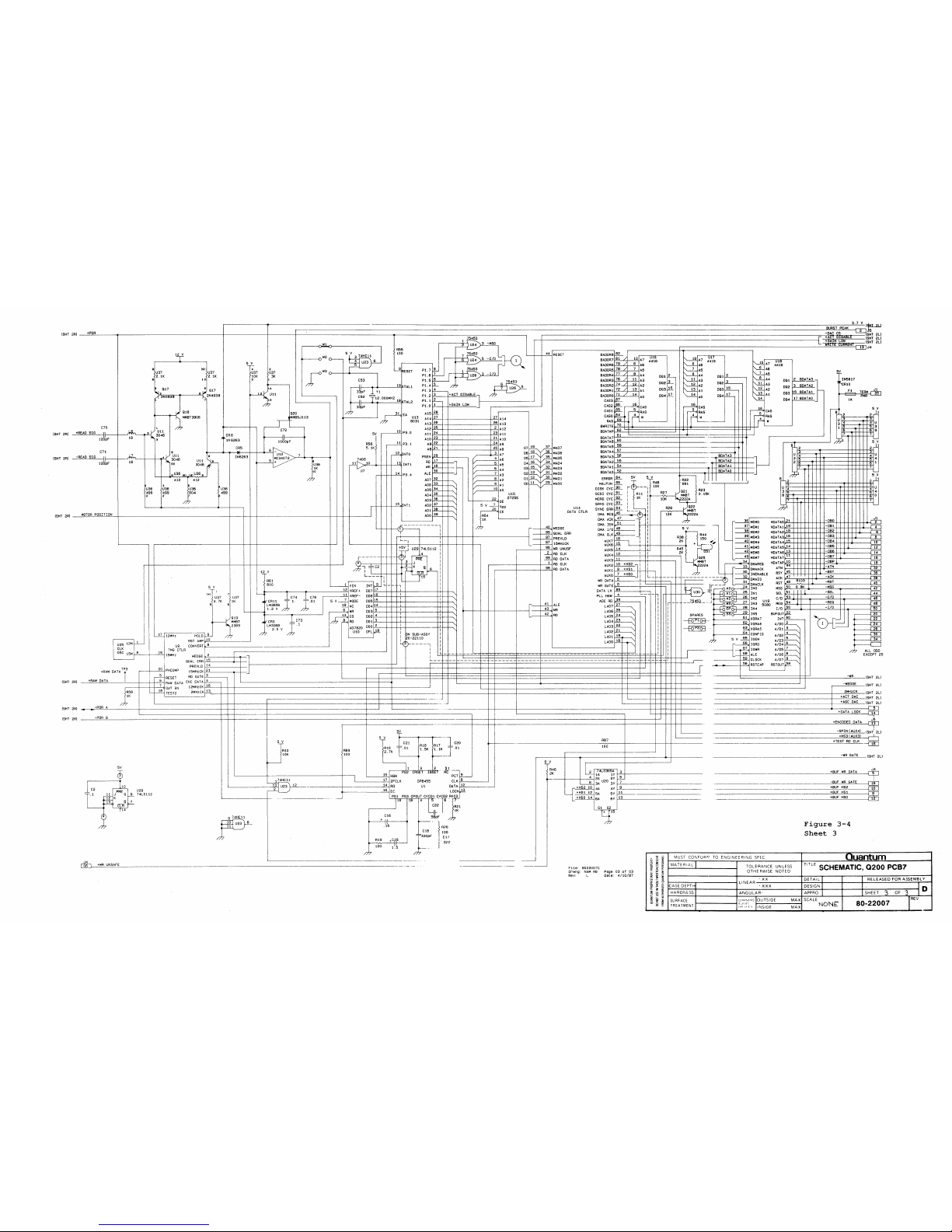

Schematic,

Printed

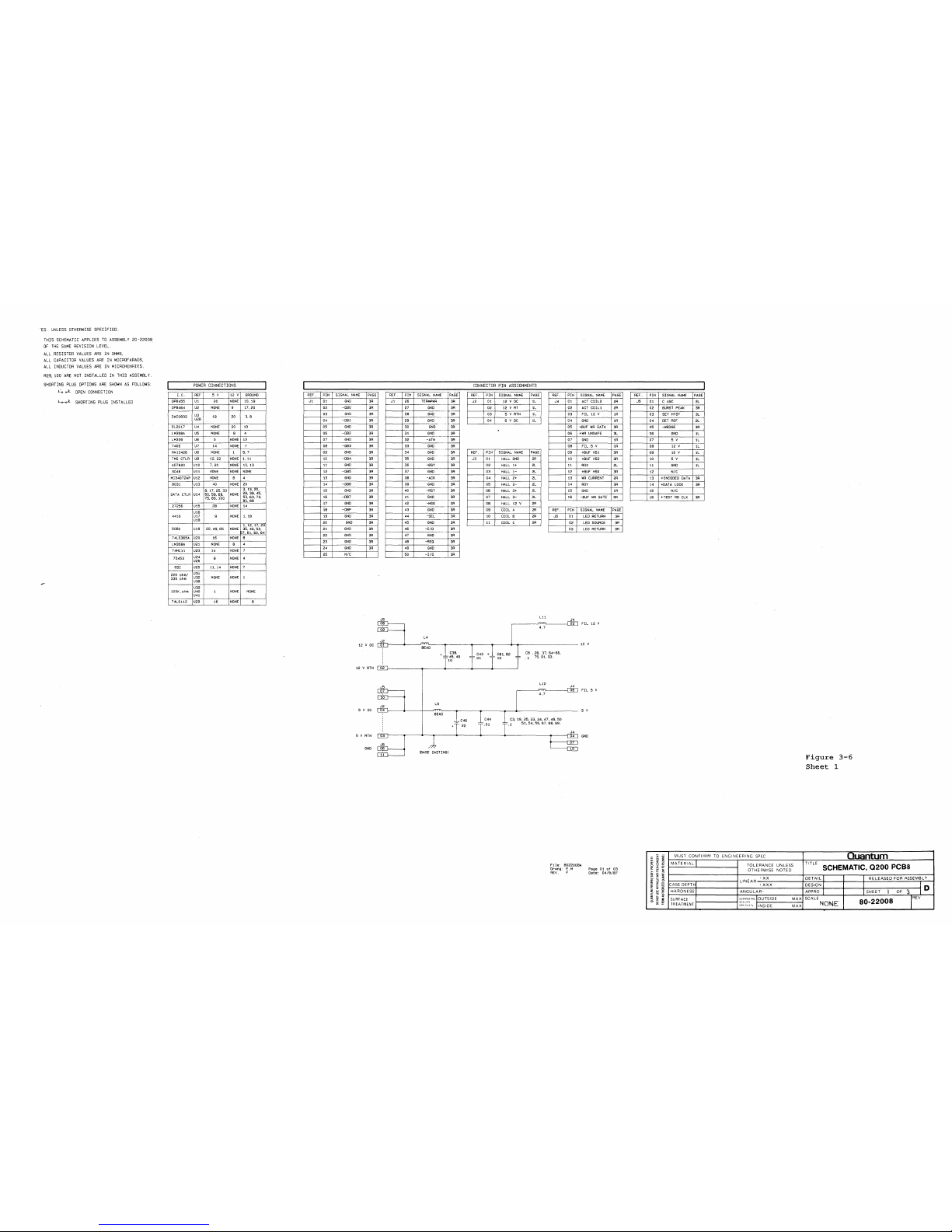

Schematic,

Schematic,

Schematic,

Printed

Schematic,

Schematic,

Schematic,

-REQ/-ACK

Buffer

In-Line

In-Line

Sparing

View

Format:

Connector.

Bus.

Bus

Startup

PCB

Conceptual

Interface

AMC

Circuit

Block

Command

Command

Circuit

Circuit

Circuit

Full

Sparing

Sparing

of

View

Timing

Locations

Sequence.

Handshake.

. . . . . .

of

Drive,

Wedges,

Block

. . . . . .

Typical

Current

Layout;

and

ADC

Waveforms

Diagram.

Sequence.

Sequence

PCB-7,

PCB-7,

PCB-7,

PCB-8,

PCB-8,

PCB-8,

PCB-9,

PCB-9,

PCB-9,

and

Field-Found

Showing

Sectors,

Diagram

Circuit

Diagram

Profile

Plug,

Block

Diagram

Circuit

. . . . .

.. ..

Board

Board

Board

Empty

of

Overflow

Parts

Sheet

Sheet

Sheet

Parts

Sheet

Sheet

Sheet

Parts

Sheet

Sheet

Sheet

Q250/Q280

Ratios.

Defective

..

Air

..

..

of

. . . . • . . . . . . . . . . . .

Terminator

Diagram.

. . . . . . .

Waveforms.

. . . . . . . . .

. .

..

. . . . .

Locations

1

· ·

2

· · · · · · · ·

3

· · · ·

Locations

1

·

2

· · ·

3

·

·

Locations

1

·

2

·

3

· · ·

Sectors.

of

Defective

Defective

......

Filtration.

and

Tracks.

............

.....

a

Signal

. . . .

. . . .

..

. . . . .

...

· ·

· · · · · ·

·

·

· · · ·

·

Line

..

and

.........

· . . . . . . . . 2

...

.

..

.

(PCB-7)

· ·

·

· · · ·

(PCB-8)

·

· ·

·

· ·

(PCB-9)

·

. . . . . .

. . . . . . . .

.....

.......

......

· . . . . . . .

· .

..

· . . .

· . . . . .

· . . . . .

· .

..

· . . . . . .

·

· ·

·

·

· ·

· ·

· · ·

·

· · · ·

· · · ·

·

·

· ·

· ·

·

· · ·

· · · · · · ·

· ·

·

Target

. . . . . . . . . . . . . .

Sectors.

· ·

Sends

. .

..

Sectors

. . . . . . . .

Data

·

·

. .

.

...

. . . . . .

. .

..

.

·

·

·

·

·

·

· ·

·

·

·

·

·

·

2-1

2-3

2-5

2-6

2-9

2-10

2-13

2-16

2-17

-2

2-22

2-25

2-28

2-31

2-34

2-35

2-36

3-2

3-3

3-4

3-5

3-6

3-7

3-8

3-9

3-10

3-11

3-12

3-13

4-2

4-3

4-7

4-7

4-8

2

5-1

5-2

5-3

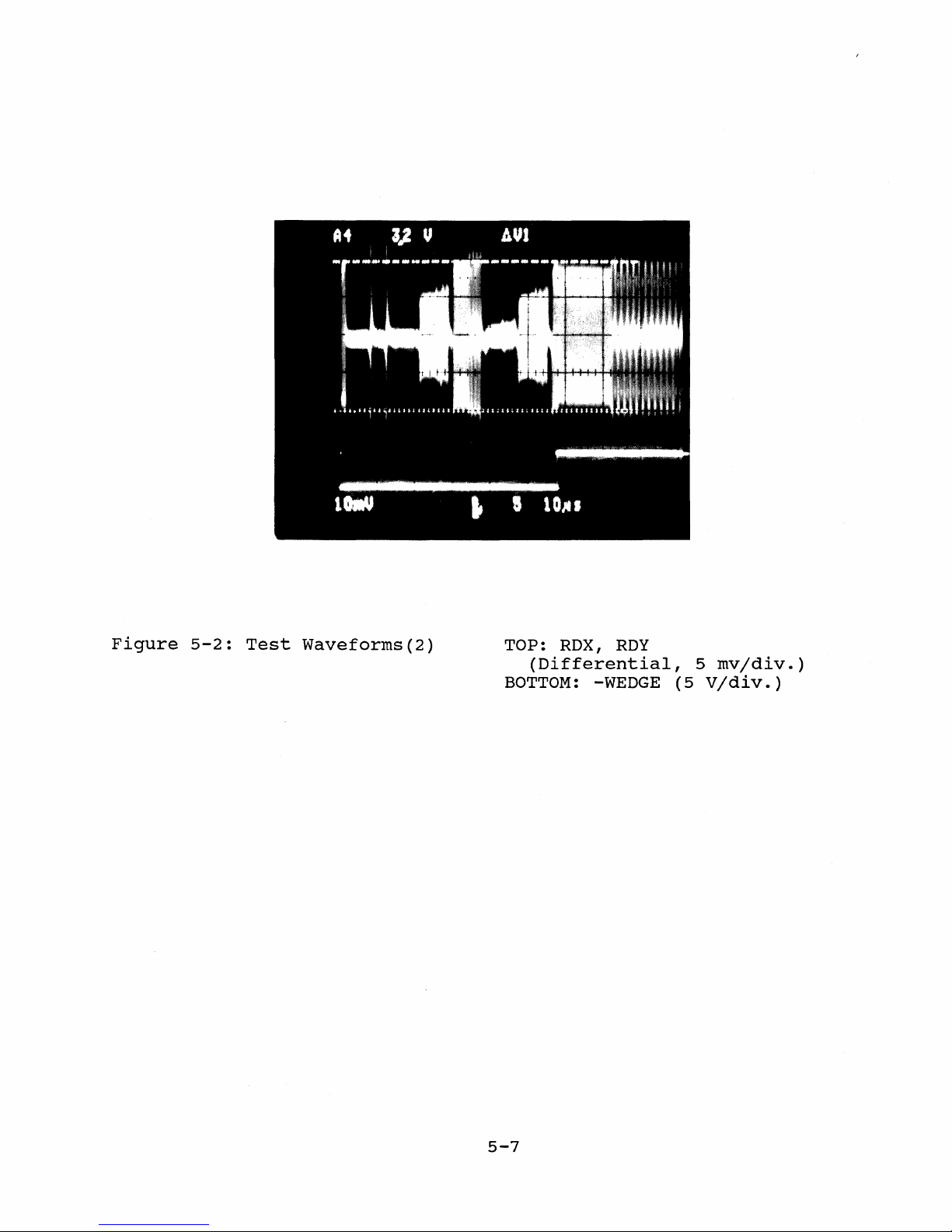

Test

Test

Test

Waveforms(1)

Waveforms(2)

Waveforms(3)

v

· . . . .

· .

· . . . . .

5-6

5-7

5-8

Page 7

2-1

2-2

2-3

J1

Pin

Assignments.

DC

Power

Requirements

Microprocessors

LIS

and

T o F

. . . .

Buffer

.

.....

RAM.

TAB

..

. . . . .

.

L E S

...

. . . • . •

· • •

.

2-9

2-15

2-32

4-1

5-1

Available

Test

Connector

Spare

and

J5

Defective

Signals

. .

Sectors

.

· . .

· . •

4-8

5-5

vi

Page 8

1.1

Features

Q250

System

and

Interface

plug-in

(PCB).

electronics

and

actuator

the

flex

The

following

throughput:

o

o

o

o

Q280

EPROM

These

except

rotor

circuit

Seeks

processed

14

KByte

and

Optional

(See

concerning

Cylinder

accessing

drives

(SCSI)

IC,

both

drives

the

are

inside

features

are

FIFO

from

the

DisCache

the

Q200

and

feature

on-board,

controllers,

models

require

spindle

use

no

motor,

contained

the

sealed

of

the

Q250/Q280

initiated

immediately--other

simultaneously.

data

SCSI

buffer

bus

increases

Series

this

data

option.)

head

skewing

sequentially

ANSI-standard,

and,

the

same

operational

headstack,

on

the

PCB. A

assembly.

drives

balances

as

well

as

data

Programmers

scheme

across

with

the

printed

adjustments.

single

enable

the

to

and

buffer

Manual

minimizes

cylinder

Small

exception

circuit

flex

circuit,

IC

high

commands

transfer

from

size

for

the

to

details

latency

boundaries.

Computer

board

All

is

mounted

data

are

of

drive.

60

of

a

heads,

data

to

KBytes.

when

on

o

o

Defect

Multiple

to

o RLL

on

management

2

Kbytes.

1,7

the

disks.

scheme

block

transfer

(run-length-Iimited)

minimizes

of

up

to

encoding

seeks

64K-1

to

spare

blocks,

increases

each

data

sectors.

with

density

up

1-1

Page 9

SCSI

commands

management,

Programmable

initially

defective

to

reformat,

correcting

be

handled

of

17

bits,

relieve

error

options

and

throughout

sectors

(2)

code

in

the

or

correction,

can

data

(ECC) ,

host

detect

the

host

allow

the

be

automatically

can

be

or

computer.

three

users

product's

corrected

(3)

burst

system

and

flexible

all

of

physical

life.

reassigned

with

error

The

ECC

errors

many

tasks,

sector

ways

For

a

Reed-Solomon

detection

can

correct

of

17

addressing.

to

handle

example,

without

and

bits

such

correction

one

each.

as

defect

defects

(1)

the

error

burst

need

can

error

Q200

Series

factory-written

thermal

headstack

which

bit

sizes

1.2

Signals

level,

document,

"-ACK,"

when

other

Signal

Asserted

Asserted

use

and

of

they

signals,

and

assembly

a

track

512,

Logic

on

and

the

and

are

Type

when

when

tm

drives

in

mechanical

dedicated

densities

1024,

Conventions

the

SCSI

false

or

names

the

timing

low,

as

low

high

employ

wedges

effects

are

minimized,

servo

ensure

and

2048

bus

are

non-asserted

of

such

diagrams

as

they

on

the

a

hard-sectored

between

which

surface.

high

bytes

all

signals

might

PCB,

are

Examples

-paR

+POR

all

in

data

are

true

when

are

are

drawn

be

observed

indicated

format

sectors

tend

to

comparison

In

addition,

integrity.

supported.

or

asserted

they

are

always

to

as

on

all

misalign

with

when

at

high

preceded

show

with

the

an

follows:

with

servo

surfaces.

heads

other

drives

conservative

Logical

they

are

level.

by a minus,

signals

oscilloscope.

data

on

the

block

asserted

Thus,

linear

at

In

low

this

as

Differential

Analog

Note

example,

the

"+ACK"

that

signals

on

the

ANSI

"-ACK"

as

timing

Standard

when

"ACK"

diagrams.

listing

in

Asserted

positive

WRITE

for

the

text,

when

than

CURRENT,

SCSI,

connector

and

1-2

+READ

-READ

5 V

ANSI

pin

shows

SIG

is

SIG

X3.131-1986

connections,

positive

more

uses,

true

but

signals

for

describes

Page 10

SECTION

2.

PRINCIPLES

OF

OPERATION

2.1

2.1.1

The

single

surface

brackets.

yo

'\~'ST

~:K

ASSEMBLY

for

Head

Base

piece,

the

See

r-

/

Disk

Assembly

Casting

aluminum

rest

Figure

HEADS

ACTUATOR

UPPER

AND

LOWER

MAGNETS

Assembly

of

the

2-1

alloy

drive

for

(HDA)

base

relative

casting

mechanism,

locations.

! I!

/t:tD

/'

'

/'

!

provides

PCB,

and

DISK

shock

CLAMP

MAGNETIC

a

mounting

DISK

RECIRCULATION

FIL

TER

BASE

mount

~

",

,

CASTING

/~/

FACEPLATE

Figure

2-1:

Exploded

View

MOUNTING

HOLES

~

/'

PRINTED CIRCUIT

BOARD

MOUNTING

BRACKET

2-1

Page 11

2.1.2

Disk

Stack

Assembly

Three

hub

the

prevents

head

area,

2.1.3

The

permanent

the

aluminum

and

clamped

surfaces

head

surface.

and

when

Rotary

positioner

magnet

headstack

alternating

bolted

magnet

spindle

2.1.4

The

flex

to

the

plates.

or

Headstack

headstack

circuit,

positioner

entire

stack

mini-composite

steel

circuit,

flexures.

which

alloy

in

of

the

and

This

the

positioner

is

plates,

mounting

poles

base

These

off

of

assembly

and

assembly

is

at

slider-type

The

contains

disks

place.

disks,

media

only

disks

a

proprietary

hub

bonded

casting.

prevent

the

disk

Assembly

consists

rotary

balance

the

center

heads

(two

A

thin

and

wear

when

occurs

are

not

Assembly

and

a

shaft.

to

the

Resilient

surface.

positioner

each

heads,

and

a

read

for

the

Q250)

film

magnetic

lubricated

the

heads

in

the

landing

rotating

(Actuator)

design

rotary

magnet

The

consisting

single

magnets

plates

crash

the

of

heads

the

from

read/write

assembly.

of

other

the

so

mounting

mounted

actuator

are

preamplifier/write

are

metal

with

are

a

in

zone

at

full

phase

are

which,

stops

being

The

that

the

hub.

to

Whitney-style

connected

placed

carbon

contact

outside

speed.

of

upper

coil

composed

in

are

driven

heads,

head

mass

The

driver

on

is

sputtered

overcoat

molded

turn,

mounted

into

spacers,

arms

center

heads

by

the

chip.

the

with

the

and

of

are

and

are

spring

flex

motor

that

the

data

lower

to

two

to

the

the

rotary

of

the

on

2.1.5

AIRLOCK

zone,

The

is

and

dedicated

prevents

motor,

motor

it

starts

in

an

and

place.

spinning,

rotates,

2.1.6

To

DC

achieve

interference,

closed-loop

motor

3662

is

rpm.

Automatic

a

mechanical

is

covered

landing

damage

during

electronic

pulls

the

As

releasing

Drive

Motor

accurate

the

digital

dynamically

A

12 V motor

Actuator

by

zone

shipment.

return

headstack

dc

power

airflow

the

headstack.

speed

Q250/Q280

servo

balanced,

Lock

means

u.s.

Patents

for

spring

is

applied

increases,

control

uses

system,

control

(AIRLOCK)

of

locking

the

heads

When

extracts

into

the

with

a

brushless

synchronized

four

IC

commutates

and

dc

landing

to

and

minimum

pole,

the

pending

ensures

power

energy

the

motor

the

airvane

three

heads

tack

patent

data

is

removed

from

zone.

and

on

electromagnetic

dc

spindle

by

a 2

phase,

the

motor

in

the

applications.

integrity

from

the

spinning

AIRLOCK

the

disk

AIRLOCK

motor

MHz

clock.

and

rotates

coils

landing

and

the

latches

stack

in

a

The

in

at

2-2

Page 12

accordance

degrees

start

up

with

around

and

signals

the

produces

motor.

dynamic

from

three

The

IC

also

braking

Hall-effect

limits

to

stop

devices

the

the

motor

motor

mounted

current

quickly.

at

120

on

contaminants

heavy

aluminum

ferro-fluid

through

are

final

the

processed

assembly

tromagnetic

reduced

by

teflon.

2.1.7

The

of

Air

Q250

11

microinches

. 3

FILTER

are

magnetic

bearing

and

Interference)

grounding

Filtration

and

Q280

MICRON

CIRCULATION

kept

housing,

core

coated

is

in

are

.

out

of

bolted

seals

prevent

or

to

a

Class

and

the

rotating

Winchester

the

drive

to

the

along

the

eliminate

100

clean

electrostatic

shaft

drives

by

base

outside

bearing

dust,

room

mounting

casting.

air

chips,

environment.

discharge

with

with

from

shaft.

a

brush

a

nominal

the

motor

Two

entering

Motor

and

oxides,

(ESD)

of

flying

inside

conductive

the

components

and

EMI

(Elec-

are

conductive

height

a

drive

Figure

2-2:

Inside

View

of

Drive,

2-3

Showing

Air

Filtration

Page 13

To

keep

drives

sealed

disks

tion

filter,

shown,

equalize

the

are

with

pump

allows

internal

air

circulating

assembled

a

metal

the

enclosed

as

shown

outside

and

in

cover.

in

air

external

a

Class

air

Figure

into

within

100

During

through

2-2.

the

pressures.

the

clean

the

an

Another

sealed

drive

room

life

internal

area

free

environment,

of

the

0.3

0.3

micron

of

of

particles,

drive,

micron

the

drive

and

the

recircula-

filter,

to

the

then

rotating

not

2.2

2.2.1

Q200

seven

lists,

tains

area

data,

in

DICEY.

within

the

on

the

that

with

zation

ber,

and

At

3662

area,

passes

data

Series

tracks

serial

thirty-two

consists

and

the

data

tracks--written

disk.

identifies

the

data

area.

the

head

D),

a

rpm,

passes

under

transfer

Drive

Disk

Electronics

Format

drives

are

number

of

12

bytes

servo

In

the

areas,

In

number

checksum

a

complete

under

the

rate

employ

reserved

ID

sectors

a

preamble

of

ECC. A

wedges

a

wedge,

area

each

the

bursts,

(bursts

that

its

head

of

in

about

823

for

and

and

are

in

a

as

burst

allows

sector,

head

about

user

disk

factory

tracks

drive

test

thirty-two

and

synchronization

short

the

staggered

servo

a

wedge,

servo

track

postamble

tracks--three

sequence

and

begins

this

A

and

error

is

followed

C)

detection,

or

including

in

512

microseconds.

410

microseconds,

10 M bits/sec,

system

data.

servo

starts

ends

with

the

(refer

a

sector

wedge

i.e.,

to

uses

Each

wedges.

area,

flushes

so

they

with

with

a

preamble

by

the

and

and

The

giving

1.25

Figure

--

such

data

track

Each

512

bytes

the

ECC

times

as

don't

a

unique

servo

and

servo

number

a

short

512-byte

data

a

maximum

MBytes/sec.

2-3),

as

while

defect

con-

user

data

of

buffers

many

overlap

qual

burst.

synchronitrack

num-

(bursts

postamble.

data

itself

as

area

As

B

user

2.2.2

This

to

simplified

section

the

Simplified

summarizes

more

detailed

block

Explanation--Block

sections

diagram

the

of

operation

that

the

system.

2-4

Diagram

of

follow.

the

drive,

Refer

to

as

an

Figure

introduction

2-4,

a

Page 14

SERVO

TRACKS

I /

-~~~-j

/

+

STo~A~

/

10i

----T----- -

TO

CENTER

OF

DISK

1

SERVO & DATA

TRACK

LAYOUT

TRACKS

QUAL.

AREA

50us

PRE

AMBLE

rr---w...---I--<- /

'-

'-

'-

'-

'-

S

Y

N

C

PRE

AMB

~

I e

'-

'-

'-

'-

TRACK

NO.

/

105

/

/

/

/

104

/

/

/

/

LE

'-

\

103

102

101

S

Y

N

C

'-

'-

'-

'-

'-

P

0

S

T

'-

~

512

452us

DETAIL

OF A BURST

CHECKSUM

HEAD

NO.

{

SECTOR

c=J

P

A&C)

B&D)

E

0

C

S

C

T

DATA

BYTES

(BURSTS

NO.

(BURSTS

[

[

LOGICAL~

TRACK

NO.5

DETAIL

OF

ONE

SECTOR

12

BYTES

Figure

2-3:

Disk

Format:

Wedges,

2-5

Sectors,

and

Tracks

Page 15

Power-On

Voltages

low,

as

on-reset

until

At

the

the

initial

inner,

amplitude

calculates

optimize

may

be

when

the

(PaR)

circuit

voltages

power-on,

outer,

measurements

and

stores

seek

-------,

-------,

and

I

I

I

I

applied

power

are

the

and

settle

in

any

has

failed

resets

high

drive

middle

are

made

adaptive

times.

sequence.

the

enough

is

tracks;

and

gain

ELECTRONIC

RETURN

SPRING

When

or

has

just

major

and

circuits

stable.

recalibrated:

at

each

from

these

parameters

2MHz

UB

the

been

location,

the

that

RESET

uP

OTHER

CIRCUIT

dc

voltages

applied,

and

keeps

the

actuator

servo-burst

microprocessor

are

later

the

them

seeks

+12V

+5V

are

power-

reset

used

to

to

R/W

HEADS

______

HEAD

DISK

ASM

(HDA)

PRE-AMP

WRITE

DRIVER

...J

Figure

2-4:

Electronics

2-6

Block

ALE.

-WR.

-RD

*64KB

WITH

DISCACHE

Diagram

50BO

12MHz

SCSI

BUS

TO

HOST

Page 16

Architecture

A

standard

Series

for

ferent

without

drive.

drives

EPROMS

DisCache.

8-bit

with

microprocessor

An

8031

it.

are

Firmware

used

Special

is

for

used

the

EPROMs

operated

for

is

in

Q250

drives

a

and

may

at

without

plug-in

Q280,

be

used

12

MHz

32

and

for

controls

DisCache,

K X 8

for

drives

custom

each

an

EPROM.

with

applications.

Q200

8032

Dif-

and

communication

MAD

controller

dynamic

of

serial

generates

SCSI

(multiplexed

RAM

is

the

IC,

RAM

(4

KBytes

DMA

controller,

conversions,

the

Bus

Operations

Communications

bus.

can

reconnect

Before

The

play

the

the

interface

and

disk

accumulated

read

the

option),

bus.

error

from,

data

Users

is

data

is

transferred

detected,

Servo

between

address/data)

manages

(64

KBytes

with

ECC

with

role

arbitration

is

in

buffer

is

checked

can

select

the

access

for

DisCache)

performs

handles

syndrome.

the

host

is

implemented

of

initiator

written

RAM

also

stored

with

through

the

via

the

major

bus.

to

drives

all

and

or

functions.

to,

a

(via

DMA

in

the

error-correcting

the

action

MODE

circuit

the

with

is

reserved

serial

RLL

encoding

other

with

target,

full

transfers).

RAM.

5080

to

SELECT

components

DICEY, a

buffer,

DisCache).

to

parallel

SCSI

a

5080

and

sector

After

via

DMA,

be

taken

command.

proprietary

which

for

Q250/Q280

and

decoding,

devices

SCSI

performs

of

incoming

As

a

full

code

then

in

the

is

over

is

16

The

upper

and

parallel

is

over

Controller

disconnect/

the

disk

sector

(at

the

on

to

event

the

data-

KBytes

2

use.

and

the

SCSI

is

is

user's

the

that

8-bit

of

KBytes

DICEY

to

SCSI

IC

data

being

read,

SCSI

an

that

is

While

tion

position

microprocessor

tion

output

New

bursts,

decelerates,

seek

As

the

the

processor

tude,

track-following,

are

stored

at

DAC

track

(digital-to-analog

is

converted

and

forming

in

the

servo

AMC

servo

bursts

(amplitude

ADC

reads

if

possible.

in

buffer

all

times.

immediately

sector

a

closed

the

actuator

shortest

pass

measurement

(analog-to-digital

head

track

When a

to

a

numbers

time.

under

position

Once

and

RAM--the

starts

converter)

high

current,

are

loop.

via

the

the

from

the

head

sector

microprocessor

READ

a

or

seek

read

The

microprocessor

head

head,

their

circuit),

converter).

the

is

on

2-7

numbers

WRITE

by

via

which

on

the

position

and

burst

track,

of

knows

command

commanding

the

MAD

drives

fly

from

DAC

amplitudes

placed

When

with

the

the

the

current

the

exact

arrives,

the

head

bus.

the

The

actuator.

the

DAC

servo

accelerates,

to

achieve

are

measured

on

the

MAD

seeking,

the

highest

microprocessor

posi-

the

posi-

then

the

bus

micro-

ampli-

head

by

by

Page 17

keeps

position

each

bursts

side

the

A

head

so

of

and

following

that

the

D

on

the

data

logical

the

amplitudes

track

are

track

track

exactly,

of

the

equal.

a

are

two

For

kept

by

adjusting

servo

example,

equal.

bursts

in

the

written

Figure

head

on

2-3,

There

Each

amplified

(automatic-gain-control)

differentiated

a

data

drop-outs

for

write

The

(under

the

2.2.3

A

necting

standard

Universal

the

AMP

(without

should

backwards.

is

one

head

pulse

and

every

preamplifier/write

head,

50-pin

mating

receptacle

can

first

detector.

clock

rare.

magnetic

command

which

SCSI

connector

to

the

SCSI

Header

connector

strain

not

be

head

either

by

to

signals

of

writes

Bus

standard

single-ended

PIN

relief),

used

for

each

read

the

preamplifier

find

RLL

the

connector

the

A

phase-locked

for

1,7

transition

driver

microprocessor)

magnetic

Physical

is

provided

improperly.

1-499508-2

due

to

surface:

or

write.

amplifier.

zero

DICEY.

encoding

Interface

SCSI

bus.

non-shielded

and

or

equivalent.

the

crossings,

loop

allows

on

the

chip

transitions

at

position

See

has

a

The

(with

danger

four

chip

Careful

inside

strain

on

When

in

That

circuit

1.33

disk.

and

Figures

connector

key

slot

recommended

Unkeyed

of

plugging

the

reading,

the

output

and

converted

derives

design

data

the

HDA

sends

on

the

J1

on

2-5

to

relief)

Q250,

the

HDA,

is

filtered,

makes

bits

selects

current

disk.

the

and

is

prevent

mating

or

mating

the

six

on

output

then

PCB

used.

connector

by

to

synchronized

drop-ins

to

be

the

reversals

for

2-9.

installing

connector

PIN

1-746195-2

connectors

the

is

an

then

pulses

stored

head

conThe

J1

is

in

Q280.

AGC

by

or

to

a

is

A

50-conductor

with

of

together

reflections,

same

satisfactory

connected

is

a

100

bus.

20

minimum

ohms

using

to

feet

flat

conductor

+/-

10%

a common

cables

Table

(6

2-1

transmission

ground;

meters),

cable

is

recommended.

of

different

gives

pin

a

or

size

cable.

J1

quality,

25

length

a

25-signal

of

pin

is

left

28

AWG

SCSI

To

minimize

impedances

assignments.

all

open.

suitable

2-8

twisted-pair

and

a

devices

discontinuities

should

odd

pins

Maximum

for

use

ribbon

characteristic

are

daisy-chained

not

Note

except

in

that

total

a

cabinet.

be

pin

and

used

to

25

cable

cable

impedance

signal

in

the

achieve

are

length

Page 18

CENTER

KEY

SLOT

Ground

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

DDDDDDDDDDDDDDDCCCCCCCCCC

DOCOCDOCCCCCCDCCCCCCCCCCC

CONNECTOR

Figure

Table

Signal

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

Name

-Data

-Data

-Data

-Data

-Data

-Data

-Data

-Data

-Data

Ground

Ground

Ground

Open

Terminator

Ground

Ground

-ATN

Ground

-BSY

-ACK

-RST

-MSG

-SEL

-C/D

-REQ

-I/O

PCB

2-1:

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

POSITION

2-5:

0

1

2

3

4

5

6

7

P

Jl

Pin

Jl

(-DBO)

(-DBl)

(-DB2)

(-DB3)

(-DB4)

(-DB5)

(-DB6)

(-DB7)

(-DBP)

Power

#1

Connector

Assignments

(TERMPWR)

INDICATOR

2-9

Page 19

2.2.4

All

signals

2-6

for

physical

provided

the

terminators

SCSI

are

a

typical

end

as

terminators.

Bus

of

Signal

true

circuit).

the

bus.

plugged

low

Descriptions

and

use

A

Three

Drives

in.

See

open

collector

termination

resistor

are

shipped

Figure

CAUTION

is

networks

2-9

for

drivers

required

from

locations

in

the

(see

at

sockets

factory

each

on

Figure

are

with

the

PCB.

5'1

Only

are

all

packages).

the

current

to

Plug-in

plugged

with

the

about

r---------

the

allowed

other

bus

carry.

a

PCB.

the

__

two

to

devices

If

drivers

from

terminator

in

correctly.

dark

band,

All

correct

~~----

devices

have

the

may

the

at

the

terminators:

on

the

bus

additional

be

damaged

+5 V supply

physical

(unplug

terminators

because

than

CAUTION

packages

On

and

must

terminators

orientation,

TERMPWR

__

~--------------~--~------~--------~

each

face

face

(PIN26)

are

package,

the

consult

ends

remove

all

the

48

polarized,

the

"1"

same

5V

of

the

terminators

three

are

they

rnA

will

they

and

pin

1

that

is

way.

Figure

SCSI

terminator

not

removed,

sink

are

must

is

be

marked

screened

If

in

doubt

2-9.

bus

from

more

rated

on

5V

~----~----~--------~---------------+--~------4---~------1

~----~----~--~----~---------------r----------T---~----~

DEVICE

WITH

TERMINATOR

Figure

"----------..

2-6:

SCSI

DEVICES

Bus.

-SIGNAL

GROUND

-------)

V

WITHOUT

Typical

2-10

TERMINATORS

Circuit

of

a

Signal

DEVICE

WITH

TERMINATOR

Line

Page 20

Each

Q250/Q280

bus

driver

has

the

following

output

characteristics:

Each

True

False

signal

(Signal

(Signal

received

characteristics:

True

Maximum

False

Minimum

SCSI

Up

tion

to

Bus

eight

is

Information

low a defined

byte

a

that

of

total

comprise

described

(Signal

total

(Signal

input

Signals

devices

allowed

transfers

-REQ/-ACK

information

of

18

logic

an

briefly

-BSY (BUSY). An

used.

Asserted)

Non-Asserted)

by

Asserted)

input

Non-Asserted)

hysteresis

can

between

on

can

signals:

8-bit

DATA

below.

"oR-tied"

=

0.0

to

0.4

=

2.5

to

the

load

be

supported

only

the

Q250

=

0.0

=

-0.4

=

0.2

two

SCSI

or

Q280

to

=

2.0

V

SCSI

DATA

0.8

mA

to

dc.

on

devices

BUS

(request/acknowledge)

be

transferred

nine

BUS

signal

control

with

that

with

parity.

indicates

V

5.25

must

V

at

5.25

the

signals

dc

at

have

dc.

0.4

SCSI

at

are

handshake

each

Each

48

mAo

V

dc.

the

following

V

dc.

V

dc.

bus,

any

but

given

asynchronous

handshake.

and

nine

of

the

that

the

communica-

time.

and

protocol.

There

signals

signals

bus

is

input

fol-

One

are

is

being

-SEL

a

-C/D

whether

indicates

-I/O

direction

tiator.

also

-MSG

(SELECT).

target

to

reselect

(CONTROL/DATA). A

CONTROL

CONTROL.

(INPUT/OUTPUT).

of

data

Assertion

used

to

distinguish

(MESSAGE). A

A

or

-REQ (REQUEST). A

a

-REQ/-ACK

-ACK

(ACKNOWLEDGE).

acknowledgement

data

transfer

for

signal

an

initiator.

signal

DATA

information

A

signal

movement

indicates

signal

signal

A

signal

a

-REQ/-ACK

used

by

driven

driven

on

the

input

between

driven

driven

handshake.

driven

an

initiator

by a target

is

on

by a target

DATA

to

BUS

the

SELECTION

by a target

by a target

by

data

transfer

the

with

initiator.

and

an

initiator

to

select

that

DATA

BUS.

that

respect

RESELECTION

during

to

the

indicate

to

handshake.

a

target

indicates

Assertion

controls

to

This

MESSAGE

a

indicate

an

inisignal

phases.

request

or

by

the

is

phase.

for

an

2-11

Page 21

-ATN (ATTENTION). A

ATTENTION

condition.

signal

driven

by

an

initiator

to

indicate

the

-RST

(RESET).

-DB(7-0,P)

signal,

has

the

that

highest

significance,

defined

the

Data

(i.e.,

as

signal

parity

a

generate

have

valid

parity

during

TERMPWR.

terminations

event

of

2.2.5

Delay-time

signal

Thus,

without

conditions

the

considering

An

(DATA

form

priority

and

one

when

is

non-asserted.

-DB(P)

system

parity

is

and

detection

the

4.0

V

dc

in

other

5 V

failure.

SCSI

Bus

measurements

following

"oR-tied"

BUS).

a

DATA

Eight

BUS.

during

priority

the

is

odd.

decrease

signal

configured

have

parity

disabled

ARBITRATION

to

5.25

SCSI

V

devices,

Timing

for

existing

at

delays

delays

signal

data-bit

-DB(7)

is

The

so

or

phase.

dc

each

that

(except

in

the

that

the

arbitration

downward

asserted

use

of

that

detection

not

provided

to

SCSI

device's

cable

cable.

indicates

signals,

is

the

most

to

and

is

parity

all

SCSI

is

devices

enabled,

implemented).

by

each

keep

device

the

are

own

skew

delay)

the

plus

a

significant

phase.

-DB(O).

defined

a

system

or

Parity

device

line

terminated

calculated

SCSI

bus

can

RESET

parity-bit

Bit

A

data

as

option

on a bus

all

SCSI

for

connector.

be

condition.

bit

and

number,

bit

zero

when

devices

is

not

the

bus

in

from

measured

is

the

ARBITRATION

must

be

wait

examined

from

time.

BUS

CLEAR

device

(1)

to

DELAY

stop

The

deasserted

(2)

-SEL

ARBITRATION

(3)

NOTE:

device

becoming

settle

bus

clear

For

to

delay

The

the

clear

both

delay

DELAY

asserting

to

see

(800

driving

BUS

is

transition

first

the

deasserted.

to

detect

minus

(2.2

microseconds).

if

arbitration

nanoseconds).

all

FREE

phase

for

received

phase.

condition

bus

is

BUS

the

-BSY

bus

a

bus

from

of

-RST

1200

If

FREE

excess

for

arbitration

has

signals

is

detected

settle

another

to

above,

nanoseconds

an

SCSI

phase,

time.

The

been

The

maximum

after:

(-BSY

delay

SCSI

asserted.

the

maximum

device

it

mlnlmum

until

won.

and

period).

device

from

requires

must

clear

There

time

time

-BSY

time

the

for

-SEL

during

for

and

more

the

an

DATA

is

an

both

bus

SCSI

BUS

no

maximum

SCSI

the

an

SCSI

-SEL

than

within

device

can

first

a

bus

a

2-12

Page 22

IBusy)

-BSY

(Select)

-SEL

(Control/Data)

-C/D

(Input/Output)

I/O

IReQuest)

-REG

HANDSHAKE

IAcknowledge)

-ACK

Note:

(At

tent

i onl

-ATN

-AST

and

-ATN

are

IMessagel

-MSG

shown

de-asserted

Ihigh)

IResetl

-RST

(Data

bitl

DB

(7-0.

PI

Note'

BUS

SET

DELAY

Maxl_

tiM

for

an

SCSI

device

to

Issert

BSY

and

ita

SCSI

10

bit

on

the

detl

bita

Ifter

't

detecta

Bua

Free

Phase

BUS

fREE

DELAY

Mini.,.

tlae

that

an

SCSI

device

ahall

weit

fro.

Its

detection

of

Bus

Free

Phase

until

Its

assertion

of

BSY.

BUS

ClEAR

DELAY

Maxi.,.

tlae

for

an

SCSI

d.vlce

to

atop

driving

all

bus

signals

after

Bus

Free

Phase

Is

detectea

or

SEL

recl.ved

fro.

an SCSI

a.vice

during

arbitration.

S

SETTLE

...

0_EL_A_Y_,-J../2

deskew

delays

___

~---

Target

asserts

BSY

II

'----Bus

Settle

Deley

I I

-BSY

I

I~----~---+-r--------------------~----------~----------~~---------+----~--------~------~~--------

+-~

I

r--systells

with

1_1_.

no

arbitratiorn~~+-

______________________ ~ ________

-T

_____________

~~~r-

________ ~ ____

~~--------+-------~----------~~~----~--------SEL

I"

sUrt

here

(

I I

J--t--------r-------

-C/O

r--+----~-------

-

1/0

r+---t--------f--.,.---

-REG

)---t-----~-------

-ACK

ATN

,-4-------;-------MSG

---+-----+------------;-;-+-----r-----~--_;_+----------------------r_--------~----------~~~~~~~~~~~------~~~----~--------~--r_----~-------RST

--~,------V-~~~--~--~V71n~1~t.~.t~o~r7.1D~,7T.~rO=.~t7.1D~---r----'r.-

~,r_----

__

~~;_--;_----------~~~~~~~~~~~~~~--~~~~.r_--~,------~~r-~~r-~--~----

-4r------DB(7-0.PI

/)

I I I

First

\ \ I :

/ I

Initiator

tries I II

Initiator

has

!Jus:

1st

LAST

:

data

first

data

Status

byte'

Message \ :

Bus

is

\

/

BUS

FREE I to

get

ous I

nd I ts

T g t

read

I . t . h

I)

\

byte)1 I released

\,

/

PHASE

I I I a

se

ec

ar

e I

COMMAND COMMAND

I I

WCl

e

perlp

era

Target

)

DB

(7) -Most

SIgnIfIcant

bit

//

/ : I I

BYTE BYTE

I

peripheral I Target

'requests'

data

'requests' I ITarget

'reQuests,1

I ,

-HIghest

prIorIty

lD

for

arOltratlon//

I I

Target

'reqUests'

I I

transfer

w,th

,nitlato

r

initiator

to

I I

initiator

to

takel II

\

(,

/ I I I I

take

status

I I

~essage

I I )

Note:

DB

(P)

- Data

parity

loddl

Par1ty

Is

not

valid

du~ing

arbitration.

//

I I

command

from I I I I I I I

SEL

and r : I :

init,

atDr

.:

:

I:

: I I

BSY

are

~

----j

r

STATUS

PHASE

~

MESSAGE r-BUS

----...J

both

false ~ ARBITRATION

~

c==

SELECTION

=-==:J.

r-.

CO~MAND

PHASE

---,----1 I

CATA

PHASE

I

r:=

--<!==

PHASE

~

r--

FREE

---I

for

at

least

J---

PHASE

PHASE

----'

I I

I--

(Ending

Statu.)

==1

t--

---;

t--

-.---J

one

Bus

~

---j

\ \ I I I I

t--

--j

r--

PHASE

I

Settle r-Implementation

of I

During

this

phase

the \ .--

The

Target

asserts

I I

DATA

IN

PHASE:

Read

PerIpheral.

I

f--

Target

I

~Target

I

f--Target

,

Delay I

this

phasee

is

a I 110

signal

is

\ I

CIO

and

deasserts

110 I I I

requests

that

a I I

requests

I I

deasserts

BSY

"

I

system

option

I

deasserted

'to

\ I and

MSG

for

all

of

the

f--

Data

is

to

be

sent

from

Target

to

I I

status

byte

be I I ..

essage

I I

to

indicate

t~at\

I I

distinguish

this

Phase

) I

handshakes

of

this

phase

I

Initiator

I

sent

to

the

I I

byte

isl

to

be I I

the

bus

Is

I

,---

At

least

one Bus I

~~~:e

the

Reselection

: I I : I

Initiator

I I

sent

from I I

available

for

I

I

~~~:

~~~~y

on~u~u~O

:

NON-ARBITRATING

I ~ The

transfer

is

from

f--

Target

asserts

110.

deasserts

C/O and I :

Target

asserts

II

:

i~~~~;t~~,

::

~~~~:quent

II

:

Set

Delay

aftee

Bus I SYSTEMS:

In

systems

I I

init,ator

to

Target

I

MSG

during

the

REG/ACK

handshake of I I

C/O

and I/O I I I I

I

~~:~

~:~:~t:~s

The I with

the

Arbitration

I I I

th.s

phase.

I r

=~~

~~~~~:rts

I

t-Terget

asserts

I r

Initiator

releasef

I

Initiator

asserts

BSY

I

~:~:m~~~ed

atler

:

L,

pH~~OCSEDHUA~~..

l--

HANDSHAKE

PROCEDURE

: I

th

h d h k :

~~g'

~~~in~nd

: I

all

bus

S~gnals

I

:

~~~i~;sI~w~liC~~

the:

detecting

the

Bus

free

1

M

.'

MC

I

I:

Of\h~~

~h:S:.

I

the

REG/ACK

I I

~~;~~no!la~s

I

I

data

bus I

Phase

the

Initiator

I

~

~~~T~~;ein~~~:~~~

L

The

Target

first

drives

data

17-0P)

I I I

haneshake

(5) I I

~~~~~e~SY

:

L-

The

Initiator

waits

I

~~!t~u:

~~~!~U~e~:y.

I

drives

data

(7-0.P)

to

:

~~a!~e~~ed~:!~:~

~::~:sp7~!t:

~~ble

: I Only one

byte I of

this

phase. I continuously

I

I

an

Arbitration

Delay I Then

it

asserts

the

data

;~~~~

~~s;~:~tv~~~es.

I skew

delay

then

asserts

REO

Data I I of

status

is

~The

message I

false

for a BUS

I

I

then

examines

the

I

~~~i~~~\~~;~a~~~

10

bit

deskew

delay

plus

a I

t7-0.PIshall

remain

valid

until

ACK

I I

transferred.

I

byte

could I Settle

Delay I

I

data

bus.

If • higher I th T t'

10

b' t cable

skew

delay

and I

is

t~ue

at

the

Target,

I I I

indicate

I I

I

priority

SCSI

device

I

:~~er

~wo

a~~:ke!

,.

asserts

ACK.

The l I

ISh

d h k£ I

COMMAND I Th f 11

I

:

~~t~l~u!s(~~~ei~\~:e:

delays

the

InitIator

~~:~;a~~~a

c(~~~~~~e~n~~1

_

The

Initiator

shall

read

data

(7-0.pl

:-

p~~ce~~r:

a I

COHPLETE

1001.

:-

Ph:seo~i~7i~;

:

I

highestl

the

initiator I asserts

SEl.

I

after

REG

Is

true

then

.sserts

ACK

I under Data in I I an

A~bltration

r

lOesleesaSaersbsitsrya.

tliOtnnaond

I

REO

is

false.

I I phase I Phase

If

I

I

ARBlTRATI0N

SYSTEMS:

L

~hen

ACK

becomes

true

at

the

Target

I L See handshake :

imile~ented,

or

:

higher

priority

SCSI

I

!~a~~s;:~~e:~~~e~rbitration

When

ACK

is

true

at

:

the

Target

",ay chaoge

cr

release

datal

I

procedure

Se

ec

Ion ,

dev~~e

~Dtbi~

is

true

the

initiator

that

won

the

Target

the

Target

I

i7-0.PI

and

deassert

R~:;

I under Data

in

Phase

~~en

~he

\~lt

~~tor

arbitration

has

both

~~:~s

d;::S~~~:

~~~o.

PI

I

phase

w,ns

arbitration

and

BSY

and

SEL

asserted

I---

After

REG

Is

falSE

t~E

I"itiator

I

asserts

SEl. ane

changes

the

data

I

deasserts

ACK.

After

A:';

is

false

bus

after

two

Bus

Woen

REQ

becomes I

Target

atay

conLnue

thE

transfer

by

r---

Bus

deYlees haVing

I

lost

arbitratIon

shall

I

re

lease

SSy

ana

I

the,"

own

SCSI

I

device

10

bit

.,thln

I

:f~~~

;:;t~:c~~!:Y

I

true

I

r---

The

Init,.tor that

I

wins

arbltratlon

I

waits

at

l'eas'::. l Bus

I

I

I

Clear

Delay

plus

a 8us

Settle

Qelay

after

assertlng

Sel

before

changing

any

s,gnals

on

the

bus.

~~;I~u~e~:y:~e~he

false

at

the

Initiator

I

driving

dot.

(7"O.PI

aod

asserting

asserted

with

both

the

the

Initiator

may

I

REO

initiator

ID

bit

and

the

Change

or

release

data

I

desired

Target·s

lD

b,t.

(7-0,pi

and

deassert

ACK

I

Two

deskew

delays

J--

DAlA

OUl

PHASE

'-lte

Peclpheral.

later

BSY

is

released

I

t-

IN

ALL

SYSTEMS:

THE

I

Target

Oeterm,nes

that

I

it

is

selected

WOen

I

SEL

and

Its

SCSI

:

device

ID

bit

arc

true

I and

BSY

and

I/O

are

I

false

for

at

least

a Bus

I

Settle

[lelay.

The

I TdrOI t

thfn

c:~crts

I

f."\

loltt'lln

a

~c~l_tion

I Abc-l T

,mr.

I

t '

..

:

dl'~k.LW

dflaV5

I

at

tl.. r

the

i.,it

later

I

d('tf(t~

t:::V trw.:

It

I

rE:lcdt"·p

....

~~~

2'ld

rf'ay

cljanQ( de:::-

tJ,.,:.

~

~gnal~

..

2-13

The

Ta"get

cont

inues

req,Je~

t

ing

command

bytes.

lne

nurebe!'"

of

bytes

depends

on

the

corr:-:-and

group

code

I

dct<eted

from

the

first

I

cc"~a"d

byte

rro

,eved.

I!

I

I

I

~-

Data

15

to

be

H"~

I

Target.

I

L

Target

O<'f>S("t, , D.I/O. and

MSG

I

dur

lng

th('

~l~

li

'':'

..

~

tlc"'ldsnake

of

tn1s

I phasE.

~cfcr

tc

ttlC

llandooa,e

t

procedure

of

tl"',(

Ccm:nand

Phase.

Figure

2-7:

SCSI

Bus

Timing

Diagram

Page 23

BUS

FREE

device

-SEL

-BSY

BUS

to

BUS

for

BUS

both

when

SET

assert

FREE

the

SETTLE

settle

protocol

DELAY

must

wait

deasserted

going

DELAY

-BSY

phase

purpose

DELAY

after

definitions.

(800

from

to

ARBITRATION

(1.8

microseconds).

and

(-BSY

of

(400

changing

nanoseconds).

its

detection

for

a

bus

its

SCSI

and

-SEL

entering

nanoseconds).

certain

The

of

settle

delay)

phase.

The

ID

bit

on

the

both

deasserted

ARBITRATION

The

control

signals

minimum

the

BUS

until

maximum

DATA

phase.

time

time

FREE

time

BUS

for

to

as

that

phase

its

for

after

a

bus

wait

called

an

(-BSY

assertion

an

it

settle

for

the

out

SCSI

SCSI

detects

bus

in

and

of

device

delay)

to

the

CABLE

SKEW

pagation

between

DATA

tiator

I/O

DESKEW

of

RESET

RELEASE

to

signal

DELAY

certain

HOLD

asserted.

SELECTION

target

(or

selected

out

is

required

-BSY

is

not

after

the

SELECTION

initiator

(or

RELSELECTION)

DELAY

time

any

allowed

two

DELAY

release

from

(45

signals.

TIME

There

ABORT

initiator)

(or

reselected)

a SELECTION

selection

TIMEOUT

(or

target)

(10

nanoseconds).

between

SCSI

(400

the

devices.

nanoseconds).

DATA

deasserted

nanoseconds).

(25

microseconds).

is

no

maximum

TIME

(200

takes

to

ensure

(or

timeout

DELAY

(250

waits

phase

before

any

two

BUS

signals

to

asserted.

The

time.

microseconds).

from

until

that

its

asserting

a

target

RESELECTION)

period.

milliseconds).

for

a -BSY

starting

The

maximum

SCSI

The

following

minimum

The

minimum

The

most

recent

a -BSY

(or

phase

response

the

difference

bus

signals

maximum

the

time

required

time

maximum

detection

response.

initiator)

has

The

minimum

during

timeout

when

time

transition

for

time

been

procedure.

in

measured

for

an

for

which

that

of

This

does

not

aborted.

time

the

SELECTION

pro-

ini-

of

deskew

-RST

a

being

timeassert

This

that

the

is

an

Figure

signals

2.2.6

Voltage

drive

regulated

her,

external

section

to

2-7

are

is

and

Power

and

listed

power

the

ground

4.3).

an

SCSI

many

of

Requirements

current

in

must

PCB

ground

may

bus

timing

the

above

requirements

Table

be

2-2.

supplied.

plane,

be

connected

diagram

delays.

for

There

the

headstack,

to

2-14

the

is

Supply

a

tab

showing

dc

power

no

regulation

returns

and

on

the

all

of

supplied

are

the

base

base

the

SCSI

to

on

the

connected

casting.

casting

bus

the

drive;

toget-

An

(see

Page 24

No

damage

.or

manner,

time

voltage

and

while

of

to

but

power

or

return

powering

data

data

loss.

occurs

may

This

line,

up

or

if

power

be

lost

includes

transient

down.

is

in

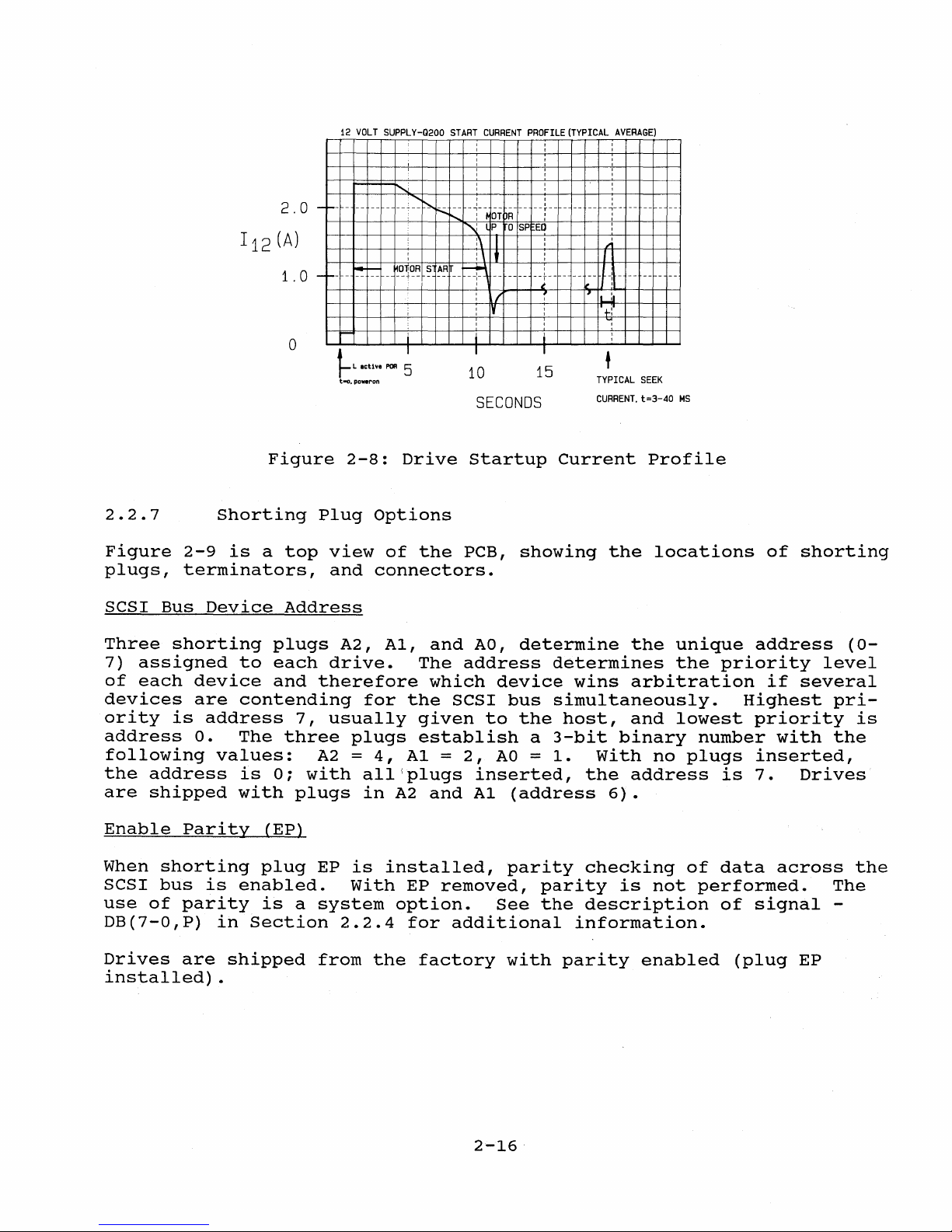

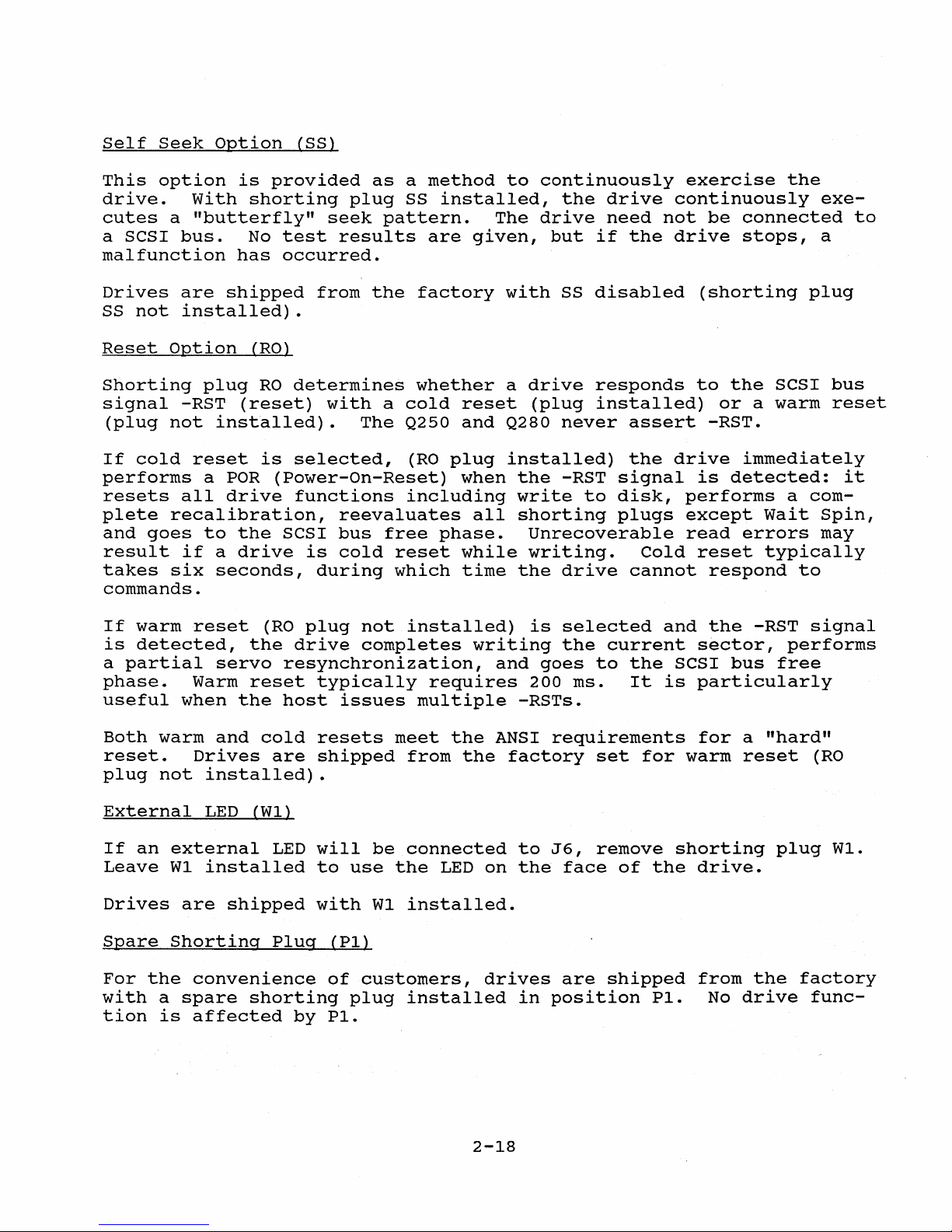

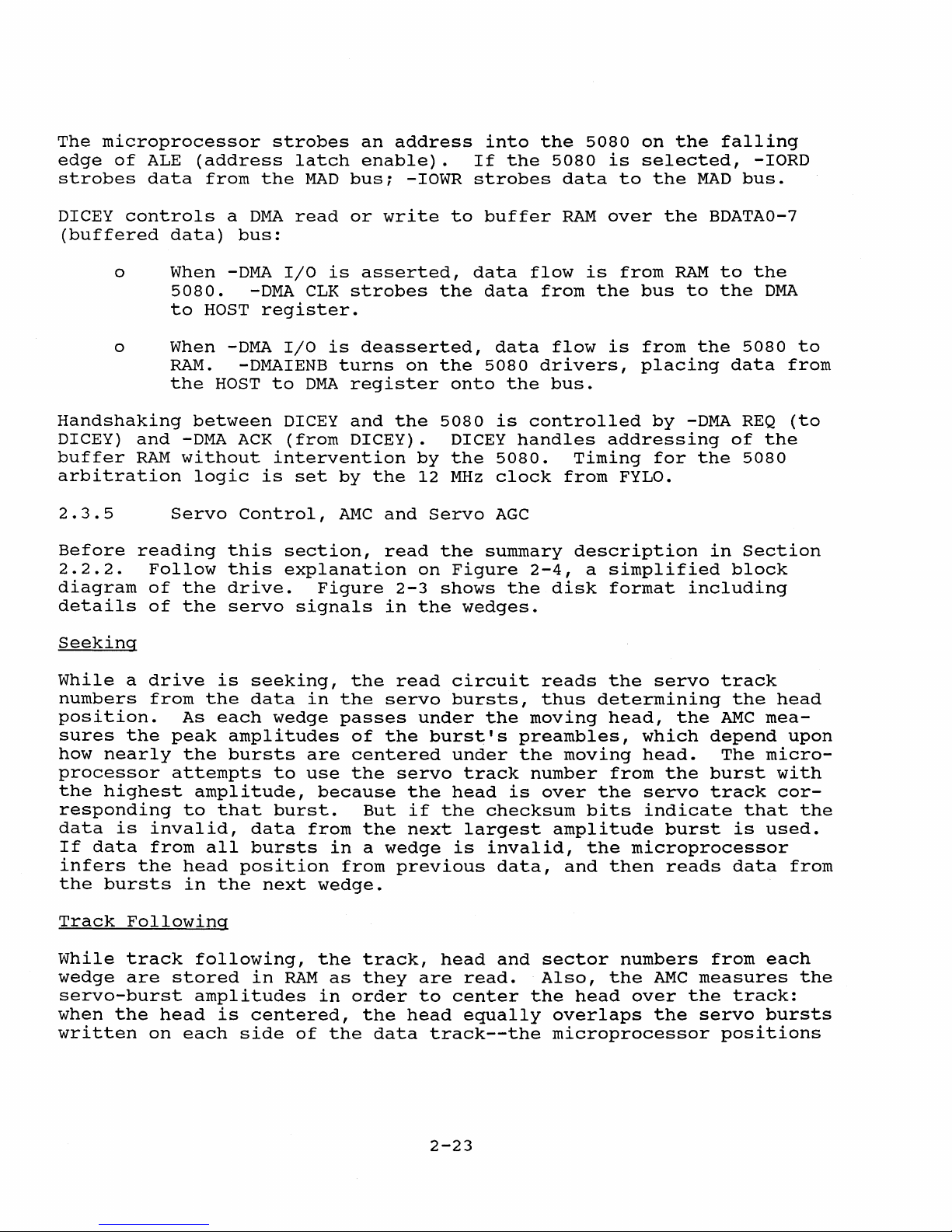

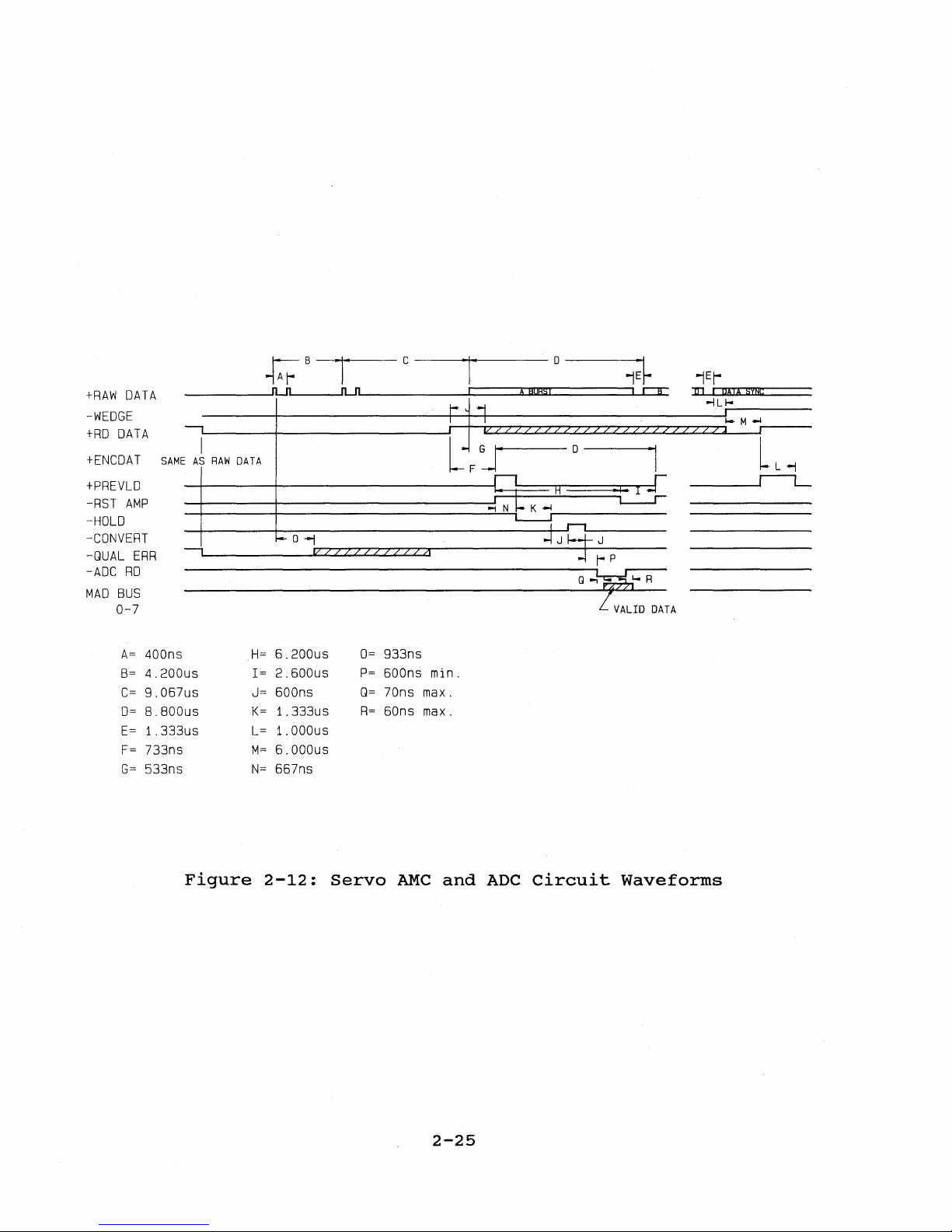

the