A

B

COMPAL CONFIDENTIAL

C

D

E

1 1

MODEL NAME :

COMPAL P/N :

PCB NO :

Revision :

2 2

LA-1931

0.2

DBL10 -- Sapporo X

DA8BL10L000

DBL10 -- Sapporo X Schematics Document

uFCBGA/uFCPGA NorthWood MT

2003-06-09 0.2 Gerber Out Version

3 3

4 4

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, IN C. NEIT HER TH IS SHEE T NOR T HE INF ORMATION IT CONTAIN S

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITTEN CON SENT OF COMPAL ELE CTRONICS , INC.

C

D

Size Document Number Rev

Date: Sheet

Compal Electronics, In c.

LA-1931

Cover Sheet

E

0.2

of

147Monday, June 09, 2003

A

Compal confidential

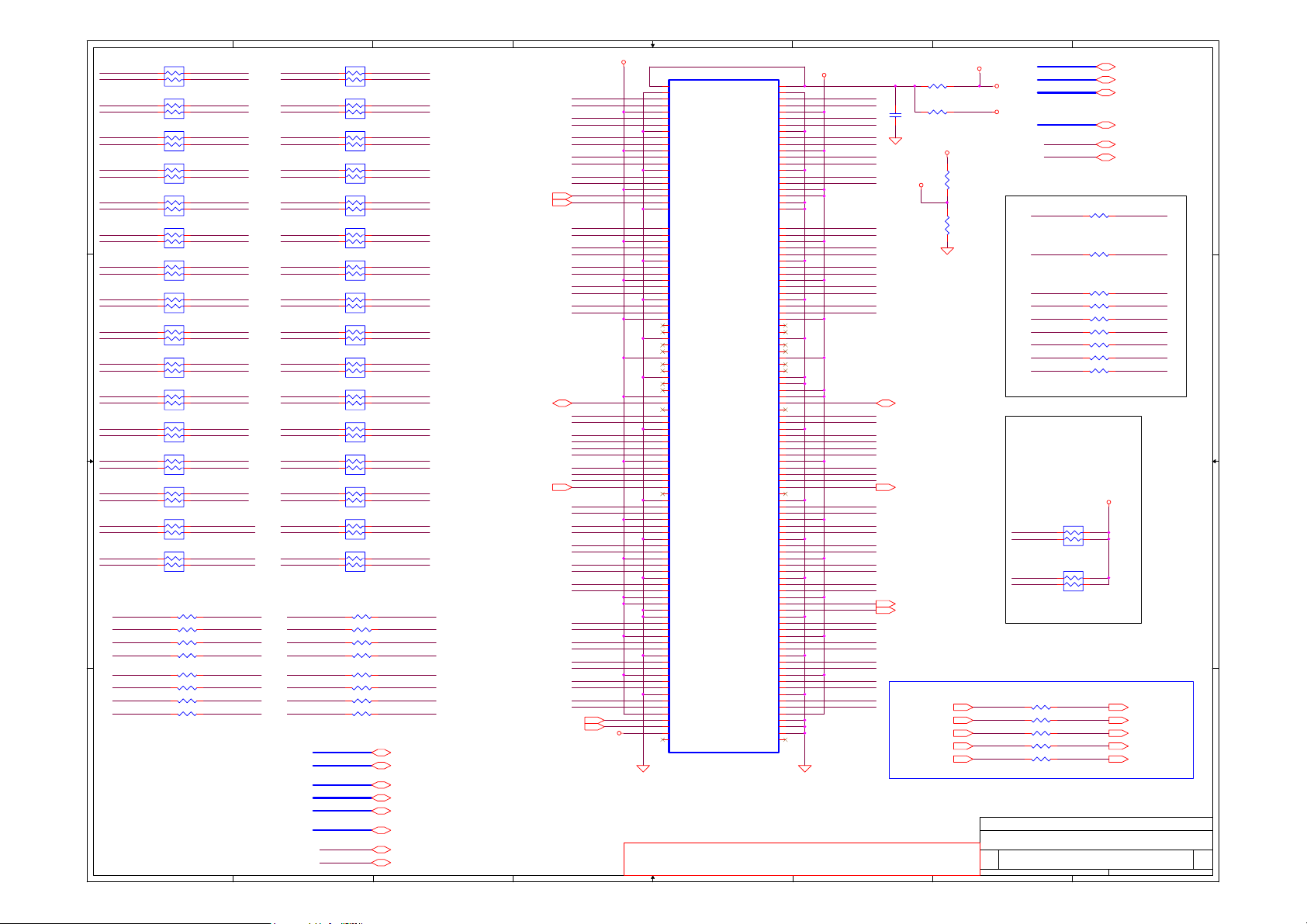

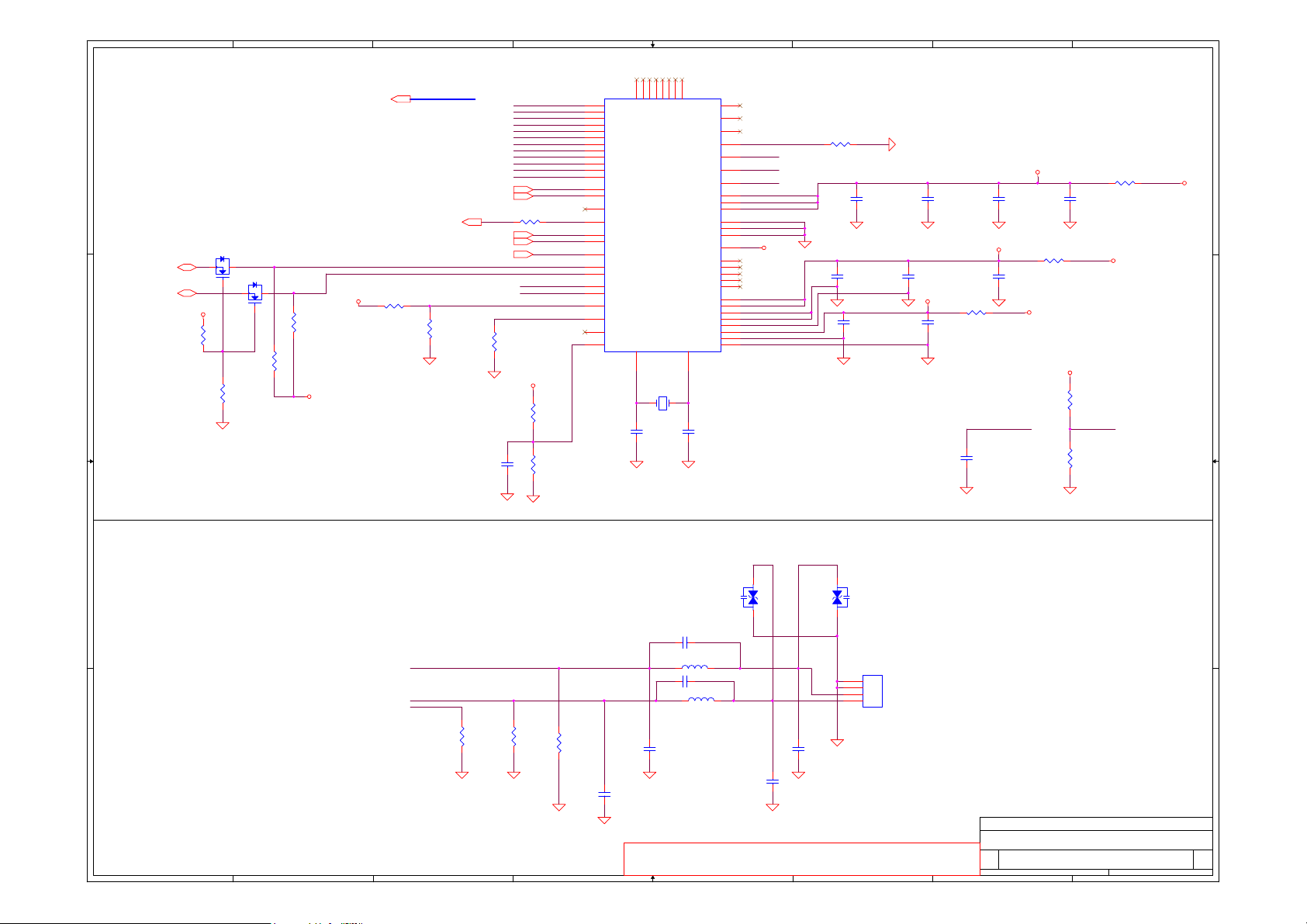

Model : DBL10 -- Sapporo X

B

C

D

E

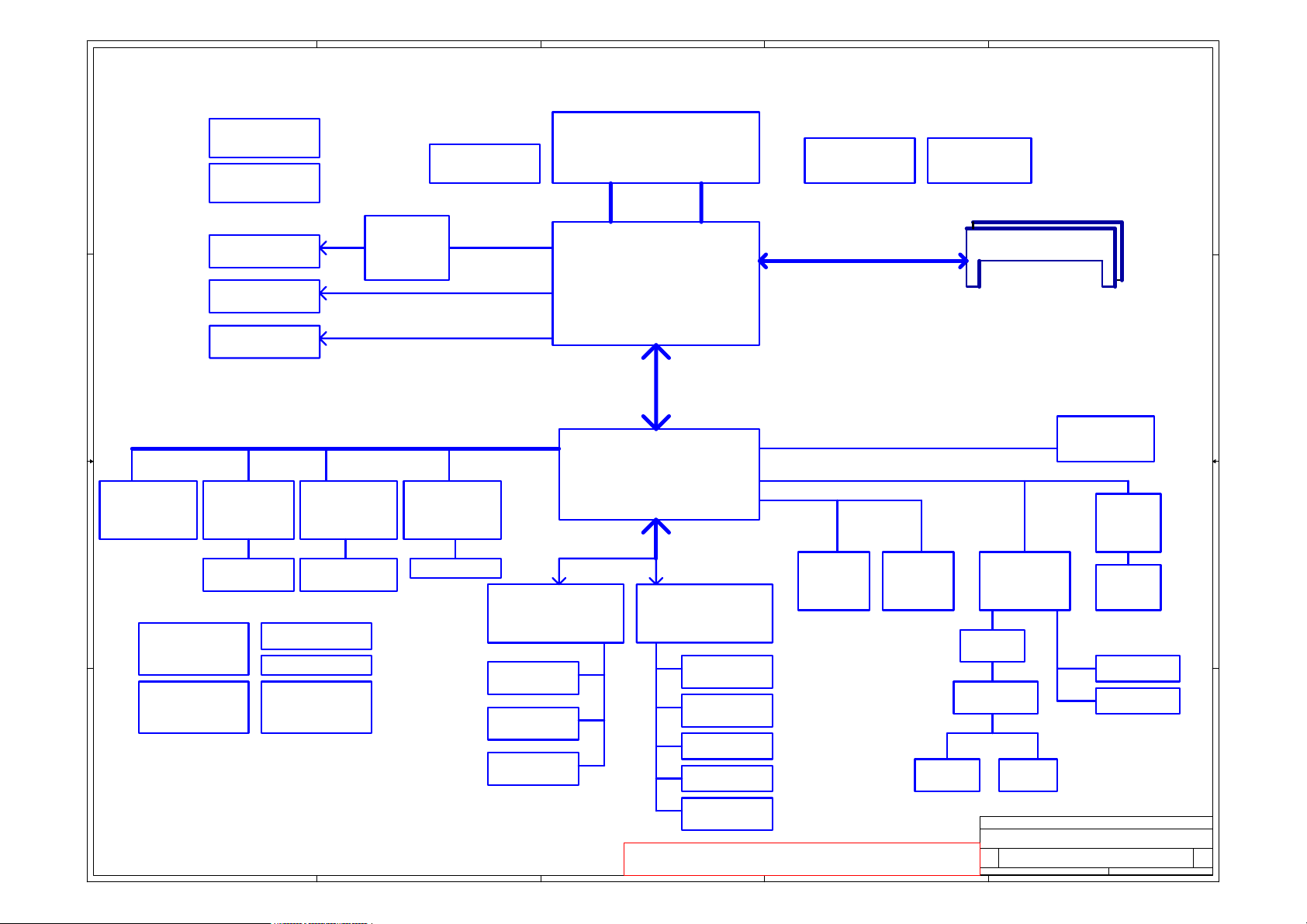

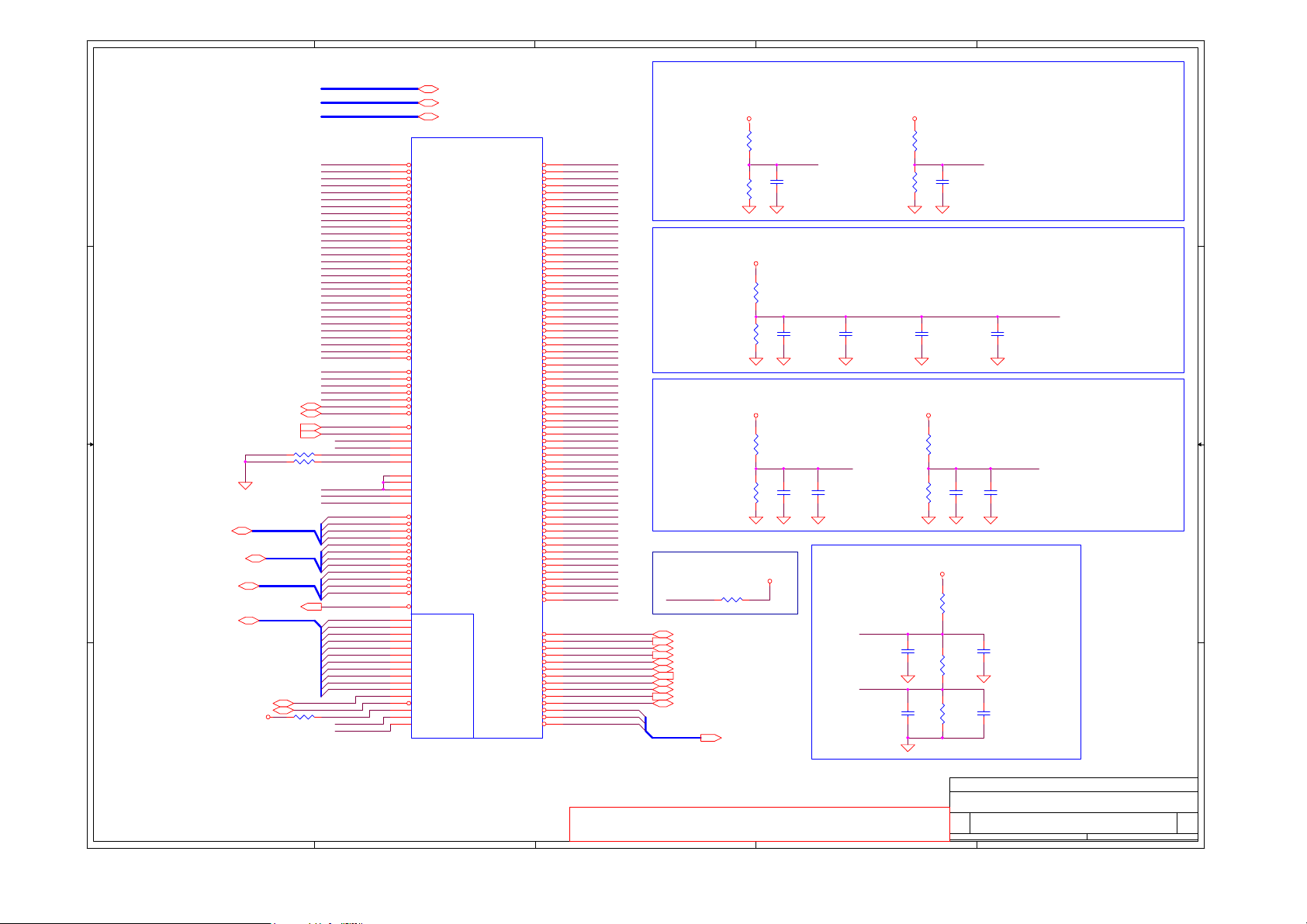

Block Diagram

Fan Control 1

+12VALW

1 1

+5VALW

+12VALW

+5VALW

TV OUT Connector

+3VS

CRT Connector

+5VS

+3VS

LVDS Connector

2 2

B+

page 33

Fan Control 2

page 33

page 15

page 16

page 16

TV Encoder

CH7011A

+3VS

page 15

CPU Bypass

page 6

TV-OUT Signal

by DVOC

CRT Signal

LVDS Signal

+1.2VP

+CPU_CORE

+1.5VS

+2.5V

+3VS

+CPU_CORE

Prescott-MT -- 533

Celeron-MT -- 400

400/533 MHz

478pin

page 4,5

HD#(0..63)HA#(3.. 31)

uFCPGA CPU

System Bus

INTEL

Montara-GT 852GME

732 BGA

page 7,8,9,10

Thermal Sensor

ADM1032AR

+5VS +3VS

page 5

Memory

BUS(DDR)

+2.5V 200/266/333MHz

Clock Generator

ICS950810CG

page 14

DDR-DIMM X2

BANK 0, 1, 2, 3

+2.5V

+1.25VS

page 11,12,13

HUB LINK 1.5

+1.5VS

66MHz

NorthWood-MT -- 533

USB Ports X2

( X1 reserve )

+5V

+5VS

+3VS

+3V

page 28

MIC Phone

+5VDDA

LINE IN

+5VDDA

Compal Electronics , Inc .

Block Diagram

E

page 27

MDC

page 28

RJ11

Cable

Cable

page 29

of

247Monday, June 09, 2003

0.2

Super I/O

page 30

FIR

page 30

page 30

+3VS

+3VALW

+1.5VS

+1.5VALW

+CPU_CORE

VCC5REF

VCC5REFSUS

LPC BUS

page 30

48MHz

24.576MHz

page 26

USB 2.0/1.1

AC-LINK

ATA100

IDE ODD

+5VCD

page 26

PIDE IRQ15SIDE IRQ14

INT. Speaker

page 29

D

+5VALW

INTEL

ICH4-M

421 BGA

page 17,18,19

+3VS

33MHz

IDE HDD

+5VS

Embedded Controller

NS PC87591L

+3VS

+3VALW

EC DEBUG & Int. KB

+5VALW

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY ORDISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC .

C

page 31

+3VALW

page 31

BIOS & Ext. IO

+3VALW

+5VALW

page 32

LID SW & Kill SW

+3VALW

page 33

Touch Pad

+5VS

page 33

LID Hibernation

+RTC_VREF

page 35

AC97 Codec

ALC202

+5VALW -> +VDDA

+3VS

EQ

+5VCD

page 29

AMP TPA6011A4

page 29

HeadPhone

+AUD_VREF

page 29

Title

Size Document Number Re v

LA-1931

Date: Sheet

IEEE 1394

VT6301S

+3V

+3VS

1394 Conn.

B

PCI BUS

IDSEL:AD16

PIRQE#

page 20

page 20

+5VS

+5VS

Debug COM Port

+5V

SMs FDC47N227

+3VS

Paralle l

+3VS 33MHz

LAN

RTL8101L

+3V

+2.5VLAN

RJ45

page 33

IDSEL:AD17

PIRQF#

page 23

page 24

SW Board Conn

+5VALW

RTC Batt.

DC/DC Interface

Suspend

IDSEL:AD18

PIRQG#

Minipci CONN

WIRELESS & Dubug

+3V

+3VS

+5VS

page 25

3 3

On/Off BTN &

User Keys

+3VALW

Power Circuit

DC/DC

4 4

A

IDSEL:AD20

PIRQA#

CardBus

CB1410

+3V

+3VS

page 21

PWR Controller & Slot

+12VALW +5VALW

+3VALW

page 22

page 33

page 33

page 36

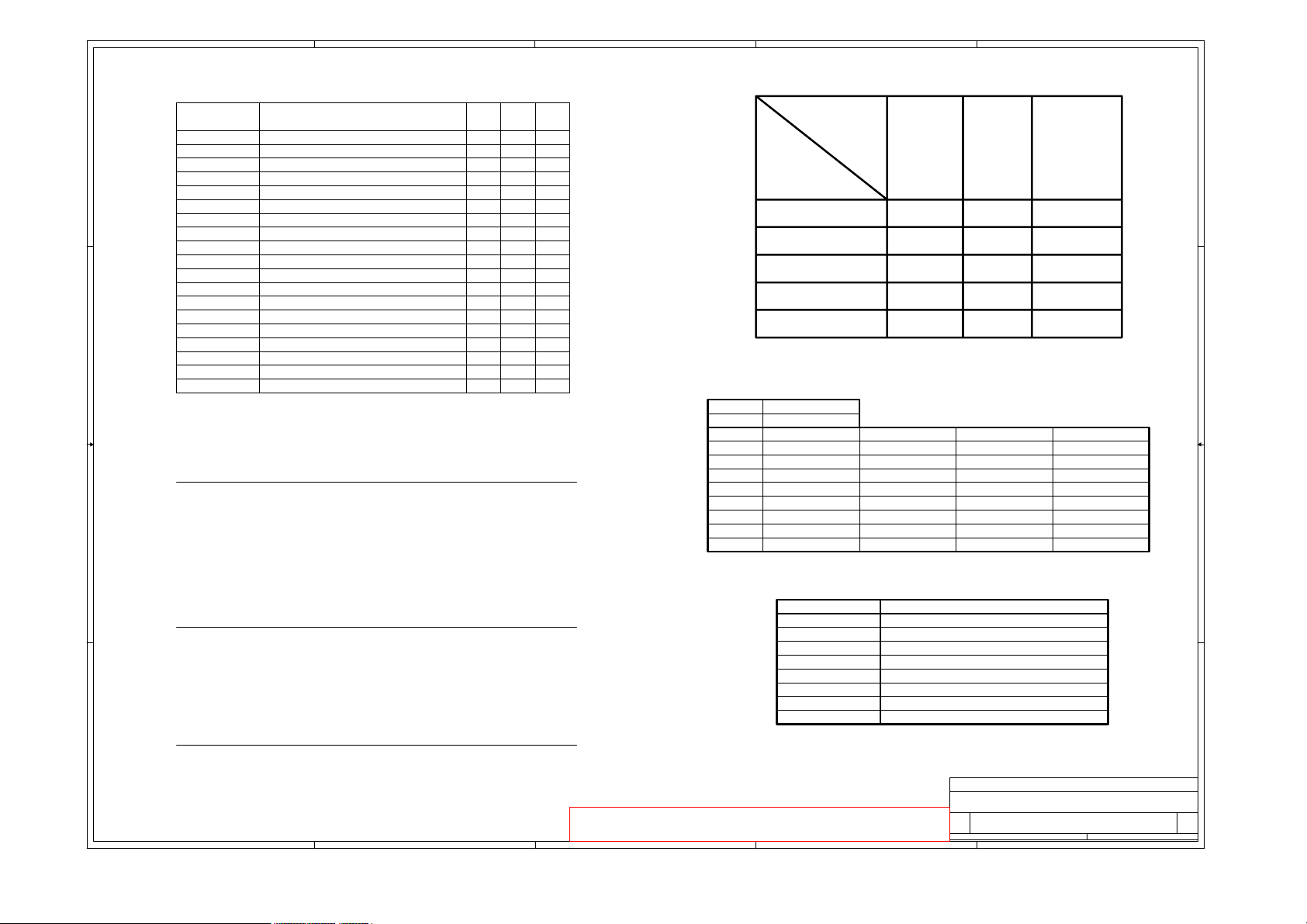

5

4

3

2

1

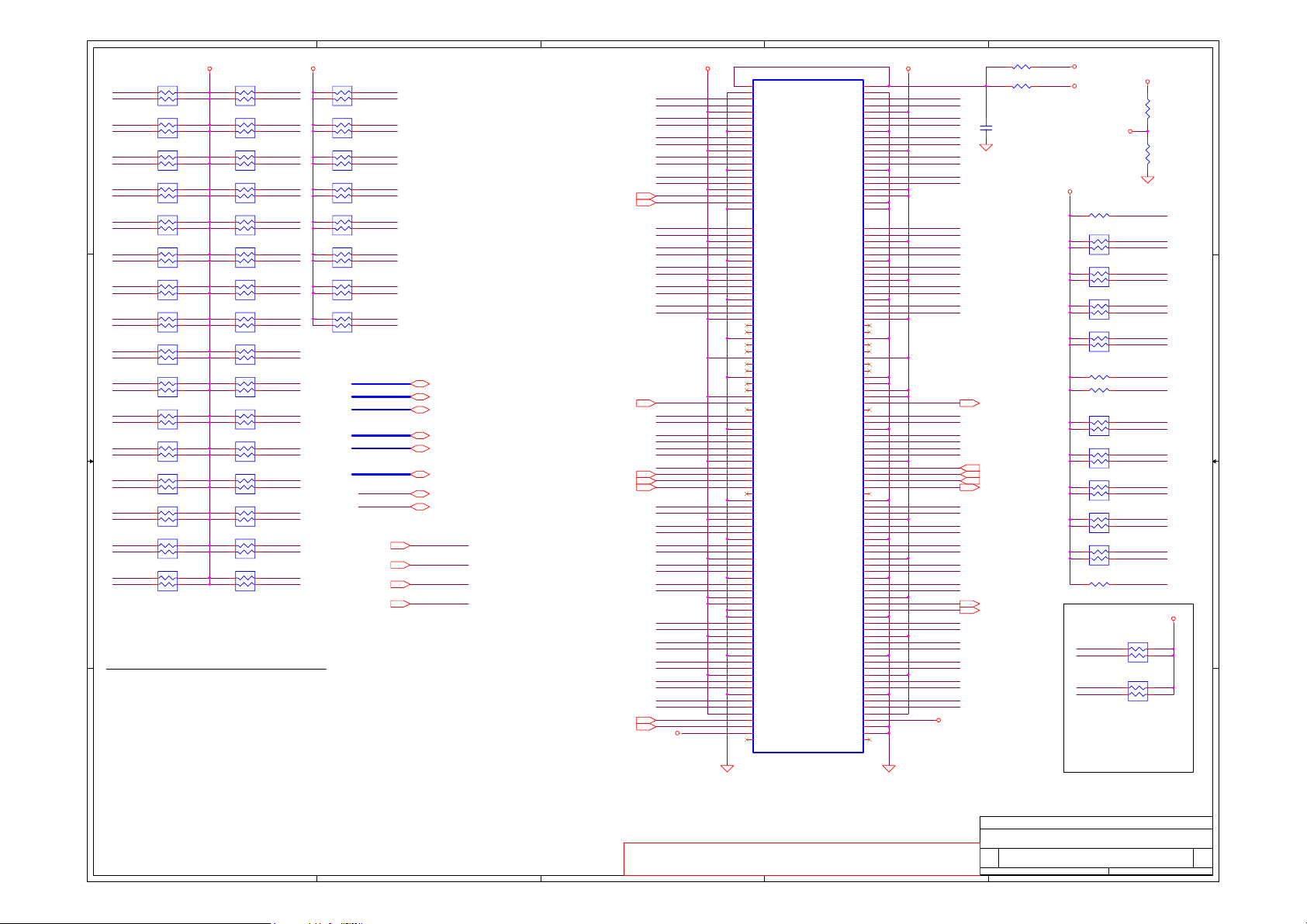

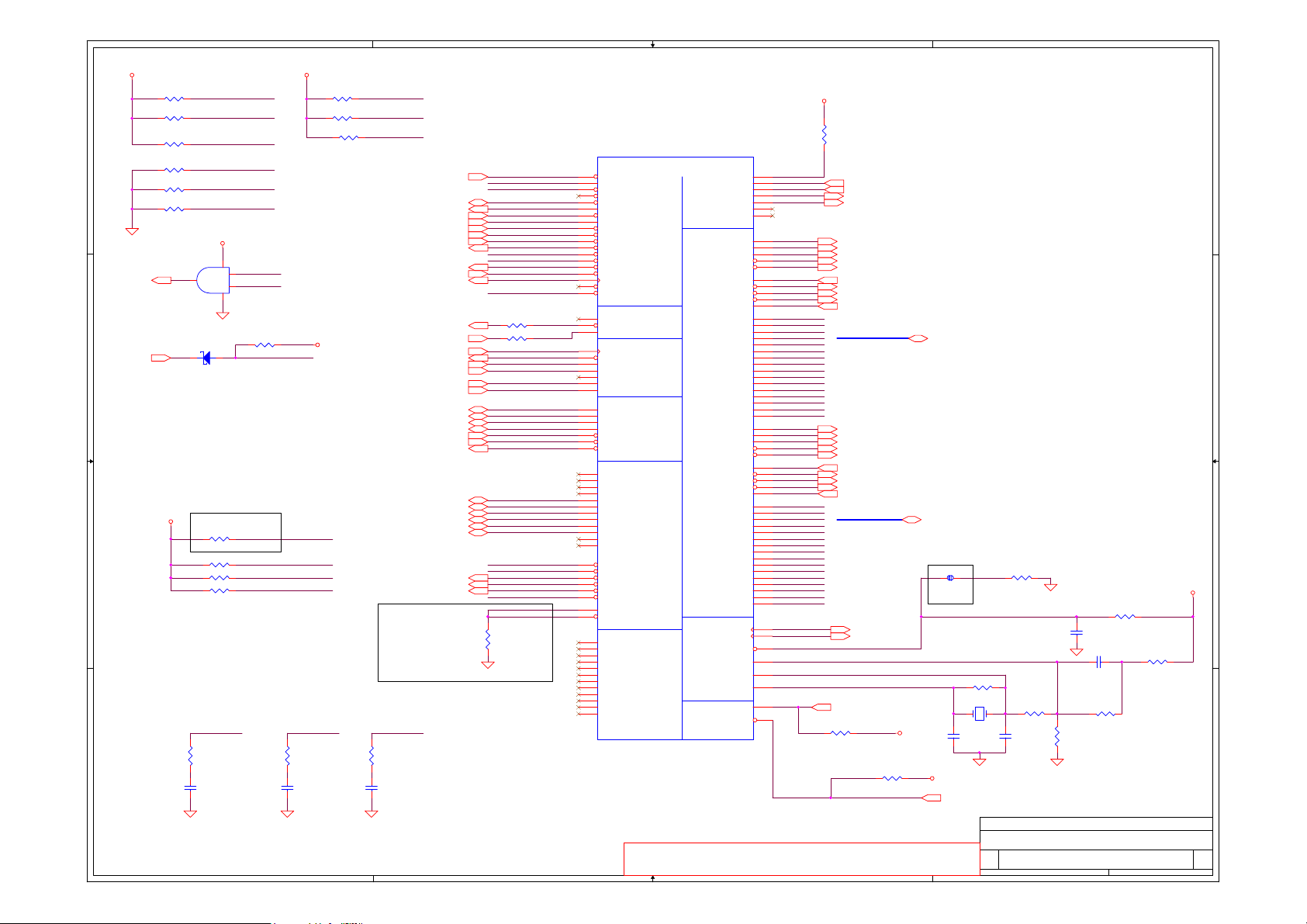

Voltage Rails

Power Plane Description

D D

C C

VIN

B+

+CPU_CORE

+1.2V

+1.25VS 1.25V switched power rail

+1.5VALW 1.5V always on power rail

+1.5V

+1.5VS

+2.5V 2.5V power rail

+3VALW

+3V

+3VS

+5VALW

+5V

+5VS

+12VALW

+RTCBATT

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU A GTL Bus

1.5V power rail

1.5V switched power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail

5V switched power rail

12V always on power rail

RTC power ONON

S1 S3 S5

N/A N/A N/A

ON OFF

ON

ON OFF OFF

ON

ON OFF

ON OFF OFF

ON

ON ON

ON

ON

ON

ON

ON

ON

ON

ON

ON ON

ON

ON

ON

OFF OF F

ON

ON

OFF OF F

ON

N/AN/AN/A

OFF

OFF

OFF

ON

OFF

ON

OFF

ON

Power Managment table

Signal

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

+1.5VALW

+3VALW

+5VALW

+12VALW

ON

+5V

+3V

+2.5V

+1.2V

ON ON

ON ON ON

ON ON

ON OFF

OFF OFF OFF

+5VS

+3VS

+1.5VS

+CPU_CORE

+1.25VS

OFF

OFF

Board ID Table for AD channel

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices ( follow PCI IRQ routing plannig ver0.2.04 )

Device IDSEL# REQ#/GNT# Interrupts - (ICH4-M)

CardB us (ENE-CB1410)

IEEE 1394 (VIA -VT6301S)

LAN (Realtek-RTL8101L)

B B

Mini-PCI

AD20

AD16 0

AD17

AD18

2

3PIRQF#

1/1

PIRQA#

PIRQE#

PIRQG#

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

100K +/- 5%Ra

Rb V min

0

8.2K +/- 1%0V0.216 V 0.250 V 0.289 V

18K +/- 1%

33K +/- 1%

56K +/- 1%

100K +/- 1%

200K +/- 1%

7 NC

AD_BID

Vtyp

AD_BID

V

AD_BID

max

0V 0V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

3.300 V

EC SM Bus1 address

Device

Smart B attery

EEPROM(24C16)

EC SM Bus2 address

Addres s Addres s

1010 000X b

Devic e

ADM1032

1001 100X b0001 011X b

Board ID

0

1

2

3

4

PCB Revision

0.1

5

6

7

A A

ICH4 SM Bus address

Device

CLK GEN ( ICS-950810)

5

Address

1101 001X

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, IN C. NEIT HER TH IS SHEE T NOR T HE INF ORMATION IT CONTAIN S

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITTEN CON SENT OF COMPAL ELE CTRONICS , INC.

3

2

Note & Revision

Size Document Number Rev

LA-1931

Date: Sheet

1

of

347Monday, June 09, 2003

0.2

5

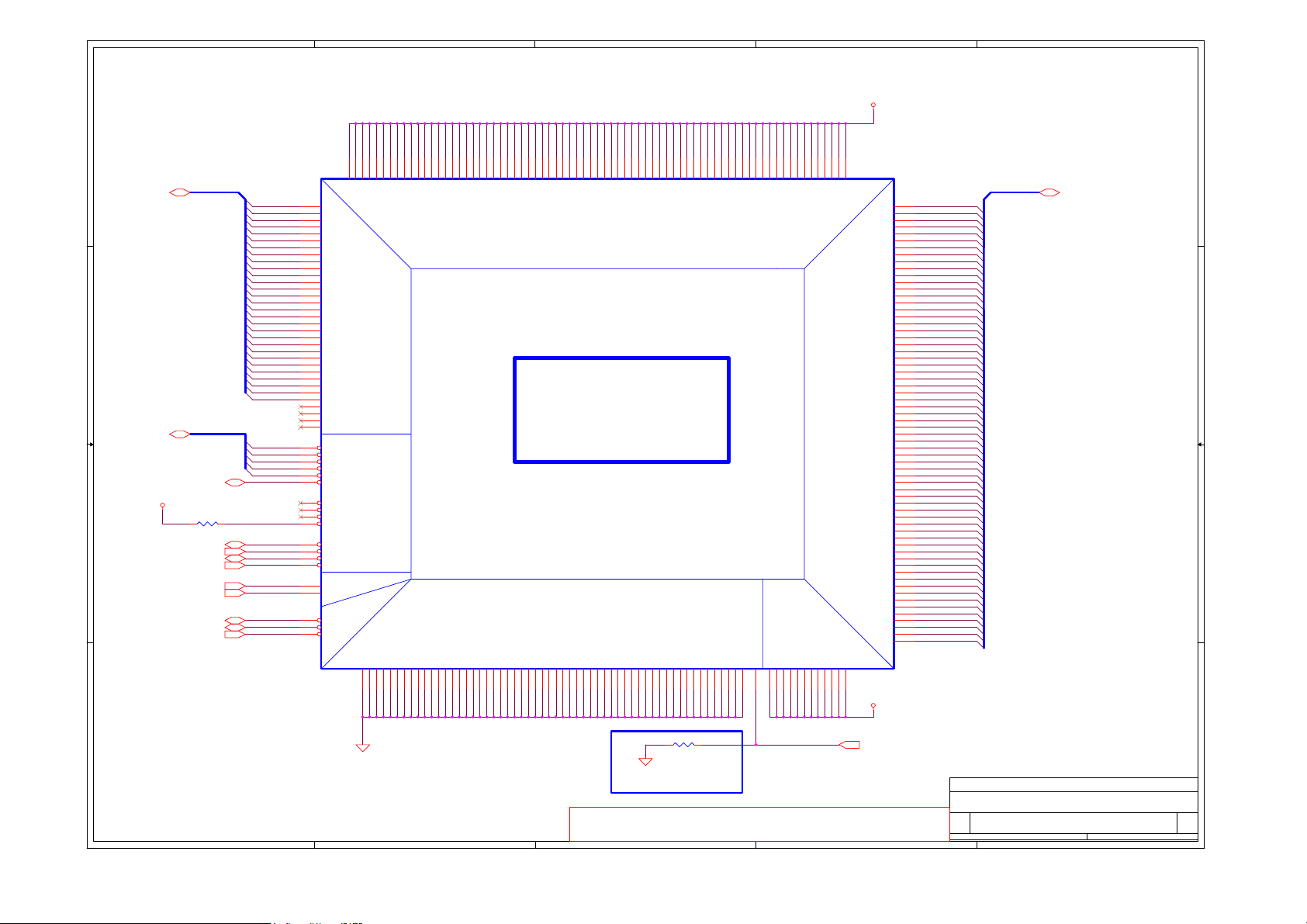

D D

A10

A12

A14

A16

VCC_0

VCC_1

VCC_2

HOST

ADDR

CONTROL

CLK

CON

TROL

VSS_0H1VSS_1H4VSS_2

A18

VCC_3

H23

JCPU1A

HA#[3..31]<7> HD#[0..63] <7>

C C

H_R EQ#[0..4]<7>

+CPU_CORE

B B

H_R EQ#[0..4]

H_ADS#<7>

R15 56_0402_1%

1 2

H_BREQ0#<7>

H_BPRI#<7>

H_BNR#<7>

H_LOCK#<7>

CLK_CPU_BCLK<14>

CLK_CPU_BCLK#<14>

H_HIT#<7 >

H_HITM#<7>

H_DEFER#<7>

HA#3

K2

HA#4

K4

HA#5

L6

HA#6

K1

HA#7

L3

HA#8

M6

HA#9

L2

HA#10

M3

HA#11

M4

HA#12

N1

HA#13

M1

HA#14

N2

HA#15

N4

HA#16

N5

HA#17

T1

HA#18

R2

HA#19

P3

HA#20

P4

HA#21

R3

HA#22

T2

HA#23

U1

HA#24

P6

HA#25

U3

HA#26

T4

HA#27

V2

HA#28

R6

HA#29

W1

HA#30

T5

HA#31

U4

V3

W2

Y1

AB1

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADS#

CLK_CPU_BCLK

CLK_CPU_BCLK#

FOX_PZ47803-274A-42_Prescott

AF22

AF23

J1

K5

J4

J3

H3

G1

AC1

V5

AA3

AC3

H6

D2

G2

G4

F3

E3

E2

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

BCLK0

BCLK1

HIT#

HITM#

DEFER#

A20

VCC_4

H26

VCC_5

VSS_3

A11

AA10

AA12

VCC_6A8VCC_7

VSS_4

VSS_5

A13

A15

AA14

VCC_8

VSS_6

A17

AA16

VCC_9

VSS_7

A19

VCC_10

VSS_8

4

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

POWER

Northwood-MT

Prescott-MT

GND

VSS_9

VSS_10

VSS_11

VSS_12A3VSS_13A9VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

A21

A24

A26

AA1

AA11

AA4

AA7

AA13

AA15

AA9

AA17

AA19

AA23

AA26

AB10

AB12

AB3

AB14

AB6

AB16

AB18

AB20

AB21

AB24

AE18

VCC_36

VSS_34

AB8

AE20

VCC_37

VSS_35

AC11

AE6

VCC_38

VSS_36

AC13

AE8

VCC_39

VSS_37

AC15

AF11

VCC_40

VCC_41

VSS_38

VSS_39

AC17

AF13

VCC_42

VSS_40

AC19

3

AF15

AC2

AF17

VCC_43

VCC_44

VSS_41

VSS_42

AC22

AF19

VCC_45

VSS_43

AC25

AF2

VCC_46

VSS_44

AC5

AF21

VCC_47

VSS_45

AC7

AF5

VCC_48

VSS_46

AC9

AF7

AD10

AF9

VCC_49

VCC_50

VSS_47

VSS_48

AD12

B11

VCC_51

VSS_49

AD14

B13

AD16

B15

VCC_52

VCC_53

VSS_50

VSS_51

AD18

B17

AD21

B19

VCC_54

VSS_52

AD23

VCC_55

VSS_53

AD4

VCC_56B7VCC_57B9VCC_58

VSS_54

VSS_55

AD8

C10

C12

C14

VCC_59

VCC_61

BOOTSELECT

AD1

C16

C18

C20

VCC_62

VCC_63

VCC_64

VCC_65C8VCC_66

POWER

VCC_81

VCC_82

VCC_83

VCC_84

F13

F15

F17

F19

D11

VCC_85

F9

D13

VCC_67

F11

D15

D17

VCC_68

VCC_79E8VCC_80

E20

D19

D9

VCC_69

VCC_70

VCC_71D7VCC_72

HOST

ADDR

VCC_76

VCC_77

VCC_78

E14

E16

E18

+CPU_CORE

E10

VCC_73

VCC_74

VCC_75

E12

+CPU_CORE

2

HD#[0..63]HA#[3..31]

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#0

B21

1

BOOTSEL

A A

Pop: Northwood

Depop: Prescott

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, IN C. NEIT HER TH IS SHEE T NOR T HE INF ORMATION IT CONTAIN S

5

4

3

R8

@0_0402_5%

12

R_C

BOOTSELECT <44>

2

Compal Electronics, Inc.

Title

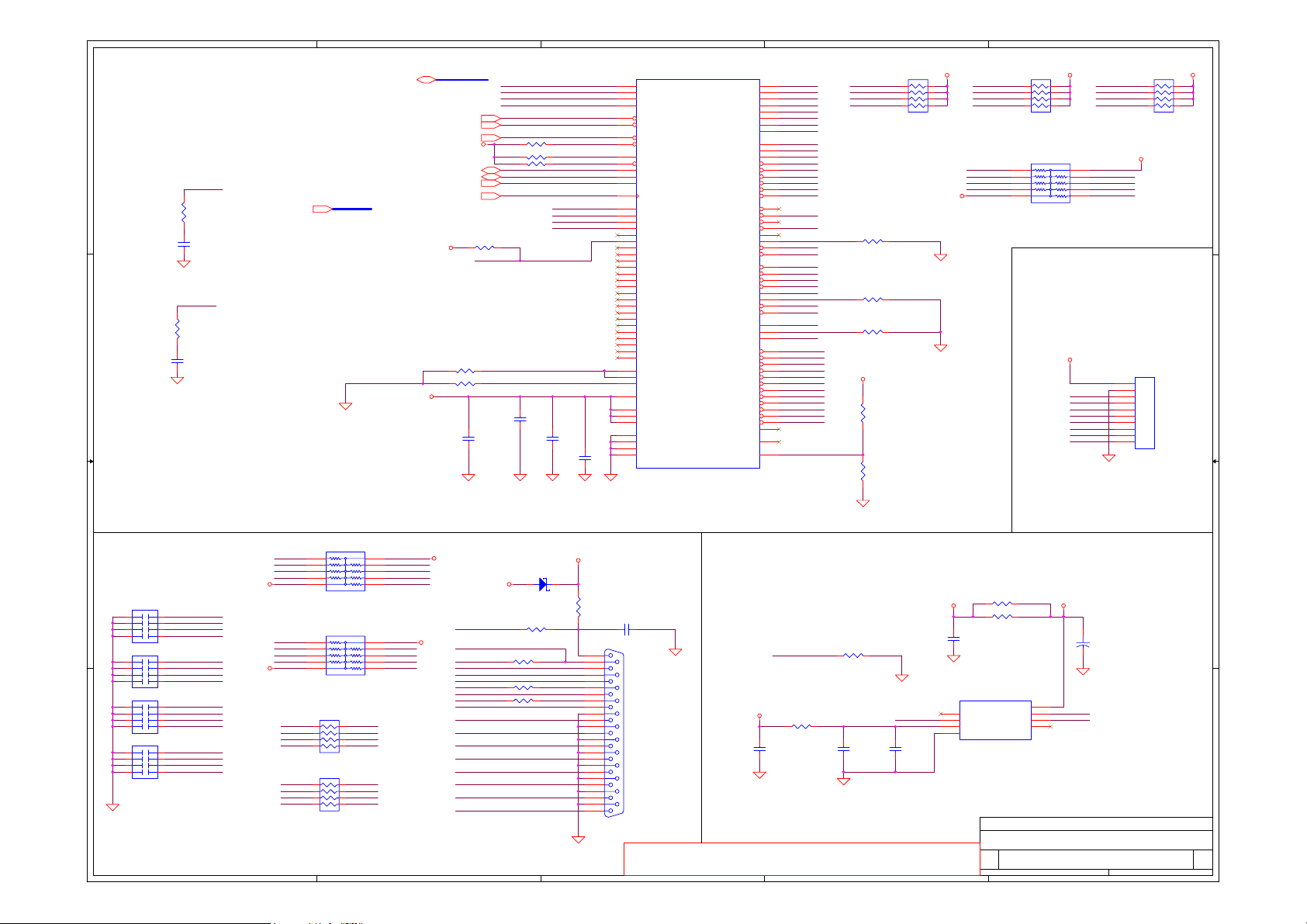

Prescott / P4 uFCPGA (1/2)

Size Document Number Rev

LA-1931

Custom

Date: Sheet

1

of

447Monday, June 09, 2003

0.2

5

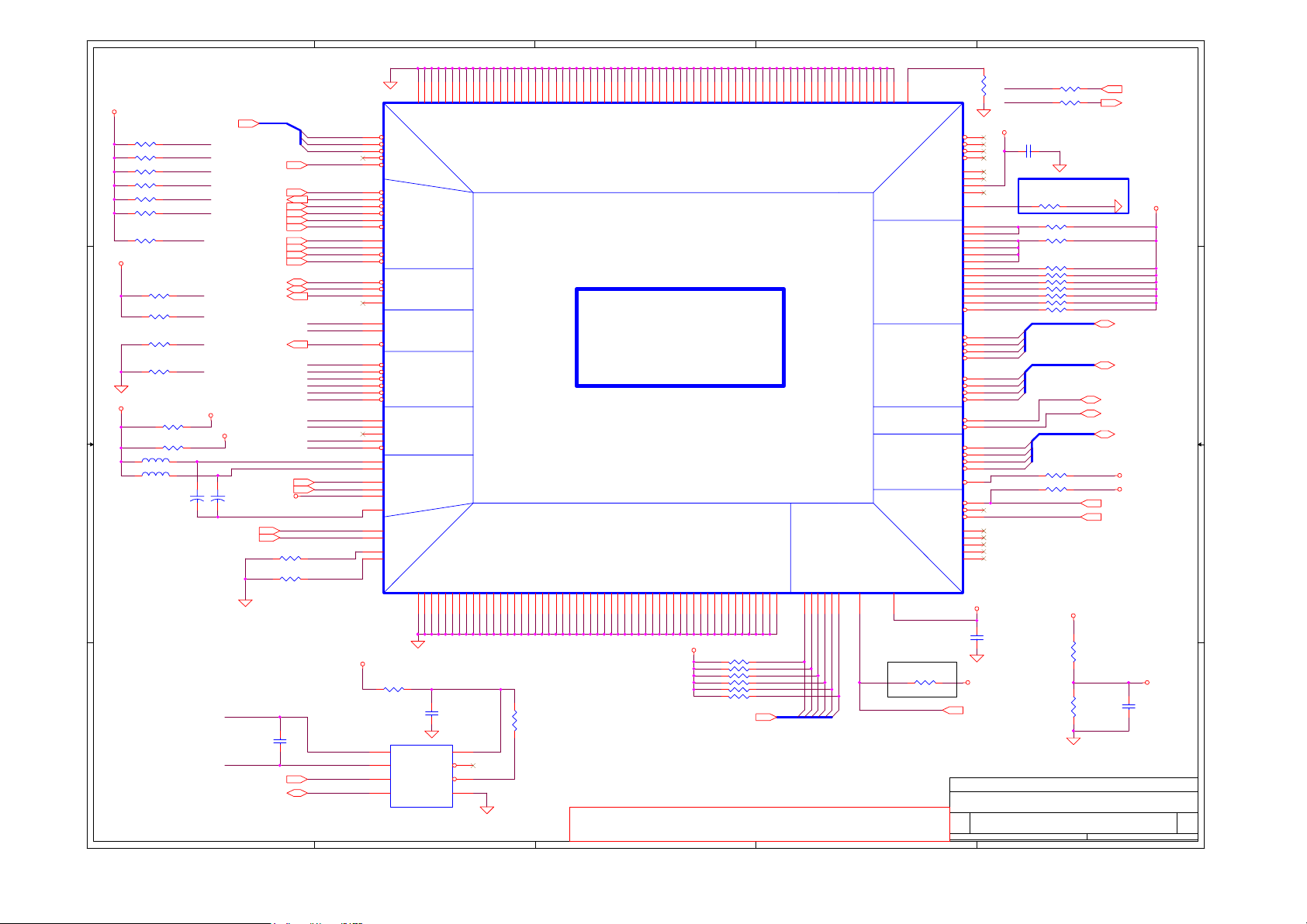

+CPU_CORE

H_RS#[0..2]<7>

ITP_BPM#0

1 2

R49 51_0402_5%

D D

+CPU_CORE

C C

+IOPLL

B B

ITP_BPM#1

1 2

R44 51_0402_5%

ITP_BPM#2

1 2

R14 51_0402_5%

ITP_BPM#3

1 2

R38 51_0402_5%

ITP_BPM#4

1 2

R41 51_0402_5%

ITP_BPM#5

1 2

R13 51_0402_5%

H_PWRGD

1 2

R84 300_0402_5%

ITP_TDI

12

R9 150_ 0402_5%

ITP_T MS

12

R1 39.2_0603_1%

ITP_TRST#

12

R21 680_0402_5 %

ITP_TCK

12

R19 27.4_ 0603_1%

0_0603_5%

R325

1 2

@0_0805_5%

R324

1 2

L26

1 2

LQG21F4R7N00_0805

1 2

LQG21F4R7N00_0805

L27

C331

@33U_D2_16VM

+CPU_CORE

1

+

2

CLK_CPU_ITP<14>

CLK_CPU_ITP#<14>

+1.2V

1

+

C332

33U_D2_16VM

2

H_RS#[0..2]

H_TRDY#<7>

H_A20M#<17>

H_FERR#<17>

H_IGNNE#<17>

H_SMI#<17>

H_PWRGD<17>

H_STPCLK#<17>

H_INTR<17>

H_NMI<17>

H_INIT#<17>

H_RESET#<7>

H_DBSY#<7>

H_DRDY#<7>

H_BSEL0<14>

H_THERMTRIP#<18>

VCCIOPLL

VCCA

VCCSENSE<44>

VSSSENSE<44>

+1.2V

1 2

R82 61.9_0603_1 %

1 2

R20 61.9_0603_1 %

Comp0/1 need keep 25

mils trace width

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_INTR

H_NMI

H_INIT#

H_RESET#

H_DBSY#

H_DRDY#

H_BSEL0

H_THERMDA

H_THERMDC

H_THERMTRIP#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_T MS

ITP_TRST#

VCCSENSE

VSSSENSE

VSSA

FOX_PZ47803-274A-42_Prescott

+3VS

AB23

AB25

AD6

AD5

AC6

AC4

AD20

AE23

AD22

AC26

AD26

F1

G5

F4

AB2

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

B3

C4

A2

AB5

Y6

AA5

AB4

D4

C1

D5

F7

E6

A5

A4

AF3

L24

P1

CPU Temperature Sensor

1 2

H_THERMDA

1

A A

5

C24

2200P_0603_50V7K

H_THERMDC

EC_SMC2<32>

EC_SMD2<32>

2

200_0402_5%

GND

JCPU1B

RS#0

RS#1

RS#2

RSP#

TRDY#

CON

TROL

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

LINT0

LEGACY

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCIOPLL

VCCA

VCCSENSE

VSSSENSE

VCCVIDLB

VSSA

ITP_CLK0

ITP_CLK1

COMP0

COMP1

R61

U6

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

4

AE11

AE13

AE15

VSS_57

VSS_58

MISC

THER

MAL

MISC

MISC

ITP

CLK

VSS_129F8VSS_130

G21

G24

1

2

VDD1

ALERT#

THERM#

4

AE17

AE19

AE22

AE24

AE7

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

ITP

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

J22

J25

C27

1U_0402_6.3V4Z

1

6

4

5

GND

VSS_65

VSS_136

3

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

C11

C13

C15

C17

C19

C22

C25

D10

D12

D14

D16

D18

D20

D21

D24

E11

E13

E15

E17

E19

E23

E26

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85B4VSS_86B8VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92C2VSS_93

VSS_94

VSS_95C5VSS_96C7VSS_97C9VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

GROUND

Northwood-MT

Prescott-MT

GROUND MISC

VID0

VSS_137J5VSS_138

VSS_139

VSS_140K3VSS_141K6VSS_142L1VSS_143

VSS_144

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_168

VSS_169U5VSS_170V1VSS_171

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

L23

L26

K21

K24

12

R48

10K_0402_5%

M22

M25

P22

N21

N24

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, IN C. NEIT HER TH IS SHEE T NOR T HE INF ORMATION IT CONTAIN S

T21

P25

T24

R23

R26

3

V23

V26

U22

U25

W21

W24

+3VS

R270 1K_0402_5%

1 2

R271 1K_0402_5%

1 2

R272 1K_0402_5%

1 2

R267 1K_0402_5%

1 2

R266 1K_0402_5%

1 2

R16 1K_0402_5%

1 2

CPU_VID[0..5]<44>

Y22

VID1

VSS_180

VSS_181

Y5

Y25

AE5

AE4

AE3

CPU_VID2

CPU_VID0

CPU_VID1

VSS_117E4VSS_118E7VSS_119E9VSS_120

VID2

VID3

AE2

AE1

CPU_VID3

CPU_VID4

F10

F12

F14

VSS_121

VID4

VID5

AD3

CPU_VID5

2

F16

F18

F22

F25

F5

VSS_122

VSS_123

VSS_124

VSS_125F2VSS_126

VSS_127

REF

OPTIMIZED/COM PAT#

ITP

DATA

ADDR

DATA

MISC

VIDPWRGD

AF4

AD2

Pop: Prescott

Depop: Northwood

2

AF26

VSS_128

SKTOCC#

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI10

TESTHI11

TESTHI12

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

PROCHOT#

VCCVID

R12

@2.43 K_0603_1%

1

H_SKTOCC#

R320

@33_0402_5%

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

MCERR#

12

H_DPSLPR#

H_GHI#

+H_GTLREF

J26

DP#0

K25

DP#1

K26

DP#2

L25

DP#3

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

SLP#

NC1

NC2

NC3

NC4

NC5

12

Title

Size Document Number Rev

Custom

Date: Sheet

220P_0603_50V8J

AA21

AA6

F20

F6

AE26

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

H_GHI#

A6

H_DPSLPR#

AD25

H_DSTBN#0

E22

H_DSTBN#1

K22

H_DSTBN#2

R22

H_DSTBN#3

W22

H_DSTBP#0

F21

H_DSTBP#1

J23

H_DSTBP#2

P23

H_DSTBP#3

W23

H_ADSTB#0

L5

H_ADSTB#1

R5

H_DBI#0

E21

H_DBI#1

G25

H_DBI#2

P26

H_DBI#3

V21

AE25

H_PROCHOT#

C3

V6

H_SLP#

AB26

A22

A7

AF25

AF24

AE21

+1.2V

1

C276

0.1U_0402_16V7K

2

+1.2V

H_VID_PWRGD <35>

Compal Electronics, Inc.

Prescott / P4 uFCPGA & Thermal sensor (2/2)

LA-1931

R321

0_0402_5%

1 2

1 2

R55

0_0402_5%

C33

1 2

R_G

R326 @0_0402_5%

1 2

1 2

R80 56_0402_5%

1 2

R79 56_0402_5%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

H_DS TBN#[0..3]

H_DSTBP# [0..3]

H_D BI#[0..3]

12

R323 150_0402_5%

1 2

R10 100K_0402_1%

GTL Reference Voltage

Layout note :

H_DPSLP# <8,17>

PM_CPUPERF# <18>

+CPU_CORE

R52 56_0402_5%

R78 56_0402_5%

R37 56_0402_5%

R40 56_0402_5%

R43 56_0402_5%

R57 300_0402_5 %

R322 @56_0402_5%

H_DS TBN#[0..3] <7>

H_DSTBP #[0..3] <7>

H_ADSTB#0 <7>

H_ADSTB#1 <7>

H_D BI#[0..3] <7>

+3VALW

+CPU_CORE

H_PROCHOT# <43>

H_SLP# <17>

1. Place R_A and R_B near CPU (Within 1.5").

+CPU_CORE

R56

51.1_0603_1%

12

R59

86.6_0603_1%

1

C34

1U_0603_6.3V6M

2

of

547Monday, June 09, 2003

1

+H_GTLREF

0.2

A

Layout note :

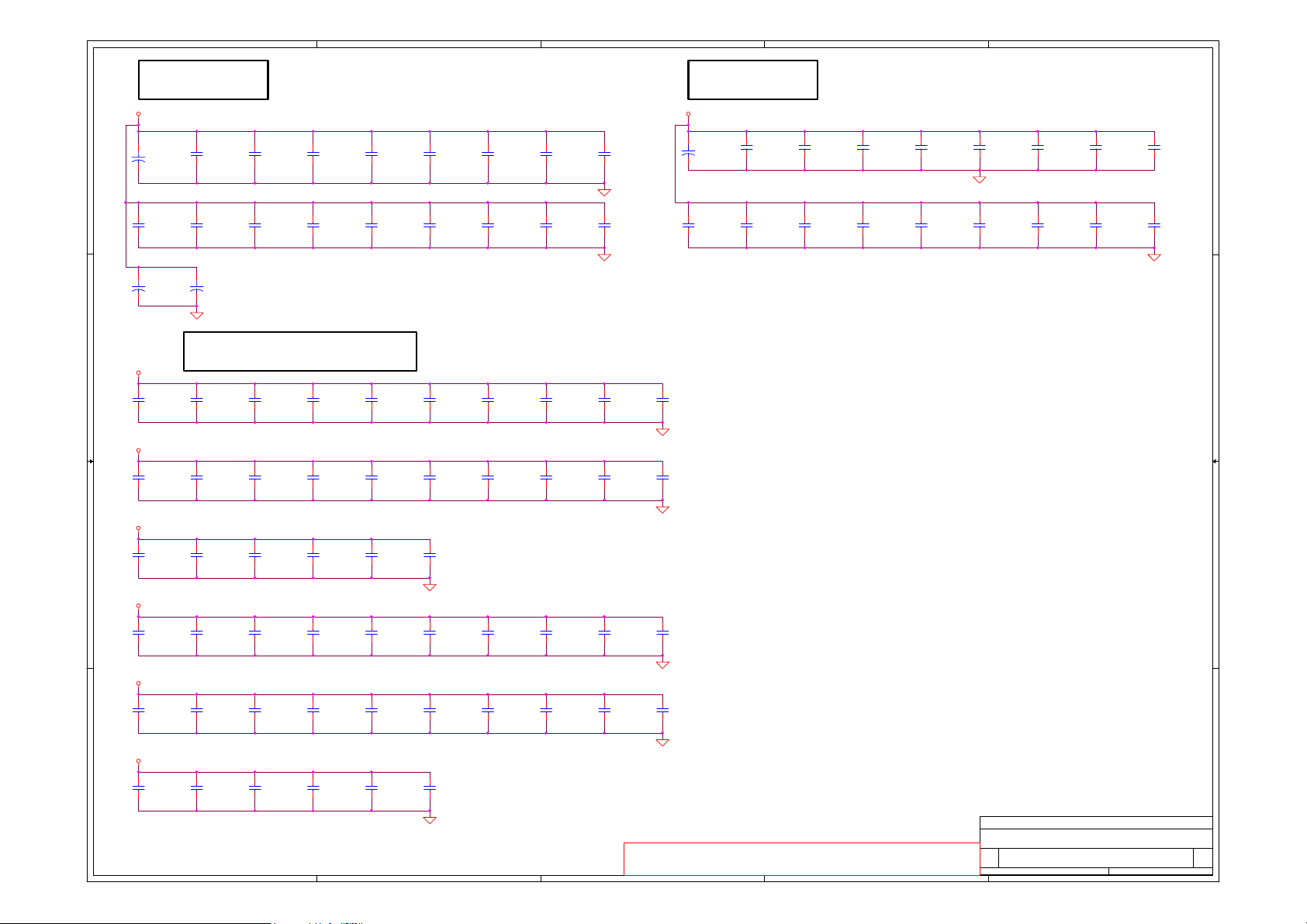

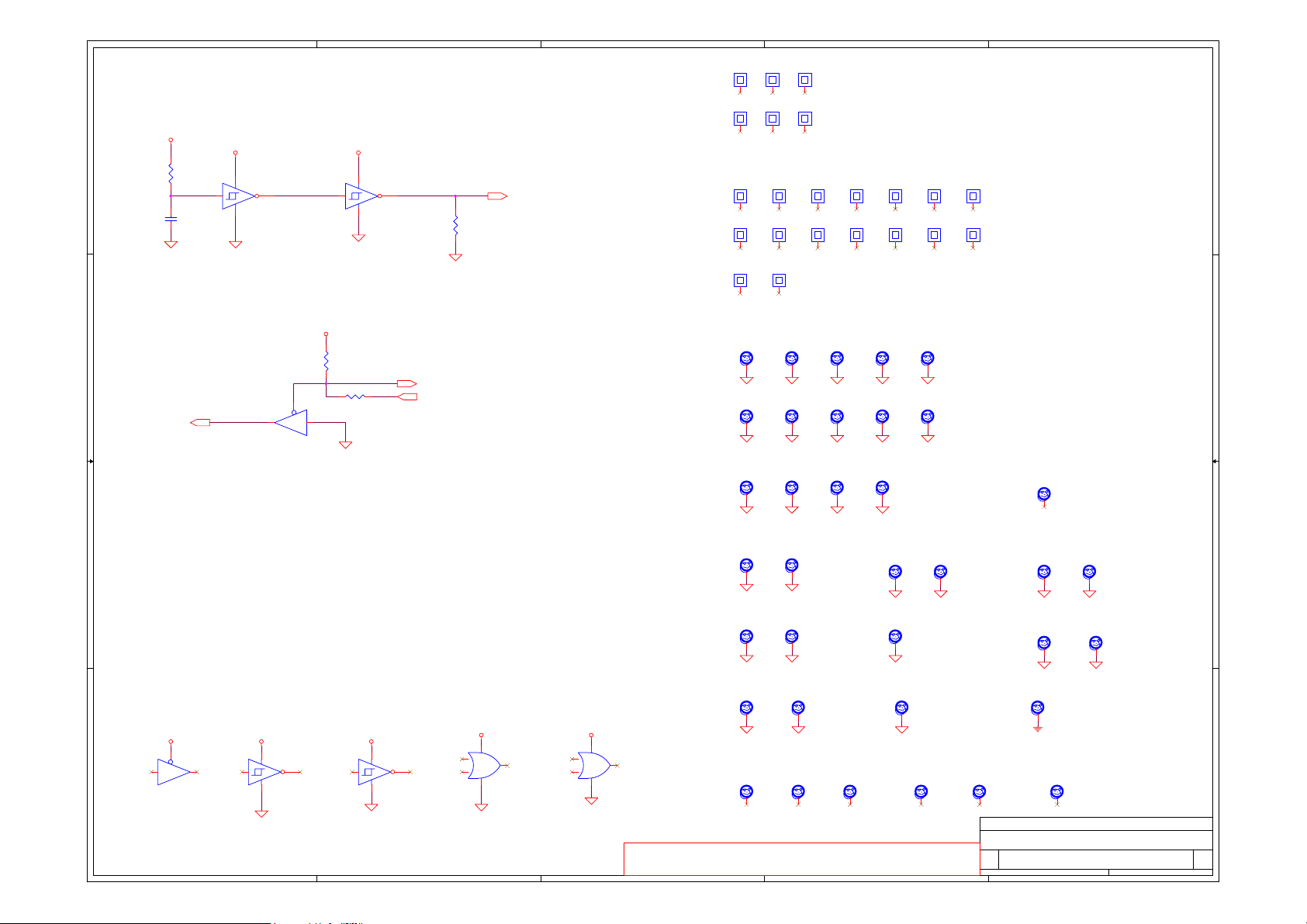

1 1

+CPU_CORE

2 2

+CPU_CORE

Place close to CPU, Use 2~3 vias per PA D.

Place 22uF caps x31 pcs, populated 14pcs.

1

C308

22U_1206_6.3V6M

2

1

C306

22U_1206_6.3V6M

2

B

1

C313

22U_1206_6.3V6M

2

1

C297

22U_1206_6.3V6M

2

C

Place on CPU inside

1

C321

22U_1206_6.3V6M

2

1

C323

22U_1206_6.3V6M

2

1

C315

22U_1206_6.3V6M

2

1

C298

22U_1206_6.3V6M

2

1

C307

22U_1206_6.3V6M

2

1

C322

22U_1206_6.3V6M

2

D

1

C314

22U_1206_6.3V6M

2

1

C299

22U_1206_6.3V6M

2

E

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

For Desktop's CPU:

470uFx15/12mOhm H=1.8 each

Total 0.923m ohm

F

+CPU_CORE

+CPU_CORE

+CPU_CORE

1

+

C20

470U_D4_2.5VM

2

1

+

C18

@470U_D4_2.5VM

2

1

+

C319

470U_D4_2.5VM

2

G

1

+

C30

470U_D2_2.5VM

2

1

+

C45

470U_D4_2.5VM

2

1

+

C325

470U_D4_2.5VM

2

H

1

+

2

1

+

2

1

+

2

C11

@470U_D4_2.5VM

C53

470U_D4_2.5VM

C329

470U_D4_2.5VM

1

+

2

1

+

2

I

C40

470U_D4_2.5VM

C304

470U_D4_2.5VM

1

+

2

1

+

2

C26

470U_D4_2.5VM

C291

470U_D4_2.5VM

J

3 3

+CPU_CORE

1

2

4 4

+CPU_CORE

1

C343

@22U_1206_6.3V6M

2

Please place these cap on the socket north side

C338

@22U_1206_6.3V6M

1

C344

@22U_1206_6.3V6M

2

1

C335

@22U_1206_6.3V6M

2

1

2

1

C339

@22U_1206_6.3V6M

2

C336

@22U_1206_6.3V6M

1

2

1

C340

@22U_1206_6.3V6M

2

C345

@22U_1206_6.3V6M

1

C341

@22U_1206_6.3V6M

2

1

C337

@22U_1206_6.3V6M

2

1

C342

@22U_1206_6.3V6M

2

5 5

6 6

7 7

8 8

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

C

D

E

F

G

H

Compal Electronics, Inc.

Title

CPUDecoupling CAP.

Size Document Number Re v

LA-1931

Custom

Date: Sheet

I

of

647Monday, June 09, 2003

J

0.2

5

4

3

2

1

HA#[3..31]

H_R EQ#[0..4]

HD#[0..63]

D D

C C

H_ADSTB#0<5>

H_ADSTB#1<5>

CLK_MCH_BCLK#<14>

CLK_MCH_BCLK<14>

R331 27 .4_0402_1%

1 2

1 2

R367 27 .4_0402_1%

+1.5VS

HUB_PSTRB<17>

HUB_PSTRB#<17>

H_D STBN#[0..3]

H_DSTBP# [0..3]

H_D BI#[0..3]

H_RESET#<5>

H_PD[0..10]

1 2

48.7_0603_1%

B B

A A

H_DST BN#[0..3]<5>

H_DSTBP# [0..3]<5>

H_DBI#[0..3]<5>

H_PD[0..10]<17>

R492

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

CLK_MCH_BCLK#

CLK_MCH_BCLK

+HYSWING

+HXSWING

+HYRCOMP

+HXRCOMP

+HVREF

+HCCVREF

+HAVREF

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_PD0

H_PD1

H_PD2

H_PD3

H_PD4

H_PD5

H_PD6

H_PD7

H_PD8

H_PD9

H_PD10

HLRCOMP

+HUB_PSWING

+HUB_VREF

W25

AA27

W24

W23

W27

AA28

W28

AB27

AB28

AA26

AD29

AE29

HA#[3..31] <4>

H_R EQ#[0..4] <4>

HD#[0..63] <4>

U26A

Montara-GT

P23

HA#3

T25

HA#4

T28

HA#5

R27

HA#6

U23

HA7#

U24

HA#8

R24

HA#9

U28

HA#10

V28

HA#11

U27

HA#12

T27

HA#13

V27

HA#14

U25

HA#15

V26

HA#16

Y24

HA#17

V25

HA#18

V23

HA#19

HA#20

Y25

HA#21

HA#22

HA#23

HA#24

HA#25

Y27

HA#26

HA#27

HA#28

HA#29

Y26

HA#30

HA#31

R28

HREQ#0

P25

HREQ#1

R23

HREQ#2

R25

HREQ#3

T23

HREQ#4

HADSTB#0

HADSTB#1

BCLK#

BCLK

HYSWING

HXSWING

HYRCOMP

HXRCOMP

HDVREF0

HDVREF1

HDVREF2

HCCVREF

HAVREF

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

DINV0#

DINV1#

DINV2#

DINV3#

CPURST#

HL_0

HL_1

HL_2

HL_3

HL_4

HL_5

HL_6

HL_7

HL_8

HL_9

HL_10

HLSTB

HLSTB#

HLRCOMP

PSWING

HLVREF

HOST

HUB I/F

T26

K28

B18

H28

B20

K21

J21

J17

Y28

Y22

J28

C27

E22

D18

K27

D26

E21

E18

J25

E25

B25

G19

F15

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

T2

U2

W1

RG82G4350MA1_uFCBGA732_MONTARA-GT

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HIT#

HLOCK#

BREQ0#

BNR#

BPRI#

DBSY#

RS#0

RS#1

RS#2

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

N23

P26

M27

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_BREQ0#

H_RS#0

H_RS#1

H_RS#2

HXSWING and HYSWING Ref. Voltage

12

R337

301_0402_1 %

+HYSWING +HXSWING

1

12

R338

150_0402_1%

C387

0.1U_0402_10V6K

2

Host data Ref. Voltage

+CPU_CORE

12

R385

49.9_0603_1%

12

R376

100_0603_1%

1

C423

1U_0402_6.3V4Z

2

1

C456

0.1U_0402_10V6K

2

Host Address Ref. Voltage

+CPU_CORE

12

R384

49.9_0603_1%

+HAVREF

1

1

C418

C427

2

0.1U_0402_10V6K

2

HUBLink reference Voltage

+HUB_PSWING

C588

0.01U_0402_25V7Z

+HUB_VREF

C592

0.01U_0402_25V7Z

Placed by GMCH

H_BREQ0#

H_ADS# <4>

H_TRDY# <5>

H_DRDY# <5>

H_DEFER# <4>

H_HITM# <4>

H_HIT# <4>

H_LOCK# <4>

H_BREQ0# <4>

H_BNR# <4>

H_BPRI# <4>

H_DBSY# <5>

H_RS#[0..2]

R383

100_0603_1 %

H_RS#[0..2] <5>

12

1U_0402_6.3V4Z

+CPU_CORE

12

R35220_0402_5%

+CPU_CORE+CPU_CORE

R392

150_0402_1 %

1.Place R385 and R376 within 0.5" of U77 pin K21 J21 J17

2.Place C423 C456 C424 C457 in order from U77 to divider

3.+HVREF 10mil trace, 20mil space.

100_0603_1 %

1.Place R337 and R338 within 0.5" of U77 pin K28

2.Place R387 and R392 within 0.5" of U77 pin B18

3.+HYSWING, +HXSWING 10mil trace, 20mil space.

12

R387

301_0402_1 %

12

1

C447

0.1U_0402_10V6K

2

+HVREF

1

2

C389

R455

80.6_0402_1%

1

2

1

2

1

C457

@0.1U_0402_10V6K

2

+HCCVREF

1

C390

2

0.1U_0402_10V6K

C593

0.1U_0402_10V6K

C591

0.1U_0402_10V6K

1

2

+CPU_CORE

R335

1

2

1

2

C424

@0.1U_0402_10V6K

12

R334

49.9_0603_1%

12

1U_0402_6.3V4Z

+1.5VS

12

12

R491

51.1_0603_1%

12

R490

40.2_0603_1%

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, IN C. NEIT HER TH IS SHEE T NOR T HE INF ORMATION IT CONTAIN S

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITTEN CON SENT OF COMPAL ELE CTRONICS , INC.

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, In c.

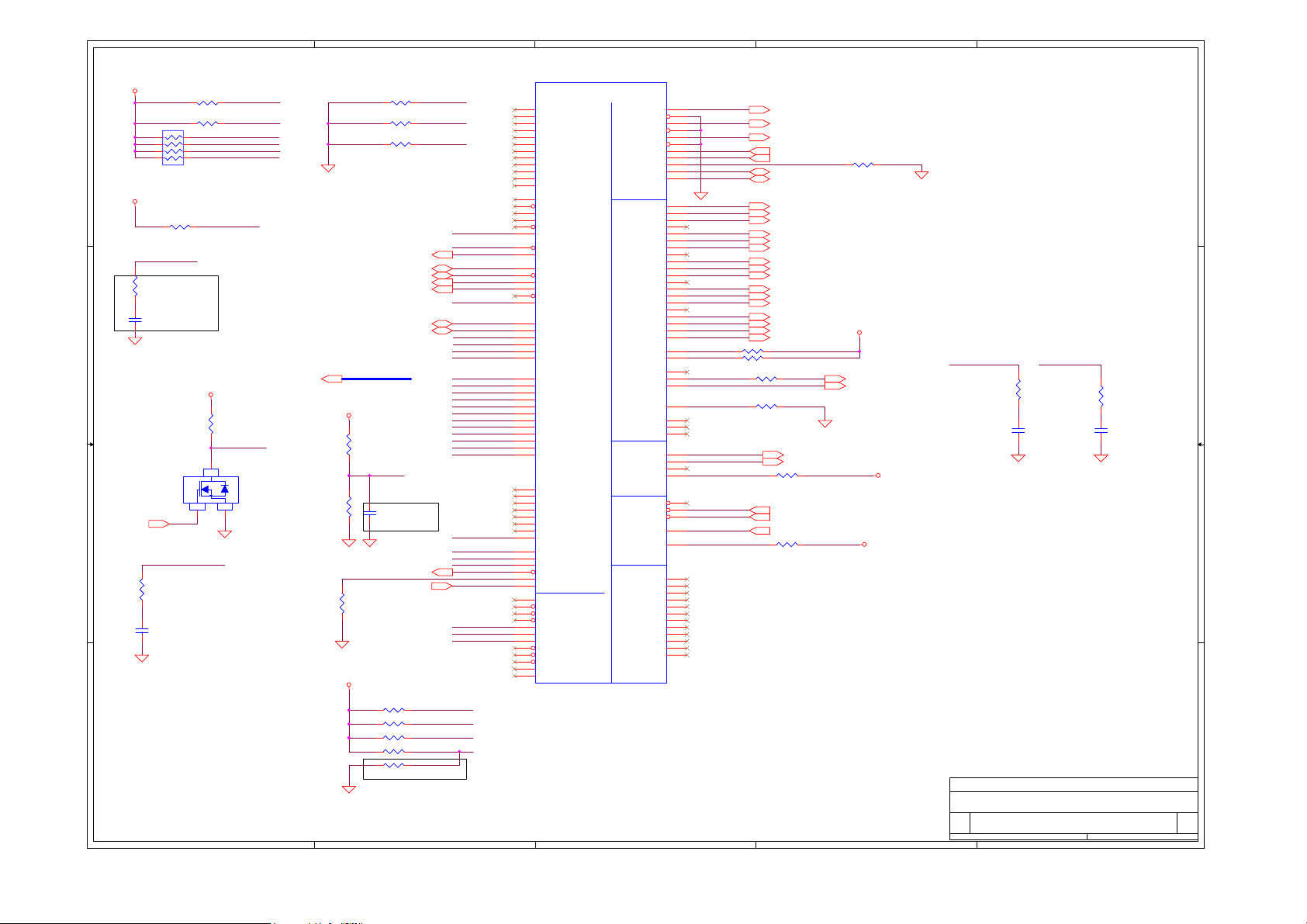

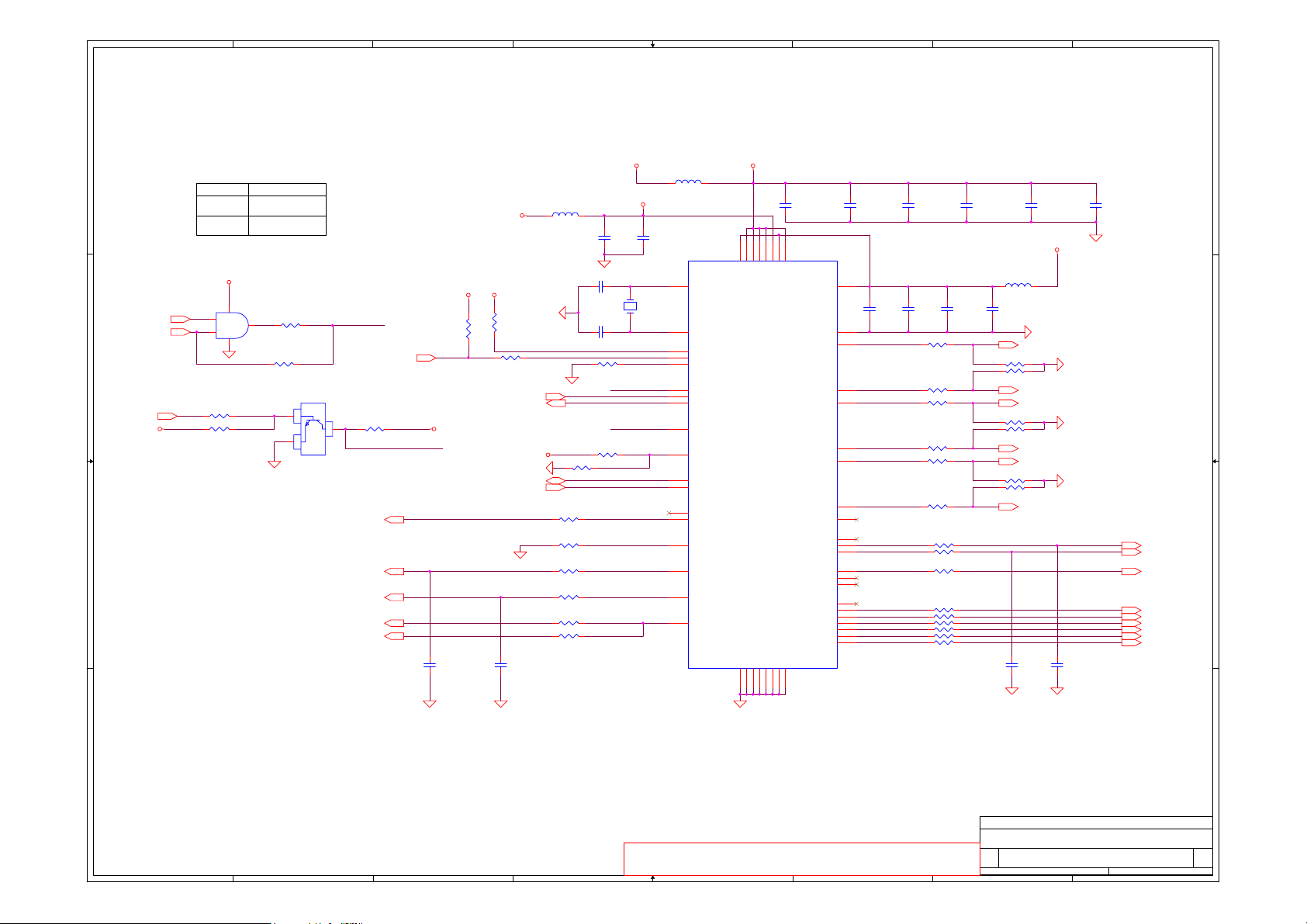

Montara-GT (1/4)

LA-1931

0.2

of

747Monday, June 09, 2003

1

5

4

3

2

1

I2C BUS PULL UP

+1.5VS

RP65

18

27

D D

+1.5VS_DVO

DVOBC_CLKINT

12

C C

RTCCLK<18>

B B

A A

36

45

2.2K_0804_8P4R_5%

1 2

R470 100 K_0402_5%

R465

@22_0402_5%

C578

@10P_0402_50V8K

CLK_MCH_66M

12

R464

@33_0402_5%

1

C577

@10P_0402_25V8K

2

+1.5VS

12

1

5

MI2CCLK

R4282.2K_0402_5%

MI2CDATA

R4272.2K_0402_5%

MDDCCLK

MDDCDATA

MDVICLK

MDVIDATA

DVOBCINTR#

W/O TV-OUT

R465 = 50K;

C578 = 50K.

W/ TV-OUT

De-Pop

R468

1K_0402_5%

D

S

3G2

DVOC_TV_D[0..11]<15>

DPMS

Q34

BSS138_SOT23

1K_0402_1%

R489

40.2_0603_1%

+1.5VS

R471

12

+1.5VS

R477100K_0402_5%

R451100K_0402_5%

R4481K_0402_5%

DVOBC_CLKINT<15>

TV_CLK<15>

TV_CLK#<15>

TV_HSYNC<15>

TV_VSYNC<15>

MI2CCLK<15>

MI2CDATA<15>

DVOC_TV_D[0..11]

R486

1K_0402_1%

+GVREF

Close to Ball F1

C601

0.1U_0402_16V4Z

AGP_BUSY#<18>

CLK_MCH_66M<14>

1 2

R484 @1K_0402_5%

1 2

R496 @1K_0402_5%

1 2

R495 @1K_0402_5%

1 2

R497 @1K_0402_5%

1 2

R533 1K_0402_5%

DVOB_FLDSTL

12

DVOC_FLDSTL

12

ADDID7

12

DVODETECT

4

DVOB_FLDSTL

DVOBCINTR#

DVOBC_CLKINT

DVOC_FLDSTL

MI2CCLK

MI2CDATA

MDVICLK

MDVIDATA

MDDCCLK

MDDCDATA

DVOC_TV_D0

DVOC_TV_D1

DVOC_TV_D2

DVOC_TV_D3

DVOC_TV_D4

DVOC_TV_D5

DVOC_TV_D6

DVOC_TV_D7

DVOC_TV_D8

DVOC_TV_D9

DVOC_TV_D10

DVOC_TV_D11

ADDID7

DVODETECT

DPMS

+GVREF

CLK_MCH_66M

GST2

GST1

GST0

GST2

GST1

GST0

W/O TV-OUT

De-Pop

W/ TV-OUT

Pop

U26B

Montara-GT

R3

DVOBD0/GAD3

R5

DVOBD1/GAD2

R6

DVOBD2/GAD5

R4

DVOBD3/GAD4

P6

DVOBD4/GAD7

P5

DVOBD5/GAD6

N5

DVOBD6/GAD8

P2

DVOBD7/GCBE0#

N2

DVOBD8/GAD10

N3

DVOBD9/GAD9

M1

DVOBD10/GAD12

M5

DVOBD11/GAD11

P3

DVOBCLK/GADSTB0

P4

DVOBCLK#/GADSTB0#

T6

DVOBHSYNC/GAD0

T5

DVOBVSYNC/GAD1

L2

DVOBBLANK#/GCBE1#

M2

DVOBFLDSTL/GAD14

G2

DVOBCINTR#/GAD30

M3

DVOBCCLKINT/GAD13

J3

DVOCCLK/GADSTB1

J2

DVOCCLK#/GADSTB1#

K6

DVOCHSYNC/GAD17

L5

DVOCVSYNC/GAD16

L3

DVOCBLANK#/GAD18

H5

DVOCFLDSTL/GAD31

K7

MI2CCLK/GIRDY#

N6

MI2CDATA/GDEVS EL#

N7

MDVICLK/GTRDY#

M6

MDVIDATA/GFRAME#

P7

MDDCCLK/GSTOP#

T7

MDDCDATA/GAD15

K5

DVOCD0/GAD19

K1

DVOCD1/GAD20

K3

DVOCD2/GAD21

K2

DVOCD3/GAD22

J6

DVOCD4/GAD23

J5

DVOCD5/GCBE3#

H2

DVOCD6/GAD25

H1

DVOCD7/GAD24

H3

DVOCD8/GAD27

H4

DVOCD9/GAD26

H6

DVOCD10/GAD29

G3

DVOCD11/GAD28

E5

ADDID0/GSBA0

F5

ADDID1/GSBA1

E3

ADDID2/GSBA2

E2

ADDID3/GSBA3

G5

ADDID4/GSBA4

F4

ADDID5/GSBA5

G6

ADDID6/GSBA6

F6

ADDID7/GSBA7

L7

DVODETECT/GPAR

D5

DPMS/GPIPE#

F1

GVREF

F7

AGPBUSY#

D1

DVO_GRCOMP

Y3

GCLKIN

F2

GSBSTB

F3

GSBSTB#

B2

GGNT#

B3

GREQ#

C2

GST2

C3

GST1

C4

GST0

D2

GWBF#

D3

GRBF#

L4

GCBE#2

D7

RSVD1

AA5

RSVD2

RG82G435 0MA1_uFCBGA732_MONTARA-GT

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

DVO

BLUE#

GREEN

GREEN#

HSYNC

VSYNC

DAC

REFSET

DDCACLK

DDCADATA

IYAM0

IYAM1

IYAM2

IYAM3

IYBM0

IYBM1

IYBM2

IYBM3

LVDS

ICLKAM

ICLKAP

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

RSVD3

RSVD4

RSVD5

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

CLKS

DPWR#

DPSLP#

RSTIN#

PWROK

MISCNC

EXTTS0

BLUE

RED

RED#

IYAP0

IYAP1

IYAP2

IYAP3

IYBP0

IYBP1

IYBP2

IYBP3

LIBG

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

3

C9

D9

C8

D8

A7

A8

H10

J9

E8

B6

G9

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

R483 2.2K_0402_5%

B4

R476 2.2K_0402_5%

C5

G8

PANEL_BKEN

F8

A5

A10

D12

F12

B12

CLK_MCH_DISPLAY

B7

B17

H9

LCLKCTLB

C6

AA22

H_DPSLP#

Y23

AD28

J11

D6

B1

AH1

A2

AJ2

A28

AJ28

A29

B29

AH29

AJ29

AA9

AJ4

INTCRT_B <16>

INTCRT_G <16>

INTCRT_R <16>

INTCRT_HSYNC <16>

INTCRT_VSYNC <16>

INTDDCCK <16>

INTDDCDA <16>

LCD_A0- <16>

LCD_A1- <16>

LCD_A2- <16>

LCD_A0+ <16>

LCD_A1+ <16>

LCD_A2+ <16>

LCD_B0- <16>

LCD_B1- <16>

LCD_B2- <16>

LCD_B0+ <16>

LCD_B1+ <16>

LCD_B2+ <16>

LCD_ACLK- <16>

LCD_ACLK+ <16>

LCD_BCLK- <16>

1 2

1 2

R485 0_0402_5%

R444 1.5K_0603_1%

LCD_BCLK+ <16>

1 2

1 2

CLK_MCH_DISPLAY <14>

CLK_VCH <14>

1 2

R456 1K_0402_5%

H_DPSLP# <5,17>

PCIRST# <15,17,20,21,22,23,25,26,31,32>

SYS_PWROK <18,35>

1 2

R466 10K_0603_1%

R450

127_0603_1%

1 2

+3VS

ENBKL <32>

ENVDD <16>

+3VS

LCLKCTLB H:1.2V

PSB Voltage Select

+3VS

Title

Size Document Number Rev

2

Date: Sheet

CLK_MCH_DISPLAY

R443

@33_0402_5%

C552

@10P_0402_25V8K

LA-1931

CLK_VCH

12

1

2

Compal Electronics, In c.

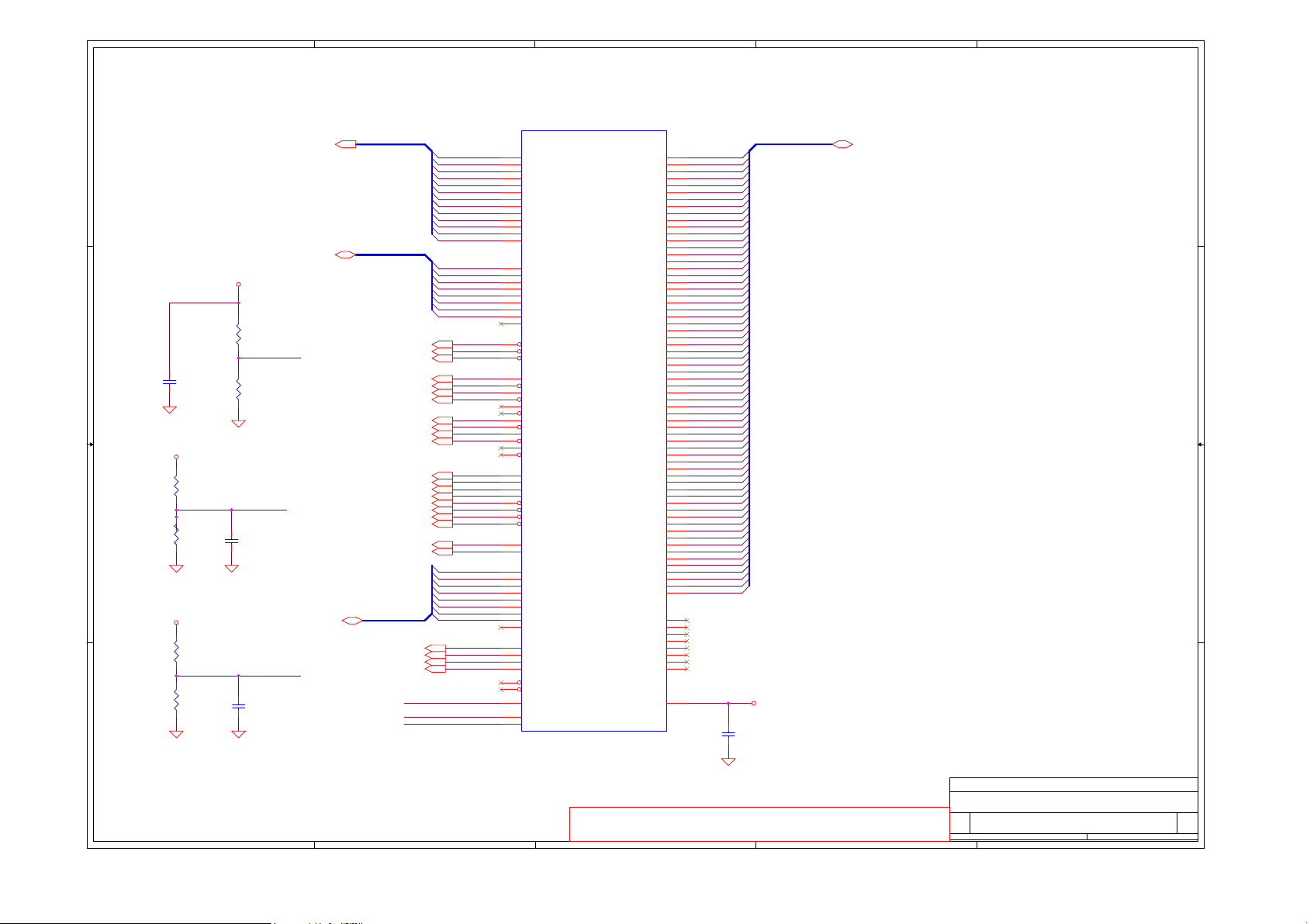

Montara-GT (2/4)

1

12

R405

@33_0402_5%

1

C470

@10P_0402_25V8K

2

847Monday, June 09, 2003

0.2

of

5

4

3

2

1

D D

DDR_SDQS[0..7]<11>

+2.5V

12

R487

R366

R365

R395

R396

60.4_0603_1%

1

C598

0.1U_0402_10V6K

2

+2.5V

12

12

+2.5V

12

12

+SMRCOMP

12

R488

60.4_0603_1%

+SMVSWINGL

1

C459

0.1U_0402_10V6K

2

+SMVSWINGH

1

C541

0.1U_0402_10V6K

2

DDR_SDM[0..7]<11>

C C

604_0603_1 %

150_0603_1 %

B B

150_0603_1 %

604_0603_1 %

A A

DDR_SMA[0..12]

DDR_SDQS[0..7]

DDR_SWE#<11>

DDR_SRAS#<11>

DDR_SCAS#<11>

DDR_CLK0<11>

DDR_CLK0#<11>

DDR_CLK1<11>

DDR_CLK1#<11>

DDR_CLK3<12>

DDR_CLK3#<12>

DDR_CLK4<12>

DDR_CLK4#<12>

DDR_CKE0<11>

DDR_CKE1<11>

DDR_CKE2<12>

DDR_CKE3<12>

DDR_SCS#0<11>

DDR_SCS#1<11>

DDR_SCS#2<12>

DDR_SCS#3<12>

DDR_SBS0<11>

DDR_SBS1<11>

DDR_SDM[0..7]

DDR_SMAB1<12>

DDR_SMAB2<12>

DDR_SMAB4<12>

DDR_SMAB5<12>

Need place Via as closed as pin.

+SMRCOMP

+SMVSWINGL

+SMVSWINGH

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

DDR_SDM0

DDR_SDM1

DDR_SDM2

DDR_SDM3

DDR_SDM4

DDR_SDM5

DDR_SDM6

DDR_SDM7

DDR_SMAB1

DDR_SMAB2

DDR_SMAB4

DDR_SMAB5

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SWE#

DDR_SRAS#

DDR_SCAS#

DDR_CLK0

DDR_CLK0#

DDR_CLK1

DDR_CLK1#

DDR_CLK3

DDR_CLK3#

DDR_CLK4

DDR_CLK4#

DDR_CKE0

DDR_CKE1

DDR_CKE2

DDR_CKE3

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

DDR_SBS0

DDR_SBS1

U26C

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AB5

AG2

AH5

AH8

AE12

AH17

AE21

AH24

AH27

AD15

AD25

AC21

AC24

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AC7

AB7

AC9

AC10

AD23

AD26

AC22

AC25

AD22

AD20

AE5

AE6

AE9

AH12

AD19

AD21

AD24

AH28

AH15

AD16

AC12

AF11

AD10

AC15

AC16

AB1

AJ22

AJ19

Montara-GT

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SDQS0

MEMORY

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SWE#

SRAS#

SCAS#

SCK0

SCK0#

SCK1

SCK1#

SCK2

SCK2#

SCK3

SCK3#

SCK4

SCK4#

SCK5

SCK5#

SCKE0

SCKE1

SCKE2

SCKE3

SCS#0

SCS#1

SCS#2

SCS#3

SBA0

SBA1

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

SDM8

SMAB1

SMAB2

SMAB4

SMAB5

RCVENOUT#

RCVENIN#

SMRCOMP

SMVSWINGL

SMVSWINGH

RG82G435 0MA1_uFCBGA732_MONTARA-GT

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

SMVREF0

DDR_SDQ0

AF2

DDR_SDQ1

AE3

DDR_SDQ2

AF4

DDR_SDQ3

AH2

DDR_SDQ4

AD3

DDR_SDQ5

AE2

DDR_SDQ6

AG4

DDR_SDQ7

AH3

DDR_SDQ8

AD6

DDR_SDQ9

AG5

DDR_SDQ10

AG7

DDR_SDQ11

AE8

DDR_SDQ12

AF5

DDR_SDQ13

AH4

DDR_SDQ14

AF7

DDR_SDQ15

AH6

DDR_SDQ16

AF8

DDR_SDQ17

AG8

DDR_SDQ18

AH9

DDR_SDQ19

AG10

DDR_SDQ20

AH7

DDR_SDQ21

AD9

DDR_SDQ22

AF10

DDR_SDQ23

AE11

DDR_SDQ24

AH10

DDR_SDQ25

AH11

DDR_SDQ26

AG13

DDR_SDQ27

AF14

DDR_SDQ28

AG11

DDR_SDQ29

AD12

DDR_SDQ30

AF13

DDR_SDQ31

AH13

DDR_SDQ32

AH16

DDR_SDQ33

AG17

DDR_SDQ34

AF19

DDR_SDQ35

AE20

DDR_SDQ36

AD18

DDR_SDQ37

AE18

DDR_SDQ38

AH18

DDR_SDQ39

AG19

DDR_SDQ40

AH20

DDR_SDQ41

AG20

DDR_SDQ42

AF22

DDR_SDQ43

AH22

DDR_SDQ44

AF20

DDR_SDQ45

AH19

DDR_SDQ46

AH21

DDR_SDQ47

AG22

DDR_SDQ48

AE23

DDR_SDQ49

AH23

DDR_SDQ50

AE24

DDR_SDQ51

AH25

DDR_SDQ52

AG23

DDR_SDQ53

AF23

DDR_SDQ54

AF25

DDR_SDQ55

AG25

DDR_SDQ56

AH26

DDR_SDQ57

AE26

DDR_SDQ58

AG28

DDR_SDQ59

AF28

DDR_SDQ60

AG26

DDR_SDQ61

AF26

DDR_SDQ62

AE27

DDR_SDQ63

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

SMVREF0

AJ24

C408

0.1U_0402_10V6K

1

2

DDR_SDQ[0..63]

+SDREF

DDR_SDQ[0..63] <11>DDR_SMA[0..12]<11,12>

TOPOLOGY 1 FOR DDR

SMAA[12:6,3,0], SBA[1:0], SRAS#, SCAS#, SWE#

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, IN C. NEIT HER TH IS SHEE T NOR T HE INF ORMATION IT CONTAIN S

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WR ITTEN CON SENT OF COMPAL ELE CTRONICS , INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, In c.

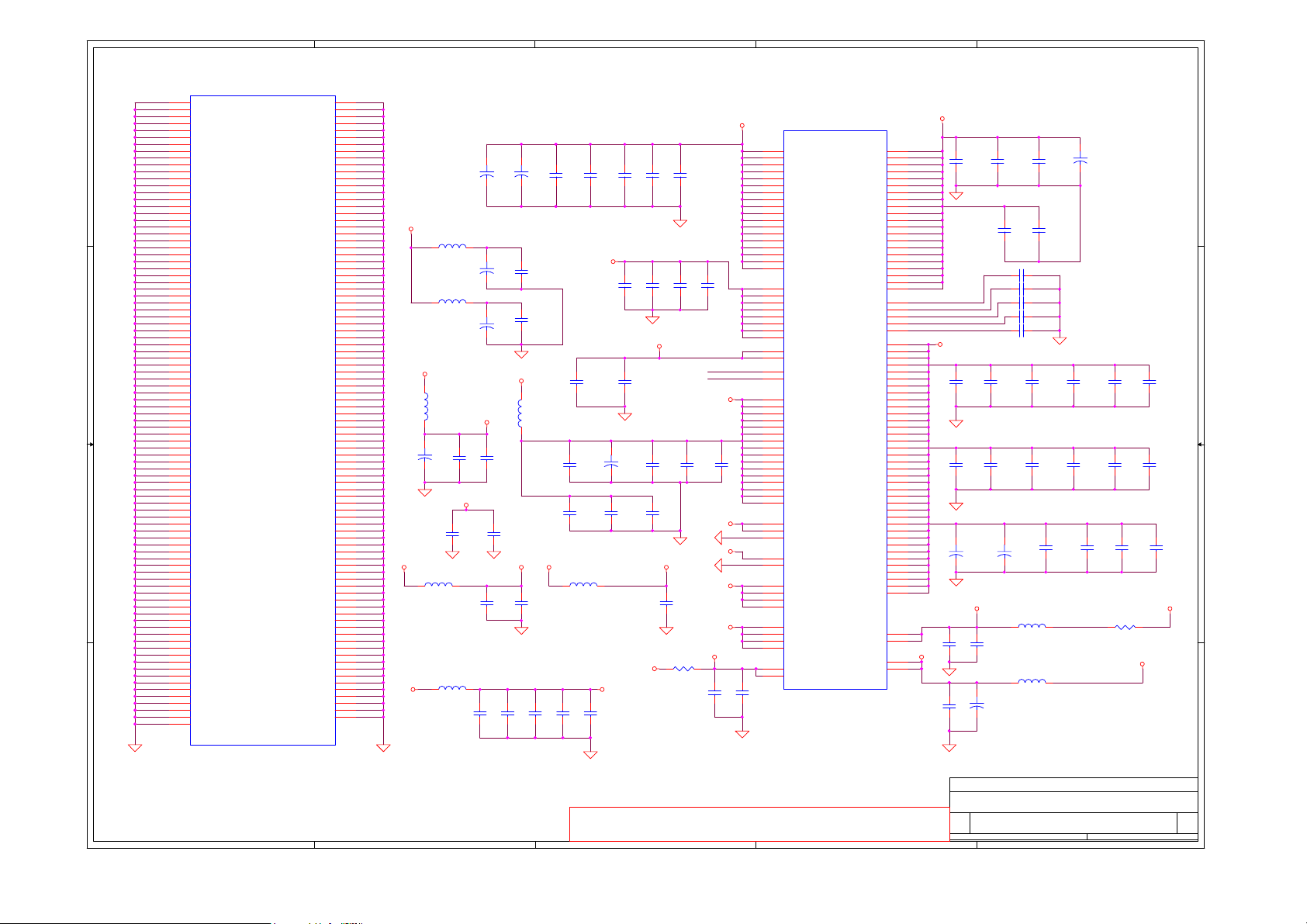

Montara-GT (3/4)

LA-1931

0.2

of

947Monday, June 09, 2003

1

5

U26D

C1

VSS0

G1

VSS1

L1

VSS2

U1

VSS3

AA1

VSS4

AE1

VSS5

R2

VSS6

D D

C C

B B

A A

AG3

VSS7

AJ3

VSS8

D4

VSS9

G4

VSS10

K4

VSS11

N4

VSS12

T4

VSS13

W4

VSS14

AA4

VSS15

AC4

VSS16

AE4

VSS17

B5

VSS18

U5

VSS19

Y5

VSS20

Y6

VSS21

AG6

VSS22

C7

VSS23

E7

VSS24

G7

VSS25

J7

VSS26

M7

VSS27

R7

VSS28

AA7

VSS29

AE7

VSS30

AJ7

VSS31

H8

VSS32

K8

VSS33

P8

VSS34

T8

VSS35

V8

VSS36

Y8

VSS37

AC8

VSS38

E9

VSS39

L9

VSS40

N9

VSS41

R9

VSS42

U9

VSS43

W9

VSS44

AB9

VSS45

AG9

VSS46

C10

VSS47

J10

VSS48

AA10

VSS49

AE10

VSS50

D11

VSS51

F11

VSS52

H11

VSS53

AB11

VSS54

AC11

VSS55

AJ11

VSS56

J12

VSS57

AA12

VSS58

AG12

VSS59

A13

VSS60

D13

VSS61

F13

VSS62

H13

VSS63

N13

VSS64

R13

VSS65

U13

VSS66

AB13

VSS67

AE13

VSS68

J14

VSS69

P14

VSS70

T14

VSS71

AA14

VSS72

AC14

VSS73

D15

VSS74

H15

VSS75

N15

VSS76

R15

VSS77

U15

VSS78

AB15

VSS79

AG15

VSS80

F16

VSS81

J16

VSS82

P16

VSS83

T16

VSS84

AA16

VSS85

AE16

VSS86

A17

VSS87

D17

VSS88

H17

VSS89

N17

VSS90

RG82G435 0MA1_uFCBGA732_MONTARA-GT

Montara-GT

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

R17

U17

AB17

AC17

F18

J18

AA18

AG18

A19

D19

H19

AB19

AE19

F20

J20

AA20

AC20

A21

D21

H21

M21

P21

T21

V21

Y21

AA21

AB21

AG21

B24

F22

J22

L22

N22

R22

U22

W22

AE22

A23

D23

AA23

AC23

AJ23

F24

H24

K24

M24

P24

T24

V24

AA24

AG24

A25

D25

AA25

AE25

G26

J26

L26

N26

R26

U26

W26

AB26

A27

F27

AC27

AG27

AJ27

AC28

AE28

C29

E29

G29

J29

L29

N29

U29

W29

AA29

AJ10

AJ12

AJ18

AJ20

C22

D28

E28

L6

T9

AJ26

AJ1

4

+1.5VS

L37

KC FBM-L11-201209-221LMAT_0805

1 2

CLOSE TO PIN

C525

220U_D2_4VM

1 2

L28

KC FBM-L11-201209-221LMAT_0805

+1.5VS

C501

@220U_D2_4VM

47U_1210_6.3V4Z

1 2

FLM1608081R8K_0603

47U_1210_6.3V4Z

220U_D2_4VM

12

L35

FLM1608081R8K_0603

1

0.01U_04 02_25V7Z

1

+

2

2

C535

0.1U_0402_10V6K

+1.5VS_DLVDS

1

C468

2

L32

C512

0.1U_0402_10V6K

L33

1 2

FLM1608081R8K_0603

C465

C400

1

150U_D2_6.3VM

+

2

C358

150U_D2_6.3VM

+VCCADPLLA

1

+

0.1U_0402_10V6K

2

+VCCADPLLB

1

+

C478

2

C432

0.1U_0402_10V6K

+1.5VS_DAC

C534

1

2

1

C491

22U_1210_6.3V6M

2

1

0.01U_04 02_25V7Z

2

C484

22U_1206_16V4Z_V1

1

1

2

2

0.1U_0402_10V6K

1

+

2

C461

10U_1206_6.3V7K

1

C562

2

1

2

0.1U_0402_10V6K

+1.5VS

L31

BLM21A601SPT_0805

1 2

C579

0.1U_0402_10V6K

C580

0.1U_0402_10V6K

1

C521

2

1

2

C505

CLOSE TO VCC

C442

0.1U_0402_10V6K

1

1

2

2

+1.5VS

C480

10U_1206_6.3V7K

C599

1

0.1U_0402_10V6K

2

1

C618

150U_D 2_6.3VM

2

1

C546

2

0.1U_0402_10V6K

L29

1 2

FLM1608081R8K_0603

C520

0.1U_0402_10V6K

1

1

2

2

C530

0.1U_0402_10V6K

C500

0.1U_0402_10V6K

+2.5V_TXLVDS+2.5V

3

C479

0.1U_0402_10V6K

1

1

2

2

C540

0.1U_0402_10V6K

CLOSE TO VCCHL

C561

0.1U_0402_10V6K

1

1

2

2

+1.5VS

1

C369

2

1

1

+

2

2

C513

10U_1206_6.3V7K

1

1

C545

2

2

0.1U_0402_10V6K

+1.5VS_DLVDS+1.5VS+1.5VS_ALVDS+1.5VS

+3VS

10U_1206_6.3V7K

1

C428

2

0.1U_0402_10V6K

C572

0.1U_0402_10V6K

1

2

C600

0.1U_0402_10V6K

+1.5VS_DVO

C544

1

0.1U_0402_10V6K

2

0.1U_0402_10V6K

+1.5VS_DAC

+1.5VS_ALVDS

+1.5VS_DLVDS

1

2

+2.5V_TXLVDS

R493

0_0603_5%

1 2

C609

+1.5VS

1

2

+VCCADPLLA

+VCCADPLLB

1

2

C543

+VCC_GPIO

1

0.1U_0402_10V6K

2

U26E

Montara-GT

J15

VCC0

P13

VCC1

T13

VCC2

N14

VCC3

R14

VCC4

U14

VCC5

P15

VCC6

T15

VCC7

AA15

VCC8

N16

VCC9

R16

VCC10

U16

VCC11

P17

VCC12

T17

VCC13

AA17

VCC14

AA19

VCC15

W21

VCC16

H14

VCC17

V1

VCCHL0

Y1

VCCHL1

W5

VCCHL2

U6

VCCHL3

U8

VCCHL4

W8

VCCHL5

V7

VCCHL6

V9

VCCHL7

D29

VCCAHPLL

Y2

VCCAGPLL

A6

VCCADPLLA

B16

VCCADPLLB

E1

VCCDVO_0

J1

VCCDVO_1

N1

VCCDVO_2

E4

VCCDVO_3

J4

VCCDVO_4

M4

VCCDVO_5

E6

VCCDVO_6

H7

VCCDVO_7

J8

VCCDVO_8

L8

VCCDVO_9

M8

VCCDVO_10

N8

VCCDVO_11

R8

VCCDVO_12

K9

VCCDVO_13

M9

VCCDVO_14

P9

VCCDVO_15

A9

VCCADAC0

B9

VCCADAC1

B8

VSSADAC

A11

VCCALVDS

B11

VSSALVDS

G13

VCCDLVDS0

B14

VCCDLVDS1

J13

VCCDLVDS2

B15

VCCDLVDS3

F9

VCCTXLVDS0

B10

VCCTXLVDS1

D10

VCCTXLVDS2

A12

VCCTXLVDS3

A3

VCCGPIO_0

A4

VCCGPIO_1

1

RG82G435 0MA1_uFCBGA732_MONTARA-GT

C585

2

POWER

2

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

VTTLF20

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCQSM0

VCCQSM1

VCCASM0

VCCASM1

G15

H16

H18

J19

H20

L21

N21

R21

U21

H22

M22

P22

T22

V22

Y29

K29

F29

AB29

A26

A20

A18

A22

A24

H29

M29

V29

AC1

AG1

AB3

AF3

Y4

AJ5

AA6

AB6

AF6

Y7

AA8

AB8

Y9

AF9

AJ9

AB10

AA11

AB12

AF12

AA13

AJ13

AB14

AF15

AB16

AJ17

AB18

AF18

AB20

AF21

AJ21

AB22

AF24

AJ25

AF27

AC29

AF29

AG29

0.1U_0402_10V6K

AJ6

AJ8

VCC_ASM

AD1

AF1

C597

0.1U_0402_10V6K

+CPU_CORE

1

2

C420

0.1U_0402_10V6K

+2.5V

C502

0.1U_0402_10V6K

1

2

C394

0.1U_0402_10V6K

C529

0.1U_0402_10V6K

1

2

C455

0.1U_0402_10V6K

C771 & C772 change to 100u

next Reversion

1

C506

+

150U_D2_4VM

2

C547

1

1

2

2

1

1

+

2

2

C419

0.1U_0402_10V6K

0.1U_0402_10V6K

C417 0.1U_0402_10V6K

C406 0.1U_0402_10V6K

C380 0.1U_0402_10V6K

C379 0.1U_0402_10V6K

C378 0.1U_0402_10V6K

1

2

1

2

150U_D2_4VM

C560

4.7U_1206_10V7K

C612

100U_D_16VM

1

1

2

2

KC FBM-L11-201209-221LMAT_0805

C429

10U_1206_6.3V7K

0.1U_0402_10V6K

1

1

C368

C443

2

2

1 2

1 2

1 2

1 2

1 2

C439

0.1U_0402_10V6K

1

1

2

2

C528

0.1U_0402_10V6K

C477

0.1U_0402_10V6K

1

1

2

1

C587

2

0.1U_0402_10V6K

2

C499

0.1U_0402_10V6K

1

C388

+

0.1U_0402_10V6K

2

L39

1 2

L40

1 2

KC FB M-L11-201209-221LMAT_0805

1

1

+

C357

150U_D2_4VM

2

0.1U_0402_10V6K

1

C469

2

0.1U_0402_10V6K

1

C381

2

0.1U_0402_10V6K

1

C519

2

0_0805_5%

1 2

1

C403

2

0.1U_0402_10V6K

1

C426

2

0.1U_0402_10V6K

1

C558

2

0.1U_0402_10V6K

R429

+1.5VS

1

C542

2

+2.5V+2.5V_QSM

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC . NEITHER THIS SHEE T NOR THE IN FORMATION IT C ONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN C ONSENT OF COMPAL EL ECTRONICS , INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, In c.

Montara-GT(4/4)

LA-1931

0.2

of

10 47Monday, June 09, 2003

1

A

RP100 10_0404_4P2R_5%

DDR_SDQ0 DDR_DQ0

DDR_SDQ1 DDR_DQ1

DDR_SDQ4 DDR_DQ4

DDR_SDQ5

DDR_SDQ2 DDR_DQ2

1 1

DDR_SDQ6 DDR_DQ6

DDR_SDQ8 DDR_DQ8

DDR_SDQ13 DDR_DQ13

DDR_SDQ12

DDR_SDQ9 DDR_DQ9

DDR_SDQ15 DDR_DQ15

DDR_SDQ14 DDR_DQ14

DDR_SDQ10 DDR_DQ10

DDR_SDQ11 DDR_DQ11

DDR_SDQ18 DDR_DQ18

DDR_SDQ16 DDR_DQ16

2 2

DDR_SDQ20 DDR_DQ20

DDR_SDQ21 DDR_DQ21

DDR_SDQ23 DDR_DQ23

DDR_SDQ25 DDR_DQ25

DDR_SDQ31 DDR_DQ31

DDR_SDQ24 DDR_DQ24

DDR_SDQ28 DDR_DQ28

DDR_SDQ60 DDR_DQ60

DDR_SDQ61

DDR_SDQ57 DDR_DQ57

DDR_SDQ56 DDR_DQ56

3 3

4 4

1 4

2 3

RP101 10_0404_4P2R_5%

1 4

2 3

RP97 10_0404_4P2R_5%

1 4

2 3

RP95 10_0404_4P2R_5%

1 4

2 3

RP94 10_0404_4P2R_5%

1 4

2 3

RP92 10_0404_4P2R_5%

1 4

2 3

RP88 10_0404_4P2R_5%

1 4

2 3

RP86 10_0404_4P2R_5%

1 4

2 3

RP80 10_0404_4P2R_5%

1 4

2 3

RP84 10_0404_4P2R_5%

1 4

2 3

RP75 10_0404_4P2R_5%

1 4

2 3

RP82 10_0404_4P2R_5%

1 4

2 3

RP73 10_0404_4P2R_5%

1 4

2 3

RP78 10_0404_4P2R_5%

1 4

2 3

RP24 10_0404_4P2R_5%

1 4

2 3

RP26 10_0404_4P2R_5%

1 4

2 3

DDR_SDQS0

R507 10_0402_5%

DDR_SDQS1

R500 10_0402_5%

DDR_SDQS2

R459 10_0402_5%

DDR_SDQS3 DDR_DQS3

R440 10_0402_5%

DDR_SDQS4

R361 10_0402_5%

DDR_SDQS5

R343 10_0402_5%

DDR_SDQS6

R333 10_0402_5%

DDR_SDQS7

R330 10_0402_5%

A

12

12

12

12

12

12

12

12

DDR_DQ5

DDR_DQ3DDR_SDQ3

DDR_DQ7DDR_SDQ7

DDR_DQ12

DDR_DQ17DDR_SDQ17

DDR_DQ19DDR_SDQ19

DDR_DQ22DDR_SDQ22

DDR_DQ61

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

B

RP68 10_0404_4P2R_5%

DDR_SDQ27 DDR_DQ27

DDR_SDQ29 DDR_DQ29

DDR_SDQ30 DDR_DQ30

DDR_SDQ26 DDR_DQ26

DDR_SDQ37 DDR_DQ37

DDR_SDQ33

DDR_SDQ32

DDR_SDQ36

DDR_SDQ39

DDR_SDQ35

DDR_SDQ38

DDR_SDQ34

DDR_SDQ40 DDR_DQ40

DDR_SDQ44

DDR_SDQ41

DDR_SDQ45

DDR_SDQ43

DDR_SDQ47 DDR_DQ47

DDR_SDQ46 DDR_DQ46

DDR_SDQ42

DDR_SDQ52

DDR_SDQ50 DDR_DQ50

DDR_SDQ48

DDR_SDQ53

DDR_SDQ51

DDR_SDQ54 DDR_DQ54

DDR_SDQ49

DDR_SDQ62 DDR_DQ62

DDR_SDQ63 DDR_DQ63

DDR_SDQ58 DDR_DQ58

DDR_SDQ59 DDR_DQ59

1 4

2 3

RP70 10_0404_4P2R_5%

1 4

2 3

RP56 10_0404_4P2R_5%

1 4

2 3

RP54 10_0404_4P2R_5%

1 4

2 3

RP47 10_0404_4P2R_5%

1 4

2 3

RP49 10_0404_4P2R_5%

1 4

2 3

RP43 10_0404_4P2R_5%

1 4

2 3

RP45 10_0404_4P2R_5%

1 4

2 3

RP38 10_0404_4P2R_5%

1 4

2 3

RP40 10_0404_4P2R_5%

1 4

2 3

RP34 10_0404_4P2R_5%

1 4

2 3

RP36 10_0404_4P2R_5%

1 4

2 3

RP30 10_0404_4P2R_5%

1 4

2 3

RP28 10_0404_4P2R_5%

1 4

2 3

RP21 10_0404_4P2R_5%

1 4

2 3

RP19 10_0404_4P2R_5%

1 4

2 3

DDR_SDM0

R506 10_0402_5%

DDR_SDM1

R498 10_0402_5%

DDR_SDM2 DDR_DM2

R475 10_0402_5%

DDR_SDM3

R449 10_0402_5%

DDR_SDM4 DDR_DM4

R363 10_0402_5%

DDR_SDM5 DDR_DM5

R345 10_0402_5%

DDR_SDM6 DDR_DM6

R332 10_0402_5%

DDR_SDM7

R329 10_0402_5%

DDR_SDQ[0..63]

DDR_SDQS[0..7]

DDR_SDM[0 ..7]

DDR_SMA[1..2]

DDR_SMA[4..5]

DDR_SMA[6..12]

DDR_SMA0

DDR_SMA3

B

DDR_DQ33

DDR_DQ32

DDR_DQ36

DDR_DQ39

DDR_DQ35

DDR_DQ38

DDR_DQ34

DDR_DQ44

DDR_DQ41

DDR_DQ45

DDR_DQ43

DDR_DQ42

DDR_DQ52

DDR_DQ48

DDR_DQ53

DDR_DQ51

DDR_DQ49

DDR_DQ55DDR_SDQ55

DDR_DM0

12

DDR_DM1

12

12

DDR_DM3

12

12

12

12

DDR_DM7

12

DDR_SDQ[0..6 3] <9>

DDR_SDQS[0..7] <9>

DDR_SDM[0..7 ] <9>

DDR_SMA[1..2] <9,12>

DDR_SMA[4..5] <9,12>

DDR_SMA[6..12] <9>

DDR_SMA0 <9>

DDR_SMA3 <9>

C

DDR_CLK0<9>

DDR_CLK0#<9>

DDR_CKE1<9>

DDR_SCS#0<9>

Layout note

Place these resistors

close to DIMM0,

all trace length<500 mil

DDR TOPOLOGY 1 FOR SMAA[0, 3, 6:12], SBA[1, 0], SRAS#, SCAS#, SWE#

C

D

+2.5V

JP21

1

VREF

3

DDR_DQ4

DDR_DQ5

DDR_DQS0

DDR_DQ3

DDR_DQ2

DDR_DQ8

DDR_DQ13

DDR_DQS1

DDR_DQ15

DDR_DQ18

DDR_DQ16

DDR_DQS2

DDR_DQ21

DDR_DQ23

DDR_DQ25

DDR_DQ31

DDR_DQS3

DDR_DQ27

DDR_DQ29

DDR_CKE1

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SBS0

DDR_SWE#

DDR_ SCS#0

DDR_DQ32

DDR_DQ36

DDR_DQS4

DDR_DQ39

DDR_DQ35

DDR_DQ40

DDR_DQ44

DDR_DQS5

DDR_DQ43

DDR_DQ47

DDR_DQ52

DDR_DQ50

DDR_DQ51

DDR_DQ54

DDR_DQ57

DDR_DQ56

DDR_DQS7

DDR_DQ62 DDR_DQ58

DDR_DQ63

SMDATA<12,14,17>

SMCLK<12,14,17>

+3VS

D

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

KLINK_5746-2-111

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC . NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY ORDISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC .

E

2

VREF

4

VSS

6

DQ4

8

DQ5

10

VDD

12

DM0

14

DQ6

16

VSS

18

DQ7

20

DQ12

22

VDD

24

DQ13

26

DM1

28

VSS

30

DQ14

32

DQ15

34

VDD

36

VDD

38

VSS

40

VSS

42

DQ20

44

DQ21

46

VDD

48

DM2

50

DQ22

52

VSS

54

DQ23

56

DQ28

58

VDD

60

DQ29

62

DM3

64

VSS

66

DQ30

68

DQ31

70

VDD

72

CB4

74

CB5

76

VSS

78

DM8

80

CB6

82

VDD

84

CB7

86

DU/RESET#

88

VSS

90

VSS

92

VDD

94

VDD

96

CKE0

98

DU/BA2

100

A11

102

A8

104

VSS

106

A6

108

A4

110

A2

112

A0

114

VDD

116

BA1

118

RAS#

120

CAS#

122

S1#

124

DU

126

VSS

128

DQ36

130

DQ37

132

VDD

134

DM4

136

DQ38

138

VSS

140

DQ39

142

DQ44

144

VDD

146

DQ45

148

DM5

150

VSS

152

DQ46

154

DQ47

156

VDD

158

CK1#

160

CK1

162

VSS

164

DQ52

166

DQ53

168

VDD

170

DM6

172

DQ54

174

VSS

176

DQ55

178

DQ60

180

VDD

182

DQ61

184

DM7

186

VSS

188

DQ62

190

DQ63

192

VDD

194

SA0