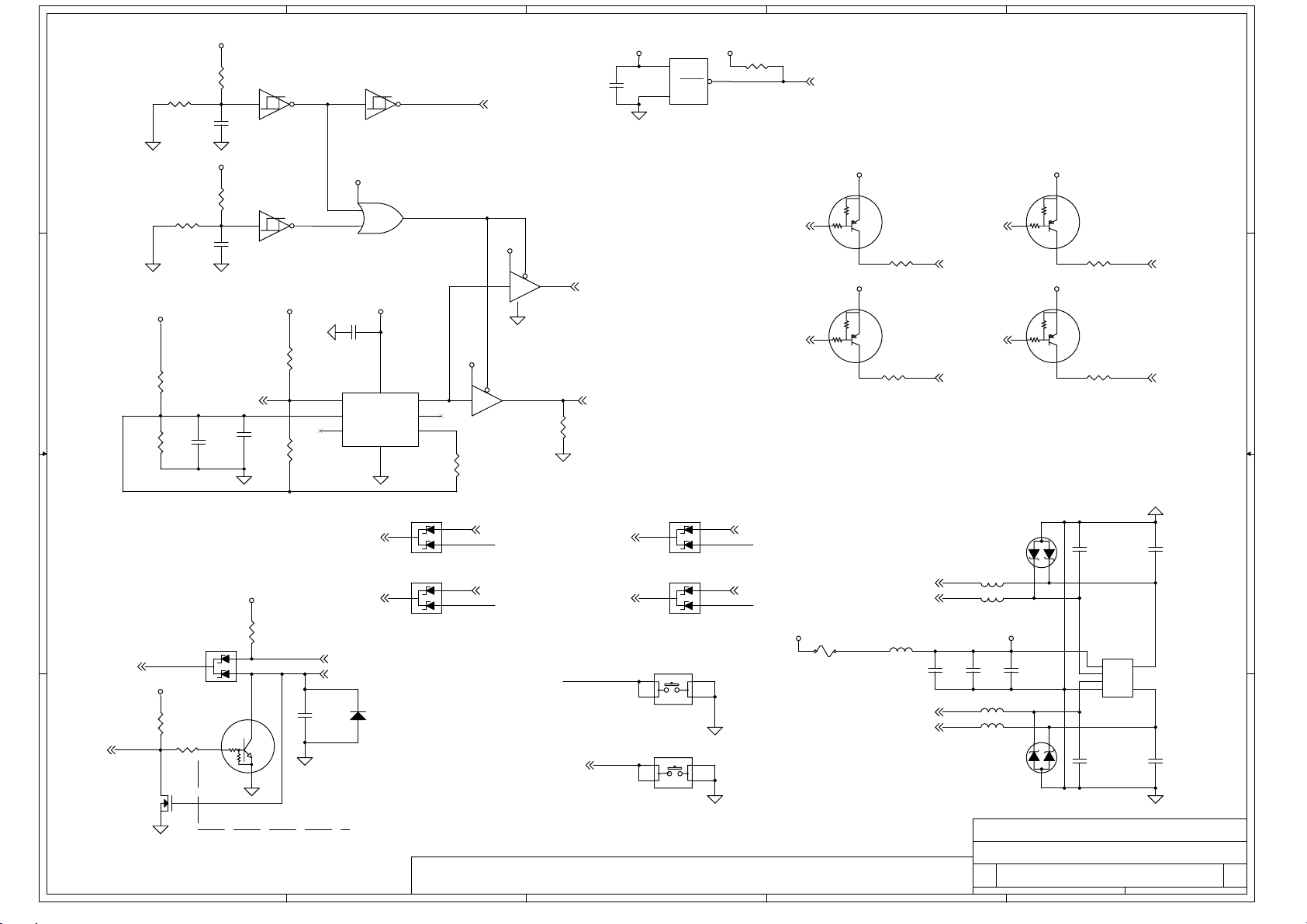

Page 1

A

B

C

D

E

COMPAL CONFIDENTIAL

MODEL NAME : 888J2 LA-971

4 4

REVISION HISTORY

Date: 2000/07/11 REV.: 0.1 Description: A-TEST Release Date: 2000-7-14

3 3

2 2

1 1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

A

B

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

1C

of

237Friday, December 01, 2000

E

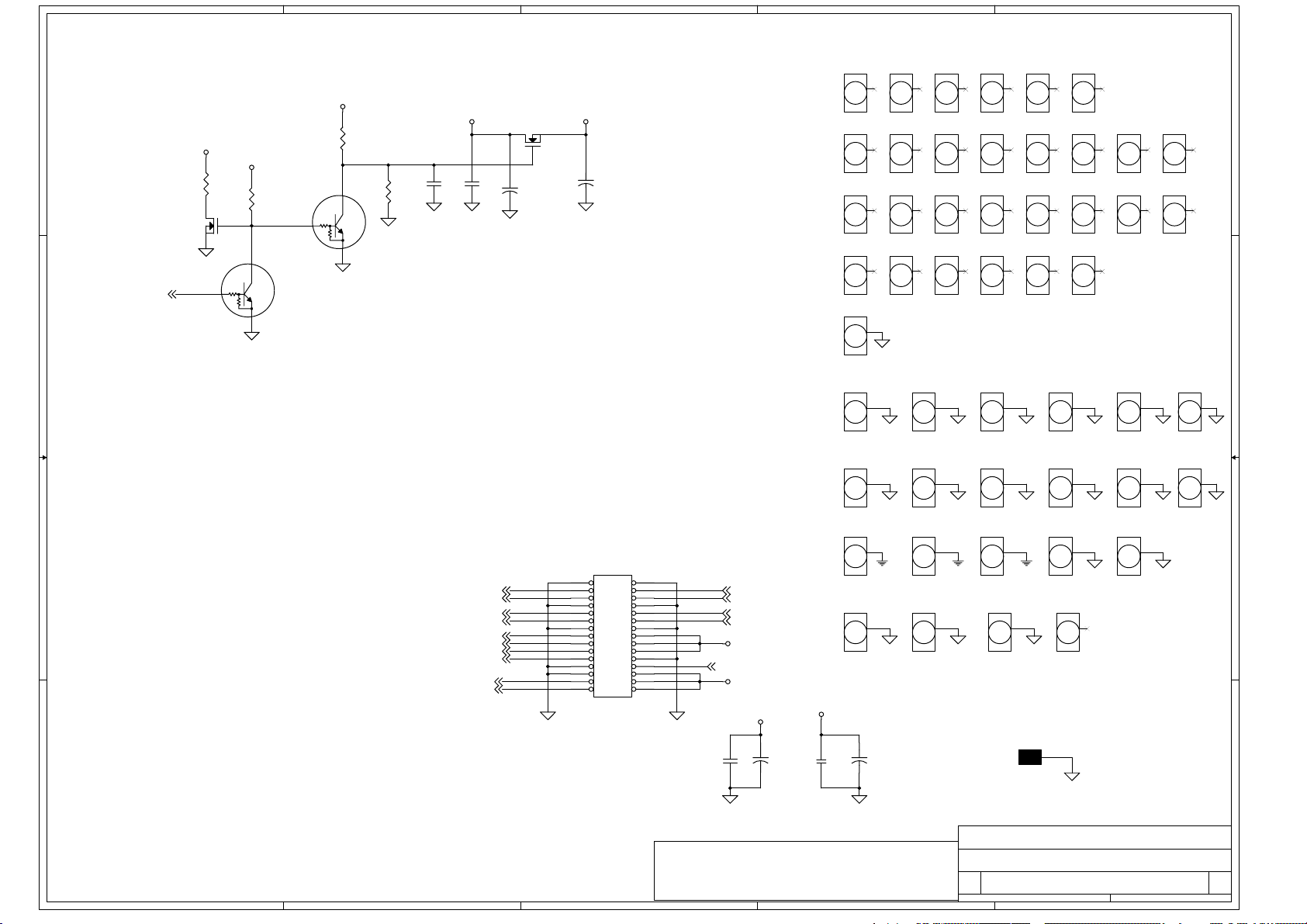

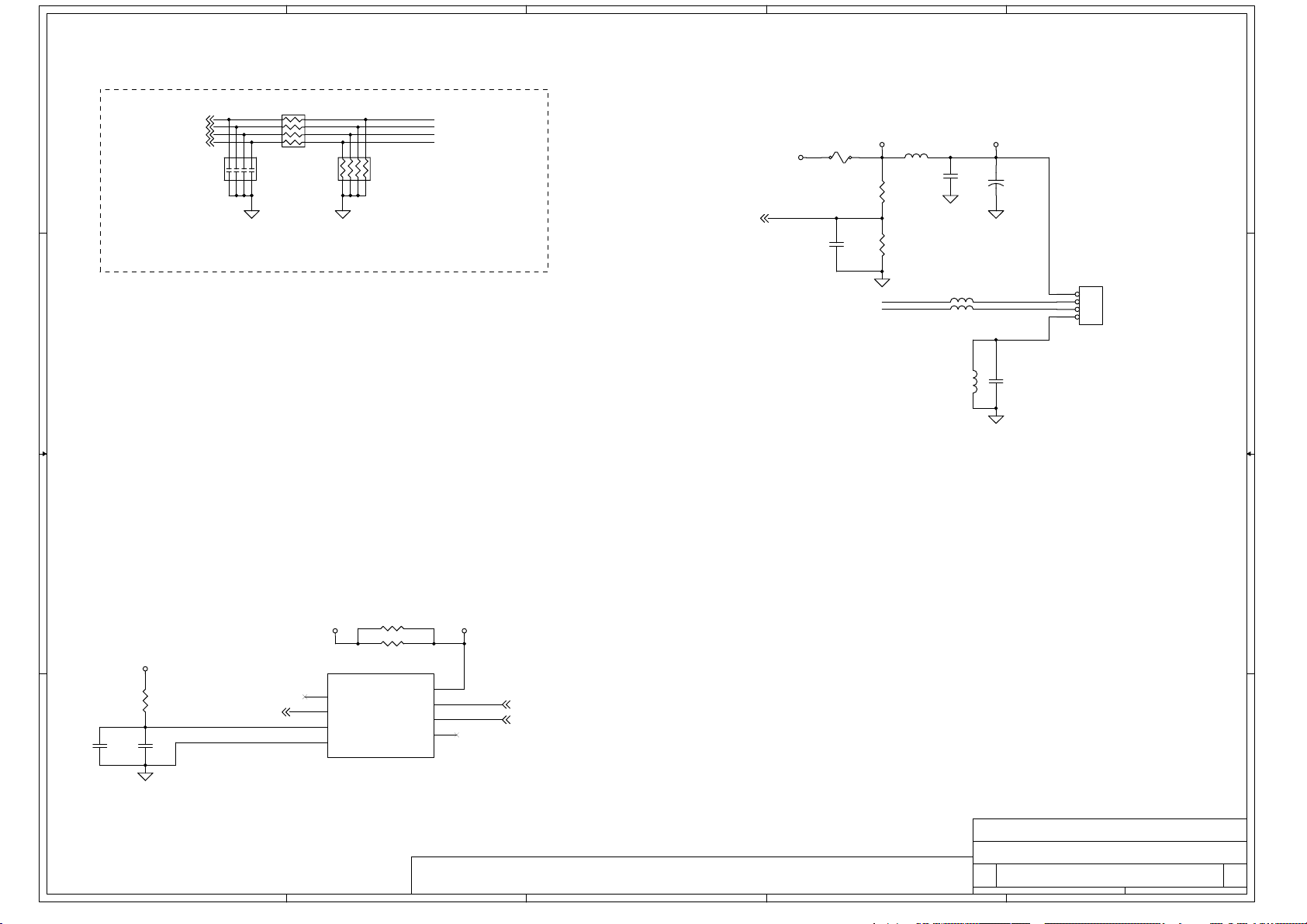

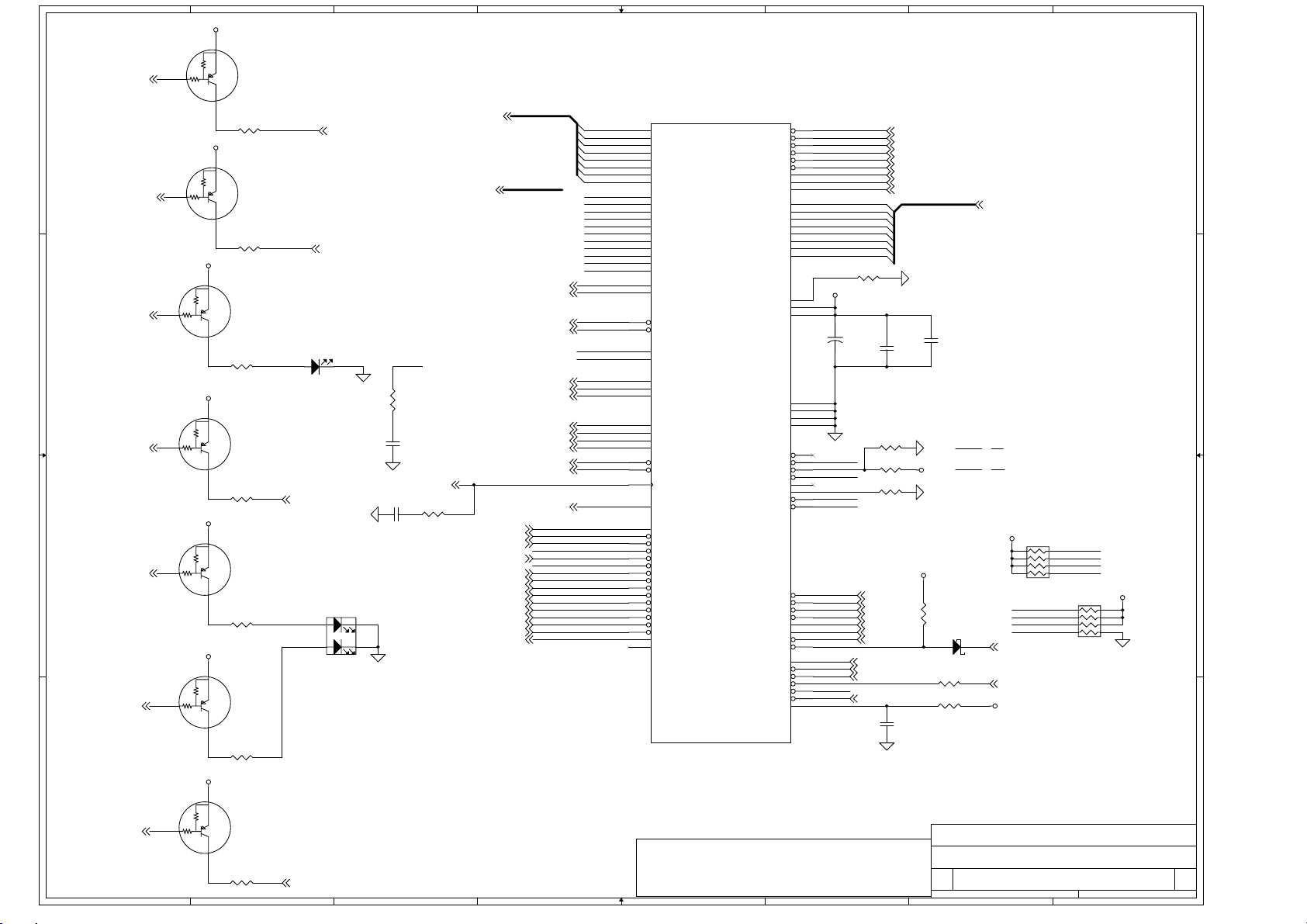

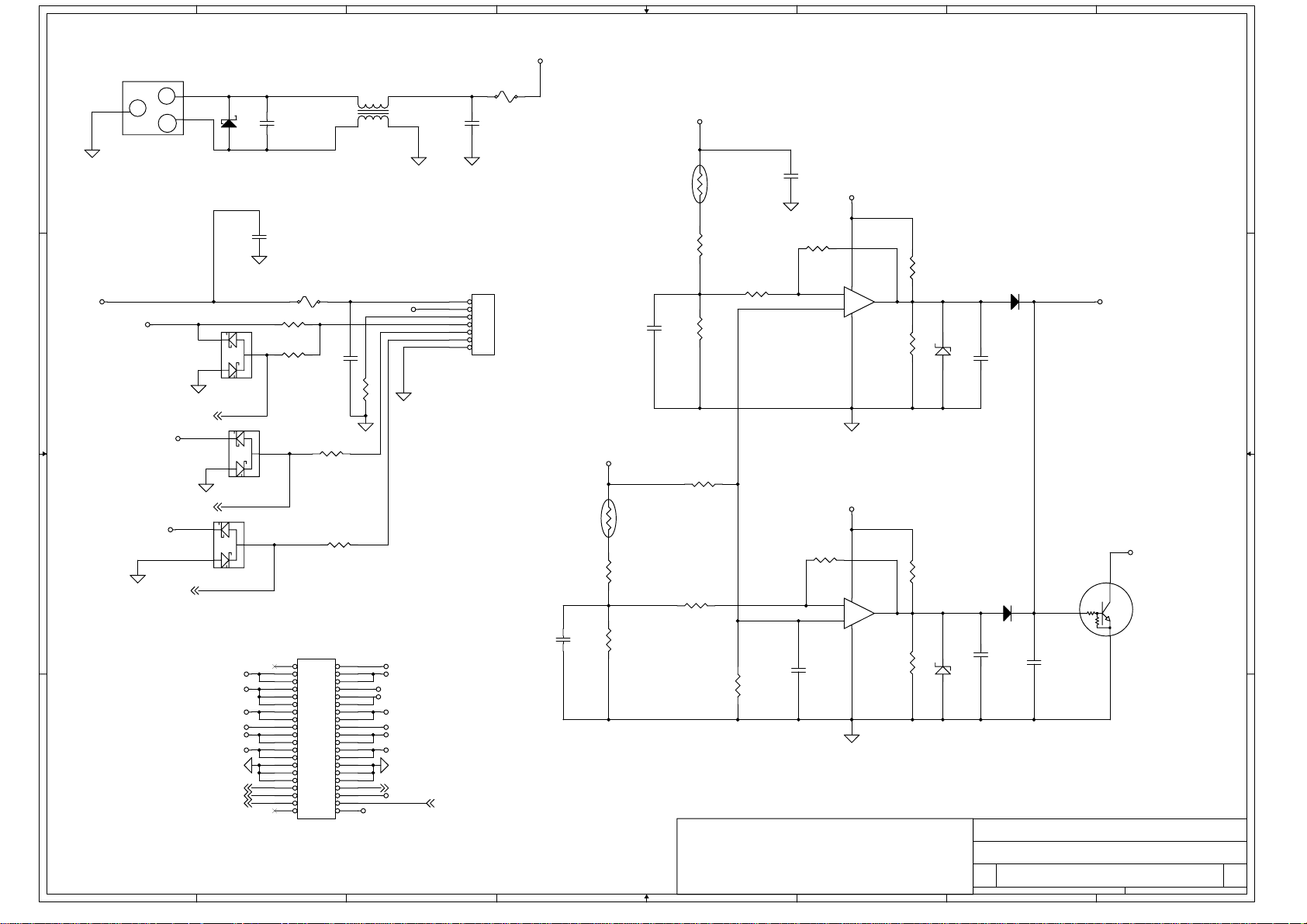

Page 2

A

B

C

D

E

Model Name: 888J2

888J2 BLOCK DIAGRAM

PCB No: LA971

4 4

Mininote

uBGA2 CPU

LCD & CRT

PAGE 14,15

ATI MOBILITY M

VGA

440ZX-100M

BUS#0,DEV#0

HOST-TO-PCI BRIDGE

3 3

PIRQA#

PAGE 12,13

BUS#0,DEV#1

PCI-TO-PCI BRIDGE

PAGE 3,4

PSB

IDSEL: AD11

IDSEL: AD12

PAGE 6,7,8

PULL UP/FDOWN

GEYSERVILLE

MEMORY BUSAGP BUS

PAGE 5

SODIMM

-BANK 2,3

ON BOARD 64MB

-BANK 0

PAGE 9,10

PCI BUS

CPU DECOUPING

INTERNAL IDE

IDE

PRIMARY MASTER

PAGE 18

EXTERNAL MODULE

IDE / FDD

2 2

SECONDARY MASTER

PAGE 19

PIIX4M

BUS#0,DEV#7

FUNC 0: PCI-TO-ISA BRIDGE

FUNC 1: IDE INTERFACE

FUNC 2: USB INTERFACE

FUNC 3: POWER MANAGEMENT

IDSEL: AD18

IDSEL: AD18

PIRQD#

PAGE 16

IEEE 1394

PHY/CONN.

PAGE 23

CARDBUS/1394

PCI4450

PCMCIA

SOCKET

LPT PORT

TRACK PAT

USB CONN

PAGE 31

ISA

SIO

SMC37N869

PAGE 30

ISA

EC/KBC

PC87570

PAGE 27

FIR

PAGE 20

1 1

IDSEL: AD15

MASTER 3

PIRQA#

SIRQ

AUDIO

CS4281-CQ

PAGE 21 PAGE 24

AC

LINK

CS4297-CODEC

AUDIO AMP.

PAGE 22

CONNECTOR

IDSEL: AD19

MASTER 4

PIRQC#

PAGE 25,26

CLOCK

ICS9248-92

PAGE 11

PCI / ISA

PULL UP/DOWN

RESISTERS

PAGE 17

POWER

INTERFACE

PAGE 32

IDSEL: AD28

MASTER 0

IDSEL: AD27

MASTER 1

PIRQD#,

PIRQB#

MINI PCI

MODEM / LAN

PAGE 33

DC/DC POWER

+2.5V POWER

CPU_IO POWER

+3VALW POWER

+5VALW POWER

+12VALW POWER

CPU_CORE POWER

PAGE 34,35

KB

CONNECTOR

PAGE 27

A

BIOS

EC BUFFER

PAGE 28

B

PS2

INTERFACE

PAGE 29

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

of

337Friday, December 01, 2000

E

1C

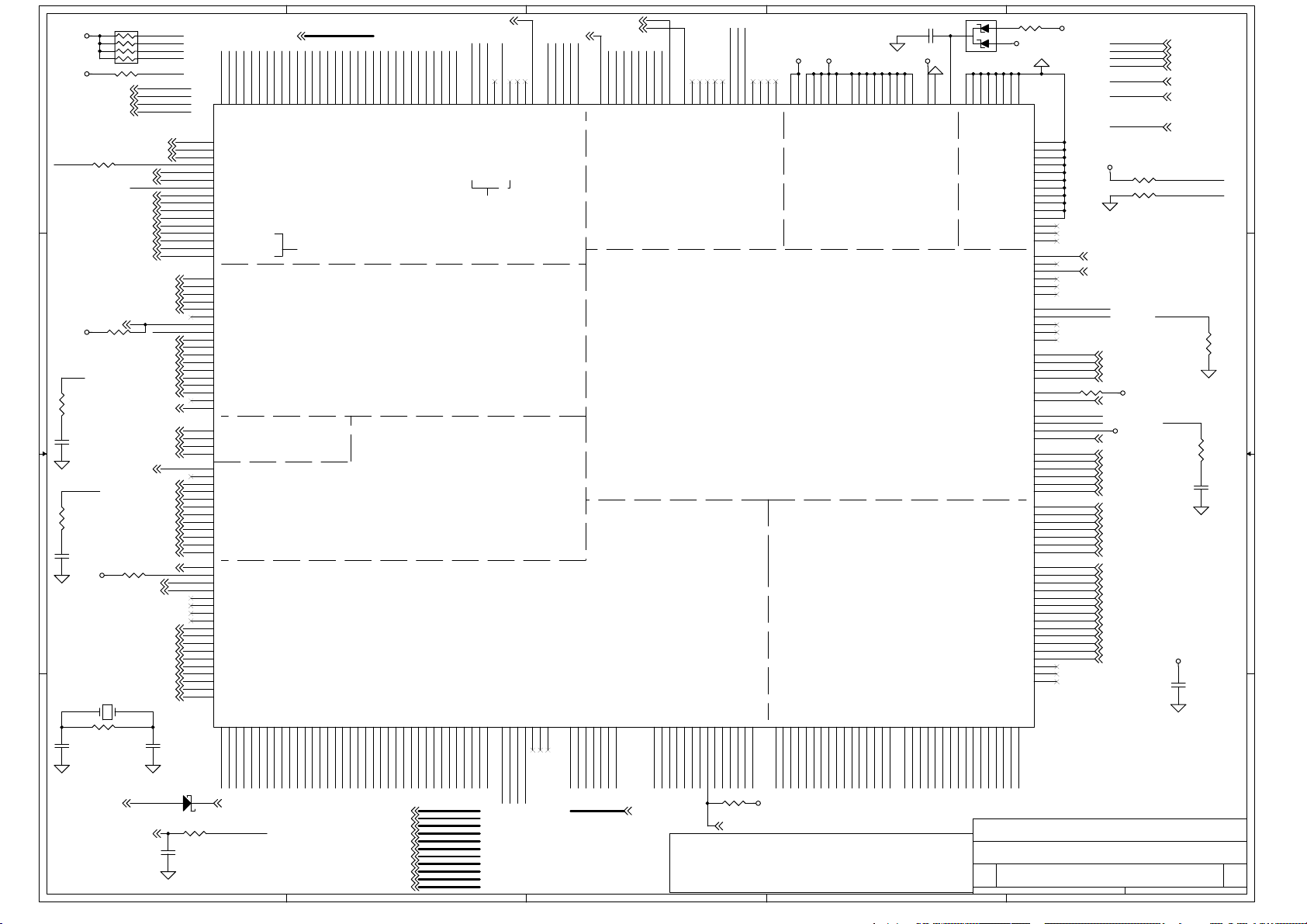

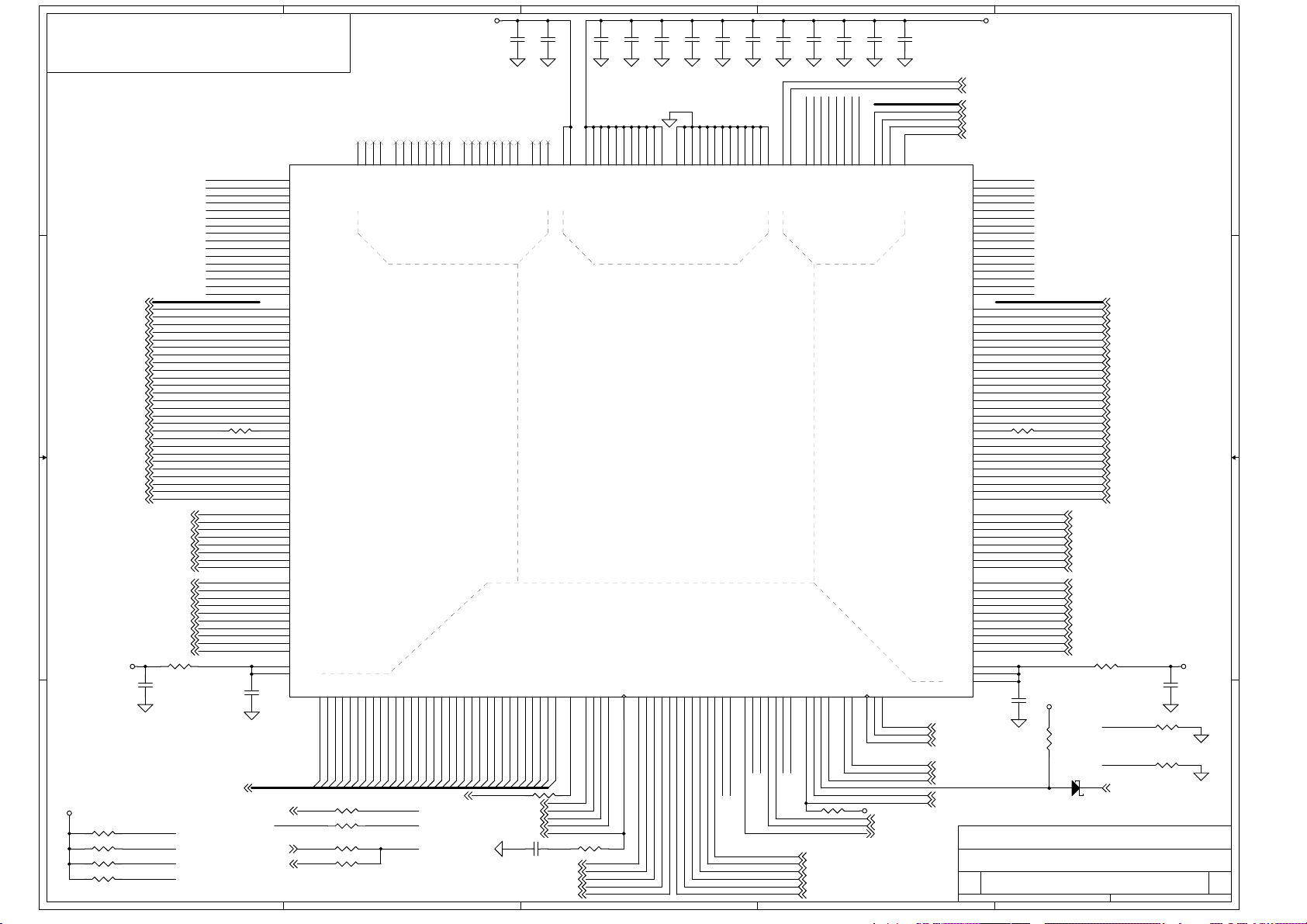

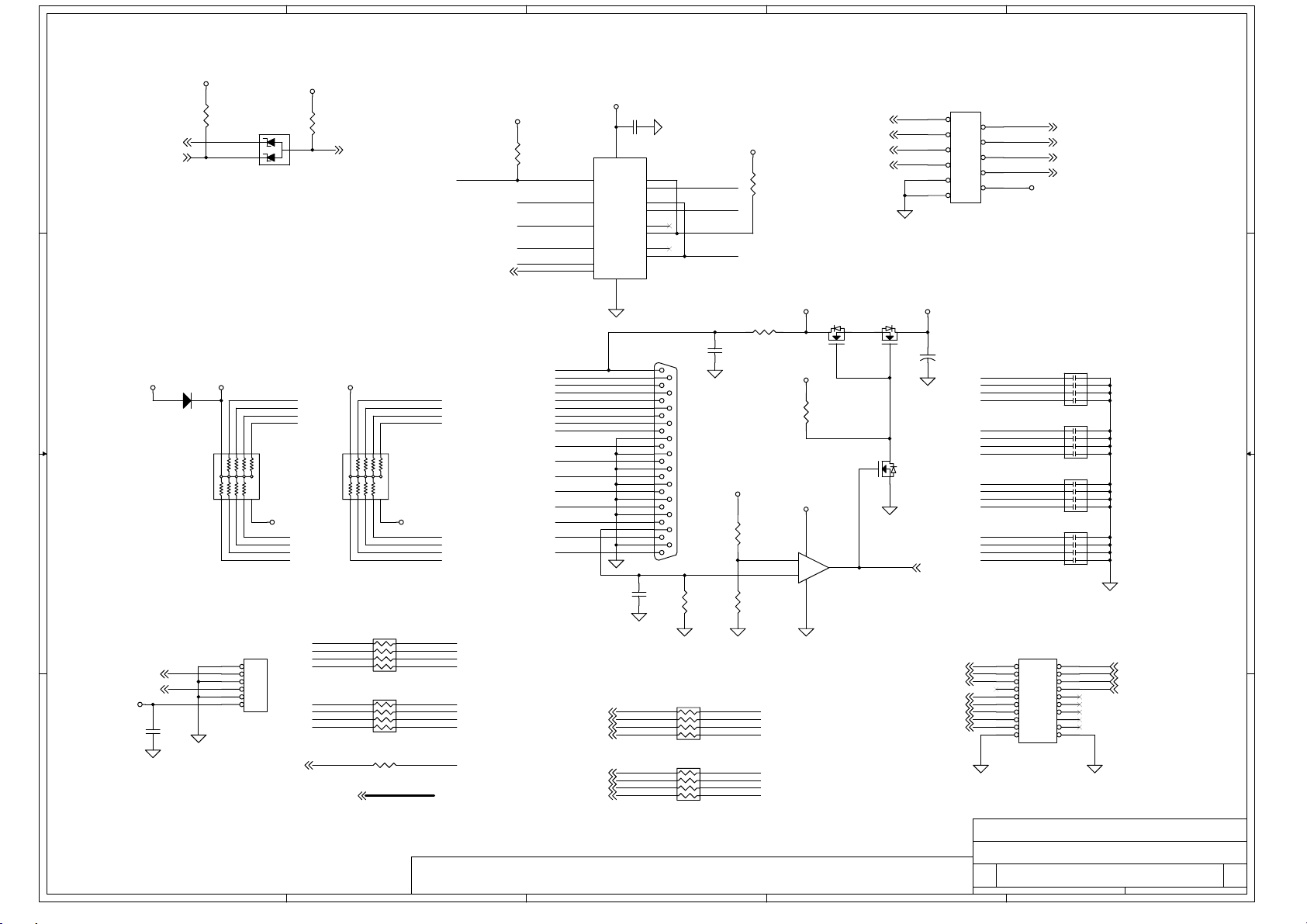

Page 3

A

B

C

D

E

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

AD9

AA21

W21

W19

AD10

AC12

AC13

AB10

AC15

AD13

AD14

AA14

AA11

AB20

W20

AA12

AB15

AB18

AC19

AC11

AB12

AA15

AB16

AB2

AA1

AB1

V21

Y21

AA2

W3

W5

W2

W1

L3

K3

J2

L4

L1

K5

K1

J1

J3

K4

G1

H1

E4

F1

F4

F2

E1

C4

D3

D1

E2

D5

D4

C3

C1

B3

A3

B2

C2

A4

A5

B4

C5

T2

V4

V2

Y2

E6

C6

U4

T4

R1

V1

Y4

U3

U2

U1

Y1

V5

U2A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

RP#

ADS#

AERR#

AP0#

AP1#

BERR#

BINIT#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BP2#

BP3#

BPM0#

BPM1#

TRDY#

RS0#

RS1#

RS2#

RSP#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TDO

TDI

TMS

TRST#

TCK

PREQ#

PRDY#

SELPSB0

SELPSB1

INTR/LINT0

NMI/LINT1

STPCLK#

SLP#

THERMDA

THERMDC

BGA2_495

B

COPPERMINE

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

DBSY#

DRDY#

PICCLK

PICD1

PICD0

INIT#

FLUSH#

RESET#

BCLK

EDGCTRLN

D10

D0#

D11

D1#

C7

D2#

C8

D3#

B9

D4#

A9

D5#

C10

D6#

B11

D7#

C12

D8#

B13

D9#

A14

B12

E12

B16

A13

D13

D15

D12

B14

E14

C13

A19

B17

A18

C17

D17

C18

B19

D18

B20

A20

B21

D19

C21

E18

C20

F19

D20

D21

H18

F18

J18

F21

E20

H19

E21

J20

H21

L18

G20

P18

G21

K18

K21

M18

L21

R19

K19

T20

J21

L20

M19

U18

R18

V20

T21

U21

R21

V18

P21

P20

U19

AA3

T1

AA18

Y20

AB21

AA10

AC9

A6

M3

AA16

110_1%_0603

R49

C

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

R142 1K

1 2

R129 56.2_1%_0603

R132

10

1 2

12

C190

10PF

HD#[0..63]

DBSY# 7

DRDY# 7

+CPU_IO

FOR PIII A2 VERSION

GT_CPUINIT# 6

FLUSH# 6

CPURST# 7

HCLK_CPU 7,12

HD#[0..63] 7

C60

2200PF

+5VS

12

R30 1K

1 2

12

C57

.1UF

THERMDA

THERMDC

+CPU_CORE

+CPU_CORE

1617VCC

U3

1

NC

2

VCC

3

DXP

4

DXN

5

SMBDATA

NC

6

ADD1

7

GND

8 9

GND NC

MAX1617A

+CPU_CORE

+

C22

220U_E

2.5V

12

12

C49

C67

2.2U_0805

2.2U_0805

12

12

12

C186

C193

C201

C73

.1U

.1U

12

C210

.1U

12

C72

.1U

C184

.1U

12

C211

.1U

12

C19

.1U

.1U

12

.1U

12

D

+5VS

12

R29

200

16

NC

15

STBY

14

SMBCLK

13

NC

12

11

ALERT

10

ADD0

12

R31

1K

+5VS

+

C48

+

C23

220U_E

220U_E

2.5V

2.5V

12

12

C68

C14

2.2U_0805

2.2U_0805

12

12

12

C196

C197

C182

.1U

.1U

.1U

12

12

12

C214

C213

C212

.1U

.1U

.1U

12

12

12

C20

C42

C15

.1U

.1U

.1U

Title

SCHEMATICS, M/B LA-971

Size Document Number Rev

B

401166

Date: Sheet

from 87570

SMCLK 28,29,35

SMDATA 28,29,35

12

12

C185

.1U

12

C222

.1U

12

C11

.1U

R32

10K

+

12

.1U

12

.1U

12

C242

220U_E

2.5V

C194

C221

ATF#

12

C39

2.2U_0805

C71

.1U

12

.1U

12

.1U

12

C183

C220

C18

.1U

+

C217

220U_E

2.5V

12

C195

.1U

12

C219

.1U

12

C21

.1U

ATF# 29

12

C17

2.2U_0805

12

12

C204

C205

.1U

.1U

12

12

C218

C165

.1U

.1U

12

12

C74

C13

.1U

.1U

Compal Electronics, Inc.

E

12

C203

.1U

12

C168

.1U

12

C16

.1U

437Friday, December 01, 2000

12

C202

.1U

12

C172

.1U

12

C70

.1U

of

12

C32

.1U

1C

+3VS+CPU_IO+CPU_IO

R173

10K

1 2

12

C69

47PF

HREQ#07

HREQ#17

HREQ#27

HREQ#37

HREQ#47

ADS#7

IERR#6

BREQ0#7

BPRI#7

BNR#7

HLOCK#7

HIT#7

HITM#7

DEFER#7

HTRDY#7

RS#07

RS#17

RS#27

GT_A20M#6

GT_SMI#6

PREQ#6

GT_NMI6

SLP#6

66MHZ

100MHZ

RESERVED

133MHZ

HA#[3..31]

FERR# 17

FERR#1.5

RP1 8P4R-1K

1 8

2 7

3 6

4 5

R26 @56_0603

R146 10K

R41 @10K

R43 1K

THERMDA

THERMDC

12

12

12

12

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

HA#[3..31]7

4 4

R48

R47

1K

1.5K

1 2

1 2

2

FERR#1.5

3 3

2 2

1 1

SELPSB[1:0] STSEM BUS FREQUENCY

00

01

10

11

Q1

FDV301N

PVT change

+CPU_IO

A

13

GT_IGNNE#6

PWRGD_CPU6

GT_INTR6

GT_STPCLK#6

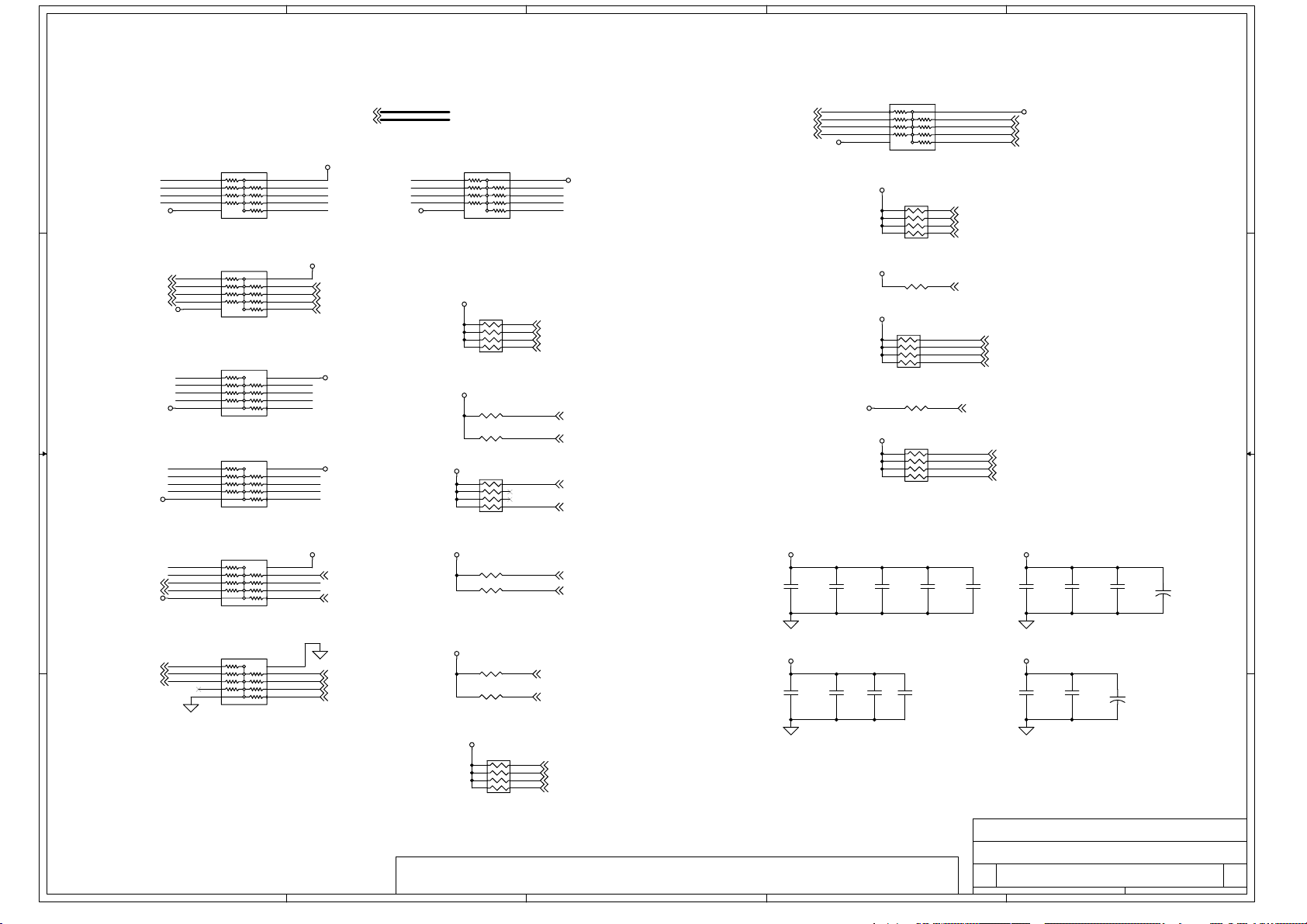

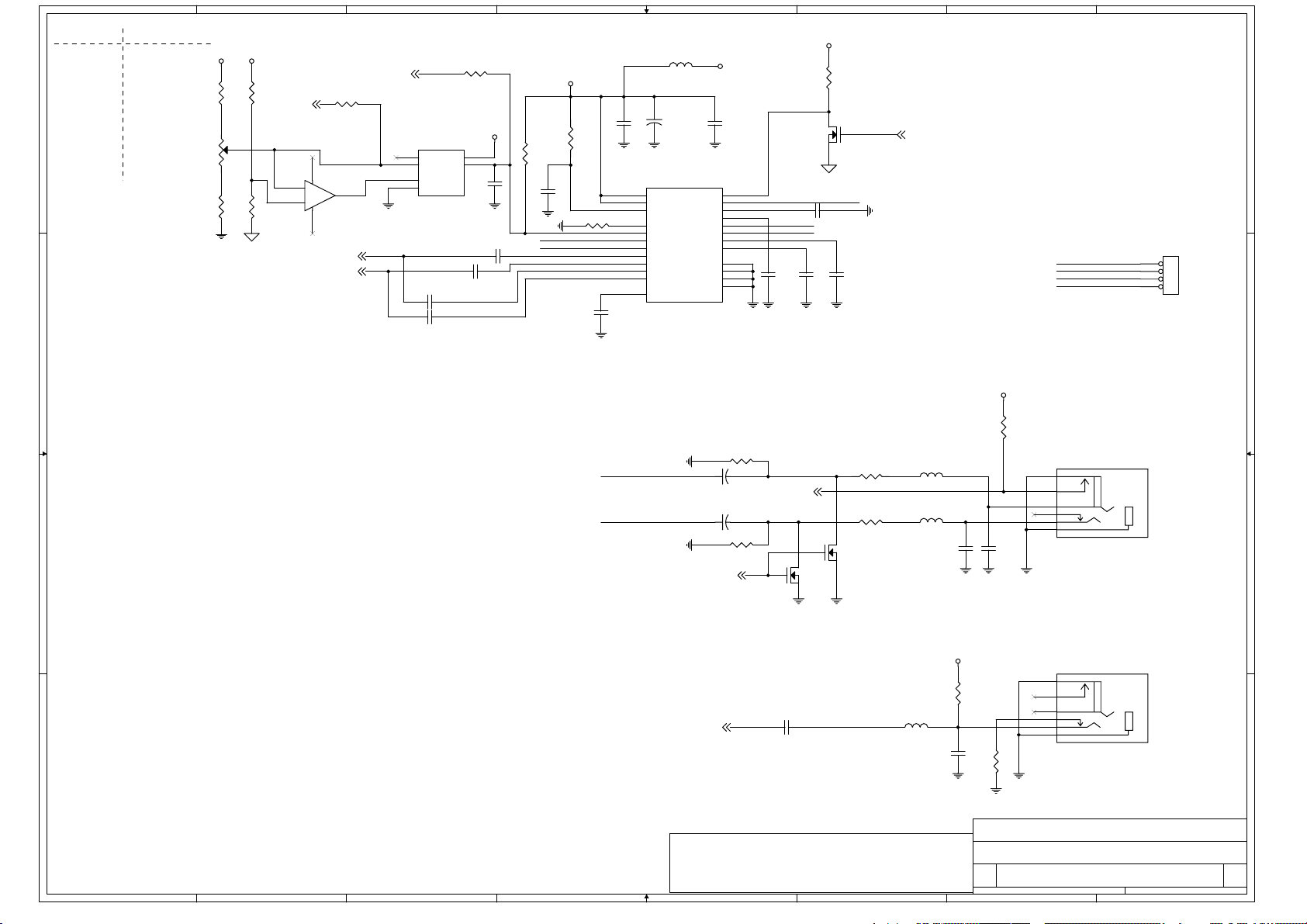

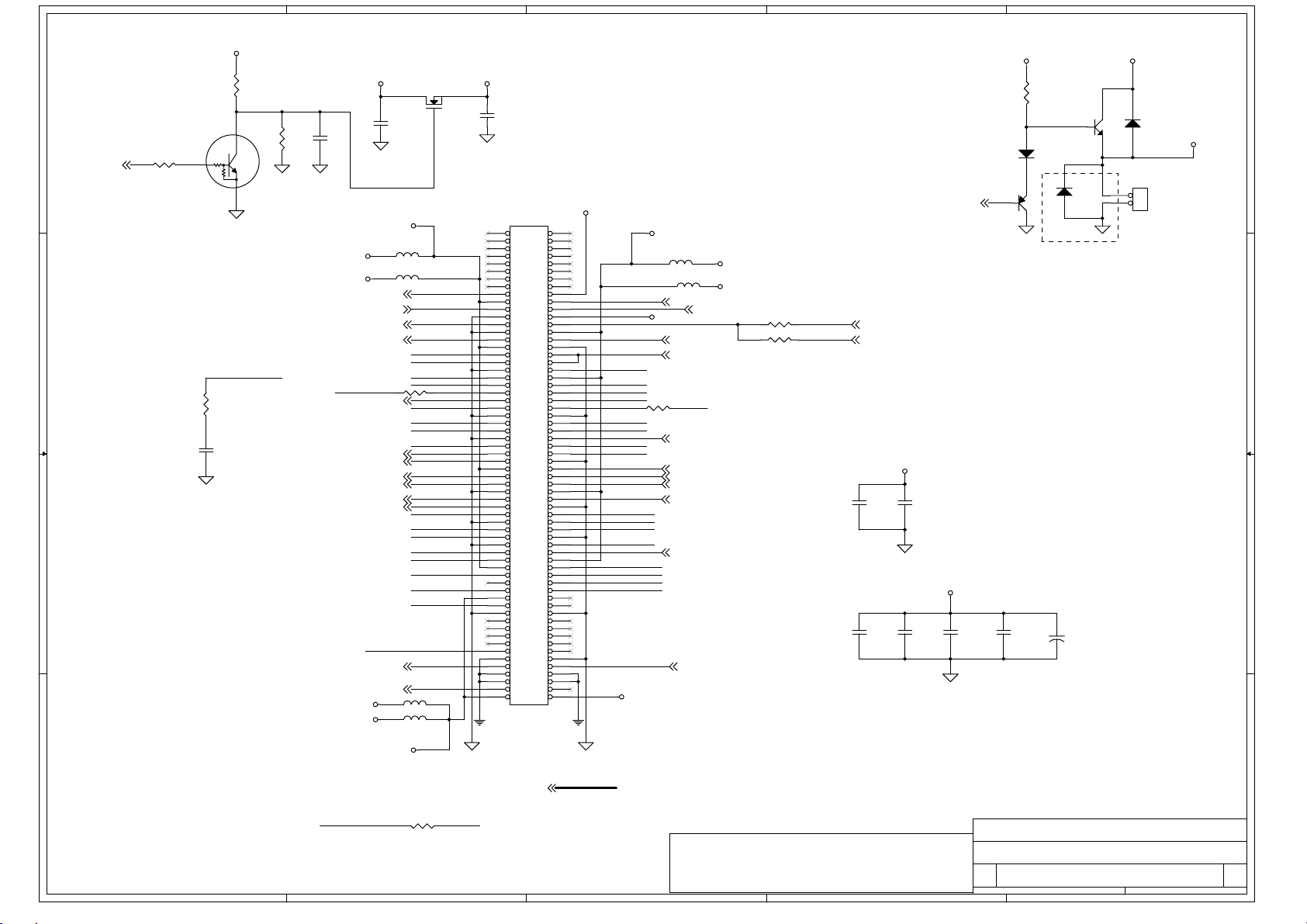

Page 4

A

B

C

D

E

1 2

R6

12

C235

.1UF

1 2

L18 4.7Uh

VCCTREF

12

+2.5V_CLK+2.5V_CLK

A

R4

2K_1%_0603

R138

2K_1%_0603

1 2

1 2

R135

2K_1%_0603

CPU_LO/HI#6

+CPU_IO

56.2_1%_0603

+CPU_IO

+CPU_IO

R139

1.5K_1%_0603

1 2

1 2

R143

1K_1%_0603

1K_1%_0603

12

C75

.1UF

4 4

3 3

2 2

1 1

12

C171

.1UF

+

33U_E

12

+CPU_CORE

12

C207

.1UF

R46

VCCT_VCCA

C174

VCCT_VSSA

VCCTREF

12

C234

.1UF

R42 1.5K

1 2

C169

.1UF

4.7U_1206

CLKREF

CMOSREF

1 2

12

U2B

C192

.1UF

L2

VCCA

PLL ANALOG VOLTAGE

M2

VSSA

E5

VREF0

E16

12

C25

R35

1K

VREF1

E17

VREF2

F5

VREF3

F17

VREF4

U5

VREF5

Y17

VREF6

VREF7

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

RSVD

CLKREF

CMOSREF1

CMOSREF2

GHI#

RTTIMPEDP

TESTHI

TESTLO1

TESTLO2

TESTP1

TESTP2

TESTP3

TESTP4

BGA2_495

COPPERMINE

POWER,

GROUND,

RESERVED

SIGNALS

B

Y18

H8

H10

H12

H14

H16

J7

J9

J11

J13

J15

K8

K10

K12

K14

K16

L7

L9

L11

L13

L15

M8

M10

M12

M14

M16

N7

N9

N11

N13

N15

P8

P10

P12

P14

P16

R7

R9

R11

R13

R15

T8

T10

T12

T14

T16

U7

U9

U11

U13

U15

AB19

P2

AA9

AD18

R2

AD19

AD17

12

Y5

N5

AD20

H4

AA17

G4

R14

1K

1 2

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

A2

A7

A8

A12

A21

B1

B5

B6

B7

B8

B10

B15

B18

C9

C11

C15

C16

C19

D2

D6

D7

D9

E3

E7

E8

E9

E10

E11

E13

E19

F3

F6

F7

F8

F9

F10

F11

F12

F13

F14

F15

F16

F20

G3

G19

H2

H7

H9

H11

H13

H15

H20

J4

J8

J10

J12

J14

J16

J19

K2

K7

K9

K11

K13

K15

K20

L5

L8

L10

L12

L14

L16

L19

M7

M9

M11

M13

M15

M20

N2

N3

N4

N8

N10

N12

N14

N16

N18

N19

N20

P5

P7

P9

P11

P13

P15

P19

R3

R4

R5

R8

R10

+CPU_IO

CPU_VID[0..4]

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

CPU_VID[0..4] 6

G10

G11

G12

G13

G14

G15

G16

G17

H17

K17

M17

N17

P17

R17

U17

V10

V11

V12

V13

V14

V15

V16

V17

W10

W11

W12

W13

W14

W15

W16

W17

AA6

AA7

AA8

AB6

AB7

AB8

AC6

AC7

AC8

AD6

AD7

AD8

G6

G7

G8

G9

H6

J6

J17

K6

L6

L17

M6

N6

P1

P6

R6

T6

T17

U6

V6

V7

V8

V9

W6

W7

W8

W9

Y6

Y7

Y8

U2C

VCCT0

VCCT1

VCCT2

VCCT3

VCCT4

VCCT5

VCCT6

VCCT7

VCCT8

VCCT9

VCCT10

VCCT11

VCCT12

VCCT13

VCCT14

VCCT15

VCCT16

VCCT17

VCCT18

VCCT19

VCCT20

VCCT21

VCCT22

VCCT23

VCCT24

VCCT25

VCCT26

VCCT27

VCCT28

VCCT29

VCCT30

VCCT31

VCCT32

VCCT33

VCCT34

VCCT35

VCCT36

VCCT37

VCCT38

VCCT39

VCCT40

VCCT41

VCCT42

VCCT43

VCCT44

VCCT45

VCCT46

VCCT47

VCCT48

VCCT49

VCCT50

VCCT51

VCCT52

VCCT53

VCCT54

VCCT55

VCCT56

VCCT57

VCCT58

VCCT59

VCCT60

VCCT61

VCCT62

VCCT63

VCCT64

VCCT65

VCCT66

VCCT67

VCCT68

VCCT69

VCCT70

VCCT71

BGA2_495

D

COPPERMINE

POWER, GROUND AND NC

Title

Size Document Number Rev

B

Date: Sheet

R12

VSS102

R14

VSS103

R16

VSS104

R20

VSS105

T3

VSS106

T5

VSS107

T7

VSS108

T9

VSS109

T11

VSS110

T13

VSS111

T15

VSS112

T18

VSS113

T19

VSS114

U8

VSS115

U10

VSS116

U12

VSS117

U14

VSS118

U16

VSS119

U20

VSS120

V3

VSS121

V19

VSS122

W4

VSS123

W18

VSS124

Y3

VSS125

Y9

VSS126

Y10

VSS127

Y11

VSS128

Y12

VSS129

Y13

VSS130

Y14

VSS131

Y15

VSS132

Y16

VSS133

Y19

VSS134

AA4

VSS135

AA13

VSS136

AA20

VSS137

AB3

VSS138

VID4

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VID3

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VID0

VID1

VID2

VSS159

VSS160

VSS161

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

AB4

AB5

AB9

AB11

AB13

AB14

AB17

AC1

AC2

AC4

AC5

AC10

AC14

AC16

AC18

AC21

AD1

AD2

AD3

AD4

AD5

AD16

AD21

A15

A16

A17

C14

D8

D14

D16

E15

G2

G5

G18

H3

H5

J5

M4

M5

P3

P4

AA5

AA19

AC3

AC17

AC20

AD15

CPU_VID4

CPU_VID3

CPU_VID0

CPU_VID1

CPU_VID2

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

1C

of

537Friday, December 01, 2000

E

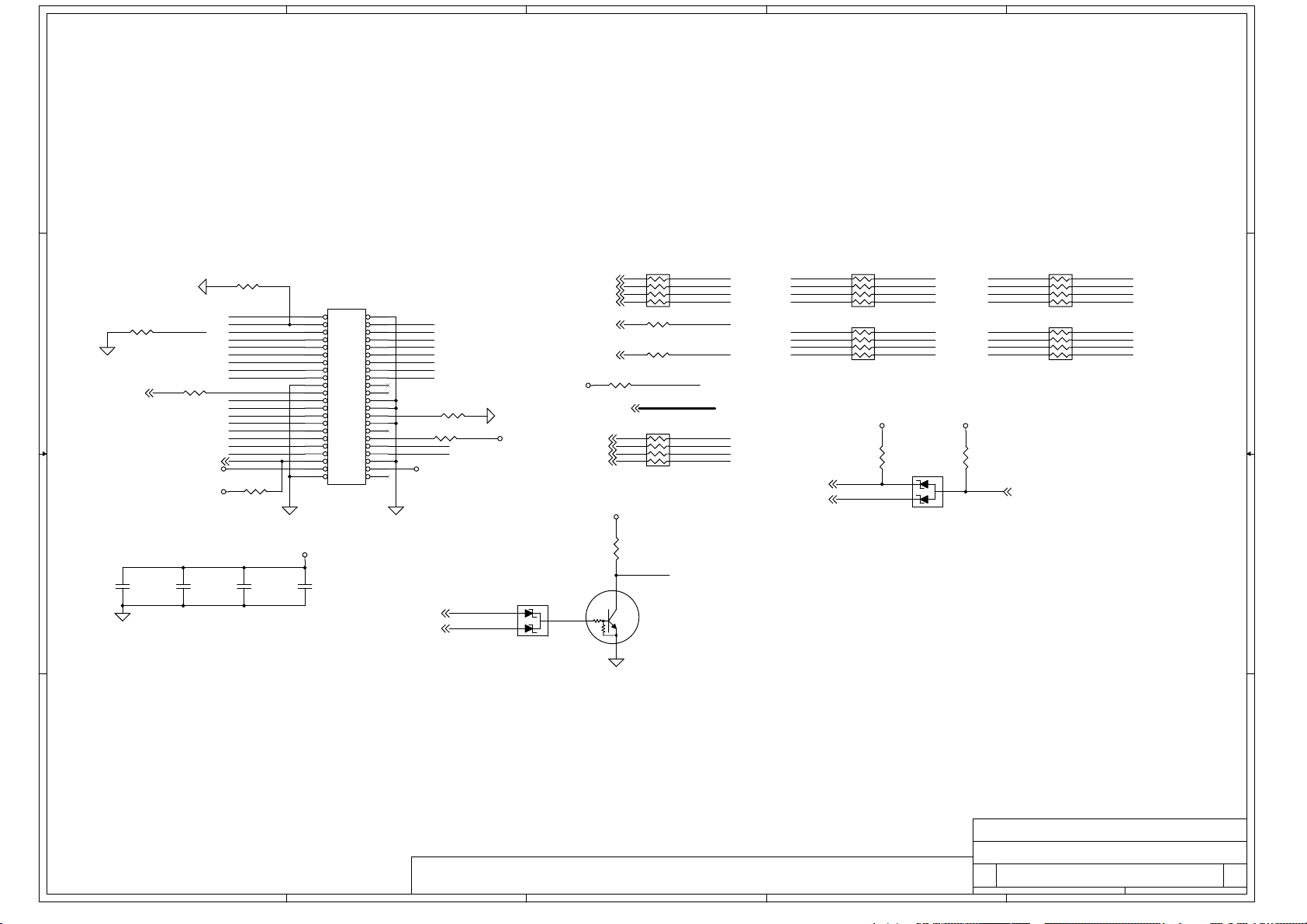

Page 5

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4 4

+3V

3 3

VID[4:0] CPU VCC

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

2 2

01011

01100

01101

01110

01111

10000

10001

10010

10011

10100

10101

10110

10111

11000

1 1

11001

11010

11011

11100

11101

11110

11111

A

U16

STPCLK#17

CPUINIT#17 GT_CPUINIT# 4

GT_LO/HI#17

CPU_STP#17

IGNNE#17

CRESET#7

R213 10K

VR_POK30,36

VR_ON29,33,36

14.3MGCL12

2.00

1.95

1.90

STPCLK#

CPUINIT#

INTR

INTR17

NMI

NMI17

SMI#

SMI#17 GT_SMI# 4

SUSTAT1#

GT_LO/HI#

CPU_STP#

A20M#

A20M#17

R212

12

R228

@33

C296

@27P

23

STPCLK#

22

INIT#

16

INTR

20

NMI

17

SMI#

19

SUS_ST1#

14

LO/HI#

13

CPU_STP#

24 48

A20M# GT_A20M#

28

DEEP_SLP

37 36

DIN DOUT

12

44

@0

12

12

IGN_PLLTMR#

43

IGN_VGATE#

40

RESERVED0

39

RESERVED1

35

RESERVED2

45

RESERVED3

29

VGATE

15

VR_ON

38

STB#

26

XIN

25

XOUT

@G_ASIC

1.85

1.80

1.75

1.70

1.65

1.60

1.55

1.50

1.45

1.40

1.35

1.30

NO CPU

1.275

1.250

1.225

1.200

1.175

+5V

1 2

R62 @1K

RP2

10P8R-1K

6

7

8

9

10

+5V

CPU_VID[0..4]

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

1.150

1.125

1.100

1.075

1.050

1.025

1.000

0.975

0.950

R57

@0

1 2

R184

@0

1 2

R185

@0

R215

@0

1 2

1 2

1 2

R216

@0

0.925

NO CPU

A

B

GT_STPCLK#

GT_SUS_ST1#

A_GT_SUS_ST1#

GT_CPU_STP#

GT_IGNNE#IGNNE#

CPUPWRGDCRESET#

LP_TRANS#

VRCHGNG#

CPU_VID[0..4] 5

4 5

8 9

14 15

18 19

22 23

1

3

8

GT_INIT#

4

GT_INTR

1

GT_NMI

5

GT_SMI#

11

46

10

GT_LO/HI#

47

221

941

34

33

VR_HI/LO#

12

32

VRPWRGD

7

VCC1

30

VCC2

6

GND0

18

GND1

27

GND2

31

GND3

42

GND4

+5V

5

4

3

2

1

1 2

R179 1K

U15

B0 D0

B1 D1

B2 D2

B3 D3

B4 D4

BE#

@SN74CBT3383

VR_HI/LO#

B

VCC

GNDBX

GT_STPCLK#

GT_CPUINIT#

GT_INTR

GT_NMI

GT_SMI#

GT_SUSTAT1#

CPU_LO/HI#

GT_CPU_STP#

GT_A20M#

GT_IGNNE#IGNNE#

PWRGD_CPU

VR_HI/LO#

VRCHGNG#

V_GOOD

+GCL_VCC

12

C292

@.01UF

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

23

C0A0

67

C1A1

1011

C2A2

1617

C3A3

2021

C4A4

24

1213

VID0

VID1

VID2

VID3

VID4

12

@.1UF

C265

GT_STPCLK# 4

GT_INTR 4

GT_NMI 4

GT_SUSTAT1# 7,13SUSTAT1#17

CPU_LO/HI# 5

GT_CPU_STP# 12

GT_A20M# 4

GT_IGNNE# 4

PWRGD_CPU 4

VR_HI/LO#

VRCHGNG# 17

V_GOOD 30

12

12

C293

C294

@.1UF

@.1UF

VID0 36

VID1 36

VID2 36

VID3 36

VID4 36

+5V

L25

1 2

@0_0805

C

With SpeedStep CPU Support:

Mount: U16: G_ASIC (SA658370000)

+3V

12

C283

@.1UF

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4 VID4

CPU_STP#

INTR

SMI#

CPUINIT#

A20M#

NMI

IGNNE#

SUSTAT1#

STPCLK# GT_STPCLK#

VR_POK

VR_HI/LO#

1 8

2 7

3 6

4 5

1 2

R54 0

1 8

2 7

3 6

4 5

8P4R-0

1 8

2 7

3 6

4 5

8P4R-0

1 2

R234 0

1 2

1 2

R214 10K

for without Geyserville

C

D

+CPU_IO

12

12

12

.1UF

12

.1UF

C173

C227

C175

.1UF

12

C230

.1UF

C176

.1UF

12

C228

.1UF

U15: 74CBT3383 (SA433830000)

R57, R184, R185, R216 R215: 0ohm

(1.6V for high performance)

RP56: 8P4R-4.7K

R214: 1Kohm

R242: 680ohm

R208: 1Kohm

R136: 1.5Kohm

R236: 100Kohm

R240: 4.7Kohm R239: 1.5Kohm

R207: 100KohmR209: 100Kohm

R236: 100Kohm R140: 1.5Kohm

RP4

8P4R-0

RP50

RP49

R223

0

VID0

VID1

VID2

VID3

GT_CPU_STP#

GT_INTR

GT_SMI#

GT_CPUINIT#

GT_A20M#

GT_NMI

GT_IGNNE#

GT_SUSTAT1#

V_GOOD

12

R232

31.6K_1%_0603

PWRGD_CPU

12

R231

100K_1%_0603

D

12

C177

.1UF

12

C226

.1UF

E

12

12

12

12

12

12

12

C178

.1UF

12

C231

.1UF

C179

.1UF

12

C225

.1UF

C187

.1UF

12

C216

.1UF

C198

.1UF

12

C208

.1UF

C206

.1UF

12

C200

.1UF

C215

.1UF

12

C191

.1UF

C224

.1UF

12

C181

.1UF

12

C229

.1UF

+

Remove:

RP4: 8P4R-0

R54: 0ohm

RP50: 8P4R-0

RP49: 8P4R-0

R223: 0ohm

R232: 31.6Kohm 1%

R214: 10Kohm

R231: 100Kohm 1%

R234: 0ohm

without Geyserville,

GHI#(CPU_LO/HI#) can

OPEN

RP47

8P4R-1.5K

RP56

@8P4R-4.7K

GT_NMI

GT_INTR

GT_IGNNE#

GT_A20M#

GT_CPUINIT#

GT_STPCLK#

GT_SMI#

CPU_LO/HI#

PWRGD_CPU

IGNNE#

NMI

INTR

A20M#

CPUINIT#

STPCLK#

SMI#

VRCHGNG#

GT_LO/HI#

CRESET#

GT_SUSTAT1#

GT_CPU_STP#

E

+CPU_IO

+2.5V_CLK

+3VS

+3V

Title

SCHEMATICS, M/B LA-971

Size Document Number Rev

B

401166

Date: Sheet

1 8

2 7

3 6

4 5

1 2

R147 1.5K

1 2

R227 1K

1 2

R224 680

1 2

R145 1.5K

1 2

R44 1.5K

1 2

R45 270_0603

1 2

R37 1.5K

1 2

R136 @1.5K

1 2

R140 1.5K

1 8

2 7

3 6

4 5

1 2

R241 @1K

1 2

R242 @680

1 2

R240 @4.7K

1 2

R239 @1.5K

1 2

R236 @100K

1 2

R208 @1K

1 2

R207 @100K

1 2

R209 @100K

Compal Electronics, Inc.

C243

220U_E

2.5V

SLP# 4

FLUSH# 4

IERR# 4

PREQ# 4

of

637Friday, December 01, 2000

1C

Page 6

1 1

2 2

3 3

4 4

HD#[0..63]4

HD#[0..63]

A

B

C

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

2.32K_1%_0603

R53

1 2

12

.01UF

C87

12

.1UF

C86

12

.1UF

C79

1UF_0805

12

RB751V

C253

3.48K_1%_0603

R56

1 2

VCCTREF

+3V

2 1

R187 1K

D15

A

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

D22

D21

C21

E18

HD12#

HA14#

E23

HA#15

B20

HD11#

HA13#

F25

HA#14

E19

HD10#

HA12#

F24

HA#13

A20

HD9#

HA11#

F23

HA#12

150UF_E_10V

4.7U_1206

E20

HD8#

HA10#

F22

HA#11

C297

B21

HD7#

HA9#

G22

HA#10

C299

+

12

C20

G26

HA#9

A21

HD6#

HA8#

F26

HA#8

HD5#

HA7#

G24

HA#7

HD4#

HA6#

H23

HA#6

A22

HD3#

HA5#

G23

HA#5

+3V

E21

HD2#

HA4#

H22

HA#4

HD1#

HA3#

G25

HA#3

HD0#

B22

U12A

B

HA#[3..31]

HA#[3..31] 4

C

E11

B23

A7

HD55#

HD56#

RS#2

RS#2 4

A9

L25

A10

HD53#

HD54#

RS#0

RS#1

L26

RS#0 4

RS#1 4

B10

C8

HD52#

HTRDY#

H25

K26

HTRDY# 4

C12

HD50#

HD51#

DRDY#

DRDY# 4

B7

K23

A11

HD48#

HD49#

DBSY#

L23

DBSY# 4

B17

A17

B16

A16

B15

A15

B13

E14

A13

B12

B14

E13

A12

B11

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HOST BUS INTERFACE (Processor System

Bus)

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HLOCK#

HITM#

HIT#

L22

HIT# 4

HITM# 4

BREQ0#

BPRI#

BNR#

B26

H26

H24

K22

L24

BREQ0# 4

BPRI# 4

BNR# 4

HLOCK# 4

ADS#

K21

J22

J23

K24

K25

J25

ADS# 4

HREQ#0 4

HREQ#1 4

HREQ#2 4

HREQ#3 4

HREQ#4 4

HA30#

HA31#

D23

HA#31

HA29#

E22

HA#30

HA28#

A23

HA#29

HA27#

C24

HA#28

HA26#

B24

HA#27

C23

HA#26

DEFER#

J26

DEFER# 4

E17

HD22#

HD23#

HA24#

HA25#

D24

HA#25

HD21#

HA23#

A24

HA#24

B18

HD20#

HA22#

C25

HA#23

A19

HD19#

HA21#

A25

HA#22

A18

HD18#

HA20#

C26

HA#21

B19

HD17#

HA19#

B25

HA#20

HD16#

HA18#

D26

HA#19

HD15#

HA17#

E25

D25

HA#17

HA#18

HD13#

HD14#

HA15#

HA16#

E26

HA#16

C11

C10

D9

10

443ZX-M/443BX

R59

HD62#

HD63#

HCLKIN

N23

HCLK_CPU 4,12

B8A8B9

HD60#

HD61#

HD58#

HD59#

CRESET#

CRESET# 6

HD57#

CPURST#

M26

CPURST# 4

+3V

AGPREF

1 2

12

C92

5PF

+5V

1 2

REFVCC5

D20

D19

D18

C19

C17

D17

C16

C15

D16

D14

D15

C14

D13

D12

C13

D11

D

Title

Size Document Number Rev

Date: Sheet

B

4011661CSCHEMATICS, M/B LA-971

Compal Electronics, Inc.

E

737Friday, December 01, 2000

of

12

C531

1UF_0603

12

C532

1UF_0603

+CPU_IO

443ZX-M/443BX

RSMRST#17,30

R71 0

1 2

BXPWROKRSMRST#

VSS64

VSS65

VSS66BXPWROK

AF13

AF26AF3

AF1

VSS62

VSS63

AD22

AD18

VSS60

VSS61

AD9

GT_SUSTAT1#6,13

AD4

SUSTAT#

VSS58

VSS59

AB25

AD5

+3V

R58 1K

1 2

M25

TESTIN#

VSS57

AB15

AB24

VSS55

VSS56

AB12

AB3

.1UF

.1UF

AE23

NC1

NC2

VSS53

VSS54

AA21

AE22

AA19

12

C82

12

C91

P22

NC0

VSS51

VSS52

AA8

AGPREF

N4

AGPREF

VSS50

AA6

REFVCC5

C2

REFVCC5

VSS48

VSS49

VTTB

VSS46

VSS47

+CPU_IO

M24

F17

VTTA

VSS45

T12

T15V3V24W6W21

VCCTREF

E16

GTL_REFA

GTL_REFB

VSS42

VSS43

VSS44

R16

R22

M23

R14

VCC40

VSS40

VSS41

R13

AF14

VCC39

VSS39

AF2

VCC38

VSS38

AE26

VCC37

VSS37

P26R5R11

AE1

P15

AA18

AA20

VCC35

VCC36

VSS35

VSS36

P13

P14

AA9

VCC33

VCC34

VSS33

VSS34

P12

12

.1UF

C77

12

.1UF

C84

12

.1UF

C101

12

.1UF

C95

12

.1UF

C81

12

.1UF

C93

12

.01UF

C97

12

.01UF

C98

AA7

VCC32

VCC30

VCC31

V21Y6Y21

VCC29

V6

VCC28

T16

VCC27

T14

VCC26

T13

VCC25

T11

VCC24

R15

POWER and GROUND

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

M13

M14

M16

M22N1N12

N13

N14

N15

N24

R12

VCC22

VCC23

VSS22

VSS23

P16

VCC21

VSS21

.1UF

.1UF

.01UF

P11

VCC20

VSS20

L15M5M11

P1

VCC19

VSS19

L12

12

C99

12

C83

12

C80

N26

VCC18

VSS18

N22

VCC17

VSS17

N16

VCC16

VSS16

N11

VCC15

VSS15

M15

VCC14

VSS14

F21H6H21J3J24

M12

VCC13

VSS13

F19

L16

VCC12

VSS12

L14

VCC11

VSS11

L13

VCC10

VSS10

E24F6F8

.1UF

.1UF

.1UF

.1UF

.01UF

.01UF

.01UF

.01UF

L11

E15

J21

VCC9

VSS9

C96

C94

C89

C100

C90

C85

C88

C78

J6

VCC8

VSS8

12

12

12

12

12

12

12

12

G21

VCC7

VSS7

C22E3E12

G6

VCC6

VSS6

C18

F20

VCC5

VSS5

F18

VCC4

VSS4

F9

VCC3

VSS3

A26C5C9

F7

VCC2

VSS2

A14

B1

VCC1

VSS1

A1

U12D

D

+3V

E

Page 7

A

B

C

D

E

U12C

AB5

G_AD0

AE2

G_AD1

AD3

G_AD2

AD2

G_AD3

AD1

G_AD4

AC3

G_AD5

AC1

G_AD6

AB4

G_AD7

AB1

G_AD8

AA5

G_AD9

AA3

G_AD10

AA4

G_AD11

AA2

G_AD12

AA1

G_AD13

Y5

G_AD14

Y3

G_AD15

W1

G_AD16

V2

G_AD17

W2

G_AD18

U5

G_AD19

V1

G_AD20

U4

G_AD21

U3

G_AD22

U1

G_AD23

T3

G_AD24

T4

G_AD25

T2

G_AD26

T1

G_AD27

U6

G_AD28

R3

G_AD29

R4

G_AD30

R2

G_AD31

AB2

G_CBE0#

Y4

G_CBE1#

V4

G_CBE2#

U2

G_CBE3#

W3

G_FRAME#

V5

G_IRDY#

W4

G_TRDY#

W5

G_DEVSEL#

Y2

G_PAR

Y1

G_STOP

K1

SBA0

M2

SBA1

M1

SBA2

N2

SBA3

P2

SBA4

P4

SBA5

P3

SBA6

R1

SBA7

L5

G_REQ#

L3

G_GNT#

M4

RBF#

M3

PIPE#

AC2

AD_STBA

T5

AD_STBB

N3

SB_STB

L4

ST0

L2

ST1

L1

ST2

N5

GCLKIN

P5

GCLKO

R197

443ZX-M/443BX

10

1 2

12

C270

5PF

B

AGP INTERFACE

PCI INTERFACE

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0#

CBE1#

CBE2#

CBE3#

FRAME#

IRDY#

TRDY#

DEVSEL#

PAR

STOP#

SERR#

PLOCK#

PHOLD#

PHLDA#

WSC#

PREQ0#

PREQ1#

PREQ2#

PREQ3#

PREQ4#

PGNT0#

PGNT1#

PGNT2#

PGNT3#

PGNT4#

PCIRST

CLKRUN#

PCLKIN

K6

K2

K4

K3

K5

J1

J2

H2

H1

J5

H3

H5

H4

G1

G2

G4

D1

D3

D2

C1

A2

C3

B3

D4

E5

A4

D5

B4

B5

A5

E6

C6

J4

G3

E4

C4

E2

E1

F5

F3

G5

F4

F1

F2

B6

D6

AE3

A6

C7

F10

D8

D10

E7

D7

E10

E8

E9

A3

AC4

B2

+3V

GC/BE#013

GC/BE#113

GC/BE#213

GC/BE#313

GFRAME#13

GIRDY#13

GTRDY#13

GDEVSEL#13

GSTOP#13

GSBA[0..7]13

GREQ#13

GGNT#13

RBF#13

PIPE#13

R225 0

R61 0

SBSTB13

ST013

ST113

ST213

1 2

R206

18_0603

D17

1

2

RB717F

D16

1

2

RB717F

GAD[0..31]

GFRAME#

GIRDY#

GTRDY#

GDEVSEL#

GSTOP#

GSBA[0..7]

GREQ#

GGNT#

RBF#

PIPE#

1 2

1 2

ST0

ST1

ST2

REQ#1

REQ#3

REQ#0

REQ#4

R205

18_0603

1 2

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GSBA0

GSBA1

GSBA2

GSBA3

GSBA4

GSBA5

GSBA6

GSBA7

R_ADSTBA

R_ADSTBB

SBSTB

AGPCLKI

AGPCLKO

GAD[0..31]13

8.2K

R65

GTRDY#

1 2

R63 8.2K

GIRDY#

1 2

GDEVSEL#

4 4

3 3

2 2

1 1

GSTOP#

ADSTBA

ADSTBB

GFRAME#

GREQ#

GGNT#

SBSTB

RBF#

PIPE#

GPAR13

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PX4_REQ1#17

PX4_REQ2#17

A

8.2K

R64

R220 8.2K

8.2K

R229

R60 8.2K

R219 8.2K

R193 8.2K

R190 8.2K

R202 8.2K

8.2K

R55

8.2K

R195

R222

100K

1 2

ADSTBA13

ADSTBB13

GCLKO13

+3VS

+3VS

ADSTBA

ADSTBB

12

R176

10K

3

12

R177

10K

3

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

SERR#

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

GNT#0

GNT#1

GNT#2

GNT#3

GNT#4

AD[0..31]

CLKRUN#

R155

47

1 2

12

C247

15PF

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

AD[0..31] 17,22,25,34

C/BE#0 17,22,25,34

C/BE#1 17,22,25,34

C/BE#2 17,22,25,34

C/BE#3 17,22,25,34

FRAME# 17,18,22,25,34

IRDY# 17,18,22,25,34

TRDY# 17,18,22,25,34

DEVSEL# 17,18,22,25,34

PAR 17,18,22,25,34

STOP# 17,18,22,25,34

SERR# 17,18,22,34

PLOCK# 18

PHLD# 17,18

PHLDA# 17,18

REQ#0 34

REQ#1 34

REQ#2 17

REQ#3 22

REQ#4 25

GNT#0 34

GNT#1 34

GNT#2

GNT#3 22

GNT#4 25

PCIRST# 17,22,23,25,34

CLKRUN# 13,17,18,22,25,31,34

PCLK_BX 12

+3VS

D

REQ#4

GNT#4

6

7

8

9

10

RP43

10P8R-10K

1 2

R182 10K

1 2

R183 10K

5

REQ#2

4

GNT#2

3

REQ#3

2

GNT#3

1

+3VS

REQ#0

GNT#0

REQ#1

GNT#1

PCI REQ ASSIGMENT

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

MiniPCI(Compal)

MINI PCI

NO USED

PCMCIA CONTROLLER

PCI AUDIO

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

E

+3VS

1C

of

837Friday, December 01, 2000

Page 8

A

B

C

D

E

U12B

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

AB14

AF15

AE15

AC15

AD15

AE16

AD13

AC13

AC25

AB26

AE14

AC14

AA22

AA24

AE13

AD14

AE12

AC12

AF16

AA17

AF12

AB13

AE11

AA10

AA23

AA26

AF11

AD12

AA25

AC22

AF23

AE24

AD23

AC23

AF24

AF17

AB16

AE17

AC17

AF18

AE19

AF19

AC18

AC19

AE20

AD20

AF21

AC21

AF25

AD16

AC16

AD17

AB17

AE18

AD19

AB18

AB19

AF20

AC20

AB20

AE21

AD21

AF22

Y22

CSA0#/RASA0#

CSA#1/RASA1#

CSA2#/RASA2#

CSA3#/RASA3#

CSA4#/RASA4#

CSA5#/RASA5#

DQMA0/CASA0#

DQMA1/CASA1#

DQMA2/CASA2#

DQMA3/CASA3#

DQMA4/CASA4#

DQMA5/CASA5#

DQMA6/CASA6#

DQMA7/CASA7#

DQMB1/CASB1#

DQMB5/CASB5#

WEA#

WEB#

SRASA#

SRASB#

SCASA#

SCASB#

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAB0#

MAB1#

MAB2#

MAB3#

MAB4#

MAB5#

MAB6#

MAB7#

MAB8#

MAB9#

MAB10#

MAB11#

MAB12#

MAB13#

CSB0#/RASB0#

CSB1#/RASB1#

CSB2#/RASB2#

CSB3#/RASB3#

CSA4#/RASB4#

CSA5#/RASB5#

DRAM INTERFACE

4 4

CS0#11

CS2#10

CS3#10

FOR 443ZX-M IS NC PIN

CAS0#10,11

CAS1#10,11

CAS2#10,11

CAS3#10,11

CAS4#10,11

CAS5#10,11

CAS6#10,11

CAS7#10,11

FOR 443ZX-M IS NC PIN

BMWEA#10,11

SRASA#10,11

SCASA#10,11

3 3

FOR 443ZX-M IS NC PIN

CKE011

CKE210

CKE310

FOR 443ZX-M IS NC PIN

2 2

443ZX-M/443BX

MA[0..13]10,11

MA[0..13]

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DCLKO

DCLKRD

DCLKWR

AE25

AD24

AD26

AC24

AC26

AB23

AF4

AE4

AF5

AD6

AE6

AB7

AC7

AF7

AB8

AB9

AC9

AE9

AB10

AC10

AF10

AD11

Y24

Y25

W23

W24

W26

W25

V26

U24

U23

T22

T23

T26

R24

R25

P23

N25

AC5

AE5

AB6

AC6

AF6

AD7

AE7

AC8

AD8

AF8

AE8

AF9

AD10

AE10

AB11

AC11

Y23

Y26

W22

V22

V23

V25

U22

U25

U26

T24

T25

U21

R23

R26

P24

P25

AB21

AB22

AD25

FOR 443ZX-M IS NC PIN

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD6

MDD7

MDD8

MDD9

MDD10

MDD11

MDD12

MDD13

MDD14

MDD15

MDD16

MDD17

MDD18

MDD19

MDD20

MDD21

MDD22

MDD23

MDD24

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

MDD31

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

MDD48

MDD49

MDD50

MDD51

MDD52

MDD53

MDD54

MDD55

MDD56

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63

DCLKO1

R66 33

MDD5

1 8

MDD6

2 7

MDD37

3 6

MDD40

4 5

MDD36

MDD4

MDD7 MD7

MDD38

MDD14

MDD45

MDD44

MDD15

MDD46

MDD47 MD47

MDD12

MDD13

MDD59

1 8

MDD54

2 7

MDD24

3 6

MDD52

4 5

MDD22 MD22

1 8

MDD53

2 7

MDD20

3 6

MDD21

4 5

MDD27

1 8

MDD58

2 7

MDD56

3 6

MDD55

4 5

MDD31

1 8

MDD63

2 7

MDD29

3 6

MDD61

4 5

MDD32

MDD34

MDD3

MDD1

MDD0

MDD33

MDD2

MDD11

1 8

MDD43

2 7

MDD42

3 6

MDD41

4 5

MDD39

1 8

MDD8

2 7

MDD10

3 6

MDD9

4 5

MDD51

1 8

MDD19

2 7

MDD18

3 6

MDD50

4 5

MDD49

1 8

MDD17

2 7

MDD16

3 6

MDD48 MD48

4 5

MDD25

1 8

MDD26

2 7

MDD57

3 6

MDD23

4 5

MDD30

1 8

MDD62

2 7

MDD60

3 6

MDD28

4 5

1 2

R69

15

1 2

12

C102

47PF

MD[0..63]

MD5

MD6

MD37

MD40

MD36

18

MD4

27

36

MD38

45

MD14

18

MD45

27

MD44

36

MD15

45

MD46

18

27

MD12

36

MD13

45

MD59

MD54

MD24

MD52

MD53

MD20

MD21

MD27

MD58

MD56

MD55

MD31

MD63

MD29

MD61

MD32

45

MD34

36

MD35MDD35

27

MD3

18

MD1

18

MD0

27

MD33

36

MD2

45

MD11

MD43

MD42

MD41

MD39

MD8

MD10

MD9

MD51

MD19

MD18

MD50

MD49

MD17

MD16

MD25

MD26

MD57

MD23

MD30

MD62

MD60

MD28

DCLKO 12

DCLKWR 12

MD[0..63] 10,11

RP9

8P4R-10

RP55

8P4R-10

RP53

8P4R-10

RP12

8P4R-10

RP6

8P4R-10

RP46

8P4R-10

RP45

8P4R-10

RP44

8P4R-10

RP13

8P4R-10

RP54

8P4R-10

RP52

8P4R-10

RP8

8P4R-10

RP7

8P4R-10

RP48

8P4R-10

RP5

8P4R-10

RP3

8P4R-10

R70 10K

MA12

1 2

R68 10K

MA10

1 2

R67 10K

MA6

1 2

Pin Name Function Low High Interal Resistor

MAB12#

+3V

MAB10#

MAB6#

Host Frequency Select

Quick Start Select

Host Bus Buffer Mode Select

66MHz

Stop Clock Mode

Desktop GTL+

100MHz

Quick Start Mode

Mobile Low Power

GTL+

Pull-down

Pull-down

Pull-down none

Status Register

NBXCFG[13]

PMCR[3]

1 1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

A

B

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

1C

of

937Friday, December 01, 2000

E

Page 9

A

B

C

D

E

F

G

H

SODIMM X 1

(H:5.6mm)

Support 3 SDRAM CLOC K

PIN 60, 77, 78 Difference

4 4

BANK 2,3

33

10

12

12

R249

R246

C322

1000PF

C313

.1UF

15PF

1 2

33PF

1 2

12

C306

1UF_0805

12

C314

.1UF

C318

C316

12

C321

22UF_1206

CLK_SDRAM212

CLK_SDRAM312

3 3

+3V

12

12

2 2

+3V

12

C307

.1UF

C311

.1UF

C324

.1UF

12

C310

.1UF

CLK_SDRAM2

CLK_SDRAM3

MA[0..13]9,11

MD[0..63]9,11

12

C323

1000PF

12

C309

.1UF

12

12

1 2

1 2

MA[0..13]

MD[0..63]

C308

1000PF

C315

.1UF

CAS3#9,11

CAS2#9,11

CLK_SDRAM2

SRASA#9,11

BMWEA#9,11

CS2#9

CS3#9

CAS1#9,11

CAS0#9,11

SDAP412,17

+3V

1 2

R250 10K

+3V +3V

JP13

1

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MA0

MA1

MA2

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MA6

MA8 MA11

MA10

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

VSS

DQ0

DQ1

DQ2

DQ3

VCC

DQ4

DQ5

DQ6

DQ7

VSS

CE0#

CE1#

VCC

A0

A1

A2

VSS

DQ8

DQ9

DQ10

DQ11

VCC

DQ12

DQ13

DQ14

DQ15

VSS

RESVD/DQ64

RESVD/DQ65

CLK0

VCC

RAS#

WE#

S0#

S1#

OE#

VSS

RESVD/DQ66

RESVD/DQ67

VCC

DQ16

DQ17

DQ18

DQ19

VSS

DQ20

DQ21

DQ22

DQ23

VCC

A6

A8

VSS

A9

A10

VCC

CE2#/RESVD

CE3#/RESVD

VSS

DQ24

DQ25

DQ26

DQ27

VCC

DQ28

DQ29

DQ30

DQ31

VSS

SDA

VCC

SODIMM-J34

RESVD/DQ68

RESVD/DQ69

RESVD/DQ70

RESVD/DQ71

CE6#/RESVD

CE7#/RESVD

VSS

DQ32

DQ33

DQ34

DQ35

VCC

DQ36

DQ37

DQ38

DQ39

VSS

CE4#

CE5#

VCC

VSS

DQ40

DQ41

DQ42

DQ43

VCC

DQ44

DQ45

DQ46

DQ47

VSS

CKE0

VCC

CAS#

CKE1

A12

A13

CLK1

VSS

VCC

DQ48

DQ49

DQ50

DQ51

VSS

DQ52

DQ53

DQ54

DQ55

VCC

BA0

VSS

BA1

A11

VCC

VSS

DQ56

DQ57

DQ58

DQ59

VCC

DQ60

DQ61

DQ62

DQ63

VSS

SCL

VCC

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

A3

32

A4

34

A5

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

A7

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

MA3

MA4

MA5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MA12

MA13

CLK_SDRAM3

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MA7

MA12MA9

MA13

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

1 2

R245 10K

CAS7# 9,11

CAS6# 9,11

CKE2 9

SCASA# 9,11

CKE3 9

CAS5# 9,11

CAS4# 9,11

SCKP4 12,17

+3V

SODIMM

1 1

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

A

B

C

D

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

F

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

G

1C

of

10 37Friday, December 01, 2000

H

Page 10

A

B

C

D

E

F

G

H

32MB/64MB SDRAM

64Mbit 4Mx16 : Row: MA0-MA11

Column: MA0-MA7

Bank address: 2

4 4

3 3

2 2

128Mbit 8Mx16 : Row: MA0-MA11

Column: MA0-MA8

Bank address: 2

CLK_SDRAM0

12

R244

33

12

C300

15PF

CLK_SDRAM0 12

PLACE THE TERMINATOR

ON THE DRAM INPUT

BANK0

BMWEA#9,10

SCASA#9,10

SRASA#9,10

CS0#9

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA13

MA12

MA11

CAS0#

CAS1#

BMWEA#

SCASA#

SRASA#

CS0#

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA13

MA12

MA11

CAS2#

CAS3#

BMWEA#

SCASA#

SRASA#

CS0#

+3V

11427394349

23 2

A0 DQ0

24

A1

VCC

VCC

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BA1

A13/BA0

DQMH

WE#

CAS#

RAS#

CS#

+3V

11427394349

VCC

VCCQ

VSS

VSS

VSS

2841546124652

VCC

VCC

VCC

VCCQ

VCCQ

VSS

VSS

VSS

VSSQ

2841546124652

25

26

29

30

31

32

33

34

22

35

21

20

39

16

17

18

19

23 2

A0 DQ0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10/AP

35

A11

21

A12/BA1

20

A13/BA0

39

DQMH

16

WE#

17

CAS#

18

RAS#

19

CS#

VCCQ

VSSQ

VCCQ

VSSQ

VCCQ

VSSQ

VCCQ

VSSQ

VCCQ

VSSQ

VSSQ

VSSQ

U19

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

CKE

CLK

RVD

RVD

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

CKE

CLK

RVD

RVD

U21

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

8MX16S

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

8MX16S

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

CKE0

CLK_SDRAM0

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

CKE0

CLK_SDRAM0

CKE0 9

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA13

MA12

MA11

CAS4#

CAS5#

BMWEA#

SCASA#

SRASA#

CS0#

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA13

MA12

MA11

CAS6#

CAS7#

BMWEA#

SCASA#

SRASA#

CS0#

+3V

11427394349

23 2

A0 DQ0

24

A1

VCC

VCC

25

26

29

30

31

32

33

34

22

35

21

20

39

16

17

18

19

23 2

24

25

26

29

30

31

32

33

34

22

35

21

20

39

16

17

18

19

VCC

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BA1

A13/BA0

DQMH

WE#

CAS#

RAS#

CS#

VSS

VSS

2841546124652

+3V

11427394349

A0 DQ0

A1

VCC

VCC

VCC

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BA1

A13/BA0

DQMH

WE#

CAS#

RAS#

CS#

VSS

VSS

2841546124652

VCCQ

VSS

VCCQ

VSS

VCCQ

VCCQ

VSSQ

VSSQ

VCCQ

VCCQ

VSSQ

VSSQ

VCCQ

VSSQ

VSSQ

VCCQ

VSSQ

VSSQ

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

CKE

RVD

RVD

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

CKE

RVD

RVD

CLK

CLK

U25

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

8MX16S

U20

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

8MX16S

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

CKE0

CLK_SDRAM0

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

CKE0

CLK_SDRAM0

+3V +3V

12

12

C343

C338

.1UF

C330

1000PF

12

A

C333

1000PF

1000PF

+3V +3V

12

1 1

+

C335

4.7UF_A

12

C364

.1UF

12

C363

.1UF

12

C349

.1UF

12

12

C342

.1UF

12

C359

.1UF

B

C340

1UF_0805

12

C347

.1UF

12

12

C360

.1UF

C369

1UF_0805

12

12

C

1000PF

C329

C361

.1UF

12

C365

1UF_0805

12

C331

1000PF

12

C328

.1UF

12

C327

.1UF

12

12

C341

.1UF

12

C346

.1UF

D

12

C332

.1UF

12

C339

.1UF

12

C348

C362

.1UF

1000PF

12

12

C357

C344

1UF_0805

.1UF

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

F

Title

Size Document Number Rev

B

Date: Sheet

MA[0..13]9,10

MD[0..63]9,10

CAS0#9,10

CAS1#9,10

CAS2#9,10

CAS3#9,10

CAS4#9,10

CAS5#9,10

CAS6#9,10

CAS7#9,10

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

G

MA[0..13]

MD[0..63]

CAS0#

CAS1#

CAS2#

CAS3#

CAS4#

CAS5#

CAS6#

CAS7#

1C

of

11 37Friday, December 01, 2000

H

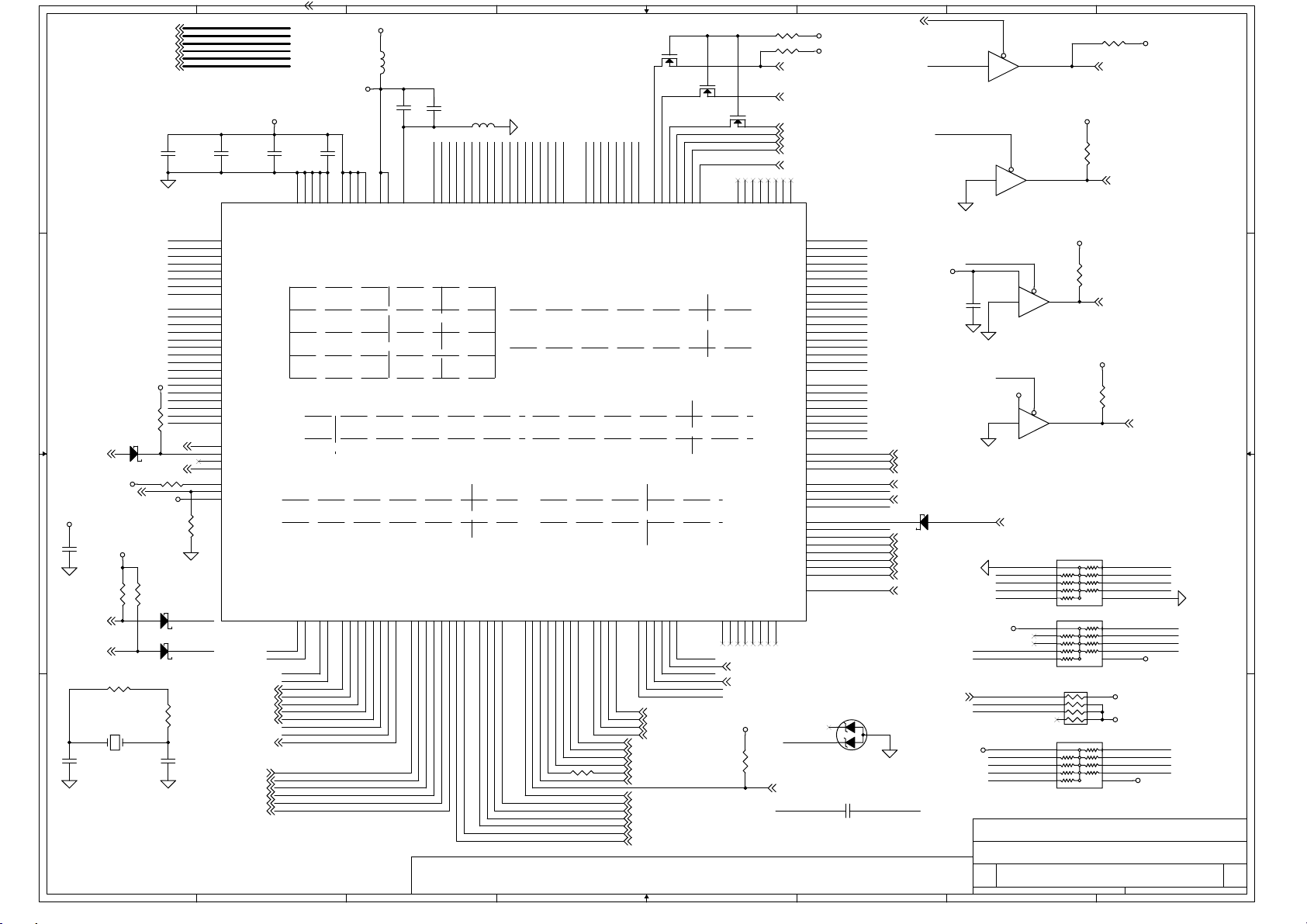

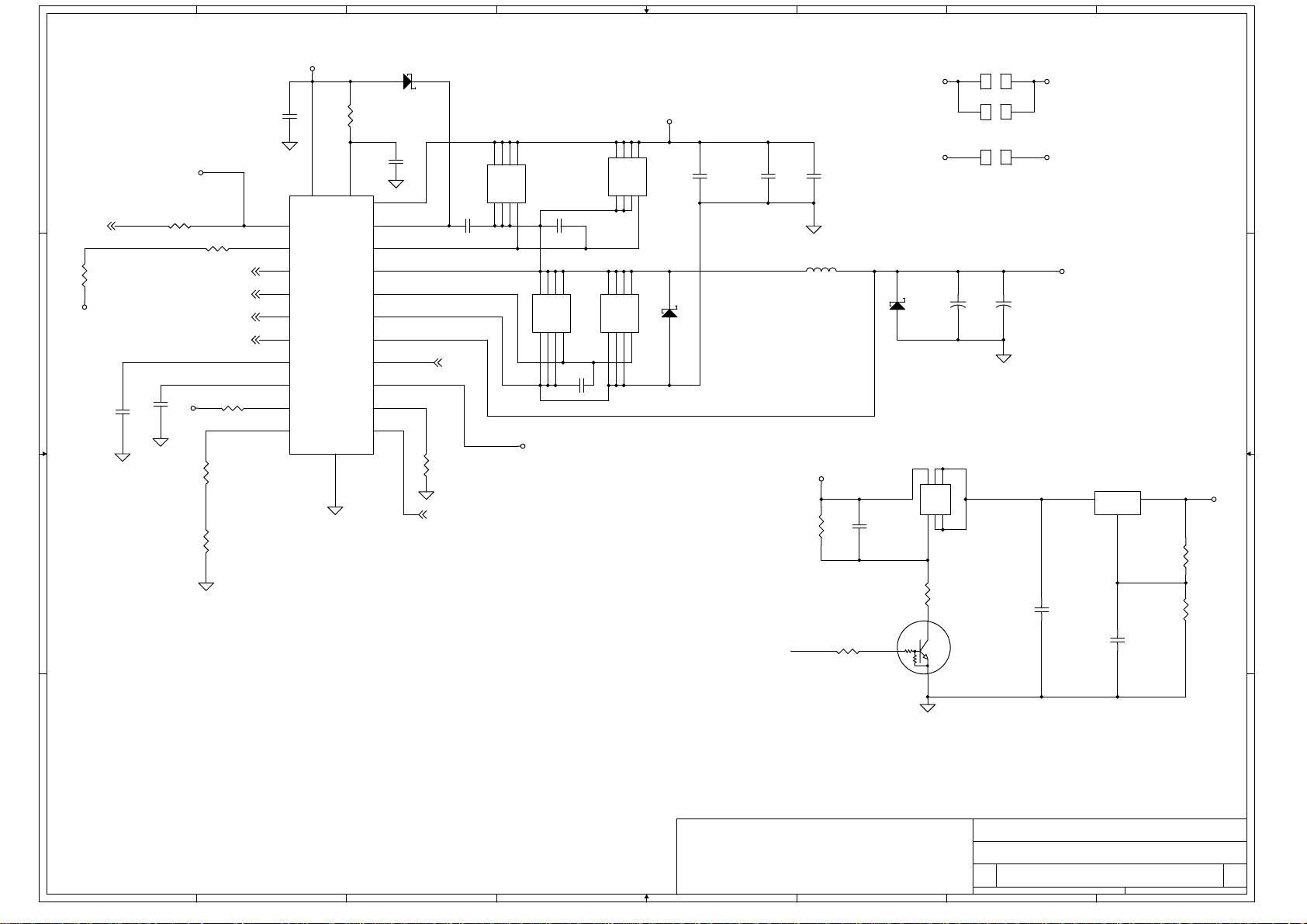

Page 11

A

B

CLOCK GENERATOR & BUFFER

C

D

E

21

12

12

R186

10K

12

C275

.01UF

C271

1000PF

C254

10PF

+3VS

+VCLK_+3VS

C259

.01UF

12

SDAP410,17

SCKP410,17

12

12

C258

1000PF

C272

1000PF

1 2

1 2

R168

12

2M_0603

PWRDWN#

R164

10K

Y1

14.318MHZ

C257

10PF

SDAP4

SCKP4

12

R188 10

12

+3VS

R167

@10K

R163

10K

12

C256

.1UF

1 2

12

12

U13

7

VDDPCI

12

C268

.1UF

15

VDDPCI

21

VDD48

25

VDDCOR

46

VDDREF

48

VDDREF

28

VDDSDRAM

34

VDDSDRAM

40

VDDC

4

XIN

5

XOUT

39

SDRAM_IN

6

MODE

18

SEL_100/66#

26

SDRAM7/PCI_STP#

27

SDRAM6/CPU_STP#

44

PWR_DWN#

19

SDATA

20

SCLK

47

NC

3

GND

10

GND

17

GND

24

GND

31

GND

37

GND

43

GND

ICS9248-92

REF0

REF1

REF2

CPUCLK1

CPUCLK0

PCICLKF

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

48/24MHZA

48/24MHZB

SDRAM5

SDRAM4

SDRAM3

SDRAM2

SDRAM1

SDRAM0

SDRAMFB

CLK_14MOSC

2

CLK_14.3M_SIO

1

CLK_14.3MGCL

45

CLK_HCLK_CPU HCLK_CPU

41

42

CLK_PCLK_PIIX4

8

CLK_PCLK_BX

9

CLK_PCLK_PCM

11

CLK_PCLK_MINI

12

CLK_PCLK_SIO

13

CLK_PCLK_AUD

14

16

CLK_48M

22

23

29

30

SDRAM3

32

SDRAM2

33

35

SDRAM0

36

CLK_DCLKWR

38

IMI C9806 CLOCK TABLE

PIN 6 PIN 18

S1 S0 CPUCLK PCICLK

00

01

1X

60MHZ 30MHZ

33MHZ66MHZ

100MHZ 33MHZ

R175 22

1 2

R174 22

1 2

R189 22

1 2

R194 15

1 2

R171 33

1 2

R162 33

1 2

R161 33

1 2

R170 33

1 2

R160 33

1 2

R169 33

1 2

R172 22

1 2

R201 10

1 2

R204 22

1 2

R198 10

1 2

R200 22

1 2

12

C280

33PF

*

ICS 9248-92 CLOCK TABLE

MODE PIN26,27 FUNCTION

1

*

0

14MOSC 17

14.3M_SIO 31

14.3MGCL 6

HCLK_CPU 4,7

PCLK_PIIX4 17

PCLK_BX 8

PCLK_PCM 22

PCLK_MINI 34

PCLK_SIO 31

PCLK_AUD 25

48M 17

CLK_SDRAM3 10

CLK_SDRAM2 10

CLK_SDRAM0 11

DCLKWR 9

SDRAM7,SDRAM6

PCI_STOP#, CPU_STOP#

SEL_100/66# CPUCLK PCICLK

0

*

1

66.6MHZ 33.3MHZ

33.3MHZ100MHZ

+3VS

4 4

+3V

+2.5V_CLK

3 3

2 2

1 1

CHB2012U170

1 2

CHB2012U170

4.7UF_0805_10V

1 2

CHB2012U170

4.7UF_0805_10V

PCI_STP#17

GT_CPU_STP#6

L24

L23

DCLKO9

SUSA#17,28

12

C267

4.7UF_0805_10V

12

C276

12

C282

R199

@47

C279

@15PF

SUSA#

12

12

12

12

.01UF

RB751V

D18

12

C269

.1UF

+VCLK_SDRAM

C273

.1UF

+VCLK_CPUP

C274

L22

1 2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL

ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION.

THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION

OF R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER

THIS SHEET NOR THE INFORMATION CONTAINS MAY BE USED BY OR DISCLOSED TO ANY

A

B

THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Title

Size Document Number Rev

B

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, M/B LA-971

401166

1C

of

12 37Friday, December 01, 2000

E

Page 12

5

4

3

2

1

+2.5V

+2.5V

T=80mil

+

C180

10UF_P_6.3V

D D

(175mA)

T=20mil

+3V

C C

R403

100K_1%_0603

C528

@2.2UF_0805_X7R

+2.5VP

B B

A A

4

3

+

C233

22UF_B_6.3V

1 2

GGREQ#17

VIN

ON/OFF#

80mil

JOPEN1

2MM

Q14

2SB1132

3 1

2

1

EXT

VSS

2

12

R192

10K

3

VOUT

U10

S-816A25

+2.5V

D19

RB717F

T=40mil

12

L14

CHB2012B121

C27

.1UF

5

+3V+3VS

12

1

2

1 2

R134

12

R196

8.2K

ADSTBA8

ADSTBB8

CLKRUN#8,17,18,22,25,31,34

(800mA)

0_0805

C38

.1UF

12

L17

CHB2012B121

(25mA)

T=20mil

AVDD

+

C158

10UF_P_6.3V

+

AGP_BUSY#

GREQ#

T=40mil

12

12

C199

.01UF

12

+2.5VP

C232

22UF_B_6.3V

GCLKO8

1 2

R40 @0

@10PF

C31

.1UF

R36

@33

C58

VDDC

@10PF

PVDD

R39

@33

C66

12

12

R28

@33

C166

+

10UF_P_6.3V

12

12

12

12

C47

@10PF

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GCLKO

1 2

CBRST#22,23,34