Page 1

5

4

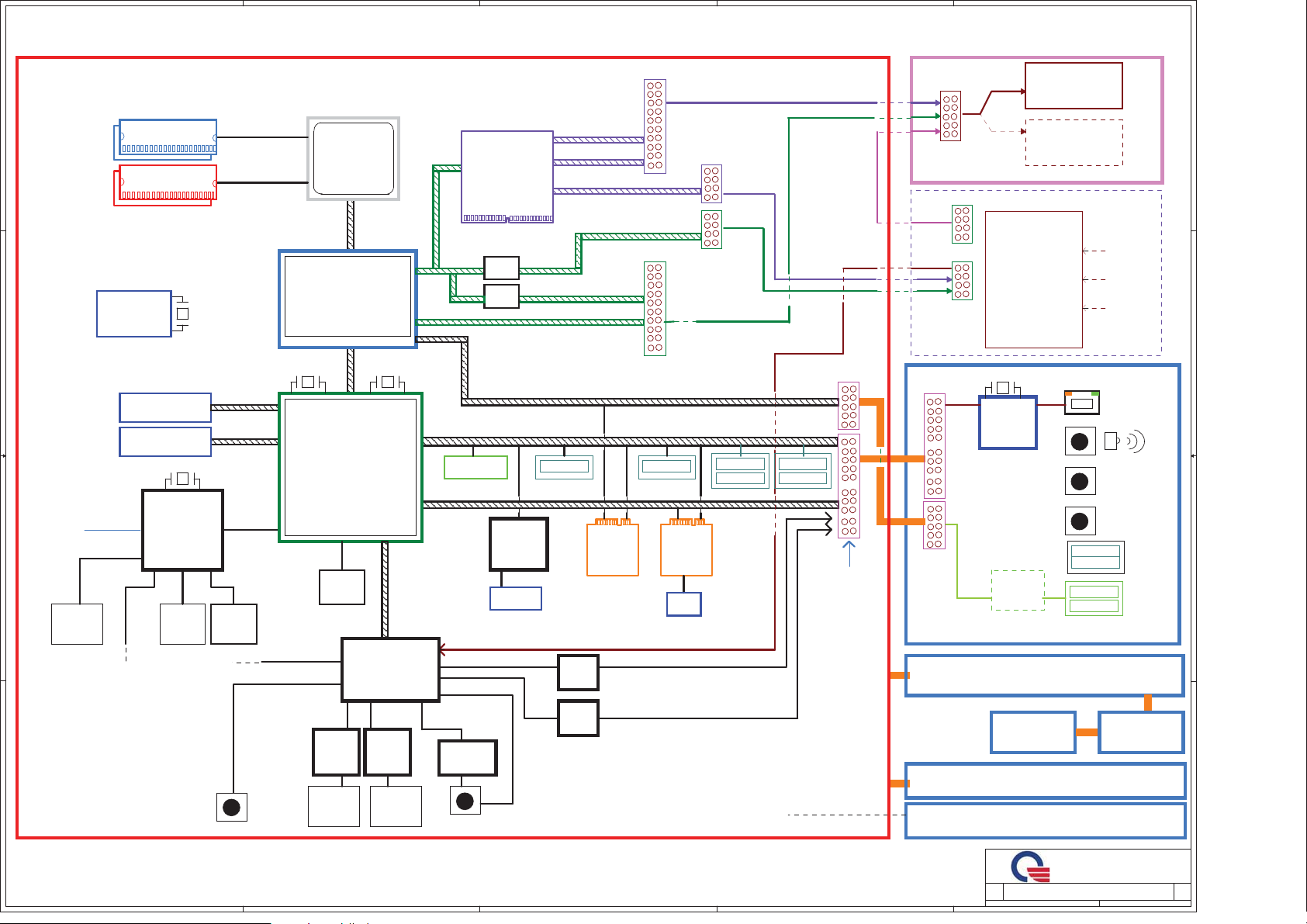

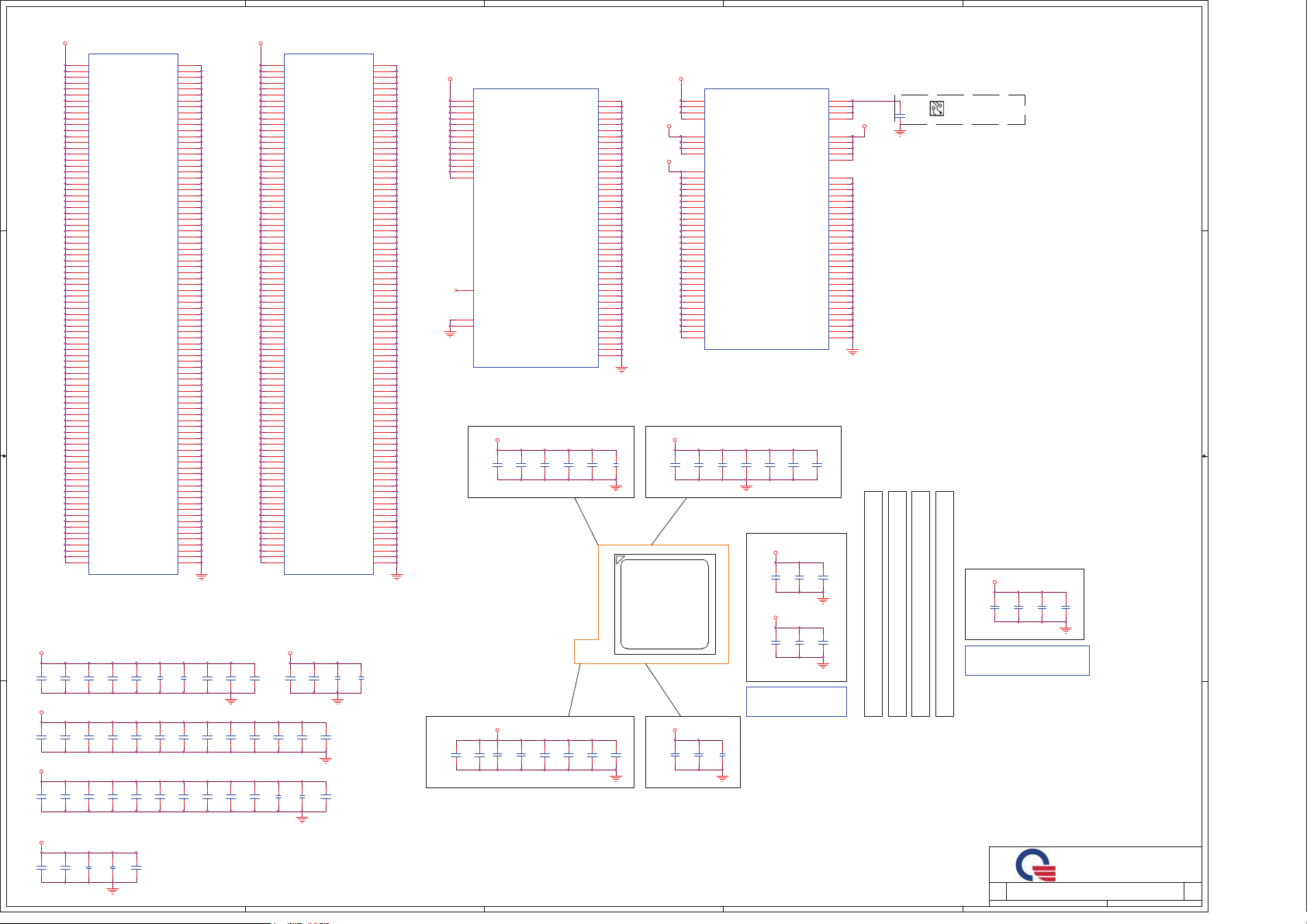

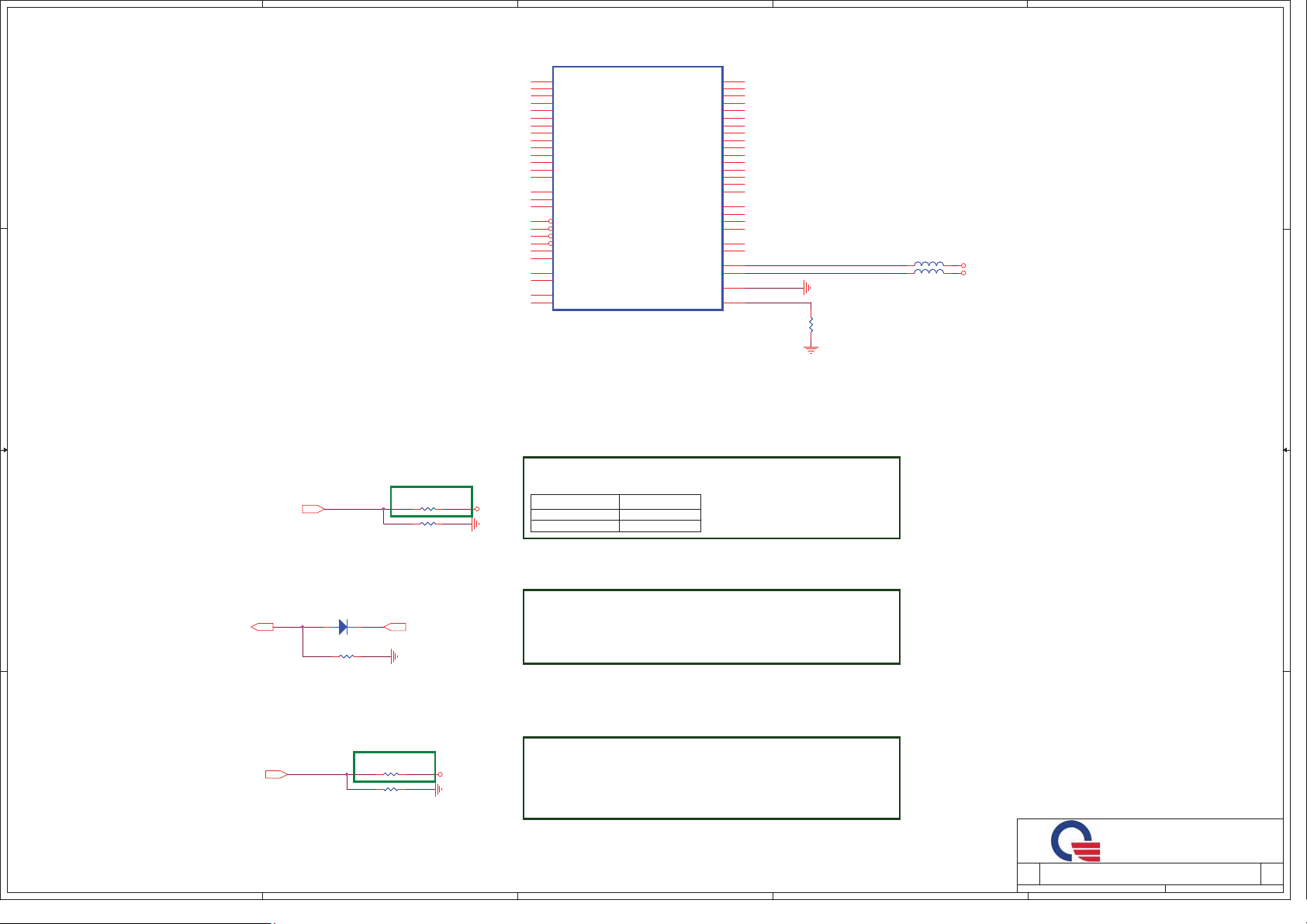

M3 System Block Diagram

3

2

1

/9'6'3&211

M/B

D D

C C

CLOCK GEN

SLG8SP628

IR Blaster

DDR3-SODIMM 1&2

DDR3-SODIMM 3&4

14.318MHz

6$7$+''RU66'

6$7$2''

32.768KHz

,7(.%&

,7

DDR3 1066/1333 MT/s

DDR3 1066/1333 MT/s

SATA Gen2

SATA Gen1

LPC

I2C

B B

)$1

*6HQVRU

85$7

63,520

'0LF

AM3 socket

CPU

AMD

Athlon II

HT-Link

NB

AMD

RS880M

A-Link

SB

AMD

SB820M

63,520

2SWLRQ

32.768KHz25MHz

$]DOLD

$XGLR&RGHF

,'7+''

PCIE2.0 16X

MXM 3.0

Type A

MUX

0~3

PI3PCIE

2612-A

MUX

4~7

PI3PCIE

2612-A

PCI-E_NB

USB2.0

&DPHUD

PCI-E_SB

UMA_DP2

UMA_DP1

UMA_LVDS

LQ

576*5

&DUGUHDGHU

&RQQ

MXM_LVDS

MXM_DP1

MXM_DP3

86%3RUWV

)RUGRQJOH

'59

SLQ

/9'6'3&211

SLQ

86%3RUWV

)RU%7

0LQL3&,(

&DUG

0LQL3&,(

&DUG

:/$1%7

5)LQ

79

'3&211

SLQ

'3&211

SLQ

a

86%3RUWV

6LGH

63',)

/LQH2XW

SLQSLQ

a

86%3RUWV

5HDU

IR Blaster

LED Panel

3DQHO&RQQHFWRU

Scalar Board

SLQ

SLQ

3&,(B6%B

SLQ

SLQ

3&,(B1%B

25MHz

*/$1

57(

1(&

86%

Rear I/O Board

ODD board

LCD Panel (LVDS)

LCD Panel (DP)

ST Mars

+'0,LQ

+'0,LQ

2SWLRQ

$9LQ

5-

,5%ODVWHU

6XE:RRIHU

/LQH2XW

86%3RUWV

86%3RUWV

86%3RUWV

86%3RUWV

FRQQHFW6FDODU

$8',2

$PSOLILHU

660

$8',2

$PSOLILHU

660 73$$

0LF

'59

6XE:RRIHU

PWR BTN

ODD Eject

IR Board

A A

/LQHLQ

5

&RQQHFWRUWR

LQW6SHDNHU

&RQQHFWRUWR

LQW6SHDNHU

4

+HDG3KRQH0LF&RPER-DFN

&RQQHFW$XGLR&RGHF

DMic

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Nu mb e r Rev

Size Document Nu mb e r Rev

Size Document Nu mb e r Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

PROJECT :

System Block Diagram

System Block Diagram

System Block Diagram

ZN8

ZN8

ZN8

143Monday, March 22, 2010

143Monday, March 22, 2010

1

143Monday, March 22, 2010

A

A

A

of

of

of

Page 2

5

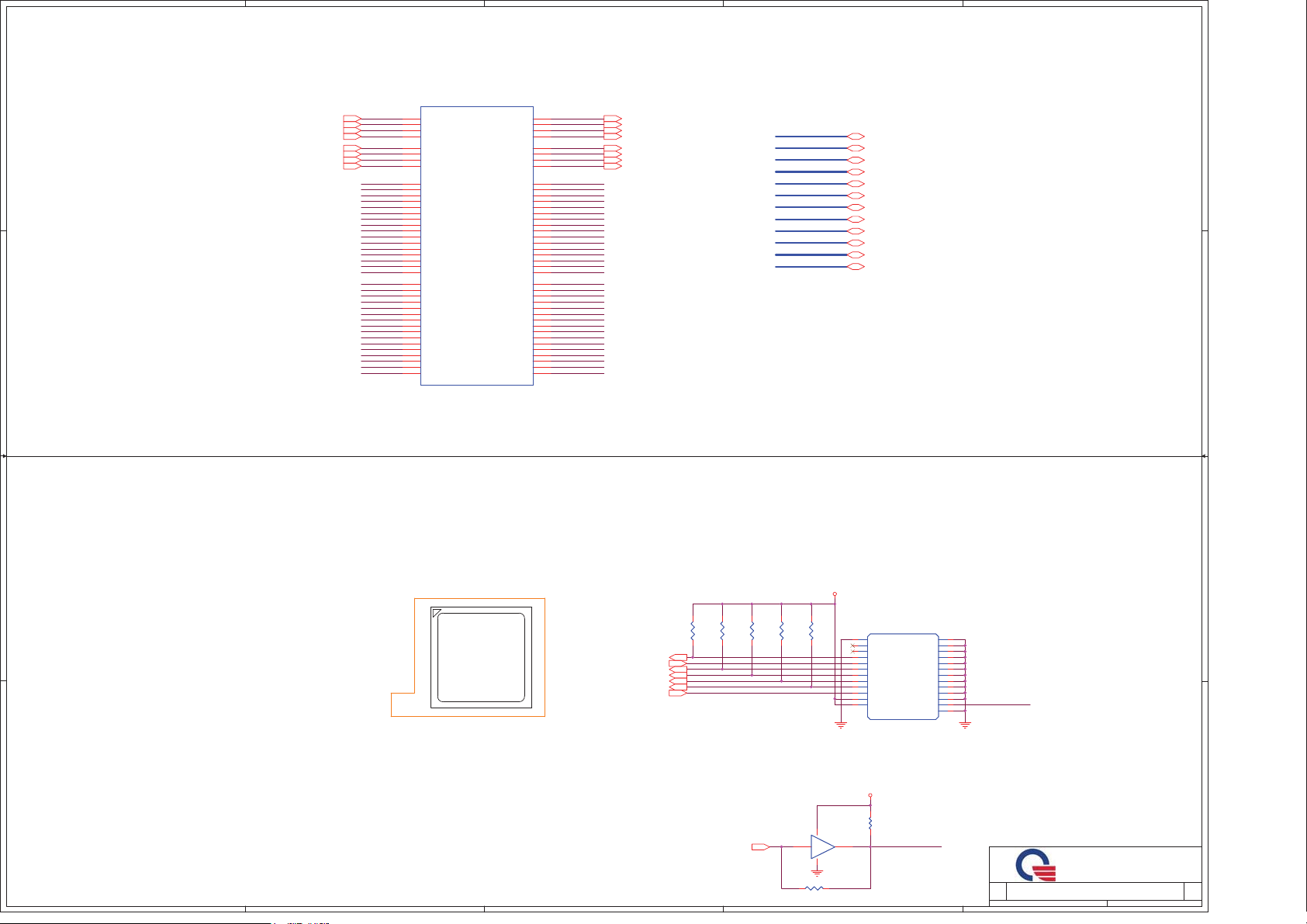

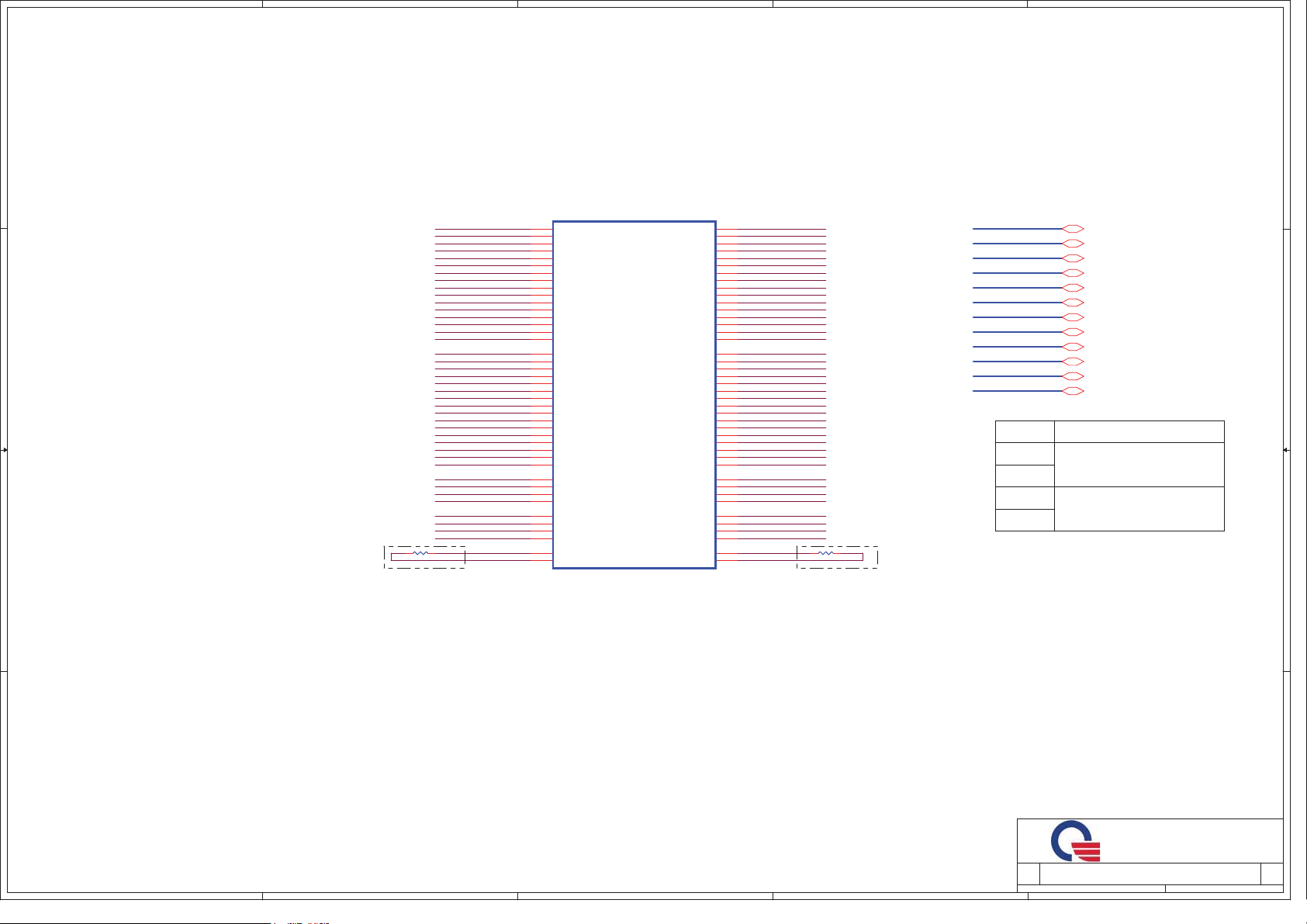

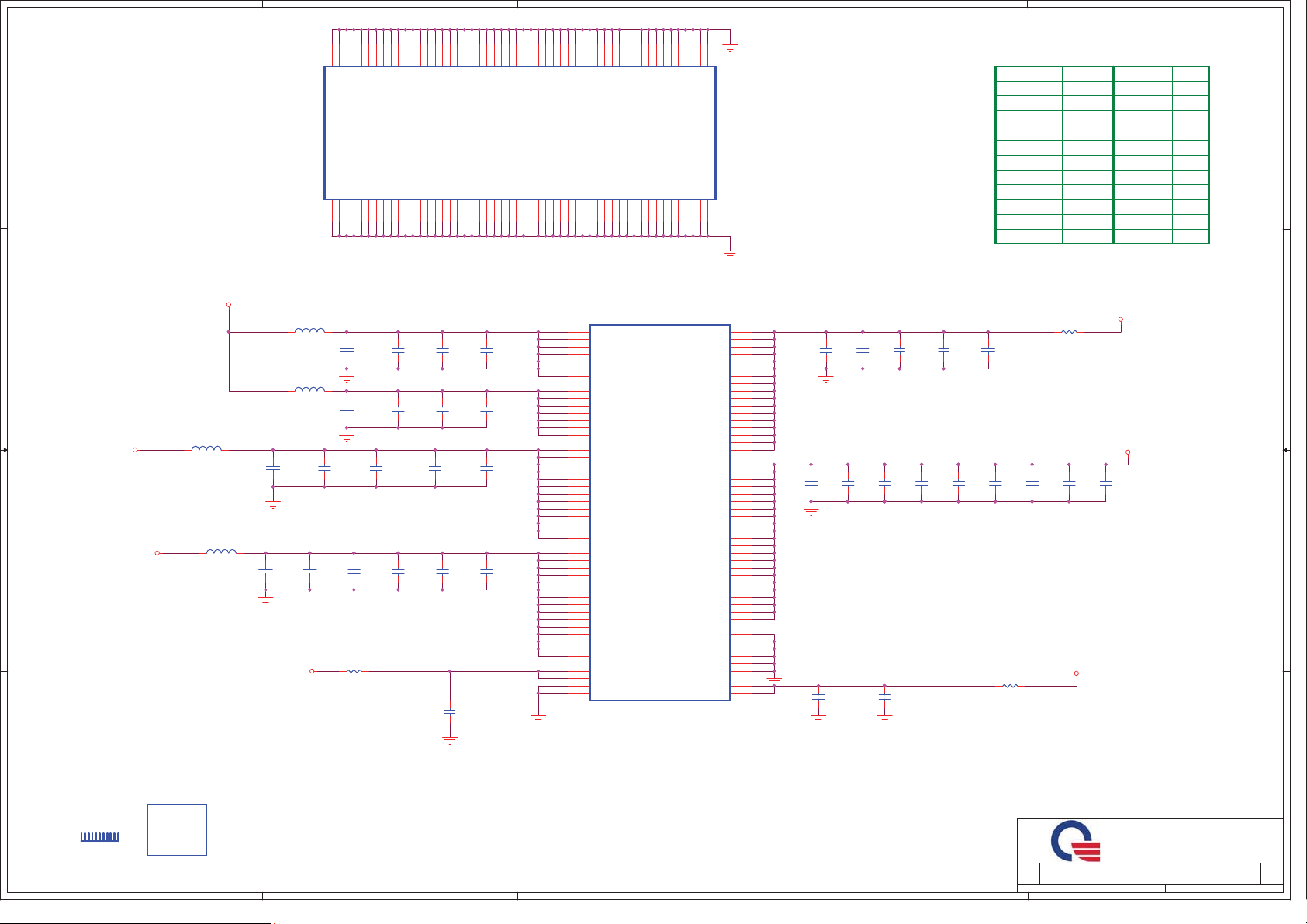

CLK_GEN_SLG8SP628

4

3

2

1

VCC3 CLK_VDD CLK_VDDIO

L10

L10

BK1608HS600

BK1608HS600

22U/6.3V_8

D D

22U/6.3V_8

C113

C113

C117

0.1u/10V_4

0.1u/10V_4

C117

0.1u/10V_4

0.1u/10V_4

C92

C92

C517

C517

0.1u/10V_4

0.1u/10V_4

C495

C495

0.1u/10V_4

0.1u/10V_4

C488

C488

0.1u/10V_4

0.1u/10V_4

C491

C491

0.1u/10V_4

0.1u/10V_4

C519

C519

0.1u/10V_4

0.1u/10V_4

C520

C520

0.1u/10V_4

0.1u/10V_4

,&6/356 31$/356

6/*63

5701

U20

U20

4

CLK_VDD_USB

L46

L46

BK1608HS600

BK1608HS600

C C

CLK_VDD

B B

R86 8.2K_4R86 8.2K_4

CLK_PD#

C496

C496

0.1u/10V_4

0.1u/10V_4

C511 33PC511 33P

C500 33PC500 33P

C493

C493

2.2U_0805

2.2U_0805

21

Y4

Y4

14.318MHZ/20P

14.318MHZ/20P

PCLK_SMB13,17,18,19,20,24

PDAT_SMB13,17,18,19,20,24

C492

C492

10uF_0805

10uF_0805

CG_XIN

CG_XOUT

CLK_VDDVCC3

C486

C486

22U/6.3V_8

22U/6.3V_8

CLK_VDDIO

1 2

CG_XIN

CG_XOUT

CLK_PD#

T106T106

T114T114

T115T115

T116T116

T117T117

VDDDOT

16

VDDSRC

26

VDDATIG

35

VDDSB_SRC

40

VDDSATA

48

VDDCPU

55

VDDHTT

56

VDDREF

63

VDD48

11

VDDSRC_IO0

17

VDDSRC_IO1

25

VDDATIG_IO

34

VDDSB_SRC_IO

47

VDDCPU_IO

1

GND48

7

GNDDOT

10

GNDSRC0

18

GNDSRC1

24

GNDATIG

33

GNDSB_SRC

43

GNDSATA

46

GNDCPU

52

GNDHTT

60

GNDREF

61

X1

62

X2

2

SMBCLK

3

SMBDAT

51

PD#

23

CLKREQ0#

45

CLKREQ1#

44

CLKREQ2#

39

CLKREQ3#

38

CLKREQ4#

SLG8SP628

SLG8SP628

31$/63

31$/

CPUK8_0T

CPUK8_0C

ATIG0T

ATIG0C

ATIG1T

ATIG1C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

QFN64

QFN64

TGND065TGND166TGND267TGND368TGND469TGND570TGND671TGND772TGND873TGND9

SRC2C

SRC3T

SRC3C

SRC4T

SRC4C

SRC6T/SATAT

SRC6C/SATAC

SRC7T/27M_SS

SRC7C/27M_NS

HTT0T/66M

HTT0C/66M

48MHz_0

REF0/SEL_HTT66

REF1/SEL_SATA

REF2/SEL_27

74

CPUCLK_R

50

CPUCLK#_R

49

NBGFX_CLK_R NBGFX_CLK

30

NBGFX_CLK#_R NBGFX_CLK#

29

CLK_PCIE_MXM_R CLK_MXM

28

CLK_PCIE_MXM#_R

27

CLK_SBLINK_R CLK_SBLINK

37

CLK_SBLINK#_R CLK_SBLINK#

36

SBSRC_CLK_R

32

SBSRC_CLK#_R

31

22

21

20

CLK_PCIE_TV#_R

19

15

14

13

12

CLK_PCIE_USB3.0_R CLK_PCIE_USB3.0

9

8

CLK_PCIE_LOMP_R CLK_PCIE_LOMP

42

41

6

5

NBHT_REFCLK_R

54

NBHT_REFCLK#_R

53

CLK_48M_USB_R

64

SEL_HTT66

59

SEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATA

58

SEL_27

57

C112

C112

*10p/50V_4

*10p/50V_4

VCC1.2

Place within 0.5"

of CLKGEN

B-1

RP23 0X2RP23 0X2

RP20 0X2RP20 0X2

RP19 0X2RP19 0X2

RP25 0X2RP25 0X2

RP28 0X2RP28 0X2

RP17 0X2RP17 0X2

RP16 0X2RP16 0X2

RP15 0X2RP15 0X2

RP24 0X2RP24 0X2

T76T76

T75T75

RP10 0X2RP10 0X2

R294 22_4R294 22_4

R87 33_4R87 33_4

C487

C487

*10p/50V_4

*10p/50V_4

L16

L16

BK1608HS600

BK1608HS600

Clock chip has internal serial terminations

for differencial pairs, external resistors are

reserved for debug purpose.

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

Ra

R308 158/F_4R308 158/F_4

R307 90.9/F_4R307 90.9/F_4

C121

C121

22U/6.3V_8

22U/6.3V_8

R319 *261/F_4R319 *261/F_4

CLK_MXM#

SBSRC_CLK

SBSRC_CLK#

CLK_PCIE_TVCLK_PCIE_TV_R

CLK_PCIE_TV#

CLK_PCIE_WLANCLK_PCIE_WLAN_R

CLK_PCIE_WLAN#CLK_PCIE_WLAN#_R

CLK_PCIE_USB3.0#CLK_PCIE_USB3.0#_R

CLK_PCIE_LOMNCLK_PCIE_LOMN_R

CLK_NB_HTREF_PR

CLK_NB_HTREF#_PR

CLK_48M_USB

EXT_NB_OSC

Rb

EXT_SB_OSC

C111

C111

0.1u/10V_4

0.1u/10V_4

CPUCLK

CPUCLK#

C489

C489

C122

C122

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

CPUCLK 5

CPUCLK# 5

NBGFX_CLK 9

NBGFX_CLK# 9

CLK_MXM 21

CLK_MXM# 21

CLK_SBLINK 9

CLK_SBLINK# 9

SBSRC_CLK 12

SBSRC_CLK# 12

CLK_PCIE_TV 24

CLK_PCIE_TV# 24

CLK_PCIE_WLAN 24

CLK_PCIE_WLAN# 24

CLK_PCIE_USB3.0 30

CLK_PCIE_USB3.0# 30

CLK_PCIE_LOMP 30

CLK_PCIE_LOMN 30

CLK_NB_HTREF_PR 9

CLK_NB_HTREF#_PR 9

CLK_48M_USB 13,22

EXT_NB_OSC 9

EXT_SB_OSC 13

B-34

C497

C497

0.1u/10V_4

0.1u/10V_4

C518

C518

C521

C521

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

To CPU

To NB

To NB

To SB

To LAN Controller

To Mini PCIE Slot(TV)

To Mini PCIE Slot(WLAN)

To 6 in 1 Controller

To USB 3.0

To NB HT BUS

To SB USB

To NB

200 Mhz

RS880M for VGA

100 Mhz

100 Mhz

100 Mhz

48 Mhz

CLOCK INPUT TABLE

66 MHz 3.3V single ended HTT clock

SEL_HTT66

CLK_VDD

R85

R85

*8.2K_4

*8.2K_4

A A

R312

R312

8.2K_4

8.2K_4

5

4

R299

R299

8.2K_4

8.2K_4

SEL_SATA

SEL_HTT66

SEL_27

R90

R90

8.2K_4

8.2K_4

3

SEL_SATA

SEL_27

1

*0 100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

1*

0

100 MHz spreading differential SRC clock

1

27MHz and 27M SS outputs

0*

100 MHz SRC clock

* default

2

CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPPSB_REFCLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock Generator

Clock Generator

Clock Generator

Date: Sheet

Date: Sheet

Date: Sheet

RS780

100M DIFF

100M DIFF

14M SE (1.1V)

vref

100M DIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

100M DIFF

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZN8

ZN8

ZN8

243Monday, March 22, 2010

243Monday, March 22, 2010

243Monday, March 22, 2010

of

of

1

of

1A

1A

1A

Page 3

5

4

3

2

1

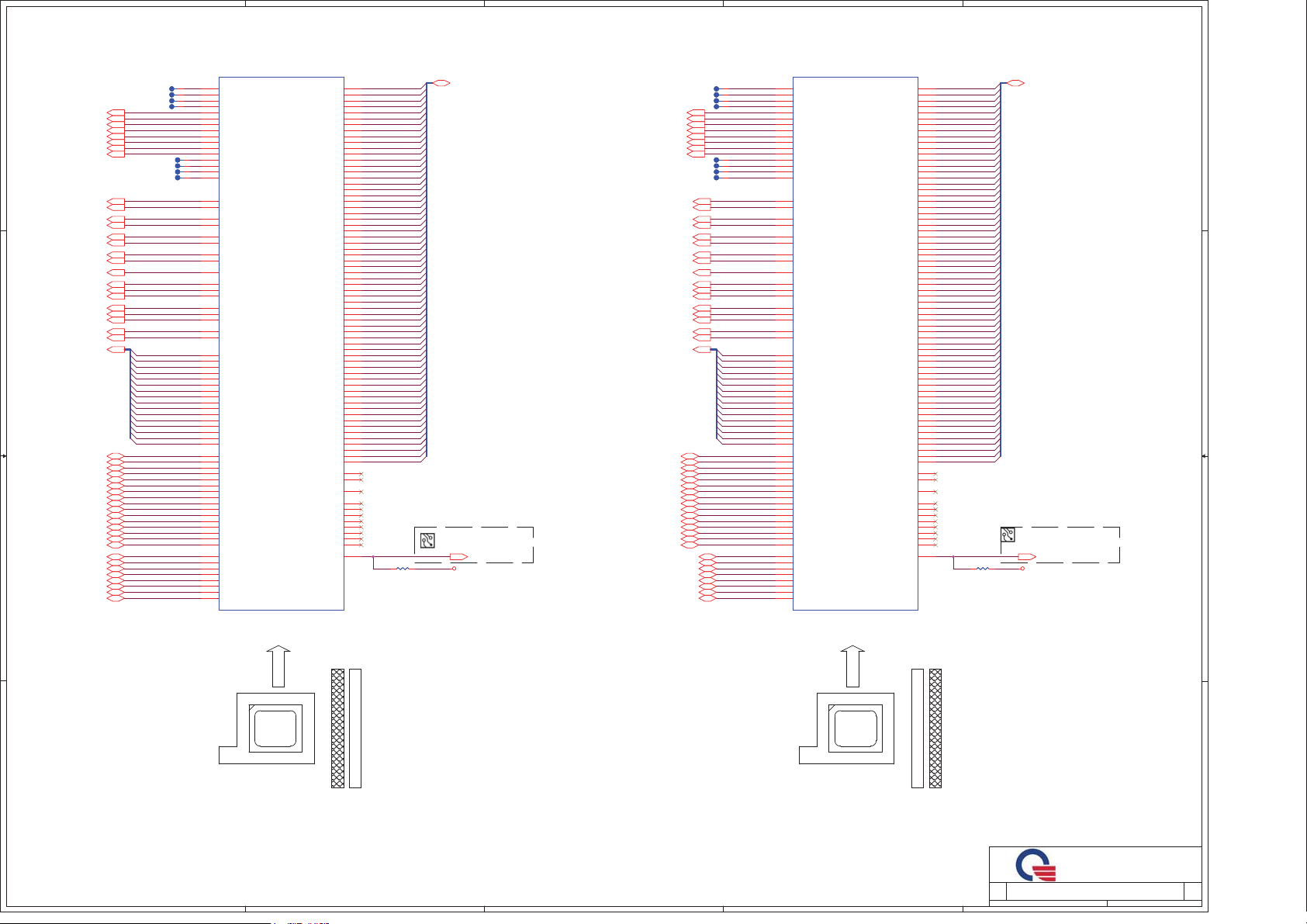

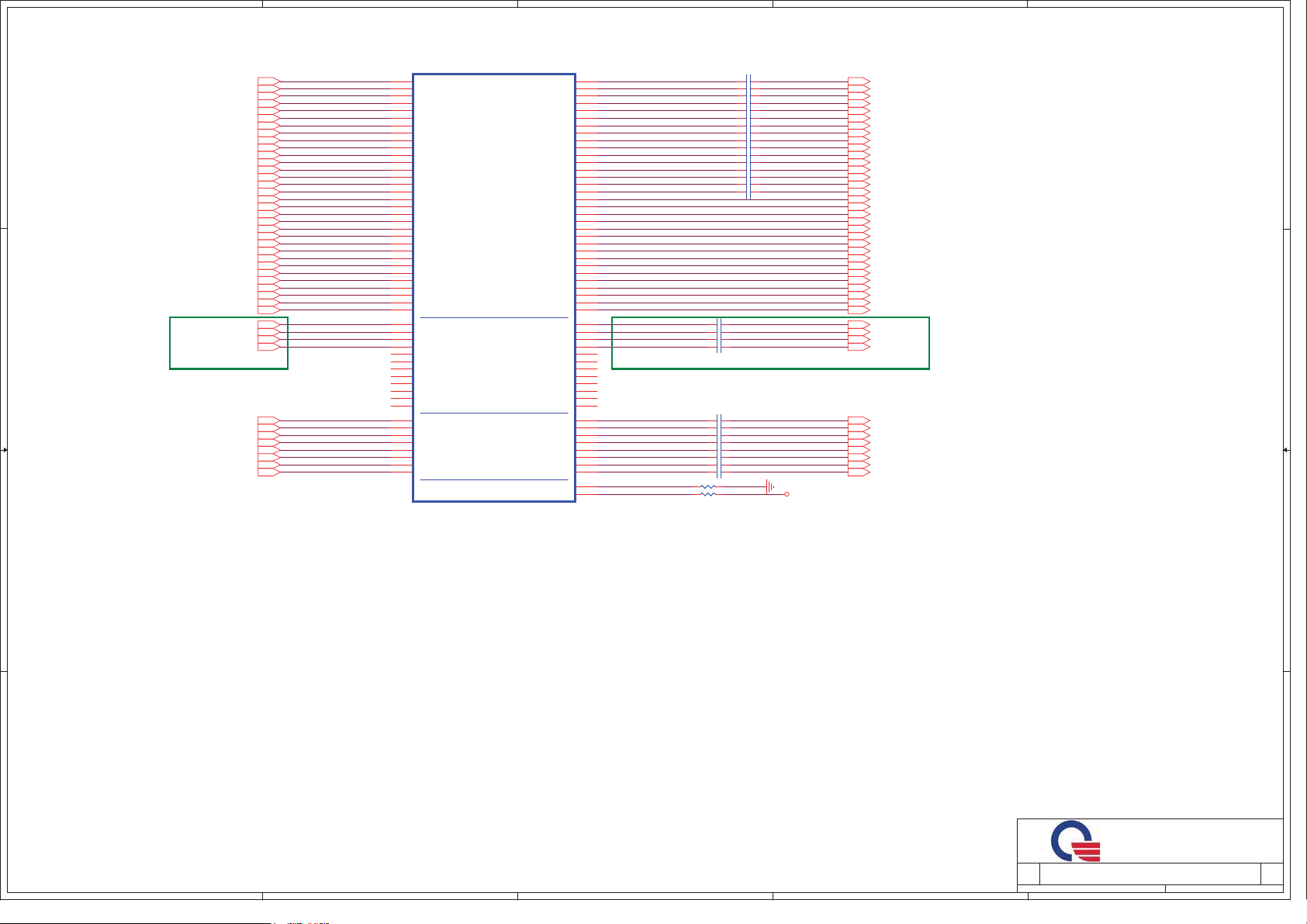

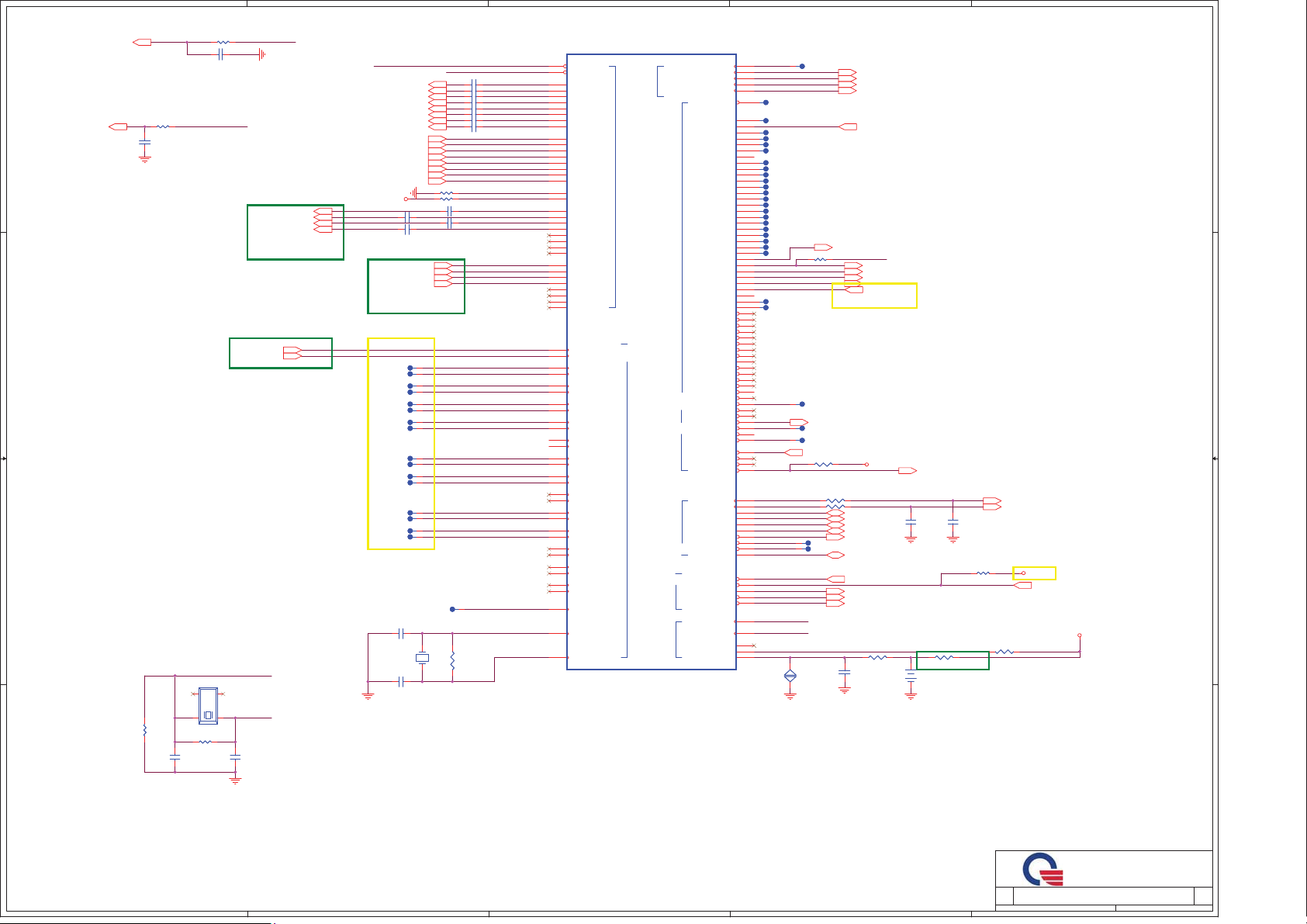

CPU HyperTransport and Debug

U24A

U24A

HT_CADINP15

HT_CADINN15

HT_CADINP14

HT_CADINN14

HT_CADINP13

HT_CADINN13

HT_CADINP12

HT_CADINN12

HT_CADINP11

HT_CADINN11

HT_CADINP10

HT_CADINN10

HT_CADINP9

HT_CADINN9

HT_CADINP8

HT_CADINN8

HT_CADINP7

HT_CADINN7

HT_CADINP6

HT_CADINN6

HT_CADINP5

HT_CADINN5

HT_CADINP4

HT_CADINN4

HT_CADINP3

HT_CADINN3

HT_CADINP2

HT_CADINN2

HT_CADINP1

HT_CADINN1

HT_CADINP0

HT_CADINN0

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

AM3_SOCKET

AM3_SOCKET

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

HT LINK

HT LINK

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

D D

C C

HT_CLKINP17

HT_CLKINN17

HT_CLKINP07

HT_CLKINN07

HT_CTLINP17

HT_CTLINN17

HT_CTLINP07

HT_CTLINN07

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_CADOUTP15

HT_CADOUTN15

HT_CADOUTP14

HT_CADOUTN14

HT_CADOUTP13

HT_CADOUTN13

HT_CADOUTP12

HT_CADOUTN12

HT_CADOUTP11

HT_CADOUTN11

HT_CADOUTP10

HT_CADOUTN10

HT_CADOUTP9

HT_CADOUTN9

HT_CADOUTP8

HT_CADOUTN8

HT_CADOUTP7

HT_CADOUTN7

HT_CADOUTP6

HT_CADOUTN6

HT_CADOUTP5

HT_CADOUTN5

HT_CADOUTP4

HT_CADOUTN4

HT_CADOUTP3

HT_CADOUTN3

HT_CADOUTP2

HT_CADOUTN2

HT_CADOUTP1

HT_CADOUTN1

HT_CADOUTP0

HT_CADOUTN0

HT_CLKOUTP1 7

HT_CLKOUTN1 7

HT_CLKOUTP0 7

HT_CLKOUTN0 7

HT_CTLOUTP1 7

HT_CTLOUTN1 7

HT_CTLOUTP0 7

HT_CTLOUTN0 7

HT_CADOUTP[15..0]

HT_CADOUTN[15..0]

HT_CLKOUTP[1..0]

HT_CLKOUTN[1..0]

HT_CTLOUTP[1..0]

HT_CTLO UTN[1. .0]

HT_CADINP[15..0]

HT_CADINN[15..0]

HT_CLKINP[1..0]

HT_CLKINN[1..0]

HT_CTLINP[1..0]

HT_CTLINN[1..0]

HT_CADOUTP[15..0] 7

HT_CADOUTN[15..0] 7

HT_CLKOUTP[1..0] 7

HT_CLKOUTN[1..0] 7

HT_CTLOUTP[1..0] 7

HT_CTLOUTN[1..0] 7

HT_CADINP[15..0] 7

HT_CADINN[15..0] 7

HT_CLKINP[1..0] 7

HT_CLKINN[1..0] 7

HT_CTLINP[1..0] 7

HT_CTLINN[1..0] 7

B B

R317

R317

*1K/F_4

*1K/F_4

R318

R318

*1K/F_4

*1K/F_4

1.5VSUS

1

3

5

7

9

11

13

15

17

19

21

23

HDT Connector

CN12

CN12

KEY

KEY

ASP-68200-07

ASP-68200-07

Use buffered reset

2

4

6

8

10

12

14

16

18

20

22

24

25

CPU_LDT_HDT_RST#

A1

AL1

AM3

Top View

A31

AL31

R314

R314

R315

R315

R316

*1K/F_4

*1K/F_4

R316

*1K/F_4

*1K/F_4

300/F_4

300/F_4

CPU_DBREQ#5

CPU_DBRDY5

CPU_TCK5

CPU_TMS5

CPU_TDI5

CPU_TRST#5

CPU_TDO5

HDT Header

+

U22

U22

-

*74LVC07+-

*74LVC07

3 5

4

2

VCC3

R306

R306

*1K/F_4

*1K/F_4

CPU_LDT_HDT_RST#

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

CPU HyperTransport and Debug

CPU HyperTransport and Debug

CPU HyperTransport and Debug

ZN8

ZN8

ZN8

of

of

of

340Monday, March 22, 2010

340Monday, March 22, 2010

1

340Monday, March 22, 2010

1A

1A

1A

A A

Open

Open

CPU_LDT_RST#5,12

5

4

3

2

Drain

Drain

1 2

R310 0R310 0

Page 4

A

B

C

D

E

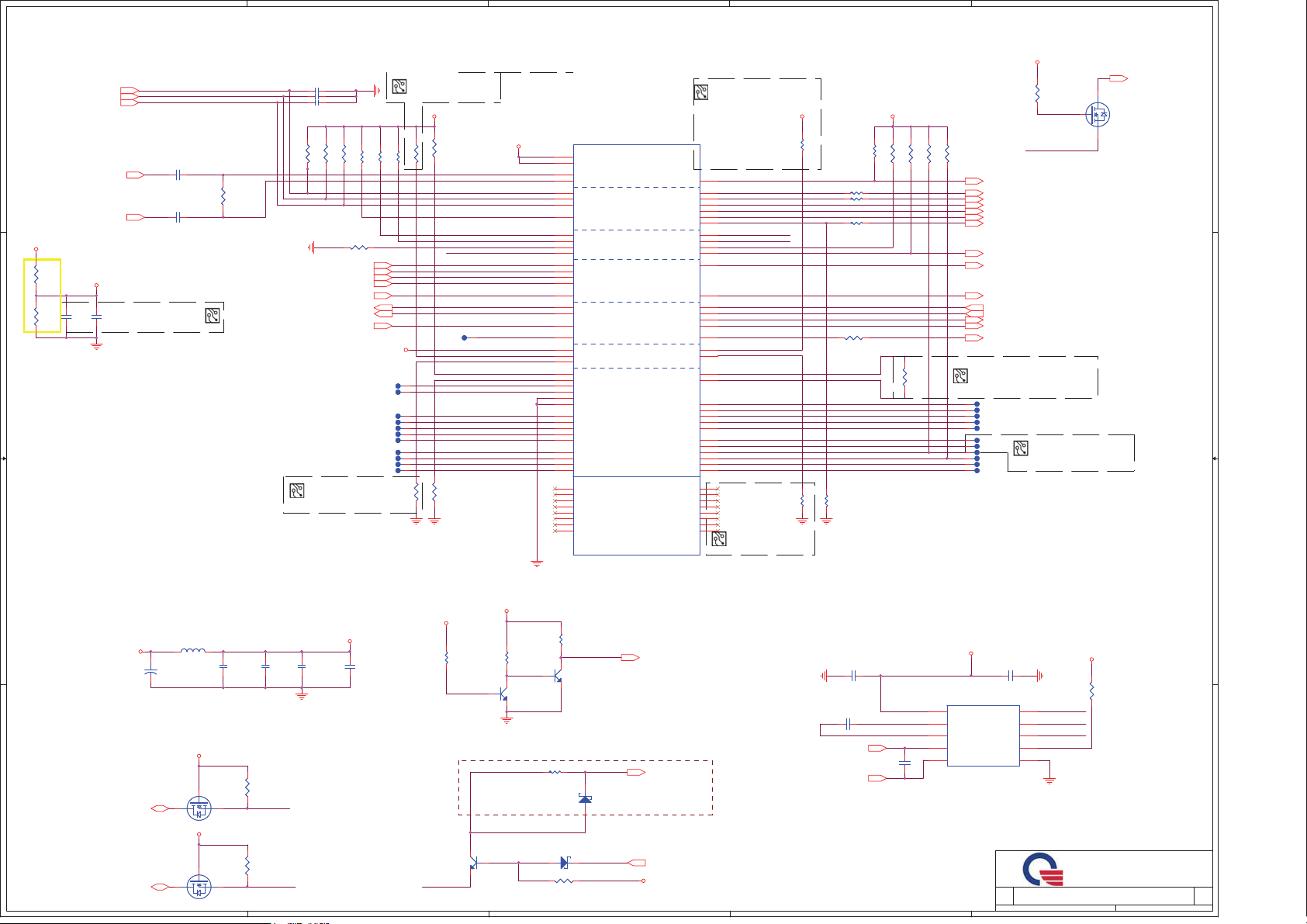

CPU Memory

Pin naming for memory pins indicate

"DDR3"/"DDR2" connections.

M_CLK_DDR_A318

4 4

3 3

2 2

M_CLK_DDR#_A318

M_CLK_DDR_A017

M_CLK_DDR#_A017

M_CLK_DDR_A218

M_CLK_DDR#_A218

M_CLK_DDR_A117

M_CLK_DDR#_A117

M_CS#_A117

M_CS#_A017

M_ODT_A117

M_ODT_A017

M_CS#_A318

M_CS#_A218

M_ODT_A318

M_ODT_A218

M_A_RST#17,18

M_A_CAS#17,18

M_A_WE#17,18

M_A_RAS#17,18

M_BA_A217,18

M_BA_A117,18

M_BA_A017,18

M_CKE_A117,18

M_CKE_A017,18

M_A_A[15..0]17,18 M_B_A[15..0]19,20

M_A_DQS717,18

M_A_DQS#717,18

M_A_DQS617,18

M_A_DQS#617,18

M_A_DQS517,18

M_A_DQS#517,18

M_A_DQS417,18

M_A_DQS#417,18

M_A_DQS317,18

M_A_DQS#317,18

M_A_DQS217,18

M_A_DQS#217,18

M_A_DQS117,18

M_A_DQS#117,18

M_A_DQS017,18

M_A_DQS#017,18

M_A_DM717,18

M_A_DM617,18

M_A_DM517,18

M_A_DM417,18

M_A_DM317,18

M_A_DM217,18

M_A_DM117,18

M_A_DM017,18

DDR3 Memory Interface A

U24B

U24B

T44T44 T40T40

T42T42

T45T45

T46T46 T38T38

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

AG21

MA_CLK_H7

AG20

MA_CLK_L7

AE20

MA_CLK_H6

AE19

MA_CLK_L6

U27

MA_CLK_H5

U26

MA_CLK_L5

V27

MA_CLK_H4

W27

MA_CLK_L4

W26

MA_CLK_H3

W25

MA_CLK_L3

U24

MA_CLK_H2

V24

MA_CLK_L2

G19

T50T50

T49T49

T51T51

T52T52

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AH29

H19

G20

G21

N25

M25

M27

N24

N26

N27

R24

R25

R26

R27

U25

W24

D29

C29

C25

D25

G15

AJ25

H15

E20

Y27

L27

P25

Y25

P27

T25

T27

E19

F19

F15

B29

E24

E18

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA1_ODT1

MA1_ODT0

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MEM CHA

MEM CHA

AM3_SOCKET

AM3_SOCKET

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

W30

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

R133 1K/FR133 1K/F

M_A_DQ[63..0] 17,18 M_B_DQ[63..0] 19,20

Route as 60 ohms

with 5/1 0 W/S from CPU pins.

MEM_MA_EVENT_L 17,18

1.5VSUS 1.5VSUS

EVENT pins are for future AM3r2 EVENT pins are for future AM3r2

Pin naming for memory pins indicate

"DDR3"/"DDR2" connections.

M_CLK_DDR_B320

M_CLK_DDR#_B320

M_CLK_DDR_B019

M_CLK_DDR#_B019

M_CLK_DDR_B220

M_CLK_DDR#_B220

M_CLK_DDR_B119

M_CLK_DDR#_B119

M_CS#_B119

M_CS#_B019

M_ODT_B119

M_ODT_B019

M_CS#_B320

M_CS#_B220

M_ODT_B320

M_ODT_B220

M_B_RST#19,20

M_B_CAS#19,20

M_B_WE#19,20

M_B_RAS#19,20

M_BA_B219,20

M_BA_B119,20

M_BA_B019,20

M_CKE_B119,20

M_CKE_B019,20

M_B_DQS719,20

M_B_DQS#719,20

M_B_DQS619,20

M_B_DQS#619,20

M_B_DQS519,20

M_B_DQS#519,20

M_B_DQS419,20

M_B_DQS#419,20

M_B_DQS319,20

M_B_DQS#319,20

M_B_DQS219,20

M_B_DQS#219,20

M_B_DQS119,20

M_B_DQS#119,20

M_B_DQS019,20

M_B_DQS#019,20

T39T39

T37T37

T63T63

T62T62

T61T61

T57T57

M_B_DM719,20

M_B_DM619,20

M_B_DM519,20

M_B_DM419,20

M_B_DM319,20

M_B_DM219,20

M_B_DM119,20

M_B_DM019,20

DDR3 Memory Interface B

U24C

U24C

AJ19

MB_CLK_H7

AK19

MB_CLK_L7

AL19

MB_CLK_H6

AL18

MB_CLK_L6

U31

MB_CLK_H5

U30

MB_CLK_L5

W29

MB_CLK_H4

W28

MB_CLK_L4

Y31

MB_CLK_H3

Y30

MB_CLK_L3

V31

MB_CLK_H2

W31

MB_CLK_L2

A18

MB_CLK_H1

A19

MB_CLK_L1

C19

MB_CLK_H0

D19

MB_CLK_L0

AE30

MB0_CS_L1

AC31

MB0_CS_L0

AF31

MB0_ODT1

AD29

MB0_ODT0

AE29

MB1_CS_L1

AB31

MB1_CS_L0

AG31

MB1_ODT1

AD31

MB1_ODT0

B19

MB_RESET_L

AC29

MB_CAS_L

AC30

MB_WE_L

AB29

MB_RAS_L

N31

MB_BANK2

AA31

MB_BANK1

AA28

MB_BANK0

M31

MB_CKE1

M29

AH17

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AJ23

AK29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

AM3_SOCKET

AM3_SOCKET

MEM CHB

MEM CHB

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

V29

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

MEM_MB_EVENT_L

R137 1K/FR137 1K/F

Route as 60 ohms

with 5/10 W/S from CPU pins.

MEM_MB_EVENT_L 19,20

MEM CHA

CPU

TO DIMMA0 & DIMMA1

1 1

A

A0

B

C

CPU

TO DIMMB0 & DIMMB1

D

MEM CHB

B0

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

CPU Memory

CPU Memory

CPU Memory

PROJECT :

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Date: Sheet

Date: Sheet

Date: Sheet

ZN8

ZN8

ZN8

of

of

of

440Monday, March 22, 2010

440Monday, March 22, 2010

E

440Monday, March 22, 2010

1A

1A

1A

Page 5

5

4

3

2

1

CPU Control and Miscellaneous

VCC3

3

Q34

Q34

RHU002N06

RHU002N06

1

CPU_THERMTRIP# 13

R347 1K/FR347 1K/F

CPU_M_VREF

T55T55

T59T59

T129T129

T58T58

T54T54

T60T60

T119T119

T127T127

T123T123

T43T43

T126T126

R348 *1K/FR348 *1K/F

Layout: Keep trace to r es istors

less than 1" from CPU pins.

1.5VSUS 1.5VSUS

39.2F

39.2F

R337

R337

R394 511/FR394 511/F R395 511/FR395 511/F

R342 39.2/FR342 39.2/F

CPU_CLKIN_SC

CPU_CLKIN_SC#

CPU_PWRGD

LDT_STOP#

CPU_LDT_RST#

CPU_PRESENT#

CPU_SIC

CPU_SID

CPU_SA0

CPU_ALERT#

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

CPU_VDD_FB

CPU_VDD_FB#

T56T56

CPU_M_ZN

CPU_M_ZP

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_H_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST7_ANALOG_T

CPU_TEST6_DIECRACKMON

CPU_TEST3_GATE0

CPU_TEST2_DRAIN0

CPUVDDA

CPU_VTT_SUS_SENSE

Pin naming for VID pins indi cat e

"Serial VID"/"Parallel VID" connections.

U24D

U24D

C10

VDDA_1

D10

VDDA_2

MISC.

MISC.

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

SA0

ALERT_L

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

M_VDDIO_PWRGD

VDDR_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST3

TEST2

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

INT. MISC.

INT. MISC.

RSVD6

RSVD7

RSVD8

AM3_SOCKET

AM3_SOCKET

AH10

AH11

A8

B8

C9

D8

C7

AL3

AL6

AK6

AK4

AL4

AL10

AJ10

AL9

A5

G2

G1

F3

E12

F12

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AH7

AJ6

C18

C20

F2

G24

G25

H25

L25

L26

CORE_TYPE

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

SVC/VID3

SVD/VID2

PVIEN/VID1

THERMDC

THERMDA

DBRDY

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

VID5

VID4

VID0

TDO

Layout: Keep CPU_HTREF0

less than 1.5" from in length.

CPU_CORE_TYPE

G5

CPU_VID5_R

D2

CPU_VID4_R

D1

CPU_SVC

C1

CPU_SVD

E3

CPU_PVEN

E2

CPU_VID0_R

E1

CPU_THERMDC

AG9

CPU_THERMDA

AG8

CPU_THERMTRIP#_1.5

AK7

CPU_PROCHOT#_1.5

AL7

CPU_TDO

AK10

CPU_DBRDY

B6

CPU_VDDIO_FB_H

AK11

CPU_VDDIO_FB_L

AL11

CPU_VDDNB_FB_H

G4

CPU_VDDNB_FB_L

G3

CPU_PSI#

F1

CPU_HTREF1

V8

CPU_HTREF0

V7

CPU_TEST29_H_FBCLKOUT_H

C11

CPU_TEST29_L_FBCLKOUT_L

D11

CPU_TEST24_SCANCLK1

AK8

CPU_TEST23_TSTUPD

AH8

CPU_TEST22_SCANSHIFTEN

AJ9

CPU_TEST21_SCANEN

AL8

CPU_TEST20_SCANCLK2

AJ8

CPU_TEST28_H_PLLCHRZ_H

J10

CPU_TEST28_L_PLLCHRZ_L

H9

CPU_TEST27_SINGLECHAIN

AK9

CPU_TEST26_BURNIN_L

AK5

CPU_TEST10_ANALOGOUT

G7

CPU_TEST8_DIG_T

D4

L30

L31

AD25

AE24

AE25

AJ18

AJ20

AK3

Layout: Keep CPU_HTREF0

less than 1.5" from in length.

CPU_VDDHT

R104 44.2/FR104 44.2/F

R138 44.2/FR138 44.2/F

R392 *0_4R392 *0_4

R391 *0_4R391 *0_4

R389 *0_4R389 *0_4

R388 0/J_4R388 0/J_4

R390 49.9/FR390 49.9/F

R324

R324

10K

10K

2

CPU_THERMTRIP#_1.5

R386 1K/FR386 1K/F

R349 10KR349 10K

R336 10KR336 10K

R150

R150

*80.6/F_4

*80.6/F_4

R346 *301R346 *301

R338 301R338 301

CPU_CORE_TYPE 39

CPU_VID5 39

CPU_VID4 39

CPU_SVC 39

CPU_SVD 39

CPU_PVEN 39

CPU_VID0 39

CPU_PROCHOT#_1.5 12

CPU_TDO 3

CPU_DBRDY 3

CPU_VDDIO_FB_H 37

CPU_VDDIO_FB_L 37

CPU_VDDNB_FB_H 39

CPU_VDDNB_FB_L 39

PSI 39

Layout: Route as 80 ohms diff impedance.

Keep trace to resistor < 1" from CPU pins.

T125T125

T41T41

T124T124

T121T121

T120T120

T47T47

T48T48

T118T118

T122T122

T53T53

T128T128

Layout: Route CPU_TEST28_H/L

as differential traces and as short

as possible.

CPU_PWRGD12

LDT_STOP#9,12

CPU_LDT_RST#3,12

D D

C637

CPUCLK2

CPUCLK#2

1.5VSUS

B-2

R165

R165

2K/F

2K/F

R164

R164

2K/F

2K/F

C C

B B

SMDDR_VREF

CPU_M_VREF

C384

C384

C385

C385

0.1u/10V

0.1u/10V

Layout: Place within 500

mils of the CPU socket.

1000P

1000P

C637

3900p

3900p

C636

C636

3900p

3900p

NEED X5R

NEED X5R

R393

R393

169_0603F

169_0603F

C622 *180PC622 *180P

C623 *180PC623 *180P

C624 *180PC624 *180P

R396 301R396 301

R397 301R397 301

R343 10K/FR343 10K/F

R398 301R398 301

R344 0/J_4R344 0/J_4

CPU_TDI3

CPU_TRST#3

CPU_TCK3

CPU_TMS3

CPU_DBREQ#3

CPU_VDD_FB39

CPU_VDD_FB#39

CPU_VDDIO_PWRGD16,29,35,36,39

Layout: Keep trace to r es istors

less than 1" from CPU pins.

1.5VSUS

BLM21PG221SN1D(220_100M_2A)_8

BLM21PG221SN1D(220_100M_2A)_8

VDDA

L35

L35

C389

C389

LS0805-100M-N

+

+

100U/16V

100U/16V

VCC3

Q32

Q32

2

RHU002N06

A A

THERM_CLK_EC29,30,31

THERM_DAT_EC29,30,31

5

RHU002N06

3

3

VCC3

2

Q31

Q31

RHU002N06

RHU002N06

1

1

C375

C375

4.7u/6.3V_6

4.7u/6.3V_6

R303

R303

4.7K_4

4.7K_4

SCLK

R302

R302

4.7K_4

4.7K_4

SDATA

C367

C367

0.22u/6.3V_4

0.22u/6.3V_4

CPUVDDA

C371

C371

3300P/50V_4

3300P/50V_4

CPUVDDA

C382

C382

*10U/6.3V_8

*10U/6.3V_8

4

R345 1K/FR345 1K/F

CPU_ALERT#

SYS_SHDN_1#

VCC3

2

SYS_SHDN#_3904

reserve for

power shutdown

( if can )

PWROK_EC_3904

2

Q33

Q33

1 3

MMBT3904

MMBT3904

1 3

R326

R326

1K/F_4

1K/F_4

MMBT3904

MMBT3904

Q35

Q35

R304 0_4R304 0_4

R325

R325

1K/F_4

1K/F_4

THERM_ALERT#

MMBT3904

MMBT3904

2

Q36

Q36

1 3

D18

D18

CH501H-40PT

CH501H-40PT

2 1

R305 10K/F_4R305 10K/F_4

CPU Thermal

THERM_ALERT# 14,29

SYS_SHDN# 34

D19

D19

*CH500H

*CH500H

2 1

PWROK_EC 16,29,39

VCC3

3

Senser

C512 0.1UC512 0.1U

C220 2200P_0603C220 2200P_0603

NB_THERMDA9

NB_THERMDC9

2

THERM_VCC

CPU_THERMDA

CPU_THERMDC THERM_ALERT#

C104

C104

2200P_0603

2200P_0603

VCC3

C513

C513

*0.1U

*0.1U

sub-address:98h

U21

U21

1

VCC

2

DXP1

3

DXN1

4

DXP2

5

DXN2

10

SMCLK

9

SMDATA

8

ALERT#

7

THERM#

6

GND

G782

G782

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CPU Control & Misc

CPU Control & Misc

CPU Control & Misc

Date: Sheet

Date: Sheet of

Date: Sheet of

VCC3

R311

R311

10K

10K

SCLK

SDATA

SYS_SHDN_1#

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

ZN8

ZN8

ZN8

1A

1A

540Monday, March 22, 2010

540Monday, March 22, 2010

540Monday, March 22, 2010

1A

of

Page 6

5

4

3

2

1

CPU_CORE CPU_CORE

U24E

U24E

B3

VDD_1

C2

VDD_2

C4

VDD_3

D3

VDD_4

D5

VDD_5

E4

VDD_6

E6

VDD_7

F5

VDD_8

F7

VDD_9

G6

D D

C C

B B

G8

H7

H11

H23

J12

J14

J16

J18

J20

J22

J24

K11

K13

K15

K17

K19

K21

K23

L10

L12

L14

L16

L18

L20

L22

M2

M3

M7

M9

M11

M13

M15

M17

M19

M21

M23

N8

N10

N12

N14

N16

N18

N20

N22

P11

P13

P15

P17

P19

P21

P23

R4

R5

R8

R10

R12

R14

R16

R18

R20

R22

T11

T13

J8

K7

K9

L4

L5

L8

P7

P9

T2

T3

T7

T9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

VDD_51

VDD_52

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

VDD_63

VDD_64

VDD_65

VDD_66

VDD_67

VDD_68

VDD_69

VDD_70

VDD_71

VDD_72

VDD_73

VDD_74

VDD_75

VDD_76

VDD_77

VDD_78

VDD_79

VDD_80

VDD_81

VDD_82

VDD_83

VDD_84

VDD_85

AM3_SOCKET

AM3_SOCKET

A3

VSS_1

A7

VSS_2

A9

VSS_3

A11

VSS_4

B4

VSS_5

B9

VSS_6

B11

VSS_7

B14

VSS_8

B16

VSS_9

B18

VSS_10

B20

VSS_11

B22

VSS_12

B24

VSS_13

B26

VSS_14

B28

VSS_15

B30

VSS_16

C3

VSS_17

D14

VSS_18

D16

VSS_19

D18

VSS_20

D20

VSS_21

D22

VSS_22

D24

VSS_23

D26

VSS_24

D28

VSS_25

D30

VSS_26

E11

VSS_27

F4

VSS_28

F14

VSS_29

F16

VSS_30

F18

VSS_31

F20

VSS_32

F22

VSS_33

F24

VSS_34

F26

VSS_35

F28

VSS_36

F30

VSS_37

G9

VSS_38

G11

VSS_39

H8

VSS_40

H10

VSS_41

H12

VSS_42

H14

VSS_43

H16

VSS_44

H18

VSS_45

H24

VSS_46

H26

VSS_47

H28

VSS_48

H30

VSS_49

J4

VSS_50

J5

VSS_51

POWER/GND1

POWER/GND1

J7

VSS_52

J9

VSS_53

J11

VSS_54

J13

VSS_55

J15

VSS_56

J17

VSS_57

J19

VSS_58

J21

VSS_59

J23

VSS_60

K2

VSS_61

K3

VSS_62

K8

VSS_63

K10

VSS_64

K12

VSS_65

K14

VSS_66

K16

VSS_67

K18

VSS_68

K20

VSS_69

K22

VSS_70

K24

VSS_71

K26

VSS_72

K28

VSS_73

K30

VSS_74

L7

VSS_75

L9

VSS_76

L11

VSS_77

L13

VSS_78

L15

VSS_79

L17

VSS_80

L19

VSS_81

L21

VSS_82

L23

VSS_83

M8

VSS_84

M10

VSS_85

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AE10

AE12

AF11

W10

W12

W14

W16

W18

W20

W22

AG4

AG5

AG7

T15

T17

T19

T21

T23

U8

U10

U12

U14

U16

U18

U20

U22

V9

V11

V13

V15

V17

V19

V21

V23

W4

W5

W8

Y2

Y3

Y7

Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

AA8

AB7

AB9

AC4

AC5

AC8

AD2

AD3

AD7

AD9

AF7

AF9

AH2

AH3

U24F

U24F

VDD_86

VDD_87

VDD_88

VDD_89

VDD_90

VDD_91

VDD_92

VDD_93

VDD_94

VDD_95

VDD_96

VDD_97

VDD_98

VDD_99

VDD_100

VDD_101

VDD_102

VDD_103

VDD_104

VDD_105

VDD_106

VDD_107

VDD_108

VDD_109

VDD_110

VDD_111

VDD_112

VDD_113

VDD_114

VDD_115

VDD_116

VDD_117

VDD_118

VDD_119

VDD_120

VDD_121

VDD_122

VDD_123

VDD_124

VDD_125

VDD_126

VDD_127

VDD_128

VDD_129

VDD_130

VDD_131

VDD_132

VDD_133

VDD_134

VDD_135

VDD_136

VDD_137

VDD_138

VDD_139

VDD_140

VDD_141

VDD_142

VDD_143

VDD_144

VDD_145

VDD_146

VDD_147

VDD_148

VDD_149

VDD_150

VDD_151

VDD_152

VDD_153

VDD_154

VDD_155

VDD_156

VDD_157

VDD_158

VDD_159

VDD_160

VDD_161

VDD_162

VDD_163

VDD_164

VDD_165

VDD_166

VDD_167

VDD_168

VDD_169

VDD_170

AM3_SOCKET

AM3_SOCKET

M12

VSS_86

M14

VSS_87

M16

VSS_88

M18

VSS_89

M20

VSS_90

M22

VSS_91

N4

VSS_92

N5

VSS_93

N7

VSS_94

N9

VSS_95

N11

VSS_96

N13

VSS_97

N15

VSS_98

N17

VSS_99

N19

VSS_100

N21

VSS_101

N23

VSS_102

P2

VSS_103

P3

VSS_104

P8

VSS_105

P10

VSS_106

P12

VSS_107

P14

VSS_108

P16

VSS_109

P18

VSS_110

P20

VSS_111

P22

VSS_112

R7

VSS_113

R9

VSS_114

R11

VSS_115

R13

VSS_116

R15

VSS_117

R17

VSS_118

R19

VSS_119

R21

VSS_120

R23

VSS_121

T8

VSS_122

T10

VSS_123

T12

VSS_124

T14

VSS_125

T16

VSS_126

T18

VSS_127

T20

VSS_128

T22

VSS_129

U4

VSS_130

U5

VSS_131

U7

VSS_132

U9

VSS_133

U11

VSS_134

U13

VSS_135

POWER/GND2

POWER/GND2

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W7

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

Y14

Y16

Y18

Y20

Y22

AA4

AA5

AA7

AA9

NBCORE

A4

A6

B5

B7

C6

C8

D7

D9

E8

E10

F9

F11

G10

G12

B2

H20

AE7

U24G

U24G

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

VDDNB_7

VDDNB_8

VDDNB_9

VDDNB_10

VDDNB_11

VDDNB_12

VDDNB_13

VDDNB_14

NP/RSVD

NP/VSS

NP/VSS

AM3_SOCKET

AM3_SOCKET

Bottom Side Decoupling

1.5VSUS

C348 22uFC348 22uF

CPU_CORE

C281 22uFC281 22uFC373 22uFC373 22uF

CPU_CORE

A A

C308 10uFC308 10uF

NBCORE

C350 22uFC350 22uF

C331 22uFC331 22uF

C280 22uFC280 22uF

C243 22uFC243 22uF

C265 22uFC265 22uF

C309 10uFC309 10uF

C310 10uFC310 10uF

C230 10uFC230 10uF C347 22uFC347 22uF

C380 22uFC380 22uF

C329 0.01UC329 0.01U

C361 0.01UC361 0.01U

C306 0.01UC306 0.01UC254 10uFC254 10uF

C287 10uFC287 10uF

C282 22uFC282 22uF

C242 10uFC242 10uF

C362 180pfC362 180pf

5

C253 0.01UC253 0.01U

C267 22uFC267 22uF

C245 22uFC245 22uF

C302 10uFC302 10uF

C276 0.22uC276 0.22u

C312 0.22uC312 0.22u

C275 22uFC275 22uF

C301 22uFC301 22uF

C244 4.7UC244 4.7U

C307 4.7UC307 4.7U

C241 180pfC241 180pf

C283 22uFC283 22uF

C300 4.7UC300 4.7U

C266 22uFC266 22uF

C249 0.01UC249 0.01U

1.2VDDR

C161 22uFC161 22uF

C530 0.01UC530 0.01U

C628 0.01UC628 0.01U

C626 0.22uC626 0.22u

C232 0.22uC232 0.22u

C295 0.22uC295 0.22u

C528 10uFC528 10uF

C197 10uFC197 10uF

C227 180pfC227 180pf

C235 0.01UC235 0.01U

4

Processor Power and Ground

CPU_VDDHT

U24H

AA11

VSS_171

AA13

VSS_172

AA15

VSS_173

AA17

VSS_174

AA19

VSS_175

AA21

VSS_176

AA23

VSS_177

AB2

VSS_178

AB3

VSS_179

AB8

VSS_180

AB10

VSS_181

AB12

VSS_182

AB14

VSS_183

AB16

VSS_184

AB18

VSS_185

AB20

VSS_186

AB22

VSS_187

AC7

VSS_188

AC9

VSS_189

AC11

VSS_190

AC13

VSS_191

AC15

VSS_192

AC17

VSS_193

AC19

VSS_194

AC21

VSS_195

AC23

VSS_196

AD8

VSS_197

AD10

VSS_198

AD12

VSS_199

AD14

VSS_200

AD16

VSS_201

AD20

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

POWER/GND3

POWER/GND3

CPU_VDDNB_RUN CPU_VDDR

NBCORE

C370 10uFC370 10uF

C364 10uFC364 10uF

C342 0.22uC342 0.22u

C355 0.22uC355 0.22u

C377 4. 7uFC377 4.7uF

C354 0.01UC354 0.01U

A1

AL1

CPU_VDDHT

C527 4.7uFC527 4.7uF

C532 0.22uC532 0.22u

C196 4.7uFC196 4.7uF

VLDT_HT3_RUN

C534 180pfC534 180pf

C526 0.22uC526 0.22u

C194 180pfC194 180pf

3

U24H

AJ1

VLDT_A_1

AJ2

VLDT_A_2

AJ3

VLDT_A_3

AJ4

1.2VDDR

C529 10uFC529 10uF

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

A12

B12

C12

D12

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

VLDT_A_4

VDDR_1

VDDR_2

VDDR_3

VDDR_4

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

AM3_SOCKET

AM3_SOCKET

C632 4. 7uFC632 4.7uF

C631 4. 7uFC631 4.7uF

C531 0.22uC531 0.22u

1.2VDDR 1.2VDDR

1.5VSUS

VLDT_B_1

VLDT_B_2

VLDT_B_3

VLDT_B_4

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDR_9

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

POWER/GND4

POWER/GND4

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

C166 0.22uC166 0.22u

C167 0.22uC167 0.22u

CPU_VDDIO_SUS

AM3

Top View

A31

1.5VSUS

C318 4.7uFC318 4.7uF

1.5VSUS

C277 4. 7uFC277 4.7uF

C330 4.7uFC330 4.7uF

C326 4. 7uFC326 4.7uF

AL31

Layout: Place across each

VDDIO-GND plane split.

1.2VDDR

C163 4.7uFC163 4.7uF

C629 0.01UC629 0.01U

C633 4.7uFC633 4.7uF

CPU_VDDR

VLDT_HT3_RUN_B

H1

H2

H5

H6

AG12

AH12

AJ12

AK12

AL12

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

C627 0.22uC627 0.22u

C288 180pfC288 180pf

C264 180pfC264 180pf

2

DIMMs

C602

C602

10uF

10uF

Layout: Place as close as

possible to CPU socket.

CPU_VDDR

1.2VDDR

C630 4.7uFC630 4.7uF

C165 4.7uFC165 4.7uF

Layout: Place behind the DIMMs,

evenly spaced on VTT fill.

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Date: Sheet

Date: Sheet

Date: Sheet

C634 4.7uFC634 4.7uF

C162 4.7uFC162 4.7uF

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

CPU Power & GND

CPU Power & GND

CPU Power & GND

1

ZN8

ZN8

ZN8

1A

1A

1A

of

of

of

640Monday, March 22, 2010

640Monday, March 22, 2010

640Monday, March 22, 2010

Page 7

5

D D

C C

B B

4

U23A

U24

U25

N24

N25

AC24

AC25

AB25

AB24

AA24

AA25

W21

W20

U20

U21

U19

U18

AB23

AA22

M22

M23

R21

R20

C23

Y25

Y24

V22

V23

V25

V24

T25

T24

P22

P23

P25

P24

Y22

Y23

V21

V20

T22

T23

A24

U23A

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS880M

RS880M

HT_CADOUTP0

HT_CADOUTN0

HT_CADOUTP1

HT_CADOUTN1

HT_CADOUTP2

HT_CADOUTN2

HT_CADOUTP3

HT_CADOUTN3

HT_CADOUTP4

HT_CADOUTN4

HT_CADOUTP5

HT_CADOUTN5

HT_CADOUTP6

HT_CADOUTN6

HT_CADOUTP7

HT_CADOUTN7

HT_CADOUTP8

HT_CADOUTN8

HT_CADOUTP9

HT_CADOUTN9

HT_CADOUTP10

HT_CADOUTN10

HT_CADOUTP11

HT_CADOUTN11

HT_CADOUTP12

HT_CADOUTN12

HT_CADOUTP13

HT_CADOUTN13

HT_CADOUTP14

HT_CADOUTN14

HT_CADOUTP15

HT_CADOUTN15

HT_CLKOUTP0

HT_CLKOUTN0

HT_CLKOUTP1

HT_CLKOUTN1

HT_CTLOUTP0

HT_CTLOUTN0

HT_CTLOUTP1

HT_CTLOUTN1

R351 301/ F_4R351 301/F_4 R350 301/ F_4R350 301/F_4

HT_RXCALP

HT_RXCALN

3

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H24

H25

L21

L20

M24

M25

P19

R18

B24

B25

HT_CADINP0

HT_CADINN0

HT_CADINP1

HT_CADINN1

HT_CADINP2

HT_CADINN2

HT_CADINP3

HT_CADINN3

HT_CADINP4

HT_CADINN4

HT_CADINP5

HT_CADINN5

HT_CADINP6

HT_CADINN6

HT_CADINP7

HT_CADINN7

HT_CADINP8

HT_CADINN8

HT_CADINP9

HT_CADINN9

HT_CADINP10

HT_CADINN10

HT_CADINP11

HT_CADINN11

HT_CADINP12

HT_CADINN12

HT_CADINP13

HT_CADINN13

HT_CADINP14

HT_CADINN14

HT_CADINP15

HT_CADINN15

HT_CLKINP0

HT_CLKINN0

HT_CLKINP1

HT_CLKINN1

HT_CTLINP0

HT_CTLINN0

HT_CTLINP1

HT_CTLINN1

HT_TXCALP

HT_TXCALN

2

HT_CADOUTP[15..0]

HT_CADOUTN[15..0]

HT_CLKOUTP[1..0]

HT_CLKOUTN[1..0]

HT_CTLOUTP[1..0]

HT_CTLOUTN[1..0]

HT_CADINP[15..0]

HT_CADINN[15..0]

HT_CLKINP[1..0]

HT_CLKINN[1..0]

HT_CTLINP[1..0]

HT_CTLINN[1..0]

signals

HT_TXCALP

HT_TXCALN

HT_RXCALP

HT_RXCALN

HT_CADOUTP[15..0] 3

HT_CADOUTN[15..0] 3

HT_CLKOUTP[1..0] 3

HT_CLKOUTN[1..0] 3

HT_CTLOUTP[1..0] 3

HT_CTLOUTN[1..0] 3

HT_CADINP[15..0] 3

HT_CADINN[15..0] 3

HT_CLKINP[1..0] 3

HT_CLKINN[1..0] 3

HT_CTLINP[1..0] 3

HT_CTLINN[1..0] 3

RS880M

R430

301 ohm 1%

R434

301 ohm 1%

1

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

RS880M-HT Link I/ F

RS880M-HT Link I/ F

RS880M-HT Link I/ F

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

ZN8

ZN8

ZN8

1A

1A

740Monday, March 22, 2010

740Monday, March 22, 2010

1

740Monday, March 22, 2010

1A

of

of

of

Page 8

5

NB_EXP_RX_P021

NB_EXP_RX_N021

NB_EXP_RX_P121

NB_EXP_RX_N121

NB_EXP_RX_P221

B-42

NB_EXP_RX_N221

NB_EXP_RX_P321

NB_EXP_RX_N321

NB_EXP_RX_P421

NB_EXP_RX_N421

NB_EXP_RX_P521

NB_EXP_RX_N521

NB_EXP_RX_P621

NB_EXP_RX_N621

NB_EXP_RX_P721

NB_EXP_RX_N721

NB_EXP_RX_P821

NB_EXP_RX_N821

NB_EXP_RX_P921

NB_EXP_RX_N921

NB_EXP_RX_P1021

NB_EXP_RX_N1021

NB_EXP_RX_P1121

NB_EXP_RX_N1121

NB_EXP_RX_P1221

NB_EXP_RX_N1221

NB_EXP_RX_P1321

NB_EXP_RX_N1321

NB_EXP_RX_P1421

NB_EXP_RX_N1421

NB_EXP_RX_P1521

NB_EXP_RX_N1521

PCIE_RXP024

PCIE_RXN024

PCIE_RXP130

PCIE_RXN130

A_RXP012

A_RXN012

A_RXP112

A_RXN112

A_RXP212

A_RXN212

A_RXP312

A_RXN312

D D

C C

4

U23B

U23B

AE3

AD4

AE2

AD3

AD1

AD2

AA8

AA7

AA5

AA6

M8

P7

M7

P5

M5

R8

P8

R6

R5

P4

P3

W6

U5

U6

U8

U7

W5

D4

C4

A3

B3

C2

C1

E5

F5

G5

G6

H5

H6

J6

J5

J7

J8

L5

L6

L8

T4

T3

V5

Y8

Y7

Y5

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

GPP_RX4P

GPP_RX4N

GPP_RX5P

GPP_RX5N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

RS880M

RS880M

PART 2 OF 6

PART 2 OF 6

PCIE I/F GFX

PCIE I/F GFX

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

A5

B5

A4

B4

C3

B2

D1

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

AC1

AC2

AB4

AB3

AA2

AA1

Y1

Y2

Y4

Y3

V1

V2

AD7

AE7

AE6

AD6

AB6

AC6

AD5

AE5

AC8

AB8

3

NB_EXP_TX_P0-R

NB_EXP_TX_N0-R

NB_EXP_TX_P1-R

NB_EXP_TX_N1-R

NB_EXP_TX_P2-R

NB_EXP_TX_N2-R

NB_EXP_TX_P3-R

NB_EXP_TX_N3-R

NB_EXP_TX_P4-R

NB_EXP_TX_N4-R

NB_EXP_TX_P5-R

NB_EXP_TX_N5-R

NB_EXP_TX_P6-R

NB_EXP_TX_N6-R

NB_EXP_TX_P7-R

NB_EXP_TX_P8

NB_EXP_TX_N8

NB_EXP_TX_P9

NB_EXP_TX_N9

NB_EXP_TX_P10

NB_EXP_TX_N10

NB_EXP_TX_P11

NB_EXP_TX_N11

NB_EXP_TX_P12

NB_EXP_TX_N12

NB_EXP_TX_P13

NB_EXP_TX_N13

NB_EXP_TX_P14

NB_EXP_TX_N14

NB_EXP_TX_P15

NB_EXP_TX_N15

PCIE_TXP0_C

PCIE_TXN0_C

PCIE_TXP1_C

PCIE_TXN1_C

A_TXP0_C

A_TXN0_C

A_TXP1_C

A_TXN1_C

A_TXP2_C

A_TXN2_C

A_TXP3_C

A_TXN3_C

NB_PCIECALRP

NB_PCIECALRN

C699 0. 1U/10V_X7RC699 0. 1U/10V_X7R

C700 0. 1U/10V_X7RC700 0. 1U/10V_X7R

C701 0. 1U/10V_X7RC701 0. 1U/10V_X7R

C702 0. 1U/10V_X7RC702 0. 1U/10V_X7R

C507 0. 1U/10V_X7RC507 0. 1U/10V_X7R

C508 0. 1U/10V_X7RC508 0. 1U/10V_X7R

C506 0. 1U/10V_X7RC506 0. 1U/10V_X7R

C505 0. 1U/10V_X7RC505 0. 1U/10V_X7R

C510 0. 1U/10V_X7RC510 0. 1U/10V_X7R

C509 0. 1U/10V_X7RC509 0. 1U/10V_X7R

C503 0. 1U/10V_X7RC503 0. 1U/10V_X7R

C504 0. 1U/10V_X7RC504 0. 1U/10V_X7R

R301 1.27K/F_4R301 1.27K/F_4

R82 2K/F_4R82 2K/F_4

C5530.1uF 10% 16V X7R 0402 C5530.1uF 10% 16V X7R 0402

C5540.1uF 10% 16V X7R 0402 C5540.1uF 10% 16V X7R 0402

C5510.1uF 10% 16V X7R 0402 C5510.1uF 10% 16V X7R 0402

C5520.1uF 10% 16V X7R 0402 C5520.1uF 10% 16V X7R 0402

C5500.1uF 10% 16V X7R 0402 C5500.1uF 10% 16V X7R 0402

C5490.1uF 10% 16V X7R 0402 C5490.1uF 10% 16V X7R 0402

C5450.1uF 10% 16V X7R 0402 C5450.1uF 10% 16V X7R 0402

C5480.1uF 10% 16V X7R 0402 C5480.1uF 10% 16V X7R 0402

C5440.1uF 10% 16V X7R 0402 C5440.1uF 10% 16V X7R 0402

C5420.1uF 10% 16V X7R 0402 C5420.1uF 10% 16V X7R 0402

C5400.1uF 10% 16V X7R 0402 C5400.1uF 10% 16V X7R 0402

C5390.1uF 10% 16V X7R 0402 C5390.1uF 10% 16V X7R 0402

C5380.1uF 10% 16V X7R 0402 C5380.1uF 10% 16V X7R 0402

C5370.1uF 10% 16V X7R 0402 C5370.1uF 10% 16V X7R 0402

C5360.1uF 10% 16V X7R 0402 C5360.1uF 10% 16V X7R 0402

C5350.1uF 10% 16V X7R 0402 C5350.1uF 10% 16V X7R 0402

NB_EXP_TX_P0

NB_EXP_TX_N0

NB_EXP_TX_P1

NB_EXP_TX_N1

NB_EXP_TX_P2

NB_EXP_TX_N2

NB_EXP_TX_P3

NB_EXP_TX_N3

NB_EXP_TX_P4

NB_EXP_TX_N4

NB_EXP_TX_P5

NB_EXP_TX_N5

NB_EXP_TX_P6

NB_EXP_TX_N6

NB_EXP_TX_P7

NB_EXP_TX_N7NB_EXP_TX_N7-R

B-42

VCC1.1

2

NB_EXP_TX_P0 27

NB_EXP_TX_N0 27

NB_EXP_TX_P1 27

NB_EXP_TX_N1 27

NB_EXP_TX_P2 27

NB_EXP_TX_N2 27

NB_EXP_TX_P3 27

NB_EXP_TX_N3 27

NB_EXP_TX_P4 27

NB_EXP_TX_N4 27

NB_EXP_TX_P5 27

NB_EXP_TX_N5 27

NB_EXP_TX_P6 27

NB_EXP_TX_N6 27

NB_EXP_TX_P7 27

NB_EXP_TX_N7 27

NB_EXP_TX_P8 21

NB_EXP_TX_N8 21

NB_EXP_TX_P9 21

NB_EXP_TX_N9 21

NB_EXP_TX_P10 21

NB_EXP_TX_N10 21

NB_EXP_TX_P11 21

NB_EXP_TX_N11 21

NB_EXP_TX_P12 21

NB_EXP_TX_N12 21

NB_EXP_TX_P13 21

NB_EXP_TX_N13 21

NB_EXP_TX_P14 21

NB_EXP_TX_N14 21

NB_EXP_TX_P15 21

NB_EXP_TX_N15 21

PCIE_TXP0 24

PCIE_TXN0 24

PCIE_TXP1 30

PCIE_TXN1 30

A_TXP0 12

A_TXN0 12

A_TXP1 12

A_TXN1 12

A_TXP2 12

A_TXN2 12

A_TXP3 12

A_TXN3 12

1

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

RS880M-PCIE I/F

RS880M-PCIE I/F

RS880M-PCIE I/F

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

ZN8

ZN8

ZN8

1A

1A

840Monday, March 22, 2010

840Monday, March 22, 2010

1

840Monday, March 22, 2010

1A

of

of

of

Page 9

5

Enables Debug Bus acess

through memory I/O pads and GPIO.

0 : Enable RS880M , Default

1 : Disable RS880M

(RX881 use DAC_VSYNC)

D D

Indicates if memory Side port

is available or not

0: Reserved

1: Required setting. Select with a pull-up

resistor on the strap

( RX881 use DAC_HSYNC)

INT_CRT_HSYNC_NB

C C

VCC1.1

R356 3K/J_4R356 3K/J_4

B-35

R373 150/F_4R373 150/F_4

For A11 version

R335 *49.9/F_4R335 *49.9/F_4

R333 *49.9/F_4R333 *49.9/F_4

VCC3

R360

R360

4.7K/J_4

4.7K/J_4

B B

DDR3 based CPU : Level shifted to 1.8 V on the

Northbridge side using an open-drain buffer and

pulled up to 1.8V_S0 through a 2.2k Ohm 5% resistor

on the Northbridge side.

LDT_STOP#5,12

ALLOW_LDTSTOP12

A A

ALLOW_LDTSTOP

LDT_STOP#

* Although defined as 3.3V I/Os, a 1.8V signaling level is supported on

LDT_STOP#/ALLOW_LDTSTOP given that Vih is 1.4V.

3.3V to 1. 8V level translation is not required.

EDID_CLKEDID_CLK

EDID_DATA

2

5

INT_CRT_VSYNC_NB

for EXT Gen.

CLK_SBLINK

CLK_SBLINK#

R359

R359

4.7K/J_4

4.7K/J_4

VCC1.8

+

U8

+

U8

Open

Open

4

Drain

Drain

-

74LVC07

-

74LVC07

3 5

R120 *0/short_4R120 *0/short_4

OC

3.3V Input

VCC3

B-66

R375 150/F_4R375 150/F_4

VCC3

VCC1.8

R119

R119

1K/F_4

1K/F_4

NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#

NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#NB_LDT_STOP#

R121 1K/F_4R121 1K/F_4

NB_ALLOW_LDTSTOP

R357 3K/J_4R357 3K/J_4

R352

R352

*3K/J_4

*3K/J_4

A_RST#_SB12

NB_PWRGD16

CLK_NB_HTREF_PR2

CLK_NB_HTREF#_PR2

EXT_NB_OSC2

NBGFX_CLK2

NBGFX_CLK#2

CLK_SBLINK2

CLK_SBLINK#2

DP_AUX0P26

DP_AUX0N26

DP_AUX1P26

DP_AUX1N26

R374 *2K/FR374 *2K/F

R372 *2K/FR372 *2K/F

VCC1.8

STRP_DATA

4

VCC3

INT_CRT_RED28

INT_CRT_GREEN28

INT_CRT_BLU28

INT_CRT_HSYNC10,28

INT_CRT_VSYNC10,28

INT_CRT_DDCDAT28

INT_CRT_DDCCLK28

R111 0R111 0

1 2

NB_REFCLK_N

VCC3

BLM18PG181SN1D(180,1.5A)_6

BLM18PG181SN1D(180,1.5A)_6

VCC1.8

BLM18PG181SN1D(180,1.5A)_6

BLM18PG181SN1D(180,1.5A)_6

C233

C233

10U/6.3V_8

10U/6.3V_8

4

140ohm CS11402FB19

R364 *0/short_4R364 *0/short_4

R353 140/F_4R353 140/F_4

R365 *0/short_4R365 *0/short_4

R354 150/F_4R354 150/F_4

R366 *0/short_4R366 *0/short_4

R355 150/F_4R355 150/F_4

R361 *0/short_4R361 *0/short_4

R362 *0/short_4R362 *0/short_4

R371 *0/short_4R371 *0/short_4

R370 *0/short_4R370 *0/short_4

R115 715/ F_6R115 715/F_6

20mA

120mA

RP27 0_4P2R_4RP27 0_4P2R_4

4

R313 *4.7KR313 *4.7K

R309 *4.7KR309 *4.7K

PLLVDD18 - Graphics PLL

L29

L29

2

B-36

B-4

LCD_CLK21,26

LCD_DAT21,26

R358 150RR358 150R

L33

L33

+3V_AVDD_NB

+1.8V_AVDDDI_NB

+1.8V_AVDDQ_NB

+1.1V_PLLVDD

+1.8V_PLLVDD18

+1.8V_VDDA18HTPLL

+1.8V_VDDA18PCIEPLL

NB_RST#_INNB_RST#_IN

NB_PWRGD

NB_LDT_STOP#

NB_ALLOW_LDTSTOP

3

1

B-3

T36T36

C238

C238

2.2U/6.3V_6

2.2U/6.3V_6

+1.8V_PLLVDD18

C203

C203

0.1U/10V_4

0.1U/10V_4

INT_CRT_RED_R

INT_CRT_GRE_R

INT_CRT_BLU_R

INT_CRT_HSYNC_NB

INT_CRT_VSYNC_NB

INT_DDCDAT_NB

INT_DDCCLK_NB

DAC_RSET_NBDAC_RSET_NB

STRP_DATA

RS880_AUX_CAL

BLM18PG181SN1D(180,1.5A)_6

BLM18PG181SN1D(180,1.5A)_6

VCC1.1

VCC1.8

BLM18PG181SN1D(180,1.5A)_6

BLM18PG181SN1D(180,1.5A)_6

L30

L30

3

U23C

U23C

F12

AVDD1(NC)

E12

AVDD2(NC)

F14

AVDDDI(NC)

G15

AVSSDI(NC)

H15

AVDDQ(NC)

H14

AVSSQ(NC)

E17

C_Pr(DFT_GPIO5)

F17

Y(DFT_GPIO2)

F15

COMP_Pb(DFT_GPIO4)

G18

RED(DFT_GPIO0)

G17

REDb(NC)

E18

GREEN(DFT_GPIO1)

F18

GREENb(NC)

E19

BLUE(DFT_GPIO3)

F19

BLUEb(NC)

A11

DAC_HSYNC(PWM_GPIO4)

B11

DAC_VSYNC(PWM_GPIO6)

F8

DAC_SCL(PCE_RCALRN)

E8

DAC_SDA(PCE_TCALRN)

G14

DAC_RSET(PWM_GPIO1)

A12

PLLVDD(NC)

D14

PLLVDD18(NC)

B12

PLLVSS(NC)

H17

VDDA18HTPLL

D7

VDDA18PCIEPLL1

E7

VDDA18PCIEPLL2

D8

SYSRESETb

A10

POWERGOOD

C10

LDTSTOPb

C12

ALLOW_LDTSTOP

C25

HT_REFCLKP

C24

HT_REFCLKN

E11

REFCLK_P/OSCIN(OSCIN)

F11

REFCLK_N(PWM_GPIO3)

T2

GFX_REFCLKP

T1

GFX_REFCLKN

U1

GPP_REFCLKP

U2

GPP_REFCLKN

V4

GPPSB_REFCLKP(SB_REFCLKP)

V3

GPPSB_REFCLKN(SB_REFCLKN)

B9

I2C_CLK

A9

I2C_DATA

A8

DDC_CLK0/AUX0P(NC)

B8

DDC_DATA0/AUX0N(NC)

B7

DDC_CLK1/AUX1P(NC)

A7

DDC_DATA1/AUX1N(NC)

B10

STRP_DATA

G11

RSVD

C8

AUX_CAL(NC)

RS880M

RS880M

L28

L28

R117 0/ J_6R117 0/J_6

3

+1.1V_PLLVDD+3V_AVDD_NB

C222

C222

2.2U/6.3V_6

2.2U/6.3V_6

+1.8V_AVDDDI_NB

C223

C223

0.1U/10V_4

0.1U/10V_4

+1.8V_AVDDQ_NB

C224

C224

0.1U/10V_4

0.1U/10V_4

PART 3 OF 6

PART 3 OF 6

TXOUT_L2N(DBG_GPIO0)

TXOUT_L3N(DBG_GPIO2)

TXOUT_U1P(PCIE_RESET_GPI O3)

TXOUT_U1N(PCIE_RESET_GPI O2)

TXOUT_U3P(PCIE_RESET_GPI O5)

CRT/TVOUT

CRT/TVOUT

TXCLK_LP(DBG_GPIO1)

TXCLK_LN(DBG_GPIO3)

TXCLK_UP(PCIE_RESET_GPIO4)

TXCLK_UN(PCIE_RESET_GPIO1)

LVTM

LVTM

PM

PM

LVDS_DIGON(PCE_TCALRP)

LVDS_BLON(PCE_RCALRP)

LVDS_ENA_BL(PWM_GPIO2)

CLOCKs PLL PWR

CLOCKs PLL PWR

MIS.

MIS.

SUS_STAT#(PWM_GPIO5)

THERMALDIODE_P

THERMALDIODE_N

PLLVDD - Graphics PLLAVDD-DAC Analog

AVDDI-DAC Digital

AVDDQ-DAC Bandgap Reference

TXOUT_L0P(NC)

TXOUT_L0N(NC)

TXOUT_L1P(NC)

TXOUT_L1N(NC)

TXOUT_L2P(NC)

TXOUT_L3P(NC)

TXOUT_U0P(NC)

TXOUT_U0N(NC)

TXOUT_U2P(NC)

TXOUT_U2N(NC)

TXOUT_U3N(NC)

VDDLTP18(NC)

VSSLTP18(NC)

VDDLT18_1(NC)

VDDLT18_2(NC)

VDDLT33_1(NC)

VDDLT33_2(NC)

VSSLT1(VSS)

VSSLT2(VSS)

VSSLT3(VSS)

VSSLT4(VSS)

VSSLT5(VSS)

VSSLT6(VSS)

VSSLT7(VSS)

TMDS_HPD(NC)

HPD(NC)

TESTMODE

2

A22

B22

A21

B21

B20

A20

A19

B19

B18

A18

A17

B17

D20

D21

D18

D19

B16

A16

D16

D17

+1.8V_VDDLTP18_NB

A13

B13

+1.8V_VDDLT_18_NB

A15

B15

A14

B14

C14

D15

C16

C18

C20

E20

C22

E9

F7

G12