Page 1

5

4

3

2

1

Tonga-e (ZN5)

D D

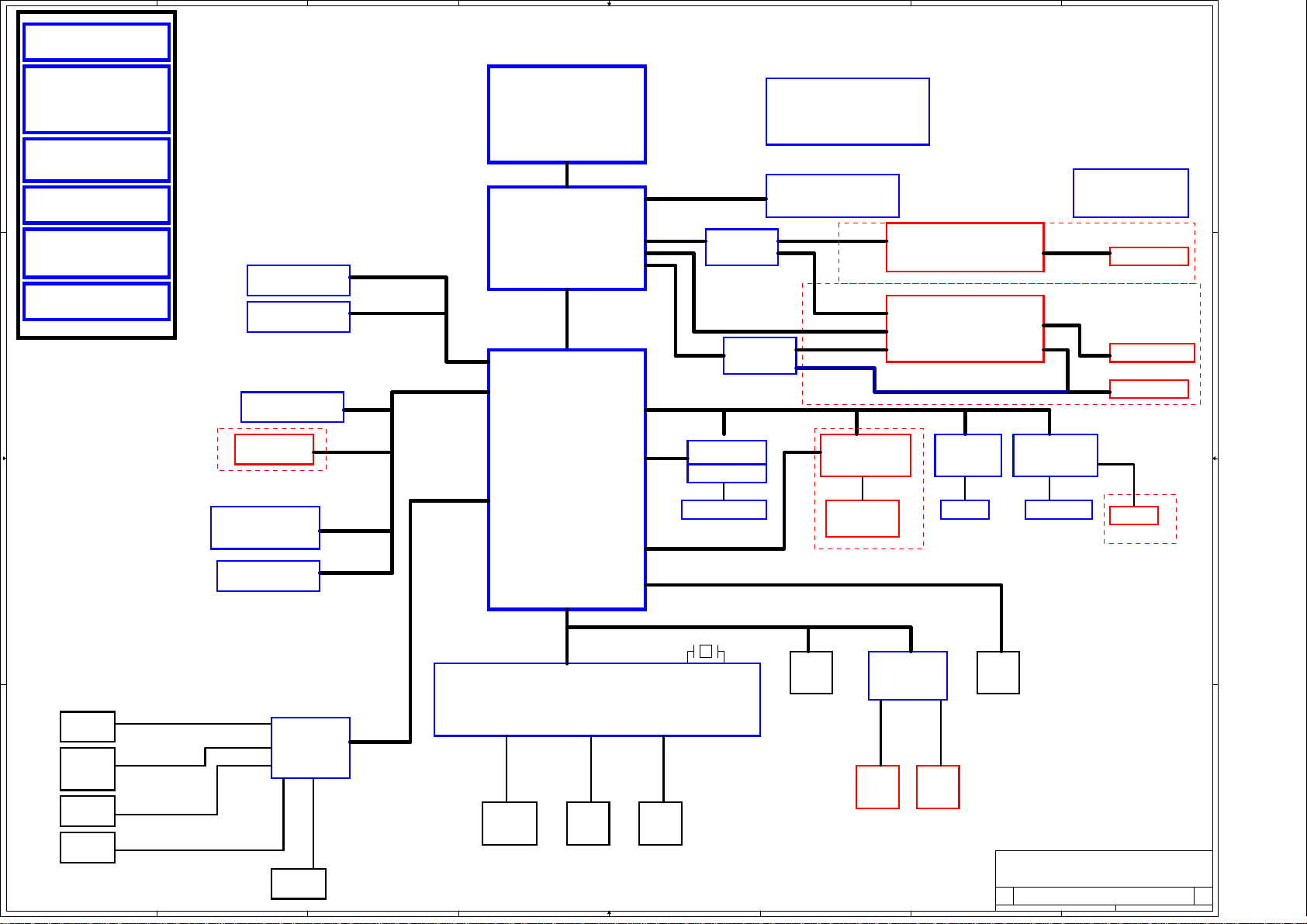

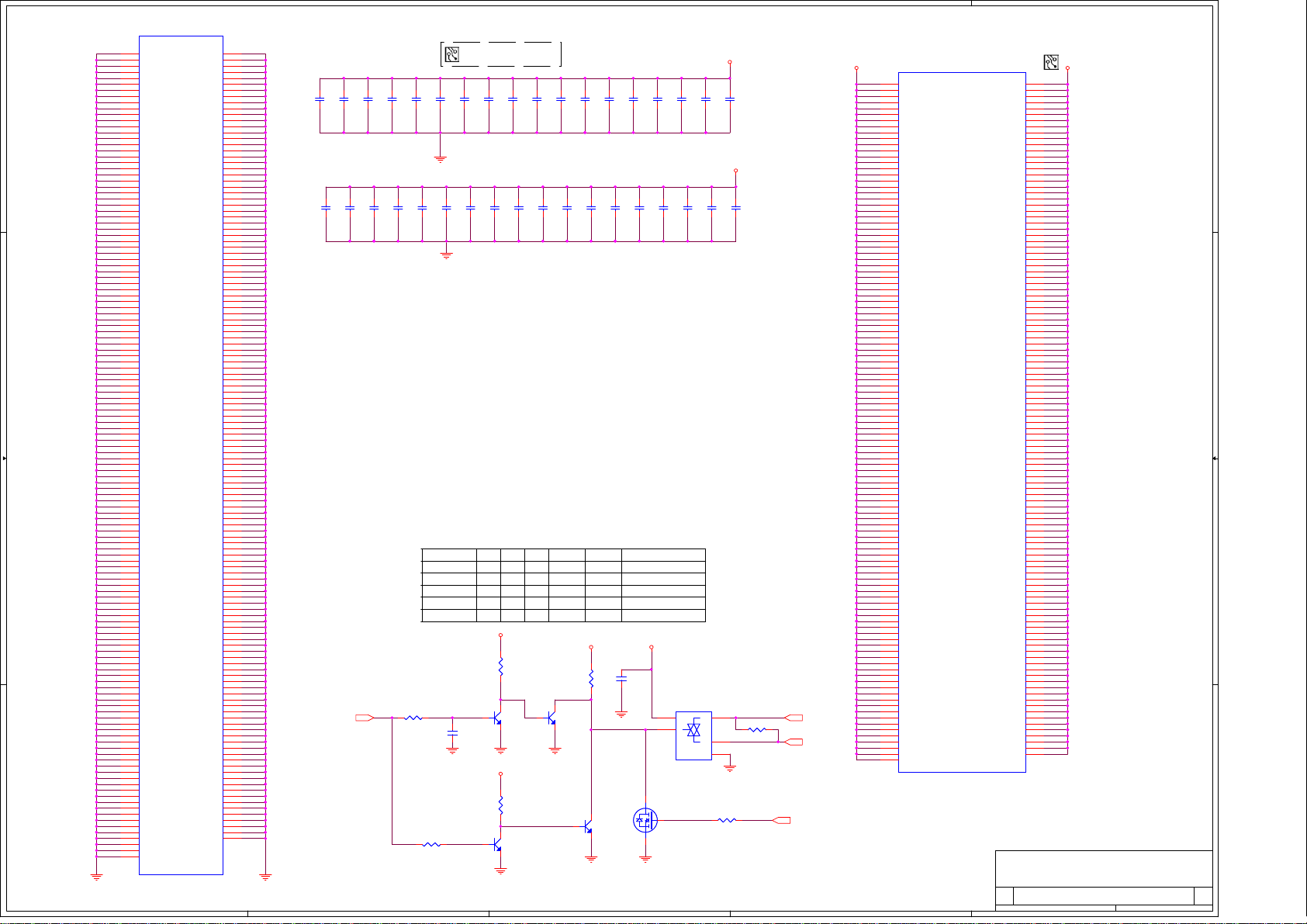

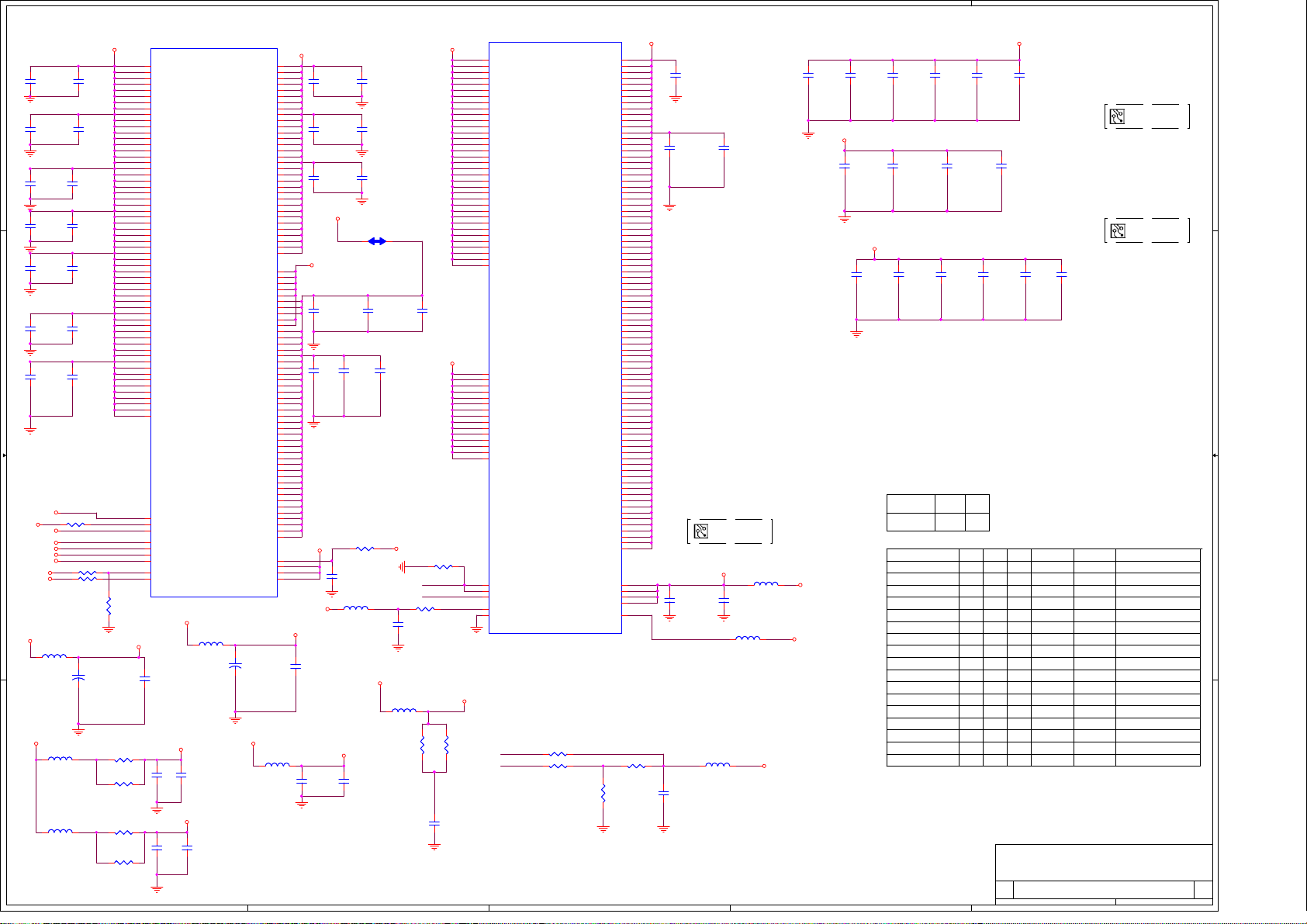

01--SCHMETICS INDEX

01

02--BLOCK DIAGRAM

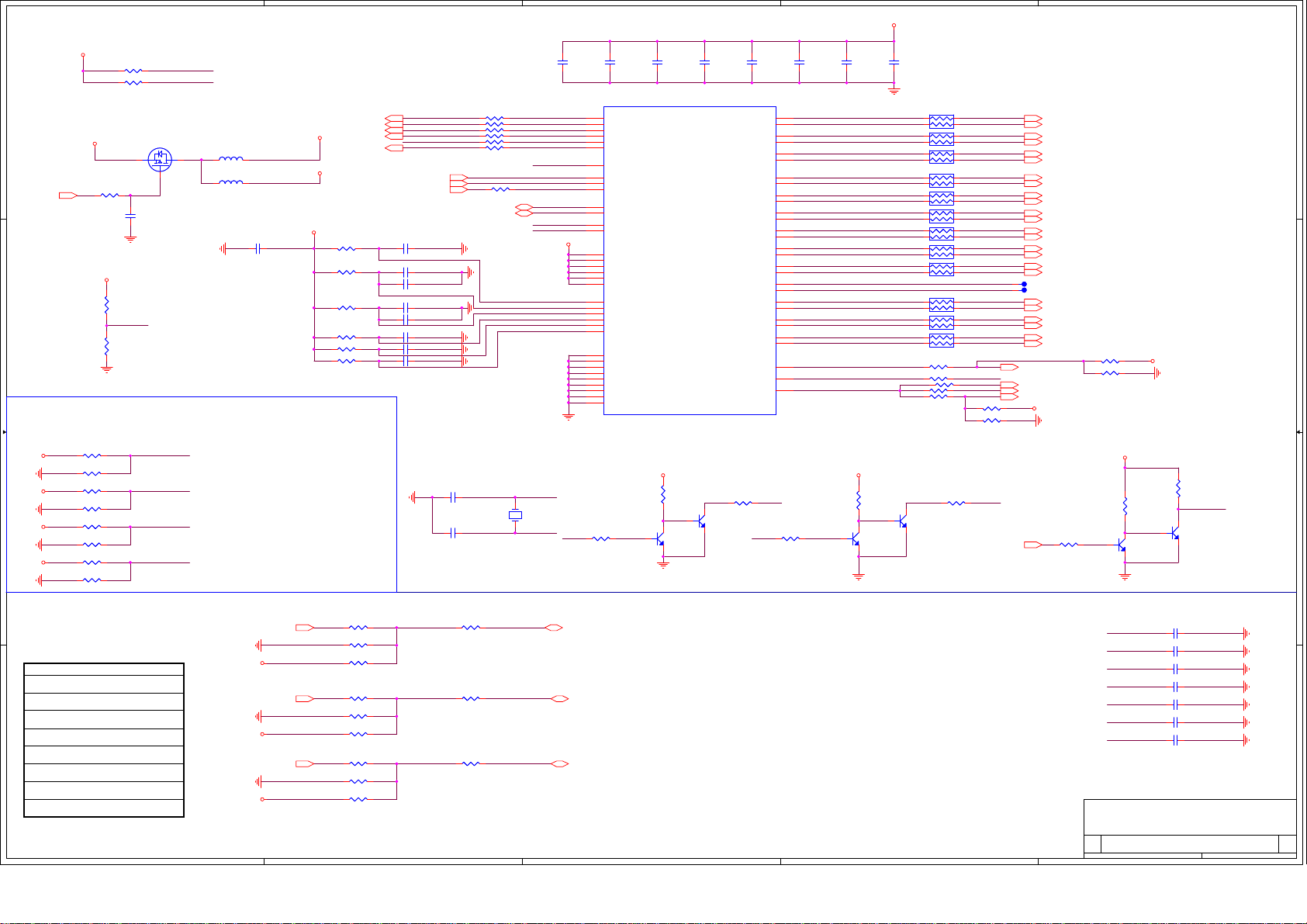

03--CLK. GEN./CK505

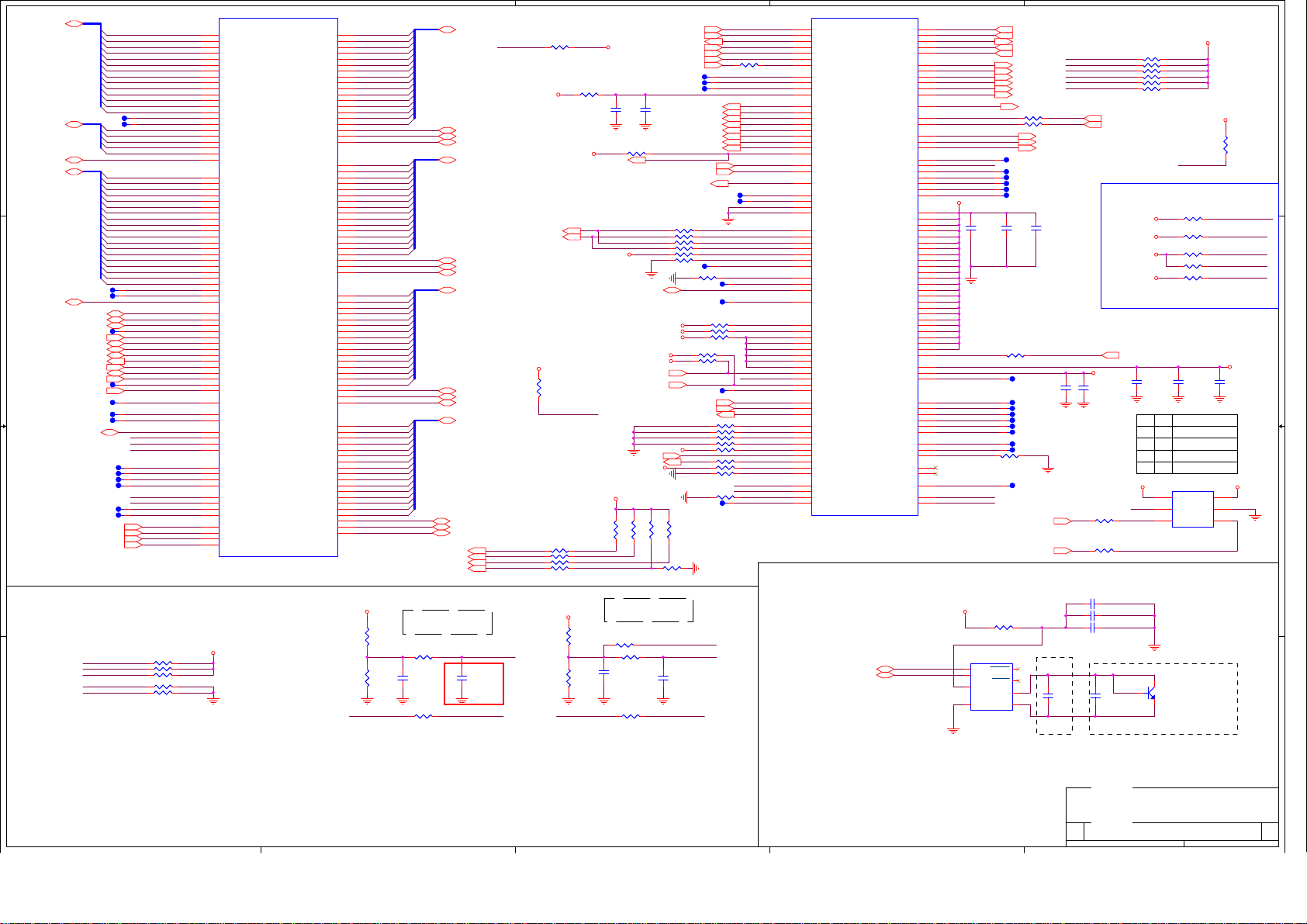

04--CPU(1/2) Host Bus

05--CPU(2/2) Power

06--NB(1/5) Host

07--NB(2/5) VGA,DMI,PCIE

08--NB(3/5) DDR III

09--NB(4/5) Power

10--NB(5/5) VSS

11--SB(1/4) HOST

12--SB(2/4) PCIE, PCI, USB, DMI

13--SB(3/4) SATA, GPIO

14--SB(4/4) Power, VSS

C C

15--DDR III SO-DIMM

16--MXM3.0

17--LVDS TRANSMITTER

18--SATA HDD/ODD

19--MINI PCIE (WLAN/TV), IR

20--LCD PANEL, INVERTER

21--LAN PHY BOAZMAN

22--TPM, RJ45

23--JMB380 (Card Reader, 1394)

24--ON Board USB

25--FAN, CCD, PS2

26--SUPER IO SCH5327

27--AUDIO CODEC ALC272

28--LINE OUT, CRT

29--LED/SERIAL PORT/XDP

B B

30--CIR

31--DC-IN,+12V

32--VRD1.1 NCP5392

33--V_1P1_CORE

34--5VSB,3VSB,VCC3,VCC

35--V_3P3_CL/V_1V_1P1

36--DDR3_V-SM_V-SM-VTT

37--SCREW HOLE

38--SCHEMATICS CHANGE LIST(EVT1 to EVT2)

39--SCHEMATICS CHANGE LIST(EVT2 to DVT)

BOM Option Note

IV@

INSTALL FOR UMA SKU

EV@

INSTALL FOR DISCRETE GRAPHIC SKU

INSTALL FOR PROTO ONLY

PROTO

NI UNINSTALL

INSTALL FOR ALL SKU

A A

5

4

I

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Schematics Index

Schematics Index

Schematics Index

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

PROJECT :

ZN5

ZN5

ZN5

1 40Friday, March 05, 2010

1 40Friday, March 05, 2010

1

1 40Friday, March 05, 2010

X4

X4

X4

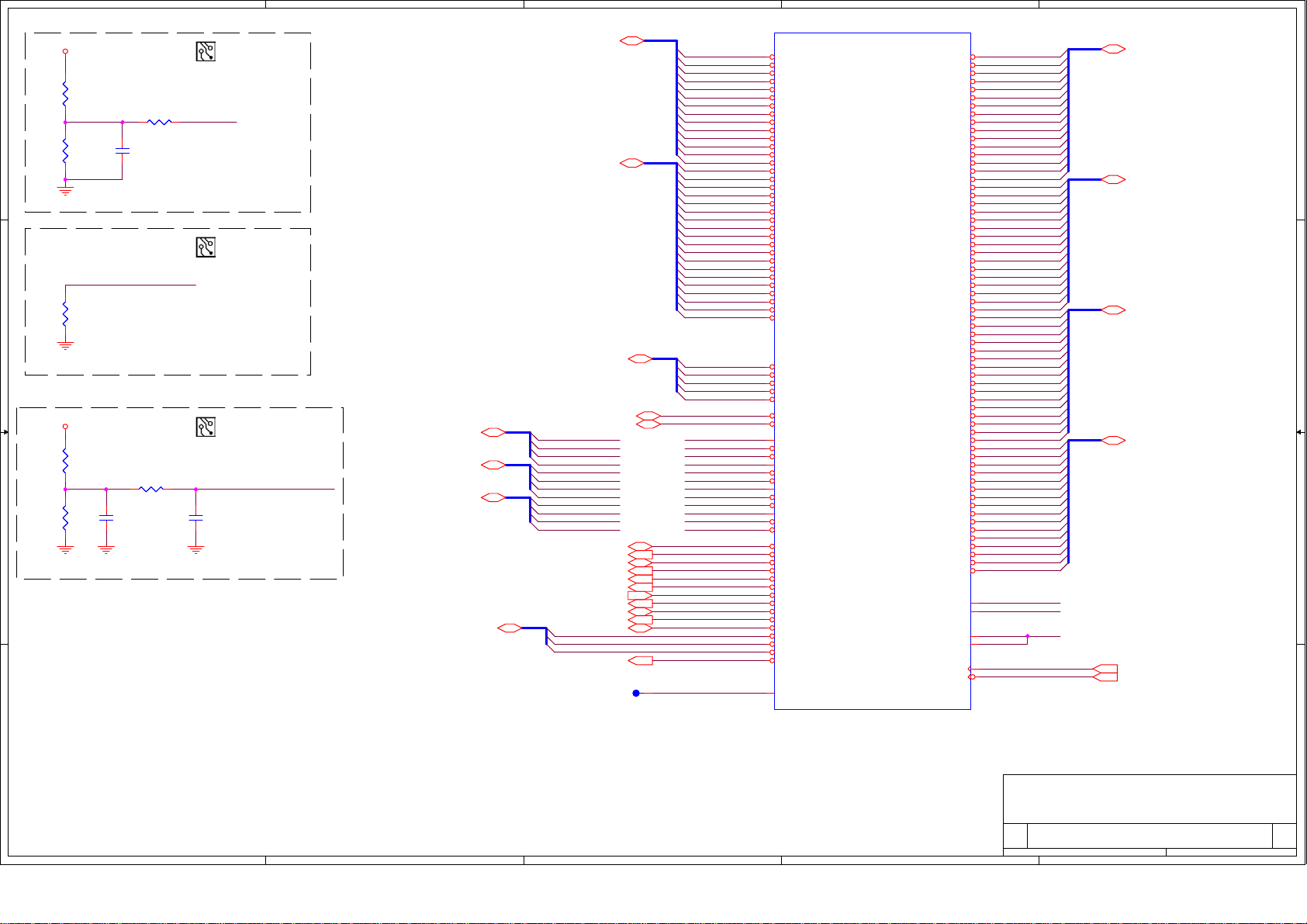

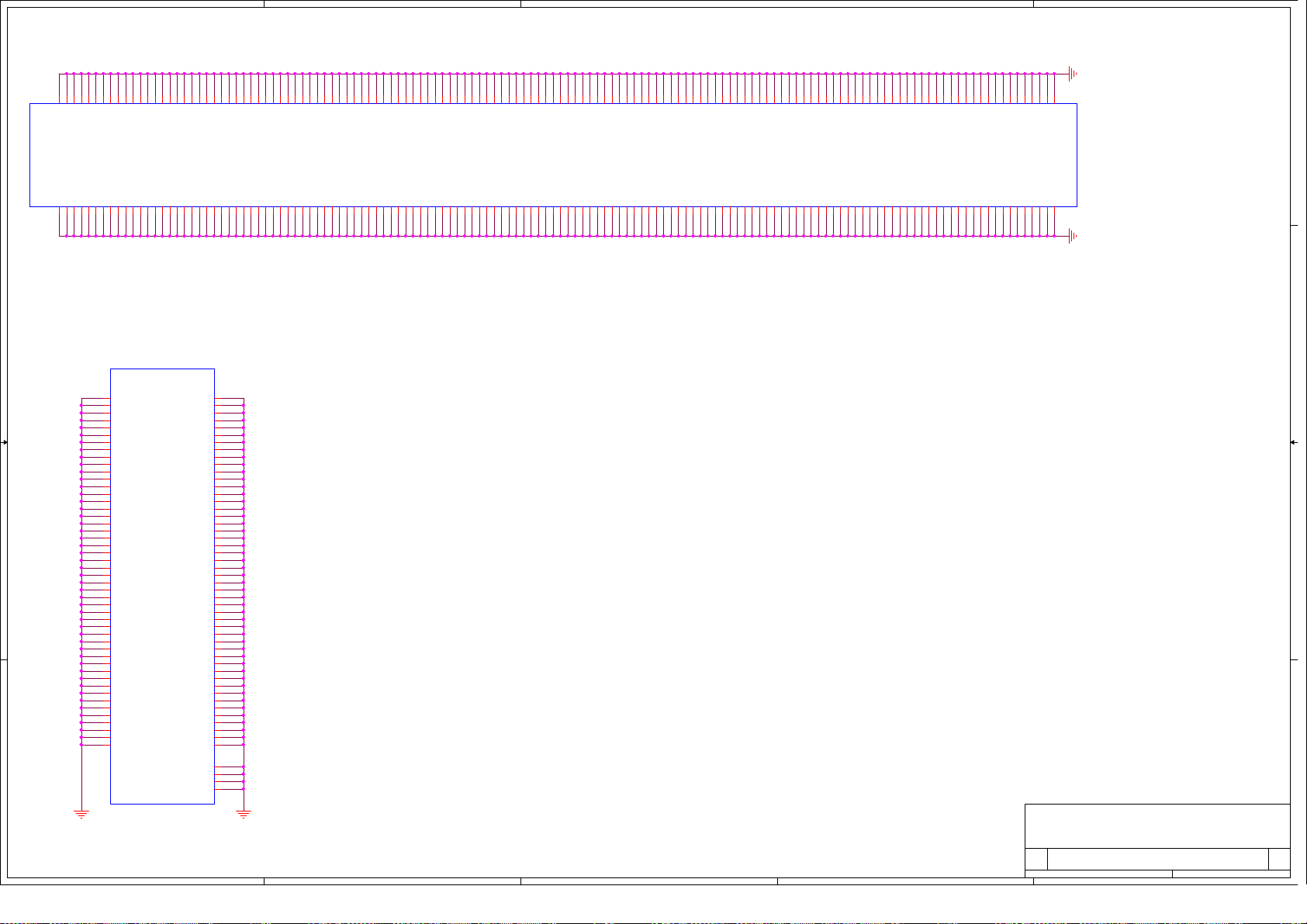

Page 2

1

2

3

4

5

6

7

8

VCCP

V_1P1_CORE

V_1P1_PCIEXPRESS

V_1P1_ICH

V_FSB_VTT

A A

V_1P1_CL_MCH

V_3P3_CL

VCC3

3VSB

VCC

5VSB

+12V

V_SM

V_1P5_ICH

System Power

B B

C C

SATA - HDD(3.5)

SATA - ODD

Camera

USB/wirless KB

Dongle

USB*4(Rear)

USB-0 for DEBUG

USB*2(Side)

Page 23

Page 23

Page 17

Page 17

Page 24

USB-0,7,8,9

USB-3,5

Tonga-E _ZN5 System Block Diagram

Intel

Yorkfield LP

Wolfdale/Conroe

E7XX0/E8XX0

USB-1

USB-4

SATA 1

SATA 2

USB 2.0

Azalia

LGA775

NB

Eaglelake

Q43

1254 pin

SB

ICH10D

676 pin

Page 3,4

FSB(800/1067/1333HZ)

PCI-E 2.0 16X

Page 5,6,7,8,9

DMI

Page 10,11,12,13

800/1067 MHZ DDR III

MUX

PI3PCIE2612-A

MUX

PI3PCIE2612-A

PCI-Express 1X

PCIE-2 PCIE-1

MINI CARD-1

USB-10

Page 18

WLAN

Bluetooth

USB-11

SPI

CLOCK GENERATOR

CK505

CV193

CH A/B: DDRIII-SO-DIMM

Page 14

SDVO

PCI-E(0-3)

PCI-E(7-15)

PCI-E(4-6)

PCIE-3

MINI CARD-2

TV card

Page 18

TV antenna or WLAN antenna

(F connect)

Page 2

LVDS Transmitter

CH7308B

MXM CONNECTOR

VER:3.0

LAN

82567QM

Page 20

RJ45

Page 16

Page 15

PCIE-4

Card Reader

/JMB380

Media Slot

LCD PANEL

LVDS

LVDS

DP

/JMB385

Page 20

21.5" Full HD

LVDS_CONNECT 1

LVDS_CONNECT 2

DP connect

1394a

02

LPC_BUS

SUPER IO

32.768KHz

TPM EC ITE8512

Page 22

Page 30

FLASH

ROM

SMSC SCH5327

H.P

Page 26

A_MIC IN

Page 26

D D

2WX2

INT SPK

Page 26

DMIC IN

Page 26

1

2

AUDIO CODEC

ALC272

Page 26

LINE OUT

Page 27

PS2

Keyboard

Page 25

3

FAN

Page 24

4

PS2

Mouse

Page 25

Page 25

IR

Blaster

Page 30

5

6

CIR

Page 30

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

System Block Diagram

System Block Diagram

System Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

PROJECT :

ZN5

ZN5

ZN5

8

2 40Friday, March 05, 2010

2 40Friday, March 05, 2010

2 40Friday, March 05, 2010

X4

X4

X4

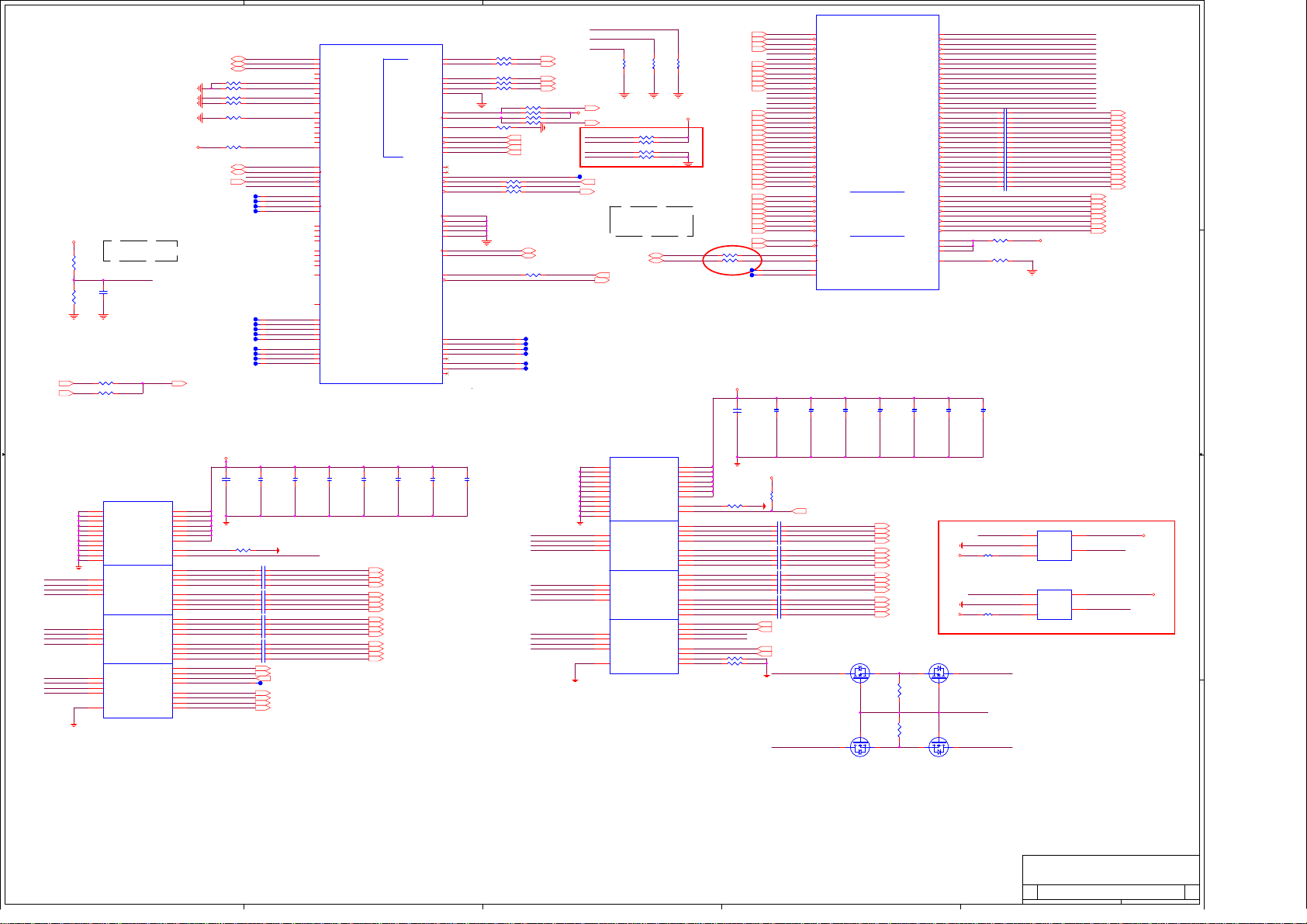

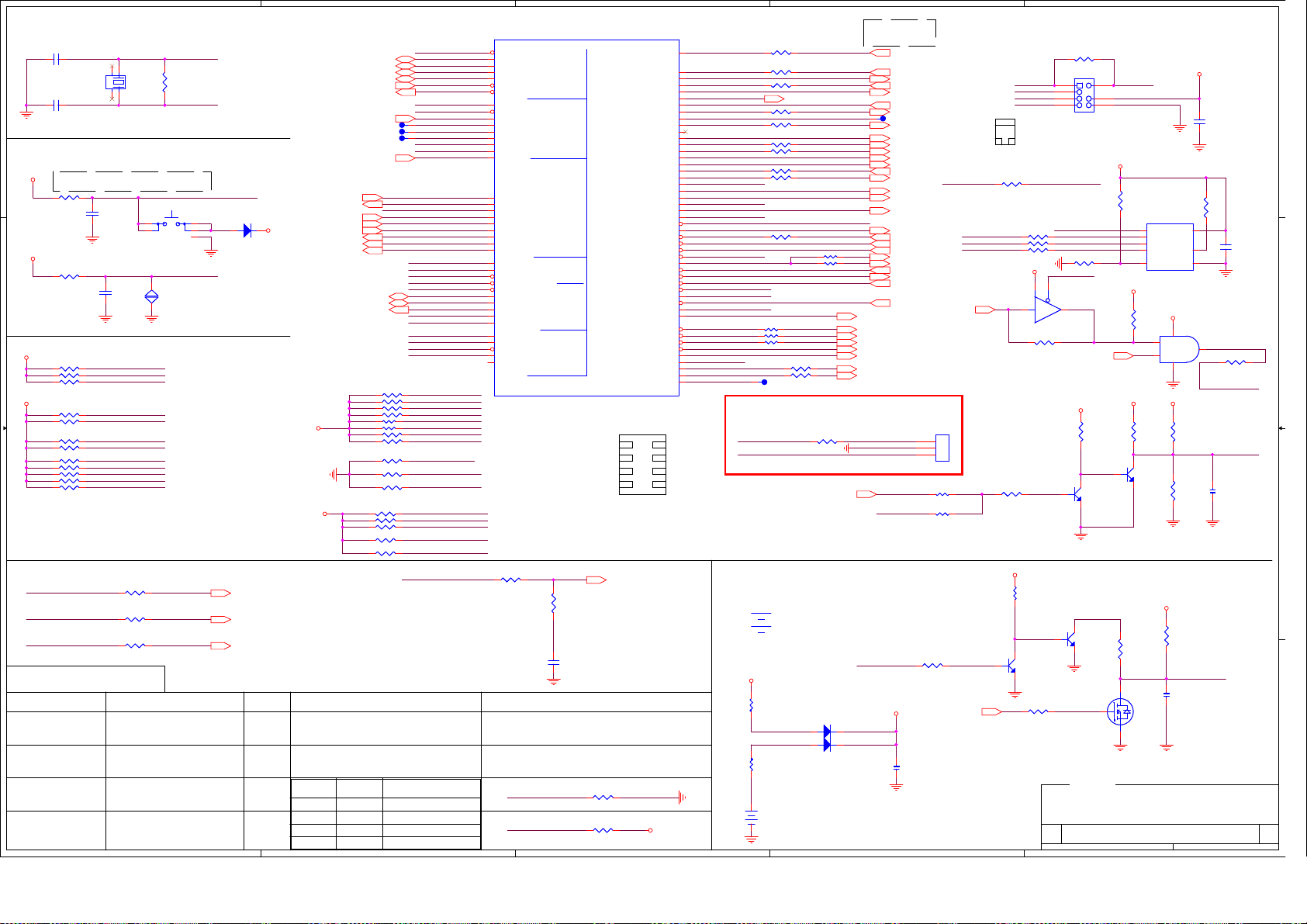

Page 3

5

Clock Generator

4

3

CKVDD_IO

2

1

03

CKVDD

PM_STPPCI#

R5012.2K

R5012.2K

0402I 5%

0402I 5%

PM_STPCPU#

R5022.2K

R5022.2K

0402I 5%

0402I 5%

D D

1A600 oh m 0603I

1A600 oh m 0603I

1A6

1A6

C102 10U

C102 10U

0805

0805

I

I

X5R

X5R

6.3V

6.3V

CKVDD_IO

3VSB

Q47_D

L5 PBY16 0808T-601 Y-N

L5 PBY16 0808T-601 Y-N

Q47_G

3

Q47

Q47

AO3413

AO3413

S

S

OT23-3

OT23-3

2

L4 PBY16 0808T-601 Y-N

L4 PBY16 0808T-601 Y-N

20V

20V

3A

3A

I

I

00 ohm 0603I

00 ohm 0603I

1

R493 47K

R493 47K

SLP_M3 5,36

C C

CKVDD

0402I 5%

0402I 5%

C499

C499

1U

1U

0603

0603

10V

10V

7R

7R

X

X

I

I

R107

R107

1K

1K

0402

0402

5

5

%

%

I

I

SEL_SRC1

R115

R115

1K

1K

0402

0402

I

I

%

%

5

5

CKVDD

CKVDD

PCLK_TPM22

PCLK_EC29,30

PCLK_DEB UG19

PCLK_SIO26

PCLK_ICH12

R146 0

R146 0

R148 0

R148 0

R147 0

R147 0

R101 0

R101 0

R100 0

R100 0

R109 0

R109 0

5%

5%

0805I 5%

0805I 5%

0805I 5%

0805I 5%

0805I 5%

0805I 5%

0805I 5%

0805I 5%

0805I 5%

0805I 5%

0805I

0805I

PCLK_TPM

PCICLK_PCI4

PCLK_ICH

PM_STPCPU#11

PM_STPPCI#11

CK_PWRGD11

C127 0.1U

C131 0.1U

C122 10U

C130 0.1U

C129 0.1U

C112 0.1U

C111 0.1U

C105 0.1U

C105 0.1U

0402I X7R

0402I X7R

0402I X7R

0402I X7R

0603I X5R

0603I X5R

0402I X7R

0402I X7R

0402I X7R

0402I X7R

0402I X7R

0402I X7R

0402I X7R

0402I X7R

0402I

0402I

R136 33

R136 33

R149 33

R149 33

R527 33 0402I5%R527 33 0402I5%

R528 33 0402I5%R528 33 0402I5%

R170 33 0402I5%R170 33 0402I5%

R522 33 0402I5%R522 33 0402I5%

10VC127 0.1U

10V

10VC131 0.1U

10V

6.3VC1 22 10U

6.3V

10VC130 0.1U

10V

10VC129 0.1U

10V

10VC112 0.1U

10V

10VC111 0.1U

10V

10V

10V

X7R

X7R

%

%

%

%

SMBCLK_MAIN16,20,26 ,29

SMBDATA_MAIN16,20,26 ,29

R508 0

R508 0

5%

5%

0402I5

0402I5

0402I5

0402I5

0402I

0402I

VDD_CK_VDD_PLL3

VDD_CK_VDD_PCI

VDD_CK_VDD_48

VDD_CK_VDD_REF

VDD_CK_VDD_CPU

VDD_CK_VDD_SRC

PCLK_TPM_R

PCLK_EC_ RPCLK_EC

PCLK_DEB UG_RPCLK_DEB UG

PCLK_SIO _RPCLK_SIO

PCICLK_PCI4_R

PCLK_ICH_ R

SEL_SRC1

PM_STPCPU#

PM_STPPCI#

CK_PWRGD_R

SMBCLK_MAIN

SMBDATA_MAIN

CG_XIN

CG_XOUT

CKVDD_IO

C116

C116

10U

10U

0805

0805

10V

10V

X7R

X7R

N

N

Pin17-18. SRC1 enabled

Strap Configuration

R518 10K

CKVDD

CKVDD

CKVDD

B B

CKVDD

R518 10K

R517 10K

R517 10K

R520 10K

R520 10K

R519 10K

R519 10K

R521 10K

R521 10K

R529 10K

R529 10K

R530 10K

R530 10K

R531 10K

R531 10K

I 5%

I 5%

PCLK_DEB UG_R

0402NI 5%

0402NI 5%

0402I 5%

0402I 5%

PCLK_SIO _R

0402NI 5%

0402NI 5%

0402I 5%

0402I 5%

PCICLK_PCI4

0402NI 5%

0402NI 5%

0402I 5%

0402I 5%

PCLK_ICH_ R

0402I 5%

0402I 5%

0402N

0402N

Internal 33 ohm resistor enabled

SATA output from PLL2

CPUSTP#/PCISTP enabled

ITPCLK enabled

C528 27P

C528 27P

C530 27P

C530 27P

21

CG_XIN

Y1

Y1

14.318MHZ

14.318MHZ

CG_XOUT

Critical

Critical

30PPM

30PPM

I

I

BSEL0

NPO

NPO

0402I

50V

0402I

50V

NPO

NPO

0402I

50V

0402I

50V

I

I

48

37

38

56

64

63

60

59

12

20

26

36

45

49

16

61

55

39

42

52

23

19

15

11

29

58

R545 4.7K

R545 4.7K

C133

C133

10U

10U

0805

0805

6.3V

6.3V

X5R

X5R

I

I

U6

U6

1

PCI0/CR#_A

3

PCI1/CR#_B

4

*PCI2/SR_ENABLE

5

**PCI3/SATA_SEL

6

PCI4/SRC5_EN

7

PCI_F5/ITP_EN

SEL_SRC1_25_24.576**

CPU_STOP#/SRCC5

PCI_STOP#/SRCT5

CKPWRGD/PD#

SCL

SDA

XTAL_IN

XTAL_OUT

VDDIO

VDDPLL3IO

VDDSRCIO

VDDSRCIO

VDDSRCIO

VDDCPUIO

VDDPLL3

2

VDDPCI

9

VDD48

VDDREF

VDDCPU

VDDSRC

GNDSRC

GNDCPU

GNDSRC

GND

GND

GND48

8

GNDPCI

GNDSRC

GNDREF

CV193

CV193

SSOP64

SSOP64

T

T

Critical

Critical

I

I

Q54_B

0402I 5%

0402I 5%

C126

CLK_CPU_BCLK_R

54

CLK_CPU_BCLK#_R

53

CLK_MCH_B CLK_R

51

CLK_MCH_B CLK#_R

50

XDP_DCLKOUT_DP_R

47

XDP_DCLKOUT_DN_R

46

DREFCLK_R

13

DREFCLK#_ R

14

DREFSSCLK _R

17

DREFSSCLK #_R

18

CLK_PCIE_SATA_R

21

CLK_PCIE_SATA#_R

22

MXM_PEGCLK_R

24

MXM_PEGCLK#_R

25

CLK_PCIE_EXP_R

27

CLK_PCIE_EXP#_R

28

CLK_PCIE_ICH_R

41

CLK_PCIE_ICH#_R

40

U6_44

44

U6_43

43

CLK_PCIE_MINI_R

30

CLK_PCIE_MINI#_R

31

CLK_PCIE_MINI2_R

34

CLK_PCIE_MINI2#_R

35

CLK_PCIE_JMB385_ R

33

CLK_PCIE_JMB385# _R

32

10

57

62

R494 4.7K

R494 4.7K

C126

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

Q48_B

0402I 5%

0402I 5%

C113

C128

Q54_C

CK505

CK505

R532

R532

1K

1K

0402

0402

5%

5%

I

I

I

I

2

C128

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

SRCC1/25MHz1/24.576MHz

*Internal 100K Pull High

**Internal 100K Pull Low

Q55_C FSA

Q55

Q55

MMBT3904-7-F

MMBT3904-7-F

SOT23-3

SOT23-3

1 3

40V

40V

200mA

200mA

I

I

C114

C114

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

CKVDD CKVDD

Q54

Q54

MMBT3904-7-F

MMBT3904-7-F

SOT23-3

SOT23-3

2

40V

40V

200mA

200mA

1 3

C113

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

CPUT0

CPUC0

CPUT1

CPUC1

SRCT8/CPU_ITPT

SRCC8/CPU_ITPC

DOT96T/SRCT0

DOT96C/SRCC0

SRCT1/25MHz0

SRCT2/SATAT

SRCC2/SATAC

SRCT3/CR#_C

SRCC3/CR#_D

SRCT4

SRCC4

SRCT6

SRCC6

SRCT7/CR#_F

SRCC7/CR#_E

SRCT9

SRCC9

SRCT10

SRCC10

SRCT11/CR#_H

SRCC11/CR#_G

USB48/FS_A

FS_B/TESTMODE

REF/FS_C/TESTSEL

R5231K

R5231K

0402I 5%

0402I 5%

BSEL2

C125

C115

C115

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

FSA

FSB BSEL1

FSC

2

C125

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

RP2 33X 2

RP2 33X 2

5%

5%

RP3 33X 2

RP3 33X 2

RP4 33X 2

RP4 33X 2

5%

5%

RP8 IV@2 2X2

RP8 IV@2 2X2

RP9 IV@3 3X2

RP9 IV@3 3X2

RP10 33X2

RP10 33X2

RP11 EV@33X2

RP11 EV@33X2

RP12 33X2

RP12 33X2

RP5 33X 2

RP5 33X 2

5%

5%

RP13 33X2

RP13 33X2

RP6 33X 2

RP6 33X 2

RP7 33X 2

RP7 33X 2

R507 1K 040 2I5%R507 1K 040 2I

R114 33 0402I5%R114 33 0402I

R503 IV@22 04 02NI5%R503 IV@22 04 02NI

R102 33 0402I5%R102 33 0402I

R489

R489

1K

1K

0402

0402

5%

5%

I

I

Q49

Q49

Q48_C

MMBT3904-7-F

MMBT3904-7-F

2

S

Q48

Q48

MMBT3904-7-F

MMBT3904-7-F

SOT23-3

SOT23-3

40V

40V

200mA

200mA

1 3

S

40V

40V

1 3

200mA

200mA

I

I

1

3

1

3

1

3

3

1

3

1

3

1

3

1

3

1

1

3

3

1

3

1

1

3

R524 33

R524 33

5%

5%

5%

5%

Q49_C

OT23-3

OT23-3

I

I

2

4P2RI

4P2RI

4

2

4P2RI 5%

4P2RI 5%

4

2

4P2RI

4P2RI

4

4

4P2RI 5%

4P2RI 5%

2

4

4P2RI 5%

4P2RI 5%

2

4

4P2RI 5%

4P2RI 5%

2

4

4P2RI 5%

4P2RI 5%

2

4

4P2RI 5%

4P2RI 5%

2

2

4P2RI

4P2RI

4

4

4P2RI 5%

4P2RI 5%

2

4

4P2RI 5%

4P2RI 5%

2

2

4P2RI 5%

4P2RI 5%

4

0402I 5%

0402I 5%

R104 47K

R104 47K

R103 33K

R103 33K

FSC

R4991K

R4991K

0402I 5%

0402I 5%

ICH_VRMPW RGD11,29

0402I 5%

0402I 5%

0402I 5%

0402I 5%

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_B CLK 6

CLK_MCH_B CLK# 6

XDP_DCLKOUT_DP 4 ,29

XDP_DCLKOUT_DN 4,29

DREFCLK 7

DREFCLK# 7

DREFSSCLK 7

DREFSSCLK # 7

CLK_PCIE_SATA 13

CLK_PCIE_SATA# 13

MXM_PEGCLK 16

MXM_PEGCLK# 16

CLK_PCIE_EXP 7

CLK_PCIE_EXP# 7

CLK_PCIE_ICH 12

CLK_PCIE_ICH# 12

T173T173

T174T174

CLK_PCIE_MINI 19

CLK_PCIE_MINI# 19

CLK_PCIE_MINI2 19

CLK_PCIE_MINI2# 19

CLK_PCIE_JMB385 23

CLK_PCIE_JMB385# 23

CLKUSB_4 8 12

CLK14SMC 26

14M_CH7308B 17

14M_ICH 11

CKVDD

R491 10K

R491 10K

0402NI 5%

0402NI 5%

Q44_B

R167 47K

R167 47K

5%

5%

R166 33K

R166 33K

R487

R487

10K

10K

0402

0402

5%

5%

NI

NI

2

To CPU

To NB

To CPU

To NB

To NB

To SB

To MXM

To NB

To SB

To WLAN

To TV

To Card Reader

CKVDD

0402I

0402I

0402I 5%

0402I 5%

CKVDD

Q44_C

Q44

Q44

2

MMBT3904-7-F

MMBT3904-7-F

SOT23-3

SOT23-3

40V

40V

200mA

200mA

1 3

NI

NI

R486

R486

10K

10K

CK_PWRGD_R

Q43

Q43

MMBT3904-7-F

MMBT3904-7-F

SOT23-3

SOT23-3

1 3

40V

40V

200mA

200mA

NI

NI

0402 NI

0402 NI

5%

5%

BSEL0

R548 10K

R547 0

FREQ. SEL TABLE

BSEL Frequency Select Table

FSC FSB FSA Frequency

0

0

0

0

1

0

A A

1

1

0

1

1

101

1

266Mhz0

1

133Mhz

1

166Mhz

0

200Mhz

333Mhz

001

1

100Mhz

0

400Mhz

Reserved

5

CPU_BSEL 04

V_FSB_VTT

CPU_BSEL 14

V_FSB_VTT

CPU_BSEL 24

V_FSB_VTT

R547 0

R546 0

R546 0

R549 470

R549 470

5%

5%

R504 0

R504 0

R497 0

R497 0

R498 470

R498 470

5%

5%

R490 0

R490 0

R492 0

R492 0

R496 470

R496 470

5%

5%

0402I 5%

0402I 5%

0402NI 5%

0402NI 5%

0402I

0402I

0402I 5%

0402I 5%

0402NI 5%

0402NI 5%

0402I

0402I

0402I 5%

0402I 5%

0402NI 5%

0402NI 5%

0402I

0402I

R548 10K

BSEL1

R500 10K

R500 10K

BSEL2

R488 10K

R488 10K

4

MCH_BSEL0

0402I 5%

0402I 5%

MCH_BSEL1

0402I 5%

0402I 5%

MCH_BSEL2

0402I 5%

0402I 5%

MCH_BSEL0 7

MCH_BSEL1 7

MCH_BSEL2 7

PCICLK_PCI4

C542 10P

PCLK_SIO

C541 22P

CLKUSB_4 8

C155 10P

14M_ICH

C103 10P

PCLK_ICH

C163 22P

PCLK_DEB UG

C540 22P

14M_CH7308B

C517 10P

C517 10P

I COG

I COG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CLK. GEN./ CK505

CLK. GEN./ CK505

CLK. GEN./ CK505

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

50VC542 10P

50V

0402NI COG

0402NI COG

50VC541 22P

50V

0402I COG

0402I COG

50VC155 10P

50V

0402NI COG

0402NI COG

50VC103 10P

50V

0402I COG

0402I COG

50VC163 22P

50V

0402I COG

0402I COG

50VC540 22P

50V

0402I NPO

0402I NPO

50V

50V

0402N

0402N

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

ZN5

ZN5

ZN5

3 40Friday, March 05, 2010

3 40Friday, March 05, 2010

3 40Friday, March 05, 2010

X4

X4

X4

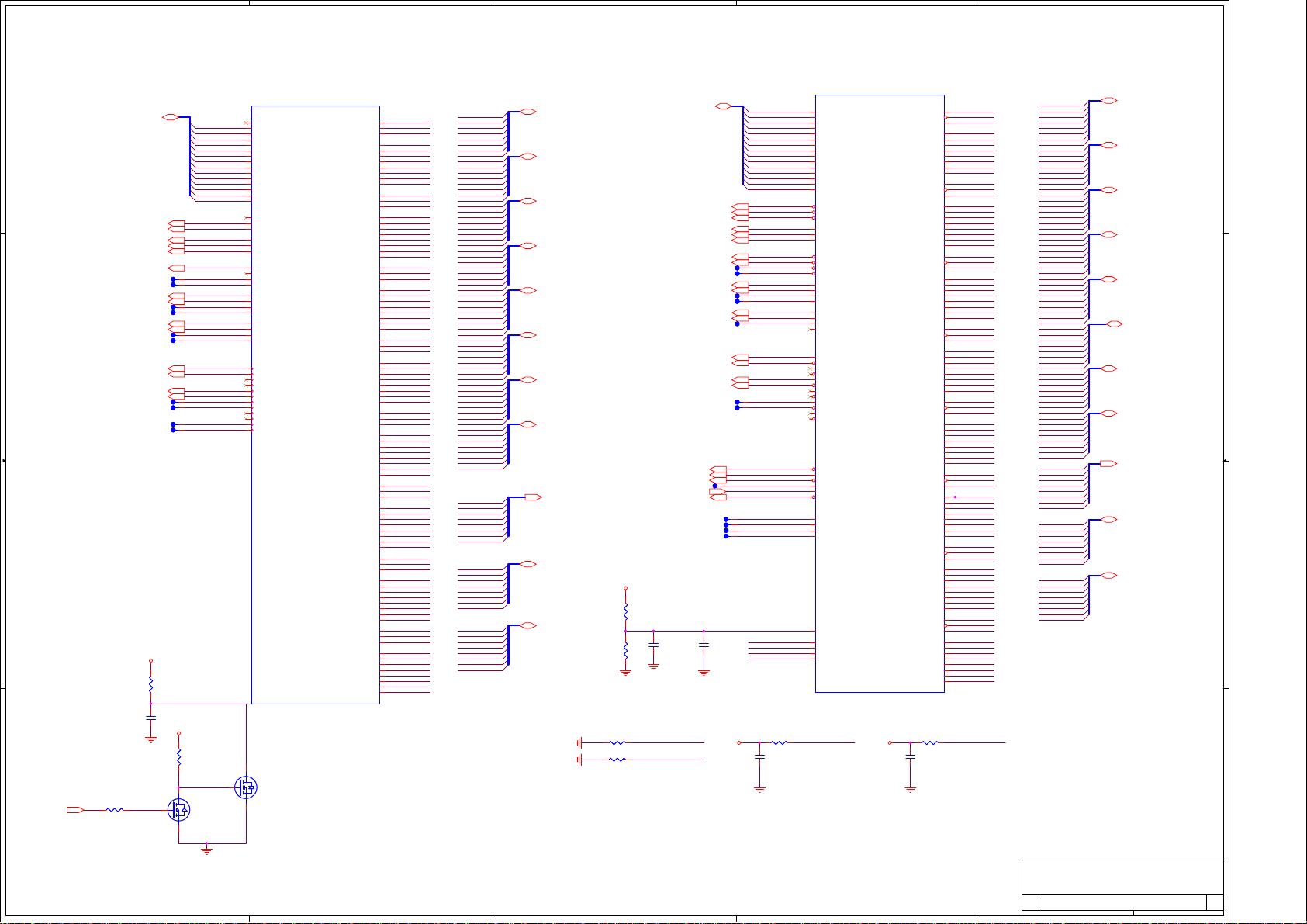

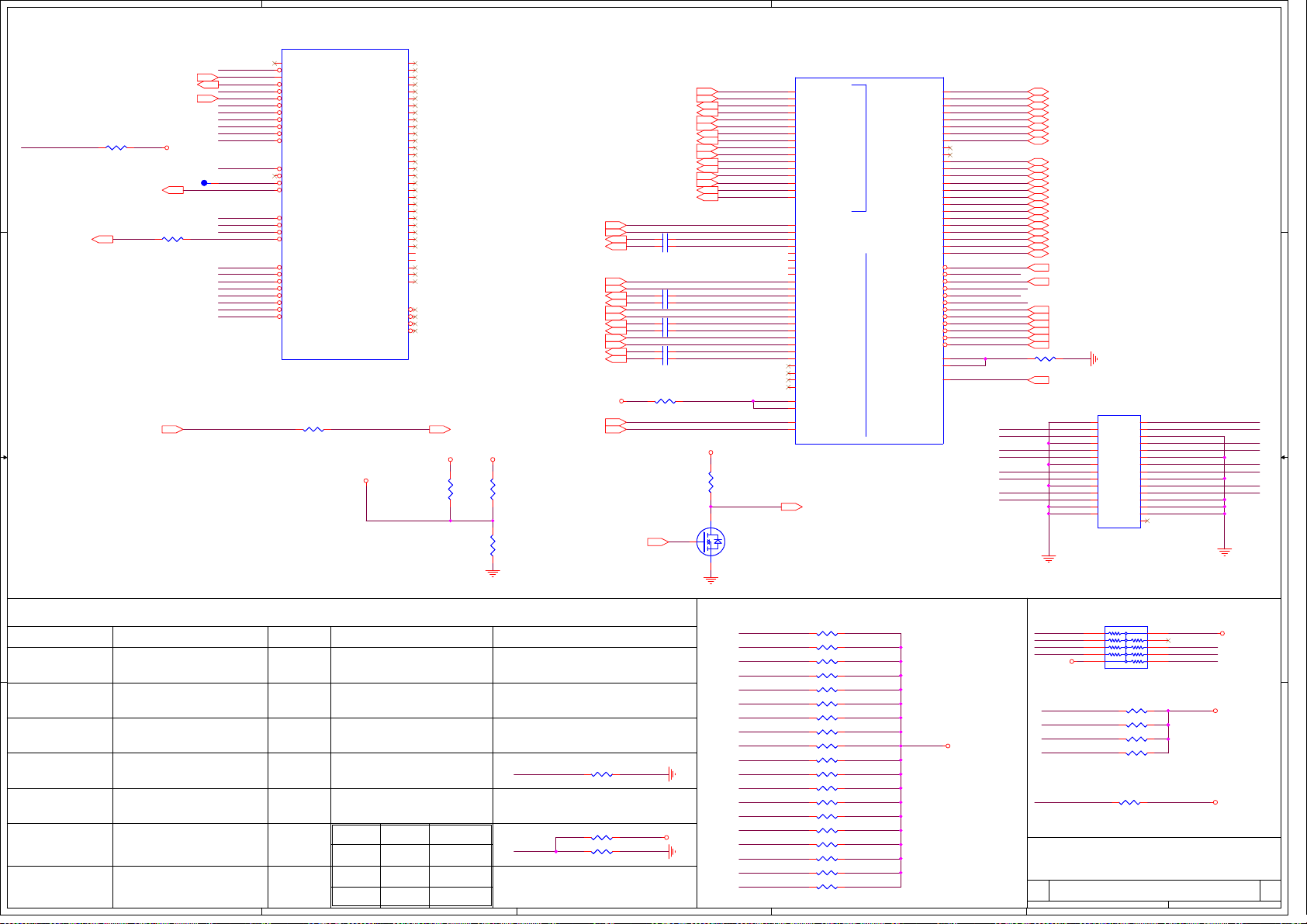

Page 4

5

H_A#[3..1 6]6

D D

H_REQ#[0..4]6

H_ADSTB#06

H_A#[17..35]6

H_ADSTB#16

C C

B B

H_ADS#6

H_BNR#6

H_BPRI#6

H_DBSY#6

H_DRDY#6

H_HITM#6

H_IERR#29

H_INIT#13

H_LOCK#6

H_TRDY#6

H_DEFER#6

H_BREQ#6

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

TP_LGA775_N4

T82T82

TP_LGA775_P5

T93T93

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

TP_LGA775_AC4

T77T77

TP_LGA775_AE5

T91T91

H_ADSTB#1

H_ADS#

H_BNR#

H_HIT#

H_HIT#6

TP_LGA775_H4

T83T83

H_BPRI#

H_DBSY#

H_DRDY#

H_HITM#

H_IERR#

H_INIT#

H_LOCK#

H_TRDY#

TP_LGA775_AD3

T76T76

H_DEFER#

TP_LGA775_AB3

T80T80

TP_LGA775_U2

T81T81

TP_LGA775_U3

T87T87

H_BREQ#

BPMb#3

BPMb#2

CPU_TEST10

TP_LGA775_J16

T101T101

TP_LGA775_H15

T106T106

TP_LGA775_H16

T104T104

TP_LGA775_J17

T110T110

CPU_GTLREF0

CPU_GTLREF1

TP_LGA775_E24

T132T132

TP_LGA775_H29

T137T137

H_CPURST#5,6 ,29

H_RS#06

H_RS#16

H_RS#26

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

AB6

AA4

AD6

AA5

AB5

AC5

AB4

AF5

AF4

AG6

AG4

AG5

AH4

AH5

AJ5

AJ6

AC4

AE4

AD5

AB2

AD3

AB3

H15

H16

E24

H29

G23

L5

P6

M5

L4

M4

R4

T5

U6

T4

U5

U4

V5

V4

W5

N4

P5

K4

J5

M6

K6

J6

R6

W6

Y6

Y4

D2

C2

D4

H4

G8

B2

C1

E4

P3

C3

E3

G7

U2

U3

F3

G3

G4

H5

J16

J17

H1

H2

B3

F5

A3

XU1A

XU1A

H_A3

H_A4

H_A5

H_A6

H_A7

H_A8

H_A9

H_A10

H_A11

H_A12

H_A13

H_A14

H_A15

H_A16

RSVD_0

RSVD_1

REQ_0

REQ_1

REQ_2

REQ_3

REQ_4

H_ADSTB_0

H_A17

H_A18

H_A19

H_A20

H_A21

H_A22

H_A23

H_A24

H_A25

H_A26

H_A27

H_A28

H_A29

H_A30

H_A31

H_A32

H_A33

H_A34

H_A35

RSVD_2

RSVD_3

H_ADSTB_1

ADS#

BNR#

HIT#

FC35

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

FC36

DEFER#

FC37

FC29

FC30

BR0#

BPMb#3

BPMb#2

TESTHI10

FC31

FC32

FC33

FC34

GTLREF0

GTLREF1

FC10

FC15

RESET#

RS0#

RS1#

RS2#

I

I

H_DSTBP0

H_DSTBN0

H_DINV0

H_DSTBP1

H_DSTBN1

H_DINV1

H_DSTBP2

H_DSTBN2

H_DINV2

H_DSTBP3

H_DSTBN3

H_DINV3

LGA775_ C_ELCritical

LGA775_ C_ELCritical

H_D0

H_D1

H_D2

H_D3

H_D4

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

H_D32

H_D33

H_D34

H_D35

H_D36

H_D37

H_D38

H_D39

H_D40

H_D41

H_D42

H_D43

H_D44

H_D45

H_D46

H_D47

H_D48

H_D49

H_D50

H_D51

H_D52

H_D53

H_D54

H_D55

H_D56

H_D57

H_D58

H_D59

H_D60

H_D61

H_D62

H_D63

IC design

XDP

XDP_TDO

R388 62 0402I 5%R388 62 0402I 5%

XDP_TDI

R384 62 0402I 5%R384 62 0402I 5%

XDP_TMS

R383 62 0402I 5%R383 62 0402I 5%

XDP_TCK

R386 62 0402I 5%R386 62 0402I 5%

XDP_TRST#

R390 62 0402I 5%R390 62 0402I 5%

A A

VTT_OUT_RIGHT

4

H_D#0

B4

H_D#1

C5

H_D#2

A4

H_D#3

C6

H_D#4

A5

H_D#5

B6

H_D#6

B7

H_D#7

A7

H_D#8

A10

H_D#9

A11

H_D#10

B10

H_D#11

C11

H_D#12

D8

H_D#13

B12

H_D#14

C12

H_D#15

D11

H_DSTBP0

B9

H_DSTBN0

C8

H_DINV#0

A8

H_D#16

G9

H_D#17

F8

H_D#18

F9

H_D#19

E9

H_D#20

D7

H_D#21

E10

H_D#22

D10

H_D#23

F11

H_D#24

F12

H_D#25

D13

H_D#26

E13

H_D#27

G13

H_D#28

F14

H_D#29

G14

H_D#30

F15

H_D#31

G15

H_DSTBP1

E12

H_DSTBN1

G12

H_DINV#1

G11

H_D#32

G16

H_D#33

E15

H_D#34

E16

H_D#35

G18

H_D#36

G17

H_D#37

F17

H_D#38

F18

H_D#39

E18

H_D#40

E19

H_D#41

F20

H_D#42

E21

H_D#43

F21

H_D#44

G21

H_D#45

E22

H_D#46

D22

H_D#47

G22

H_DSTBP2

G19

H_DSTBN2

G20

H_DINV#2

D19

H_D#48

D20

H_D#49

D17

H_D#50

A14

H_D#51

C15

H_D#52

C14

H_D#53

B15

H_D#54

C18

H_D#55

B16

H_D#56

A17

H_D#57

B18

H_D#58

C21

H_D#59

B21

H_D#60

B19

H_D#61

A19

H_D#62

A22

H_D#63

B22

H_DSTBP3

C17

H_DSTBN3

A16

H_DINV#3

C20

R379

R379

57.6

57.6

0402

0402

1%

1%

I

I

V_FSB_VTT

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

0.635*VCC1.2 +/-2%

R379_1 CPU_GTLREF1R362_1

R380 10 0402

R380 10 0402

I 5%

I 5%

C329

C329

R367

R367

1U

1U

100

100

0603

0603

0402

0402

10V

10V

I

I

X

X

7R

7R

1%

1%

I

I

H_D#[0..15] 6

H_FERR#

H_DSTBP0 6

H_DSTBN0 6

H_DINV#0 6

H_D#[16..31] 6

VCC_VRM_S ENSE32

VSS_VRM_ SENSE32

H_DSTBP1 6

H_DSTBN1 6

H_DINV#1 6

H_D#[32..47] 6

H_DSTBP2 6

H_DSTBN2 6

H_DINV#2 6

H_D#[48..63] 6

Connected with VR's PSI#

H_DSTBP3 6

H_DSTBN3 6

H_DINV#3 6

XDP_BPM# 3_R29

XDP_BPM# 2_R29

XDP_BPM# 1_R29

XDP_BPM# 0_R29

0402I 5%

0402I 5%

XDP_BPM# 3_R

XDP_BPM# 1_R

XDP_BPM# 0_R

Stuff them for Kentsfield support

CPU_GTLREF0

C334

C334

220P

220P

0402

0402

50V

50V

X7R

X7R

I

I

CPU_GTLREF3CPU_GTLREF0 CPU_GTLREF1 CPU_GTLREF2

R4040

R4040

R560 62

R560 62

V_1P5_I CH

V_FSB_VTT

R554

R554

51

51

0402

0402

NI

NI

5%

5%

R370 0 0402NI 5%R370 0 0402NI 5%

R385 0 0402NI 5%R385 0 0402NI 5%

R403 0 0402NI 5%R403 0 0402NI 5%

R394 0 0402NI 5%R394 0 0402NI 5%

0402I

0402I

5%

5%

as design guide page 113

R450 0 0402

5%R450 0 0402

5%

I

I

R362

R362

57.6

57.6

0402

0402

NI

NI

1%

1%

R366

R366

100

100

0402

0402

NI

NI

1%

1%

H_VID_SEL32

VTT_OUT_LEFT

R371

R371

51

51

0402

0402

1%

1%

I

I

BPMb#3

BPMb#2XDP_BPM# 2_R

BPMb#1

BPMb#0

R35 680 0402

I

I

VCC_VRM_S ENSE

VSS_VRM_ SENSE

VCCP

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

0.635*VCC1.2 +/-2%

R365 0

R365 0

R378 10

R378 10

R381 0

R381 0

V_FSB_VTT

ICH_DPRSTP#

V_FSB_VTT

VTT_OUT_RIGHT

C407

C407

10U

10U

0805

0805

I

I

X

X

5R

5R

6.3V

6.3V

5%R35 680 0402

5%

H_PECI26

V_FSB_VTT

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_LEFT

VTT_OUT_LEFT

H_DPSLP#11

H_CPUSLP#7,26

VTT_OUT_LEFT

ICH_DPRSTP#7,11

CPU_PSI5 ,32

VTT_OUT_RIGHT

12

12

R374

R374

R411

R411

51

51

51

51

0402

0402

0402

0402

1%

1%

1%

1%

I

I

I

I

0402I 5%

0402I 5%

0402I 5%

0402I 5%

C327

C327

1U

1U

0603

0603

I

I

X7R

X7R

10V

10V

3

C418

C418

0.01U

0.01U

0402

0402

I

I

X

X

7R

7R

25V

25V

R419 0 0402NI 5%R419 0 0 402NI 5 %

R421 0 0402NI 5%R421 0 0402NI 5 %

R418 0 0402I 5%R418 0 0402I 5%

R423 0 0402I 5%R423 0 0402I 5%

R425 0 0402NI 5%R425 0 0 402NI 5 %

R34 0 0402NI 5%R34 0 0402NI 5%

CPU_THERMTRIP# _ICH13,26

12

R412

R412

51

51

0402

0402

1%

1%

I

I

R405 0 0402

R405 0 0402

NI 5%

NI 5%

0402I 5%

0402I 5%

H_SMI#13

H_A20M#13

H_FERR#13

H_INTR13

H_NMI13

H_IGNNE#13

H_STPCLK#13

T17T17

T128T128

T120T120

CLK_CPU_BCLK3

CLK_CPU_BCLK#3

H_SKTOCC#11,26,27

T134T134

R422 51 0402

I

I

R449 51 0402I 5%R449 51 0402I 5%

R402 51 0402I 5%R402 51 0402I 5%

R447 51 0402I 5%R447 51 0402I 5%

R369 51 0402NI 5%R369 51 040 2NI 5%

R398 51 0402NI 5%R398 51 040 2NI 5%

H_PWRGD11,2 9

H_PROCHOT#31

12

GTLR1

C335

C335

220P

220P

0402

0402

I

I

X

X

7R

7R

50V

50V

XU1B

XU1_M3

PSI#

XU1_A24

XU1B

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

C23

VCCIOPLL

D23

VCC_PLL

AM2

VID_0

AL5

VID_1

AM3

VID_2

AL6

VID_3

AK4

VID_4

AL4

VID_5

AM5

VID_6

AM7

VID_7

AN7

VID_SELECT

F28

BCLK_0

G28

BCLK_1

AE8

SKTOCC#

AL1

FC25

AK1

FC24

AJ7

VSS_1

AH7

VSS_2

AN3

VCC_SENSE

AN4

VSS_SENSE

AN5

VCC_MB_REGULATION

AN6

VSS_MB_REGULATION

AL8

VCC_1

AL7

VSS_3

F29

RSVD_4

F6

FC21

G6

RSVD_5

G5

PECI

AL3

VRDSEL

F26

TESTHI_0

W3

TESTHI_1

F25

TESTHI_2

G25

TESTHI_3

G27

TESTHI_4

G26

TESTHI_5

G24

TESTHI_6

F24

TESTHI_7

P1

DPSLP#

W2

TDI_M

L2

SLP#

AK6

FC8

N1

PWRGOOD

AL2

PROCHOT#

M2

THERMTRIP#

A13

COMP_0

T1

COMP_1

G2

COMP_2

R1

COMP_3

J2

FC3

T2

DPRSTP#

Y3

PSI#

AE3

FC18

B13

COMP_8

G1

BPMb#0

U1

TDO_M

A24

FC23

E29

FC26

I

I

VTT_OUT_RIGHT

VTT_OUT_LEFT

FC0/BOOTSELECT

LGA775_ C_ELCritical

LGA775_ C_ELCritical

H_SMI#

H_A20M#

H_FERR#

H_INTR

H_NMI

H_IGNNE#

R399 0

R399 0

0402I 5%

0402I 5%

XU1_A23

XU1_B23

XU1_C23

H_VCCPLL

H_VID032

H_VID132

H_VID232

H_VID332

H_VID432

H_VID532

H_VID632

H_VID732

5%R422 51 0402

5%

T97T97

T84T84

T94T94

R444 1K 0 402

NI

NI

T138T138

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_VID7

H_VID_SEL

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_SKTOCC#

XU1_AL1

T2T2

XU1_AK1

T1T1

VCC_SENSE_R

VSS_SENSE_R

VCC_PKGS ENSE_R

VSS_PKG SENSE_R

TP_LGA775_AL8

TP_LGA775_AL7

TP_LGA775_F29

H_CPU_PD_ F6

TP_LGA775_G6

H_PECI

VRDSEL

CPU_TEST0

CPU_TEST1

XU1_F25

H_DPSLP#

H_TDI_TDO_M

H_CPUSLP#

H_FORCEPH#

H_PWRGD

H_PROCHOT#

CPU_THERMTRIP# _ICH

COMP0

R43049.9 0402 I1% R43049.9 0402 I1%

COMP1

R40149.9 0402 I1% R40149.9 0402 I1%

COMP2

R40649.9 0402 I1% R40649.9 0402 I1%

COMP3

R40049.9 0402 I1% R40049.9 0402 I1%

COMP4

R39549.9 0402 NI1% R39549.9 0402 NI1%

ICH_DPRSTP#

R3770 0402 NI5% R3770 0402 NI5%

COMP7

R38749.9 0402 I1% R38749.9 0402 I1%

COMP8

R42624.9 0402 I1% R42624.9 0402 I1%

BPMb#0

H_TDI_TDO_M

5%R444 1K 0 402

5%

TP_LGA775_G7 CPU_GTLREF2

Thermal Sensor

SBDATA16,26

SBCLK16,26

2

TRST#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

DBR#

ITPCLK_0

ITPCLK_1

BSEL_0

BSEL_1

BSEL_2

RSVD_8

BPMb#1

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

FC40

VTT_SEL

RSVD_14

RSVD_15

RSVD_16

RSVD_17

FC20

FC22

FC39

RSVD_7

MSID_0

MSID_1

RSVD_6

GTLREF3

GTLREF2

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

N5

C9

E7

AE6

D16

A20

E23

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

F23

D14

E6

D1

E5

J3

AA2

V2

Y1

W1

V1

AH2

G10

F2

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_BPM# 0

XDP_BPM# 1

XDP_BPM# 2

XDP_BPM# 3

XDP_BPM# 4

XDP_BPM# 5

XDP_DBRESET#

XDP_R_DCL KOUT_DP

XDP_R_DCL KOUT_DN

CPU_BSEL 0

CPU_BSEL 1

CPU_BSEL 2

TP_LGA775_N5

BPMb#1

TP_LGA775_E7

TP_LGA775_AE6

TP_LGA775_D16

TP_LGA775_A20

TP_LAG775_E23

V_FSB_VTT

C456

C456

1U

1U

0603

0603

I

I

7R

7R

X

X

10V

10V

VRMPWG_R

R33 0

R33 0

R413 51

R413 51

3VSB

R356 0

R356 0

U32

U32

7

THERM

SDAT

8

SCLK

1

VDD

5

GND

EMC1402-2 -ACZL-TR

EMC1402-2 -ACZL-TR

MSOP8

MSOP8

Critical

Critical

I

I

1 2

1 2

ALERT

DP

DN

VTT_OUT_RIGHT

VTT_OUT_LEFT

TP_VTT_SEL

TP_LAG775_F23

TP_LAG775_D14

TP_LAG775_E6

TP_LAG775_D1

H_DCLKPH

H_ACLKPH

TP_LAG775_AA2

TP_LAG775_V2

CPU_BOOT

as design guide page 113

TP_LGA775_AH2

CPU_GTLREF3

Address: 9AH

XDP_TCK 29

XDP_TDI 29

XDP_TDO 29

XDP_TMS 29

XDP_TRST# 29

XDP_BPM# 0 29

XDP_BPM# 1 29

XDP_BPM# 2 29

XDP_BPM# 3 29

XDP_BPM# 4 29

XDP_BPM# 5 29

XDP_DBRESET# 29

R416 PO@0 0402I 5%R416 PO@0 0402I 5%

R414 PO@0 0402I5%R414 PO@0 0402I

5%

T88T88

T96T96

T92T92

T105T105

T115T115

T129T129

C442

C442

10U

10U

0805

0805

I

I

5R

5R

X

X

6.3V

6.3V

T135T135

T121T121

T100T100

T95T95

T78T78

T90T90

T89T89

T86T86

T79T79

0402I 5%

0402I 5%

T85T85

CTRL_GTLREF211

CTRL_GTLREF112

0603I 5%

0603I 5%

4

6

2

3

CPU_BSEL 0 3

CPU_BSEL 1 3

CPU_BSEL 2 3

C424

C424

0.1U

0.1U

0402

0402

I

I

7R

7R

X

X

10V

10V

VRMPWG

0402I 5%

0402I 5%

C336

C336

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

LM86VCC

H_THERMDA

C321

C321

100P

100P

0603

0603

50V

50V

NPO

NPO

I

I

H_THERMDC

XDP_BPM# 0

XDP_BPM# 1

XDP_BPM# 2

XDP_BPM# 3

XDP_BPM# 4

XDP_BPM# 5

VTT_OUT_LEFT

C332

C332

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

0402 I

0402 I

0402 I5%

0402 I5%

C672 100P

0402I NPO

0402I NPO

C671 10U

0805I X5R

0805I X5R

C320 0.1U

0402I X7R

0402I X7R

1

R368 51 0402I 5%R368 51 0402I 5%

1 2

R393 51 0402I 5%R393 51 0402I 5%

1 2

R375 51 0402I 5%R375 51 0402I 5%

1 2

R391 51 0402I 5%R391 51 0402I 5%

1 2

R389 51 0402I 5%R389 51 0402I 5%

1 2

R392 51 0402I 5%R392 51 0402I 5%

1 2

XDP_DCLKOUT_DP 3,29

XDP_DCLKOUT_DN 3,29

Termination

VTT_OUT_LEFT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

VTT_OUT_LEFT

VRMPWG 11,32

C331

C331

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

S1 S0

000

111

V_FSB_VTT

GTLR1

U35_4

R3610

5% R3610

5%

U35_3

R3600

R3600

50VC672 100P

50V

6.3VC6 71 10U

6.3V

10VC320 0.1U

10V

2

C55

C55

100P

100P

0603

0603

NI

NI

NPO

NPO

50V

50V

Near SO-DIMMNear Thermal Sensor

01

6

5

4

Q12

Q12

MMBT3904-7-F

MMBT3904-7-F

1 3

100mA

100mA

SOT23-3

SOT23-3

I

I

50V

50V

VTT_OUT_RIGHT

H_TDI_TDO_M

Near CPU

5%

5%

5%

5%

C330

C330

0.1U

0.1U

0402

0402

10V

10V

X7R

X7R

I

I

RATIO SET

0.615xVTT

0.63xVTT

0.65xVTT

0.67xVTT

U35

U35

VTT

GTLR

S1

GTL3004

GTL3004

I

I

VTT_OUT_LEFT

R37262

R37262

0402I 5%

0402I 5%

R44062

R44062

0402I 5%

0402I 5%

R39662

R39662

0402I

0402I

R373680

R373680

0402I

0402I

R37651

R37651

0402I 5%

0402I 5%

1

VDD

2

GND

3

S0

04

R397

R397

51

51

0402

0402

1 2

I

I

5

5

%

%

H_BREQ#

H_CPURST#

H_IERR#

PSI#

CPU_TEST10

VTT_OUT_RIGHT

C341

C341

1U

1U

0603

0603

10V

10V

X7R

X7R

I

I

VCC3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CPU(1/2)- Host Bus

CPU(1/2)- Host Bus

CPU(1/2)- Host Bus

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

1

ZN5

ZN5

ZN5

X4

X4

4 40Friday, March 05, 2010

4 40Friday, March 05, 2010

4 40Friday, March 05, 2010

X4

Page 5

5

XU1D

XU1D

C10

VSS_4

D12

VSS_5

C24

VSS_6

K2

VSS_7

C22

VSS_8

AN1

VSS_9

B14

VSS_10

K7

VSS_11

AE16

VSS_12

B11

VSS_13

AL10

VSS_14

D D

C C

B B

A A

AK23

AL16

AL24

AK13

AL20

AK16

AK20

AM27

AL13

AL17

AK30

AL23

AE28

AE29

AE30

AN20

AF10

AE24

AM24

AN23

AM16

AE25

AE27

AJ28

AH13

AH16

AK17

AH17

AH20

AH23

AM13

AH24

AJ30

AJ10

AJ16

AK29

AJ17

AK10

AM10

AJ23

AM23

AH10

AJ29

AK27

AK28

AM20

AJ24

AM17

VSS_15

H12

VSS_16

AF7

VSS_17

AK7

VSS_18

H7

VSS_19

E14

VSS_20

L28

VSS_21

Y5

VSS_22

E11

VSS_23

VSS_24

VSS_25

VSS_26

D21

VSS_27

VSS_28

D18

VSS_29

AN2

VSS_30

VSS_31

VSS_32

VSS_33

AM1

VSS_34

VSS_35

VSS_36

C19

VSS_37

E28

VSS_38

VSS_39

D24

VSS_40

VSS_41

A12

VSS_42

L25

VSS_43

J7

VSS_44

VSS_45

VSS_46

K5

VSS_47

J4

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

H9

VSS_55

H8

VSS_56

H13

VSS_57

AC6

VSS_58

AC7

VSS_59

AH6

VSS_60

C16

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

F19

VSS_66

VSS_67

AD7

VSS_68

VSS_69

VSS_70

E17

VSS_71

VSS_72

VSS_73

AE5

VSS_74

VSS_75

AE7

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

AF3

VSS_81

AK5

VSS_82

VSS_83

AF6

VSS_84

VSS_85

VSS_86

F22

VSS_87

AH3

VSS_88

VSS_89

VSS_90

F16

VSS_91

VSS_92

F13

VSS_93

AG7

VSS_94

F10

VSS_95

L26

VSS_96

AD4

VSS_97

H11

VSS_98

L24

VSS_99

L23

VSS_100

VSS_101

A15

VSS_102

VSS_103

B24

VSS_104

L3

VSS_105

H27

VSS_106

A21

VSS_107

AE2

VSS_108

VSS_109

VSS_110

VSS_111

B20

VSS_112

VSS_113

H26

VSS_114

B17

VSS_115

H25

VSS_116

H24

VSS_117

AA3

VSS_118

AA7

VSS_119

H23

VSS_120

AA6

VSS_121

H10

VSS_122

H22

VSS_123

H21

VSS_124

H20

VSS_125

H19

VSS_126

H18

VSS_127

AB7

VSS_128

H17

VSS_129

VSS_130

VSS_131

AC3

VSS_132

H14

VSS_133

P28

VSS_134

V6

VSS_135

AK2

VSS_136

P27

VSS_137

Critical

Critical

I

I

5

VSS_268

VSS_267

VSS_266

VSS_265

VSS_264

VSS_263

VSS_262

VSS_261

VSS_260

VSS_259

VSS_258

VSS_257

VSS_256

VSS_255

VSS_254

VSS_253

VSS_252

VSS_251

VSS_250

VSS_249

VSS_248

VSS_247

VSS_246

VSS_245

VSS_244

VSS_243

VSS_242

VSS_241

VSS_240

VSS_239

VSS_238

VSS_237

VSS_236

VSS_235

VSS_234

VSS_233

VSS_232

VSS_231

VSS_230

VSS_229

VSS_228

VSS_227

VSS_226

VSS_225

VSS_224

VSS_223

VSS_222

VSS_221

VSS_220

VSS_219

VSS_218

VSS_217

VSS_216

VSS_215

VSS_214

VSS_213

VSS_212

VSS_211

VSS_210

VSS_209

VSS_208

VSS_207

VSS_206

VSS_205

VSS_204

VSS_203

VSS_202

VSS_201

VSS_200

VSS_199

VSS_198

VSS_197

VSS_196

VSS_195

VSS_194

VSS_193

VSS_192

VSS_191

VSS_190

VSS_189

VSS_188

VSS_187

VSS_186

VSS_185

VSS_184

VSS_183

VSS_182

VSS_181

VSS_180

VSS_179

VSS_178

VSS_177

VSS_176

VSS_175

VSS_174

VSS_173

VSS_172

VSS_171

VSS_170

VSS_169

VSS_168

VSS_167

VSS_166

VSS_165

VSS_164

VSS_163

VSS_162

VSS_161

VSS_160

VSS_159

VSS_158

VSS_157

VSS_156

VSS_155

VSS_154

VSS_153

VSS_152

VSS_151

VSS_150

VSS_149

VSS_148

VSS_147

VSS_146

VSS_145

VSS_144

VSS_143

VSS_142

VSS_141

VSS_140

VSS_139

VSS_138

LGA775_C_EL

LGA775_C_EL

AG13

AG16

AG17

E8

AG20

AG23

AF20

AL28

AA23

V26

AM4

AB1

AJ27

R30

T7

E27

AE17

AE20

P24

Y2

H3

AN24

AF17

AG24

AF23

AF24

AN27

AN28

AF25

AF26

AF27

AF28

AF29

F7

H28

AF30

AE13

AG10

F4

AA30

N3

AB23

AB24

AB25

M7

AN16

AB26

AB27

AN17

AB28

M1

AB29

L7

L6

AB30

AK24

C13

V7

AH1

AE26

AJ4

B8

B5

B1

D3

A9

D5

D6

A6

C4

D9

E2

A2

A18

H6

AF13

AE10

AF16

P29

V3

P30

R23

R24

U7

R25

R26

R27

R28

R29

E25

T6

V23

V24

T3

V25

AN10

E20

R7

V27

R5

V28

V29

R2

V30

E26

P7

AA24

AA25

P4

AA26

AA27

AN13

AA28

N7

N6

AA29

L27

Y7

AL27

RC delay to turn the switch

D15

L29

on only after 50 msec after

L30

RESER# is high

C7

P23

W7

AJ20

P25

W4

AJ13

AM28

P26

H_CPURST#4,6,29

For fast switch off of the IC if RESET# is asserted

( needed because BIOS uses processor only resets

that will restart the invaild PSI assertion.

4

In CPU socket

C30

C38

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

C27

C27

C40

C40

C38

C30

C23

C23

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

ON CPU socket bottom side.

C371

C371

C363

C360

C353

C353

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

C360

C352

C352

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

Voltage translation

required for the swith IC

4

C363

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

Yorkfield/Wolfdale CPU Power Status and max current table

POWER PLANE

VCC_CORE

VCC_CORE

VTT

VTT

VCC_PLL

R27 5.11K

R27 5.11K

04021

04021

%I

%I

R32 1K

R32 1K

04025%I

04025%I

Place these parts reference

to Intel demo board.

C31

C31

C36

C36

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

C369

C369

C372

C372

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

S0

O

O

O

O

O

Q4_B

2

C19

C19

10U

10U

0603

0603

5R

5R

X

X

6.3V

6.3V

I

I

Q7_B

2

C29

C29

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

C361

C361

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

VCC

1 3

VCC

1 3

C32

C32

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

C370

C370

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

S3

X

X

X

X

X

R29

R29

1K

1K

0402

0402

%

%

5

5

I

I

Q4_C

Q4

Q4

MMBT3904-7-F

MMBT3904-7-F

200mA

200mA

SOT23-3

SOT23-3

40V

40V

I

I

R30

R30

1K

1K

0402

0402

5%

5%

I

I

Q7

Q7

MMBT3904-7-F

MMBT3904-7-F

200mA

200mA

SOT23-3

SOT23-3

40V

40V

I

I

3

C28

C28

C33

C374

C374

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

1 3

Voltage

C24

C24

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

VID

VID

VCC1.2

VCC1.2

VCC1.5

Q3_C

Q3

Q3

MMBT3904-7-F

MMBT3904-7-F

200mA

200mA

SOT23-3

SOT23-3

40V

40V

I

I

C33

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

C350

C350

C351

C351

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

I(max)

100A

75A

4.6A

4.5A

260mA

VCC VCC

R28

R28

1K

1K

0402

0402

5%

5%

I

I

Q6

Q6

2

MMBT3904-7-F

MMBT3904-7-F

1 3

200mA

200mA

S

S

OT23-3

OT23-3

40V

40V

I

I

C354

C354

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

S4/S5

Q7_C

C25

C25

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

X

X

X

X

X

2

C-step Erratum for PSI

3

C39

C39

C37

C37

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

C358

C358

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

Note

Yorkfield@65W

Wolfdale

After VCC stable

Before VCC stable

C20

C20

0.1U

0.1U

0402

0402

X7R

X7R

10V

10V

I

I

5

4

Q5

Q5

ME2N7002E

ME2N7002E

S

S

OT23-3

OT23-3

3

60V

60V

250mA

250mA

I

I

2

1

VCCP

C26

C26

C35

C362

C362

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

VCC

C

74V1G66CTR

74V1G66CTR

I

I

Q5_G

C35

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

C34

C34

10U

10U

10U

10U

X5R

X5R

X5R

X5R

25V

25V

25V

25V

1206

1206

1206

1206

I

I

I

I

VCCP

C373

C373

C359

C359

C349

C349

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

Switch for PSI# connection between

processor and VR.This type of switch

neded as we can not tolerate a delay to

be placed on PSI# assertions.

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

U56

U56

1

IO

2

OI

3

GND

R31 100

R31 100

%I

%I

10U

10U

X5R

X5R

25V

25V

1206

1206

I

I

R19 0

R19 0

04025

04025

04025%NI

04025%NI

AUTO_PSI_DISABLE 11,32

VRM_PSI 32

CPU_PSI 4,32

VCCP

2

1

05

XU1C

XU1C

AG22

VCC_CORE_1

K29

VCC_CORE_2

AM26

VCC_CORE_3

AE12

VCC_CORE_4

AE11

VCC_CORE_5

W23

VCC_CORE_6

W24

VCC_CORE_7

W25

VCC_CORE_8

T25

VCC_CORE_9

Y28

VCC_CORE_10

AL18

VCC_CORE_11

AC25

VCC_CORE_12

W30

VCC_CORE_13

Y30

VCC_CORE_14

AN14

VCC_CORE_15

AD28

VCC_CORE_16

Y26

VCC_CORE_17

AC29

VCC_CORE_18

M29

VCC_CORE_19

U24

VCC_CORE_20

J23

VCC_CORE_21

AC27

VCC_CORE_22

AM18

VCC_CORE_23

AM19

VCC_CORE_24

AB8

VCC_CORE_25

AC26

VCC_CORE_26

J8

VCC_CORE_27

J28

VCC_CORE_28

T30

VCC_CORE_29

AM9

VCC_CORE_30

AF15

VCC_CORE_31

AC8

VCC_CORE_32

AE14

VCC_CORE_33

N23

VCC_CORE_34

W29

VCC_CORE_35

U29

VCC_CORE_36

AC24

VCC_CORE_37

AC23

VCC_CORE_38

Y23

VCC_CORE_39

AN26

VCC_CORE_40

AN25

VCC_CORE_41

AN18

VCC_CORE_42

AN11

VCC_CORE_43

Y27

VCC_CORE_44

Y25

VCC_CORE_45

U27

VCC_CORE_46

AD24

VCC_CORE_47

AE23

VCC_CORE_48

AE22

VCC_CORE_49

AN19

VCC_CORE_50

V8

VCC_CORE_51

K8

VCC_CORE_52

AE21

VCC_CORE_53

AM30

VCC_CORE_54

AE19

VCC_CORE_55

AC30

VCC_CORE_56

AE15

VCC_CORE_57

M30

VCC_CORE_58

K27

VCC_CORE_59

M24

VCC_CORE_60

AN21

VCC_CORE_61

T8

VCC_CORE_62

AC28

VCC_CORE_63

N25

VCC_CORE_64

AE18

VCC_CORE_65

W26

VCC_CORE_66

AD25

VCC_CORE_67

M8

VCC_CORE_68

N30

VCC_CORE_69

AD26

VCC_CORE_70

AJ26

VCC_CORE_71

AM29

VCC_CORE_72

M25

VCC_CORE_73

M26

VCC_CORE_74

L8

VCC_CORE_75

U25

VCC_CORE_76

Y8

VCC_CORE_77

AJ12

VCC_CORE_78

AD27

VCC_CORE_79

U23

VCC_CORE_80

M23

VCC_CORE_81

AG29

VCC_CORE_82

N27

VCC_CORE_83

AM22

VCC_CORE_84

U28

VCC_CORE_85

K28

VCC_CORE_86

U8

VCC_CORE_87

AK18

VCC_CORE_88

AD8

VCC_CORE_89

K24

VCC_CORE_90

AH28

VCC_CORE_91

AH21

VCC_CORE_92

AK12

VCC_CORE_93

AH22

VCC_CORE_94

T29

VCC_CORE_95

AM14

VCC_CORE_96

AM25

VCC_CORE_97

AE9

VCC_CORE_98

Y29

VCC_CORE_99

AK25

VCC_CORE_100

AK19

VCC_CORE_101

AG15

VCC_CORE_102

J22

VCC_CORE_103

T24

VCC_CORE_104

AG21

VCC_CORE_105

AM21

VCC_CORE_106

J25

VCC_CORE_107

U30

VCC_CORE_108

AL21

VCC_CORE_109

AG25

VCC_CORE_110

AJ18

VCC_CORE_111

J19

VCC_CORE_112

AH30

VCC_CORE_113

Critical

Critical

I

I

2

VCC_CORE_225

VCC_CORE_224

VCC_CORE_223

VCC_CORE_222

VCC_CORE_221

VCC_CORE_220

VCC_CORE_219

VCC_CORE_218

VCC_CORE_217

VCC_CORE_216

VCC_CORE_215

VCC_CORE_214

VCC_CORE_213

VCC_CORE_212

VCC_CORE_211

VCC_CORE_210

VCC_CORE_209

VCC_CORE_208

VCC_CORE_207

VCC_CORE_206

VCC_CORE_205

VCC_CORE_204

VCC_CORE_203

VCC_CORE_202

VCC_CORE_201

VCC_CORE_200

VCC_CORE_199

VCC_CORE_198

VCC_CORE_197

VCC_CORE_196

VCC_CORE_195

VCC_CORE_194

VCC_CORE_193

VCC_CORE_192

VCC_CORE_191

VCC_CORE_190

VCC_CORE_189

VCC_CORE_188

VCC_CORE_187

VCC_CORE_186

VCC_CORE_185

VCC_CORE_184

VCC_CORE_183

VCC_CORE_182

VCC_CORE_181

VCC_CORE_180

VCC_CORE_179

VCC_CORE_178

VCC_CORE_177

VCC_CORE_176

VCC_CORE_175

VCC_CORE_174

VCC_CORE_173

VCC_CORE_172

VCC_CORE_171

VCC_CORE_170

VCC_CORE_169

VCC_CORE_168

VCC_CORE_167

VCC_CORE_166

VCC_CORE_165

VCC_CORE_164

VCC_CORE_163

VCC_CORE_162

VCC_CORE_161

VCC_CORE_160

VCC_CORE_159

VCC_CORE_158

VCC_CORE_157

VCC_CORE_156

VCC_CORE_155

VCC_CORE_154

VCC_CORE_153

VCC_CORE_152

VCC_CORE_151

VCC_CORE_150

VCC_CORE_149

VCC_CORE_148

VCC_CORE_147

VCC_CORE_146

VCC_CORE_145

VCC_CORE_144

VCC_CORE_143

VCC_CORE_142

VCC_CORE_141

VCC_CORE_140

VCC_CORE_139

VCC_CORE_138

VCC_CORE_137

VCC_CORE_136

VCC_CORE_135

VCC_CORE_134

VCC_CORE_133

VCC_CORE_132

VCC_CORE_131

VCC_CORE_130

VCC_CORE_129

VCC_CORE_128

VCC_CORE_127

VCC_CORE_126

VCC_CORE_125

VCC_CORE_124

VCC_CORE_123

VCC_CORE_122

VCC_CORE_121

VCC_CORE_120

VCC_CORE_119

VCC_CORE_118

VCC_CORE_117

VCC_CORE_116

VCC_CORE_115

VCC_CORE_114

LGA775_C_EL

LGA775_C_EL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCCP

AK9

M28

AF12

N8

AF19

K26

J14

AN22

N24

AH8

W8

AD29

AL29

AG8

AA8

AG18

J30

AF14

M27

J9

AK14

Y24

AF21

AD30

AL9

AG19

J27

J12

W28

T28

J13

J24

AM12

AL26

AG28

AH27

AH29

AH19

AJ14

AH11

AF22

AF9

N26

AG9

AN12

AK8

T27

AJ19

U26

AJ8

AN15

AL22

AH12

N28

T26

AM8

AL19

K23

P8

K25

J11

J29

AH9

AJ25

AL30

N29

AG14

AK11

AJ9

AL12

AH25

AN30

AL14

K30

AJ11

AL11

AM11

AJ21

AG30

AK21

AF8

AM15

AD23

AF11

AK15

AG27

J21

J18

J26

AL15

AF18

AH15

AN9

AG26

AJ15

J10

AK26

AG11

AN29

AK22

R8

T23

AH14

AN8

AL25

W27

AH26

AH18

J20

AJ22

AG12

J15

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

CPU(2/2)- Power

CPU(2/2)- Power

CPU(2/2)- Power

ZN5

ZN5

ZN5

5 40Friday, March 05, 2010

5 40Friday, March 05, 2010

1

5 40Friday, March 05, 2010

X4

X4

X4

Page 6

5

V_FSB_VTT

R443

R443

301

301

0402

0402

%

%

1

1

I

D D

C C

B B

A A

I

R443_1

R442

R442

100

100

0402

0402

I

I

%

%

1

1

R448

R448

16.5

16.5

0402

0402

I

I

1

1

%

%

V_FSB_VTT

R455

R455

57.6

57.6

0402

0402

1%

1%

I

I

R452

R452

100

100

0402

0402

I

I

1%

1%

49.9/F as schematic checklist

R441 49.9

R441 49.9

0402I 1%

0402I 1%

C395

C395

0.1U

0.1U

0402

0402

I

I

X7R

X7R

10V

10V

H_RCOMP

49.9/F as schematic checklist

R451 49.9

R451 49.9

C431

C431

0.1U

0.1U

0402

0402

I

I

X7R

X7R

10V

10V

0402I 1%

0402I 1%

0.25*VCCP

W:10,S:10 , L<3"

BreakoutL<0.25"

H_SWING

W:10,S:7 , L<0.5"

BreakoutL<0.25"

0.365*VCCP

W:10,S:20 , L<1.5"

C430

C430

220P

220P

0402

0402

I

I

X7R

X7R

50V

50V

MCH_GTLREF0R455_1

4

H_A#[3..16]4

H_A#[17..35]4

H_REQ#[0..4]4

H_ADSTB#04

H_DSTBP[3..0]4

H_DSTBN[3..0]4

H_DINV#[3..0]4

H_RS#[2..0]4

H_DSTBP0

H_DSTBP1

H_DSTBP2

H_DSTBP3

H_DSTBN0

H_DSTBN1

H_DSTBN2

H_DSTBN3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_ADSTB#14

H_ADS#4

H_TRDY#4

H_DRDY#4

H_DEFER#4

H_HITM#4

H_HIT#4

H_LOCK#4

H_BREQ#4

H_BNR#4

H_BPRI#4

H_DBSY#4

H_CPURST#4,5,29

T133T133

3

U3A

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_DSTBP0

H_DSTBN0

H_DINV#0

H_DSTBP1

H_DSTBN1

H_DINV#1

H_DSTBP2

H_DSTBN2

H_DINV#2

H_DSTBP3

H_DSTBN3

H_DINV#3

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BREQ#

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

H_CPURST#

TP_MCH_N25

U3A

L36

FSB_AB_3

L37

FSB_AB_4

J38

FSB_AB_5

F40

FSB_AB_6

H39

FSB_AB_7

L38

FSB_AB_8

L43

FSB_AB_9

N39

FSB_AB_10

N35

FSB_AB_11

N37

FSB_AB_12

J41

FSB_AB_13

N40

FSB_AB_14

M45

FSB_AB_15

R35

FSB_AB_16

T36

FSB_AB_17

R36

FSB_AB_18

R34

FSB_AB_19

R37

FSB_AB_20

R39

FSB_AB_21

U38

FSB_AB_22

T37

FSB_AB_23

U34

FSB_AB_24

U40

FSB_AB_25

T34

FSB_AB_26

Y36

FSB_AB_27

U35

FSB_AB_28

AA35

FSB_AB_29

U37

FSB_AB_30

Y37

FSB_AB_31

Y34

FSB_AB_32

Y38

FSB_AB_33

AA37

FSB_AB_34

AA36

FSB_AB_35

G38

FSB_REQB_0

K35

FSB_REQB_1

J39

FSB_REQB_2

C43

FSB_REQB_3

G39

FSB_REQB_4

J40

FSB_ADSTBB_0

T39

FSB_ADSTBB_1

C39

FSB_DSTBPB_0

B39

FSB_DSTBNB_0

B40

FSB_DINVB_0

K31

FSB_DSTBPB_1

J31

FSB_DSTBNB_1

F33

FSB_DINVB_1

J25

FSB_DSTBPB_2

K25

FSB_DSTBNB_2

F26

FSB_DINVB_2

C32

FSB_DSTBPB_3

D32

FSB_DSTBNB_3

D30

FSB_DINVB_3

J42

FSB_ADSB

L40

FSB_TRDYB

J43

FSB_DRDYB

G44

FSB_DEFERB

K44

FSB_HITMB

H45

FSB_HITB

H40

FSB_LOCKB

L42

FSB_BREQ0B

J44

FSB_BNRB

H37

FSB_BPRIB

H42

FSB_DBSYB

G43

FSB_RSB_0

L44

FSB_RSB_1

G42

FSB_RSB_2

D27

FSB_CPURSTB

N25

RSVD_05

EAGLELAKE_FCBGA1254

EAGLELAKE_FCBGA1254

Critical

Critical

I

I

EAGLELAKE_DDR3

EAGLELAKE_DDR3

SYM_REV = 1.5GC

SYM_REV = 1.5GC

1 OF 9

1 OF 9

FSB

FSB

2

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_DVREF

FSB_ACCVREF

HPL_CLKINP

HPL_CLKINN

F44

C44

D44

C41

E43

B43

D40

B42

B38

F38

A38

B37

D38

C37

D37

B36

E37

J35

H35

F37

G37

J33

L33

G33

L31

M31

M30

J30

G31

K30

M29

G30

J29

F29

H29

L25

K26

L29

J26

M26

H26

F25

F24

G25

H24

L24

J24

N24

C28

B31

F35

C35

B35

D35

D31

A34

B32

F31

D28

A29

C30

B30

E27

B28

B24

A23

C22

B23

P29

P30

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

MCH_GTLREF0

CLK_MCH_BCLK

CLK_MCH_BCLK#

1

H_D#[0..15] 4

H_D#[16..31] 4

H_D#[32..47] 4

H_D#[48..63] 4

CLK_MCH_BCLK 3

CLK_MCH_BCLK# 3

06

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

NB (1/5) HOST

NB (1/5) HOST

NB (1/5) HOST

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZN5

ZN5

ZN5

X4

X4

X4

6 40Friday, March 05, 2010

6 40Friday, March 05, 2010

6 40Friday, March 05, 2010

1

Page 7

5

MCH_BSEL0

MCH_BSEL03

MCH_BSEL13

MCH_BSEL23

R457 1K 0402NI 5%R 457 1K 0402NI 5%

R467 1K 0402NI 5%R 467 1K 0402NI 5%

R454 0 0402I 5%R454 0 0402I 5%

R461 1K 0402NI 5%R 461 1K 0402NI 5%

55

50

34

27

22

17

6

19

18

43

42

41

40

54

53

52

51

39

38

37

36

47

46

45

44

26

25

24

23

33

32

31

30

CL_DATA013

CL_CLK013

CL_RST#13

CL_PWROK 13

U38_19

C_EXT_DPTX0P

C_EXT_DPTX0N

C_EXT_DPTX1P

C_EXT_DPTX1N

C_PEG_TXP4_R

C_PEG_TXN4_R

C_PEG_TXP5_R

C_PEG_TXN5_R

C_EXT_DPTX2P

C_EXT_DPTX2N

C_EXT_DPTX3P

C_EXT_DPTX3N

C_PEG_TXP6_R

C_PEG_TXN6_R

C_PEG_TXP7_R

UMADP_AUXDP

UMADP_AUXDN

UMA_HPD

U38_23

PEG_RXP6_R

PEG_RXN6_R

PEG_RXP7_R

PEG_RXN7_R

R453 1K 0402NI 5%R 453 1K 0402NI 5%

R456 1K

R456 1K

VCC3

C511

C511

2.2U

2.2U

0603

0603

I

I

X5R

X5R

6.3V

6.3V

0402 I5%

0402 I5%

0402I 5%

0402I 5%

T147T147

T145T145

T143T143

T146T146

T99T99

T22T22

T11T11

T20T20

T13T13

T9T9

T148T148

T21T21

T12T12

R5090

R5090

C683 0.1U 0402I X7R 10VC683 0.1U 0402I X7R 10V

C684 0.1U 0402I X7R 10VC684 0.1U 0402I X7R 10V

C685 0.1U 0402I X7R 10VC685 0.1U 0402I X7R 10V

C686 0.1U 0402I X7R 10VC686 0.1U 0402I X7R 10V

C56 0.1U 0402I X7 R 10VC56 0.1U 0402I X7R 10V

C57 0.1U 0402I X7 R 10VC57 0.1U 0402I X7R 10V

C73 0.1U 0402I X7 R 10VC73 0.1U 0402I X7R 10V

C72 0.1U 0402I X7 R 10VC72 0.1U 0402I X7R 10V

C687 0.1U 0402I X7R 10VC687 0.1U 0402I X7R 10V

C688 0.1U 0402I X7R 10VC688 0.1U 0402I X7R 10V

C689 0.1U 0402I X7R 10VC689 0.1U 0402I X7R 10V

C690 0.1U 0402I X7R 10VC690 0.1U 0402I X7R 10V

C59 0.1U 0402I X7 R 10VC59 0.1U 0402I X7R 10V

C58 0.1U 0402I X7 R 10VC58 0.1U 0402I X7R 10V

C75 0.1U 0402I X7 R 10VC75 0.1U 0402I X7R 10V

C74 0.1U 0402I X7 R 10VC74 0.1U 0402I X7R 10V

D D

V_FSB_VTT

CLPWROK sequence request

1. asserted after VCC_CL ramp to 1.0V

2. asserted before PWROK

V_1P1_CL_MCH

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

R462

R462

0.316*VCC_CL+-2%

1K

1K

0402

0402

1%

1%

I

I

CL_VREF

C461

C461

R465

R465

0.1U

0.1U

464

464

0402

0402

0402

0402

I

I

I

I

X7R

X7R

1%

1%

10V

10V

C C

R474 0

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_RXP6

PEG_RXN6

PEG_RXP7

PEG_RXN7

R474 0

R473 0

R473 0

U38

U38

1

11

16

20

21

28

29

35

48

49

56

2

3

4

5

7

8

9

10

12

13

14

15

PWRGD_140MS1 1,26,29

MCH_CLPWROK35

B B

57

A A

T

T

Critical

Critical

I

I

QFN56

QFN56

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

IN_0+

IN_0IN_1+

IN_1-

IN_2+

IN_2IN_3+

IN_3-

OUT+

OUTX+

X-

GND

CL_PWROK

0402NI 5%

0402NI 5%

0402I 5%

0402I 5%

PI3PCIE2612-AZFE

PI3PCIE2612-AZFE

SEL: (H,L)=(Dx,Tx)

SEL: (H,L)=(Dx,Tx)

VDD

VDD

VDD

VDD

VDD

VDD

VDD

LE#

SEL

D0+

D0-

D1+

D1-

TX0+

TX0-

TX1+

TX1-

D2+

D2-

D3+

D3-

TX2+

TX2-

TX3+

TX3-

AUX+

AUX-

HPD

NC

RX0+

RX0-

RX1+

RX1-

MCH_BSEL1

MCH_BSEL2

TP_MCH_K16

EXP_SLR

EXP_SM

U3_L17

TCEN

DUALX8_ENABLE

CL_DATA0

CL_CLK0

CL_VREF

CL_RST#

CL_PWROK

JTAG_TDI

JTAG_TDO

JTAG_TCK

JTAG_TMS

TP_MCH_A44

TP_MCH_BD1

TP_MCH_BD45

TP_MCH_BE2

TP_MCH_BE44

TP_MCH_A45

TP_MCH_B2