Page 1

8

7

6

5

4

3

2

1

1

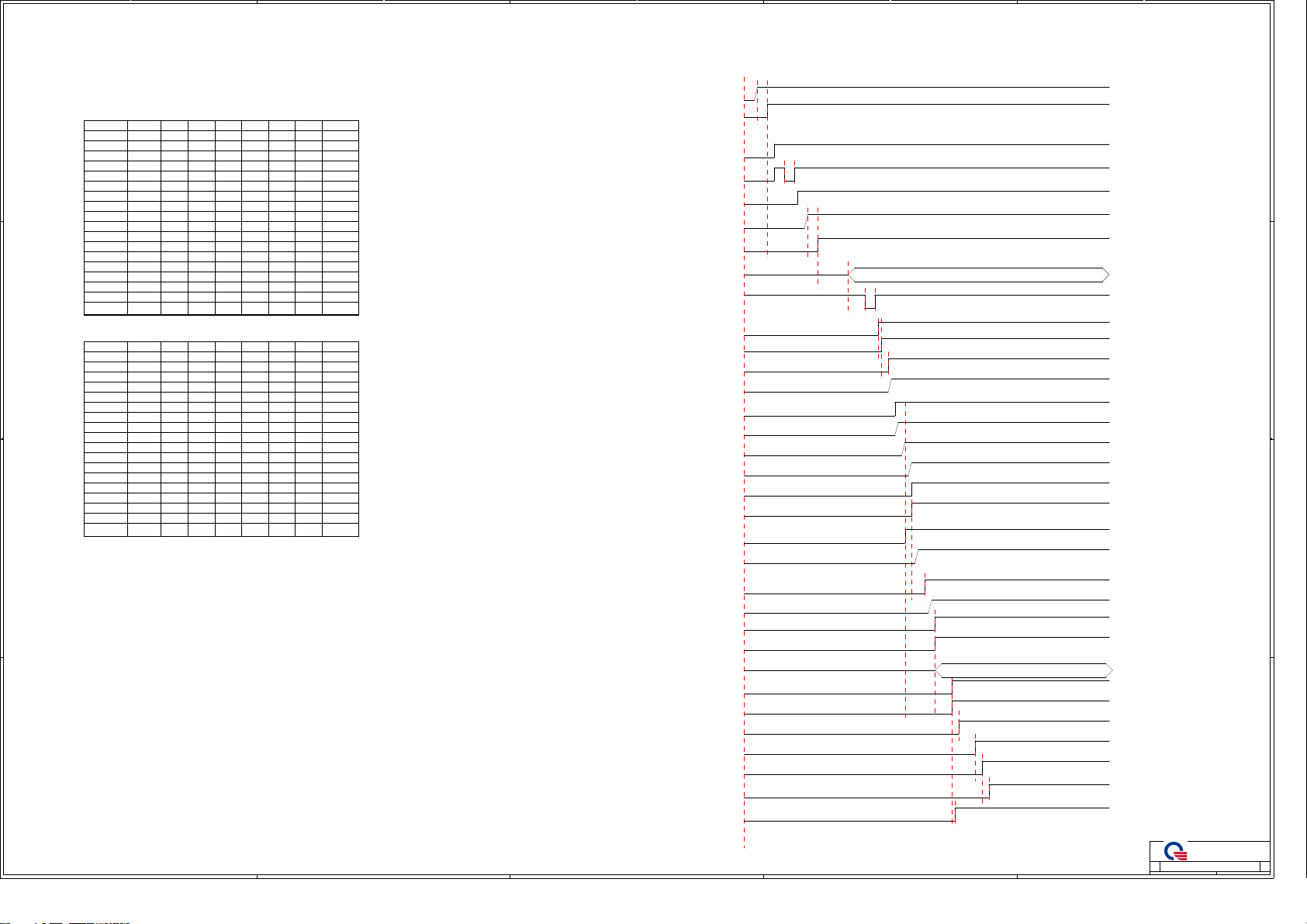

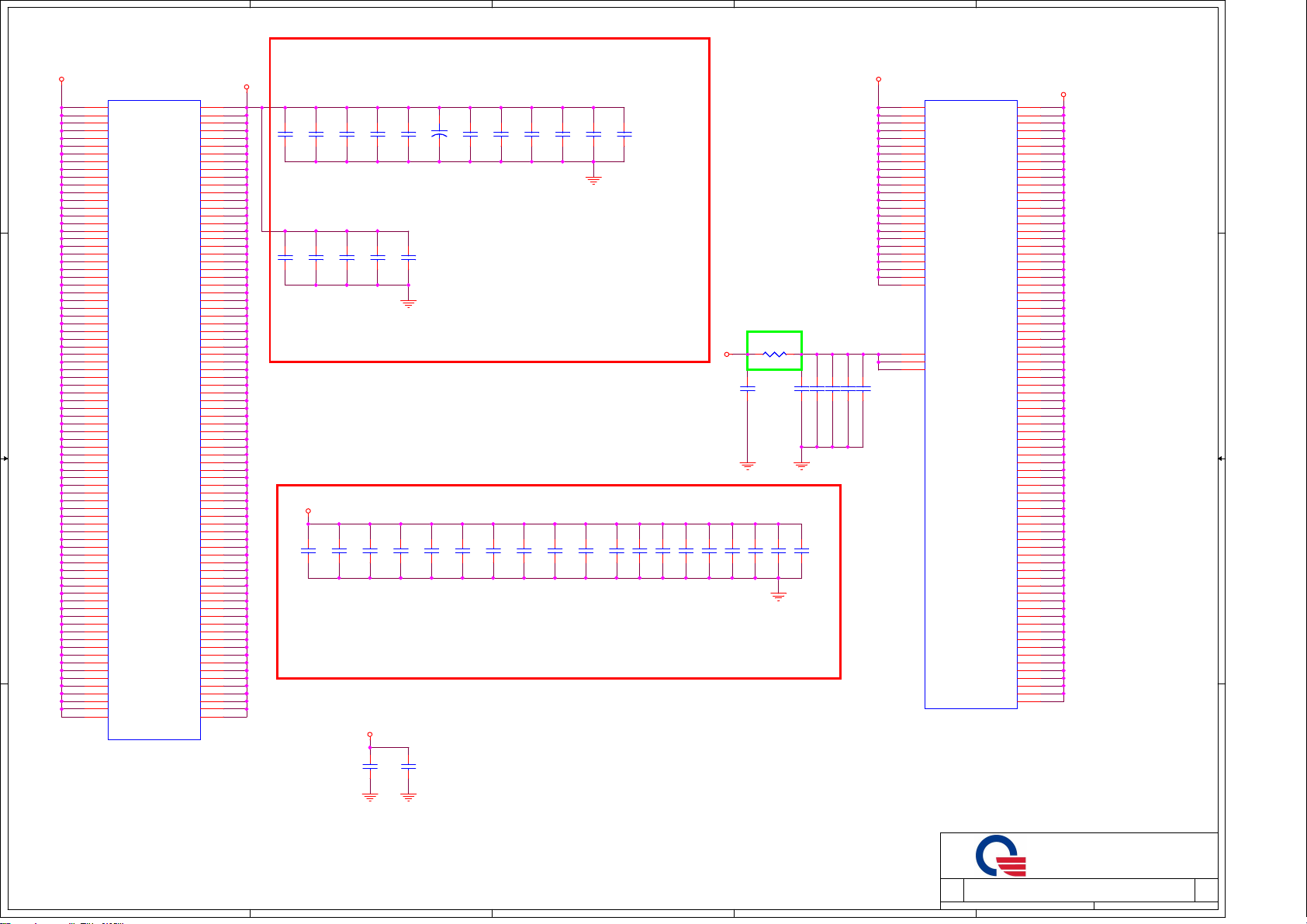

Schematic Page Description :

D D

01 -- Page Description 19 -- PCH 1/6 (DMI/FDI/VIDEO)

02 -- System Block Diagram

03 -- Power Map

04 -- Power Sequence 1/2

05 -- Power Sequence 2/2

06 -- Clock

C C

07 -- SMBus Block Diagram

08 -- GPIO list

09 -- CLOCK GENERATOR

10 -- MCP 1/7(CLK/CTRL/MISC)

20 -- PCH 2/6(SATA/RTC/HDA/LPC)

21 -- PCH 3/6(PCIE/USB/CLK/NV)

22 -- PCH 4/6(GPIO/CPU)

23 -- PCH 5/6(POWER)

24 -- PCH 6/6(GND)

25 -- MXM 3.0

26 --AUDIO CODEC ALC269

27 --LINE OUT/CRT

28 --JMB380 (Card Reader/1394)

39 -- ADP AC IN & HDD12V

41 -- V_AXG (ISL6314)

42 -- DDR3 1.5V(TPS51116)

43 -- CPU_VTT(ISL6314CRZ)

44 -- CPU_CORE (NCP5392)

45 --1.05V_PCH, 1.05V_ME,1.8V

46 -- Discharge Circuit

47 -- CHANGE LIST1

48 -- CHANGE LIST2

49 -- ANNOTATIONS

11 -- MCP 2/7(DDR3 CHANNEL A) 29 -- SATA HDD/ODD

12 -- MCP 3/7(DDR3 CHANNEL B)

13 -- MCP 4/7(PCIE/DMI)

14 -- MCP 5/7( VCCP)

B B

15 -- MCP 6/7(MISC/VCC)

16 -- MCP 7/7(GND)

17 -- DDR3 CHA DIMM0

18 -- DDR3 CHB DIMM0

30 --MINI PCIE(WLAN/TV/IR/BT)

31 --ON BOARD USB

32 --LCD PANEL/INVERTER

33 --LAN(RTL8111DL)

34 --LAN Transformer & RJ45

35 --FAN/D board/CCD/PS2

36 -- EC ITE 8512N/FLASH

37 -- XDP

38 -- SCREW HOLE

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Page Description

Page Description

Page Description

Date: Sheet of

Date: Sheet of

8

7

6

5

4

3

Date: Sheet of

PROJECT :

2

ZN2

ZN2

ZN2

A

A

A

1 49Tuesday, March 16, 2010

1 49Tuesday, March 16, 2010

1 49Tuesday, March 16, 2010

1

Page 2

5

4

3

2

1

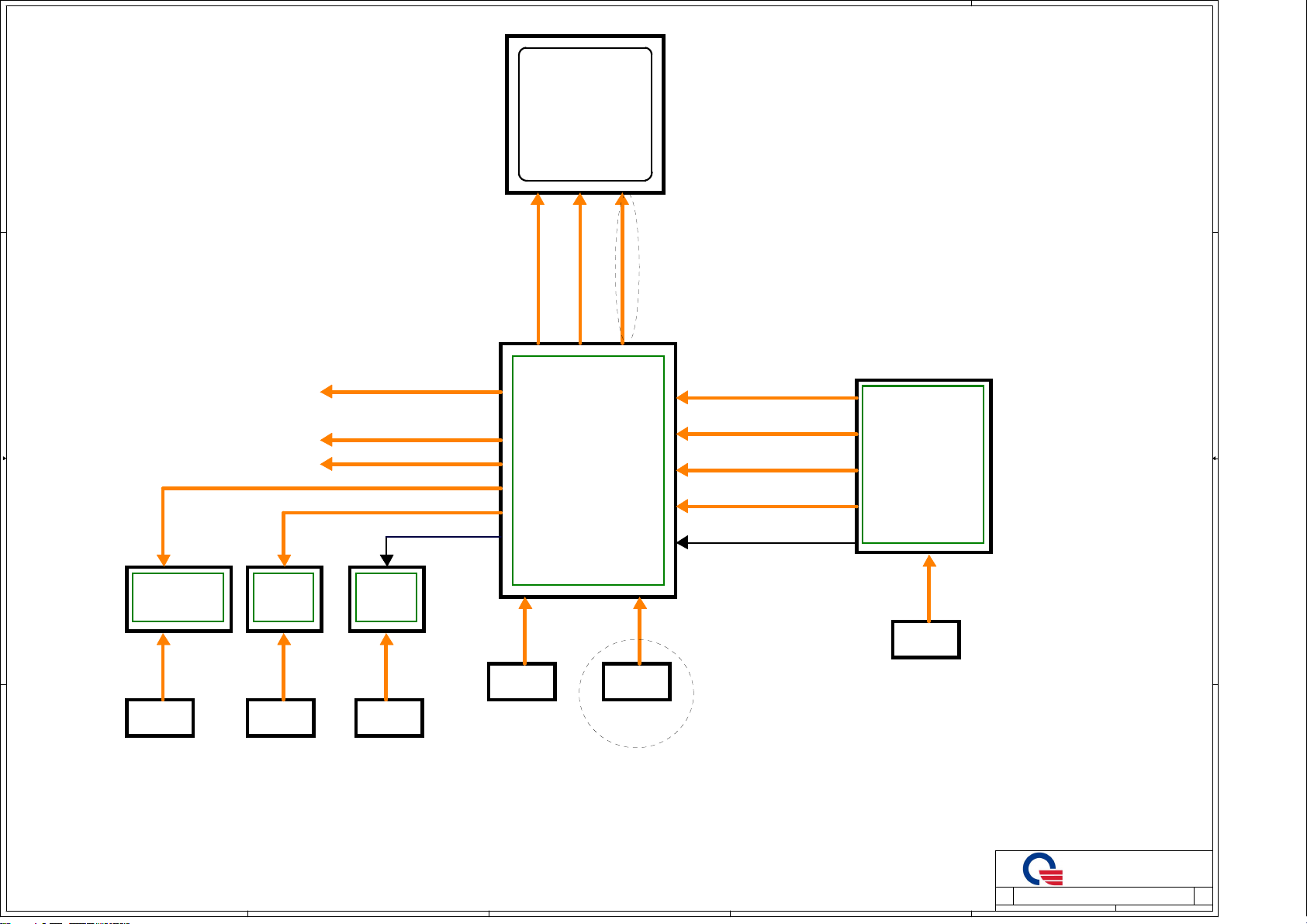

Block Diagram :

D D

MXM CNN

(Graphics)

Mobile PCI-E Module

TYPE-A (314 pin)

VRM 11.1

CPU Core

NCP5392

PCIE 2.0 x16(PEG)

Lynnfield/

Clarkdale

Processor

64-bit/45nm

LGA1156

(37.5x37.5mm)

Channel A

Dual channel DDR3

800/1066/1333MHz 1.5V

Channel B

(95W)

LVDS

PECI

LPC

DMI

x4

PCI-E x1 PCIE 3

USB 2.0

SPI

RTC

Battery

8Mb SPI

Ignition

FW

32.768KHz

LCD Panel CNN

AUO/CHIMEI

(21'' 16:10)

C C

ADPIN

CNN

ADPIN

DCIN/VIN

+5VPCU

B B

+3VPCU

System Power

VIN

MAINON

GFX_VR_EN

SUSON

MAINON

VRON

S5_PWRON

SUSD

MAIND

S5_PWRON

MAIND

+5VPCU/+3VPCU

12VCC

V_AXG

+1.5V_SUS

CPU_VTT_1.1V

+VCC_CORE

+5V_S5

+5V_S5_USB

+5V

+3V_S5

+3V

LCD Panel CNN

AUO/CHIMEI

(21'' 16:10)

SATA HDD(3.5")

SATA ODD

REAR USB x4

SIDE USB x2

USB Dongle x1

CAREMA with

MIC

BLUE TOOTH

+5V_S5

+1.5V_SUS

MAINON

MAINON

+1.8V

+1.05V

INT SPK

CNN(2Wx2)

AUDIO CODEC

ALC269Q

LQFP48

AMP.

Converter

Backlight control

LVDS

(Non-MXM option)

SATA 0

SATA 1

USB 0,1,8,11

USB 2,3

USB 9

USB 4

USB 10

From EC

SATA II

USB 2.0

Azailia

FDI

(*1)

Ibex Peak

PCH

QLLT1071

(25x25mm)

(3.5W)

32.768KHz

EC/KBC

ITE8512

LQFP128

VTT_CPU

1.1V

PCIE 5

PCIE 1

USB 5

PCIE 2

USB 12

DDR3 DIMM

SO-DIMM0

DDR3 DIMM

SO-DIMM1

25MHz

GB LAN

Realtek

RTL8111DL

CARD READER

(JMICRO JMB385)

Mini PCIE1

WLAN CNN

Mini PCIE2

TV Tuner CARD CNN

Annt.

CLOCK Generator

CK505

Reset Circuit

LED Indicator

MAIN SW CNN

RJ45 CNN

6 in 1

CNN

14.318MHz

INT MIC

A A

On WCM

Head

Phone

(*1)FDI - Used only for the Clarkdale processor.

5

MIC

IN

Line

Out

FAN CTRL

(CPU/

System)

4

2Mb SPI

BIOS

ROM

3

IR

RECEIVER

IR

Blaster

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

ZN2

ZN2

ZN2

2 49Tuesday, March 16, 2010

2 49Tuesday, March 16, 2010

1

2 49Tuesday, March 16, 2010

A

A

A

Page 3

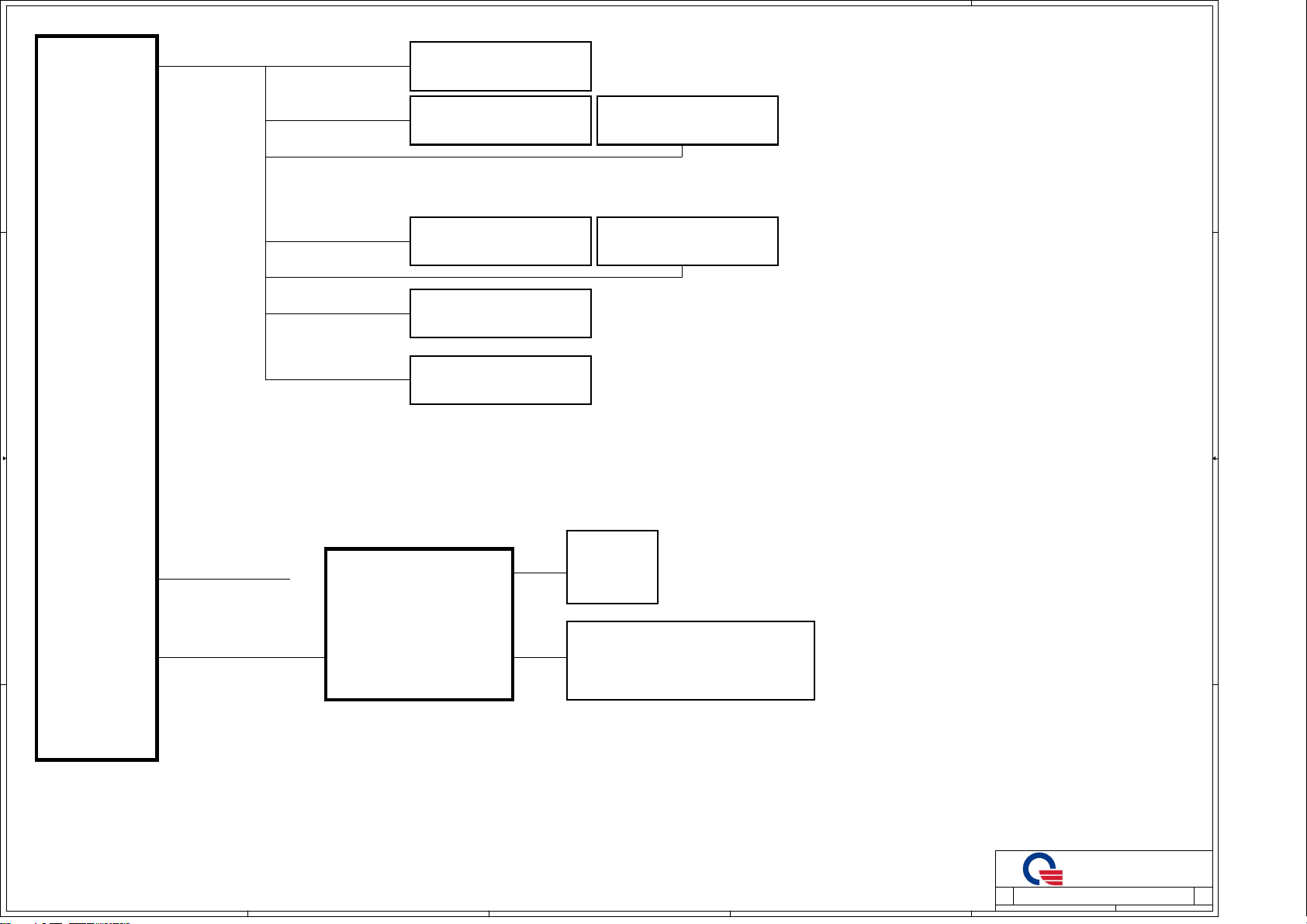

Power Rail

+VCC_CORE

V_AXG

5

Destination

Lynnfield :

Default for initial power up

for 92W TDP SKU

for 79W TDP SKU

Voltage

0.65V~1.4V

1.1V

0.5~1.3V

4

S0 Current

90A(TDC)

10A (TDC)

16A (TDC)

3

VIN

MAINON

2

1

3

+12V

NCP1587Adaptor

D D

+1.1V_VTT

+1.8V

+1.5V_SUS

SMDDR_VTERM

+1.05V

+1.5V

C C

+3V

+5V

B B

Lynnfield : Memory controller

& shared cache

Ibex Peak : DMI

Ibex Peak : CPU_IO 1.05V~1.1V~1.16V

Lynnfield : Internal processor PLL

Ibex Peak : Internal PLL & VRMs

Ibex Peak : Dual channel NAND I/F 1.71V~1.8V~1.89V

DIMM :

1.045V~1.1V~1.155V

1.1V

1.71V~1.8V~1.89V

1.71V~1.8V~1.89V

1.425V~1.5V~1.575VLynnfield : CPU I/O Voltage for DDRIII

0.75V 2ADDRIII Terminator:

Ibex Peak : VccCore 1.629A

Ibex Peak : Vcc core I/O buffer

Ibex Peak : DMI buffer voltage 0.998V~1.05V~1.1V

Ibex Peak : Display PLL A power

Ibex Peak : Display PLL B power

0.998V~1.05V~1.1V

0.998V~1.05V~1.1V

0.998V~1.05V~1.1V

0.998V~1.05V~1.1V

Mini PCIE : +1.5V(WLAN)

Ibex Peak : I/O buffer voltage

CH7308 : LVDD

ALC662 : DVDD

Mini PCIE : +3.3V(WLAN)

CAREMA

Ibex Peak : Core well Ref. voltage

SATA ODD

SATA HDD(2.5'' x SSD)

ALC662S : AVDD

Touch Screen

LCD Panel

USB: x 12 ports 6A5V

3.14V~3.3V~3.47V

3.14V~3.3V~3.47V

4.75V~5V~5.25V

30A(TDC)

0.065A

0.001A

1.1A

0.196A

0.156A

6A

3.251A

0.065A

0.075A

0.075A

0.357A

0.069AIbex Peak : Display DAC Analog power

0.001A

+5VPCU

NCP1587

+3VPCU

TPS51116RGE

MOS

D

MOS

D

MOS

D

MOS

D

+1.5V_SUS

SMDDR_VTERM

S5_Power_ON

G

S

MAINON

G

S

S5_Power_ON

G

S

MAINON

G

S

MAINONMAINON SUSON

G

D

S

+5V_S5

+5V

+3V_S5

+3V

+1.5V

LDO

LDO

D

G

OP

S

D

G

OP

S

+1.8V

+1.05V

MXM_12V

HDD_12V

+3V_S5

+5V_S5

Ibex Peak : Intel Management Engine

Ibex Peak : Suspend well I/O Buffer

Suspend Voltage

LAN 82578DM : VDD

CLK Gen.CK505 : VDD

EC(IT8512) : VSTBY

SPI FLASH ROM

3.14V~3.3V~3.47V

3.14V~3.3V~3.47V

3.14V~3.3V~3.47V

Ibex Peak : Suspend well Ref. Voltage 4.75V~5V~5.25V

INVERTER : Vin

0.086A

0.168A

0.006AIbex Peak : HD Audio controller

0.001A

NCP1589A

MAINON

NCP5380

+1.1V_VTT

+12V power up

V_AXG

FAN_CPU

A A

+3VPCU

+5VPCU

GFX_VR_EN

NCP5392TMNR2G

+VCC_CORE

15VPCU

Quanta Computer Inc.

Quanta Computer Inc.

VIN

VRON

5

4

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Power Map

Power Map

Power Map

1

ZN2

ZN2

ZN2

A

A

A

3 49Tuesday, March 16, 2010

3 49Tuesday, March 16, 2010

3 49Tuesday, March 16, 2010

Page 4

5

Power Sequence

CPU

D D

RTC

RTC_RST#

+VCCRTC

21

logical AND of the PCH’s PWROK and SYS_PWROK

C C

AND

Clarkdale

Lynnfield

MEM_PWRGD

H_PWRGOOD

PROCPWRGD

PCH

MEPWROK

PWROK

SYS_PWROK

ICH_SUSCLK

SYS_PWROK

8

+1.1V_VTT

CPU_VTT_PG

3.3V Leavel

shift to 1.1V

12

+3V_S5

+5V_S5

+3V

+5V

+1.05V

+1.8V

+1.1V_VTT

4

DDR3

other PCI/PCIe device

6

6

12

12

12

12

12

PROCPWRGD

6

+1.5V_SUS

6

SMDDR_VTERM

HWPG

15

CPU_VTT_PG

15

3.3V Leavel

shift to 1.1V

15

SYS_PWROK

USB Port

+5V_S5

AND

CLOCK Gen

3

DVDD12/EVDD12

LAN

RTL811DL

+3V_S5

+1.5V_SUS_PG

3V&5V_PCU_PG

+1.1V_VTT_PG

AND

+1.05V_PG

Control VR delay for meet chipset spec

V_AXG_PG

PWROK_EC

VR_READY

VR_READY

EN

+1.8V

12

+1.05V

2

6

+3V_S5

MAINON

LDO

D

12

OP

G

S

11

12

+3V

D

S

MOS

G

MAINON

11

S5_Power_ON

G

MOS

D

S

5

+3VPCU

S5_Power_ON

6

G

MOS

+5V_S5

D

S

1

4

DC Jack

3

NCP1587

5

3

VIN

3

+5VPCU

12

+5V

MAINON

LDO

D

OP

+1.5V

G

S

D

S

MOS

G

MAINON

MAINON

11

G

MOS

12

D

S

6

+1.5V_SUS

11

11

TPS51116RGE

11

6

SMDDR_VTERM

MAINON

11

ICH_PWBTN#

SUSB#

B B

For platform not supporting Intel AMT it can be

connected to PWROK.

SYS_PWROK be used on the platform to indicate that the processor VR power is

good and therefore it can be connected to the same source as PWROK on PCH.

SUSC#

ITE

ITE8512

EC

+3V_S5

HWPG

VRON

VRON

16

A A

MAINON

15

11

16

Control signal

RTC Power

PCU Power

S5 Power

S0 Power

5

+3V

S5_Power_ON

12

5

6

8910

+3VPCU

3 1

ICH_RSMRST#

7

4

+12V

NCP1587

MAINON 11

PWRBTSW#

+1.1V_VTT

IronLake will drive Gfx_VR_EN when VTT ramps

+VCCRTC

V_AXG

17

+VCC_CORE

NCP1589A

GFX_VR_EN

14

NCP5380

VRON

16

NCP5392TMNR2G

13

VR_READY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZN2

ZN2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Power Se quence 1/2

Power Se quence 1/2

Power Se quence 1/2

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

1

ZN2

4 49Tuesday, March 16, 2010

4 49Tuesday, March 16, 2010

4 49Tuesday, March 16, 2010

A

A

A

Page 5

5

4

3

2

1

5

POWER SEQUENCE

SUSON

MAINON

9ms,min

Minimum duration of PWRBTN# a ssertion = 16ms

10ms,min

20ns,min

see PCH EDS P.380

100ms,min

16ms,min

Clock

30us,min

D D

C C

Voltage Rails

Power S0 Ctl SignalS3 S 4 S5

Voltage

+VCCRTC 3V

VIN 19.5V

+5VPCU

+5V_S5

+3V_S5

+1.5V_SUS

SMDDR_VTERM

+12V

+5V

+3V

+1.5V

+1.05V

+1.8V

+1.1V_VTT

V_AXG

+VCC_CORE

VIN_MXM

+5V_MXM

+3V_MXM

USBVCC2

3VPCU_EC

LCDVCC

CCD_PWR

VIN_LCD

VDDA_CODEC

ON

ON ON ON ON

ON ON ON ON OFF

5V

ON ON ON ON OFF

3.3V+3VPCU

5V

3.3V

1.5V

0.75V

12V

5V

3.3V

1.5V

1.05V

1.8V

1.1V / 1.05V

???V

???V

ONONON

ON ON

ON ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

Voltage

G3

PCU

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

PCUPower S0 S 3 S4 S5

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

G3

OFF

Adaptor in

Adaptor in

Adaptor in EC

S5_PWRON

PCH SUS,

S5_PWRON

Sys Management, PCH Resume Well, Intel HD Audio, USB, WLAN,

SUSON

DDR3 Memory

SUSON

DDR3 Memory

MAINON

MAINON

SATA, PCI REF

MAINON

PCI Express*, SATA, HV CMOS,CRT, Band Gap voltages, Intel HD Audio

MAINON

mini PCIe, Intel HD Audio

MAINON

PCH core, PCH PLL voltages, PCH CLK Buffer, SATA, USB, PCH fuse,Display Link, Display Port, PCIe

MAINON

LVDSIO, SFR, FLASH

MAINON

CPU VTT, FDI,PEG, DMI, VCCTTADDR, PCH DMI,PCH V_CPU_IO

GFX_VR_EN

mini PCIe, Intel HD Audio

VRON

CPU Core

+VCCRTC

RTC_RST#

VIN/+5VPCU/+3VPCU

NBSWON#

S5_PWRON

+3V_S5/+5V_S5

ICH_RSMRST#

ICH_SUSCLK

ICH_PWRBTN#

SUSC# (S4)

SUSB# (S3)

+1.5V_SUS/SMDDR_VTERM

+1.5V/+3V/+1.8V/+5V

+1.1V_VTT/+1.05V/V _AXG

+12V

VTT stable to VTTPWRGOOD = 0 .0001ms~500ms

CPU_VTT_PG

HWPG

B B

GFX_VR_EN

V_AXG

IronLake will drive Gfx_VR_EN when VTT ramps

VRON

99ms,min

+VCC_CORE

VR_READY/SYS_PWROK

CK_PWRGD_R

CLK_BUF_BCLK (CK505 Clock)

PWROK_EC

PCHPWROK/MEPWROK

MEM_PWRGD

H_PWRGOOD

A A

SUS_STAT#

PLTRST#

SPI data

5

4

3

2

Clock

3ms~20ms

And logic (VR_READY&PWROK_EC)

1ms,min

99ms,min

VDDQ must be stable for >= 10 0ns before DRAM_PWROK assertion

1ms,min

100ms,min

1ms,min

60us,min

500us,min

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

ZN2

PROJECT :

ZN2

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Power Sequ ence 2/2

Power Sequ ence 2/2

Power Sequ ence 2/2

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

ZN2

5 49Tuesday, March 16, 2010

5 49Tuesday, March 16, 2010

5 49Tuesday, March 16, 2010

A

A

A

Page 6

5

4

3

2

1

6

CPU

D D

Clarkdale

Lynnfield

CLKOUT_DP [120MHz] (reserved)

CLK_PCIE_DMI [100MHz]

CLK_CPU_BCLK [133MHz]

C C

MXM card

TV card

WLAN card

CLK_PCIE_VGAN [100MHz]

CLK_PCH_SRC1[100MHz]

CLK_PCH_SRC3 [100MHz]

CLK_PCH_SRC2 [100MHz]

CLK_PCIE_LOM [100MHz]

CLK_PCI_775 [33MHz]

PCH

CLK_BUF_DREFCLK [96MHz]

CLK_BUF_PCIE_3GPLL [100MHz]

CLK_BUF_DREFSSCLK [100MHz]

CLK_BUF_BCLK [133MHz]

CLK_ICH_14M [14.318MHz]

Clock

Gen.

B B

Card

reader

JMB380

Crystal

24.576MHz

Ex X'tal

A A

5

LAN

8111DL

Crystal

25MHz

Ex X'tal

EC

ITE8512

Crystal

32.768KHz

Ex X'tal

4

Crystal

32.768KHz

Ex X'tal Ex X'tal

(RTC)

Crystal

32.768KHz

(reserved)

3

2

Crystal

14.318MHz

Ex X'tal

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock

Clock

Clock

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

ZN2

ZN2

ZN2

6 49Tuesday, March 16, 2010

6 49Tuesday, March 16, 2010

1

6 49Tuesday, March 16, 2010

A

A

A

Page 7

5

SMBCLK/SMBDAT

4

3

2

1

7

Clock

D D

DDR CHA SO-DIMM

DDR CHB SO-DIMM

Mini PCIe Slot Mini PCIe Slot

PCH

XPD

C C

EDID EEPRom

B B

SML0CLK/SML0DAT

SMBCLK1

MXM

LPC

SMBCLK0

A A

5

EC

SMBCLK2

4

External Thermal IC

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SMBus Block Diagram

SMBus Block Diagram

SMBus Block Diagram

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

ZN2

ZN2

ZN2

7 49Tuesday, March 16, 2010

7 49Tuesday, March 16, 2010

1

7 49Tuesday, March 16, 2010

A

A

A

Page 8

5

4

3

2

1

8

GPIO/PIN

I/ONAME

I

B

D D

I

I

O

O

I

O

O

O

O

C C

I

O

O

O

O

I

I

I

I

B B

I

I

I

I

O

O

O

I

I

DESCRIPTION

ACTIVE

INITAL : HIGH / ACTIVE : LOW

GPIO/PIN

I/ONAME

DESCRIPTION

ACTIVE

I

B

I

I

O

O

I

O

O

O

O

I

O

O

O

O

I

I

I

I

I

I

I

I

O

O

O

I

I

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

GPIO List

GPIO List

GPIO List

PROJECT :

1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

ZN2

ZN2

ZN2

A

A

A

8 49Tuesday, March 16, 2010

8 49Tuesday, March 16, 2010

8 49Tuesday, March 16, 2010

Page 9

5

Clock Generator

+3V

D D

C C

180ohm/1.5A

L31

L31

CLK_ICH_14M

C437

C437

*10P/50V_4

*10P/50V_4

BKP1608HS181T_6_1.5A

BKP1608HS181T_6_1.5A

C418

C418

C405

C405

4.7U/10V_8

4.7U/10V_8

4.7U/10V_8

4.7U/10V_8

C138

C138

0.1U/16V_4

0.1U/16V_4

CLK_ICH_14M21

150mA(20mil)

C129

C129

C128

C128

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

C431 33P/50V_4C431 33P/50V_4

C427 33P/50V_4C427 33P/50V_4

4

C145

C145

C146

C146

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

R385 33_J_4R385 33_J_4

Y3

Y3

14.318MHZ

14.318MHZ

2 1

+3V_CLK

CLK_SDATA

CLK_SCLK

CPU_SELCLK_ICH_14M

XTAL_IN

XTAL_OUT

U16

U16

1

VDD_DOT

5

VDD_27

17

VDD_SRC

24

VDD_CPU

29

VDD_REF

31

SDA

32

SCL

30

REF_0/CPU_SEL

28

XTAL_IN

27

XTAL_OUT

2

VSS_DOT

8

VSS_27

9

VSS_SATA

12

VSS_SRC

21

VSS_CPU

26

VSS_REF

33

GND

9LRS3197

9LRS3197

3

VDD_SRC_I/O

VDD_CPU_I/O

DOT_96

DOT_96#

27M

27M_SS

SRC_1/SATA

SRC_1#/SATA#

SRC_2

SRC_2#

*CPU_STOP#

CPU_1

CPU_1#

CPU_0

CPU_0#

CKPWRGD/PD#

15

18

CLK_BUF_DREFCLKP_R

3

CLK_BUF_DREFCLKN_R

4

6

7

CLK_BUF_PCIE_3GPLLP_R

10

CLK_BUF_PCIE_3GPLLN_R

11

CLK_BUF_DREFSSCLKP_R

13

CLK_BUF_DREFSSCLKN_R

14

R104 10K_J_4R104 10K_J_4

16

20

19

CLK_BUF_BCLKP_R

23

CLK_BUF_BCLKN_R

22

CK_PWRGD_R

25

TP49TP49

TP50TP50

RP16 0X2RP16 0X2

RP13 0X2RP13 0X2

RP12 0X2RP12 0X2

+3V

TP47TP47

TP48TP48

RP11 0X2RP11 0X2

1

3

1

3

1

3

1

3

+VDDIO_CLK

2

4

2

4

2

4

2

4

2

80mA(20mil)

C428

C428

0.1U/16V_4

0.1U/16V_4

Place each 0.1uF cap as close as

possible to each VDD IO pin. Place

the 10uF caps on the VDD_IO plane.

CLK_BUF_DREFCLKP 21

CLK_BUF_DREFCLKN 21

CLK_BUF_PCIE_3GPLLP 21

CLK_BUF_PCIE_3GPLLN 21

CLK_BUF_DREFSSCLKP 21

CLK_BUF_DREFSSCLKN 21

CLK_BUF_BCLKP 21

CLK_BUF_BCLKN 21

C421

C421

0.1U/16V_4

0.1U/16V_4

C413

C413

10U/10V/Y5V_8

10U/10V/Y5V_8

1

1.05V to 3.3V from external power supply

L35 *BKP1608HS181T_6_1.5AL35 *BKP1608HS181T_6_1.5A

L34 BKP1608HS181T_6_1.5AL34 BKP1608HS181T_6_1.5A

C424

C424

10U/10V/Y5V_8

10U/10V/Y5V_8

C308 may be can save

+3V

+1.05V

9

B B

CPU_CLK select

A A

CPU_SEL

CPU0/1=133MHz

(default)

+1.05V

+3V

R392

R392

*10K_J_4

*10K_J_4

0 1

5

R399

R399

*10K_J_4

*10K_J_4

CPU_SEL

R390

R390

10K_J_4

10K_J_4

CPU0/1=100MHz

C436

C436

*10P/50V_4

*10P/50V_4

ICH_SMBDATA21

ICH_SMBCLK21

4

+3V

R400

R400

2.2K_J_4

2

3

Q18

Q18

2N7002K

2N7002K

+3V

2

3

Q19

Q19

2N7002K

2N7002K

2.2K_J_4

CLK_SDATA

1

R401

R401

2.2K_J_4

2.2K_J_4

1

CLK_SCLK

3

CLK_SDATA 17,18,30,32,37

CLK_SCLK 17,18,30,32,37

CLK EnableSMBus

VR_READY19,44

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

+3V

R367

R367

10K_J_4

10K_J_4

R370

R370

*10K_J_4

*10K_J_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Clock Generator

Clock Generator

Clock Generator

R373

R373

0_J_4

0_J_4

C410

C410

0.22u/10V/X5R_4

0.22u/10V/X5R_4

CK_PWRGD_R

ZN2

ZN2

ZN2

9 49Tuesday, March 16, 2010

9 49Tuesday, March 16, 2010

9 49Tuesday, March 16, 2010

1

A

A

A

Page 10

5

4

3

2

1

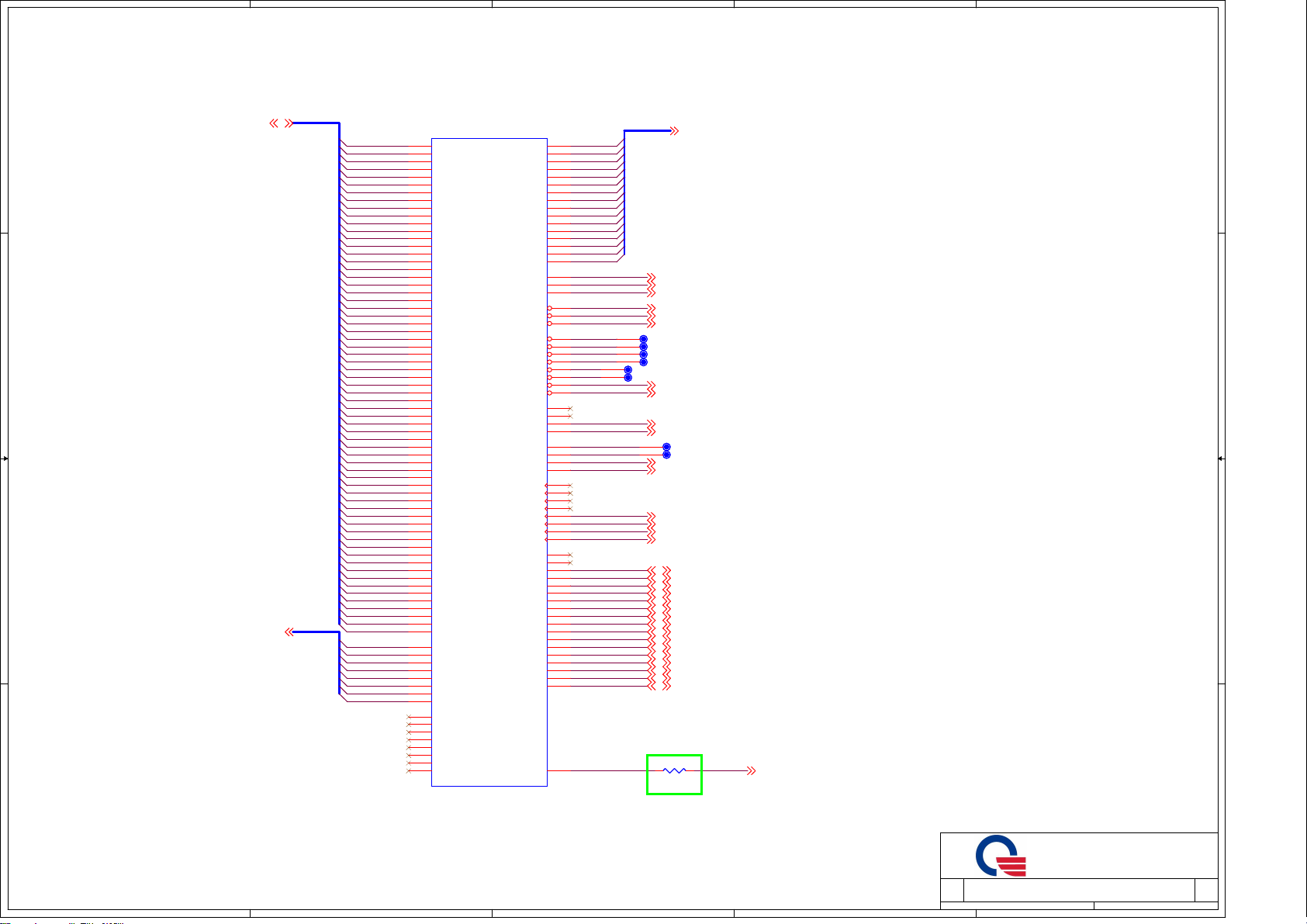

CN3E

CN3E

120MHz DP REFCLK

133MHz CPU BCLK

D D

PM_EXTTS#118

PM_EXTTS#017

C C

PM_SYNC

H_PECI

H_PROCHOT_N

H_THERMTRIP_N

H_CATERR_N

CPU_RESET_OUT_N

H_PWRGOOD

+1.1V_VTT

R9 *51_F_4R9 *51_F_4

A02

R288 *49.9_F_4R288 *49.9_F_4

R284 49.9_F_4R284 49.9_F_4

R290 51_F_4R290 51_F_4

R8 49.9_F_4R8 49.9_F_4

R10 *51_F_4R10 *51_F_4

R281 *49.9_F_4R281 *49.9_F_4

DPCLK_PCH21

DPCLK_PCH#21

CLK_CPU_BCLKP22

CLK_CPU_BCLKN22

H_PWRGOOD22

CPU_VTT_PG36,43

MEM_PW RGD19

H_PECI22,36

VCCP_PSI_N44

H_THERMTRIP_N

PM_SYNC19

+1.1V_VTT

+1.1V_VTT

CPU_TMS37

CPU_TCK037

CPU_TDI37

CPU_TRST_N37

H_CPURST_N

R287 0_J_4R287 0_J_4

R280 0_J_4R280 0_J_4

H_CATERR_N

H_PROCHOT_N

R340 *0_J_4R340 *0_J_4

R337 *0_J_4R337 *0_J_4

R15 20_F_4R15 20_F_4

R13 20_F_4R13 20_F_4

R29 49.9_F_4R29 49.9_F_4

R289 49.9_F_4R289 49.9_F_4

R28 130_F_4R28 130_F_4

R27 24.9_F_4R27 24.9_F_4

R31 100_F_4R31 100_F_4

CPU_TMS

CPU_TCK0

CPU_TDI

TDI_TDO_M

CPU_TRST_N

R33910K_F_4 R33910K_F_4

R33810K_F_4 R33810K_F_4

VCCPWRGOOD1

VCCPWRGOOD0

PM_EXT_TS#1

PM_EXT_TS#0

XDP_CPU_CFG15

R326*1.5K_F_4 R326*1.5K_F_4

XDP_CPU_CFG7

R333*1.5K_F_4 R333*1.5K_F_4

XDP_CPU_CFG6

R332*1.5K_F_4 R332*1.5K_F_4

XDP_CPU_CFG5

R331*1.5K_F_4 R331*1.5K_F_4

XDP_CPU_CFG4

R328*1.5K_F_4 R328*1.5K_F_4

XDP_CPU_CFG3

R330*1.5K_F_4 R330*1.5K_F_4

XDP_CPU_CFG2

R329*1.5K_F_4 R329*1.5K_F_4

XDP_CPU_CFG1

R335*1.5K_F_4 R335*1.5K_F_4

XDP_CPU_CFG0

R334*1.5K_F_4 R334*1.5K_F_4

A02

VID[7:0] : 00101110 =>1.325V@VCC,Max

B B

CFG H L Notes

0

1

2

3

4

5

6

RSVD

RSVD

NORM

DISABLE

RSVD

RSVD

RSVD

ENABLE

H:1x16, L:2x8

LANE REVERSAL

DP PRESENCE

CFG 0-6 all internal PULL-UP

Need to be placed close to processor

A A

to minimize ESD risk

PLTRST#21,22,28,30,33

5

R282 1K_F_4R282 1K_F_4

R291 1.3K_F_4R291 1.3K_F_4

A02 PDG1.5 change

R283

R283

665 _F_4

665 _F_4

XDP_PFRST_N 37

H_CPURST_N

C304

C304

0.1U/16V/X7R_4

0.1U/16V/X7R_4

2009B FMB processors supported

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_VID7

1.1V level

4

AA8

BCLK_DP1

Y8

BCLK_DN1

AA7

BCLK_DP0

AA6

BCLK_DN0

AF34

RSTIN_N

AH36

VCCPWRGOOD1

AH35

VCCPWRGOOD0

AG37

VTTPWRGOOD

AH37

SM_DRAMPWROK

AG35

PECI

AG38

PSI_N

AG39

CATERR_N

AH34

PROCHOT_N

AF35

THERMTRIP_N

AH39

PM_SYNC

AB4

PM_EXT_TS_N1

AB5

H_COMP3

H_COMP2

H_COMP1

H_COMP0

SM_RCOMP2

SM_RCOMP1

SM_RCOMP0

PM_EXT_TS_N0

C11

COMP3

B11

COMP2

AF2

COMP1

AF36

COMP0

AE1

SM_RCOMP2

AD1

SM_RCOMP1

AG1

SM_RCOMP0

AN40

TMS

AN37

TCK

AM37

TDI

AF37

TDI_M

AM39

TRST_N

L11

CFG17

H7

CFG16

K12

CFG15

K9

CFG14

L8

CFG13

J12

CFG12

K8

CFG11

K10

CFG10

H12

CFG9

G12

CFG8

F9

CFG7

E9

CFG6

H9

CFG5

H10

CFG4

F10

CFG3

E10

CFG2

G8

CFG1

E8

CFG0

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

5/10

5/10

0 1 1 1 0 1 0 0

R274

R274

R272

R272

R275

1K_F_4

1K_F_4

R297

R297

*1K_F_4

*1K_F_4

1K_F_4

1K_F_4

R299

R299

*1K_F_4

*1K_F_4

R275

1K_F_4

1K_F_4

R300

R300

*1K_F_4

*1K_F_4

R276

R276

*1K_F_4

*1K_F_4

R301

R301

1K_F_4

1K_F_4

3

R273

R273

*1K_F_4

*1K_F_4

R298

R298

1K_F_4

1K_F_4

BCLK_ITP_DP

BCLK_ITP_DN

VID_5_CSC2

VID_4_CSC1

VID_3_CSC0

VID2_MSID2

VID1_MSID1

VID0_MSID0

GFX_VR_EN

GFX_IMON

VCC_SENSE

VSS_SENSE

VTT_SELECT

VTT_SENSE

VSS_SENSE_VTT

VAXG_SENSE

VSSAXG_SENSE

SKTOCC_N

TAPPWRGOOD

CPU_RESETOBS_N

R278

R278

R277

R277

*1K_F_4

*1K_F_4

1K_F_4

1K_F_4

R302

R302

R303

R303

*1K_F_4

*1K_F_4

1K_F_4

1K_F_4

VID7

VID6

GFX_VID6

GFX_VID5

GFX_VID4

GFX_VID3

GFX_VID2

GFX_VID1

GFX_VID0

FC_AG40

FC_AE38

TDO

TDO_M

ISENSE

VSS_280

PREQ_N

PRDY_N

DBR_N

BPM_N7

BPM_N6

BPM_N5

BPM_N4

BPM_N3

BPM_N2

BPM_N1

BPM_N0

+1.1V_VTT

R279

R279

*1K_F_4

*1K_F_4

R304

R304

1K_F_4

1K_F_4

AK39

AK40

U33

U34

U35

U36

U37

U38

U39

U40

GFX_EN

F12

J11

G11

C12

E11

E12

B12

G10

GFX_IMON

F6

near the processor socket.(NU_for LFD CPU.)

T35

T34

TP_MCP_FC_AG40

AG40

VTT_SELECT

AF39

TP_MCP_FC_AE38

AE38

AE35

AE36

VCCGT_SENSE_P

A13

VCCGT_SENSE_N

B13

CPU_TDO

AM38

TDI_TDO_M

AF38

ISENSE

T40

T39

AK38

AK37

AJ38

AL40

AK34

AL39

AK31

AK30

AL30

AM31

AK32

AK33

AL32

AL33

H_VID7

H_VID6

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

R336 0_F_6R336 0_F_6

XDP_CPU_PRDY_N

XDP_CPU_DBR_N

1

1

Thermal Trip

CAD NOTE:

PLACE TDO TERMINATION NEAR XDP CONNECTOR

PLACE TCK/TDI/TMS END TERMINATION NEAR CPU

GFX_VR_EN

XDP_CPU_BCLK_P 37

XDP_CPU_BCLK_N 37

H_VID7 44

H_VID6 44

H_VID5 44

H_VID4 44

H_VID3 44

H_VID2 44

H_VID1 44

H_VID0 44

R3251K_F_6 R3251K_F_6

G_VID7 41

G_VID6 41

G_VID5 41

G_VID4 41

G_VID3 41

G_VID2 41

G_VID1 41

VCC_SENSE 44

VSS_SENSE 44

TP2TP2

TP3TP3

VSENSE_DIE_CPU0_VTT_P 43

VSENSE_DIE_CPU0_VTT_N 43

VCCGT_SENSE_P 41

VCCGT_SENSE_N 41

CPU_TDO 37

VR_HOT44

2

GFX_VR_EN

H_ISENSE 44

XDP_CPU_PREQ_N 37

XDP_CPU_PRDY_N 37

SYS_RST_N 19,37

XDP_CPU_PWRGD 37

CPU_RESET_OUT_N 37

VR_HOT

R126 *0_J_4R126 *0_J_4

dGPU_PRSNT# 22,25,36

+1.1V_VTT

R327

R327

NU_for LFD CPU.

+1.1V_VTT

GFX_VR_EN 41

T17T17

+1.1V_VTT

*4.7K_J_4R7*4.7K_J_4

R7

R6

*0_J_4R6*0_J_4

+1.1V_VTT +1.1V_VTT

3

Q13

2

R292

R292

*62_J_4

*62_J_4

R293 *0_J_4R293 *0_J_4

+1.1V_VTT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Q13

*FDV301N

*FDV301N

1

Q14

Q14

2

*MMBT3904

*MMBT3904

1 3

R286

R286

*2.21K_F_4

*2.21K_F_4

R285

R285

100_J_4

100_J_4

MCP (CLK/CTRL/MISC)

MCP (CLK/CTRL/MISC)

MCP (CLK/CTRL/MISC)

GFX_VR_EN

Q1

Q1

2

*TR NPN MMBT3904 40V 0.2A

*TR NPN MMBT3904 40V 0.2A

1 3

XDP_CPU_PRDY_N

R296

R296

*10K_J_4

*10K_J_4

SYS_SHDN#H_THERMTRIP_N

PCH_THERMTRIP#

H_PROCHOT_N

Q12

Q12

2

TR NPN MMBT3904 40V 0.2A

TR NPN MMBT3904 40V 0.2A

1 3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

8.2K_J_4

8.2K_J_4

VTT_SELECT_VID3 43

+1.1V_VTT

D34

D34

*BAS316

*BAS316

C296

C296

*1U/16V_6

*1U/16V_6

SYS_SHDN# 40

PCH_THERMTRIP# 22

ZN2

ZN2

ZN2

10 49Tuesday, March 16, 2010

10 49Tuesday, March 16, 2010

10 49Tuesday, March 16, 2010

1

R295 51_F_4R295 51_F_4

10

A

A

A

Page 11

5

4

3

2

1

11

M_A_DQ[63:0]17

D D

C C

B B

M_DM_A[7:0]17

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_DM_A7

M_DM_A6

M_DM_A5

M_DM_A4

M_DM_A3

M_DM_A2

M_DM_A1

M_DM_A0

CN3A

CN3A

AP40

SA_DQ63

AP39

SA_DQ62

AU39

SA_DQ61

AU38

SA_DQ60

AN39

SA_DQ59

AN38

SA_DQ58

AT40

SA_DQ57

AT39

SA_DQ56

AW37

SA_DQ55

AV36

SA_DQ54

AW34

SA_DQ53

AY34

SA_DQ52

AU37

SA_DQ51

AV37

SA_DQ50

AY35

SA_DQ49

AW35

SA_DQ48

AW33

SA_DQ47

AU33

SA_DQ46

AW30

SA_DQ45

AV30

SA_DQ44

AU34

SA_DQ43

AV33

SA_DQ42

AU31

SA_DQ41

AU30

SA_DQ40

AN30

SA_DQ39

AR29

SA_DQ38

AR27

SA_DQ37

AN26

SA_DQ36

AP30

SA_DQ35

AP28

SA_DQ34

AT28

SA_DQ33

AN27

SA_DQ32

AW7

SA_DQ31

AV7

SA_DQ30

AV5

SA_DQ29

AU5

SA_DQ28

AY8

SA_DQ27

AU8

SA_DQ26

AY5

SA_DQ25

AW5

SA_DQ24

AV4

SA_DQ23

AV2

SA_DQ22

AT1

SA_DQ21

AT3

SA_DQ20

AW4

SA_DQ19

AW3

SA_DQ18

AU2

SA_DQ17

AT4

SA_DQ16

AR4

SA_DQ15

AP1

SA_DQ14

AM2

SA_DQ13

AM3

SA_DQ12

AR2

SA_DQ11

AR3

SA_DQ10

AN2

SA_DQ9

AN3

SA_DQ8

AK2

SA_DQ7

AK1

SA_DQ6

AH2

SA_DQ5

AG2

SA_DQ4

AL1

SA_DQ3

AL2

SA_DQ2

AJ4

SA_DQ1

AH1

SA_DQ0

AT38

SA_DM7

AU35

SA_DM6

AW31

SA_DM5

AN29

SA_DM4

AV6

SA_DM3

AU1

SA_DM2

AN1

SA_DM1

AJ2

SA_DM0

AM11

SA_ECC_CB7

AK11

SA_ECC_CB6

AL9

SA_ECC_CB5

AK9

SA_ECC_CB4

AP11

SA_ECC_CB3

AR11

SA_ECC_CB2

AN10

SA_ECC_CB1

AP10

SA_ECC_CB0

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

SA_MA15

SA_MA14

SA_MA13

SA_MA12

SA_MA11

SA_MA10

SA_MA9

SA_MA8

SA_MA7

SA_MA6

SA_MA5

SA_MA4

SA_MA3

SA_MA2

SA_MA1

SA_MA0

SA_BS2

SA_BS1

SA_BS0

SA_RAS_N

SA_CAS_N

SA_WE_N

SA_CS_N7

SA_CS_N6

SA_CS_N5

SA_CS_N4

SA_CS_N3

SA_CS_N2

SA_CS_N1

SA_CS_N0

SA_ODT3

SA_ODT2

SA_ODT1

SA_ODT0

SA_CKE3

SA_CKE2

SA_CKE1

SA_CKE0

SA_CKP3

SA_CKN3

SA_CKP2

SA_CKN2

SA_CKP1

SA_CKN1

SA_CKP0

SA_CKN0

SA_DQSP8

SA_DQSN8

SA_DQSP7

SA_DQSN7

SA_DQSP6

SA_DQSN6

SA_DQSP5

SA_DQSN5

SA_DQSP4

SA_DQSN4

SA_DQSP3

SA_DQSN3

SA_DQSP2

SA_DQSN2

SA_DQSP1

SA_DQSN1

SA_DQSP0

SA_DQSN0

SM_DRAMRST#

1/10

1/10

SA_DIMM_VREF

AR10

AT11

AU24

AW11

AU13

AT19

AW12

AU14

AW13

AV14

AY13

AW14

AU15

AV15

AY15

AW18

AU12

AU19

AV20

AT20

AU22

AT22

AK23

AL23

AM22

AK22

AU23

AU21

AW24

AV21

AY24

AW23

AV24

AV23

AY10

AV10

AW10

AU10

AP19

AN19

AN21

AP21

AP18

AN18

AR22

AR21

AL10

AM10

AR39

AR38

AW36

AV35

AV32

AW32

AR28

AT29

AY6

AW6

AU4

AU3

AP2

AP3

AK3

AJ3

AV8

AF3

DIMM_VREFA

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

M_BA_A2

M_BA_A1

M_BA_A0

M_A_RAS#

M_A_CAS#

M_A_WE#

1

1

1

1

1

1

M_CS#_A1

M_CS#_A0

M_ODT_A1

M_ODT_A0

M_CKE_A1

M_CKE_A0

M_CLK_DDR_A1

M_CLK_DDR#_A1

M_CLK_DDR_A0

M_CLK_DDR#_A0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

0_J_4

0_J_4

A02

TP39TP39

TP38TP38

TP41TP41

TP42TP42

TP37TP37

TP6TP6

R26

R26

M_A_A[15:0] 17

M_BA_A2 17

M_BA_A1 17

M_BA_A0 17

M_A_RAS# 17

M_A_CAS# 17

M_A_WE# 17

M_CS#_A1 17

M_CS#_A0 17

M_ODT_A1 17

M_ODT_A0 17

1

TP7TP7

1

TP44TP44

M_CKE_A1 17

M_CKE_A0 17

M_CLK_DDR_A1 17

M_CLK_DDR#_A1 17

M_CLK_DDR_A0 17

M_CLK_DDR#_A0 17

M_A_DQS7 17

M_A_DQS#7 17

M_A_DQS6 17

M_A_DQS#6 17

M_A_DQS5 17

M_A_DQS#5 17

M_A_DQS4 17

M_A_DQS#4 17

M_A_DQS3 17

M_A_DQS#3 17

M_A_DQS2 17

M_A_DQS#2 17

M_A_DQS1 17

M_A_DQS#1 17

M_A_DQS0 17

M_A_DQS#0 17

DDR3_DRAMRST# 17,18

VREF_DQ_DDRA 17

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP (DDR3 CHANNEL A)

MCP (DDR3 CHANNEL A)

MCP (DDR3 CHANNEL A)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZN2

ZN2

ZN2

A

A

11 49Tuesday, March 16, 2010

11 49Tuesday, March 16, 2010

11 49Tuesday, March 16, 2010

1

A

Page 12

5

4

3

2

1

12

D D

C C

B B

A A

M_B_DQ[63:0]18

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_DM_B[7:0]18

M_B_DQ0

M_DM_B7

M_DM_B6

M_DM_B5

M_DM_B4

M_DM_B3

M_DM_B2

M_DM_B1

M_DM_B0

CN3B

CN3B

AL36

SB_DQ63

AJ35

SB_DQ62

AM34

SB_DQ61

AN35

SB_DQ60

AJ37

SB_DQ59

AJ36

SB_DQ58

AM35

SB_DQ57

AL35

SB_DQ56

AP37

SB_DQ55

AN34

SB_DQ54

AT35

SB_DQ53

AP34

SB_DQ52

AP36

SB_DQ51

AN33

SB_DQ50

AT36

SB_DQ49

AR35

SB_DQ48

AT33

SB_DQ47

AR34

SB_DQ46

AR31

SB_DQ45

AT31

SB_DQ44

AM32

SB_DQ43

AR33

SB_DQ42

AP31

SB_DQ41

AT32

SB_DQ40

AT26

SB_DQ39

AP25

SB_DQ38

AP22

SB_DQ37

AT23

SB_DQ36

AR26

SB_DQ35

AR25

SB_DQ34

AP23

SB_DQ33

AN23

SB_DQ32

AT9

SB_DQ31

AL8

SB_DQ30

AR6

SB_DQ29

AN8

SB_DQ28

AM8

SB_DQ27

AR9

SB_DQ26

AR7

SB_DQ25

AT6

SB_DQ24

AP5

SB_DQ23

AN7

SB_DQ22

AM4

SB_DQ21

AL5

SB_DQ20

AR5

SB_DQ19

AP6

SB_DQ18

AN5

SB_DQ17

AL6

SB_DQ16

AK7

SB_DQ15

AJ7

SB_DQ14

AG4

SB_DQ13

AG6

SB_DQ12

AL4

SB_DQ11

AK6

SB_DQ10

AH7

SB_DQ9

AG5

SB_DQ8

AE6

SB_DQ7

AF5

SB_DQ6

AC6

SB_DQ5

AC7

SB_DQ4

AJ8

SB_DQ3

AH8

SB_DQ2

AD6

SB_DQ1

AD7

SB_DQ0

AK35

SB_DM7

AM33

SB_DM6

AN32

SB_DM5

AN24

SB_DM4

AT7

SB_DM3

AM7

SB_DM2

AH4

SB_DM1

AE4

SB_DM0

AP13

SB_ECC_CB7

AN14

SB_ECC_CB6

AN12

SB_ECC_CB5

AM12

SB_ECC_CB4

AP14

SB_ECC_CB3

AN15

SB_ECC_CB2

AT13

SB_ECC_CB1

AR12

SB_ECC_CB0

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

SB_MA15

SB_MA14

SB_MA13

SB_MA12

SB_MA11

SB_MA10

SB_MA9

SB_MA8

SB_MA7

SB_MA6

SB_MA5

SB_MA4

SB_MA3

SB_MA2

SB_MA1

SB_MA0

SB_BS2

SB_BS1

SB_BS0

SB_RAS_N

SB_CAS_N

SB_WE_N

SB_CS_N7

SB_CS_N6

SB_CS_N5

SB_CS_N4

SB_CS_N3

SB_CS_N2

SB_CS_N1

SB_CS_N0

SB_ODT3

SB_ODT2

SB_ODT1

SB_ODT0

SB_CKE3

SB_CKE2

SB_CKE1

SB_CKE0

SB_CKP3

SB_CKN3

SB_CKP2

SB_CKN2

SB_CKP1

SB_CKN1

SB_CKP0

SB_CKN0

SB_DQSP8

SB_DQSN8

SB_DQSP7

SB_DQSN7

SB_DQSP6

SB_DQSN6

SB_DQSP5

SB_DQSN5

SB_DQSP4

SB_DQSN4

SB_DQSP3

SB_DQSN3

SB_DQSP2

SB_DQSN2

SB_DQSP1

SB_DQSN1

SB_DQSP0

SB_DQSN0

2/10

2/10

SB_DIMM_VREF

AV11

AY12

AW28

AW15

AW16

AY25

AY16

AT17

AU16

AW17

AV17

AY18

AU17

AV18

AU18

AU20

AV12

AW25

AU25

AW26

AW27

AU26

AK24

AL24

AM24

AM23

AV29

AV26

AW29

AY27

AU28

AV27

AU29

AU27

AV9

AU9

AY9

AW8

AR19

AR18

AN17

AN16

AT15

AR15

AR17

AR16

AR14

AR13

AL37

AM36

AR36

AR37

AP32

AR32

AT25

AR24

AR8

AP8

AN6

AM6

AH6

AJ5

AF4

AE5

AG3

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

M_BA_B2

M_BA_B1

M_BA_B0

M_B_RAS#

M_B_CAS#

M_B_WE#

1

1

M_CS#_B1

M_CS#_B0

M_ODT_B1

M_ODT_B0

M_CKE_B1

M_CKE_B0

M_CLK_DDR_B1

M_CLK_DDR#_B1

M_CLK_DDR_B0

M_CLK_DDR#_B0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

DIMM_VREFB

1

1

1

1

TP4TP4

TP5TP5

M_B_A[15:0] 18

M_BA_B2 18

M_BA_B1 18

M_BA_B0 18

M_B_RAS# 18

M_B_CAS# 18

M_B_WE# 18

TP36TP36

TP34TP34

TP35TP35

TP40TP40

M_CS#_B1 18

M_CS#_B0 18

M_ODT_B1 18

M_ODT_B0 18

1

TP8TP8

1

TP46TP46

M_CKE_B1 18

M_CKE_B0 18

M_CLK_DDR_B1 18

M_CLK_DDR#_B1 18

M_CLK_DDR_B0 18

M_CLK_DDR#_B0 18

M_B_DQS7 18

M_B_DQS#7 18

M_B_DQS6 18

M_B_DQS#6 18

M_B_DQS5 18

M_B_DQS#5 18

M_B_DQS4 18

M_B_DQS#4 18

M_B_DQS3 18

M_B_DQS#3 18

M_B_DQS2 18

M_B_DQS#2 18

M_B_DQS1 18

M_B_DQS#1 18

M_B_DQS0 18

M_B_DQS#0 18

R30

R30

0_J_4

0_J_4

VREF_DQ_DDRB 18

A02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP (DDR3 CHANNEL B)

MCP (DDR3 CHANNEL B)

MCP (DDR3 CHANNEL B)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZN2

ZN2

ZN2

A

A

12 49Tuesday, March 16, 2010

12 49Tuesday, March 16, 2010

12 49Tuesday, March 16, 2010

1

A

Page 13

5

4

3

2

1

13

CN3C

CN3C

AC3

AC4

AD3

AD4

AC2

AA3

AA4

W3

W2

U1

V1

U3

U2

R1

T1

T3

T4

P3

P4

L2

L3

J1

K1

J3

J2

G1

H1

G3

G2

E1

F1

D2

E2

C3

D3

B4

C4

A5

B5

B6

C6

A7

A6

B8

C8

C9

D9

DMI_RXP3

DMI_RXN3

DMI_RXP2

DMI_RXN2

DMI_RXP1

DMI_RXN1

DMI_RXP0

DMI_RXN0

FDI_FSYNC_1

FDI_FSYNC_0

FDI_LSYNC_1

FDI_LSYNC_0

FDI_INT

PEG_RXP15

PEG_RXN15

PEG_RXP14

PEG_RXN14

PEG_RXP13

PEG_RXN13

PEG_RXP12

PEG_RXN12

PEG_RXP11

PEG_RXN11

PEG_RXP10

PEG_RXN10

PEG_RXP9

PEG_RXN9

PEG_RXP8

PEG_RXN8

PEG_RXP7

PEG_RXN7

PEG_RXP6

PEG_RXN6

PEG_RXP5

PEG_RXN5

PEG_RXP4

PEG_RXN4

PEG_RXP3

PEG_RXN3

PEG_RXP2

PEG_RXN2

PEG_RXP1

PEG_RXN1

PEG_RXP0

PEG_RXN0

PEG_CLKP

PEG_CLKN

3/10

3/10

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

PEG_TXP15

PEG_TXN15

PEG_TXP14

PEG_TXN14

PEG_TXP13

PEG_TXN13

PEG_TXP12

PEG_TXN12

PEG_TXP11

PEG_TXN11

PEG_TXP10

PEG_TXN10

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

D D

FDI_FSYNC119

FDI_FSYNC019

FDI_LSYNC119

FDI_LSYNC019

FDI_INT19

R22

R22

R24

R24

*1K_F_4

*1K_F_4

C C

R21

R21

R23

R25

R25

*1K_F_4

*1K_F_4

R23

*1K_F_4

*1K_F_4

*1K_F_4

*1K_F_4

*1K_F_4

*1K_F_4

A02

B B

100MHz (PCIE\DMI\FDI)

DMI_TXP319

DMI_TXN319

DMI_TXP219

DMI_TXN219

DMI_TXP119

DMI_TXN119

DMI_TXP019

DMI_TXN019

PEG_RXP1525

PEG_RXN1525

PEG_RXP1425

PEG_RXN1425

PEG_RXP1325

PEG_RXN1325

PEG_RXP1225

PEG_RXN1225

PEG_RXP1125

PEG_RXN1125

PEG_RXP1025

PEG_RXN1025

PEG_RXP925

PEG_RXN925

PEG_RXP825

PEG_RXN825

PEG_RXP725

PEG_RXN725

PEG_RXP625

PEG_RXN625

PEG_RXP525

PEG_RXN525

PEG_RXP425

PEG_RXN425

PEG_RXP325

PEG_RXN325

PEG_RXP225

PEG_RXN225

PEG_RXP125

PEG_RXN125

PEG_RXP025

PEG_RXN025

CLK_PCIE_DMI21

CLK_PCIE_DMI#21

PEG_RXP15

PEG_RXN15

PEG_RXP14

PEG_RXN14

PEG_RXP13

PEG_RXN13

PEG_RXP12

PEG_RXN12

PEG_RXP11

PEG_RXN11

PEG_RXP10

PEG_RXN10

PEG_RXP9

PEG_RXN9

PEG_RXP8

PEG_RXN8

PEG_RXP7

PEG_RXN7

PEG_RXP6

PEG_RXN6

PEG_RXP5

PEG_RXN5

PEG_RXP4

PEG_RXN4

PEG_RXP3

PEG_RXN3

PEG_RXP2

PEG_RXN2

PEG_RXP1

PEG_RXN1

PEG_RXP0

PEG_RXN0

DMI_TXP3

DMI_TXN3

DMI_TXP2

DMI_TXN2

DMI_TXP1

DMI_TXN1

DMI_TXP0

DMI_TXN0

FDI_TXP7

FDI_TXN7

FDI_TXP6

FDI_TXN6

FDI_TXP5

FDI_TXN5

FDI_TXP4

FDI_TXN4

FDI_TXP3

FDI_TXN3

FDI_TXP2

FDI_TXN2

FDI_TXP1

FDI_TXN1

FDI_TXP0

FDI_TXN0

PEG_TXP9

PEG_TXN9

PEG_TXP8

PEG_TXN8

PEG_TXP7

PEG_TXN7

PEG_TXP6

PEG_TXN6

PEG_TXP5

PEG_TXN5

PEG_TXP4

PEG_TXN4

PEG_TXP3

PEG_TXN3

PEG_TXP2

PEG_TXN2

PEG_TXP1

PEG_TXN1

PEG_TXP0

PEG_TXN0

R2

R3

N1

P1

N3

N2

L1

M1

Y6

Y5

Y4

Y3

R8

R7

W5

W4

W8

W7

U8

U7

V4

V3

U6

U5

R5

R6

M8

N8

N6

N5

K7

L7

M4

M3

L6

L5

H8

J8

K3

K4

J6

J5

F7

G7

H4

H3

G6

G5

F3

F4

E5

F5

E7

E6

C7

D7

D11

C10

B10

A11

PEG_TXP15

PEG_TXN15

PEG_TXP14

PEG_TXN14

PEG_TXP13

PEG_TXN13

PEG_TXP12

PEG_TXN12

PEG_TXP11

PEG_TXN11

PEG_TXP10

PEG_TXN10

PEG_TXP9

PEG_TXN9

PEG_TXP8

PEG_TXN8

PEG_TXP7

PEG_TXN7

PEG_TXP6

PEG_TXN6

PEG_TXP5

PEG_TXN5

PEG_TXP4

PEG_TXN4

PEG_TXP3

PEG_TXN3

PEG_TXP2

PEG_TXN2

PEG_TXP1

PEG_TXN1

PEG_TXP0

PEG_TXN0

PEG_COMPO

PEG_RBIAS

FDI_TXP7

FDI_TXN7

FDI_TXP6

FDI_TXN6

FDI_TXP5

FDI_TXN5

FDI_TXP4

FDI_TXN4

FDI_TXP3

FDI_TXN3

FDI_TXP2

FDI_TXN2

FDI_TXP1

FDI_TXN1

FDI_TXP0

FDI_TXN0

R14

R14

750_F_4

750_F_4

DMI_RXP3 19

DMI_RXN3 19

DMI_RXP2 19

DMI_RXN2 19

DMI_RXP1 19

DMI_RXN1 19

DMI_RXP0 19

DMI_RXN0 19

PEG_TXP15 25

PEG_TXN15 25

PEG_TXP14 25

PEG_TXN14 25

PEG_TXP13 25

PEG_TXN13 25

PEG_TXP12 25

PEG_TXN12 25

PEG_TXP11 25

PEG_TXN11 25

PEG_TXP10 25

PEG_TXN10 25

PEG_TXP9 25

PEG_TXN9 25

PEG_TXP8 25

PEG_TXN8 25

PEG_TXP7 25

PEG_TXN7 25

PEG_TXP6 25

PEG_TXN6 25

PEG_TXP5 25

PEG_TXN5 25

PEG_TXP4 25

PEG_TXN4 25

PEG_TXP3 25

PEG_TXN3 25

PEG_TXP2 25

PEG_TXN2 25

PEG_TXP1 25

PEG_TXN1 25

PEG_TXP0 25

PEG_TXN0 25

R16

R16

49.9_F_4

49.9_F_4

CHB (FDI_TX[7:4])

CHA (FDI_TX[3:0])

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

FDI_TXN[7:0] 19

FDI_TXP[7:0] 19

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP (PCIE/DMI)

MCP (PCIE/DMI)

MCP (PCIE/DMI)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZN2

ZN2

ZN2

A

A

13 49Tuesday, March 16, 2010

13 49Tuesday, March 16, 2010

13 49Tuesday, March 16, 2010

1

A

Page 14

5

4

3

2

1

14

+VCC_CORE +VCC_CORE

CN3F

CN3F

R40

VCC181

R39

VCC180

D D

C C

B B

R38

VCC179

R37

VCC178

R36

VCC177

R35

VCC176

R34

VCC175

R33

VCC174

P40

VCC173

P39

VCC172

P38

VCC171

P37

VCC170

P36

VCC169

P35

VCC168

P34

VCC167

P33

VCC166

N39

VCC165

N38

VCC164

N36

VCC163

N35

VCC162

N33

VCC161

M40

VCC160

M39

VCC159

M37

VCC158

M36

VCC157

M34

VCC156

M33

VCC155

M30

VCC154

M28

VCC153

M27

VCC152

M25

VCC151

M24

VCC150

M22

VCC149

M21

VCC148

M19

VCC147

M17

VCC146

L40

VCC145

L38

VCC144

L37

VCC143

L35

VCC142

L34

VCC141

L32

VCC140

L31

VCC139

L29

VCC138

L28

VCC137

L26

VCC136

L25

VCC135

L23

VCC134

L22

VCC133

L20

VCC132

L19

VCC131

L17

VCC130

K39

VCC129

K38

VCC128

K36

VCC127

K35

VCC126

K33

VCC125

K32

VCC124

K30

VCC123

K29

VCC122

K27

VCC121

K26

VCC120

K24

VCC119

K23

VCC118

K21

VCC117

K20

VCC116

K18

VCC115

K17

VCC114

J40

VCC113

J39

VCC112

J37

VCC111

J36

VCC110

J34

VCC109

J33

J31

J30

J28

J27

J25

J24

VCC_NCTF_2

VCC108

VCC107

VCC106

VCC105

VCC104

VCC103

VCC102

6/10

6/10

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

VCC101

VCC100

VCC99

VCC98

VCC97

VCC96

VCC95

VCC94

VCC93

VCC92

VCC91

VCC90

VCC89

VCC88

VCC87

VCC86

VCC85

VCC84

VCC83

VCC82

VCC81

VCC80

VCC79

VCC78

VCC77

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

VCC56

VCC55

VCC54

VCC53

VCC52

VCC51

VCC50

VCC49

VCC48

VCC47

VCC46

VCC45

VCC44

VCC43

VCC42

VCC41

VCC40

VCC39

VCC38

VCC37

VCC36

VCC35

VCC34

VCC33

VCC32

VCC31

VCC30

VCC29

VCC28

VCC27

VCC26

VCC25

VCC24

VCC23

J22

J21

J19

J18

H40

H38

H37

H35

H34

H32

H31

H29

H28

H26

H25

H23

H22

H20

H19

G39

G38

G36

G35

G33

G32

G30

G29

G27

G26

G24

G23

G21

G20

F40

F39

F37

F36

F34

F33

F31

F30

F28

F27

F25

F24

F22

F21

E40

E38

E37

E35

E34

E32

E31

E29

E28

E26

E25

E23

E22

D39

D38

D36

D35

D33

D32

D30

D29

D27

D26

D24

D23

C40

C39

C37

C36

C34

C33

C31

C30

PLACE ALL 22UF, 0805 CAPS

INSIDE THE SOCKET CAVITY

C13

C13

C17

C17

C351

C351

C18

C18

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C21

C21

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C28

C28

C27

C27

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C339

C339

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C10

C10

C22

C22

C328

C328

C333

C333

+

+

330U/2V_7343

330U/2V_7343

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

PLACE ALL 22UF, 0805 CAPS

INSIDE THE SOCKET CAVITY.

ON BOTTOM OF BOARD

+1.1V_VTT

C327

C327

22U/6.3V_8

22U/6.3V_8

PLACE ALL 22UF, 0805 CAPS

INSIDE THE SOCKET CAVITY

C353

C353

C371

C338

C338

22U/6.3V_8

22U/6.3V_8

+1.1V_VTT

C365

C365

0.1U/16V/X7R_4

0.1U/16V/X7R_4

C371

22U/6.3V_8

22U/6.3V_8

C377

C377

C331

C331

C372

C372

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

0.1U/16V/X7R_4

0.1U/16V/X7R_4

C347

C347

22U/6.3V_8

22U/6.3V_8

C19

C19

C352

C352

C11

C11

C12

C12

C321

C321

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C373

C373

22U/6.3V_8

22U/6.3V_8

C320

C320

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

+1.8V

R12 0_F_6R12 0_F_6

C323

C323

22U/6.3V_8

22U/6.3V_8

C334

C334

22U/6.3V_8

22U/6.3V_8

C14

C14

C29 2.2U/6.3V_6C29 2.2U/6.3V_6

C45

C45

C20

C20

C16

C16

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C23

C23

C46

C46

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C24

C24

C47 0.1U/16V/X7R_4C47 0.1U/16V/X7R_4

C42 22U/6.3V_8C42 22U/6.3V_8

C359

C359

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

+VCC_CORE

CN3G

CN3G

C28

VCC22

C27

VCC21

C25

VCC20

C24

VCC19

C23

VCC18

B38

VCC17

B37

VCC16

B35

VCC15

B34

VCC14

B32

VCC13

B31

VCC12

B29

VCC11

B28

VCC10

B26

VCC9

B25

VCC8

B23

VCC7

A38

VCC_NCTF_1

A36

VCC6

A35

VCC5

A33

VCC4

A27

VCC3

A26

VCC2

A24

VCC1

A23

VCC0

VCCPLL

AG8

VCCPLL2

C44 0.1U/16V/X7R_4C44 0.1U/16V/X7R_4

C30 0.1U/16V/X7R_4C30 0.1U/16V/X7R_4

AF8

C34 22U/6.3V_8C34 22U/6.3V_8

VCCPLL1

AF7

VCCPLL0

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

7/10

7/10

VTT67

VTT66

VTT65

VTT77

VTT76

VTT75

VTT74

VTT73

VTT72

VTT71

VTT70

VTT69

VTT68

VTT62

VTT61

VTT60

VTT59

VTT58

VTT57

VTT64

VTT63

VTT48

VTT47

VTT46

VTT45

VTT44

VTT56

VTT55

VTT54

VTT53

VTT52

VTT51

VTT50

VTT49

VTT12

VTT43

VTT42

VTT41

VTT40

VTT39

VTT11

VTT10

VTT38

VTT37

VTT36

VTT35

VTT34

VTT33

VTT32

VTT31

VTT30

VTT29

VTT28

VTT27

VTT26

VTT25

VTT24

VTT23

VTT22

VTT21

VTT20

VTT19

VTT18

VTT17

VTT16

VTT15

VTT14

VTT13

VTT9

VTT8

VTT7

VTT6

VTT5

VTT4

VTT3

VTT2

VTT1

VTT0

W6

W1

V6

V2

T2

P8

P7

P6

N7

M9

M11

M10

L10

AB7

V8

V7

T8

T7

T6

AJ23

AC5

AK19

AJ19

AJ17

AE8

AC8

AL21

AL20

AK21

AK20

AJ29

AJ27

AJ25

AJ21

Y38

Y37

Y36

Y35

Y34

Y33

V40

V39

V38

V37

V36

V35

V34

V33

AJ32

AJ31

AG33

AF33

AE40

AE39

AE34

AE33

AD40

AD39

AD38

AD37

AD36

AD35

AD34

AD33

AC40

AC39

AC38

AC37

AC36

AC35

AC34

AC33

AA38

AA37

AA36

AA35

AA34

AA33

+1.1V_VTT

A A

Quanta Computer Inc.

Quanta Computer Inc.

For DMI bus split power plane

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP (VCCP)

MCP (VCCP)

MCP (VCCP)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZN2

ZN2

ZN2

14 49Tuesday, March 16, 2010

14 49Tuesday, March 16, 2010

14 49Tuesday, March 16, 2010

1

A

A

A

Page 15

5

4

3

2

1

15

D D

VAXG tie to GND for LFD CPU.

CN3D

CN3D

A12

RSVD_A12

A4

RSVD_NCTF_A4

AD2

RSVD_AD2

AE2

RSVD_AE2

AH40

RSVD_AH40

AJ39

RSVD_AJ39

AK12

RSVD_AK12

AK13

RSVD_AK13

AK14

RSVD_AK14

AK15

RSVD_AK15

AK16

C C

1

XDP_TESTIN_N

TP43TP43

B B

RSVD_AK16

AK18

RSVD_AK18

AK25

RSVD_AK25

AK26

RSVD_AK26

AK27

RSVD_AK27

AK28

RSVD_AK28

AK29

RSVD_AK29

AL12

RSVD_AL12

AL14

RSVD_AL14

AL15

RSVD_AL15

AL17

RSVD_AL17

AL18

RSVD_AL18

AL26

RSVD_AL26

AL27

RSVD_AL27

AL29

RSVD_AL29

AM13

RSVD_AM13

AN11

RSVD_TP

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

RSVD_NCTF_AU40

RSVD_NCTF_AV1

RSVD_NCTF_AV39

RSVD_NCTF_AW2

RSVD_NCTF_AW38

RSVD_NCTF_AY3

RSVD_NCTF_AY37

GFX_DPRSLPVR

4/10

4/10

RSVD_AM14

RSVD_AM15

RSVD_AM16

RSVD_AM17

RSVD_AM18

RSVD_AM19

RSVD_AM20

RSVD_AM21

RSVD_AM25

RSVD_AM26

RSVD_AM27

RSVD_AM28

RSVD_AM29

RSVD_AM30

RSVD_NCTF_B3

RSVD_NCTF_C2

RSVD_NCTF_D1

RSVD_M12

RSVD_L12

AM14

AM15

AM16

AM17

AM18

AM19

AM20

AM21

AM25

AM26

AM27

AM28

AM29

AM30

AU40

AV1

AV39

AW2

AW38

AY3

AY37

B3

C2

D1

J10

L12

M12

TP45TP45

1

V_AXG +1.5V_SUS

CN3H

CN3H

M16

VAXG48

M15

VAXG47

M14

VAXG46

L16

VAXG45

L15

VAXG44

L14

VAXG43

K16

VAXG42

K15

VAXG41

K14

VAXG40

J16

VAXG39

J15

VAXG38

J14

VAXG37

H17

VAXG36

H15

VAXG35

H14

VAXG34

G18

VAXG33

G17

VAXG32

G15

VAXG31

G14

VAXG30

F19

VAXG29

F18

VAXG28

F17

VAXG27

F15

VAXG26

F14

VAXG25

E20

VAXG24

E18

VAXG23

E17

VAXG22

E15

VAXG21

E14

VAXG20

D21

VAXG19

D20

VAXG18

D18

VAXG17

D17

VAXG16

D15

VAXG15

D14

VAXG14

C21

VAXG13

C20

VAXG12

C18

VAXG11

C17

VAXG10

C15

VAXG9

C14

VAXG8

B18

VAXG7

B17

VAXG6

B15

VAXG5

B14

VAXG4

A18

VAXG3

A17

VAXG2

A15

VAXG1

A14

8/10

8/10

VAXG0

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

VDDQ18

VDDQ17

VDDQ16

VDDQ15

VDDQ14

VDDQ13

VDDQ12

VDDQ11

VDDQ10

VDDQ9

VDDQ8

VDDQ7

VDDQ6

VDDQ5

VDDQ4

VDDQ3

VDDQ2

VDDQ1

VDDQ0

C35

C35

CAVITY

C379

C364

C374

C374

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C362

C362

22U/6.3V_8

22U/6.3V_8

C364

22U/6.3V_8

22U/6.3V_8

C363

C363

22U/6.3V_8

22U/6.3V_8

C36

C36

C379

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

PLACE BACKSIDE OF MCP CAVITY

AY26

AY23

AY17

AY14

AY11

AW9

AV28

AV25

AV22

AV19

AV16

AV13

AU11

AT21

AT18

AT10

AJ15

AJ13

AJ11

+1.5V_SUS

C43

C43

22U/6.3V_8

22U/6.3V_8

C32

C32

22U/6.3V_8

22U/6.3V_8

SOCKET CAVITY

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP (MISC/VCC)

MCP (MISC/VCC)

MCP (MISC/VCC)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZN2

ZN2

ZN2

A

A

15 49Tuesday, March 16, 2010

15 49Tuesday, March 16, 2010

15 49Tuesday, March 16, 2010

1

A

Page 16

5

4

3

2

1

16

CN3I

D D

C C

B B

CN3I

Y7

VSS274

W38

VSS273

W37

VSS272

W36

VSS271

W35

VSS270

W34

VSS269

W33

VSS268

V5

VSS267

U4

VSS266

T5

VSS265

T38

VSS264

T37

VSS263

T36

VSS262

T33

VSS261

R4

VSS260

P5

VSS259

P2

VSS258

N40

VSS257

N4

VSS256

N37

VSS255

N34

VSS254

M7

VSS253

M6

VSS252

M5

VSS251

M38

VSS250

M35

VSS249

M32

VSS248

M29

VSS247

M26

VSS246

M23

VSS245

M20

VSS244

M2

VSS243

M18

VSS242

M13

VSS241

L9

VSS240

L4

VSS239

L39

VSS238

L36

VSS237

L33

VSS236

L30

VSS235

L27

VSS234

L24

VSS233

L21

VSS232

L18

VSS231

L13

VSS230

K6

VSS229

K5

VSS228

K40

VSS227

K37

VSS226

K34

VSS225

K31

VSS224

K28

VSS223

K25

VSS222

K22

VSS221

K2

VSS220

K19

VSS219

K13

VSS218

K11

VSS217

J9

VSS216

J7

VSS215

J4

VSS214

J38

VSS213

J35

VSS212

J32

VSS211

J29

VSS210

J26

VSS209

J23

VSS208

J20

VSS207

J17

VSS206

J13

VSS205

9/10

9/10

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

VSS204

VSS203

VSS202

VSS201

VSS200

VSS199

VSS198

VSS197

VSS196

VSS195

VSS194

VSS193

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

H6

H5

H39

H36

H33

H30

H27

H24

H21

H2

H18

H16

H13

H11

G9

G40

G4

G37

G34

G31

G28

G25

G22

G19

G16

G13

F8

F38

F35

F32

F29

F26

F23

F20

F2

F16

F13

F11

E4

E39

E36

E33

E30

E3

E27

E24

E21

E19

E16

E13

D8

D6

D5

D40

D4

D37

D34

D31

D28

D25

D22

D19

D16

D13

D12

D10

C5

C38

C35

CN3J

CN3J

C32

VSS135

C29

VSS134

C26

VSS133

C22

VSS132

C19

VSS131

C16

VSS130

C13

VSS129

B9

VSS128

B7

VSS127

B39

CGC_TP_NCTF

B36

VSS126

B33

VSS125

B30

VSS124

B27

VSS123

B24

VSS122

B16

VSS121

AY7

VSS120

AY4

VSS119

AY36

VSS118

AY33

VSS117

AV38

VSS115

AV34

VSS114

AV31

VSS113

AV3

VSS112

AU7

VSS111

AU6

VSS116

AU36

VSS110_1

AU32

VSS110

AT8

VSS109_1

AT5

VSS109

AT37

VSS108

AT34

VSS107

AT30

VSS105

AT27

VSS104

AT24

VSS103

AT2

VSS102

AT16

VSS101

AT14

VSS100

AT12

VSS99

AR40

VSS98

AR30

VSS98

AR23

VSS97

AR20

VSS96

AR1

VSS95

AP9

VSS94

AP7

VSS93

AP4

VSS92

AP38

VSS91

AP35

VSS90_1

AP33

VSS90

AP29

VSS87

AP27

VSS86

AP26

VSS85

AP24

VSS84

AP20

VSS83

AP17

VSS82

AP16

VSS81

AP15

VSS80

AP12

VSS79

AN9

VSS78

AN4

VSS77

AN36

VSS76

AN31

VSS74

AN28

VSS73

AN25

VSS72

AN22

VSS71

AN20

VSS70

AN13

VSS69

AM9

VSS75

10/10

10/10

CN CPU SOCKET SMD LGA1156

CN CPU SOCKET SMD LGA1156

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

VSS61

VSS60

VSS59

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

VSS52

VSS52_1

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS28

VSS32

VSS31

VSS30

VSS29

VSS27

VSS26

VSS25

VSS24

VSS23

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VSS12

VSS11

VSS10

VSS9

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

VSS0

AM5

AM40

AM1

AL7

AL38

AL34

AL31

AL3

AL28

AL25

AL22

AL19

AL16

AL13

AL11

AK8

AK5

AK4

AK36

AK17

AK10

AJ9

AJ6

AJ40

AJ34

AJ33

AJ30

AJ28

AJ26

AJ24

AJ22

AJ20

AJ18

AJ16

AJ14

AJ12

AJ1

AH5

AH38

AH33

AH3

AG7

AG36

AG34

AF6

AF40

AF1

AE7

AE37

AE3

AD8

AD5

AC1

AB8

AB6

AB40

AB39

AB38

AB37

AB36

AB35

AB34

AB33

AB3

AA5

A37

A34

A28

A25

A16

A A

Quanta Computer Inc.

Quanta Computer Inc.