A

smd.db-x7.ru

MODEL

ZM3 MB

4 4

3 3

2 2

REV CHANGE LIST

3A

Reference to ECN E201307-3790

B

C

D

E

Model

ZM3 MB

Page FROM TO

1

2

3

4

5

6

7

8

9

10

11

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

1 1

QUANTA

COMPUTER

A

PROJECT : ZM3 DOC. NO. 204

APPROVED BY : Kent Weng

B

CHECKED BY : Kent Weng

REV:

3A

REV:

3A

REV:

3A

C

D

ASSY: 31ZM3MB0090/31ZM3MB00A0

DATE : SHEET OFDRAWN BY :

7, 18, 2013 1 1Edison Hsu

DATE : SHEET OFDRAWN BY :

7, 18, 2013 1 1Edison Hsu

DATE : SHEET OFDRAWN BY :

7, 18, 2013 1 1Edison Hsu

E

1

smd.db-x7.ru

2

3

4

5

6

7

8

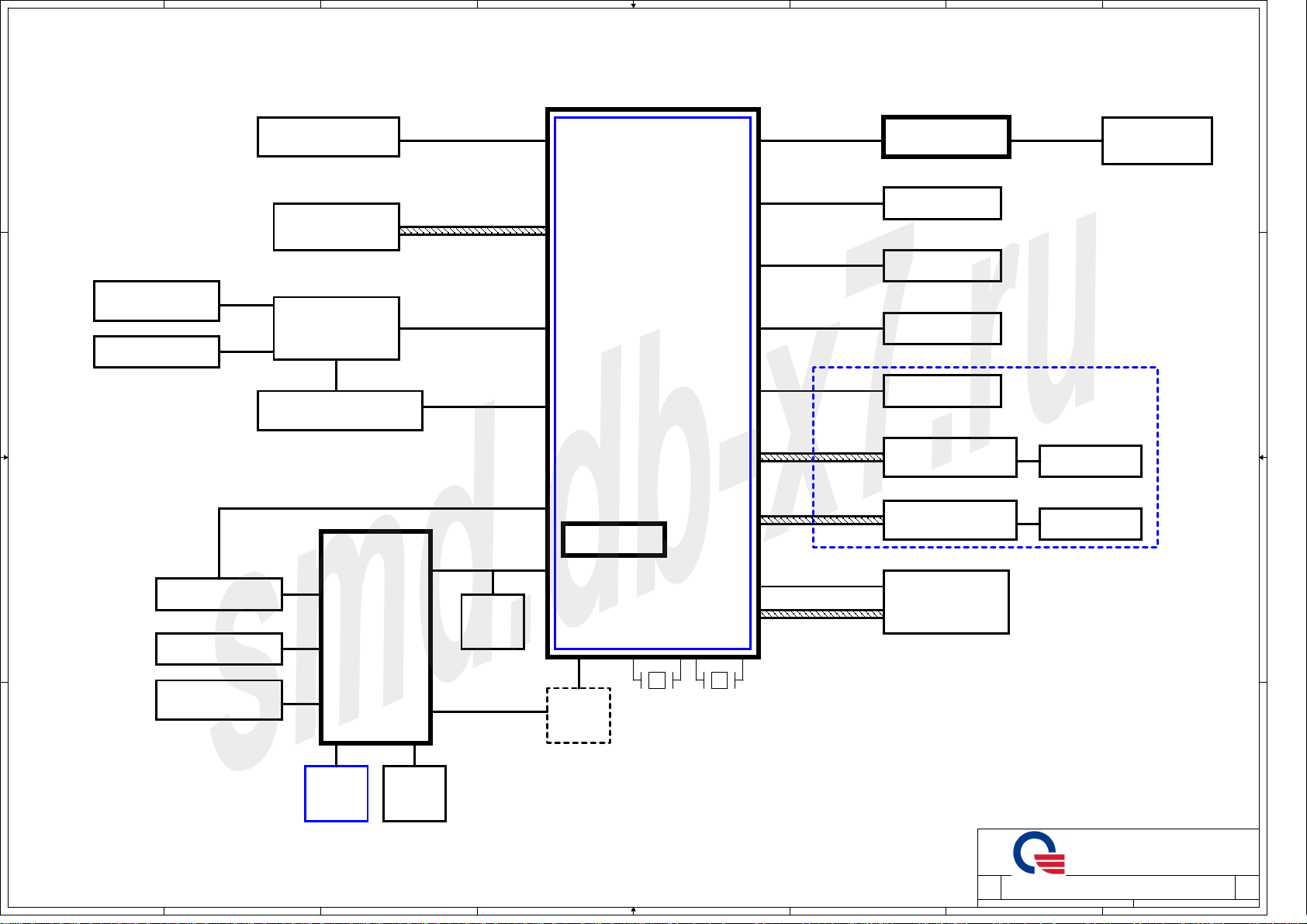

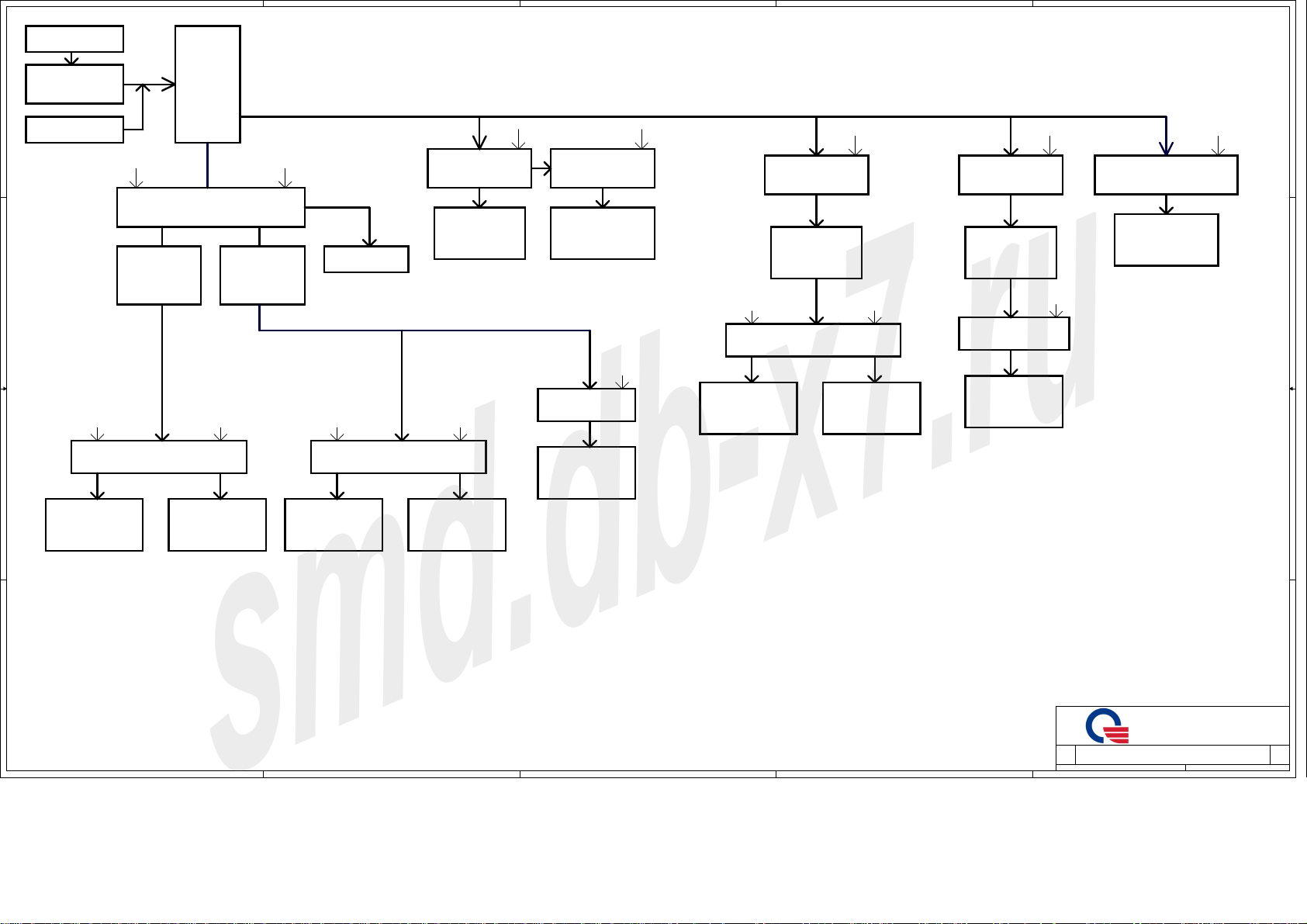

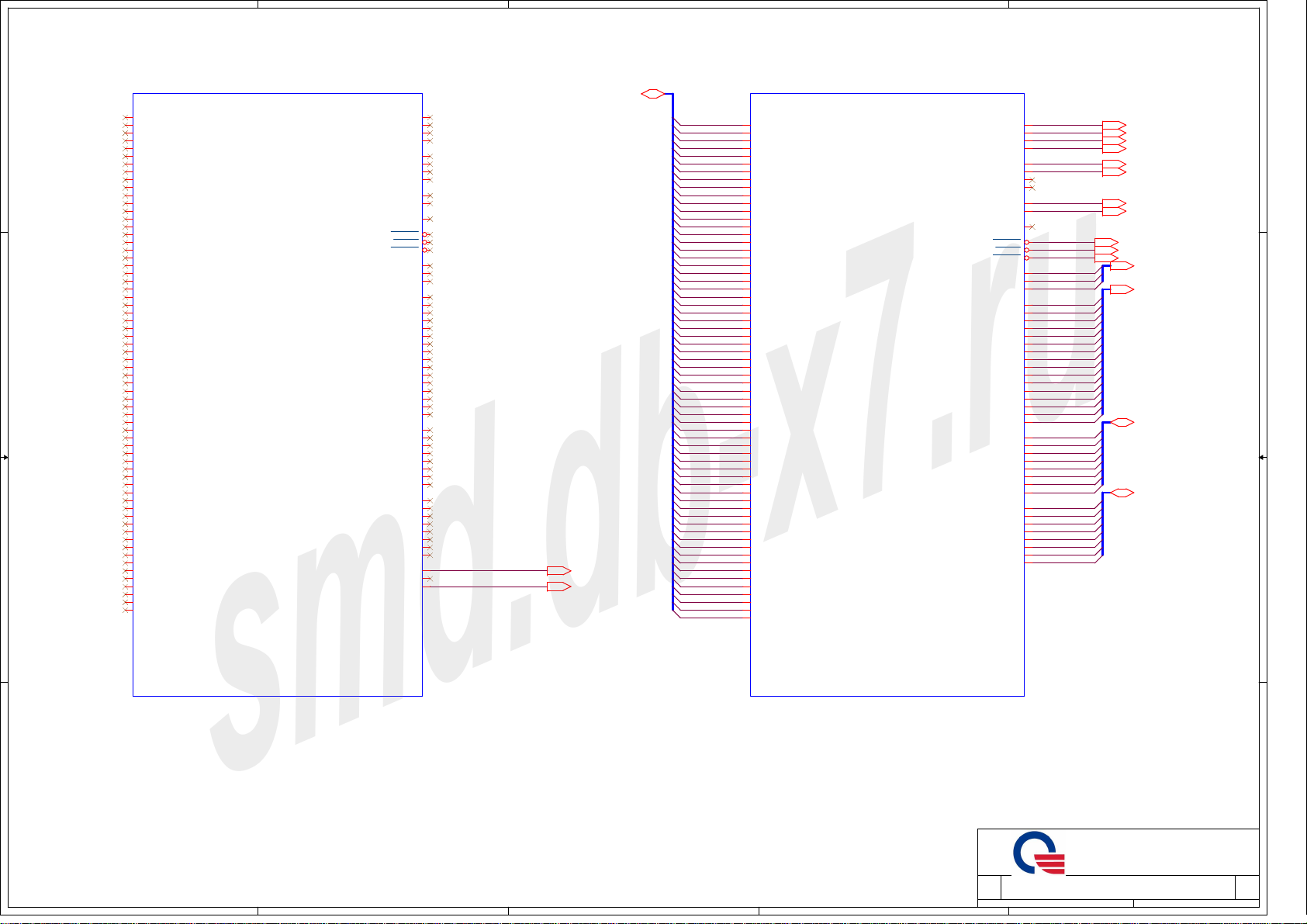

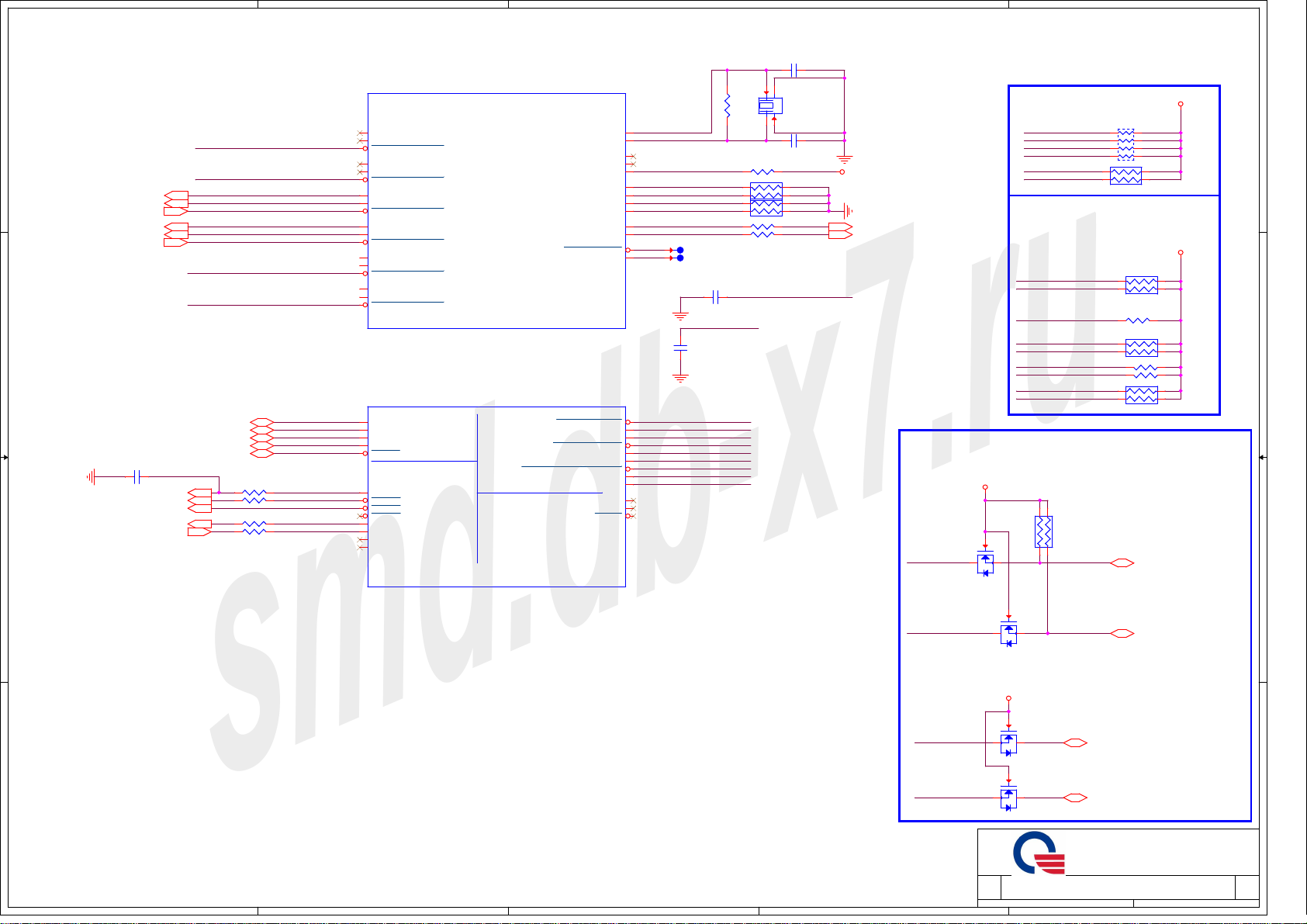

ZM3 BLOCK DIAGRAM

A A

DDR3L SO-DIMMx1

8GB(Max)

PAGE 19 PAGE 20

HDD Conn

2.5" 7,0mm

HP+MIC

Combo Jack x1

(left)

B B

Speaker Conn x2

PAGE 25

PAGE 25

Audio Codec

Camera*1 /DMIC CONN

(Front)

C C

Touch PAD CONN

PAGE 34

PS/2

ALC3223

PAGE 30

PAGE 25

PAGE 21

KBC

Keyboard CONN

THERMAL IC

NCT7718W

PAGE 34

PAGE 36

ITE 8528E

PAGE 32

1333 /1600 MT/S

SATA 6Gb/S

HDA

USB2.0

I2C

LPC

TPM

PAGE 31

HSPI

Haswell ULT

15W

DC+GT2 / GT3

Lynx Point LP

MCP 1168pins

iPTT

40 mm X 24 mm

SPI

SPI ROM

64Mbit

PAGE 33

24MHz

PAGE 7~18

32.768KHz

eDP(x1 lanes) eDP to LVDS

PS8620

DDI

USB2.0

USB2.0/USB3.0

HDMI CONN

Touch Panel CONN

USB3.0 port x2

(left)

PAGE 22

PAGE 29

IO board

USB2.0

USB2.0

PCIE

USB2.0

PCIE

USB2.0 port x1

(Right)

Card Reader

RTL5176E

GIGA LAN

RTL8111GUS

Bluetooth

WiFi

PAGE 31

lvds single link

SD CONN Only

(Right)

RJ45

Panel CONN

1366X768(HD)

(Right)

PAGE 21

D D

1

2

PWM FAN

PAGE 36

SPI ROM

64Mbit

PAGE 33

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

4

5

6

Thursday, July 18, 2013

7

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZM3

ZM3

ZM3

1 47

1 47

1 47

3A

3A

3A

8

1

smd.db-x7.ru

2

3

4

5

6

7

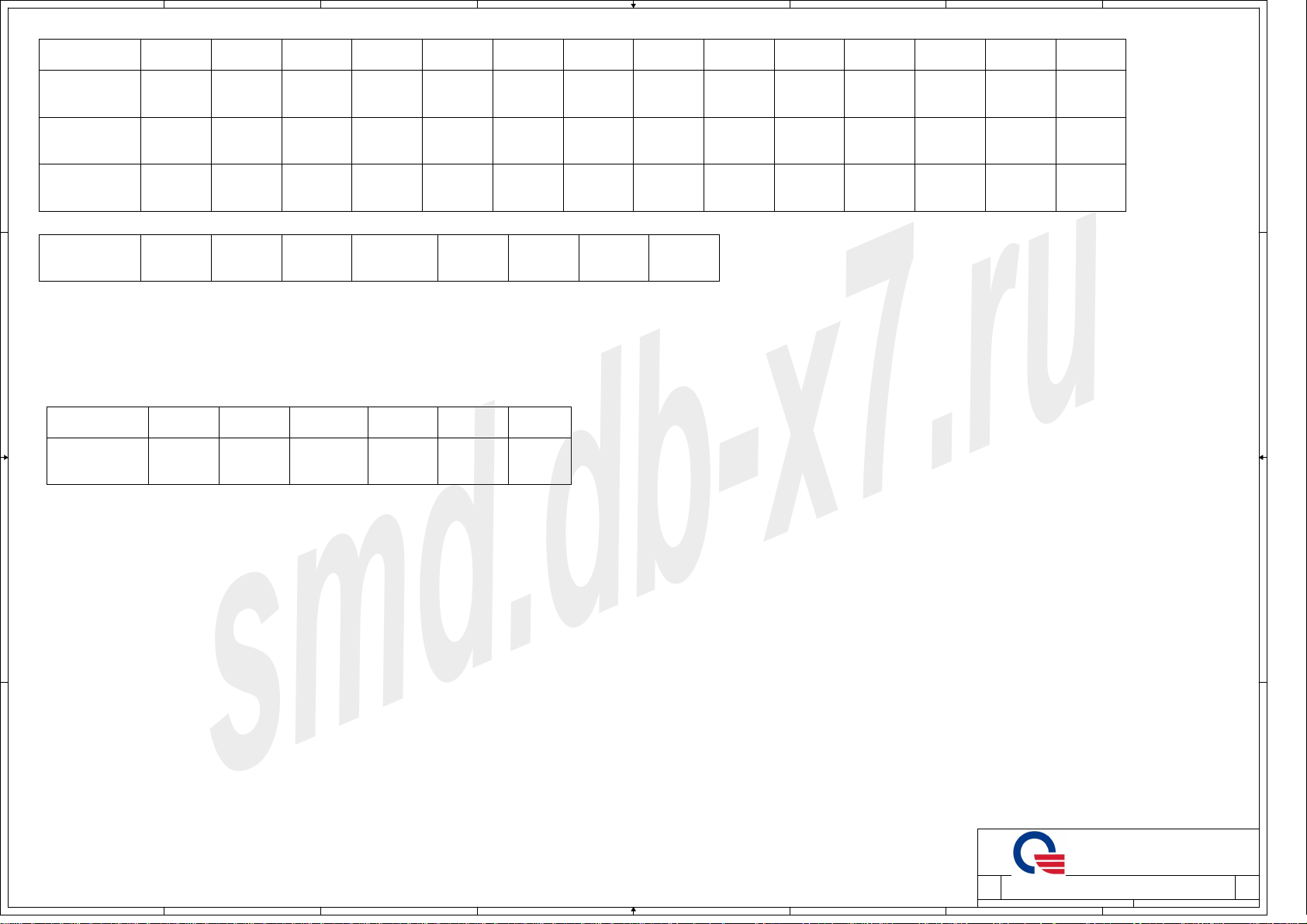

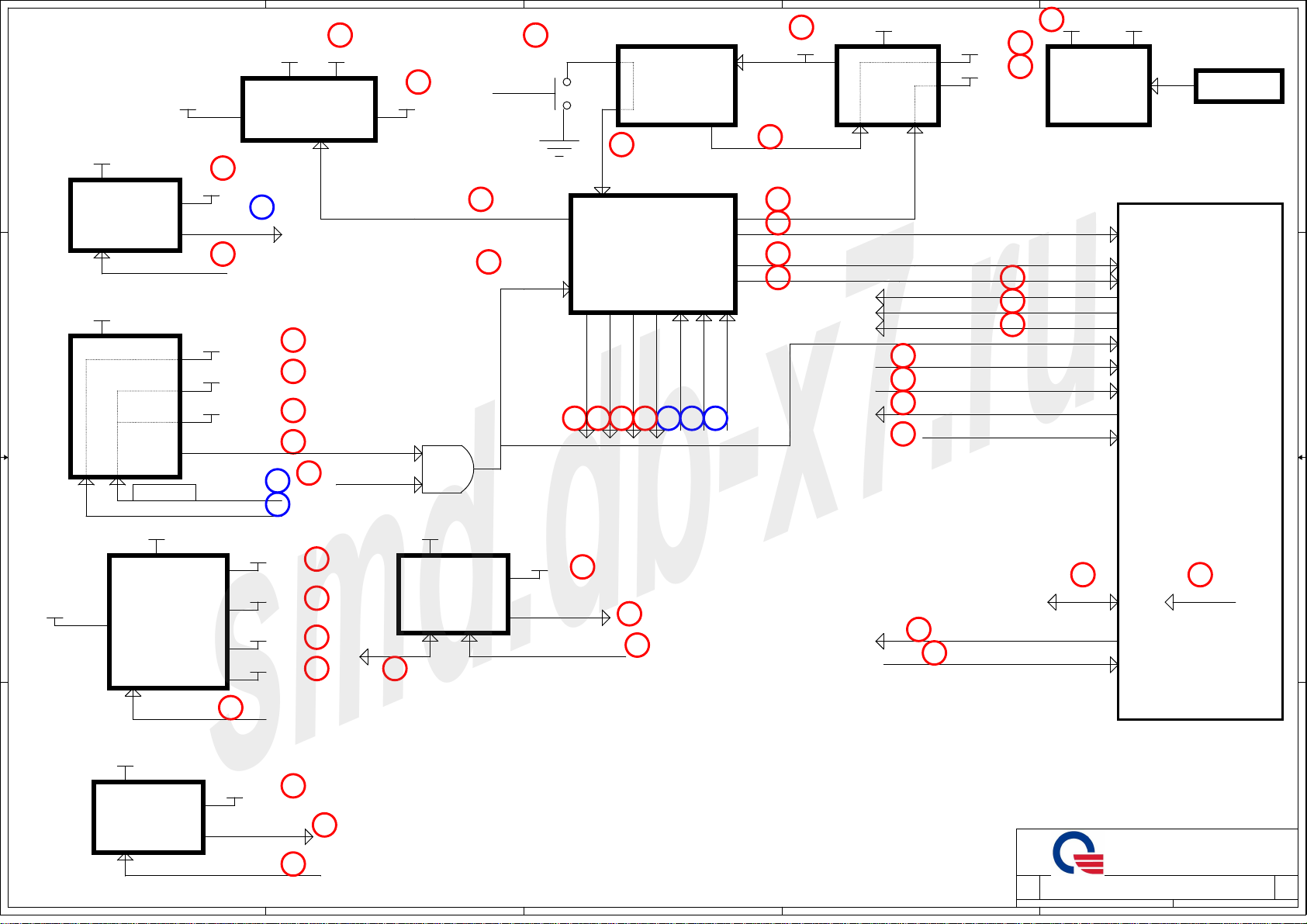

HSIO Port 1 2 3 4 5 6 7 8 9 10 11 12 13 14

8

USB3.0

A A

USB3_1

Port 1

USB3_2

Port 2

PCIE

SATA

USB2.0

B B

USB2_0

Port 1

USB2_1

Port 2

USB3_3

X

PCIE1

X

USB2_2

Port 3

USB3_4

X

PCIE2

X

USB2_3

Cardreader

PCIE3

GIGA LAN

USB2_4

Camera

PCIE4

WIFI

USB2_5

X

PCIE5

X

USB2_6

BT

PCIE5

X

USB2_7

Touch

Panel

PCIE5

X

PCIE5

X

PCIE6

X

SATA3

X

PCIE6

X

SATA2

X

PCIE6

X

SATA1

HDD

PCIE6

X

SATA0

X

CLK:

Port 1 2 3 4 5

CLK

0

CLK0

X

CLK1

X

CLK2

GIGA LAN

CLK3

WIFI

CLK4

X

CLK5

X

C C

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013 2 47

Date: Sheet of

Thursday, July 18, 2013 2 47

Date: Sheet of

1

2

3

4

5

6

Thursday, July 18, 2013 2 47

7

PROJECT :

PORT ASSIGNMENT

PORT ASSIGNMENT

PORT ASSIGNMENT

ZM3

3A

3A

3A

8

1

smd.db-x7.ru

2

3

4

5

6

7

8

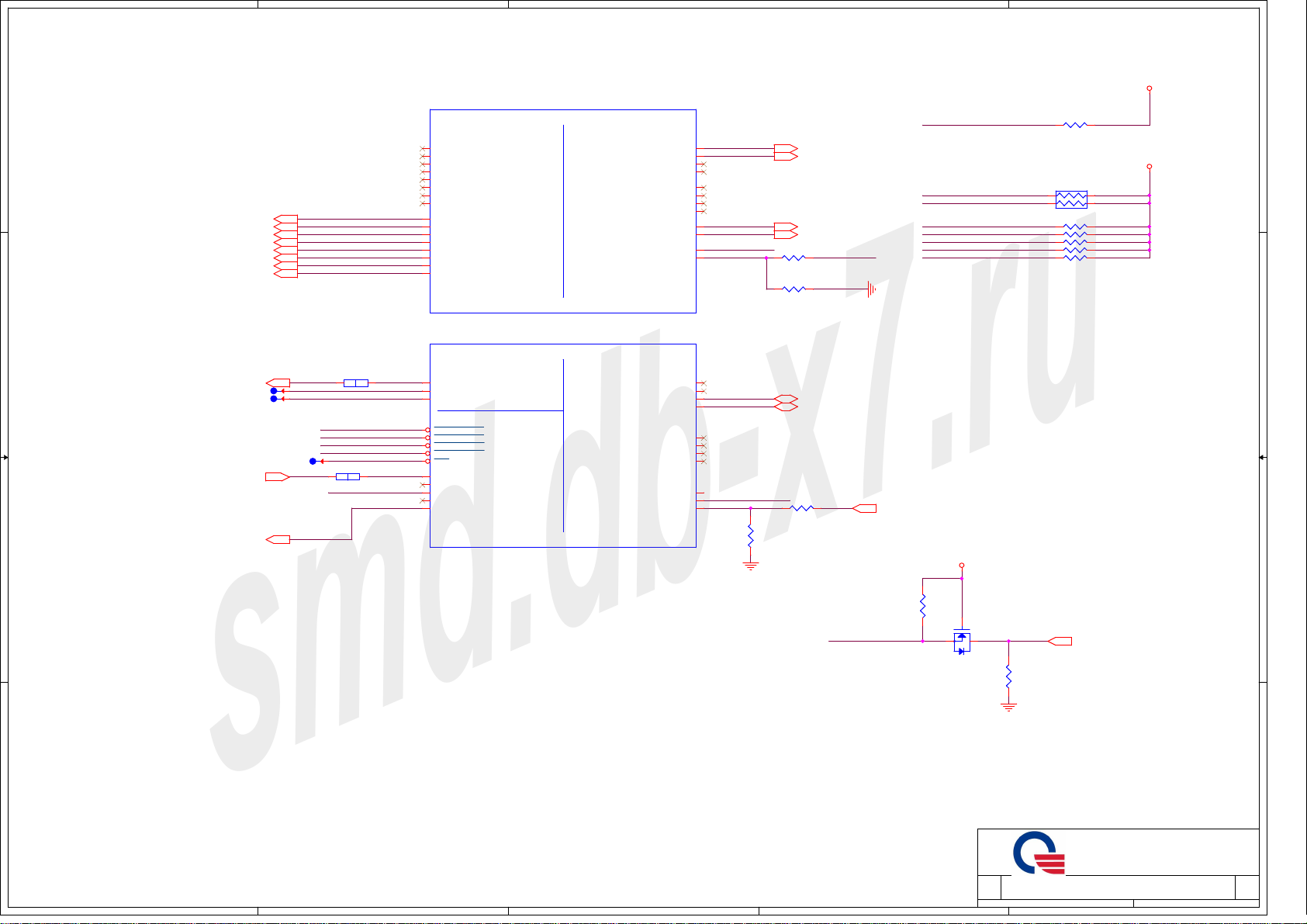

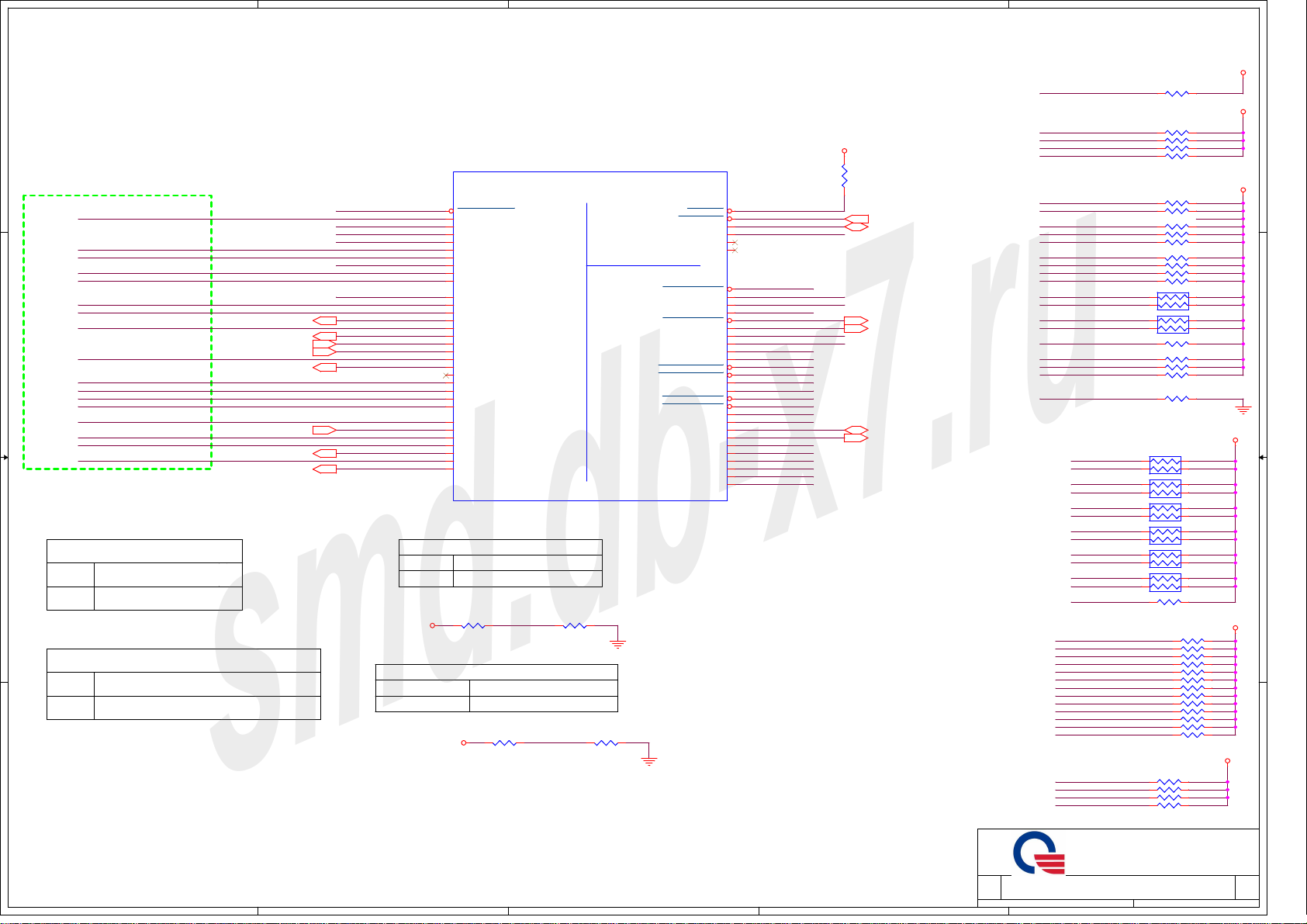

+3.3V_SUS

MB

2.2K2.2K

SMBCLK

AP2

SMBDATA

A A

AH1

+3.3V_SUS

+3.3V_RUN

DMN66D0LDW

DMN66D0LDW

SMB_PCH_SCLK

SMB_PCH_DAT

+3.3V_RUN

Touchpad

2.2K2.2K

SODIMM

Haswell

ULT

SMB_CLK0

AN1

SMB_DAT0

AK1

+3.3V_SUS

B B

AU3

SMB_CLK_ME1

AH3

SMB_DATA_ME1

+3.3V_ALW

2.2K2.2K

2.2K2.2K

AddressIC

00010010 (0x12h)OZ8618NL

SMBUS

Function

Thermal IC

Charge IC

Battery

NCT7718 1001100xb (98h)

Battery 00010110 (0X16h)

2.2K2.2K

MB

C C

SIO

ITE8528E

SMBDAT1

115

SMBCLK1

116

110

SMBCLK0

111 SMBDAT0

94

SMBCLK3

95

SMBDAT3

+3.3V_ALW

2.2K2.2K

+3.3V_RUN

2.2K2.2K

D D

1

2

+3.3V_SUS

DMN66D0LDW

DMN66D0LDW

330

330

0

0

V3.3_THERMAL

3

MOS

MOS

5

6

10

11

Battery

Charger

8

7

20

21

4

THERMAL(NCT7718)

eDP to LVDS

PS8620

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

6

7

Thursday, July 18, 2013

PROJECT :

SMBUS

SMBUS

SMBUS

ZM3

ZM3

ZM3

3 47

3 47

3 47

8

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

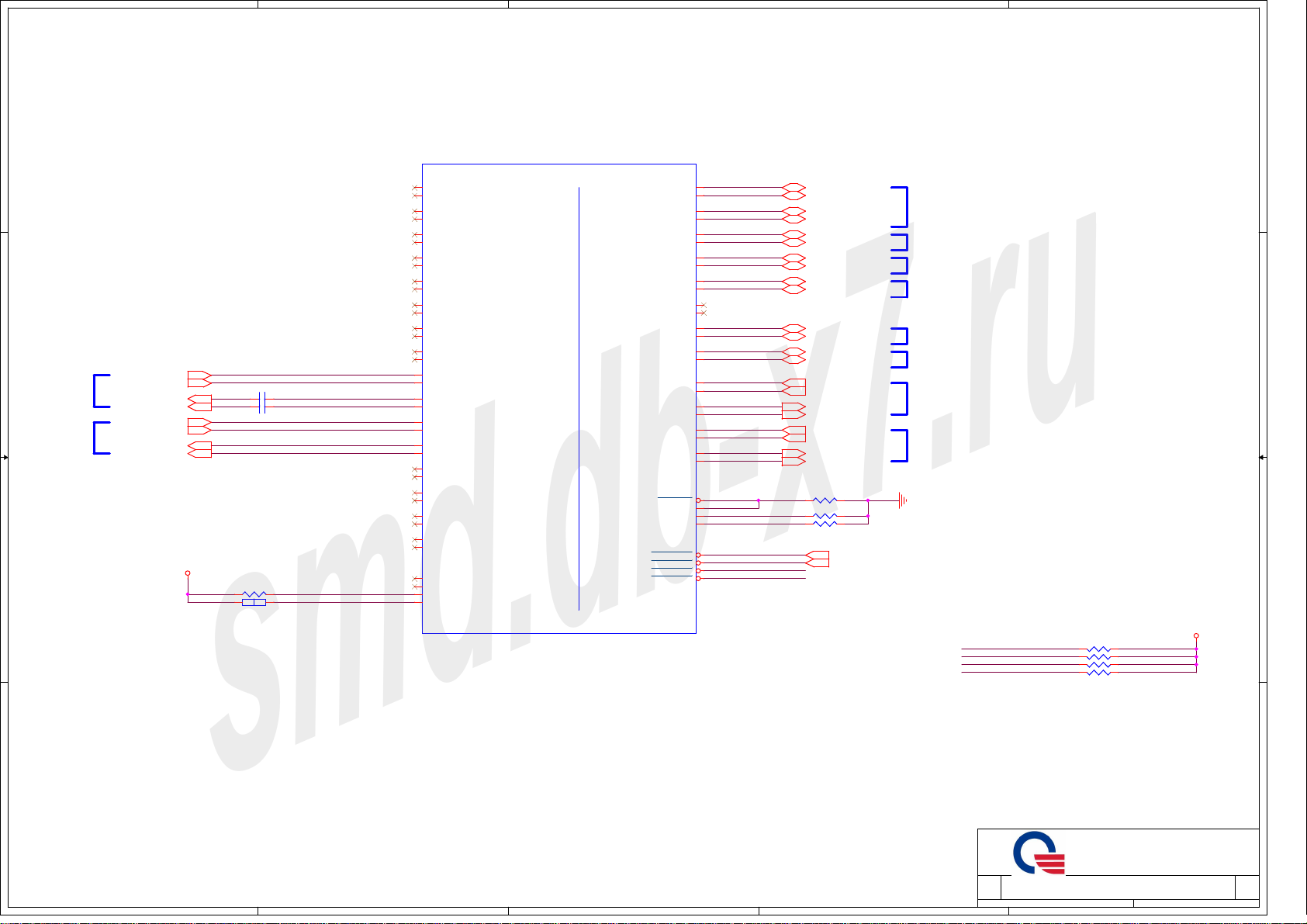

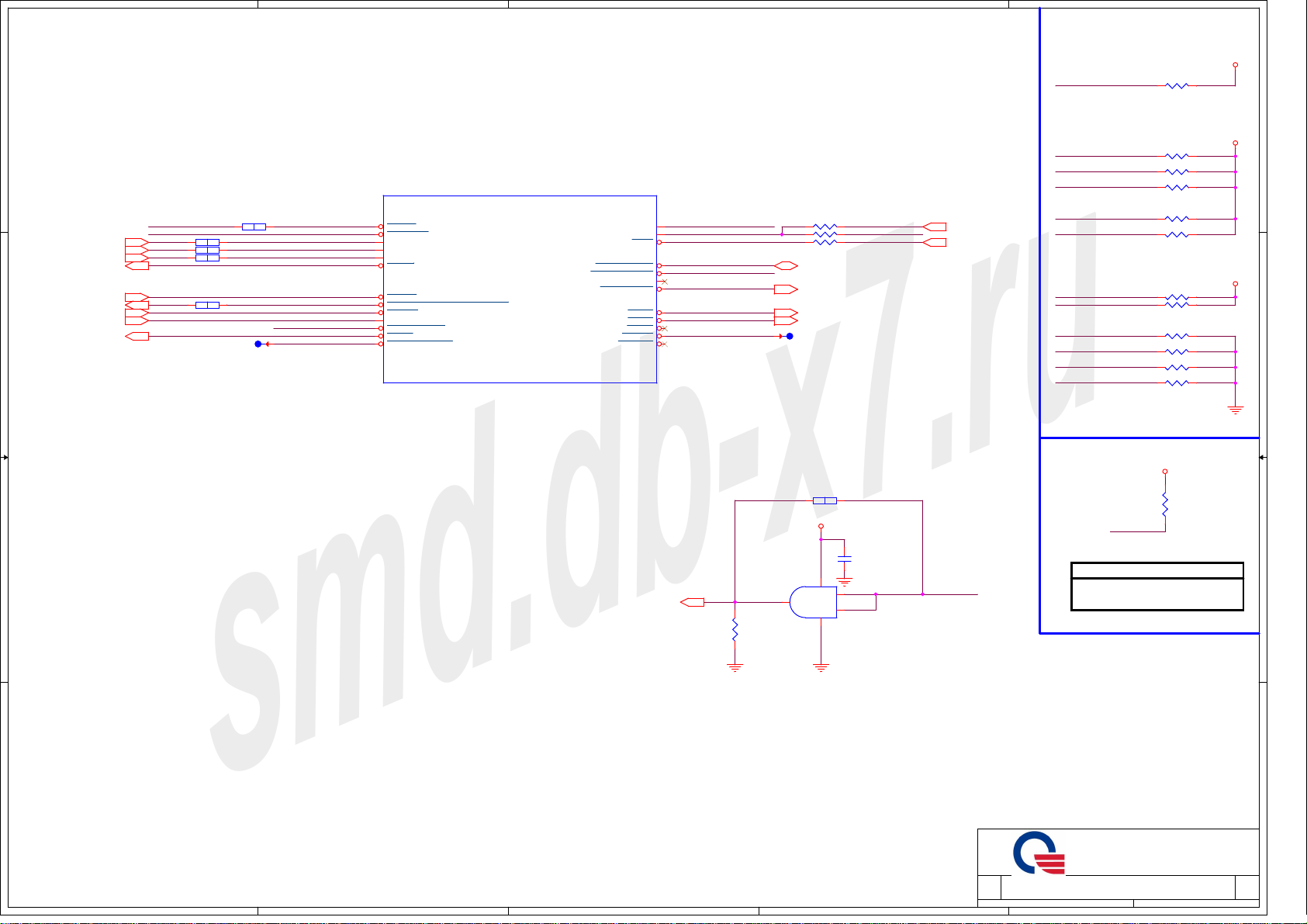

Adapter 65W

Charger

(BQ24715RGRR)

D D

Battery 3S1P

+3.3V_EN2 ALW_ON

C C

SUS_ON

B B

+PWR_SRC

TI

TPS51275RUKR

+3.3V_ALW

Load Switch

TPS22966DPUR

RUN_ON

+5V_ALW

+10V_ALW

SUS_ON

Load Switch

TPS22966DPUR

SLP_S4#

TI

TPS51362RVER

+V_VDDQ_VR

RUN_ON

TI

TPS51206DSQR

+0.6V_DDR_VTT

RUN_ON

RichTek

RT8068AZQW

+1.5V_RUN

DDR_PG_CTRL

MODPHY_EN

SLP_S4#

TI

TPS51362RVER

+1.05V_SUS

Load Switch

TPS22966DPUR

+1.05V_RUN+V1.05DX_MODPHY

RUN_ON

TI

TLV62130RGTR

+1.8V_SUS

Load Switch

TPS22965DSGR

+1.8V_RUN

VER : 1A

SLP_S4#

RUN_ON

IMVP_VR_ON

ON

NCP81101MNTWG

+VCCIN

+3.3V_SUS

A A

5

+3.3V_RUN

+5V_RUN+5V_SUS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013 4 47

Date: Sheet of

Thursday, July 18, 2013 4 47

Date: Sheet of

4

3

2

Thursday, July 18, 2013 4 47

PROJECT :

Power Block Diagram

Power Block Diagram

Power Block Diagram

ZM3

ZM3

ZM3

1

3A

3A

3A

5

smd.db-x7.ru

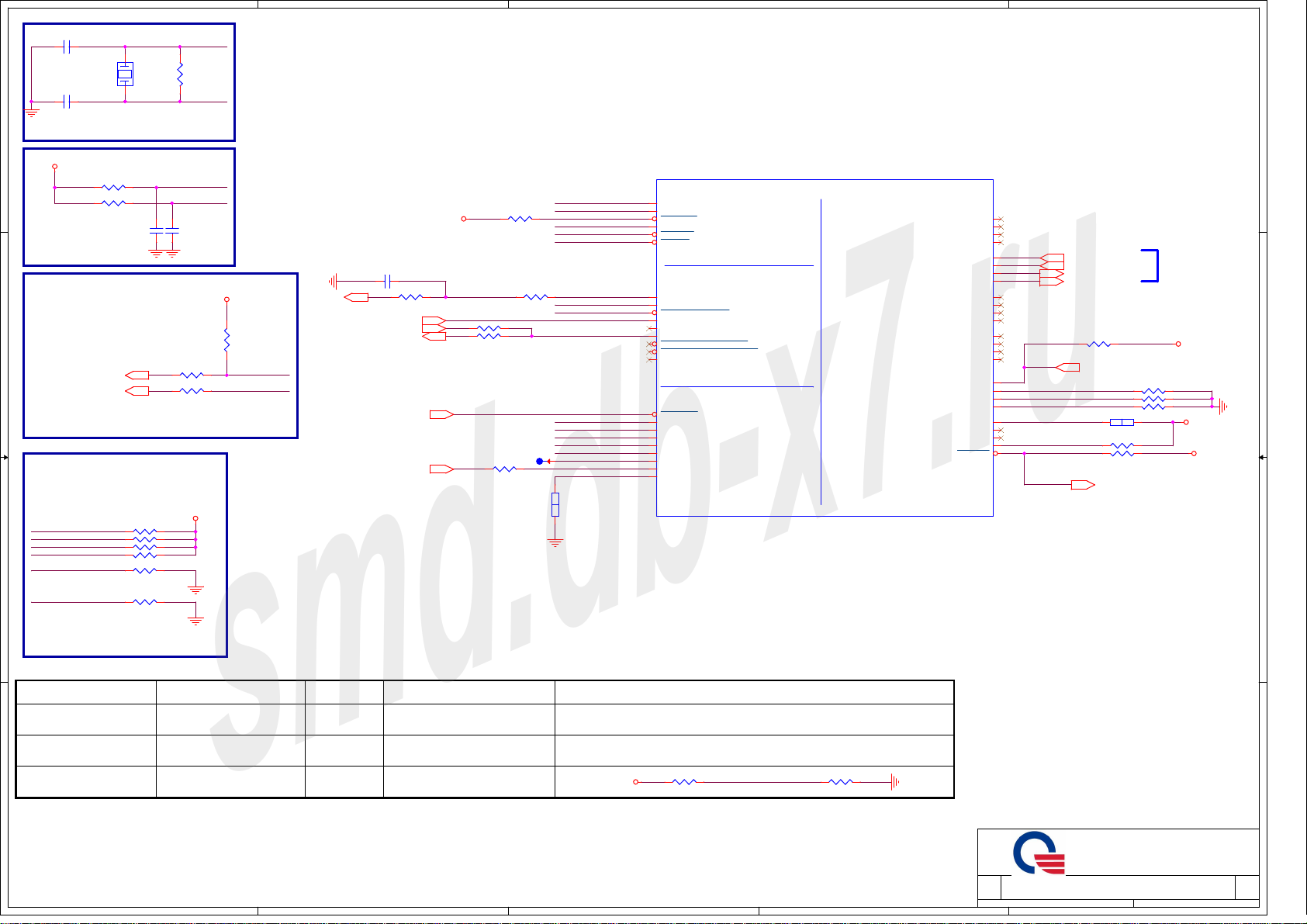

Battery Mode

+VAD +12V_ALW

+5V_ALW

D D

+PWR_SRC

+1.05V_SUS

1.05V

VR

EN

+PWR_SRC

C C

DDR/VTT

VR

S3

S4

RC Delay

+VAD

B B

+5V_ALW

+3.3V_ALW

+1.05V_SUS

+V_VDDQ

RUN MOS

SW ( IC )

G

1.05V_PWRGD

PG

+3.3V_SUS

+V_VDDQ

+DDR_VTTREF

+DDR_VTT

DDR_PWRGD

PG

SIO_SLP_S3#

SIO_SLP_S4#

SUS MOS

SW ( IC )

10

11

9

19

20

21

22

17

16

+5V_RUN

+3.3V_RUN

+1.35V_RUN

+1.05V_RUN

2

G

28

1.5V_RUN_PWRGD

24

25

26

27

4

9

+3.3V_SUS

SVID

35

SUS_ON

+PWR_SRC

IMVP

VR

LATCH

(POWER_SW_IN0#)

8

29

PG

EN

3

HWPG

+VCCIN

IMVP_PWRGD

H_VR_ENABLE_MCP

CPU

36

32

3

2

+3.3V_RTC_LDO

+PWR_SRC

3V/5VPWR

BTN

EN2

3.3V_ALW_ON

6

SYS_PWR_SW#

(S5 start point.

(Only available when S5 -> S0)

EC

SYS_PWROK

23

RUN_ON

30 30

EC_PWROK

VCCST_PWRGD#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

151617

4

6

ALW_ON

12

RSMRST#

13

AC_PRESENT

SIO_PWRBTN#

14 15

2

1

+3.3V_ALW

+5V_ALW

VR

EN1

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

30

EC_PWROK

30

VCCST_PWRGD#

37

PLTRST#

SYS_PWROK

36

EC_PWROK to SYS_PWROK delay 5-99mS

5

7

CHARGER

16

17

1

+VCHGR+PWR_SRC

Battery

DPWROK

ACPRESENT

PWRBTN#

SLP_S5#

SLP_S4#

SLP_S3#

APWROK

PCH_PWROK

VCCST_PWRGD

PLTRST#

SYS_PWROK

Haswell ULT

35 34

33

31

31

H_VR_ENABLE_MCP

33

IMVP_PWRGD

SVID

VR_EN

VR_READY

MCP

CPUPWRGOOD

23

RUN_ON

+5V_ALW

A A

1.5V

VR

EN

5

1.5V_RUN_PWRGD

PG

+1.5V_RUN

RUN_ON

25

23

28

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013 5 47

Date: Sheet of

Thursday, July 18, 2013 5 47

Date: Sheet of

4

3

2

Thursday, July 18, 2013 5 47

PROJECT :

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

ZM3

3A

3A

3A

1

5

smd.db-x7.ru

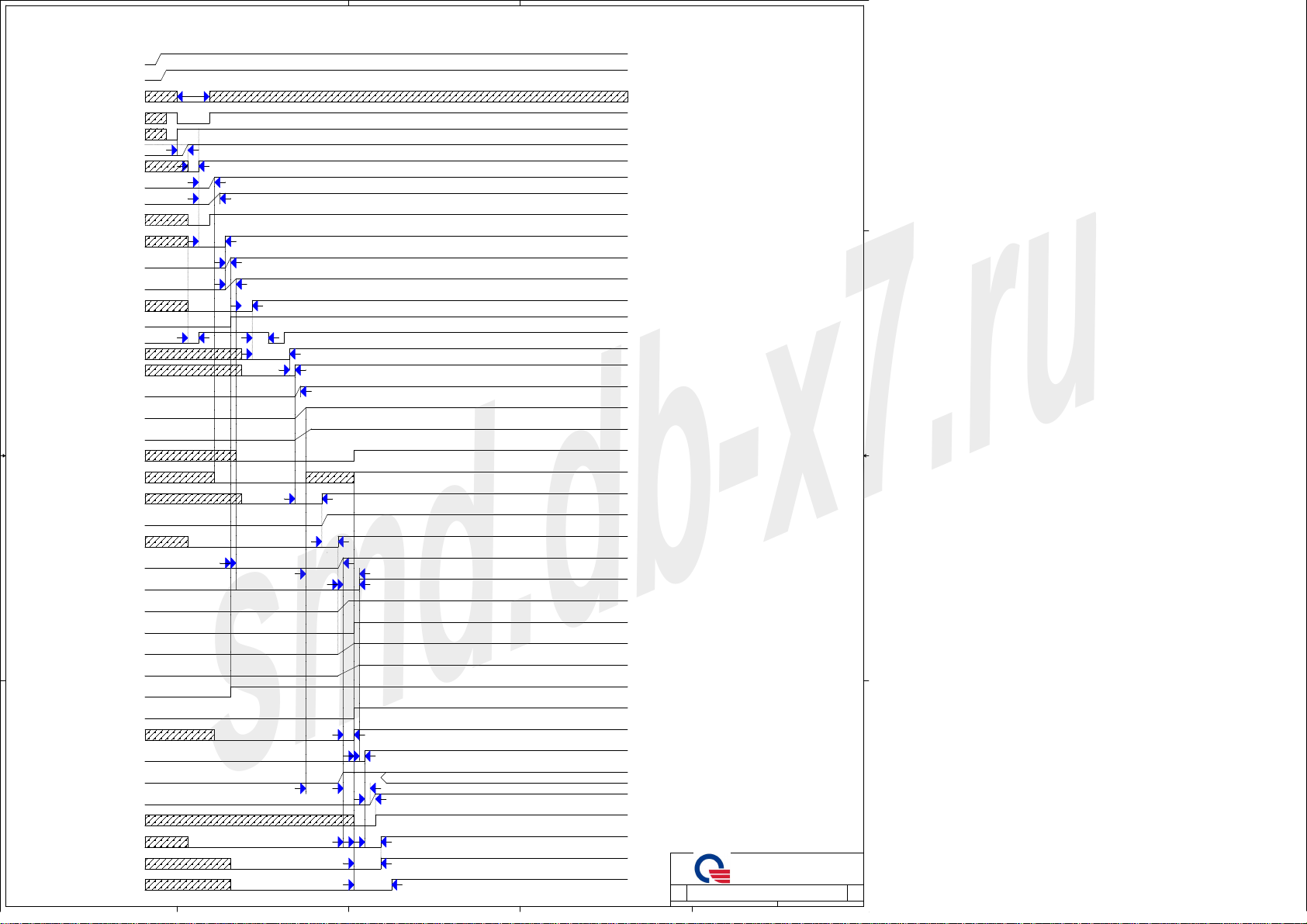

R0E Power Sequence

4

3

Shark Bay ULT PSS, 490828, Rev1.1

2

1

(G3 to S0)

+PWR_SRC

+5V_ALW2 and +3.3V_RTC_LDO

POWER_ SW_IN0#

D D

+3.3V_SUS

(PCH MCU on)(VCCDSW)

RSMRST#(EC)

(DPWROK, suspend power well)

C C

+1.05V_RUN

(VccCorePCH, VCCST, VCCASW)

B B

VCCST_PWRGD(EC)

HWPG

(APWROK, ALL_SYS_PWRGD)

A A

CPU SVID BUS(CPU)

+VCCIN

(VCCIN- CPU CORE)

EC_PWROK(EC)

(PCH_PWROK(PWROK))

LATCH

3.3V_ALW_ON

+3.3V_ALW

(EC on)

ALW_ON(EC)

+5V_ALW

+10V_ALW

SYS_PWR_SW#

SUS_ON(EC)

+5V_SUS

SUSACK#(PCH IPU)

SIO_PWRBTN#(EC)

SIO_SLP_S5#(PCH)

SIO_SLP_S4#(PCH)

+1.05V_SUS

+V_VDDQ_VR

(VDDQ)

+1.8V_SUS

(VDD1)

1.05V_PWRGD

1.2V_SUS_PWRGD

SIO_SLP_S3#(PCH)

+0.6V_DDR_VTT

RUN_ON(EC)

+1.5V_RUN

1.5V_RUN_PWRGD

+3.3V_RUN

+5V_RUN

SIO_EXT_SCI#

SIO_EXT_SMI#

IMVP_VR_ON(EC)

(VR_EN)

IMVP_PWRGD

(VR_READY)

SYS_PWROK

PLTRST#(PCH)

5

G3 mode: > EC reset time + output ALW_ON

S5 mode: > Power button DE-BOUNCE time

G3 mode: Asserted by HW latch of power button event

S0 mode: Be keeped on high by ALW_ON

? ms (3.3_ALW_ON to +3.3V_ALW)

? ms (EC, EC reset time about 50.4ms, 1650 Tick*(1/32.768K))

? ms (ALW_ON to +5V_ALW)

? ms (ALW_ON to +10V_ALW)

G3 mode: EC don't care this event.

S5 mode: Upon power always exist, and this pin keeped on high. Start from this event.

500us

? ms (EC, ALW_ON to SUS_ON, EC)

? ms (SUS_ON to +3.3_SUS)

? ms (SUS_ON to +5V_SUS)

? ms (+3.3V_SUS to RSMRST#, t05=min 10ms)

(VCCDSW (+3.3V_SUS) to DPWROK (RSMRST#), t04=min 10ms)

For a non-DeepSx system SUS_ACK# will rise with +3.3V_SUS due to weak internal pull-up

? ms(EC, RSMRST# (DPWROK) to SIO_PWRBTN#)

minimum duration of PWRBTN# assertion=16ms. PWRBTN# can assert before or after than RSMRST#

? ms (RSMRST# to SLP_S5, t07=min 5ms)

? us (SIO_SLP_S5# to SIO_SLP_S4#, t09=min 30us)

? us (SIO_SLP_S4# to SIO_SLP_S3#, t10=min 30us)

4

(For a non-DeepSx system, DPWROK and RSMRST# go high at the same time)

Be keeped on low by tied to 1.5V_RUN_PWRGD during this OD period.

? ms (EC, SLP_S3# to RUN_ON)

? ms (VccSUS (+3.3_SUS) to VccASW (+1.05V_PCH), t29= min 0ms)

? ms (VCCSUS to VccCorePCH (+1.05V_SUS), t31=min 0ms)

? ms (VDDQ (+V_VDDQ_VR) to VCCST_PWRGD, tCPU01=min 1ms)

? ms(VCCST (+1.05V_RUN) to VCCST_PWRGD, tCPU00=min 1ms)

? ms (EC, RUN_ON to VCCST_PWRGD)

? ms (VCCASW (+1.05V_RUN) to APWROK (HW PG), t11=min 1ms)

? ms (VCCST_PWRGD to VR_EN (IMVP_VR_EN), tCPU05=max 100ns)

? ms (EC, HWPG to IMVP_VR_ON)

? ms(VDDQ (+V_VDDQ_VR) ramping&stable to VCCIN ramping, tCPU03=min 100ns)

? ms(VCCST (+1.05V_RUN) ramping&stable to VCCIN ramping, tCPU04=min 100ns)

valid

? ms(VR_EN (IMVP_VR_EN) asserted until VCCIN ramped to Vboot, tCPU07=max 2.5ms)

? ms(VccCorePCH (+1.05V_RUN) stable to PWROK (EC_PWROK), t41= min 5ms)

? ms(ALL_SYS_PWRGD (HWPG) to PWROK (EC_PWROK), t14= min 5ms)

? ms(APWROK (HWPG) to PWROK (EC_PWROK), t30= min 0ms)

? ms (EC, IMVP_VR_ON to EC_PWROK)

? ms(ALL_SYS_PWRGD (HWPG) to SYSPWROK, t15= min 99ms)

? ms(ALL_SYS_PWRGD (HWPG) to PLTRST#, tULT14=max 99ms)

S0G3

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013 6 47

Date: Sheet of

Thursday, July 18, 2013 6 47

Date: Sheet of

2

Thursday, July 18, 2013 6 47

PROJECT :

G3 to S0

G3 to S0

G3 to S0

ZM3

1

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

Haswell ULT (DISPLAY)

+VCCIOA_OUT

U12A

D D

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

INT_HDMI_TXN222

INT_HDMI_TXP222

INT_HDMI_TXN122

INT_HDMI_TXP122

INT_HDMI_TXN022

INT_HDMI_TXP022

INT_HDMI_TXCN22

INT_HDMI_TXCP22

INT_HDMI_TXN2

INT_HDMI_TXP2

INT_HDMI_TXN1

INT_HDMI_TXP1

INT_HDMI_TXN0

INT_HDMI_TXP0

INT_HDMI_TXCN

INT_HDMI_TXCP

C51

C50

C53

B54

C49

B50

A53

B53

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

HSW_ULT_DDR3L

1 OF 19

EDP_COMP

C45

EDP_TXN0

B46

EDP_TXP0

A47

EDP_TXN1

B47

EDP_TXP1

C47

EDP_TXN2

C46

EDP_TXP2

A49

EDPDDI

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

B49

A45

B45

D20

A43

EDP_AUXN

EDP_AUXP

EDP_COMP

EDP_TXN0 20

EDP_TXP0 20

EDP_AUXN 20

EDP_AUXP 20

R301 *0_4_NC

R300 *0_4_NC

HDMI_SCL

HDMI_SDA

PIRQ_GPIO77

PIRQ_GPIO78

PIRQ_GPIO80

LCD_PW MDP_UTIL

PIRQ_GPIO79

DGPU_PW R_EN

R91 24.9/F_4

RP11 2.2KX2

R39 10K_4

R40 10K_4

R240 10K_4

R250 10K_4

R42 10K_4

2

1

4

3

+3.3V_RUN

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

U12I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

9 OF 19

+3V

+3V

+3V

+3V

+3V

C C

LCD_PW M20

T4

T27

SMB_INT#34

THERMAL_STP#_CTRL36

B B

R269 SJ_0402

T2

R34 SJ_0402

2

112

PIRQ_GPIO77

PIRQ_GPIO78

PIRQ_GPIO79

PIRQ_GPIO80

PCI_PME_N

2

112

DGPU_PW R_EN

eDP SIDEBAND

+3V

+3V

+3V

+3V

PCIE

HSW_ULT_DDR3L

DISPLAY

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

HDMI_SCL

HDMI_SDA

INT_HDMI_HPD

EDP_HP_R

12

HDMI_SCL 22

HDMI_SDA 22

need check have VGA function

R83 1K_4

R85

100K_4

EDP_HP 20

INT_HDMI_HPD

1M_4

R217

+3.3V_RUN

2

Q25

2N7002W

31

12

R214

20K/F_4

INT_HDMI_HP 22

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

4

3

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 1/12

Haswell ULT 1/12

Haswell ULT 1/12

1

ZM3

ZM3

ZM3

7 47

7 47

7 47

3A

3A

3A

5

smd.db-x7.ru

Haswell ULT (DDR3L)

4

3

2

1

U12C

AH63

SA_DQ0

D D

C C

B B

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

SM_VREF_CA

M_B_DQ[63..0]19

SM_VREF_CA 19

SM_VREF_DQ1 19

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

U12D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_CLKN0

M_B_CLKP0

M_B_CLKN1

M_B_CLKP1

M_B_CKE0

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_RAS#

M_B_WE#

M_B_CAS#

M_B_BS#0

M_B_BS#1

M_B_BS#2

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_CLKN0 19

M_B_CLKP0 19

M_B_CLKN1 19

M_B_CLKP1 19

M_B_CKE0 19

M_B_CKE1 19

M_B_CS#0 19

M_B_CS#1 19

M_B_RAS# 19

M_B_WE# 19

M_B_CAS# 19

M_B_BS#[2..0] 19

M_B_A[15..0] 19

M_B_DQSN[7..0] 19

M_B_DQSP[7..0] 19

3 OF 19

4 OF 19

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

4

3

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 2/12

Haswell ULT 2/12

Haswell ULT 2/12

1

ZM3

ZM3

ZM3

8 47

8 47

8 47

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

GPIO Pull-up/Pull-down(CLG)

+3.3V_SUS

Hasswell ULT(GPIO,LPIO,MISC)

D D

+V1.05S_VCCST

U12J

not use function pin net

GPIO8

GPIO17

GPIO24

GPIO28

TPM_RST#

SLATE_MODE_HALL_IN

SNSR_HUB_RST_ACCEL_DRDY_N

C C

DGPU_HOLD_RST#

SENSOR_HUB_INT

USB2_CAM1_PWR_EN

LPT_LAN_RST#

SNR_HUB_EN

BT_WAKE#

GPIO33

SENSOR_STANDBY_N

DEVSLP2

WLAN_ON/OFF#31 BT_RADIO_DIS# 31

LCD_DBC21

USB_MCARD1_DET#31

PCIE_MCARD1_DET#31

MODPHY_EN17

SIO_EXT_SCI#32

DEVSLP130

ACZ_SPKR25

AUDIO_PWR_EN

GPIO12

GPIO15

KB_DET#

SIO_WAKE_SCI#

LPT_CR_RST#

WLAN_ON/OFF#

LCD_DBC

USB_MCARD1_DET#

PCIE_MCARD1_DET#

MODPHY_EN

SIO_EXT_SCI#

DEVSLP1

No Reboot Strap(GPIO81)

B B

NC

PU

Default

EN

+3.3V_RUN

TLS CONFIDENTIALITY STRAP(GPIO15)

NC

PU

Default

EN

R1547

R1547_NC

+V3.3S_1.8S_LPSS_SDIO

P1

BMBUSY/GPIO76

AU2

AM7

AD6

AD5

AN5

AD7

AN3

AG6

AP1

AL4

AT5

AK4

AB6

AT3

AH4

AM4

AG5

AG3

AM3

AM2

Y1

T3

U4

Y3

P3

Y2

P2

C4

L2

N5

V2

+3V_S5

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

+3V_S5

GPIO15

+3V

GPIO16

+3V

GPIO17

+3V_S5

GPIO24

DSW

GPIO27

+3V_S5

GPIO28

+3V_S5

GPIO26

+3V_S5

GPIO56

+3V_S5

GPIO57

+3V_S5

GPIO58

+3V_S5

GPIO59

+3V_S5

GPIO44

+3V_S5

GPIO47

+3V

GPIO48

+3V

GPIO49

+3V

GPIO50

HSIOPC/GPIO71

+3V_S5

GPIO13

+3V_S5

GPIO14

DSW

GPIO25

+3V_S5

GPIO45

+3V_S5

GPIO46

+3V_S5

GPIO9

+3V_S5

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

10 OF 19

GPIO86:Boot BIOS Strap Bit

PUPDLPC

SPI (Default IPD)

R81

*1K_4_NC

GPIO66 : Top-Block Swap

ENABLE

DISABLE(Default)

R258

*1K_4_NC

BBS

+3V

+3V

+3V

+3V

+3V

+3V

HSW_ULT_DDR3L

DSW

GPIO

+3V

R78

*1K_4_NC

SDIO_D0

R262

*1K_4_NC

+3V

CPU/

MISC

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

UART0_RTS/GPIO93

SERIAL IO

+3V

UART0_CTS/GPIO94

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

R119

1K_4

D60

PCH_THRMTRIP#

V4

SIO_RCIN#

T4

IRQ_SERIRQ

AW15

PCH_OPIRCOMP DEVSLP2

AF20

AB21

R6

GSPI_CS

L6

DSP_RST#

N6

HDMI_PD#_LPT

L8

BBS

R7

L5

N7

TOUCHPANEL_EN

K2

TOUCH_PANEL_INTR#

J1

GPIO91

K3

GPIO92

J2

GPIO93

G1

GPIO94

K4

URAT1_RX

G2

URAT1_TX

J3

URAT1_RST

J4

URAT1_CTS

F2

I2C_DA0

F3

I2C_CK0

G4

I2C_DA1

F1

I2C_CK1

E3

SDIO_CK

F4

SDIO_CMD

D3

SDIO_D0

E4

SDIO_D1

C3

SDIO_D2

E2

SDIO_D3

SIO_RCIN# 32

IRQ_SERIRQ 32

EC_CS_EXT 32

I2C_DA1 34

I2C_CK1 34

A A

SIO_WAKE_SCI#

LCD_DBC

GPIO12

SIO_EXT_SCI#

GPIO15

DGPU_HOLD_RST#

PCIE_MCARD1_DET#

DEVSLP1

SIO_RCIN#

AUDIO_PWR_EN

USB_MCARD1_DET#

GSPI_CS

IRQ_SERIRQNFC_IRQ_R

GPIO91

GPIO92

GPIO93

GPIO94

HDMI_PD#_LPT

DSP_RST#

TOUCH_PANEL_INTR#

TOUCHPANEL_EN

PCH_OPIRCOMP

I2C_DA0

I2C_CK0

I2C_DA1

I2C_CK1

URAT1_RX

URAT1_TX

URAT1_RST

URAT1_CTS

SDIO_CK

SDIO_CMD

SDIO_D1

SDIO_D2

SDIO_D3

GPIO8

GPIO24

GPIO28

NFC_IRQ_R

SENSOR_HUB_INT

LPT_CR_RST#

TPM_RST#

SLATE_MODE_HALL_IN

SNSR_HUB_RST_ACCEL_DRDY_N

LPT_LAN_RST#

SNR_HUB_EN

BT_WAKE#

USB2_CAM1_PWR_EN

KB_DET#

GPIO17

GPIO33

SENSOR_STANDBY_N

R73 10K_4

R23 10K_4

R84 10K_4

R244 10K_4

R30 10K_4

R27 10K_4

R227 10K_4

R239 *10K_4_NC

R26 *10K_4_NC

R35 10K_4

R235 *4.7K_4_NC

R29 10K_4

R28 10K_4

R36 10K_4

2

4

4

2

3

1

3

1

3

1

1

3

3

1

3

1

R246 10K_4

R21 10K_4

R20 10K_4

R236 10K_4

R53 10K_4

R51 10K_4

R242 10K_4

R62 10K_4

R253 10K_4

R19 10K_4

R54 10K_4

R68 10K_4

R64 10K_4

1

3

3

1

RP18 10KX2

RP17 10KX2

R24 10K_4

R22 *10K_4_NC

R41 10K_4

R25 10K_4

R286 49.9/F_4

4

RP7 10KX2

2

4

RP6 10KX2

2

4

RP2 10KX2

2

RP3 10KX2

2

4

4

RP8 10KX2

2

4

RP10 10KX2

2

R254 10K_4

R230 10K_4

R31 10K_4

R249 10K_4

R265 10K_4

+3.3V_SUS

+3.3V_RUN

+3.3V_RUN

+3.3V_SUS

+3.3V_RUN

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

4

3

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 3/12

Haswell ULT 3/12

Haswell ULT 3/12

1

ZM3

ZM3

ZM3

9 47

9 47

9 47

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

D D

C C

PCIE_RXN324

GIGA LAN

WIFI

B B

PCIE_RXP324

PCIE_TXN324

PCIE_TXP324

PCIE_RXN431

PCIE_RXP431

PCIE_TXN431

PCIE_TXP431

+V1.05S_AUSB3PLL

1 2

C232 0.1U/16V/X7R_4

1 2

C233 0.1U/16V/X7R_4

1 2

R98 3K/F_4

R97 SJ_0402

112

2

PCIE_TXN3_C

PCIE_TXP3_C

PCIE_RCOMP

PCIE_IREF

Haswell ULT (PCIE,USB)

U12K

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

11 OF 19

HSW_ULT_DDR3L

PCIE USB

+3V_S5

+3V_S5

+3V_S5

+3V_S5

USB2N0

DSW

USB2P0

USB2N1

DSW

USB2P1

USB2N2

DSW

USB2P2

USB2N3

DSW

USB2P3

USB2N4

DSW

USB2P4

USB2N5

DSW

USB2P5

USB2N6

DSW

USB2P6

USB2N7

DSW

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

RSVD

RSVD

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_BIAS

USBPLLMON_N

USBPLLMON_P

USB_OC0#

USB_OC1#

USB_OC2#

GPIO43

USBP0- 29

USBP0+ 29

USBP1- 29

USBP1+ 29

USBP2- 24

USBP2+ 24

USBP3- 24

USBP3+ 24

USBP4- 21

USBP4+ 21

USBP6- 31

USBP6+ 31

USBP7- 21

USBP7+ 21

USB3.0_RX1- 29

USB3.0_RX1+ 29

USB3.0_TX1- 29

USB3.0_TX1+ 29

USB3.0_RX2- 29

USB3.0_RX2+ 29

USB3.0_TX2- 29

USB3.0_TX2+ 29

R89 22.6/F_4

R82 49.9/F_4

R86 49.9/F_4

USB_OC0# 29

USB_OC1# 24

USB3.0 COMBO (Left)

USB2.0 (Right)

Cardreader

Camara

Bluetooth

Touch Panel

USB3.0 Port

USB3.0 Port

HARRIS_BEACH_CS REV 3.0

USB_OC0#

USB_OC1#

USB_OC2#

GPIO43

1 2

R66 10K_4

1 2

R252 10K_4

1 2

R238 10K_4

1 2

R243 10K_4

+3.3V_SUS

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

4

3

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 4/12

Haswell ULT 4/12

Haswell ULT 4/12

1

ZM3

ZM3

ZM3

10 47

10 47

10 47

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

C212 15P/50V/_4

C214 15P/50V/_4

D D

+RTC_CELL

C C

12

Y1

32.768KHZ

R80 20K/F_4

R266 20K/F_4

C48

1U/6.3V_4

HDA_SYNC25

HDA_RST#25,32

PCH JTAG Debug (CLG)

MP remove(Intel)

XDP_TMS

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

XDP_TCK1

B B

RSVD_PGDMON

HARRIS_BEACH_CS REV 3.0

R318 51_4

R134 51_4

R135 51_4

R319 *1K_4_NC

R320 *51_4_NC

R87 *1K_4_NC

RTC_X1

R256

10M_4

RTC_X2

RTC_RST#

SRTC_RST#

C215

1U/6.3V_4

R277 33_4

R272 33_4

+1.05V_SUS

+3.3V_SUS

R276

*1K_4_NC

HDA_SYNC_R

HDA_RST#_R

DFXTESTMODE

HIGH - DFXTESTMODE DISABLED(DEFAULT)

LOW - DFXTESTMODE ENABLED

HDA_BITCLK25

C218 *33P/50V/NPO_4_NC

R274 33_4

HDA_SDIN025

PCH_MELOCK32

HDA_SDOUT25

XDP_TRST_CPU_N18

XDP_TCK018

12

+RTC_CELL

R77 1M_4

R273 0_4

R279 1K_4

R275 33_4

R331 *0_4_NC

T1

RTC_X1

RTC_X2

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BITCLK_RHDA_BITCLK_L

HDA_SYNC_R

HDA_RST#_R

HDA_SDOUT_R

XDP_TCK1

XDP_TDI

PCH_JTAG_TDO

XDP_TMS

RSVD_PGDMON

PM_TEST_RST_N

PCH_JTAGX

PCH_EDM

2

R237

2

SJ_0402

1

1

Haswell ULT (RTC, HDA, JTAG, SATA)

U12E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

5 OF 19

HARRIS_BEACH_CS REV 3.0

HSW_ULT_DDR3L

RTC

AUDIO SATA

JTAG

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

+3V

SATA0GP/GPIO34

+3V

SATA1GP/GPIO35

+3V

SATA2GP/GPIO36

+3V

SATA3GP/GPIO37

SATA_RCOMP

SATA_IREF

RSVD

RSVD

SATALED

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

GPIO35

V6

GPIO36

AC1

GPIO37

A12

SATA_IREF

L11

K10

C12

SATA_RCOMP

U3

PCH_SATA_LED#

SATA_RXN1 30

SATA_RXP1 30

SATA_TXN1 30

SATA_TXP1 30

1 2

R229 10K

SMC_EXTSMI_N 32

R251 10K_4

R38 10K_4

R233 10K_4

R278 SJ_0402

112

1 2

R280 3K/F_4

1 2

R225 10K_4

PCH_SATA_LED# 37

1 2

1 2

1 2

2

HDD

+3.3V_RUN

+V1.05S_ASATA3PLL

+3.3V_RUN

PCH Strap Table

Pin Name Strap description

SPKR

HDA_SDO

INTVRMEN

A A

No reboot mode setting PWROK

Flash Descriptor Security

Override / Intel ME Debug Mode

Integrated 1.05V VRM enable ALWAYS

5

Sampled

PWROK

Configuration

0 = Default (weak pull-down 20K)

1 = Setting to No-Reboot mode

0 = Security Effect (Int PD)

1 = Can be Override

Should be always pull-up

4

+RTC_CELL

note

R271 *330K_4_NC

3

PCH_INTVRMEN

R270 330K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 5/12

Haswell ULT 5/12

Haswell ULT 5/12

1

ZM3

ZM3

ZM3

11 47

11 47

11 47

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

Haswell ULT (CLK)

C228 12P/50V/_4

U12F

D D

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

CLK_PCIE_LANN24

CLK_PCIE_LANP24

PCIE_CLK_REQ2#24

CLK_PCIE_WLANN31

CLK_PCIE_WLANP31

PCIE_CLK_REQ3#31

C C

CLK_PCIE_LANN

CLK_PCIE_LANP

PCIE_CLK_REQ2#

CLK_PCIE_WLANN

CLK_PCIE_WLANP

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

6 OF 19

CLOCK

SIGNALS

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

A25

B25

K21

M21

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

XTAL24_IN

XTAL24_OUT

TESTLOW _0

TESTLOW _1

TESTLOW _2

TESTLOW _3

LPC_CLK_0

LPC_CLK_1

T5

T6

EC32 *10P/50V_4_NC

LPC_CLK_1

EC12

*22P/50V_4_NC

R95 3K/F_4

R287 22_4

R88 22_4

12

Haswell ULT (LPC/SPI/SMB/CLINK)

U12G

LPC_LAD031,32

LPC_LAD131,32

LPC_LAD231,32

LPC_LAD331,32

EC30 *10P/50V_4_NC

12

PCH_SPI_CLK33

PCH_SPI_CS0#33

PCH_SPI_CS1#33

PCH_SPI_SI33

PCH_SPI_SO33

B B

LPC_LFRAME#31,32

R50 15

R231 15

R57 15

R58 15

PCH_SPI_CS0#_R

PCH_SPI_SI_R

PCH_SPI_SO_R

AU14

AW12

AY12

AW11

AV12

AA3

AC2

AA2

AA4

AF1

Y7

Y4

Y6

LAD0

LAD1

LAD2

LAD3

LFRAME

SPI_CLK

SPI_CS0

SPI_CS1

SPI_CS2

SPI_MOSI

SPI_MISO

SPI_IO2

SPI_IO3

HSW_ULT_DDR3L

LPC

7 OF 19

SMBUS

+3V_S5

C-LINKSPI

+3V_S5

+3V_S5

+3V_S5

+3V_S5

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML1ALERT/PCHHOT/GPIO73

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

AN2

PCH_SMB_ALERT#

AP2

SMBCLK

AH1

SMBDATA

AL2

CARD_+3.3V_EN

AN1

SMB_CLK0

AK1

SMB_DAT0

AU4

GPIO73

AU3

SMB_CLK_ME1

AH3

SMB_DATA_ME1

AF2

AD2

AF4

4

3

R295

1M_4

1

2

C231 12P/50V/_4

1 2

RP19 10KX2

3

1

RP9 10KX2

1

3

1 2

1 2

Y2

24MHz

4

2

2

4

LPC_CLK_EC

+V1.05S_AXCK_LCPLL

LPC_CLK_EC 32

LPC_CLK_DEBUG 31

SMBus/Pull-up(CLG)

DMN66D0LDW-7

SMBCLK

Q28A

+3.3V_RUN

5

3 4

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

SMB_CLK0

SMB_DAT0

PCH_SMB_ALERT#

SMBCLK

SMBDATA

CARD_+3.3V_EN

GPIO73

SMB_DATA_ME1

SMB_CLK_ME1

2

4

RP15

2.2KX2

1

3

RN1 10KX4

1

2

3

4

5

6

7

8

RP1 10KX2

2

1

4

3

RP4 2.2KX2

3

1

R55 10K_4

RP16 2.2KX2

3

1

R248 10K_4

R232 10K_4

RP5 2.2KX2

1

3

SMB_PCH_CLK 19,34

+3.3V_RUN

+3.3V_SUS

4

2

4

2

2

4

DMN66D0LDW-7

SMBDATA

SMB_CLK_ME1

A A

5

4

3

SMB_DATA_ME1

2

6 1

+3.3V_SUS

5

34

Q29A

DMN66D0LDW-7

2

Q29B

DMN66D0LDW-7

61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

PROJECT :

Haswell ULT 6/12

Haswell ULT 6/12

Haswell ULT 6/12

SMBCLK1 32

SMBDAT1 32

SMB_PCH_DAT 19,34

ZM3

ZM3

ZM3

12 47

12 47

12 47

1

3A

3A

3A

2

Q28B

5

smd.db-x7.ru

4

3

2

1

Haswell ULT (SYSTEM POWER MANAGEMENT)

D D

U12H

2

ME_SUS_PWR_ACK_R

SYS_PWROK32

EC_PWROK32,36

APWROK32

RSMRST#32

ME_SUS_PWR_ACK32

SIO_PWRBTN#32

AC_PRESENT32

C C

SLP_S0#32

R226 SJ_0402

R268 SJ_0402

R33 SJ_0402

R59 SJ_0402

R63 SJ_0402

2

112

2

112

2

112

2

112

T3

112

SUSACK#_R

SYS_PWROK_R

EC_PWROK_R

APWROK_R

PLTRST#

RSMRST#

ME_SUS_PWR_ACK_R

SIO_PWRBTN#

AC_PRESENT

PM_BATLOW#

PCH_SLP_WLAN#

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

DSW

DSW

DSW

DSW

+3V_S5

DSW

8 OF 19

+3V

+3V_S5

+3V_S5

DSW

DSWVRMEN

DPWROK

DSW

WAKE

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

DSW

SLP_S4

DSW

SLP_S3

DSW

SLP_A

DSW

SLP_SUS

DSW

SLP_LAN

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

DSWVRMEN

DPWROK_RSYS_RESET#

PCIE_WAKE#_R

CLKRUN#

TPM_LPC_PD

1 2

R259 *0_4_NC

1 2

R264 0_4

1 2

R76 *0__NC

CLKRUN# 32PLTRST#24,31

SIO_SLP_S5# 32,42

SIO_SLP_S4# 19,32,42

SIO_SLP_S3# 19,32,42

T24

RSMRST#

DPWROK 32

EC_WAKE# 32

PCH Pull-high/low(CLG)

ME_SUS_PWR_ACK_R

PCIE_WAKE#_R

AC_PRESENT

PM_BATLOW#

SIO_PWRBTN#

TPM_LPC_PD

CLKRUN#

SYS_RESET#

RSMRST#

SYS_PWROK_R

DPWROK_R

APWROK_R

R49 10K_4

R69 10K_4

R52 *10K_4_NC

R72 10K_4

R74 *10K_4_NC

R188 *4.7K_4_NC

R46 8.2K/J_4

R234 10K_4

R263 10K_4

1 2

R228 *47K_4_NC

1 2

R261 100K_4

1 2

R32 *47K_4_NC

+RTC_CELL

+3.3V_SUS

+3.3V_SUS

+3.3V_RUN

112

+3.3V_RUN

3 5

2

C211

*0.1U/16V/X7R_4_NC

2

1

PLTRST#

R267

330K_4

DSWVRMEN

On Die DSW VR Enable

High = Enable (Default)

Low = Disable

R70 SJ_0402

B B

BUF_PLT_RST#32

1 2

R241

100K_4

U10

4

*TC7SH08FU_NC

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

4

3

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 7/12

Haswell ULT 7/12

Haswell ULT 7/12

1

ZM3

ZM3

ZM3

13 47

13 47

13 47

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

Haswell ULT MCP(POWER)

CPU VDDQ

D D

6X10UF MLCC

4X2.2UF MLCC

+V_VDDQ

C234 10U/6.3V_6

C235 10U/6.3V_6

C236 10U/6.3V_6

C237 10U/6.3V_6

C238 10U/6.3V_6

C239 10U/6.3V_6

1/21: 2.2Ux4 --> 1Ux2 , 0.1Ux2

C109 1U/6.3V_4

1 2

C103 0.1U/16V/X7R_4

1 2

+V1.05S_VCCST

R310

10K_4

VCCST_PWRGD_L

31

2

VCCST_PWRGD#32

C C

+V1.05S_VCCST

+3.3V_RUN

R111 *10K_4_NC

R112 *10K_4_NC

Q31

2N7002W

H_VR_ENABLE_MCP44

VR_READY

H_VR_ENABLE_MCP

IMVP_PWRGD44

+V1.05S_VCCST

+1.05V_RUN

8

R94 SJ_0805

112

+V1.05S_VCCST

2

C94 0.1U/16V/X7R_4

+VCCIOA_OUT

D8 SDMK0340L-7-F

+VCCIN

Haswell ULT 15W : 4.2A Haswell ULT 15W : 32A

+V_VDDQ

+VCCIO_OUT

VR_SVID_CLK44

1 2

R113 10K_4

2 1

R1087 1K_4

+V1.05S_VCCST

+VCCIN

C285

0.1U/16V/X7R_4

1 2

VCCSENSE

H_CPU_SVIDALRT#

VR_SVID_CLK

VR_SVID_DATA

H_VR_ENABLE_MCP

VR_READY

FIVR_EN_BUF

MCP_RSVD_69

T14

T9

MCP_RSVD_70

MCP_RSVD_71

T7

T19

MCP_RSVD_72

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

L59

J58

F59

N58

E63

A59

E20

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

U59

V59

C24

C28

C32

U12L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

HSW_ULT_DDR3L

1.4A 32A

HSW ULT POWER

12 OF 19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

CPU VCC

+VCCIN

C98 10U/6.3V_6

C96 10U/6.3V_6

C97 10U/6.3V_6

C137 10U/6.3V_6

C138 10U/6.3V_6

C139 10U/6.3V_6

C140 10U/6.3V_6

C121 10U/6.3V_6

C115 10U/6.3V_6

C118 10U/6.3V_6C113 1U/6.3V_4

C99 10U/6.3V_6

C141 10U/6.3V_6

C128 10U/6.3V_6

C133 10U/6.3V_6

C142 10U/6.3V_6

C143 10U/6.3V_6

C136 10U/6.3V_6

C125 10U/6.3V_6

C110 10U/6.3V_6

C134 10U/6.3V_6

C114 10U/6.3V_6

C91 10U/6.3V_6

C101 10U/6.3V_6

C105 10U/6.3V_6

1 2

C130 100P/50V_4

1 2

C112 100P/50V_4

C120 100P/50V_4

1 2

C102 100P/50V_4

1 2

1/21: 22Ux23 --> 10Ux23

23 X 22UF(0805 MLCC)

VCCSENSE

FIVR_EN_BUF

R312 100/F_4

R140 150

+VCCIN

VCCSENSE 44

+V1.05S_VCCST

B B

SVID ALERT

H_CPU_SVIDALRT#

R322 43_4

SVID DATA

VR_SVID_DATA

+V1.05S_VCCST

R324

75_4

+V1.05S_VCCST

12

R315

130_4

+VCCIO_OUT

+VCCIO_OUT

12

R329

*75_4_NC

R314

*130_4_NC

VR_SVID_ALERT# 44

VR_SVID_DATA 44

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

4

3

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 8/12

Haswell ULT 8/12

Haswell ULT 8/12

ZM3

ZM3

ZM3

3A

3A

14 47

14 47

1

14 47

3A

5

smd.db-x7.ru

Haswell ULT (GND)

4

3

2

1

D D

C C

B B

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

U12N

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HSW_ULT_DDR3L

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

U12O

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HSW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

G18

G22

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

H13

U12P

D5

D8

G3

G5

G6

G8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HSW_ULT_DDR3L

16 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_SENSE

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

AT2

AU44

AV44

D15

F22

H22

J21

100/F_4

R313

U12R

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSSSENSE 44

HSW_ULT_DDR3L

18 OF 19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

U12Q

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

5

TP_DC_TEST_AY60

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

T29

A A

T25

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

HSW_ULT_DDR3L

17 OF 19

4

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

A3

A4

A60

A61

A62

AV1

AW1

AW2

AW3

AW61

AW62

AW63

DC_TEST_A3_B3

TP_DC_TEST_A4

TP_DC_TEST_A60

DC_TEST_A61_B61

TP_DC_TEST_A62

TP_DC_TEST_AV1

TP_DC_TEST_AW1

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_AW63

3

T26

T30

T31

T22

T23

T28

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

2

Thursday, July 18, 2013

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Haswell ULT 9/12

Haswell ULT 9/12

Haswell ULT 9/12

ZM3

ZM3

ZM3

1

15 47

15 47

15 47

3A

3A

3A

5

smd.db-x7.ru

4

3

2

1

U12S

HSW_ULT_DDR3L

12/26: Debug support

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

MCP_RSVD_19

AU63

MCP_RSVD_20

C63

MCP_RSVD_21

C62

MCP_RSVD_22

B43

A51

MCP_RSVD_24

B51

MCP_RSVD_25

L60

MCP_RSVD_26

N60

W23

Y22

AY15

PROC_OPI_COMP

AV62

D58

P22

N21

P20

R20

TP11

TP12

TP13

TP16

TP10

TP9

TP5

R291 49.9/F_4

NOA_RCOMP

TD_IREF

AC60

AC62

AC63

AA63

AA60

AA62

AA61

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

U63

U62

V63

J20

H18

B12

A5

E1

D1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

RESERVED

PROC_OPI_RCOMP

19 OF 19

CFG0

CFG1

D D

TP14

TP23

TP6

TP4

TP22

TP21

TP19

TP3

TP2

TP18

TP17

TP20

TP15

R316 49.9/F_4

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

NOA_STBN_0

NOA_STBN_1

NOA_STBP_0

NOA_STBP_1

1/10 Del REFPKG_OCC pull high +3.3V_RUN

C C

R283

8.2K/F_4

Processor Strapping

1 0

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG1

PCH/ PCH LESS MODE SELECTION

(DEFAULT) NORMAL OPERATION; NO STALL STALL

(DEFAULT) NORMAL OPERATION PCH-LESS MODE

CFG0

CFG1

R330 *1K_4_NC

R317 *1K_4_NC

CFG3

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

B B

CFG4

DISPLAY PORT PRESENCE STRAP

CFG 8

ALLOW THE USE OF NOA ON LOCKED UNITS

CFG9

NO SVID PROTOCOL CAPABLE VR CONNECTED

CFG10

SAFE MODE BOOT

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO

EMBEDDED DISPLAY PORT

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE,

NOA WILL BE DISABLED IN LOCKED

UNITS AND ENABLED IN UN-LOCKED

UNITS

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

POWER FEATURES ACTIVATED

DURING RESET

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED; NOA WILL BE AVAILABLE

REGARDLESS OF THE LOCKING OF THE UNIT

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

CFG3

CFG4

CFG8

CFG9

CFG10

R323 *1K_4_NC

R133 1K_4

R328 *1K_4_NC

R131 *1K_4_NC

R132 *1K_4_NC

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

Thursday, July 18, 2013

Date: Sheet of

5

4

3

2

Thursday, July 18, 2013

PROJECT :

Haswell ULT 10/12

Haswell ULT 10/12

Haswell ULT 10/12

1

ZM3

ZM3

ZM3

16 47

16 47

16 47

3A

3A

3A

5

smd.db-x7.ru

VCCHSIO

D D

+3.3V_SUS

C C

+V3.3DX_1.5DX_1.8DX_AUDIO

2

R79 SJ_0402

112

+1.05V_RUN

+V1.05DX_MODPHY

1.84A

+1.05V_SUS

+V3.3DX_1.5DX_1.8DX_AUDIO

+1.05V_SUS

114mA

C72 1U/6.3V_4

+1.05V_RUN

+3.3V_SUS

+3.3V_SUS

+3.3V_RUN

+3.3V_SUS

4

C69 10U/6.3V_6

C60 *1U/6.3V_4_NC

C61 1U/6.3V_4

C62 1U/6.3V_4

C52 1U/6.3V_4

*C80-->4.7U

C73 10U/6.3V_6

C70 1U/6.3V_4

C66 1U/6.3V_4

C65 1U/6.3V_4

1/21: 22U --> 10U

C76 10U/6.3V_6

C41 1U/6.3V_4

C55 1U/6.3V_4

1/21: 22U --> 1U

+1.05V_RUN

C781U/6.3V_4

+V1.05S_AUSB3PLL

+V1.05S_ASATA3PLL

+V1.05S_APLLOPI

+V1.05S_AXCK_DCB

+V1.05S_AXCK_LCPLL

Haswell ULT PCH(POWER)

3.3 SUS: 205mA

1.05 SUS: 2066mA

1.05 RUN: 2578mA

3.3 RUN: 58mA

AA21

AH14

AH13

AH10

AE20

AE21

W21

AC9

M20

K9

L10

M9

N8

P9

B18

B11

Y20

J13

AA9

V8

W9

J18

K19

A20

J17

R21

T21

K18

V21

U12M

VCCHSIO

VCCHSIO

VCCHSIO

VCC1_05

VCC1_05

VCCUSB3PLL

VCCSATA3PL L

RSVD

VCCAPLL

VCCAPLL

DCPSUS3

VCCHDA

DCPSUS2

VCCSUS3_3

VCCSUS3_3

VCCDSW3 _3

VCC3_3

VCC3_3

VCCCLK

VCCCLK

VCCACLKPLL

VCCCLK

VCCCLK

VCCCLK

RSVD

RSVD

RSVD

VCCSUS3_3

VCCSUS3_3

13 OF 19

1.838A

57mA

10mA

11mA

25mA

62mA

114mA

200mA

41mA

42mA

31mA

LPT LP POWER

HSW_ULT_DDR3L

HSIO

OPI

USB3

HDA

VRM

GPIO/LPC

3

THERMAL SENSOR

SERIAL IO

SUS OSCILLATOR

RTC

SPI

CORE

USB2

1mA

1.632A

658mA

109mA

3mA

41mA

17mA

VCCSUS3_3

18mA

VCCASW

VCCASW

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCC1_05

DCPSUSBYP

DCPSUSBYP

VCCASW

VCCASW

VCCASW

DCPSUS1

DCPSUS1

VCCTS1_5

VCCSDIO

VCCSDIO

1mA

DCPSUS4

VCC1_05

VCC1_05

VCCRTC

DCPRTC

VCCSPI

VCC3_3

VCC3_3

RSVD

+1.05V_RUN

C58 1U/6.3V_4

C57 0.1U/16V/X7R_4

C56 0.1U/16V/X7R_4

AH11

AG10

AE7

Y8

AG14

AG13

J11

H11

H15

AE8

AF22

AG19

AG20

AE9

AF9

AG8

AD10

AD8

J15

K14

K16

U8

T9

AB8

AC20

AG16

AG17

R292 SJ_0402

C64 1U/6.3V_4

+VCCRTCEXT

R37 SJ_0402

C28 0.1U/16V/X7R_4

C51 1U/6.3V_4

+DCPSUSBYP

C63 1U/6.3V_4

C67 0.1U/16V/X7R_4

C54 1U/6.3V_4

C71 1U/6.3V_4

2

112

10U/6.3V_6

12

12

12

C53 0.1U/16V/X7R_4

2

112

12

C75 *10U/6.3V_6_NC

C80 1U/6.3V_4

C68 1U/6.3V_4

12

C77 1U/6.3V_4

+1.05V_SUS

+1.5V_RUN

+3.3V_RUN

12

C224

+V3.3S_1.8S_LPSS_SDIO +3.3V_RUN

+V1.05A_AOSCSUS

C30 1U/6.3V_4

+1.05V_RUN

12

C227

0.1U/16V/X7R_4

2

+3.3V_SUS

+RTC_CELL

+3.3V_SUS

+1.05V_RUN

+1.05V_RUN

C74 10U/6.3V_6

C59 1U/6.3V_4

+V1.05S_AXCK_LCPLL

C226

1U/6.3V_4

VCCSUS3

129mA

+1.05V_RUN

R247 SJ0603

2

112

+1.05V_SUS

VCC1_05

2.6A

VCCASW

473mA

2

R47 SJ_0402

112

C27

10U/6.3V_6

+DCPSUSBYP

1

C284 *0.47U/10V_4_nc

+V1.05A_AOSCSUS

12

C29

0.1U/16V/X7R_4

+3.3V_SUS

1mA

C31

1U/6.3V_4

C221

0.1U/16V/X7R_4

12

C217

0.1U/16V/X7R_4

41mA

C220

1U/6.3V_4

42mA

C216

1U/6.3V_4 C82

2