Page 1

5

4

3

2

1

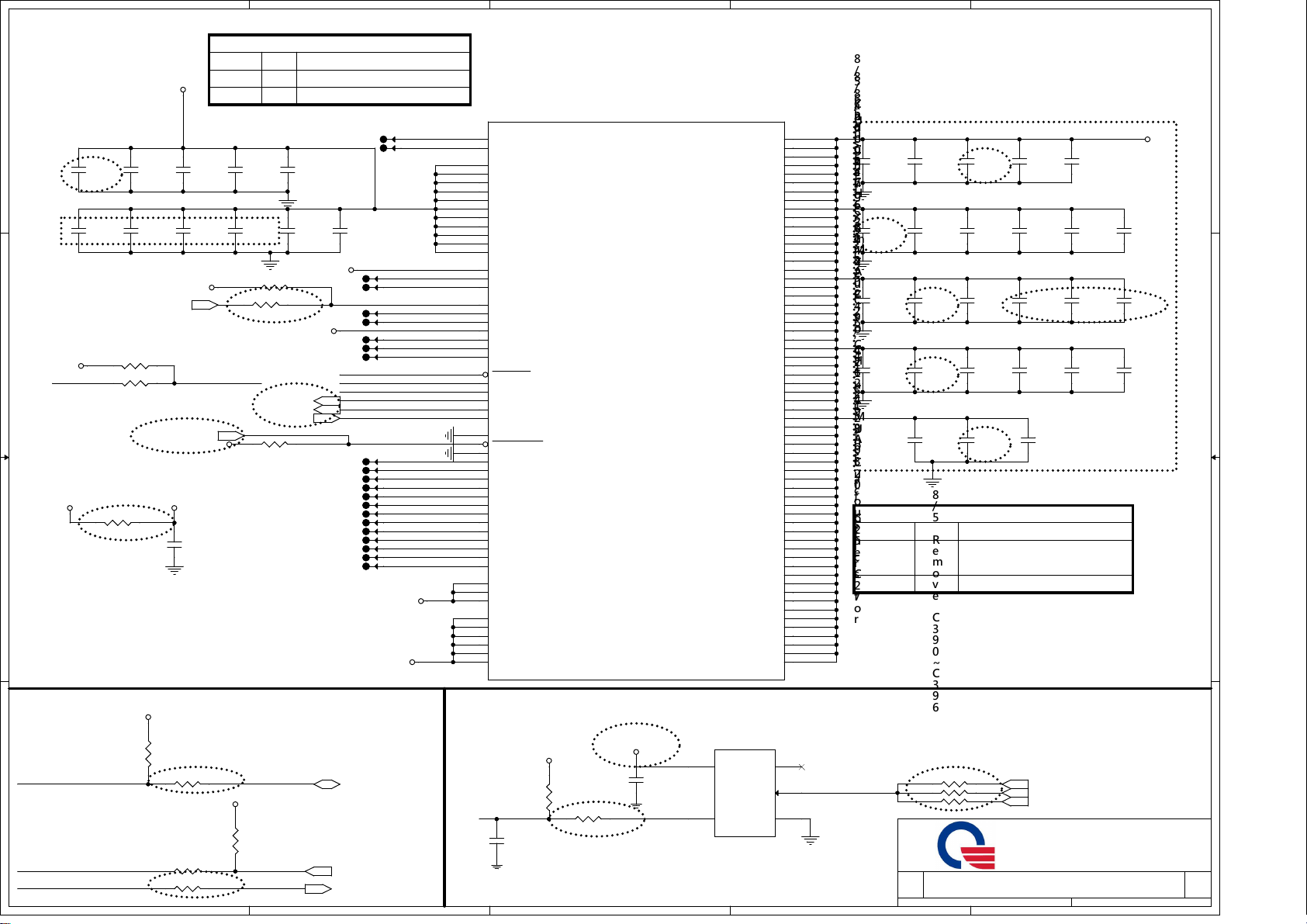

ZHN SHB ULT SYSTEM BLOCK DIAGRAM

01

Memory Down

D D

P14

P15

C C

Cardreader

GL823

P28

B B

Channel A 1Rx16

Channel B 1Rx16

NGFF SATA

P20

Daughter Board

I/O Board Conn.

USB2 Port

DB side

Google Debug conn

P28

PWR GATED

PWR GATED

Dual Channel DDR3L

1600 MHZ

SATA0

USB2-6

USB2-4

Azalia

Haswell ULT 15W

IMC

MCP 1168pins

DC+GT3

40 mm X 24 mm

SATA

Integrated PCH

USB2.0

IHDA

LPC

P2~P13

SMBUS

eDP

DDI

USB3.0/2.0

CLK

PCI-E x1

I2C

SPI

eDP

USB2-2

DDI1

USB3-1

USB2-1

USB2-0

PCIECLOCK-0

X'TAL

32.768KHz

X'TAL 24MHz

SPI ROM

W25Q64FVSSIG

EDP Conn.

CCD(Camera)

HDMI Conn.

PWR GATED

P18

USB3 Port

MB side

PWR GATED

PWR GATED

LTE

Mini Card

P16

P10

P21

SIM card

PCIE-1

USB2-3

I2C1

I2C0

TRACKPAD

PWR GATED

P8

MINI CARD

WLAN+BT

PWR GATED

ALS

ISL29023

TOUCH

SCREEN

P25

BQ24707A

Batery Charger

P19

P28

TPS51216

PP1350

P29 P30

TPS51225

AMIC

A A

5

Int. MIC

P23 P26P23

Combo HP

AUDIO CODEC

Speaker

PWR GATED

4

X'TAL

32.768KHz

Thermal IC

TI TM4E1G31H6ZRBIALC283

EC

P28

K/B Con.

Fan Driver

(PWM Type)

P25 P25

3

SLB9655TT1.2 FW4.32

TPM

HALL

SENSOR

P27

P22

2

PP3300_DSW/PP5000

TPS51622

+VCCIN

TPS51211

PP1050_PCH_SUS

TPS54318

PP1500_PCH_TS

Thermal Protection

P32

Discharger

P31

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

P33P34

P33

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZHN

ZHN

ZHN

1 39Monday, August 26, 2013

1 39Monday, August 26, 2013

1

1 39Monday, August 26, 2013

3B

3B

3B

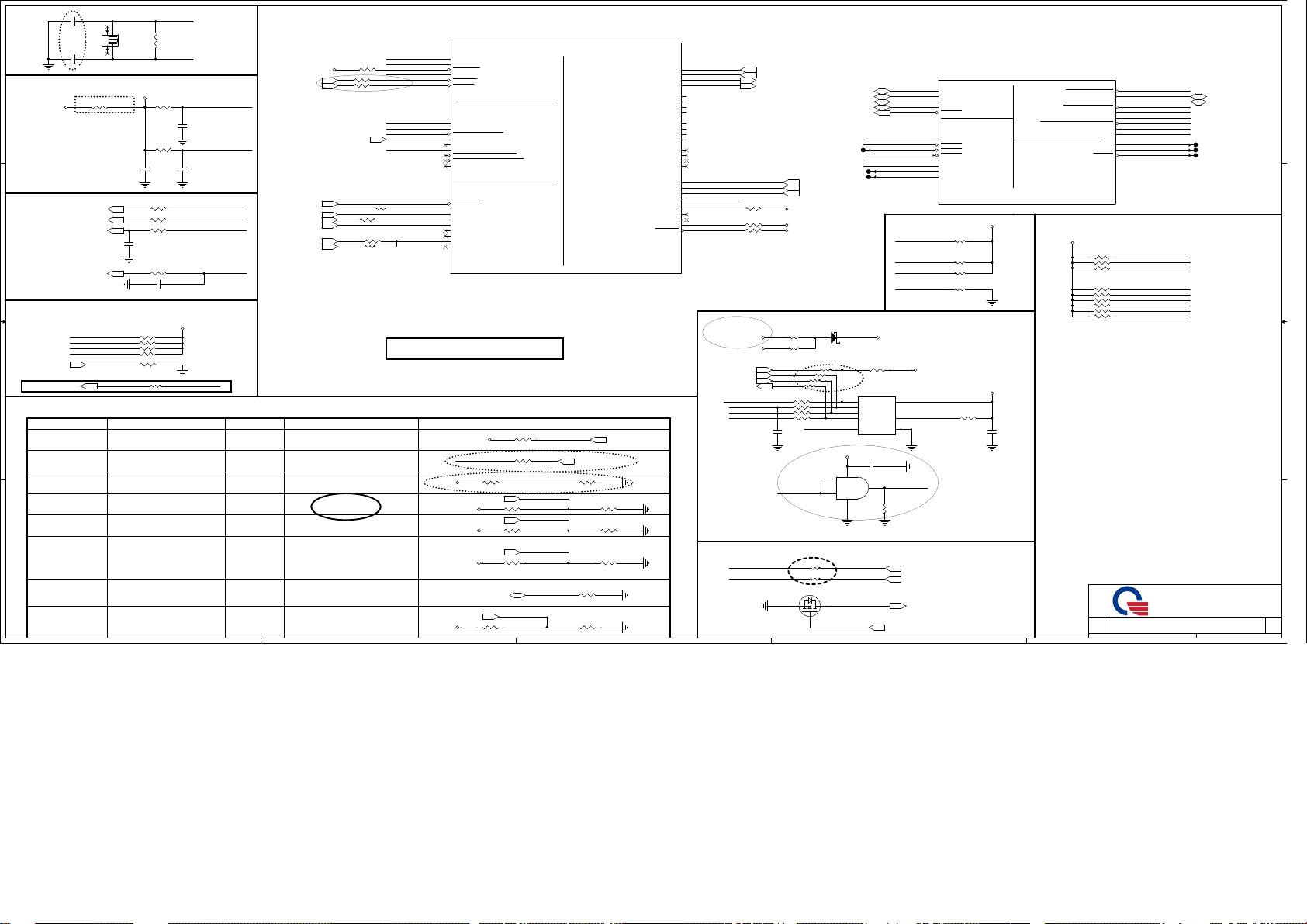

Page 2

5

4

3

2

1

Haswell ULT (DISPLAY,eDP)

U24A

HSW_ULT_DDR3L

02

D D

HDMI

INT_HDMITX2N[18]

INT_HDMITX2P[18]

INT_HDMITX1N[18]

INT_HDMITX1P[18]

INT_HDMITX0N[18]

INT_HDMITX0P[18]

INT_HDMICLK-[18]

INT_HDMICLK+[18]

DP

C C

PCH_BL_PWM[16,26]

PCH_BL_EN[16,26]

PCH_EDP_VDD_EN[16,26]

TP97

SIM_DET[21]

TOUCH_INT_L_DX[16]

ALS_INT_L[28]

B B

TRACKPAD_INT_DX[25]

PCH_BL_PWM

PCH_BL_EN

PCH_EDP_VDD_EN

PCH_GPIO77

PCH_GPIO78

PCH_GPIO79

PCH_GPIO80 SIM_DET

PCI_PME#

SIM_DET

TOUCH_INT_L_DX

ALS_INT_L

TRACKPAD_INT_DX

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U24I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

+3V

GPIO55

+3V

GPIO52

+3V

GPIO54

+3V

GPIO51

+3V

GPIO53

eDP SIDEBAND

+3V

+3V

+3V

+3V

+3V_S5

PCIE

1 OF 19

HSW_ULT_DDR3L

9 OF 19

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_TXN0

EDP_TXP0

EDP_AUXN

EDP_AUXP

EDP_RCOMP

HDMI_DDCCLK_SW [18]

HDMI_DDCDATA_SW [18]

R342

100K_4

EDP_TXN0 [16]

EDP_TXP0 [16]

EDP_AUXN [16]

EDP_AUXP [16]

R25 24.9/F_4

R343 *0_4

R356 *0_4

DP_UTIL [16]

INT_HDMI_HPD [18]

EDP_HPD [16]

PCH_BL_PWMDP_UTIL

Haswell C-1 2c BGA 1.6GHz ULV 15W 2+2 i5-4200U QS for proto/AJ0QEVEVT01

eDP Panel

+VCCIOA_OUT

eDP_RCOMP

Trace length < 100 mils

Trace width = 20 mils

Trace spacing = 25 mils

PCH_GPIO77

PCH_GPIO78

PCH_GPIO79

PCH_GPIO80

TOUCH_INT_L_DX

ALS_INT_L

TRACKPAD_INT_DX

DDPB/C_CTRLDATA has an iPD 20K,

When PU at rising edge of

PCH_PWROK, the DDI port will

be detected

R30 10K_4

R391 10K_4

R27 10K_4

R383 10K_4

R376 10K_4

R378 10K_4

R24 10K_4

R385 10K_4

PP3300_PCH

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

5

4

3

Monday, August 26, 2013

2

PROJECT :

Haswell 1/5 (DDI/eDP)

Haswell 1/5 (DDI/eDP)

Haswell 1/5 (DDI/eDP)

ZHN

ZHN

ZHN

2 39

2 39

2 39

1

3B

3B

3B

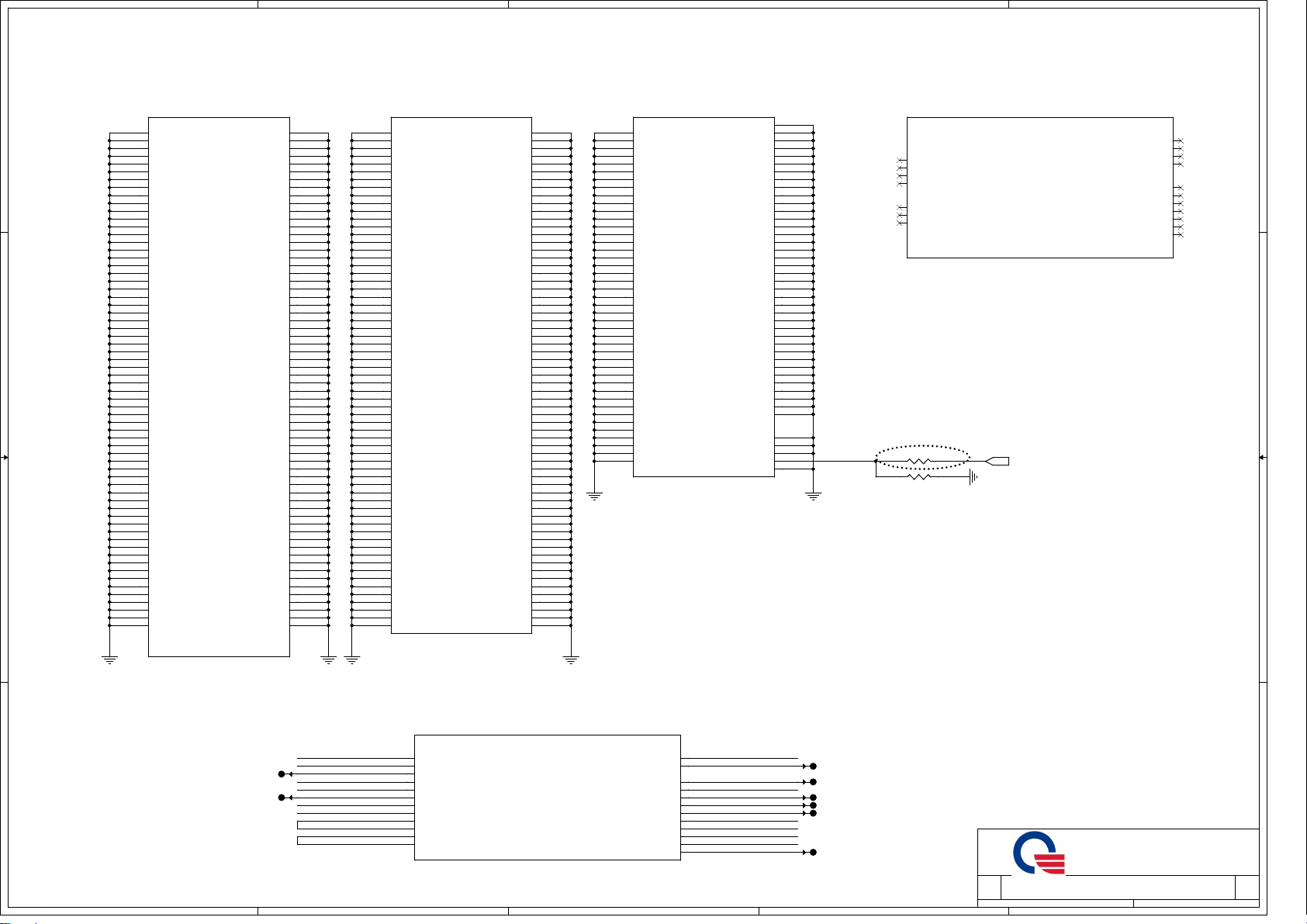

Page 3

5

4

3

2

1

Haswell ULT (DDR3L) Haswell Processor (DDR3L)

U24C

M_A_DQ<0>[14]

M_A_DQ<1>[14]

M_A_DQ<2>[14]

M_A_DQ<3>[14]

M_A_DQ<4>[14]

D D

C C

M_A_DQ<5>[14]

M_A_DQ<6>[14]

M_A_DQ<7>[14]

M_A_DQ<8>[14]

M_A_DQ<9>[14]

M_A_DQ<10>[14]

M_A_DQ<11>[14]

M_A_DQ<12>[14]

M_A_DQ<13>[14]

M_A_DQ<14>[14]

M_A_DQ<15>[14]

M_A_DQ<16>[14]

M_A_DQ<17>[14]

M_A_DQ<18>[14]

M_A_DQ<19>[14]

M_A_DQ<20>[14]

M_A_DQ<21>[14]

M_A_DQ<22>[14]

M_A_DQ<23>[14]

M_A_DQ<24>[14]

M_A_DQ<25>[14]

M_A_DQ<26>[14]

M_A_DQ<27>[14]

M_A_DQ<28>[14]

M_A_DQ<29>[14]

M_A_DQ<30>[14]

M_A_DQ<31>[14]

M_A_DQ<32>[14]

M_A_DQ<33>[14]

M_A_DQ<34>[14]

M_A_DQ<35>[14]

M_A_DQ<36>[14]

M_A_DQ<37>[14]

M_A_DQ<38>[14]

M_A_DQ<39>[14]

M_A_DQ<40>[14]

M_A_DQ<41>[14]

M_A_DQ<42>[14]

M_A_DQ<43>[14]

M_A_DQ<44>[14]

M_A_DQ<45>[14]

M_A_DQ<46>[14]

M_A_DQ<47>[14]

M_A_DQ<48>[14]

M_A_DQ<49>[14]

M_A_DQ<50>[14]

M_A_DQ<51>[14]

M_A_DQ<52>[14]

M_A_DQ<53>[14]

M_A_DQ<54>[14]

M_A_DQ<55>[14]

M_A_DQ<56>[14]

M_A_DQ<57>[14]

M_A_DQ<58>[14]

M_A_DQ<59>[14]

M_A_DQ<60>[14]

M_A_DQ<61>[14]

M_A_DQ<62>[14]

M_A_DQ<63>[14]

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

6/25 Add TP127~TP132 for XDP by Intel.

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

+VREF_CA_CPU

AR51

+VREFDQ_SA_M3

AP51

+VREFDQ_SB_M3

TP127

TP128

TP129

TP41

TP40

M_A_A<0> [14]

M_A_A<1> [14]

M_A_A<2> [14]

M_A_A<3> [14]

M_A_A<4> [14]

M_A_A<5> [14]

M_A_A<6> [14]

M_A_A<7> [14]

M_A_A<8> [14]

M_A_A<9> [14]

M_A_A<10> [14]

M_A_A<11> [14]

M_A_A<12> [14]

M_A_A<13> [14]

M_A_A<14> [14]

M_A_A<15> [14]

M_A_DIM0_CK_DDR0_DN [14]

M_A_DIM0_CK_DDR0_DP [14]

M_A_DIM0_CKE0 [14]

M_A_DIM0_CS0_N [14]

M_A_RAS_N [14]

M_A_WE_N [14]

M_A_CAS_N [14]

M_A_BS0 [14]

M_A_BS1 [14]

M_A_BS2 [14]

M_A_DQS_DN<0> [14]

M_A_DQS_DN<1> [14]

M_A_DQS_DN<2> [14]

M_A_DQS_DN<3> [14]

M_A_DQS_DN<4> [14]

M_A_DQS_DN<5> [14]

M_A_DQS_DN<6> [14]

M_A_DQS_DN<7> [14]

M_A_DQS_DP<0> [14]

M_A_DQS_DP<1> [14]

M_A_DQS_DP<2> [14]

M_A_DQS_DP<3> [14]

M_A_DQS_DP<4> [14]

M_A_DQS_DP<5> [14]

M_A_DQS_DP<6> [14]

M_A_DQS_DP<7> [14]

U24D

M_B_DQ<0>[15]

M_B_DQ<1>[15]

M_B_DQ<2>[15]

M_B_DQ<3>[15]

M_B_DQ<4>[15]

M_B_DQ<5>[15]

M_B_DQ<6>[15]

M_B_DQ<7>[15]

M_B_DQ<8>[15]

M_B_DQ<9>[15]

M_B_DQ<10>[15]

M_B_DQ<11>[15]

M_B_DQ<12>[15]

M_B_DQ<13>[15]

M_B_DQ<14>[15]

M_B_DQ<15>[15]

M_B_DQ<16>[15]

M_B_DQ<17>[15]

M_B_DQ<18>[15]

M_B_DQ<19>[15]

M_B_DQ<20>[15]

M_B_DQ<21>[15]

M_B_DQ<22>[15]

M_B_DQ<23>[15]

M_B_DQ<24>[15]

M_B_DQ<25>[15]

M_B_DQ<26>[15]

M_B_DQ<27>[15]

M_B_DQ<28>[15]

M_B_DQ<29>[15]

M_B_DQ<30>[15]

M_B_DQ<31>[15]

M_B_DQ<32>[15]

M_B_DQ<33>[15]

M_B_DQ<34>[15]

M_B_DQ<35>[15]

M_B_DQ<36>[15]

M_B_DQ<37>[15]

M_B_DQ<38>[15]

M_B_DQ<39>[15]

M_B_DQ<40>[15]

M_B_DQ<41>[15]

M_B_DQ<42>[15]

M_B_DQ<43>[15]

M_B_DQ<44>[15]

M_B_DQ<45>[15]

M_B_DQ<46>[15]

M_B_DQ<47>[15]

M_B_DQ<48>[15]

M_B_DQ<49>[15]

M_B_DQ<50>[15]

M_B_DQ<51>[15]

M_B_DQ<52>[15]

M_B_DQ<53>[15]

M_B_DQ<54>[15]

M_B_DQ<55>[15]

M_B_DQ<56>[15]

M_B_DQ<57>[15]

M_B_DQ<58>[15]

M_B_DQ<59>[15]

M_B_DQ<60>[15]

M_B_DQ<61>[15]

M_B_DQ<62>[15]

M_B_DQ<63>[15]

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

TP130

TP131

TP132

TP35

TP31

M_B_A<0> [15]

M_B_A<1> [15]

M_B_A<2> [15]

M_B_A<3> [15]

M_B_A<4> [15]

M_B_A<5> [15]

M_B_A<6> [15]

M_B_A<7> [15]

M_B_A<8> [15]

M_B_A<9> [15]

M_B_A<10> [15]

M_B_A<11> [15]

M_B_A<12> [15]

M_B_A<13> [15]

M_B_A<14> [15]

M_B_A<15> [15]

M_B_DIM0_CK_DDR0_DN [15]

M_B_DIM0_CK_DDR0_DP [15]

M_B_DIM0_CKE0 [15]

M_B_DIM0_CS0_N [15]

M_B_RAS_N [15]

M_B_WE_N [15]

M_B_CAS_N [15]

M_B_BS0 [15]

M_B_BS1 [15]

M_B_BS2 [15]

M_B_DQS_DN<0> [15]

M_B_DQS_DN<1> [15]

M_B_DQS_DN<2> [15]

M_B_DQS_DN<3> [15]

M_B_DQS_DN<4> [15]

M_B_DQS_DN<5> [15]

M_B_DQS_DN<6> [15]

M_B_DQS_DN<7> [15]

M_B_DQS_DP<0> [15]

M_B_DQS_DP<1> [15]

M_B_DQS_DP<2> [15]

M_B_DQS_DP<3> [15]

M_B_DQS_DP<4> [15]

M_B_DQS_DP<5> [15]

M_B_DQS_DP<6> [15]

M_B_DQS_DP<7> [15]

03

B B

3 OF 19

A A

5

4

3

4 OF 19

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

2

Monday, August 26, 2013

PROJECT :

Haswell 2/5 (DDR3 I/F)

Haswell 2/5 (DDR3 I/F)

Haswell 2/5 (DDR3 I/F)

ZHN

ZHN

ZHN

3B

3B

3 39

3 39

1

3 39

3B

Page 4

5

4

3

2

1

04

D D

C C

DRAM COMP

B B

H_PECI (50ohm)

Route on microstrip only

Spacing >18 mils

Trace Length: 0.4~6.125 iches

H_PWRGOOD (50ohm)

Trace Length: 1~11.25 inches

CPU_PLTRST# (50ohm)

Trace Length: 10~17 inches

H_PECI[26]

H_PROCHOT#[17,26,29,32]

CPU_PGOOD[26]

R90 200/F_4

R91 120/F_4

R92 100/F_4

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

TP71

TP80

R380 56_4

R360 *Short_4

SM_RCOMP[0:2]

Trace length < 500 mils

Trace width = 12~15 mils

Trace spacing = 20 mils

TP108

XDP PU/PD

PROC_DETECT

CATERR#

H_PECI

H_PROCHOT#_RH_PROCHOT#

H_PWRGOOD_R

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

DDR_PG_CTRL

Haswell ULT (SIDEBAND)

D61

PROC_DETECT

K61

CATERR

N62

PECI

K63

PROCHOT

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST

AV61

SM_PG_CNTL1

XDP_TDO_CPU

XDP_TCK0

XDP_TRST#

U24B

R29 *51_4

R433 51_4

R462 *51_4

MISC

THERMAL

PWR

DDR3L

DSW

+1.05V_VCCST

HSW_ULT_DDR3L

JTAG

2 OF 19

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

XDP_PRDY#

K62

XDP_PREQ#

E60

XDP_TCK0

E61

XDP_TMS_CPU

E59

XDP_TRST#

F63

XDP_TDI_CPU

F62

XDP_TDO_CPU

J60

XDP_BPM#0

H60

XDP_BPM#1

H61

XDP_BPM#2

H62

XDP_BPM#3

K59

XDP_BPM#4

H63

XDP_BPM#5

K60

XDP_BPM#6

J61

XDP_BPM#7CPU_DRAMRST#

XDP_PRDY# [13]

XDP_PREQ# [13]

XDP_TCK0 [8,13]

XDP_TMS_CPU [13]

XDP_TRST# [8,13]

XDP_TDI_CPU [8,13]

XDP_TDO_CPU [8,13]

XDP_BPM#0 [13]

XDP_BPM#1 [13]

TP73

TP75

TP76

TP74

TP10

TP9

TCK,TMS

Trace Length < 9000mils

BPM#[0:7]

Trace Length 1~6 inches

Length match < 300 mils

PU/PD of CPU

+1.05V_VCCST

H_PROCHOT#

A A

H_PWRGOOD_R

R386 62_4

R359 10K_4

5

DRAMRST

CPU DRAM

CPU_DRAMRST#

PP1350

12

R130

470_4

R140 *Short_4

4

12

C285

*0.1u/10V_4

3

DDR3_DRAMRST# [14,15]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

2

Monday, August 26, 2013

PROJECT :

Haswell 3/5 (SideBand)

Haswell 3/5 (SideBand)

Haswell 3/5 (SideBand)

ZHN

ZHN

ZHN

4 39

4 39

4 39

1

3B

3B

3B

Page 5

5

4

3

2

1

VDDQ Output Decoupling Recommendations

330uFx2 7343

C281

10u/6.3V_6

C386

10u/6.3V_6

+VCCIN

22uFx11

10uFx10

+1.35V_CPU 1.4A

C92

10u/6.3V_6

C387

2.2u/6.3V_6

R367 100/F_4

R368 *Short_4

300mA

300mA

VCCST_PWRGD[13]

VRON_CPU[32]

VCORE_PGOOD[10,32]

R26 150_6

PP1350

6/21 Add C384~C388 by

Intel DDR.

D D

C388

2.2u/6.3V_6

C385

22u/6.3V_8

5/16 modify C282,C283

value by Intel suggest.

C C

+1.05V_VCCST

VRON_CPU VCORE_PGOOD

0415 VCCST_PWRGD need PP1050_RUN

power good

C91

10u/6.3V_6

C384

10u/6.3V_6

VCC_SENSE[32]

R358 *10K_4

R357 10K_4

PWR_DEBUG[13]

+1.05V_VCCST

0729 Add PWR_DEBUG to CN15.

+1.05V_VCCSTPP1050_PCH

R59 *SHORT_8

C68

*4.7u/6.3V_6

B B

BOT socket side

5 onTOP, 6 on BOT inside socket cavity

0805

5 onTOP, 5 on BOT inside socket cavity

0805

TP5

TP8

C90

10u/6.3V_6

+VCCIN

C282

10u/6.3V_6

TP17

TP29

TP30

TP69

TP36

TP24

TP42

TP12

TP13

TP11

TP81

TP22

TP34

TP33

TP25

TP39

TP32

TP43

TP15

TP26

ULT_RVSD_63

ULT_RVSD_64

VCC_SENSE_R

ULT_RVSD_65

+VCCIO_OUT

ULT_RVSD_66

ULT_RVSD_67

ULT_RVSD_68

H_CPU_SVIDART#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

VCCST_PWRGD

VRON_CPU

VCORE_PGOOD

PWR_DEBUG

ULT_RVSD_69

ULT_RVSD_70

ULT_RVSD_71

ULT_RVSD_72

ULT_RVSD_73

ULT_RVSD_74

ULT_RVSD_75

ULT_RVSD_76

ULT_RVSD_77

ULT_RVSD_78

ULT_RVSD_79

ULT_RVSD_80

ULT_RVSD_81

+1.05V_VCCST

+VCCIN

C283

10u/6.3V_6

+VCCIOA_OUT

ULT_RVSD_61

ULT_RVSD_62

Haswell ULT (POWER)

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

L59

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

F59

N58

AC58

E63

AB23

A59

E20

AD23

AA23

AE59

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

J58

U24L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

8/5 Change CH6221M9A02 to CH6221M9A03

8/6 Unstuff C22,C25,C26,C41,C49 for acoustic

8/26 Change C244, C49, C21, C23, C20, C25, C27

and C247 from 22uF to 47 uF. Unstuff others for

acoustic

C35

*22u/6.3V_8

C49

47u/6.3V_8

C246

*22u/6.3V_8

C44

*22u/6.3V_8

C266

*22u/6.3V_8

C262

*22u/6.3V_8

C21

47u/6.3V_8

C27

47u/6.3V_8

C22

*22u/6.3V_8

C244

47u/6.3V_8

C260

*22u/6.3V_8

C267

*22u/6.3V_8

C26

*22u/6.3V_8

C247

47u/6.3V_8

8/5 Remove C390~C396

VCC Output Decoupling Recommendations

470uFx4 7343

22uFx8

22uFx11

10uFx11

TOP socket side

4 on TOP, 4 on BOT near socket edge

0805

0805

TOP, inside socket cavity

0805

BOT, inside socket cavity

C62

*22u/6.3V_8

C41

*22u/6.3V_8

C23

47u/6.3V_8

C24

*22u/6.3V_8

C245

*22u/6.3V_8

+VCCIN 32A

C248

*22u/6.3V_8

C46

*22u/6.3V_8

C20

47u/6.3V_8

C43

*22u/6.3V_8

05

+VCCIN

C42

*22u/6.3V_8

C25

47u/6.3V_8

C45

*22u/6.3V_8

SVID

H_CPU_SVIDDAT

A A

Place PU resistor

close to CPU

Place PU resistor

close to CPU

H_CPU_SVIDART#

H_CPU_SVIDCLK

+1.05V_VCCST

R379

130/F_4

R381 *Short_4

R389 43_4

R388 *Short_4

5

Layout note: need routing together

and ALERT need between CLK and DATA.

+1.05V_VCCST

R387

75_4

VR_SVID_DATA [32]

VR_SVID_ALERT# [32]

VR_SVID_CLK [32]

4

VCCST PWRGD

+1.05V_VCCST

R336

10K_4

R312

C233

*0.1u/10V_4

PP3300_DSW

VCCST_PWRGD_RVCCST_PWRGD

*Short_4

3

C1

0.1u/10V_4

U20

5

VCC

4

Y

74AUP1G07GW

GND

1

NC

2

VCCST_PWRGD_EN

A

3

2

R306 *0_4

R307 *Short_4

R305 *0_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Haswell 4/5 (POWER)

Haswell 4/5 (POWER)

Haswell 4/5 (POWER)

Monday, August 26, 2013

Monday, August 26, 2013

Monday, August 26, 2013

PP1050_PGOOD [13,26,31]

PCH_PWROK [7,26]

SYS_PWROK [7,13,26]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZHN

ZHN

ZHN

1

G Path

5 39

5 39

5 39

3B

3B

3B

Page 6

5

4

3

2

1

Haswell ULT (CFG,RSVD)

U24S

HSW_ULT_DDR3L

06

D D

C C

CFG0[13]

CFG1[13]

CFG2[13]

CFG3[13]

CFG4[8,13]

CFG5[13]

CFG6[13]

CFG7[13]

CFG8[13]

CFG9[13]

CFG10[13]

CFG11[13]

CFG12[13]

CFG13[13]

CFG14[13]

CFG15[13]

NOA_STBN_0[13]

NOA_STBN_1[13]

NOA_STBP_0[13]

NOA_STBP_1[13]

R57 49.9/F_4

R352 8.2K_4

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

NOA_STBN_0

NOA_STBN_1

NOA_STBP_0

NOA_STBP_1

CFG_RCOMP

TD_IREF

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

J20

H18

B12

A5

E1

D1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

RESERVED

PROC_OPI_RCOMP

19 OF 19

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

OPI_COMP1

R461 49.9/F_4

Processor Strapping

1 0

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG1

PCH/ PCH LESS MODE SELECTION

B B

CFG3

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

CFG 8

ALLOW THE USE OF NOA ON LOCKED UNITS

(DEFAULT) NORMAL OPERATION; NO STALL

(DEFAULT) NORMAL OPERATION

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED

TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE, NOA

WILL BE DISABLED IN LOCKED UNITS AND

ENABLED IN UN-LOCKED UNITS

STALL

PCH-LESS MODE

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS

CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED; NOA WILL BE AVAILABLE

REGARDLESS OF THE LOCKING OF THE UNIT

CFG0

CFG1

CFG3

CFG8

R417 *1K_4

R423 *1K_4

R409 *1K_4

R403 *1K_4

CFG9

NO SVID PROTOCOL CAPABLE VR

CONNECTED

A A

CFG10

SAFE MODE BOOT

5

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

POWER FEATURES ACTIVATED

DURING RESET

4

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

3

CFG9

CFG10

R394 *1K_4

R56 *1K_4

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

PROJECT :

Haswell 5/5 (CFG/GND)

Haswell 5/5 (CFG/GND)

Haswell 5/5 (CFG/GND)

1

ZHN

ZHN

ZHN

6 39

6 39

6 39

3B

3B

3B

Page 7

5

4

3

2

1

Haswell ULT PCH (PM)

U24H

PCH_SUSPWRACK

TP37

SUSACK#_R

SYS_RESET#

SYS_PWROK_R

PCH_PWROK_R

APWROK_RPCH_PWROK

PCI_PLTRST#

PCH_RSMRST#

PCH_PWRBTN#

PCH_ACPRESENT

PCH_BATLOW#

PCH_SLP_S0#_R

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

+3V_S5

PCH_SUSACK_L[26]

D D

SYS_PWROK[5,13,26]

PCH_SUSWARN_L[26]

PCH_PWRBTN_L[26]

C C

SYS_RESET#[13,17]

SYS_PWROK

PCH_RSMRST_L[26]

ACPRESENT[29]

PCH_SLP_S0_L[13,26]

R421 *Short_4

R478 *Short_4

R453 *0_4

R147 *Short_4

R61 *Short_4

R415 *Short_4

R428 *0_4

C265 *1u/6.3V_4

R482 *Short_4

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

+3V

+3V_S5

+3V_S5

DSW

DSW

DSW

DSW

+3V_S5

DSW

+3V_S5

DSWVRMEN

DSW

SUS_STAT/GPIO61

DSW

DSW

DSW

DSW

DSW

DPWROK

WAKE

CLKRUN/GPIO32

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AW7

DSWVREN

AV5

DPWROK_R

AJ5

PCIE_PCH_WAKE#

V5

CLKRUN#

AG4

PCH_SUS_STAT

AE6

PCH_SUSCLK

AP5

PCH_SLP_S5_L

AJ6

PCH_SLP_S4_L

AT4

PCH_SLP_S3_L

AL5

PCH_SLP_A_L

AP4

PCH_SLP_SUS_L

AJ7

PCH_SLP_LAN#

6/25 R74 stuff by Google.

Deep Sx

R477 *Short_4

R74 *Short_4

R38 *Short_4

LPC_CLKRUN_L

TP27

TP23

TP38

07

DSWVREN [8]

PCH_DPWROK [26]

PCH_WAKE_L [26]

LPC_CLKRUN_L [26]

PCH_SLP_S5_L [13,26,30,35]

PCH_SLP_S4_L [13]

PCH_SLP_S3_L [13,26,30,31,33,35]

PCH_SLP_A_L [13]

PCH_SLP_SUS_L [26,35]

R427 0_4

SUSACK#_RPCH_SUSPWRACK

8 OF 19

4/22 modify, default skip EC control

PCH PM PU/PD

PP3300_PCH

CLKRUN#

B B

A A

SYS_RESET#

PCH_RSMRST#

SYS_PWROK

DPWROK_R

PCH_SUSPWRACK

SYS_PWROK

PCH_ACPRESENT

PCH_BATLOW#

PCIE_PCH_WAKE#

PCH_PWRBTN#

R37 8.2K_4

R406 10K_4

R479 10K_4

R80 *10K_4

R473 100K/F_4

R454 10K_4

R426 *1K_4

R62 10K_4

R444 8.2K_4

R75 10K_4

R151 *10K_4

5

PP3300_PCH_SUS

PP3300_DSW

PCH PWROK

PCH_PWROK[5,26]

100K_4

PLTRST# Buffer

PP3300_PCH

2

PCI_PLTRST#

4/22 modify, default is bypass PLTRST#

4

1

PCH_PWROK PCH_PWROK_R

R487

PCI_PLTRST# PLTRST#

C94 *0.1u/10V_4

4

U6

3 5

*TC7SH08FU

3

R155

100K_4

R483 *Short_4

R474 *0_4

Non Deep Sx

R152 *Short_4

PLTRST# [13,19,21,22,26]

DPWROK_RPCH_RSMRST_L

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

2

PROJECT :

PCH 1/6 (PM)

PCH 1/6 (PM)

PCH 1/6 (PM)

ZHN

ZHN

ZHN

7 39

7 39

7 39

1

3B

3B

3B

Page 8

RTC Clock 32.768KHz (RTC)

C278 15p/50V _4

C286 15p/50V _4

7/2 C278,C286 change to CH01506JB06.

D D

RTC Circuitry (RTC)

HDA

C C

PCH JTAG

JTAG_TCK,JTAG_TMS

Trace Length < 9000mils

20130513 add by Intel.

B B

ULT Strapping Table

R168 *SHORT_6

PP3300_RTC

+3V_RTC

Trace width = 20 mils

20MIL

6/18 del D9 by Acer.

PCH_AZ_CODEC_RST#[23]

PCH_AZ_CODEC_SDOUT[23]

PCH_AZ_CODEC_BITCLK[23]

PCH_AZ_CODEC_SYNC[23]

XDP_TMS

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

XDP_TCK1[13]

XDP_TDI_CPU[4,13]

Pin Name Strap description

GPIO81(SPKR)

HDA_SDO

INTVRMEN

GPIO66

GPIO86

GPIO15

A A

CFG4

DSWVREN

5

Y3

32.768KHZ

+3V_RTC

R488 33_4

R492 33_4

R490 33_4

C302

*10p/50V_4

R494 33_4

C312 *10p/5 0V_4

RTC_X1

R460

10M_4

RTC_X2

+3V_RTC

Trace width = 30 mils

R160

20K/F_4

C98

1u/6.3V_4

R159

20K/F_4

C105

C97

1u/6.3V_4

1u/6.3V_4

23

4 1

MP remove(Intel)

R47 *0_4

PP1050_PCH_SUS

PCH_JTAG_TDO

R418 *51_4

R78 *51_4

R73 51_4

R420 *1K_4

XDP_TCK1

R83 *51_4

No reboot on TCO Timer

expiration

Flash Descriptor Security

Override / Intel ME Debug Mode

Integrated 1.05V VRM enable ALW AYS

Top-Block Swap override

Boot BIOS Strap Bit

TLS(Transport layer security)

DP presence strap

Deep Sx well on die VR enable

5

PCH_RTCRST_R

PCH_SRTCRST_R

HDA_RST#_R

HDA_SDO_R

HDA_BCLK_R

HDA_SYNC_R

Sampled

PWROK

PWROK

5/13 modify, default skip EC control

+3V_RTC

PCH_SRTCRST[26 ]

PCH_RTCRST[13,26]

XDP_TRST#[4,13]

XDP_TDO_CPU[4,13]

0 = Default enable (iPD 20K)

1 =Disable No-Reboot mode

0 = Default can program ME (iPD 20K)

1 =can't program ME

R157 *0_4

R156 *0_4

RTCRST_L and SRTCRST_L

please take out layout

PCH_AZ_CODEC_SDIN0[23]

XDP_TCK0

XDP_TDI[13]

XDP_TDO[13]

XDP_TMS[13]

XDP_TCK0[4,13]

Configuration note

1=Should be always pull-up

0 = Default disable (iPD 20K)

1 = Enable TBS function

0 = Default SPI (iPD 20K)

1 =LPC

0 = Default enable w/o

confidentiality(iPD 20K)

1 =Default enable with

confidentiality

0 = Enable an external display

port is connected to the eDP

1 =disable

1=Should be always pull-up

R475 1M_4

R82 *0_4

R55 *Short_4

R429 *Short_4

R35 *0_4

4

Haswell ULT PCH (RTC/HDA/SATA/SPI)

U24E

AW5

RTC_X1

RTC_X2

SM_INTRUDER#

PCH_INTVRMEN

PCH_SRTCRST_R

PCH_RTCRST_R

HDA_BCLK_R

HDA_SYNC_R

HDA_RST#_R

HDA_SDO_R

XDP_TCK1

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

6/18 del RTC battery circuit by Acer.

Note: R493 need stuff on MP.

PP3300_PCH

HDA_SDO_R

R484 330K_4

+3V_RTC

GPIO66[10]

DSWVREN[7]

R330 *1K_4

GPIO86[10]

R1 *1K_4

GPIO15[10]

R50 *8.2K_4

CFG4[6,13]

R476 330K_4

PP3300_PCH

PP3300_PCH

PP3300_PCH_SUS

+3V_RTC

4

HSW_ULT_DDR3L

RTC

AUDIO SATA

JTAG

5 OF 19

PCH_INTVRMEN

GPIO66

GPIO86

GPIO15

x86 stuff

CFG4

DSWVREN

SPKR

R485 *330K_4

R64 1K_4

R472 *330K_4

R400 *1K_4

R493 *0_4

+3V

+3V

+3V

+3V

SPKR [10,23]

PCH_HDA_SDO [26]

R340 *1K_4

R7 *1K_4

R58 *1K_4

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

3

SATA_TP0/PETP6_L3

SATA_TP1/PETP6_L2

SATA_TP2/PETP6_L1

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

4/23 modify for

WP circuit

3

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

EC_SMI_L

U1

PCH_NMI_DBG_L

V6

EC_SCI_L

AC1

GPIO37

A12

SATA_IREF

L11

K10

C12

U3

R351 *Short_4

SATA_RCOMP

R350 3.01K/F_4

SATA_LED#

R395 10K_4

SATA_RCOMP

Impedance = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

PCH dual I/O SPI ROM

PP3300_DSW

PCH_SPI_CS0#_R[17]

PCH_SPI_CLK_R[17]

PCH_SPI_SI_R[17]

PCH_SPI_SO_R[17]

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

SATA_RXN0_SSD [20]

SATA_RXP0_SSD [20]

SATA_TXN0_SSD [20]

SATA_TXP0_SSD [20]

iSSD

R408 *SHORT_6

R407 *0_6

near SPI ROM as possible

R413 33_4

R450 33_4

R449 33_4

R412 33_4

SPI_WP_ME

SPI_WP_ME

SPI_HOLD_ME

2

Haswell ULT PCH(LPC,SPI,SMBUS,C-LINK,THERMAL)

LPC_LAD0[22,26]

LPC_LAD1[22,26]

LPC_LAD2[22,26]

LPC_LAD3[22,26]

LPC_LFRAME#[22,26]

PCH_SPI_CLK

PCH_SPI_CS1#

TP93

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

TP14

PCH_SPI_IO3

EC_SMI_L [26]

EC_SCI_L [26]

+V1.05S_ASATA3PLL

+V1.05S_ASATA3PLL

PP3300_PCH

R451 *Sho rt_4

R459 *Short_4

R411 *Sho rt_4

C280

*22p/50V_4

R105 *Short_4

R458 *Short_4

1

TP94

PCH_NMI_DBG_L [26]

EC_SMI_L

EC_SCI_L

PCH_NMI_DBG_L

GPIO37

W25Q64FVSSIG(SOIC) / AKE3EFP0N06----->8MB

D23 RB500V-40

R414 *Sho rt_4

SPI_WP_ME_ROM

2

1

+3V_PCH_ME

3 5

+3V_PCH_MEPP3300_PCH

R424 4.7K_4

U25

1

CE#

VDD

6

SCK

5

SI

2

SO

HOLD#

3

WP#

VSS

ROM-8M

C80 0.1u/10V_4

4

U3

TC7SH08FU

8

7

SPI_HOLD_ME

4

SPI_WP_ME_ROM

R410

10K_4

4/23 modify for WP circuit

near SPI ROM as possible

Q12N7002K

3

2

SPI_WP_ME

GPIO_SPI_WP [17]

SPI_HOLD#_BIOS [17]

PCH_SPI_WP_D [10]

PCH_SPI_WP_D co nnect to GPIO58 at GRB

SPI_WP_ME [26,27]

2

U24G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

R401 10K_4

R32 10K_4

R396 10K_4

R404 10K_4

+3V_PCH_ME

From Screw/EC

HSW_ULT_DDR3L

LPC

PP3300_PCH

+3V_PCH_ME

R452 100K_4

C275

0.1u/10V_4

To debug header

To PCH

+3V_S5

+3V_S5

+3V_S5

SMBUS

+3V_S5

+3V_S5

+3V_S5

+3V_S5

SML1ALERT/PCHHOT/GPIO73

+3V_S5

+3V_S5

C-LINKSPI

SMBus

1

AN2

SMBALERT/GPIO11

SML0ALERT/GPIO60

SML1CLK/GPIO75

SML1DATA/GPIO74

7 OF 19

PP3300_PCH_SUS

R430 10K_4

R448 10K_4

R437 10K_4

R106 2.2K_4

R110 2.2K_4

R126 2.2K_4

R121 2.2K_4

R118 2.2K_4

R113 2.2K_4

SMBALERT#

AP2

SMB_PCH_CLK

SMBCLK

AH1

SMB_PCH_DAT

SMBDATA

AL2

SMB0ALERT#

AN1

SMB_ME0_CLK

SML0CLK

AK1

SMB_ME0_DAT

SML0DATA

AU4

SMB1ALERT#

AU3

SMB_ME1_CLK

AH3

SMB_ME1_DAT

AF2

CL_CLKPCH_SPI_CS0#

CL_CLK

AD2

CL_DAT

CL_DATA

AF4

CL_RST#

CL_RST

SMB0ALERT#

SMB1ALERT#

SMBALERT#

SMB_PCH_CLK

SMB_PCH_DAT

SMB_ME0_CLK

SMB_ME0_DAT

SMB_ME1_CLK

SMB_ME1_DAT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

PROJECT :

PCH 2/6 (RTC/HDA/SATA/SPI)

PCH 2/6 (RTC/HDA/SATA/SPI)

PCH 2/6 (RTC/HDA/SATA/SPI)

1

LVDS Bridge

SMB_PCH_CLK [13]

SMB_PCH_DAT [13]

TP95

TP96

TP102

ZHN

ZHN

ZHN

8 39

8 39

8 39

08

3B

3B

3B

Page 9

5

4

3

2

1

Haswell ULT PCH (PCIE,USB3.0,USB2.0)

PCIE USB

+3V_S5

+3V_S5

+3V_S5

+3V_S5

HSW_ULT_DDR3L

11 OF 19

4

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

DSW

USB2N0

DSW

USB2P0

DSW

USB2N1

DSW

USB2P1

DSW

USB2N2

DSW

USB2P2

DSW

USB2N3

DSW

USB2P3

DSW

USB2N4

DSW

USB2P4

DSW

USB2N5

DSW

USB2P5

DSW

USB2N6

DSW

USB2P6

DSW

USB2N7

DSW

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

RSVD

RSVD

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USBP0- [21]

USBP0+ [21]

USBP1- [27]

USBP1+ [27]

USBP2- [16]

USBP2+ [16]

USBP3- [19]

USBP3+ [19]

USBP4- [28]

USBP4+ [28]

USBP5- [21]

USBP5+ [21]

USBP6- [28]

USBP6+ [28]

USB3_RXN0 [27]

USB3_RXP0 [27]

USB3_TXN0 [27]

USB3_TXP0 [27]

USBCOMP

R135 22.6/F_4

USBCOMP

Impedance = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC0# [26]

USB_OC2# [26]

USB Overcurrent

PP3300_PCH_SUS

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

RP2

10

9

8

7 4

10K_10P8R

LTE

MB USB3.0_A

CCD

BT

MB USB2.0

SIM USB2.0

CardReader

MB USB3.0_A

MB U3

MB U2

1

2

3

56

3

CLK_PCIE_WLANN[19]

CLK_PCIE_WLANP[19]

WLAN

CLK_PCIE_NGFFN[21]

CLK_PCIE_NGFFP[21]

NGFF

TP64

TP66

PCIE_CLKREQ_WLAN#[19]

PCIE_CLKREQ_NGFF#[21]

CLK_PCIE_REQ0#

CLK_PCIE_REQ1#

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

U24K

F10

D D

C C

PCIE_RX3-_WLAN[19]

PCIE_RX3+_WLAN[19]

WLAN

PCIE_TX3-_WLAN[19]

PCIE_TX3+_WLAN[19]

PCIE_RX2-_NGFF[21]

B B

PCIE_RX2+_NGFF[21]

NGFF

PCIE_TX2-_NGFF[21]

PCIE_TX2+_NGFF[21]

TP2

TP1

TP4

TP3

C256 0.1u/10V_4

C257 0.1u/10V_4

C254 0.1u/10V_4

C255 0.1u/10V_4

PCIE_RXN1

PCIE_RXP1

PCIE_TXN1

PCIE_TXP1

PCIE_TX3PCIE_TX3+

PCIE_TX2PCIE_TX2+

20130506 Reserve PCIE circuit.

R354 3.01K/F_4

+V1.05S_AUSB3PLL

A A

R355 *Short_4

5

PCIE_RCOMP

PCIE_IREF

E10

C23

C22

F8

E8

B23

A23

H10

G10

B21

C21

E6

F6

B22

A21

G11

F11

C29

B30

F13

G13

B29

A29

G17

F17

C30

C31

F15

G15

B31

A31

E15

E13

A27

B27

PERN5_L0

PERP5_L0

PETN5_L0

PETP5_L0

PERN5_L1

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD

RSVD

PCIE_RCOMP

PCIE_IREF

Haswell ULT PCH (CLOCK)

CLK_PCIE_REQ2#

CLK_PCIE_REQ1#

CLK_PCIE_N0

CLK_PCIE_P0

CLK_PCIE_REQ0#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

R416 10K_4

R43 10K_4

R397 10K_4

R384 10K_4

R31 10K_4

R299 10K_4

R298 10K_4

R136 10K_4

R137 10K_4

U24F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

R398 *Short_4

R253 *Short_4

PP3300_PCH

+3V

+3V

+3V

+3V

+3V

+3V

CLK_PCIE_REQ2#

CLK_PCIE_REQ1#

2

HSW_ULT_DDR3L

CLOCK

SIGNALS

6 OF 19

*18p/50V_4

XTAL24_IN

XTAL24_OUT

A25

XTAL24_IN

B25

XTAL24_OUT

K21

RSVD

M21

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

C86

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

PCLK_TPMCLK_PCI_EC

C89

*18p/50V_4R390 10K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

C253 12p/50V_4

R345

Y2

1M_4

24MHz

2 4

1 3

C252 12p/50V_4

XTAL24_IN

XTAL24_OUT

ICLK_BIAS

R353 3.01K/F_4

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLK_PCH_PCI3

CLK_PCH_PCI4

CLK_PCIE_XDPN

CLK_PCIE_XDPP

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

PCH 3/6 (PCIE/USB/CLK)

PCH 3/6 (PCIE/USB/CLK)

PCH 3/6 (PCIE/USB/CLK)

1

+V1.05S_AXCK_LCPLL

6/18 Del R132.

R14122_4

R13122_4

CLK_PCIE_XDPN [13]

CLK_PCIE_XDPP [13]

ZHN

ZHN

ZHN

9 39

9 39

9 39

09

PCLK_TPM [22]

CLK_PCI_EC [26]

3B

3B

3B

Page 10

5

4

3

2

1

PCH GPIO PU/PD

Haswell ULT PCH (GPIO,CPU/MISC,NCTF)

U24J

P1

AU2

AM7

AD6

Y1

T3

AD5

AN5

AD7

AN3

AG6

AP1

AL4

AT5

AK4

AB6

U4

Y3

P3

Y2

AT3

AH4

AM4

AG5

AG3

AM3

AM2

P2

C4

L2

N5

V2

ID2 ID1 ID0

0

1

1

1

PP3300_WLAN_EN[19,26,35]

WLAN_WAKE_L_Q

PP3300_LTE_EN[21,26]

LTE_WAKE_L_Q

BMBUSY/GPIO76

+3V_S5

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

+3V_S5

GPIO15

+3V

GPIO16

+3V

GPIO17

+3V_S5

GPIO24

DSW

GPIO27

+3V_S5

GPIO28

+3V_S5

GPIO26

+3V_S5

GPIO56

+3V_S5

GPIO57

+3V_S5

GPIO58

+3V_S5

GPIO59

+3V_S5

GPIO44

+3V_S5

GPIO47

+3V

GPIO48

+3V

GPIO49

+3V

GPIO50

HSIOPC/GPIO71

+3V_S5

GPIO13

+3V_S5

GPIO14

DSW

GPIO25

+3V_S5

GPIO45

+3V_S5

GPIO46

+3V_S5

GPIO9

+3V_S5

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

R39 10K_4

R434 10K_4

R446 10K_4

RAM_ID

AKD5JGSTL10

0 0

AKD5JGETW04

0 1

01

AKD5JGSTL10

0 0

AKD5JGETW04

0 1

AKD5JGST407

1 0

TP19

TP20

TP28

PP3300_CCD_EN

PCH_SPI_WP_D

LTE_DISABLE_L

PP3300_SSD_EN

RAM_ID2

TPM_LP_EN_L

PP3300_SSD_IO_EN

GPIO50

MODPHY_EN

RAM_ID0

GPIO14

TOUCH_INT_L

PCH_GPIO76

LTE_WAKE_L_Q

TRACKPAD_INT_L

PCH_SSD_12_EN

PCH_SSD_18_EN

GPIO24

WK_GPIO27

GPIO28

ODD_PRSNT#

GPIO56

RAM_ID1

WLAN_WAKE_L_Q

DEVSLP0

GPIO70

GPIO38

GPIO39

RAM ID

4/22 modify

Vender Freq.

Micron(4G)

Hynix(4G)

D D

4/22 modify

TRACKPAD_INT_L[25]

GPIO15[8]

LTE_DISABLE_L need PU to +3V_LTE

PCH_SPI_WP_D[8]

LTE_DISABLE_L[21]

4/23 modify

MODPHY_EN[11]

EC_IN_RW[25]

TOUCH_INT_L[16]

PP5000_CODEC_EN[23]

WLAN_DISABLE_L[19]

C C

R88 *Short_4

DEVSLP0[20]

6/24 Connect DEVSLP0 to SSD.

SPKR[8,23]

PP3300_PCH_SUS

PP3300_PCH_SUSPP3300_PCH

LTE_WAKE_L_Q

WLAN_WAKE_L_Q

I PathG Path

R101

*0_4

R146 10K_4

R145 10K_4

B B

R97

0_4

Micron(2G)

Hynix(2G)

Elpida(2G)

G PathI Path

R144

0_4

PCH_SPI_WP_D

GPIO14

TRACKPAD_INT_L

TOUCH_INT_L

5

R89 10K_4

R81 10K_4

PP3300_PCH_SUSPP3300_DSW

R150

*0_4

A A

R143 10K_4

R139 10K_4

HSW_ULT_DDR3L

+3V

DSW

GPIO

+3V

+3V

+3V

+3V

+3V

+3V

RAM_ID2

RAM_ID1

RAM_ID0

Q PN Mfr. PN

MT41K256M16HA-125:E

H5TC4G63AFR-PBA

EDJ4216EFBG-GNL-F

MT41K256M16HA-125:E

H5TC4G63AFR-PBA

EDJ4216EFBG-GNL-F

5

2

6

Q23

2N7002DW

4

10 OF 19

R45 *10K_4

R435 *10K_4

R447 *10K_4

43

1

SERIAL IO

+3V

CPU/

MISC

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

RCIN/GPIO82

PCH_OPI_RCOMP

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

PP3300_PCH_SUS

1600MHz0

1600MHz

1600MHzElpida(4G) AKD5JGST4070

1600MHz

1600MHz

1600MHz

WLAN_WAKE_L [19]

LTE_WAKE_L [21]

SERIRQ

RSVD

RSVD

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

THRMTRIP

CPU thermal trip

VCORE_PGOOD[5,32]

THRMTRIP#

EC_RCIN_L

IRQ_SERIRQ

OPI_COMP2

GPIO84

GPIO85

GPIO86

GPIO87

GPIO88

GPIO89

GPIO90

GPIO91

GPIO92

GPIO93

GPIO94

GPIO0

GPIO1

GPIO2

GPIO3

I2C0_SDA_GPIO4

I2C0_SCL_GPIO5

I2C1_SDA_GPIO6

I2C1_SCL_GPIO7

GPIO64

GPIO65

GPIO66

GPIO67

GPIO68

GPIO69

IMVP_PWRGD_3V

+1.05V_VCCST

THRMTRIP#

3

R463 49.9/F_4

+1.05V_VCCST

3

2

1

R314

2

1K_4

1 3

Q12 MMBT3904-7-F

U23

NC1VCC

2

A

GND3Y

74AUP1G07GW

EC_RCIN_L [26]

IRQ_SERIRQ [22,26]

GPIO86 [8]

I2C0_SDA_GPIO4 [25]

I2C0_SCL_GPIO5 [25]

I2C1_SDA_GPIO6 [16,28]

I2C1_SCL_GPIO7 [16,28]

GPIO66 [8]

Q11

FDV301N

R313

1K_4

+1.05V_VCCST

5

C249

0.1u/10V_4

4

4/23 modify, those

3 power enable pin

are PD 100K

already

strapping

4/23 modify, follow

Intel suggestion to

un-stuff for unused

GPIO

TRACKPAD

TOUCHSCREEN / ALS

strapping

SYS_SHDN# [26,33,34]

PP3300_PCH

12

2

R344

10K_4

IMVP_PWRGD_3V [26]

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

20130507 Add R1014 for PU DEVSLP0.

EC_RCIN_L

IRQ_SERIRQ

PCH_SSD_12_EN

PCH_SSD_18_EN

DEVSLP0

PCH_GPIO76

ODD_PRSNT#

TPM_LP_EN_L

PP3300_SSD_IO_EN

GPIO50

GPIO70

GPIO38GPIO83

GPIO39

GPIO83

GPIO84

GPIO85

GPIO87

GPIO88

GPIO89

GPIO90

GPIO91

GPIO92

GPIO93

GPIO94

GPIO0

GPIO1

GPIO2

GPIO3

GPIO64

GPIO65

GPIO67

GPIO68

GPIO69

I2C0_SDA_GPIO4

I2C0_SCL_GPIO5

I2C1_SDA_GPIO6

I2C1_SCL_GPIO7

20130613 change R331,R332 to 4.7K.

WK_GPIO27

GPIO27 : If not used then use

8.2-kΩ to 10-kΩ pull-down to GND.

5/31 Reserve R16 and R575 to PU.

GPIO28

PP3300_CCD_EN

PP3300_SSD_EN

PP3300_CCD_EN

PP3300_SSD_EN

PCH 4/6 (GPIO/MISC)

PCH 4/6 (GPIO/MISC)

PCH 4/6 (GPIO/MISC)

Monday, August 26, 2013

Monday, August 26, 2013

Monday, August 26, 2013

R44 10K_4

R36 10K_4

R399 *10K_4

R33 *10K_4

R382 10K_4

R393 10K_4

R440 10K_4

R402 10K_4

R405 *10K_4

R392 10K_4

R348 10K_4

R375 10K_4

R6 10K_4

R28 *10K_4

R8 *10K_4

R5 *10K_4

R20 *10K_4

R2 *10K_4

R4 *10K_4

R377 *10K_4

R364 *10K_4

R369 *10K_4

R365 *10K_4

R363 *10K_4

R3 *10K_4

R362 *10K_4

R366 *10K_4

R370 *10K_4

R329 *10K_4

R349 *10K_4

R335 *10K_4

R341 *10K_4

R339 *10K_4

R333 4.7K_4

R334 4.7K_4

R331 4.7K_4

R332 4.7K_4

R96 10K_4

R79 *10K_4

R49 10K_4

R16 *10K_4

R575 *10K_4

R15 100K_4

R570 100K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZHN

ZHN

ZHN

1

10

PP3300_PCH

PP3300_DSW

PP3300_PCH_SUS

10 39

10 39

10 39

GSPUARTI2C SDIO useless GPIO

3B

3B

3B

Page 11

5

C225 *1u/6.3V_4

C13 1u/6.3V_4

C29 1u/6.3V_4

PP1050_PCH

D D

+1.05V_DCPSUS2

C87

*1u/6.3V_4

PP3300_DSW

PP3300_PCH_SUS

R48 *SHORT_8

Deep Sx

Non Deep Sx

PP3300_PCH

C C

PP1050_PCH

0412 MOW-WW15 a 0.47uF cap between VccDSW3_3

and DcpSusByp is required if the 1.9A inrush

current requirement cannot meet

+V1.05DX_MODPHY

*10u/6.3V_6

R54 *SHORT_6

R46 *0_6

C37

1u/6.3V_4

R22 *SHORT_8

C17 1u/6.3V_4

PP3300_PCH_SUS

1.741A

C32

*1u/6.3V_4

C5

+V1.05S_AIDLE

C18

*1u/6.3V_4

+V3.3DX_1.5DX_1.8DX_AUDIO

0.114A

PP3300_PCH_SUS

41mA

C14

22u/6.3V_8

PP1050_PCH

63mA

PCH VCCHSIO Power

C227

PP5000

B B

PP3300_PCH

PP3300_DSW

R301

100K_4

MODPHY_EN[10]

+V1.05DX_MODPHY +V1.05S_AUSB3PLL +V1.05DX_MODPHY +V1.05S_ASATA3PLL

A A

L11 2.2uH/210mA_8

22u/6.3V_8

5/21 change 47uF to 22uF. 5/21 change 47uF to 22uF.

C237

R296

*100K_4

5

R295

*100K_4

1 2

R297 *Short_4

C243

*47u/6.3V_8

0.1u/10V_4

12

C228

1u/6.3V_4

C250

1u/6.3V_4

U21

SLG59M1470V

1

VDD

2

D_01

D_02_033S_02_03

GND

S_01

ON

9

12

C226

*0.047u/25V_4

L8 2.2uH/210mA_8

4

1.838A

+V1.05S_AUSB3PLL

+V1.05S_ASATA3PLL

+V1.05S_APLLOPI

+1.05V_DCPSUS3

C84 22u/6.3V_8

+VCCPDSW

+V3.3S_VCCPCORE

+V1.05S_AXCK_DCB

+V1.05S_AXCK_LCPLL

C48 1u/6.3V_4

8

7

5

20130513 C277 reserve by vendor.

C240

22u/6.3V_8

4

U24M

K9

VCCHSIO

L10

VCCHSIO

M9

VCCHSIO

N8

VCC1_05

P9

VCC1_05

B18

VCCUSB3PLL

B11

VCCSATA3PLL

Y20

RSVD

AA21

VCCAPLL

W21

VCCAPLL

J13

DCPSUS3

AH14

VCCHDA

AH13

DCPSUS2

AC9

VCCSUS3_3

AA9

VCCSUS3_3

AH10

VCCDSW3_3

V8

VCC3_3

W9

VCC3_3

J18

VCCCLK

K19

VCCCLK

A20

VCCACLKPLL

J17

VCCCLK

R21

VCCCLK

T21

VCCCLK

K18

RSVD

M20

RSVD

V21

RSVD

AE20

VCCSUS3_3

AE21

VCCSUS3_3

R303 *SHORT_8

R304 *SHORT_8

12

C229

0.1u/10V_4

42mA41mA

C234

*47u/6.3V_8

3

Haswell ULT PCH (Power)

HSW_ULT_DDR3L

+V1.05DX_MODPHYPP1050_PCH_SUS

GPIO/LPC

LPT LP POWER

C258

1u/6.3V_4

HSIO

OPI

USB3

HDA

VRM

VCCAPLL power

PCH HDA Power

+3V_ADO

RTC

SPI

CORE

THERMAL SENSOR

SERIAL IO

SUS OSCILLATOR

USB2

13 OF 19

PP1050_PCH +V1.05S_AXCK_DCB

VCCSUS3_3

DCPSUSBYP

DCPSUSBYP

L9 2.2uH/210mA_8

4/23

modify,Intel

suggest 0 ohm

R17 *SHORT_8

*47u/6.3V_8

VCCRTC

DCPRTC

VCCSPI

VCCASW

VCCASW

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCCASW

VCCASW

VCCASW

DCPSUS1

DCPSUS1

VCCTS1_5

VCC3_3

VCC3_3

VCCSDIO

VCCSDIO

DCPSUS4

RSVD

VCC1_05

VCC1_05

C241

47u/6.3V_8

C9

AH11

AG10

AE7

Y8

AG14

AG13

J11

H11

H15

AE8

AF22

AG19

AG20

AE9

AF9

AG8

AD10

AD8

J15

K14

K16

U8

T9

AB8

AC20

AG16

AG17

11mA

PP3300_PCH

R128 *0_6

+V3.3DX_1.5DX_1.8DX_AUDIO

R125 *SHORT_6

3

C88

1u/6.3V_4

Place close to ball

+V3.3A_DSW_PRTCSUS

+VCCRTCEXT

+V3.3M_PSPI

PCH_VCC_1_1_20

PCH_VCC_1_1_21

+V1.05S_CORE_PCH

+PCH_VCCDSW

+1.05V_DCPSUS1

0.109A

+V3.3S_VCCSDIO

+1.05V_DCPSUS4

0.2A

C235

47u/6.3V_8

+V1.05S_APLLOPIPP1050_PCH

57mA

C15

*47u/6.3V_8

C60

1u/6.3V_4

5/21 change 0.1uF to 1uF.

2

18mA

R52 *SHORT_6

R53 *SHORT_6

C73

1u/6.3V_4

+V1.05M_VCCASW

C51

*1u/6.3V_4

3mA

1mA

C40

*1u/6.3V_4

+V1.05S_VCCUSBCORE

5/21 modify to stuff.

C30

1u/6.3V_4

2

R67 *SHORT_6

C74

1u/6.3V_4

C75

0.1u/10V_4

C47

0.1u/10V_4

PP1050_PCH

PP1050_PCH

C78

C52

1u/6.3V_4

1u/6.3V_4

+V1.05M_VCCASW

0.658A

C50

C61

22u/6.3V_8

1u/6.3V_4

+V1.5S_VCCATS

+V3.3S_VCCPTS

17mA

R84 *SHORT_8

C79

1u/6.3V_4

PP1050_PCH +V1.05S_AXCK_LCPLL

L10 2.2uH/210mA_8

PP3300_PCH_SUS

PP3300_RTC

C57

C58

0.1u/10V_4

1u/6.3V_4

C36

10u/6.3V_6

R68 *SHORT_8

R9 *SHORT_6

R18 *SHORT_6

C31

5/21 change 1uF to 0.1uF.

0.1u/10V_4

R19 *SHORT_6

C39

1u/6.3V_4

PP1050_PCH

7/11 R40 connection

change to PP3300_PCH

by leakage.

R42 *0_6

R40 0_6

C33

0.1u/10V_4

R34 *SHORT_8

PP1050_PCH

PP1500_PCH_TS

PP3300_PCH

PP3300_PCH

31mA

C236

47u/6.3V_8

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

Date: Sheet of

Monday, August 26, 2013

C242

47u/6.3V_8

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

PCH 5/6 (POWER)

PCH 5/6 (POWER)

PCH 5/6 (POWER)

1

PP3300_DSW

PP3300_PCH

PP1050_PCH

+VCCPDSW

+PCH_VCCDSW

5/21 modify to stuff.

C251

1u/6.3V_4

1

C63

0.47u/25V_6

place near CPU

ZHN

ZHN

ZHN

11 39

11 39

11 39

11

3B

3B

3B

Page 12

5

4

3

2

1

Haswell ULT (GND)

HSW_ULT_DDR3L

D D

C C

B B

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U24N

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

U24O

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

HSW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

G18

G22

H13

HSW_ULT_DDR3L

U24P

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

VSS

16 OF 19

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

VSS_SENSE_R

U24R

AT2

RSVD

AU44

RSVD

AV44

RSVD

D15

RSVD

F22

RSVD

H22

RSVD

J21

RSVD

R374 *Short_4

R373 100/F_4

HSW_ULT_DDR3L

18 OF 19

VSS_SENSE [32]

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

12

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

U24Q

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

TP_DC_TEST_AY60

TP106

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_B2

A A

5

TP65

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61