5

4

3

2

1

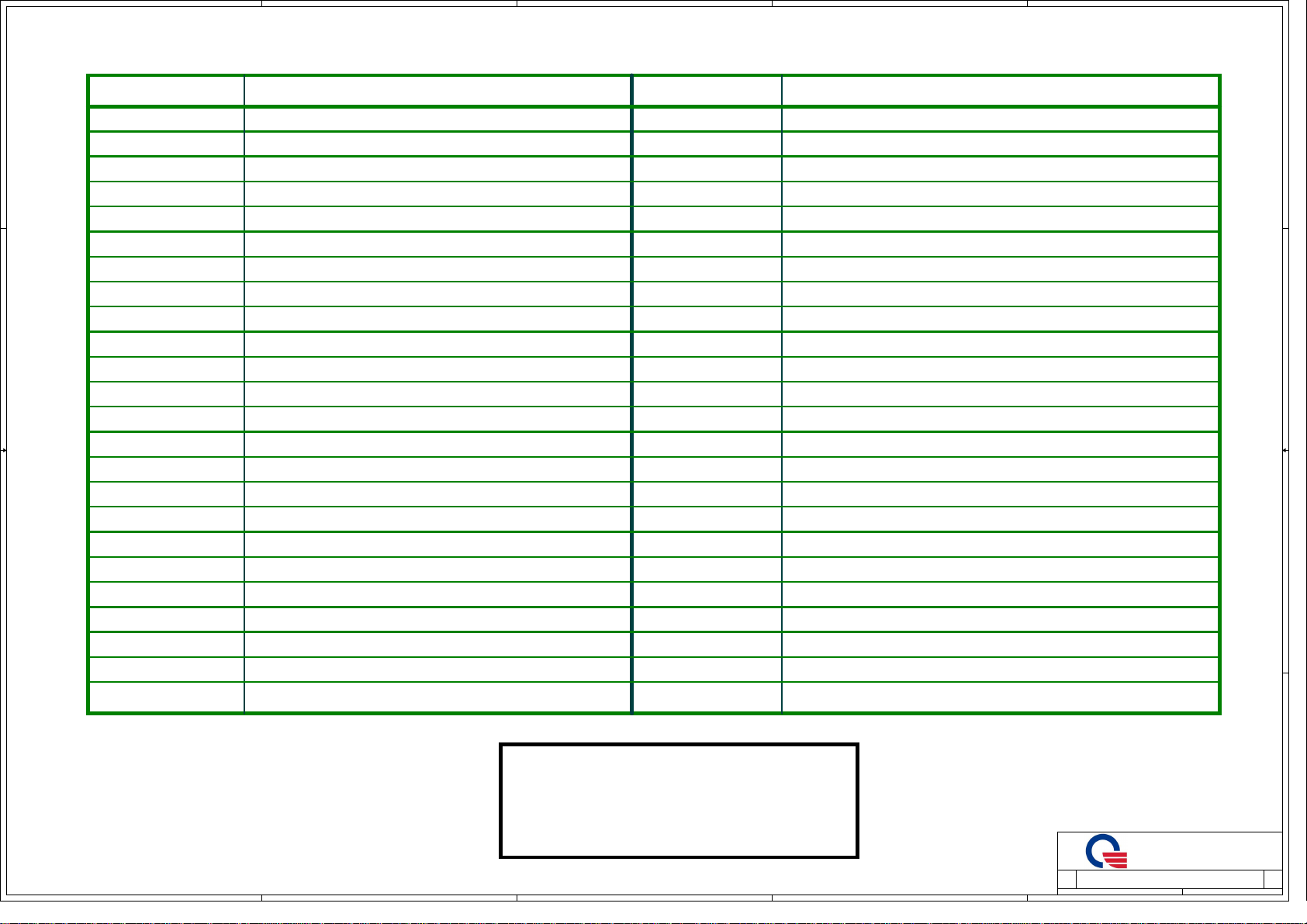

TABLE OF CONTENT

PAGE

D D

03

04

05

06

07

08

09

C C

B B

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

TITLE

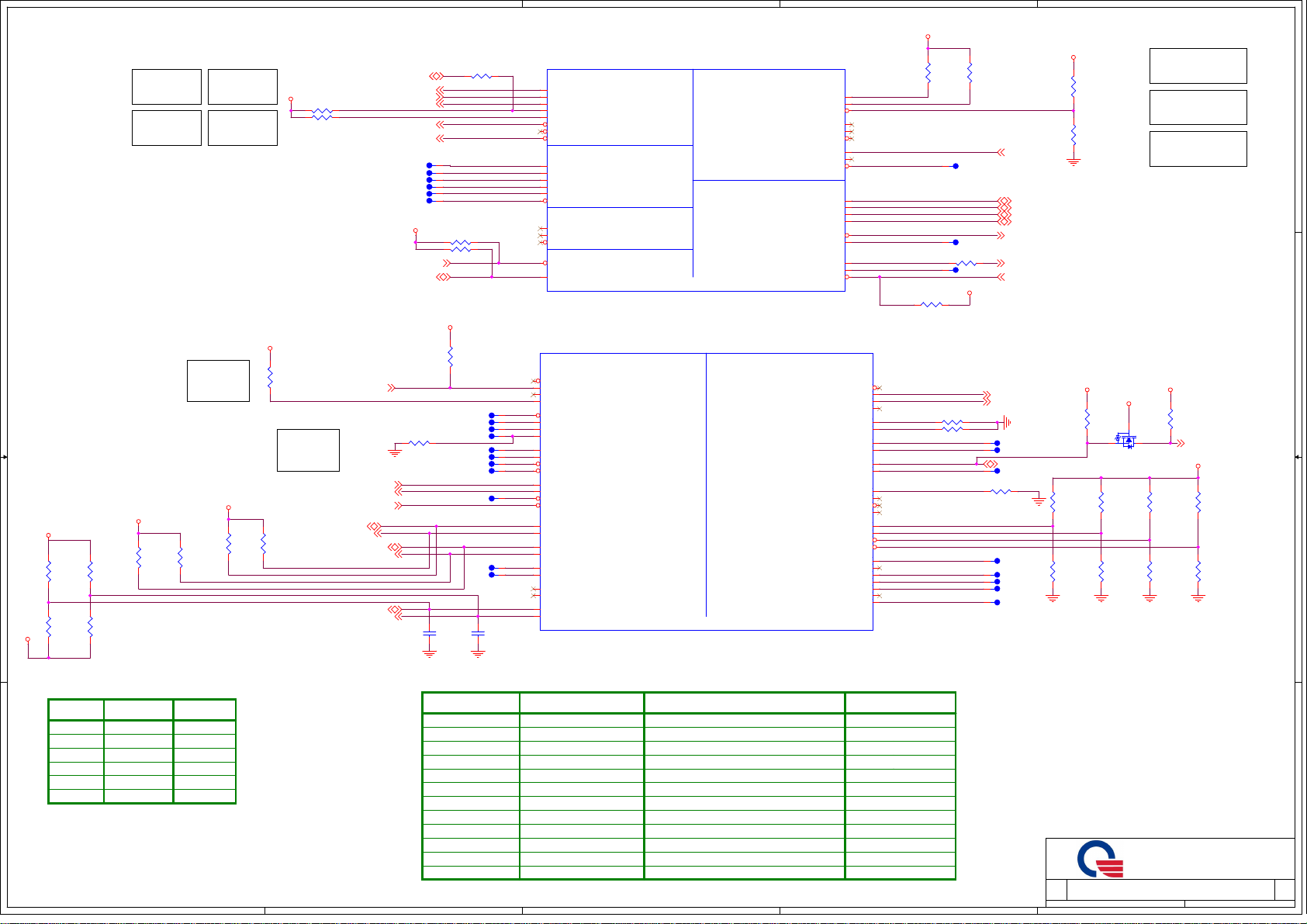

BLOCK DIAGRAM02

SKL ULT SYSTEM CTL

SKL ULT - DEBUG

SKL ULT - DDR3L CH A

SKL ULT - DDR3L CH B

SKL ULT - PCIE/SATA/USB/DSI

SKL ULT - I2S/DMIC/SD/UFS

SKL ULT - SPI/LPC/SMB/ISH

SKL ULT - SERVO

SKL ULT - CORE POWER

SKL ULT - GT POWER

SKL ULT - IO/MEM/SA POWER

SKL ULT - RESERVED

SKL ULT - GND

SPI TPM & BIOS SPI

LPDDR3 CH A

LPDDR3 CH B

EMMC

LED/TEMP SENSORS

EDP PANEL/Hall Sensor

USB3.0

USBPD EC

USBC PORT

HDMI

PAGE

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

TITLE

NGFF-WIFI/BT/DB

TP & KB CONN

NAU88L25/MAX98357

MEC1322

Thermal Protect

USBPD

BATT CHARGER

PMIC-1

PMIC-2

POWER GATES 1

POWER GATES 2

IMVP8

IMVP8 CORE

IMVP8 GT/SA

Power Tree

Change List

EU1B2 ,EUCP4040 ,U135 ,X5

CN4 ,J1P2 ,CN3 ,LCP4022 ,LCP4041 ,J8L1 ,U8 ,SW1 ,J1C1 ,U97 ,U98

A A

,CN12 ,CN8 ,U1 ,U23 ,UAP1012 ,CRCP4008 ,CRCP4009 ,CRCP4010

,CRCP4011 ,CRCP4014 ,CRCP4043 ,CRCP4042 ,CRCP4044 ,UCP4034

,UCP4036 ,UCP4040

5

4

Notes:

Part Value Prefix : "*" means no stuff

Net Value suffix : "*" means Low Active

Part : "*" means NO STUFF

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

Block Diagram

Block Diagram

Block Diagram

1

ZHD

ZHD

ZHD

8A

8A

1 41Tuesday, May 23, 2017

1 41Tuesday, May 23, 2017

1 41Tuesday, May 23, 2017

8A

5

www.schematic-x.blogspot.com

4

3

2

1

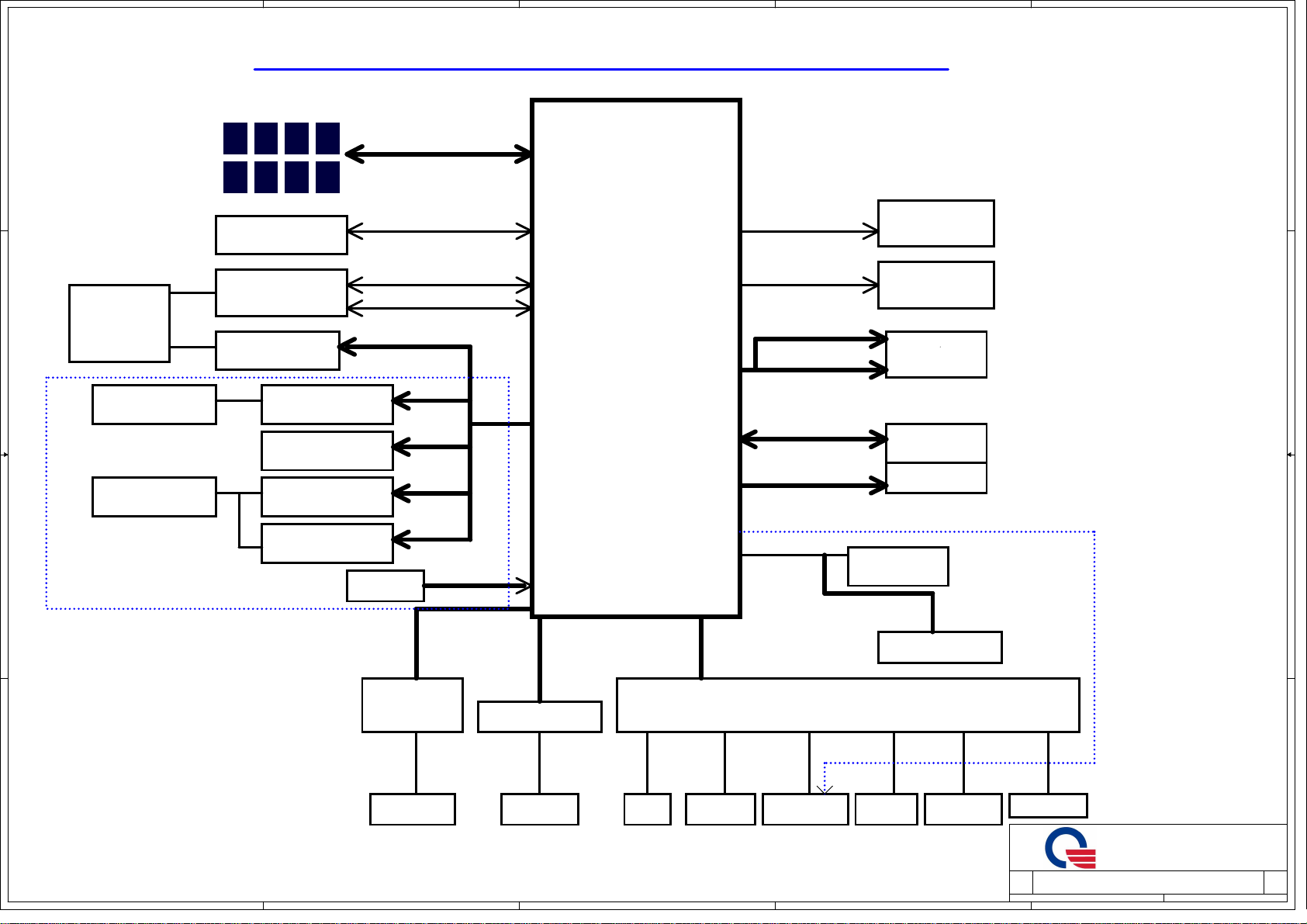

ZHD SKL ULT SYSTEM BLOCK DIAGRAM

D D

Memory Down

02

Dual Channel LPDDR III

IMC

SKY LAKE ULT

MCP

EMMC

USB TYPE C MUX

DP*4

USB TYPE C

C C

USB TYPE C

CONN.

USB2.0

EMMC

USB3.0

Integrated PCH

DDI

CHARGER

Micro SD(I/O)

GL3213

(cardreader)

CCD(Camera)

USB3 Re-driverUSB3.0(I/O)

USB3.0/2.0

USB3.0/2.0

USB2.0

USB3.0

eDP

DP

USB3.0/2.0

PCI-E x1

USB2.0

EDP

USB3

USB2

eDP Conn.

(Touch)

HDMI Conn.

USB3 CONN.

NGFF

WLAN+BT

Blue Tooth

USB Charger

B B

D-MIC

DB Board

USB2.0

Int. D-MIC

I2S

LPC

CLK

I2C_1

SPI

SPI ROM

128M

TPM(SLB9670)

NAU88L25

AUDIO CODEC

A A

AUDIO JACK

5

4

MAX98357AETE+T*

Speaker

LED

Charger/Power

3

K/B Con.

Touch PAD

EC

MEC1322

HALL

SENSOR

2

Fan Driver

(Fan signal)

SPI 512K

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZHD

ZHD

ZHD

2 41Tuesday, May 23, 2017

2 41Tuesday, May 23, 2017

2 41Tuesday, May 23, 2017

1

8A

8A

8A

5

4

3

2

1

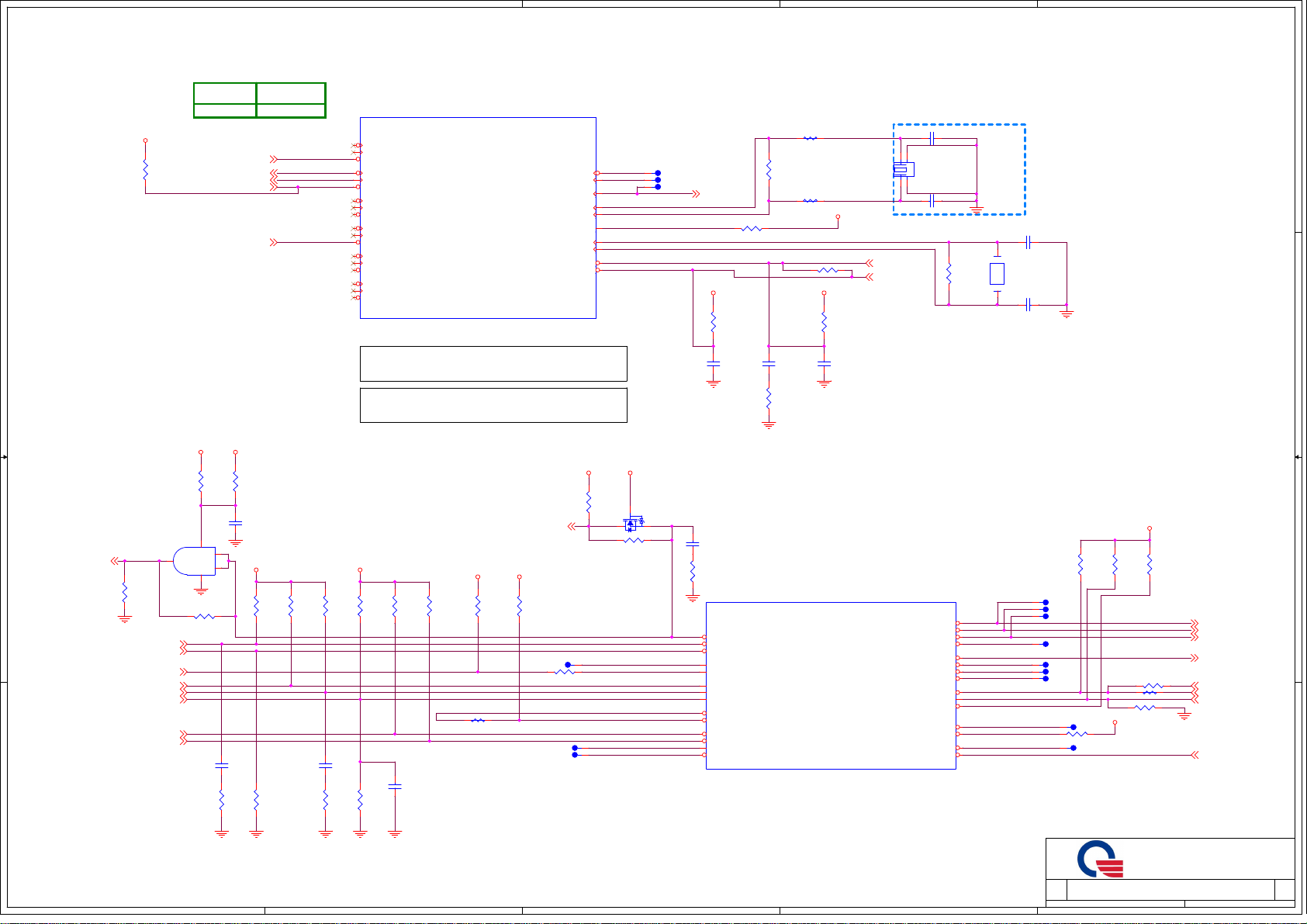

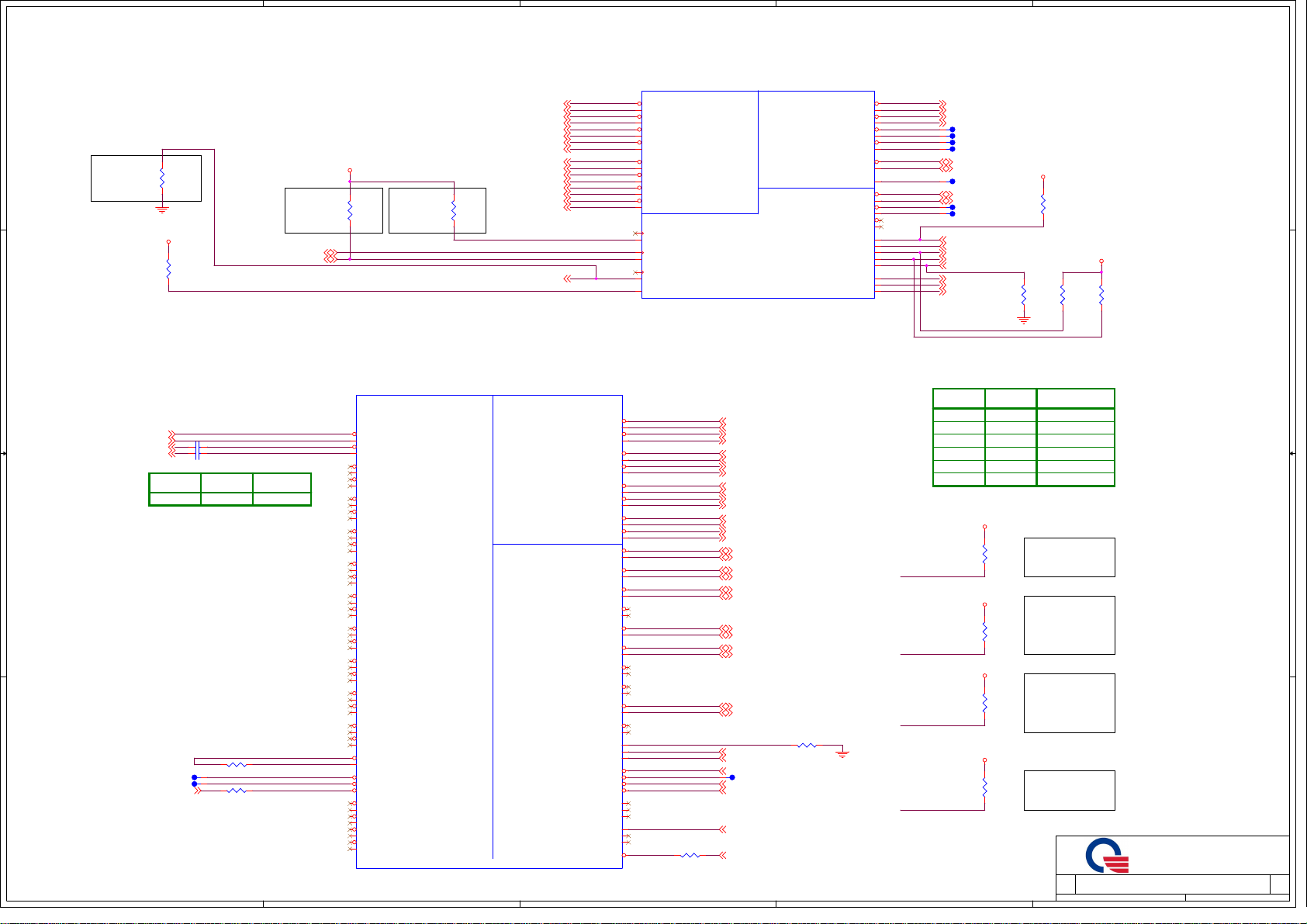

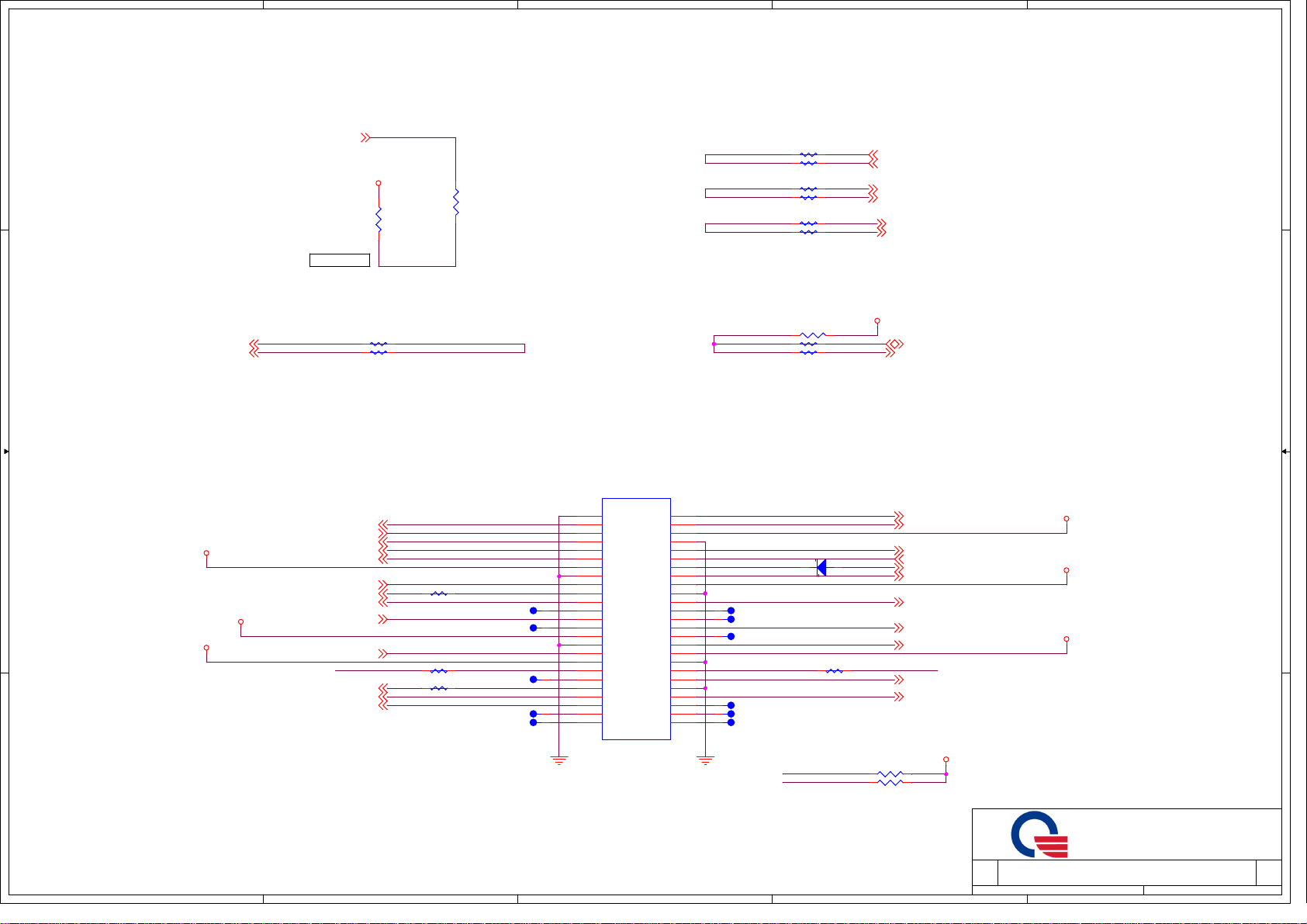

SKL ULT - SYSTEM CTL

PCIe Clock ASSIGNMENT

WIFI1

D D

C C

BUF_PCH_PLT_RST*[19,26,29]

B B

A A

+V3P3A

R1113

100K_2

4

RAP3047

*100K_2

RAP3048 *0_4

PCH_SYSRST*[10,29]

PCH_RSMRST*[29]

ROP_VCCST_PWRGD[33]

ROP_SYS_PWROK[33]

PCH_PWROK[33,37]

ROP_DSW_PWROK[33,34]

PCIE_WAKE*[26]

EC_PCH_WAKE*[29]

TRACKPAD_INT*[4,27,29]

WIFI_PCIE_CLK_DN[26]

WIFI_PCIE_CLK_DP[26]

WIFI_CLK_REQ*[26]

AUDIO_INT_WAK*[9]

RAP3046

*0_4

1

2

3 5

U135

SN74AHC1G08DCKR

+V3P3A+V3P3S

RAP3045

0_4

CPM4431

0.1U/16V_4

+V3P3S

C6001

*0.1U/16V_4

R6001

*10/F_4

RAP1003

10K_2

RAP1067

1M_2

RAP1004

100K_2

CLKOUT_SRC_N_0

D42

CLKOUT_SRC_P_0

C42

GPP_B_5_SRCCLKREQB_0

AR10

CLKOUT_SRC_N_1

B42

CLKOUT_SRC_P_1

A42

GPP_B_6_SRCCLKREQB_1

AT7

CLKOUT_SRC_N_2

D41

CLKOUT_SRC_P_2

C41

GPP_B_7_SRCCLKREQB_2

AT8

CLKOUT_SRC_N_3

D40

CLKOUT_SRC_P_3

C40

GPP_B_8_SRCCLKREQB_3

AT10

CLKOUT_SRC_N_4

B40

CLKOUT_SRC_P_4

A40

GPP_B_9_SRCCLKREQB_4

AU8

CLKOUT_SRC_N_5

E40

CLKOUT_SRC_P_5

E38

GPP_B_10_SRCCLKREQB_5

AU7

REV = 1

SRTC REST_N

0 - SAVE ME RTC REGISTER WHEN BATTERY IS REMOVED

1 - CLEAR ME RTC REGISTER

RTESTB

1 - SAVE REGISTER BIT IN RTC WELL (DEFAULT)

0 - RESETS THER REGISTER BITS IN THE RTC WELL

+V3P3A_DSW

RAP1061

RAP1005

10K_2

R3587

100K_2

RAP1011

10K_2

CAP14472

*0.1u/10V_2

100K_2

C6003

*0.1U/16V_4

R6003

*10/F_4

U80J

SKYLAKE_ULT

CLOCK SIGNALS

10 OF 20

+V1P00S_VCCST

RAP1008

100K_2

RAP1062

1K_2

RAP1459 *SHORT_2

TPM_PLTRST#[16]

+V3P3A

RAP1002

*10K_2

RAP1064 60.4_4

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD_8_SUSCLK

XTAL_IN

XTAL_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRSTB

RTESTB

+V3P3A +V1P8S

TP39

TP17

TP18

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

RAP3049

10K_2

RAP3051 *0_2

PCH_PLT_RST*

PM_CPUPWRGD

VCCST_PWRGD_MCP

PCH_SUSPWRACK*

PCH_SUSACK*

PM_LANPHY_ENABLE

USB_WAKEOUT_INTRUDET*

QPM3390

PJA138K

321

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTC_X1

RTC_X2

SRTCRST*

RTC_RST*

TP273

TP272

TP120

SUS_CLK [26]

RAP1091 2.7K/F_4

RAP1072

20K_4

CAP1073

1U/6.3V_4

C6004

*0.1U/16V_4

R6008

*10/F_4

For ESD

GPP_B_13_PLTRSTB

AN10

SYS_RESETB

B5

RSMRSTB

AY17

CPUPWRGD

A68

VCCST_PWRGD

B65

SYS_PWROK

B6

PCH_PWROK

BA20

DSW_PWROK

BB20

GPP_A_13_SUSWARNB_SUSPWRDNACK

AR13

GPP_A_15_SUSACKB

AP11

WAKEB

BB15

GPD_2_LAN_WAKEB

AM15

GPD_11_LANPHYPC

AW17

GPD_7_USB2_WAKEOUTB

AT15

REV = 1

RAP1089 *SHORT_4

RAP1087

1M_4

RAP1090 *SHORT_4

RAP3052 *0_2

C6002

*0.1U/16V_4

R6002

*10/F_4

For ESD (ZAS)

SYSTEM POWER MANAGEMENT

+VCCF24NS_1P0

+V3P3A_RTC+V3P3A_RTC

RAP1078

20K_4

CAP1079

1U/6.3V_4

U80K

SKYLAKE_ULT

11 OF 20

XTAL24_IN_R

XTAL24_OUT_R

SRTCRST* [29]

RTC_RST* [29]

GPP_B_11_EXT_PWR_GATEB

C186 33P/50V_4

4

3

X5

24MHz,30ppm

1

2

C187 33P/50V_4

GPP_B_12_SLP_S0B

GPD_4_SLP_S3B

GPD_5_SLP_S4B

GPD_10_SLP_S5B

SLP_SUSB

SLP_LANB

GPD_9_SLP_WLANB

GPD_6_SLP_AB

GPD_3_PWRBTNB

GPD_1_ACPRESENT

GPD_0_BATLOWB

GPP_A_11_PMEB

INTRUDERB

GPP_B_2_VRALERTB

Trace length < 1000 mils

RTC_X1

RAP1088

10M_4

RTC_X2

C291 15P/50V_4

12

X6

32.768KHz,20ppm

C289 15P/50V_4

X6: Metal

AT11

AP15

BA16

PCH_SLP_S5*

AY16

AN15

PCH_SLP_LAN*

AW15

PCH_SLP_WLAN*

BB17

PCH_SLP_SA*

AN16

BA15

AY15

PCH_BATLOW*

AU13

EC_HID_INT*

AU11

SM_INTRUDER*

AP16

MPHY_EXT_PWR_GATE*

AM10

AM11

RAP3020

1M_2

TP100

TP101

TP102

TP75

TP79

TP20

TP78

TP21

RAP1075 1M_4

TP22

RAP1081

*100K_2

RAP1458 *0_2

RAP1457 *SHORT_2

R5150 100K/F_4

+V3P3A_RTC

+V3P3A_DSW

RAP1077

10K_2

PM_SLP_S0* [29,33]

PM_SLP_S3* [29,33,35,36]

PM_SLP_S4* [29,33,34,35]

PCH_EC_SLP_SUS* [29]

ROP_PCH_PWRBTN* [33]

EC_PCH_PWRBTN* [29]

EC_PCH_ACPRESENT [29]

HSJ_MIC_DET [28]

For ESD For ESD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

SKL ULT SYSTEM CTL

SKL ULT SYSTEM CTL

SKL ULT SYSTEM CTL

ZHD

ZHD

ZHD

3 41Tuesday, May 23, 2017

3 41Tuesday, May 23, 2017

1

3 41Tuesday, May 23, 2017

8A

8A

8A

5

4

3

2

1

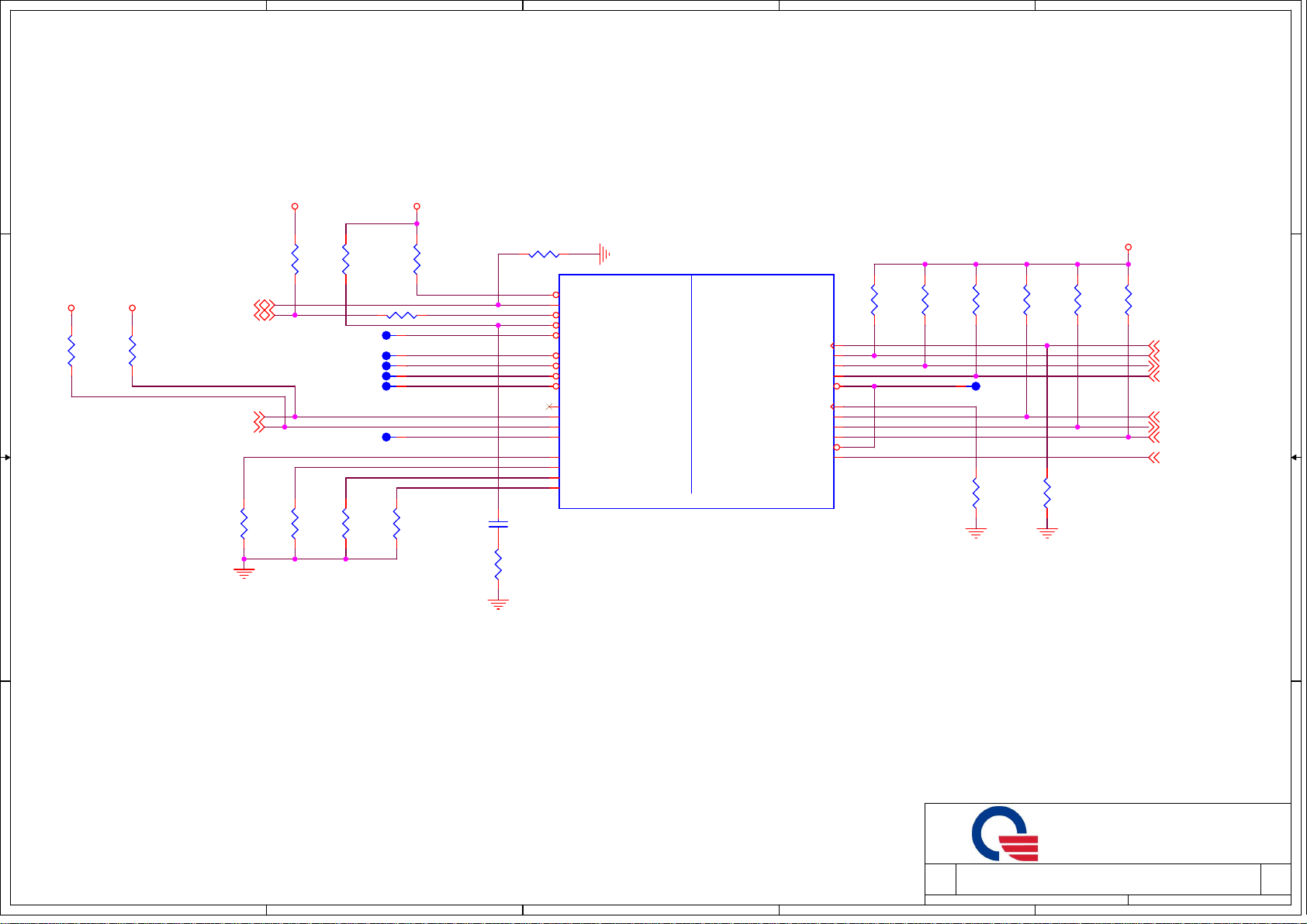

SKL ULT - DEBUG

D D

+V1P00S_VCCSTG

R66

1K/F_4

+V3P3A

C C

B B

RAP1452

10K_2

+V3P3A

RAP1453

100K_2

SOC_PROCHOT*[29]

TCH_PNL_INTR*[7,21]

TRACKPAD_INT*[3,27,29]

PECI[29]

R45

49.9_4

R46

49.9_4

+V1P00S_VCCST

R88

1K_2

R1180 499/F_4

TP98

TP268

TP269

TP23

TP24

TP242

R47

49.9_4

R49

*49.9_4

SOC_CATERR*

PECI

SOC_THRMTRIP*

XDP_BPM<2>

XDP_BPM<3>

CPU_POPIRCOMP

PCH_POPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

R48

49.9_4

R5037 365/F_4

CATERR_N

D63

PECI

A54

PROCHOT_N

C65

THRMTRIPB

C63

SKTOCC_N

A65

MBP_N[0]

C55

MBP_N[1]

D55

MBP_N[2]

B54

MBP_N[3]

C56

GPP_E_3_CPU_GP_0

A6

GPP_E_7_CPU_GP_1

A7

GPP_B_3_CPU_GP_2

BA5

GPP_B_4_CPU_GP_3

AY5

CPU_POPIRCOMP

AT16

PCH_POPIRCOMP

AU16

EDRAM_OPIO_RCOMP

H66

CPU_EOPIO_RCOMP

H65

C6005

*0.1U/16V_4

R6009

*10/F_4

REV = 1

U80D

SKYLAKE_ULT

4 OF 20

JTAGCPU MISC

CPU_JTAG_TCK

CPU_JTAG_TDI

CPU_JTAG_TDO

CPU_JTAG_TMS

CPU_JTAG_TRST_N

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRSTB

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

R129

*49.9_4

XDP_JTAG_TRST*

PCH_JTAG_TCLK

R130

*49.9_4

R131

*49.9_4

TP271

R136

49.9_4

R132

49.9_4

+V1P00S_VCCSTG

R133

49.9_4

R138

49.9_4

R134

49.9_4

CPU_JTAG_TCLK [10]

CPU_JTAG_TDI [10]

CPU_JTAG_TDO [10]

CPU_JTAG_TMS [10]

PCH_JTAG_TDI [10]

PCH_JTAG_TDO [10]

PCH_JTAG_TMS [10]

XDP_TCLK_JTAGX [10]

For ESD

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

PROJECT :

Size Document Number Rev

Size Document Number Rev

SKL ULT - DEBUG

SKL ULT - DEBUG

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

SKL ULT - DEBUG

ZHD

ZHD

ZHD

4 41Tuesday, May 23, 2017

4 41Tuesday, May 23, 2017

4 41Tuesday, May 23, 2017

1

8A

8A

8A

5

4

3

2

1

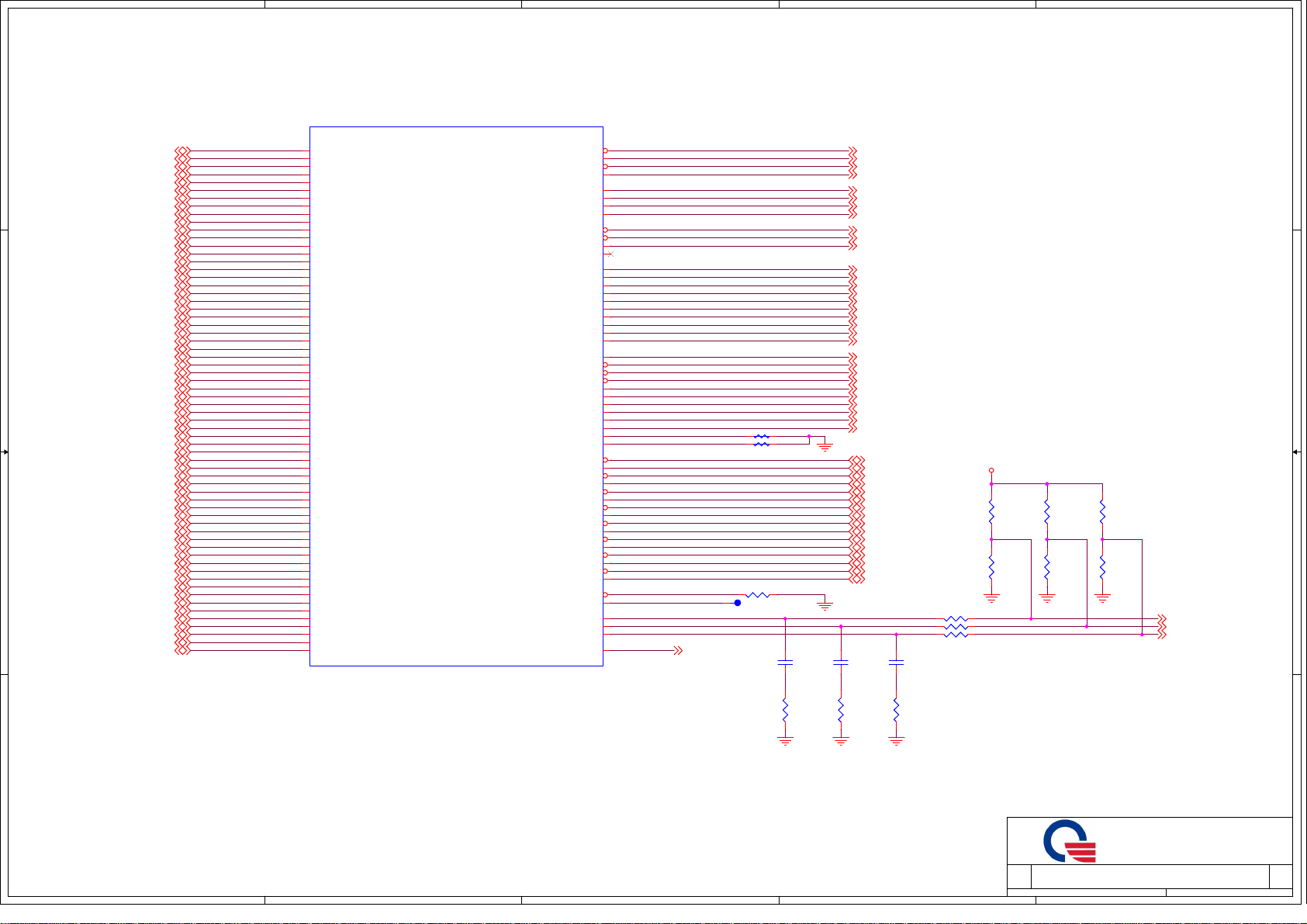

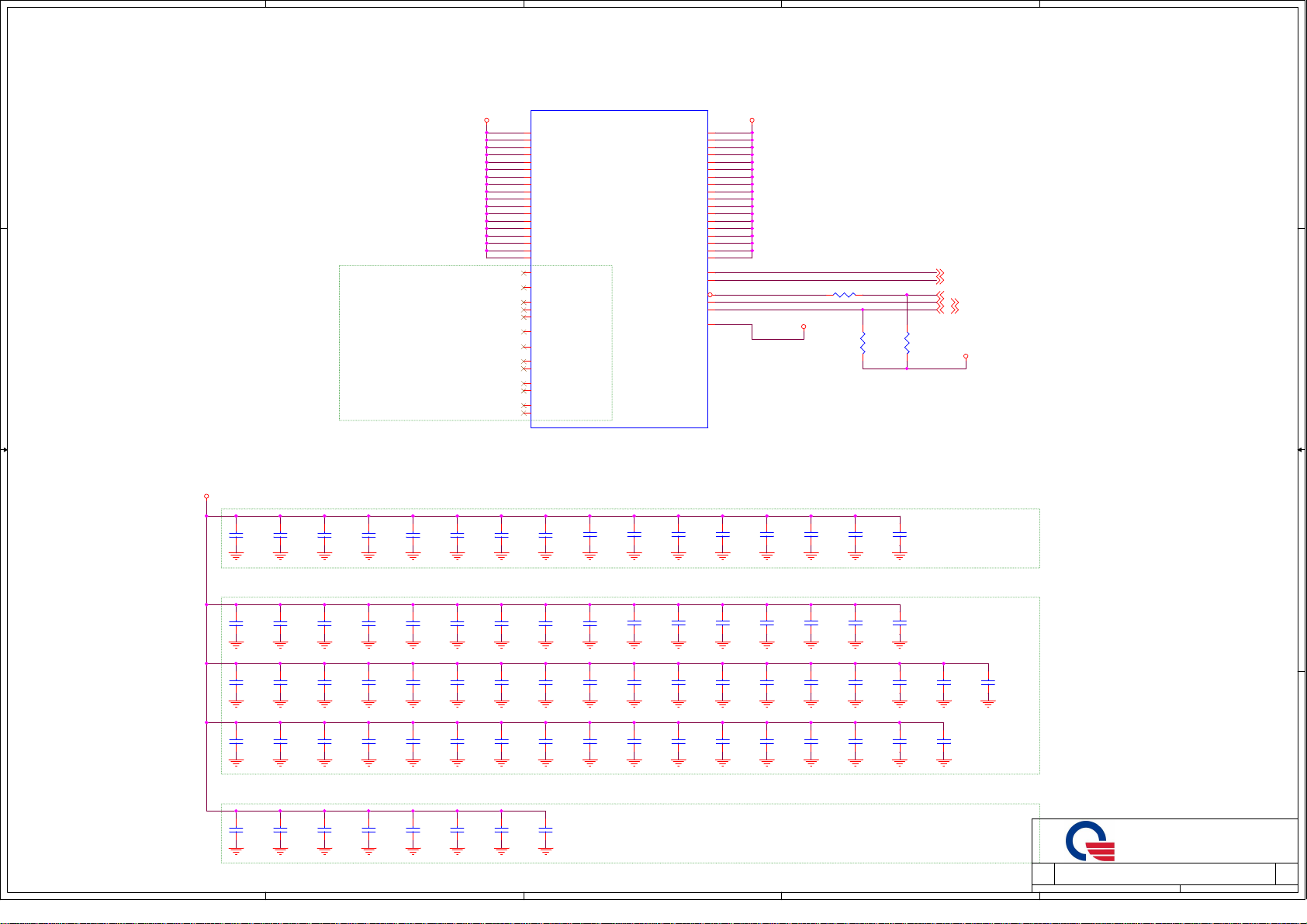

SKL ULT - DDR CHANNEL A

U80B

D D

DDRDQ_IL00_NIL00[0]

M_A_DQ<0>[17] M_A_CLK_DDR_DN*<0> [17]

M_A_DQ<1>[17]

M_A_DQ<2>[17]

M_A_DQ<3>[17]

M_A_DQ<4>[17]

M_A_DQ<5>[17]

M_A_DQ<6>[17]

M_A_DQ<7>[17]

M_A_DQ<8>[17]

M_A_DQ<9>[17]

M_A_DQ<10>[17]

M_A_DQ<11>[17]

M_A_DQ<12>[17]

M_A_DQ<13>[17]

M_A_DQ<14>[17]

M_A_DQ<15>[17]

M_A_DQ<16>[17]

M_A_DQ<17>[17]

M_A_DQ<18>[17]

M_A_DQ<19>[17]

M_A_DQ<20>[17]

M_A_DQ<21>[17]

M_A_DQ<22>[17]

M_A_DQ<23>[17]

C C

B B

M_A_DQ<24>[17]

M_A_DQ<25>[17]

M_A_DQ<26>[17]

M_A_DQ<27>[17]

M_A_DQ<28>[17]

M_A_DQ<29>[17]

M_A_DQ<30>[17]

M_A_DQ<31>[17]

M_A_DQ<32>[17]

M_A_DQ<33>[17]

M_A_DQ<34>[17]

M_A_DQ<35>[17]

M_A_DQ<36>[17]

M_A_DQ<37>[17]

M_A_DQ<38>[17]

M_A_DQ<39>[17]

M_A_DQ<40>[17]

M_A_DQ<41>[17]

M_A_DQ<42>[17]

M_A_DQ<43>[17]

M_A_DQ<44>[17]

M_A_DQ<45>[17]

M_A_DQ<46>[17]

M_A_DQ<47>[17]

M_A_DQ<48>[17]

M_A_DQ<49>[17]

M_A_DQ<50>[17]

M_A_DQ<51>[17]

M_A_DQ<52>[17]

M_A_DQ<53>[17]

M_A_DQ<54>[17]

M_A_DQ<55>[17]

M_A_DQ<56>[17]

M_A_DQ<57>[17]

M_A_DQ<58>[17]

M_A_DQ<59>[17]

M_A_DQ<60>[17]

M_A_DQ<61>[17]

M_A_DQ<62>[17]

M_A_DQ<63>[17]

AL71

AL68

DDRDQ_IL00_NIL00[1]

DDRDQ_IL00_NIL00[2]

AN68

DDRDQ_IL00_NIL00[3]

AN69

AL70

DDRDQ_IL00_NIL00[4]

DDRDQ_IL00_NIL00[5]

AL69

AN70

DDRDQ_IL00_NIL00[6]

DDRDQ_IL00_NIL00[7]

AN71

DDRDQ_IL01_NIL01[0]

AR70

AR68

DDRDQ_IL01_NIL01[1]

DDRDQ_IL01_NIL01[2]

AU71

AU68

DDRDQ_IL01_NIL01[3]

DDRDQ_IL01_NIL01[4]

AR71

DDRDQ_IL01_NIL01[5]

AR69

AU70

DDRDQ_IL01_NIL01[6]

DDRDQ_IL01_NIL01[7]

AU69

AF65

DDRDQ_IL10_NIL02[0]

DDRDQ_IL10_NIL02[1]

AF64

DDRDQ_IL10_NIL02[2]

AK65

AK64

DDRDQ_IL10_NIL02[3]

DDRDQ_IL10_NIL02[4]

AF66

AF67

DDRDQ_IL10_NIL02[5]

DDRDQ_IL10_NIL02[6]

AK67

DDRDQ_IL10_NIL02[7]

AK66

AF70

DDRDQ_IL11_NIL03[0]

DDRDQ_IL11_NIL03[1]

AF68

AH71

DDRDQ_IL11_NIL03[2]

DDRDQ_IL11_NIL03[3]

AH68

DDRDQ_IL11_NIL03[4]

AF71

AF69

DDRDQ_IL11_NIL03[5]

DDRDQ_IL11_NIL03[6]

AH70

AH69

DDRDQ_IL11_NIL03[7]

DDRDQ_IL02_NIL04[0]

BB65

DDRDQ_IL02_NIL04[1]

AW65

AW63

DDRDQ_IL02_NIL04[2]

DDRDQ_IL02_NIL04[3]

AY63

BA65

DDRDQ_IL02_NIL04[4]

DDRDQ_IL02_NIL04[5]

AY65

DDRDQ_IL02_NIL04[6]

BA63

BB63

DDRDQ_IL02_NIL04[7]

DDRDQ_IL03_NIL05[0]

BA61

AW61

DDRDQ_IL03_NIL05[1]

DDRDQ_IL03_NIL05[2]

BB59

DDRDQ_IL03_NIL05[3]

AW59

BB61

DDRDQ_IL03_NIL05[4]

DDRDQ_IL03_NIL05[5]

AY61

BA59

DDRDQ_IL03_NIL05[6]

DDRDQ_IL03_NIL05[7]

AY59

DDRDQ_IL12_NIL06[0]

AT66

AU66

DDRDQ_IL12_NIL06[1]

DDRDQ_IL12_NIL06[2]

AP65

AN65

DDRDQ_IL12_NIL06[3]

DDRDQ_IL12_NIL06[4]

AN66

DDRDQ_IL12_NIL06[5]

AP66

AT65

DDRDQ_IL12_NIL06[6]

DDRDQ_IL12_NIL06[7]

AU65

AT61

DDRDQ_IL13_NIL07[0]

DDRDQ_IL13_NIL07[1]

AU61

DDRDQ_IL13_NIL07[2]

AP60

AN60

DDRDQ_IL13_NIL07[3]

DDRDQ_IL13_NIL07[4]

AN61

AP61

DDRDQ_IL13_NIL07[5]

DDRDQ_IL13_NIL07[6]

AT60

DDRDQ_IL13_NIL07[7]

AU60

REV = 1

SKYLAKE_ULT

DDR CH - A

2 OF 20

DDR0_CLK_N[0]

DDR0_CLK_P[0]

DDR0_CLK_N[1]

DDR0_CLK_P[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS_N[0]

DDR0_CS_N[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[5]_CAA0

DDR0_MA[9]_CAA1

DDR0_MA[6]_CAA2

DDR0_MA[8]_CAA3

DDR0_MA[7]_CAA4

DDR0_BA[2]_CAA5_BG0

DDR0_MA[12]_CAA6

DDR0_MA[11]_CAA7

DDR0_MA[15]_CAA8_ACT_N

DDR0_MA[14]_CAA9_BG1

DDR0_MA[13]_CAB0

DDR0_CAS_N_CAB1_MA15

DDR0_WE_N_CAB2_MA14

DDR0_RAS_N_CAB3_MA16

DDR0_BA[0]_CAB4

DDR0_MA[2]_CAB5

DDR0_BA[1]_CAB6

DDR0_MA[10]_CAB7

DDR0_MA[1]_CAB8

DDR0_MA[0]_CAB9

DDR0_MA[3]

DDR0_MA[4]

DDRDQSN_IL00_NIL00

DDRDQSP_IL00_NIL00

DDRDQSN_IL01_NIL01

DDRDQSP_IL01_NIL01

DDRDQSN_IL10_NIL02

DDRDQSP_IL10_NIL02

DDRDQSN_IL11_NIL03

DDRDQSP_IL11_NIL03

DDRDQSN_IL02_NIL04

DDRDQSP_IL02_NIL04

DDRDQSN_IL03_NIL05

DDRDQSP_IL03_NIL05

DDRDQSN_IL12_NIL06

DDRDQSP_IL12_NIL06

DDRDQSN_IL13_NIL07

DDRDQSP_IL13_NIL07

DDR0_ALERT_N

DDR0_PARITY

DDR_VREF_CA

DDR_VREF_DQ[0]

DDR_VREF_DQ[1]

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

AH66

AH65

AG69

AG70

BA64

AY64

AY60

BA60

AR66

AR65

AR61

AR60

AW50

AT52

AY67

AY68

BA67

AW67

TP_M_A_A<3>

TP_M_A_A<4>

TP_DDR0_ALERT*

DDR_CA_VREF

DDR_VREFDQ_CHA

DDR_VREFDQ_CHB

DDR_VTT_CTRL [34]

R1115 *SHORT_2

*SHORT_2

R1116

TP238

*0_2

R1117

CAP1020

22nF/16V_4

M_A_CLK_DDR_DP<0> [17]

M_A_CLK_DDR_DN*<1> [17]

M_A_CLK_DDR_DP<1> [17]

M_A_CKE<0> [17]

M_A_CKE<1> [17]

M_A_CKE<2> [17]

M_A_CKE<3> [17]

M_A_CS*<0> [17]

M_A_CS*<1> [17]

M_A_ODT<0> [17]

M_A_CA_A<0> [17]

M_A_CA_A<1> [17]

M_A_CA_A<2> [17]

M_A_CA_A<3> [17]

M_A_CA_A<4> [17]

M_A_CA_A<5> [17]

M_A_CA_A<6> [17]

M_A_CA_A<7> [17]

M_A_CA_A<8> [17]

M_A_CA_A<9> [17]

M_A_CA_B<0> [17]

M_A_CA_B<1> [17]

M_A_CA_B<2> [17]

M_A_CA_B<3> [17]

M_A_CA_B<4> [17]

M_A_CA_B<5> [17]

M_A_CA_B<6> [17]

M_A_CA_B<7> [17]

M_A_CA_B<8> [17]

M_A_CA_B<9> [17]

M_A_DQS_DN*<0> [17]

M_A_DQS_DP<0> [17]

M_A_DQS_DN*<1> [17]

M_A_DQS_DP<1> [17]

M_A_DQS_DN*<2> [17]

M_A_DQS_DP<2> [17]

M_A_DQS_DN*<3> [17]

M_A_DQS_DP<3> [17]

M_A_DQS_DN*<4> [17]

M_A_DQS_DP<4> [17]

M_A_DQS_DN*<5> [17]

M_A_DQS_DP<5> [17]

M_A_DQS_DN*<6> [17]

M_A_DQS_DP<6> [17]

M_A_DQS_DN*<7> [17]

M_A_DQS_DP<7> [17]

RAP1026 5.11_4

RAP1027 10/F_4

RAP1028

CAP1022

22nF/16V_4

CAP1024

22nF/16V_4

+VDDQ_MEM

10/F_4

RAP1029

8.2K/F_4

RAP1030

8.2K/F_4

RAP1031

8.2K/F_4

RAP1032

8.2K/F_4

RAP1033

8.2K/F_4

RAP1034

8.2K/F_4

CA_VREF [17,18]

VREFDQ_CHA [17]

VREFDQ_CHB [18]

RAP1021

24.9_4

A A

5

4

3

RAP1023

24.9_4

RAP1025

24.9_4

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

SKL ULT - DDR3L CH A

SKL ULT - DDR3L CH A

SKL ULT - DDR3L CH A

ZHD

ZHD

ZHD

5 41Tuesday, May 23, 2017

5 41Tuesday, May 23, 2017

5 41Tuesday, May 23, 2017

1

8A

8A

8A

5

4

3

2

1

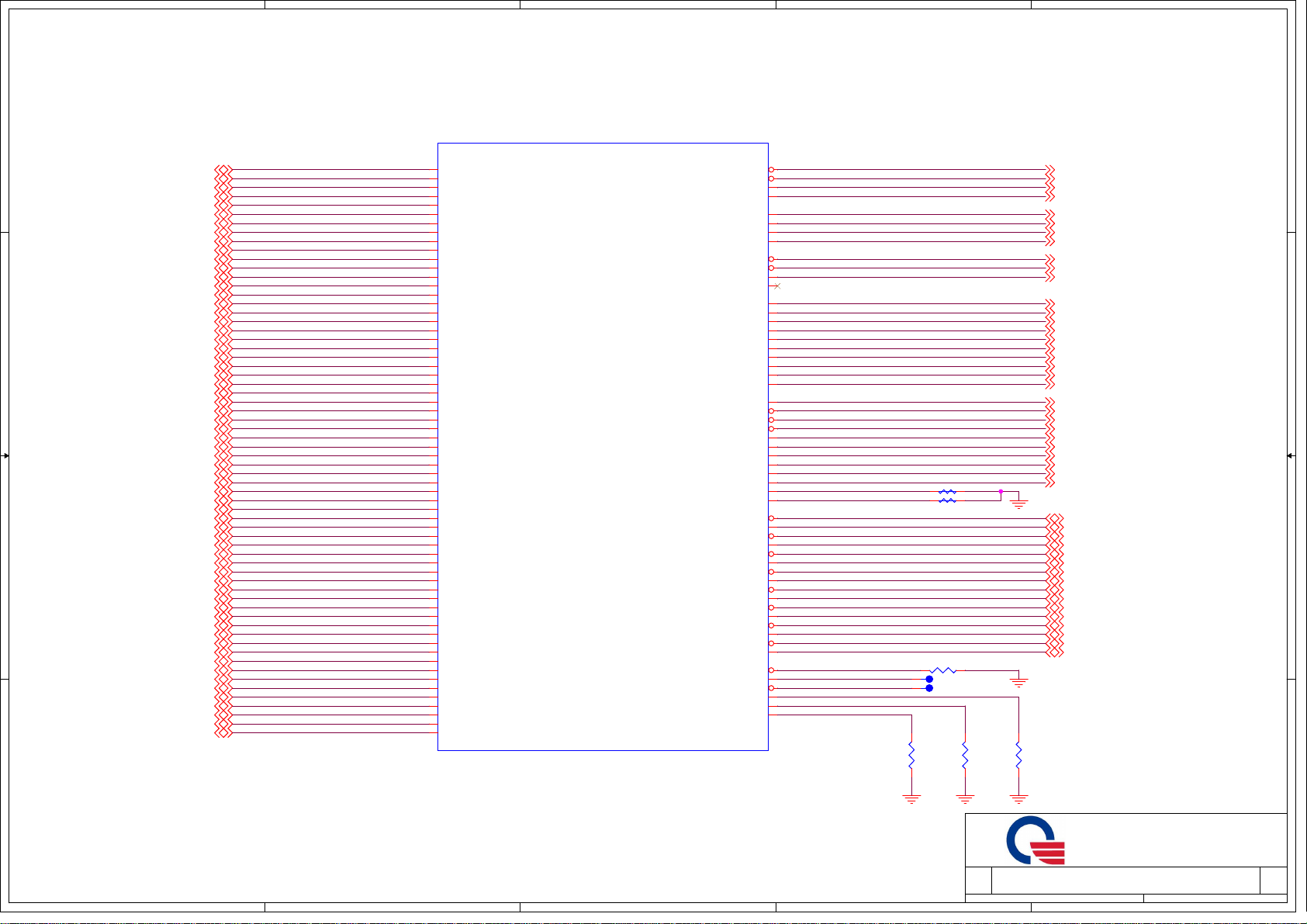

SKL ULT - DDR CHANNEL B

D D

DDRDQ_IL04_NIL10[0]

M_B_DQ<0>[18]

M_B_DQ<1>[18]

M_B_DQ<2>[18]

M_B_DQ<3>[18]

M_B_DQ<4>[18]

M_B_DQ<5>[18]

M_B_DQ<6>[18]

M_B_DQ<7>[18]

M_B_DQ<8>[18]

M_B_DQ<9>[18]

M_B_DQ<10>[18]

M_B_DQ<11>[18]

M_B_DQ<12>[18]

M_B_DQ<13>[18]

M_B_DQ<14>[18]

M_B_DQ<15>[18]

M_B_DQ<16>[18]

M_B_DQ<17>[18]

M_B_DQ<18>[18]

C C

B B

M_B_DQ<19>[18]

M_B_DQ<20>[18]

M_B_DQ<21>[18]

M_B_DQ<22>[18]

M_B_DQ<23>[18]

M_B_DQ<24>[18]

M_B_DQ<25>[18]

M_B_DQ<26>[18]

M_B_DQ<27>[18]

M_B_DQ<28>[18]

M_B_DQ<29>[18]

M_B_DQ<30>[18]

M_B_DQ<31>[18]

M_B_DQ<32>[18]

M_B_DQ<33>[18]

M_B_DQ<34>[18]

M_B_DQ<35>[18]

M_B_DQ<36>[18]

M_B_DQ<37>[18]

M_B_DQ<38>[18]

M_B_DQ<39>[18]

M_B_DQ<40>[18]

M_B_DQ<41>[18]

M_B_DQ<42>[18]

M_B_DQ<43>[18]

M_B_DQ<44>[18]

M_B_DQ<45>[18]

M_B_DQ<46>[18]

M_B_DQ<47>[18]

M_B_DQ<48>[18]

M_B_DQ<49>[18]

M_B_DQ<50>[18]

M_B_DQ<51>[18]

M_B_DQ<52>[18]

M_B_DQ<53>[18]

M_B_DQ<54>[18]

M_B_DQ<55>[18]

M_B_DQ<56>[18]

M_B_DQ<57>[18]

M_B_DQ<58>[18]

M_B_DQ<59>[18]

M_B_DQ<60>[18]

M_B_DQ<61>[18]

M_B_DQ<62>[18]

M_B_DQ<63>[18]

AY39

DDRDQ_IL04_NIL10[1]

AW39

DDRDQ_IL04_NIL10[2]

AY37

DDRDQ_IL04_NIL10[3]

AW37

DDRDQ_IL04_NIL10[4]

BB39

DDRDQ_IL04_NIL10[5]

BA39

DDRDQ_IL04_NIL10[6]

BA37

DDRDQ_IL04_NIL10[7]

BB37

DDRDQ_IL05_NIL11[0]

AY35

DDRDQ_IL05_NIL11[1]

AW35

DDRDQ_IL05_NIL11[2]

AY33

DDRDQ_IL05_NIL11[3]

AW33

DDRDQ_IL05_NIL11[4]

BB35

DDRDQ_IL05_NIL11[5]

BA35

DDRDQ_IL05_NIL11[6]

BA33

DDRDQ_IL05_NIL11[7]

BB33

DDRDQ_IL14_NIL12[0]

AU40

DDRDQ_IL14_NIL12[1]

AT40

DDRDQ_IL14_NIL12[2]

AT37

DDRDQ_IL14_NIL12[3]

AU37

DDRDQ_IL14_NIL12[4]

AR40

DDRDQ_IL14_NIL12[5]

AP40

DDRDQ_IL14_NIL12[6]

AP37

DDRDQ_IL14_NIL12[7]

AR37

DDRDQ_IL15_NIL13[0]

AT33

DDRDQ_IL15_NIL13[1]

AU33

DDRDQ_IL15_NIL13[2]

AU30

DDRDQ_IL15_NIL13[3]

AT30

DDRDQ_IL15_NIL13[4]

AR33

DDRDQ_IL15_NIL13[5]

AP33

DDRDQ_IL15_NIL13[6]

AR30

DDRDQ_IL15_NIL13[7]

AP30

DDRDQ_IL06_NIL14[0]

AY31

DDRDQ_IL06_NIL14[1]

AW31

DDRDQ_IL06_NIL14[2]

AY29

DDRDQ_IL06_NIL14[3]

AW29

DDRDQ_IL06_NIL14[4]

BB31

DDRDQ_IL06_NIL14[5]

BA31

DDRDQ_IL06_NIL14[6]

BA29

DDRDQ_IL06_NIL14[7]

BB29

DDRDQ_IL07_NIL15[0]

AY27

DDRDQ_IL07_NIL15[1]

AW27

DDRDQ_IL07_NIL15[2]

AY25

DDRDQ_IL07_NIL15[3]

AW25

DDRDQ_IL07_NIL15[4]

BB27

DDRDQ_IL07_NIL15[5]

BA27

DDRDQ_IL07_NIL15[6]

BA25

DDRDQ_IL07_NIL15[7]

BB25

DDRDQ_IL16_NIL16[0]

AU27

DDRDQ_IL16_NIL16[1]

AT27

DDRDQ_IL16_NIL16[2]

AT25

DDRDQ_IL16_NIL16[3]

AU25

DDRDQ_IL16_NIL16[4]

AP27

DDRDQ_IL16_NIL16[5]

AN27

DDRDQ_IL16_NIL16[6]

AN25

DDRDQ_IL16_NIL16[7]

AP25

DDRDQ_IL17_NIL17[0]

AT22

DDRDQ_IL17_NIL17[1]

AU22

DDRDQ_IL17_NIL17[2]

AU21

DDRDQ_IL17_NIL17[3]

AT21

DDRDQ_IL17_NIL17[4]

AN22

DDRDQ_IL17_NIL17[5]

AP22

DDRDQ_IL17_NIL17[6]

AP21

DDRDQ_IL17_NIL17[7]

AN21

REV = 1

U80C

SKYLAKE_ULT

DDR CH - B

3 OF 20

DDR1_CLK_N[0]

DDR1_CLK_N[1]

DDR1_CLK_P[0]

DDR1_CLK_P[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS_N[0]

DDR1_CS_N[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[5]_CAA0

DDR1_MA[9]_CAA1

DDR1_MA[6]_CAA2

DDR1_MA[8]_CAA3

DDR1_MA[7]_CAA4

DDR1_BA[2]_CAA5_BG0

DDR1_MA[12]_CAA6

DDR1_MA[11]_CAA7

DDR1_MA[15]_CAA8_ACT_N

DDR1_MA[14]_CAA9_BG1

DDR1_MA[13]_CAB0

DDR1_CAS_N_CAB1_MA15

DDR1_WE_N_CAB2_MA14

DDR1_RAS_N_CAB3_MA16

DDR1_BA[0]_CAB4

DDR1_MA[2]_CAB5

DDR1_BA[1]_CAB6

DDR1_MA[10]_CAB7

DDR1_MA[1]_CAB8

DDR1_MA[0]_CAB9

DDR1_MA[3]

DDR1_MA[4]

DDRDQSN_IL04_NIL10

DDRDQSP_IL04_NIL10

DDRDQSN_IL05_NIL11

DDRDQSP_IL05_NIL11

DDRDQSN_IL14_NIL12

DDRDQSP_IL14_NIL12

DDRDQSN_IL15_NIL13

DDRDQSP_IL15_NIL13

DDRDQSN_IL06_NIL14

DDRDQSP_IL06_NIL14

DDRDQSN_IL07_NIL15

DDRDQSP_IL07_NIL15

DDRDQSN_IL16_NIL16

DDRDQSP_IL16_NIL16

DDRDQSN_IL17_NIL17

DDRDQSP_IL17_NIL17

DDR1_ALERT_N

DDR1_PARITY

DRAM_RESETB

DDR_COMP[0]

DDR_COMP[1]

DDR_COMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

TP_M_B_A<3>

TP_M_B_A<4>

TP_DDR1_ALERT*

TP_DDR1_PARITY

TP_DDR3_DRAMRST*

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

R1118 *SHORT_2

*SHORT_2

R1119

R1120 *0_2

TP33

TP34

RAP1017

162_4

RAP1018

80.6_4

M_B_CLK_DDR_DN*<0> [18]

M_B_CLK_DDR_DN*<1> [18]

M_B_CLK_DDR_DP<0> [18]

M_B_CLK_DDR_DP<1> [18]

M_B_CKE<0> [18]

M_B_CKE<1> [18]

M_B_CKE<2> [18]

M_B_CKE<3> [18]

M_B_CS*<0> [18]

M_B_CS*<1> [18]

M_B_ODT<0> [18]

M_B_CA_A<0> [18]

M_B_CA_A<1> [18]

M_B_CA_A<2> [18]

M_B_CA_A<3> [18]

M_B_CA_A<4> [18]

M_B_CA_A<5> [18]

M_B_CA_A<6> [18]

M_B_CA_A<7> [18]

M_B_CA_A<8> [18]

M_B_CA_A<9> [18]

M_B_CA_B<0> [18]

M_B_CA_B<1> [18]

M_B_CA_B<2> [18]

M_B_CA_B<3> [18]

M_B_CA_B<4> [18]

M_B_CA_B<5> [18]

M_B_CA_B<6> [18]

M_B_CA_B<7> [18]

M_B_CA_B<8> [18]

M_B_CA_B<9> [18]

M_B_DQS_DN*<0> [18]

M_B_DQS_DP<0> [18]

M_B_DQS_DN*<1> [18]

M_B_DQS_DP<1> [18]

M_B_DQS_DN*<2> [18]

M_B_DQS_DP<2> [18]

M_B_DQS_DN*<3> [18]

M_B_DQS_DP<3> [18]

M_B_DQS_DN*<4> [18]

M_B_DQS_DP<4> [18]

M_B_DQS_DN*<5> [18]

M_B_DQS_DP<5> [18]

M_B_DQS_DN*<6> [18]

M_B_DQS_DP<6> [18]

M_B_DQS_DN*<7> [18]

M_B_DQS_DP<7> [18]

RAP1019

200_4

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

SKL ULT - DDR3L CH B

SKL ULT - DDR3L CH B

SKL ULT - DDR3L CH B

Size Document Number Rev

PROJECT :

Size Document Number Rev

1

ZHD

ZHD

ZHD

6 41Tuesday, May 23, 2017

6 41Tuesday, May 23, 2017

6 41Tuesday, May 23, 2017

8A

8A

8A

5

4

3

2

1

SKL ULT - PCIE/SATA/USB/SSIC/DSI/CSI

U80A

SKYLAKE_ULT

DDI1_TXN[0]

DDI1_LANE_DN*<0>[24]

DDI1_LANE_DP<0>[24]

R879

2.2K_4

U80H

SKYLAKE_ULT

DDI1_LANE_DN*<1>[24]

DDI1_LANE_DP<1>[24]

DDI1_LANE_DN*<2>[24]

DDI1_LANE_DP<2>[24]

DDI1_LANE_DN*<3>[24]

DDI1_LANE_DP<3>[24]

DDI2_LANE_DN*<0>[25]

DDI2_LANE_DP<0>[25]

DDI2_LANE_DN*<1>[25]

DDI2_LANE_DP<1>[25]

DDI2_LANE_DN*<2>[25]

DDI2_LANE_DP<2>[25]

DDI2_LANE_DN*<3>[25]

DDI2_LANE_DP<3>[25]

DDI1_CTRL_DATA

DDI2_CTRL_CLK

DDI2_CTRL_DATA

TCH_PNL_RST*[21]

D D

PORT D DETECT

1 = DETECT

0 = NOT DETECTED

INTERNAL PD

R1064

*2.2K_4

+V3P3S

INTERNAL PD

PORT C DETECT

1 = DETECT

0 = NOT DETECTED 0 = NOT DETECTED

R877

2.2K_4

INTERNAL PD

PORT B DETECT

1 = DETECT

+V1P00S_VCCSTG

DDI2_CTRL_CLK[25]

RAP1013

24.9_4

C C

DDI2_CTRL_DATA[25]

EDP_COMP

E55

DDI1_TXP[0]

F55

DDI1_TXN[1]

E58

F58

DDI1_TXP[1]

DDI1_TXN[2]

F53

DDI1_TXP[2]

G53

DDI1_TXN[3]

F56

DDI1_TXP[3]

G56

DDI2_TXN[0]

C50

DDI2_TXP[0]

D50

DDI2_TXN[1]

C52

DDI2_TXP[1]

D52

A50

DDI2_TXN[2]

DDI2_TXP[2]

B50

DDI2_TXN[3]

D51

DDI2_TXP[3]

C51

GPP_E_18_DDPB_CTRLCLK

L13

GPP_E_19_DDPB_CTRLDATA

L12

N7

GPP_E_20_DDPC_CTRLCLK

GPP_E_21_DDPC_CTRLDATA

N8

GPP_E_22_DDPD_CTRLCLK

N11

GPP_E_23_DDPD_CTRLDATA

N12

DP_COMP

E52

REV = 1

DDI

DISPLAY SIDEBANDS

1 OF 20

EDP

SSIC / USB3PCIE/USB3/SATA

USB3_1_RXN

H8

USB3_1_RXP

PCIE_1_USB3_5_RXN

PCIE_RX_DN*<1>[26]

PCIE_RX_DP<1>[26]

PCIE_TX_DN*<1>[26]

PCIE_TX_DP<1>[26]

C827 0.1U/16V_4

C828 0.1U/16V_4

PCIE_TX_C_DN*<1>

PCIE_TX_C_DP<1>

PCIe SATA ASSIGNMENT

WIFI1 --

B B

PCIE_RCOMPN

RAP1053 100/F_4

TP256

TP255

R5107 0_2

A A

SD_CDZ[8,10,22]

5

PCIE_RCOMPP

H13

PCIE_1_USB3_5_RXP

G13

B17

PCIE_1_USB3_5_TXN

PCIE_1_USB3_5_TXP

A17

PCIE_2_UFS_0A_USB3_6_RXN

G11

PCIE_2_UFS_0A_USB3_6_RXP

F11

D16

PCIE_2_UFS_0A_USB3_6_TXN

PCIE_2_UFS_0A_USB3_6_TXP

C16

PCIE_3_UFS_0B_LAN_0A_RXN

H16

PCIE_3_UFS_0B_LAN_0A_RXP

G16

D17

PCIE_3_UFS_0B_LAN_0A_TXN

PCIE_3_UFS_0B_LAN_0A_TXP

C17

PCIE_4_LAN_0B_RXN

G15

PCIE_4_LAN_0B_RXP

F15

B19

PCIE_4_LAN_0B_TXN

PCIE_4_LAN_0B_TXP

A19

PCIE_5_LAN_0C_RXN

F16

PCIE_5_LAN_0C_RXP

E16

C19

PCIE_5_LAN_0C_TXN

PCIE_5_LAN_0C_TXP

D19

PCIE_6_RXN

G18

PCIE_6_RXP

F18

D20

PCIE_6_TXN

PCIE_6_TXP

C20

PCIE_7_SATA_0_RXN

F20

PCIE_7_SATA_0_RXP

E20

B21

PCIE_7_SATA_0_TXN

PCIE_7_SATA_0_TXP

A21

PCIE_8_SATA_1A_RXN

G21

PCIE_8_SATA_1A_RXP

F21

D21

PCIE_8_SATA_1A_TXN

PCIE_8_SATA_1A_TXP

C21

PCIE_9_LAN_0D_RXN

E22

PCIE_9_LAN_0D_RXP

E23

B23

PCIE_9_LAN_0D_TXN

PCIE_9_LAN_0D_TXP

A23

PCIE_10_LAN_0E_RXN

F25

PCIE_10_LAN_0E_RXP

E25

D23

PCIE_10_LAN_0E_TXN

PCIE_10_LAN_0E_TXP

C23

PCIE_RCOMPN

F5

PCIE_RCOMPP

E5

PRDY_N

D56

PREQ_N

D61

GPP_A_7_PIRQAB

BB11

E28

PCIE_11_SATA_1B_RXN

PCIE_11_SATA_1B_RXP

E27

PCIE_11_SATA_1B_TXN

D24

PCIE_11_SATA_1B_TXP

C24

PCIE_12_SATA_2_RXN

E30

F30

PCIE_12_SATA_2_RXP

PCIE_12_SATA_2_TXN

A25

PCIE_12_SATA_2_TXP

B25

REV = 1

USB3_2_SSIC_1_RXN

USB3_2_SSIC_1_RXP

USB3_2_SSIC_1_TXN

USB3_2_SSIC_1_TXP

USB3_3_SSIC_2_RXN

USB3_3_SSIC_2_RXP

USB3_3_SSIC_2_TXN

USB3_3_SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E_9_USB2_OCB_0

GPP_E_10_USB2_OCB_1

GPP_E_11_USB2_OCB_2

GPP_E_12_USB2_OCB_3

GPP_E_4_SATA_DEVSLP_0

GPP_E_5_SATA_DEVSLP_1

GPP_E_6_SATA_DEVSLP_2

GPP_E_0_SATAXPCIE_0_SATAGP_0

GPP_E_1_SATAXPCIE_1_SATAGP_1

GPP_E_2_SATAXPCIE_2_SATAGP_2

8 OF 20

4

GPP_E_8_SATA_LEDB

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB2_OC*<1>

USB2_OC*<2>

R5159 0_2

3

USB3_RX_DN*<1> [24]

USB3_RX_DP<1> [24]

USB3_TX_DN*<1> [24]

USB3_TX_DP<1> [24]

USB3_RX_DN*<2> [22]

USB3_RX_DP<2> [22]

USB3_TX_DN*<2> [22]

USB3_TX_DP<2> [22]

USB3_RX_DN*<3> [22]

USB3_RX_DP<3> [22]

USB3_TX_DN*<3> [22]

USB3_TX_DP<3> [22]

USB3_RX_DN*<4> [22]

USB3_RX_DP<4> [22]

USB3_TX_DN*<4> [22]

USB3_TX_DP<4> [22]

USB2_DN*<1> [24]

USB2_DP<1> [24]

USB2_DN*<2> [21]

USB2_DP<2> [21]

USB2_DN*<3> [26]

USB2_DP<3> [26]

USB2_DN*<5> [22]

USB2_DP<5> [22]

USB2_DN*<6> [22]

USB2_DP<6> [22]

USB2_DN*<9> [22]

USB2_DP<9> [22]

USB2_COMP

USB2_OTG_ID [29]

USB2_OTG_VBUS_SNS [29]

USB2_OC*<0> [31]

USB2_OC*<2> [22]

USB2_OC*<3> [22]

R1056 113/F_4

TP253

SPI_TPM_IRQ* [16]

TCH_PNL_INTR* [4,21]

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E_13_DDSP_HPD_0

GPP_E_14_DDSP_HPD_1

GPP_E_15_DDSP_HPD_2

GPP_E_16_DDSP_HPD_3

GPP_E_17_EDP_HPD

L_BKLTEN

L_BKLTCTL

L_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP_TX_DN*<0> [21]

EDP_TX_DP<0> [21]

EDP_TX_DN*<1> [21]

EDP_TX_DP<1> [21]

TP279

TP280

TP281

TP282

EDP_AUX_DN* [21]

EDP_AUX_DP [21]

TP148

DDI1_AUX_DN* [24]

DDI1_AUX_DP [24]

TP230

TP231

DDI1_HPD [29]

DDI2_HPD [25]

EC_SMI* [29]

EC_SCI* [29]

EDP_HPD [21]

L_BKLT_EN [21]

L_BRIGHTNESS [21]

L_VDD_EN [21]

+V3P3A

RAP1455

100K_2

R1134

*100K_2

RAP1016

100K_2

+V3P3A

RAP1014

100K_2

USB3 PORT USB2 PORT ASSIGNMENT

1

USBC CONN1

2

--

-4

3

3

9

5

CCD

BLUETOOTH

USB-A CONN

USB 3.0 Conn.

Card reader62

+V3P3A

RING OSC BYPASS

1 = BYPASS MODE ENABLE

RAP1434

0 = RING OSC

20K_2

USB2_OC*<0>

+V3P3A

USB2_OC*<1>

+V3P3A

USB2_OC*<2>

+V3P3A

USB2_OC*<3>

2

QUALIFIED BY DFXTESTMODE

XTAL INPUT FREQ[1:0]

00 = 24 MHZ

01 = 25 MHZ

10 = 250 MHZ

11 = 100 MHZ

RAP1438

QUALIFIED BY DFXTESTMODE

20K_2

HVM ONLY REMOVED IN SPT

XTAL INPUT FREQ[1:0]

00 = 24 MHZ

01 = 25 MHZ

10 = 250 MHZ

RAP1436

11 = 100 MHZ

20K_2

QUALIFIED BY DFXTESTMODE

HVM ONLY REMOVED IN SPT

XTAL INPUT MODE (HVM ONLY)

1 = INPUT DIFFERENTIAL

RAP1440

0 = INPUT SINGLE-ENDED

20K_2

QUALIFIED BY DFXTESTMODE

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

SKL ULT - PCIE/SATA/USB/DSI

SKL ULT - PCIE/SATA/USB/DSI

SKL ULT - PCIE/SATA/USB/DSI

ZHD

ZHD

ZHD

7 41Tuesday, May 23, 2017

7 41Tuesday, May 23, 2017

1

7 41Tuesday, May 23, 2017

8A

8A

8A

5

+V1P8A

4

3

2

1

SKL ULT - I2S/DMIC/SDIO/UFS

C1109

0.1U/16V_4

U138

14

VCC

1

1OE

4

2OE

10

3OE

13

4OE

SN74LVC125APWR

MERGE_I2S_PCHTXD_AUDRXD[28]

R5146

10K_4

BOOT_BEEP

D D

SECURITY MEASURES STRAP OPTION

1 = FLASH DESCRIPTOR IS OVERRIDE

C C

+V1P8A

2

1A

3

R5137 0_4

1Y

5

2A

6

R5138 0_4

2Y

9

3A

8

R3499 33/F_2

3Y

12

R5139 0_4

4A

11

4Y

7

GND

0 = DEFAULT

MERGE_I2S_SFRM[28]

MERGE_I2S_SCL[28]

DMIC_CLK0_L[21]

DMIC_DATA0_L[21]

+V3P3S

MERGE_I2S_PCHRXD_AUDTXD

RAP1046

*20K_2

I2S0_SFRM

MERGE_I2S_SFRM

I2S0_SCLK

MERGE_I2S_SCL

I2S0_TXD

MERGE_I2S_PCHTXD_AUDRXD

MERGE_I2S_PCHRXD_AUDTXD

I2S0_RXD

R5139 put close to Pin 12 of U136.

I2S1_PCHRXD_NAUTXD[28]

I2S1_PCHTXD_NAURXD[28]

I2S_MCLK[28]

I2S1_SFRM[28]

R5142 0_4

R5143

R5140

R5141 *0_4

R5057 33_4

R5058 33_4

I2S1_SCL[28]

R1106 33_4 R4434

R5059 33_4

R5060 33_4

R3501 *SHORT_2

R3502 *SHORT_2

R3503 33/F_2

R3504 *SHORT_2

R899 33_4

0_4

*0_4

R900 33_4

R5147

*0_4

I2S0_SFRM

I2S0_SCLK

I2S0_TXD

I2S0_RXD

I2S1_PCHRXD_NAUTXD_C

I2S1_SCLK_C

I2S_MCLK_C

I2S1_SFRM_C

I2S1_PCHTXD_NAURXD_C

I2S2_SFRM

I2S2_SCLK

I2S2_TXD

I2S2_RXD

DMIC_CLK0_R

PCH_BUZZER

+VCCPAZIO

1

3

RAP1431

100K_2

+V3P3A_EC

Q105

PJA3413

2

RAP1430

100K_2

AZA_SYNC_SSP0_SFRM

BA22

AZA_BCLK_SSP0_SCLK

AY22

AZA_SDO_SSP0_TXD

BB22

AZA_SDI_0_SSP0_RXD

BA21

AZA_SDI_1_SSP1_RXD

AY21

AZA_RSTB_SSP1_SCLK

AW22

GPP_D_23_SSP_MCLK

J5

SSP1_SFRM

AY20

SSP1_TXD

AW20

GPP_F_1_SSP2_SFRM

AK7

GPP_F_0_SSP2_SCLK

AK6

GPP_F_2_SSP2_TXD

AK9

GPP_F_3_SSP2_RXD

AK10

GPP_D_19_DMIC_CLK_0

H5

GPP_D_20_DMIC_DATA_0

D7

GPP_D_17_DMIC_CLK_1

D8

GPP_D_18_DMIC_DATA_1

C8

GPP_B_14_SPKR

AW5

FLASH_DSC_OVERRIDE* [29]

FROM EC - ACTIVE LOW

REV = 1

U80G

SKYLAKE_ULT

7 OF 20

SDIO/SDXCAUDIO

GPP_G_0_SD_CMD

GPP_G_1_SD_DATA0

GPP_G_2_SD_DATA1

GPP_G_3_SD_DATA2

GPP_G_4_SD_DATA3

GPP_G_5_SD_CDB

GPP_G_6_SD_CLK

GPP_A_17_SD_PWR_EN_B_ISH_GP_7

GPP_G_7_SD_WP

GPP_A_16_SD_1P8_SEL

SD_RCOMP

GPP_F_23

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

SD_RCOMP

BOOT_BEEP

R5009 *0_2

RAP1050 200_4

+V3P3A

100K_2

SD_CDZ [7,10,22]

TOP SWAP STRAP

1 = TOP SWAP ENABLE

U80I

CSI-2

EMMC

9 OF 20

0 = TOP SWAP DISABLE

INTERNAL PD

CSI2_CLKN_0

CSI2_CLKP_0

CSI2_CLKN_1

CSI2_CLKP_1

CSI2_CLKN_2

CSI2_CLKP_2

CSI2_CLKN_3

CSI2_CLKP_3

CSI2_COMP

GPP_D_4_FLASHTRIG

GPP_F_13_EMMC_DATA0

GPP_F_14_EMMC_DATA1

GPP_F_15_EMMC_DATA2

GPP_F_16_EMMC_DATA3

GPP_F_17_EMMC_DATA4

GPP_F_18_EMMC_DATA5

GPP_F_19_EMMC_DATA6

GPP_F_20_EMMC_DATA7

GPP_F_21_EMMC_RCLK

GPP_F_22_EMMC_CLK

GPP_F_12_EMMC_CMD

EMMC_RCOMP

3

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

CSI2_COMP

EMMC_RCOMP

EMMC_D<0> [19]

EMMC_D<1> [19]

EMMC_D<2> [19]

EMMC_D<3> [19]

EMMC_D<4> [19]

EMMC_D<5> [19]

EMMC_D<6> [19]

EMMC_D<7> [19]

EMMC_RCLK [19]

EMMC_CLK [19]

EMMC_CMD [19]

RAP1054

200_4

RAP1055

100/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

SKL ULT - I2S/DMIC/SD/UFS

SKL ULT - I2S/DMIC/SD/UFS

SKL ULT - I2S/DMIC/SD/UFS

ZHD

ZHD

ZHD

8A

8A

8 41Tuesday, May 23, 2017

8 41Tuesday, May 23, 2017

8 41Tuesday, May 23, 2017

1

8A

RAP1433

*20K_2

B B

CSI2_DN_0

A36

CSI2_DP_0

B36

CSI2_DN_1

C38

CSI2_DP_1

D38

CSI2_DN_2

C36

CSI2_DP_2

D36

CSI2_DN_3

A38

CSI2_DP_3

B38

CSI2_DN_4

C31

CSI2_DP_4

D31

CSI2_DN_5

C33

CSI2_DP_5

D33

CSI2_DN_6

A31

CSI2_DP_6

B31

CSI2_DN_7

A33

CSI2_DP_7

B33

CSI2_DN_8

A29

CSI2_DP_8

B29

CSI2_DN_9

C28

CSI2_DP_9

D28

CSI2_DN_10

A A

5

4

A27

B27

C27

D27

CSI2_DP_10

CSI2_DN_11

CSI2_DP_11

SKYLAKE_ULT

REV = 1

5

4

3

2

1

SKL ULT - SPI/LPC/SMB/ISH

U80E

SPI - TOUCH

C LINK

SKYLAKE_ULT

SMBUS, SMLINKSPI - FLASH

LPC

5 OF 20

U80F

SKYLAKE_ULT

6 OF 20

GPP_C_0_SMBCLK

GPP_C_1_SMBDATA

GPP_C_2_SMBALERTB

GPP_C_3_SML0CLK

GPP_C_4_SML0DATA

GPP_C_5_SML0ALERTB

GPP_C_6_SML1CLK

GPP_C_7_SML1DATA

GPP_B_23_SML1ALERTB_PCHHOTB

GPP_A_1_LAD_0_ESPI_IO_0

GPP_A_2_LAD_1_ESPI_IO_1

GPP_A_3_LAD_2_ESPI_IO_2

GPP_A_4_LAD_3_ESPI_IO_3

GPP_A_5_LFRAMEB_ESPI_CSB

GPP_A_14_SUS_STATB_ESPI_RESETB

GPP_A_9_CLKOUT_LPC_0_ESPI_CLK

GPP_A_10_CLKOUT_LPC_1

GPP_A_8_CLKRUNB

ISHLPSS

GPP_D_16_ISH_UART0_CTSB_SML0BALERTB

GPP_C_14_UART1_RTSB_ISH_UART1_RTSB

GPP_C_15_UART1_CTSB_ISH_UART1_CTSB

GPP_D_9_ISH_SPI_CSB

GPP_D_10_ISH_SPI_CLK

GPP_D_11_ISH_SPI_MISO

GPP_D_12_ISH_SPI_MOSI

GPP_D_5_ISH_I2C0_SDA

GPP_D_6_ISH_I2C0_SCL

GPP_D_7_ISH_I2C1_SDA

GPP_D_8_ISH_I2C1_SCL

GPP_F_10_I2C5_SDA_ISH_I2C2_SDA

GPP_F_11_I2C5_SCL_ISH_I2C2_SCL

GPP_D_13_ISH_UART0_RXD_SML0BDATA

GPP_D_14_ISH_UART0_TXD_SML0BCLK

GPP_D_15_ISH_UART0_RTSB

GPP_C_12_UART1_RXD_ISH_UART1_RXD

GPP_C_13_UART1_TXD_ISH_UART1_TXD

GPP_A_18_ISH_GP_0

GPP_A_19_ISH_GP_1

GPP_A_20_ISH_GP_2

GPP_A_21_ISH_GP_3

GPP_A_22_ISH_GP_4

GPP_A_23_ISH_GP_5

GPP_A_12_BM_BUSYB_ISH_GP_6

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

SPI0_MOSI_IO_0

BOOT HALT

1 = DISABLE

0 = ENABLE

INTERNAL PU

SPI0_IO_2

RAP1049

2.2K_4

RAP3043

*4.7K_4

CONSENT STRAP

1 = DISABLE

0 = ENABLE

INTERNAL PU

+V3P3_TP_OUT

RAP1009

4.7K_2

D D

C C

+V1P8A

+V1P8S

RAP1047

2.2K_4

RAP3044

*4.7K_4

B B

SPI0_MISO_IO_1

JTAG ODT

1 = DISABLE

0 = ENABLE

INTERNAL PU

SPI0_IO_3

PERSONALITY STRAP

1 = DISABLE

0 = ENABLE

INTERNAL PU

NO REBOOT STRAP

1 = NO REBOOT

0 = REBOOT

INTERNAL PD

+V3P3A

RAP1010

4.7K_2

RAP3053

4.7K_2

+V3P3S

RAP3054

4.7K_2

+V3P3A

RAP1432

*20K_2

R217 *1K_2

R891 *249K_4

BOOT BIOS STRAP

1 = LPC

0 = SPI

INTERNAL PD

SCREW_SPI_WP_STATUS[16]

TP137

TP138

TP139

TP140

TP141

TP142

+V3P3A

RAP1000 100K_2

R894 10K_2

+V3P3A_WIFI

C1138

33P/50V_4

RAP1044 1K_2

ITCH_SPI_CLK

ITCH_SPI_MISO

ITCH_SPI_MOSI

ITCH_SPI_IO2

ITCH_SPI_IO3

ITCH_SPI_CS*

R1144

100K_2

TP177

TP178

TP179

TP180

TP278

TP274

TP277

TP191

TP233

TP275

TP276

C1139

33P/50V_4

SPI0_CLK

AV2

SPI0_MISO_IO_1

AW3

SPI0_MOSI_IO_0

AV3

SPI0_IO_2

AW2

SPI0_IO_3

AU4

SPI0_FLASH_0_CSB

AU3

SPI0_FLASH_1_CSB

AU2

SPI0_TPM_CSB

AU1

GPP_D_1_SPI1_CLK

M2

GPP_D_2_SPI1_MISO_IO_1

M3

GPP_D_3_SPI1_MOSI_IO_0

J4

GPP_D_21_SPI1_IO_2

V1

GPP_D_22_SPI1_IO_3

V2

GPP_D_0_SPI1_CSB

M1

MLK_CLK

G3

MLK_DATA

G2

MLK_RSTB

G1

GPP_A_0_RCINB

AW13

GPP_A_6_SERIRQ

AY11

REV = 1

GPP_B_15_GSPI0_CSB

AN8

GPP_B_16_GSPI0_CLK

AP7

GPP_B_17_GSPI0_MISO

AP8

GPP_B_18_GSPI0_MOSI

AR7

GPP_B_19_GSPI1_CSB

AM5

GPP_B_20_GSPI1_CLK

AN7

GPP_B_21_GSPI1_MISO

AP5

GPP_B_22_GSPI1_MOSI

AN5

GPP_C_8_UART0_RXD

AB1

GPP_C_9_UART0_TXD

AB2

GPP_C_10_UART0_RTSB

W4

GPP_C_11_UART0_CTSB

AB3

GPP_C_20_UART2_RXD

AD1

GPP_C_21_UART2_TXD

AD2

GPP_C_22_UART2_RTSB

AD3

GPP_C_23_UART2_CTSB

AD4

GPP_C_16_I2C0_SDA

U7

GPP_C_17_I2C0_SCL

U6

GPP_C_18_I2C1_SDA

U8

GPP_C_19_I2C1_SCL

U9

GPP_F_4_I2C2_SDA

AH9

GPP_F_5_I2C2_SCL

AH10

GPP_F_6_I2C3_SDA

AH11

GPP_F_7_I2C3_SCL

AH12

GPP_F_8_I2C4_SDA

AF11

GPP_F_9_I2C4_SCL

AF12

REV = 1

XDP_SPI0_IO2[10]

FLASH_SPI_CLK[16]

FLASH_SPI_MISO[16]

FLASH_SPI_MOSI[16]

FLASH_SPI_CS*[16]

TPM_SPI_CS*[16]

EC_PCH_RCIN*[29]

LPC_SERIRQ[29]

WLAN_PCIE_WAKE*[26]

RAP1035 *20K_2

PCHRXD_SERVOTXD[10]

PCHTXD_SERVORXD[10]

I2C0_SDA[21]

I2C0_SCL[21]

I2C1_SDA[27]

I2C1_SCL[27]

I2C4_SDA[28]

I2C4_SCL[28]

+V3P3A

RAP1051

SMB_CLK

SMB_DATA

TLS_CONFIDENTIALITY

EXT_BOOT_STALL_STRAP

PM_SUS_STAT*

EC_LPC_CLK_R

PCH_LPC_CLK1

P2

P3

P4

P1

I2C0_SDA

M4

I2C0_SCL

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

10K_2

RPM3429 22_2

RAP1001 10K_2

R1141

R1142

EN_PP1800_DX_AUDIO

PCH_MEM_CFG0

PCH_MEM_CFG1

PCH_MEM_CFG2

PCH_MEM_CFG3

RAP1052

10K_2

TP80

TP77

TP131

+V3P3A

USB_A0_ILIM_SEL [22]

USB_A1_ILIM_SEL [22]

*100K_2

*100K_2

R1143 *100K_2

EC_IN_RW [27]

LPC_LAD<0> [29]

LPC_LAD<1> [29]

LPC_LAD<2> [29]

LPC_LAD<3> [29]

LPC_FRAME* [29]

EC_LPC_CLK [29]

LPC_CLKRUN* [29]

TP213

TP212

AUDIO_IRQ* [28]

TP254

TP221

TP222

TP223

TP224

TP225

+V3P3A

R892

*10K_4

R1097

*4.7K/J_4

R1040

SP@100K_2

R1044

SP@100K_2

R5088

10K_4

+V1P8A

2

1

R1041

SP@100K_2

R1045

SP@100K_2

GPP_C_2_SMBALERTB

TLS CONFIDENTIALITY

1 = ENABLE

0 = DISABLE

INTERNAL PD

GPP_C_5_SML0ALERTB

ESPI/LPC EC

1 = ESPI

0 = LPC

INTERNAL PD

GPP_B_23_SMLALERTB_PCHHOTB

EXT BOOT STALL BYPASS

1 = ENABLE

0 = DISABLE

INTERNAL PD

+V3P3A+V1P8A

QPM3388

R1131

FDV301N

100K_2

3

R1042

SP@100K_2

R1046

SP@100K_2

AUDIO_INT_WAK* [3]

+V3P3A

R1043

SP@100K_2

R1047

SP@100K_2

Memory straps pin

I2C PORT ASSIGNMENT0LEVEL

RESERVED

TRACKPAD

1

NFC

2

RESERVED

3

AUDIO CODEC

4

A A

ISHISH 0

+3.3V

+3.3V

+1.8V

+1.8V

+1.8V

+1.8V

PCH_MEM_CFG[3:0]

3210

0

0000

0001

1

2

0010

3

0011

0100

4

0101

5

6 R1044,R1041,R1042,R1047

0110 H9CCNNN8JTBLAR-NUD

7

0111

1000

8 MT52L256M32D1PF-107

MEMORY PN

H9CCNNN8JTBLAR-NUD

H9CCNNNBLTBLAR-NUD

K4E8E324EB-EGCF

K4E8E324EB-EGCF

H9CCNNNBLTBLAR-NUD

K4E6E304EB-EGCF

H9CCNNNBJTALAR-NUD

Specification

(HYX ,SINGLE CHANNEL (2PCS), 2GB, 1866Mbps)

(HYX , DUAL CHANNEL (4PCS) ,8GB, 1866Mbps)

(SAM , DUAL CHANNEL (4PCS) ,4GB, 1866Mbps)

(SAM ,SINGLE CHANNEL (2PCS), 2GB, 1866Mbps)

(HYX ,SINGLE CHANNEL (2PCS), 4GB, 1866Mbps)

(SAM , DUAL CHANNEL (4PCS) ,8GB, 1866Mbps)

(HYX ,DUAL CHANNEL (4PCS) ,4GB, 1866Mbps)

(HYX ,SINGLE CHANNEL (2PCS) ,4GB, 1866Mbps)

(MIC , DUAL CHANNEL (4PCS) ,4GB, 1866Mbps)

9 1001 MT52L512M32D2PF-107 (MIC , DUAL CHANNEL (4PCS) ,8GB, 1866Mbps) R1040,R1045,R1046,R1043

C test new 2/21 add

C2 test new 4/17 add

5

10 1010 H9CCNNN8GTALAR-NUD (HYX ,DUAL CHANNEL (4PCS) ,4GB, 1866Mbps) R1044,R1041,R1046,R1043

11 1011 MT52L512M32D2PF-107 (MIC , SINGLE CHANNEL (2PCS) ,4GB, 1866Mbps) R1040,R1041,R1046,R1043

4

3

Stuff

R1044,R1045,R1046,R1047

R1040,R1045,R1046,R1047

R1044,R1041,R1046,R1047

R1040,R1041,R1046,R1047

R1044,R1045,R1042,R1047

R1040,R1045,R1042,R1047

R1040,R1041,R1042,R1047

R1044,R1045,R1046,R1043

2

EDF8132A3MA-JD-F (1GB, 1866Mbps)

(2GB, 1866Mbps)K4E6E304EB-EGCF

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

SKL ULT - SPI/LPC/SMB/ISH

SKL ULT - SPI/LPC/SMB/ISH

SKL ULT - SPI/LPC/SMB/ISH

ZHD

ZHD

ZHD

9 41Tuesday, May 23, 2017

9 41Tuesday, May 23, 2017

1

9 41Tuesday, May 23, 2017

8A

8A

8A

5

4

3

2

1

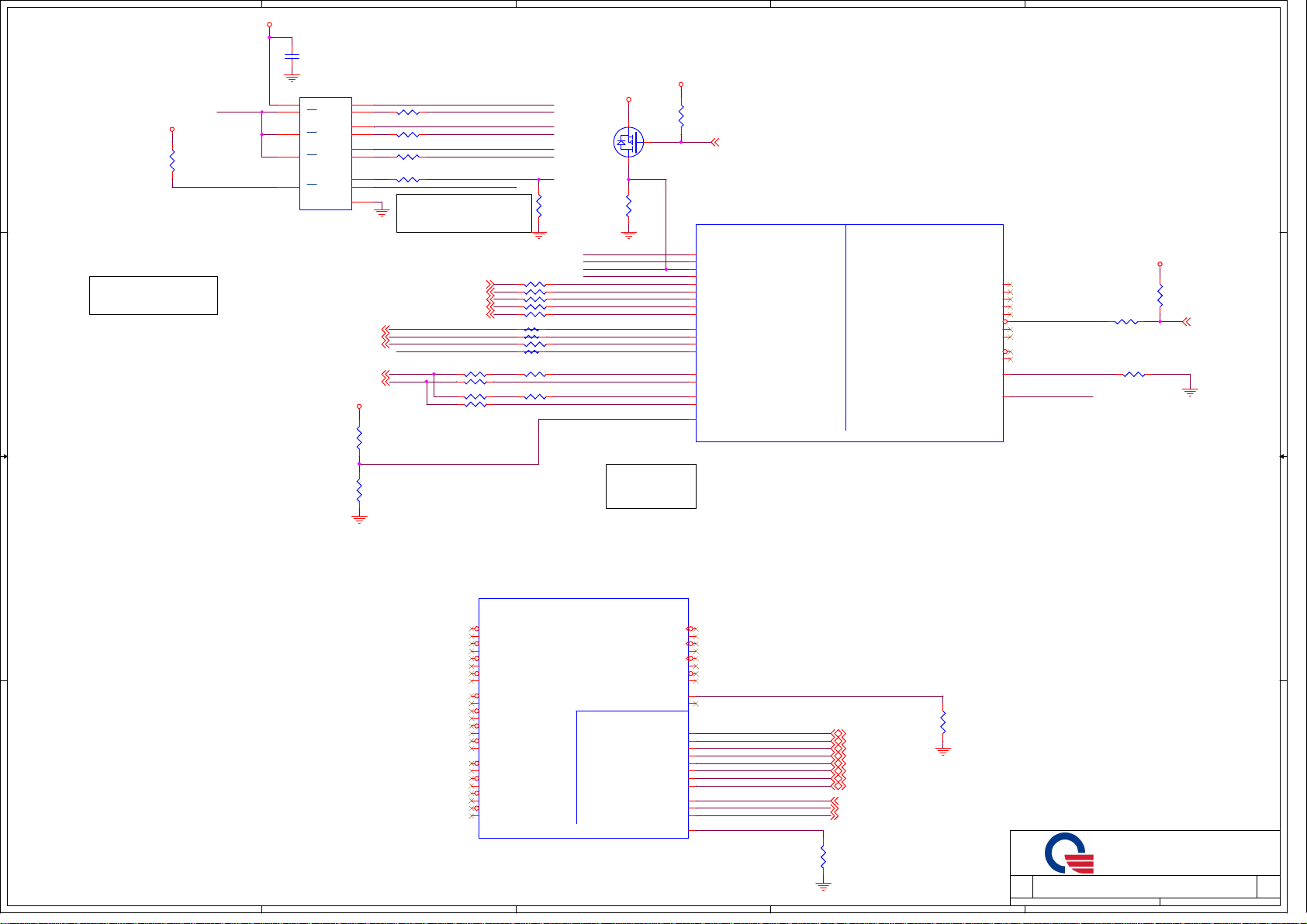

SKL ULT - XDP/CHROME SERVO

D D

C C

CPU_JTAG_TCLK[4]

XDP_TCLK_JTAGX[4]

CFG<0>[14]

+V1P00S_VCCSTG

RAP1343

150/F_4

CAD NOTE:

ROUTE WITH MINIMAL STUB W ITH RESPECT TO CFG<0>

RAP1351 *SHORT_4

RAP1352 *SHORT_4

EAR_N

RAP1344

1K/F_4

XDP_TCLK0

XDP_TDO

XDP_TDI

XDP_TMS

RAP1376 *SHORT_4

RAP1377 *SHORT_4

RAP1381 *SHORT_4

RAP1382 *SHORT_4

RAP1383 *SHORT_4

RAP1384 *SHORT_4

RAP1387 100K/F_4

RAP1385 *SHORT_4

RAP1386 *SHORT_4

CPU_JTAG_TDO [4]

PCH_JTAG_TDO [4]

CPU_JTAG_TDI [4]

PCH_JTAG_TDI [4]

CPU_JTAG_TMS [4]

PCH_JTAG_TMS [4]

+V3P3A

XDP_SPI0_IO2 [9]

XDP_OVERRIDE* [35]

GOOGLE CHROME SERVO SOCKET CONNECTOR

CN17

SERVO_PCH_SPI_CS*[16]

SERVO_PCH_SPI_MISO[16]

+V3P3A_EC_SPI_SERVO

B B

+V3P3DSW_EC

+V3P3_INA

A A

SERVO_PCH_SPI_HOLD*[16]

SERVO_EC_SPI_CLK[29]

SERVO_EC_SPI_MOSI[29]

PCHTXD_SERVORXD[9]

USBPDRXD_SERVOTXD[23]

USBPDTXD_SERVORXD[23]

SD_CDZ[7,8,22]

ECTXD_SERVORXD[29]

DEVICE_PROCHOT*[20,29,32,33,37]

USBPD_BOOT0[23] LID_OPEN [21,29]

EC_USBPD_RST*[23,29]

RAP1360 *SHORT_2

RAP1364 *SHORT_2

SD_CD*_R_R

TP81

TP82

+V3P3_INA

TP83

TP84

TP85

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

*AXK750147G

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

SERVO_EC_RST*

TP91

TP90

TP89

I2C_SCL_INA_R I2C_SCL_INAI2C_SDA_INA I2C_SDA_INA_R

TP88

TP87

TP86

1

CR15 RB500V-40

RAP1429 *SHORT_2RAP1428 *SHORT_2

I2C_SCL_INA

I2C_SDA_INA

2

RPM3576 4.7K_4

RPM3577

SERVO_PCH_SPI_CLK [16]

SERVO_PCH_SPI_MOSI [16]

SERVO_EC_SPI_CS* [29]

SERVO_EC_SPI_MISO [29]

V3P3DSW_ENA [27,29,34]

PCHRXD_SERVOTXD [9]

MECH_PWRBTN* [27,29,33]

PCH_SYSRST* [3,29]

ECRXD_SERVOTXD [29]

SERVO_SPI_WP* [16]

+V3P3_INA

4.7K_4

+V3P3_BIOS_SPI_SERVO

+V3P3A

+V3P3A_EC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

SKL ULT - SERVO

SKL ULT - SERVO

SKL ULT - SERVO

Size Document Number Rev

PROJECT :

Size Document Number Rev

1

ZHD

ZHD

ZHD

10 41Tuesday, May 23, 2017

10 41Tuesday, May 23, 2017

10 41Tuesday, May 23, 2017

8A

8A

8A

5

4

3

2

1

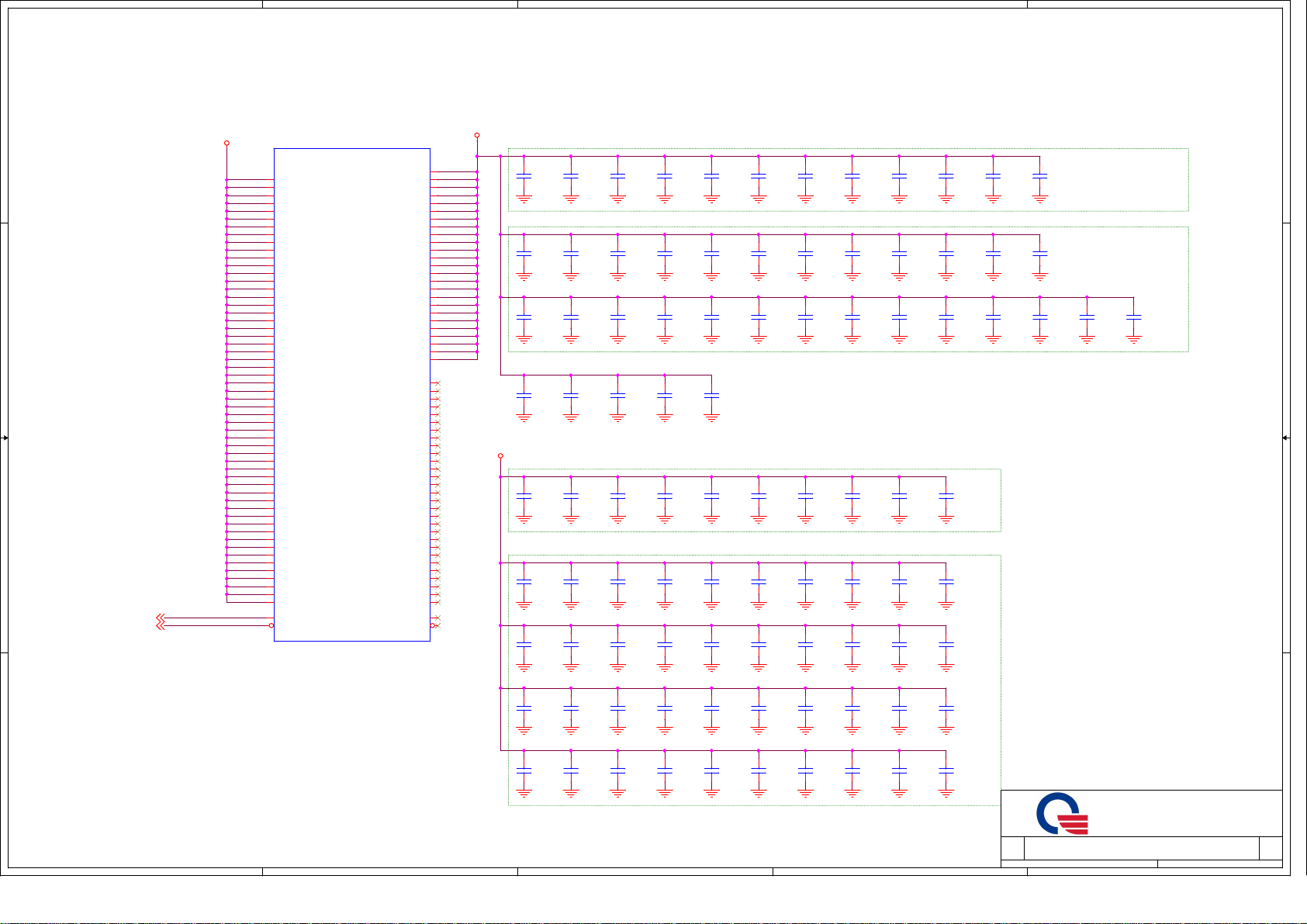

SKL ULT - POWER CORE

U80L

D D

C C

EDRAM ONLY REQUIRED FOR 2+3E SKU

+VCCCORE +VCCCORE

VCCCORE

A30

VCCCORE

A34

VCCCORE

A39

VCCCORE

A44

VCCCORE

AK33

VCCCORE

AK35

VCCCORE

AK37

VCCCORE

AK38

VCCCORE

AK40

VCCCORE

AL33

VCCCORE

AL37

VCCCORE

AL40

VCCCORE

AM32

VCCCORE

AM33

VCCCORE

AM35

VCCCORE

AM37

VCCCORE

AM38

VCCCORE

G30

VCCCOREG0

K32

VCCCOREG1

AK32

VCCEDRAM

AB62

VCCEDRAM

P62

VCCEDRAM

V62

VCC_EDRAM_1P8

H63

VCC_EDRAM_FUSEPRG

G61

VCCEDRAM_SENSE

AC63

VSSEDRAM_SENSE

AE63

VCCEOPIO

AE62

VCCEOPIO

AG62

VCCEOPIO_SENSE

AL63

VSSEOPIO_SENSE

AJ62

REV = 1

SKYLAKE_ULT

CPU POWER 1 OF 4

12 OF 20

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE

VCCCORE_SENSE

VSSCORE_SENSE

VIDALERT_N

VIDSCK

VIDSOUT

VCCFUSEPRG

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

CPU_SVIDALRT*_R

B63

A63

D64

G20

RPM3558 220_4

+V1P00S_VCCSTG

RAP1450

100/F_4

VCCCORE_SENSE [37]

VSSCORE_SENSE [37]

CPU_SVIDALRT* [37]

RAP1451

+V1P00S_VCCST

56_4

CPU_SVIDCLK [37]

CPU_SVIDDAT [37]

CORE

+VCCCORE

CAPS PLACE CLOSE TO SOC ON SAME SIDE

CAP1201

CAP1208

CAP1215

CAP1171

CAP1181

CAP1191

22u/6.3V_6

CAP1203

22u/6.3V_6

CAP1206

1U/6.3V_2

CAP1431

1U/6.3V_2

CAP14476

22u/6.3V_6

4

22u/6.3V_6

CAP1210

22u/6.3V_6

CAP1213

1U/6.3V_2

CAP1433

1U/6.3V_2

CAP14477

22u/6.3V_6

22u/6.3V_6

22u/6.3V_6

22u/6.3V_6

B B

CAPS PLACE ON OPPOSITE SIDE OF SOC

CAP1193

CAP1183

CAP1173

22u/6.3V_6

CAP1176

1U/6.3V_2

CAP1425

1U/6.3V_2

A A

5

CAPS PLACE CLOSE TO SOC ON SAME SIDE

CAP14473

22u/6.3V_6

22u/6.3V_6

CAP1186

1U/6.3V_2

CAP1427

1U/6.3V_2

CAP14474

22u/6.3V_6

22u/6.3V_6

CAP1196

1U/6.3V_2

CAP1428

1U/6.3V_2

CAP14475

22u/6.3V_6

22u/6.3V_6

CAP1217

22u/6.3V_6

CAP1220

1U/6.3V_2

CAP1435

1U/6.3V_2

CAP14478

22u/6.3V_6

CAP1172

22u/6.3V_6

CAP1223

22u/6.3V_6

CAP1226

1U/6.3V_2

CAP1437

1U/6.3V_2

CAP14479

22u/6.3V_6

CAP1192

22u/6.3V_6

CAP1229

22u/6.3V_6

CAP1231

1U/6.3V_2

CAP1439

1U/6.3V_2

CAP14480

22u/6.3V_6

CAP1174

10u/6.3V_4

CAP1234

22u/6.3V_6

CAP1235

1U/6.3V_2

CAP1441

1U/6.3V_2

CAP1184

10u/6.3V_4

CAP1443

10u/6.3V_4

CAP1177

1U/6.3V_2

CAP1424

1U/6.3V_2

3

CAP1194

10u/6.3V_4

CAP1444

10u/6.3V_4

CAP1187

1U/6.3V_2

CAP1426

1U/6.3V_2

CAP1204

10u/6.3V_4

CAP1445

10u/6.3V_4

CAP1197

1U/6.3V_2

CAP1429

1U/6.3V_2

CAP1211

10u/6.3V_4

CAP1446

10u/6.3V_4

CAP1207

1U/6.3V_2

CAP1430

1U/6.3V_2

CAP1218

10u/6.3V_4

CAP1447

10u/6.3V_4

CAP1214

1U/6.3V_2

CAP1432

1U/6.3V_2

CAP1224

10u/6.3V_4

CAP1448

10u/6.3V_4

CAP1221

1U/6.3V_2

CAP1434

1U/6.3V_2

CAP1442

10u/6.3V_4

CAP1449

10u/6.3V_4

CAP1227

1U/6.3V_2

CAP1436

1U/6.3V_2

2

CAP1232

1U/6.3V_2

CAP1438

1U/6.3V_2

CAP1236

1U/6.3V_2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

SKL ULT - CORE POWER

SKL ULT - CORE POWER

SKL ULT - CORE POWER

ZHD

ZHD

ZHD

1

8A

8A

11 41Tuesday, May 23, 2017

11 41Tuesday, May 23, 2017

11 41Tuesday, May 23, 2017

8A

5

4

3

2

1

SKL ULT - POWER GRAPHICS

D D

+VCCGT

VCCGT

A48

VCCGT

A53

VCCGT

A58

VCCGT

A62

VCCGT

A66

VCCGT

AA63

VCCGT

AA64

VCCGT

AA66

VCCGT

AA67

VCCGT

AA69

VCCGT

AA70

VCCGT

AA71

VCCGT

AC64

VCCGT

AC65

VCCGT

AC66

VCCGT

AC67

VCCGT

AC68

VCCGT

AC69

VCCGT

AC70

VCCGT

AC71

VCCGT

M62

K48

K50

K52

K53

K55

K56

K58

K60

N63

N64

N66

N67

N69

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

J70

J69

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

REV = 1

C C

B B

VCCGT_SENSE[37]

VSSGT_SENSE[37]

U80M

SKYLAKE_ULT

CPU POWER 2 OF 4

SLICED GT

UNSLICED GT

VCCGTU_SENSE

VSSGTU_SENSE

13 OF 20

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

VCCGTU

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

+VCCGT

CAPS PLACE CLOSE TO SOC ON SAME SIDE

C51

22u/6.3V_6

CAPS PLACE ON OPPOSITE SIDE OF SOC

CAP1156

10u/6.3V_4

CAP1102

1U/6.3V_2

C1029

22u/6.3V_6

+VCCGT

CAPS PLACE CLOSE TO SOC ON SAME SIDE

CAP1101

*10u/6.3V_4

CAPS PLACE ON OPPOSITE SIDE OF SOC

CAP1456

*10u/6.3V_4

CAP14466

*10u/6.3V_4

C62

22u/6.3V_6

CAP1157

10u/6.3V_4

CAP1109

1U/6.3V_2

C1030

22u/6.3V_6

CAP1108

*10u/6.3V_4

CAP1457

*10u/6.3V_4

CAP1467

*10u/6.3V_4

C63

22u/6.3V_6

CAP1162

10u/6.3V_4

CAP1116

1U/6.3V_2

C1031

22u/6.3V_6

CAP1115

*10u/6.3V_4

CAP1458

*10u/6.3V_4

CAP1468

*10u/6.3V_4

C64

22u/6.3V_6

CAP1165

10u/6.3V_4

CAP1123

1U/6.3V_2

C1032

22u/6.3V_6

CAP1122

*10u/6.3V_4

CAP1459

*10u/6.3V_4

CAP1469

*10u/6.3V_4

C65

22u/6.3V_6

CAP1167

10u/6.3V_4

CAP1130

1U/6.3V_2

C1033

22u/6.3V_6

CAP1129

*10u/6.3V_4

CAP1460

*10u/6.3V_4

CAP1470

*10u/6.3V_4

CAP1155

22u/6.3V_6

CAP1169

10u/6.3V_4

CAP1137

1U/6.3V_2

CAP1136

*10u/6.3V_4

CAP1461

*10u/6.3V_4

CAP1471

*10u/6.3V_4

CAP1159

22u/6.3V_6

CAP1179

10u/6.3V_4

CAP1142

1U/6.3V_2

CAP1141

*10u/6.3V_4

CAP1462

*10u/6.3V_4

CAP1472

*10u/6.3V_4

CAP1161

22u/6.3V_6

CAP1189

10u/6.3V_4

CAP1148

1U/6.3V_2

CAP1147

*10u/6.3V_4

CAP1463

*10u/6.3V_4

CAP1473

*10u/6.3V_4

CAP1164

22u/6.3V_6

CAP1199

10u/6.3V_4

CAP1103

1U/6.3V_2

CAP1150

*10u/6.3V_4

CAP1464

*10u/6.3V_4

CAP1474

*10u/6.3V_4

CAP1166

22u/6.3V_6

CAP1450

10u/6.3V_4

CAP1110

1U/6.3V_2

CAP1152

*10u/6.3V_4

CAP1465

*10u/6.3V_4

CAP1475

*10u/6.3V_4

CAP1168

22u/6.3V_6

CAP1451

10u/6.3V_4

CAP1117

1U/6.3V_2

CAP1178

22u/6.3V_6

CAP1452

10u/6.3V_4

CAP1124

1U/6.3V_2

CAP1131

1U/6.3V_2

CAP1138

1U/6.3V_2

CAP1477

CAP1476

*1U/6.3V_2

*1U/6.3V_2

A A

5

4

CAP1486

*1U/6.3V_2

CAP1487

*1U/6.3V_2

CAP1478

*1U/6.3V_2

CAP1488

*1U/6.3V_2

3

CAP1479

*1U/6.3V_2

CAP1489

*1U/6.3V_2

CAP1480

*1U/6.3V_2

CAP1490

*1U/6.3V_2

CAP1481

*1U/6.3V_2

CAP1491

*1U/6.3V_2

CAP1482

*1U/6.3V_2

CAP1492

*1U/6.3V_2

CAP1483

*1U/6.3V_2

CAP1493

*1U/6.3V_2

CAP1484

*1U/6.3V_2

CAP1494

*1U/6.3V_2

2

CAP1485

*1U/6.3V_2

CAP1495

*1U/6.3V_2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

SKL ULT - GT POWER

SKL ULT - GT POWER

SKL ULT - GT POWER

ZHD

ZHD

ZHD

12 41Tuesday, May 23, 2017

12 41Tuesday, May 23, 2017

12 41Tuesday, May 23, 2017

1

8A

8A

8A

Loading...

Loading...