Page 1

1

2

3

4

5

6

7

8

01

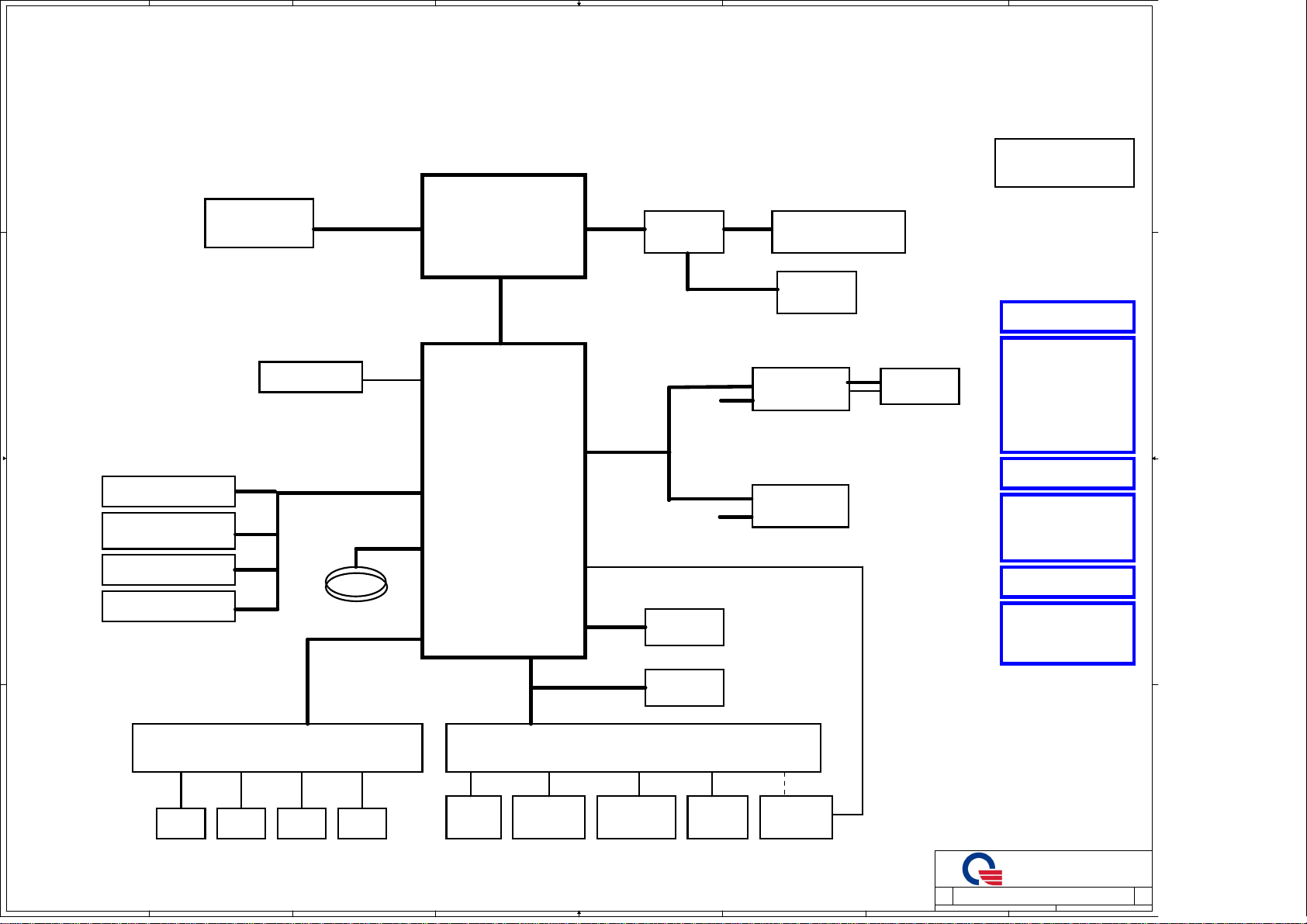

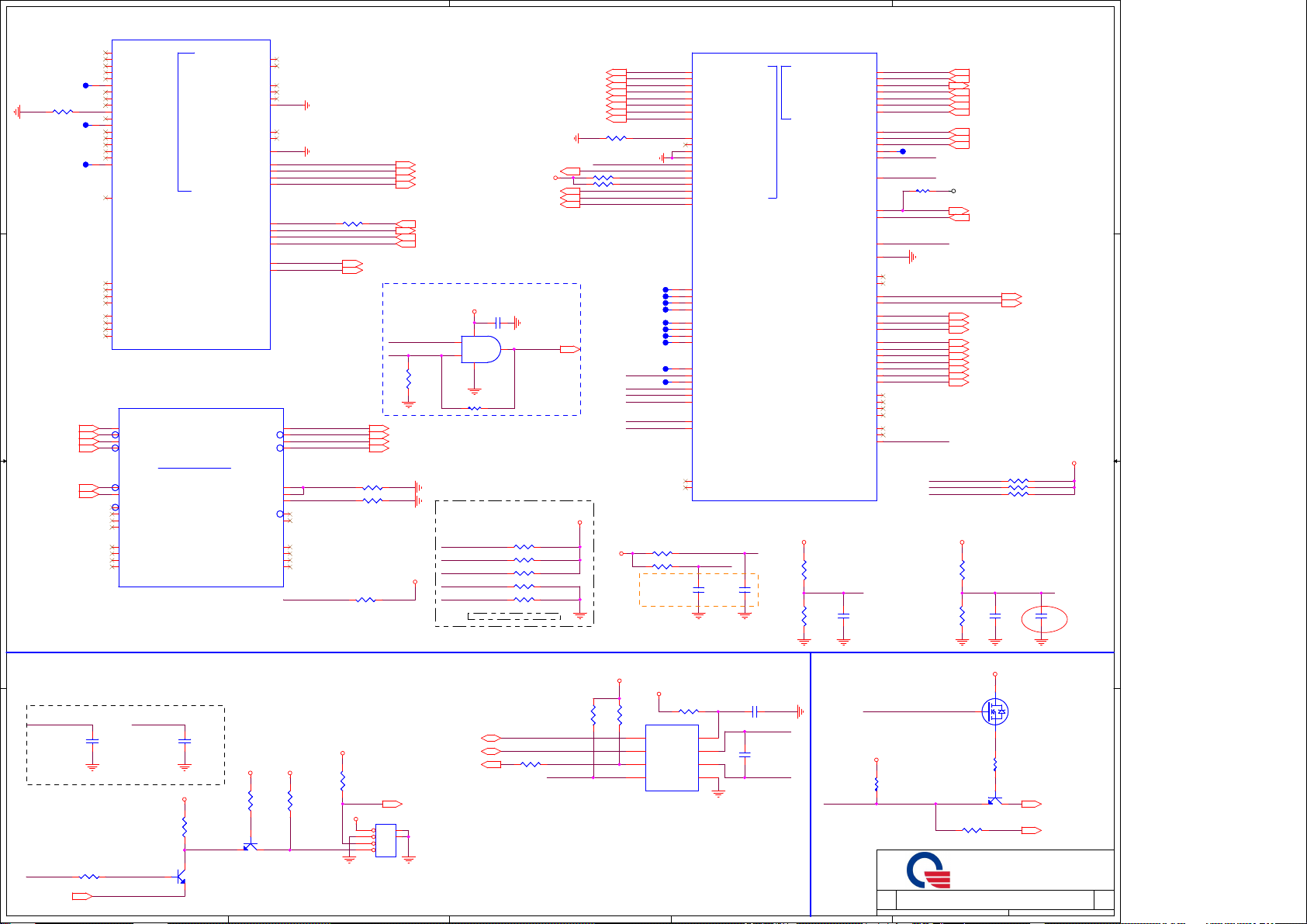

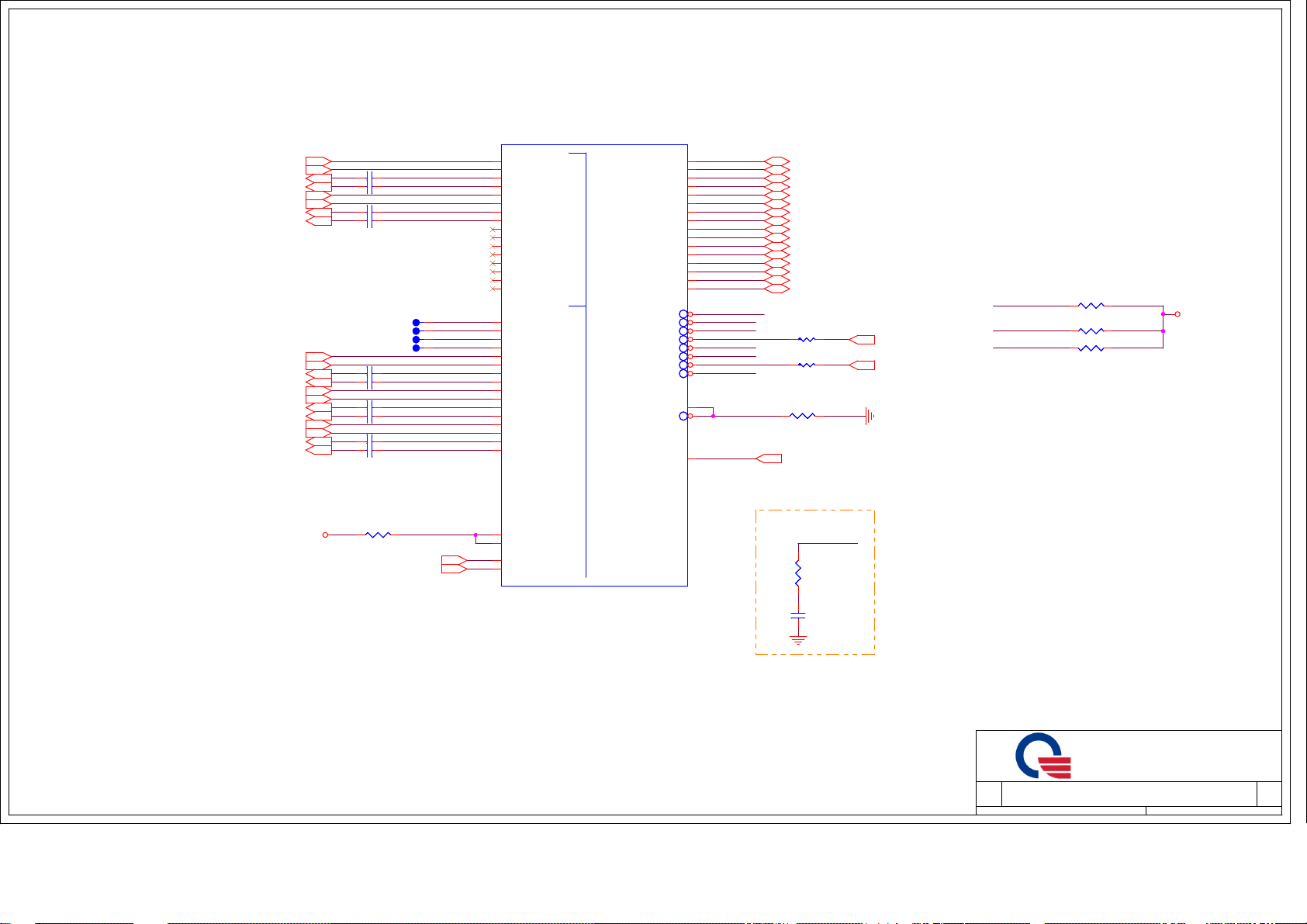

ZGA Block Diagram

A A

CK505

P2

Pineview

Graphics Interfaces

INT_LVDS

CH7036

PCIE-4

P24

USB-5

11.6"Panel

Up to 1280*800 or 1366*768

HDMI

P25

3G/WiMAX

P21

USB-1

P15

SIM Card

P21

Charger

+3VPCU

+5VPCU

+3V_S5

+5V_S5

+3VSUS

P27

DDRIII-SODIMM

P3

667 MT/s

N475 1.83G: AJ0Q4KSUT03

N455 1.66G: AJ0Q4L5VT03

CPU

P5,6,7,8

DDR SYSTEM MEMORY

DMI

DMI(x2)

B B

SATA - SSD

P20

SATA 0

SATA

DMI

+3V

PCI-Express(Port1~4)

Tigerpoint

CCD

4 in 1 Card Reader

Realtek RTS5138

C C

USB port*2

Bluetooth module

USB-2

P15

USB-4

P22

USB-0,3

P18

USB-6

P16

USB 2.0 (Port0~7)

BATTERY

P12

Intel High Definition Audio

USB

RTC

IHDA

SB

P9,10,11,12,13,14

PN : AJ0QMJN0T07

LPC

LPC

PCI-E

SMBUS

PCIE-2

SPI Flash

P12

TPM

ST19NP18ER28PVLR

P26

USB-7

WLAN/WiMAX

P21

+5V

VCC_CORE

+1.5VSUS

+SMDDR_VREF

+0.75V_DDR_VTT

+1.5V

+1.05V

+1.5V

Discharge

VCCGFX

P28

P29

P30

P31

P32

Audio Codec

D D

Int. SPK

CONN

1

Int. DMIC

CONN

2

Realtek ALC271

MIC

Jack

HP

Jack

3

P17

K/B Con.

EC

Touch Pad /B

Con.

4

NPCE781L

SPI Flash

P22P15 P15

5

Charger

P23

P23

Light Sensor

TSL2561FN

6

P26

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZGA

ZGA

ZGA

1 38Wednesday, July 07, 2010

1 38Wednesday, July 07, 2010

1 38Wednesday, July 07, 2010

8

1B

1B

1B

Page 2

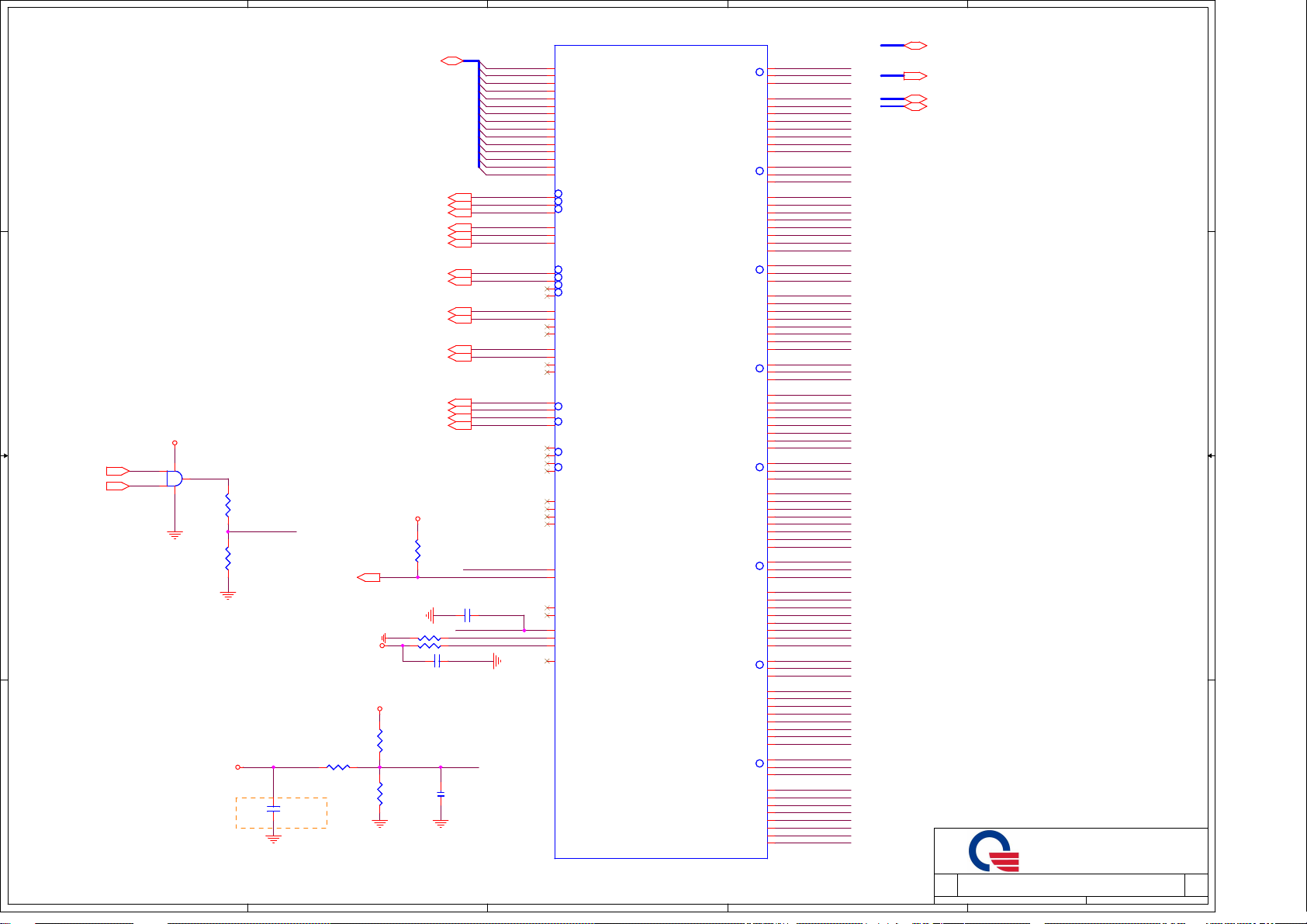

5

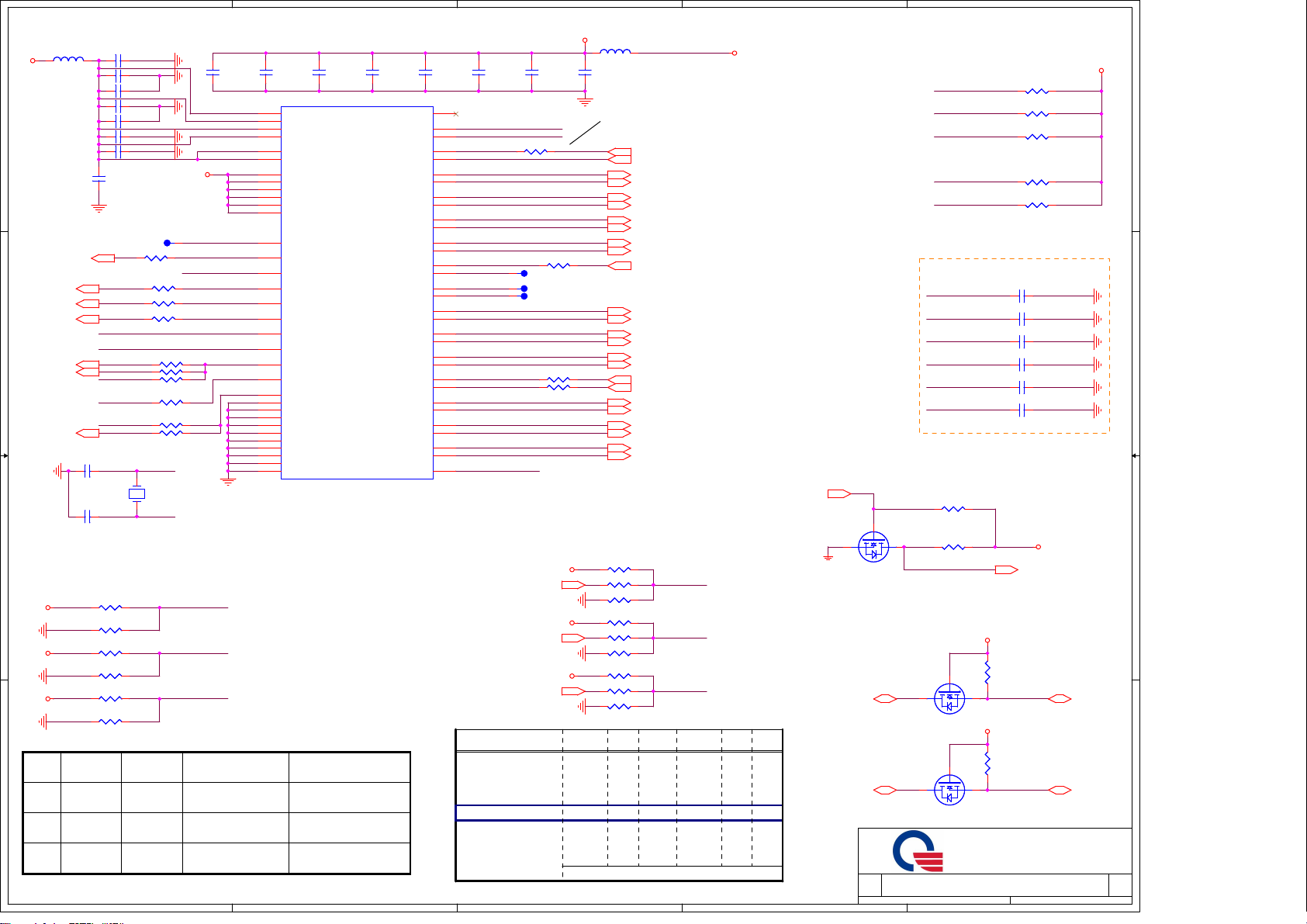

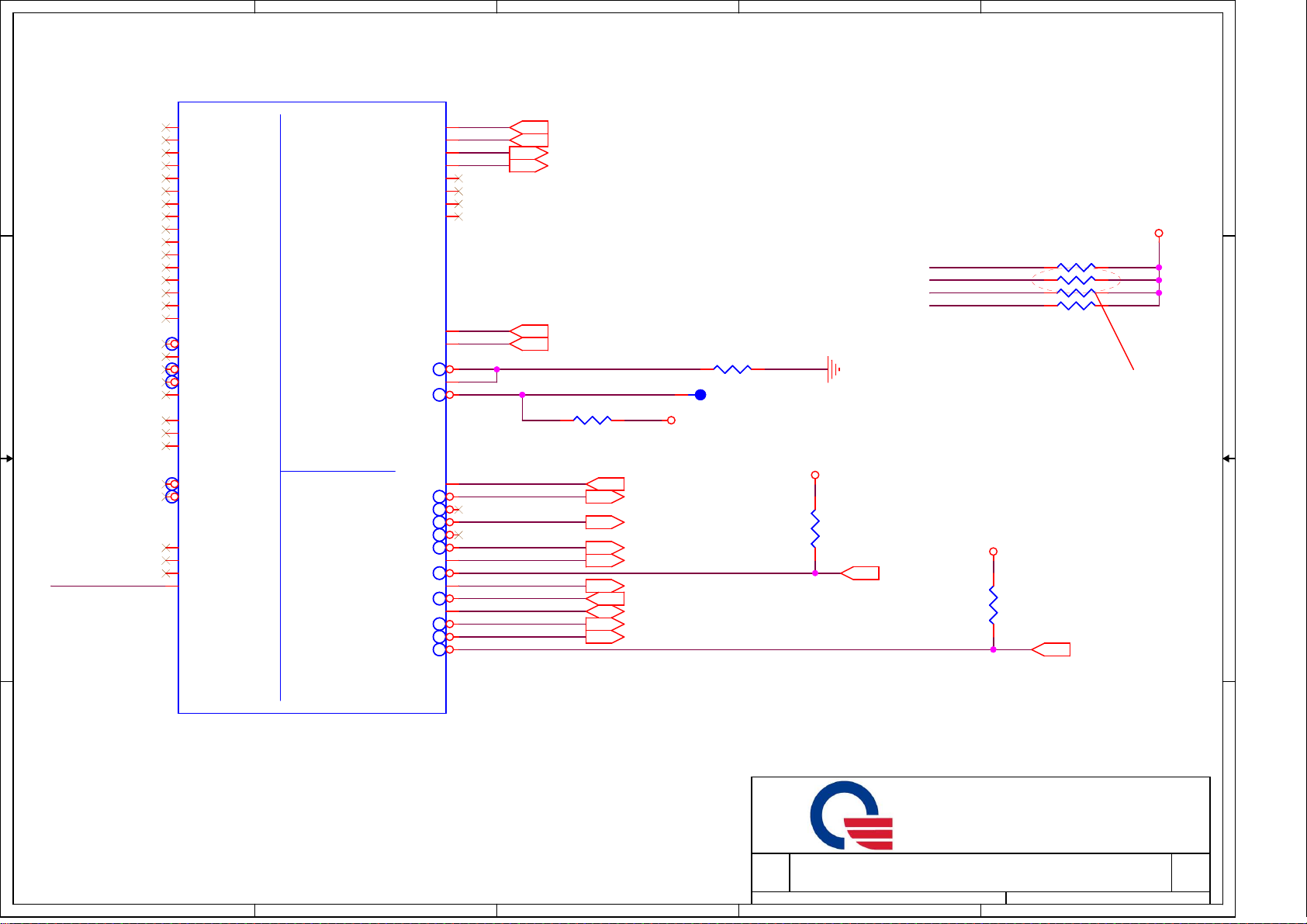

Clock Generator(CLK)

PBY160808T-301Y-N/2A/300ohm_6

PBY160808T-301Y-N/2A/300ohm_6

+3V

L32

L32

D D

PCLK_DEBUG(21)

PCLK_TPM(26)

LCLK_EC(23)

PCLK_ICH(11)

C C

CLK_Card48(22)

CLKUSB_48(9)

14M_ICH(12)

<Layout note>

Crystal place within 500mil of CK505

B B

+3V

+3V

+3V

SLG8SP513VTR

(AL8SP513000)

Pin 11

Pin 13

Pin 14

PCI2

PCI4/

SEL_LCDCLK#

PCIF5/ITP_EN

A A

C346

C346

*0.1u/10V_4

*0.1u/10V_4

C356

C356

*0.1u/10V_4

*0.1u/10V_4

C350

C350

*10u/10V_8

*10u/10V_8

C364

C364

0.1u/10V_4

0.1u/10V_4

C348

C348

0.1u/10V_4

0.1u/10V_4

C377

C377

0.1u/10V_4

0.1u/10V_4

C361

C361

0.1u/10V_4

0.1u/10V_4

C380

C380

10u/10V_8

10u/10V_8

R367 33_4R367 33_4

R374 33_4R374 33_4

R371 33_4R371 33_4

PCLK_ICH

R379 33_4R379 33_4

CG_XIN

CG_XOUT

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

C349

C349

33p/50V_4

33p/50V_4

21

CL=20p

C354

C354

33p/50V_4

33p/50V_4

R365 10K_4R365 10K_4

R366 *10K_4R366 *10K_4

R363 *10K_4R363 *10K_4

R361 10K_4R361 10K_4

R378 *10K_4R378 *10K_4

R377 10K_4R377 10K_4

ICS9LPRS365

(ALPRS365000)

PCI2/TME

PCI4/

27_Select

PCIF5/ITP_EN

5

T53T53

R385 22_4R385 22_4

R384 22_4R384 22_4

R393 2.2K_4R393 2.2K_4

R386 1K_4R386 1K_4

R376 10K_4R376 10K_4

R375 33_4R375 33_4

CG_XIN

Y4

Y4

14.318MHZ

14.318MHZ

CG_XOUT

PCLK_ICH_R

C378

C378

*10u/10V_8

*10u/10V_8

VDD_CK_VDD_REF

0.25A

+1.05V_VDD

PCLK_DEBUG_R

PCLK_2

PCLK_TPM_R

PCLK_EC_R

PCLK_ICH_R

PCLK_2

PCLK_EC_R

PULL HIGH PULL DOWN

NO OVERCLOCKING NORMAL RUN

PIN 20/21 IS SRC0

PIN 24/25 IS 27MHz

PIN 53/54 IS CPUITP PIN 53/54 IS SRC8

The Beads for power 3.3V/1.05 are for EMI solution.

It is recommended to add it for better power/EMI performance.

C379

C379

10u/10V_8

10u/10V_8

U25

U25

9

VDD_PCI

16

VDD_48

23

VDD_PLL3

4

VDD_REF

46

VDD_SRC

62

VDD_CPU

19

VDD_96_IO

27

VDD_PLL3_IO

33

VDD_SRC_IO_1

52

VDD_SRC_IO_3

43

VDD_SRC_IO_2

56

VDD_CPU_IO

8

PCI0/CR#_A

10

PCI1/CR#_B

11

PCI2/TME

12

PCI3

13

PCI4/27M_Select

14

PCI_F5/ITP_EN

3

XTAL_IN

2

FSA

FSB CLKREQ_3G#_R

FSC

XTAL_OUT

17

USB_48/FSA

64

FSB/TEST_MODE

5

REF0/FSC/TESTSEL

65

VSS_BODY

15

VSS_PCI

18

VSS_48

VSS_IO2227M_NosSS/SRC1(LCDCLK)

26

VSS_PLL3

59

VSS_CPU

30

VSS_SRC1

36

VSS_SRC2

49

VSS_SRC3

1

VSS_REF

SLG8SP513VTR ,ICS9LPRS365BKLFT

<MAIN> : SLG8SP513VTR(AL8SP513000)

<SECOND> : ICS9LRS3165BKLFT(AL003165000)

<SECOND> : ICS9LPRS365BKLFT(ALPRS365000)

CLKREQA# CONTROL SRC0(default) or SRC2

CLKREQB# CONTROL SRC1(default) or SRC4

CLKREQC# CONTROL SRC2

CLKREQD# CONTROL SRC4

CLKREQE# CONTROL SRC6

CLKREQF# CONTROL SRC8

CLKREQG# CONTROL SRC9

CLKREQH# CONTROL SRC10

(default)

PIN 20/21 IS DOT96

PIN 24/25 IS LCDCLK

4

C369

C360

C360

0.1u/10V_4

0.1u/10V_4

C369

0.1u/10V_4

0.1u/10V_4

CK505

CK505

SRC11#/CR#_G

27M_SS/SRC1#(LCDCLK#

SRC0#/DOT96#

CKPWRGD/PWRDWN#

SLG8SP513

SLG8SP513

(default)

(default)

4

SCLK

SDA

PCI_STOP#

CPU_STOP#

CPU0

CPU0#

CPU1

CPU1#

SRC8/ITP

SRC8#/ITP#

SRC10

SRC10#

SRC11/CR#_H

SRC9

SRC9#

SRC7/CR#_F

SRC7#/CR#_E

SRC6

SRC6#

SRC4

SRC4#

SRC3/CR#_C

SRC3#/CR#_D

SRC2/SATA

SRC2#/SATA#

SRC0/DOT96

NC

C375

C375

0.1u/10V_4

0.1u/10V_4

55

SMBCK1

7

SMBDT1

6

45

PM_STPCPU#

44

61

60

58

57

54

53

41

42

CLKREQ_Dec#_R

40

39

37

38

51

50

48

47

34

35

31

CLKREQ_WLAN#_R

32

28

29

24

25

20

21

VR_PWRGD_CK410

63

FSC

0

0

0

0

1

1

1

1

C376

C376

0.1u/10V_4

0.1u/10V_4

R420 *0_4R420 *0_4

CPU_BSEL0(5)

CPU_BSEL1(5)

CPU_BSEL2(5)

FSB FSA

0

0

1

1

0

0

1

1

3

+1.05V_VDD

0.08A

C371

C371

0.1u/10V_4

0.1u/10V_4

PM_STPPCI#PM_STPPCI#_R

R416 475/F_4R416 475/F_4

T62T62

T63T63

T64T64

R404 475/F_4R404 475/F_4

+1.05V

+1.05V

+1.05V

BSEL0BSEL1BSEL2

CPU

0

266.66

1

133.33

0

200.00

1

166.66

0

333.33

1

100.00

0

400.00

1

3

2

L31

L31

PBY160808T-301Y-N/2A/300ohm_6

PBY160808T-301Y-N/2A/300ohm_6

C367

C367

*0.1u/10V_4

*0.1u/10V_4

1/19 : 439549_439549_CorbettPark_Schm_Rev0.5: If this pin is

used as PCI_STOP#, it is required to provide a 10-k pull-up to

Vcc3_3. It is not recommended to connect this signal to the

Tiger Point(NM10) as it may cause unexpected system behavior.

PM_STPPCI# (12)

PM_STPCPU# (12)

CLK_CPU_BCLK (5)

CLK_CPU_BCLK# (5)

CLK_MCH_BCLK (5)

CLK_MCH_BCLK# (5)

CLK_PCIE_DMIP (5)

CLK_PCIE_DMIN (5)

CLK_PCIE_Dec (26)

CLK_PCIE_Dec# (26)

CLKREQ_Dec# (26)

CLK_PCIE_ICH (9)

CLK_PCIE_ICH# (9)

CLK_PCIE_SATA (10)

CLK_PCIE_SATA# (10)

PE2CLK+ (21)

PE2CLK- (21)

CLKREQ_3G# (21)

CLKREQ_WLAN# (21)

PE4CLK+ (21)

PE4CLK- (21)

DREFSSCLK (5)

DREFSSCLK# (5)

DREFCLK (5)

DREFCLK# (5)

R392 *1K_4R392 *1K_4

R391 0_4R391 0_4

R395 *0_4R395 *0_4

R388 *1K_4R388 *1K_4

R389 0_4R389 0_4

R387 *0_4R387 *0_4

R369 *1K_4R369 *1K_4

R370 0_4R370 0_4

R368 *0_4R368 *0_4

SRC

100

PCI

33.33

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

14.318

100

100

33.33

100

14.31833.33

100

100

100

33.33

+1.05V

To SB

To CPU (Core CLK)

To CPU (Host CLK)

To CPU (DMI CLK)

To Decoder

To SB (DMI CLK)

To SB (SATA CLK)

To Mini Card 1 (WLAN)

To Mini Card 2 (3G/Wimax)

To CPU (SS CLK)

To CPU (PLL CLK)

VR_PWRGD_CK410#(29)

<20090721(B2A)>

Change Q3,Q5,Q6 from BAM700200F6 to BAM70020002 (with ESD protection function)

Clock Gen I2C

REF

USB

48

DOT

96

964814.31833.33

964814.318

9648

964814.31833.33

964814.31833.33

964814.318

RESERVED

2

1

<20090721(B2A)_Intel MOW WW28,2009>

Stuff R56,R60 to solve system maybe boot failure issue

PM_STPPCI#_R

PM_STPCPU#

CLKREQ_WLAN#_R

CLKREQ_Dec#_R

CLKREQ_3G#_R

<20090527(A1A)_Silego suggestion>

The EMI capacitor should be placed

between pin and series resistor for

good EMI and SI

R419 10K_4R419 10K_4

R418 10K_4R418 10K_4

R411 10K_4R411 10K_4

R417 10K_4R417 10K_4

R406 10K_4R406 10K_4

<EMI>

PCLK_DEBUG_R

PCLK_EC_R

PCLK_ICH_R

FSA

FSC

PCLK_TPM_R

C343 *22p/50V_4C343 *22p/50V_4

C340 *33p/50V_4C340 *33p/50V_4

C351 *33p/50V_4C351 *33p/50V_4

C362 *22p/50V_4C362 *22p/50V_4

C347 *33p/50V_4C347 *33p/50V_4R409 475/F_4R409 475/F_4

C345 *33p/50V_4C345 *33p/50V_4

VR PWRGD

R400 *10K_4R400 *10K_4

2

R394 10K_4R394 10K_4

1

PCLK_SMB(12,21)

PDAT_SMB(12,21)

3

VR_PWRGD_CK410

2N7002K

2N7002K

Q25

Q25

+3V

2

3

2N7002K

2N7002K

3

2N7002K

2N7002K

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

1

Q23

Q23

Q24

Q24

+3V

2

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

+3V

VR_PWRGD_CK410 (12)

R359

R359

2.2K_4

2.2K_4

SMBCK1

R360

R360

2.2K_4

2.2K_4

SMBDT1

ZGA

ZGA

ZGA

1

2 38Wednesday, July 07, 2010

2 38Wednesday, July 07, 2010

2 38Wednesday, July 07, 2010

02

+3V

SMBCK1 (3,21,25,26)

SMBDT1 (3,21,25,26)

1B

1B

1B

Page 3

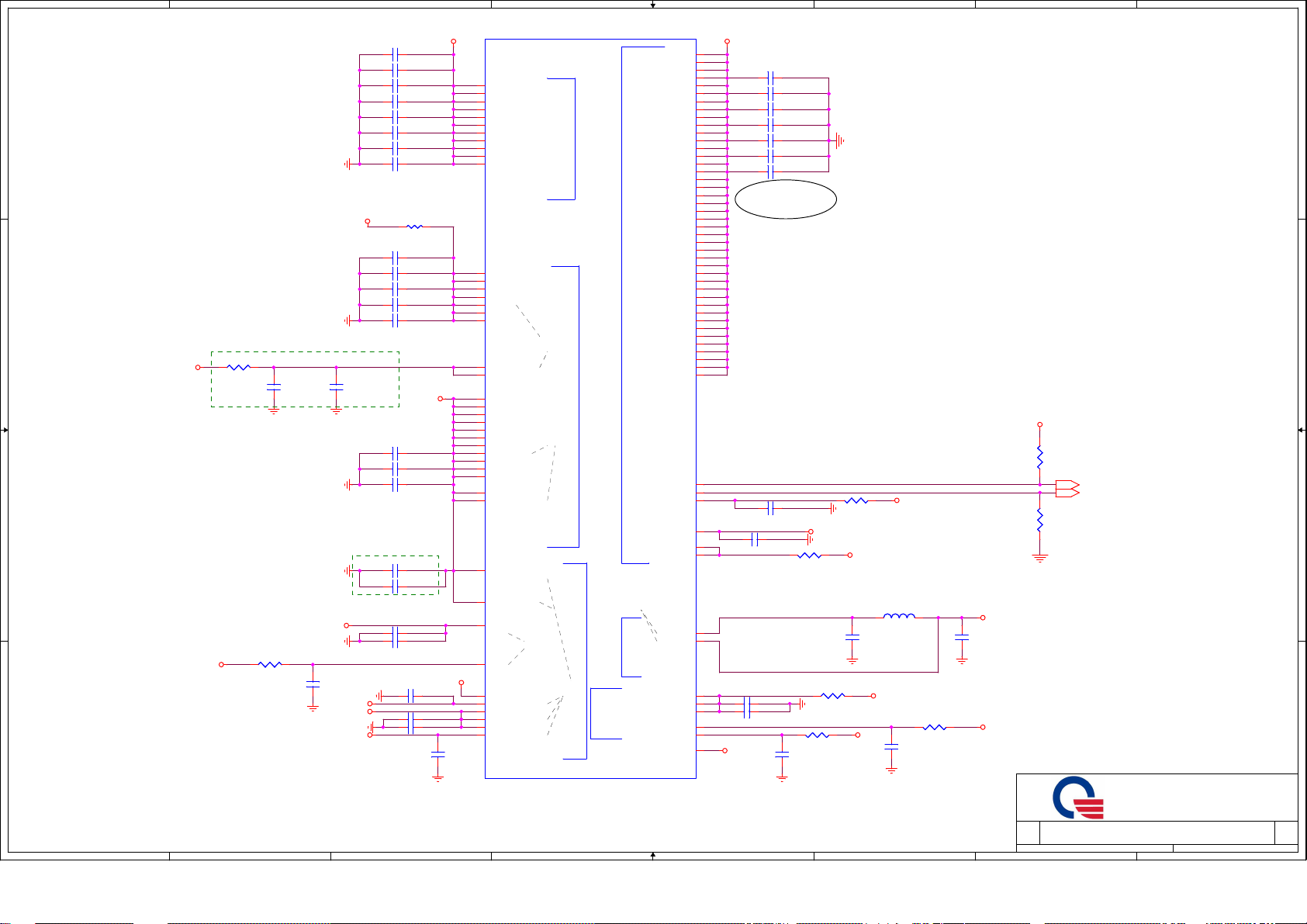

5

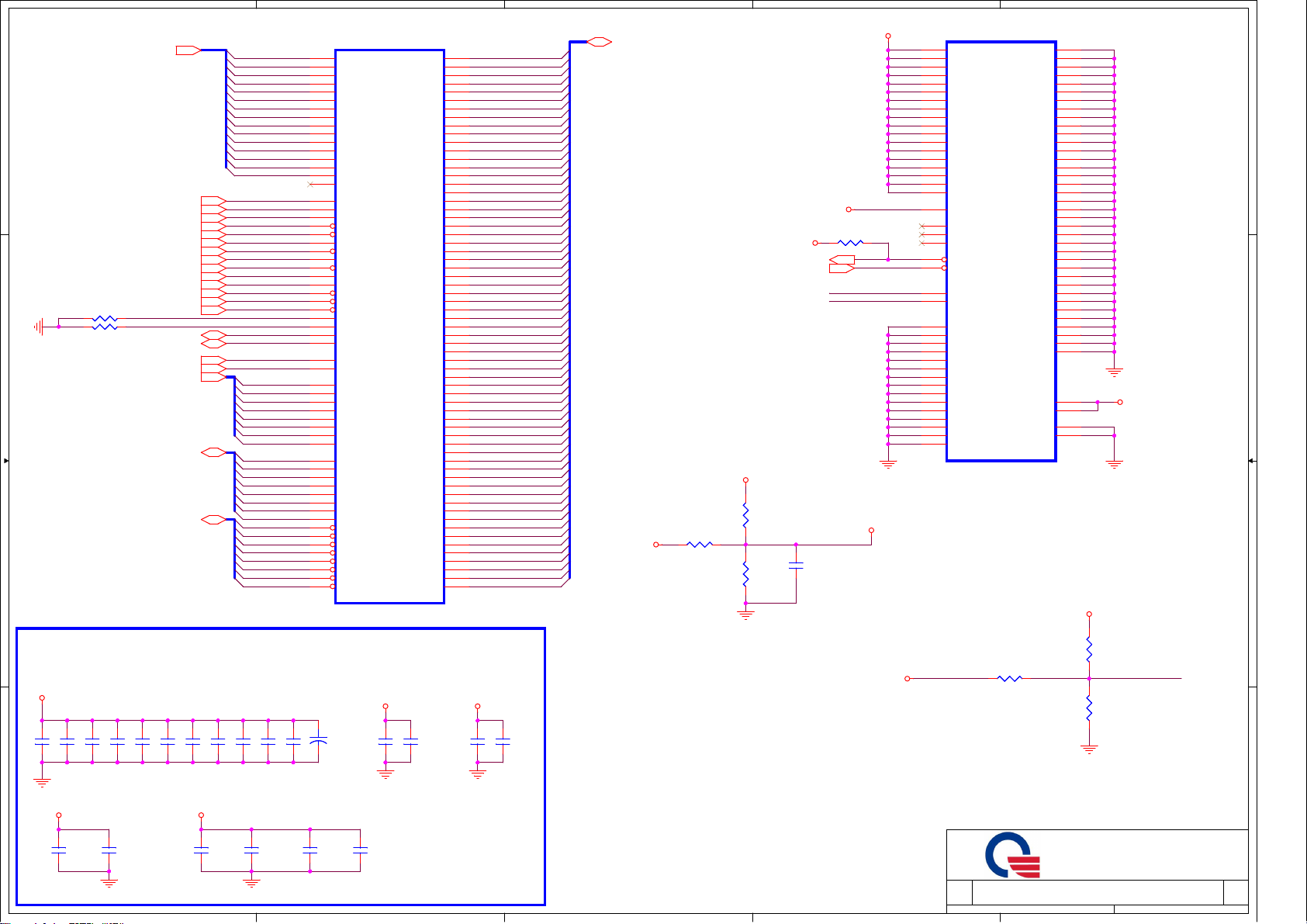

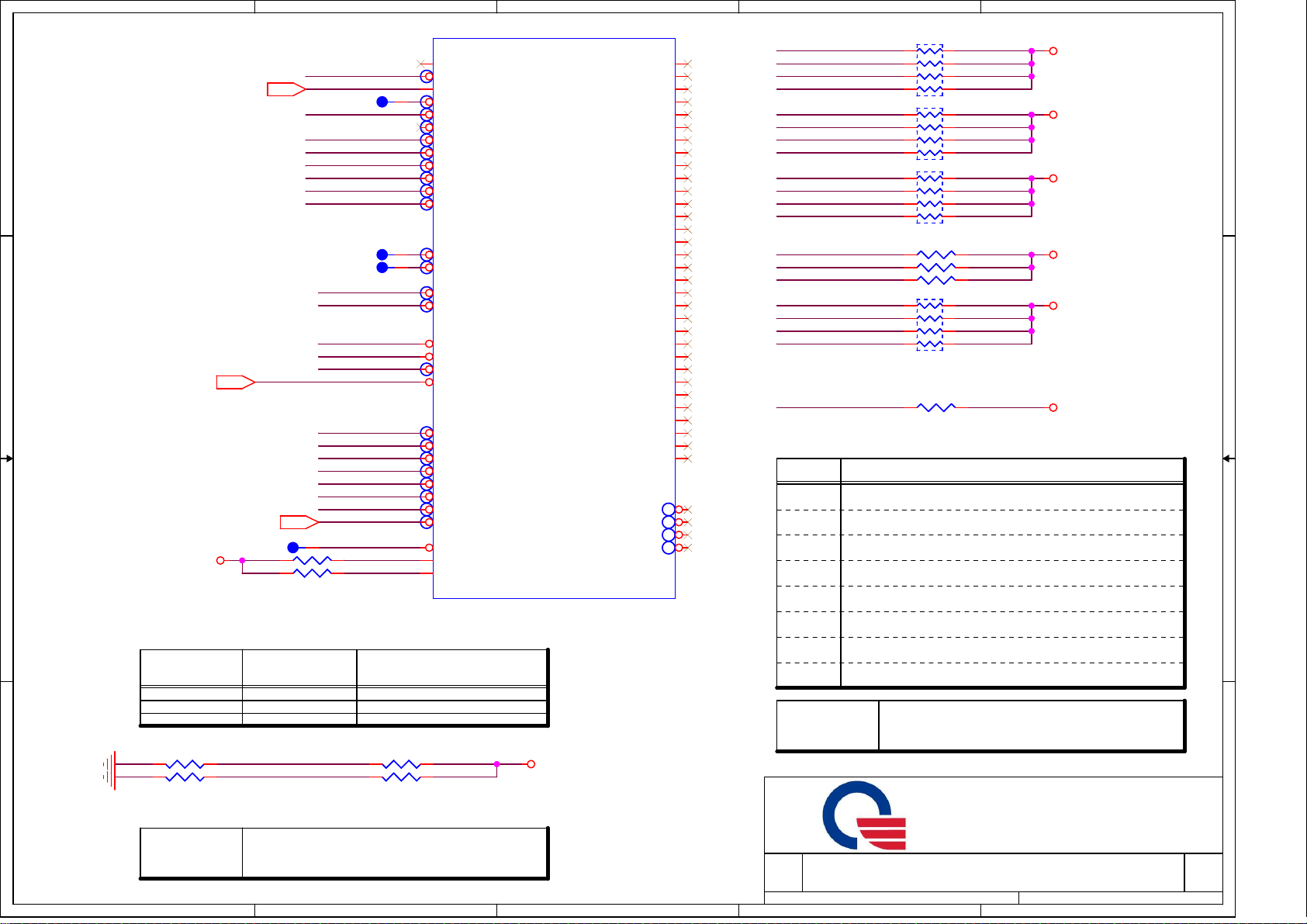

DDR_STD(DDR)

M_A_A[14:0](6)

D D

M_A_BS0(6)

M_A_BS1(6)

M_A_BS2(6)

M_CS#0(6)

M_CS#1(6)

M_CLK0(6)

M_CLK0#(6)

M_CLK1(6)

M_CLK1#(6)

M_CKE0(6)

M_CKE1(6)

M_A_CAS#(6)

M_A_RAS#(6)

R353 10K_4R353 10K_4

R357 10K_4R357 10K_4

C C

B B

M_A_WE#(6)

SMBCK1(2,21,25,26)

SMBDT1(2,21,25,26)

M_ODT0(6)

M_ODT1(6)

M_A_DM[7:0](6)

M_A_DQS[7:0](6)

M_A_DQS#[7:0](6)

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

DIMM0_SA0

DIMM0_SA1

SMBCK1

SMBDT1

M_A_DM0

M_A_DM1

M_A_DM3

M_A_DM2

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS3

M_A_DQS2

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#3

M_A_DQS#2

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

107

119

109

108

114

121

101

103

102

104

115

110

113

197

201

202

200

116

120

136

153

170

187

137

154

171

188

135

152

169

186

98

97

96

95

92

91

90

86

89

85

84

83

80

78

79

73

74

11

28

46

63

12

29

47

64

10

27

45

62

4

JDIM1A

JDIM1A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

BA0

BA1

BA2

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DDR3-DIMM0_H=4_STD

DDR3-DIMM0_H=4_STD

3

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

(204P)

(204P)

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

M_A_DQ5

M_A_DQ1

M_A_DQ7

M_A_DQ6

M_A_DQ4

M_A_DQ0

M_A_DQ2

M_A_DQ3

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ24

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ29

M_A_DQ25

M_A_DQ30

M_A_DQ31

M_A_DQ20

M_A_DQ16

M_A_DQ19

M_A_DQ22

M_A_DQ21

M_A_DQ17

M_A_DQ23

M_A_DQ18

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ47

M_A_DQ46

M_A_DQ49

M_A_DQ48

M_A_DQ51

M_A_DQ55

M_A_DQ53

M_A_DQ52

M_A_DQ50

M_A_DQ54

M_A_DQ61

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ56

M_A_DQ60

M_A_DQ62

M_A_DQ63

M_A_DQ[63:0] (6)

+SMDDR_VREF

R171

R171

1K/F_4

1K/F_4

R184 *0_6R184 *0_6

R181

R181

1K/F_4

1K/F_4

PM_EXTTS#0(5)

DDR3_DRAMRST#(6)

+1.5VSUS

+SMDDR_VREF_DIMM

R381 *10K_4R381 *10K_4

+3V

C183

C183

470p/50V_4

470p/50V_4

2

+1.5VSUS

2.48A

+3V

+SMDDR_VREF_DQ0

+SMDDR_VREF_DIMM

+SMDDR_VREF_DIMM

JDIM1B

JDIM1B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

DDR3-DIMM0_H=4_STD

DDR3-DIMM0_H=4_STD

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

(204P)

(204P)

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

GND

GND

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

205

206

+1.5VSUS

1

+0.75V_DDR_VTT

R53

R53

1K/F_4

Place these Caps near So-Dimm0.

+1.5VSUS

C319

C104

C104

10u/6.3V_6

10u/6.3V_6

C339

C339

0.1u/10V_4

0.1u/10V_4

5

C319

10u/6.3V_6

10u/6.3V_6

C127

C127

10u/6.3V_6

10u/6.3V_6

C100

C100

10u/6.3V_6

10u/6.3V_6

A A

+3V

C154

C154

10u/6.3V_6

10u/6.3V_6

C341

C341

2.2u/6.3V_6

2.2u/6.3V_6

C314

C314

10u/6.3V_6

10u/6.3V_6

C108

C108

0.1u/10V_4

0.1u/10V_4

+0.75V_DDR_VTT

C353

C353

0.1u/10V_4

0.1u/10V_4

C136

C136

0.1u/10V_4

0.1u/10V_4

C144

C144

0.1u/10V_4

0.1u/10V_4

C352

C352

0.1u/10V_4

0.1u/10V_4

C315

C315

0.1u/10V_4

0.1u/10V_4

C313

C313

0.1u/10V_4

0.1u/10V_4

C344

C344

0.1u/10V_4

0.1u/10V_4

+

+

C169

C169

C90

C90

330u/2V_7343

330u/2V_7343

0.1u/10V_4

0.1u/10V_4

C342

C342

0.1u/10V_4

0.1u/10V_4

+SMDDR_VREF_DIMM

C184

C184

2.2u/6.3V_6

2.2u/6.3V_6

4

+SMDDR_VREF_DQ0

C59

C59

0.1u/10V_4

0.1u/10V_4

C56

C56

2.2u/6.3V_6

2.2u/6.3V_6

3

+SMDDR_VREF

2

R55 *0_6R55 *0_6

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

DDRIII SO-DIMM-0

DDRIII SO-DIMM-0

DDRIII SO-DIMM-0

Date: Sheet of

Date: Sheet of

Date: Sheet of

1K/F_4

+SMDDR_VREF_DQ0

R54

R54

1K/F_4

1K/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZGA

ZGA

ZGA

3 38Wednesday, July 07, 2010

3 38Wednesday, July 07, 2010

3 38Wednesday, July 07, 2010

1

1A

1A

1A

Page 4

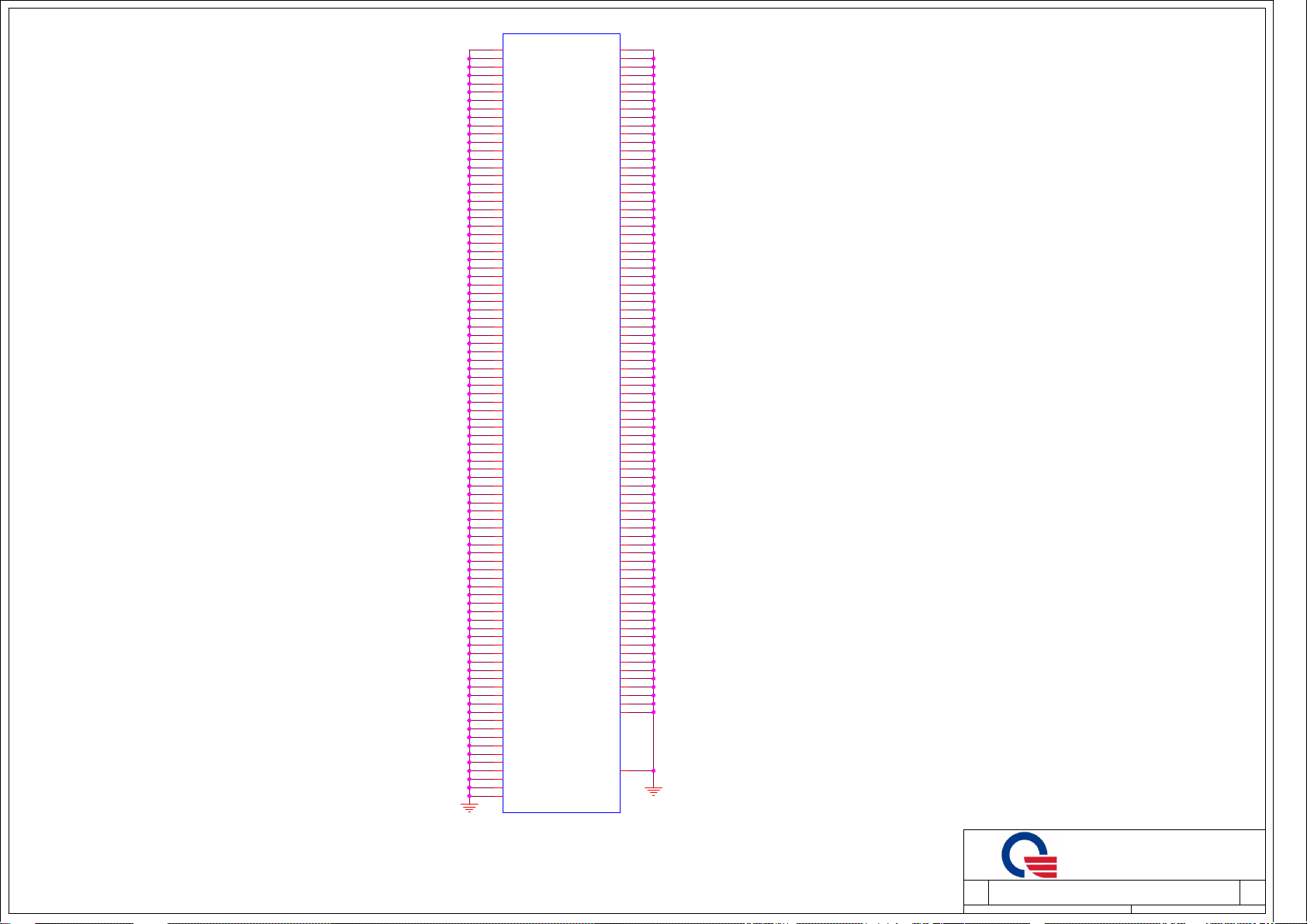

5

D D

C C

4

3

2

1

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLANK

BLANK

BLANK

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZGA

ZGA

ZGA

1A

1A

1A

4 38Wednesday, July 07, 2010

4 38Wednesday, July 07, 2010

4 38Wednesday, July 07, 2010

1

Page 5

5

PINEVIEW_M

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

EXP_CLKINN

EXP_CLKINP

RSVD

RSVD

RSVD

RSVD

RSVD_K2

RSVD_J1

RSVD_M4

RSVD_L3

PINEVIEW_M

REV = 1.1

REV = 1.1

VGA

VGA

PM_EXTTS#_1/DPRSLPVR

MISC

MISC

3 OF 6

3 OF 6

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

DMI

DMI

1 OF 6

1 OF 6

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

CRT_DDC_DATA

CRT_DDC_CLK

DAC_IREF

DPL_REFCLKINP

DPL_REFCLKINN

DPL_REFSSCLKINP

DPL_REFSSCLKINN

PM_EXTTS#_0

PWROK

RSTINB

HPL_CLKINN

HPL_CLKINP

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

EXP_RCOMPO

EXP_ICOMPI

EXP_RBIAS

RSVD_TP

RSVD_TP

RSVD_K3

RSVD_L2

RSVD_M2

RSVD_N2

M30

M29

N31

P30

P29

N30

L31

L30

P28

Y30

Y29

AA30

AA31

K29

J30

L5

AA3

W8

W9

G2

G1

H3

J2

L10

L9

L8

N11

P11

K3

L2

M2

N2

U21C

U21C

D12

XDP_RSVD_00

A7

XDP_RSVD_01

D6

XDP_RSVD_02

C5

XDP_RSVD_03

C7

XDP_RSVD_04

T32T32

C6

XDP_RSVD_05

D8

XDP_RSVD_06

B7

XDP_RSVD_07

A9

R303 1K/F_4R303 1K/F_4

D D

C C

DMI_TXP0(9)

DMI_TXN0(9)

DMI_TXP1(9)

DMI_TXN1(9)

CLK_PCIE_DMIN(2)

CLK_PCIE_DMIP(2)

B B

XDP_RSVD_08

D9

XDP_RSVD_09

C8

XDP_RSVD_10

T33T33

B8

XDP_RSVD_11

C10

XDP_RSVD_12

D10

XDP_RSVD_13

B11

XDP_RSVD_14

B10

XDP_RSVD_15

B12

XDP_RSVD_16

T34T34

C11

XDP_RSVD_17

L11

RSVD

AA7

RSVD_TP

AA6

RSVD_TP

R5

RSVD_TP

R6

RSVD_TP

AA21

RSVD_TP

W21

RSVD_TP

T21

RSVD_TP

V21

RSVD_TP

Pineview-M 1.66G

Pineview-M 1.66G

U21A

U21A

F3

F2

H4

G3

N7

N6

R10

R9

N10

N9

K2

J1

M4

L3

Pineview-M 1.66G

Pineview-M 1.66G

4

R344 *0/short_4R344 *0/short_4

CLK_MCH_BCLK# (2)

CLK_MCH_BCLK (2)

<Layout note>

Place within 500mil from CPU pin

EXP_COMP

R162 49.9/F_4R162 49.9/F_4

EXP_RBIAS

R159 750/F_4R159 750/F_4

<Layout note>

Place within 500mil from CPU pin

PM_EXTTS#0

R343 10K_4R343 10K_4

3

INT_TXLCLKN(25)

INT_TXLCLKP(25)

INT_TXLOUTN0(25)

INT_TXLOUTP0(25)

INT_TXLOUTN1(25)

INT_TXLOUTP1(25)

INT_TXLOUTN2(25)

INT_TXLOUTP2(25)

DREFCLK (2)

DREFCLK# (2)

DREFSSCLK (2)

DREFSSCLK# (2)

PM_DPRSLPVR (12,29)

PM_EXTTS#0 (3)

IMVP_PWRGD (12,29)

PLTRST# (12,21,23,25,26)

<20090610(A1A)_Sighting Report Rev002_Number:3359187>

Avoid a glitch during system power up

INT_LVDS_PWM(15)

+3V

LVDS_CLK(15)

LVDS_DATA(15)

INT_LVDS_DIGON(15)

LCD Panel Backlight

+3V

C338 0.1u/10V_4C338 0.1u/10V_4

U23

IMVP_PWRGD

LBKLT_EN

DMI_RXP0 (9)

DMI_RXN0 (9)

DMI_RXP1 (9)

DMI_RXN1 (9)

U23

2

1

R352

R352

100K_4

100K_4

R350 *0_4R350 *0_4

<Layout note>

PLACE TCK/TDI/TMS TERMINATION NEAR CPU

TC7SH08FU

TC7SH08FU

3 5

4

XDP PU

XDP_TMS

XDP_TDI

H_PREQ#

+3V

XDP_TCK

XDP_TRST#

R165 51/J_4R165 51/J_4

R168 51/J_4R168 51/J_4

R173 51/J_4R173 51/J_4

R315 51/J_4R315 51/J_4

R170 51/J_4R170 51/J_4

XDP_BPM#5 : Length<200mil

R189 2.37K/F_4R189 2.37K/F_4

LBKLT_EN

R193 *2.2K/J_4R193 *2.2K/J_4

R196 *2.2K/J_4R196 *2.2K/J_4

INT_LVDS_BLON (15)

+1.05V

+3V

U25

U26

R23

R24

N26

N27

R26

R27

LIBG

R22

J28

N22

N23

L27

L26

LCTLA_CLK

L23

LCTLB_DATA

K25

K23

K24

H26

T19T19

G11

T36T36

E15

T23T23

G13

T21T21

F13

T37T37

B18

T39T39

B20

T41T41

C20

T42T42

B21

T18T18

G5

XDP_TDI

D14

T35T35

D13

XDP_TCK

B14

XDP_TMS

C14

XDP_TRST#

C16

H_THERMDA

D30

H_THERMDC

E30

C30

D31

R347 2.2K/J_4R347 2.2K/J_4

R346 2.2K/J_4R346 2.2K/J_4

<EMI>

C215

C215

*220P/50V_4

*220P/50V_4

U21D

U21D

LVD_A_CLKM

LVD_A_CLKP

LVD_A_DATAM_0

LVD_A_DATAP_0

LVD_A_DATAM_1

LVD_A_DATAP_1

LVD_A_DATAM_2

LVD_A_DATAP_2

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LBKLT_EN

LBKLT_CTL

LCTLA_CLK

LCTLB_CLK

LDDC_CLK

LDDC_DATA

LVDD_EN

BPM_1B_0

BPM_1B_1

BPM_1B_2

BPM_1B_3

BPM_2_0#/RSVD

BPM_2_1#/RSVD

BPM_2_2#/RSVD

BPM_2_3#/RSVD

RSVD

TDI

TDO

TCK

TMS

TRST_B

THRMDA_1

THRMDC_1

RSVD_C30

RSVD_D31

Pineview-M 1.66G

Pineview-M 1.66G

LVDS_CLK

LVDS_DATA

C214

C214

*220P/50V_4

*220P/50V_4

2

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

ICH

ICH

LVDS

LVDS

THERMTRIP_B

CPUPWRGOOD

CPU

CPU

4 OF 6

4 OF 6

<Layout note>

Place within 500mil from CPU pin and 5mil spacing

Max 500mil Near CPU pin

R126

R126

976/F_4

976/F_4

R119

R119

3.32K/F_4

3.32K/F_4

SMI_B

A20M_B

FERR_B

LINT00

LINT10

IGNNE_B

STPCLK_B

DPRSTP_B

DPSLP_B

INIT_B

PRDY_B

PREQ_B

PROCHOT_B

GTLREF

VSS

RSVD

RSVD

BCLKN

BCLKP

BSEL_0

BSEL_1

BSEL_2

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

EXTBGREF

C138

C138

1U/6.3V_4

1U/6.3V_4

E7

H7

H6

F10

F11

E5

F8

G6

G10

G8

E11

F15

E13

C18

W1

A13

H27

L6

E17

H10

J10

K5

H5

K6

H30

H29

H28

G30

G29

F29

E29

L7

D20

H13

D18

K9

D19

K7

T20T20

H_PREQ#

H_THRMTRIP#

R318 68_4R318 68_4

H_PWRGD

H_GTLREF

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

H_EXBGREF

1

H_SMI# (10)

H_A20M# (10)

H_FERR# (10)

H_INTR (10)

H_NMI (10)

H_IGNNE# (10)

H_STPCLK# (10)

ICH_DPRSTP# (12,29)

H_DPSLP# (12)

H_INIT# (10)

<20090511(A1A)_ Checklist Rev0. 7>

+1.05V

PROCHOT_B:68ohm±5% pull-up to Vcc1_05

(VCCP) at both CPU side and Intel MVP

H_PROCHOT# (29)

H_PWRGD (12)

CLK_CPU_BCLK# (2)

CPU_BSEL0 (2)

CPU_BSEL1 (2)

CPU_BSEL2 (2)

VID0 (29)

VID1 (29)

VID2 (29)

VID3 (29)

VID4 (29)

VID5 (29)

VID6 (29)

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

<Layout note>

Place within 500mil from CPU pin

+1.05V+1.05V

R309

R309

1K/F_4

1K/F_4

R311

R311

2K/F_4

2K/F_4

CLK_CPU_BCLK (2)

R123 470/J_4R123 470/J_4

R121 470/J_4R121 470/J_4

R122 470/J_4R122 470/J_4

1D: No Stuff C8007 (CRB v1.0)

H_GTLREFH_EXBGREF

C316

C316

1U/6.3V_4

1U/6.3V_4

+1.05V

C317

C317

*220P/50V_4

*220P/50V_4

04

CPU FAN CTRL(THM)

CPU Thermal monitor(THM)

8/11 B-test : for EMI

C33

C33

*220p/50V_6

*220p/50V_6

5

FAN_SIG

FAN_PWM_B

CPUFAN#

FAN_SIG (23)

2ND_MBCLK(23)

2ND_MBDATA(23)

THERM_ALERT#(12)

R355 *0_4R355 *0_4

THERM_ALERT#_R

FAN_ON#

ALERT#:pull up at SB side

3

C32

C32

*220p/50V_6

*220p/50V_6

+5V

+3V

R52

R52

R50

2

1 3

R50

10K_4

10K_4

Q1

MMBT3904Q1MMBT3904

+3V

R43

R43

10K_4

10K_4

Q3

2

MMBT3904Q3MMBT3904

1 3

10K_4

10K_4

FAN_PWM_CNFAN_PWM_E

+3V

R49

R49

10K_4

10K_4

FAN_SIG

+5V

CN13

CN13

6

345

2

1

FAN

FAN

4

FAN_PWM_CN

A A

R40 10K_4R40 10K_4

FAN_ON#

CPUFAN#(23)

R349

R349

10K_4

10K_4

+3V

R354

R354

*10K_4

*10K_4

8

7

6

4

GMT : AL000780000

WND : AL83L771K01

+3V

R342 *0/short_4R342 *0/short_4

U22

U22

VCC

SCLK

DXP

SDA

DXN

ALERT#

GND

OVERT#

G780P81U

G780P81U

GMT ADDRESS: 4CH

EC ADDRESS: 98H

1

2

3

5

C336 0.1u/10V_4C336 0.1u/10V_4

H_THERMDA

C333

C333

2200p/50V_4

2200p/50V_4

H_THERMDC

<Layout Note>

Routing 10:10 mils and

away from noise source

with ground gard

2

125 Degree Protection(CPU)

IMVP_PWRGD

+1.05V

R167

CPU

H_THRMTRIP#

R167

56_4

56_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

+1.05V

3

Q10

Q10

2N7002K

2N7002K

2

R146

R146

1K_4

1K_4

R163 *0_4R163 *0_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Pineview DMI/Display

Pineview DMI/Display

Pineview DMI/Display

Q12

Q12

1 3

MMBT3904

MMBT3904

1

2

1

<20090721(B2A)>

Change Q7 from BAM700200F6

to BAM70020002 (with ESD

protection function)

SYS_SHDN# (28,29)

PM_THRMTRIP# (10)

ZGA

ZGA

ZGA

Tigerpoint

1B

1B

1B

385

385

385

Page 6

5

D D

C C

DDR3 PWROK

SUSON(23,30,32)

HWPG_1.5V(23,30)

B B

A A

+3V_S5

53

1

4

2

U9

U9

TC7SH08FU

TC7SH08FU

+SMDDR_VREF

5

R142

R142

12.1K/F_4

12.1K/F_4

DDRAM_PWROK

R143

R143

10K_4

10K_4

<EMI>

DG 2.1 : It is strongly recommended that the SODIMM VREF motherboard traces, going from

their VREF resistor dividers to their specified SODIMM VREF pins, be ground referenced

on the motherboard where ever possible to help minimize risks of any possible noise

being coupled onto VREF. If they can't be referenced to ground we recommend placing

a site for a 0603 capacitor near the VREF divider. These 0603 capacitor sites must be

connected on one end to the non ground reference plane the VREF trace is referenced

to and the other end must be connected to ground.

DDR3_DRAMRST#(3)

<Layout note>

Close to DDR_VREF pin

R330 *0_4R330 *0_4

C324

C324

*1000p/50V_4

*1000p/50V_4

<Layout note>

Close to pin

+1.5VSUS

4

M_A_A[14..0](3)

M_A_WE#(3)

M_A_CAS#(3)

M_A_RAS#(3)

M_A_BS0(3)

M_A_BS1(3)

M_A_BS2(3)

M_CS#0(3)

M_CS#1(3)

M_CKE0(3)

M_CKE1(3)

M_ODT0(3)

M_ODT1(3)

M_CLK0(3)

M_CLK0#(3)

M_CLK1(3)

M_CLK1#(3)

+1.5VSUS

R339 80.6/F_4R339 80.6/F_4

R323 80.6/F_4R323 80.6/F_4

+1.5VSUS

R325

R325

1K/F_4

1K/F_4

DDR_VREF

R335

R335

1K/F_4

1K/F_4

4

R296

R296

*10K_4

*10K_4

DDRAM_PWROK

C329 0.1U/10V_4C329 0.1U/10V_4

C322 0.01U/25V_4C322 0.01U/25V_4

C330

C330

0.1u/16V_6

0.1u/16V_6

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_WE#

M_A_CAS#

M_A_RAS#

M_A_BS0

M_A_BS1

M_A_BS2

M_CS#0

M_CS#1

M_CKE0

M_CKE1

M_ODT0

M_ODT1

M_CLK0

M_CLK#0

M_CLK1

M_CLK#1

DDR_VREF

SM_RCOMP

SM_RCOMP#

AH19

AJ18

AK18

AK16

AJ14

AH14

AK14

AJ12

AH13

AK12

AK20

AH12

AJ11

AJ24

AJ10

AK22

AJ22

AK21

AJ20

AH20

AK11

AH22

AK25

AJ21

AJ25

AH10

AH9

AK10

AK24

AH26

AH24

AK27

AG15

AF15

AD13

AC13

AC15

AD15

AF13

AG13

AD17

AC17

AB15

AB17

AB4

AK8

AB11

AB13

AL28

AK28

AJ26

AK29

AJ8

U21B

U21B

DDR_A_MA_0

DDR_A_MA_1

DDR_A_MA_2

DDR_A_MA_3

DDR_A_MA_4

DDR_A_MA_5

DDR_A_MA_6

DDR_A_MA_7

DDR_A_MA_8

DDR_A_MA_9

DDR_A_MA_10

DDR_A_MA_11

DDR_A_MA_12

DDR_A_MA_13

DDR_A_MA_14

DDR_A_W EB

DDR_A_CASB

DDR_A_RASB

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CSB_0

DDR_A_CSB_1

DDR_A_CSB_2

DDR_A_CSB_3

DDR_A_CKE_0

DDR_A_CKE_1

DDR_A_CKE_2

DDR_A_CKE_3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_0

DDR_A_CKB_0

DDR_A_CK_1

DDR_A_CKB_1

DDR_A_CK_3

DDR_A_CKB_3

DDR_A_CK_4

DDR_A_CKB_4

RSVD_AD17

RSVD_AC17

RSVD_AB15

RSVD_AB17

VSS

RSVD

RSVD_TP

RSVD_TP

DDR_VREF

DDR_RPD

DDR_RPU

RSVD

Pineview-M 1.66G

Pineview-M 1.66G

DDR_A

DDR_A

3

3

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

2 OF 6

2 OF 6

DDR_A_DQS_0

DDR_A_DQSB_0

DDR_A_DM_0

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQS_1

DDR_A_DQSB_1

DDR_A_DM_1

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_DM_2

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_DM_3

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQS_4

DDR_A_DQSB_4

DDR_A_DM_4

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQS_5

DDR_A_DQSB_5

DDR_A_DM_5

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQS_6

DDR_A_DQSB_6

DDR_A_DM_6

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQS_7

DDR_A_DQSB_7

DDR_A_DM_7

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

AD3

AD2

AD4

AC4

AC1

AF4

AG2

AB2

AB3

AE2

AE3

AB8

AD7

AA9

AB6

AB7

AE5

AG5

AA5

AB5

AB9

AD6

AD8

AD10

AE8

AG8

AG7

AF10

AG11

AF7

AF8

AD11

AE10

AK5

AK3

AJ3

AH1

AJ2

AK6

AJ7

AF3

AH2

AL5

AJ6

AG22

AG21

AD19

AE19

AG19

AF22

AD22

AG17

AF19

AE21

AD21

AE26

AG27

AJ27

AE24

AG25

AD25

AD24

AC22

AG24

AD27

AE27

AE30

AF29

AF30

AG31

AG30

AD30

AD29

AJ30

AJ29

AE29

AD28

AB27

AA27

AB26

AA24

AB25

W24

W22

AB24

AB23

AA23

W27

M_A_DQS0

M_A_DQS#0

M_A_DM0

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQS1

M_A_DQS#1

M_A_DM1

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQS2

M_A_DQS#2

M_A_DM2

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQS3

M_A_DQS#3

M_A_DM3

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQS4

M_A_DQS#4

M_A_DM4

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQS5

M_A_DQS#5

M_A_DM5

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQS6

M_A_DQS#6

M_A_DM6

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQS7

M_A_DQS#7

M_A_DM7

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

2

1

05

M_A_DQ[63..0] (3)

M_A_DM[7..0] (3)

M_A_DQS[7..0] (3)

M_A_DQS#[7..0] (3)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

2

Wednesday, July 07, 2010

PROJECT :

Pineview DDR

Pineview DDR

Pineview DDR

ZGA

ZGA

ZGA

1B

1B

1B

386

386

1

386

Page 7

1

A A

B B

C C

D D

1

<Layout note>

Close to pin

+1.5VSUS

<Layout note>

VCCA_DDR and VCCACK_DDR rails can be

on the same source but make sure the

plane shapes are split near Pineview-M

to avoid noise coupling

VCCGFX

2

R148 0_6R148 0_6

R351 0_6R351 0_6

2

C123

C123

22U/6.3V_8

22U/6.3V_8

C193 2.2U/6.3V_6C193 2.2U/6.3V_6

C162 1U/6.3V_4C162 1U/6.3V_4

C157 1U/6.3V_4C157 1U/6.3V_4

C176 1U/6.3V_4C176 1U/6.3V_4

C187 1U/6.3V_4C187 1U/6.3V_4

C177 1U/6.3V_4C177 1U/6.3V_4

C166 1U/6.3V_4C166 1U/6.3V_4

C168 1U/6.3V_4C168 1U/6.3V_4

+1.5VSUS

C194 2.2U/6.3V_6C194 2.2U/6.3V_6

C161 1U/6.3V_4C161 1U/6.3V_4

C178 1U/6.3V_4C178 1U/6.3V_4

C201 1U/6.3V_4C201 1U/6.3V_4

C205 1U/6.3V_4C205 1U/6.3V_4

VCC1.5_VCCCK_DDR

C141

C141

1U/6.3V_4

1U/6.3V_4

C101 22u/6.3V_8C101 22u/6.3V_8

C133 4.7U/6.3V_6C133 4.7U/6.3V_6

C143 1U/6.3V_4C143 1U/6.3V_4

<Layout note>

Close to pin AA19

C114 *0.1u/10V_4C114 *0.1u/10V_4

C189 *0.1u/10V_4C189 *0.1u/10V_4

+1.8V

C337

C337

1u/6.3V_4

1u/6.3V_4

C207 1U/6.3V_4C207 1U/6.3V_4

C208 1U/6.3V_4C208 1U/6.3V_4

VCCGFX_VCCACRTDAC

+1.05V

+1.05V

+1.05V

3

R176 0_8R176 0_8

+1.05V

C149 1U/6.3V_4C149 1U/6.3V_4

C113 1U/6.3V_4C113 1U/6.3V_4

C119 1U/6.3V_4C119 1U/6.3V_4

3

VCCGFX

AK13

AK19

AL11

AL16

AL21

AL25

AA10

AA11

AA19

AC31

+3V

C321

C321

*1u/6.3V_4

*1u/6.3V_4

W14

W16

W18

W19

AK9

AK7

AL7

U10

W10

W11

V11

A21

T13

T14

T16

T18

T19

V13

V19

T30

T31

J31

U5

U6

U7

U8

U9

V2

V3

V4

C3

B2

C2

U21E

U21E

VCCGFX

1.38A

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

2.27A

VCCCK_DDR

VCCCK_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCACK_DDR

VCCACK_DDR

VCCD_AB_DPL

VCCD_HMPLL

VCCSFR_AB_DPL

0.154A

VCCACRTDAC

0.006A

VCC_GIO

VCCRING_EAST

VCCRING_WEST

VCCRING_WEST

VCCRING_WEST

VCC_LGI_VID

5 OF 6

5 OF 6

Pineview-M 1.66G

Pineview-M 1.66G

GFX/MCH

GFX/MCH

1.32A

0.33A

4

PINEVIEW_M

PINEVIEW_M

DDR

DDR

EXP\CRT\PLL

EXP\CRT\PLL

4

REV = 1.1

REV = 1.1

POWER

POWER

DMI

DMI

3.5A

CPU

CPU

0.08A

0.06A

LVDS

LVDS

0.104A

VCCSFR_DMIHMPLL

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCSENSE

VSSSENSE

VCCA

VCC

VCCP

VCCP

VCCALVD

VCCDLVD

0.48A

VCCA_DMI

VCCA_DMI

VCCA_DMI

RSVD

VCCP

5

VCC_CORE

A23

A25

A27

C170 1U/6.3V_4C170 1U/6.3V_4

B23

B24

C192 1U/6.3V_4C192 1U/6.3V_4

B25

B26

C202 1U/6.3V_4C202 1U/6.3V_4

B27

C24

C199 1U/6.3V_4C199 1U/6.3V_4

C26

D23

C198 22u/6.3V_8C198 22u/6.3V_8

D24

D26

C171 22u/6.3V_8C171 22u/6.3V_8

D28

E22

C188 22u/6.3V_8C188 22u/6.3V_8

E24

E27

F21

F22

12/17: power suggest to add PC75

F25

03/25: move PC75 to page 29

G19

G21

G24

H17

H19

H22

H24

J17

J19

J21

J22

K15

K17

K21

L14

L16

L19

L21

N14

N16

N19

N21

C29

B29

VCC1.5_VCCA

Y2

C303 0.01U/25V_4C303 0.01U/25V_4

D4

C129 *0.1u/10V_4C129 *0.1u/10V_4

B4

VCCP_VCCP

B3

VCC1.8_LCCALVD

V30

W31

VCCP_DMI

T1

C304 1U/6.3V_4C304 1U/6.3V_4

T2

C110 1U/6.3V_4C110 1U/6.3V_4

T3

VCCP_VCCAPLL_DMI

P2

VCC1.8_DMIHMPLL

AA1

E2

+1.05V

5

R281 0_6R281 0_6

+1.05V

R298 0_4R298 0_4

R279 0_6R279 0_6

R280 0_4R280 0_4

C302

C302

1u/6.3V_4

1u/6.3V_4

6

<Layout note>

Close to pin

<20090526(A1A)_EDS Rev0.7>

D4 pin is VCCP, not VCC

+1.05V

+1.5V

R345 0.1uH/300mA_6R345 0.1uH/300mA_6

C335

C335

22U/6.3V_8

22U/6.3V_8

+1.05V

R282 *0_4R282 *0_4

+1.8V

C305

C305

*1u/6.3V_4

*1u/6.3V_4

6

+1.8V

C334

C334

1u/6.3V_4

1u/6.3V_4

+1.05V

7

8

06

VCC_CORE

R212

R212

100/F_4

100/F_4

VCCSENSE (29)

VSSSENSE (29)

R213

R213

100/F_4

100/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

7

PROJECT :

Pineview Power

Pineview Power

Pineview Power

ZGA

ZGA

ZGA

387

387

8

387

1B

1B

1B

Page 8

1

PINEVIEW_M

PINEVIEW_M

U21F

U21F

REV = 1.1

A11

A16

A19

A29

A3

A30

A4

AA13

AA14

AA16

AA18

AA2

AA22

AA25

AA26

AA29

AA8

AB19

AB21

AB28

AB29

AB30

AC10

AC11

AC19

AC2

AC21

AC28

AC30

AD26

AD5

AE1

AE11

AE13

AE15

AE17

AE22

AE31

AF11

AF17

AF21

AF24

AF28

AG10

AG3

AH18

AH23

AH28

AH4

A A

AH6

AH8

AJ1

AJ16

AJ31

AK1

AK2

AK23

AK30

AK31

AL13

AL19

AL2

AL23

AL29

AL3

AL30

AL9

B13

B16

B19

B22

B30

B31

C12

C21

C22

C25

C31

D22

E10

E19

E21

E25

F17

F19

B5

B9

C1

E1

E8

REV = 1.1

VSS

VSS

VSS

RSVD_NCTF

RSVD_NCTF

RSVD_NCTF

RSVD_NCTF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD_NCTF

VSS

VSS

RSVD_NCTF

RSVD_NCTF

VSS

RSVD_NCTF

RSVD_NCTF

VSS

VSS

RSVD_NCTF

VSS

RSVD_NCTF

RSVD_NCTF

RSVD_NCTF

VSS

VSS

VSS

VSS

VSS

RSVD_NCTF

RSVD_NCTF

VSS

VSS

RSVD_NCTF

VSS

VSS

VSS

VSS

RSVD_NCTF

VSS

RSVD_NCTF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Pineview-M 1.66G

Pineview-M 1.66G

GND

GND

6 OF 6

6 OF 6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F24

F28

F4

G15

G17

G22

G27

G31

H11

H15

H2

H21

H25

H8

J11

J13

J15

J4

K11

K13

K19

K26

K27

K28

K30

K4

K8

L1

L13

L18

L22

L24

L25

L29

M28

M3

N1

N13

N18

N24

N25

N28

N4

N5

N8

P13

P14

P16

P18

P19

P21

P3

P4

R25

R7

R8

T11

U22

U23

U24

U27

V14

V16

V18

V28

V29

W13

W2

W23

W25

W26

W28

W30

W4

W5

W6

W7

Y28

Y3

Y4

T29

07

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

1

Wednesday, July 07, 2010

PROJECT :

Pineview GND

Pineview GND

Pineview GND

ZGA

ZGA

ZGA

1B

1B

1B

388

388

388

Page 9

1

08

TGP

U20B

U20B

DMI_RXN0(5)

DMI_RXP0(5)

DMI_TXN0(5)

DMI_TXP0(5)

DMI_RXN1(5)

DMI_RXP1(5)

DMI_TXN1(5)

DMI_TXP1(5)

3/11 : cancel Lan function

LAN

PE2RX-(21)

WLAN

A A

Decoder

3G

PE2RX+(21)

PE2TX-(21)

PE2TX+(21)

PE3RX-(26)

PE3RX+(26)

PE3TX-(26)

PE3TX+(26)

PE4RX-(21)

PE4RX+(21)

PE4TX-(21)

PE4TX+(21)

C167 0.1U/10V_4C167 0.1U/10V_4

C173 0.1U/10V_4C173 0.1U/10V_4

C190 0.1U/10V_4C190 0.1U/10V_4

C179 0.1U/10V_4C179 0.1U/10V_4

C137 0.1U/10V_4C137 0.1U/10V_4

C131 0.1U/10V_4C131 0.1U/10V_4

C148 0.1U/10V_4C148 0.1U/10V_4

C142 0.1U/10V_4C142 0.1U/10V_4

C159 0.1U/10V_4C159 0.1U/10V_4

C156 0.1U/10V_4C156 0.1U/10V_4

DMI_TXN0_C

DMI_TXP0_C

DMI_TXN1_C

DMI_TXP1_C

T65T65

T66T66

T67T67 R294 *0_4R294 *0_4

T68T68 R284 1K/F_4R284 1K/F_4

PCIE_TXN2_C

PCIE_TXP2_C

PCIE_TXN3_C

PCIE_TXP3_C

PCIE_TXN4_C

PCIE_TXP4_C

R23

R24

P21

P20

T21

T20

T24

T25

T19

T18

U23

U24

V21

V20

V24

V23

K21

K22

J23

J24

M18

M19

K24

K25

L23

L24

L22

M21

P17

P18

N25

N24

DMI0RXN

DMI0RXP

DMI0TXN

DMI0TXP

DMI1RXN

DMI1RXP

DMI1TXN

DMI1TXP

DMI2RXN

DMI2RXP

DMI2TXN

DMI2TXP

DMI3RXN

DMI3RXP

DMI3TXN

DMI3TXP

PERN1

PERP1

PETN1

PETP1

PERN2

PERP2

PETN2

PETP2

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

TGP

H7

USBP0N

H6

USBP0P

H3

USBP1N

H2

USBP1P

J2

USBP2N

J3

DMI

DMI

USB

USB

PCI-E

PCI-E

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

OC0#

OC1#

OC2#

OC3#

OC4#

OC5#/GPIO29

OC6#/GPIO30

OC7#/GPIO31

USBRBIAS

USBRBIAS#

CLK48

K6

K5

K1

K2

L2

L3

M6

M5

N1

N2

USBOC#

D4

USBOC#

C5

USBOC#

D3

USBOC#L1

D2

USBOC#

E5

USBOC#

E6

USBOC#R1

C2

USBOC#

C3

G2

G3

CLKUSB_48

F4

USBRBIAS

USBP0- (18)

USBP0+ (18)

USBP1- (21)

USBP1+ (21)

USBP2- (15)

USBP2+ (15)

USBP3- (18)

USBP3+ (18)

USBP4- (22)

USBP4+ (22)

USBP5- (21)

USBP5+ (21)

USBP6- (16)

USBP6+ (16)

USBP7- (21)

USBP7+ (21)

R285 *0_4R285 *0_4

<Layout note>

Close to pin within 200mil ; keep away from CLK/High speed signals

R302 22.6/F_4R302 22.6/F_4

CLKUSB_48 (2)

SYSTEM (Right down)

SIM

CCD

System (Left)

Card reader

3G

BT

WLAN

USBOC#L (18,23)

USBOC#R (18,23)

USBOC#R1

USBOC#L1

USBOC#

12/21: CRB ties some unused OC pins together with 1k

R290 8.2K_4R290 8.2K_4

+3V_S5

R291 8.2K_4R291 8.2K_4

+1.5V

<Layout note>

Close to pin within 500mil

R153 24.9/F_4R153 24.9/F_4

CLK_PCIE_ICH#(2)

CLK_PCIE_ICH(2)

DMI_COMP

H24

J22

W23

W24

DMI_ZCOMP

DMI_IRCOMP

DMI_CLKN

DMI_CLKP

Tiger Point

Tiger Point

EMI

CLKUSB_48

R297

R297

*10/F_4

2

2

1

*10/F_4

C311

C311

*10P/50V_4

*10P/50V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

PROJECT :

Tiger Point DMI/PCIE/USB

Tiger Point DMI/PCIE/USB

Tiger Point DMI/PCIE/USB

ZGA

ZGA

ZGA

389

389

389

1B

1B

1B

Page 10

5

4

3

2

1

09

TGP

U20C

U20C

TGP

INIT#

INTR

NMI

SMI#

AE6

AD6

AC7

AD7

AE8

AD8

AD9

AC9

AD4

AC4

AD11

AC11

AD25

U16

Y20

Y21

Y18

AD21

AC25

AB24

Y22

T17

AC21

AA16

AA21

V18

AA20

SATARBIAS#

GA20

KBRST#

SATA_RXN0 (20)

SATA_RXP0 (20)

SATA_TXN0 (20)

SATA_TXP0 (20)

CLK_PCIE_SATA# (2)

CLK_PCIE_SATA (2)

SATALED#

R334 10K/J_4R334 10K/J_4

GA20 (23)

H_A20M# (5)

H_IGNNE# (5)

H_INIT# (5)

H_INTR (5)

H_NMI (5)

KBRST# (23)

SERIRQ (23,26)

H_SMI# (5)

H_STPCLK# (5)

SATA SSD

<Layout note>

Close to pin within 500mil

R327 24.9/F_4R327 24.9/F_4

T69T69

+3V

+1.05V

R186

R186

56/J_4

56/J_4

<20090514(A1A)_Checklist Rev0.7>

SERIRQ:8.2K pull-up

A20GATE:10K pull-up

SERIRQ

GA20

KBRST#

PCH_GPIO36

<Layout note>

Close to pin within 200mil

<Layout note>

Close to pin

+1.05V

H_FERR# (5)

R187

R187

56/J_4

56/J_4

R332 8.2K_4R332 8.2K_4

R204 10K_4R204 10K_4

R200 10K/J_4R200 10K/J_4

R197 10K/J_4R197 10K/J_4

<20100105(A1A)>

SY3 GA20: 8.2K pull-up

<Layout note>

Close to pin within 1"

PM_THRMTRIP# (5)

+3V

D D

C C

B B

PCH_GPIO36

R12

AE20

AD17

AC15

AD18

Y12

AA10

AA12

Y10

AD15

W10

V12

AE21

AE18

AD19

U12

AC17

AB13

AC13

AB15

Y14

AB16

AE24

AE23

AA14

V14

AD16

AB11

AB10

AD23

RSVD03

RSVD04

RSVD05

RSVD06

RSVD07

RSVD08

RSVD09

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

GPIO36

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA

SATA

SATA_CLKN

SATA_CLKP

SATARBIAS#

SATARBIAS

SATALED#

A20GATE

A20M#

CPUSLP#

IGNNE#

INIT3_3V#

HOST

HOST

FERR#

RCIN#

SERIRQ

STPCLK#

THERMTRIP#

3

3

Tiger Point

Tiger Point

NOTE

:

1. CPUSLP# is supported only on nettop platforms.

A A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

Wednesday, July 07, 2010

Wednesday, July 07, 2010

Wednesday, July 07, 2010

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Tiger Point Sata/Host

Tiger Point Sata/Host

Tiger Point Sata/Host

ZGA

ZGA

ZGA

1B

1B

1B

3810

3810

1

3810

Page 11

5

PCI_DEVSEL#

PCLK_ICH(2)

PCI_IRDY#

D D

<20090601(A1A)_Checklist Rev0.7>

Strap1#/strap2#: signals have weak

internal pull-ups

C C

EC_SCI#(23)

+3V

B B

EC_SCI#

PCI_INTH#(26)

T30T30

R132 10K/J_4R132 10K/J_4

R139 8.2K/J_4R139 8.2K/J_4

PCI_SERR#

PCI_STOP#

PCI_LOCK#

PCI_TRDY#

PCI_PERR#

PCI_FRAME#

PCI_REQ1#

PCI_REQ2#

PCH_GPIO48

PCH_GPIO17

PCH_GPIO22

PCI_INTA#

PCI_INTB#

PCI_INTC#

PCI_INTD#

PCI_INTE#

PCI_INTF#

PCI_INTG#

PCI_INTH#

PCH_A16WP

ICH Boot BIOS select

PCH_GPIO17

(INT PU)

0 1 SPI

1 0 PCI

1 1 LPC

R138*1K_4 R138*1K_4

R2781K_4 R2781K_4

PCH_GPIO48

(INT PU)

PCH_GPIO48

PCH_GPIO17

T29T29

T15T15

4

A5

B15

J12

A23

B7

C22

B11

F14

A8

A10

D10

A16

A18

E16

G16

A20

G14

A2

C15

C9

B2

D7

B3

H10

E8

D6

H8

F8

D11

K9

M13

Boot BIOS Location

(Default)

R137*1K_4 R137*1K_4

R266*1K_4 R266*1K_4

U20A

U20A

PAR

DEVSEL#

PCICLK

PCIRST#

IRDY#

PME#

SERR#

STOP#

PLOCK#

TRDY#

PERR#

FRAME#

GNT1#

GNT2#

REQ1#

REQ2#

GPIO48/ STRAP1#

GPIO17/ STRAP2#

GPIO22

GPIO1

PIRQA#

PIRQB#

PIRQC#

PIRQD#

PIRQE#/GPIO2

PIRQF#/GPIO3

PIRQG#/GPIO4

PIRQH#/GPIO5

STRAP0#

RSVD01

RSVD02

Tiger Point

Tiger Point

PCI

PCI

TGP

TGP

+3V

3

C/BE0#

C/BE1#

C/BE2#

C/BE3#

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

1

1

B22

D18

C17

C18

B17

C19

B18

B19

D16

D15

A13

E14

H14

L14

J14

E10

C11

E12

B9

B13

L12

B8

A3

B5

A6

G12

H12

C8

D9

C7

C1

B1

H16

M15

C13

L16

2

PCI_INTA#

PCI_INTC#

PCI_INTF#

PCI_INTB#

PCI_IRDY#

PCI_LOCK#

PCI_PERR#

PCI_TRDY#

PCI_DEVSEL#

PCI_FRAME#

PCI_REQ1#

PCI_REQ2#

PCI_STOP#

PCI_SERR#

EC_SCI#

PCI_INTD#

PCI_INTH#

PCI_INTG#

PCI_INTE#

PCH_GPIO22

IRQ

PIRQA

PIRQB

PIRQC

PIRQD

PIRQE

PIRQF

PIRQG

PIRQH

PCI_GNT#2 Internal PU

RP2 8.2K_8P4RRP2 8.2K_8P4R

RP4 8.2K_8P4RRP4 8.2K_8P4R

1

3

5

7

RP3 8.2K_8P4RRP3 8.2K_8P4R

1

3

5

7

1

3

5

7

R268 8.2K/J_4R268 8.2K/J_4

R267 8.2K/J_4R267 8.2K/J_4T16T16

R140 10K_4R140 10K_4

RP1 8.2K_8P4RRP1 8.2K_8P4R

1

3

5

7

USB UHCI Controller #1, #4

AC'97 Codec; option for SMBUS

USB UH Controller #3; SATA/IDE Native Mode

USB UHCI Controller #2

Internal LAN; Option for SCI, TCO, HPET#0,1,2

Option for SCI, TCO, HPET#0,1,2

Option for SCI, TCO, HPET#0,1,2

USB EHCI Controller; Option for SCI, TCO, HPET#0,1,2

Should not be PD

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

R2698.2K_4 R2698.2K_4

Description

+3V

+3V

+3V

+3V

+3V

+3V

1

10

A A

A16 SWAP Override strap

PCH_A16WP

(INT PU)

5

Low = A16 swap override enabled

High = Default

4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

3

Date: Sheet of

Wednesday, July 07, 2010

Wednesday, July 07, 2010

Wednesday, July 07, 2010

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

TigerPoint PCI(3/6)

TigerPoint PCI(3/6)

TigerPoint PCI(3/6)

ZGA

ZGA

ZGA

1

1B

1B

1B

3811

3811

3811

Page 12

5

EMI

14M_ICH

R320

R320

*33/J_4

*33/J_4

C323

C323

*10P/50V_4

D D

*10P/50V_4

debug port for google require

CN14

CN14

1

PCH_GPIO24

2

PCH_GPIO26

3

PCH_GPIO27

4

PCH_GPIO28

5

PCH_GPIO33

6

PCH_GPIO34

7

PCH_GPIO38

8

PCH_GPIO39

9

12

1011

*88513-104N

*88513-104N

+3V

C C

R151 10K_4R151 10K_4

R308 10K_4R308 10K_4

R312 10K_4R312 10K_4

place near to Tiger point.

SPI_CS#

SPI_MISO

SPI_MOSI_R

ACZ_BITCLK_AUDIO(17)

ACZ_RESET#_AUDIO(17)

ACZ_SDIN0(17)

ACZ_SDOUT_AUDIO(17)

ACZ_SYNC_AUDIO(17)

+3V

14M_ICH(2)

SPI FLASH(CLG)

U11

U11

2

SO

VDD

5

SI

HOLD

C331

C331

1u/10V_6

1u/10V_6

1 3

2

6

1

RTCRST#VCCRTC_3

WP

SCK

CE

VSS

MX25L1605DM2I-12G

MX25L1605DM2I-12G

At 11/24 add

Winbond W25X16AVSSIG AKE38ZP0N01

MXIC MX25L1605AM2C-15G AKE37FP0Z13

EON EN25F16-100HIP AKE38ZA0Q00

AMIC A25L016 AKE38ZN0800

G3

G3

12

*SHORT_PAD

*SHORT_PAD

R415 2K/F_4R415 2K/F_4

8

R120 3.3K_4R120 3.3K_4

7

MANU_SW_R1SPI_CLK

3

4

VCCRTC

SPI_MISO_RSPI_MISO

SPI_MOSI

SPI_CS#

C332

C332

1u/10V_6

1u/10V_6

R338

R338

20K/F_6

20K/F_6

R307 47/F_4R307 47/F_4

R152 10K_4R152 10K_4

+3V

1/13 Comfirm by vendor mail :

If the Southbridge enables 'Long Wait Abort' by

default, the flash device should be 50MHz (or faster)

RTC(RTC)

B B

D30

R348

R348

1K_4

1K_4

D30

CH500H-40

CH500H-40

D31

D31

CH500H-40

CH500H-40

+3VPCU

20MIL 20MIL

Q26

Q26

MMBT3904

MMBT3904

A A

CN22

CN22

RTC_CONN

RTC_CONN

1 2

5

4

LPCFRAME#(21,23,26)

R160 33/J_4R160 33/J_4

R161 33/J_4R161 33/J_4

R185 33/J_4R185 33/J_4

R175 33/J_4R175 33/J_4

<20090529(A1A)_Checklist Rev0.7>

If integrated LAN is not used

LAN_RST# tie it to GND.

C318 15P/50V_4C318 15P/50V_4

21

Y3

Y3

32.768K/10PPM

32.768K/10PPM

C320 15P/50V_4C320 15P/50V_4

PCLK_SMB(2,21)

PDAT_SMB(2,21)

SPI_MOSI

SPI_CLK

C96

C96

.1u/10V_4

.1u/10V_4

MANU_SW_R1

4

R310 47/F_4R310 47/F_4

R305 47/F_4R305 47/F_4

R422 2K/F_4R422 2K/F_4

1.Level 1 Environment-related Substances Should NEVER be Used.

2.Purchase ink, paint, wire rods, and Molding resins only from the business Partners that Sony approves as Green Partners.

+3V

VCCRTC_2VCCRTC_1VCCRTC_4

LPCAD0(21,23,26)

LPCAD1(21,23,26)

LPCAD2(21,23,26)

LPCAD3(21,23,26)

+3V

R438

R438

100K/F_4

100K/F_4

D26 BAS316D26 BAS316

T24T24

T25T25

ACZ_BITCLK_R

ACZ_RST#_R

ACZ_SDOUT_R

ACZ_SYNC_R

14M_ICH

R319

R319

10M/J_4

10M/J_4

RTC_X1

RTC_X2

RTCRST#

SMBALERT#

PCLK_SMB

PDAT_SMB

SMB_LINK_ALERT#

SMLINK0

SMLINK1

SPI_MISO

SPI_MOSI_R

SPI_CS#

SPI_CLK_R

T22T22

PLT_RST#

68.1K/F_4

68.1K/F_4

150K/F_4

150K/F_4

U20D

U20D

AA5

LDRQ1#/GPIO23

V6

LAD0/FW H0

AA6

LAD1/FW H1

Y5

LAD2/FW H2

W8

LAD3/FW H3

Y8

LDRQ0#

Y4

LFRAME#

P6

HDA_BIT_CLK

U2

HDA_RST#

W2

HDA_SDI0

V2

HDA_SDIN1

P8

HDA_SDIN2

AA1

HDA_SDOUT

Y1

HDA_SYNC

AA3

CLK14

U3

EE_CS

AE2

EE_DIN

T6

EE_DOUT

V3

EE_SHCLK

T4

LAN_CLK

P7

LANR_STSYNC

B23

LAN_RST#

AA2

LAN_RXD0

AD1

LAN_RXD1

AC2

LAN_RXD2

W3

LAN_TXD0

T7

LAN_TXD1

U4

LAN_TXD2

W4

RTCX1

V5

RTCX2

T5

RTCRST#

E20

SMBALERT#/GPIO11

H18

SMBCLK

E23

SMBDATA

H21

SMLALERT#

F25

SMLINK0

F24

SMLINK1

R2

SPI_MISO

T1

SPI_MOSI

M8

SPI_CS#

P9

SPI_CLK

R4

SPI_ARB

Tiger Point

Tiger Point

MANU_SW_R (23)

Platform Reset

+3V

C299 *0.1u/10V_4C299 *0.1u/10V_4

U19

U19

2

1

3 5

R283 *0/short_4R283 *0/short_4

+5V_S5

R421

R421

R414

R414

LPC AUDIO LAN

LPC AUDIO LAN

EPROM

EPROM

*TC7SH08FU

*TC7SH08FU

4

3

TGP

TGP

BM_BUSY#/GPIO0

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO12

GPIO13

GPIO14

GPIO15

DPRSLPVR

STP_PCI#

STP_CPU#

GPIO24

GPIO25

GPIO26

GPIO27

GPIO28

CLKRUN#

GPIO33

GPIO34

GPIO38

GPIO39

CPUPWRGD/GPIO49

THRM#

VRMPWRGD

MISC

MISC

RTC SMB SPI

RTC SMB SPI

R286

R286

100K_4

100K_4

3

MCH_SYNC#

PWRBTN#

SUSCLK

SYS_RESET#

PLTRSTB

WAKE#

INTRUDER#

PWROK

RSMRST#

INTVRMEN

SPKR

SLP_S3#

SLP_S4#

SLP_S5#

BATLOW #

DPRSTP#

DPSLP#

RSVD31

ACZ_SDOUT

(INT PD)

RI#

0

0

1

SUS_STAT#/LPCPD#

PLTRST# (5,21,23,25,26)

D23,D24 are just for preventing EC/SB F/W error

to cause to leakage current.If test OK,

they can be connected directly.

BM_BUSY#

T15

RECOVER_KEY#_R1

W16

DEVELOPER#_R1

W14

EC_SMI#

K18

LID#_ICH

H19

MANU

M17

MBID2

A24

MBID1

C23

MBID0

P5

HDMI_CON_HP_TP

E24

AB20

Y16

AB19

PCH_GPIO24

R3

DMI_AC_ENABLE

C24

PCH_GPIO26

D19

PCH_GPIO27

D20

PCH_GPIO28

F22

CLKRUN#

AC19

PCH_GPIO33

U14

PCH_GPIO34

AC1

PCH_GPIO38

AC23

PCH_GPIO39

AC24

AB22

AB17

V16

MCH_SYNC#

AC18

DNBSWON#

E21

ICH_RI#

H23

G22

SUSCLK

D22

SYS_RST#

G18

PLT_RST#

G23

PCIE_WAKE#

C25

SM_INTRUDER#

T8

TPT_PWROK

U10

EC_RSMRST#

AC3

ICH_INTVRMEN

AD3

J16

H20

E25

F21

B25

AB23

AA18

F20

T17T17

PM_BATLOW#

<20090721(B2A)>

Stuff U19 and C275 and un-stuff R205 for power sequence

ACZ_SYNC

(INT PD)

0

0

1

1 1 x 4s(1 port/4 lanes)

2

D24 BAS316D24 BAS316

D23 BAS316D23 BAS316

D21 BAS316D21 BAS316

R1180_4 R1180_4

HDMI_CON_HP_TP (25)

PM_DPRSLPVR (5,29)

PM_STPPCI# (2)

PM_STPCPU# (2)

1C: Intel suggestion enable AC mode

CLKRUN# (23,26)

H_PWRGD (5)

THERM_ALERT# (5)

VR_PWRGD_CK410 (2)

DNBSWON# (23)

T31T31

SUSCLK (23)

PCIE_WAKE# (21)

EC_RSMRST# (23)

SB_BEEP (17)

SUSB# (23)

SUSC# (23)

ICH_DPRSTP# (5,29)

H_DPSLP# (5)

R328 332K/F_4R328 332K/F_4

TPT Power OK

U14

U14

HWPG(23)

IMVP_PWRGD(5,29)

ECPWROK(23)

Description

4 x 1s

*

Reserved1

Reserved

2

2

1

R205 *0_4R205 *0_4

MBID2

MBID1

MBID0

1

R130 2.2K_4R130 2.2K_4

R127 2.2K_4R127 2.2K_4

R273 8.2K_4R273 8.2K_4

R188 10K/J_4R188 10K/J_4

R117 *10K_4R117 *10K_4

R150 8.2K_4R150 8.2K_4

R154 10K_4R154 10K_4

R115 10K_4R115 10K_4

R129 10K_4R129 10K_4

R128 10K_4R128 10K_4

R274 10K_4R274 10K_4

R276 8.2K_4R276 8.2K_4

R277 8.2K_4R277 8.2K_4

R272 *8.2K_4R272 *8.2K_4

R116 10K_4R116 10K_4

R182 1K/F_4R182 1K/F_4

R183 8.2K_4R183 8.2K_4

R331 1K/F_4R331 1K/F_4

R333 8.2K_4R333 8.2K_4

R195 10K_4R195 10K_4

R275 1K_4R275 1K_4

R172 10K_4R172 10K_4

R190 10K_4R190 10K_4

+3V_S5

R261

R261

R271

R271

10K_4

10K_4

10K_4

10K_4

R262

R262

R270

R270

*10K_4

*10K_4

*10K_4

*10K_4

RECOVER_KEY#_R (23)

DEVELOPER#_R (23)

EC_SMI# (23)

LID# (15,23)

MANU_SW_TPT (23)

VCCRTC

R164 1M/F_6R164 1M/F_6

+3V

C209 0.1u/10V_4C209 0.1u/10V_4

TC7SH08FU

TC7SH08FU

4

3 5

<20090515(A1A)_Checklist Rev0.7>

BATLOW#:8.2K pull-up to V3ALWAYS

WAKE#:10K pull-up to VccSus3_3

SYS_RST#:10K pull-up to VccSus3_3

PCLK_SMB

PDAT_SMB

PM_BATLOW#

THERM_ALERT#

DNBSWON#

LID#_ICH

EC_SMI#

SYS_RST#

SMBALERT#

SMB_LINK_ALERT#

PCIE_WAKE#

SMLINK1

SMLINK0

HDMI_CON_HP_TP

ICH_RI#

RECOVER_KEY#_R1

DEVELOPER#_R1

MCH_SYNC#

CLKRUN#

BM_BUSY#

DMI_AC_ENABLE

TPT_PWROK

EC_RSMRST#

TPT_PWROK

INTVRMEN

Enable internal VccSus1_5 VRM

1

(default)

Disable

0

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

Date: Sheet of

Wednesday, July 07, 2010

PROJECT :

TigerPoint GPIO

TigerPoint GPIO

TigerPoint GPIO

ZGA

ZGA

ZGA

1

11

+3V_S5

+3V

R304

R304

10K_4

10K_4

R306

R306

*10K_4

*10K_4

3812

3812

3812

1A

1A

1A

Page 13

1

<Layout note>

Place 0402 caps close to ball

Place 0603/0805 caps close to ICH

12

D20 1SS355D20 1SS355

VCC5_VCC5REF

TGP

U20E

U20E

A A

TGP

VCCRTC

F12

F5

Y6

AE3

Y25

F6

W18

AA8

M9

M20

N22

J10

K17

P15

V10

H25

AD13

F10

G10

R10

T9

VCCP_VCC1_05

VCC1.5_VCC1.5

VCCP_VCC1_05

VCC3_VCC3

6mA

VCC5REF

10mA

VCC5REF_SUS

45mA

VCCSATAPLL

6uA

24mA

VCCDMIPLL

10mA

VCCUSBPLL

14mA