QUANTA ZAK, ZAN, ZAP, ZAQ Schematics

5

4

3

2

1

Octopus_A_Yorp_DVT

SCH: 650-01771-03-SCH

ASSY:650-01771-03

PCB: 651-01771-03

D D

TABLE OF CONTENTS TABLE OF CONTENTS

SHEET NO. S

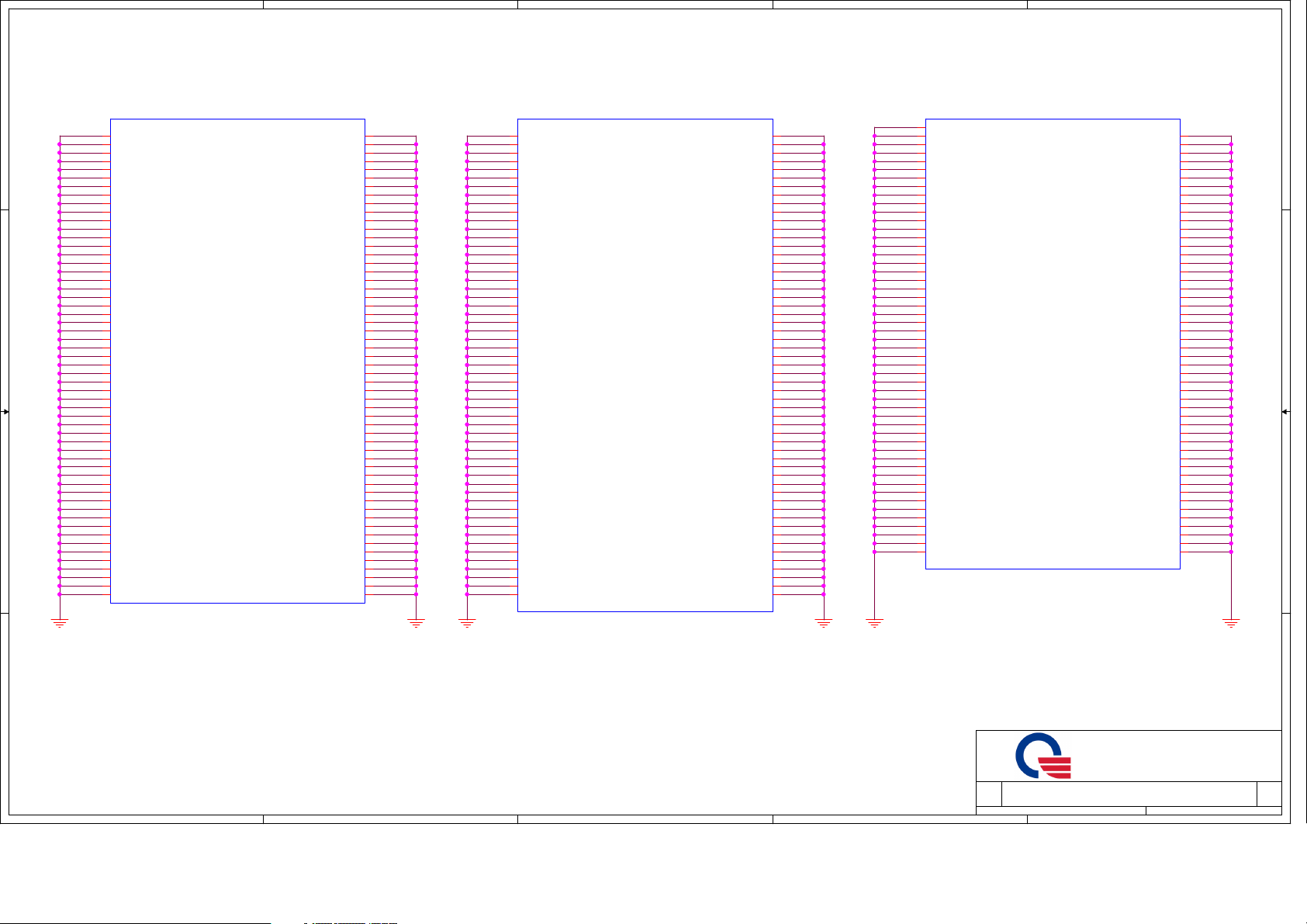

1

2

3

4

5

6

7

C C

8

9

10

11

12

13

14

15

16

B B

17

18

19

20

21

22

23

24

25

26

A A

27

28

29

30

5

TABLE OF CONTENTS

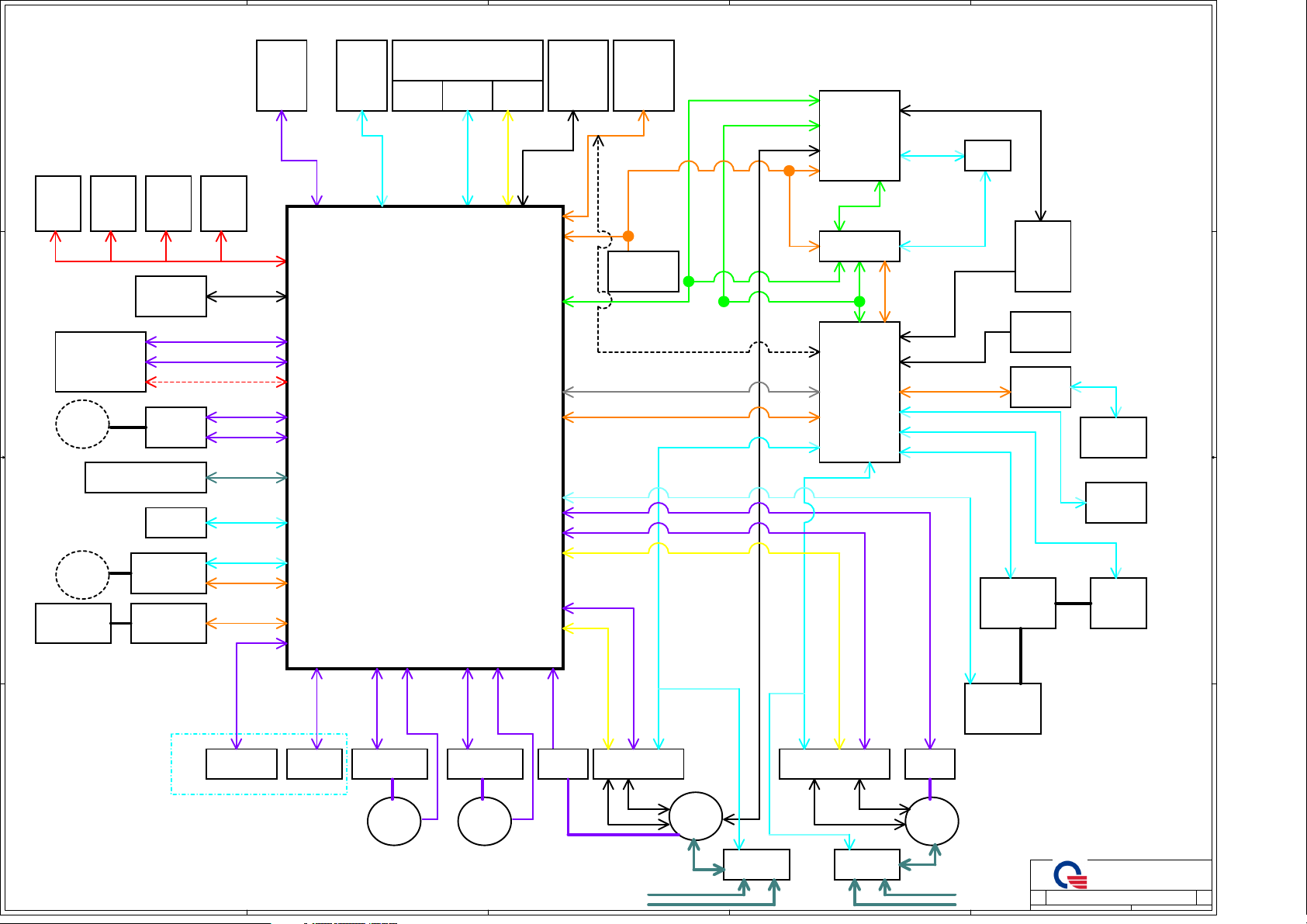

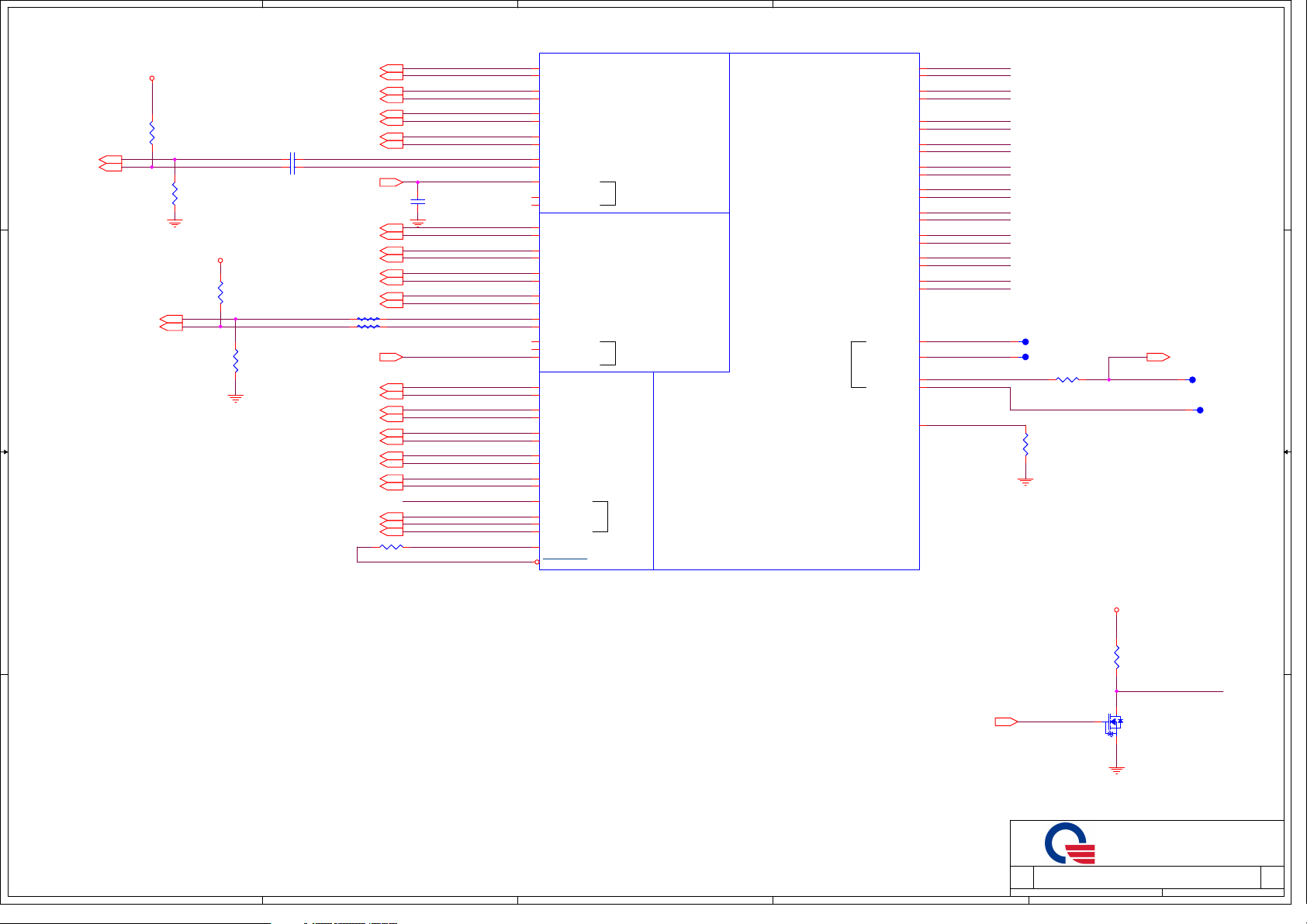

SYSTEM BLOCK DIAGRAM

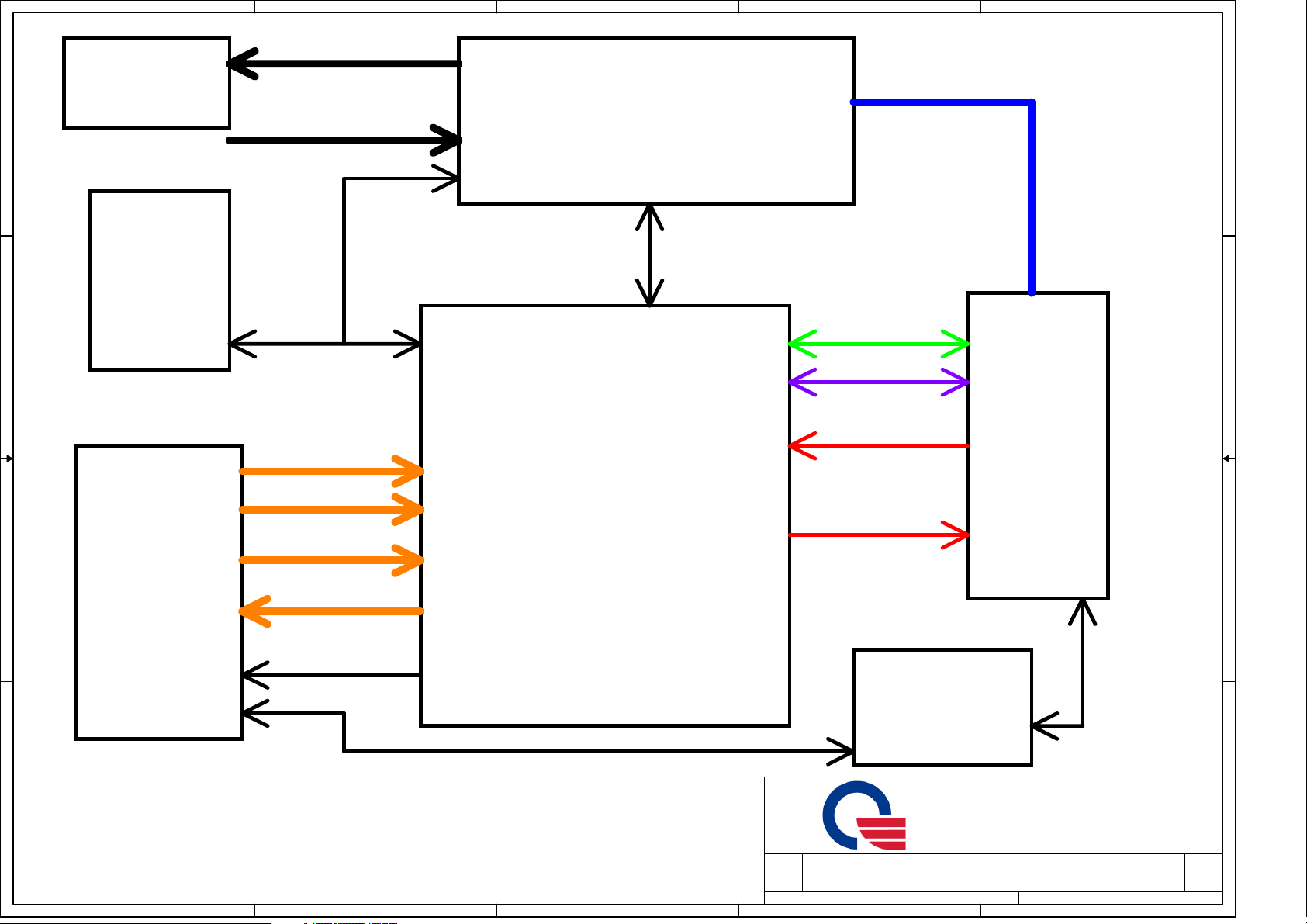

USB TYPE-C BLOCK DIAGRAM

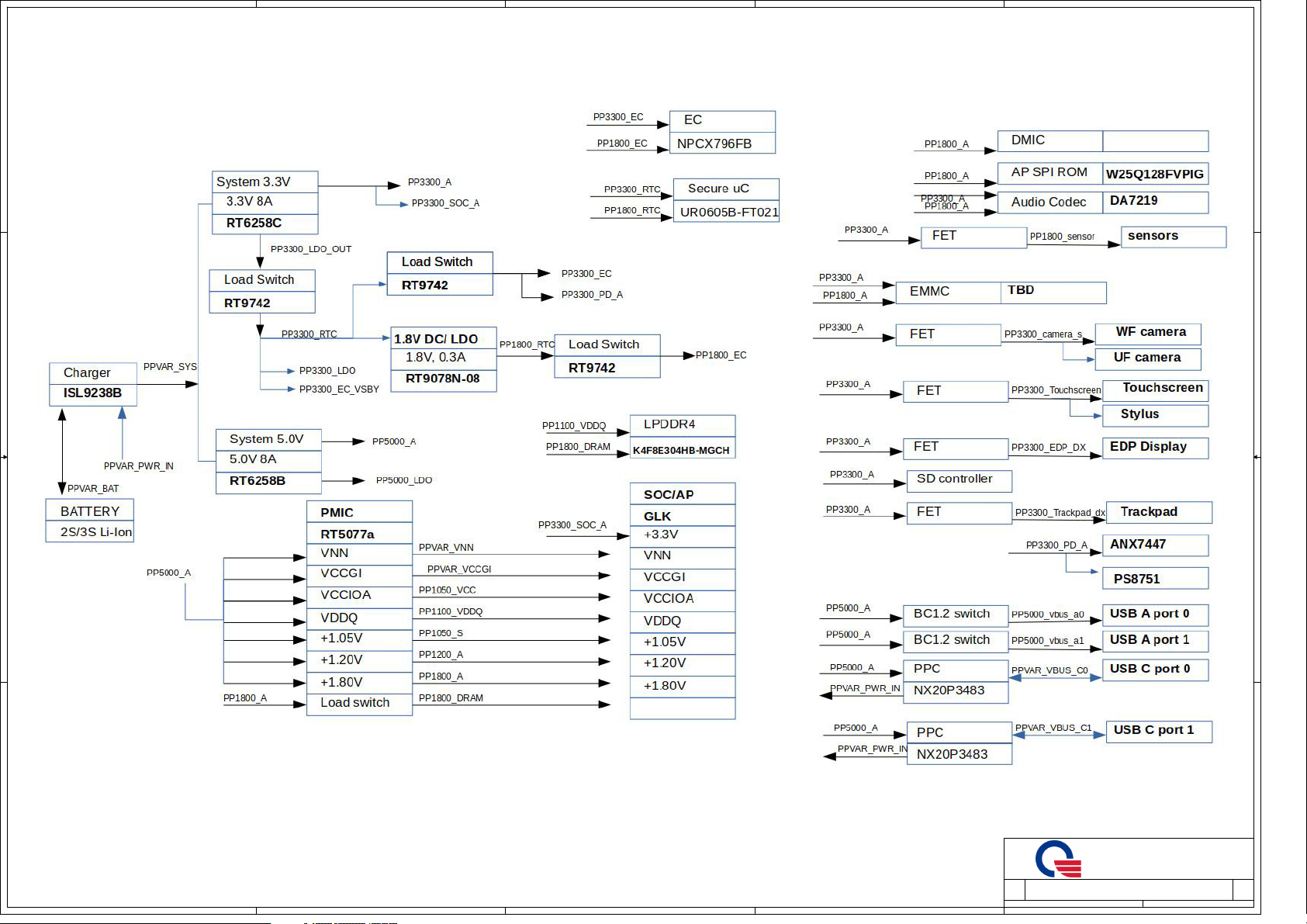

POWER TREE

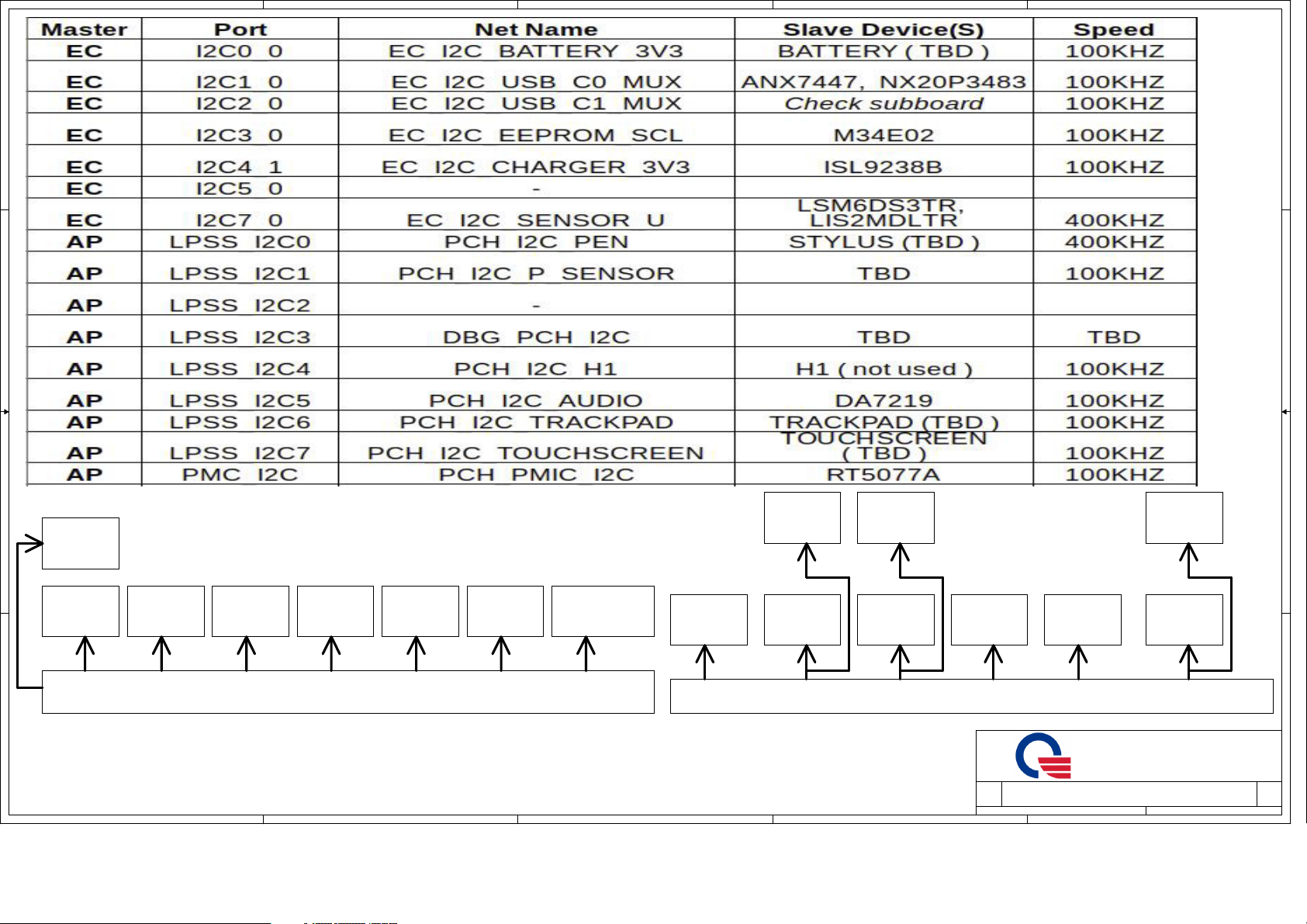

I2C MAP

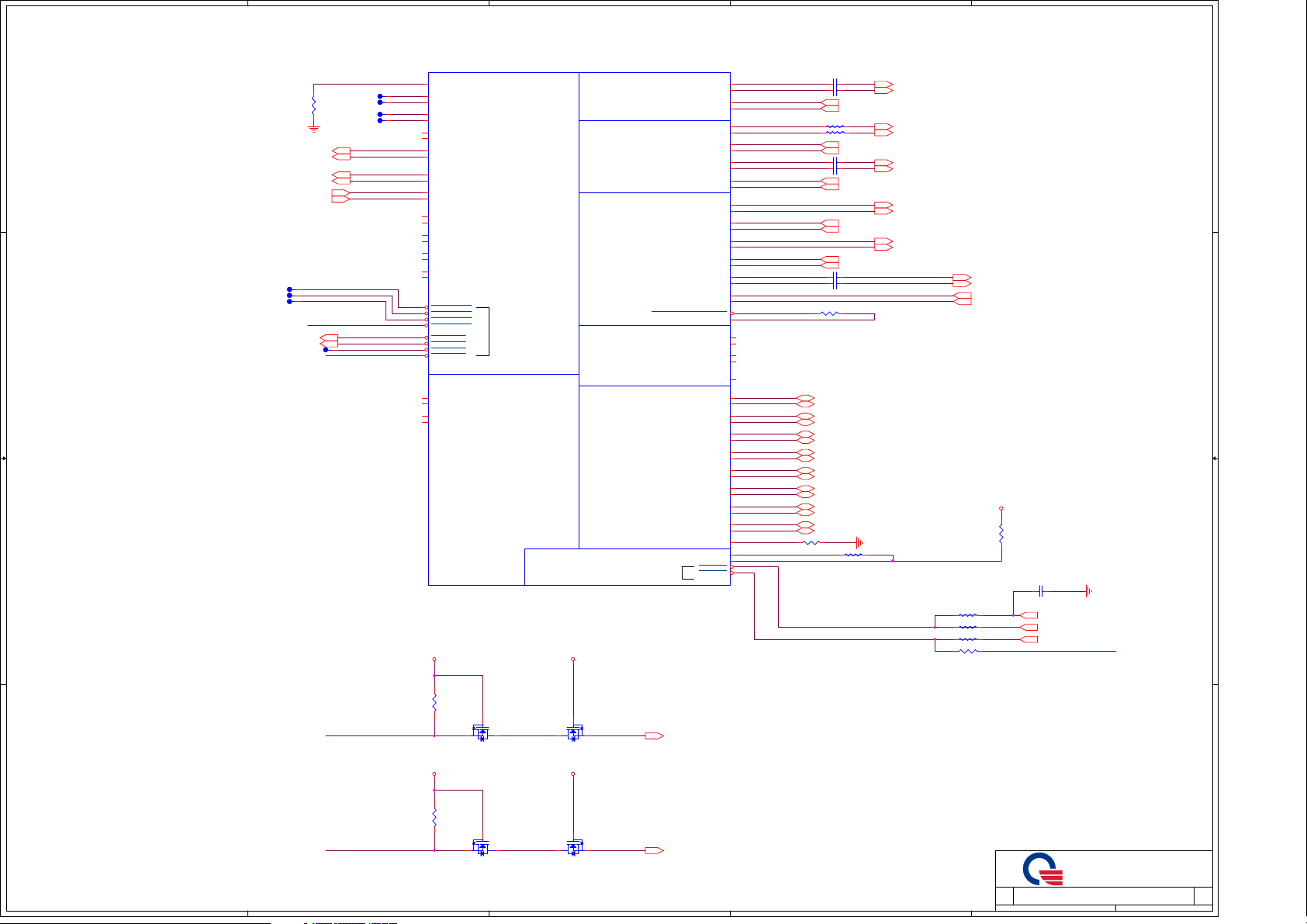

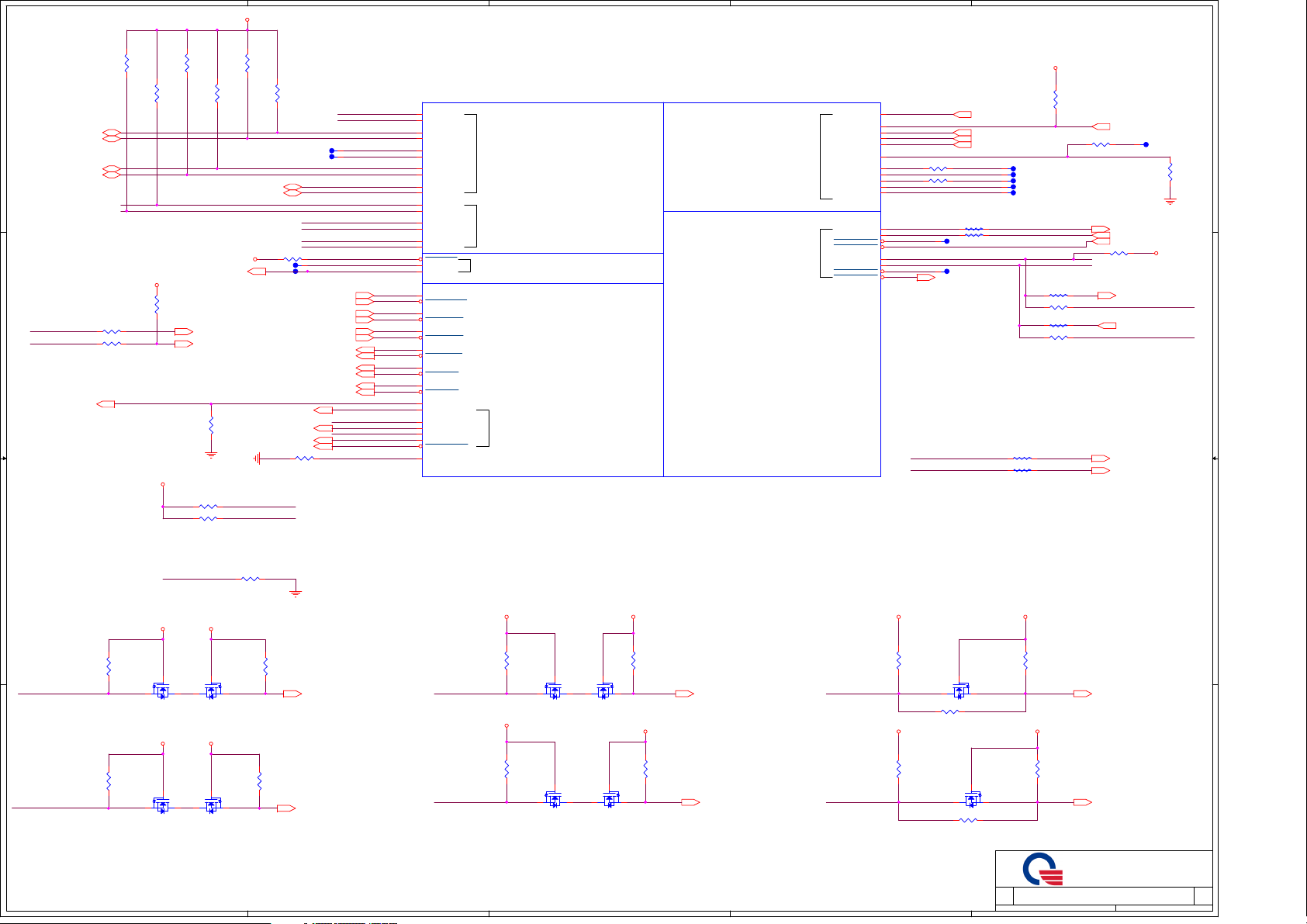

SOC DRAM I/F

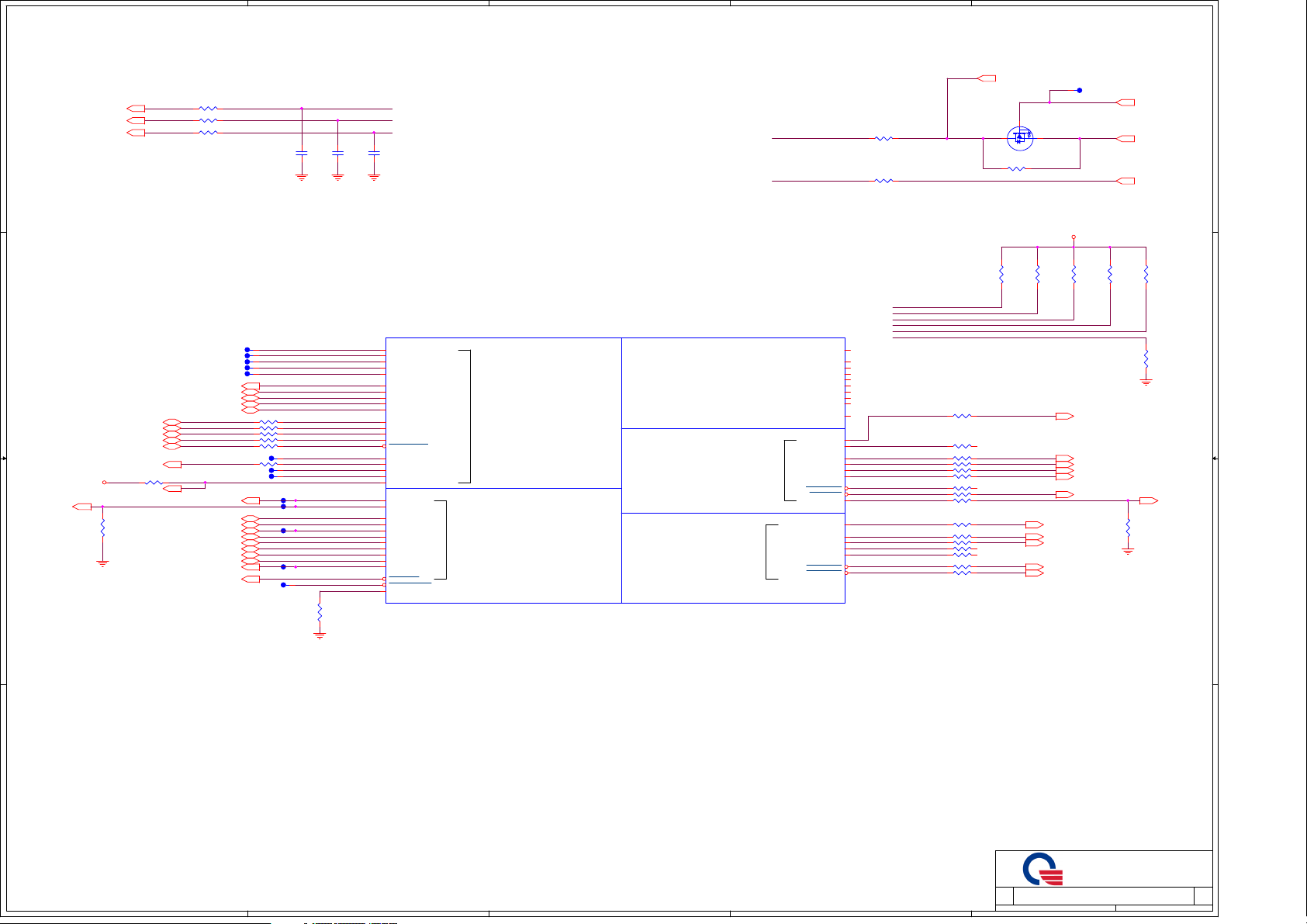

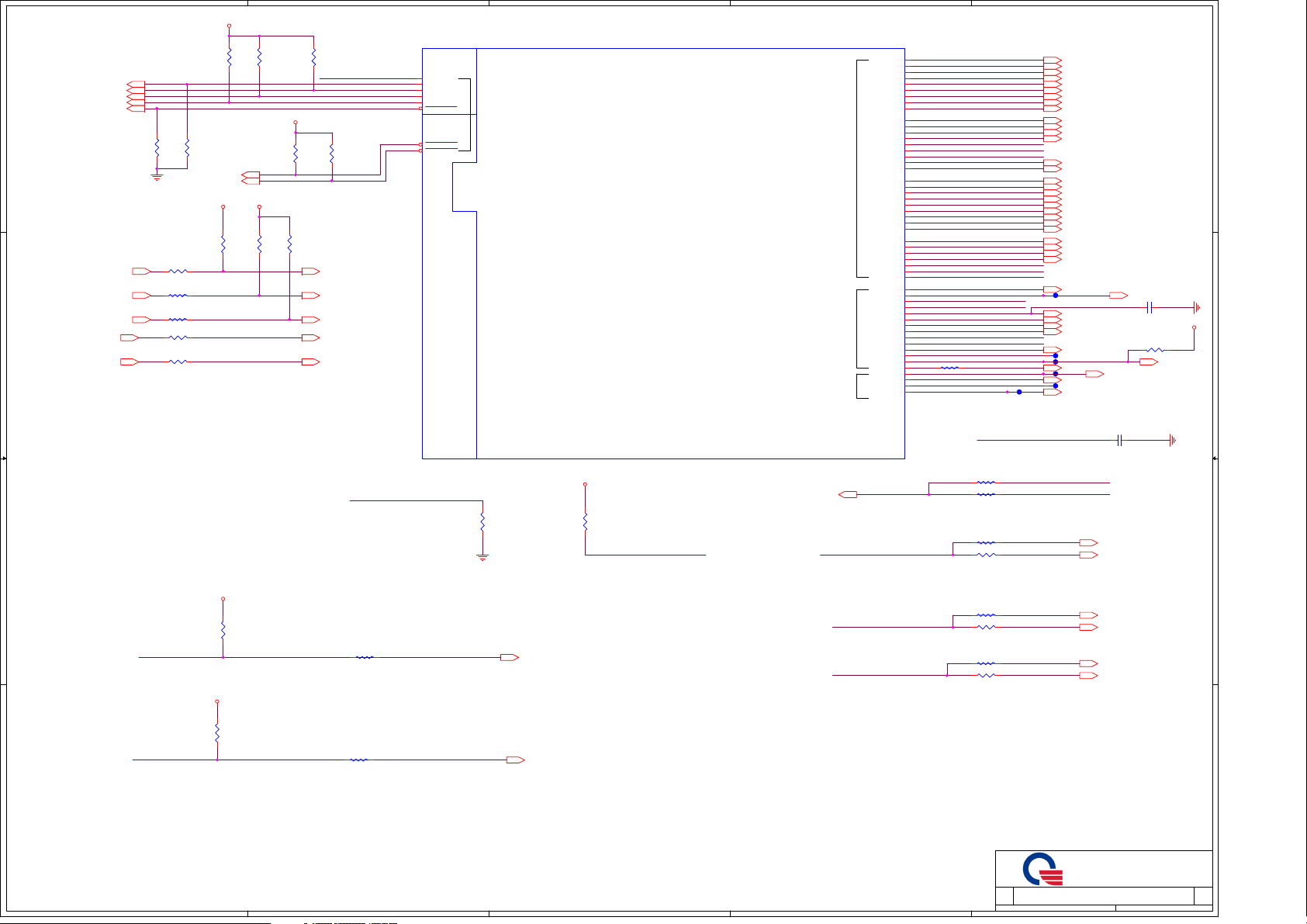

SOC EDP/MIPI/DDI

SOC PCIE/USB/SATA

SOC AUDIO/EMMC/LPC/SPI

SOC I2C/CNVI/UART/SPI

SOC PMU/RTC/SVID/THERMAL/MISC

SOC JTAG/GPIO/ITP

SOC GROUND

SOC POWER

SOC DECOUPLING

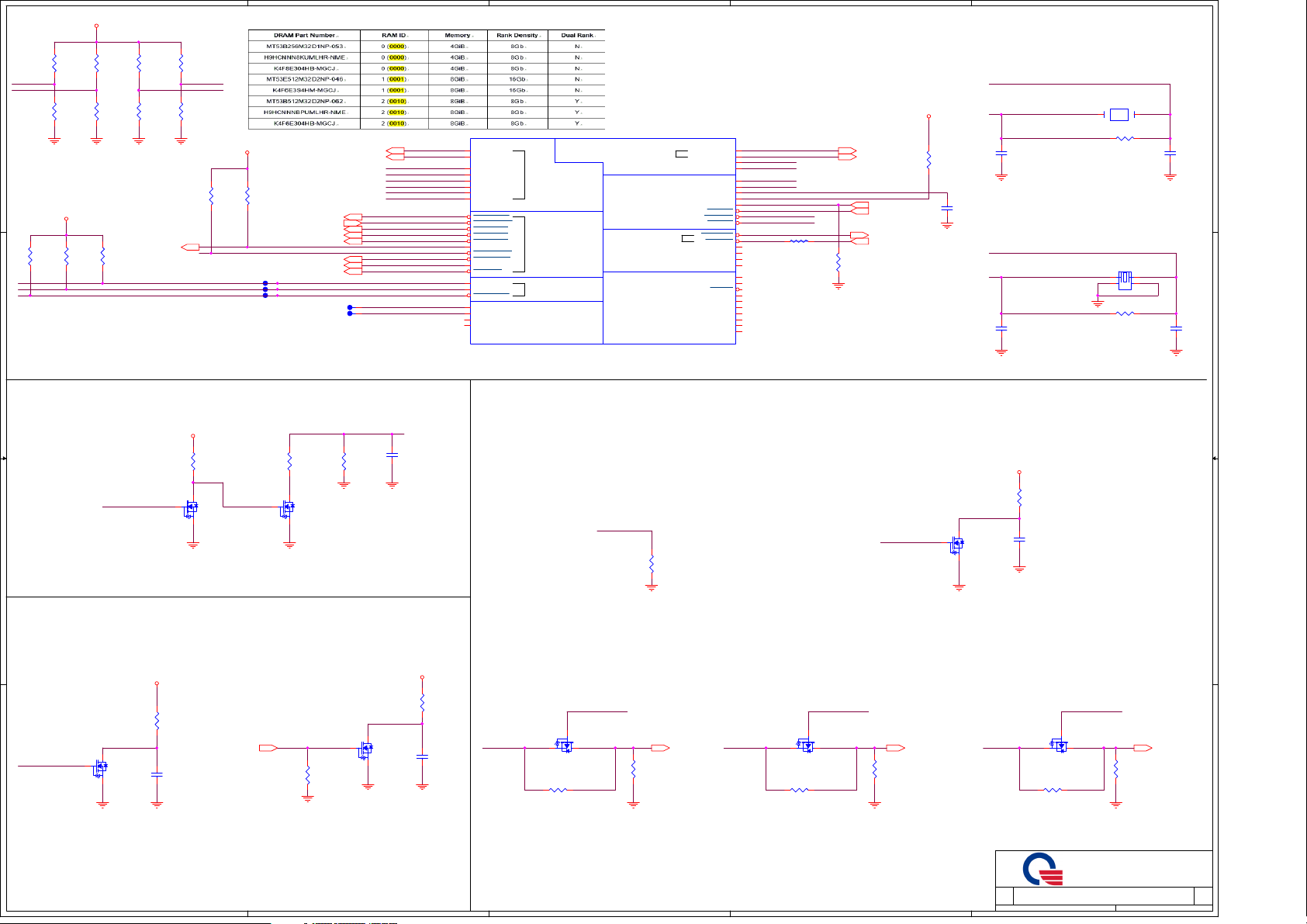

MEMORY CH 00/01 LPDDR4

MEMORY CH 10/11 LPDDR4

EC-NUVOTON

SPI ROM

MIPI60 DEBUG HEADER

H1 SECURE MICROCONTROLLER

SERVO

eMMC/SD

AUDIO

KB, TP, PEN

LID: eDP, CAM, TOUCH, SENSOR

SENSOR: COMPASS, GYRO

WIFI/BT CONNECTOR

USB C TCPC/MUX

USB A CONNECTIONS (MLB)

HEET NAME

4

SHEET NO. SHEET NAME

31

32

33

34

35

36

37

38

39

40

41

42

43

44

USB C CONNECTOR ( MLB )

USB C VBUS CONTROL

PMIC

POWER: 1.8V(EC) 3.3V AND 5V

POWER - LOAD SWITCHES

INAs

BATTERY CHARGER

LTE

CONNECTORS TO SUB BOARD

AR CONNECCTOR

BLANK

BLANK

MOV DIAGRAM

POWER SEQUENCE

SOC STRAPPING45

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

2

Wednesday, January 09, 2019

PROJECT :

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

1

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

1 45

1 45

1 45

1A

1A

1A

5

www.schematic-x.blogspot.com

4

3

2

1

Octopus(Gemini Lake)

Block Diagram ver.0.8

DRAM

EMMC

USB2.0

USB3.0

CAMERA

(B-Panel)

USB2.0

DRAM I/F

EMMC 5.1*

PCIe0

USB2-2

CNVi

USB2-5

USB3-5

Apr,24,2018

D D

MAX 8GB DDR4 OR LPDDR4

LPDDR4

x32

(2400)

2GB

C C

LPDDR4

x32

(2400)

2GB

WiFi-BT Module

(2x2 801.11AC)

PCIE M.2 1216

JFP2 CNVi

Micro-SD

LPDDR4

x32

(2400)

2GB

EMMC

1

6/32/64GB

PCIe Gen2 x1

USB2.0

CNVi

USB-to-SD

GL3213S

(104MB/s)

LPDDR4

x32

(2400)

2GB

Stylus

(EMR)

I2C

USB2-6 PDM

ISPLAY(EDP)11.6 " ?

D

1366x768 ?

Touch

Screen

GLK

DMIC

Dual?)

Backlight

EDP

BACKLIT CTL

I2C

EDP(2 Lnes)

(

UART-AP

UART-EC

SBU1,2

PDM

SPI-AP-SPI

UART

UART

USB

SPI

H1

rbox

I2C

I2C

INA

UART-H1

I2C-7 EDPI2C-0

/I2S

SPI

UART-0

I2S-0

eSPI

AP SPI ROM

(

I2S

SPI-AP-EC

BIOS) 16MB

I2S (WoV)

UART-AP

UART-EC

Servo Header

DMIC

EC(Nuvoton)

NPCX79_0BX

I2S

with option

of WoV

EC-SPI

I2C

SPI-Sensor

I2C-Sensor

I2C-Battery

I2C-Charger

Keyboard

GMR/Hall

Sensor

I

MU/Accel

(6-Axis)

I2C

E-Compass

(Optional)

MIPI160 Debug H eader

Track Pad

B B

Audio

Jack

Speakers x2

Audio Jack

Codec DA7219

Speaker Amp.

Max98357A x2

I2C

I2C

I2S

I2S

Debug

I2C-6

I2C-5

I2S-2

I2S-1

USB3-2

USB2-7

USB2-3

USB3-3

USB2-1

USB3-1

PMIC_I2C

USB2-4

USB3-4

DDI-1

USB3-0

DDI-0

USB2-0

I2C-PMIC

USB2.0

USB3.0

DP

USB3.0

DP

Charger

(

Buck-Boost)

ISL9238B

I2C-PMIC

Lid Accel

Li-lon

Battery

Pack

2S or 3S

45Whr+

PMIC

DP

USB2.0

C1.2

4

TYPE-A

USB3.0

USB2.0

USB3.0

BC1.2

SLGC55545VTR

TYPE-A

USB2.0

BC1.2

MAX14637

USB3.0

AR Camera-W

A A

5

optional

USB2.0

Camera-W

B

SLGC55545VTR

USB3.0

I2C

TCPC+Mux+VCONN

ANX7447

SS

CC/SBU

PPVAR_PWR_IN

PP5000_A

3

TYPE-C

Port0

SBU1,2

PPC

(NX20P3483)

TCPC+Mux+VCONN

PS8751BQFN52GTR -A3

I2C

DP

USB3.0

SS

CC/SBU

PPC

(NX20P3483)

2

USB2.0

BC1.2

M

AX14637

TYPE-C

Port1Port1 Port0

PPVAR_PWR_IN

PP5000_A

RT5077A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

SYSTEM BLOCK DIAGRAM

Wednesday, January 09, 2019

Wednesday, January 09, 2019

Wednesday, January 09, 2019

1

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

2 45

2 45

2 45

1A

1A

1A

5

4

3

2

1

PPVAR_PWR_IN

Charger

D D

PP5000_A

Vout

PPVAR_Cx_VBUS

NX20P3483

Vin

(Power Mux)

Vbus Sink/Source

EC

C C

I2C

ANX7447

CC 1,2

SBU 1,2

SSRX0,1

DDI(0,1,2,3)

AUX

-SS Mux

-VCONN

USB-C

SSTX0,1

USB3-AP

B B

SoC

(SSTX)

-Sink control

-Source control

USB3-AP

(SSRx)

HDP

MAX14637

USB2.0

(BC 1.2)

USB2.0

A A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

USB TYPE-C BLOCK DIAGRAM

USB TYPE-C BLOCK DIAGRAM

USB TYPE-C BLOCK DIAGRAM

Date: Sheet

Date: Sheet of

5

4

3

Date: Sheet of

Wednesday, January 09, 2019

Wednesday, January 09, 2019

Wednesday, January 09, 2019

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

PROJECT :

PROJECT :

PROJECT :

ZAK_ZAN_ZAP_ZAQ

of

3 45

3 45

3 45

1

1A

1A

1A

5

4

3

2

1

Power Tree

D D

C C

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, January 0 9, 2019

Date: Sheet of

Wednesday, January 0 9, 2019

Date: Sheet of

5

4

3

2

Wednesday, January 0 9, 2019

PROJECT :

Power Tree

Power Tree

Power Tree

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

1

4 45

4 45

4 45

1A

1A

1A

5

D D

C C

4

3

2

1

B B

VBUS

0xE4

VBUS

0xE4

LID ACCEL

0x3E

PMIC

PEN

0x09

LPSS_I2C0 LPSS_I2C1 LPSS_I2C3 LPSS_I2C4

A A

PMC_I2C

P-Sensor

0x28

5

Intel Debug

H1

PCH

Audio

0x1A

ISH_I2C0

LPSS_I2C5

4

Trackpad

0x15

ISH_I2C1

LPSS_I2C6

TouchScreen

0x10

ISH_I2C2

LPSS_I2C7

BATT USB_C0

I2C0

3

USB_C0

0x58

I2C1 I2C2 I2C3 I2C4 I2C7

0x16

EEPROM

0xA0

Charger

0x12

EC(Nuvoton)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

2

Wednesday, January 09, 2019

PROJECT :

I2C MAP

I2C MAP

I2C MAP

BASE IMU

0xD0

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

5 45

5 45

5 45

1

1A

1A

1A

5

4

3

2

1

(CPU)

AN15

AN17

AU12

AN12

AN13

AU13

AU15

BA10

BJ26

BL26

BJ27

BK27

BJ23

BK23

BJ22

BL22

BD27

BF27

BH27

BC27

BH21

BF23

BD23

BF21

BK19

BJ20

BL20

BJ21

BJ17

BJ16

BK15

BL16

BA21

AY23

BA23

BA17

AY21

AY17

AY19

BA19

AY3

BD3

BD1

BC3

AY1

BA3

BA2

BE2

AR8

AP3

AU2

AV3

AW3

AN2

AP1

AR3

AV1

AR5

BA8

AU7

AU5

BA5

BA7

AU8

U4B

MEM_CH1_DQ B8

MEM_CH1_DQ B9

MEM_CH1_DQ B10

MEM_CH1_DQ B11

MEM_CH1_DQ B12

MEM_CH1_DQ B13

MEM_CH1_DQ B14

MEM_CH1_DQ B15

MEM_CH1_DQ B0

MEM_CH1_DQ B1

MEM_CH1_DQ B2

MEM_CH1_DQ B3

MEM_CH1_DQ B4

MEM_CH1_DQ B5

MEM_CH1_DQ B6

MEM_CH1_DQ B7

MEM_CH1_DQ B24

MEM_CH1_DQ B25

MEM_CH1_DQ B26

MEM_CH1_DQ B27

MEM_CH1_DQ B28

MEM_CH1_DQ B29

MEM_CH1_DQ B30

MEM_CH1_DQ B31

MEM_CH1_DQ B16

MEM_CH1_DQ B17

MEM_CH1_DQ B18

MEM_CH1_DQ B19

MEM_CH1_DQ B20

MEM_CH1_DQ B21

MEM_CH1_DQ B22

MEM_CH1_DQ B23

MEM_CH1_DQ A0

MEM_CH1_DQ A1

MEM_CH1_DQ A2

MEM_CH1_DQ A3

MEM_CH1_DQ A4

MEM_CH1_DQ A5

MEM_CH1_DQ A6

MEM_CH1_DQ A7

MEM_CH1_DQ A8

MEM_CH1_DQ A9

MEM_CH1_DQ A10

MEM_CH1_DQ A11

MEM_CH1_DQ A12

MEM_CH1_DQ A13

MEM_CH1_DQ A14

MEM_CH1_DQ A15

MEM_CH1_DQ A16

MEM_CH1_DQ A17

MEM_CH1_DQ A18

MEM_CH1_DQ A19

MEM_CH1_DQ A20

MEM_CH1_DQ A21

MEM_CH1_DQ A22

MEM_CH1_DQ A23

MEM_CH1_DQ A24

MEM_CH1_DQ A25

MEM_CH1_DQ A26

MEM_CH1_DQ A27

MEM_CH1_DQ A28

MEM_CH1_DQ A29

MEM_CH1_DQ A30

MEM_CH1_DQ A31

DDR4_LP3_LP4DDR4_LP3_LP4

MEM_CH1_DQ SA0_P

MEM_CH1_DQ SA0

MEM_CH1_DQ SA1_P

MEM_CH1_DQ SA1

MEM_CH1_DQ SA2_P

MEM_CH1_DQ SA2

MEM_CH1_DQ SA3_P

MEM_CH1_DQ SA3

MEM_CH1_DQ SB0_P

MEM_CH1_DQ SB0

MEM_CH1_DQ SB1_P

MEM_CH1_DQ SB1

MEM_CH1_DQ SB2_P

MEM_CH1_DQ SB2

MEM_CH1_DQ SB3_P

DDR1

2 OF 13

MEM_CH1_DQ SB3

MEM_CH1_CA B5

MEM_CH1_CA B0

MEM_CH1_CA B3

MEM_CH1_CA B4

MEM_CH1_CA B2

MEM_CH1_CA B1

MEM_CH1_CA A5

MEM_CH1_CA A2

MEM_CH1_CA A1

MEM_CH1_CA A3

MEM_CH1_CA A0

MEM_CH1_CA A4

MEM_CH1_CL KB_P

MEM_CH1_CL KB

MEM_CH1_CL KA_P

MEM_CH1_CL KA

MEM_CH1_CK E0B

MEM_CH1_CK E1B

MEM_CH1_CS 0B

MEM_CH1_CS 1B

MEM_CH1_CS 0A

MEM_CH1_CS 1A

MEM_CH1_CK E0A

MEM_CH1_CK E1A

MEM_CH0_RC OMP

MEM_CH1_RE SET

MEM_CH1_RC OMP

MEM_CH0_RE SET

NCTF9

NCTF3

NCTF6

NCTF7

NCTF8

NCTF13

NCTF11

NCTF14

NCTF10

NCTF12

NCTF4

NCTF5

NCTF1

NCTF2

BJ24

BK25

BD25

BF25

BL18

BJ18

AV19

AV21

AR13

AR15

BB3

BC2

AW7

AW8

AT1

AT3

BH9

BC13

BD11

BD13

BF11

BE5

BH5

BH6

BF13

BG4

BE7

BK11

BJ12

BK9

BJ11

BJ10

BJ4

BL6

BJ5

BJ9

BJ6

BJ8

BF17

BD17

BF15

BH15

BJ13

BL12

BF1

BF2

BC7

BH2

BC8

BG2

BK13

BJ14

AY29

BC15

AY27

AV27

AY25

BC43

DDR_RCOMP_ CH0

DDR_RST_CH1_ L

DDR_RCOMP_ CH1

DDR_VREF_C A_CH1

DDR_VREF_D Q_CH1

DDR_RST_CH0_ L

DDR_1A_DQ S_0_P (17)

DDR_1A_DQ S_0_N (17 )

DDR_1A_DQ S_1_P (17)

DDR_1A_DQ S_1_N (17 )

DDR_1A_DQ S_2_P (17)

DDR_1A_DQ S_2_N (17 )

DDR_1A_DQ S_3_P (17)

DDR_1A_DQ S_3_N (17 )

DDR_1B_DQ S_0_P (17)

DDR_1B_DQ S_0_N (17 )

DDR_1B_DQ S_1_P (17)

DDR_1B_DQ S_1_N (17 )

DDR_1B_DQ S_2_P (17)

DDR_1B_DQ S_2_N (17 )

DDR_1B_DQ S_3_P (17)

DDR_1B_DQ S_3_N (17 )

DDR_1B_CA <5> (17)

DDR_1B_CA <0> (17)

DDR_1B_CA <3> (17)

DDR_1B_CA <4> (17)

DDR_1B_CA <2> (17)

DDR_1B_CA <1> (17)

DDR_1A_CA <5> (17)

DDR_1A_CA <2> (17)

DDR_1A_CA <1> (17)

DDR_1A_CA <3> (17)

DDR_1A_CA <0> (17)

DDR_1A_CA <4> (17)

DDR_1B_CL K_P (17)

DDR_1B_CL K_N (17)

DDR_1A_CL K_P (17)

DDR_1A_CL K_N (17)

DDR_1B_CK E<0> (17)

DDR_1B_CK E<1> (17)

DDR_1B_CS <0> (17)

DDR_1B_CS <1> (17)

DDR_1A_CS <0> (17)

DDR_1A_CS <1> (17)

DDR_1A_CK E<0> (17)

DDR_1A_CK E<1> (17)

DDR_RST_CH1_ L (17 )

TP143

TP144

DDR_RST_CH0_ L (16 )

PP1100_VDDQ

D D

DDR_0B_DQ <8>(16)

DDR_0B_DQ <9>(16)

DDR_0B_DQ <10>(16)

DDR_0B_DQ <11>(16)

DDR_0B_DQ <12>(16)

DDR_0B_DQ <13>(16)

DDR_0B_DQ <14>(16)

DDR_0B_DQ <15>(16)

DDR_0B_DQ <0>(16)

DDR_0B_DQ <1>(16)

DDR_0B_DQ <2>(16)

DDR_0B_DQ <3>(16)

DDR_0B_DQ <4>(16)

DDR_0B_DQ <5>(16)

DDR_0B_DQ <6>(16)

DDR_0B_DQ <7>(16)

DDR_0B_DQ <24>(16)

DDR_0B_DQ <25>(16)

DDR_0B_DQ <26>(16)

DDR_0B_DQ <27>(16)

DDR_0B_DQ <28>(16)

DDR_0B_DQ <29>(16)

DDR_0B_DQ <30>(16)

DDR_0B_DQ <31>(16)

DDR_0B_DQ <16>(16)

DDR_0B_DQ <17>(16)

DDR_0B_DQ <18>(16)

DDR_0B_DQ <19>(16)

DDR_0B_DQ <20>(16)

DDR_0B_DQ <21>(16)

DDR_0B_DQ <22>(16)

DDR_0B_DQ <23>(16)

DDR_0A_DQ <0>(16)

DDR_0A_DQ <1>(16)

DDR_0A_DQ <2>(16)

DDR_0A_DQ <3>(16)

C C

DDR_0A_DQ <4>(16)

DDR_0A_DQ <5>(16)

DDR_0A_DQ <6>(16)

DDR_0A_DQ <7>(16)

DDR_0A_DQ <8>(16)

DDR_0A_DQ <9>(16)

DDR_0A_DQ <10>(16)

DDR_0A_DQ <11>(16)

DDR_0A_DQ <12>(16)

DDR_0A_DQ <13>(16)

DDR_0A_DQ <14>(16)

DDR_0A_DQ <15>(16)

DDR_0A_DQ <16>(16)

DDR_0A_DQ <17>(16)

DDR_0A_DQ <18>(16)

DDR_0A_DQ <19>(16)

DDR_0A_DQ <20>(16)

DDR_0A_DQ <21>(16)

DDR_0A_DQ <22>(16)

DDR_0A_DQ <23>(16)

DDR_0A_DQ <24>(16)

DDR_0A_DQ <25>(16)

DDR_0A_DQ <26>(16)

DDR_0A_DQ <27>(16)

DDR_0A_DQ <28>(16)

DDR_0A_DQ <29>(16)

DDR_0A_DQ <30>(16)

DDR_0A_DQ <31>(16)

B B

BK37

BK41

BA35

AY33

BA33

AY35

BA37

AY37

AY39

BA39

BK29

BK33

BD29

BF29

BH29

BF33

BC29

BD33

BF35

BH35

AR53

AP55

AP53

AN54

AU54

AV53

AV55

AW53

AU51

AU48

AU49

BA46

BA48

BA49

BA51

AR51

AY55

BA54

BA53

AY53

BC53

BD55

BE54

BD53

AN43

AN44

AR48

AU41

AU43

AN41

AN39

AU44

BJ36

BJ35

BL36

BJ39

BL40

BJ40

BL34

BL30

BJ29

BJ33

BJ34

BJ30

U4A

MEM_CH0_DQ B8

MEM_CH0_DQ B9

MEM_CH0_DQ B10

MEM_CH0_DQ B11

MEM_CH0_DQ B12

MEM_CH0_DQ B13

MEM_CH0_DQ B14

MEM_CH0_DQ B15

MEM_CH0_DQ B0

MEM_CH0_DQ B1

MEM_CH0_DQ B2

MEM_CH0_DQ B3

MEM_CH0_DQ B4

MEM_CH0_DQ B5

MEM_CH0_DQ B6

MEM_CH0_DQ B7

MEM_CH0_DQ B24

MEM_CH0_DQ B25

MEM_CH0_DQ B26

MEM_CH0_DQ B27

MEM_CH0_DQ B28

MEM_CH0_DQ B29

MEM_CH0_DQ B30

MEM_CH0_DQ B31

MEM_CH0_DQ B16

MEM_CH0_DQ B17

MEM_CH0_DQ B18

MEM_CH0_DQ B19

MEM_CH0_DQ B20

MEM_CH0_DQ B21

MEM_CH0_DQ B22

MEM_CH0_DQ B23

MEM_CH0_DQ A0

MEM_CH0_DQ A1

MEM_CH0_DQ A2

MEM_CH0_DQ A3

MEM_CH0_DQ A4

MEM_CH0_DQ A5

MEM_CH0_DQ A6

MEM_CH0_DQ A7

MEM_CH0_DQ A8

MEM_CH0_DQ A9

MEM_CH0_DQ A10

MEM_CH0_DQ A11

MEM_CH0_DQ A12

MEM_CH0_DQ A13

MEM_CH0_DQ A14

MEM_CH0_DQ A15

MEM_CH0_DQ A16

MEM_CH0_DQ A17

MEM_CH0_DQ A18

MEM_CH0_DQ A19

MEM_CH0_DQ A20

MEM_CH0_DQ A21

MEM_CH0_DQ A22

MEM_CH0_DQ A23

MEM_CH0_DQ A24

MEM_CH0_DQ A25

MEM_CH0_DQ A26

MEM_CH0_DQ A27

MEM_CH0_DQ A28

MEM_CH0_DQ A29

MEM_CH0_DQ A30

MEM_CH0_DQ A31

DDR0

1 OF 13

DDR4_LP3_LP4DDR4_LP3_LP4

MEM_CH0_DQ SA0_P

MEM_CH0_DQ SA0

MEM_CH0_DQ SA1_P

MEM_CH0_DQ SA1

MEM_CH0_DQ SA2_P

MEM_CH0_DQ SA2

MEM_CH0_DQ SA3_P

MEM_CH0_DQ SA3

MEM_CH0_DQ SB0_P

MEM_CH0_DQ SB0

MEM_CH0_DQ SB1_P

MEM_CH0_DQ SB1

MEM_CH0_DQ SB2_P

MEM_CH0_DQ SB2

MEM_CH0_DQ SB3_P

MEM_CH0_DQ SB3

MEM_CH0_CK E1B

MEM_CH0_CK E0B

MEM_CH0_CS 0B

MEM_CH0_CS 1B

MEM_CH0_CS 1A

MEM_CH0_CS 0A

MEM_CH0_CK E1A

MEM_CH0_CK E0A

MEM_CH0_CL KB_P

MEM_CH0_CL KB

MEM_CH0_CL KA_P

MEM_CH0_CL KA

MEM_CH0_CA B5

MEM_CH0_CA B0

MEM_CH0_CA B3

MEM_CH0_CA B4

MEM_CH0_CA B2

MEM_CH0_CA B1

NCTF14

MEM_CH0_CA A2

MEM_CH0_CA A1

MEM_CH0_CA A3

MEM_CH0_CA A0

MEM_CH0_CA A4

NCTF12

NCTF13

NCTF10

NCTF11

MEM_CH0_CA A5

NCTF5

NCTF3

NCTF4

NCTF8

NCTF6

NCTF9

NCTF7

NCTF2

NCTF1

AT53

AT55

AW49

AW48

BC54

BB53

AR41

AR43

AV37

AV35

BL38

BJ38

BF31

BD31

BJ32

BK31

BG54

BH54

BJ42

BF39

BK43

BL44

BD39

BJ43

BF54

BF55

BE49

BE51

BC49

BC48

BD45

BH50

BH47

BF45

BH43

BD41

BH51

BD43

BF43

BF41

BG52

BK45

BJ46

BJ44

BJ47

BJ45

BK47

BJ51

BJ52

BJ48

BJ50

BL50

AY31

AV29

DDR_VREF_D Q_CH0

DDR_VREF_C A_CH0

DDR_0A_DQ S_0_P (16)

DDR_0A_DQ S_0_N (16 )

DDR_0A_DQ S_1_P (16)

DDR_0A_DQ S_1_N (16 )

DDR_0A_DQ S_2_P (16)

DDR_0A_DQ S_2_N (16 )

DDR_0A_DQ S_3_P (16)

DDR_0A_DQ S_3_N (16 )

DDR_0B_DQ S_0_P (16)

DDR_0B_DQ S_0_N (16 )

DDR_0B_DQ S_1_P (16)

DDR_0B_DQ S_1_N (16 )

DDR_0B_DQ S_2_P (16)

DDR_0B_DQ S_2_N (16 )

DDR_0B_DQ S_3_P (16)

DDR_0B_DQ S_3_N (16 )

DDR_0B_CK E<1> (16)

DDR_0B_CK E<0> (16)

DDR_0B_CS <0> (16)

DDR_0B_CS <1> (16)

DDR_0A_CS <1> (16)

DDR_0A_CS <0> (16)

DDR_0A_CK E<1> (16)

DDR_0A_CK E<0> (16)

DDR_0B_CL K_P (16)

DDR_0B_CL K_N (16)

DDR_0A_CL K_P (16)

DDR_0A_CL K_N (16)

DDR_0B_CA <5> (16)

DDR_0B_CA <0> (16)

DDR_0B_CA <3> (16)

DDR_0B_CA <4> (16)

DDR_0B_CA <2> (16)

DDR_0B_CA <1> (16)

DDR_0A_CA <2> (16)

DDR_0A_CA <1> (16)

DDR_0A_CA <3> (16)

DDR_0A_CA <0> (16)

DDR_0A_CA <4> (16)

DDR_0A_CA <5> (16)

TP141

TP142

DDR_1B_DQ <8>(17)

DDR_1B_DQ <9>(17)

DDR_1B_DQ <10>(17)

DDR_1B_DQ <11>(17)

DDR_1B_DQ <12>(17)

DDR_1B_DQ <13>(17)

DDR_1B_DQ <14>(17)

DDR_1B_DQ <15>(17)

DDR_1B_DQ <0>(17)

DDR_1B_DQ <1>(17)

DDR_1B_DQ <2>(17)

DDR_1B_DQ <3>(17)

DDR_1B_DQ <4>(17)

DDR_1B_DQ <5>(17)

DDR_1B_DQ <6>(17)

DDR_1B_DQ <7>(17)

DDR_1B_DQ <24>(17)

DDR_1B_DQ <25>(17)

DDR_1B_DQ <26>(17)

DDR_1B_DQ <27>(17)

DDR_1B_DQ <28>(17)

DDR_1B_DQ <29>(17)

DDR_1B_DQ <30>(17)

DDR_1B_DQ <31>(17)

DDR_1B_DQ <16>(17)

DDR_1B_DQ <17>(17)

DDR_1B_DQ <18>(17)

DDR_1B_DQ <19>(17)

DDR_1B_DQ <20>(17)

DDR_1B_DQ <21>(17)

DDR_1B_DQ <22>(17)

DDR_1B_DQ <23>(17)

DDR_1A_DQ <0>(17)

DDR_1A_DQ <1>(17)

DDR_1A_DQ <2>(17)

DDR_1A_DQ <3>(17)

DDR_1A_DQ <4>(17)

DDR_1A_DQ <5>(17)

DDR_1A_DQ <6>(17)

DDR_1A_DQ <7>(17)

DDR_1A_DQ <8>(17)

DDR_1A_DQ <9>(17)

DDR_1A_DQ <10>(17)

DDR_1A_DQ <11>(17)

DDR_1A_DQ <12>(17)

DDR_1A_DQ <13>(17)

DDR_1A_DQ <14>(17)

DDR_1A_DQ <15>(17)

DDR_1A_DQ <16>(17)

DDR_1A_DQ <17>(17)

DDR_1A_DQ <18>(17)

DDR_1A_DQ <19>(17)

DDR_1A_DQ <20>(17)

DDR_1A_DQ <21>(17)

DDR_1A_DQ <22>(17)

DDR_1A_DQ <23>(17)

DDR_1A_DQ <24>(17)

DDR_1A_DQ <25>(17)

DDR_1A_DQ <26>(17)

DDR_1A_DQ <27>(17)

DDR_1A_DQ <28>(17)

DDR_1A_DQ <29>(17)

DDR_1A_DQ <30>(17)

DDR_1A_DQ <31>(17)

DDR_RCOMP_ CH0

DDR_RCOMP_ CH1

R307

110_1%_ 4

R309

110_1%_ 4

DDR_RST_CH0_ L

DDR_RST_CH1_ L

R26

*1K_1%_ 2

R29

*1K_1%_ 2

PLACE AS CLOSE TO SOC AS POSSIBLE

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet

Wednesday, J anuary 09, 2019

Wednesday, J anuary 09, 2019

Wednesday, J anuary 09, 2019

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

SOC DRAM I/F

SOC DRAM I/F

SOC DRAM I/F

1

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

of

6 45

6 45

6 45

1A

1A

1A

5

4

3

2

1

Gemini lake (DISPLAY,eDP)

(CPU)

PP3300_PD_A

USB C PORT 0

D D

DDI0_AUX_P(29)

DDI0_AUX_N(29)

R21

100K_5%_2

R22

100K_5%_2

C336 0.1u/16V_4

C337 0.1u/16V_4

USB C PORT 1

PP3300_PD_A

R459

*2AC@100K_5%_2

DDI1_AUX_P(39)

DDI1_AUX_N(39)

C C

R460

*2AC@100K_5%_2

LOCAL DISPLAY PANEL

SOC_EDP_BKLTCTL_1V8(26)

SOC_EDP_BKLTEN(26)

EN_PP3300_EDP_DX(35)

B B

DDI0_TX0_P(29)

DDI0_TX0_N(29)

DDI0_TX1_P(29)

DDI0_TX1_N(29)

DDI0_TX2_P(29)

DDI0_TX2_N(29)

DDI0_TX3_P(29)

DDI0_TX3_N(29)

USB_C0_HPD_1V8_ODL(18,29)

DDI1_TX0_P(39)

DDI1_TX0_N(39)

DDI1_TX1_P(39)

DDI1_TX1_N(39)

DDI1_TX2_P(39)

DDI1_TX2_N(39)

DDI1_TX3_P(39)

DDI1_TX3_N(39)

C338 *Short_0201

C339 *Short_0201

DDI0_AUX_C_P

DDI0_AUX_C_N

C84Q

*10p/25V_2

DDI1_AUX_C_P

DDI1_AUX_C_N

1228_Q_Changed C338/C339 to a short pad

EDP_TX0_P(26)

EDP_TX0_N(26)

EDP_TX1_P(26)

EDP_TX1_N(26)

EDP_TX2_P(26)

EDP_TX2_N(26)

EDP_TX3_P(26)

EDP_TX3_N(26)

EDP_AUX_PANEL_P(26)

EDP_AUX_PANEL_N(26)

EDP_HPD_PANEL_1V8_ODL

R2 100_1%_2

EDP_PLLOBS_DP

EDP_PLLOBS_DN

AH1

AH3

AE2

AE3

AG2

AG3

AC12

AC10

C39

C43

AA2

AA3

AD1

AD3

AC2

AC3

AC7

AC5

C42

C38

AE12

AE13

AC15

AC17

AE10

AE8

AE5

AE7

W17

W15

C40

C41

AA5

AA7

AJ2

AJ3

B43

Y3

Y1

A42

B39

B41

U4C

DDI0_TXP_ 0

DDI0_TXN_ 0

DDI0_TXP_ 1

DDI0_TXN_ 1

DDI0_TXP_ 2

DDI0_TXN_ 2

DDI0_TXP_ 3

DDI0_TXN_ 3

DDI0_AUXP

DDI0_AUXN

DDI0_HPD

DDI0_DDC_ SCL

DDI0_DDC_ SDA

DDI1_TXP_ 0

DDI1_TXN_ 0

DDI1_TXP_ 1

DDI1_TXN_ 1

DDI1_TXP_ 2

DDI1_TXN_ 2

DDI1_TXP_ 3

DDI1_TXN_ 3

DDI1_AUXP

DDI1_AUXN

DDI1_DDC_ SCL

DDI1_DDC_ SDA

DDI1_HPD

EDP_TXP _0

EDP_TXN _0

EDP_TXP _1

EDP_TXN _1

EDP_TXP _2

EDP_TXN _2

EDP_TXP _3

EDP_TXN _3

EDP_AUX P

EDP_AUX N

EDP_HPD

PNL0_BK LCTL

PNL0_BK LTEN

PNL0_VD DEN

EDP_RCO MP_P

EDP_RCO MP

GLK_SOC_RVP2

eDP/DDI_A

1.8V/3.3V

1.8V/3.3V

1.8V/3.3V

DDI0/DDI_B

DDI1/DDI_C

3 OF 13

MDSI

1.8V

MDSI_A_CL KP

MDSI_A_CL KN

MDSI_C_CL KP

MDSI_C_CL KN

MDSI_A_DP _0

MDSI_A_DN _0

MDSI_A_DP _1

MDSI_A_DN _1

MDSI_A_DP _2

MDSI_A_DN _2

MDSI_A_DP _3

MDSI_A_DN _3

MDSI_C_DP _0

MDSI_C_DN _0

MDSI_C_DP _1

MDSI_C_DN _1

MDSI_C_DP _2

MDSI_C_DN _2

MDSI_C_DP _3

MDSI_C_DN _3

MIPI_I2C_SCL

MIPI_I2C_SDA

MDSI_C_TE

MDSI_A_TE

MDSI_RCOM P

AL2

AM3

AG13

AG12

AN5

AN7

AJ15

AJ17

AJ7

AJ5

AJ10

AJ12

AG15

AG17

AG8

AG10

AG7

AG5

AE15

AE17

TP_PCH_GPIO47

R53

TP_PCH_GPIO46

R54

T53

T55

AL5

TP_MDSIA_CLKP

TP_MDSIA_CLKN

TP_MDSIC_CLKP

TP_MDSIC_CLKN

TP_MDSIA_D0_P

TP_MDSIA_D0_N

TP_MDSIA_D1_P

TP_MDSIA_D1_N

TP_MDSIA_D2_P

TP_MDSIA_D2_N

TP_MDSIA_D3_P

TP_MDSIA_D3_N

TP_MDSIC_D0_P

TP_MDSIC_D0_N

TP_MDSIC_D1_P

TP_MDSIC_D1_N

TP_MDSIC_D2_P

TP_MDSIC_D2_N

TP_MDSIC_D3_P

TP_MDSIC_D3_N

MCSI1_RCOMP

TP31

TP37

R1

150_1%_2

(LDS)

ALL NC

R502 *0_5%_2

PP1800_SOC_A

GP_INTD_DSI_TE2

TP_WIFI_RST_N

GP_INTD_DSI_TE2 (20)USB_C1_HPD_1V8_ODL(18,39)

TP72

TP135

R731

100K_5%_2

EDP_HPD_PANEL_1V8_ODL

3

2

EDP_HPD_PANEL(26)

A A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

SOC EDP/MIPI/DDI

SOC EDP/MIPI/DDI

SOC EDP/MIPI/DDI

Wednesday, January 09, 2019

Wednesday, January 09, 2019

Wednesday, January 09, 2019

Q78

PJE138K

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

PROJECT :

PROJECT :

PROJECT :

ZAK_ZAN_ZAP_ZAQ

7 45

7 45

7 45

1

of

1A

1A

1A

5

4

3

2

1

Gemini lake (SATA , ODD, CLK ,USB,PCIE)

(CPU)

CLKDRV_RCOMP

TP162

TP163

R7

56_1%_4

TP112

D D

PCIE_WLAN_CLK_P(28)

PCIE_WLAN_CLK_N(28)

PCIE_PCH_TX_WLAN_RX_C_P(28)

PCIE_PCH_TX_WLAN_RX_C_N(28)

PCIE_PCH_RX_WLAN_TX_P(28)

PCIE_PCH_RX_WLAN_TX_N(28)

TP157

TP145

TP171

WIFI_DISABLE_L(28)

C C

LTE_WAKE_L(38)

TP164

TP113

PCIE_CLKREQ0_ODL

PCIE_CLKREQ1_ODL

PCIE_CLKREQ2_ODL

WLAN_PCIE_CLKREQ_ODL

WLAN_PCIE_WAKE_ODL

3V3 IO TOLERANT

B B

(NGF)

U4D

L10

PCIE_REF_CLK_RCOMP

R12

R10

N7

N5

R7

R5

N8

N10

E2

F2

G7

H6

A7

C7

D4

E5

C9

B9

E7

F6

A46

C45

B45

C44

F47

D47

F45

D50

J3

J2

J7

J5

PCIE_CLKOUT0P

PCIE_CLKOUT0N

PCIE_CLKOUT1P

PCIE_CLKOUT1N

PCIE_CLKOUT2P

PCIE_CLKOUT2N

PCIE_CLKOUT3P

PCIE_CLKOUT3N

PCIE_P0_TXP

PCIE_P0_TXN

PCIE_P0_RXP

PCIE_P0_RXN

PCIE_P1_TXP

PCIE_P1_TXN

PCIE_P1_RXP

PCIE_P1_RXN

PCIE_P2_TXP

PCIE_P2_TXN

PCIE_P2_RXP

PCIE_P2_RXN

PCIE_CLKREQ0

PCIE_CLKREQ1

PCIE_CLKREQ2

PCIE_CLKREQ3

PCIE_WAKE0

PCIE_WAKE1

PCIE_WAKE2

PCIE_WAKE3

SATA_P0_TXP

SATA_P0_TXN

SATA_P0_RXP

SATA_P0_RXN

PCIe

1.8V/3.3V

SATA

SATA/USB3

USB3

PCIe/USB3

4 OF 13

PP1800_SOC_A PP3300_WLAN_DX

SSIC

USB2

SATA_P1_USB3_P5_TXP

SATA_P1_USB3_P5_TXN

SATA_P1_USB3_P5_RXP

SATA_P1_USB3_P5_RXN

USB3_P0_TXP

USB3_P0_TXN

USB3_P0_RXP

USB3_P0_RXN

USB3_P1_TXP

USB3_P1_TXN

USB3_P1_RXP

USB3_P1_RXN

PCIE_P3_USB3_P4_TXP

PCIE_P3_USB3_P4_TXN

PCIE_P3_USB3_P4_RXP

PCIE_P3_USB3_P4_RXN

PCIE_P4_USB3_P3_TXP

PCIE_P4_USB3_P3_TXN

PCIE_P4_USB3_P3_RXP

PCIE_P4_USB3_P3_RXN

PCIE_P5_USB3_P2_TXP

PCIE_P5_USB3_P2_TXN

PCIE_P5_USB3_P2_RXP

PCIE_P5_USB3_P2_RXN

PCIE2_USB3_SATA3_RCOMP

PCIE2_USB3_SATA3_RCOMP_P

USB2_DP0

USB2_DN0

USB2_DP1

USB2_DN1

USB2_DP2

USB2_DN2

USB2_DP3

USB2_DN3

USB2_DP4

USB2_DN4

USB2_DP5

USB2_DN5

USB2_DP6

USB2_DN6

USB2_DP7

USB2_DN7

USB2_RCOMP

USB2_DUALROLE

USB2_VBUS_SNS

USB2_OC0

1.8V

USB2_OC1

H1

H2

H4

G5

B15

C15

F15

D15

C14

A14

J11

H11

C10

A10

H9

F9

C11

B11

D11

F11

B13

C13

F13

D13

C5

C6

AA10

NC1

AA8

NC2

W13

NC5

W12

NC4

U15

NC3

U7

U5

N2

N3

L2

L3

R13

R15

M1

M3

R2

R3

P1

P3

U8

U10

U12

V1

V3

U54

U53

USB3_P5_SD_TX_C_P

USB3_P5_SD_TX_C_N

USB3_P0_C0_TX_C_P

USB3_P0_C0_TX_C_N

USB3_P1_A0_TX_C_P

USB3_P1_A0_TX_C_N

USB3_P2_TX_C_P

USB3_P2_TX_C_N

USB2_RCOMP

USB_OTG_ID_HOSTORSLAVE

USB_OTG

C272 *Short_0201

C303 *Short_0201

R3 100_1%_2

R9 113_1%_2

USB_A_OC_ODL

USB_C_OC_ODL

INTERNAL PULL-UP

SD CARD I/F FOR HIGHER SPEED D EVICE

C346 0.1u/10V_2

C349 0.1u/10V_2

USB3_P5_SD_RX_P (23)

USB3_P5_SD_RX_N (23)

USB3_P0_C0_RX_P (29)

USB3_P0_C0_RX_N (29)

C305 0.1u/10V_2

C307 0.1u/10V_2

USB3_P1_A0_RX_P (30)

USB3_P1_A0_RX_N (30)

USB3_P4_C1_RX_P (39)

USB3_P4_C1_RX_N (39)

USB3_P3_A1_RX_P (39)

USB3_P3_A1_RX_N (39)

C365 ACM@0.1u/10V_2

C410 ACM@0.1u/10V_2

USB2_P0_C0_P (31)

USB2_P0_C0_N (31)

USB2_P1_A0_P (30)

USB2_P1_A0_N (30)

USB2_P2_BT_P (28)

USB2_P2_BT_N (28)

USB2_P3_A1_P (39)

USB2_P3_A1_N (39)

USB2_P4_C1_P (39)

USB2_P4_C1_N (39)

USB2_P5_SD_P (23)

USB2_P5_SD_N (23)

USB2_P6_UCAM_P (26)

USB2_P6_UCAM_N (26)

USB2_P7_WCAM_P (26)

USB2_P7_WCAM_N (26)

R747 *Short_0201

USB3_P5_SD_TX_P (23)

USB3_P5_SD_TX_N (23)

0102_Q_Changed C272/C303 to a short pad

USB3_P0_C0_TX_P (29)

USB3_P0_C0_TX_N (29)

USB3_P1_A0_TX_P (30)

USB3_P1_A0_TX_N (30)

USB3_P4_C1_TX_P (39)

USB3_P4_C1_TX_N (39)

USB3_P3_A1_TX_P (39)

USB3_P3_A1_TX_N (39)

TYPE C PORT 0

TYPE A PORT 0

WIFI-BT

TYPE A PORT 1

TYPE C PORT 1

USB-USD CARD

CAMERA UFC

CAMERA WFC

SD CARD

TYPE C PORT 0

TYPE A PORT 0

TYPE C PORT 1, sub board

IF YOU KEEP CAPS ON THE MLB FO R TYPE-A AND TYPE-C TX LINES

MAKE SURE TO REMOVE THEM FROM THE DAUGHTERBOARD

USB3_P2_WCAM_TX_P (40)

USB3_P2_WCAM_TX_N (40)

USB3_P2_WCAM_RX_P (40)

USB3_P2_WCAM_RX_N (40)

TYPE A PORT 1, sub board

AR WFC

PP1800_SOC_A

R9093

100K_5%_2

1226_Q_added DNS 10pF on USB_A0_OC_ODL for

PPVAR_VBUS_IN noise coupling

C110Q *10p/25V_2

R331 *Short_0201

R332 *Short_0201

R326 *Short_0201

R329 *0_5%_2

USB_A0_OC_ODL (30)

USB_A1_OC_ODL (39)

USB_C_OC (18)

USB_C1_OC_ODL

R10

10K_1%_2

R11

10K_1%_2

2

Q1B

*PMDXB600UNE

2

Q2B

*PMDXB600UNE

61

61

WLAN_PCIE_CLKREQ_ODL

PP1800_SOC_A PP3300_WLAN_DX

A A

WLAN_PCIE_WAKE_ODL

AVOIDS ANY LEAKAGE WITHOUT SOF TWARE EFFORTS

5

4

5

3 4

Q1A

*PMDXB600UNE

0107_Q_DNS Q1,Q2 since pin53, pin55 of M.2 are

not used in Jefferson peak 9560

5

3 4

Q2A

*PMDXB600UNE

3

WLAN_PCIE_CLKREQ_3V3_ODL (28)

WLAN_PCIE_WAKE_3V3_ODL (28)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

2

Wednesday, January 09, 2019

PROJECT :

SOC PCIE/USB/SATA

SOC PCIE/USB/SATA

SOC PCIE/USB/SATA

1

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

8 45

8 45

8 45

1A

1A

1A

5

4

3

2

1

Gemini lake (EMMC/LPC/I2C/GPIO/HDA)

(CPU)

EC_I2S_SCLK(18)

D D

EC_I2S_SFRM(18)

EC_I2S_TX_PCH_RX(18)

R281 20_1%_2

R295 20_1%_2

R298 20_1%_2

(CPU)

C C

HEADPHONE

DMIC'S

B B

PP1800_SOC_A

EMMC_RCLK(23)

TEST POINTS ON EMMC CLOSE TO SOC

TO-EC

SPEAKER AMP

I2S_SCLK_HP(24)

I2S_SFRM_HP(24)

I2S_PCH_RX_HP_TX(24)

I2S_PCH_TX_HP_RX(24)

I2S_MCLK_HP(24)

DMIC_CLK2(26,40)

R282 4.7K_5%_2

DMIC_CAM2_DATA(40)

R590

100K_1%_6

LTE_OFF_ODL(38)

I2S_SCLK_SPKR(24)

I2S_SFRM_SPKR(24)

WLAN_PE_RST(28)

I2S_PCH_TX_SPKR_RX(24)

EMMC_CLK(23)

EMMC_DAT0(23)

EMMC_DAT1(23)

EMMC_DAT2(23)

EMMC_DAT3(23)

EMMC_DAT4(23)

EMMC_DAT5(23)

EMMC_DAT6(23)

EMMC_DAT7(23)

EMMC_CMD(23)

EMMC_RST_ODL(23)

I2S0_SCLK_R

I2S0_SFRM_R

I2S0_PCH_RX

C571

2.2p/25V_2

TP70

TP53

TP54

TP57

TP59

I2S0_SCLK_R

I2S0_SFRM_R

I2S0_PCH_RX

I2S0_PCH_TX

R32 20_1%_2

R33 20_1%_2

R36 20_1%_2

R37 20_1%_2

R40 20_1%_2

TP51

TP52

TP61

TP44

TP41

TP42 R198

TP43

TP30

I2S2_SCLK_R

I2S2_SFRM_R

I2S2_PCH_RX

I2S2_PCH_TX

I2S2_MCLK_R

DMIC_CLK1_R

DMIC_CLK2_R

DMIC_DATA_R

TP_GPIO_174

TP_EN_PP3300_EMMC

RCOMP_EMMC0

R284

200_1%_2

C572

2.2p/25V_2

C573

2.2p/25V_2

U4J

C26

AVS_I2S0_MCLK

B25

AVS_I2S0_BCLK

C25

AVS_I2S0_WS_SYNC

C24

AVS_I2S0_SDI

B23

AVS_I2S0_SDO

M23

AVS_I2S1_MCLK

L21

AVS_I2S1_BCLK

J21

AVS_I2S1_WS_SYNC

M21

AVS_I2S1_SDI

P23

AVS_I2S1_SDO

A22

AVS_HDA_BCLK

C23

AVS_HDA_WS_SYNC

B21

AVS_HDA_SDI

C22

AVS_HDA_SDO

C21

AVS_HDA_RST

B19

AVS_DMIC_CLK_A1

C20

AVS_DMIC_CLK_B1

C19

AVS_DMIC_DATA_1

C18

AVS_DMIC_CLK_AB2

A18

AVS_DMIC_DATA_2

J13

EMMC_CLK

L15

EMMC_RCLK

M19

EMMC_D0

H19

EMMC_D1

J19

EMMC_D2

P17

EMMC_D3

P19

EMMC_D4

J15

EMMC_D5

L17

EMMC_D6

M17

EMMC_D7

M13

EMMC_CMD

U44

EMMC_RST

G51

EMMC_PWR_EN

L13

EMMC_RCOMP

1.8V

1.8V/3.3V

1.8V

AUDIO-AVS

RSVD

LPC/eSPI

LPC set 3.3V

eMMC

FAST_SPI

7 OF 13

(MIC)

1.8V/3.3V

1.8V

RSVD

DMIC_CLK1_R

DMIC_DATA_R

RSVD6

RSVD5

RSVD7

RSVD8

RSVD9

RSVD3

RSVD4

RSVD2

RSVD10

RSVD1

LPC_CLKOUT0

LPC_CLKOUT1

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_CLKRUN

LPC_FRAME

LPC_SERIRQ

FST_SPI_CLK

FST_SPI_MOSI_IO0

FST_SPI_MISO_IO1

FST_SPI_IO2

FST_SPI_IO3

FST_SPI_CS0

FST_SPI_CS1

R300 20_1%_2

WOV

R317 20_1%_2

ESPI_CS_L

ESPI_IO0

ESPI_IO1

ESPI_IO2

ESPI_IO3

L29

M29

P29

M27

P27

L27

L25

P25

native SD card support dropped

L23

J25

C37

A38

A34

C34

B35

C35

C33

B33

B37

B29

B31

C30

A30

C29

C31

C32

ESPI_CLK

ESPI_CLK_R ESPI_CLK

ESPI_IO0_R

ESPI_IO1_R

ESPI_IO2_R

ESPI_IO3_R

ESPI_CS_L_R

ESPI_RESET_L_R

PCH_SPI_CLK_R

PCH_SPI_MOSI_R

PCH_SPI_MISO

PCH_SPI_CS0_L_R

SPK_PA_EN_R

R285 33_5%_2

R67 *33_5%_2

R71 33_5%_2

R73 33_5%_2R189 33_1%_2

R74 33_5%_2

R76 33_5%_2

R90 *33_5%_2

R93 33_5%_2

R128 33_5%_2

R591 33_5%_2

R592 33_5%_2

R593 33_5%_2

R640 *33_5%_2

R642 *33_5%_2

R643 33_5%_2

R644 33_5%_2

DMIC_CLK1 (26)

Q40

1

3

PMZ370UNE

R173 *0_5%_2

R407

20K_1%_2

ESPI_IO0

ESPI_IO1

ESPI_IO2

ESPI_IO3

ESPI_CS_L

TP66

2

PP1800_SOC_A

R187

*20K_1%_2

PCH_SPI_CLK (19)

PCH_SPI_MOSI (19)

PCH_SPI_MISO_R (19)

PCH_SPI_CS0_L (19)

SPK_PA_EN (24)

R283

*20K_1%_2

ESPI_CLK (18)

ESPI_IO0 (18)

ESPI_IO1 (18)

ESPI_IO2 (18)

ESPI_IO3 (18)

ESPI_CS_L (18)

PCH_SLP_S0_L (11,33)

DMIC_CLK1_G (26)

DMIC_DATA (26)

R358

*20K_1%_2

TO-EC

100K_1%_6

TO-FLASH

R363

*20K_1%_2

R365

20K_1%_2

ESPI_RESET_L (18)

A A

Quanta Computer Inc.

Quanta Computer Inc.

No extermal PU/PD on GPIO_174, using internal PD for setting VDD2 to 1.2v (GPIO_174)

R282 is for strapping high to enable eSPI mode (GPIO_175)

5

4

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number R

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

3

2

Wednesday, January 09, 2019

PROJECT :

SOC AUDIO/EMMC/LPC/SPI

SOC AUDIO/EMMC/LPC/SPI

SOC AUDIO/EMMC/LPC/SPI

1

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

9 45

9 45

9 45

ev

1A

1A

1A

5

PP1800_SOC_A

4

3

2

1

(CPU)

MODE SELECTION: PULL HI =1.8V

PP1800_SOC_A

R438

H1_SLAVE_SPI_CLK_R (21)

H1_SLAVE_SPI_MISO (21)

H1_SLAVE_SPI_CS_L_R (21)

GPIO_81_DEBUG (12)

TP50

R8Q *Short_0201

R9Q *Short_0201

4.7K_5%_2

TP62

TP63

TP47

TP36

PCHTX_MIPI60RX_UART

PCHRX_MIPI60TX_UART

R336 *Short_0201

R337 *0_5%_2

R338 *Short_0201

R342 *0_5%_2

H1_SLAVE_SPI_MOSI_R (21)

R239 *33_5%_2

PCHTX_MIPI60RX_UART (20)

PCHRX_MIPI60TX_UART (20)

H1_PCH_INT_ODL (21)

R311 *4.7K_5%_2

PCHRX_SERVOTX_UART (21,22)

PCH_I2C_AUDIO_SCL (24)

PCH_I2C_AUDIO_SDA (24)

TP64

R23

3.3K_1%_2

PP1800_SOC_A

PCHTX_SERVORX_UART (21,22)

PCHTX_MIPI60RX_UART

PCHRX_MIPI60TX_UART

R396

2.2K_1%_2

R573

20K_1%_2

R660

4.7K_5%_2

R661

4.7K_5%_2

PCH_I2C_H1_SCL(21)

PCH_I2C_H1_SDA(21)

PP1800_SOC_A

EN_PP3300_WLAN_L(35)

CNVI_BRI_DT (28)

CNVI_RGI_DT (28)

R717

10K_1%_2

R422 *20K_1%_2

R287 *20K_1%_2

R312

2.2K_1%_2

CNVI_CLK_PCH_RX_WLAN_TX_P(28)

CNVI_CLK_PCH_RX_WLAN_TX_N(28)

CNVI_D0_PCH_RX_WLAN_TX_P(28)

CNVI_D0_PCH_RX_WLAN_TX_N(28)

CNVI_D1_PCH_RX_WLAN_TX_P(28)

CNVI_D1_PCH_RX_WLAN_TX_N(28)

WLAN_CLKREQ0(28)

CNVI_RF_RESET_L(28)

CNVI_RGI_RSP

CNVI_BRI_RSP

R313

2.2K_1%_2

R5 10K_1%_2

TP160

TP161

CNVI_CLK_PCH_TX_WLAN_RX_P(28)

CNVI_CLK_PCH_TX_WLAN_RX_N(28)

CNVI_D0_PCH_TX_WLAN_RX_P(28)

CNVI_D0_PCH_TX_WLAN_RX_N(28)

CNVI_D1_PCH_TX_WLAN_RX_P(28)

CNVI_D1_PCH_TX_WLAN_RX_N(28)

CNVI_BRI_RSP(28)

CNVI_RGI_RSP(28)

R6 150_1%_2

I2C MAY BE PROBLEM IF THE I2C PULL-UP VOLTAGE IS TURNED OFF WHEN DEVICE IS OFF.

AA39

AA41

U49

U51

U46

U48

R44

R43

R49

R51

C50

A50

C48

C47

B47

C46

A26

B27

C27

H29

H31

M31

P31

D29

F29

F35

D35

J35

H35

L31

J31

J29

F19

H17

J17

D19

D17

F17

F33

U4I

SIO_I2C0_SCL

SIO_I2C0_SDA

SIO_I2C1_SCL

SIO_I2C1_SDA

SIO_I2C2_SCL

SIO_I2C2_SDA

SIO_I2C3_SCL

SIO_I2C3_SDA

SIO_I2C4_SCL

SIO_I2C4_SDA

SIO_I2C5_SCL

SIO_I2C5_SDA

SIO_I2C6_SCL

SIO_I2C6_SDA

SIO_I2C7_SCL

SIO_I2C7_SDA

SMB_ALERT

SMB_CLK

SMB_DATA

CNV_WGR_CLK_P

CNV_WGR_CLK

CNV_WGR_D0_P

CNV_WGR_D0

CNV_WGR_D1_P

CNV_WGR_D1

CNV_WT_CLK_P

CNV_WT_CLK

CNV_WT_D0_P

CNV_WT_D0

CNV_WT_D1_P

CNV_WT_D1

CLKIN_XTAL_LCP

XTAL_CLKREQ

CNV_BRI_DT

CNV_BRI_RSP

CNV_RGI_DT

CNV_RGI_RSP

CNV_RF_RESET

CNV_WT_RCOMP

1.8V

1.8V/3.3V

1.8V/3.3V

1.8V

LPSS_I2C

LPSS SMBus

SMBUS set 3.3V

CNVI

PCH_I2C_PEN_SCL

PCH_I2C_PEN_SDA

TP77

TP78

PCH_I2C_AUDIO_SCL_Q

PCH_I2C_AUDIO_SDA_Q

PCH_I2C_TRACKPAD_SCL

PCH_I2C_TRACKPAD_SDA

PCH_I2C_TOUCHSCREEN_SCL

PCH_I2C_TOUCHSCREEN_SDA

TP_SMB_ALERT_N

TP_PCH_SMB_CLK

CNVI_BRI_DT_R

CNVI_BRI_RSP

CNVI_RGI_DT_R

CNVI_RGI_RSP

CNVI_RF_RESET_L

CNVI_WT_RCOMP

PLACEMENMT OF THE LEVEL SHIFTERS AND PULL-UPS DON'T NEED TO BE NEAR AP

6 OF 13

LPSS_SPI

LPSS_UART

1.8V

1.8V

SIO_SPI_0_CLK

SIO_SPI_0_TXD

SIO_SPI_0_RXD

SIO_SPI_0_FS0

SIO_SPI_0_FS1

SIO_SPI_2_CLK

SIO_SPI_2_TXD

SIO_SPI_2_RXD

SIO_SPI_2_FS0

SIO_SPI_2_FS1

SIO_SPI_2_FS2

SIO_UART0_TXD

SIO_UART0_RXD

SIO_UART0_RTS

SIO_UART0_CTS

SIO_UART2_TXD

SIO_UART2_RXD

SIO_UART2_RTS

SIO_UART2_CTS

M39

J37

L39

L37

J39

M37

M33

R230 *33_5%_2

P35

P33

R231 *33_5%_2

P37

TP_PCH_GPIO_87_PD_DURING_RSMRST

L35

N54

P53

N53

M55

GPIO65 USED FOR DNXMODE WITH PULL-UP

L54

M53

K53

L53

PCHTX_UART2

PCHRX_UART2

EN_PP3300_DX_LTE_SOC (38)

R327 *Short_0201

R328 *Short_0201

TP48

TP1

(ADO)

PCH_I2C_AUDIO_SCL_Q

PCH_I2C_AUDIO_SDA_Q

R395

2.2K_1%_2

D D

PCH_I2C_P_SENSOR_SCL(38)

PCH_I2C_P_SENSOR_SDA(38)

DBG_PCH_I2C_SCL(20)

DBG_PCH_I2C_SDA(20)

PP1800_SOC_A

CNVI_BRI_DT_R

CNVI_RGI_DT_R

C C

WLAN_CLKOUT_LCP(28)

R574 33_1%_2

R575 33_1%_2

Close To SoC

PP1800_SOC_A

B B

(TSN)

R100

2.2K_1%_2

R101

2.2K_1%_2

A A

PCH_I2C_TOUCHSCREEN_SDA

TN@PMDXB600UNE

R23 is for strapping low boot from SPI (GPIO_84)

R438 is for strapping high to set LPC to 1.8V mode (GPIO_83)

R311 is reserved for strapping high to force DNX FW

2

Q11B

TN@PMDXB600UNE

2

Q30B

5

CNVI_RF_RESET_L

3 4

61

PP3300_TOUCHSCREEN_DXPP1800_SOC_A

3 4

61

R1132 75K_1%_4

PP3300_TOUCHSCREEN_DXPP1800_SOC_A

5

Q11A

TN@PMDXB600UNE

5

Q30A

TN@PMDXB600UNE

R104

TN@1.5K_5%_2

PCH_I2C_TOUCHSCREEN_3V3_SCL (26)

R105

TN@1.5K_5%_2

PCH_I2C_TOUCHSCREEN_3V3_SDA (26)

load(GPIO_65)

(PEN)

(TPD)

PCH_I2C_TRACKPAD_SCLPCH_I2C_TOUCHSCREEN_SCL

PCH_I2C_TRACKPAD_SDA

4

PP1800_SOC_A PP3300_TRACKPAD_DX

R638

2.2K_1%_2

PP1800_SOC_A

R554

2.2K_1%_2

PMDXB600UNE

2

Q14B

PMDXB600UNE

2

Q15B

3 4

61

61

3 4

5

Q14A

PMDXB600UNE

PP3300_TRACKPAD_DX

5

Q15A

PMDXB600UNE

3

R555

1.5K_5%_2

R556

1.5K_5%_2

PCH_I2C_TRACKPAD_3V3_SCL (25)

PCH_I2C_TRACKPAD_3V3_SDA (25)

PCH_I2C_PEN_SCL

PP1800_SOC_A PP1800_PEN_DX

R110

2.2K_1%_2

5

3 4

Q35A PEN@PMDXB600UNE

R4Q *PEN@0_5%_2

PP1800_SOC_A PP1800_PEN_DX

R143

2.2K_1%_2

PCH_I2C_PEN_SDA

2

6 1

Q35B PEN@PMDXB600UNE

R5Q *PEN@0_5%_2

R155

PEN@1.5K_5%_2

PCH_I2C_PEN_1V8_SCL (25)

R160

2

Size Document Number R

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PEN@1.5K_5%_2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

SOC I2C/CNVI/UART/SPI

SOC I2C/CNVI/UART/SPI

SOC I2C/CNVI/UART/SPI

Wednesday, January 09, 2019

Wednesday, January 09, 2019

Wednesday, January 09, 2019

PCH_I2C_PEN_1V8_SDA (25)

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

1

10 45

10 45

10 45

ev

1A

1A

1A

5

R371

100K_5%_2

R373

*100K_5%_2

PP1800_SOC_A

R376

*100K_5%_2

R378

100K_5%_2

R382

100K_5%_2

R385

*100K_5%_2

R399

*100K_5%_2

DRAM_ID3

R402

100K_5%_2

(CPU)

DRAM_ID0

DRAM_ID1 DRAM_ID2

D D

PP3300_SOC_A

R276

R557

100K_5%_2

PP1050_VCCRAM_S

R56

R58

*68_1%_2

*169_1%_4

C C

R63

*84.5_1%_4

SUSPWRDNACK(18)

100K_5%_2

PLT_RST_L(12,18,21,23,28)

EC_PCH_PWR_BTN_ODL(12,18)

PCH_SLP_S0_L(9,33)

PCH_SLP_S3_L(33)

PCH_SLP_S4_L(33)

SYS_RST_ODL(12,18,21,22)

PCH_SUSCLK(28)

TP81

TP82

TP83

BT_DISABLE_L(28)

4

U4E

PCH_PMIC_I2C_SCL(33)

PCH_PMIC_I2C_SDA(33)

TP87

TP88

TP_AP_PMC_SPI_CLK

DRAM_ID0

DRAM_ID1

DRAM_ID2

DRAM_ID3

TP_AP_PMC_SPI_TX

PCH_SLP_S0_L

PCH_SLP_S3_L

PCH_SLP_S4_L

SUSPWRDNACK

PMU_BATLOW_L

TP_PCH_GPIO_78

TP_PCH_GPIO_77

TP_PCH_GPIO_76

DEBUG_OBS_PORT_A0

DEBUG_OBS_PORT_A1

R46

PMC_I2C_SCL

R48

PMC_I2C_SDA

L48

PMC_SPI_CLK

N48

PMC_SPI_FS0

N44

PMC_SPI_FS1

L49

PMC_SPI_FS2

L51

PMC_SPI_RXD

N49

PMC_SPI_TXD

D54

PMU_PLTRST

E54

PMU_PWRBTN

C52

PMU_SLP_S0

D51

PMU_SLP_S3

J49

PMU_SLP_S4

F54

SUSPWRDNACK

J48

PMU_BATLOW

C51

PMU_RSTBTN

G49

PMU_SUSCLK

E52

SUS_STAT

F55

SVID0_CLK

G53

SVID0_DATA

G54

SVID0_ALERT

D1

DEBUG_PORT_A0

D2

DEBUG_PORT_A1

A54

NC2

C54

NC11

1.8V

PMU set 3.3V

1.8V/3.3V

1.05V

3

Gemini lake (PMU/PMIC/RTC)

OSCIN

OSCOUT

RTC_X1

RTC_X2

INTRUDER

SOC_PWROK

RSM_RST

RTC_TEST

RTC_RST

THERMTRIP

PROCHOT

SKTOCC

NC15

NC16

NC14

NC10

NC17

NC3

NC4

NC1

NC5

NC6

NC7

NC8

NC9

B17

C17

PCH_OSCIN

U2

PCH_OSCOUT

T1

PCH_RTC_X1

D23

PCH_RTC_X2

F23

RTC_EXPAD

J23

H25

INTRUDER

EC_PCH_PWROK

D25

PCH_RSMRST_L

F27

PCH_RTEST_ODLPLT_RST_L

F25

PCH_RTCRST_ODL

D27

J53

J54

AG43

H53

AG44

H55

A4

BH1

A53

F37

BL2

BL3

BL53

C2

C3

R41

R735

*Short_0201

OSC_CLK_OUT_0

1.8V

iCLK

RTC

PMC

RTC is 3.3V

1.8V

Thermal

PMU

SVID

Spare

Misc

8 OF 13

OSC_CLK_OUT_1

VCC_RTC_EXTPAD

1.8V

2

EC_IN_RW_OD (21)

PCH_WP_OD (19)

EC_PCH_PWROK (18)

PCH_RSMRST_L (12,18)

THERMTRIP_L (33)

PCH_PROCHOT_ODL (18,37)

R46

100K_5%_2

PP3300_RTC

R8

100K_5%_2

C360

0.1u/10V_2

SEL BOM: 9H03280012

PCH_RTC_X2

PCH_RTC_X1

PCH_OSCOUT

PCH_OSCIN

Quanta suggested 20ppm/12.5pF

TXC/9H03200031

C2

2nd source:

18p/25V_2

EPSON/FC-135

SEL BOM: CS325-19.200MABJ-UT

Quanta suggested 20ppm/12pF

TXC/7V19200001

C1

2nd source:

15p/25V_2

Hosonic/E3FB19E0X0008E

Interquip/5YEA19200122SF50Q2

1

X2 32.768KHZ/20ppm/12.5pF

1 2

9H03200031

R45 10M_1%_2

X3

19.2MHZ/20ppm1/12pF

123

4

7V19200001

R722 200K_1%_2

C3

18p/25V_2

C4

15p/25V_2

PP3300_A

R190

100K_1%_2

3

PCH_SLP_S3_L SLP_S3

B B

Q56

2

PJE138K

1

PLT_RST_L

R191

1K_1%_2

3

Q57

2

0109_Q_added DNS resistor/cap on

PLT_RST_L for potential issue

PJE138K

1

R120Q

*100K_1%_2

C120Q

*1u/6.3V_2

PCH_RSMRST_L

R587

100K_1%_2

PCH_RSMRST_L

2

PCH_RSMRST_OD

3

Q80

PJE138K

1

PP3300_A

R508

499K_1%_2

C447

*1u/6.3V_2

CHECK RTCRST SIGNAL

PCH_RTEST_ODL

3

Q86

PJE138K

1

4

PP3300_RTC

R740

20K_1%_2

C582

1u/25V_4

PCH_SLP_S0_L

PCH_RSMRST_OD

312

Q79

PMZB670UPE

R516 *0_5%_2

PCH_RSMRST_OD

PCH_SLP_S3_LSLP_S0_L

R507

499K_1%_2

3

R517 *0_5%_2

312

Q81

PMZB670UPE

SLP_S3_L

R509

499K_1%_2C5

2

PCH_SLP_S4_L

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PCH_RSMRST_OD

SLP_S4_L

312

Q82

PMZB670UPE

R518 *0_5%_2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

SOC PMU/RTC/SVID/THERMAL/MISC

SOC PMU/RTC/SVID/THERMAL/MISC

SOC PMU/RTC/SVID/THERMAL/MISC

Wednesday, January 09, 2019

Wednesday, January 09, 2019

Wednesday, January 09, 2019

1

R510

499K_1%_2

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

11 45

11 45

11 45

1A

1A

1A

PP3300_RTC

R50

20K_1%_2

PCH_RTCRST_ODL

3

EC_PCH_RTCRST

A A

Q7

2

PJE138K

1

1u/25V_4

5

CHECK RTCRST SIGNAL

EC_PCH_RTCRST(18) SLP_S4_L (18,35)SLP_S3_L (18,35)SLP_S0_L (18)

EC_PCH_RTCRST

R739

100K_1%_2

2

(CPU)

D D

LAYOUT NOTE: PLACE THE R62, 65, 55, 57, R393 WITHIN 1" OF J5 MIPI60 CONNECTOR.

5

PP1800_SOC_A

R65

R393

51_1%_2

150_1%_2

TCK(20)

TDI(20)

TDO(20)

TMS(20)

TRST_L(20)

R55

R57

51_1%_2

*51_1%_2

CX_PRDY_L(20)

CX_PREQ_L(20)

PP1800_SOC_A

R397

150_1%_2

R62

51_1%_2

TP_GPIO5

PP1800_A PP3300_A

R391,R392,R341,R352 can't be

un-stuffed in MP even if removing

debugging related stuffs from MP

GPIO_81_DEBUG(10)

SYS_RST_ODL(11,18,21,22)

EC_PCH_PWR_BTN_ODL(11,18)

C C

PLT_RST_L(11,18,21,23,28)

PCH_RSMRST_L(11,18)

R340 1K_5%_2

R341 *Short_0201

R352 *Short_0201

R361 1K_5%_2

R379 *1K_5%_2

R380

*4.7K_5%_2

R391

1K_5%_2

R392

1K_5%_2

DBG_PMU_RSTBTN_L (20)

DBG_PMU_PWRBTN_L (20)

DBG_PMU_PLTRST_L (20)

DBG_RSMRST_L (20)

R394

51_1%_2

BOOT_HALT_L (20)

4

U4H

1.8V

JTAG

ITP

GPIO

AH53

AM53

AJ54

AL53

AL54

AK53

AH55

AJ53

JTAGX

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST

JTAG_PRDY

JTAG_PREQ

3

1.8V

1.8V/3.3V

1.8V

2

AG53

GPIO_8

AG54

GPIO_9

AE54

GPIO_10

AE53

GPIO_11

AD55

GPIO_12

AD53

GPIO_13

AC54

GPIO_14

AC53

GPIO_15

AB53

GPIO_16

AA49

GPIO_17

AC48

GPIO_18

AC46

GPIO_19

AE51

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

GPIO_25

GPIO_26

GPIO_27

GPIO_28

GPIO_29

GPIO_30

GPIO_31

GPIO_32

GPIO_33

GPIO_34

GPIO_35

GPIO_36

GPIO_37

GPIO_38

GPIO_39

GPIO_40

GPIO_41

GPIO_105

GPIO_134

GPIO_135

GPIO_136

GPIO_137

GPIO_138

GPIO_139

GPIO_140

GPIO_141

GPIO_142

GPIO_143

GPIO_144

GPIO_145

GPIO_146

GPIO_210

GPIO_212

GPIO_213

GPIO_214

CNVI_MFUART2_RXD_PTI_11

AE49

CNVI_MFUART2_TXD_PTI_12

AC51

CNVI_GNSS_PA_BLANKING_PTI_13

AC49

AA51

AA46

AE41

AE39

AE46

AE44

AC41

AC39

AC44

AC43

AA44

AA54

AA53

Y55

Y53

DBG_PTI_DATA_TRACE3_3

W54

DBG_PTI_DATA_TRACE3_4

W53

DBG_PTI_DATA_TRACE3_5

V53

L46

EC_AP_INT_ODL

H45

TRACKPAD_INT1_1V8_ODL

H47

PMIC_PCH_INT_1V8_ODL

L43

M43

H37

H43

J43

EC_PCH_WAKE_1V8_ODL

D43

TRACKPAD_INT2_1V8_ODL

F43

H41

PEN_EJECT

F39

PEN_EJECT

L41

F41

R558 *Short_0201

TP_GPIO210

H27

U43

TP_AP_GPIO213

U41

U39

TP69

1

DBG_PTI_CLK0 (20)

DBG_PTI_DATA_0 (20)

DBG_PTI_DATA_1 (20)

DBG_PTI_DATA_2 (20)

DBG_PTI_DATA_3 (20)

DBG_PTI_DATA_4 (20)

DBG_PTI_DATA_5 (20)

DBG_PTI_DATA_6 (20)

DBG_PTI_DATA_7 (20)

DBG_PTI_CLK1 (20)

DBG_PTI_DATA_8 (20)

DBG_PTI_DATA_9 (20)

DBG_PTI_DATA_10 (20)

DBG_PTI_DATA_14 (20)

DBG_PTI_DATA_15 (20)

DBG_PTI_CLK2 (20)

DBG_PTI_DATA_16 (20)

DBG_PTI_DATA_17 (20)

DBG_PTI_DATA_18 (20)

DBG_PTI_DATA_19 (20)

DBG_PTI_DATA_20 (20)

DBG_PTI_DATA_21 (20)

DBG_PTI_DATA_22 (20)

DBG_PTI_DATA_23 (20)

DCI_CLK_PTICLK3 (20)

DCI_DATA_PTITRACE3_0 (20)

DBG_PTI_DATA_TRACE3_1 (20)

DBG_PTI_DATA_TRACE3_2 (20)

TOUCHSCREEN_RST (26)

TP65

HP_INT_ODL (24)

PEN_PDCT_ODL (25)

PEN_INT_ODL (25)

PEN_RESET (25)

LTE_SAR_ODL (38)

TP49

TP74

EN_PP3300_TOUCHSCREEN (25,35)

TP68

TOUCHSCREEN_INT_ODL (26)

TP172

P_SENSOR_INT_L (38)

1226_Q_made R289 stuffed for no matter

internal PU is available or not

EC_AP_INT_ODL (18)

C85Q *10p/25V_2

PP1800_SOC_A

R289 100K_5%_2

EN_PP3300_CAMERA (35)

PEN_EJECT (25)

PEN_EJECT

PP1800_SOC_A

DBG_PTI_DATA_16

R362

1K_5%_2

B B

(PMC)

PMIC_PCH_INT_1V8_ODL

(CPU)

EC_PCH_WAKE_1V8_ODL

A A

R380 is reserved for strapping high (GPIO_81)

R877 is for strapping low to not allow eMMC as a boo

No extermal PU/PD on GPIO_28, using internal PD for allowing SPI as a boot source

5

PP1800_SOC_A

PP1800_SOC_A

R880

10K_2

R881

*10K_2

t source (GPIO_27)

R887 *Short_0201

R888 *Short_0201

4

PMIC_PCH_INT_ODL (33)

EC_PCH_WAKE_ODL (18)

R28973

20K_1%_2

EC_AP_INT_ODL

3

5 OF 13

R524 *Short_0201

TRACKPAD_INT_1V8_ODL(18,25)

CNVI_GNSS_PA_BLANKING_PTI_13

CNVI_MFUART2_RXD_PTI_11

CNVI_MFUART2_TXD_PTI_12

2

R531 *Short_0201

0102_Q_Changed R531 to a short pad

R14 *Short_0201

R16 *0_5%_2

R17 *Short_0201

R24 *0_5%_2

R25 *Short_0201

R61 *0_5%_2

TRACKPAD_INT1_1V8_ODL

TRACKPAD_INT2_1V8_ODLTRACKPAD_INT_1V8_ODL

Size Document Number R

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

SOC JTAG/GPIO/ITP

SOC JTAG/GPIO/ITP

SOC JTAG/GPIO/ITP

Wednesday, January 09, 2019

Wednesday, January 09, 2019

Wednesday, January 09, 2019

C86Q *10p/25V_2

CNVI_GNSS_PA_BLANKING (28)

DBG_PTI_DATA_13 (20)

CNVI_MFUART2_RXD (28)

DBG_PTI_DATA_11 (20)

CNVI_MFUART2_TXD (28)

DBG_PTI_DATA_12 (20)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

12 45

12 45

12 45

ev

1A

1A

1A

5

4

3

2

1

(CPU)

GLK ULT (GND)

D D

C C

B B

A12

A16

A20

A24

A28

A32

A36

A40

A44

A48

A51

AA12

AA13

AA15

AA17

AA21

AA23

AA25

AA27

AA35

AA43

AA48

AB1

AB3

AB55

AC8

AC13

AC23

AC25

AC27

AC29

AE18

AE23

AE25

AE27

AE43

AE48

AF1

AF3

AF4

AF6

AF8

AF9

AF11

AF12

AF14

AF16

AF18

AF23

AF25

AF29

AF40

AF42

U4K

A3

VSS6

A6

VSS13

VSS1

VSS2

VSS3

VSS4

VSS5

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS33

VSS28

VSS29

VSS30

VSS31

VSS32

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS49

VSS50

VSS61

VSS62

VSS63

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS51

VSS52

11 OF 13

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS64

VSS87

VSS65

VSS66

VSS67

VSS68

VSS77

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS78

VSS79

VSS80

VSS90

VSS97

VSS98

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS88

VSS89

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS108

VSS110

VSS107

VSS109

AF44

AF45

AF47

AF48

AF50

AF52

AF53

AF55

AG20

AL21

AG25

AG29

AG35

AG38

AJ8

AJ13

AJ18

AJ25

AJ29

AJ36

AJ38

AJ39

AJ44

AK1

AK3

AK55

AL3

AL7

AL8

AL10

AL12

AL13

AL15

AL17

AL20

AL25

AL29

AL39

AL41

AL43

AL44

AL46

AL51

AM1

AM21

AM23

AM25

AM29

AM31

AM38

AM55

AN3

AN8

AN10

AN46

AN48

AN49

AN51

AN53

AP23

AP27

AP28

AP29

AP33

AP35

AR2

AR7

AR10

AR12

AR17

AR39

AR44

AR46

AR49

AR54

AT23

AT33

AU3

AU10

AU28

AU46

AU53

AV15

AV17

AV23

AV25

AV31

AV33

AV39

AV41

AW2

AW5

AW10

AW28

AW46

AW51

AW54

AY13

AY15

AY28

AY41

AY43

B55

BA27

BA29

BB1

BB28

BB55

BC5

B2

U4M

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_124

VSS_130

VSS_121

VSS_122

VSS_123

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_131

VSS_132

VSS_135

VSS_133

VSS_134

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_147

VSS_150

VSS_146

VSS_148

VSS_149

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_178

12 OF 13

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_179

VSS_187

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_189

VSS_188

VSS_190

VSS_194

VSS_191

VSS_192

VSS_193

VSS_195

VSS_199

VSS_196

VSS_197

VSS_198

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_215

VSS_213

VSS_214

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

BC11

BC17

BC19

BC21

BC23

BC25

BC31

BC33

BC35

BC37

BC39

BC41

BC45

BC51

BD9

BD15

BD19

BD21

BD28

BD35

BD37

BD47

BE3

BE28

BE53

BF9

BF19

BF37

BF47

BG1

BG6

BG28

BG50

BG55

BH11

BH13

BH17

BH19

BH23

BH25

BH28

BH31

BH33

BH37

BH39

BH41

BH45

BJ2

BJ15

BJ19

BJ25

BJ28

BJ31

BJ37

BJ41

AL23

BJ54

BK1

BK17

BK21

BK35

BK39

BK55

BL5

BL8

BL10

BL14

BL24

BL28

BL32

BL42

BL46

BL48

BL51

C12

C16

C28

C36

D21

D28

D41

D45

D55

E28

E50

E55

G28

H13

H15

H21

H23

H28

H33

H39

F21

F31

J27

J33

J41

J45

U4L

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS17

VSS19

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS18

C1

VSS20

VSS21

VSS22

VSS23

VSS24

D6

VSS30

D9

VSS31

VSS25

VSS26

VSS27

VSS28

VSS29

VSS32

VSS33

VSS34

F1

VSS35

F4

VSS38

VSS36

VSS37

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

J8

VSS52

VSS47

VSS48

VSS49

VSS50

13 OF 13

VSS51

VSS53

VSS55

VSS54

VSS56

VSS59

VSS60

VSS61

VSS57

VSS58

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS74

VSS73

VSS75

VSS77

VSS78

VSS80

VSS81

VSS82

VSS84

VSS85

VSS93

VSS95

VSS96

VSS83

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS94

VSS97

VSS98

VSS99

VSS100

VSS101

VSS76

VSS79

J51

K1

K3

K28

K55

L5

L7

L8

L19

L33

M15

M25

M28

M35

M41

N12

N28

N46

N51

P21

P55

R8

R28

T27

T38

U13

V27

V38

V55

W2

W3

W5

W7

W8

W10

W39

W41

W43

W44

W46

W48

W49

W51

Y21

Y23

Y25

Y27

Y31

T3

U3

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

5

4

3

2

Wednesday, January 09, 2019

PROJECT :

SOC GROUND

SOC GROUND

SOC GROUND

ZAK_ZAN_ZAP_ZAQ

13 45

13 45

13 45

1

1A

1A

1A

5

4

3

2

1

SHOULD CONSIDER SPLITTING THE RAILS FOR NOISE ISOLATION

(CPU)

D D

PP1100_VDDQ_SOC

PP1100_VDDQ_IOA

PP1800_SOC_A

PP1200_SOC_A

C C

AP18

VDDQ1

AP21

VDDQ2

AP36

VDDQ3

AP38

VDDQ4

AT18

VDDQ5

AT20

VDDQ6

AT21

VDDQ7

AT35

VDDQ8

AT36

VDDQ9

AT38

VDDQ10

BA13

VDDQ11

BA15

VDDQ12

BA25

VDDQ13

BA31

VDDQ14

BA41

VDDQ15

BA43

VDDQ16

AP25

VCCIOA1

AP31

VCCIOA2

AT25

VCCIOA3

AT27

VCCIOA4

AT28

VCCIOA5

AT29

VCCIOA6

AT31

VCCIOA7

T21

VCC_1P8V_A3

T23

VCC_1P8V_A4

T25

VCC_1P8V_A5

V21

VCC_1P8V_A6

V23

VCC_1P8V_A7

V25

VCC_1P8V_A8

AJ23

VCC_1P8V_A2

AG23

VCC_1P8V_A1

AC21

VDD2_1P2_MPH Y1

AE20

VDD2_1P2_MPH Y2

AE21

VDD2_1P2_MPH Y3

AF20

VDD2_1P2_MPH Y4

AF21

VDD2_1P2_MPH Y5

AC18

VDD2_1P2_AUD_ ISH1

AC20

VDD2_1P2_AUD_ ISH2

AW12

VDD2_1P2_DSI_C SI

AL36

VDD2_1P2_GLM 1

AL38

VDD2_1P2_GLM 2

AP20

VDD2_1P2_GLM 4

AM20

VDD2_1P2_GLM 3

AL18

VDD2_1P2_PLL 1

AM18

VDD2_1P2_PLL 2

AA18

VDD2_1P2_VNNAON1

AA20

VDD2_1P2_VNNAON2

AG18

VDD2_1P2_USB 2

AJ20

VDD2_1P2_USB 3

U4G

VDD2(1.2V)

VDD2(1.2V)

DDR IO

3A

DDR IO logic

VDD1(1.8V)

0.4A

VDD1(1.8V)

3A

10 OF 13

4.5A

VCCRAM(1.05V)

RTC

0.15A

VDD3(3.3V)

VCCRAM_1P053

VCCRAM_1P054

VCCRAM_1P057

VCCRAM_1P058

VCCRAM_1P059

VCCRAM_1P0510

VCCRAM_1P0511

VCCRAM_1P0512

VCCRAM_1P0513

VCCRAM_1P0514

VCC_1P05_INT2

VCC_1P05_INT1

VCC_1P05_INT3

VCCRAM_1P051

VCCRAM_1P052

VCCRAM_1P055

VCCRAM_1P056

VCCRAM_1P0515

VCCRAM_1P0516

VCCRTC_3P3 V

VCC_3P3V_A2

VCC_3P3V_A5

VCC_3P3V_A1

VCC_3P3V_A3

VCC_3P3V_A4

VCC_3P3V_A6

VCC_3P3V_A7

VCC_3P3V_A8

VCC_3P3V_A9

AC33

AC35

AE33

AE35

AE36

AE38

AF27

AF28

AF36

AF38

AG51

AG49

AJ51

AA36

AA38

AC36

AC38

Y36

Y38

P15

AJ21

U17

AG21

T18

T20

V18

V20

Y18

Y20

PP1050_VCCRAM_S

Gemini (POWER)

PP3300_RTC

C342

PP3300_SOC_A

PP3300_SOC_A

1u/16V_4

U4F

AA28

VCC_VCG1

AA29

VCC_VCG2

AA31

VCC_VCG3

AA33

VCC_VCG4

AC28

VCC_VCG5

AC31

VCC_VCG6

AE28

VCC_VCG7

C411

1u/16V_4

AE29

AE31

AF31

AF33

AG31

AG33

AJ31

AJ33

AJ35

AL31

AL33

AL35

AM33

AM35

AM36

D31

D33

D37

D39

P39

P41

T28

T29

T31

T33

T35

T36

V28

V29

V31

V33

V35

V36

Y28

Y29

Y33

Y35

VCC_VCG8

VCC_VCG9

VCC_VCG10

VCC_VCG11

VCC_VCG12

VCC_VCG13

VCC_VCG14

VCC_VCG15

VCC_VCG16

VCC_VCG17

VCC_VCG18

VCC_VCG19

VCC_VCG20

VCC_VCG21

VCC_VCG22

VCC_VCG23

VCC_VCG24

VCC_VCG25

VCC_VCG26

VCC_VCG27

VCC_VCG28

VCC_VCG29

VCC_VCG30

VCC_VCG31

VCC_VCG32

VCC_VCG33

VCC_VCG34

VCC_VCG35

VCC_VCG36

VCC_VCG37

VCC_VCG38

VCC_VCG39

VCC_VCG40

VCC_VCG41

VCC_VCG42

VCC_VCG43

VCC_VCG44

GLM+ module, GF x

25A

SA,D-unit,GMM,P CIe,DE,fabrics,

&USB controller s

NON CPU Core AO N DOMAIN

9 OF 13

4A

VCC_VCG_SENSE

VSS_VCG_SENSE

VNN_SENSE

VNN_VSS_SENSE

SHOULD CONSIDER SPLITTING THE RAILS FOR NOISE ISOLATION

PPVAR_VNN

Sense

VNN1

VNN2

VNN3

VNN4

VNN5

VNN6

VNN7

VNN8

VNN9

VNN10

VNN11

VNN12

VNN13

VNN14

VNN15

VNN16

PPVAR_VNNPPVAR_VCCGI

AF35

AG27

AG28

AG36

AG46

AG48

AJ27

AJ28

AJ46

AJ48

AL27

AL28

AL48

AL49

AM27

AM28

NC_VNNAON

AJ49

NC1

AW44

NC2

BH55

NC3

NC4

AG41

AG39

AJ41

AJ43

BL54

PPVAR_VCCGI_SENSE_P

PPVAR_VCCGI_SENSE_N

PPVAR_VNN_SENSE_P

PPVAR_VNN_SENSE_N

TP123

TP89

TP90

TP91

PPVAR_VCCGI_SENSE_P (33)

PPVAR_VCCGI_SENSE_N (33)

PPVAR_VNN_SENSE_P (33)

R12

C295

0.01u/10V_2

C296

0.01u/10V_2

100_1%_2

R13

100_1%_2

PPVAR_VCCGI

R476

100_1%_2

R477

100_1%_2

3

C298

0.01u/10V_2

C297

0.01u/10V_2

B B

PPVAR_VNN_SENSE_P

PPVAR_VNN_SENSE_N

C293

0.01u/10V_2

PLEASE THESE COMPONENTS NEAR THE PMIC FB PINS

PPVAR_VCCGI_SENSE_P

PPVAR_VCCGI_SENSE_N

C294

0.01u/10V_2

A A

5

4

PP1200_A

R461 *Short_0805

PP1050_S

R464 *Short_0603

PP1100_VDDQ_S

R465 *Short_0805

2

PP1200_SOC_A

PP1050_VCCRAM_S

PP1100_VDDQ_SOC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

Wednesday, January 09, 2019

Date: Sheet of

Wednesday, January 09, 2019

PROJECT :

SOC POWER

SOC POWER

SOC POWER

1

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

ZAK_ZAN_ZAP_ZAQ

14 45

14 45

14 45

1A

1A

1A

Loading...

Loading...