Page 1

5

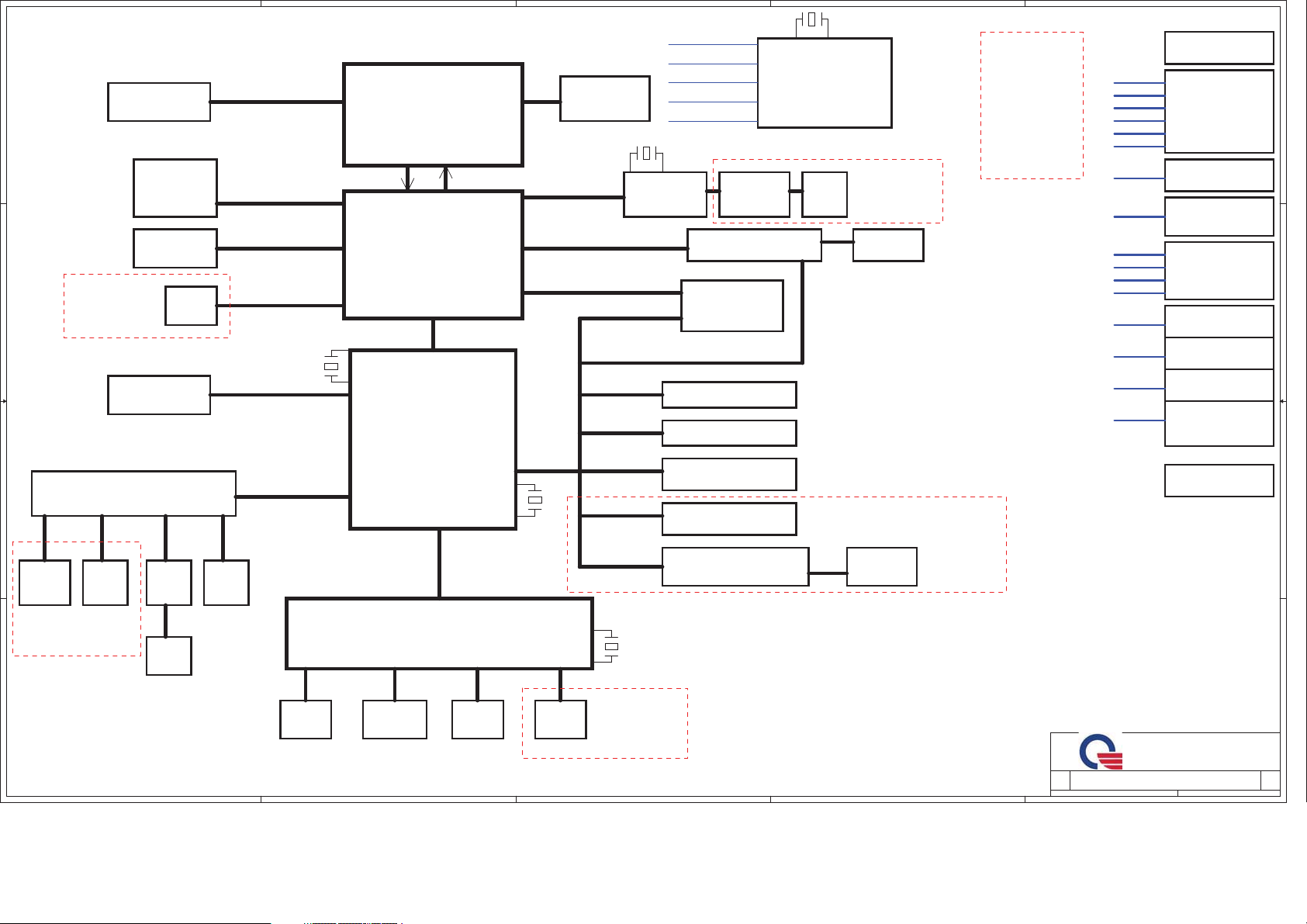

ZA8 Block Diagram

PG 19

Int. MIC

Digital

PG 19

DDR II 667 MHz

Channel A

16bit DDR2

LVDS(1ch)

R/G/B

SATA0

Azalia

HT1 800MHz

X'TAL

25MHz

D D

DDRII-SODIMM1

PG 8

Side port

memory

PG 9

LED Panel

(11.6'',1366x768)

PG 18

C C

CRT D/B

CRT

PG 18

SATA - HDD

(SSD option)

PG 22

Azalia Audio Codec

B B

H.P

JACK

PG 19 PG 19 PG 19

MIC

JACK

ALC272

AMP

G1453L

4

AMD S1g1

RS690E

465 FCBGA

21mm*21mm

A_LINK (X4)

23mm*23mm

LPC

TF20/S.C 1.2G/12W

PG 4,5,6,7

PG 9,10,11,12

SB600

PG 13,14,15,16,17

4W

8W

PCIE-2

PCIE-1 (Reserve)

PCIE-3

USB2.0

X'TAL

32.768KHz

Thermal Sensor

G781

PG 6

Port 7

Port 5

Port 3

Port 6

Port 0

Port 1/2

Port 8

3

HOST 200MHz

PCIE 100MHz

USB 48MHz

REF 14.318MHz

HTREF 66MHz

X'TAL

25MHz

LAN(10/100)

RTL8103EL

PG 20

3G Card

Mini Card (WLAN)

CCD

BT

USB2.0 I/O Ports X1

USB2.0 I/O Ports X2

Card Reader controller

RTS5159

CLOCK GENERATOR

Silego:SLG84605TTR

IDT:ICS951462

Transformer

PG 21

PG 21

PG 18

PG 23

PG 22

PG 22

PG 22

X'TAL

14.318MHz

2

PG 3

RJ45

LAN D/B

SIM CARD

PG 21

Card reader D/B

4 in 1

Connector

LED D/B

WLAN/3G SW

BT SW

WLAN/WiMax LED

3G LED

BT LED

BAT LED

PG 23

+3VPCU

+3V_S5

+3VSUS

+3V

+5VPCU

+5V

CPU_CORE

+NB_CORE

+1.8VSUS

+1.8V

+SMDDR_VTERM

+SMDDR_VREF

+2.5V

+1.5V

+1.2V_S5

+1.2V

1

CHARGER

ISL88731

3V/5V

ISL6237

CPU CORE

ISL6264A

NB CORE

UP6111AQDD

DDR

TPS51116

+2.5V

RT9025

+1.5V

RT9025

+1.2V_S5

RT9025

+1.2V

G9334+AO4466

Thermal

Protection

PG 25

PG 26

PG 27

PG 28

PG 29

PG 30

PG 30

PG 30

PG 30

PG 31

EC

Card reader D/B

Speaker

PG 19

A A

5

FAN

(PWM)

WPCE775L

Keyboard

4

Flash

ROM

PG 24 PG 23PG 23PG 6

SPI

PG 24

Touch

Pad

PS/2

X'TAL

32.768KHz

TP D/B

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet

Date: Sheet

2

Date: Sheet

PROJECT :

ZA8

ZA8

ZA8

1A

1A

135Friday, May 08, 2009

135Friday, May 08, 2009

1

135Friday, May 08, 2009

1A

of

of

of

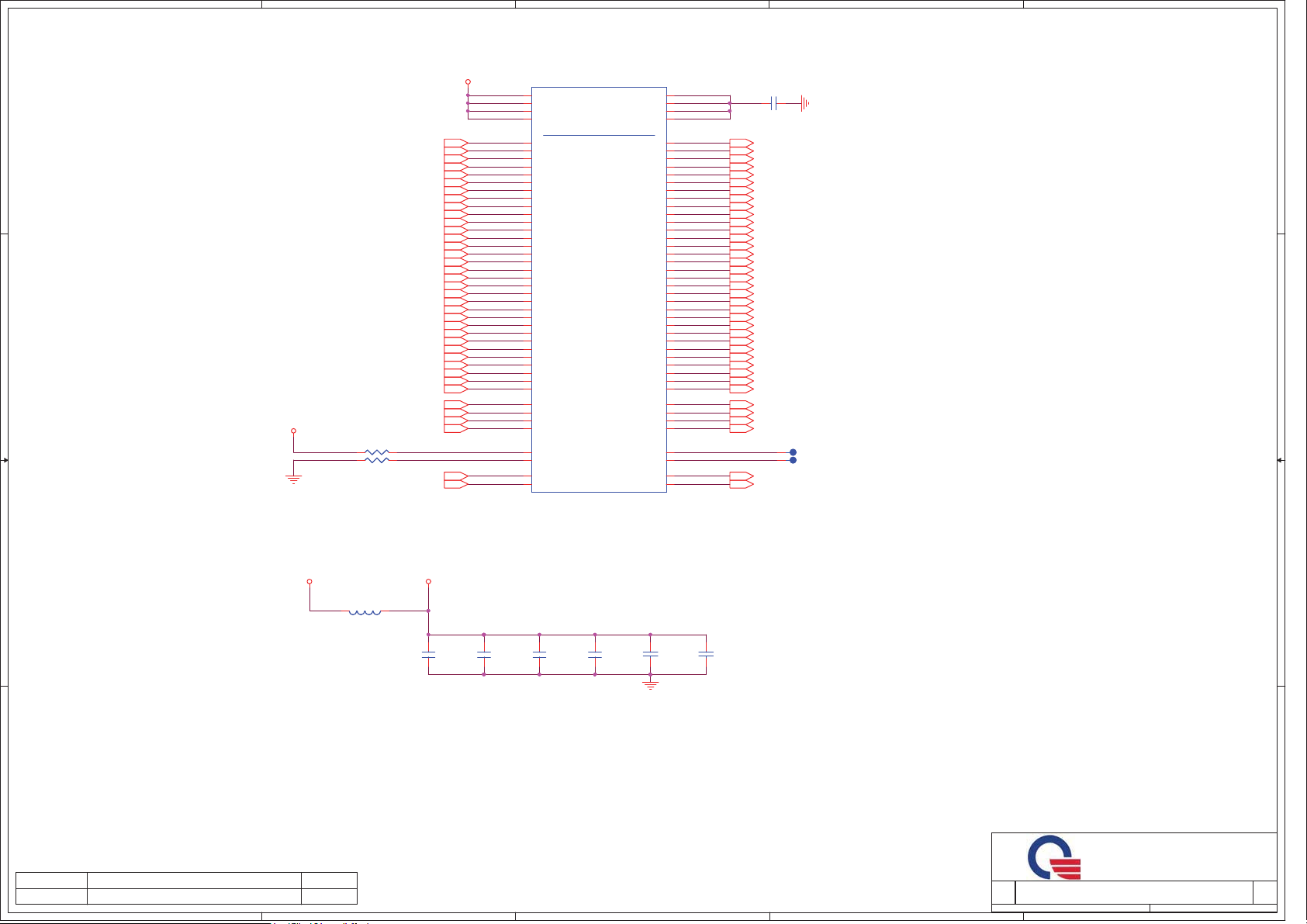

Page 2

5

4

3

2

1

ZA8 Power On Sequence

From AC,Battery VIN

D D

From PWM

From Power Button

From EC

+5VPCU +3VPCU

SYS_HWPG(PCU)

NBSWON#

S5_ON

+3V_S5

From EC

From EC

From SB

From SB

From EC

+1.2V_S5

RSMRST#

DNBSWON#

PCIE_WAKE#

SUSB#,SUSC#

SUSON

30ms

100ms

10ms

+3VSUS +1.8VSUS +SMDDR_VREF +SMDDR_VTERM

From PWM

From EC

C C

From PWM

From EC

HWPG_1.8V (SUS)

MAINON

+5V +3V +2.5V +1.8V +1.5V

HWPG_1.5V,HWPG_2.5V

VRON

10ms

10ms

CPU_CORE

From PWM

From EC

CPU_COREPG

+1.2V_ON

+1.2V_ON

+1.2V

From PWM

HWPG_1.2V

+NB_CORE

From PWM

From EC

B B

From SB

From SB

From SB

From SB

HWPG_1.2V_NB

HWPG

ECPWROK

NB_PWRGD

SB_PWRGD

CPU_PWRGD

PLTRST#

LDT_RST#

LDT_STOP#

100ms

-22ms~500ms

47ms~66ms

71ms~73ms

1.9ms~2.1ms

*Note: EC will sampling SUSB# &

SUSC# every 5ms.

Items Function Name Description

1

3G Module 3G@

2

HDT debug function HDT@

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

BOM naming rule

AMD SB600 SMBUS Table

CLK GEN RAM Mini Card (WLAN)

SB600 SDATA0/SCLK0(+3V)

SB600 SDATA1/SCLK1(+3V_S5)

Power Plane

A A

MOS CKT

5

V

+3V +3V

Reserve

VV

+3V

ReserveReserve

4

EC775 SDATA1/SCLK1(+3VPCU)

EC775 SDATA2/SCLK2(+3VPCU)

EC775 SDATA3/SCLK3(+3VPCU)

EC775 SDATA4/SCLK4(+3VPCU)

Power Plane

MOS CKT

3

EC SMBUS Table

Battery CPU thermal Sensor EC EEPROM

V

V

+3VPCU +3V +3VPCU

XX

X

2

V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SYSTEM INFORMATION

SYSTEM INFORMATION

SYSTEM INFORMATION

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

1

ZA8

ZA8

ZA8

1A

1A

235Friday, May 08, 2009

235Friday, May 08, 2009

235Friday, May 08, 2009

1A

of

of

of

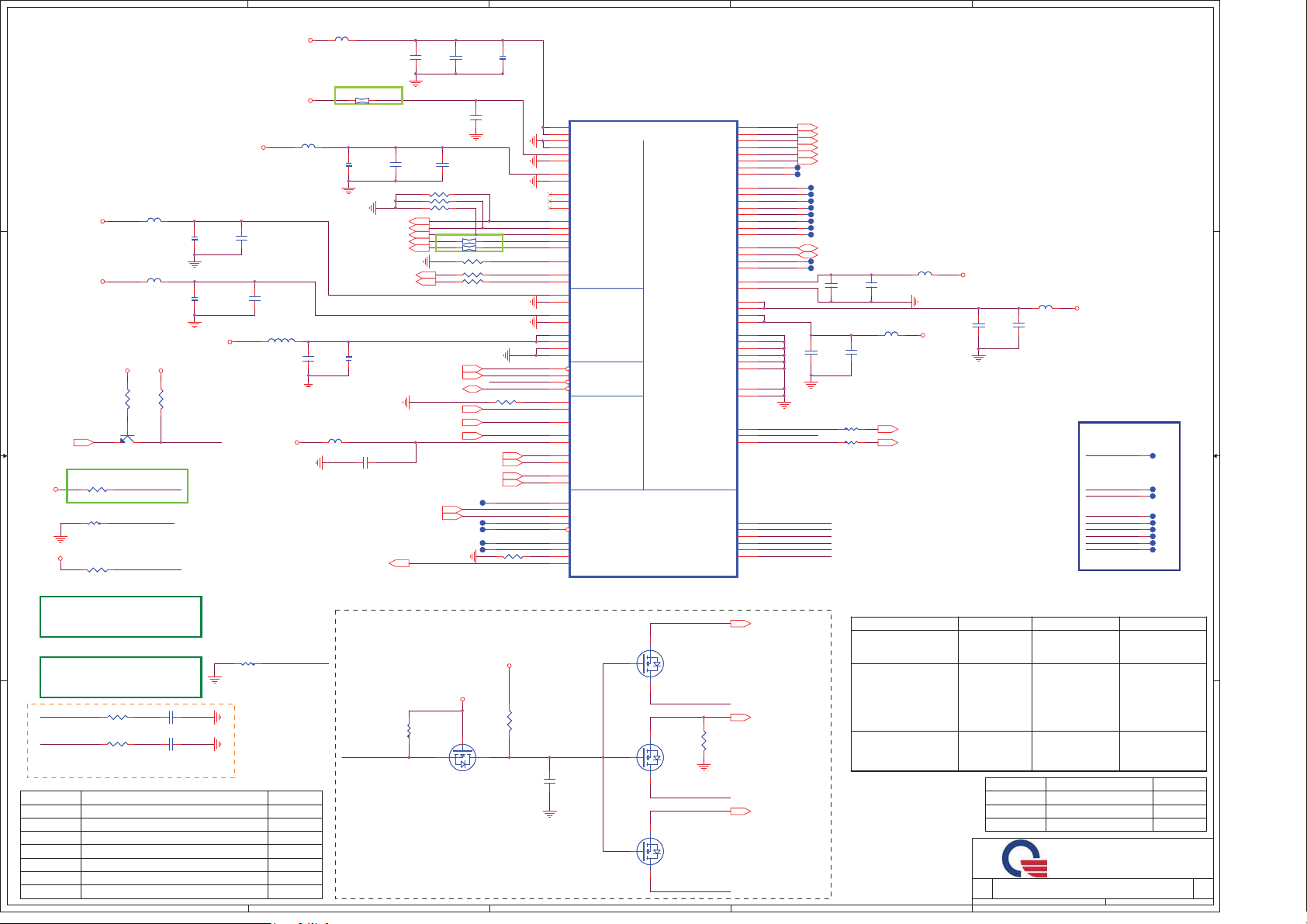

Page 3

CLK_GEN(CLK)

5

4

3

2

1

L25

L25

+3V

BK1608HS600-T/0.5A/60ohm_6

BK1608HS600-T/0.5A/60ohm_6

D D

BK1608HS600-T/0.5A/60ohm_6

BK1608HS600-T/0.5A/60ohm_6

L26

+3V

+3V

C C

L26

BK1608HS600-T/0.5A/60ohm_6

BK1608HS600-T/0.5A/60ohm_6

L24

L24

CLK_VDD

R96

R96

10K_4

10K_4

CLK_VDD

C240

C240

1u/6.3V_4

1u/6.3V_4

C226

C226

2.2u/6.3V_6

2.2u/6.3V_6

C160 22p/50V_4C160 22p/50V_4

14.318MHZ_20pF

14.318MHZ_20pF

C141 22p/50V_4C141 22p/50V_4

Parallel Resonance Cryst al

&ORFN*HQ,&

B B

EXT CLK FREQUENCY SELECT TABLE(MHZ)

FS0

CPU

Hi-Z

X

180.00

220.00

100.00

133.33

200.00

SRCCLK

[2:1]

100.00

100.00

100.00

100.00

100.00

100.00

100.00

5

FS1

FS2

A A

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 1

HTT

Hi-Z

X/3 X/6

60.00

36.56

66.66

66.66

66.66

PCI

Hi-Z

30.00

73.12

33.33

33.33

33.33 48.00

Put Decoupling Caps close to Clock Gen. power pin

C249

C252

C252

22u/6.3V_8

22u/6.3V_8

C241

C241

*0.1u/10V_4

*0.1u/10V_4

Y2

Y2

USB

48.00

48.00

48.00

48.00

48.00

48.00

CLK_VDD_USB

C229

C229

*0.1u/10V_4

*0.1u/10V_4

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

C144

C144

0.1u/10V_4

0.1u/10V_4

CLK_VDD_REF

21

R100

R100

*1M_4

*1M_4

Ioh = 5 * Iref

(2.32mA)

Voh = 0.71V @ 60 ohm

COMMENT

C247

C247

0.1u/10V_4

0.1u/10V_4

SCLK0(8,14,21)

SDATA0(8,14,21)

C249

C250

C250

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

CLK_VDD

CLK_VDD_USB

CLK_VDD_REF

CLK_XIN

CLK_XOUT

T66T66

SCLK0

SDATA0

R163

R163

475/F_4

475/F_4

CLKREQA# CONTROL SRC5,6,7

CLKREQB# CONTROL SRC2,3,4 ATIG3

CLKREQC# CONTROL SRC0,1 ATIG0,1,2

IDT: AL951462K07 ; ICS951462

Silego: AL084605K05 ; SLG84605TTR

Normal Turion/Sempron operation

4

C142

C142

0.1u/10V_4

0.1u/10V_4

B-test

U5

U5

54

VDDCPU

14

VDD_SRC1

23

VDD_SRC2

28

VDD_SRC3

44

VDD_SRC4

5

VDD_48

39

VDD_ATIG

2

VDD_REF

60

VDDHTT

53

GND_CPU

15

GND_SRC1

22

GND_SRC2

29

GND_SRC3

45

GND_SRC4

8

GND_48

38

GND_ATIG

1

GND_REF

58

GNDHTT

3

XIN

4

XOUT

11

RESET_IN#

61

NC

9

SMBCLK

10

SMBDAT

48

IREF

SLG84605TTR

SLG84605TTR

B-test

C248

C248

0.1u/10V_4

0.1u/10V_4

C251

C251

0.1u/10V_4

0.1u/10V_4

VDDA

GNDA

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

SRCCLKT6

SRCCLKC6

ATIGCLKT0

ATIGCLKC0

ATIGCLKT1

ATIGCLKC1

ATIGCLKT2

ATIGCLKC2

ATIGCLKT3

ATIGCLKC3

SRCCLKT5

SRCCLKC5

SRCCLKT4

SRCCLKC4

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT0

SRCCLKC0

SRCCLKT1

SRCCLKC1

SRCCLKT7

SRCCLKC7

CLKREQA#

CLKREQB#

CLKREQC#

48MHz_1

48MHz_0

FS1/REF1

FS0/REF0

FS2/REF2

HTTCLK0

CLK_48M_2_R

C146

C146

*10p/50V_4

*10p/50V_4

CLK_VDDA

C143

C143

0.1u/10V_4

0.1u/10V_4

CLK_VDDA

50

49

CPUCLK_EXT_R

56

CPUCLK#_EXT_R

55

52

T137T137

51

T65T65

SBLINK_CLKP_R

16

SBLINK_CLKN_R

17

NBSRC_CLKP_R

41

NBSRC_CLKN_R

40

37

36

35

34

30

31

18

19

20

21

GPP_CLK1P_R

24

GPP_CLK1N_R

25

GPP_CLK2P_R

26

GPP_CLK2N_R

27

GPP_CLK3P_R

47

GPP_CLK3N_R

46

43

42

GPP_CLK0P_R

12

GPP_CLK0N_R

13

CLKREQA#

57

CLKREQB#

32

CLKREQC#

33

CLK_48M_1_R

7

CLK_48M_2_R

6

63

64

62

59

NB_OSCIN_R

HTREFCLK_R

C266

C266

*10p/50V_4

*10p/50V_4

Add 10p for EMI issue (Suggestion by Seligo)

R140 47.5/F_4R140 47.5/F_4

R139 47.5/F_4R139 47.5/F_4

3

RP3 33X2RP3 33X2

1

1

RP13 33X2RP13 33X2

3

T134T134

T136T136

T135T135

T138T138

T50T50

T52T52

3

RP2

RP2

1

3

RP1

RP1

1

1

RP14

RP14

3

T133T133

T68T68

3

1

RP4 33X2RP4 33X2

T73T73

B-test

T160T160

R95 33_4R95 33_4

C200

C200

*10p/50V_4

*10p/50V_4

3

R135 33_4R135 33_4

R119 33_4R119 33_4

R159 33_4R159 33_4

C215

C215

*10p/50V_4

*10p/50V_4

SB_OSCIN_R

C242

C242

0.1u/10V_4

0.1u/10V_4

4

2

2

4

4

33X2

33X2

2

4

33X2

33X2

2

2

*33X2

*33X2

4

4

2

BK1608HS600-T/0.5A/60ohm_6

BK1608HS600-T/0.5A/60ohm_6

L28

L28

C261

C261

10u/10V_8

10u/10V_8

R148 *49.9/F_4R148 *49.9/F_4

USBCLK (14)

CLK_VDD

R121

R121

R127

R127

10K_4

10K_4

10K_4

10K_4

R164

R164

49.9/F_4

49.9/F_4

+3V

R144 261/F_4R144 261/F_4

R149 *49.9/F_4R149 *49.9/F_4

R84 49.9/F_4R84 49.9/F_4

R83 49.9/F_4R83 49.9/F_4

R82 49.9/F_4R82 49.9/F_4

R128

R128

10K_4

10K_4

R131 *0_4R131 *0_4

R120 *0_4R120 *0_4

R130 *0_4R130 *0_4

R76 49.9/F_4R76 49.9/F_4

R85 49.9/F_4R85 49.9/F_4

R77 49.9/F_4R77 49.9/F_4

SB_OSCIN (14)

NB_OSC (11)

HTREFCLK (11)

2

R151 49.9/F_4R151 49.9/F_4

R150 49.9/F_4R150 49.9/F_4

R74 49.9/F_4R74 49.9/F_4

0+]

0+]

0+]

CPUCLKP (6)

CPUCLKN (6)

R75 49.9/F_4R75 49.9/F_4

SBLINK_CLKP (11)

SBLINK_CLKN (11)

NBSRC_CLKP (11)

NBSRC_CLKN (11)

SBSRCCLKP (13)

SBSRCCLKN (13)

CLK_PCIE_LAN (20)

CLK_PCIE_LAN# (20)

CLK_PCIE_3G (21)

CLK_PCIE_3G# (21)

CLK_PCIE_WLAN (21)

CLK_PCIE_WLAN# (21)

CLKREQA#

B-test

CLKREQB#

B-test

CLKREQC#

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

R97

R97

*10K_4

*10K_4

R178

R178

*10K_4

*10K_4

R165

R165

*10K_4

*10K_4

+3V

B-test

R93 *Short_4R93 *Short_4

C-test

1

R177 *Short_4R177 *Short_4

B-test

1

R174 *0_4R174 *0_4

+3V

Q10

Q10

*RHU002N06

*RHU002N06

2

3

+3V

Q9

Q9

*RHU002N06

*RHU002N06

2

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

1

3

CLKREQ_WLAN# (21)

CLKREQ_LAN# (20)

CLKREQ_3G# (21)

ZA8

ZA8

ZA8

335Friday, May 08, 2009

335Friday, May 08, 2009

335Friday, May 08, 2009

of

of

of

1A

1A

1A

Page 4

5

4

3

2

1

(CPU)

4

VLDT_RUN

20mil 20mil

D D

HT_CADIN15_P(9)

HT_CADIN15_N(9)

HT_CADIN14_P(9)

HT_CADIN14_N(9)

HT_CADIN13_P(9)

HT_CADIN13_N(9)

HT_CADIN12_P(9)

HT_CADIN12_N(9)

HT_CADIN11_P(9)

HT_CADIN11_N(9)

HT_CADIN10_P(9)

HT_CADIN10_N(9)

HT_CADIN9_P(9)

HT_CADIN9_N(9)

HT_CADIN8_P(9)

HT_CADIN8_N(9)

HT_CADIN7_P(9)

HT_CADIN7_N(9)

HT_CADIN6_P(9)

HT_CADIN6_N(9)

HT_CADIN5_P(9)

HT_CADIN5_N(9)

HT_CADIN4_P(9)

HT_CADIN4_N(9)

HT_CADIN3_P(9)

HT_CADIN3_N(9)

C C

VLDT_RUN

HT_CADIN2_P(9)

HT_CADIN2_N(9)

HT_CADIN1_P(9)

HT_CADIN1_N(9)

HT_CADIN0_P(9)

HT_CADIN0_N(9)

HT_CLKIN1_P(9)

HT_CLKIN1_N(9)

HT_CLKIN0_P(9)

HT_CLKIN0_N(9)

R36 51/F_4R36 51/F_4

R35 51/F_4R35 51/F_4

HT_CTLIN0_P(9)

HT_CTLIN0_N(9)

U14AU14A

D4

D3

D2

D1

N5

P5

M3

M4

L5

M5

K3

K4

H3

H4

G5

H5

F3

F4

E5

F5

N3

N2

L1

M1

L3

L2

J1

K1

G1

H1

G3

G2

E1

F1

E3

E2

J5

K5

J3

J2

P3

P4

N1

P1

VLDT_A3

VLDT_A2

VLDT_A1

VLDT_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Athlon 64 S1

Processor Socket

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

T5

R5

R2

R3

C405

C405

4.7u/6.3V_6

4.7u/6.3V_6

HT_CADOUT15_P (9)

HT_CADOUT15_N (9)

HT_CADOUT14_P (9)

HT_CADOUT14_N (9)

HT_CADOUT13_P (9)

HT_CADOUT13_N (9)

HT_CADOUT12_P (9)

HT_CADOUT12_N (9)

HT_CADOUT11_P (9)

HT_CADOUT11_N (9)

HT_CADOUT10_P (9)

HT_CADOUT10_N (9)

HT_CADOUT9_P (9)

HT_CADOUT9_N (9)

HT_CADOUT8_P (9)

HT_CADOUT8_N (9)

HT_CADOUT7_P (9)

HT_CADOUT7_N (9)

HT_CADOUT6_P (9)

HT_CADOUT6_N (9)

HT_CADOUT5_P (9)

HT_CADOUT5_N (9)

HT_CADOUT4_P (9)

HT_CADOUT4_N (9)

HT_CADOUT3_P (9)

HT_CADOUT3_N (9)

HT_CADOUT2_P (9)

HT_CADOUT2_N (9)

HT_CADOUT1_P (9)

HT_CADOUT1_N (9)

HT_CADOUT0_P (9)

HT_CADOUT0_N (9)

HT_CLKOUT1_P (9)

HT_CLKOUT1_N (9)

HT_CLKOUT0_P (9)

HT_CLKOUT0_N (9)

HT_CPU_CTLOUT1_PHT_CTLIN1_P

HT_CPU_CTLOUT1_NHT_CTLIN1_N

HT_CTLOUT0_P (9)

HT_CTLOUT0_N (9)

T23T23

T26T26

B B

A A

Power name

VLDT_A/B

Description Voltage

HyperTransport I/O ring power supply

5

+1.2V

L12

L12

FBMJ3216HS800-T/4A/80ohm_1206

FBMJ3216HS800-T/4A/80ohm_1206

1.2V

VLDT_RUN

C89

C89

4.7u/6.3V_6

4.7u/6.3V_6

4

C91

C91

4.7u/6.3V_6

4.7u/6.3V_6

C401

C401

0.22u/10V_4

0.22u/10V_4

C403

C403

0.22u/10V_4

0.22u/10V_4

12

3

C404

C404

180p/50V_4

180p/50V_4

12

C402

C402

180p/50V_4

180p/50V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

PROJECT :

TURION 64 HT I/F

TURION 64 HT I/F

TURION 64 HT I/F

ZA8

ZA8

ZA8

1A

1A

1A

435Friday, May 08, 2009

435Friday, May 08, 2009

435Friday, May 08, 2009

of

of

1

of

Page 5

5

(CPU)

Processor DDR2 Memory Interface

+1.8VSUS

D D

R56

C114

C114

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor Socket

C430

C430

0.22u/10V_4

0.22u/10V_4

R56

2K/F_4

2K/F_4

R55

R55

2K/F_4

2K/F_4

15-20mil

CPU_M_VREF

C115

VTT_SENSE

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

C115

0.1u/10V_4

0.1u/10V_4

W17

Y10

AE10

AF10

V19

J22

V22

T19

Y26

J24

W24

U23

H26

J23

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

C434

C434

0.22u/10V_4

0.22u/10V_4

1000p/50V_4

1000p/50V_4

U14B

U14B

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

PLACE THEM CLOSE TO

CPU WITHIN 1"

+1.8VSUS

R302

R302

39.2/F_4

39.2/F_4

1 2

C C

R303

R303

39.2/F_4

39.2/F_4

1 2

B B

A A

C431

C431

4.7u/6.3V_6

4.7u/6.3V_6

C427

C427

4.7u/6.3V_6

4.7u/6.3V_6

T38T38

M_ZN

M_ZP

M_A_CS#3(8)

M_A_CS#2(8)

M_A_CS#1(8)

M_A_CS#0(8)

M_CKE1(8)

M_CKE0(8)

M_A_A[0..15](8)

M_A_BS#2(8)

M_A_BS#1(8)

M_A_BS#0(8)

M_A_RAS#(8)

M_A_CAS#(8)

M_A_WE#(8)

C437

C433

C433

4.7u/6.3V_6

4.7u/6.3V_6

C437

4.7u/6.3V_6

4.7u/6.3V_6

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

+SMDDR_VTERM

C425

C425

0.22u/10V_4

0.22u/10V_4

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

4

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

K26

T26

U26

U24

V26

U22

C423

C423

0.22u/10V_4

0.22u/10V_4

M_CLKOUT0

C441

C441

1.5p/50V_4

1.5p/50V_4

M_CLKOUT0#

M_CLKOUT1

C440

C440

1.5p/50V_4

1.5p/50V_4

M_CLKOUT1#

+SMDDR_VTERM

C421

C421

1000p/50V_4

1000p/50V_4

20-200mil

M_CLKOUT1 (8)

M_CLKOUT1# (8)

M_CLKOUT0 (8)

M_CLKOUT0# (8)

M_ODT1 (8)

M_ODT0 (8)

C429

C429

1000p/50V_4

1000p/50V_4

C435

C435

1000p/50V_4

1000p/50V_4

3

C436

C436

1000p/50V_4

1000p/50V_4

C438

C438

180p/50V_4

180p/50V_4

C428

C428

180p/50V_4

180p/50V_4

C416

C416

180p/50V_4

180p/50V_4

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

AD12

AC16

AE22

AB26

E25

A22

B16

A12

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

F26

E26

A24

A23

D16

C16

C12

B12

C439

C439

180p/50V_4

180p/50V_4

U14C

U14C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

2

DDR: DATA

DDR: DATA

Athlon 64 S1

Processor Socket

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

1

M_A_DQ[0..63] (8)

To SODIMM socket A (near)

M_A_DM[0..7] (8)

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS[0..7] (8)

M_A_DQS#[0..7] (8)

5

Power name

VTT

Description Voltage

VTT Power

5

0.9V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

PROJECT :

TURION 64 DDRII I/F

TURION 64 DDRII I/F

TURION 64 DDRII I/F

ZA8

ZA8

ZA8

1A

1A

1A

535Friday, May 08, 2009

535Friday, May 08, 2009

535Friday, May 08, 2009

of

of

1

of

Page 6

5

(CPU)

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 300-ȍ (±5%) pulldown to VSS.

R283 *300_4R283 *300_4

+1.8VSUS

R278 *300_4R278 *300_4

CPU_SIC(13)

CPU_SID(13)

D D

CPUCLKP(3)

CPUCLKN(3)

CPU_PWRGD(13)

LDT_STOP#(11,13)

LDT_RST#(13)

C C

R277 *0_4R277 *0_4

R281 *0_4R281 *0_4

C422 3900p/50V_4C422 3900p/50V_4

C417 3900p/50V_4C417 3900p/50V_4

R280

R280

680_4

680_4

R297

R297

680_4

680_4

R309

R309

169/F_6

169/F_6

R274 300_4R274 300_4

CPU_SIC_R

CPU_SID_R

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

B-test

R289

R289

680_4

680_4

CPU_COREPG(24,27)

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_HT_RESET#

H_THERMTRIP#

CPU Thermal monitor(THM)

U12

U12

2ND_MBCLK(24)

2ND_MBDATA(24)

+3V

R266

B B

THERM_ALERT#(14)

R266

*8.2K_4

*8.2K_4

+3V

3

R268 10K_4R268 10K_4

+3V

B-test

R269

R269

2

*10K_4

*10K_4

THERM_ALERT#_R

1

Q26*2N7002E-LF Q26*2N7002E-LF

THER_OVERT#

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

G781P8

G781P8

$''5(66+

CPU FAN(THM)

B-test

+5V

+3V +3V

A A

THER_OVERT# THER_OVERT#_B

R228 10K_4R228 10K_4

CPUFAN#(24)

R235 *Short_4R235 *Short_4

FAN_PWM_EC

C-test

5

R230

R230

10K_4

10K_4

FAN_PWM_E

Q18

Q18

2

MMBT3904

MMBT3904

1 3

R220 *Short_6R220 *Short_6

R223

R223

10K_4

10K_4

2

1 3

Q17

Q17

MMBT3904

MMBT3904

+5V

4

+1.8VSUS

3

Q24

Q24

R264

FDV301N

FDV301N

R265

R265

10K_4

10K_4

R262 *0_6R262 *0_6

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

+3V

C410

C410

0.1u/10V_4

0.1u/10V_4

C407

C407

2200p/50V_4

2200p/50V_4

TH_FAN_POWER

C354

C354

*0.01u/16V_4

*0.01u/16V_4

4

R264

*10K_4

*10K_4

2

1

2

1 3

Q25

Q25

MMBT3904

MMBT3904

1

VCC

2

DXP

3

DXN

5

GND

<check list>

Layout Note:Routing 10:10 mils and away

from noise source with ground gard

FANSIG(24)

R224

R224

10K_4

10K_4

FAN_PWM_CN

D18

D18

*BAS316

*BAS316

R267 100K_6R267 100K_6

SB_THERMTRIP# (14)

SYS_SHDN# (26,31)

R300 *300_4R300 *300_4

R286 300_4R286 300_4

R42 *1K/F_4R42 *1K/F_4

R51 510/F_4R51 510/F_4

R45 300_4R45 300_4

R290 *300_4R290 *300_4

R293 *300_4R293 *300_4

R298 *300_4R298 *300_4

R46 *300_4R46 *300_4

R50 *300_4R50 *300_4

R49 *300_4R49 *300_4

R52 510/F_4R52 510/F_4

R53 300_4R53 300_4

R54 300_4R54 300_4

H_THERMDA

H_THERMDC

+3V

R221

R221

10K_4

10K_4

CN10

CN10

FAN CONN

FAN CONN

B-test

Update footprint

3

2

1

ATHLON Control and Debug

+2.5V

PBY201209T-300Y-N/4A/30ohm_8

PBY201209T-300Y-N/4A/30ohm_8

L17

L17

C93

C93

*100u/6.3V_3528

*100u/6.3V_3528

VLDT_RUN

VCCSENSE(27)

VSSSENSE(27)

+1.8VSUS

6

345

2

1

H_PROCHOT#

R43

R43

300_4

300_4

T33T33

T31T31

R44

R44

*2.2K_4

*2.2K_4

3

VDDA_RUN

C94

C94

C106

C106

0.22u/10V_4

0.22u/10V_4

4.7u/6.3V_6

4.7u/6.3V_6

CPU_HT_RESET#

T35T35

CPU_ALL_PWROK

T121T121

CPU_LDTSTOP#

T122T122

CPU_SIC_R

CPU_SID_R

R37 44.2/F_4R37 44.2/F_4

R38 44.2/F_4R38 44.2/F_4

place them to CPU within 1"

T29T29

T30T30

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

T120T120

CPU_TEST16_BP2

T39T39

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

H_THERMDC

H_THERMDA

CPU_RSVD_MA0_CLK3_P

T44T44

CPU_RSVD_MA0_CLK3_N

T130T130

CPU_RSVD_MA0_CLK0_P

T43T43

CPU_RSVD_MA0_CLK0_N

T129T129

CPU_RSVD_MB0_CLK3_P

T48T48

CPU_RSVD_MB0_CLK3_N

T47T47

CPU_RSVD_MB0_CLK0_P

T45T45

CPU_RSVD_MB0_CLK0_N

T46T46

+1.8VSUS

2

1

+1.8VSUS+1.8VSUS

R41

R41

*10K_4

*10K_4

2

13

Q3 *MMBT3904Q3 *MMBT3904

12

+3V

R47

R47

*HDT@2K/F_4

*HDT@2K/F_4

3

Q4

Q4

*HDT@FDV301N

*HDT@FDV301N

+3V

R40

R40

*4.7K_4

*4.7K_4

C96

C96

3300p/50V_4

3300p/50V_4

CPU_HTREF1

CPU_HTREF0

FD1

FD1

*HDT@BAS316

*HDT@BAS316

CPU to HDT RESET#CPU_HT_RESET#

C-test

F10

AF4

AF5

W9

G10

AA9

AC9

AD9

AF9

H10

AA7

AC8

AA6

W7

W8

AB6

P20

P19

N20

N19

R26

R25

P22

R22

F8

F9

B7

A7

P6

R6

F6

E6

Y9

A9

A8

E9

E8

G9

C2

D7

E7

F7

C7

C3

Y6

U14D

U14D

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

THERMTRIP_L

PROCHOT_L

VID5

VID4

VID3

VID2

VID1

VID0

CPU_PRESENT_L

PSI_L

DBREQ_L

TDO

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

2

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

MISC

MISC

AMD NPT S1 SOCKET Processor Socket

AMD_PROCHOT (13,24)

H_THERMTRIP#

AF6

H_PROCHOT#

AC7

A5

C6

A6

A4

C5

B5

CPU_PRESENT#

AC6

A3

PSI_L is a Power Status Indicator signal. This signal is asserted

when the processor is in a low powerstate. PSI_L should be

connected to the power supply controller, if the controller

supports “skipmode, or diode emulation mode”. PSI_L is asserted by

the processor during the C3 and S1 states.

CPU_DBREQ#

E10

CPU_TDO

AE9

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

CPU_TEST24_SCANCLK1

AE7

CPU_TEST23_TSTUPD

AD7

CPU_TEST22_SCANSHIFTEN

AE8

CPU_TEST21_SCANEN

AB8

CPU_TEST20_SCANCLK2

AF7

CPU_TEST28_H_PLLCHRZ_P

J7

CPU_TEST28_L_PLLCHRZ_N

H8

CPU_TEST27_SINGLECHAIN

AF8

CPU_TEST26_BURNIN#

AE6

K8

C4

CPU_MA_RESET#

H16

CPU_MB_RESET#

B18

CPU_RSVD_VIDSTRB1

B3

CPU_RSVD_VIDSTRB0

C1

CPU_RSVD_VDDNB_FB_P

H6

CPU_RSVD_VDDNB_FB_N

G6

CPU_RSVD_CORE_TYPE

D5

R24

W18

R23

AA8

H18

H19

+1.8VSUS

R65 *220_4R65 *220_4

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

+1.8VSUS+1.8VSUS

R276

R276

300_4

300_4

PSI# (27)

R48 80.6/F_4R48 80.6/F_4

PLACE IT CLOSE TO CPU WITHIN 1"

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

T36T36

T28T28

T37T37

T41T41

T125T125

T119T119

T118T118

T25T25

T27T27

T32T32

IF no use which Net

need pull-up or down

R60 *220_4R60 *220_4

R59 220_4R59 220_4

R61 *220_4R61 *220_4

HDT CONNECTOR

+1.8VSUS

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

C126 *0.1u/10V_4C126 *0.1u/10V_4

Power name

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Filtered PLL supply voltage

VDDA

R62 *220_4R62 *220_4

R263

R263

300_4

300_4

H_VID5 (27)

H_VID4 (27)

H_VID3 (27)

H_VID2 (27)

H_VID1 (27)

H_VID0 (27)

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

Description

TURION 64 CTRL & DEBUG

TURION 64 CTRL & DEBUG

TURION 64 CTRL & DEBUG

6

CPU to HDT RESET#

25

KEY

KEY

CN5

CN5

*HDT CONN

*HDT CONN

Voltage

2.5V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZA8

ZA8

ZA8

of

of

of

635Friday, May 08, 2009

635Friday, May 08, 2009

1

635Friday, May 08, 2009

1A

1A

1A

Page 7

5

4

3

2

1

PROCESSOR POWER AND GROUND(CPU)

7

D D

U14F

U14F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

CPU_CORE CPU_CORE

C C

B B

A1

AC4

AD2

M10

N11

R11

U11

U13

U14E

U14E

VDD1

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

K10

VDD9

K12

VDD10

K14

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

L11

VDD15

L13

VDD16

M2

VDD17

M6

VDD18

M8

VDD19

VDD20

N7

VDD21

N9

VDD22

VDD23

P8

VDD24

P10

VDD25

R4

VDD26

R7

VDD27

R9

VDD28

VDD29

T2

VDD30

T6

VDD31

T8

VDD32

T10

VDD33

T12

VDD34

T14

VDD35

U7

VDD36

U9

VDD37

VDD38

VDD39

V6

VDD40

V8

VDD41

V10

VDD42

POWER

POWER

Athlon 64 S1

Processor Socket

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

+1.8VSUS

A26

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

D11

D13

D15

D17

D19

D21

D23

D25

H21

H23

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

VSS63

VSS64

J4

VSS65

GROUND

GROUND

Athlon 64 S1

Processor Socket

Athlon 64 S1g1

uPGA638

Top View

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

+

+

PC41

PC41

*330u/2V_7343

*330u/2V_7343

+1.8VSUS

+1.8VSUS

BOTTOMSIDE DECOUPLING

CPU_CORE

C102

CPU_CORE

+1.8VSUS

C112

C112

0.22u/10V_4

0.22u/10V_4

C117

C117

10u/10V_8

10u/10V_8

C100

C100

10u/6.3V_6

10u/6.3V_6

C110

C110

0.22u/10V_4

0.22u/10V_4

C116

C116

10u/10V_8

10u/10V_8

C105

C105

10u/6.3V_6

10u/6.3V_6

C109

C109

0.01u/25V_4

0.01u/25V_4

C119

C119

0.22u/10V_4

0.22u/10V_4

C103

C103

10u/6.3V_6

10u/6.3V_6

C108

C108

180p/50V_4

180p/50V_4

C118

C118

0.22u/10V_4

0.22u/10V_4

C102

10u/6.3V_6

10u/6.3V_6

C97

C97

10u/6.3V_6

10u/6.3V_6

CPU_CORE

C104

C104

10u/6.3V_6

10u/6.3V_6

For EMI request.

C111

C111

0.1u/10V_4

0.1u/10V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

C140

C157

C157

4.7u/6.3V_6

4.7u/6.3V_6

C175

C175

0.01u/25V_4

0.01u/25V_4

C147

C147

4.7u/6.3V_6

4.7u/6.3V_6

C162

C162

180p/50V_4

180p/50V_4

C182

C182

4.7u/6.3V_6

4.7u/6.3V_6

C179

C179

180p/50V_4

180p/50V_4

C140

4.7u/6.3V_6

4.7u/6.3V_6

C186

C186

0.22u/10V_4

0.22u/10V_4

C164

C164

0.22u/10V_4

0.22u/10V_4

C177

C177

0.22u/10V_4

0.22u/10V_4

C176

C176

0.22u/10V_4

0.22u/10V_4

C152

C152

0.01u/25V_4

0.01u/25V_4

C101

C101

10u/6.3V_6

10u/6.3V_6

C113

C113

0.1u/10V_4

0.1u/10V_4

C158

C158

0.22u/10V_4

0.22u/10V_4

C187

C187

180p/50V_4

180p/50V_4

C99

C99

10u/6.3V_6

10u/6.3V_6

C170

C170

0.22u/10V_4

0.22u/10V_4

C98

C98

10u/6.3V_6

10u/6.3V_6

A A

Power name Description Voltage

VDD

VDDIO

AF1

Core power supply

DDR SDRAM I/O ring power supply

5

1.05V

1.8V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

PROJECT :

TURION 64 PWR & GND

TURION 64 PWR & GND

TURION 64 PWR & GND

ZA8

ZA8

ZA8

1A

1A

1A

735Friday, May 08, 2009

735Friday, May 08, 2009

735Friday, May 08, 2009

of

of

1

of

Page 8

5

(DDR)

201

M_A_A[0..15](5)

D D

SA1_A

SA0_A

C-test

SA_A : '0' ,'0'

M_A_BS#0(5)

M_A_BS#1(5)

M_A_BS#2(5)

M_A_DM[0..7](5)

C C

M_A_DQS[0..7](5)

M_A_DQS#[0..7](5)

M_CLKOUT0(5)

M_CLKOUT0#(5)

M_CLKOUT1(5)

M_CLKOUT1#(5)

M_CKE0(5)

M_CKE1(5)

M_A_RAS#(5)

M_A_CAS#(5)

M_A_WE#(5)

M_A_CS#0(5)

M_A_CS#1(5)

+3V

2.2u/10V_8

2.2u/10V_8

C190 0.1u/10V_4C190 0.1u/10V_4

M_ODT0(5)

M_ODT1(5)

C218

C218

SDATA0(3,14,21)

SCLK0(3,14,21)

1 2

MVREF_DIM

B B

A A

+1.8VSUS MVREF_DIM

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_CLKOUT0

M_CLKOUT0#

M_CLKOUT1

M_CLKOUT1#

SA0_A

SA1_A

SDATA0

SCLK0

C224 0.1u/10V_4C224 0.1u/10V_4

MVREF_DIM

C219

C219

0.1u/10V_4

0.1u/10V_4

5

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14

84

A15

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

202

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

GND PAD0

GND PAD1

SPD Address:0xA0

(H=4.0)

STD

59

B-test

103

111

104

112

117

VDD8

VDD7

VDD9

VDD10

SO-DIMM

SO-DIMM

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

127

122

121

118

CN17

CN17

DQ0

DQ1

DQ2

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

DDR2 SODIMM-S

DDR2 SODIMM-S

132

128

4

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

50

69

83

120

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

4

+1.8VSUS

M_A_DQ1

M_A_DQ5

M_A_DQ2

M_A_DQ3

M_A_DQ0

M_A_DQ4

M_A_DQ7

M_A_DQ6

M_A_DQ12

M_A_DQ8

M_A_DQ10

M_A_DQ14

M_A_DQ13

M_A_DQ9

M_A_DQ15

M_A_DQ11

M_A_DQ21

M_A_DQ17

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ19

M_A_DQ22

M_A_DQ16

M_A_DQ29

M_A_DQ28

M_A_DQ31

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ27

M_A_DQ30

M_A_DQ32

M_A_DQ36

M_A_DQ37

M_A_DQ35

M_A_DQ33

M_A_DQ38

M_A_DQ34

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ46

M_A_DQ44

M_A_DQ45

M_A_DQ43

M_A_DQ47

M_A_DQ55

M_A_DQ54

M_A_DQ50

M_A_DQ51

M_A_DQ53

M_A_DQ48

M_A_DQ49

M_A_DQ52

M_A_DQ56

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ61

M_A_DQ63

M_A_DQ62

T71T71

T61T61

T131T131

M_A_DQ[0..63] (5)

+1.8VSUS

M_A_CS#2 (5)

M_A_CS#3 (5)

+SMDDR_VREF +1.8VSUS

R126

R126

*0_6

*0_6

MVREF_DIM

C199

C199

1u/6.3V_4

1u/6.3V_4

R122

R122

1K/F_4

1K/F_4

R125

R125

1K/F_4

1K/F_4

3

M_CKE0(5)

M_CKE1(5)

M_A_CS#1(5)

M_ODT1(5)

M_A_WE#(5)

M_A_CAS#(5)

M_A_CS#3(5)

M_ODT0(5)

M_A_RAS#(5)

M_A_BS#1(5)

M_A_A[0..15](5)

C324

C324

*0.1u/10V_4

*0.1u/10V_4

M_A_BS#2(5)

M_A_CS#2(5)

M_A_BS#0(5)

M_A_A10(5)

M_A_CS#0(5)

M_A_A13(5)

C323

C323

*0.1u/10V_4

*0.1u/10V_4

C298

C298

*0.1u/10V_4

*0.1u/10V_4

M_A_A10

M_A_A13

M_A_A0

M_A_A2

M_A_A4

M_A_A6

M_A_A15

M_A_A14

M_A_A9

M_A_A12

M_A_A3

M_A_A5

M_A_A1

M_A_A8

M_A_A7

M_A_A11

C321

C321

*0.1u/10V_4

*0.1u/10V_4

*10u/10V_8C327 *10u/10V_8C327

*10u/10V_8C328 *10u/10V_8C328

10u/10V_8C326 10u/10V_8C326

10u/10V_8C329 10u/10V_8C329

0.1u/10V_4C194 0.1u/10V_4C194

0.1u/10V_4C305 0.1u/10V_4C305

0.1u/10V_4C304 0.1u/10V_4C304

0.1u/10V_4C197 0.1u/10V_4C197

0.1u/10V_4C193 0.1u/10V_4C193

0.1u/10V_4C299 0.1u/10V_4C299

0.1u/10V_4C302 0.1u/10V_4C302

0.1u/10V_4C306 0.1u/10V_4C306

0.1u/10V_4C301 0.1u/10V_4C301

0.1u/10V_4C308 0.1u/10V_4C308

0.1u/10V_4C307 0.1u/10V_4C307

0.1u/10V_4C300 0.1u/10V_4C300

0.1u/10V_4C195 0.1u/10V_4C195

0.1u/10V_4C196 0.1u/10V_4C196

+1.8VSUS

2

R133 47_4R133 47_4

R166 47_4R166 47_4

RP6 0404-47X2RP6 0404-47X2

1 2

3 4

RP7 0404-47X2RP7 0404-47X2

1 2

3 4

RP19 0404-47X2RP19 0404-47X2

1 2

3 4

RP15 0404-47X2RP15 0404-47X2

1 2

3 4

RP12 0404-47X2RP12 0404-47X2

1 2

3 4

RP8 0404-47X2RP8 0404-47X2

1 2

3 4

RP18 0404-47X2RP18 0404-47X2

1 2

3 4

RP17 0404-47X2RP17 0404-47X2

1 2

3 4

RP16 0404-47X2RP16 0404-47X2

1 2

3 4

RP21 0404-47X2RP21 0404-47X2

1 2

3 4

RP9 0404-47X2RP9 0404-47X2

1 2

3 4

RP11 0404-47X2RP11 0404-47X2

1 2

3 4

RP10 0404-47X2RP10 0404-47X2

1 2

3 4

RP20 0404-47X2RP20 0404-47X2

1 2

3 4

C322

C322

*0.1u/10V_4

*0.1u/10V_4

C325

C325

*0.1u/10V_4

*0.1u/10V_4

+SMDDR_VTERM

+SMDDR_VTERM

+SMDDR_VTERM

1

8

+1.8VSUS

0.1u/10V_4C202 0.1u/10V_4C202

0.1u/10V_4C206 0.1u/10V_4C206

0.1u/10V_4C203 0.1u/10V_4C203

0.1u/10V_4C205 0.1u/10V_4C205

0.1u/10V_4C204 0.1u/10V_4C204

0.1u/10V_4C297 0.1u/10V_4C297

0.1u/10V_4C309 0.1u/10V_4C309

0.1u/10V_4C303 0.1u/10V_4C303

0.1u/10V_4C277 0.1u/10V_4C277

0.1u/10V_4C220 0.1u/10V_4C220

0.1u/10V_4C290 0.1u/10V_4C290

0.1u/10V_4C222 0.1u/10V_4C222

0.1u/10V_4C221 0.1u/10V_4C221

0.1u/10V_4C223 0.1u/10V_4C223

0.1u/10V_4C276 0.1u/10V_4C276

0.1u/10V_4C275 0.1u/10V_4C275

Reserve for EMI

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

PROJECT :

DDRII SODIMM X 1

DDRII SODIMM X 1

DDRII SODIMM X 1

ZA8

ZA8

ZA8

1A

1A

835Friday, May 08, 2009

835Friday, May 08, 2009

835Friday, May 08, 2009

1

1A

of

of

of

Page 9

5

4

3

2

1

(CLG)

U10A

AC21

AB22

AB20

AA20

AA19

AA25

AA24

AB23

AA23

AB24

AB25

AC24

AC25

U10A

R19

R18

R21

R22

U22

U21

U18

U19

W19

W20

Y19

T24

R25

U25

U24

V23

U23

V24

V25

W21

W22

Y24

W25

P24

P25

A24

C24

RS690E

RS690E

Power rail (RS690)

+NB_CORE

+1.2V

D D

C C

+1.8V

+3.3V

Measured

value

3A

0.6A

0.07A

0.13A

CRB spec

2.5A

0.7A

0.05A

0.3A

VDDHT_PKG

HT_CADOUT15_P(4)

HT_CADOUT15_N(4)

HT_CADOUT14_P(4)

HT_CADOUT14_N(4)

HT_CADOUT13_P(4)

HT_CADOUT13_N(4)

HT_CADOUT12_P(4)

HT_CADOUT12_N(4)

HT_CADOUT11_P(4)

HT_CADOUT11_N(4)

HT_CADOUT10_P(4)

HT_CADOUT10_N(4)

HT_CADOUT9_P(4)

HT_CADOUT9_N(4)

HT_CADOUT8_P(4)

HT_CADOUT8_N(4)

HT_CADOUT7_P(4)

HT_CADOUT7_N(4)

HT_CADOUT6_P(4)

HT_CADOUT6_N(4)

HT_CADOUT5_P(4)

HT_CADOUT5_N(4)

HT_CADOUT4_P(4)

HT_CADOUT4_N(4)

HT_CADOUT3_P(4)

HT_CADOUT3_N(4)

HT_CADOUT2_P(4)

HT_CADOUT2_N(4)

HT_CADOUT1_P(4)

HT_CADOUT1_N(4)

HT_CADOUT0_P(4)

HT_CADOUT0_N(4)

HT_CLKOUT1_P(4)

HT_CLKOUT1_N(4)

HT_CLKOUT0_P(4)

HT_CLKOUT0_N(4)

HT_CTLOUT0_P(4)

HT_CTLOUT0_N(4)

R261 49.9/F_4R261 49.9/F_4

R32 49.9/F_4R32 49.9/F_4

HT_RXCALN HT_TXCALN

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALP

HT_RXCALN

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

C25

D24

HT_TXCALPHT_RXCALP

HT_CADIN15_P (4)

HT_CADIN15_N (4)

HT_CADIN14_P (4)

HT_CADIN14_N (4)

HT_CADIN13_P (4)

HT_CADIN13_N (4)

HT_CADIN12_P (4)

HT_CADIN12_N (4)

HT_CADIN11_P (4)

HT_CADIN11_N (4)

HT_CADIN10_P (4)

HT_CADIN10_N (4)

HT_CADIN9_P (4)

HT_CADIN9_N (4)

HT_CADIN8_P (4)

HT_CADIN8_N (4)

HT_CADIN7_P (4)

HT_CADIN7_N (4)

HT_CADIN6_P (4)

HT_CADIN6_N (4)

HT_CADIN5_P (4)

HT_CADIN5_N (4)

HT_CADIN4_P (4)

HT_CADIN4_N (4)

HT_CADIN3_P (4)

HT_CADIN3_N (4)

HT_CADIN2_P (4)

HT_CADIN2_N (4)

HT_CADIN1_P (4)

HT_CADIN1_N (4)

HT_CADIN0_P (4)

HT_CADIN0_N (4)

HT_CLKIN1_P (4)

HT_CLKIN1_N (4)

HT_CLKIN0_P (4)

HT_CLKIN0_N (4)

HT_CTLIN0_P (4)

HT_CTLIN0_N (4)

R33 100/F_4R33 100/F_4

(CLG)

VMA_MA0

VMA_MA1

VMA_MA2

VMA_MA3

VMA_MA4

VMA_MA5

VMA_MA6

VMA_MA7

VMA_MA8

VMA_MA9

VMA_MA10

VMA_MA11

VMA_MA12

T12T12

VMA_BA0

VMA_BA1

VMA_BA2

VMA_RAS#

VMA_CAS#

VMA_WE#

B B

A A

VMA_CS0#

VMA_CKE

VMA_ODT

VMA_CLK0

VMA_CLK0#

VMA_DM0

VMA_DM1

VMA_WDQS0

VMA_RDQS0

VMA_WDQS1

VMA_RDQS1

DESIGN NOTE:THE FOLLOWING DEBUG

POINTS SHOULD BE PROVIDED.

U10F

U10F

W12

MEM_A0(NC)

AD10

MEM_A1(NC)

AB12

MEM_A2(NC)

AB11

MEM_A3(NC)

W14

MEM_A4(NC)

AB15

MEM_A5(NC)

AB14

MEM_A6(NC)

AE9

MEM_A7(NC)

AA12

MEM_A8(NC)

AC9

MEM_A9(NC)

AE10

MEM_A10( NC)

Y14

MEM_A11( NC)

AD9

MEM_A12( NC)

AA11

MEM_A13( NC)

AC11

MEM_BA0( NC)

AE11

MEM_BA1( NC)

AD11

MEM_BA2( NC)

AA15

MEM_RASb(NC)

Y15

MEM_CASb(NC)

AC14

MEM_WEb(NC )

V12

MEM_CSb(NC)

AD12

MEM_CKE( NC)

Y9

MEM_ODT (NC)

W15

MEM_CKP( NC)

V15

MEM_CKN(NC)

AC16

MEM_DM0(NC)

AD19

MEM_DM1/DVO_D8(DVO_D8)

AE17

MEM_DQS0P/DVO_IDCKP(DVO_I DCK P )

AD17

MEM_DQS0N/DVO_IDCKN(DVO_IDCKN)

AD21

MEM_DQS1P(NC)

AC20

MEM_DQS1N(NC)

RS690E

RS690E

PAR 6 OF 6

PAR 6 OF 6

MEM_DQ0/DVO_VSYNC(DVO_VSYNC)

MEM_DQ1/DVO_HSYNC(DVO_HSYNC)

MEM_DQ2/DVO_DE(DVO_DE)

MEM_DQ3/DVO_D0(DVO_D0)

MEM_DQ4(NC)

MEM_DQ5/DVO_D1(DVO_D1)

MEM_DQ6/DVO_D2(DVO_D2)

MEM_DQ7/DVO_D4(DVO_D4)

MEM_DQ8/DVO_D3(DVO_D3)

MEM_DQ9/DVO_D5(DVO_D5)

MEM_DQ10/DVO_D6(DVO_D6)

MEM_DQ11/DVO_D7(DVO_D7)

MEM_DQ12(NC)

MEM_DQ13/DVO_D9(DVO_D9)

MEM_DQ14/DVO_D10(DVO_D10)

MEM_DQ15/DVO_D11(DVO_D11)

SBD_MEM/DVO_I/F

SBD_MEM/DVO_I/F

MEM_COMPP(NC)

MEM_COMPN(NC)

MEM_VREF (NC)

IOPLLVDD18(NC)

IOPLLVSS(NC)

IOPLLVDD12(NC)

+1.8V

R23

R23

1K/F_4

1K/F_4

R26

R26

1K/F_4

1K/F_4

AD13

AE13

AC13

AD14

AC15

AD15

AE15

AE16

AD16

AC17

AD18

AE19

AC19

AE20

AD20

AE21

Y11

W11

AE12

AA17

Y17

AB17

VMA_DQ0

VMA_DQ1

VMA_DQ2

VMA_DQ3

VMA_DQ4

VMA_DQ5

VMA_DQ6

VMA_DQ7

VMA_DQ8

VMA_DQ9

VMA_DQ10

VMA_DQ11

VMA_DQ12

VMA_DQ13

VMA_DQ14

VMA_DQ15

MEM_VREF1

C50

C50

0.1u/10V_4

0.1u/10V_4

MEM_COMPP

MEM_COMPN

MEM_VREF1

IOPLLVDD18

IOPLLVDD12

R25 40.2/F_4R25 40.2/F_4

R24 40.2/F_4R24 40.2/F_4

C92

C92

4.7u/6.3V_6

4.7u/6.3V_6

SCL use 2.2uF

+1.8V_SPM

L11

L11

FBMH1608HM221/1.5A/220ohm_8

FBMH1608HM221/1.5A/220ohm_8

L16

L16

FBMH1608HM221/1.5A/220ohm_8

FBMH1608HM221/1.5A/220ohm_8

C73

C73

4.7u/6.3V_6

4.7u/6.3V_6

+1.8V

+1.2V

SPM(CLG)

VMA_CLK0

R29

R29

68/F_4

68/F_4

VMA_CLK0#

VMA_DQ4

VMA_DQ6

VMA_DQ7

VMA_DQ0

VMA_DQ1

VMA_DQ3

VMA_DQ2

VMA_DQ5

VMA_DQ15

VMA_DQ14

VMA_DQ13

VMA_DQ11

VMA_DQ10

VMA_DQ8

VMA_DQ9

VMA_DQ12

VMA_DM0

VMA_DM1

VMA_WDQS0

VMA_RDQS0

VMA_WDQS1

VMA_RDQS1

VMA_CLK0

VMA_CLK0#

VMA_BA2

VMA_BA1

VMA_BA0

VMA_MA12

VMA_MA11

VMA_MA10

VMA_MA9

VMA_MA8

VMA_MA7

VMA_MA6

VMA_MA5

VMA_MA4

VMA_MA3

VMA_MA2

VMA_MA1

VMA_MA0

VMA_ODT

VMA_CKE

VMA_CS0#

VMA_WE#

VMA_RAS#

VMA_CAS#

U11

U11

B9

UDQ7

B1

UDQ6

D9

UDQ5

D1

UDQ4

D3

UDQ3

D7

UDQ2

C2

UDQ1

C8

UDQ0

F9

LDQ7

F1

LDQ6

H9

LDQ5

H1

LDQ4

H3

LDQ3

H7

LDQ2

G2

LDQ1

G8

LDQ0

B3

UDM

F3

LDM

B7

UDQS

A8

UDQS

F7

LDQS

E8

LDQS

J8

CK

K8

CK

L1

BA2

L3

BA1

L2

BA0

R2

A12

P7

A11

M2

A10

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K9

ODT

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

H5PS1G63EFR-20L

H5PS1G63EFR-20L

Btest

Hynix 64MB

Samsung 64MB

Hynix 128MB

Samsung 128MB

J2

VREF

A1

VDD1

E1

VDD2

J9

VDD3

M9

VDD4

R1

VDD5

A9

VDDQ1

C1

VDDQ2

C3

VDDQ3

C7

VDDQ4

C9

VDDQ5

E9

VDDQ6

G1

VDDQ7

G3

VDDQ8

G7

VDDQ9

G9

VDDQ10

J1

VDDL

A2

NC1

E2

NC2

R3

NC4

R7

NC5

R8

NC6

A3

VSS1

E3

VSS2

J3

VSS3

N1

VSS4

P9

VSS5

A7

VSSQ1

B2

VSSQ2

B8

VSSQ3

D2

VSSQ4

D8

VSSQ5

E7

VSSQ6

F2

VSSQ7

F8

VSSQ8

H2

VSSQ9

H8

VSSQ10

J7

VSSDL

15mil

VMREFA1

C87

C87

0.1u/10V_4

0.1u/10V_4

C399

C399

4.7u/6.3V_6

4.7u/6.3V_6

AKD5FG-TW03

AKD5FG-T501

AKD5LG-TW02

AKD5LG-T510

R256 1K/F_4R256 1K/F_4

R257 1K/F_4R257 1K/F_4

C398 0.1u/10V_4C398 0.1u/10V_4

+1.8V_SPM

BLM18PG221SN1D/1.4A/220ohm_6

BLM18PG221SN1D/1.4A/220ohm_6

L41

L41

C81

C81

0.1u/10V_4

0.1u/10V_4

C476

C476

0.1u/10V_4

0.1u/10V_4

Btest-For EMI

IC SDRAM(84P) H5PS5162FFR-25C(FBGA)

IC SDRAM(84P) K4N51163QG-HC25(FBGA)

IC SDRAM(84P) H5PS1G63EFR-20L(FBGA)STNBS

IC SDRAM(84P)K4N1G164QE-HC20(FBGA)STNBSQ

+1.8V

BLM18PG221SN1D/1.4A/220ohm_6

BLM18PG221SN1D/1.4A/220ohm_6

C66

C66

C61

C61

C72

C72

C83

C83

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

+1.8V_SPM

C477

C477

C478

C478

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

Description Voltage

+1.8V_SPM+1.8V_VDDL

Power name

IOPLLVDD18

IOPLLVDD12

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

+1.8V_SPM

Btest-For EMI

1.2V power for memory I/O PLLs

1.8V power for memory I/O PLLs

R34

R34

+

C57

+

C57

*100u/6.3V_3528

*100u/6.3V_3528

1.8V

1.2V

+1.8V

Power name

IOPLLVDD18

IOPLLVDD12

Description Voltage

1.2V power for memory I/O PLLs

1.8V power for memory I/O PLLs

5

1.8V

1.2V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

RS690E HT LINK I/F

RS690E HT LINK I/F

RS690E HT LINK I/F

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

PROJECT :

ZA8

ZA8

ZA8

935Friday, May 08, 2009

935Friday, May 08, 2009

1

935Friday, May 08, 2009

1A

1A

1A

of

of

of

Page 10

5

(CLG)

D D

Follow AMD check list, use X7R for all caps in this page

G5

G4

AB7

AB6

AC4

AD4

M8

M7

M4

M5

W4

W5

W9

C C

A_RX2P(13)

A_RX2N(13)

A_RX3P(13)

A_RX3N(13)

PCIE_RXP2_LAN(20)

PCIE_RXN2_LAN(20)

PCIE_RXP3_WLAN(21)

PCIE_RXN3_WLAN(21)

PCIE_RXP1_3G(21)

PCIE_RXN1_3G(21)

A_RX0P(13)

B B

A_RX0N(13)

A_RX1P(13)

A_RX1N(13)

R253 *10K/F_4R253 *10K/F_4

R250 *8.25K/F_4R250 *8.25K/F_4

T10T10

T14T14

U10B

U10B

GFX_RX0P

GFX_RX0N

J8

GFX_RX1P

J7

GFX_RX1N

J4

GFX_RX2P

J5

GFX_RX2N

L8

GFX_RX3P

L7

GFX_RX3N

L4

GFX_RX4P

L5

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

P8

GFX_RX7P

P7

GFX_RX7N

Y4

SB_RX2P(GPP_RX0P)

Y5

SB_RX2N(GPP_RX0N)

SB_RX3P(GPP_RX1P)

SB_RX3N(GPP_RX1N)

P4

GPP_RX2P

P5

GPP_RX2N

R4

GPP_RX3P

R5

GPP_RX3N

R7

GPP_RX0P(NC)

R8

GPP_RX0N(NC)

U4

GPP_RX1P(NC)

U5

GPP_RX1N(NC)

SB_RX0P

SB_RX0N

V9

SB_RX1P

SB_RX1N

NC(PCE_ISET)

NC(PCE_TXISET)

RS690E

RS690E

4

PART 2 OF 6

PART 2 OF 6

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

PCIE I/F GFX

PCIE I/F GFX

PCE_CALRP(PCE_PCAL)

PCE_CALRN(PCE_NCAL)

GFX_TX7P

GFX_TX7N

SB_TX2P(GPP_TX0P)

SB_TX2N(GPP_TX0N)

SB_TX3P(GPP_TX1P)

SB_TX3N(GPP_TX1N)

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX0P(NC)

GPP_TX0N(NC)

GPP_TX1P(NC)

GPP_TX1N(NC)

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

J1

H2

K2

K1

K3

L3

L1

L2

N2

N1

P2

P1

P3

R3

R1

R2

AA1

AA2

Y2

Y3

U2

U1

V2

V1

V3

W3

W1

W2

AC1

AC2

AB1

AB2

AE4

AE3

A_TX2P_C

A_TX2N_C

A_TX3P_C

A_TX3N_C

GPP_TX2P_C

GPP_TX2N_C

GPP_TX3P_C

GPP_TX3N_C

T3T3

T5T5

GPP_TX1P_C

GPP_TX1N_C

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

A_CALRP

A_CALRN

3

C369 0.1u/10V_4C369 0.1u/10V_4

C384 0.1u/10V_4C384 0.1u/10V_4

C379 0.1u/10V_4C379 0.1u/10V_4