Page 1

5

4

3

2

1

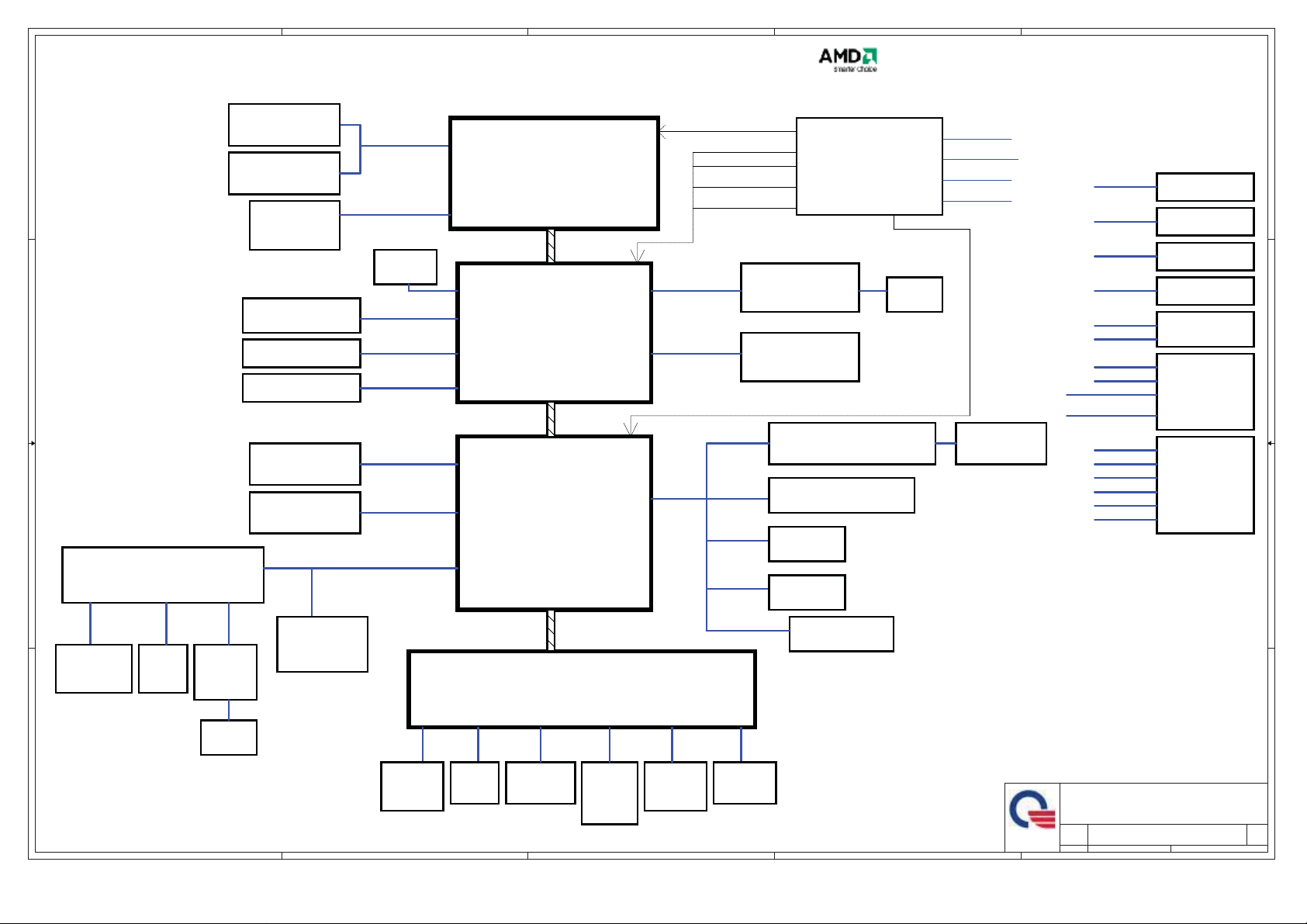

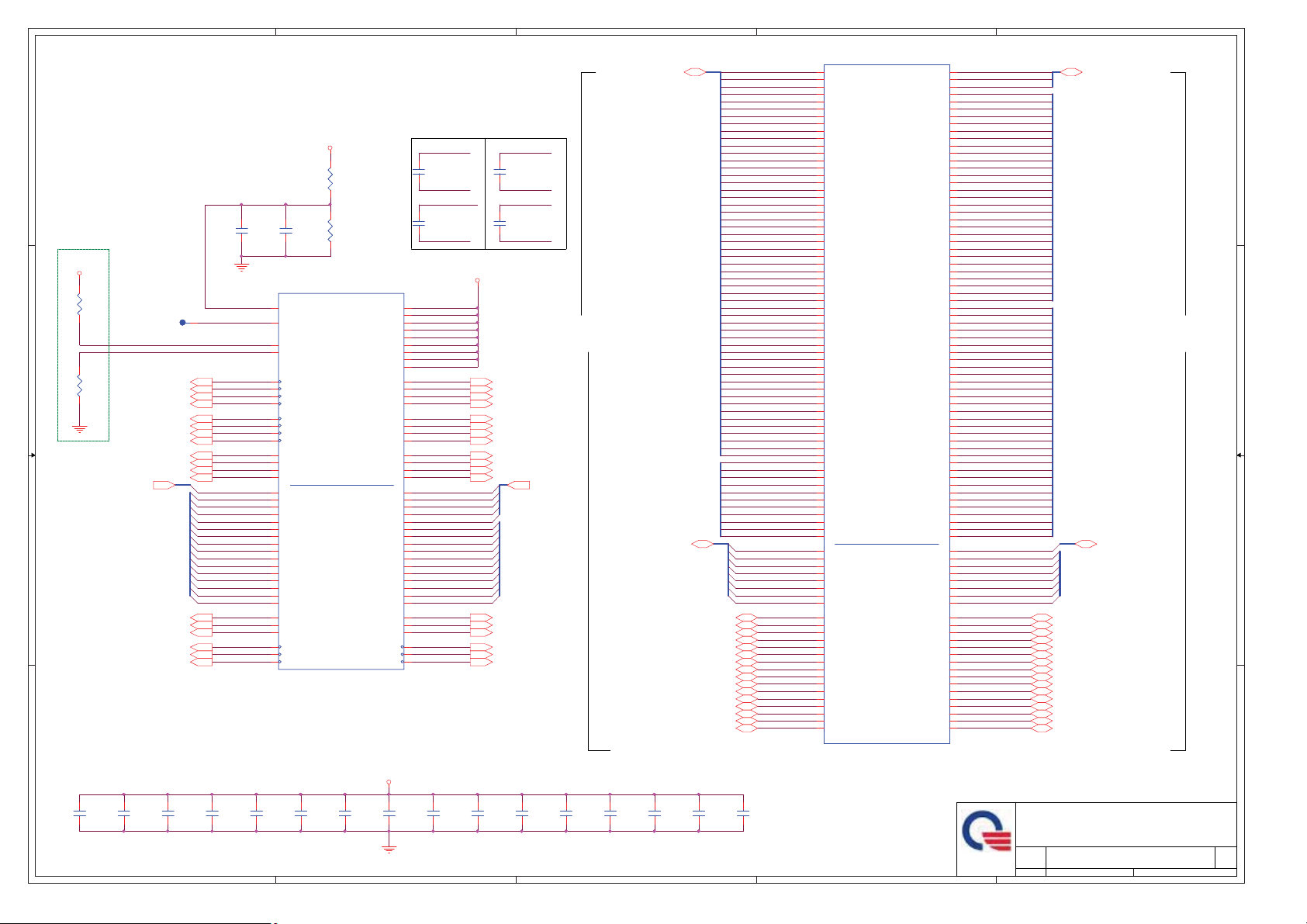

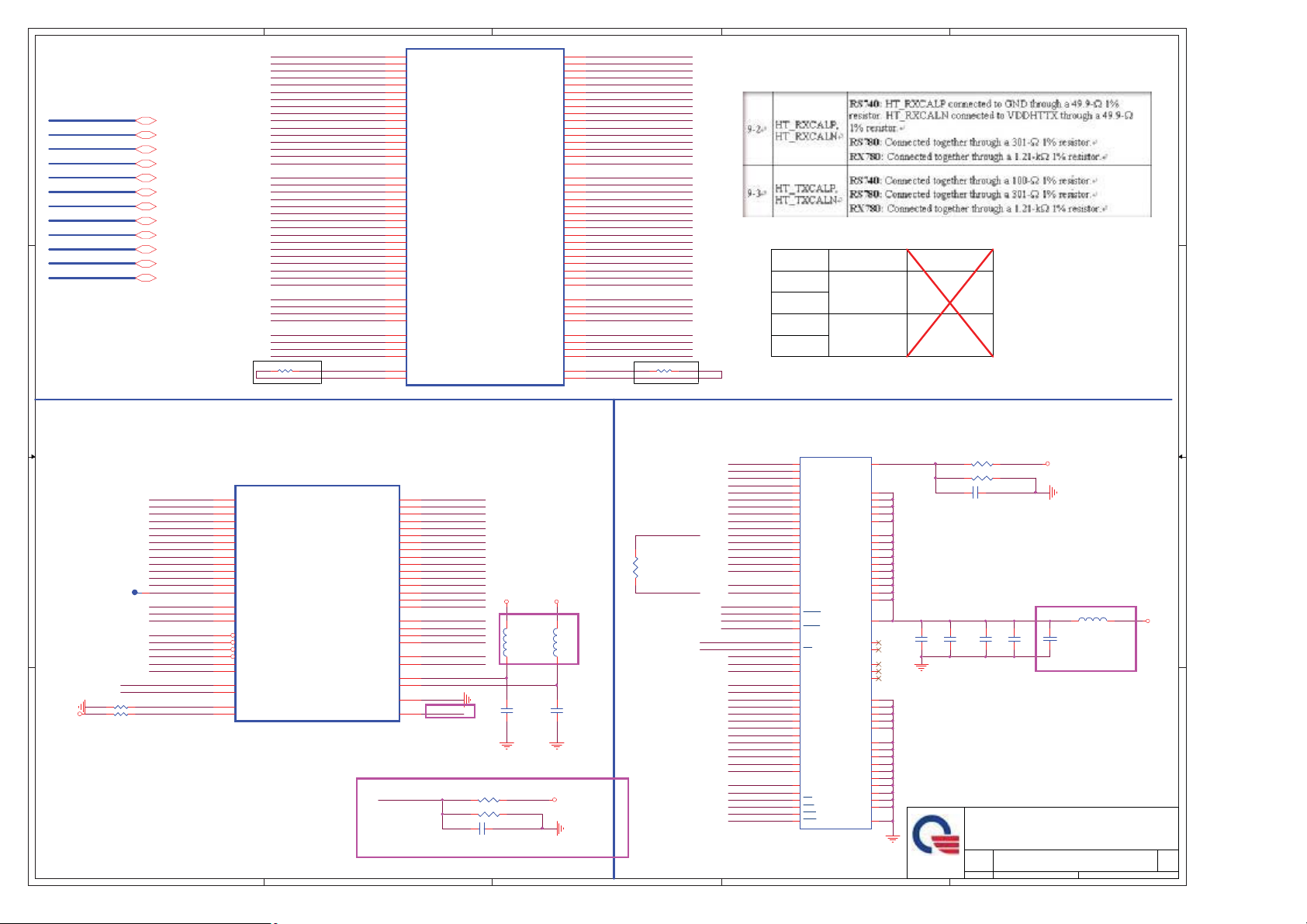

Z08 SYSTEM BLOCK DIAGRAM

DDRII-SODIMM1

+1.8VSUS

D D

+SMDDR_VREF

DDRII-SODIMM2

+1.8VSUS

+SMDDR_VREF

PG 7,8

PG 7,8

CPU THERMAL

SENSOR

+3V

PG 8

DDR II 667 M HZ

+1.2V

+2.5V

+1.8VSUS

VCC_CORE

+SMDDR_VTERM

Side port

AMD S1g1

Caspian Processor

(638 S1g1 socket)

PG 4,5,6

HT_LINK(1.0)

800 MHZ

PG 9

NB

LVDS Panel(LED)

+3V

VIN

C C

+3V

+5V

+5V

SATA- HDD

+3V

+5V

CRT

HDMI

PG 18

PG 18

PG 19

PG 24

SATA- ODD

+5V

B B

Azalia Audio Codec

+3V

CX20561-15z

PG 20

PG 24

LVDS(1ch)

GFX_TX0-3

SATA0

SATA4

Azalia

+1.1V_NB

+1.2V

+1.8V

+3V

+NB_CORE

A_LINK (X4)

+1.2V

+1.2V_S5

+1.8V

+3V_S5

+3V

+5V

VCCRTC

MODEM CONN.

(MDC)

HP+SPDF

JACK

+5V

PG 20 PG 20 PG 20

MIC

JACK

+3V

+5V

AMP

G1441

+3.3V_SUS

PG 24

+3V

+3VPCU

RS780MN

21mm X 21mm, 528pin BGA

PG 9,10,11,12

SB

SB710

21mm X 21mm, 528pin BGA

PG 13,14,15,16,17

LPC

EC

WPCE775

USB2.0

PG 26

PCIE 0

PCIE 3

CPU_CLK

HTREF_CLK

NBGFX_CLK

NBGPP_CLK

SBLINK_CLK

+3V_S5

Mini Card (WLAN)

+1.5V

+3V

USBP4

USBP8

USBP10

USBP5

USBP0;USBP1

CLOCK GENERATOR

ICS9LPRS476AKLFT

SLG8SP628VTR

RTM880N-795

+3V

Giga LAN

BCM5784M

PG 21 PG 21

PG 22

Card Reader controller

+3V

USB2.0 I/O Ports X1

+5VPCU

BT CONN.

+3VSUS

WEBCAM

+3V

RTS5159E

PG 25

PG 22

PG 18

USB2.0 Board

HOST 200MHz

PCIE 100MHz

USB 48MHz

REF 14MHz

PG 3

RJ45

SBSRC_CLK

Card Reader

PG 23 PG 23

VCC_CORE

+NB_CORE

+2.5V

+1.5V

+1.2V

+1.2V_S5

+1.8VSUS

+1.8V

+SMDDR_VTERM

+SMDDR_VREF

+3VPCU

+3V_S5

+3VSUS

+3V

+5VPCU

+5V

01

CPU CORE

NB CORE

(1.0~1.1V)

+2.5V

+1.5V

+1.2V

+1.8VSUS

SMDDR

3V/5V

Speaker

A A

5

PG 20

POWER/B

PG 25

+3VPCU +5V

4

FAN

PG 8

Keyboard

PG 25

SPI

Flash

ROM

PG 26

+3VPCU

Touch

Pad

3

PG 25

MMB/B

+3V

PG 26

PROJECT : Z08

PROJECT : Z08

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

BLOCKDIAGRAM

BLOCKDIAGRAM

BLOCKDIAGRAM

1

1A

1A

1A

36

1Tuesday,April 28, 2009

36

1Tuesday,April 28, 2009

36

1Tuesday,April 28, 2009

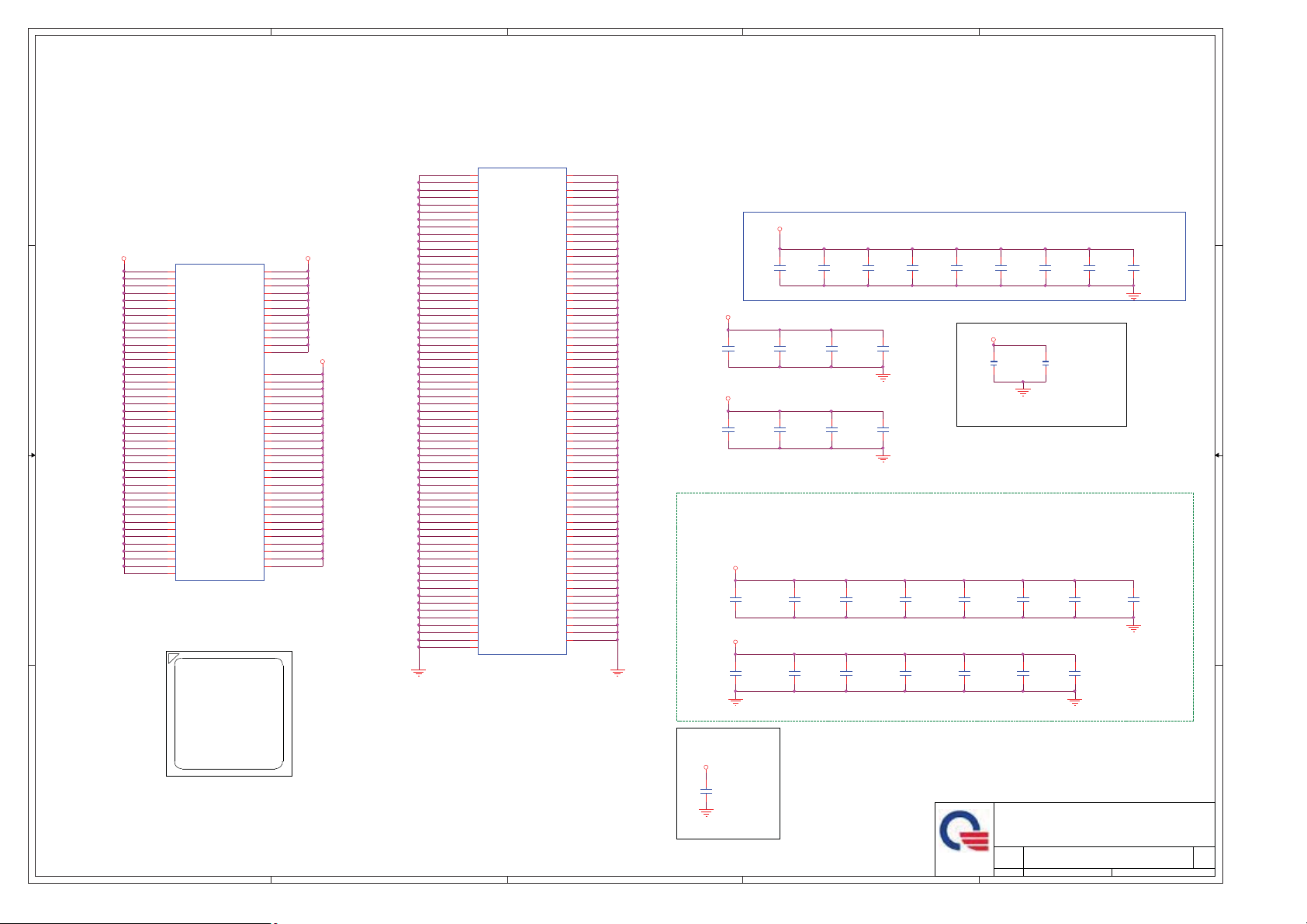

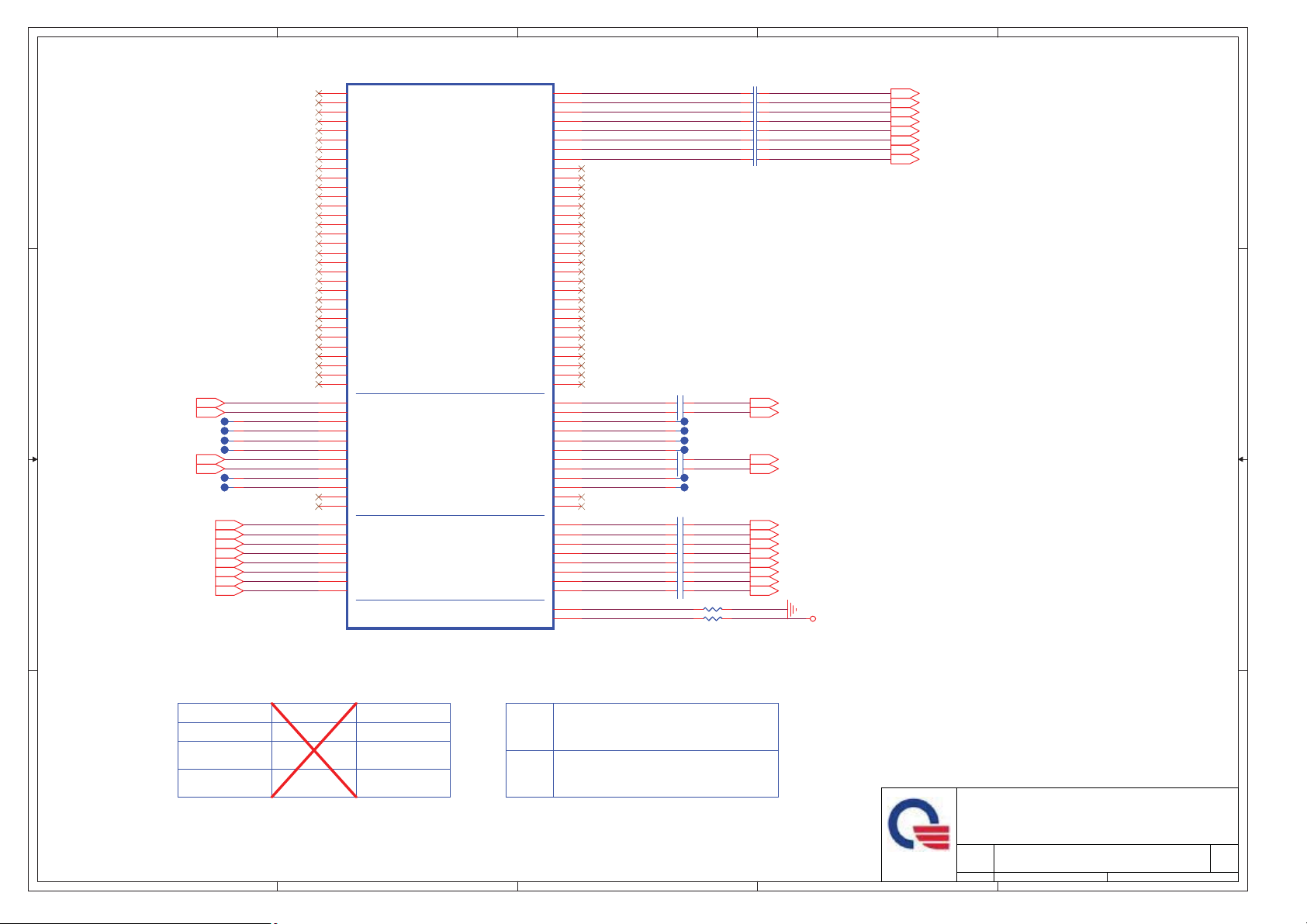

Page 2

5

4

3

2

1

Model

D D

HW

C C

Power

B B

REV

2009/04/09

C1A

2009/04/16

2009/04/17 7.Page 26: Add Q37,Q38,R484,R485 for MMB leakage.

2009/04/23 20.Page 19:Modify HDMI detect circuit_Del R174,R447,R441,Q35,Q36,R442;add R312,R488,D31.

2009/04/27 23.Page 20:Mount U14,C435,C418;unmount L47 for Audio noise issue.

2009/04/17

1.Page 11: Exchange Pin define for LVDS ON & PWM.

2.Page 21: U20 Footprint change to trf-10-1-24p-nb4.

3.Page 16: L39 Footprint from RC0603 chenge to RC0805.

4.Page 21: R389,R425 P/N change to CS12204JA44.

5.Page 22: CN23 Footprint change to mipcie-as0b223-s40n-7f-52p-nb4.

6.Page 23: R460 change to 33 ohm;C586 change to 10P for EMI.

8.Page 26: Add CP8,CP9 for EMI.2009/04/21

9.Page 24: Remove R284;mount C347 for EMI.

10.Page 20: Remove R312;mount C365 for EMI.

11.Page 3: Mount C248 and change to 15P for EMI.

12.Page 23: Remove R295;Mount C358 and change to 15P for EMI.

13.Page 12: Add C597,C598 30P (+NB_CORE) for EMI.

14.R120,R112,R388,R116,R387 change to short pad_0402.

15.Page 19: Del Q20,Q21,R196,R204;add R486,R487 for AMD suggestion.2009/04/22

16.Page 18: CN2 footprint from msc-rb30-5-fg-30p-l to msc-rb30-5-fg-30p-l-nb4.

17.R8,R10,R214,R216,R437,R200,R28,R4,R419,R266,R265,R275,R287,R293,

R314,R319,R325,R332,R334,R258,R283,R146,R148,R198 change to short pad_0402.

18.R106,R79,R117,R118,R480,R267,R482,L1 change to short pad_0603.

19.R105,R438,R223,R249,R29,R181,L21 change to short pad_0805.

21.Page 18:U2 pin7 modify voltage from +5V to +3V.

22.Page 26:Swap NET CP8,CP9.

And 3RD_MBCLK & 3RD_MBDATA pull high from +3V to +3VPCU.

Add C599,C600 30P (+1.2V_VDDHTTX) for EMI.

Add C601,C602 30P (+1.2V) for EMI.

24.Page 26:Modify Y1 Footprint.2009/04/28

1.Page27

2.Page32

3.Page32

4.PL5,PL8,PL10,PL11 Footprint change to choke-etqp4lr36wfc-nb4.

5.page27: 1.add PC163

2.PR110,PR139,PR149 change to short pad

3.PR141 un-mount

6.page28: 1.PR87,PR90,PR106,PR190,PR91 change to short pad.

2.JP2,JP3 remove

3.PR92 un-mount

4.PR101 mount

7.page29: 1.JP4,JP5 remove

2.PR44,PR43,PR18,PR19,PR128,PR131,

PR117,PR5 change to short pad.

3.add PC164,PC165

4.add PR197,PR196

Mount PR141(10K ohm) for Charger Issue.2009/04/10

Change Z08A PU5 part number from AL009338014 to AL009334000.

Change PC77 from 10u/4V_8 to 10u/10V_8.

CHANGE LIST

NOTEDATE

02

8.page30: 1.Remove JP8,JP9

9.page31: 1.Remove JP1,JP6,JP7

2.PR35,PR41,PR155,PR148 change to short pad.

3.+1.8VSUS_SRC net name change to +1.8VSUS

4.VIN_1.8 net name change to VIN.

5.+1.8V_out net name change to +1.8VSUS

10.PL3,PL7 Footprint change to choke-spm10040t-r45m200-4p.2009/04/22

2009/04/23 11.page28: Del NET RT8206_VIN.

12.page29: Add PC166 27uF/25V to VIN.

13.page28: Modify component from AO4496 to AO6402A..2009/04/27

A A

PROJECT : Z08

PROJECT : Z08

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Change List

Change List

Change List

1

1A

1A

1A

36

2Tuesday, April 28, 2009

36

2Tuesday, April 28, 2009

36

2Tuesday, April 28, 2009

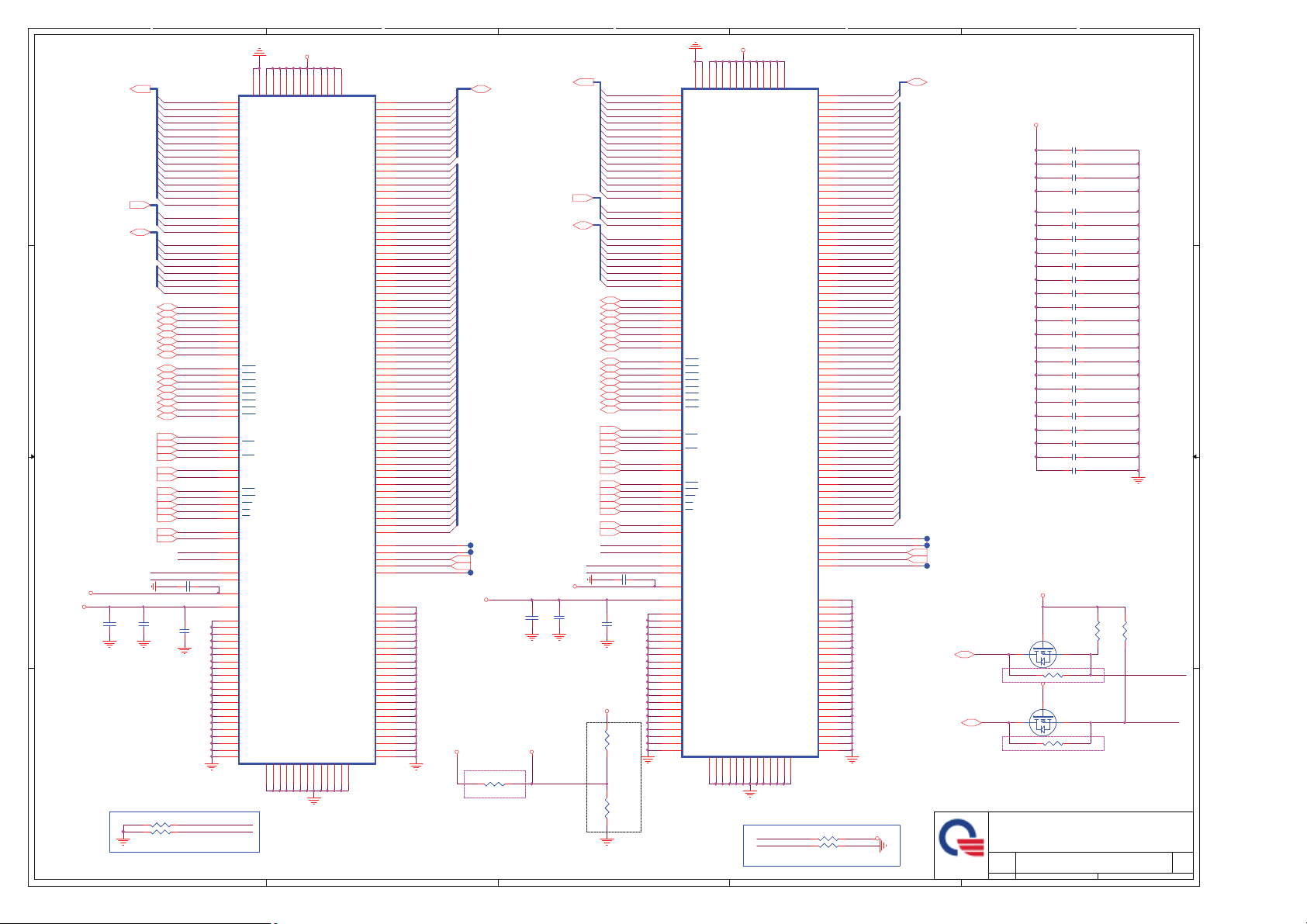

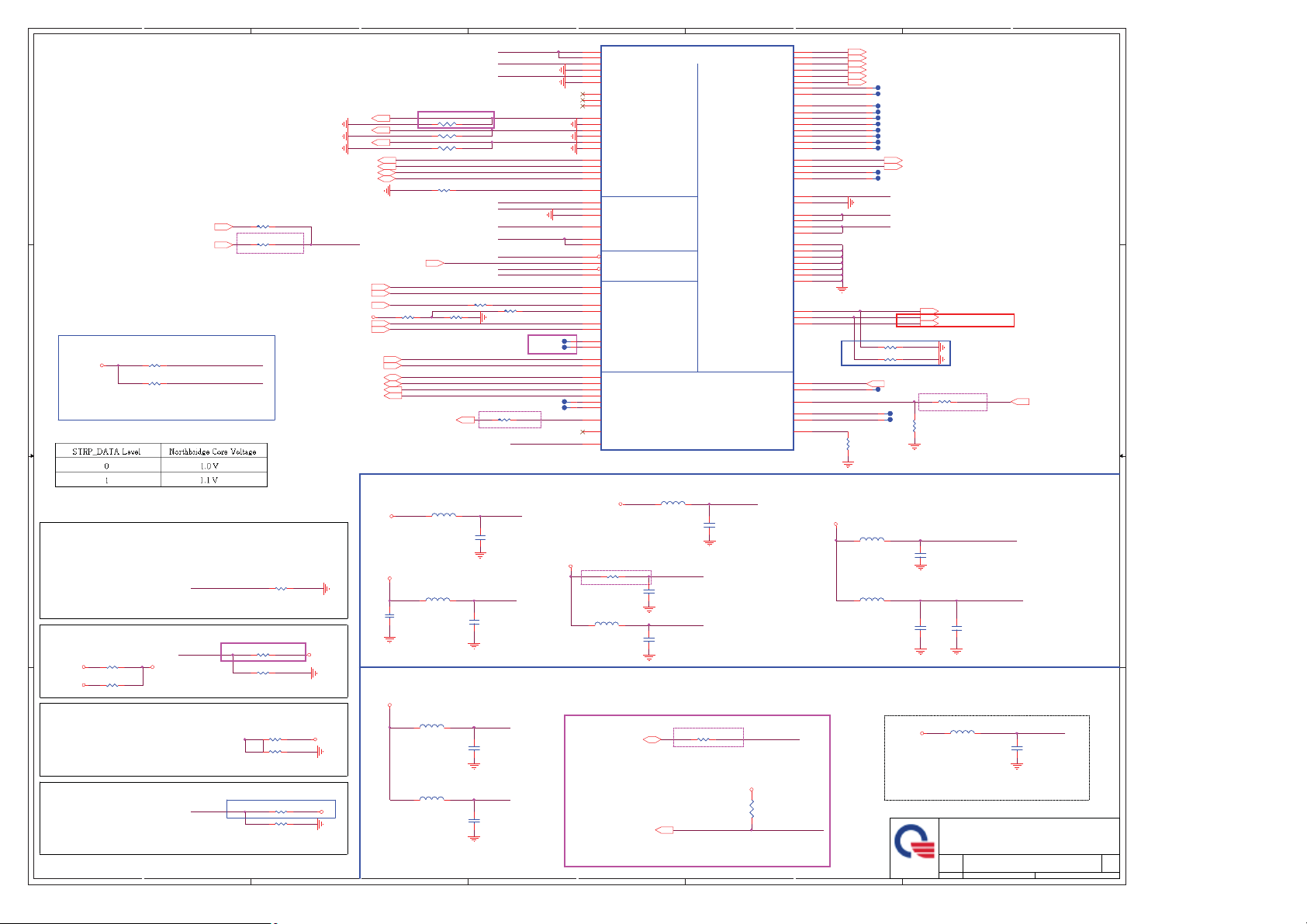

Page 3

5

4

3

2

1

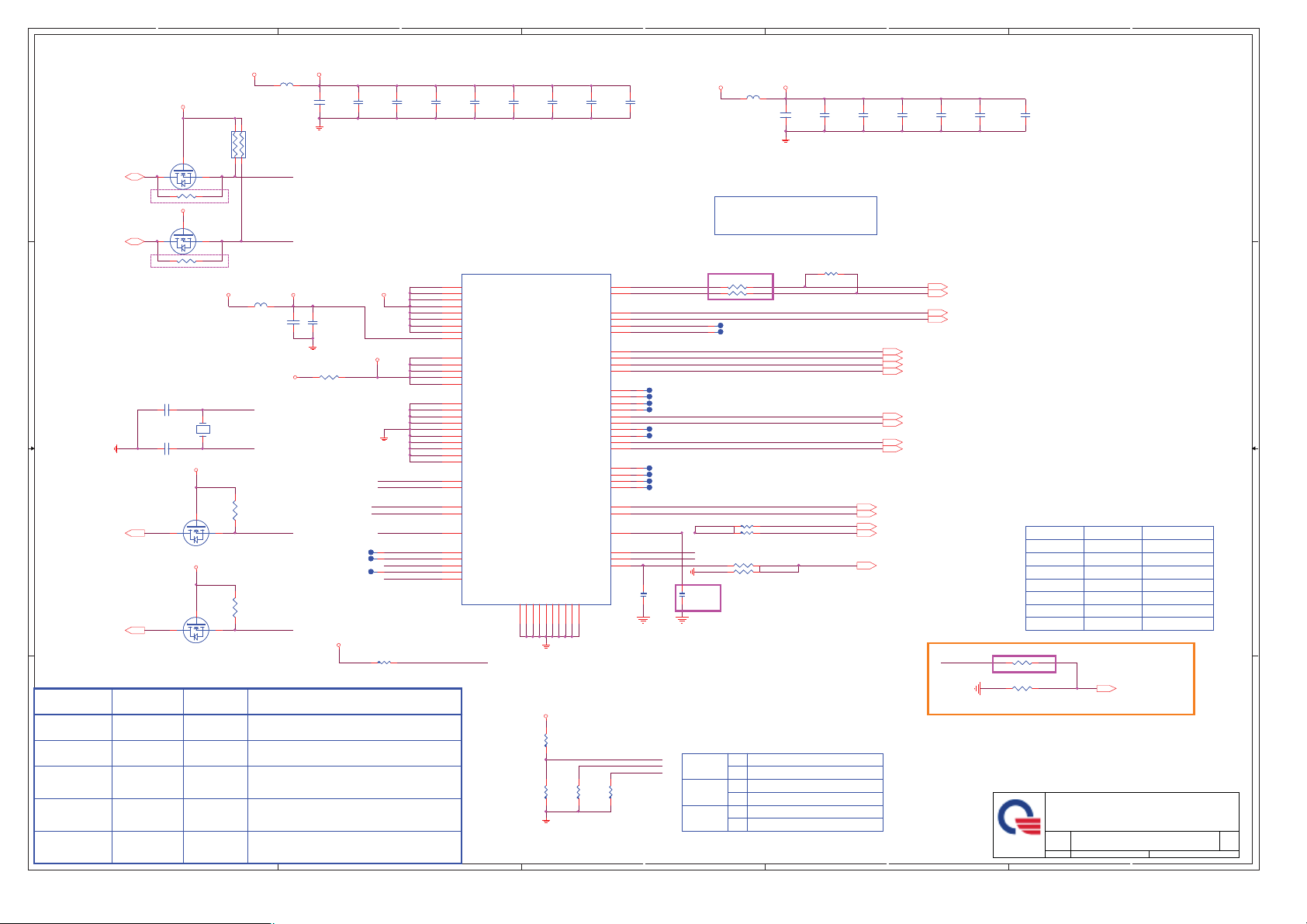

CLK_GEN_SLG8SP628(CLK)

+3V +3V_CLK_VDD

L26

L26

BK1608HS600/500mA/60ohm_6

2

4

RP15

RP15

*4.7KX2

*4.7KX2

1

3

CGCLK_SMB

CGDAT_SMB

BK1608HS600/500mA/60ohm_6

C215

C215

10u/6.3V_6

10u/6.3V_6

+3V

D D

PCLK_SMB<7,14,21,22>

PDAT_SMB<7,14,21,22>

Q22

Q22

2

*2N7002E

*2N7002E

3

R216 short0402R216 short0402

+3V

2

3

R214 short0402R214 short0402

1

Q23

Q23

*2N7002E

*2N7002E

1

change to short pad 4/22

+3V_CLK_4 8

L33 BK1608HS600/500mA/60ohm_6L33 BK1608HS600/500mA/60ohm_6

C255

C255

2.2U/6.3V_6

2.2U/6.3V_6

C C

+3V_CLK_VDD

C240 33p/50V_4C240 33p/50V_4

1 2

C244 33p/50V_4C244 33p/50V_4

1 2

LAN_CLKREQ#<21>

B B

CLKREQ_W L AN#<22>

3

3

+3V

+3V

21

2

2

CG_XIN

Y3

14.318MHZY314.318MHZ

CG_XOUT

R166

R166

10K_4

10K_4

1

Q18

Q18

RHU002N06

RHU002N06

R164

R164

*10K_4

*10K_4

1

Q17

Q17

*RHU002N06

*RHU002N06

CLKREQ4#

CLKREQ2#

RX780 RS780CLOCKS name

NBGFX_CLKP

NBGFX_CLKN

MXM_REFCLKP

MXM_REFCLKN

A A

NBGPP_CLKP

NBGPP_CLKN

SBLINK_CLKP

SBLINK_CLKN

RP1001 STUFF

RP66 STUFF

RP1005 STUFF RP1005 NC

RP1003 STUFF RP1003 STUFF

RP1001 STUFF

RP66 NC

to NB for VGA reference clock

to M82-S external reference clock -RX780only

to NB for RX780 for PCIEX2 interface reference clock only

RS780 is internal share withAC-LI NK clock,RS780not need

to NB for AC-LINK refer ence clock

5

C247

C247

0.1u/10V_4

0.1u/10V_4

R206 *0_6R206 *0_6

+3V_CLK_VDD

Clock pin function

+1.2V_CLK_ VDD IO

T70T70

T57T57

T55T55

C238

C238

C252

C252

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

+3V_CLK_VDD+3V

CG_XIN

CG_XOUT

CGCLK_SMB

CGDAT_SMB

CLK_PD#

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

R180 8.2K_4R180 8.2K_4

4

C228

C228

0.1u/10V_4

0.1u/10V_4

CLK_PD#

4

16

26

35

40

48

55

56

63

11

17

25

34

47

1

7

10

18

24

33

43

46

52

60

61

62

2

3

51

23

45

44

39

38

RTM880N-796

U6

U6

VDDDOT

VDDSRC

VDDATIG

VDDSB_SRC

VDDSATA

VDDCPU

VDDHTT

VDDREF

VDD48

VDDSRC_IO0

VDDSRC_IO1

VDDATIG_IO

VDDSB_SRC_IO

VDDCPU_IO

GND48

GNDDOT

GNDSRC0

GNDSRC1

GNDATIG

GNDSB_SRC

GNDSATA

GNDCPU

GNDHTT

GNDREF

X1

X2

SMBCLK

SMBDAT

PD#

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

SLG8SP628

SLG8SP628

C216

C216

C250

C250

0.1u/10V_4

0.1u/10V_4

SLG8SP628

0.1u/10V_4

0.1u/10V_4

C233

C233

0.1u/10V_4

0.1u/10V_4

P/N : AL8SP628000

ICS9LPRS480 P/N : ALPRS480000

P/N : AL000880000

CPUK8_0T

CPUK8_0C

ATIG0T

ATIG0C

ATIG1T

ATIG1C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

SRC6T/SATAT

SRC6C/SATAC

SRC7T/27M_SS

SRC7C/27M_NS

HTT0T/66M

HTT0C/6 6M

REF0/SEL_HTT66

REF1/SEL_SATA

REF2/SEL_27

74

R194

R194

8.2K_4

8.2K_4

R195

R195

*8.2K_4

*8.2K_4

SRC2C

SRC3T

SRC3C

SRC4T

SRC4C

48MHz_0

R202

R202

8.2K_4

8.2K_4

QFN64

QFN64

TGND065TGND166TGND267TGND368TGND469TGND570TGND671TGND772TGND873TGND9

+3V_CLK_VDD

C218

C218

0.1u/10V_4

0.1u/10V_4

50

49

30

29

28

27

37

36

32

31

22

21

20

19

15

14

13

12

9

8

42

41

6

5

54

53

64

59

58

57

R184

R184

8.2K_4

8.2K_4

SEL_SATA

SEL_HTT66

SEL_27

C219

C219

0.1u/10V_4

0.1u/10V_4

CPUCLKP_R

CPUCLKN_R

EXT_GFX_CLKP_R

EXT_GFX_CLKN_R

T69T69

T68T68

T67T67

T72T72

T74T74

T76T76

T58T58

T56T56

T73T73

T75T75

CLK_48M_USB_R

SEL_HTT66

SEL_SATA

C232

C232

*10p/50V_4

*10p/50V_4

3

+1.2V +1.2V_CLK_ VDD IO

L31

L31

BK1608HS600/500mA/60ohm_6

BK1608HS600/500mA/60ohm_6

Clock chip has internal serial t e rminations

for differencialpairs,externalresistorsare

reserved for debug purpose.

Place within 0.5"

of CLKGEN

R175 0_4R175 0_4

R171 0_4R171 0_4

C249

C249

10u/6.3V_6

10u/6.3V_6

R173

R173

*261/F_4

*261/F_4

C251

C251

0.1u/10V_4

0.1u/10V_4

3/10 Modify for AMD suggestion.

T59T59

T63T63

SBLINK_CLKP

SBLINK_CLKN

SBSRC_CLKP

SBSRC_CLKN

CLK_PCIE_WL AN

CLK_PCIE_WL AN #

CLK_PCIE_LAN

CLK_PCIE_LAN #

NBHT_REFCLKP

R208 22_4R208 22_4

R209 22_4R209 22_4

R185 158/F_4R185 158/F_4

R183 90.9/F_4R183 90.9/F_4

C248

C248

15p/50V_4

15p/50V_4

4/21 Mount C248 and change to 15P for EMI.

1

SEL_HTT66

SEL_SATA

SEL_27

*0

1 *

0

1

0*

* default

NBHT_REFCLKN

CLK_48M_USB

EXT_NB_OSCSEL_27

66 MHz 3.3V single ended HTT clock

100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

100 MHz spreading differential SRC clock

27MHz and 27M SS outputs

100 MHz SRC clock

C241

C241

0.1u/10V_4

0.1u/10V_4

CPUCLKP

CPUCLKN

NBGFX_CLKP

NBGFX_CLKN

NBHT_REFCLKP <11>

NBHT_REFCLKN <11>

CLK_Card48 <23>

CLK_48M_USB <14>

EXT_NB_OSC <11>

2

C237

C237

C242

C242

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

CPUCLKP <4>

CPUCLKN <4>

NBGFX_CLKP <11>

NBGFX_CLKN <11>

SBLINK_CLKP <11>

SBLINK_CLKN <11>

SBSRC_CLKP <13>

SBSRC_CLKN <13>

CLK_PCIE_WL AN <22>

CLK_PCIE_WL AN # <22>

CLK_PCIE_LAN <21 >

CLK_PCIE_LAN # <21>

To NB for HT_REF

To SB for USBCLK

To NB for REFCLK

SEL_SATA

C220

C220

C217

C217

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

To CPU for CLKIN

To NB for GFX_REF

To NB for GPPSB_REF

To SB for PCIE_RCLK

To Minicard (WLAN)

To LAN chip

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFC LK

GPP_REFCLK

GPPSB_REFCLK

0226 Modify for AMD suggestion.

R193 33_4R193 33_4

R192 *90.9/F_4R192 *90.9/F_4

1 2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

RX780 RS780

100MDIFF

100MDIFF

14MSE (1.8V)

NC vref

100MDIFF

100MDIFF

100MDIFF

EXT_SB_OSC <1 3 >

PROJECT : Z08

PROJECT : Z08

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

CLOCK GENERATOR_SLG8SP628

CLOCK GENERATOR_SLG8SP628

CLOCK GENERATOR_SLG8SP628

1

03

100MDIFF

100MDIFF

14MSE (1.1V)

100MDIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

100MDIFF

To SB for OSC

3Tuesday, April 28, 2009

3Tuesday, April 28, 2009

3Tuesday, April 28, 2009

1A

1A

1A

1A

1A

1A

36

36

36

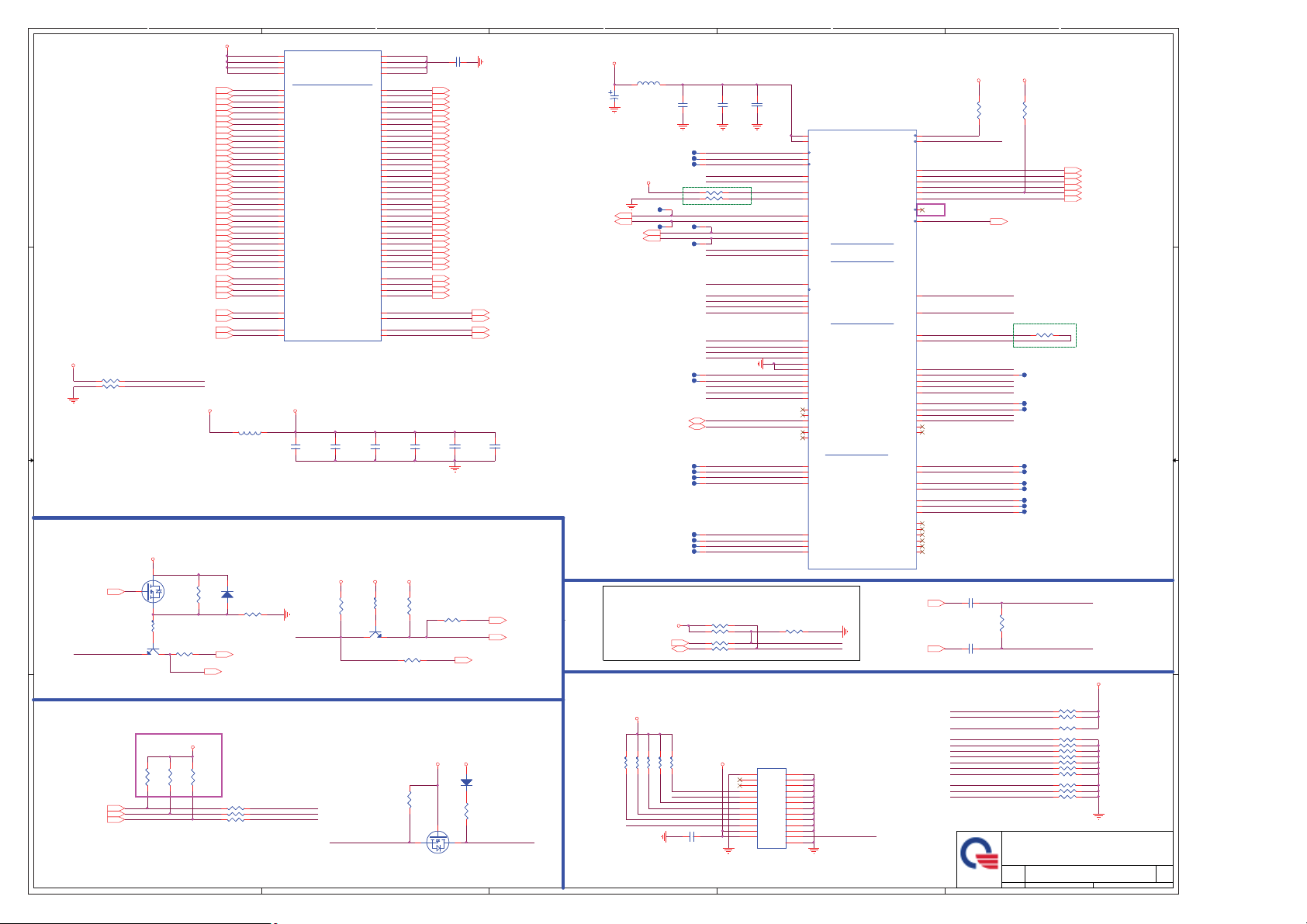

Page 4

5

HT_NB_CPU_CAD_H15<9>

HT_NB_CPU_CAD_L15<9>

HT_NB_CPU_CAD_H14<9>

HT_NB_CPU_CAD_L14<9>

HT_NB_CPU_CAD_H13<9>

HT_NB_CPU_CAD_L13<9>

HT_NB_CPU_CAD_H12<9>

HT_NB_CPU_CAD_L12<9>

D D

C C

VLDT_RUN

R99 *51/F_4R99 *51/F _4

R97 *51/F_4R97 *51/F _4

B B

CPU_COREPG<17,26,29>

H_THERMTRIP#

HT_NB_CPU_CAD_H11<9>

HT_NB_CPU_CAD_L11<9>

HT_NB_CPU_CAD_H10<9>

HT_NB_CPU_CAD_L10<9>

HT_NB_CPU_CAD_H9<9>

HT_NB_CPU_CAD_L9<9>

HT_NB_CPU_CAD_H8<9>

HT_NB_CPU_CAD_L8<9>

HT_NB_CPU_CAD_H7<9>

HT_NB_CPU_CAD_L7<9>

HT_NB_CPU_CAD_H6<9>

HT_NB_CPU_CAD_L6<9>

HT_NB_CPU_CAD_H5<9>

HT_NB_CPU_CAD_L5<9>

HT_NB_CPU_CAD_H4<9>

HT_NB_CPU_CAD_L4<9>

HT_NB_CPU_CAD_H3<9>

HT_NB_CPU_CAD_L3<9>

HT_NB_CPU_CAD_H2<9>

HT_NB_CPU_CAD_L2<9>

HT_NB_CPU_CAD_H1<9>

HT_NB_CPU_CAD_L1<9>

HT_NB_CPU_CAD_H0<9>

HT_NB_CPU_CAD_L0<9>

HT_NB_CPU_CLK_H1<9>

HT_NB_CPU_CLK_L1<9>

HT_NB_CPU_CLK_H0<9>

HT_NB_CPU_CLK_L0<9>

HT_NB_CPU_CTL_H1<9>

HT_NB_CPU_CTL_L1<9>

HT_NB_CPU_CTL_H0<9>

HT_NB_CPU_CTL_L0<9>

HT_NB_CPU_CTL_H1

HT_NB_CPU_CTL_L1

+1.8VSUS

3

2

1

2

1 3

MMBT3904

MMBT3904

Q11

Q11

R41

R41

10K_4

10K_4

Q13

Q13

FDV301N

FDV301N

R32 *0_6R32 *0_6

VLDT_RUN

R37

R37

*10K_4

*10K_4

SYS_SHDN# <28,33>

20mil

D4

D3

D2

D1

N5

P5

M3

M4

L5

M5

K3

K4

H3

H4

G5

H5

F3

F4

E5

F5

N3

N2

L1

M1

L3

L2

J1

K1

G1

H1

G3

G2

E1

F1

E3

E2

J5

K5

J3

J2

P3

P4

N1

P1

L20

L20

FBJ3216HS800_1206

FBJ3216HS800_1206

D4

*BAS316D4*BAS316

R36 100K_6R36 100K_6

CPU_THERMTRIP# <14>

U17AU17A

VLDT_A3

VLDT_A2

VLDT_A1

VLDT_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

Athlon64 S1

Processor Socket

VLDT_RUN+1.2V

C176

C176

4.7u/6.3V_6

4.7u/6.3V_6

H_PROCHOT#

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

C175

C175

4.7u/6.3V_6

4.7u/6.3V_6

+1.8VSUS+1.8VSUS

R42

R42

300_4

300_4

Q15 MMBT3904Q15 MMBT3904

4

C192

C192

0.22u/10V_4

0.22u/10V_4

R43

R43

10K_4

10K_4

2

20mil

VLDT_RUN

AE5

VLDT_RUN

AE4

VLDT_RUN

AE3

VLDT_RUN

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

T5

R5

R2

R3

+3V

13

R45 *0_4R45 *0_4

C190

C190

0.22u/10V_4

0.22u/10V_4

R47

R47

4.7K_4

4.7K_4

C455

C455

4.7u/6.3V_6

4.7u/6.3V_6

12

R54 *0_4R54 *0_4

HT_CPU_NB_CAD_H15 <9>

HT_CPU_NB_CAD_L15 <9>

HT_CPU_NB_CAD_H14 <9>

HT_CPU_NB_CAD_L14 <9>

HT_CPU_NB_CAD_H13 <9>

HT_CPU_NB_CAD_L13 <9>

HT_CPU_NB_CAD_H12 <9>

HT_CPU_NB_CAD_L12 <9>

HT_CPU_NB_CAD_H11 <9>

HT_CPU_NB_CAD_L11 <9>

HT_CPU_NB_CAD_H10 <9>

HT_CPU_NB_CAD_L10 <9>

HT_CPU_NB_CAD_H9 < 9>

HT_CPU_NB_CAD_L9 <9>

HT_CPU_NB_CAD_H8 < 9>

HT_CPU_NB_CAD_L8 <9>

HT_CPU_NB_CAD_H7 < 9>

HT_CPU_NB_CAD_L7 <9>

HT_CPU_NB_CAD_H6 < 9>

HT_CPU_NB_CAD_L6 <9>

HT_CPU_NB_CAD_H5 < 9>

HT_CPU_NB_CAD_L5 <9>

HT_CPU_NB_CAD_H4 < 9>

HT_CPU_NB_CAD_L4 <9>

HT_CPU_NB_CAD_H3 < 9>

HT_CPU_NB_CAD_L3 <9>

HT_CPU_NB_CAD_H2 < 9>

HT_CPU_NB_CAD_L2 <9>

HT_CPU_NB_CAD_H1 < 9>

HT_CPU_NB_CAD_L1 <9>

HT_CPU_NB_CAD_H0 < 9>

HT_CPU_NB_CAD_L0 <9>

HT_CPU_NB_CLK_H1 <9>

HT_CPU_NB_CLK_L1 <9>

HT_CPU_NB_CLK_H0 <9>

HT_CPU_NB_CLK_L0 <9>

HT_CPU_NB_CTL_H1 <9>

HT_CPU_NB_CTL_L1 <9>

HT_CPU_NB_CTL_H0 <9>

HT_CPU_NB_CTL_L0 <9>

12

C189

C189

C191

C191

180p/50V_4

180p/50V_4

180p/50V_4

180p/50V_4

THERM_ALERT# <8,15>

EC_PROCHOT# < 26>

CPU_PROCHOT_SB # < 13>

3

+2.5V

L55 30ohm_4AL55 30ohm_4A

C510

C510

*100u/6.3V_3528

*100u/6.3V_3528

VLDT_RUN

VCCSENSE<29>

VSSSENSE<29>

VDDIO_FB_H<31>

VDDIO_FB_L< 31>

IfAMD SIis notused, theSIDpincanbe leftunconnectedand SIC

shouldhavea 300-Ω (±5%) pulldo wn toVSS.

SB_SCLK3<14>

SB_SDATA3<14>

T1T1

T2T2

H_THERMDC<8>

H_THERMDA<8>

+1.8VSUS

C519

C519

4.7u/6.3V_6

4.7u/6.3V_6

T216T216

T214T214

T215T215

place them to C P U within 1"

T197T197

T198T198

T38T38

T41T41

T24T24

T200T200

T27T27

T201T201

T15T15

T12T12

T19T19

T17T17

VDDA_RUN

C135

C135

0.22u/10V_4

0.22u/10V_4

CPU_HT_RESET#

CPU_ALL_PWROK

CPU_ LDTSTO P#

CPU_SIC_R

CPU_SID_R

R96 44.2F_4R96 44.2F_4

R95 44.2F_4R95 44.2F_4

CPUCLKIN

CPUCLKIN#

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

H_THERMDC

H_THERMDA

CPU_RSVD_MA0_CLK3_P

CPU_RSVD_MA0_CLK3_N

CPU_RSVD_MA0_CLK0_P

CPU_RSVD_MA0_CLK0_N

CPU_RSVD_MB0_CLK3_P

CPU_RSVD_MB0_CLK3_N

CPU_RSVD_MB0_CLK0_P

CPU_RSVD_MB0_CLK0_N

R373 *300_4R373 *300_4

R367 *300_4R367 *300_4

R369 *0_4R369 *0_4

R372 *0_4R372 *0_4

2

ATHLON Control and Debug

12

C140

C140

3300p/50V_4

3300p/50V_4

U17D

U17D

F8

VDDA2

F9

VDDA1

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

AF4

SIC

AF5

CPU_HTREF1

CPU_HTREF0

SID

P6

HT_REF1

R6

HT_REF0

F6

VDD_FB_H

E6

VDD_FB_L

W9

VDDIO_FB_H

Y9

VDDIO_FB_L

A9

CLKIN_H

A8

CLKIN_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

TEST5

W8

TEST4

Y6

TEST3

AB6

TEST2

P20

RSVD0

P19

RSVD1

N20

RSVD2

N19

RSVD3

R26

RSVD4

R25

RSVD5

P22

RSVD6

R22

RSVD7

R368300_4 R368300_4

CPU_SIC_R

CPU_SID_R CPUCLKIN#

MISC

MISC

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

PSI_L

DBREQ_L

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

CPUCLKP<3>

CPUCLKN<3>

AF6

AC7

A5

VID5

C6

VID4

A6

VID3

A4

VID2

C5

VID1

B5

VID0

AC6

A3

E10

AE9

TDO

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

H_THERMTRIP#

H_PROCHOT#

CPU_DBREQ#

CPU_TDO

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

CPU_TEST24_SCANCLK1

CPU_TEST23_TSTUPD

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST28_H_PLLCHRZ_P

CPU_TEST28_L_PLLCHRZ_N

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_MA_RESET#

CPU_MB_RESET#

CPU_RSVD_VIDSTRB1

CPU_RSVD_VIDSTRB0

CPU_RSVD_VDDNB_FB_P

CPU_RSVD_VDDNB_FB_N

CPU_RSVD_CORE_TYPE

R39

R39

300_4

300_4

3/10 Modify for AMD suggestion.

PSI_Lis a Power StatusIndicatorsignal. This signal is asserted

when theprocessor is in a lowpowerstate.PSI_L should be

connected to the power supply controller, if the controller supports

“skipmode, or diode emulationmode”. PSI_L is asserted by the

processorduring t heC3 and S1 states.

C523 3900P/50V_4C523 3900P/50V_4

C522 3900P/50V_4C522 3900P/50V_4

PWR_PSI# <29>

PLACE IT CLOSE TO CPU WITHIN 1"

ROUTE AS 80 OhmDIFFERENTIALPAIR

R381

R381

169/F_6

169/F_6

+1.8VSUS+1.8VSUS

R396

R396

300_4

300_4

R384 80.6F_4R384 80. 6F_4

T3T3

T37T37

T48T48

T33T33

T212T212

T205T205

T203T203

T34T34

T35T35

T204T204

CPUCLKIN

1

H_VID5 <29>

H_VID4 <29>

H_VID3 <29>

H_VID2 <29>

H_VID1 <29>

H_VID0 <29>

+1.8VSUS

04

3/10 Modify for AMD suggestion.

+1.8V

+1.8VSUS

+3V

FD1

2

Q32

Q32

*HDT@FDV301N

*HDT@FDV301N

FD1

*HDT@BAS316

*HDT@BAS316

R391

R391

*HDT@2K_4

*HDT@2K_4

3

CPU toHDT RESET#CPU_HT_RESET#

R397

R397

R399

R399

R393

A A

CPU_PWRG D<13>

CPU_LDT_STOP#<11,13>

CPU_LDT_RST#<11,13>

300_4

300_4

300_4

300_4

R393

300_4

300_4

R401 short_4R401 s hort_4

R398 short_4R398 s hort_4

R392 short_4R392 s hort_4

CPU_ALL_PWROK

CPU_ LDTSTO P#

CPU_HT_RESET#

R400

R400

*2.2K_4

*2.2K_4

1

5

4

+1.8VSUS

R360 220_4R360 220_4

R21 220_4R21 220_4

NOTE: HDT TERMIN ATION IS REQU IRED

FOR REV. Ax SILICON ONLY.

3

R20 220_4R20 220_4

R19 220_4R19 220_4

R402 220_4R402 220_4

C13 *0.1u/10V_4C13 *0.1u/ 10V_4

IF no use which Net

need pull-up or down

HDT CONNECTOR

+1.8VSUS

1 2

3 4

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

CN4

CN4

KEY

KEY

<FUN>

<FUN>

*HDT CONN

*HDT CONN

25

CPU toHDT RESET#

2

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

R359 *300_4R359 *300_4

R356 300_4R356 300_4

R132 510/F_4R132 510/F_4

R23 300_4R23 300_4

R364 *300_4R364 *300_4

R357 *300_4R357 *300_4

R361 *300_4R361 *300_4

R22 *300_4R22 *300_4

R394 *300_4R394 *300_4

R395 *300_4R395 *300_4

R133 510/F_4R133 510/F_4

R131 300_4R131 300_4

R134 300_4R134 300_4

PROJECT : Z08

PROJECT : Z08

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

TURI OHT,CTL I/F1/3

TURI OHT,CTL I/F1/3

TURI OHT,CTL I/F1/3

Date: Sheet of

Date: Sheet of

Date: Sheet

1

of

36

4Tuesday, April 28, 2009

36

4Tuesday, April 28, 2009

36

4Tuesday, April 28, 2009

1A

1A

1A

Page 5

5

Processor DDR2 Memory Interface

D D

CPU_M_VREF

PLACE THEM CLOSE TO

CPUWITHIN1"

+1.8VSUS

R362

R362

39.2/F_4

39.2/F_4

1 2

C C

R363

R363

39.2/F_4

39.2/F_4

1 2

MEM_MA_ADD[0..15]<7,8>

B B

A A

T6T6

VTT_SENSE

M_ZN

M_ZP

MEM_MA0_CS#3<7,8>

MEM_MA0_CS#2<7,8>

MEM_MA0_CS#1<7,8>

MEM_MA0_CS#0<7,8>

MEM_MB0_CS#3<7,8>

MEM_MB0_CS#2<7,8>

MEM_MB0_CS#1<7,8>

MEM_MB0_CS#0<7,8>

MEM_MB_CKE1<7,8>

MEM_MB_CKE0<7,8>

MEM_MA_CKE1<7,8>

MEM_MA_CKE0<7,8>

MEM_MA_BANK2<7,8>

MEM_MA_BANK1<7,8>

MEM_MA_BANK0<7,8>

MEM_MA_RAS#<7,8>

MEM_MA_CAS#<7,8>

MEM_MA_WE#<7 ,8>

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

15-20mil

C65

C65

0.1u/10V_4

0.1u/10V_4

W17

Y10

AE10

AF10

V19

J22

V22

T19

Y26

J24

W24

U23

H26

J23

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

+1.8VSUS

R80

R80

2K/F_4

2K/F_4

R68

R68

C75

C75

2K/F_4

1000p/50V_4

1000p/50V_4

U17B

U17B

2K/F_4

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

ProcessorSocket

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

+SMDDR_V TERM

4

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

K26

T26

U26

U24

V26

U22

MEM_MA_CLK1_P

C520

C520

1.5p/50V_4

1.5p/50V_4

MEM_MA_CLK1_N

MEM_MA_CLK7_P

C444

C444

1.5p/50V_4

1.5p/50V_4

MEM_MA_CLK7_N

+SMDDR_VTERM

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CLK1_P

C527

C527

1.5p/50V_4

1.5p/50V_4

MEM_MB_CLK1_N

MEM_MB_CLK7_P

C446

C446

1.5p/50V_4

1.5p/50V_4

MEM_MB_CLK7_N

20-200mil

MEM_MA_CLK7_P <7>

MEM_MA_CLK7_N <7>

MEM_MA_CLK1_P <7>

MEM_MA_CLK1_N <7>

MEM_MB_CLK7_P <7>

MEM_MB_CLK7_N <7>

MEM_MB_CLK1_P <7>

MEM_MB_CLK1_N <7>

MEM_MB0_ODT1 <7,8>

MEM_MB0_ODT0 <7,8>

MEM_MA0_ODT1 <7,8>

MEM_MA0_ODT0 <7,8>

MEM_MB_ADD[0..15] <7,8>

MEM_MB_BANK2 <7,8>

MEM_MB_BANK1 <7,8>

MEM_MB_BANK0 <7,8>

MEM_MB_RAS# <7,8>

MEM_MB_CAS# <7,8>

MEM_MB_WE# <7,8>

3

U17C

MEM_MB_DATA[0..63]<7>

MEM_MB_DM[0..7]<7>

MEM_MB_DQS7_P<7>

MEM_MB_DQS7_N<7>

MEM_MB_DQS6_P<7>

MEM_MB_DQS6_N<7>

MEM_MB_DQS5_P<7>

MEM_MB_DQS5_N<7>

MEM_MB_DQS4_P<7>

MEM_MB_DQS4_N<7>

MEM_MB_DQS3_P<7>

MEM_MB_DQS3_N<7>

MEM_MB_DQS2_P<7>

MEM_MB_DQS2_N<7>

MEM_MB_DQS1_P<7>

MEM_MB_DQS1_N<7>

MEM_MB_DQS0_P<7>

MEM_MB_DQS0_N<7>

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

AD12

AC16

AE22

AB26

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

E25

A22

B16

A12

F26

E26

A24

A23

D16

C16

C12

B12

U17C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

2

DDR: DATA

DDR: DATA

Athlon 64 S1

ProcessorSocket

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

1

MEM_MA_DATA[0..63] <7>

To SODIMM socket A (near)To SODIMM socket B (Far)

MEM_MA_DM[0..7] <7>

MEM_MA_DQS7_P <7>

MEM_MA_DQS7_N <7>

MEM_MA_DQS6_P <7>

MEM_MA_DQS6_N <7>

MEM_MA_DQS5_P <7>

MEM_MA_DQS5_N <7>

MEM_MA_DQS4_P <7>

MEM_MA_DQS4_N <7>

MEM_MA_DQS3_P <7>

MEM_MA_DQS3_N <7>

MEM_MA_DQS2_P <7>

MEM_MA_DQS2_N <7>

MEM_MA_DQS1_P <7>

MEM_MA_DQS1_N <7>

MEM_MA_DQS0_P <7>

MEM_MA_DQS0_N <7>

05

C40

C40

4.7u/6.3V_6

4.7u/6.3V_6

C518

C518

4.7u/6.3V_6

4.7u/6.3V_6

5

C42

C42

4.7u/6.3V_6

4.7u/6.3V_6

C530

C530

4.7u/6.3V_6

4.7u/6.3V_6

C516

C516

0.22u/10V_4

0.22u/10V_4

C513

C513

0.22u/10V_4

0.22u/10V_4

C53

C53

0.22u/10V_4

0.22u/10V_4

C39

C39

0.22u/10V_4

0.22u/10V_4

4

C47

C47

1000p/50V_4

1000p/50V_4

C512

C512

1000p/50V_4

1000p/50V_4

C515

C515

1000p/50V_4

1000p/50V_4

C514

C514

1000p/50V_4

1000p/50V_4

C55

C55

180p/50V_4

180p/50V_4

3

C511

C511

180p/50V_4

180p/50V_4

C51

C51

180p/50V_4

180p/50V_4

C54

C54

180p/50V_4

180p/50V_4

PROJECT : Z08

PROJECT : Z08

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size DocumentNumber Rev

Size DocumentNumber Rev

Size DocumentNumber Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet

TURION 64 DDRII I/F

TURION 64 DDRII I/F

TURION 64 DDRII I/F

1

1A

1A

1A

of

36

5Tuesday, A pril 28, 2009

36

5Tuesday, A pril 28, 2009

36

5Tuesday, A pril 28, 2009

Page 6

5

4

3

2

1

PROCESSOR POWER AND GROUND

D D

U17F

U17F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

CPU_CORE CPU_CORE

C C

B B

AC4

AD2

G4

H2

J9

J11

J13

K6

K10

K12

K14

L4

L7

L9

L11

L13

M2

M6

M8

M10

N7

N9

N11

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

V6

V8

V10

POWER

POWER

Athlon 64 S1

ProcessorSocket

A1

U17E

U17E

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

+1.8VSUS

A26

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

GROUND

GROUND

Athlon 64 S1

ProcessorSocket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

BOTTOMSIDE DECOUPLING

CPU_CORE

C102

C102

C88

C88

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

For EMI request.

C132

C132

0.1u/10V_4

0.1u/10V_4

CPU_CORE

+1.8VSUS

C85

C85

0.22u/10V_4

0.22u/10V_4

C86

C86

10u/10V_8

10u/10V_8

C108

C108

10u/6.3V_6

10u/6.3V_6

C84

C84

0.22u/10V_4

0.22u/10V_4

C152

C152

10u/10V_8

10u/10V_8

C79

C79

10u/6.3V_6

10u/6.3V_6

C83

C83

0.01U/16V_4

0.01U/16V_4

C144

C144

0.22u/10V_4

0.22u/10V_4

C93

C93

10u/6.3V_6

10u/6.3V_6

C82

C82

180p/50V_4

180p/50V_4

C70

C70

0.22u/10V_4

0.22u/10V_4

C99

C99

10u/6.3V_6

10u/6.3V_6

C126

C126

10u/6.3V_6

10u/6.3V_6

CPU_CORE

C66

C66

0.1u/10V_4

0.1u/10V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.8VSUS

C145

C145

0.22u/10V_4

0.22u/10V_4

C124

C124

0.22u/10V_4

0.22u/10V_4

C103

C103

0.22u/10V_4

0.22u/10V_4

C72

C72

0.01U/16V_4

0.01U/16V_4

+1.8VSUS

C68

C68

4.7u/6.3V_6

4.7u/6.3V_6

C143

C143

0.01U/16V_4

0.01U/16V_4

C149

C149

4.7u/6.3V_6

4.7u/6.3V_6

C90

C90

180p/50V_4

180p/50V_4

C150

C150

4.7u/6.3V_6

4.7u/6.3V_6

C449

C449

180p/50V_4

180p/50V_4

C67

C67

4.7u/6.3V_6

4.7u/6.3V_6

C95

C95

0.22u/10V_4

0.22u/10V_4

C71

C71

0.22u/10V_4

0.22u/10V_4

C91

C91

180p/50V_4

180p/50V_4

C115

C115

10u/6.3V_6

10u/6.3V_6

06

C119

C119

10u/6.3V_6

10u/6.3V_6

C69

C69

0.22u/10V_4

0.22u/10V_4

Athlon 64 S1g1

uPGA638

TopView

A A

AF1

5

4

3

For EMI request.

+1.8VSUS

C106

C106

0.1u/10V_4

0.1u/10V_4

0319 Modify for EMI.

PROJECT : Z08

PROJECT : Z08

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size DocumentNumber Rev

Size DocumentNumber Rev

Size DocumentNumber Rev

TURION 64 PWR & GND

TURION 64 PWR & GND

TURION 64 PWR & GND

Date: Sheet of

Date: Sheet of

2

Date: Sheet

1

6Tuesday, A pril 28, 2009

6Tuesday, A pril 28, 2009

6Tuesday, A pril 28, 2009

1A

1A

1A

of

36

36

36

Page 7

5

+1.8VSUS

MEM_MA_ADD[0..15]<5,8> MEM_MA_DATA[0..63] <5>

D D

MEM_MA_BANK[0..2]<5,8>

MEM_MA_DM[0..7]<5>

MEM_MA_DQS0_P<5>

MEM_MA_DQS1_P<5>

MEM_MA_DQS2_P<5>

MEM_MA_DQS3_P<5>

MEM_MA_DQS4_P<5>

MEM_MA_DQS5_P<5>

+3V

C172

C172

2.2u/10V_8

2.2u/10V_8

MEM_MA_DQS6_P<5>

MEM_MA_DQS7_P<5>

MEM_MA_DQS0_N<5>

MEM_MA_DQS1_N<5>

MEM_MA_DQS2_N<5>

MEM_MA_DQS3_N<5>

MEM_MA_DQS4_N<5>

MEM_MA_DQS5_N<5>

MEM_MA_DQS6_N<5>

MEM_MA_DQS7_N<5>

MEM_MA_CLK1_P<5>

MEM_MA_CLK1_N<5>

MEM_MA_CLK7_P<5>

MEM_MA_CLK7_N<5>

MEM_MA_CKE0<5,8>

MEM_MA_CKE1<5,8>

MEM_MA_RAS#<5,8>

MEM_MA_CAS#<5,8>

MEM_MA_WE#<5,8>

MEM_MA0_CS#0<5,8>

MEM_MA0_CS#1<5,8>

MEM_MA0_ODT0<5,8>

MEM_MA0_ODT1<5,8>

1 2

C C

B B

+0.9VSMVREF_DIMM

A A

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

DIM1_SA1

DDRDAT_SMB DDRCLK_SMB

DDRCLK_SMB

C11 0.1u/10V_4C11 0.1u/10V_4

C173

C173

C179

C179

0.1u/10V_4

0.1u/10V_4

1000p/50V_4

1000p/50V_4

201

202

102

A0

101

A1

100

A2

99

A3

GNDPAD1

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14

84

A15

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

103

104

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

GNDPAD0

VDD7

REVERSE

SPD Address:0xA0

(H=5.2)

59

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

111

SO-DIMM

SO-DIMM

121

112

117

VDD8

VDD9

VSS30

VSS29

127

122

SA_A: '0' ,'0'

R16 10K/F_4R16 10K/F_4

R18 10K/F_4R18 10K/F_4

SMbus address A0

5

DIM1_SA0

DIM1_SA1

1.Thispart should not contain anysubstanceswhichare specified in SS-00259-1

2.Purch aseink, paint,wirerods andmoldingresins only from t hebusinesspartners thatSony approvesas Green Partners.

118

CN13

CN13

DQ0

DQ1

VDD10

VDD11

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

TYC_1-1734074-1_5.2

TYC_1-1734074-1_5.2

132

128

4

FollowAMD schematic,changeDIMM2SPD Address from0xA4 to 0xA2

MEM_MB_ADD[0..15]<5,8> MEM_MB_DATA[0..63] <5>

MEM_MA_DATA0

5

MEM_MA_DATA1

7

MEM_MA_DATA2

17

MEM_MA_DATA3

19

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA6

14

MEM_MA_DATA7

16

MEM_MA_DATA8

23

MEM_MA_DATA9

25

MEM_MA_DATA10

35

MEM_MA_DATA11

37

MEM_MA_DATA12

20

MEM_MA_DATA13

22

MEM_MA_DATA14

36

MEM_MA_DATA15

38

MEM_MA_DATA16

43

MEM_MA_DATA17

45

MEM_MA_DATA18

55

MEM_MA_DATA19

57

MEM_MA_DATA20

44

MEM_MA_DATA21

46

MEM_MA_DATA22

56

MEM_MA_DATA23

58

MEM_MA_DATA24

61

MEM_MA_DATA25

63

MEM_MA_DATA26

73

MEM_MA_DATA27

75

MEM_MA_DATA28

62

MEM_MA_DATA29

64

MEM_MA_DATA30

74

MEM_MA_DATA31

76

MEM_MA_DATA36

123

MEM_MA_DATA37

125

MEM_MA_DATA35

135

MEM_MA_DATA39

137

MEM_MA_DATA38

124

MEM_MA_DATA32

126

MEM_MA_DATA33

134

MEM_MA_DATA34

136

MEM_MA_DATA40

141

MEM_MA_DATA41

143

MEM_MA_DATA46

151

MEM_MA_DATA47

153

MEM_MA_DATA44

140

MEM_MA_DATA45

142

MEM_MA_DATA42

152

MEM_MA_DATA43

154

MEM_MA_DATA52

157

MEM_MA_DATA49

159

MEM_MA_DATA54

173

MEM_MA_DATA55

175

MEM_MA_DATA53

158

MEM_MA_DATA48

160

MEM_MA_DATA51

174

MEM_MA_DATA50

176

MEM_MA_DATA61

179

MEM_MA_DATA60

181

MEM_MA_DATA63

189

MEM_MA_DATA62

191

MEM_MA_DATA56

180

MEM_MA_DATA57

182

MEM_MA_DATA58

192

MEM_MA_DATA59

194

MEMHOT_SODIMM#_1

50

MEM_MA_RESET#1

69

83

120

MEM_MA_NC5

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

+0.9VSMVREF_DIMM

MEM_MB_BANK[0..2]<5,8>

MEM_MB_DM[0..7]<5>

T31T31

T202T202

MEM_MA0_C S#2 <5,8>

MEM_MA0_C S#3 <5,8>

T199T199

C188

C188

2.2u/10V_8

2.2u/10V_8

+0.9VSMVREF_DIMM+SMDDR_VREF

R120 short0402R120 short0402

change to short pad 4/21

4

MEM_MB_DQS0_P<5>

MEM_MB_DQS1_P<5>

MEM_MB_DQS2_P<5>

MEM_MB_DQS3_P<5>

MEM_MB_DQS4_P<5>

MEM_MB_DQS5_P<5>

MEM_MB_DQS6_P<5>

MEM_MB_DQS7_P<5>

MEM_MB_DQS0_N<5>

MEM_MB_DQS1_N<5>

MEM_MB_DQS2_N<5>

MEM_MB_DQS3_N<5>

MEM_MB_DQS4_N<5>

MEM_MB_DQS5_N<5>

MEM_MB_DQS6_N<5>

MEM_MB_DQS7_N<5>

MEM_MB_CLK1_P<5>

MEM_MB_CLK1_N<5>

MEM_MB_CLK7_P<5>

MEM_MB_CLK7_N<5>

MEM_MB_CKE0<5,8>

MEM_MB_CKE1<5,8>

MEM_MB_RAS#<5,8>

MEM_MB_CAS#<5,8>

MEM_MB_WE#<5,8>

MEM_MB0_CS#0<5,8>

MEM_MB0_CS#1<5,8>

MEM_MB0_ODT0<5,8>

MEM_MB0_ODT1<5,8>

+3V

C187

C187

0.1u/10V_4

0.1u/10V_4

1 2

+0.9VSMVREF_DIMM

3

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

DIM2_SA0

DIM2_SA1DIM1_SA0

DDRDAT_SMB

C3 0.1u/10V_4C3 0.1u/10V_4

C183

C183

1000p/50V_4

1000p/50V_4

+1.8VSUS

R119

R119

*2K/F_4

*2K/F_4

R121

R121

*2K/F_4

*2K/F_4

Only for reserved

3

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14

84

A15

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

+1.8VSUS

201

202

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

GNDPAD0

GNDPAD1

REVERSE

SPD Address:0xA2

(H=9.2)

59

SA_B: '0','1'

103

111

104

112

117

VDD8

VDD7

VDD9

VDD10

SO-DIMM

SO-DIMM

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

127

122

121

DIM2_SA0

DIM2_SA1

SMbus address A2

118

CN14

CN14

5

DQ0

7

DQ1

17

VDD11

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

NC/TEST

196

VSS56

193

VSS55

190

VSS54

187

VSS53

184

VSS52

183

VSS51

178

VSS50

177

VSS49

172

VSS48

171

VSS47

168

VSS46

165

VSS45

162

VSS44

161

VSS43

156

VSS42

155

VSS41

150

VSS40

149

VSS39

145

VSS38

144

VSS37

139

VSS36

138

VSS35

133

VSS34

VSS33

VSS32

TYC_2-1734073-2_9.2

TYC_2-1734073-2_9.2

132

128

R17 10K/F_4R17 10K/F_4

R15 10K/F_4R15 10K/F_4

2

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA45

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA44

MEM_MB_DATA41

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA60

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA61

MEM_MB_DATA57

MEM_MB_DATA62

MEM_MB_DATA63

MEMHOT_SODIMM#_2

MEM_MB_RESET#2

MEM_MB_NC5

2

1

07

+1.8VSUS

*10u/10V_8C463 *10u/10V_8C463

*10u_8C164 *10u_8C164

10u/10V_8C97 10u/10V_8C97

10u/10V_8C473 10u/10V_8C473

0.1u/10V_4C478 0.1u/10V_4C478

0.1u/10V_4C45 0.1u/10V_4C45

0.1u/10V_4C50 0.1u/10V_4C50

0.1u/10V_4C104 0.1u/10V_4C104

0.1u/10V_4C476 0.1u/10V_4C476

0.1u/10V_4C456 0.1u/10V_4C456

0.1u/10V_4C452 0.1u/10V_4C452

0.1u/10V_4C466 0.1u/10V_4C466

0.1u/10V_4C460 0.1u/10V_4C460

0.1u/10V_4C49 0.1u/10V_4C49

0.1u/10V_4C451 0.1u/10V_4C451

0.1u/10V_4C110 0.1u/10V_4C110

0.1u/10V_4C470 0.1u/10V_4C470

0.1u/10V_4C105 0.1u/10V_4C105

0.1u/10V_4C469 0.1u/10V_4C469

0.1u/10V_4C74 0.1u/10V_4C74

0.1u/10V_4C60 0.1u/10V_4C60

0.1u/10V_4C56 0.1u/10V_4C56

0.1u/10V_4C109 0.1u/10V_4C109

0.1u/10V_4C450 0.1u/10V_4C450

T32T32

T30T30

MEM_MB0_CS#2 <5,8>

MEM_MB0_CS#3 <5,8>

T4T4

+3V

R12

R12

Q5

Q5

2

*RHU002N06

*RHU002N06

PDAT_SMB<3,14,21,22>

PCLK_SMB<3,14,21,22>

3

3

1

R10 short0402R10 short0402

+3V

Q4

Q4

2

*RHU002N06

*RHU002N06

1

R8 short0402R8 short0402

change to short pad 4/22

PROJECT : Z08

PROJECT : Z08

+3V

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

DDRII SODIMM X 2

DDRII SODIMM X 2

DDRII SODIMM X 2

1

*10K_4

*10K_4

R5

*10K_4R5*10K_4

DDRDAT_SMB

DDRCLK_SMB

of

7Tuesday, April28,2009

7Tuesday, April28,2009

7Tuesday, April28,2009

1A

1A

1A

36

36

36

Page 8

5

4

3

2

1

CPU Thermal

VCC

DXP

DXN

LM86VCC

1

2

3

5

FANSIG<26>

+5V

C33 .1U_4C33 .1U_4

H_THERMDA

C29

C29

2200P/50V_4

2200P/50V_4

H_THERMDC

<check list>

Layout Note:Routing 10:10 mils and away

from noise source with ground gard

TH_FAN_POWER

C447

C447

C448

C448

.01U_4

.01U_4

10U_8

10U_8

R34

R34

10K_4

10K_4

FAN_PWM_CN

+SMDDR_VTERM

C443

C443

.01U_4

.01U_4

+3V

R358

R358

10K_4

10K_4

4pin H EADER

4pin H EADER

H_THERMDA <4>

H_THERMDC <4>

CN12

CN12

1

5

2

3

64

*10u/10V_8C1 *10u/10V_8C1

*10u/10V_8C7 *10u/10V_8C7

0.1u/10V_4C43 0.1u/10V_4C43

0.1u/10V_4C491 0.1u/10V_4C491

0.1u/10V_4C116 0.1u/10V_4C116

0.1u/10V_4C498 0.1u/10V_4C498

0.1u/10V_4C24 0.1u/10V_4C24

0.1u/10V_4C154 0.1u/10V_4C154

0.1u/10V_4C117 0.1u/10V_4C117

0.1u/10V_4C27 0.1u/10V_4C27

0.1u/10V_4C17 0.1u/10V_4C17

*0.1u/10V_4C28 *0.1u/10V_4C28

*0.1u/10V_4C123 *0.1u/10V_4C123

0.1u/10V_4C35 0.1u/10V_4C35

0.1u/10V_4C31 0.1u/10V_4C31

0.1u/10V_4C23 0.1u/10V_4C23

0.1u/10V_4C486 0.1u/10V_4C486

0.1u/10V_4C41 0.1u/10V_4C41

*0.1u/10V_4C493 *0.1u/10V_4C493

0.1u/10V_4C38 0.1u/10V_4C38

0.1u/10V_4C118 0.1u/10V_4C118

0.1u/10V_4C483 0.1u/10V_4C483

*0.1u/10V_4C138 *0.1u/10V_4C138

0.1u/10V_4C130 0.1u/10V_4C130

0.1u/10V_4C496 0.1u/10V_4C496

0.1u/10V_4C21 0.1u/10V_4C21

*0.1u/10V_4C20 *0.1u/10V_4C20

0.1u/10V_4C480 0.1u/10V_4C480

3

DDRII TERMINATION

MEM_MA_CKE0<5 ,7 >

MEM_MA_CKE1<5 ,7 >

MEM_MB_CKE0<5 ,7 >

MEM_MB_CKE1<5 ,7 >

MEM_MA0_O D T0<5,7>

MEM_MA0_O D T1<5,7>

MEM_MB0_O D T0<5,7>

MEM_MB0_O D T1<5,7>

MEM_MA_BANK0<5,7>

MEM_MA_BANK1<5,7>

MEM_MA_BANK2<5,7>

MEM_MA_WE#<5,7>

MEM_MA_CAS#<5 ,7 >

MEM_MA_RAS#<5 ,7 >

MEM_MB_BANK0<5,7>

MEM_MB_BANK1<5,7>

MEM_MB_BANK2<5,7>

MEM_MB_WE#<5,7>

MEM_MB_CAS#<5 ,7 >

MEM_MB_RAS#<5 ,7 >

MEM_MA0_CS # 0<5,7>

MEM_MA0_CS # 1<5,7>

MEM_MA0_CS # 2<5,7>

MEM_MA0_CS # 3<5,7>

MEM_MB0_CS # 0<5,7>

MEM_MB0_CS # 1<5,7>

MEM_MB0_CS # 2<5,7>

MEM_MB0_CS # 3<5,7>

MEM_MA_ADD[0..15]<5,7>

MEM_MB_ADD[0..15]<5,7>

+1.8VSUS

+SMDDR_VTERM

0.1u/10V_4C467 0.1u/10V_4C467

0.1u/10V_4C471 0.1u/10V_4C471

0.1u/10V_4C462 0.1u/10V_4C462

0.1u/10V_4C147 0.1u/10V_4C147

0.1u/10V_4C458 0.1u/10V_4C458

0.1u/10V_4C490 0.1u/10V_4C490

0.1u/10V_4C477 0.1u/10V_4C477

0.1u/10V_4C487 0.1u/10V_4C487

0.1u/10V_4C141 0.1u/10V_4C141

0.1u/10V_4C468 0.1u/10V_4C468

0.1u/10V_4C142 0.1u/10V_4C142

0.1u/10V_4C484 0.1u/10V_4C484

0.1u/10V_4C465 0.1u/10V_4C465

0.1u/10V_4C481 0.1u/10V_4C481

0.1u/10V_4C474 0.1u/10V_4C474

0.1u/10V_4C146 0.1u/10V_4C146

Please put the CAP between +1.8VSUS & +SMDDR_VTERM

2

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MA0_O D T0

MEM_MA0_O D T1

MEM_MB0_O D T0

MEM_MB0_O D T1

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_WE#

MEM_MA_CAS#

MEM_MA_RAS#

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_WE#

MEM_MB_CAS#

MEM_MB_RAS#

MEM_MA0_CS # 0

MEM_MA0_CS # 1

MEM_MA0_CS # 2

MEM_MA0_CS # 3

MEM_MB0_CS # 0

MEM_MB0_CS # 1

MEM_MB0_CS # 2

MEM_MB0_CS # 3

MEM_MA_ADD1 3

MEM_MA_ADD1 0

MEM_MA_ADD0

MEM_MA_ADD2

MEM_MA_ADD4

MEM_MA_ADD6

MEM_MA_ADD1 5

MEM_MA_ADD1 4

MEM_MA_ADD9

MEM_MA_ADD1 2

MEM_MA_ADD3

MEM_MA_ADD5

MEM_MA_ADD1

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD1 1

MEM_MB_ADD0

MEM_MB_ADD2

MEM_MB_ADD4

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD1 1

MEM_MB_ADD3

MEM_MB_ADD1

MEM_MB_ADD8

MEM_MB_ADD5

MEM_MB_ADD1 2

MEM_MB_ADD9

MEM_MB_ADD1 0

MEM_MB_ADD1 3

MEM_MB_ADD1 4

MEM_MB_ADD1 5

R56 47_4R56 47_4

R85 47_4R85 47_4

RP2 47_4P2R_4RP2 47_4P2R_4

RP4 47_4P2R_4RP4 47_4P2R_4

RP8 47_4P2R_4RP8 47_4P2R_4

RP1 47_4P2R_4RP1 47_4P2R_4

RP3 47_4P2R_4RP3 47_4P2R_4

RP5 47_4P2R_4RP5 47_4P2R_4

R73 47_4R73 47_4

R67 47_4R67 47_4

RP12 47_4P2R_4RP12 47_4P2R_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

R89 47_4R89 47_4

R94 47_4R94 47_4

R88 47_4R88 47_4

R93 47_4R93 47_4

R60 47_4R60 47_4

R48 47_4R48 47_4

R55 47_4R55 47_4

R53 47_4R53 47_4

R84 47_4R84 47_4

R78 47_4R78 47_4

R90 47_4R90 47_4

R83 47_4R83 47_4

R70 47_4R70 47_4

R75 47_4R75 47_4

R69 47_4R69 47_4

R77 47_4R77 47_4

R86 47_4R86 47_4

R63 47_4R63 47_4

R58 47_4R58 47_4

R71 47_4R71 47_4

R66 47_4R66 47_4

R46 47_4R46 47_4

R91 47_4R91 47_4

R52 47_4R52 47_4

R61 47_4R61 47_4

R49 47_4R49 47_4

R92 47_4R92 47_4

R51 47_4R51 47_4

2

1

RP1147_4P2R_4 RP1147_4P2R_4

4

3

2

1

RP1047_4P2R_4 RP1047_4P2R_4

4

3

2

1

RP1447_4P2R_4 RP1447_4P2R_4

4

3

2

1

RP1347_4P2R_4 RP1347_4P2R_4

4

3

2

1

RP647_4P2R_4 RP647_4P2R_4

4

3

2

1

RP747_4P2R_4 RP747_4P2R_4

4

3

2

1

RP947_4P2R_4 RP947_4P2R_4

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

PROJECT : Z08

PROJECT : Z08

PROJECT : Z08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

DDRII TERMINATION/THM/FAN

DDRII TERMINATION/THM/FAN

DDRII TERMINATION/THM/FAN

200_6

monitor

2ND_MBCLK<26>

2ND_MBDATA<26>

D D

THERM_ALERT#<4,15>

+3V

R35

R35

*8.2K_4

*8.2K_4

+3V

3

Q10 *2N7002E-LFQ10 *2N7002E-LF

R25 10K_4R25 10K_4

2ND_MBCLK

2ND_MBDATA

+3V

R24

R24

2

10K_4

10K_4

THERM_ALERT#_R

1

THER_OVERT#

+3V

8

7

6

4

200_6

R33

R33

U1

SCLK

SDA

ALERT#

OVERT#