Page 1

5

4

3

2

1

01

D D

Quanta Project Name: XM1

C C

Dell Project Name: Nike

G94 VGA

2008-03-17

REV : A1A

X01 Stage

B B

A A

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

COMPUTER

CoverPage

CoverPage

CoverPage

XM1 G92 VGA 1A

XM1 G92 VGA 1A

XM1 G92 VGA 1A

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

1

121

121

121

of

of

of

Page 2

1

2

3

4

5

6

7

8

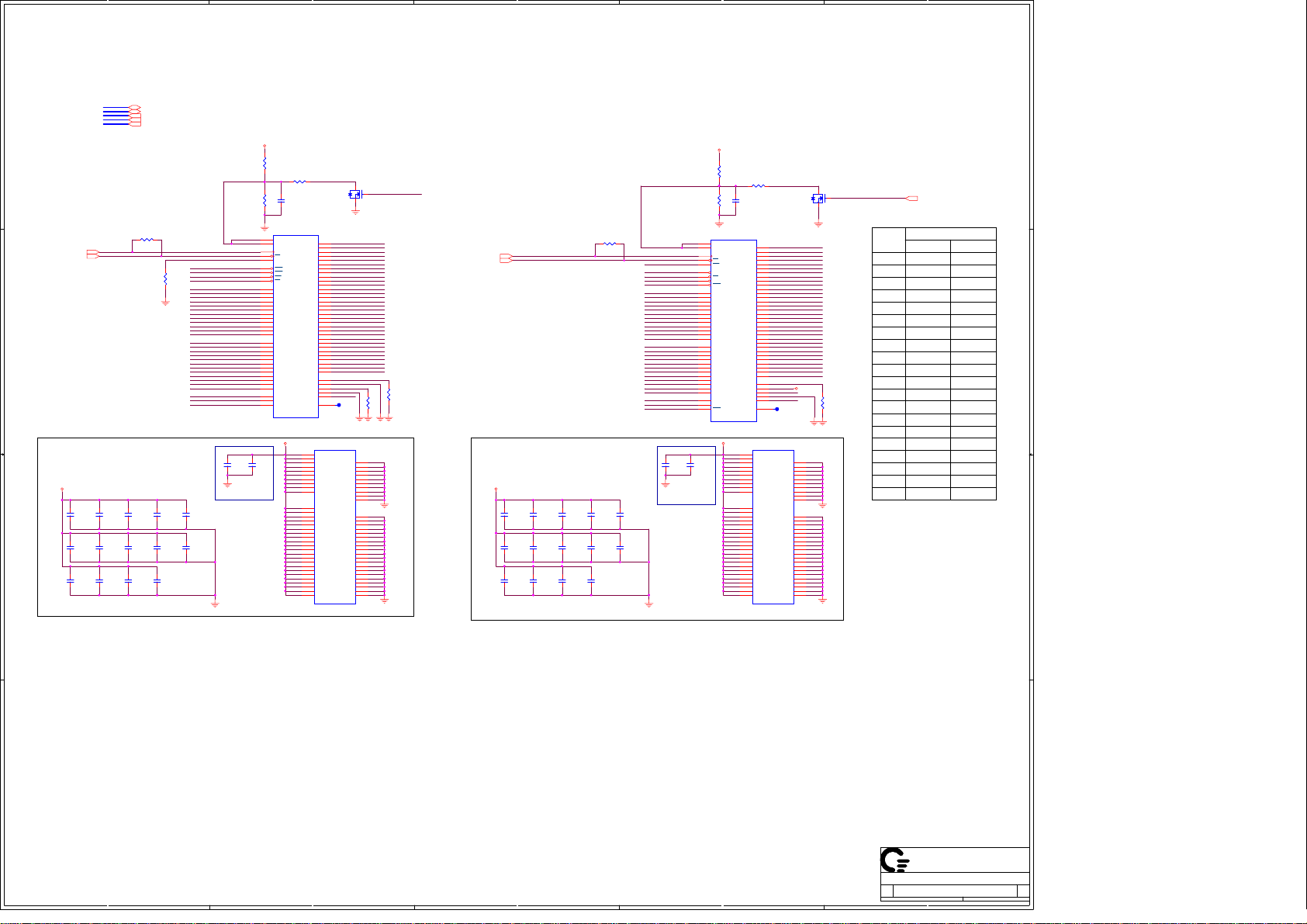

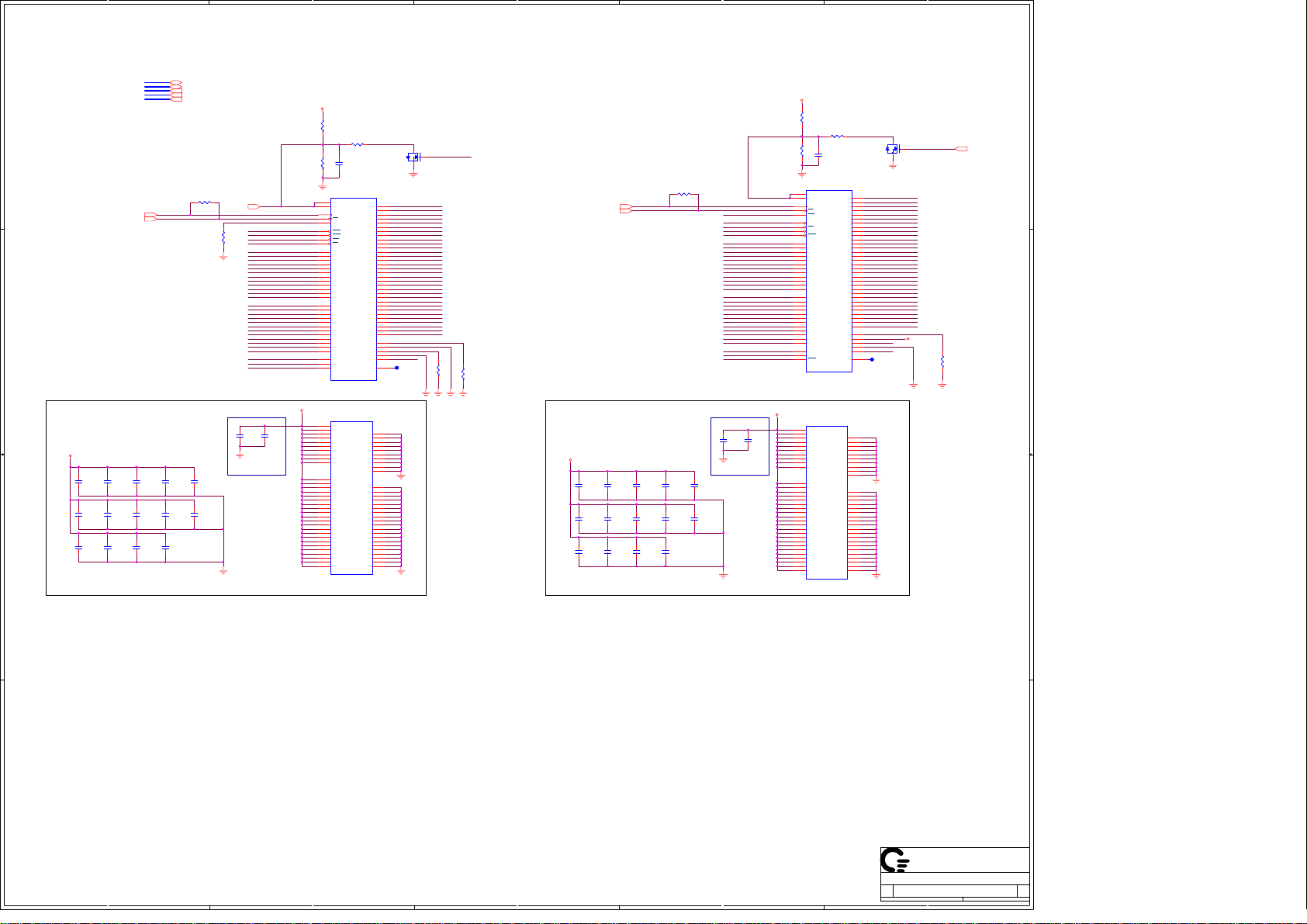

System Block Diagram for Nike G94 VGA

02

XM1 G94 PCBXM1 G94 PCB

A A

V-BIOS

SST25VF512 ADM1032ARMZ

PG 11

JTAGE

PG 11

Thermal IC

PG 18

LVDS Conn

IFPA/IFPBSPI

PG 13

GDDR3

Partition A

PG 6

B B

GFX card

Conn.

PEG

NB9E-GLM3 (G92)

1148 BGA

64 bit DATA

64 bit DATA

PG 3, 4, 5, 10, 11, 12,

13, 14, 16, 17, 18, 19

64 bit DATA

64 bit DATA

PG 3

CRT

DisplayPort(1st.)

DisplayPort(2nd.)

C C

GDDR3

Partition B

PG 7

GDDR3

Partition C

PG 8

GDDR3

Partition D

PG 9

POWER

DC/DC

1.1V_GFX PCIE and 1.8V_MEM

VCORE

NV_VCORE

D D

1

2

3

PG 20

PG 21

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

4

5

6

Date: Sheet

COMPUTER

System Block Diagram

System Block Diagram

System Block Diagram

XM1 G92 VGA 1A

XM1 G92 VGA 1A

XM1 G92 VGA 1A

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

7

of

of

of

221

221

221

8

Page 3

A B C D E F G H

PEX Conn + GPU PEX

03

1

C267

C267

4.7U

4.7U

C258

C258

0.1U

0.1U

C255

C255

0.1U

0.1U

+3.3V_RUN

C293

C293

0.01U

0.01U

+1.1V_GFX_PCIE

C294

C294

22U

22U

C392

C392

0.1U

0.1U

+1.1V_GFX_PCIE

C249

C249

C393

C393

C273

4.7U

4.7U

C2841UC284

1U

NVVDD_SENSE 21

GND_SENSE 21

C273

4.7U

4.7U

22U

22U

C287

C287

C242

C242

0.1U

0.1U

0.1U

0.1U

L5

1.2V12MIL

C26

C26

C28

C28

4.7U

4.7U

0.1U

0.1U

Title

Title

Title

G92_PCIe_&_POWER

G92_PCIe_&_POWER

G92_PCIe_&_POWER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

XM1 G92 VGA 1A

XM1 G92 VGA 1A

XM1 G92 VGA 1A

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

Date: Sheet

Date: Sheet

Date: Sheet

0.01uHL50.01uH

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

+1.1V_GFX_PCIE

321

321

321

HFDBA

of

of

of

JVDO1

JVDO1

1

2

3

SBAT_SMBCLK13,18

SBAT_SMBDAT13,18

+3.3V_RUN

2

3

4

5

DP_TX0+15

DP_TX0-15

DP_TX1+15

DP_TX1-15

DP_TX2+15

DP_TX2-15

DP_TX3+15

DP_TX3-15

DP_AUX+15

DP_AUX-15

DP2_TX0+14

DP2_TX0-14

DP2_TX1+14

DP2_TX1-14

DP2_TX2+14

DP2_TX2-14

DP2_TX3+14

DP2_TX3-14

DP2_AUX+14

DP2_AUX-14

RUNPWROK20,21

PCIE_MRX_GTX_C_P0

PCIE_MRX_GTX_C_N0

PCIE_MRX_GTX_C_P1

PCIE_MRX_GTX_C_N1

PCIE_MRX_GTX_C_P2

PCIE_MRX_GTX_C_N2

PCIE_MRX_GTX_C_P3

PCIE_MRX_GTX_C_N3

PCIE_MRX_GTX_C_P4

PCIE_MRX_GTX_C_N4

PCIE_MRX_GTX_C_P5

PCIE_MRX_GTX_C_N5

PCIE_MRX_GTX_C_P6

PCIE_MRX_GTX_C_N6

PCIE_MRX_GTX_C_P7

PCIE_MRX_GTX_C_N7

PCIE_MRX_GTX_C_P8

PCIE_MRX_GTX_C_N8

PCIE_MRX_GTX_C_P9

PCIE_MRX_GTX_C_N9

PCIE_MRX_GTX_C_P10

PCIE_MRX_GTX_C_N10

PCIE_MRX_GTX_C_P11

PCIE_MRX_GTX_C_N11

PCIE_MRX_GTX_C_P12

PCIE_MRX_GTX_C_N12

PCIE_MRX_GTX_C_P13

PCIE_MRX_GTX_C_N13

PCIE_MRX_GTX_C_P14

PCIE_MRX_GTX_C_N14

PCIE_MRX_GTX_C_P15

PCIE_MRX_GTX_C_N15

+15V_ALW

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

LPF-SC200SFYG+

LPF-SC200SFYG+

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

15

GFX_CARD_DET#

R45 0R45 0

R44 0R44 0

+5V_ALW

C358

C358

0.1U

0.1U

R59 0R59 0

R39 0R39 0

GFX_CARD_DET#

PCIE_MTX_GRX_P0

PCIE_MTX_GRX_N0

PCIE_MTX_GRX_P1

PCIE_MTX_GRX_N1

PCIE_MTX_GRX_P2

PCIE_MTX_GRX_N2

PCIE_MTX_GRX_P3

PCIE_MTX_GRX_N3

PCIE_MTX_GRX_P4

PCIE_MTX_GRX_N4

PCIE_MTX_GRX_P5

PCIE_MTX_GRX_N5

PCIE_MTX_GRX_P6

PCIE_MTX_GRX_N6

PCIE_MTX_GRX_P7

PCIE_MTX_GRX_N7

PCIE_MTX_GRX_P8

PCIE_MTX_GRX_N8

PCIE_MTX_GRX_P9

PCIE_MTX_GRX_N9

PCIE_MTX_GRX_P10

PCIE_MTX_GRX_N10

PCIE_MTX_GRX_P11

PCIE_MTX_GRX_N11

PCIE_MTX_GRX_P12

PCIE_MTX_GRX_N12

PCIE_MTX_GRX_P13

PCIE_MTX_GRX_N13

PCIE_MTX_GRX_P14

PCIE_MTX_GRX_N14

PCIE_MTX_GRX_P15

PCIE_MTX_GRX_N15

CLK_PCIE_VGA

CLK_PCIE_VGA#

PCIE_RST#

GFX_CARD_DET#

R19 *0_NCR19 *0_NC

C356

C356

C361

C361

0.1U

0.1U

0.1U

0.1U

LCD_TST 13

LCD_VCC_EN 13

THERM_ALRT# 18

FP_BACK_EN 13

R46 0R46 0

+3.3V_SUS

DP_HP_DET 15

DP_CA_DET 15

DP2_HP_DET 14

DP2_CA_DET 14

CLK_DDC2 12

DAT_DDC2 12

VGA_BLU 12

VGA_GRN 12

VGA_RED 12

VGAVSYNC 12

VGAHSYNC 12

ACAV_IN_MB/DOCK 18

PNL_BKLT_CBL_DET# 13

LVDS_CBL_DET# 13

SPDIF_DP 11

C GE

+G_PWR_SRC

C362

C362

C78

C78

0.1U

0.1U

10U

10U

PLTRST#.

PCIE_RST#

CLK_PCIE_VGA

CLK_PCIE_VGA#

PCIE_MRX_GTX_C_P0

PCIE_MRX_GTX_C_N0

PCIE_MTX_GRX_P0

PCIE_MTX_GRX_N0

PCIE_MRX_GTX_C_P1

PCIE_MRX_GTX_C_N1

PCIE_MTX_GRX_P1

PCIE_MTX_GRX_N1

PCIE_MRX_GTX_C_P2

PCIE_MRX_GTX_C_N2

PCIE_MTX_GRX_P2

PCIE_MTX_GRX_N2

PCIE_MRX_GTX_C_P3

PCIE_MRX_GTX_C_N3

PCIE_MTX_GRX_P3

PCIE_MTX_GRX_N3

PCIE_MRX_GTX_C_P4

PCIE_MRX_GTX_C_N4

PCIE_MTX_GRX_P4

PCIE_MTX_GRX_N4

PCIE_MRX_GTX_C_P5

PCIE_MRX_GTX_C_N5

PCIE_MTX_GRX_P5

PCIE_MTX_GRX_N5

PCIE_MRX_GTX_C_P6

PCIE_MRX_GTX_C_N6

PCIE_MTX_GRX_P6

PCIE_MTX_GRX_N6

PCIE_MRX_GTX_C_P7

PCIE_MRX_GTX_C_N7

PCIE_MTX_GRX_P7

PCIE_MTX_GRX_N7

PCIE_MRX_GTX_C_P8

PCIE_MRX_GTX_C_N8

PCIE_MTX_GRX_P8

PCIE_MTX_GRX_N8

PCIE_MRX_GTX_C_P9

PCIE_MRX_GTX_C_N9

PCIE_MTX_GRX_P9

PCIE_MTX_GRX_N9

PCIE_MRX_GTX_C_P10

PCIE_MRX_GTX_C_N10

PCIE_MTX_GRX_P10

PCIE_MTX_GRX_N10

PCIE_MRX_GTX_C_P11

PCIE_MRX_GTX_C_N11

PCIE_MTX_GRX_P11

PCIE_MTX_GRX_N11

PCIE_MRX_GTX_C_P12

PCIE_MRX_GTX_C_N12

PCIE_MTX_GRX_P12

PCIE_MTX_GRX_N12

PCIE_MRX_GTX_C_P13

PCIE_MRX_GTX_C_N13

PCIE_MTX_GRX_P13

PCIE_MTX_GRX_N13

PCIE_MRX_GTX_C_P14

PCIE_MRX_GTX_C_N14

PCIE_MTX_GRX_P14

PCIE_MTX_GRX_N14

PCIE_MRX_GTX_C_P15

PCIE_MRX_GTX_C_N15

PCIE_MTX_GRX_P15

PCIE_MTX_GRX_N15

C65 0.1UC65 0.1U

C61 0.1UC61 0.1U

C57 0.1UC57 0.1U

C54 0.1UC54 0.1U

C52 0.1UC52 0.1U

C50 0.1UC50 0.1U

C48 0.1UC48 0.1U

C46 0.1UC46 0.1U

C43 0.1UC43 0.1U

C41 0.1UC41 0.1U

C39 0.1UC39 0.1U

C37 0.1UC37 0.1U

C34 0.1UC34 0.1U

C33 0.1UC33 0.1U

C31 0.1UC31 0.1U

C27 0.1UC27 0.1U

R155 0R155 0

C62 0.1UC62 0.1U

C58 0.1UC58 0.1U

C55 0.1UC55 0.1U

C53 0.1UC53 0.1U

C51 0.1UC51 0.1U

C49 0.1UC49 0.1U

C47 0.1UC47 0.1U

C45 0.1UC45 0.1U

C42 0.1UC42 0.1U

C40 0.1UC40 0.1U

C38 0.1UC38 0.1U

C36 0.1UC36 0.1U

C35 0.1UC35 0.1U

C32 0.1UC32 0.1U

C30 0.1UC30 0.1U

C25 0.1UC25 0.1U

PEX_TX0

PEX_TX0#

PEX_TX1

PEX_TX1#

PEX_TX2

PEX_TX2#

PEX_TX3

PEX_TX3#

PEX_TX4

PEX_TX4#

PEX_TX5

PEX_TX5#

PEX_TX6

PEX_TX6#

PEX_TX7

PEX_TX7#

PEX_TX8

PEX_TX8#

PEX_TX9

PEX_TX9#

PEX_TX10

PEX_TX10#

PEX_TX11

PEX_TX11#

PEX_TX12

PEX_TX12#

PEX_TX13

PEX_TX13#

PEX_TX14

PEX_TX14#

PEX_TX15

PEX_TX15#

AW10

AW11

AW12

AW13

AW14

AW15

AW16

AW17

AW18

AW19

AW20

AW21

AW22

AW23

AW24

AW25

AW26

AW27

AY10

AU13

AV13

AY12

BA12

BB12

BB13

AV15

BA13

AY13

AV16

AY15

BA15

BB15

BB16

AV18

AU18

BA16

AY16

AV19

AY18

BA18

BB18

BB19

AV21

AU21

BA19

AY19

AV22

AY21

BA21

BB21

BB22

AV24

AU24

BA22

AY22

AU25

AV25

AY24

BA24

BB24

BB25

AV27

BA25

AY25

AU27

AT27

AY27

BA27

G1A

G1A

bga1504-nvidia-nb9e-glm2

bga1504-nvidia-nb9e-glm2

COMMON

COMMON

1/19 PCI_EXPRESS

1/19 PCI_EXPRESS

PEX_RST

PEX_CLKREQ

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

VDD33

VDD33

VDD33

VDD33

VDD33

VDD_SENSE

GND_SENSE

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_PLLVDD

TESTMODE

PEX_CAL_PD_VDDQ

PEX_CAL_PU_GND

PEX_TERMP

AT18

AT24

AT25

AU15

AU16

AU19

AU22

AM17

AM18

AM19

AM20

AM24

AM25

AM26

AM27

AM28

AP18

AP19

AP21

AP22

AP24

AP25

AP27

AR15

AR16

AR18

AR19

AR21

AR22

AR24

AR25

AR27

AT15

AT16

AT19

AT21

AT22

L11

L12

L13

M11

N11

NVVDD_SENSE_R

AJ22

AJ21

AP16

AP17

AM16

BB27

AM21

AM22

AM23

C2741UC274

1U

C286

C286

0.1U

0.1U

C268

C268

0.1U

0.1U

GND_SENSE_R

R153 200R153 200

R234 10KR234 10K

R235 2.49KR235 2.49K

R236 2.49KR236 2.49K

R237 2.49KR237 2.49K

C2911UC291

1U

C259

C259

0.1U

0.1U

C2601UC260

1U

C247

C247

0.1U

0.1U

C308

C308

0.1U

0.1U

R40 0R40 0

R43 0R43 0

PEX_PLLDVDD

C2721UC272

1U

C309

C309

0.1U

0.1U

+1.1V_GFX_PCIE

1

2

3

4

5

Page 4

A B C D E F G H

FrameBuffer - GPU Partition A/B

FBA_CMD[27..0] 6

FBA_D[63..0] 6

FBA_DQM[7..0] 6

FBA_DQS_RN[7..0] 6

FBA_DQS_WP[7..0] 6

1

2

3

4

T138 PADT138 PAD

T140 PADT140 PAD

T142 PADT142 PAD

T136 PADT136 PAD

T137 PADT137 PAD

T139 PADT139 PAD

T141 PADT141 PAD

T143 PADT143 PAD

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM4

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

FB_VREF

AL34

AK35

AK36

AJ34

AH34

AH35

AJ36

AK37

AL39

AL41

AL42

AK42

AJ39

AH39

AH41

AH42

AN35

AP36

AP37

AR37

AM34

AL35

AL36

AL37

AP41

AP42

AN39

AN40

AN41

AN42

AR40

AT39

AR31

AP32

AR33

AT31

AT34

AU34

AU35

AU31

BB33

BA33

AY33

BA34

BB34

AW33

AW36

AY35

AU30

AP28

AP31

AR28

AW28

AP29

AR30

AT30

AW31

BA31

BB31

BB30

AW29

BB28

BA28

AY28

AJ37

AM39

AP35

AP40

AR34

AY34

AU29

AW32

AH36

AK41

AM36

AP38

AT33

AV34

AT28

AY30

AH37

AK40

AN36

AP39

AT32

AW34

AU28

BA30

AH38

AL38

AN38

AR39

AV33

AW35

AT29

AV31

L32

G1B

G1B

bga1504-nvidia-nb9e-glm2

bga1504-nvidia-nb9e-glm2

COMMON

COMMON

2/19 FBA

2/19 FBA

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM4

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

FBA_DBI0

FBA_DBI1

FBA_DBI2

FBA_DBI3

FBA_DBI4

FBA_DBI5

FBA_DBI6

FBA_DBI7

FB_VREF

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_DEBUG

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK0

FBA_WCK0

FBA_WCK1

FBA_WCK1

FBA_WCK2

FBA_WCK2

FBA_WCK3

FBA_WCK3

FB_DLLAVDD0

FB_PLLAVDD0

G1C

C40

E39

F37

H37

G38

G39

G40

H39

C41

D40

D41

C42

D42

H40

G41

G42

J37

K37

J38

J39

L36

M34

M35

M36

J40

J41

J42

K39

L39

M38

M39

M40

W35

W36

W37

W38

AA34

AA35

AA36

AA37

W40

AA40

AA41

AA42

AB40

AB41

AB42

AD40

AB34

AB35

AB36

AB37

AE35

AE36

AE37

AG36

AD41

AD42

AE38

AF39

AE42

AG40

AG41

AG42

G37

F41

L37

K42

AA38

AC39

AE34

AE41

F39

F40

K35

K41

Y39

AB39

AD36

AE40

F38

E40

K36

K40

W39

AB38

AD35

AE39

H36

F42

L34

K38

AA39

AD39

AG35

AG39

G1C

bga1504-nvidia-nb9e-glm2

bga1504-nvidia-nb9e-glm2

COMMON

COMMON

3/19 FBB

3/19 FBB

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_RN7

FBB_DBI0

FBB_DBI1

FBB_DBI2

FBB_DBI3

FBB_DBI4

FBB_DBI5

FBB_DBI6

FBB_DBI7

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_DEBUG

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_WCK0

FBB_WCK0

FBB_WCK1

FBB_WCK1

FBB_WCK2

FBB_WCK2

FBB_WCK3

FBB_WCK3

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

FBB_CMD[27..0] 7

L2

INDUCTORL2INDUCTOR

FBB_D[63..0] 7

FBB_DQM[7..0] 7

FBB_DQS_RN[7..0] 7

FBB_DQS_WP[7..0] 7

+1.1V_GFX_PCIE

T146 PADT146 PAD

T148 PADT148 PAD

T150 PADT150 PAD

T144 PADT144 PAD

T145 PADT145 PAD

T147 PADT147 PAD

T149 PADT149 PAD

T151 PADT151 PAD

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_RN7

+1.8V_RUN +1.8V_RUN

AA32

AB32

AC32

AD32

AD34

AE32

AF32

AG32

AG34

AK34

AN34

AP30

AP33

J10

J13

J16

J19

J24

J27

J30

FBA_CMD0

AT40

FBA_CMD1

AU38

FBA_CMD2

AT38

FBA_CMD3

BA39

FBA_CMD4

AV37

FBA_CMD5

BB39

FBA_CMD6

AW38

SNN_FBA_CMD7

AW42

AW39

AY41

AU39

AV36

BA40

AY39

AU40

BA37

AY36

AY37

AT37

AU36

AV39

AY38

AV40

AU42

AW40

AU41

AW41

BB37

AW37

AY42

BB40

AT36

AT41

AT42

BA36

BB36

AK38

AK39

AM37

AN37

AU32

AU33

AV30

AW30

AH32

AJ32

SNN_FBA_CMD26

SNN_FBA_CMD28

SNN_FBA_CMD29

SNN_FBA_CMD30

FBA_DEBUG

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD27

FBA_CLK0

FBA_CLK0#

FBA_CLK1

FBA_CLK1#

FBA_PLLAVDD

T55PAD T55PAD

T23PAD T23PAD

T58PAD T58PAD

T32PAD T32PAD

T28PAD T28PAD

+1.8V_RUN

R137

R137

60.4

60.4

Place Components

Close to the GPU

FBA_CLK0 6

FBA_CLK0# 6

FBA_CLK1 6

FBA_CLK1# 6

T128PAD T128PAD

T129PAD T129PAD

T130PAD T130PAD

T131PAD T131PAD

T132PAD T132PAD

T133PAD T133PAD

T134PAD T134PAD

T135PAD T135PAD

C14

C229

C229

C228

C228

0.1U

0.1U

0.1U

0.1U

C14

C151UC15

4.7U

4.7U

1U

J33

K34

K9

L17

L18

L19

L20

L23

L24

L25

L26

L27

N41

R39

N42

V37

T41

T42

V38

R38

N40

U39

N39

V40

R41

V39

P39

V36

V41

T39

T38

T35

T36

T40

R37

M41

T37

M42

R36

V35

V42

R42

R40

R34

N37

N38

U34

V34

J35

J36

N35

N36

W41

W42

AD37

AD38

M32

N32

P32

SNN_FBB_CMD7

SNN_FBB_CMD26

SNN_FBB_CMD28

SNN_FBB_CMD29

SNN_FBB_CMD30

FBB_DEBUG

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD27

FBB_CLK0

FBB_CLK0#

FBB_CLK1

FBB_CLK1#

T27PAD T27PAD

T26PAD T26PAD

T24PAD T24PAD

T25PAD T25PAD

T29PAD T29PAD

FBB_CLK0 7

FBB_CLK0# 7

FBB_CLK1 7

FBB_CLK1# 7

T154PAD T154PAD

T156PAD T156PAD

T158PAD T158PAD

T152PAD T152PAD

T153PAD T153PAD

T155PAD T155PAD

T157PAD T157PAD

T159PAD T159PAD

19

R136 49.9

R136 49.9

R141 30.9

R141 30.9

R138 40.2

R138 40.2

+1.8V_RUN

1%

1%

1%

1%

1%

1%

R12

R12

60.4

60.4

+1.8V_RUN

04

1

2

3

4

+1.8V_RUN

R10

1.26V

R10

1.05K

1.05K

FB_VREF

R22

R22

C17

C17

2.49K

2.49K

0.01U

0.01U

DYNAMIC FB VREF SWITCHING SELECT

R11

GPIO10_FB_VREF_SW18

GPIO10_FB_VREF_SW GPIO10_FB_VREF_SW_R

Remove series resistor to disable

dynamic FB_VREF switching and set

FBVREF at 0.7*FBVDDQ (GPU and VRAM)

0

R520R52

R21

R21

10K

10K

R11

1.82K

1.82K

31

Q6

2

2N7002W-7-FQ62N7002W-7-F

55

GPIO10_FB_VREF_SW_R 6,7,8,9

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

FB_Partition_A/B

FB_Partition_A/B

FB_Partition_A/B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

XM1 G92 VGA 1A

XM1 G92 VGA 1A

XM1 G92 VGA 1A

Date: Sheet

Date: Sheet

Date: Sheet

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

421

421

421

of

of

of

Page 5

A B C D E F G H

FrameBuffer - GPU Partition C/D

05

1

2

3

4

5

FBC_CMD[27..0] 8

FBC_D[63..0] 8

FBC_DQM[7..0] 8

FBC_DQS_RN[7..0] 8

FBC_DQS_WP[7..0] 8

T162 PADT162 PAD

T164 PADT164 PAD

T166 PADT166 PAD

T160 PADT160 PAD

T161 PADT161 PAD

T163 PADT163 PAD

T165 PADT165 PAD

T167 PADT167 PAD

FBC_D0

FBC_D1

FBC_D2

FBC_D3

FBC_D4

FBC_D5

FBC_D6

FBC_D7

FBC_D8

FBC_D9

FBC_D10

FBC_D11

FBC_D12

FBC_D13

FBC_D14

FBC_D15

FBC_D16

FBC_D17

FBC_D18

FBC_D19

FBC_D20

FBC_D21

FBC_D22

FBC_D23

FBC_D24

FBC_D25

FBC_D26

FBC_D27

FBC_D28

FBC_D29

FBC_D30

FBC_D31

FBC_D32

FBC_D33

FBC_D34

FBC_D35

FBC_D36

FBC_D37

FBC_D38

FBC_D39

FBC_D40

FBC_D41

FBC_D42

FBC_D43

FBC_D44

FBC_D45

FBC_D46

FBC_D47

FBC_D48

FBC_D49

FBC_D50

FBC_D51

FBC_D52

FBC_D53

FBC_D54

FBC_D55

FBC_D56

FBC_D57

FBC_D58

FBC_D59

FBC_D60

FBC_D61

FBC_D62

FBC_D63

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQM4

FBC_DQM5

FBC_DQM6

FBC_DQM7

FBC_DQS_WP0

FBC_DQS_WP1

FBC_DQS_WP2

FBC_DQS_WP3

FBC_DQS_WP4

FBC_DQS_WP5

FBC_DQS_WP6

FBC_DQS_WP7

FBC_DQS_RN0

FBC_DQS_RN1

FBC_DQS_RN2

FBC_DQS_RN3

FBC_DQS_RN4

FBC_DQS_RN5

FBC_DQS_RN6

FBC_DQS_RN7

J21

H21

G21

F21

F18

G18

H18

G16

B16

A16

B19

A19

D17

E18

A18

C16

H24

G24

F24

E24

J22

H22

G22

F22

C24

C22

B22

A22

C21

B21

A21

C19

F34

F33

E34

D34

G32

J31

H31

G31

C34

B34

A34

D33

D32

E31

D31

C31

D39

D38

G36

F35

E36

D36

C36

D35

B40

C39

B39

A40

A39

C35

B36

A36

J18

B18

E22

D20

F32

A33

F36

B37

G19

C18

D23

D21

H33

B33

D37

C37

H19

D18

D24

E21

G33

C33

E37

C38

H16

D16

D22

D19

J32

E33

G35

A37

G1D

G1D

bga1504-nvidia-nb9e-glm2

bga1504-nvidia-nb9e-glm2

COMMON

COMMON

4/19 FBC

4/19 FBC

FBC_D0

FBC_D1

FBC_D2

FBC_D3

FBC_D4

FBC_D5

FBC_D6

FBC_D7

FBC_D8

FBC_D9

FBC_D10

FBC_D11

FBC_D12

FBC_D13

FBC_D14

FBC_D15

FBC_D16

FBC_D17

FBC_D18

FBC_D19

FBC_D20

FBC_D21

FBC_D22

FBC_D23

FBC_D24

FBC_D25

FBC_D26

FBC_D27

FBC_D28

FBC_D29

FBC_D30

FBC_D31

FBC_D32

FBC_D33

FBC_D34

FBC_D35

FBC_D36

FBC_D37

FBC_D38

FBC_D39

FBC_D40

FBC_D41

FBC_D42

FBC_D43

FBC_D44

FBC_D45

FBC_D46

FBC_D47

FBC_D48

FBC_D49

FBC_D50

FBC_D51

FBC_D52

FBC_D53

FBC_D54

FBC_D55

FBC_D56

FBC_D57

FBC_D58

FBC_D59

FBC_D60

FBC_D61

FBC_D62

FBC_D63

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQM4

FBC_DQM5

FBC_DQM6

FBC_DQM7

FBC_DQS_WP0

FBC_DQS_WP1

FBC_DQS_WP2

FBC_DQS_WP3

FBC_DQS_WP4

FBC_DQS_WP5

FBC_DQS_WP6

FBC_DQS_WP7

FBC_DQS_RN0

FBC_DQS_RN1

FBC_DQS_RN2

FBC_DQS_RN3

FBC_DQS_RN4

FBC_DQS_RN5

FBC_DQS_RN6

FBC_DQS_RN7

FBC_DBI0

FBC_DBI1

FBC_DBI2

FBC_DBI3

FBC_DBI4

FBC_DBI5

FBC_DBI6

FBC_DBI7

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBC_CMD0

FBC_CMD1

FBC_CMD2

FBC_CMD3

FBC_CMD4

FBC_CMD5

FBC_CMD6

FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD25

FBC_CMD26

FBC_CMD27

FBC_CMD28

FBC_CMD29

FBC_CMD30

FBC_DEBUG

FBC_CLK0

FBC_CLK0

FBC_CLK1

FBC_CLK1

FBC_WCK0

FBC_WCK0

FBC_WCK1

FBC_WCK1

FBC_WCK2

FBC_WCK2

FBC_WCK3

FBC_WCK3

FB_DLLAVDD1

FB_PLLAVDD1

+1.8V_RUN

N34

N9

R32

T32

T34

U32

V32

W32

W34

Y32

FBC_CMD0

C25

FBC_CMD1

A27

FBC_CMD2

E25

FBC_CMD3

D30

FBC_CMD4

D28

FBC_CMD5

E28

FBC_CMD6

G27

SNN_FBC_CMD7

D27

FBC_CMD8

C30

FBC_CMD9

B28

FBC_CMD10

B25

FBC_CMD11

A30

FBC_CMD12

D26

FBC_CMD13

F27

FBC_CMD14

F25

FBC_CMD15

B31

FBC_CMD16

B30

FBC_CMD17

D29

FBC_CMD18

A28

FBC_CMD19

E27

FBC_CMD20

C27

FBC_CMD21

G28

FBC_CMD22

B27

FBC_CMD23

G25

FBC_CMD24

H27

FBC_CMD25

H25

SNN_FBC_CMD26

A25

FBC_CMD27

A31

SNN_FBC_CMD28

F28

SNN_FBC_CMD29

C28

SNN_FBC_CMD30

D25

FBC_DEBUG

J28

FBC_CLK0

J26

FBC_CLK0#

J25

FBC_CLK1

F30

FBC_CLK1#

E30

F19

E19

B24

A24

H30

G30

H34

G34

L21

FBC_PLLAVDD

L22

C324

C324

0.1U

0.1U

C GE

T176PAD T176PAD

T60PAD T60PAD

T66PAD T66PAD

T177PAD T177PAD

T178PAD T178PAD

FBC_CLK0 8

FBC_CLK0# 8

FBC_CLK1 8

FBC_CLK1# 8

T170PAD T170PAD

T172PAD T172PAD

T174PAD T174PAD

T168PAD T168PAD

T169PAD T169PAD

T171PAD T171PAD

T173PAD T173PAD

T175PAD T175PAD

12MIL 1.2V

C311

C311

C3541UC354

0.1U

0.1U

1U

+1.8V_RUN

R142

R142

60.4

60.4

+1.1V_GFX_PCIE

L13

L13

INDUCTOR

INDUCTOR

C348

C348

4.7U

4.7U

FBD_CMD[27..0] 9

FBD_D[63..0] 9

FBD_DQM[7..0] 9

FBD_DQS_RN[7..0] 9

FBD_DQS_WP[7..0] 9

T181 PADT181 PAD

T183 PADT183 PAD

T185 PADT185 PAD

T179 PADT179 PAD

T180 PADT180 PAD

T182 PADT182 PAD

T184 PADT184 PAD

T186 PADT186 PAD

FBD_D0

FBD_D1

FBD_D2

FBD_D3

FBD_D4

FBD_D5

FBD_D6

FBD_D7

FBD_D8

FBD_D9

FBD_D10

FBD_D11

FBD_D12

FBD_D13

FBD_D14

FBD_D15

FBD_D16

FBD_D17

FBD_D18

FBD_D19

FBD_D20

FBD_D21

FBD_D22

FBD_D23

FBD_D24

FBD_D25

FBD_D26

FBD_D27

FBD_D28

FBD_D29

FBD_D30

FBD_D31

FBD_D32

FBD_D33

FBD_D34

FBD_D35

FBD_D36

FBD_D37

FBD_D38

FBD_D39

FBD_D40

FBD_D41

FBD_D42

FBD_D43

FBD_D44

FBD_D45

FBD_D46

FBD_D47

FBD_D48

FBD_D49

FBD_D50

FBD_D51

FBD_D52

FBD_D53

FBD_D54

FBD_D55

FBD_D56

FBD_D57

FBD_D58

FBD_D59

FBD_D60

FBD_D61

FBD_D62

FBD_D63

FBD_DQM0

FBD_DQM1

FBD_DQM2

FBD_DQM3

FBD_DQM4

FBD_DQM5

FBD_DQM6

FBD_DQM7

FBD_DQS_WP0

FBD_DQS_WP1

FBD_DQS_WP2

FBD_DQS_WP3

FBD_DQS_WP4

FBD_DQS_WP5

FBD_DQS_WP6

FBD_DQS_WP7

FBD_DQS_RN0

FBD_DQS_RN1

FBD_DQS_RN2

FBD_DQS_RN3

FBD_DQS_RN4

FBD_DQS_RN5

FBD_DQS_RN6

FBD_DQS_RN7

M9

N8

N7

P9

R9

R8

P7

N6

M4

M2

M1

N1

P4

R4

R2

R1

K8

J7

J6

H6

L9

M8

M7

M6

J2

J1

K4

K3

K2

K1

H3

G4

H12

J11

H10

G12

G9

F9

F8

F12

A10

B10

C10

B9

A9

D10

D7

C8

F13

J15

J12

H15

D15

J14

H13

G13

D12

B12

A12

A13

D14

A15

B15

C15

P6

L4

J8

J3

H9

C9

F14

D11

R7

N2

L7

J5

G10

E9

G15

C13

R6

N3

K7

J4

G11

D9

F15

B13

R5

M5

K5

H4

E10

D8

G14

E12

G1E

G1E

bga1504-nvidia-nb9e-glm2

bga1504-nvidia-nb9e-glm2

COMMON

COMMON

5/19 FBD

5/19 FBD

FBD_D0

FBD_D1

FBD_D2

FBD_D3

FBD_D4

FBD_D5

FBD_D6

FBD_D7

FBD_D8

FBD_D9

FBD_D10

FBD_D11

FBD_D12

FBD_D13

FBD_D14

FBD_D15

FBD_D16

FBD_D17

FBD_D18

FBD_D19

FBD_D20

FBD_D21

FBD_D22

FBD_D23

FBD_D24

FBD_D25

FBD_D26

FBD_D27

FBD_D28

FBD_D29

FBD_D30

FBD_D31

FBD_D32

FBD_D33

FBD_D34

FBD_D35

FBD_D36

FBD_D37

FBD_D38

FBD_D39

FBD_D40

FBD_D41

FBD_D42

FBD_D43

FBD_D44

FBD_D45

FBD_D46

FBD_D47

FBD_D48

FBD_D49

FBD_D50

FBD_D51

FBD_D52

FBD_D53

FBD_D54

FBD_D55

FBD_D56

FBD_D57

FBD_D58

FBD_D59

FBD_D60

FBD_D61

FBD_D62

FBD_D63

FBD_DQM0

FBD_DQM1

FBD_DQM2

FBD_DQM3

FBD_DQM4

FBD_DQM5

FBD_DQM6

FBD_DQM7

FBD_DQS_WP0

FBD_DQS_WP1

FBD_DQS_WP2

FBD_DQS_WP3

FBD_DQS_WP4

FBD_DQS_WP5

FBD_DQS_WP6

FBD_DQS_WP7

FBD_DQS_RN0

FBD_DQS_RN1

FBD_DQS_RN2

FBD_DQS_RN3

FBD_DQS_RN4

FBD_DQS_RN5

FBD_DQS_RN6

FBD_DQS_RN7

FBD_DBI0

FBD_DBI1

FBD_DBI2

FBD_DBI3

FBD_DBI4

FBD_DBI5

FBD_DBI6

FBD_DBI7

FBD_CMD0

FBD_CMD1

FBD_CMD2

FBD_CMD3

FBD_CMD4

FBD_CMD5

FBD_CMD6

FBD_CMD7

FBD_CMD8

FBD_CMD9

FBD_CMD10

FBD_CMD11

FBD_CMD12

FBD_CMD13

FBD_CMD14

FBD_CMD15

FBD_CMD16

FBD_CMD17

FBD_CMD18

FBD_CMD19

FBD_CMD20

FBD_CMD21

FBD_CMD22

FBD_CMD23

FBD_CMD24

FBD_CMD25

FBD_CMD26

FBD_CMD27

FBD_CMD28

FBD_CMD29

FBD_CMD30

FBD_DEBUG

FBD_CLK0

FBD_CLK0

FBD_CLK1

FBD_CLK1

FBD_WCK0

FBD_WCK0

FBD_WCK1

FBD_WCK1

FBD_WCK2

FBD_WCK2

FBD_WCK3

FBD_WCK3

FB_VDDQ_SENSE

G3

F5

G5

B4

E6

A4

D5

D1

D4

C2

F4

E7

B3

C4

F3

B6

C7

C6

G6

F7

E4

C5

E3

F1

D3

F2

D2

A6

D6

C1

A3

G7

G1

G2

B7

A7

N5

N4

L6

K6

F11

F10

E13

D13

J34

SNN_FBD_CMD7

SNN_FBD_CMD26

SNN_FBD_CMD28

SNN_FBD_CMD27

SNN_FBD_CMD28

FBD_DEBUG

R61 0R61 0

FBD_CMD0

FBD_CMD1

FBD_CMD2

FBD_CMD3

FBD_CMD4

FBD_CMD5

FBD_CMD6

FBD_CMD8

FBD_CMD9

FBD_CMD10

FBD_CMD11

FBD_CMD12

FBD_CMD13

FBD_CMD14

FBD_CMD15

FBD_CMD16

FBD_CMD17

FBD_CMD18

FBD_CMD19

FBD_CMD20

FBD_CMD21

FBD_CMD22

FBD_CMD23

FBD_CMD24

FBD_CMD25

FBD_CMD27

FBD_CLK0

FBD_CLK0#

FBD_CLK1

FBD_CLK1#

T189PAD T189PAD

T93PAD T93PAD

T72PAD T72PAD

T187PAD T187PAD

T188PAD T188PAD

FBD_CLK0 9

FBD_CLK0# 9

FBD_CLK1 9

FBD_CLK1# 9

T192PAD T192PAD

T194PAD T194PAD

T195PAD T195PAD

T190PAD T190PAD

T191PAD T191PAD

T193PAD T193PAD

T196PAD T196PAD

T197PAD T197PAD

+1.8V_RUN

R149

R149

60.4

60.4

FBVDDQ_SENSE 20

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

G92_FB_Partition_C/D

G92_FB_Partition_C/D

G92_FB_Partition_C/D

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

XM1 G92 VGA 1A

XM1 G92 VGA 1A

XM1 G92 VGA 1A

Date: Sheet

Date: Sheet

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

Date: Sheet

of

of

of

521

521

521

HFDBA

1

2

3

4

5

Page 6

5

4

3

2

1

06

FBA_CMD[27..0] 4

FBA_D[63..0] 4

D D

FBA_CLK04

FBA_CLK0#4

C C

FBA - bottom FBA - bottom

+1.8V_RUN +1.8V_RUN

C169

C169

0.1U

0.1U

C134

C134

0.1U

0.1U

B B

C1621UC162

1U

FBA_DQM[7..0] 4

FBA_DQS_RN[7..0] 4

FBA_DQS_WP[7..0] 4

R1

R2

+1.8V_RUN

R30

R30

549

549

R28

R28

FBA_VREF3_PD

31

2N7002W-7-FQ42N7002W-7-F

Q4

GPIO10_FB_VREF_SW_R

2

931

931

C7

R23

R23

1.33K

1.33K

0.01UC70.01U

FBAB_VREF2

R1

R2

+1.8V_RUN

R31

R31

R14

R14

549

549

R24

R24

1.33K

1.33K

FBAB_VREF2_PD

31

2N7002W-7-FQ32N7002W-7-F

Q3

GPIO10_FB_VREF_SW_R

2

GPIO10_FB_VREF_SW_R 4,7,8,9

931

931

C8

C8

0.01U

0.01U

X7R

X7R

Missor Function Signal Mapping

R126 475R126 475

FBA_CLK0

FBA_CLK0#

FBA_CMD18

FBA_CMD1

FBA_CMD10

FBA_CMD11

R127

R127

FBA_CMD8

10K

10K

FBA_DQM2

FBA_DQM0

FBA_DQM3

FBA_DQM1

FBA_DQS_WP2

FBA_DQS_WP0

FBA_DQS_WP3

FBA_DQS_WP1

FBA_DQS_RN2

FBA_DQS_RN0

FBA_DQS_RN3

FBA_DQS_RN1

FBA_CMD19

FBA_CMD25

FBA_CMD22

FBA_CMD24

FBA_CMD0

FBA_CMD2

FBA_CMD21

FBA_CMD16

FBA_CMD23

FBA_CMD20

FBA_CMD17

FBA_CMD9

FBA_CMD12

FBA_CMD3

FBA_CMD27

Close to K1& K12.

C152

C183

C183

C170

C170

0.1U

0.1U

0.1U

0.1U

C143

C143

C130

C130

0.1U

0.1U

0.1U

0.1U

C1801UC180

C1461UC146

1U

1U

C152

C148

C148

0.1U

0.1U

0.1U

0.1U

C166

C166

C154

C154

0.1U

0.1U

0.1U

0.1U

C1421UC142

1U

Note: Change to X7R

FBAB_VREF3

C182

C182

0.047U

0.047U

H1

H12

J11

J10

H4

H3

F4

H9

F9

E3

E10

N10

N3

D2

D11

P11

P2

D3

D10

P10

P3

K4

H2

K3

M4

K9

H11

K10

L9

K11

M9

K2

L4

G4

G9

H10

C194

C194

0.047U

0.047U

U4A

U4A

VREF1

VREF2

CK

CK

CKE

RAS

CAS

WE

CS

DM0

DM1

DM2

DM3

WDQS0

WDQS1

WDQS2

WDQS3

RDQS0

RDQS1

RDQS2

RDQS3

A0

A1

A2

A3

A4

A5

A6

A7

A8/AP

A9

A10

A11

BA0

BA1

BA2

H5RS5223CFR-11C

H5RS5223CFR-11C

+1.8V_RUN

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ZQ

MF

RES

SEN

RFU

NC0

U4B

U4B

K12

K1

V11

V2

M12

M1

F12

F1

A11

A2

A1

A12

C1

C4

C9

C12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

E1

E4

E9

E12

H5RS5223CFR-11C

H5RS5223CFR-11C

VDD10

VDD9

VDD8

VDD7

VDD6

VDD5

VDD4

VDD3

VDD2

VDD1

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

FBA_D19

B2

FBA_D22

B3

FBA_D16

C2

FBA_D17

C3

FBA_D21

E2

FBA_D23

F3

FBA_D20

F2

FBA_D18

G3

FBA_D5

B11

FBA_D6

B10

FBA_D3

C11

FBA_D7

C10

FBA_D4

E11

FBA_D2

F10

FBA_D0

F11

FBA_D1

G10

FBA_D29

M11

FBA_D27

L10

FBA_D26

N11

FBA_D28

M10

FBA_D24

R11

FBA_D25

R10

FBA_D31

T11

FBA_D30

T10

FBA_D10

M2

FBA_D11

L3

FBA_D9

N2

FBA_D8

M3

FBA_D12

R2

FBA_D14

R3

FBA_D13

T2

FBA_D15

T3

FBA_ZQ0

A4

A9

FBA_CMD15

V9

V4

FBA_CMD14

J3

J2

VSS10

VSS9

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

VSSQ20

VSSQ19

VSSQ18

VSSQ17

VSSQ16

VSSQ15

VSSQ14

VSSQ13

VSSQ12

VSSQ11

VSSQ10

VSSQ9

VSSQ8

VSSQ7

VSSQ6

VSSQ5

VSSQ4

VSSQ3

VSSQ2

VSSQ1

R18

R18

243

243

R116

R116

T1PAD T1PAD

10K

10K

J12

J1

V10

V3

L12

L1

G12

G1

A10

A3

T12

T9

T4

T1

P12

P9

P4

P1

L11

L2

G11

G2

D12

D9

D4

D1

B12

B9

B4

B1

FBA_CLK14

FBA_CLK1#4

FrameBuffer - DecouplingFrameBuffer - Decoupling

C139

C139

C149

C149

0.1U

0.1U

0.1U

0.1U

C160

C160

C141

C141

0.1U

0.1U

0.1U

0.1U

C1861UC186

C1991UC199

1U

1U

R123 475R123 475

C128

C128

C135

C135

0.1U

0.1U

0.1U

0.1U

C174

C174

C144

C144

0.1U

0.1U

0.1U

0.1U

C2001UC200

C1561UC156

1U

1U

Note: Change to X7R

FBAB_VREF2

FBA_CLK1

FBA_CLK1#

FBA_CMD11

FBA_CMD27

FBA_CMD8

FBA_CMD18

FBA_CMD10

FBA_DQM7

FBA_DQM4 FBA_D36

FBA_DQM6

FBA_DQM5

FBA_DQS_WP7

FBA_DQS_WP4

FBA_DQS_WP6

FBA_DQS_WP5

FBA_DQS_RN7

FBA_DQS_RN4

FBA_DQS_RN6

FBA_DQS_RN5

FBA_CMD5

FBA_CMD13

FBA_CMD21

FBA_CMD20

FBA_CMD19

FBA_CMD25

FBA_CMD4

FBA_CMD9

FBA_CMD17

FBA_CMD6

FBA_CMD23

FBA_CMD16

FBA_CMD3

FBA_CMD12

FBA_CMD1

C150

C150

0.047U

0.047U

Close to K1& K12.

C157

C157

0.1U

0.1U

C181

C181

0.1U

0.1U

H12

J11

J10

E10

N10

D11

P11

D10

P10

M4

H11

K10

K11

M9

G4

G9

H10

C179

C179

0.047U

0.047U

U5A

U5A

H1

VREF1

VREF2

CK

CK

H4

WE

H3

BA2

F4

CS

H9

CKE

F9

CAS

E3

DM0

DM1

DM2

N3

DM3

D2

WDQS0

WDQS1

WDQS2

P2

WDQS3

D3

RDQS0

RDQS1

RDQS2

P3

RDQS3

K4

A4

H2

A5

K3

A6

A9

K9

A0

A1

A2

L9

A11

A10

A3

K2

A8

L4

A7

BA1

BA0

RAS

H5RS5223CFR-11C

H5RS5223CFR-11C

+1.8V_RUN

MIRROR

K12

V11

M12

A11

A12

C12

N12

R12

V12

E12

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ZQ

MF

RES

SEN

RFU

NC0

U5B

U5B

VDD10

K1

VDD9

VDD8

V2

VDD7

VDD6

M1

VDD5

F12

VDD4

F1

VDD3

VDD2

A2

VDD1

A1

VDDQ1

VDDQ2

C1

VDDQ3

C4

VDDQ4

C9

VDDQ5

VDDQ6

J4

VDDQ7

J9

VDDQ8

N1

VDDQ9

N4

VDDQ10

N9

VDDQ11

VDDQ12

R1

VDDQ13

R4

VDDQ14

R9

VDDQ15

VDDQ16

V1

VDDQ17

VDDQ18

E1

VDDQ19

E4

VDDQ20

E9

VDDQ21

VDDQ22

H5RS5223CFR-11C

H5RS5223CFR-11C

MF LOGIC STATE

FBA_D60

B2

FBA_D58

B3

FBA_D56

C2

FBA_D57

C3

FBA_D59

E2

FBA_D61

F3

FBA_D63

F2

FBA_D62

G3

FBA_D37

B11

FBA_D35

B10

FBA_D38

C11

FBA_D32

C10

E11

FBA_D33

F10

FBA_D34

F11

FBA_D39

G10

FBA_D48

M11

FBA_D54

L10

FBA_D55

N11

FBA_D50

M10

FBA_D52

R11

FBA_D51

R10

FBA_D49

T11

FBA_D53

T10

FBA_D41

M2

FBA_D40

L3

FBA_D42

N2

FBA_D45

M3

FBA_D43

R2

FBA_D44

R3

FBA_D46

T2

FBA_D47

T3

FBA_ZQ1

A4

A9

+1.8V_RUN

FBA_CMD15

V9

V4

FBA_CMD14

J3

J2

VSS10

VSSQ20

VSSQ19

VSSQ18

VSSQ17

VSSQ16

VSSQ15

VSSQ14

VSSQ13

VSSQ12

VSSQ11

VSSQ10

VSSQ9

VSSQ8

VSSQ7

VSSQ6

VSSQ5

VSSQ4

VSSQ3

VSSQ2

VSSQ1

R15

R15

243

243

T4PAD T4PAD

J12

J1

VSS9

V10

VSS8

V3

VSS7

L12

VSS6

L1

VSS5

G12

VSS4

G1

VSS3

A10

VSS2

A3

VSS1

T12

T9

T4

T1

P12

P9

P4

P1

L11

L2

G11

G2

D12

D9

D4

D1

B12

B9

B4

B1

PIN

RAS#

CAS#

WE#

CS#

CKE

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

BA0

BA1

BA2

HIGH LOW

H10

H3

F9

F4

H4

H9

F4

F9

H9

H4

K9

K4

H11

H2

K10

K3

M9

M4

K4

K9

H2

H11

K3

K10

L4

L9

K2

K11

M4

M9

K11

K2

L9

L4

G9

G4

G4

G9

H3

H10

A A

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

GDDR3_Partition_A

GDDR3_Partition_A

GDDR3_Partition_A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

XM1 G92 VGA 1A

XM1 G92 VGA 1A

XM1 G92 VGA 1A

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

621

621

621

of

of

of

Page 7

5

4

3

2

1

07

FBB_CMD[27..0] 4

FBB_D[63..0] 4

D D

FBB_CLK04

FBB_CLK0#4

C C

FBB_DQM[7..0] 4

FBB_DQS_RN[7..0] 4

FBB_DQS_WP[7..0] 4

R125 475R125 475

+1.8V_RUN +1.8V_RUN

R33

R33

549

549

R34

R34

FBAB_VREF5_PD FBAB_VREF4_PD

31

931

931

C5

R26

R26

1.33K

1.33K

0.01UC50.01U

U2A

U2A

H1

H12

J11

J10

H4

H3

F4

H9

F9

E3

E10

N10

N3

D2

D11

P11

P2

D3

D10

P10

P3

K4

H2

K3

M4

K9

H11

K10

L9

K11

M9

K2

L4

G4

G9

H10

H5RS5223CFR-11C

H5RS5223CFR-11C

VREF1

VREF2

CK

CK

CKE

RAS

CAS

WE

CS

DM0

DM1

DM2

DM3

WDQS0

WDQS1

WDQS2

WDQS3

RDQS0

RDQS1

RDQS2

RDQS3

A0

A1

A2

A3

A4

A5

A6

A7

A8/AP

A9

A10

A11

BA0

BA1

BA2

FBAB_VREF5 FBAB_VREF4

FBB_CLK0

FBB_CLK0#

FBB_CMD18

FBB_CMD1

FBB_CMD10

R122

R122

FBB_CMD11

FBB_CMD8

10K

10K

FBB_DQM2

FBB_DQM0

FBB_DQM1

FBB_DQM3

FBB_DQS_WP2

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP3

FBB_DQS_RN2

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN3

FBB_CMD19

FBB_CMD25

FBB_CMD22

FBB_CMD24

FBB_CMD0

FBB_CMD2

FBB_CMD21

FBB_CMD16

FBB_CMD23

FBB_CMD20

FBB_CMD17

FBB_CMD9

FBB_CMD12

FBB_CMD3

FBB_CMD27

Q8

GPIO10_FB_VREF_SW_R

2

2N7002W-7-FQ82N7002W-7-F

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ZQ

MF

RES

SEN

RFU

NC0

FBB_D18

B3

FBB_D22

C2

FBB_D19

C3

FBB_D23

E2

FBB_D17

F3

FBB_D16

F2

FBB_D21

G3

FBB_D6

B11

FBB_D7

B10

FBB_D4

C11

FBB_D5

C10

FBB_D1

E11

FBB_D3

F10

FBB_D2

F11

FBB_D0

G10

FBB_D15

M11

FBB_D14

L10

FBB_D13

N11

FBB_D10

M10

FBB_D12

R11

FBB_D11

R10

FBB_D9

T11

FBB_D8

T10

FBB_D27

M2

FBB_D30

L3

FBB_D31

N2

FBB_D29

M3

FBB_D26

R2

FBB_D25

R3

FBB_D28

T2

FBB_D24

T3

FBB_ZQ0

A4

A9

FBB_CMD15 FBB_CMD15

V9

V4

FBB_CMD14 FBB_CMD14

J3

J2

R17

R17

243

243

R119

R119

T2PAD T2PAD

10K

10K

FBB_CLK14

FBB_CLK1#4

FBB_D20

B2

R124 475R124 475

FBAB_VREF4

FBB_CMD11

FBB_CMD27

FBB_CMD8

FBB_CMD18

FBB_CMD10

FBB_DQM6

FBB_DQM4

FBB_DQM7

FBB_DQM5

FBB_DQS_WP6

FBB_DQS_WP4

FBB_DQS_WP7

FBB_DQS_WP5

FBB_DQS_RN6

FBB_DQS_RN4

FBB_DQS_RN7

FBB_DQS_RN5

FBB_CMD5

FBB_CMD13

FBB_CMD21

FBB_CMD20

FBB_CMD19

FBB_CMD25

FBB_CMD4

FBB_CMD9

FBB_CMD17

FBB_CMD6

FBB_CMD23

FBB_CMD16

FBB_CMD3

FBB_CMD12

FBB_CMD1

FBB_CLK1

FBB_CLK1#

R29

R29

R20

R20

1.33K

1.33K

H1

VREF1

H12

VREF2

J11

CK

J10

CK

H4

WE

H3

BA2

F4

CS

H9

CKE

F9

CAS

E3

DM0

E10

DM1

N10

DM2

N3

DM3

D2

WDQS0

D11

WDQS1

P11

WDQS2

P2

WDQS3

D3

RDQS0

D10

RDQS1

P10

RDQS2

P3

RDQS3

K4

A4

H2

A5

K3

A6

M4

A9

K9

A0

H11

A1

K10

A2

L9

A11

K11

A10

M9

A3

K2

A8

L4

A7

G4

BA1

G9

BA0

H10

RAS

H5RS5223CFR-11C

H5RS5223CFR-11C

549

549

MIRROR

U3A

U3A

R27

R27

931

931

C6

0.01UC60.01U

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ZQ

MF

RES

SEN

RFU

NC0

B2

B3

C2

C3

E2

F3

F2

G3

B11

B10

C11

C10

E11

F10

F11

G10

M11

L10

N11

M10

R11

R10

T11

T10

M2

L3

N2

M3

R2

R3

T2

T3

A4

A9

V9

V4

J3

J2

2N7002W-7-FQ22N7002W-7-F

FBB_ZQ1

31

Q2

GPIO10_FB_VREF_SW_R

2

FBB_D53

FBB_D54

FBB_D55

FBB_D52

FBB_D50

FBB_D51

FBB_D48

FBB_D49

FBB_D35

FBB_D38

FBB_D34

FBB_D39

FBB_D33

FBB_D37

FBB_D36

FBB_D32

FBB_D56

FBB_D58

FBB_D60

FBB_D57

FBB_D61

FBB_D59

FBB_D62

FBB_D63

FBB_D44

FBB_D45

FBB_D41

FBB_D47

FBB_D46

FBB_D43

FBB_D40

FBB_D42

+1.8V_RUN

R13

R13

243

243

T3PAD T3PAD

GPIO10_FB_VREF_SW_R 4,6,8,9

+1.8V_RUN

U2B

U2B

K12

VDD10

K1

VDD9

C138

FBB - bottom

+1.8V_RUN

FrameBuffer - Decoupling

C175

C175

C151

C151

0.1U

0.1U

0.1U

0.1U

C155

C155

C167

C167

0.1U

0.1U

0.1U

B B

0.1U

C1871UC187

C1771UC177

1U

1U

C165

C165

C198

C198

0.1U

0.1U

0.1U

0.1U

C131

C131

C171

C171

0.1U

0.1U

0.1U

0.1U

C1361UC136

C1581UC158

1U

1U

C138

0.047U

0.047U

C147

C147

0.1U

0.1U

C137

C137

0.1U

0.1U

Note: Change to X7R

A A

5

V11

C163

C163

0.047U

0.047U

V2

M12

M1

F12

F1

A11

A2

A1

A12

C1

C4

C9

C12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

E1

E4

E9

E12

4

VDD8

VDD7

VDD6

VDD5

VDD4

VDD3

VDD2

VDD1

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

H5RS5223CFR-11C

H5RS5223CFR-11C

VSS10

VSSQ20

VSSQ19

VSSQ18

VSSQ17

VSSQ16

VSSQ15

VSSQ14

VSSQ13

VSSQ12

VSSQ11

VSSQ10

VSSQ9

VSSQ8

VSSQ7

VSSQ6

VSSQ5

VSSQ4

VSSQ3

VSSQ2

VSSQ1

J12

J1

VSS9

V10

VSS8

V3

VSS7

L12

VSS6

L1

VSS5

G12

VSS4

G1

VSS3

A10

VSS2

A3

VSS1

T12

T9

T4

T1

P12

P9

P4

P1

L11

L2

G11

G2

D12

D9

D4

D1

B12

B9

B4

B1

FBB - bottom

+1.8V_RUN

FrameBuffer - Decoupling

C193

C193

C132

C132

0.1U

0.1U

0.1U

0.1U

C178

C178

C176

C176

0.1U

0.1U

0.1U

0.1U

C1591UC159

C1331UC133

1U

1U

C129

C129

C195

C195

0.1U

0.1U

0.1U

0.1U

C140

C140

C185

C185

0.1U

0.1U

0.1U

0.1U

C1681UC168

C1531UC153

1U

1U

C197

C197

0.047U

0.047U

Close to K1& K12.Close to K1& K12.

C196

C196

0.1U

0.1U

C145

C145

0.1U

0.1U

Note: Change to X7R

3

2

+1.8V_RUN

U3B

U3B

K12

VDD10

K1

VDD9

C164

C164

0.047U

0.047U

V11

V2

M12

M1

F12

F1

A11

A2

A1

A12

C1

C4

C9

C12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

E1

E4

E9

E12

VDD8

VDD7

VDD6

VDD5

VDD4

VDD3

VDD2

VDD1

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

H5RS5223CFR-11C

H5RS5223CFR-11C

J12

VSS10

J1

VSS9

V10

VSS8

V3

VSS7

L12

VSS6

L1

VSS5

G12

VSS4

G1

VSS3

A10

VSS2

A3

VSS1

T12

VSSQ20

T9

VSSQ19

T4

VSSQ18

T1

VSSQ17

P12

VSSQ16

P9

VSSQ15

P4

VSSQ14

P1

VSSQ13

L11

VSSQ12

L2

VSSQ11

G11

VSSQ10

G2

VSSQ9

D12

VSSQ8

D9

VSSQ7

D4

VSSQ6

D1

VSSQ5

B12

VSSQ4

B9

VSSQ3

B4

VSSQ2

B1

VSSQ1

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Title

Title

Title

GDDR3_Partition_B

GDDR3_Partition_B

GDDR3_Partition_B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

XM1 G92 VGA 1A

XM1 G92 VGA 1A

XM1 G92 VGA 1A

Monday, March 17, 2008

Monday, March 17, 2008

Monday, March 17, 2008

Date: Sheet

Date: Sheet

Date: Sheet

1

721

721

721

of

of

of

Page 8

5

4

3

2

1

08

D D

FBC_CMD[27..0] 5

FBC_D[63..0] 5

FBC_DQM[7..0] 5

FBC_DQS_RN[7..0] 5

FBC_DQS_WP[7..0] 5

R140 475R140 475

FBCD_VREF3

FBC_CLK05

FBC_CLK0#5

C C

FBC_CLK0

FBC_CLK0#

FBC_CMD18

FBC_CMD1

FBC_CMD10

FBC_CMD11

R134

R134

FBC_CMD8

10K

10K

FBC_DQM3

FBC_DQM1

FBC_DQM0

FBC_DQM2

FBC_DQS_WP3

FBC_DQS_WP1

FBC_DQS_WP0

FBC_DQS_WP2

FBC_DQS_RN3

FBC_DQS_RN1

FBC_DQS_RN0

FBC_DQS_RN2

FBC_CMD19

FBC_CMD25

FBC_CMD22

FBC_CMD24

FBC_CMD0

FBC_CMD2

FBC_CMD21

FBC_CMD16

FBC_CMD23

FBC_CMD20

FBC_CMD17

FBC_CMD9

FBC_CMD12

FBC_CMD3

FBC_CMD27

+1.8V_RUN

R50

R50

549

549

R1

R48

R48

FBCD_VREF3_PD

31

Q10

931

931

C44

C44

R49

R49

R2

1.33K

1.33K

0.01U

0.01U

U7A

U7A

H1

H12

J11

J10

H4

H3

F4

H9

F9

E3

E10

N10

N3

D2

D11

P11

P2

D3

D10

P10

P3

K4

H2

K3

M4

K9

H11

K10

L9

K11

M9

K2

L4

G4

G9

H10

H5RS5223CFR-11C

H5RS5223CFR-11C

VREF1

VREF2

CK

CK

CKE

RAS

CAS

WE

CS

DM0

DM1

DM2

DM3

WDQS0

WDQS1

WDQS2

WDQS3

RDQS0

RDQS1

RDQS2

RDQS3

A0

A1

A2

A3

A4

A5

A6

A7

A8/AP

A9

A10

A11

BA0

BA1

BA2

FBCD_VREF3 FBCD_VREF2

Q10

GPIO10_FB_VREF_SW_R

2

2N7002W-7-F

2N7002W-7-F

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ZQ

MF

RES

SEN

RFU

NC0

FBC_D28

B3

FBC_D27

C2

FBC_D30

C3

FBC_D26

E2

FBC_D31

F3

FBC_D24

F2

FBC_D29

G3

FBC_D8

B11

FBC_D13

B10

FBC_D15

C11

FBC_D10

C10

FBC_D9

E11

FBC_D11

F10

FBC_D12

F11

FBC_D14

G10

FBC_D0

M11

FBC_D1

L10

FBC_D2

N11

FBC_D3

M10

FBC_D5

R11

FBC_D4

R10

FBC_D6

T11

FBC_D7

T10

FBC_D17

M2

FBC_D18

L3

FBC_D16

N2

FBC_D19

M3

FBC_D20

R2

FBC_D22

R3

FBC_D21

T2

FBC_D23

T3

A4

A9

V9

V4

J3

J2

FBC_CMD15

FBC_ZQ0

R139

R139

T6PAD T6PAD

R47

R47

10K

10K

243

243

FBC_CLK15

FBC_CLK1#5

FBC_D25

B2

R133 475R133 475

FBC_CLK1

FBC_CLK1#

FBC_CMD11

FBC_CMD27

FBC_CMD8

FBC_CMD18

FBC_CMD10

FBC_DQM6

FBC_DQM5

FBC_DQM4

FBC_DQM7

FBC_DQS_WP6

FBC_DQS_WP5

FBC_DQS_WP4

FBC_DQS_WP7

FBC_DQS_RN6

FBC_DQS_RN5

FBC_DQS_RN4

FBC_DQS_RN7

FBC_CMD5

FBC_CMD13

FBC_CMD21

FBC_CMD20

FBC_CMD19

FBC_CMD25

FBC_CMD4

FBC_CMD9

FBC_CMD17

FBC_CMD6

FBC_CMD23

FBC_CMD16

FBC_CMD3

FBC_CMD12

FBC_CMD1

R1

R2

+1.8V_RUN

H12

J11

J10

E10

N10

D11

P11

D10

P10

H11

K10

K11

H10

R42

R42

549

549

R41

R41

1.33K

1.33K

U6A

U6A

H1

VREF1

VREF2

CK

CK

H4

WE

H3

BA2

F4

CS

H9

CKE

F9

CAS

E3

DM0

DM1

DM2

N3

DM3

D2

WDQS0

WDQS1

WDQS2

P2

WDQS3

D3

RDQS0

RDQS1

RDQS2

P3

RDQS3

K4

A4

H2

A5

K3

A6

M4

A9

K9

A0

A1

A2

L9

A11

A10

M9

A3

K2

A8

L4

A7

G4

BA1

G9

BA0

RAS

H5RS5223CFR-11C

H5RS5223CFR-11C

R37

R37

931

931

C29

C29

0.01U

0.01U

MIRROR

FBCD_VREF2_PD

31

Q9

GPIO10_FB_VREF_SW_R

2

2N7002W-7-FQ92N7002W-7-F

FBC_D55

B2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ZQ

MF

RES

SEN

RFU

NC0

FBC_D54

B3

FBC_D53

C2

FBC_D52

C3

FBC_D49

E2

FBC_D48

F3

FBC_D51

F2

FBC_D50

G3

FBC_D46

B11

FBC_D45

B10

FBC_D47

C11

FBC_D44

C10

FBC_D43

E11

FBC_D41

F10

FBC_D40

F11

FBC_D42

G10

FBC_D37

M11

FBC_D36

L10

FBC_D39

N11

FBC_D38

M10

FBC_D33

R11

FBC_D34

R10

FBC_D35

T11

FBC_D32

T10

FBC_D61

M2

FBC_D62

L3

FBC_D57

N2

FBC_D63

M3

FBC_D60

R2

FBC_D58

R3

FBC_D59

T2

FBC_D56

T3

FBC_ZQ1

A4

A9

+1.8V_RUN

FBC_CMD15

V9

V4

FBC_CMD14FBC_CMD14

J3

J2

T5PAD T5PAD

R35

R35

243

243

GPIO10_FB_VREF_SW_R 4,6,7,9

+1.8V_RUN +1.8V_RUN

U7B

U7B

K12

VDD10

K1

VDD9

C219

C219

C254

FBC - bottom

+1.8V_RUN

FrameBuffer - Decoupling

C217

C269

C269

C220

B B

C220

0.1U

0.1U

C222

C222

0.1U

0.1U

C2611UC261

1U

C234

C234

0.1U

0.1U

0.1U

0.1U

C237

C237

C245

C245

0.1U

0.1U

0.1U

0.1U

C2571UC257

C2211UC221

1U

1U

C217

C218

C218

0.1U

0.1U

0.1U

0.1U

C250

C250

C271

C271

0.1U

0.1U

0.1U

0.1U

C2351UC235

1U

0.047U

0.047U

Close to K1& K12.

C254

0.047U

0.047U

Note: Change to X7R

A A

5

V11

V2

M12

M1

F12

F1

A11

A2

A1

A12

C1

C4

C9

C12

J4

J9

N1

N4

N9

N12

R1

R4

R9

R12

V1

V12

E1

E4

E9

E12

4

VDD8

VDD7

VDD6

VDD5

VDD4

VDD3

VDD2

VDD1

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

H5RS5223CFR-11C

H5RS5223CFR-11C