Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

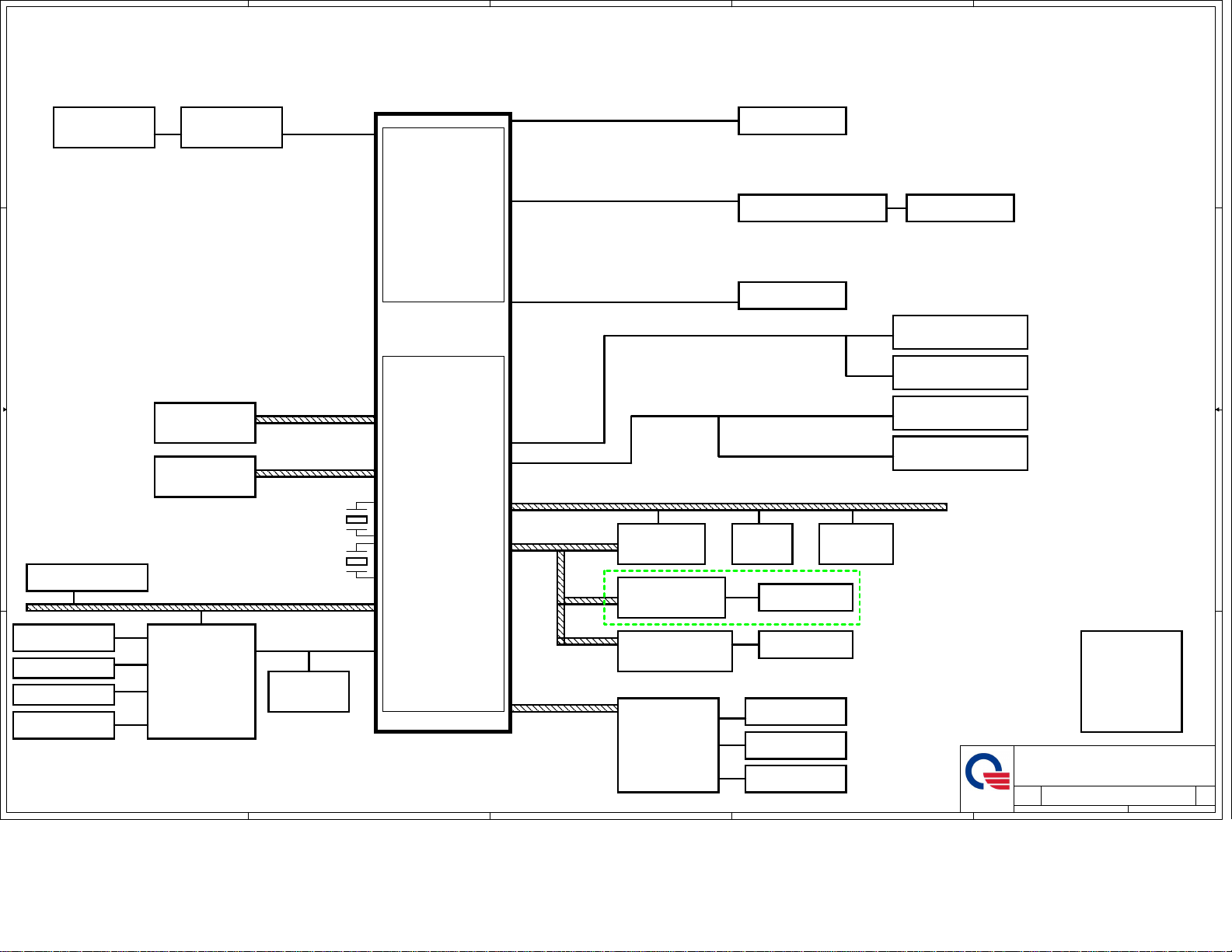

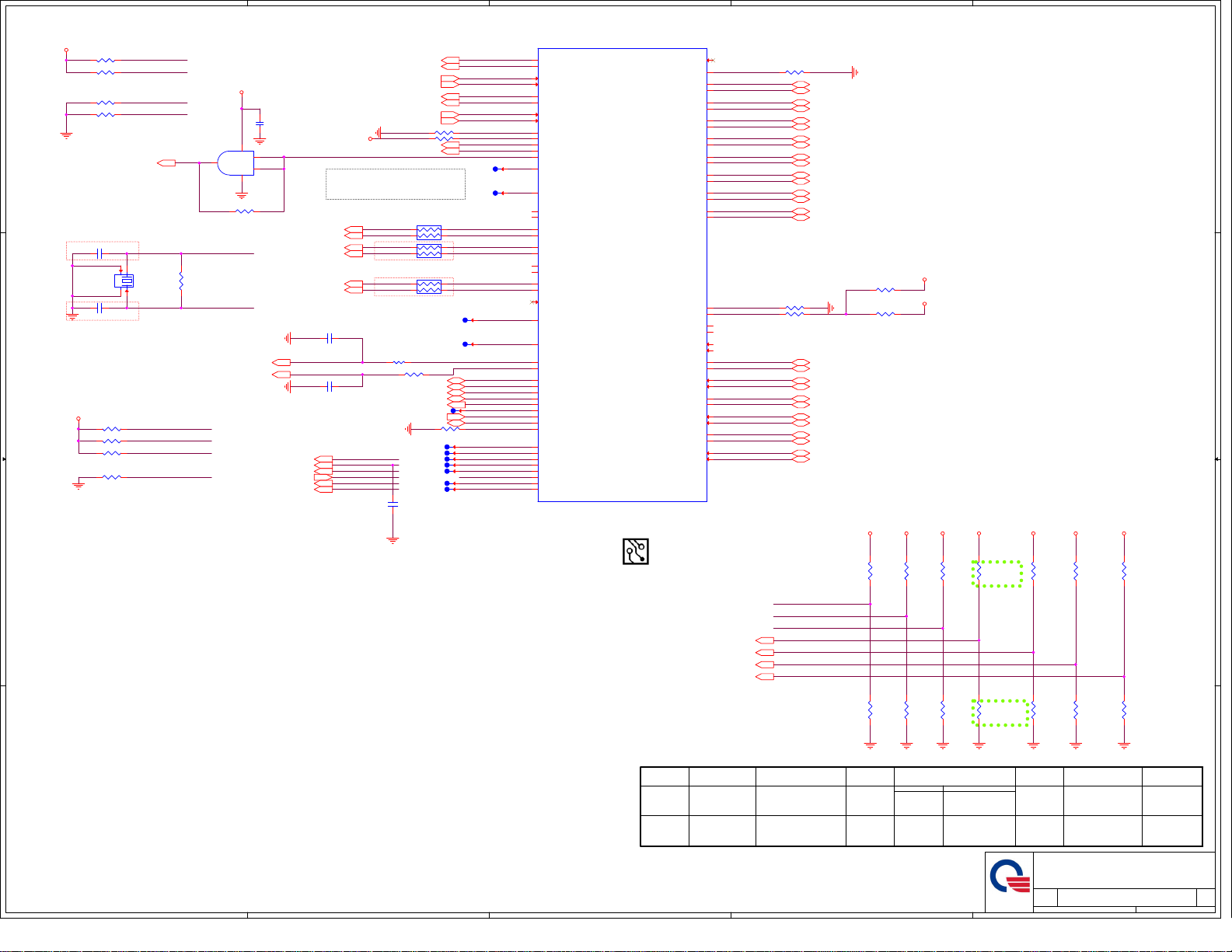

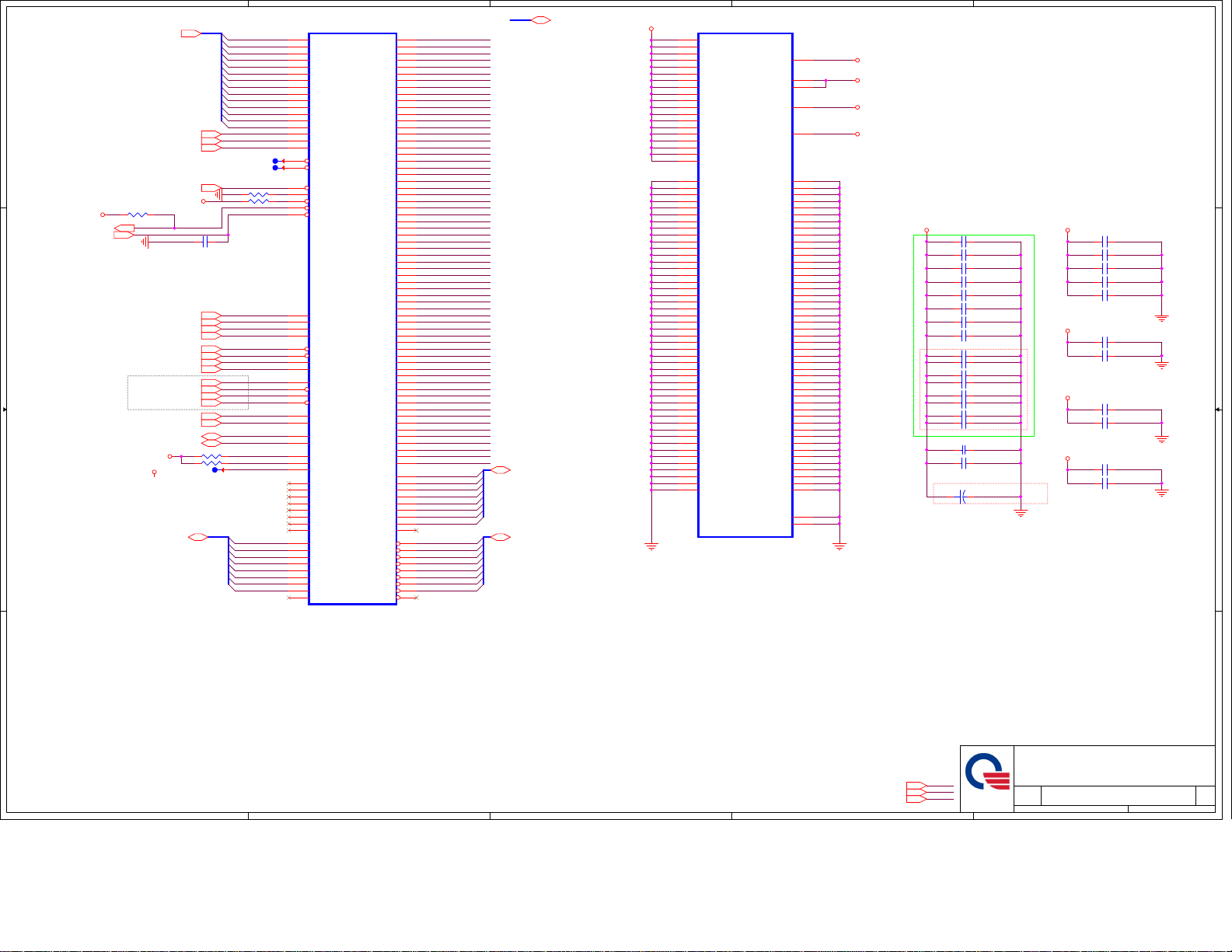

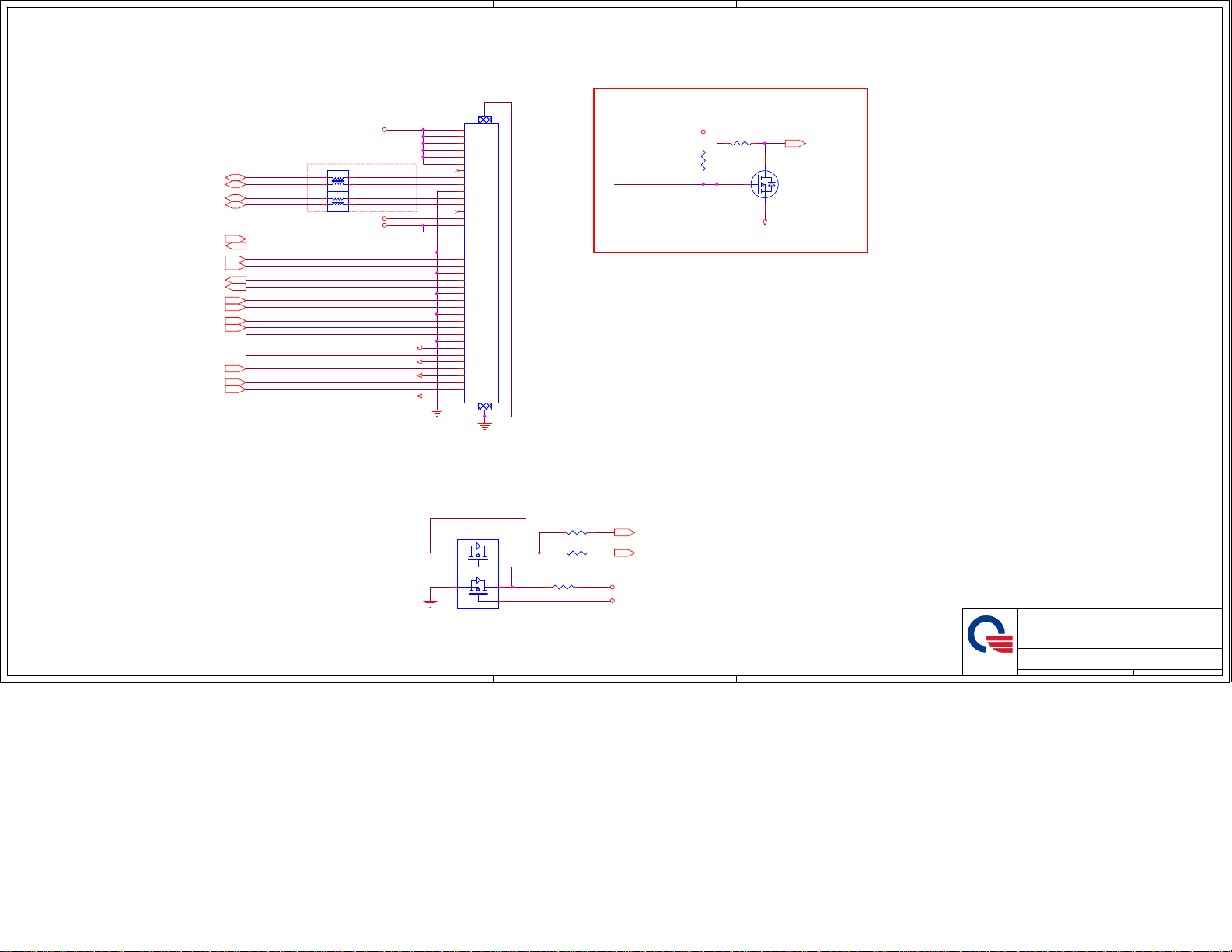

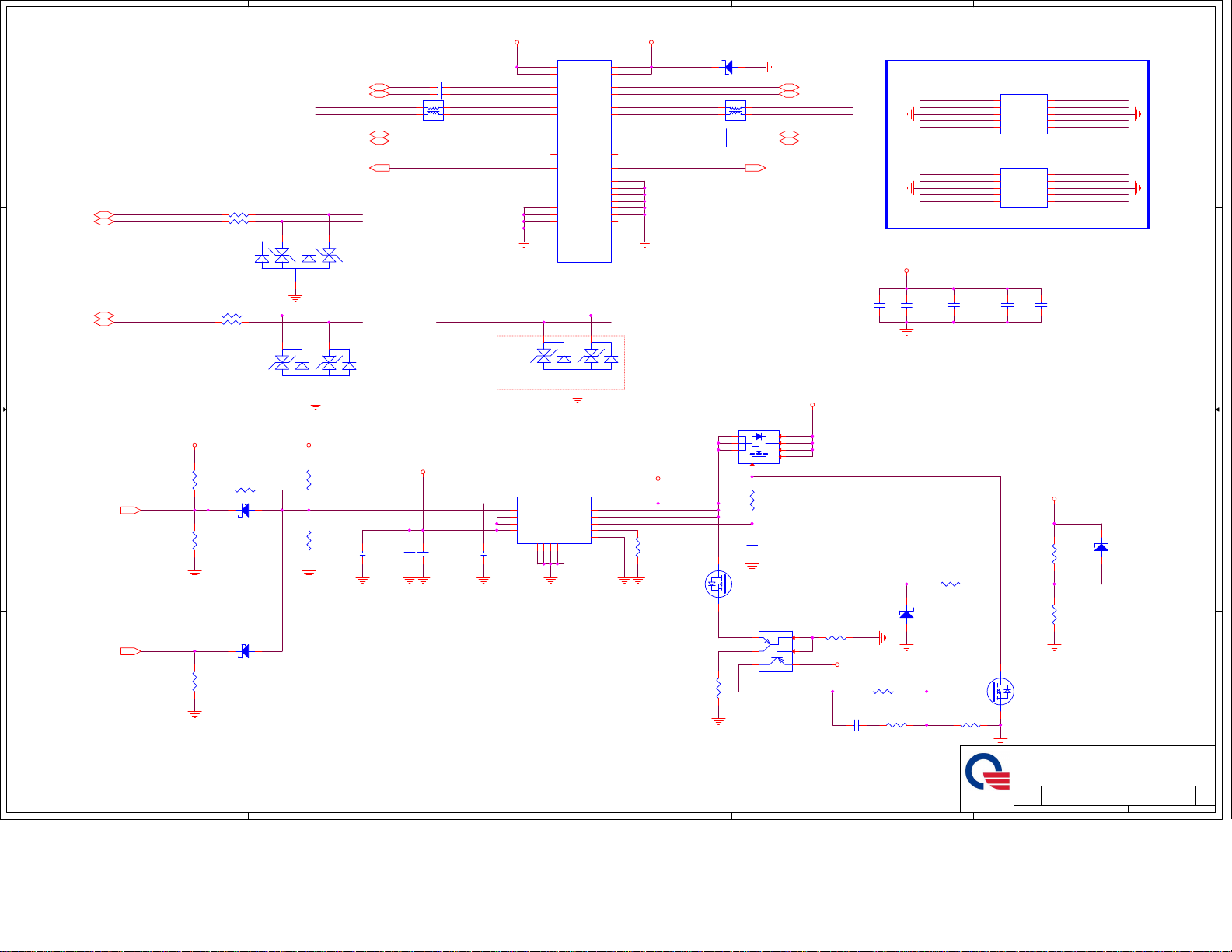

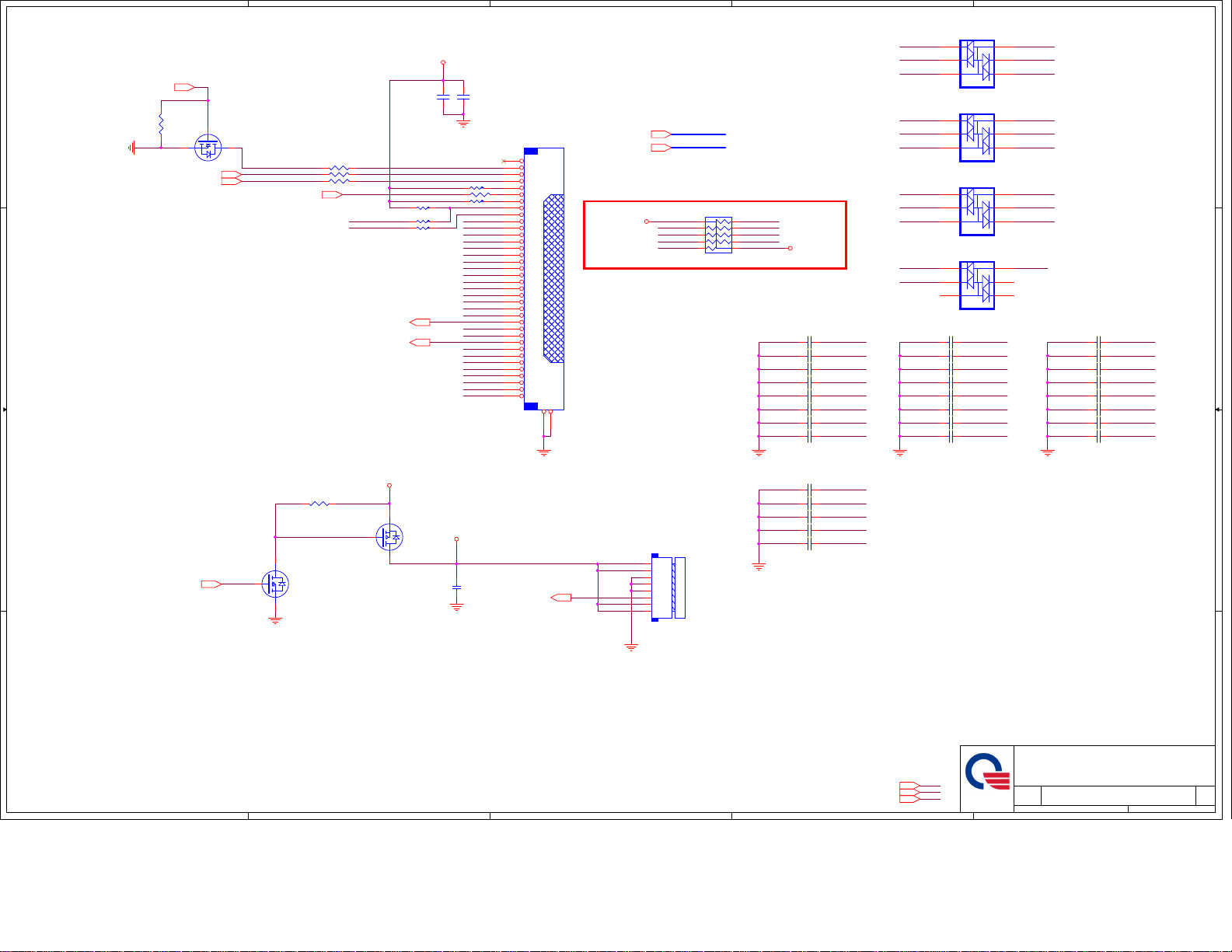

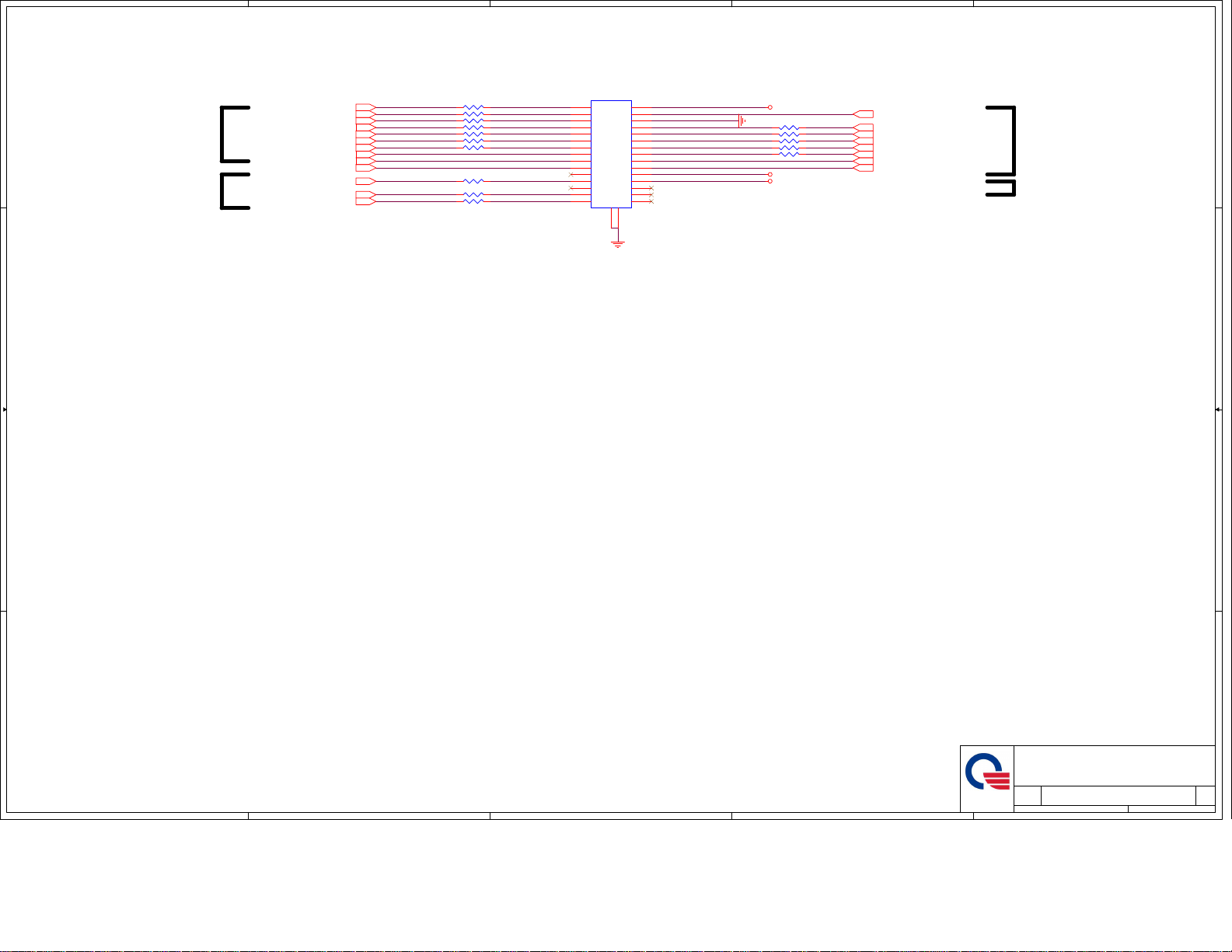

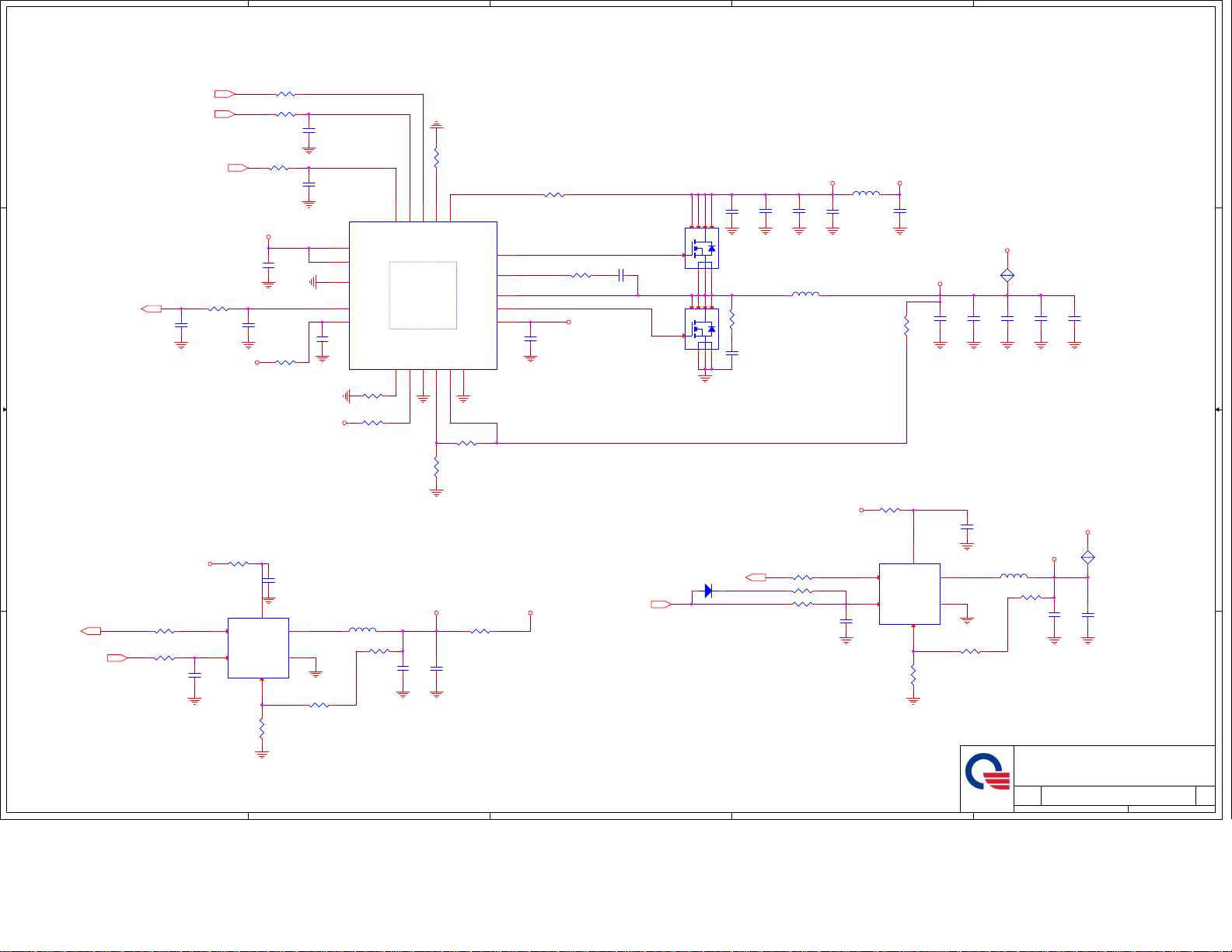

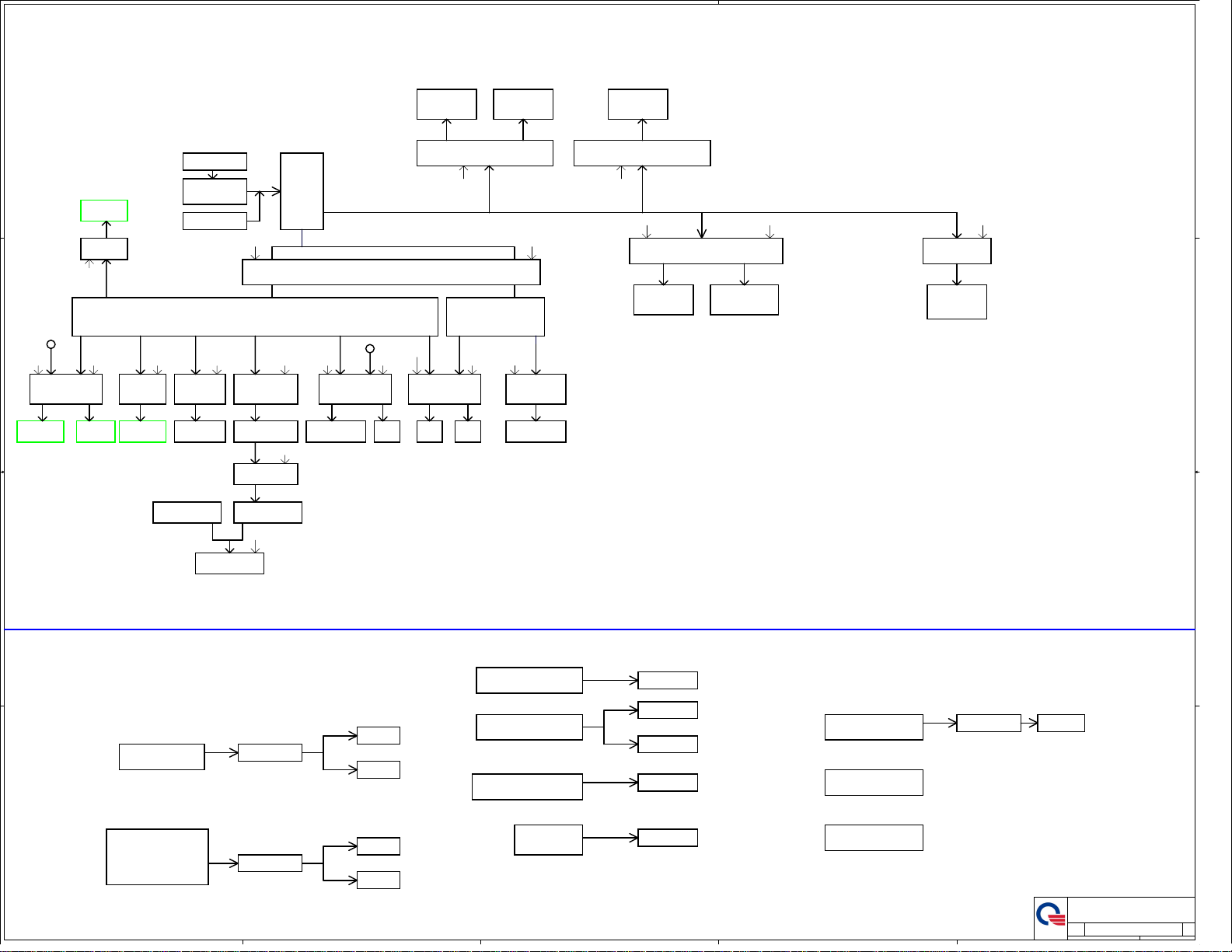

400 series Pitt / X93A (UMA) Schematics

01

D D

DDR4 1866MHz

16GB

PAGE 10

DDR4 1866MHz

16GB

PAGE 09

Single Channel-B

DDR4 1866MHz

DDI0 x2

Bristol Ridge

/ Stoney Ridge

DDI1

x2

iGPU

Processor : Daul Core

Power : 15 (Watt)

C C

DDI2

iFCH

SATA - ODD

PAGE 33

SATA HDD/

HDD to M.2 SSD

2.5" / 7, 9.5mm

B B

PAGE 33

InfineonTPM

PAGE 26SLB9670 TT1.2

Keyboard

PAGE 24

Battery PAGE 48

FAN

A A

Function Conn.

PAGE 28 HD Audio

KBC

Nuvoton

NPCE586HA0MX

Embedded Controller

PAGE 35, 36

128TQFP

PAGE 22

5

SATA1 3GB/s

SATA0 6GB/s

48MHz

32.768KHz

LPC Interface

SPI Interface

System BIOS

SPI ROM 16MB

PAGE 27

USB2.0 Interface

PCIE Gen 1 x 1 Lane

PAGE 2~8

4

HD and FHD

eDP

PAGE 11

DP to VGA Controller

Realtek RTD2166x4PAGE 12

HDMI CONN

PAGE 13

USB2.0 Interface USB 2.0 standard port

USB 2.0 standard ports

USB3.0 Interface

USB 3.0 standard port

CN18 (Upper Left)

USB Type-C port

CN22 (Lower Left)

PAGE 30NGFF

WLAN Combo

Camera

Port2

PAGE 11

Fingerprint

VFS495

Port 4

PAGE 17

10/100/1000 NIC

Realtek RTL8111HSH

PAGE 15

Card Reader controller

RTS5237S-GR

PAGE 16

RJ45

SD Socket

Digital MIC

PAGE 15

PAGE 16

PAGE 11

on Daugther Board

Conexant

CX7700-11ZP2

Speaker

PAGE 14

Combo Jack

PAGE 14

3

PAGE 15

2

CRT CONN

PAGE 12

PAGE 15

PAGE 15

PAGE 18

PAGE 20

PCB 6L STACK UP(1.2mm)

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

NB5

NB5

NB5

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1 53Tuesday, March 01, 2016

1 53Tuesday, March 01, 2016

1 53Tuesday, March 01, 2016

1A

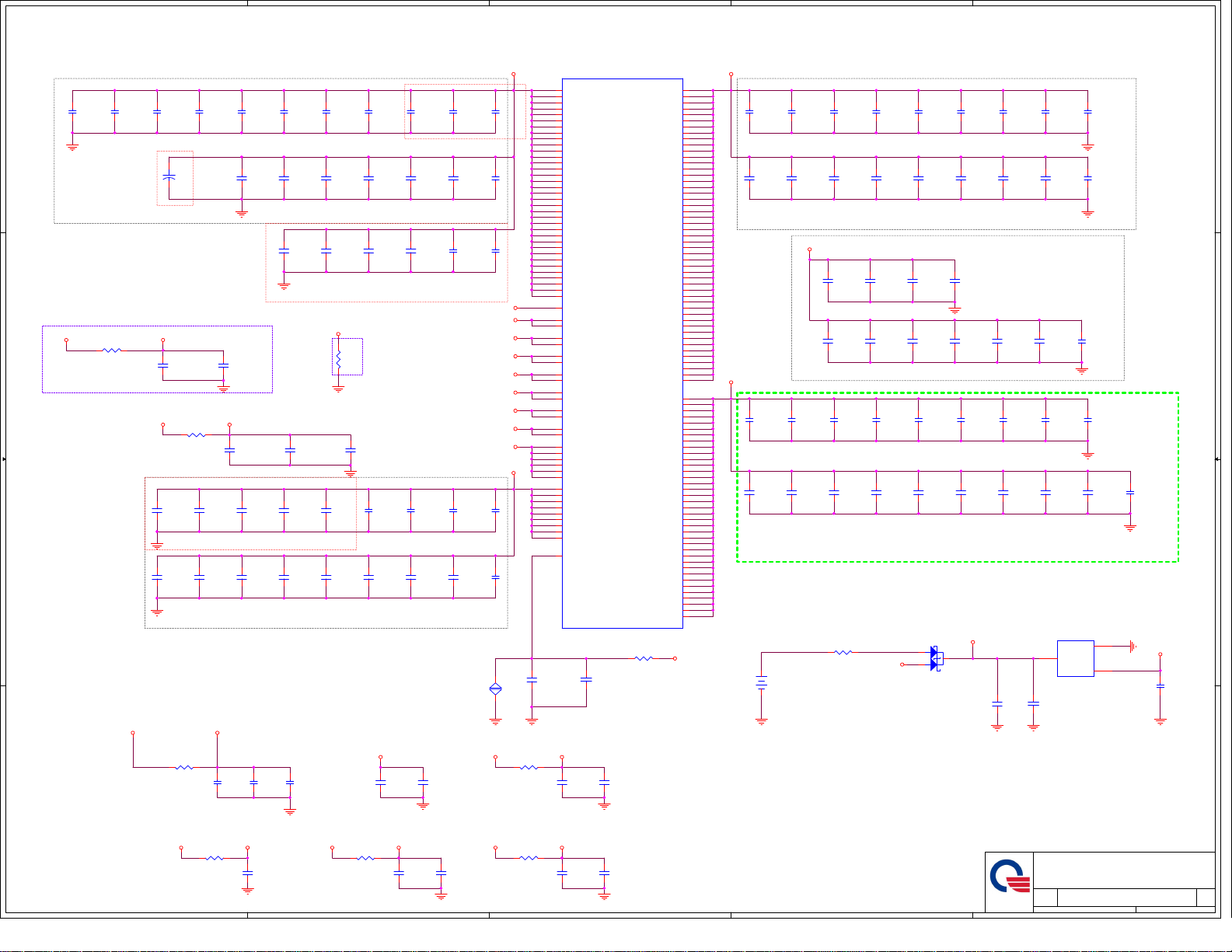

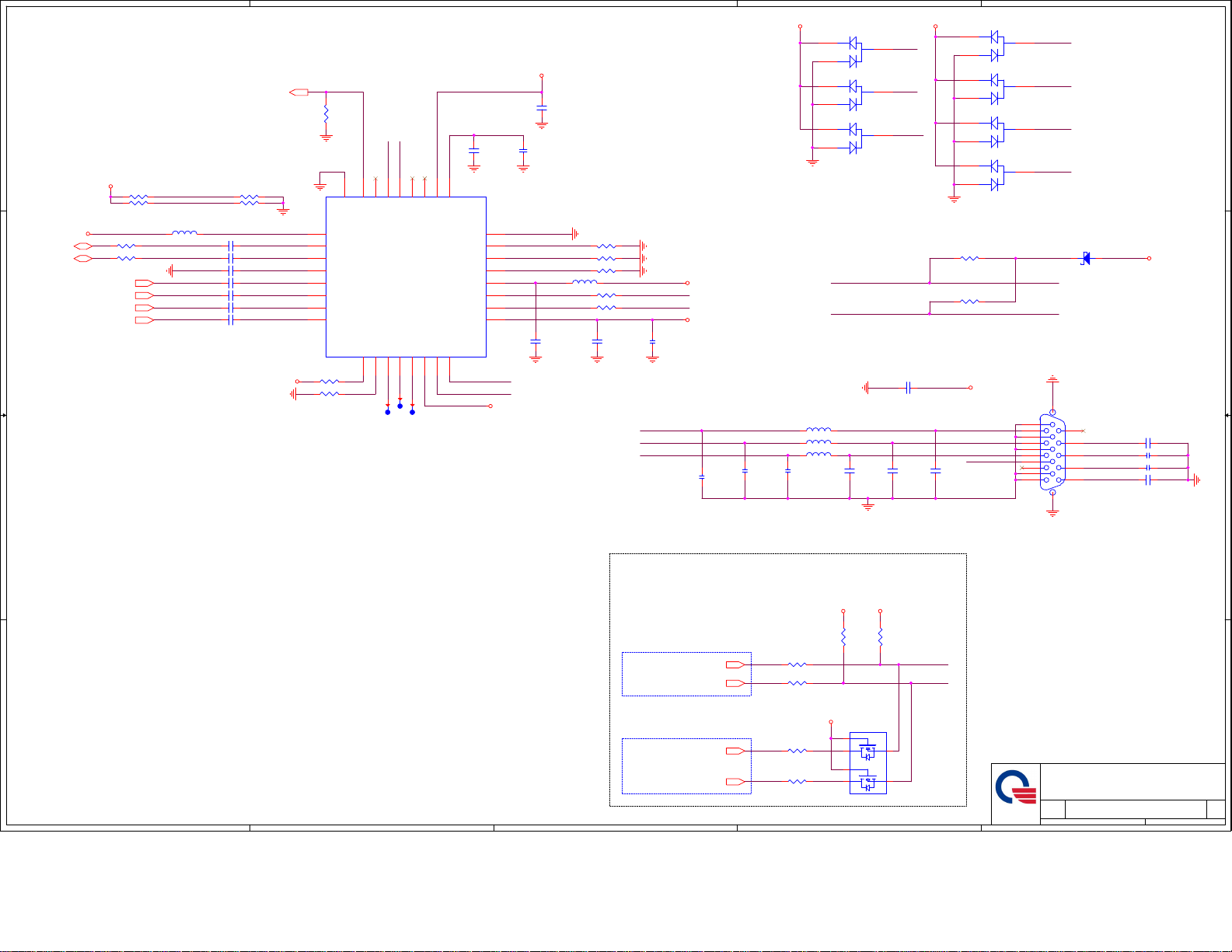

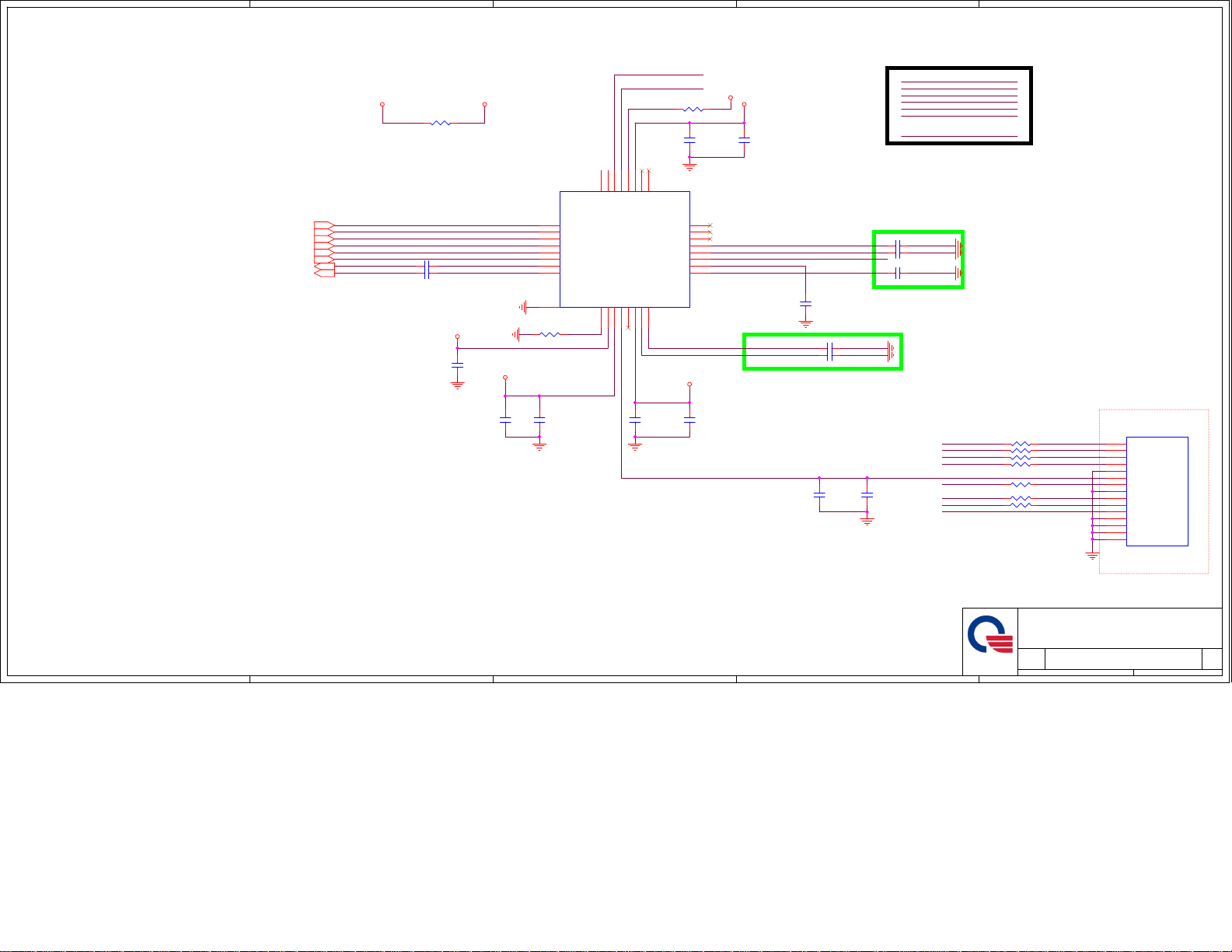

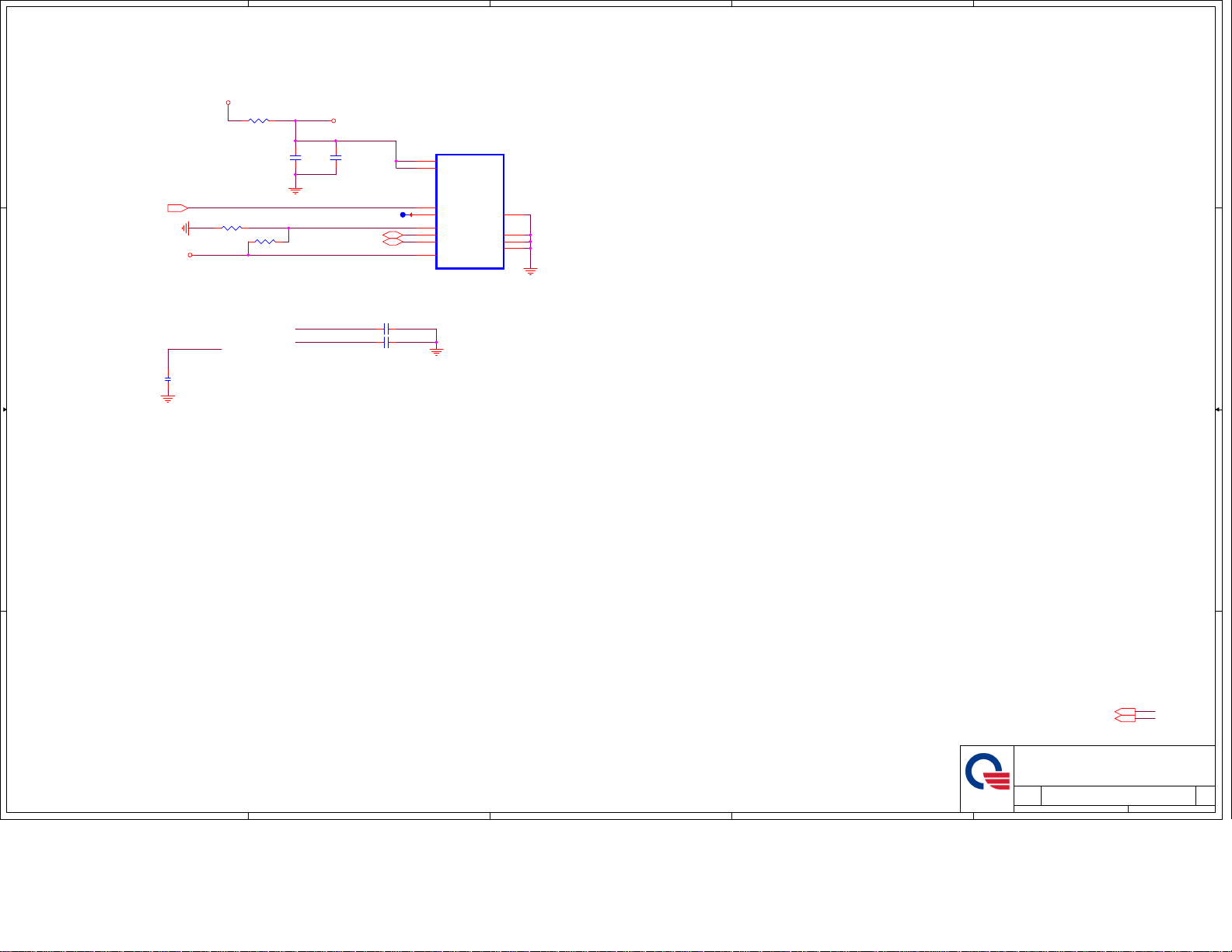

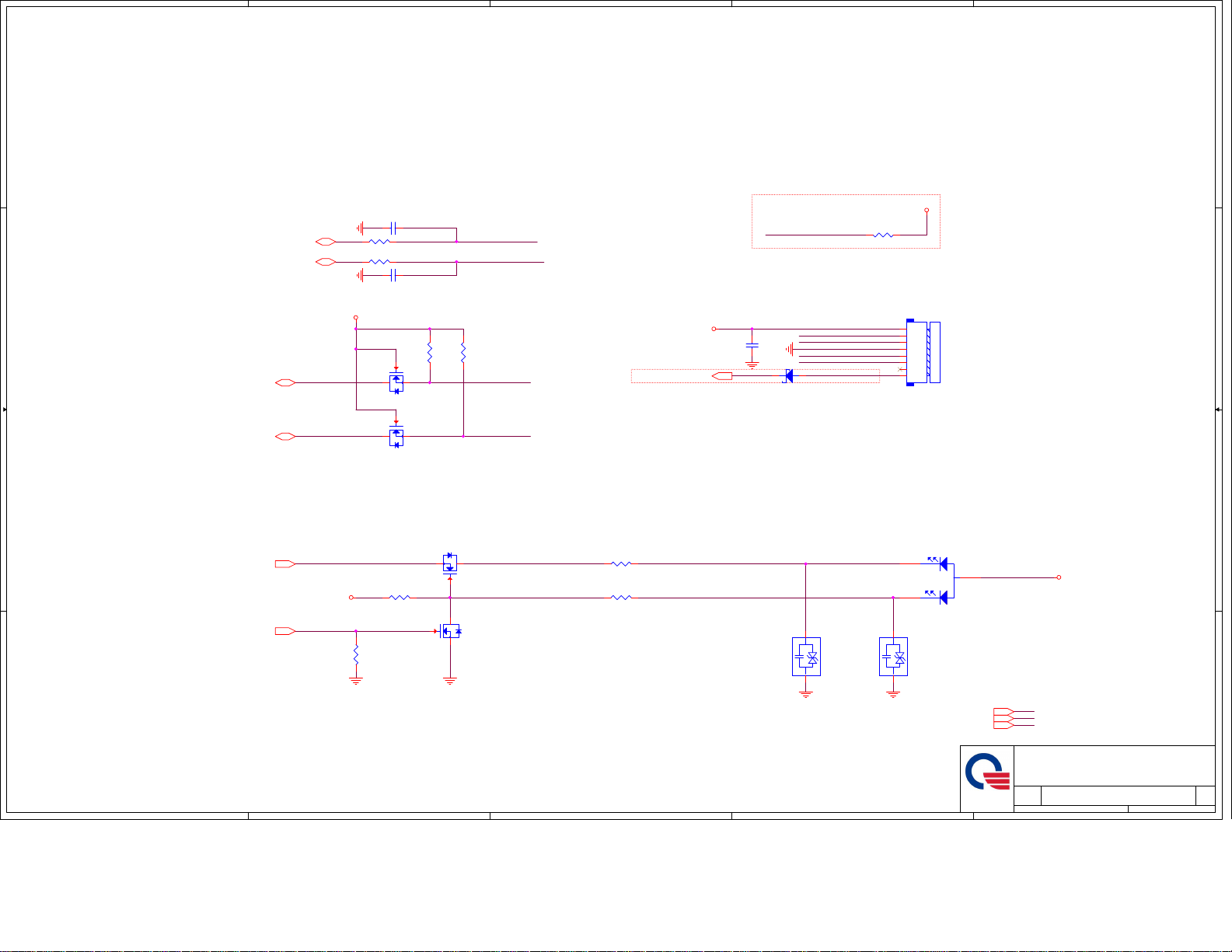

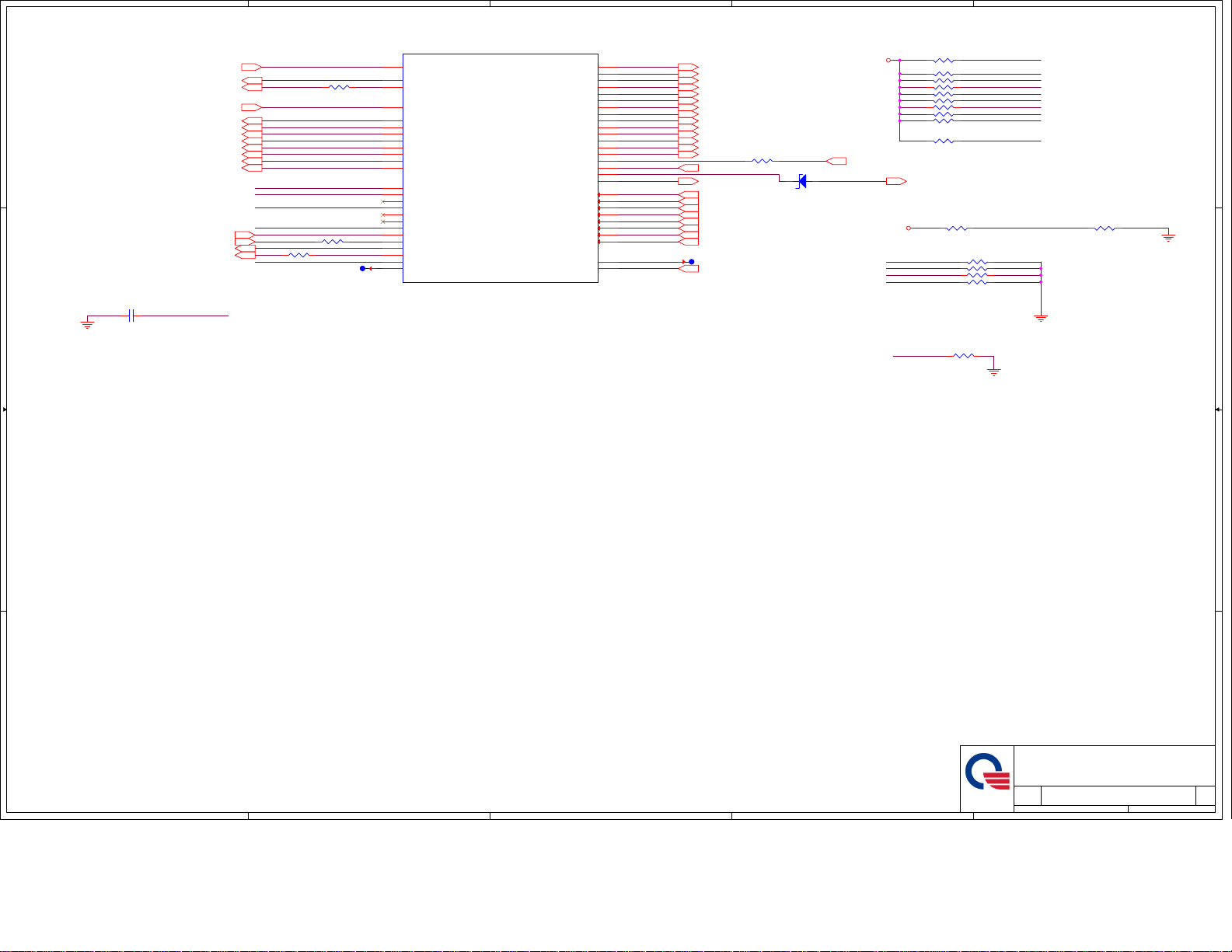

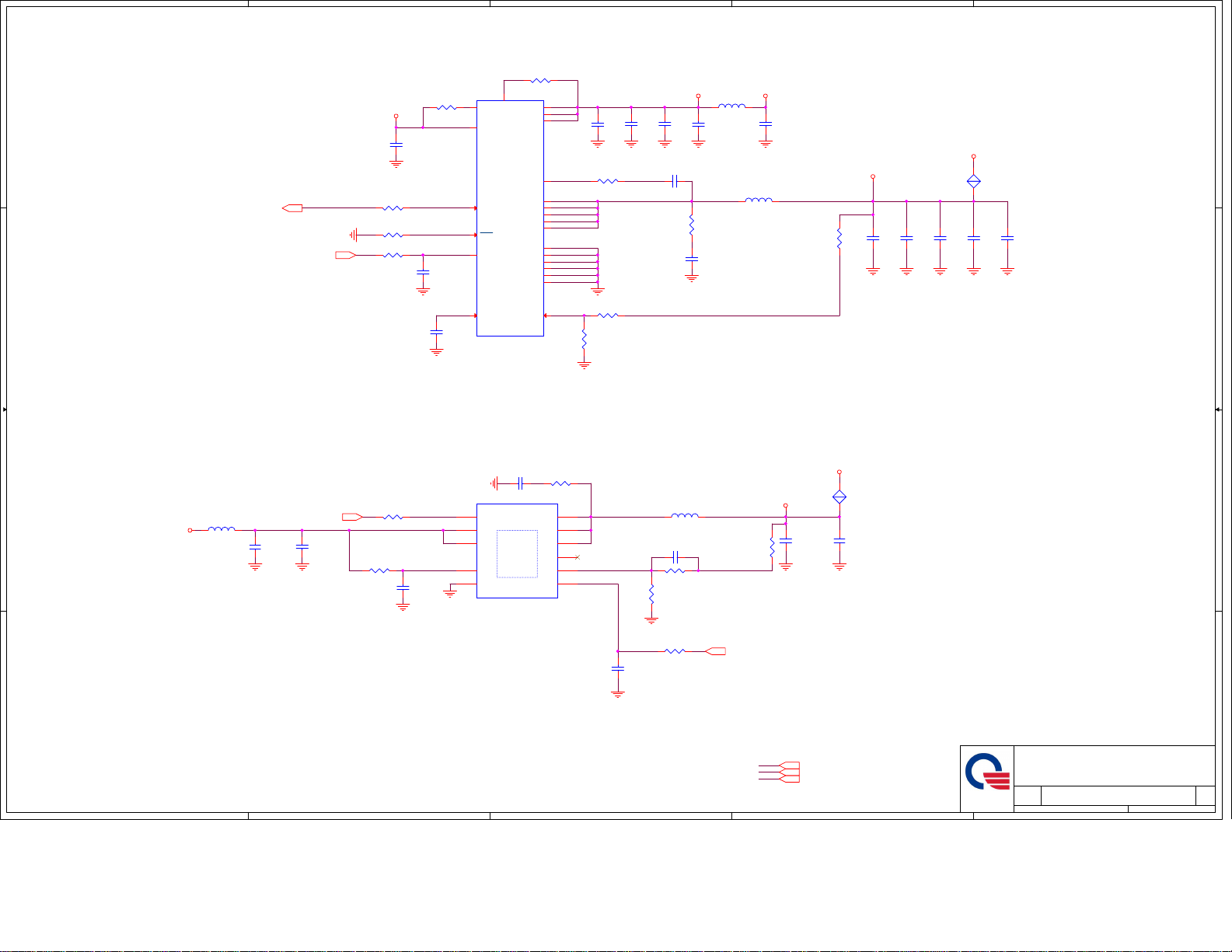

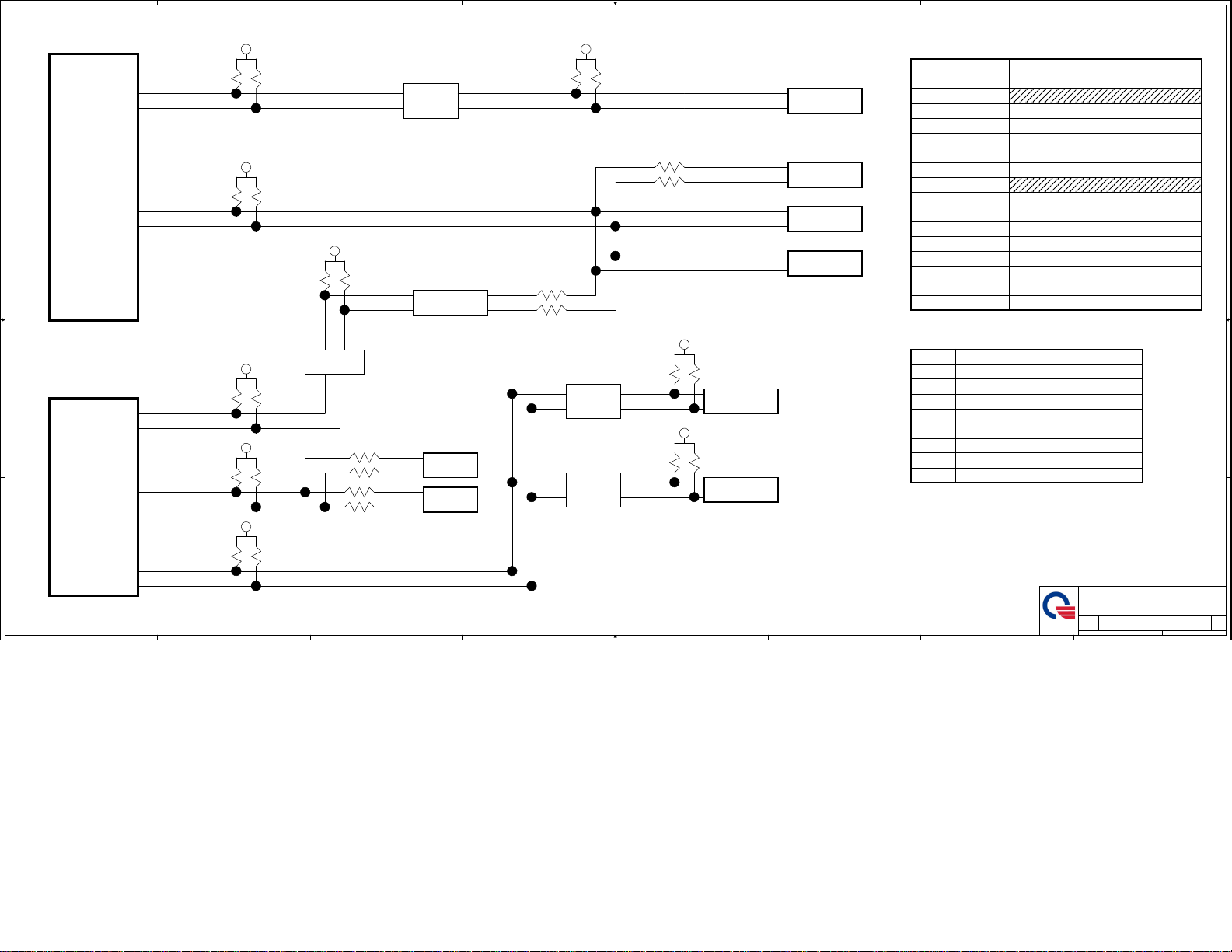

Page 2

5

4

3

2

1

U21B

U10

P10

L10

U9

T6

T5

T9

T8

P7

P6

U7

P9

N6

N5

N9

N8

L7

L6

L9

K6

K5

K9

K8

J7

J6

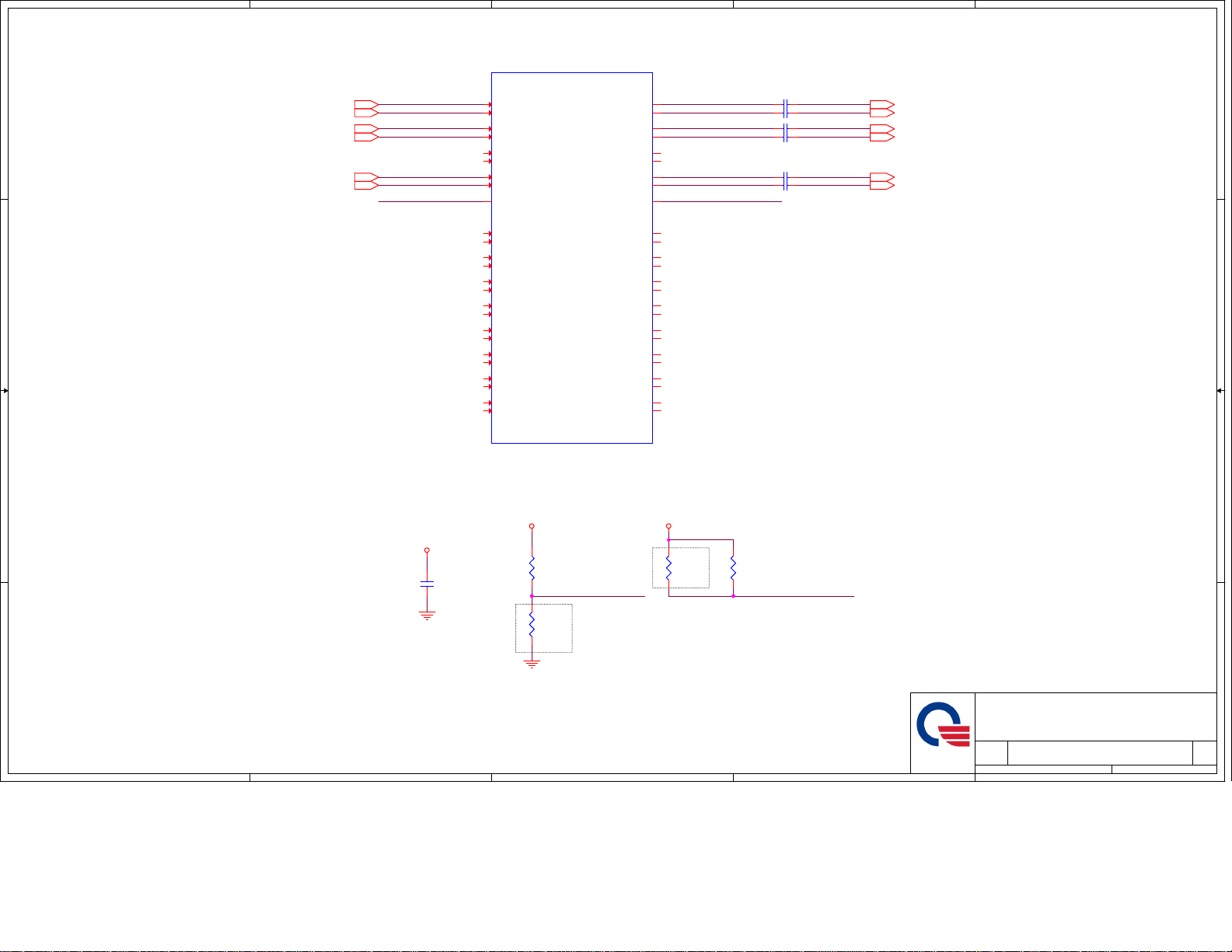

P_GPP_RXP[0]

P_GPP_RXN[0]

P_GPP_RXP[1]

P_GPP_RXN[1]

P_GPP_RXP[2]

P_GPP_RXN[2]

P_GPP_RXP[3]

P_GPP_RXN[3]

P_ZVDDP

P_GFX_RXP[0]

P_GFX_RXN[0]

P_GFX_RXP[1]

P_GFX_RXN[1]

P_GFX_RXP[2]

P_GFX_RXN[2]

P_GFX_RXP[3]

P_GFX_RXN[3]

P_GFX_RXP[4]

P_GFX_RXN[4]

P_GFX_RXP[5]

P_GFX_RXN[5]

P_GFX_RXP[6]

P_GFX_RXN[6]

P_GFX_RXP[7]

P_GFX_RXN[7]

D D

C C

B B

PCIE_RXP0_LAN[15]

PCIE_RXN0_LAN[15]

PCIE_RXP1_WLAN[30]

PCIE_RXN1_WLAN[30]

PCIE_RXP3_CARD[16]

PCIE_RXN3_CARD[16]

PCIE

For DIS GPU

FP4 REV 1.0

*FP4

P_GPP_TXP[0]

P_GPP_TXN[0]

P_GPP_TXP[1]

P_GPP_TXN[1]

P_GPP_TXP[2]

P_GPP_TXN[2]

P_GPP_TXP[3]

P_GPP_TXN[3]

P_ZVSS/P_RX_ZVDDP

P_GFX_TXP[0]

P_GFX_TXN[0]

P_GFX_TXP[1]

P_GFX_TXN[1]

P_GFX_TXP[2]

P_GFX_TXN[2]

P_GFX_TXP[3]

P_GFX_TXN[3]

P_GFX_TXP[4]

P_GFX_TXN[4]

P_GFX_TXP[5]

P_GFX_TXN[5]

P_GFX_TXP[6]

P_GFX_TXN[6]

P_GFX_TXP[7]

P_GFX_TXN[7]

R1

PCIE_TXP0_LAN_C

R2

PCIE_TXN0_LAN_C

R4

PCIE_TXP1_WLAN_C

R3

PCIE_TXN1_WLAN_C

N1

N2

N4

PCIE_TXP3_C

N3

PCIE_TXN3_C

U6

P_ZVSS_P_RX_ZVDD_095P_ZVDDP_P_TX_ZVDD_095

M2

M1

L1

L2

L4

L3

J1

J2

J4

J3

H2

H1

G1

G2

G4

G3

C432 0.1U/16V/X7R_4

C433 0.1U/16V/X7R_4

C437 0.1U/16V/X7R_4

C435 0.1U/16V/X7R_4

C430 0.1U/16V/X7R_4

C429 0.1U/16V/X7R_4

PCIE_TXP0_LAN [15]

PCIE_TXN0_LAN [15]

PCIE_TXP1_WLAN [30]

PCIE_TXN1_WLAN [30]

PCIE_TXP3_CARD [16]

PCIE_TXN3_CARD [16]

02

+0.95V +0.95V

+0.95V

R192

C255

0.1U/16V/X7R_4

A A

5

4

*1K/F_4

P_ZVSS_P_RX_ZVDD_095 P_ZVDDP_P_TX_ZVDD_095

R183

196/F_4

3

R195

196/F_4

Type1,3: R195, R183

ype2: R192, R189

T

R189

*1.69K/F_4

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

NB5

NB5

2

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

BR/ST 1/7 (PCIE)

BR/ST 1/7 (PCIE)

BR/ST 1/7 (PCIE)

Tuesday, March 01, 2016 2 53

Tuesday, March 01, 2016 2 53

Tuesday, March 01, 2016 2 53

1

1A

1A

1A

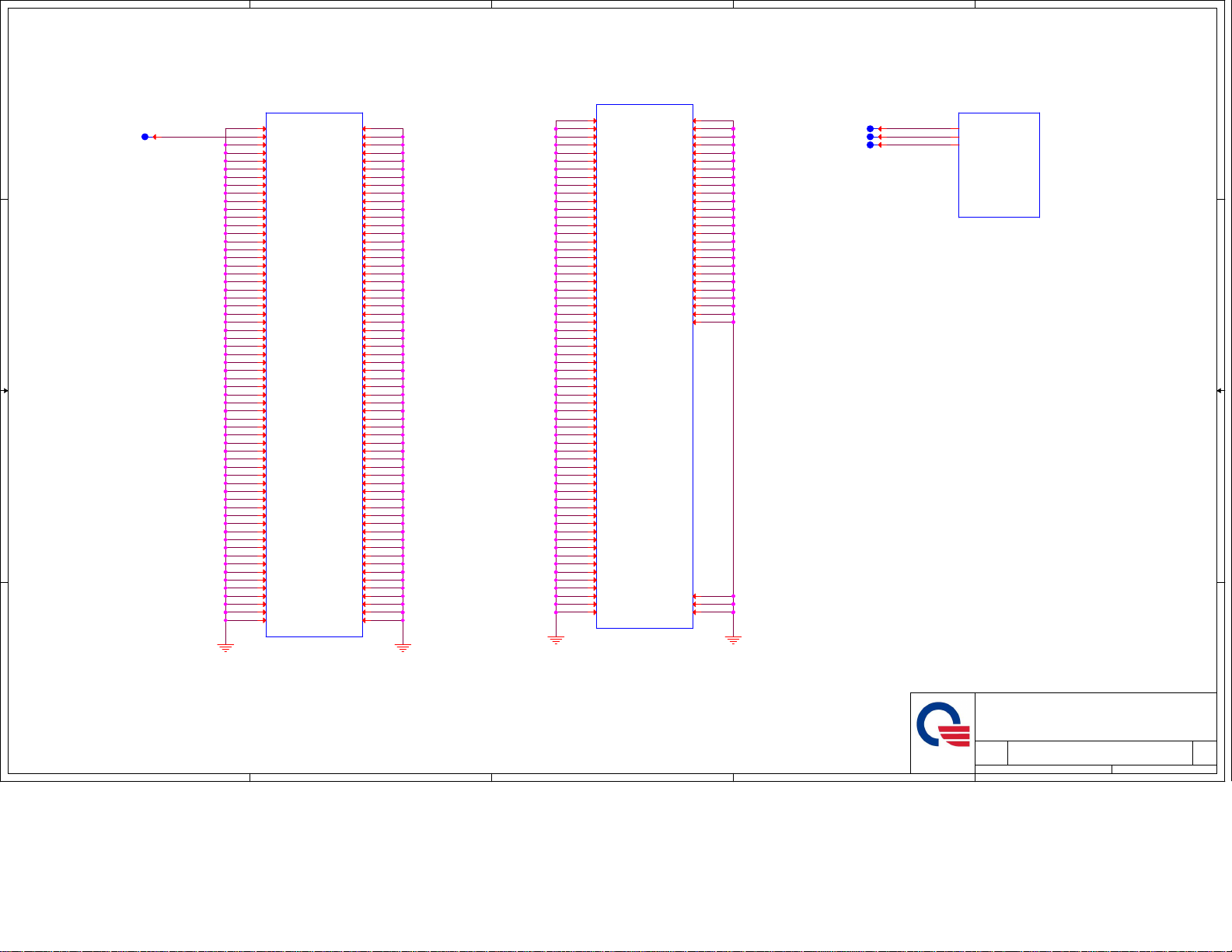

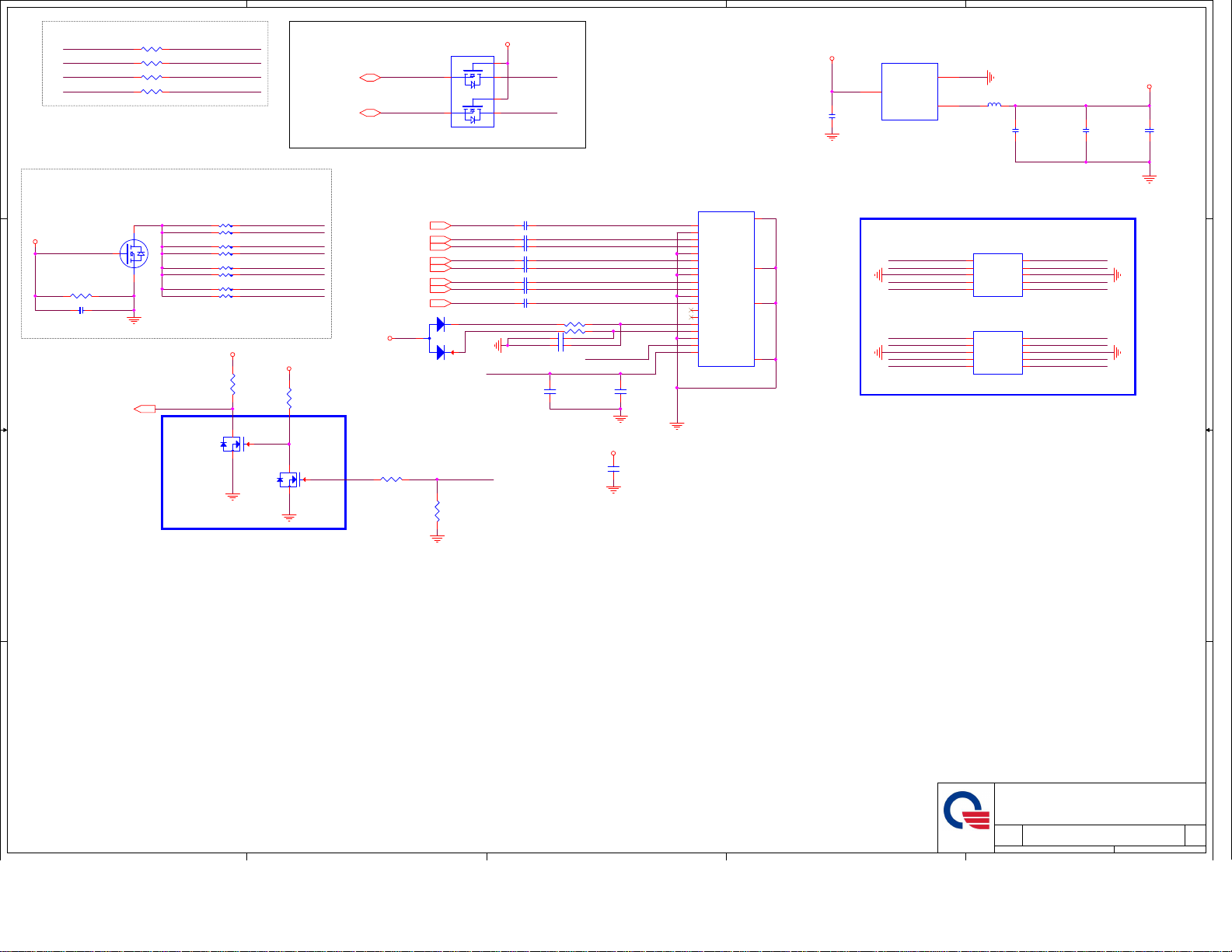

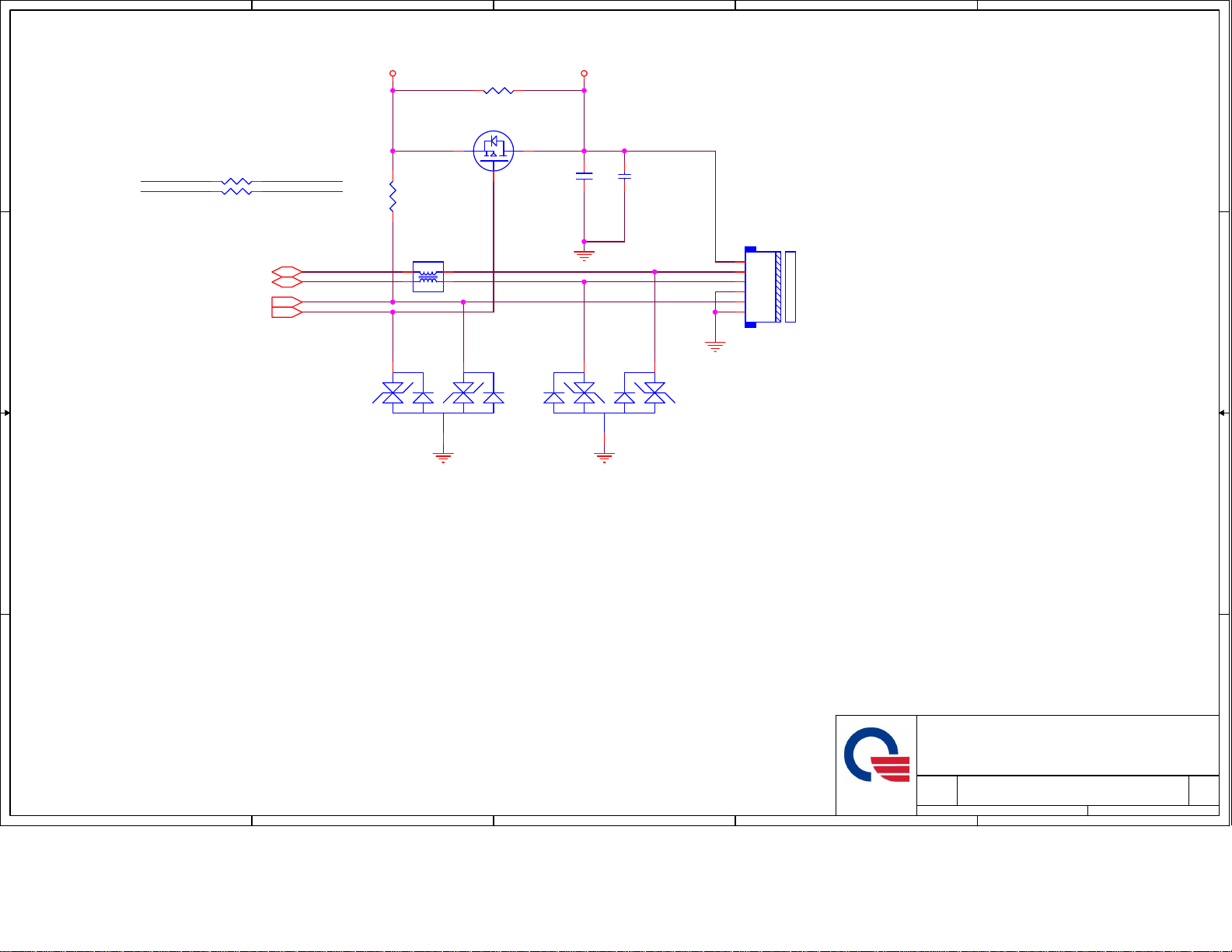

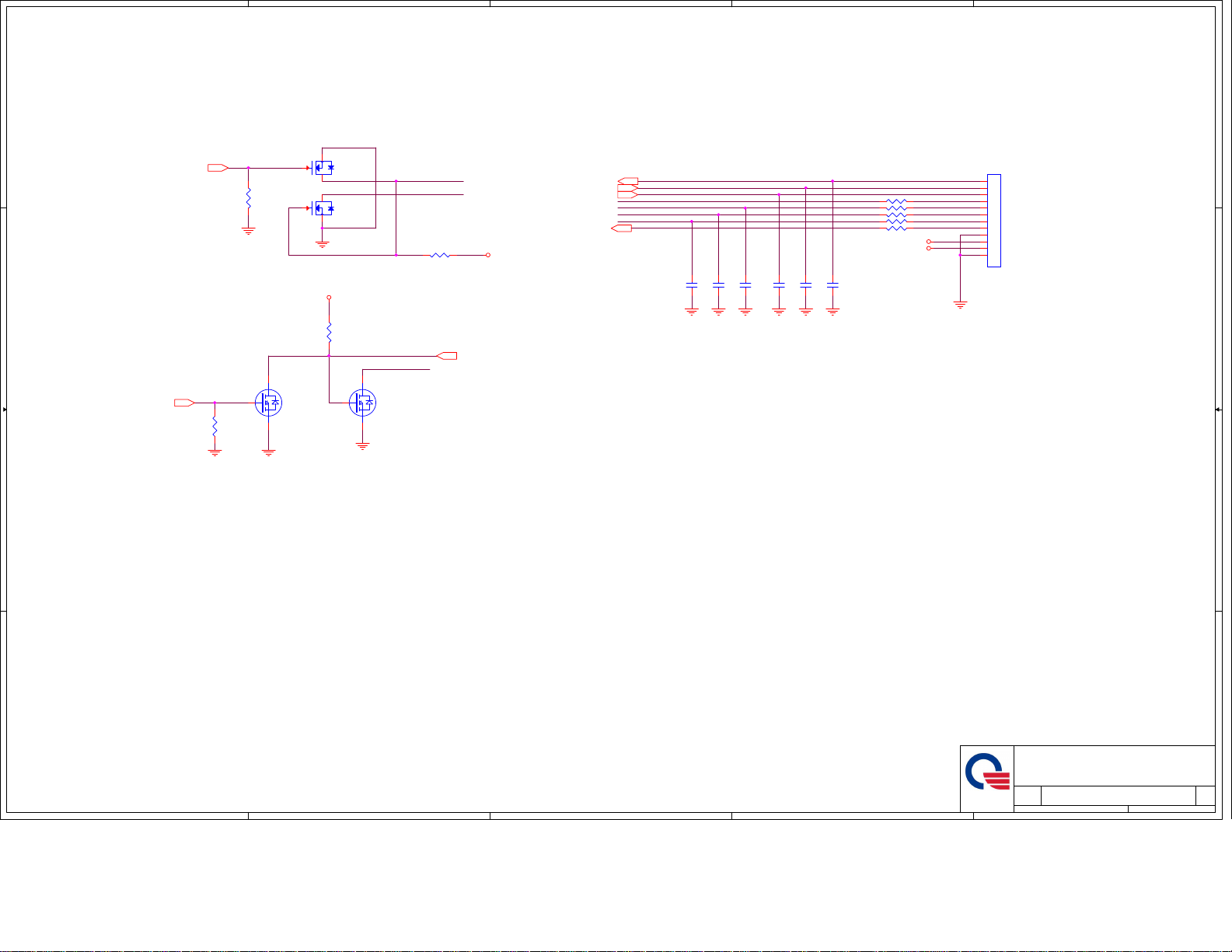

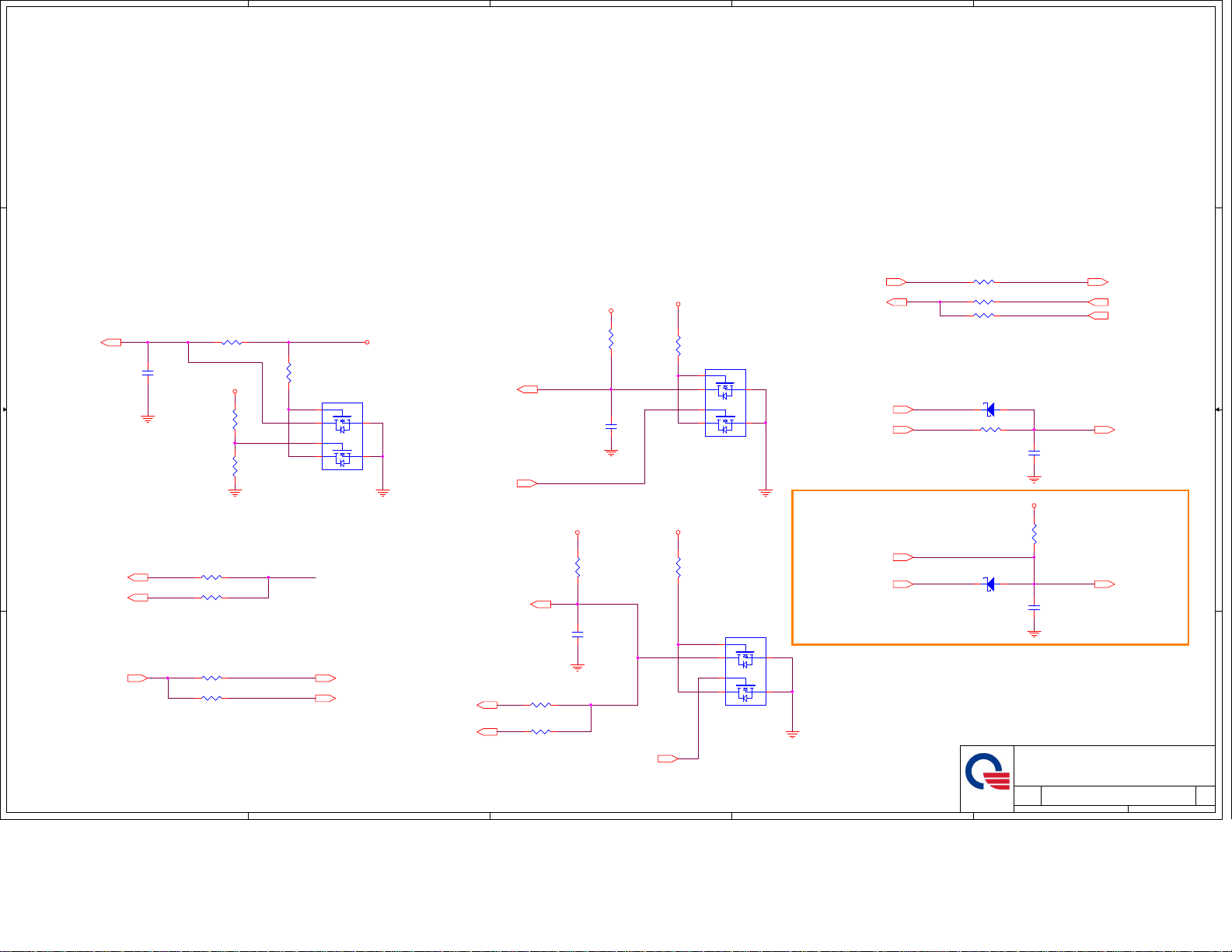

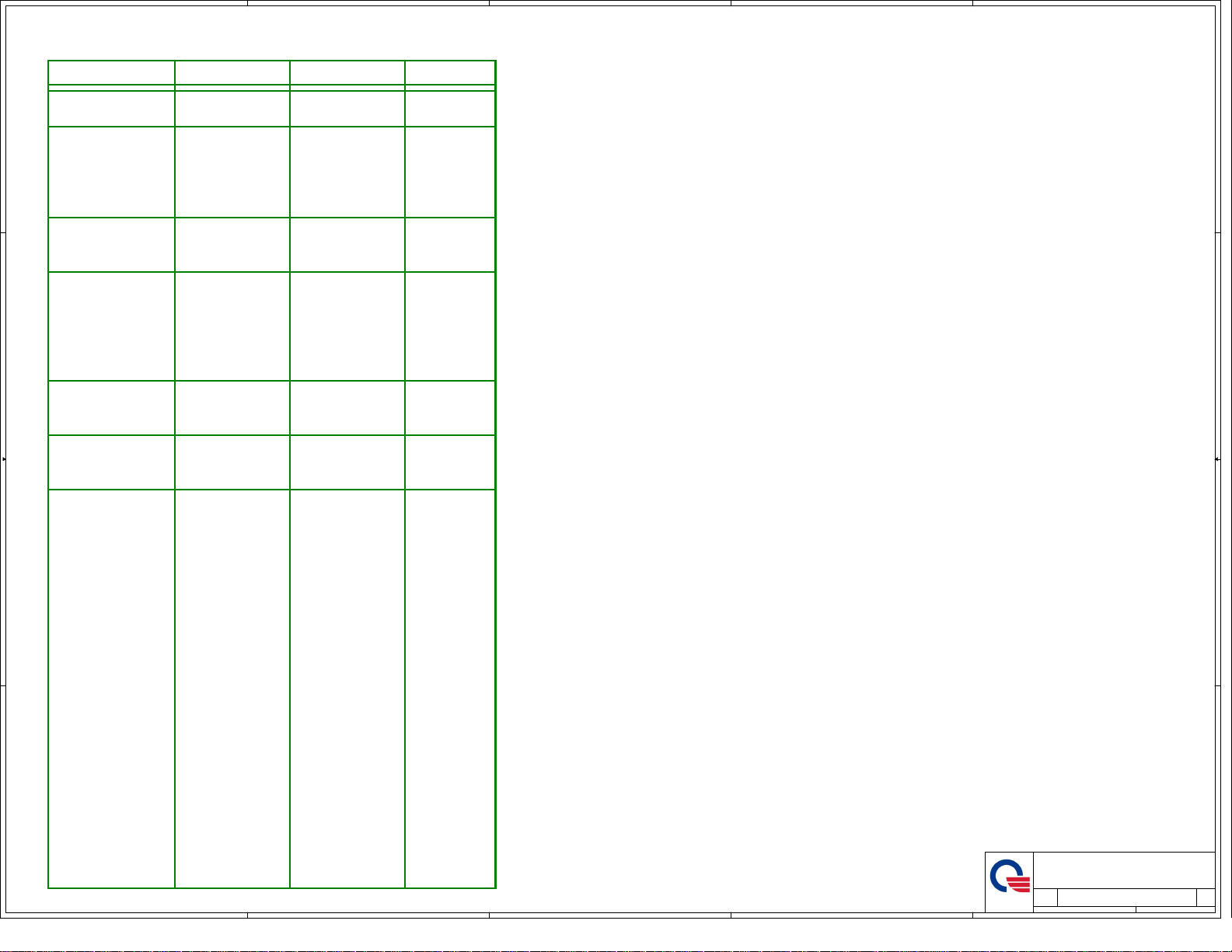

Page 3

5

4

3

2

1

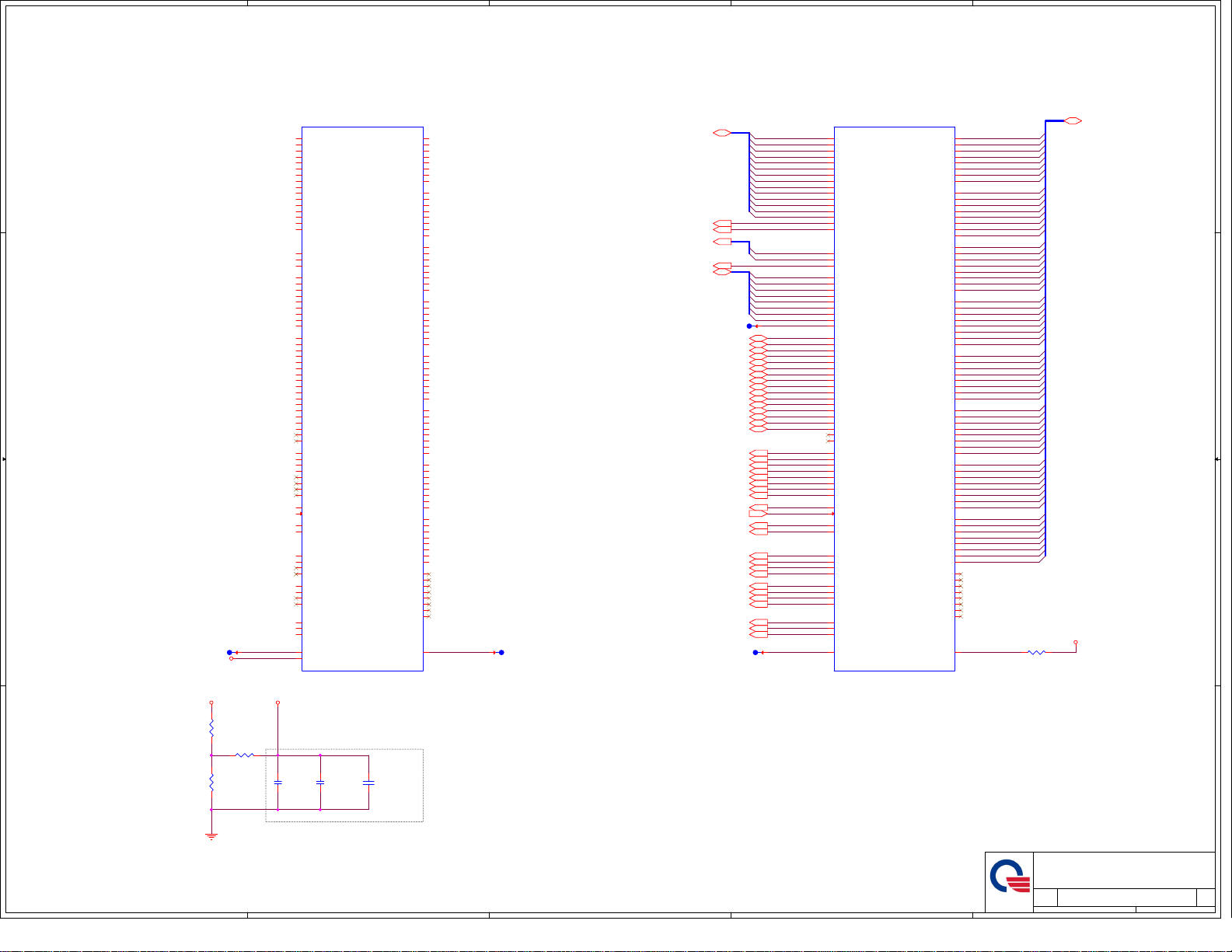

03

D D

C C

B B

TP22

M_VREF

+1.2VSUS

R104

1K/F_4

M_VREF

AE28

MA_ADD[0]

Y27

MA_ADD[1]

Y29

MA_ADD[2]

Y26

MA_ADD[3]

W28

MA_ADD[4]

W29

MA_ADD[5]

W26

MA_ADD[6]

U29

MA_ADD[7]

W25

MA_ADD[8]

U26

MA_ADD[9]

AG29

MA_ADD[10]

U27

MA_ADD[11]

T28

MA_ADD[12]

AK26

MA_ADD[13]

T26

MA_ADD[14]/MA_BG[1]

T25

MA_ADD[15]/MA_ACT_L

AG26

MA_BANK[0]

AG27

MA_BANK[1]

T29

MA_BANK[2]/MA_BG[0]

E19

MA_DM[0]

D21

MA_DM[1]

K21

MA_DM[2]

F29

MA_DM[3]

AP28

MA_DM[4]

AV26

MA_DM[5]

AR22

MA_DM[6]

BC22

MA_DM[7]

K29

MA_DM[8]

H19

MA_DQS_H[0]

G19

MA_DQS_L[0]

B22

MA_DQS_H[1]

A22

MA_DQS_L[1]

F23

MA_DQS_H[2]

E23

MA_DQS_L[2]

G27

MA_DQS_H[3]

F27

MA_DQS_L[3]

AP25

MA_DQS_H[4]

AP26

MA_DQS_L[4]

AW27

MA_DQS_H[5]

AV27

MA_DQS_L[5]

AV22

MA_DQS_H[6]

AU22

MA_DQS_L[6]

BA21

MA_DQS_H[7]

AY21

MA_DQS_L[7]

L27

MA_DQS_H[8]

L26

MA_DQS_L[8]

AE25

MA_CLK_H[0]

AE26

MA_CLK_L[0]

AD26

MA_CLK_H[1]

AD27

MA_CLK_L[1]

AB28

MA_CLK_H[2]

AB29

MA_CLK_L[2]

AB25

MA_CLK_H[3]

AB26

MA_CLK_L[3]

N29

MA_RESET_L

AE29

MA_EVENT_L

P27

MA_CKE0

P29

MA_CKE1

AK27

MA0_ODT[0]

AL26

MA0_ODT[1]

AH25

MA1_ODT[0]

AL25

MA1_ODT[1]

AH26

MA0_CS_L[0]

AL29

MA0_CS_L[1]

AH29

MA1_CS_L[0]

AL28

MA1_CS_L[1]

AG24

MA_RAS_L/MA_RAS_L_ADD[16]

AK29

MA_CAS_L/MA_CAS_L_ADD[15]

AH28

MA_WE_L/MA_WE_L_ADD[14]

B19

MA_VREFDQ

T32

M_VREF

MEMORY A

FP4 REV 1.0

U21A

H17

MA_DATA[0]

J17

MA_DATA[1]

F20

MA_DATA[2]

H20

MA_DATA[3]

E17

MA_DATA[4]

F17

MA_DATA[5]

K18

MA_DATA[6]

E20

MA_DATA[7]

A21

MA_DATA[8]

C21

MA_DATA[9]

C23

MA_DATA[10]

D23

MA_DATA[11]

B20

MA_DATA[12]

B21

MA_DATA[13]

B23

MA_DATA[14]

A23

MA_DATA[15]

G22

MA_DATA[16]

H22

MA_DATA[17]

E25

MA_DATA[18]

G25

MA_DATA[19]

J20

MA_DATA[20]

E22

MA_DATA[21]

H23

MA_DATA[22]

J23

MA_DATA[23]

F26

MA_DATA[24]

E27

MA_DATA[25]

J26

MA_DATA[26]

J27

MA_DATA[27]

H25

MA_DATA[28]

E26

MA_DATA[29]

G28

MA_DATA[30]

G29

MA_DATA[31]

AN26

MA_DATA[32]

AP29

MA_DATA[33]

AR26

MA_DATA[34]

AP24

MA_DATA[35]

AN29

MA_DATA[36]

AN27

MA_DATA[37]

AR29

MA_DATA[38]

AR27

MA_DATA[39]

AU26

MA_DATA[40]

AV29

MA_DATA[41]

AU25

MA_DATA[42]

AW25

MA_DATA[43]

AU29

MA_DATA[44]

AU28

MA_DATA[45]

AW26

MA_DATA[46]

AT25

MA_DATA[47]

AV23

MA_DATA[48]

AW23

MA_DATA[49]

AV20

MA_DATA[50]

AW20

MA_DATA[51]

AR23

MA_DATA[52]

AT23

MA_DATA[53]

AR20

MA_DATA[54]

AT20

MA_DATA[55]

BB23

MA_DATA[56]

BB22

MA_DATA[57]

BB20

MA_DATA[58]

AY19

MA_DATA[59]

BA23

MA_DATA[60]

BC23

MA_DATA[61]

BC21

MA_DATA[62]

BB21

MA_DATA[63]

K26

MA_CHECK[0]

K28

MA_CHECK[1]

N26

MA_CHECK[2]

N28

MA_CHECK[3]

J29

MA_CHECK[4]

K25

MA_CHECK[5]

L29

MA_CHECK[6]

N25

MA_CHECK[7]

AD29

MA_ZVDDIO_MEM_S

*FP4

TP20

M_B_A[13:0][9,10]

M_B_BG#1[9,10]

M_B_ACT#[9,10]

M_B_BS#[1..0][9,10]

M_B_BG#0[9,10]

M_B_DM[7..0][9,10]

TP43

M_B_DQSP0[9,10]

M_B_DQSN0[9,10]

M_B_DQSP1[9,10]

M_B_DQSN1[9,10]

M_B_DQSP2[9,10]

M_B_DQSN2[9,10]

M_B_DQSP3[9,10]

M_B_DQSN3[9,10]

M_B_DQSP4[9,10]

M_B_DQSN4[9,10]

M_B_DQSP5[9,10]

M_B_DQSN5[9,10]

M_B_DQSP6[9,10]

M_B_DQSN6[9,10]

M_B_DQSP7[9,10]

M_B_DQSN7[9,10]

M_B_CLKP0[9]

M_B_CLKN0[9]

M_B_CLKP1[9]

M_B_CLKN1[9]

M_B_CLKP2[10]

M_B_CLKN2[10]

M_B_CLKP3[10]

M_B_CLKN3[10]

M_B_RST#[9,10]

M_B_EVENT#[9,10]

M_B_CKE0[9,10]

M_B_CKE1[9,10]

M_B_ODT0[9]

M_B_ODT1[9]

M_B1_ODT0[10]

M_B1_ODT1[10]

M_B_CS#0[9]

M_B_CS#1[9]

M_B1_CS#0[10]

M_B1_CS#1[10]

M_B_RAS#[9,10]

M_B_CAS#[9,10]

M_B_WE#[9,10]

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_BG#1

M_B_ACT#

M_B_BS#0

M_B_BS#1

M_B_BG#0

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DM8

TP25

M_B_VREFDQ

AG31

MB_ADD[0]

AC30

MB_ADD[1]

AC31

MB_ADD[2]

AB32

MB_ADD[3]

AA32

MB_ADD[4]

AA33

MB_ADD[5]

AA31

MB_ADD[6]

Y33

MB_ADD[7]

AA30

MB_ADD[8]

W32

MB_ADD[9]

AG32

MB_ADD[10]

Y32

MB_ADD[11]

W33

MB_ADD[12]

AL31

MB_ADD[13]

W30

MB_ADD[14]/MB_BG[1]

V32

MB_ADD[15]/MB_ACT_L

AH32

MB_BANK[0]

AG33

MB_BANK[1]

W31

MB_BANK[2]/MB_BG[0]

D25

MB_DM[0]

D29

MB_DM[1]

E33

MB_DM[2]

J33

MB_DM[3]

AR30

MB_DM[4]

AW30

MB_DM[5]

BC30

MB_DM[6]

BC26

MB_DM[7]

N33

MB_DM[8]

B26

MB_DQS_H[0]

A26

MB_DQS_L[0]

B30

MB_DQS_H[1]

A30

MB_DQS_L[1]

F32

MB_DQS_H[2]

E32

MB_DQS_L[2]

K32

MB_DQS_H[3]

J32

MB_DQS_L[3]

AR32

MB_DQS_H[4]

AR33

MB_DQS_L[4]

AW32

MB_DQS_H[5]

AW33

MB_DQS_L[5]

BA29

MB_DQS_H[6]

AY29

MB_DQS_L[6]

BA25

MB_DQS_H[7]

AY25

MB_DQS_L[7]

P32

MB_DQS_H[8]

N32

MB_DQS_L[8]

AE33

MB_CLK_H[0]

AE32

MB_CLK_L[0]

AE30

MB_CLK_H[1]

AE31

MB_CLK_L[1]

AD32

MB_CLK_H[2]

AD33

MB_CLK_L[2]

AC33

MB_CLK_H[3]

AC32

MB_CLK_L[3]

T33

MB_RESET_L

AG30

MB_EVENT_L

U32

MB_CKE0

U33

MB_CKE1

AL30

MB0_ODT[0]

AM32

MB0_ODT[1]

AJ32

MB1_ODT[0]

AM33

MB1_ODT[1]

AJ33

MB0_CS_L[0]

AL32

MB0_CS_L[1]

AJ30

MB1_CS_L[0]

AL33

MB1_CS_L[1]

AH33

MB_RAS_L/MB_RAS_L_ADD[16]

AK32

MB_CAS_L/MB_CAS_L_ADD[15]

AJ31

MB_WE_L/MB_WE_L_ADD[14]

A19

MB_VREFDQ

MEMORY B

FP4 REV 1.0

U21I

A25

C25

C27

D27

B24

B25

B27

A27

A29

C29

B32

D32

B28

B29

A31

C31

E30

E31

G33

G32

C33

D33

G30

G31

J30

J31

L33

L32

H32

H33

L30

L31

AN31

AP32

AT32

AU32

AN33

AN32

AR31

AT33

AU30

AV32

BA33

AY32

AU33

AU31

AW31

AY33

BC31

BB30

BB28

AY27

BB32

BA31

BC29

BB29

BB27

BB26

BB24

AY23

BA27

BC27

BC25

BB25

N30

N31

R33

R32

M32

M33

R30

R31

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_CHECK[0]

MB_CHECK[1]

MB_CHECK[2]

MB_CHECK[3]

MB_CHECK[4]

MB_CHECK[5]

MB_CHECK[6]

MB_CHECK[7]

M_B_DQ[0..63] [9,10]

+1.2VSUS

AF32

M_B_ZVDDIO

MB_ZVDDIO_MEM_S

*FP4

R102 39.2/F_4

R101 *0_4

R100

A A

1K/F_4

C121

1000P/50V_4

C123

0.1U/16V/X7R_4

1 2

C122

0.47U/10V_4

Place within 1000mil of the APU

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BR/ST 2/7 (MEM)

BR/ST 2/7 (MEM)

NB5

NB5

5

4

3

2

NB5

BR/ST 2/7 (MEM)

Date: Sheet of

Tuesday, March 01, 2016 3 53

Date: Sheet of

Tuesday, March 01, 2016 3 53

Date: Sheet of

Tuesday, March 01, 2016 3 53

1

1A

1A

1A

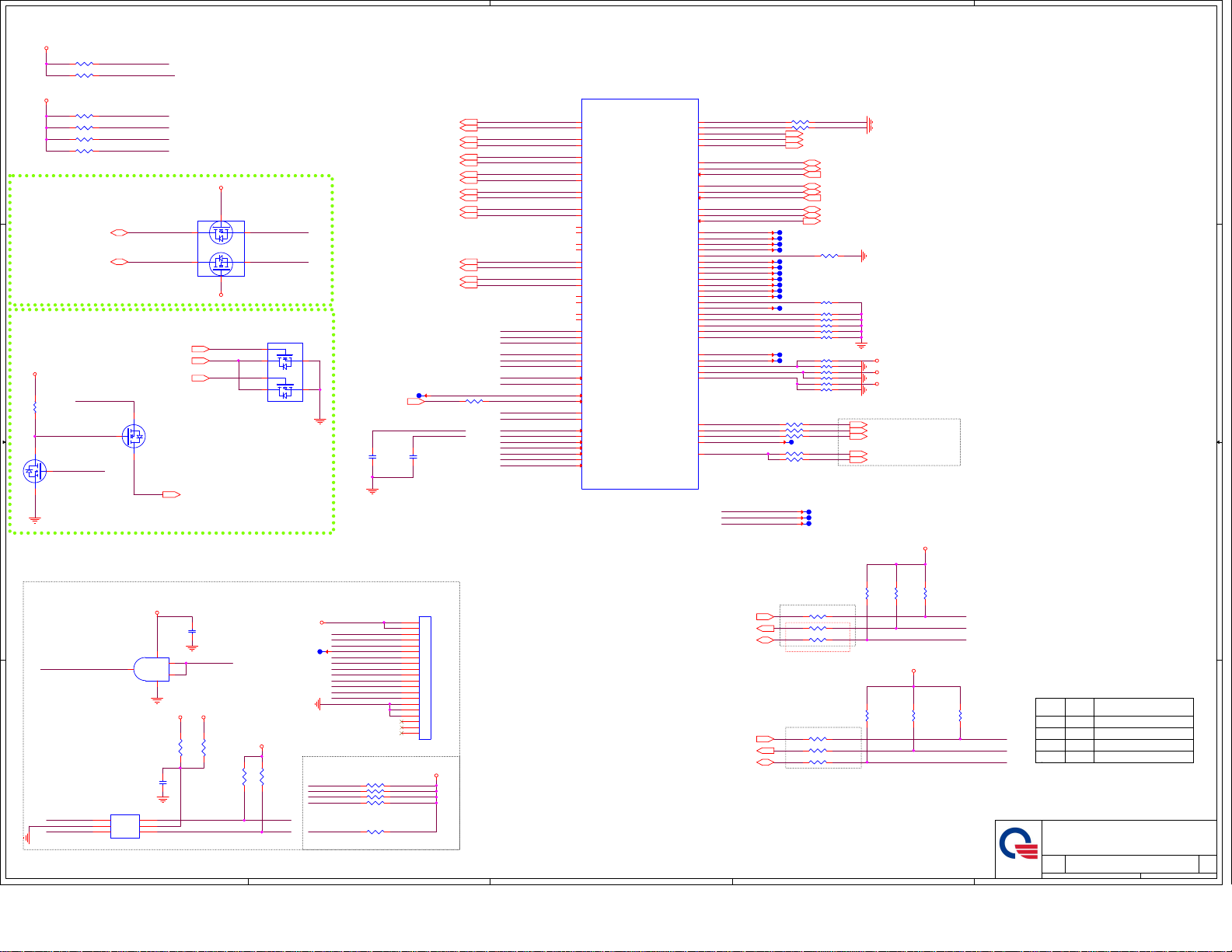

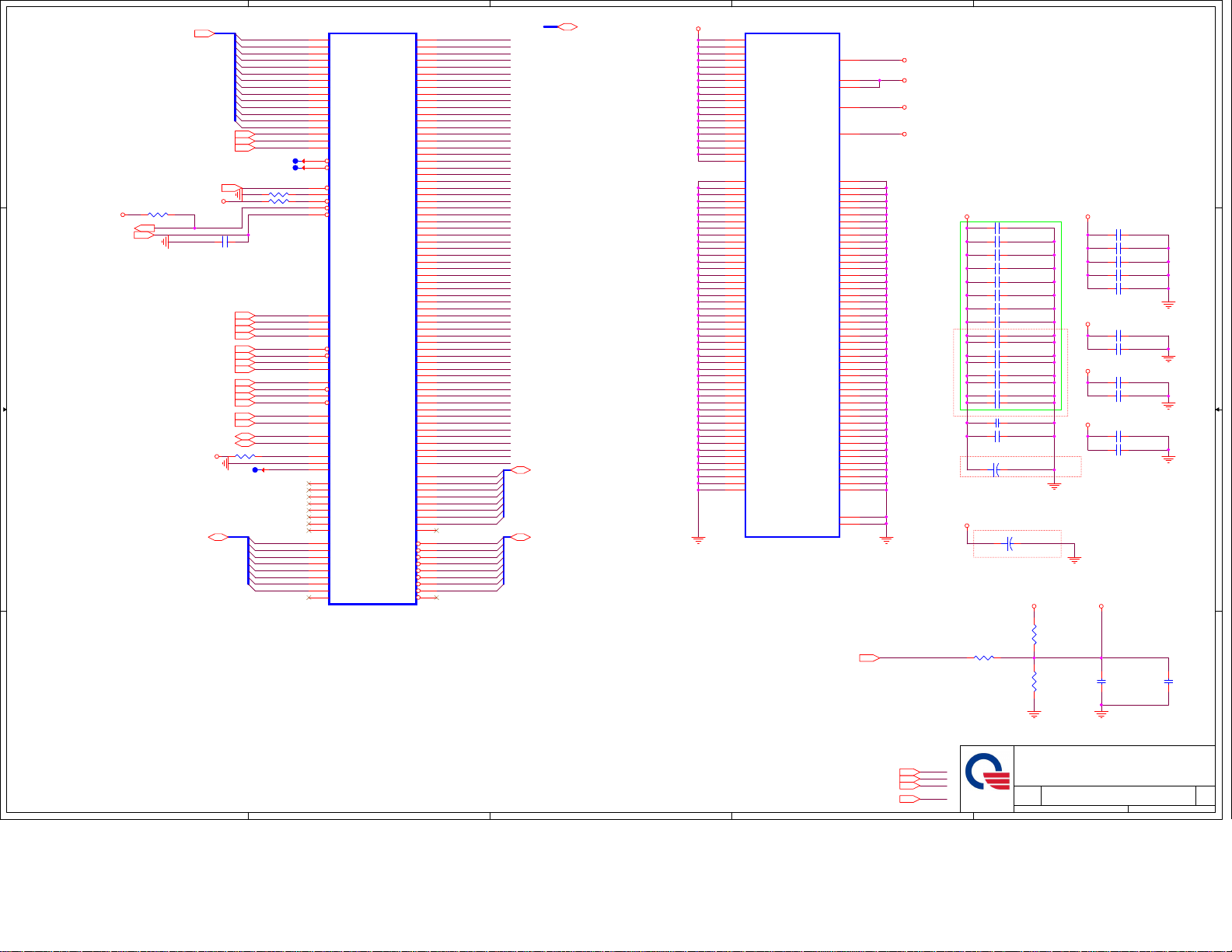

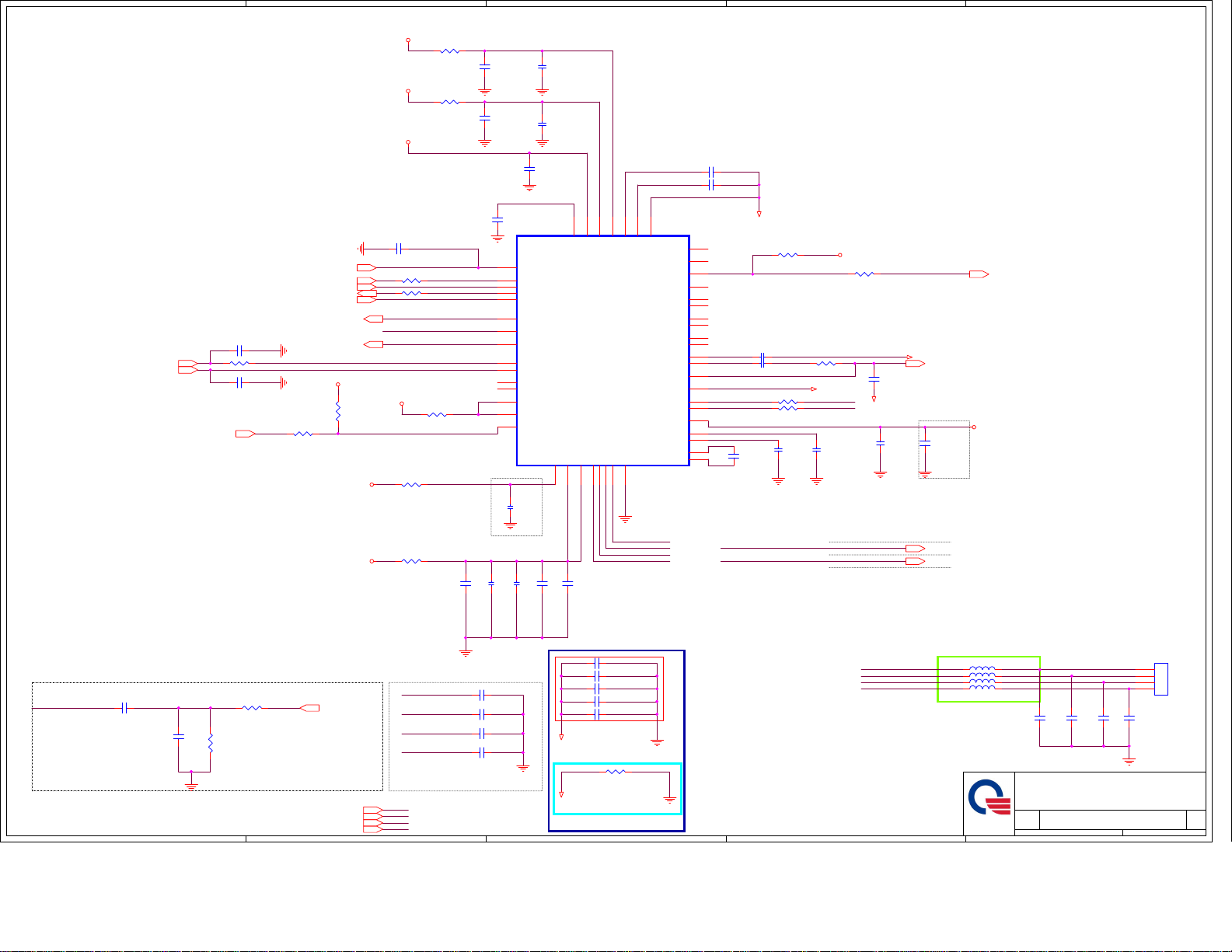

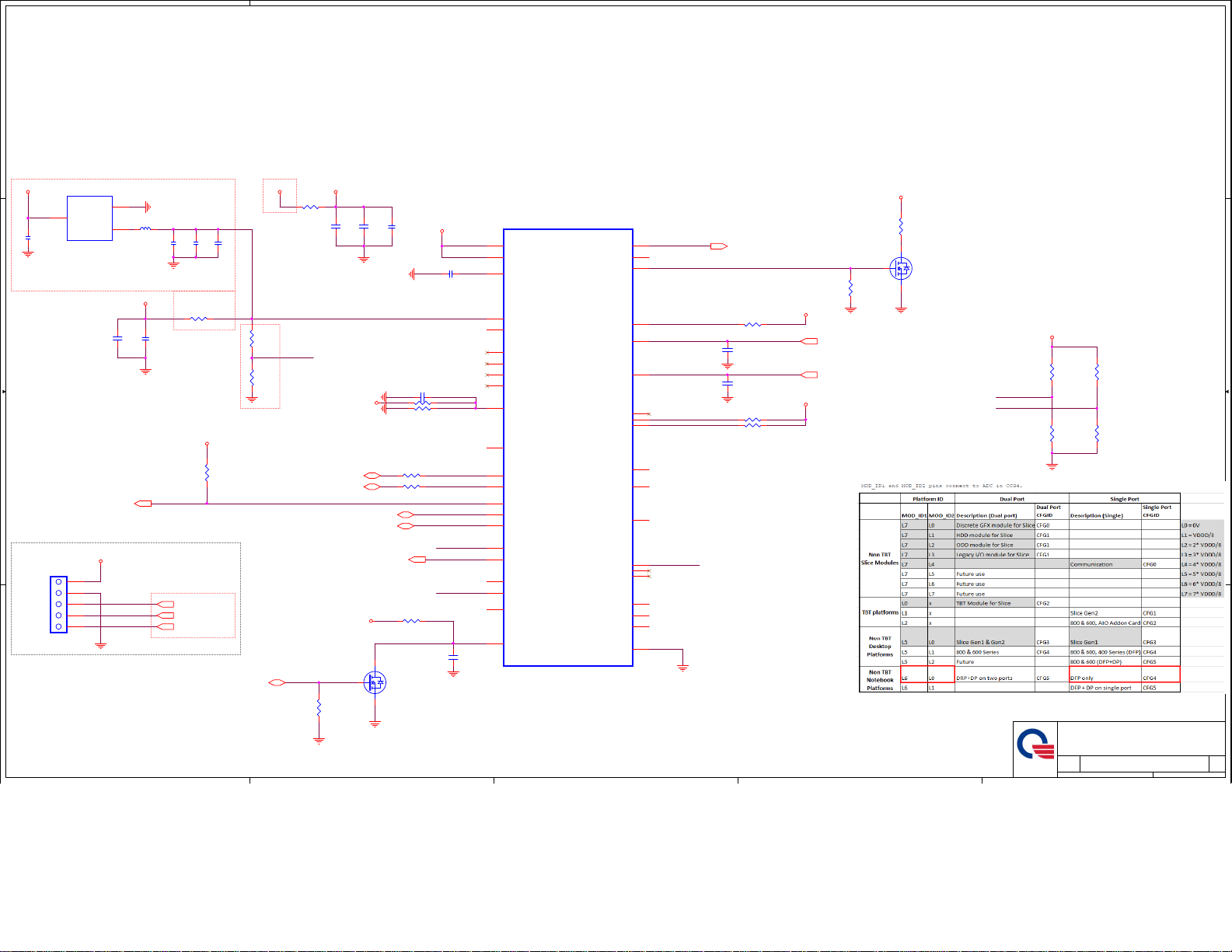

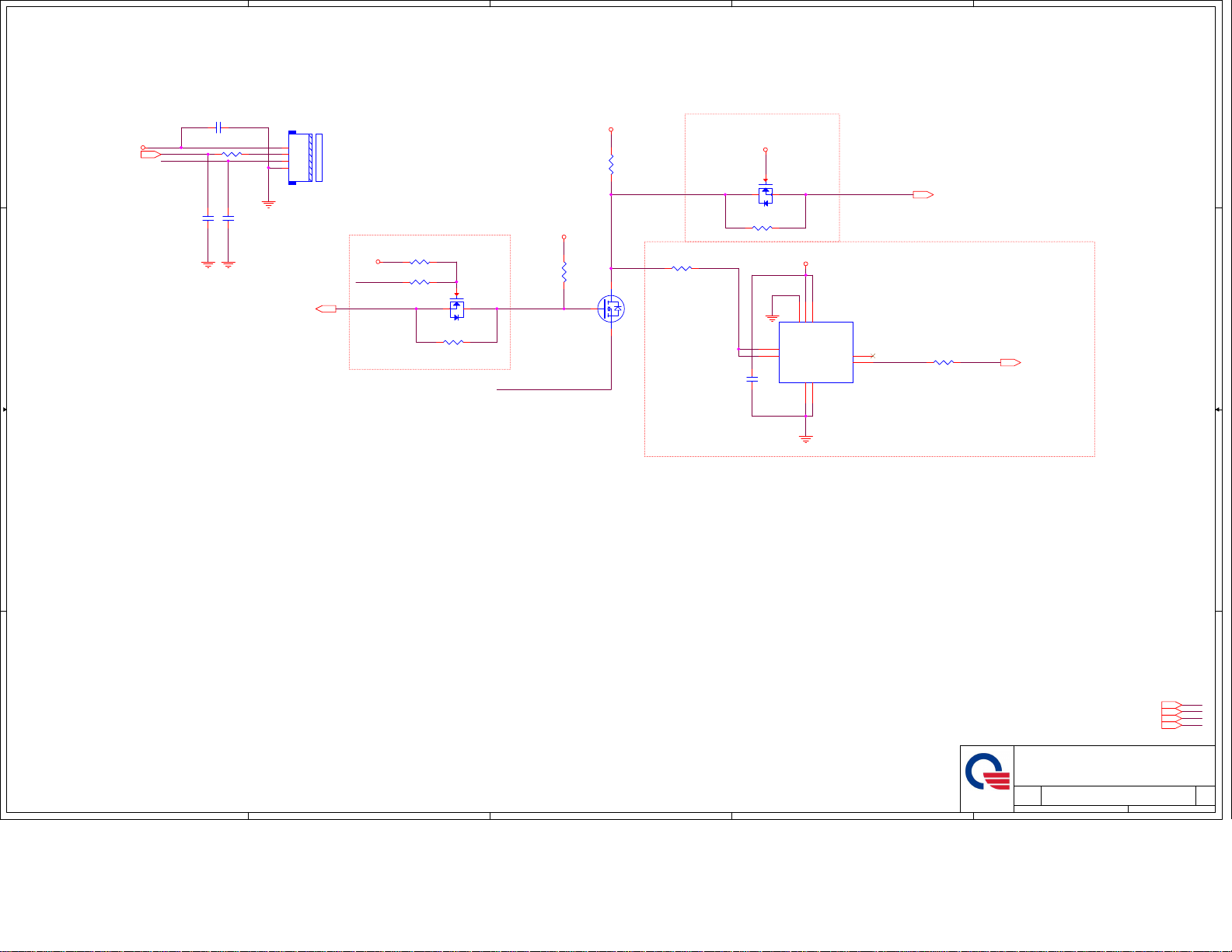

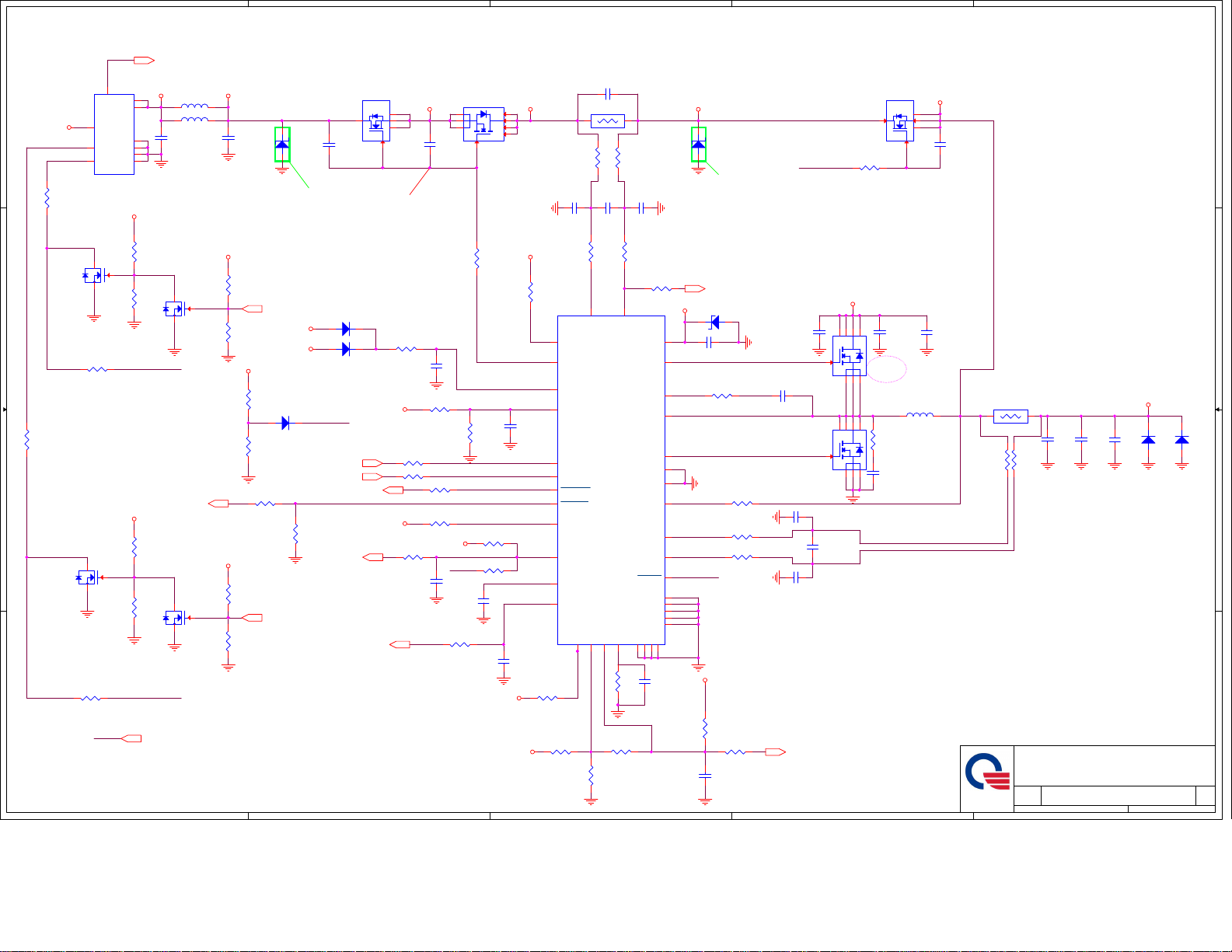

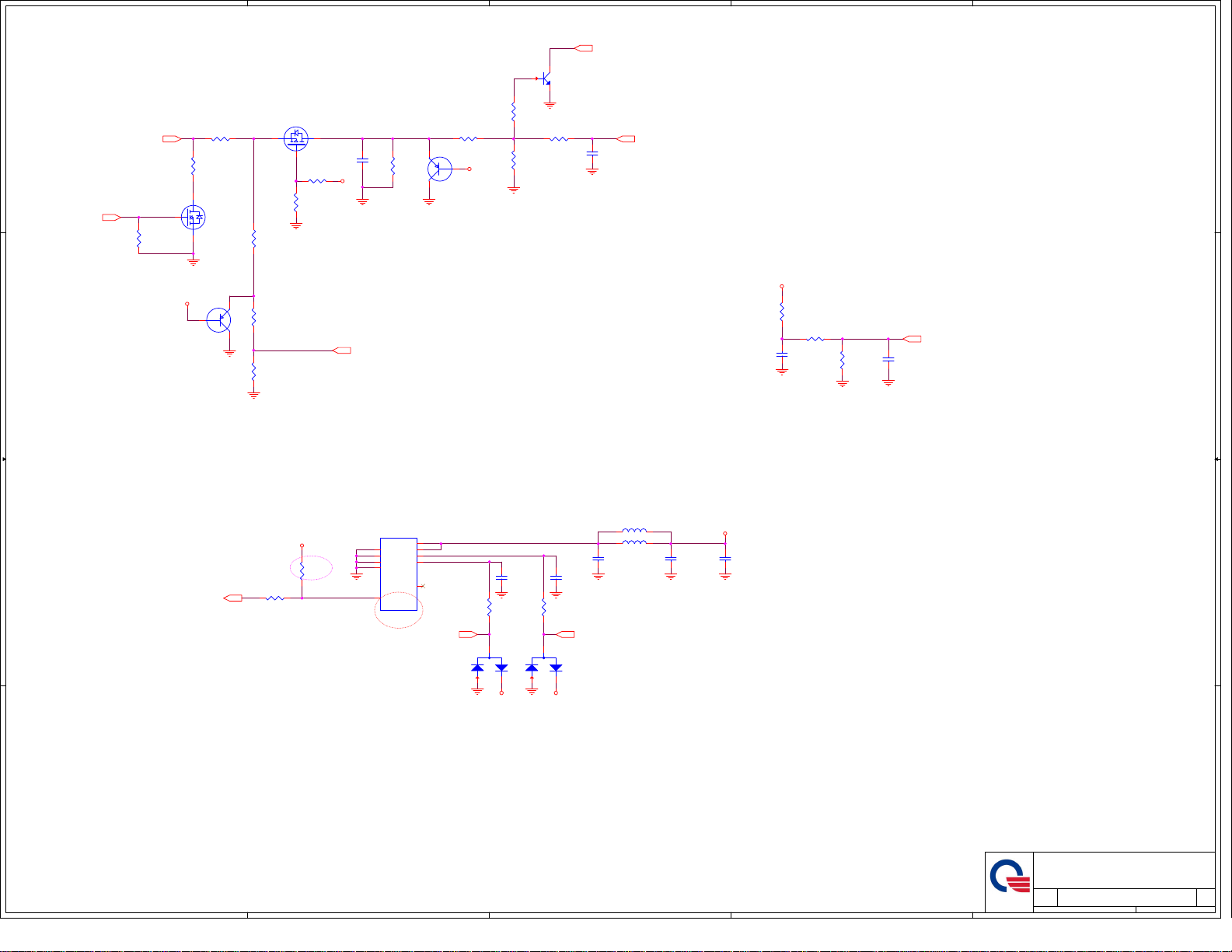

Page 4

5

4

3

2

1

+1.8V

APU_PROCHOT#

APU_RST#

APU_PW ROK

APU_PROCHOT#

APU_ALERT#

APU_SIC

APU_SID

KBC_SMDATA

1

2

3

KBC_SMCLK

KBC_PROCHOT[35]

APU_PROCHOT#[38,43,45]

OCP_PW M_OUT[36]

PJA138K

Q6

+1.8V

LS

5

6

2

+1.8V

KBC_PROCHOT

APU_PROCHOT#

FAN_FULL_ SPEED# [28,29]

43

APU_SIC

1

APU_SID

Q12

DMN5L06DW K/50V _0.302A

Q8

5

2

6

2N7002DW

43

1

HDMI

DP to VGA Chip

eDP

APU_PG[43,45]

C162

*150P/50 V_4

TP19

DDI1_TX0_P[12]

DDI1_TX0_N[12]

DDI1_TX1_P[12]

DDI1_TX1_N[12]

INT_eDP_TXP0[11]

INT_eDP_TXN0[11 ]

INT_eDP_TXP1[11]

INT_eDP_TXN1[11 ]

APU_RST#

APU_PW ROK

C187

*150P/50 V_4

IN_D2[13]

IN_D2#[13]

IN_D1[13]

IN_D1#[13]

IN_D0[13]

IN_D0#[13]

IN_CLK[13]

IN_CLK#[13]

R135 0_4

SVT

SVC

SVD

GFX_SVT_R

GFX_SVC_ R

GFX_SVD_ R

APU_SIC

APU_SID

APU_RST#

APU_PW ROK

APU_PROCHOT#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

U21C

DISPLAY/SVI2/JTAG/TEST

B6

DP2_TXP[0]

A6

DP2_TXN[0]

D7

DP2_TXP[1]

C7

DP2_TXN[1]

A7

DP2_TXP[2]

B7

DP2_TXN[2]

D9

DP2_TXP[3]

C9

DP2_TXN[3]

A2

DP1_TXP[0]

A3

DP1_TXN[0]

B4

DP1_TXP[1]

A4

DP1_TXN[1]

D5

DP1_TXP[2]

C5

DP1_TXN[2]

A5

DP1_TXP[3]

B5

DP1_TXN[3]

E2

DP0_TXP[0]

E1

DP0_TXN[0]

E3

DP0_TXP[1]

E4

DP0_TXN[1]

D1

DP0_TXP[2]

D2

DP0_TXN[2]

C1

DP0_TXP[3]

B1

DP0_TXN[3]

C15

SVT0

D17

SVC0

D19

SVD0

B15

SVT1

B16

SVC1

A18

SVD1

B18

SIC

C17

SID

D15

RESET_L

C19

PWROK

A15

PROCHOT_L

B17

ALERT_L

H15

TDI

H14

TDO

D13

TCK

G15

TMS

J14

TRST_L

C13

DBRDY

A11

DBREQ_L

FP4 REV 1.0

*FP4

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP2_AUXP

DP2_AUXN

DP2_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

TEMPIN0

TEMPIN1

TEMPIN2

TEMPINRETURN

TEST28_H

TEST28_L

DP_STEREOSYNC/TEST36

VDDCR_GFX_SENSE

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

VDDP_SENSE

VSS_SENSE

A9

DP_ZVSS

B9

DP_AUX_ZVSS

G5

APU_LVDS _BLON

G6

APU_DISP_ON

F11

APU_DPST_P WM

H9

G9

E9

F7

E7

F5

F8

INT_eDP_AUXP

E8

INT_eDP_AUXN

G8

K24

CORETYPE

RSVD_1

E15

APU_TEMPIN0

E14

APU_TEMPIN1

E12

APU_TEMPIN2

F14

APU_TEMPRETURN

AK24

APU_TEST410

TEST410

AL24

APU_TEST411

TEST411

P24

APU_THERMDA

TEST4

N24

APU_THERMDC

TEST5

AN24

APU_TEST6

TEST6

AB8

APU_TEST9

TEST9

Y9

APU_TEST10

TEST10

B10

APU_TEST14

TEST14

D11

APU_TEST15

TEST15

A10

APU_TEST16

TEST16

C11

APU_TEST17

TEST17

B11

APU_TEST11

TEST11

A14

APU_TEST18

TEST18

B14

APU_TEST19

TEST19

A13

APU_TEST28_ H

B13

APU_TEST28_ L

P26

APU_TEST31

TEST31

E11

DP_STEREOS YNC

A17

APU_TEST37

TEST37

P_STEREOSYNC: HDMI enable pin.

D

H11

VDDCR_GFX_ SENSE

J12

VDDCR_NB_S ENSE

G12

VDDCR_CPU_SENSE

AY18

VDDP_SENSE

H12

VSS_SENSE

R485 2K/F_ 4

R477 150/F_4

TP11

TP26

TP27

TP51

TP16

TP15

TP17

TP14

TP13

TP28

TP29

TP56

TP50

TP48

R447 BR@0_4

R473 0_4

R451 0_4

TP41

R442 BR@0_4

R446 0_4

Type1: R447, R442 Stuff

Type2/3: R447, R442 No Stuff

VDDCR_CPU_SENSE

VDDCR_NB_S ENSE

VDDCR_GFX_ SENSE

APU Serial VID

APU_LVDS _BLON [11]

APU_DISP_ON [11]

APU_DPST_P WM [11]

IN_DDC_SCL [13]

IN_DDC_SDA [13]

IN_HPD [13]

INT_DDI1_AUX P [12]

INT_DDI1_AUX N [12 ]

DDI1_HPD_CON [12]

INT_eDP_AUXP [11]

INT_eDP_AUXN [11]

EDP_HPD [11]

R423 0_4

R467 *1K/F_4

R457 *1K/F_4

R454 *1K/F_4

R456 *1K/F_4

R154 1K/F_4

R164 1K/F_4

R313 *1K/F_4

R312 *1K/F_4

R170 1K/F_4

R169 *1K/F_4

R404 *1K/F_4

R405 *1K/F_4

DIFFERENTIAL ROUTING

TP55

TP57

TP52

+1.8V

+1.8V

+1.8V

GFX_FB_H [45]

APU_VDDNB _FB_H [43]

APU_VDD_FB_H [4 3]

GFX_FB_L [45]

APU_VDD_VDDNB_FB_ L [43]

+1.8V

R114 301/F_4

R136 301/F_4

+1.8V

D D

C C

B B

R152 1K/F_4

R401 1K/F_4

R390 1K/F_4

R383 1K/F_4

Ty

pe1/3: LS, 1.8V

Type2: LS, 3.3V

KBC_SMCLK[12,19,29,35]

KBC_SMDATA[12,19,29,35]

APU_PROCHOT# Signal Level:

Type1/3: +1.8V

Type2: +3.3V

+1.8V

R70

2.2K_4

3

2

KBC_PROCHOT

2N7002K

Q7

1

04

R381

*1K/F_4

+1.8V

R395

*1K/F_4

R411

*1K/F_4

SVT

SVC

SVD

R422

*1K/F_4

GFX_SVT_R

GFX_SVC_ R

GFX_SVD_ R

VFIX MODE

0

0

110 0.9V

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet

VID Override table (VDD)

SVDSVC

0

11

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Tuesday, March 01, 2016 4 53

Tuesday, March 01, 2016 4 53

Tuesday, March 01, 2016 4 53

Boot Voltage

1.1V

1.0V

0.8V

BR/ST 3/7 (DIS/MISC)

BR/ST 3/7 (DIS/MISC)

BR/ST 3/7 (DIS/MISC)

1

of

1A

1A

1A

HDT+ Connector for Debug only

Can remove on MP

CPU_LDT_RST_HTPA#

A A

APU_RST# APU_RST_L_BUF

APU_PW ROK

1

2

U4

TC7SH08FU

4

0.1U/16V/X7R_4

U5

A1

Y1

GND

VCC

A23Y2

74LVC2G07GW

5

C175

+3V

C137

0.1U/16V/X7R_4

2

APU_RST#

1

3 5

+3V

+1.8V

R140

R115

0_4

*0_4

R111

1K/F_4

6

5

4

APU_PW ROK_BUF

+1.8V

+1.8V

APU_TEST18

APU_TEST19

APU_RST_L_BUF

INT

CPU_LDT_RST_HTPA#

TP59

APU_DBREQ#

APU_DBRDY

APU_TCK

APU_TMS

APU_TDI

APU_TRST#

APU_TDO

APU_PW ROK_BUF

Close to HDT & No remove.

R137

1K/F_4

APU_TDI

R431 1K/F_4

APU_TCK

R461 1K/F_4

APU_TMS

R453 1K/F_4

APU_TRST#

R413 1K/F_4

APU_DBREQ#

R475 1K/F_4

4

J1

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

HDT CONN

88511-20 01-20p-l

+1.8V

APU_SVT[43]

APU_SVC[43]

APU_SVD[43]

GFX Serial VID

GFX_SVT[45]

GFX_SVC[45]

GFX_SVD[45]

3

Place near APU within 500mil

R412 0_4

R382 0_4

R373 0_4

SI, 0221, SVID R change to 0ohm

Place near APU within 500mil

R408 BR@0_4

R396 BR@0_4

R392 BR@0_4

R372

*1K/F_4

R391

*1K/F_4

2

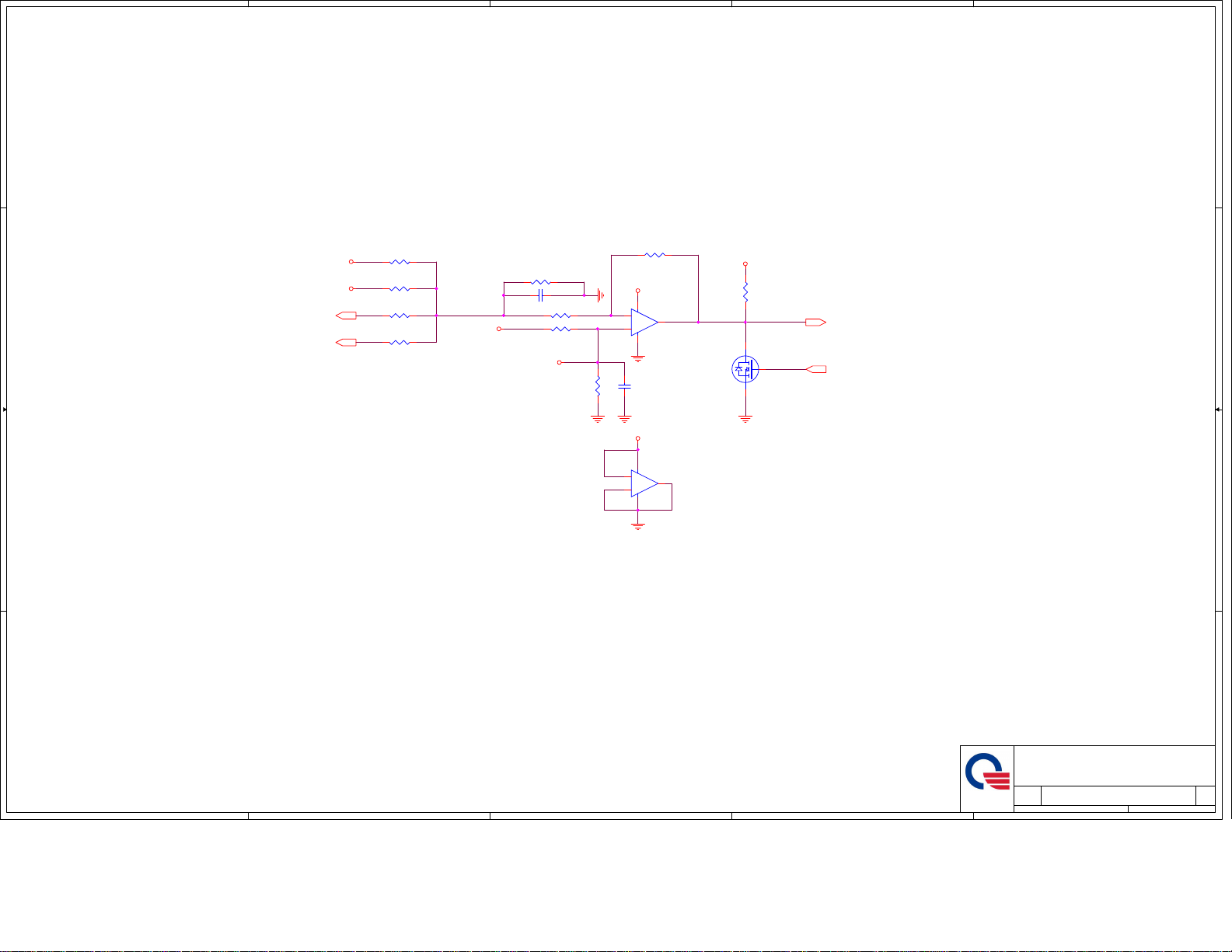

Page 5

5

+3V_DEEP_SUS+3V_DEEP_SUS

U9

*MC74VHC1G08DFT2G

PCIE_RST#_R1[15,16,26,30]

D D

KBC_ECPH_CLK[35]

KBC_ECPH_DATA[35]

+3V

R310 2.2K_4

R303 2.2K_4

R400 10K/F_4

R294 10K/F_4

R287 10K/F_4

R187 2.2K_4

R186 2.2K_4

R529 10K/F_4

R513 10K/F_4

R469 10K/F_4

R218 BR@10K/F_4

R230 *10K/F_4

R524 10K/F_4

R518 10K/F_4

+3V

R503 10K/F_4

R7737 *10K/F_4

ACZ_SDOUT_AUDIO[14]

ACZ_SYNC_AUDIO[14]

BIT_CLK_AUDIO[14]

ACZ_RST#_AUDIO[14]

R525 *1K/F_4

1 2

G2

*SOLDERJUMPER-2

ACZ_SDIN0[14]

+3V_DEEP_SUS

C C

+3V_DEEP_SUS

B B

A A

PCIE_RST#_R1

SYS_RST# internal 10K pull up

SYS_RST#

6

*DMN5L06DWK/50V_0.302A

to DDR SMBUS

FCH_3S_SMCLK

FCH_3S_SMDATA

CLKREQG#

PCIE_CLKREQ_CARD#

FPR_OFF

to TP SMBUS

SMB_NIC_SMCLK

SMB_NIC_SMDATA

PWR_BTN_OUT#

NIC_SMBUS_ALERT#

NMI_SMI_DBG#

APU_TYPE_FCH

WLAN_WAKE#

LOW_BAT#

CR_RST#

mSATA_DET

EC_RCIN#

+1.8V

Q45

+1.8V

To Azalia

R211 33_4

R207 33_4

R209 BLM15BB470SN1D(47,300MA)

R210 33_4

4

R227 0_4

R497 *2.2K_4

LS

5

43

1

2

R501 *2.2K_4

R224 *ST@10K/F_4

ACZ_SDOUT_R

ACZ_SYNC_R

ACZ_BCLK_R

ACZ_RST#_R

ACZ_SDIN0

R234

*4.7K/F_4

35

1

2

APU_S5_CLK

APU_S5_DATA

for GPIO145~148

T

ype1,3 pop those resistor

Type2 can NC them

EC32

BR@1K/F_4

4

PCIE_RST#_R PCIE_RST#

R181 33_4

C259 150P/50V_4

LPC_RST#[30,34,35]

RSMRST#[37]

PWR_BTN_OUT#[36]

SYS_PWRGD[37]

SYS_RST#[6]

NIC_SMBUS_ALERT#[15]

SLP_S3#_3R[36,37,47]

SLP_S5#_3R[15,18,30,36,37,40]

S0A3_GPIO[35,37,47]

S5_MUX_CTRL[42]

FPR_OFF[17]

RUNSCI_EC#[29,35]

ADP_PRES_OUT[35,47]

ZERO_ODD_DA#[33]

ZERO_ODD_DP#[33]

TPM_INT#[26]

LOW_BAT#[35]

PCIE_CLKREQ_WLAN#[30]

KBL_DET#[24]

PCIE_CLKREQ_CARD#[16]

NMI_SMI_DBG#[34,35]

R197 *10K/F_4

R190 *10K/F_4

R185 10K/F_4

R184 10K/F_4

RTC_CLK[6,36]

C434 18P/50V_4

C431 18P/50V_4

EC31

BR@1K/F_4

Y2

32.768KHz

PCIE_CLKREQ_LAN#_D[15]

C254

BR@1K/F_4

12

R452 33_4

C428 *100P/50V_4

TP31

TP61

R484 10K/F_4

R494 10K/F_4

R498 10K/F_4

R502 10K/F_4

R522

20M_4

C257

BR@1K/F_4

Discrete VRAM Group #1

Discrete VRAM Group #2

Discrete VRAM Group #3

UMA

C412150P/50V_4

LPC_RST#_R

PCIE_RST#

PWR_BTN_OUT#

SYS_RST#

NIC_SMBUS_ALERT#

S0A3_GPIO

APU_TEST0

APU_TEST1

APU_TEST2

EC_RCIN#

FPR_OFF

RUNSCI_EC#

DGPU_PWR_EN

LOW_BAT#

PCIE_CLKREQ_LAN#

PCIE_CLKREQ_WLAN#

PCIE_CLKREQ_CARD#

CLKREQG#

NMI_SMI_DBG#

CR_RST#

VBIOS_ID2

ACZ_BCLK_R

ACZ_SDIN0

ACZ_SDIN1

ACZ_SDIN2

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

GPIO145

GPIO146

APU_S5_CLK

APU_S5_DATA

32K_X1

32K_X2

Q38

*2N7002K

Type1 onlly

VBIOS_ID

+3V

2

3

R409 0_4

VBIOS_ID1 VBIOS_ID2

BB12

LPC_RST_L

AN7

PCIE_RST_L/EGPIO26

AE4

RSMRST_L

AE1

PWR_BTN_L/AGPIO0

BC9

PWR_GOOD

AF2

SYS_RESET_L/AGPIO1

AG2

WAKE_L/AGPIO2

AK7

SLP_S3_L

AH5

SLP_S5_L

AE8

S0A3_GPIO/AGPIO10

AH8

S5_MUX_CTRL/EGPIO42

AH6

TEST0

AK8

TEST1/TMS

AE3

TEST2

AY15

ESPI_RESET_L/KBRST_L/AGPIO129

BC19

GA20IN/AGPIO126

AD7

LPC_PME_L/AGPIO22

BB13

LPC_SMI_L/AGPIO86

AG3

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

AD5

IR_TX0/USB_OC5_L/AGPIO13

AL8

IR_TX1/USB_OC6_L/AGPIO14

AN8

IR_RX1/AGPIO15

AE2

IR_LED_L/LLB_L/AGPIO12

BC15

CLK_REQ0_L/SATA_IS0_L/ SATA_ZP0_L/AGPIO92

BB17

CLK_REQ1_L/AGPIO115

BC17

CLK_REQ2_L/AGPIO116

BB18

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

BB16

CLK_REQG_L/OSCIN/EGPIO132

AH9

USB_OC0_L/TRST_L/AGPIO16

AG1

USB_OC1_L/TDI/AGPIO17

AH2

USB_OC2_L/TCK/AGPIO18

AL9

USB_OC3_L/TDO/AGPIO24

AU6

AZ_BITCLK/I2S_BCLK_MIC

AR8

AZ_SDIN0/I2S_DATA_MIC[0]

AP6

AZ_SDIN1/I2S_LR_PLAYBACK

AR5

AZ_SDIN2/I2S_DATA_PLAYBACK

AU9

AZ_RST_L/I2S_LR_MIC

AT9

AZ_SYNC/I2S_BCLK_PLAYBACK

AR7

AZ_SDOUT/I2S_DATA_MIC1

BB10

I2C0_SCL/EGPIO145

BB9

I2C0_SDA/EGPIO146

BB7

I2C1_SCL/EGPIO147

BC7

I2C1_SDA/EGPIO148

AG7

RTCCLK

AT1

X32K_X1

AT2

X32K_X2

R410

10K/F_4

1

PCIE_CLKREQ_LAN#

3

0

0

1

1 1

ACPI/SD/AZ/GPIO/RTC/I2C/UART/MISC

S5

X

X

S5

S5

X

S5

S5

S5

X

S5

Power Domain

CZ CZ-L

S0

S0

S0

S5

S5

S0

X

S5

S5

S5

S5

S5

S5

S5

S5

S5

S5

S0

S0

S0

S0

S0

S0

S0

S5

S5

S5

S5

S5

S5

S5

S5

S0

X

S0

S0

S0

S0

S0

S0

2

+1.8V

SI, 0220, HP request to change PLT_ID to 100

PLT_ID1

R479 10K/F_4

R151 *10K/F_4

R150 *10K/F_4

+1.8V

R491 *10K/F_4

R471 10K/F_4

R533 *10K/F_4

AGPIO24AGPIO6

0

Default

1

0

U21D

S0

S5

S0

S0

S0

S0

S0

S0

S0

S5

FP4 REV 1.0

*FP4

R462 *10K/F_4

+3V_DEEP_SUS

R506 10K/F_4

R199 10K/F_4

SD0_WP/EGPIO101

S0

S0

SD0_PWR_CTRL/AGPIO102

X

S0

S0

S5

SD0_CLK/EGPIO95

S0

S0

SD0_CMD/EGPIO96

S0

S0

SD0_DATA0/EGPIO97

S0

S0

SD0_DATA1/EGPIO98

S0

S0

SD0_DATA2/EGPIO99

S0S5S0

SD0_DATA3/EGPIO100

S0S5S0

SD0_LED/EGPIO93

S0

S0

SCL0/I2C2_SCL/EGPIO113

S0

S0

SDA0/I2C2_SDA/EGPIO114

S0

S0

SCL1/I2C3_SCL/AGPIO19

S5

S5

SDA1/I2C3_SDA/AGPIO20

S5

S5

S5

S5

S5

S5

S5

AGPIO6/LDT_RST_L

S5

S5

AGPIO7/LDT_PWROK

S5

S5

S5

S5

S5

S5

VDDGFX_PD/AGPIO39

S5

X

S5

X

S0

S0

S0

S0

AGPIO66/SHUTDOWN_L

S0

S0

AGPIO68/SGPIO_CLK

S0

S0

AGPIO69/SGPIO_LOAD

S0

S0

AGPIO71/SGPIO_DATAOUT

S0

S0

AGPIO72/SGPIO_DATAIN

S0

S0

S0

S0

BLINK/USB_OC7_L/AGPIO1 1

S5

S0

GENINT1_L/AGPIO89

S0

S0

GENINT2_L/AGPIO90

S0

S0

FANIN0/AGPIO84

S0

S0

FANOUT0/AGPIO85

S0

S0

UART0_CTS_L/EGPIO135

S0

X

UART0_RXD/EGPIO136

S0

X

UART0_RTS_L/EGPIO137

S0

X

UART0_TXD/EGPIO138

X

S0

UART0_INTR/AGPIO139

X

S0

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

X

UART1_RXD/BT_I2S_SDI/EGPIO141

S5

UART1_RTS_L/EGPIO142

X

UART1_TXD/BT_I2S_SDO/EGPIO143

X

UART1_INTR/BT_I2S_LRCLK/AGPIO144

S0

SD0_CD/AGPIO25

AGPIO3

AGPIO4

AGPIO5

AGPIO8

AGPIO9

AGPIO40

AGPIO64

AGPIO65

SPKR/AGPIO91

BB2

BB5

BC2

BB4

AY5

BC3

BA3

BC5

BA5

BB6

BA15

AY17

AG5

AG4

AL5

AL6

AJ1

AJ3

AH1

AJ4

AK5

AD8

AG8

AW15

AU15

AT15

AU12

AT14

AR14

BC13

BA17

AN5

BB14

BA19

BC18

BB19

AY9

AW8

AV5

AV8

AW9

AV11

AU7

AT11

AR11

AP9

R483 *10K/F_4

PLT_ID2

R144 10K/F_4

PLT_ID3

R145 10K/F_4

BOARD_ID1

R492 10K/F_4

BOARD_ID2

R472 *10K/F_4

BOARD_ID3

R528 10K/F_4

BOARD_ID4

R463 10K/F_4

VBIOS_ID1

R512 *10K/F_4

VBIOS_ID2

R214 *10K/F_4

FCH_3S_SMCLK

FCH_3S_SMDATA

SMB_NIC_SMCLK

SMB_NIC_SMDATA

LANLINK#

VBIOS_ID1

WOL_EN

WLAN_WAKE#

VDDGFX_PD

APU_TYPE_FCH

AGPIO46

AGPIO11

R419 *150/F_4

ACCEL_INTH

DGPU_HOLD_RST#

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

EGPIO140

PLT_ID1

PLT_ID2

PLT_ID3

SWD_IO_APU [19]

SWD_XRES_APU [19]

FPR_LOCK# [17]

HDD_HALTLED [25]

WLAN_TRANSMIT_OFF# [30]

ODD_PWR [33]

mSATA_DET [33]

WLAN_OFF [30]

SWD_CLK_APU [19]

FCH_3S_SMCLK [9,10,12,21]

FCH_3S_SMDATA [9,10,12,21]

SMB_NIC_SMCLK [25]

SMB_NIC_SMDATA [25]

AGPIO3 [6]

LANLINK# [15]

FCH_WAKE#_EC [35]

WOL_EN [47]

TP32

SPKR [14]

AGPIO11 [6]

GENINT1: HVB function

Vss:enabke; NC: disable

BT_OFF [30]

TP40

EGPIO140 [22]

Pitt 15"

BOARD REVISION

DB0

DB1

DB2

SI1

SI

B

SI2

PV1

MV1

+3V_DEEP_SUS

R201 *2.2K_4

R215 *1K/F_4

R517 *2.2K_4

PLT_ID1 PLT_ID2 PLT_ID3

1 00

RD_ID1 BRD_ID2 BRD_ID3 BRD_ID4

B

EG

PIO135 EGPIO136 EGPIO137 EGPIO138

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 10 1

1 1 0 0

+3V

+3V

R288

10K/F_4

3

2

+3V

2N7002K

Q33

1

APU_TEST0

APU_TEST1

APU_TEST2

111 0

LANLINK#

WOL_EN

AGPIO46

DGPU_HOLD_RST#

R289

*10K/F_4

R449 10K/F_4

R448 *100K/F_4

R182 15K/F_4

R200 15K/F_4

R507 15K/F_4

1

EGPIO143EGPIO142EGPIO141

111 0

1111

R226 10K/F_4

R202 10K/F_4

R389 10K/F_4

R290 *10K/F_4

R291 *10K/F_4

ACCEL_INTH# [21]

05

Default

+3V_DEEP_SUS

+3V

DGPU_PWR_EN

Follow AMD checklist 53537_1_03 suggestion to stuff R118/R120/R122

TEST2 TEST1 TEST0 Description

0

0 0

0

0

0

1

1

TMS

1 TMS

FCH TAP accessible from APU when TAPEN is asserted

FCH JTAG pins are overloaded for multiple

functions, in this configuration the FCH JTAG are

used as non-JTAG pins

1

Reserved

X

Reserved

FCH JTAG multi-function pins are configured as

0

JTAG pins, in this configuration the FCH TAP

can be accessed from FCH JTAG pins

Use on ATE only

Yuba JTAG enabled

1

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BR/ST 4/7 (GPIO/AZ/UARTH)

BR/ST 4/7 (GPIO/AZ/UARTH)

NB5

NB5

5

4

3

2

NB5

BR/ST 4/7 (GPIO/AZ/UARTH)

Date: Sheet of

Tuesday, March 01, 2016 5 53

Date: Sheet of

Tuesday, March 01, 2016 5 53

Date: Sheet of

Tuesday, March 01, 2016 5 53

1

1A

1A

1A

Page 6

5

4

3

2

1

+3V

R399 *10K/F_4

R398 10K/F_4

R480 *10K/F_4

D D

R500 10K/F_4

SI, 0221, change xtal cap to 5.6pF

C268 5.6p/50V_4

C265 5.6p/50V_4

C C

+3V

R458

R426 10K/F_4

R351 *10K/F_4

R460 *150/F_4

LED_3S_SATA#[25]

1

2

48MHZ +-10PPM

4

3

4.7K_4

DEVSLP0

CAMERA_ON

SPI_TPM_CS#

EGPIO119

Y1

PCI_3S_CLKRUN#

SB_SATA_LED#

PCI_3S_SERIRQ

PCI_3S_CLKRUN#

U22

*MC74VHC1G08DFT2G

4

R219

1M/F_4

+3V

3 5

R417 0_4

48M_X1

48M_X2

CLK_R3S_KBC[30,35]

CLK_R3S_DEBUG[34]

C203

*0.1U/16V/X7R_4

2

1

SPI_TPM_CS#[26]

CLK_PCIE_LANP[15]

CLK_PCIE_LANN[15]

CLK_PCIE_CARDP[16]

CLK_PCIE_CARDN[16]

SPI_CS0#[27]

SPI_CLK[27]

SPI_SO[27]

SPI_SI[27]

SPI_WP[27]

HDD

ODD

+0.95V

Integrated Clock Mode:

Leave unconnected.

CLK_WLAN_P[30]

CLK_WLAN_N[30]

C360 *10P/50V_4

C410 *10P/50V_4

0_4P2R_4

33_4P2R_4

SI, 0221, RP2/RP3 change to 33ohm on BR, 0ohm on ST

33_4P2R_4

R432 BLM15BB470SN1D(47,300MA)

SPI_CS0#

SPI_CLK

SPI_SO

SPI_SI

SPI_TPM_CS#

SPI_WP

SATA_TXP0[33]

SATA_TXN0[33]

SATA_RXN0[33]

SATA_RXP0[33]

SATA_TXP1[33]

SATA_TXN1[33]

SATA_RXN1[33]

SATA_RXP1[33]

DEVSLP0[33]

CAMERA_ON[11]

2

RP4

4

2

RP3

4

2

RP2

4

R440 56_4

LFRAME#[30,34,35]

PCI_3S_SERIRQ[34,35]

PCI_3S_CLKRUN#[35]

C252

*15P/50V_4

R204 1K/F_4

R191 1K/F_4

1

3

1

3

1

3

TP36

TP35

LAD0[30,34,35]

LAD1[30,34,35]

LAD2[30,34,35]

LAD3[30,34,35]

TP33

R168

TP30

TP38

TP60

TP39

TP7

TP34

TP58

TP62

TP63

CLK_PCIE_LANP_R

CLK_PCIE_LANN_R

CLK_PCIE_WLAN_R

CLK_PCIE_WLAN#_R

CLK_PCIE_CARDP_R

CLK_PCIE_CARDN_R

PCI_3S_SERIRQ

10K/F_4

SATA_CALRN

SATA_CALRP

DEVSLP0

CAMERA_ON

SB_SATA_LED#

48M_X1

48M_X2

LPC_CLK0

LPC_CLK1

LFRAME#

LDRQ#0

LPC_PD#

SPI_CLK

SPI_CS0#

EGPIO119

SPI_SI

SPI_SO

SPI_WP

SPI_HOLD#

SPI_TPM_CS#

AU3

SATA_TX0P

AU4

SATA_TX0N

AV1

SATA_RX0N

AV2

SATA_RX0P

AY2

SATA_TX1P

AY1

SATA_TX1N

AW4

SATA_RX1N

AW3

SATA_RX1P

AW1

SATA_ZVSS

AW2

SATA_ZVDDP

AT17

DEVSLP[0]/EGPIO67

AT12

DEVSLP[1]/EGPIO70

BB15

SATA_ACT_L/AGPIO13 0

AU2

SATA_X1

AU1

SATA_X2

U4

GFX_CLKP

U3

GFX_CLKN

U1

GPP_CLK0P

U2

GPP_CLK0N

W4

GPP_CLK1P

W3

GPP_CLK1N

W1

GPP_CLK2P

W2

GPP_CLK2N

Y2

GPP_CLK3P

Y1

GPP_CLK3N

BC10

X25M_48M_OSC

T2

X48M_X1

T1

X48M_X2

AW14

LPCCLK0/EGPIO74

AY13

LPCCLK1/EGPIO75

BB11

LAD0

BA11

LAD1

AY11

LAD2

BA13

LAD3

AV14

LFRAME_L

BA1

ESPI_ALERT_L/LDRQ0 _L

BC14

SERIRQ/AGPIO87

BC11

LPC_CLKRUN_L/AGPIO88

AE9

LPC_PD_L/AGPIO21

BC6

SPI_CLK/ESPI_CLK/EG PIO117

BB8

SPI_CS1_L/EGPIO11 8

AW7

SPI_CS2_L/ESPI_CS _L/EGPIO119

BA9

SPI_DI/ESPI_DATA /EGPIO120

AY7

SPI_DO/EGPIO121

AW11

SPI_WP_L/EGPIO1 22

BA7

SPI_HOLD_L/EGPIO133

AW12

SPI_TPM_CS_L/AGPIO76

U21E

CLK/SATA/USB/SPI/LPC

FP4 REV 1.0

*FP4

USBCLK/25M_48M_OSC

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

USB_SS_3TXP

USB_SS_3TXN

USB_SS_3RXP

USB_SS_3RXN

AP8

AP5

AR2

AR1

AR3

AR4

AN2

AN1

AN3

AN4

AM1

AM2

AL2

AL1

AL3

AL4

AK2

AJ2

AD2

AD1

AA3

AA4

W9

W8

AA2

AA1

W5

W6

AC1

AC2

Y6

Y7

AC4

AC3

AB5

AB6

USB_ZVSS

USBSS_CALRN

USBSS_CALRP

R203 11.8K/F_4

USBP0+ [11]

USBP0- [11]

USBP1+ [15]

USBP1- [15]

USBP2+ [15]

USBP2- [15]

USBP3+ [30]

USBP3- [30]

USBP4+ [17]

USBP4- [17]

USBP5+ [20]

USBP5- [20]

USBP6+ [20]

USBP6- [20]

USBP7+ [18]

USBP7- [18]

R1881K/F_4

R1981K/F_4

USB30_TX1+ [20]

USB30_TX1- [20]

USB30_RX1+ [20]

USB30_RX1- [20]

USB30_TX2+ [20]

USB30_TX2- [20]

USB30_RX2+ [20]

USB30_RX2- [20]

USB30_TX3+ [18]

USB30_TX3- [18]

USB30_RX3+ [18]

USB30_RX3- [18]

Camera USB

DB right side USB2.0 port

DB right side USB2.0 port

WLAN Min-Card / BT

Finger Printer

left side USB Type-C

le

ft side USB Type-C

left side USB Combo 3.0/2.0.

+0.95V_DEEP_SUS

R205 0_4

R206 *0_4

Support S3~S5 wake up

+0.95V

No support S3~S5 wake up

Left side USB Type-C

Left side USB Type-C

Left side USB Combo 3.0/2.0.

+3V_DEEP_SUS +3V_DEEP_SUS +3V_DEEP_SUS+3V_DEEP_SUS+3V +3V +3V

06

STRAPS PINS

AGPIO11

1

R531

10K/F_4

R519

*2K/F_4

normal reset mode

short reset modeLDT_RST#/LDT_PWRGD

SYS_RST#

DEFAULT

1A

1A

1A

R420

B B

A A

5

4

OVERLAP COMMON PADS WHERE

POSSIBLE FOR DUAL-OP RESISTORS.

AGPIO3[5]

RTC_CLK[5,36]

AGPIO11[5]

SYS_RST#[5]

Type1/3: stuff R229

Type2: stuff R228

REQUIRED STRAPS

LPC_CLK0 BLINK

BOOT FAIL TIMER

PULL

ENABLED

HIGH

BOOT FAIL TIMER

PULL

DISABLED

LOW

3

DEFAULT

LPC_CLK0

LPC_CLK1

LFRAME#

LPC_CLK1

Use 48Mhz crystal clock

and generate both internal

and external clocks

DEFAULT

Use 100Mhz PCIE clock as

reference clock and generate

internal clocks only

Follow FAE comment: R659 change to 2K, R401 to 10k, R142 is NC

LFRAME#

SPI ROM

DEFAULT

LPC ROM

2

*10K/F_4

R421

2K/F_4

1.8V SPI ROM

3.3V SPI ROM

DEFAULT

R436

10K/F_4

R437

*2K/F_4

AGPIO3

Int Pull-Up

Type2 Type1/3

R229

R439

10K/F_4

10K/F_4

R438

R228

*2K/F_4

*2K/F_4

RTC_CLK

Int Pull-Up Int Pull-Up Int Pull-Up

NB5

NB5

NB5

Coin battery is

on board.

Coin battery is

not on board.

Enhanced reset logic

(for quicker S5 resume)

DEFAULT DEFAULT DEFAULT

Default to

traditional reset logic

R194

R121

*10K/F_4

10K/F_4

R213

R120

*2K/F_4

*2K/F_4

LDT_RST#/LDT_PWRGD

output to APU

output to Pads

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BR/ST 5/7 (SATA/USB/SPI)

BR/ST 5/7 (SATA/USB/SPI)

BR/ST 5/7 (SATA/USB/SPI)

Date: Sheet of

Tuesday, March 01, 2016 6 53

Date: Sheet of

Tuesday, March 01, 2016 6 53

Date: Sheet of

Tuesday, March 01, 2016 6 53

Page 7

5

4

3

2

1

07

U8

W7

W12

W15

W18

W21

Y8

Y10

Y13

Y16

Y19

Y22

AB7

AB9

AB12

AB15

AB18

AB21

AD6

AD10

AD13

AD16

AD19

AD22

AE7

AE12

AK9

AG10

AK10

AG13

AK13

AG16

AK16

AG19

AK19

AG22

AK22

AH7

AE18

AE21

AH21

AG6

AH12

AN6

AH15

AH18

AL7

AK6

AE15

L8

L13

L16

L19

L22

N7

N12

N15

N18

N21

P8

P13

P16

P19

P22

T7

F12

F15

G11

G14

J8

J9

J11

K7

K12

K13

K15

K16

T12

T15

T18

T21

U13

U16

U19

U22

K19

+1.5V_RTC

+VCC_CORE

C205

C197

22U/6.3V_6

C236

0.22U/10V_4

C229

22U/6.3V_6

C199

0.22U/10V_4

C170

22U/6.3V_6

C212

0.22U/10V_4

22U/6.3V_6

C177

0.22U/10V_4

C168

22U/6.3V_6

C214

0.22U/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

+0.95V

+APU_VDDGFX

C230

BR@22U/6.3V_6

C237

BR@0.22U/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

C180

C179

10U/6.3VS_6

10U/6.3VS_6

C193

C191

0.22U/10V_4

0.22U/10V_4

C189

BR@22U/6.3V_6

C163

BR@0.22U/10V_4

C209

C155

BR@22U/6.3V_6

BR@22U/6.3V_6

C210

C219

BR@0.22U/10V_4

BR@0.22U/10V_4

C164

10U/6.3V_6

C185

0.22U/10V_4

C228

C154

BOTTOM SIDE DECOUPLING UNDER APU

Type1: All +APU_VDDGFX_RUN cap Stuff.

Type2,3: All +APU_VDDGFX_RUN cap No Stuff.

+VCCRTC_2

+3VPCU

D14

BAT54CW

12

CN20

BAT_CONN

DFHS02FS058

BAT-23_2-4_2

+BAT

R277 470/F_4

BR@22U/6.3V_6

BR@0.22U/10V_4

C217

22U/6.3V_6

C208

0.22U/10V_4

C194

10U/6.3V_6

C178

0.22U/10V_4

C231

BR@22U/6.3V_6

C190

BR@0.22U/10V_4

+3VRTC

C325

0.1U/16V/X7R_4

C200

22U/6.3V_6

C196

0.22U/10V_4

C172

0.22U/10V_4

C158

BR@22U/6.3V_6

C159

BR@0.22U/10V_4

20MIL

+3VRTC

C328

1U/10V_4

12

C165

22U/6.3V_6

C195

0.22U/10V_4

C166

0.22U/10V_4

C227

BR@22U/6.3V_6

C202

BR@0.22U/10V_4

U14

3

VIN

IC AP2138N-1.5TRG1

GND

VOUT

C169

22U/6.3V_6

C218

180P/50V_4

C192

180P/50V_4

C171

BR@22U/6.3V_6

C221

BR@0.22U/10V_4

2

1

C238

BR@180P/50V_4

+1.5V_RTC

C333

10U/6.3V_6

+1.2VSUS

3A

P25

VDDIO_MEM_S3_1

P28

VDDIO_MEM_S3_2

T24

VDDIO_MEM_S3_3

T27

VDDIO_MEM_S3_4

U25

C81

22U/6.3V_6

C114

22U/6.3V_6

C119

22U/6.3V_6

C147

D D

22U/6.3V_6

C120

22U/6.3V_6

C117

22U/6.3V_6

C135

22U/6.3V_6

C134

22U/6.3V_6

C118

22U/6.3V_6

SI, 0227, stuff C118/C115/C116 for memory margin

C483

+

*220U/6.3V/ESR35_3528

SI, 0227, reserve 3528 cap for memory margin

RA, CA, CB

Type1 PX: Stuff

UMA: Stuff

Type2 PX: Stuff

UMA: No Stuff

Type3: No Stuff

+0.95V +VDDP_GFX

C C

R193 BR@0_6

RA

C253

BR@10U/6.3VS_6

+VDDCR_FCH_S5 +VDDCR_FCH_S5_R

R165 0_4

C215

0.22U/10V_4

C160

0.22U/10V_4

C132

0.22U/10V_4

C235

BR@0.22U/10V_4

C233

10U/6.3VS_6

C186

0.22U/10V_4

C125

0.22U/10V_4

C133

0.22U/10V_4

C129

0.22U/10V_4

C167

0.22U/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

C124

C127

0.22U/10V_4

0.22U/10V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

ACROSS VDDNB AND VSS SPLIT

C148

0.22U/10V_4

C126

0.22U/10V_4

+VDDP_GFX

RB

R167

only pop on

*0_4

Type2 UMA SKU.

RBCA CB

+VDDCR_FCH_S5_R

C234

10U/6.3VS_6

C152

0.22U/10V_4

C207

0.22U/10V_4

C226

0.22U/10V_4

C161

22U/6.3V_6

C223

22U/6.3V_6

ACROSS VDDNB AND VSS SPLIT

B B

C198

0.22U/10V_4

C146

0.22U/10V_4

C188

0.22U/10V_4

C213

0.22U/10V_4

C211

0.22U/10V_4

C173

0.22U/10V_4

C144

0.22U/10V_4

C115

22U/6.3V_6

C128

0.22U/10V_4

C153

180P/50V_4

+APU_VDDIO_AZ

+VDDP_GFX

+APU_VDD_33

+APU_VDD_18_S5

+APU_VDD_33_S5

+VDDP_S5

+VDDNB_CORE

C222

22U/6.3V_6

C201

0.22U/10V_4

+1.8V

+0.95V

C116

22U/6.3V_6

C130

180P/50V_4

C131

180P/50V_4

C239

22U/6.3V_6

C174

180P/50V_4

AB24

AB27

AB30

AB33

AD25

AD28

AD30

AE24

AE27

AF30

AF33

AG25

AG28

AH24

AH27

AH30

AK25

AK28

AK30

AK33

AL27

AM30

AR19

AP19

AP21

AP16

AP18

AP10

AP15

AR15

AN12

AP12

AP13

AR12

AW19

AU17

AU19

AV17

AV19

AW17

AL12

AL13

AL15

AL18

AL21

AN13

AN16

AN19

AN22

AR17

U28

V30

V33

W24

W27

Y25

Y28

Y30

AE6

AE5

AR9

VDDIO_MEM_S3_5

VDDIO_MEM_S3_6

VDDIO_MEM_S3_7

VDDIO_MEM_S3_8

VDDIO_MEM_S3_9

VDDIO_MEM_S3_10

VDDIO_MEM_S3_11

VDDIO_MEM_S3_12

VDDIO_MEM_S3_13

VDDIO_MEM_S3_14

VDDIO_MEM_S3_15

VDDIO_MEM_S3_16

VDDIO_MEM_S3_17

VDDIO_MEM_S3_18

VDDIO_MEM_S3_19

VDDIO_MEM_S3_20

VDDIO_MEM_S3_21

VDDIO_MEM_S3_22

VDDIO_MEM_S3_23

VDDIO_MEM_S3_24

VDDIO_MEM_S3_25

VDDIO_MEM_S3_26

VDDIO_MEM_S3_27

VDDIO_MEM_S3_28

VDDIO_MEM_S3_29

VDDIO_MEM_S3_30

VDDIO_MEM_S3_31

VDDIO_MEM_S3_32

VDDIO_MEM_S3_33

VDDIO_MEM_S3_34

VDDIO_MEM_S3_35

0.2A

VDDIO_AUDIO

1.5A

VDDP_GFX_2

VDDP_GFX_1

0.2A

VDD_33_1

VDD_33_2

1.5A

VDD_18_1

VDD_18_2

0.5A

VDD_18_S5_1

VDD_18_S5_2

0.2A

VDD_33_S5_1

VDD_33_S5_2

0.8A

VDDP_S5_1

VDDP_S5_2

0.2A

VDDCR_FCH_S5_1

VDDCR_FCH_S5_2

7A

VDDP_6

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

12A

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDBT_RTC_G

BOTTOM SIDE DECOUPLING UNDER APU

20MIL

VDDBT_RTC

12

R180 0_4

C142

0.22U/10V_4

C250

10U/6.3VS_6

G1

*SHORT_ PAD1

+1.5V

+APU_VDDIO_AZ

+1.8V

+1.8V_DEEP_SUS +APU_VDD_18_S5

R107 0_4

1.5V For HDA Only

A A

C151

1U/10V_4

C150

1U/10V_4

C145

1U/10V_4

C220

10U/6.3VS_6

C204

0.22U/10V_4

12

C149

1U/10V_4

U21F

POWER

FP4 REV 1.0

*FP4

R284 1K/F_4

C241

0.22U/10V_4

22~39A

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

VDDCR_CPU_16

VDDCR_CPU_17

VDDCR_CPU_18

VDDCR_CPU_19

VDDCR_CPU_20

VDDCR_CPU_21

VDDCR_CPU_22

VDDCR_CPU_23

VDDCR_CPU_24

VDDCR_CPU_25

VDDCR_CPU_26

VDDCR_CPU_42

VDDCR_CPU_31

VDDCR_CPU_43

VDDCR_CPU_32

VDDCR_CPU_44

VDDCR_CPU_33

VDDCR_CPU_45

VDDCR_CPU_34

VDDCR_CPU_46

VDDCR_CPU_35

VDDCR_CPU_47

VDDCR_CPU_36

VDDCR_CPU_28

VDDCR_CPU_29

VDDCR_CPU_40

VDDCR_CPU_30

VDDCR_CPU_37

VDDCR_CPU_49

VDDCR_CPU_38

VDDCR_CPU_39

VDDCR_CPU_48

VDDCR_CPU_41

VDDCR_CPU_27

22~30A

VDDCR_GFX_14

VDDCR_GFX_15

VDDCR_GFX_16

VDDCR_GFX_17

VDDCR_GFX_18

VDDCR_GFX_19

VDDCR_GFX_20

VDDCR_GFX_21

VDDCR_GFX_22

VDDCR_GFX_23

VDDCR_GFX_24

VDDCR_GFX_25

VDDCR_GFX_26

VDDCR_GFX_27

VDDCR_GFX_28

VDDCR_GFX_29

VDDCR_GFX_1

VDDCR_GFX_2

VDDCR_GFX_3

VDDCR_GFX_4

VDDCR_GFX_5

VDDCR_GFX_6

VDDCR_GFX_7

VDDCR_GFX_8

VDDCR_GFX_9

VDDCR_GFX_10

VDDCR_GFX_11

VDDCR_GFX_12

VDDCR_GFX_30

VDDCR_GFX_31

VDDCR_GFX_32

VDDCR_GFX_33

VDDCR_GFX_34

VDDCR_GFX_35

VDDCR_GFX_36

VDDCR_GFX_37

VDDCR_GFX_13

+3V +APU_VDD_33

R109 0_4

C143

10U/6.3VS_6

5

+3V_DEEP_SUS +APU_VDD_33_S5 +0.95V_DEEP_SUS +VDDP_S5

R171 0_4

4

C224

10U/6.3VS_6

C225

0.22U/10V_4

R175 0_6

C245

10U/6.3VS_6

C243

0.22U/10V_4

3

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BR/ST 6/7 (POWER)

BR/ST 6/7 (POWER)

NB5

NB5

2

NB5

BR/ST 6/7 (POWER)

Date: Sheet of

Tuesday, March 01, 2016 7 53

Date: Sheet of

Tuesday, March 01, 2016 7 53

Date: Sheet of

Tuesday, March 01, 2016 7 53

1

1A

1A

1A

Page 8

5

4

3

2

1

08

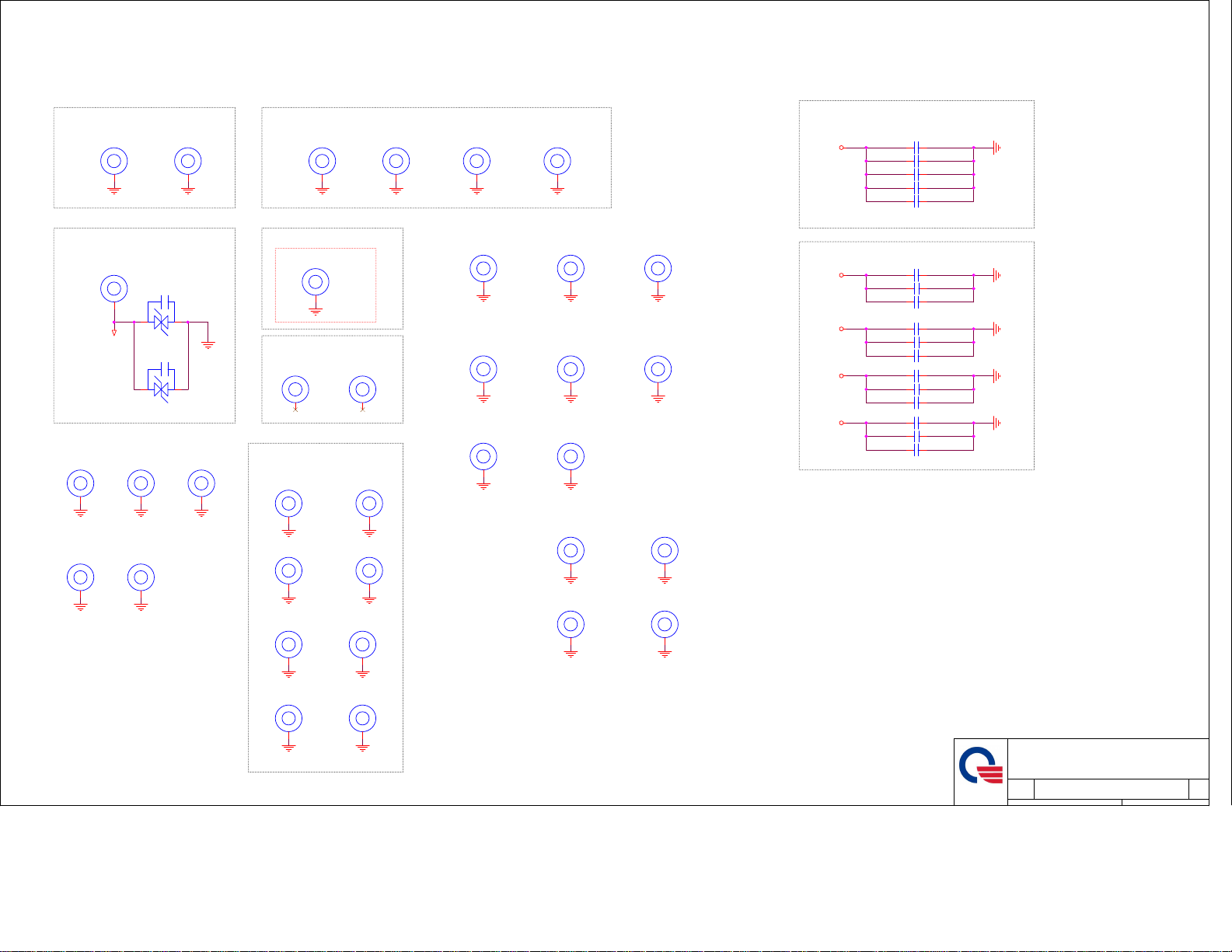

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

U21G

GND

FP4 REV 1.0

*FP4

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

L28

M4

M30

N10

N13

N16

N19

N22

N27

P1

P2

P4

P5

P12

P15

P18

P21

P30

P33

T4

T10

T13

T16

T19

T22

T30

U5

U12

U15

U18

U21

U24

V1

V2

V4

W10

W13

W16

W19

W22

Y4

Y5

Y12

Y15

Y18

Y21

Y24

AB1

AB2

AB4

AB10

AB13

AB16

AB19

AB22

AD4

AD9

AD12

AD15

AD18

AD21

AD24

AE10

AE13

AE16

AE19

AE22

AF1

AF4

AG9

AG12

AG15

AG18

AG21

AH4

AH10

AH13

AH16

AH19

AH22

AK1

AK4

AK12

AK15

AK18

AL16

AL19

AL22

AM4

AN9

AN10

AN15

AN18

AN21

AN25

AN28

AP1

AP2

AP4

AP7

AP22

AP27

AP30

AP33

AR6

AR25

AR28

AT4

AT19

AT22

AT30

AU5

AU8

AU11

AU14

AU20

AU23

AU27

AV4

AV7

AV9

AV12

AV15

AV25

D D

A8

ORIENT_APU#

TP47

C C

B B

A12

A16

A20

A24

A28

A32

B12

B33

D10

D12

D14

D16

D18

D20

D22

D24

D26

D28

D30

F19

F22

F25

F30

F33

G17

G20

G23

G26

H30

J15

J19

J22

J25

J28

K10

K22

K27

K30

K33

L12

L15

L18

L21

L25

B2

B8

C3

D4

D6

D8

F1

F2

F4

F9

G7

H4

J5

K1

K2

K4

L5

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

U21H

GND

FP4 REV 1.0

*FP4

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_215

VSS_214

AV30

AV33

AW22

AY4

AY6

AY8

AY10

AY12

AY14

AY16

AY20

AY22

AY24

AY26

AY28

AY30

BB1

BB33

BC4

BC8

BC12

BC16

BC20

BC24

BC28

BC32

L24

AL10

AK21

TP10

TP9

TP42

APU_U30

APU_U31

APU_AN30

U30

U31

AN30

RSVD_2

RSVD_3

RSVD_4

U21J

FP4 REV 1.0

*FP4

A A

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BR/ST 7/7 (GND)

BR/ST 7/7 (GND)

NB5

NB5

5

4

3

2

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

BR/ST 7/7 (GND)

Tuesday, March 01, 2016 8 53

Tuesday, March 01, 2016 8 53

Tuesday, March 01, 2016 8 53

1

1A

1A

1A

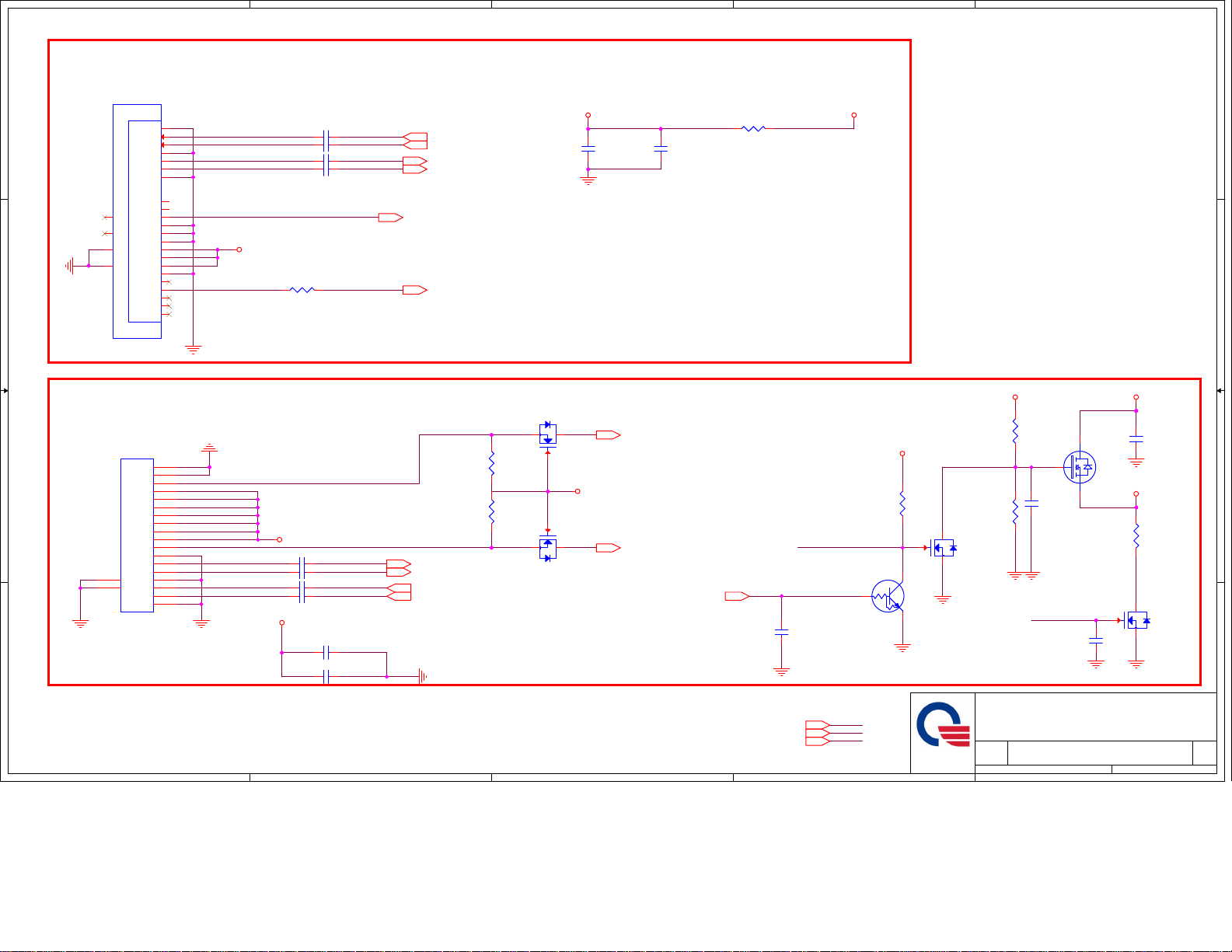

Page 9

5

M_B_A[13:0][3,10]

D D

M_B_WE#[3,10]

M_B_CAS#[3,10]

M_B_RAS#[3,10]

M_B_ACT#[3,10]

R27 1K/F_4

+1.2VSUS

M_B_EVENT#[3,10]

M_B_RST#[3,10]

C C

B B

SI, 0227, remove data group8 whitch is ECC function

+1.2VSUS

C47 *0.1U/10V_4

M_B_BS#0[3,10]

M_B_BS#1[3,10]

M_B_BG#0[3,10]

M_B_BG#1[3,10]

M_B_CS#0[3]

M_B_CS#1[3]

M_B_CKE0[3,10]

M_B_CKE1[3,10]

M_B_CLKP0[3]

M_B_CLKN0[3]

M_B_CLKP1[3]

M_B_CLKN1[3]

M_B_ODT0[3]

M_B_ODT1[3]

FCH_3S_SMCLK[5,10,12,21]

FCH_3S_SMDATA[5,10,12,21]

M_B_DM[7..0][3,10]

+3V

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

R58 0_4

R28 1K/F_4

R38 4.7K_4

TP4

TP5

TP6

M_B_ODT0

M_B_ODT1

CHB_SA0

CHB_SA1

CHB_SA2

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

144

133

132

131

128

126

127

122

125

121

146

120

119

158

151

156

152

162

165

114

143

116

134

108

150

145

115

113

149

157

109

110

137

139

138

140

155

161

253

254

256

260

166

92

91

101

105

88

87

100

104

12

33

54

75

178

199

220

241

96

JDIM2A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14/WE#

A15/CAS#

A16/RAS#

S2#/C0

S3#/C1

ACT#

PARITY

ALERT#

EVENT#

RESET#

BA0

BA1

BG0

BG1

S0#

S1#

CKE0

CKE1

CK0

CK0#

CK1

CK1#

ODT0

ODT1

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

4

8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

(260P)

DDR4 SODIMM 260 PIN

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DQS#8

M_B_DQ4

7

M_B_DQ0

20

M_B_DQ7

21

M_B_DQ3

4

M_B_DQ1

3

M_B_DQ5

16

M_B_DQ2

17

M_B_DQ6

28

M_B_DQ9

29

M_B_DQ12

41

M_B_DQ10

42

M_B_DQ14

24

M_B_DQ8

25

M_B_DQ13

38

M_B_DQ15

37

M_B_DQ11

50

M_B_DQ17

49

M_B_DQ21

62

M_B_DQ22

63

M_B_DQ18

46

M_B_DQ20

45

M_B_DQ16

58

M_B_DQ23

59

M_B_DQ19

70

M_B_DQ28

71

M_B_DQ24

83

M_B_DQ31

84

M_B_DQ27

66

M_B_DQ25

67

M_B_DQ29

79

M_B_DQ26

80

M_B_DQ30

174

M_B_DQ37

173

M_B_DQ33

187

M_B_DQ38

186

M_B_DQ35

170

M_B_DQ32

169

M_B_DQ36

183

M_B_DQ34

182

M_B_DQ39

195

M_B_DQ40

194

M_B_DQ43

207

M_B_DQ41

208

M_B_DQ47

191

M_B_DQ45

190

M_B_DQ44

203

M_B_DQ42

204

M_B_DQ46

216

M_B_DQ53

215

M_B_DQ52

228

M_B_DQ55

229

M_B_DQ50

211

M_B_DQ49

212

M_B_DQ48

224

M_B_DQ54

225

M_B_DQ51

237

M_B_DQ56

236

M_B_DQ60

249

M_B_DQ59

250

M_B_DQ63

232

M_B_DQ57

233

M_B_DQ61

245

M_B_DQ62

246

M_B_DQ58

13

M_B_DQSP0

34

M_B_DQSP1

55

M_B_DQSP2

76

M_B_DQSP3

179

M_B_DQSP4

200

M_B_DQSP5

221

M_B_DQSP6

242

M_B_DQSP7

97

11

M_B_DQSN0

32

M_B_DQSN1

53

M_B_DQSN2

74

M_B_DQSN3

177

M_B_DQSN4

198

M_B_DQSN5

219

M_B_DQSN6

240

M_B_DQSN7

95

M_B_DQSP[7:0] [3,10]

M_B_DQSN[7:0] [3,10]

3

M_B_DQ[63:0] [3,10]

2.48A

+1.2VSUS

2

JDIM2B

111

VDD1

112

VDD2

117

VDD3

118

VDD4

123

VDD5

124

VDD6

129

VDD7

130

VDD8

135

VDD9

136

VDD10

141

VDD11

142

VDD12

147

VDD13

148

VDD14

153

VDD15

154

VDD16

159

VDD17

160

VDD18

163

VDD19

1

VSS1

5

VSS2

9

VSS3

15

VSS4

19

VSS5

23

VSS6

27

VSS7

31

VSS8

35

VSS9

39

VSS10

43

VSS11

47

VSS12

51

VSS13

57

VSS14

61

VSS15

65

VSS16

69

VSS17

73

VSS18

77

VSS19

81

VSS20

85

VSS21

89

93

99

103

107

167

171

175

181

185

189

193

197

201

205

209

213

217

223

227

231

235

239

243

247

251

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

DDR4 SODIMM 260 PIN

VDDSPD

VREF_CA

(260P)

VPP1

VPP2

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

GND

GND

255

257

259

258

VTT

164

2

6

10

14

18

22

26

30

36

40

44

48

52

56

60

64

68

72

78

82

86

90

94

98

102

106

168

172

176

180

184

188

192

196

202

206

210

214

218

222

226

230

234

238

244

248

252

261

262

+VREF_CA0

+3V

+2.5VSUS

DDR_VTT

+VREF_CA0

Place these Caps near JDIM2

1uF/22uF 4pcs on each side of connector

+1.2VSUS

C26 1U/6.3V_4

C45 1U/6.3V_4

C86 1U/6.3V_4

C46 1U/6.3V_4

C79 1U/6.3V_4

C78 1U/6.3V_4

C85 1U/6.3V_4

C77 1U/6.3V_4

C54 22U/6.3V_6

C53 22U/6.3V_6

C83 22U/6.3V_6

C82 22U/6.3V_6

C48 22U/6.3V_6

C80 22U/6.3V_6

C52 22U/6.3V_6

C84 22U/6.3V_6

EC21 22U/6.3V_6

EC22 68P/50V_4 C87 0.1U/16V_4_X7R

+

C484 *220U/6.3V/ESR35_3528

SI, 0227, change 10uf x8 to 22uf

and reserve 3528 cap for memory margin

+1.2VSUS_S

+

C482 *330U/2.5V_7343

1

09

DDR_VTT

C65 1U/6.3V_4

C64 1U/6.3V_4

C57 1U/6.3V_4

C41 1U/6.3V_4

C39 10U/6.3V_6

+VREF_CA0

C51 *0.1U/16V_4_X7R

C50 *2.2U/10V_6

+2.5VSUS

C90 10U/6.3V_6

C89 10U/6.3V_6

+3V

C88 2.2U/10V_6

SI, 0225, reserve 330uF for memory margin

+1.2VSUS

+VREF_CA0

R36

1K/F_4

DDR_VTTREF[40]

A A

+5VPCU[15,18,19,20,38,39,40,41,42,43,45,47,49]

+1.2VSUS[3,7,10,40]

DDR_VTT[10,40,47]

+3V[4,5,6,7,10,11,12,13,14,15,16,17,21,22,25,26,28,29,30,33,35,37,38,43,45,47,49]

5

4

3

2

R34 *0_6

NB5

NB5

NB5

+VREF_CA0

R35

1K/F_4

PROJECT : 400 SERIES

PROJECT : 400 SERIES

PROJECT : 400 SERIES

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

System Memory 1/2 (4H)

System Memory 1/2 (4H)

System Memory 1/2 (4H)

Date: Sheet of

Date: Sheet of

Date: Sheet of

C66

0.1U/16V/X7R_4

1

9 53Tuesday, March 01, 2016

9 53Tuesday, March 01, 2016

9 53Tuesday, March 01, 2016

C67

1000P/50V_4

1A

1A

1A

Page 10

5

M_B_A[13:0][3,9]

D D

M_B_WE#[3,9]

M_B_CAS#[3,9]

M_B_RAS#[3,9]

M_B_ACT#[3,9]

FCH_3S_SMCLK[5,9,12,21]

FCH_3S_SMDATA[5,9,12,21]

+1.2VSUS

M_B_DM[7..0][3,9]

M_B_BS#0[3,9]

M_B_BS#1[3,9]

M_B_BG#0[3,9]

M_B_BG#1[3,9]

M_B1_CS#0[3]

M_B1_CS#1[3]

M_B_CKE0[3,9]

M_B_CKE1[3,9]

M_B_CLKP3[3]

M_B_CLKN3[3]

M_B_CLKP2[3]

M_B_CLKN2[3]

M_B1_ODT0[3]

M_B1_ODT1[3]

+3V

+1.2VSUS

C19 *0.1U/10V_4

R19 4.7K_4

R18 4.7K_4

TP1

R8 *1K/F_4

+1.2VSUS

M_B_EVENT#[3,9]

M_B_RST#[3,9]

C C

DB0, 1026, follow DDR4 CRB

B B

SI, 0227, remove data group8 whitch is ECC function

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

TP2

TP3

R22 0_4

R9 1K/F_4

CHA_SA1

CHA_SA2

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

JDIM1A

144

A0

133

A1

132

A2

131

A3

128

A4

126

A5

127

A6

122

A7

125

A8

121

A9

146

A10/AP

120

A11

119

A12

158

A13

151

A14/WE#

156

A15/CAS#

152

A16/RAS#

162

S2#/C0

165

S3#/C1

114

ACT#

143

PARITY

116

ALERT#

134

EVENT#

108

RESET#

150

BA0

145

BA1

115

BG0

113

BG1

149

S0#

157

S1#

109

CKE0

110

CKE1

137

CK0

139

CK0#

138

CK1

140

CK1#

155

ODT0

161

ODT1

253

SCL

254

SDA

256

SA0

260

SA1

166

SA2

92

CB0

91

CB1

101

CB2

105

CB3

88

CB4

87

CB5

100

CB6

104

CB7

12

DM0

33

DM1

54

DM2

75

DM3

178

DM4

199

DM5

220

DM6

241

DM7

96

DM8

4

M_B_DQ[63:0] [3,9]

8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36