Page 1

5

4

3

2

1

01

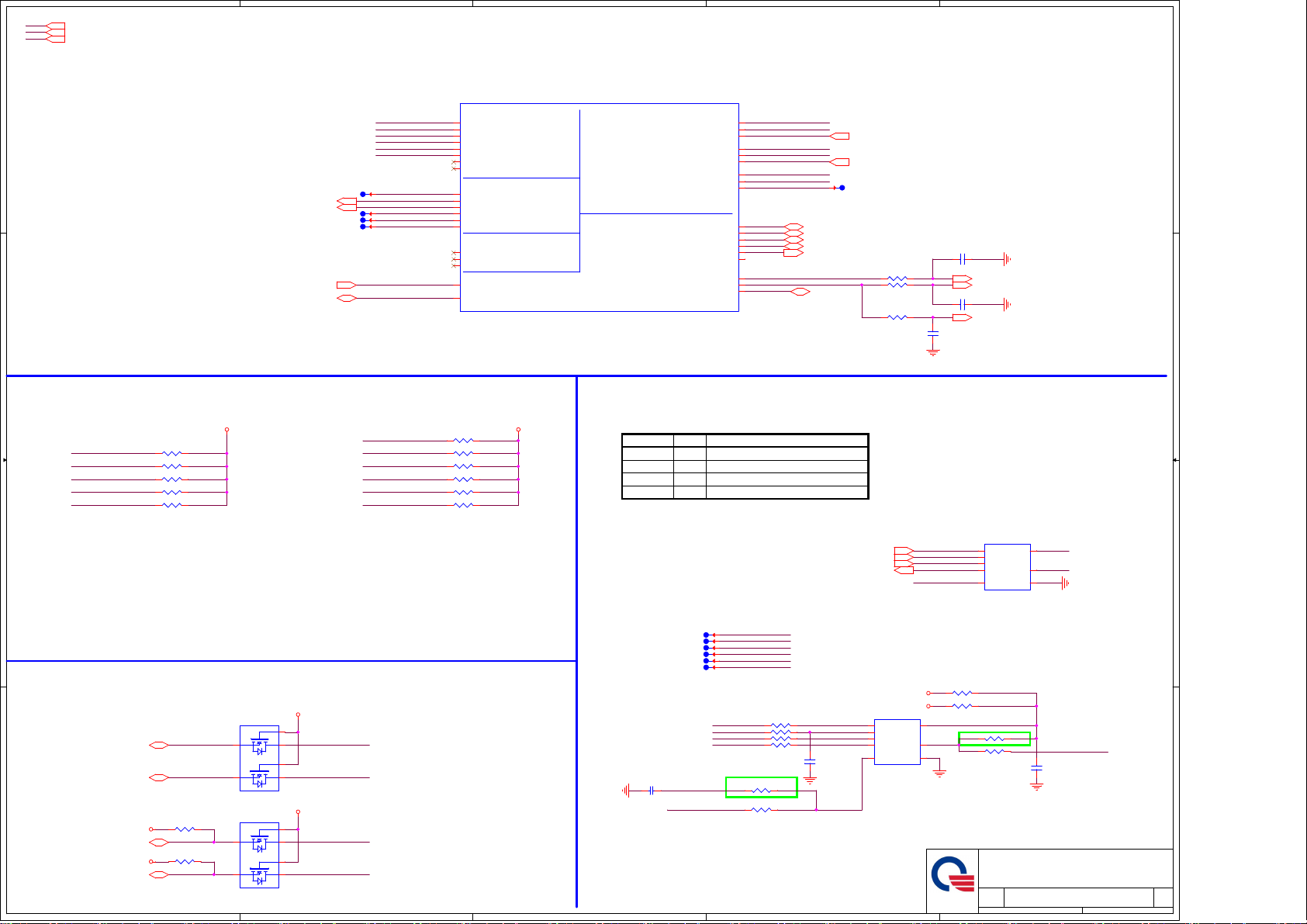

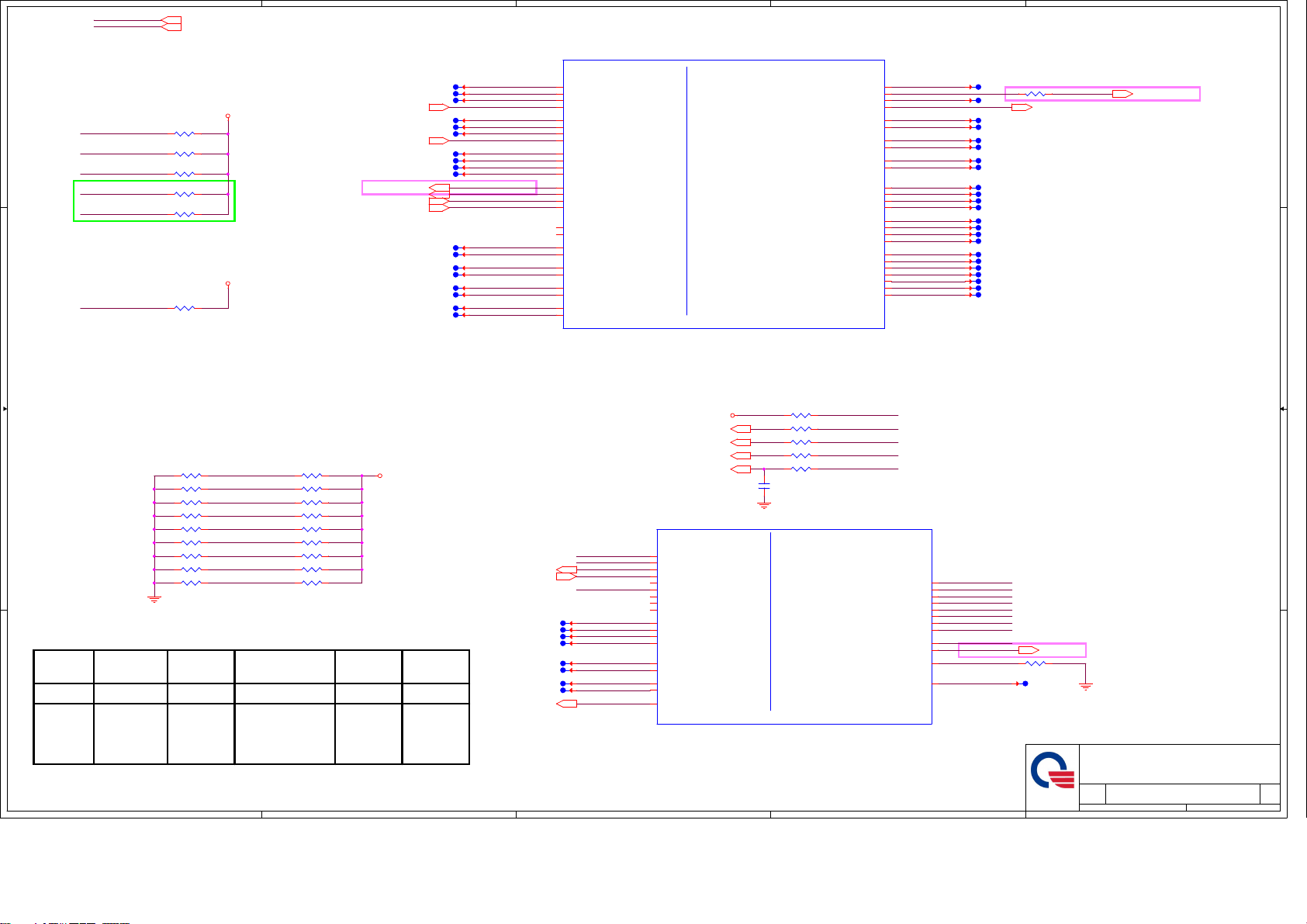

Chocolate

DIS (14" / 15" / 17")

PCB 6L STACK UP

D D

C C

System BIOS

SPI ROM

B B

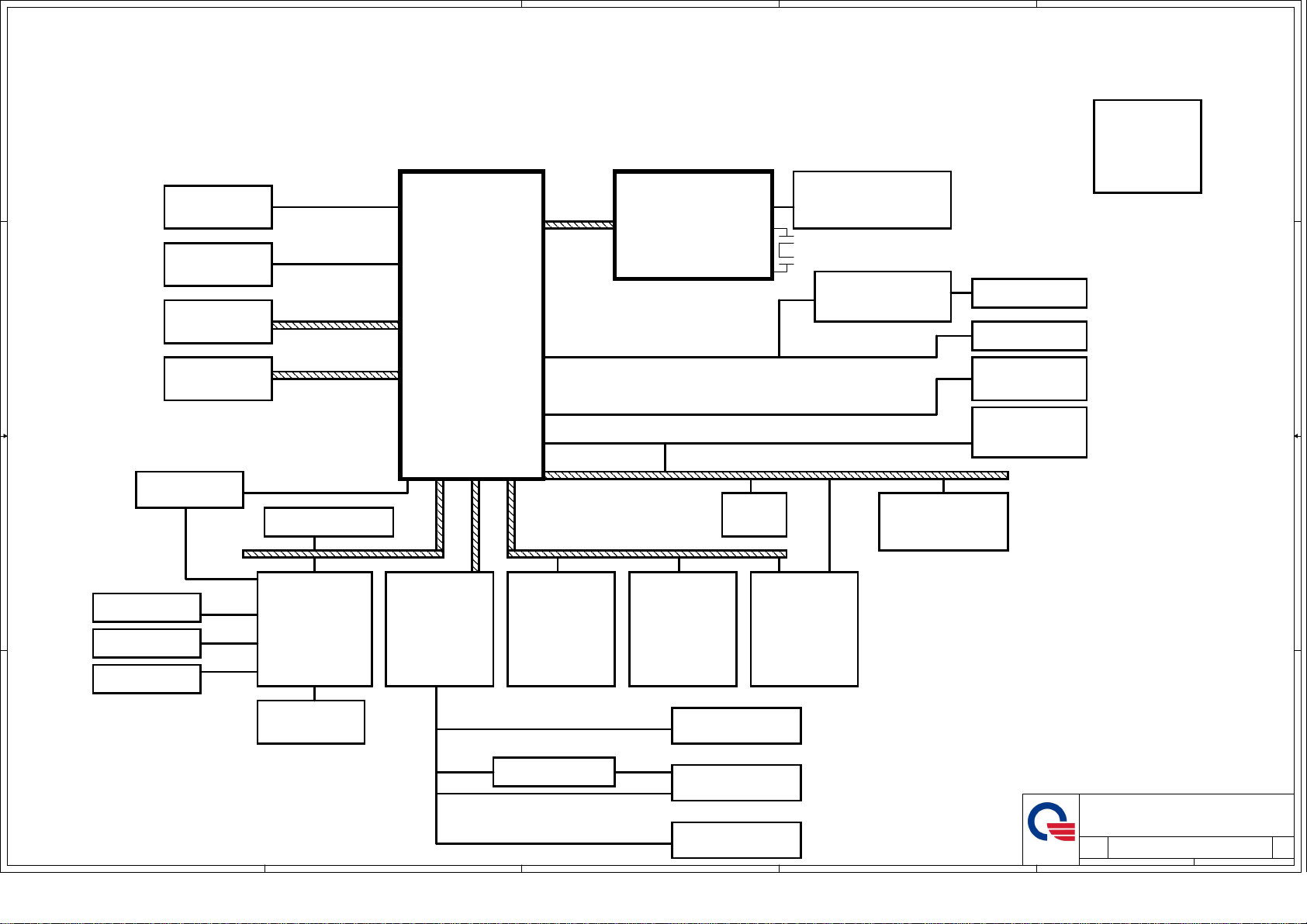

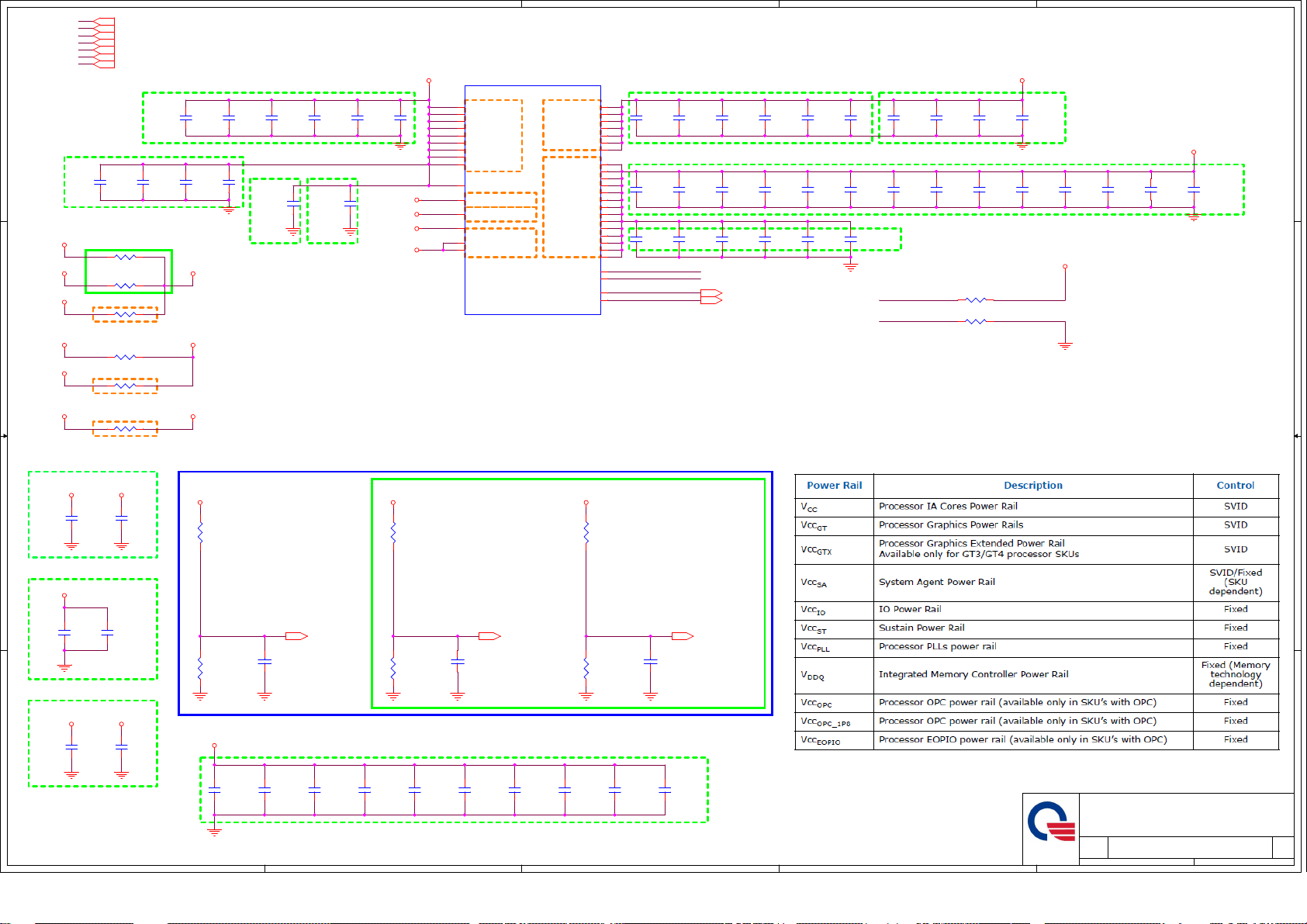

Intel SKYLAKE ULT Platform Block Diagram

DDR3L SODIMM1

Maxima 8GBs

DDR3L SODIMM2

Maxima 8GBs

SATA0 - 1st HDD

Package : 9.5 (mm)

Power :

SATA ODD

Package : 12.7 (mm)

Power :

PAGE 17

PAGE 18

PAGE 34

PAGE 34

PAGE 10

DDR3L

DDR3L

SATA0 6GB/s

SATA1 3GB/s

SPI Interface

PAGE 32TPM

SLB9665TT2.0 FW 5

LPC Interface PCIE Gen 1 x 1 Lane

SKYLAKE U

Processor

Processor : Daul Core

Power : 15 (Watt)

Package : BGA1356

Size : 40 X 24 (mm)

HP

Azalia

PAGE 2~16

PCI-E Gen3

x 4 Lane

eDP X 2

DP Port 1

USB3.0 Interface

USB2.0 Interface

AMD MESO XT

Power : 25 (Watt)

Package : S3

Size : 23 x 23 (mm)

PAGE 19~24

USB 3.0 Port 1,2,3(USB 2.0 Port 0,1,5)

Camera

Port2

PAGE 28

VRAM DDR3L x 4 (900 MHz)

256 x 16 x 4, 64 bit

Max 4GBs

RTD2136

Package : QFN-32

PAGE 18 19

PAGE 22

Touch Screen

Port7

Elan EKTH3915 for 14",15"

Elan EKTH3918 for 17"

LVDS (2CH)

eDP

HDMI Conn

USB3.0 Port x 1

Port 1

PAGE 32

PAGE 27/27

PAGE 27/27

PAGE 28

PAGE 33

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

G-Sensor

HP3DC2TR

Keyboard

Touch Pad

A A

H.P

PAGE32

PAGE 31

PAGE 31

SM BUS

Embedded Controller

iTE 8987

Power :

Package : LQPF128

Size : 14 x 14 (mm)

PAGE 35

FAN

PAGE 31

Audio Codec

ALC3241

Power :

Package : MQFN

Size : 6 x 6 (mm)

PAGE 29

Card Reader

RTS5237S-GRT

Power :

Package : LQPF48

Size : 7 x 7 (mm)

Head Phone AMP

HPA022642RTJR

DB

LAN Controller

RTL8111HSH(Giga)

RTL8107EH(10/100)

Power :

Package : OFN32

DB

Speaker

Combo Jack

Digital MIC

5

4

3

M2 Card

Intel Rambo Peak

WLAN / BT Combo

Port6

PAGE 34

PAGE 29

PAGE 29

PAGE 28

www.schematic-x.blogspot.com

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Block Diagram

Block Diagram

NB5

NB5

2

NB5

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1 49Wednesday, May 13, 2015

1 49Wednesday, May 13, 2015

1 49Wednesday, May 13, 2015

1A

1A

1A

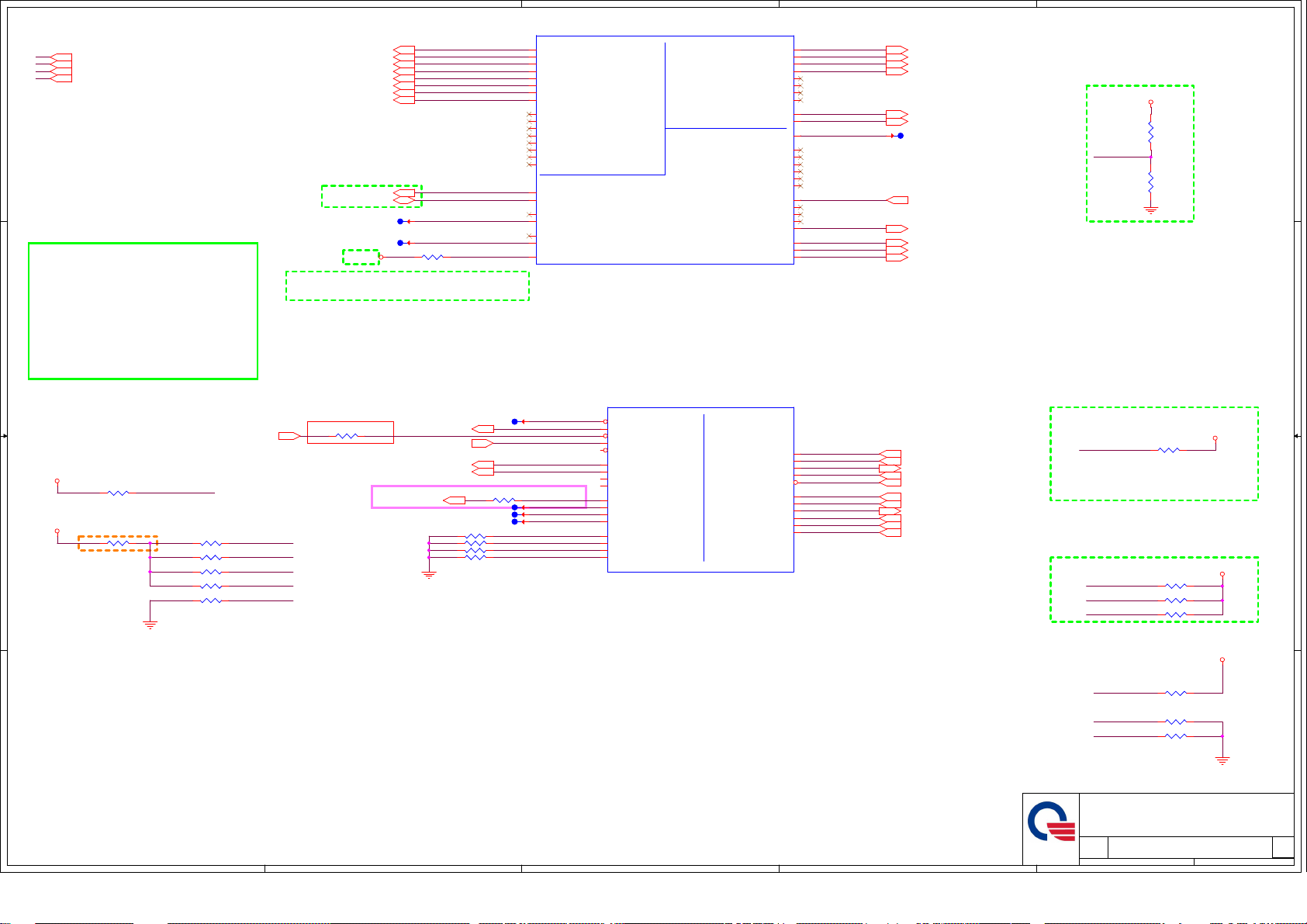

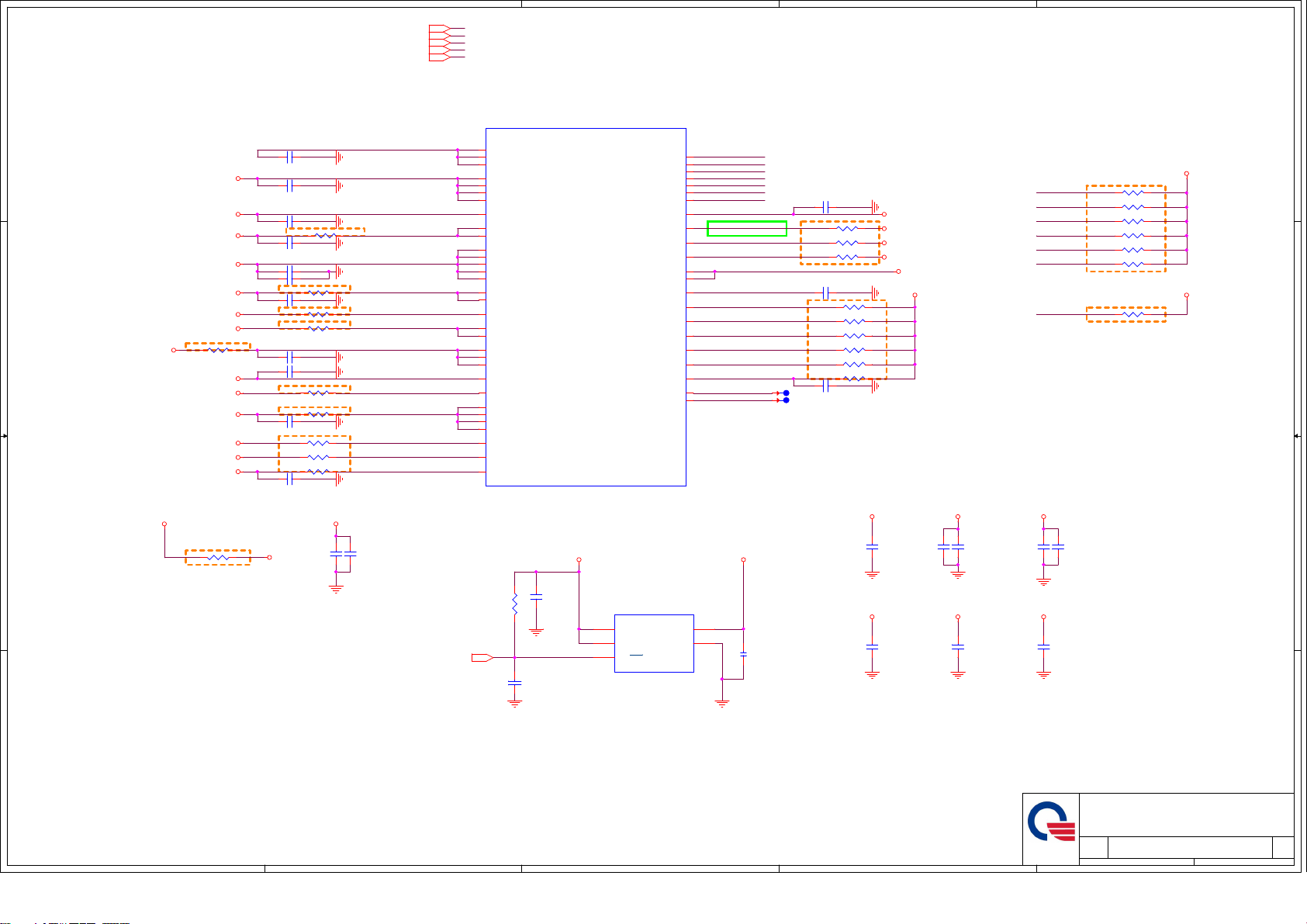

Page 2

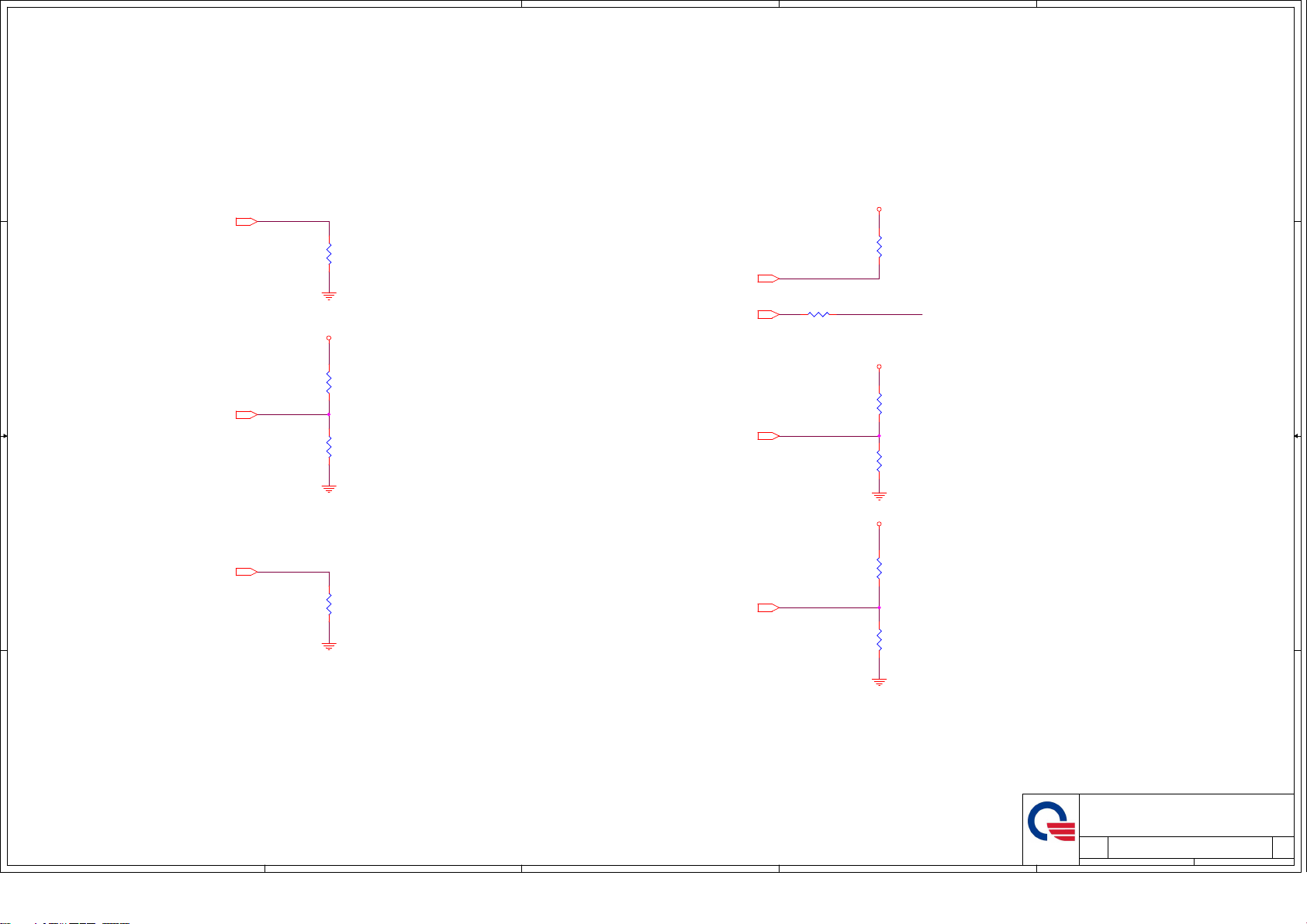

+3V

1

R90

*10K/F_4

R100

100K_4

02

2

INT_EDP_TXN0 [27]

INT_EDP_TXP0 [27]

INT_EDP_TXN1 [27]

INT_EDP_TXP1 [27]

INT_EDP_AUXN [27]

INT_EDP_AUXP [27]

TP46

HDMI_HPD_CON [28]

ULT_EDP_HPD [27,28]

PCH_LVDS_BLON [28]

PCH_DPST_PWM [27]

PCH_DISP_ON [28]

Reserve EDP_HPD opposites circuit!

ULT_EDP_HPD

SKL_ULT

DDI

DISPLAY SIDEBANDS

3

?

Q

Need apply PN

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

1 OF 20

C47

INT_EDP_TXN0

C46

INT_EDP_TXP0

D46

INT_EDP_TXN1

C45

INT_EDP_TXP1

A45

B45

A47

B47

E45

INT_EDP_AUXN

F45

INT_EDP_AUXP

B52

EDP_DISP_UTIL

G50

F50

E48

F48

G46

F46

L9

HDMI_HPD_CON

L7

L6

N9

L10

ULT_EDP_HPD

R12

PCH_LVDS_BLON

R11

PCH_DPST_PWM

U13

PCH_DISP_ON

?

SDVO_CLK[28]

SDVO_DATA[28]

+VCCIO

IN_D2#[28]

IN_D2[28]

IN_D1#[28]

IN_D1[28]

IN_D0#[28]

IN_D0[28]

IN_CLK#[28]

IN_CLK[28]

TP121

TP122

4

IN_D2#

IN_D2

IN_D1#

IN_D1

IN_D0#

IN_D0

IN_CLK#

IN_CLK

DDPC_CTRLDATA

DDPD_CTRLDATA

R96 24.9/F_4

EDP_RCOMP

U17A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

*SKL_ULT

REV = 1

5

+3V [4,10,11,12,13,14,15,16,17,18,27,28,29,30,31,32,33,34,35,41,43]

+1.0V [4,6,16,32,35,40]

+VCCSTPLL [4,5,6,9,40,41]

+VCCIO [6,16,40]

D D

DDPB_CTRLDATA/ GPP_E19

Display Port B Detected

This signal has a weak internal pull-down.

0 = Port B is not detected.

1 = Port B is detected.

1222 del for DDP not use

C C

HDMI

eDP_COMPIO and ICOMPO signals should be shorted near

balls and routed with typical impedance <25 mohms

1125 change R96 connection from +1.0V to +VCCIO

U17D

CATERR#

TP45

TP38

TP98

TP97

PROC_POPIRCOMP

PCH_OPI_RCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

EC_PECI

PROCHOT#

PM_THRMTRIP#

3D_FW_GPIO_R

CPU_GP1

CPU_GP2

CPU_GP3

H_PROCHOT#[35,36,41]

0114

+VCCSTPLL

R405 *49.9/F_4

+1.0V

0423 change to shortpad

B B

R74 *0_4/S

CATERR#

R389 *51_4

R390 51_4

R407 51_4

R408 51_4

R391 51_4

Close to Chipset

Del TP39, Add R557 with 0ohm

mount for 3D camera

JTAGX_PCH

JTAG_TMS_PCH

JTAG_TDI_PCH

JTAG_TDO_PCH

JTAG_TCK_PCH

R381 499/F_4

3D_FW_GPIO[33]

EC_PECI[35]

PM_THRMTRIP#[35]

XDP_BPM0[16]

XDP_BPM1[16]

R198 49.9/F_4

R191 49.9/F_4

R107 49.9/F_4

R101 49.9/F_4

R557 *0_4

D63

A54

C65

C63

A65

C55

D55

B54

C56

BA5

AY5

AT16

AU16

H66

H65

A6

A7

*SKL_ULT

REV = 1

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SKL_ULT

CPU MISC

Need apply PN

?

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

PDC

JTAGX

4 OF 20

B61

XDP_TCK0

D60

XDP_TDI_CPU

A61

XDP_TDO_CPU

C60

XDP_TMS_CPU

B59

XDP_TRST#_CPU

B56

JTAG_TCK_PCH

D59

JTAG_TDI_PCH

A56

JTAG_TDO_PCH

C59

JTAG_TMS_PCH

C61

XDP_TRST#_CPU

A59

JTAGX_PCH

XDP_TCK0 [16]

XDP_TDI_CPU [16]

XDP_TDO_CPU [16]

XDP_TMS_CPU [16]

XDP_TRST#_CPU [2,16]

JTAG_TCK_PCH [16]

JTAG_TDI_PCH [16]

JTAG_TDO_PCH [16]

JTAG_TMS_PCH [16]

XDP_TRST#_CPU [2,16]

JTAGX_PCH [16]

Close to EC

PM_THRMTRIP#

Processor pull-up (CPU)

TO BE REPLACED WITH 1K OHMS FOR SKL .

470 OHM IS FOR I/P

R404 1K_4

PLACE NEAR CPU

XDP_TMS_CPU

XDP_TDI_CPU

XDP_TDO_CPU

R392 *51_4

R388 *51_4

R378 *51_4

+VCCSTPLL

+1.0V

1231 un-install R378, R392

+1.0V

H_PROCHOT#

XDP_TCK0

XDP_TRST#_CPU

A A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

R44 1K_4

R406 51_4

R384 51_4

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

02 -- SKYPAKE 1/20(eDP/DDI)

02 -- SKYPAKE 1/20(eDP/DDI)

02 -- SKYPAKE 1/20(eDP/DDI)

1

2 49Friday, May 22, 2015

2 49Friday, May 22, 2015

2 49Friday, May 22, 2015

1A

1A

1A

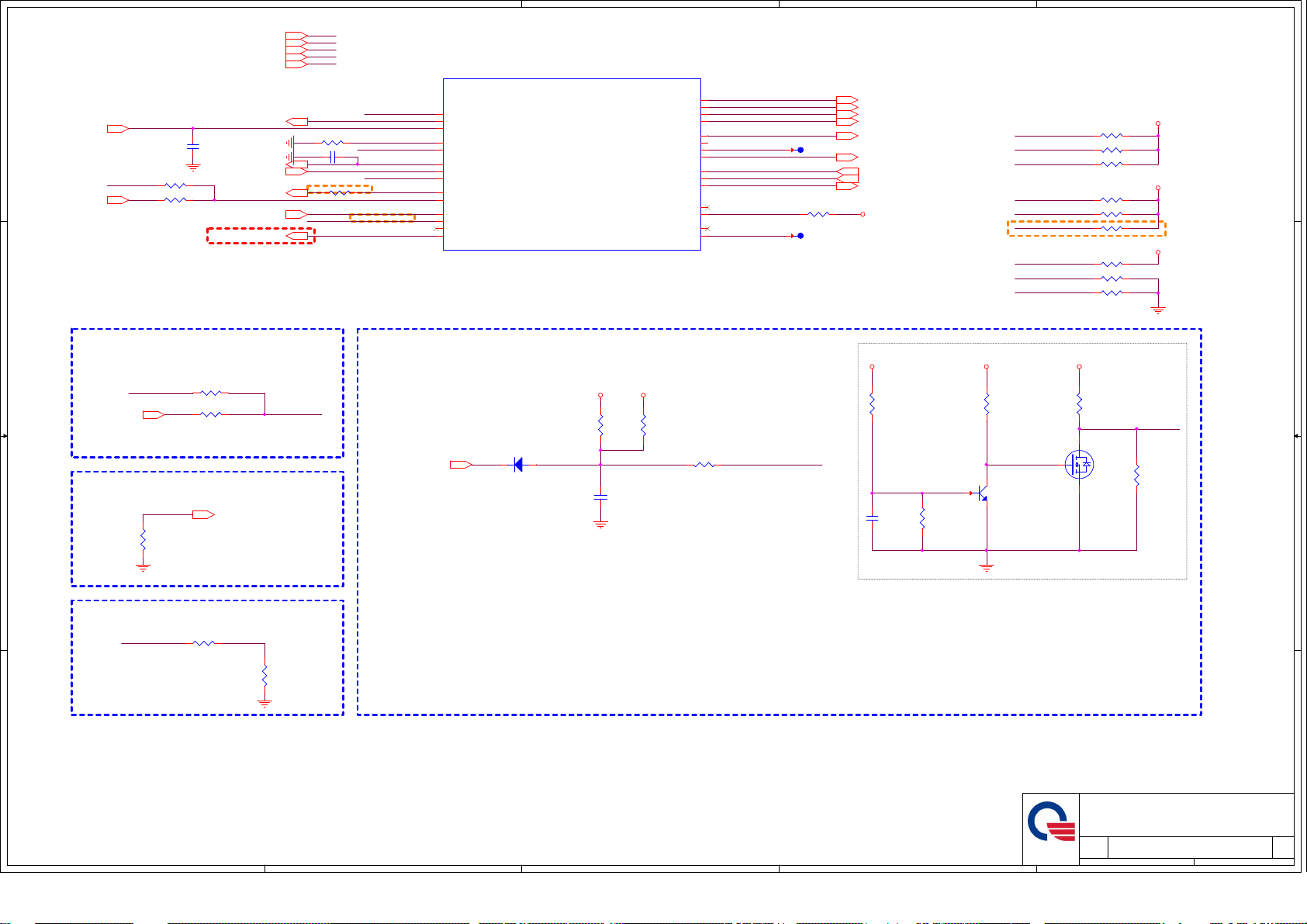

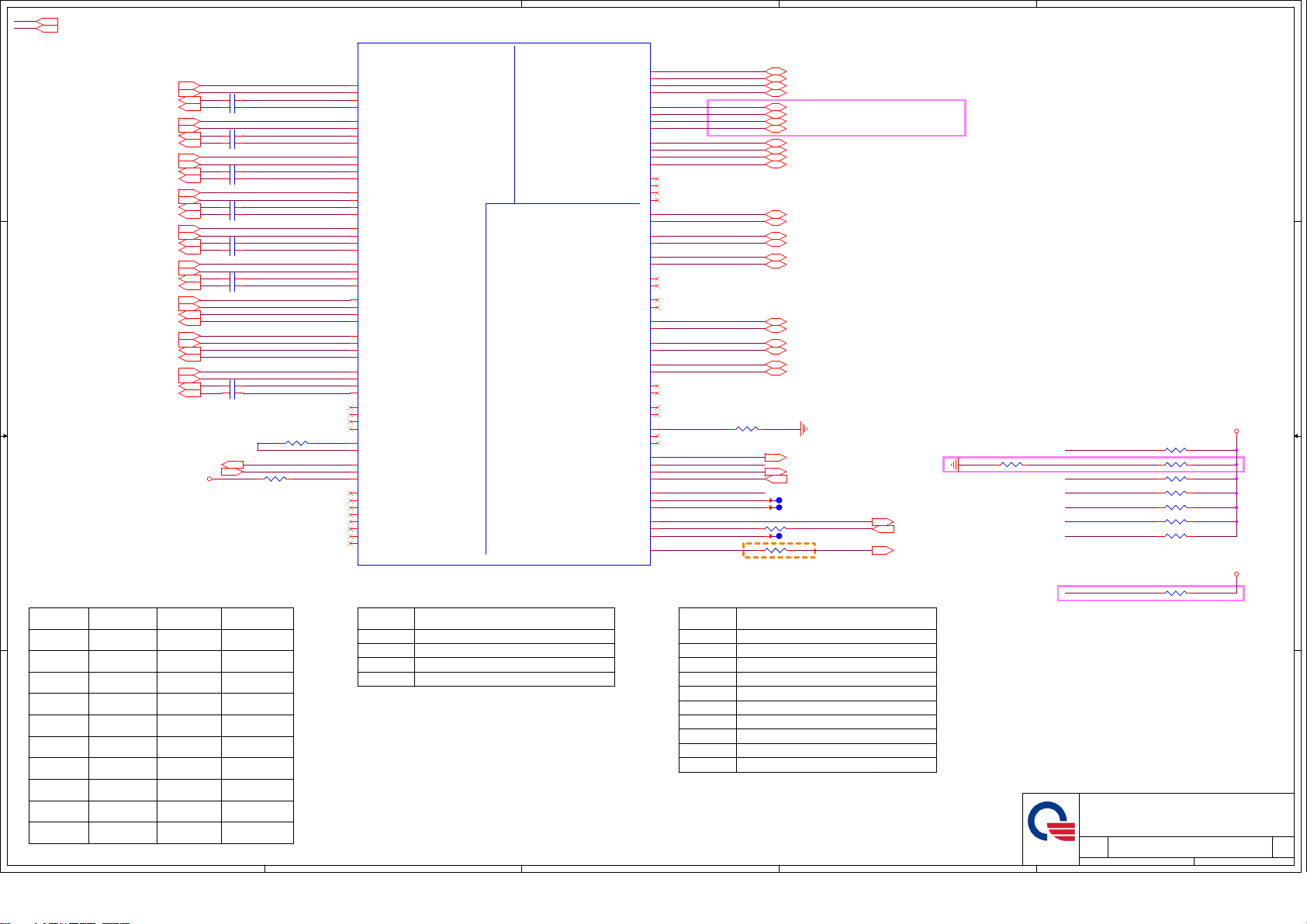

Page 3

5

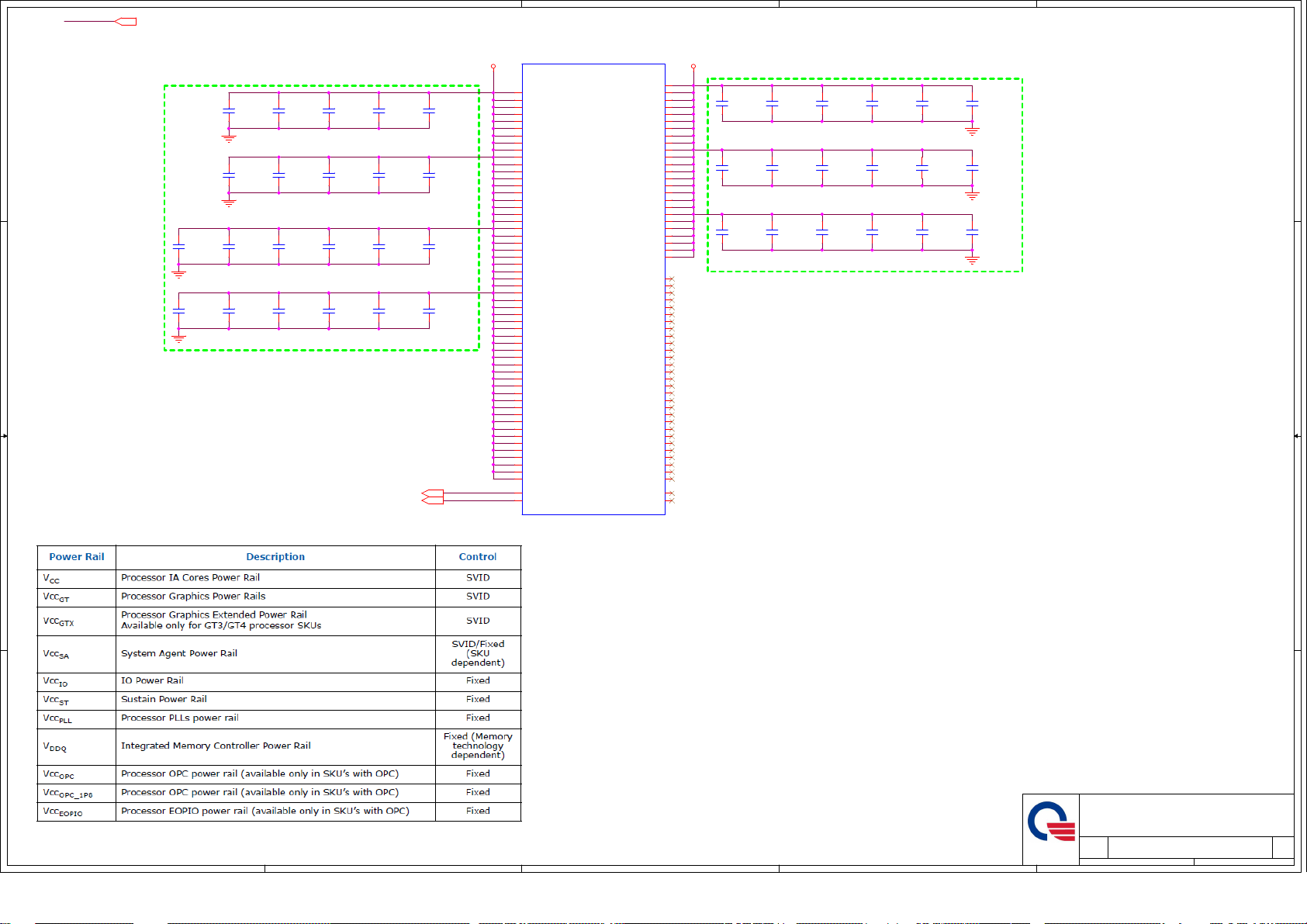

M_A_DQSN[7:0][17]

M_A_DQSP[7:0][17]

M_B_DQSN[7:0][18]

M_B_DQSP[7:0][18]

M_A_DQ[63:0][17]

M_B_DQ[63:0][18]

D D

+1.35VSUS [6,17,18,38,40]

4

SkyLake ULT Processor (DDR3L)

3

2

1

03

?

U17B

AL71

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

C C

B B

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

*SKL_ULT

REV = 1

SKL_ULT

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

NIL-DDR CH A

Need apply PN

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

2 OF 20

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

M_A_A5

BB54

M_A_A9

BA52

M_A_A6

AY52

M_A_A8

AW52

M_A_A7

AY55

M_A_BS#2

AW54

M_A_A12

BA54

M_A_A11

BA55

M_A_A15

AY54

M_A_A14

AU46

M_A_A13

AU48

AT46

AU50

AU52

AY51

M_A_A2

AT48

AT50

M_A_A10

BB50

M_A_A1

AY50

M_A_A0

BA50

M_A_A3

BB52

M_A_A4

AM70

M_A_DQSN0

AM69

M_A_DQSP0

AT69

M_A_DQSN1

AT70

M_A_DQSP1

AH66

M_B_DQSN0

AH65

M_B_DQSP0

AG69

M_B_DQSN1

AG70

M_B_DQSP1

BA64

M_A_DQSN2

AY64

M_A_DQSP2

AY60

M_A_DQSN3

BA60

M_A_DQSP3

AR66

M_B_DQSN2

AR65

M_B_DQSP2

AR61

M_B_DQSN3

AR60

M_B_DQSP3

AW50

AT52

DDR0_PAR

AY67

SM_VREF

AY68

SMDDR_VREF_DQ0_M3

BA67

SMDDR_VREF_DQ1_M3

AW67

DDR_VTT_CNTL

M_A_CLKN0 [17]

M_A_CLKP0 [17]

M_A_CLKN1 [17]

M_A_CLKP1 [17]

M_A_CKE0 [17]

M_A_CKE1 [17]

M_A_CS#0 [17]

M_A_CS#1 [17]

M_A_DIM0_ODT0 [17]

M_A_DIM0_ODT1 [17] M_B_DIM0_ODT0 [18]

M_A_A5 [17]

M_A_A9 [17]

M_A_A6 [17]

M_A_A8 [17]

M_A_A7 [17]

M_A_BS#2 [17]

M_A_A12 [17]

M_A_A11 [17]

M_A_A15 [17]

M_A_A14 [17]

M_A_A13 [17]

M_A_CAS# [17]

M_A_WE# [17]

M_A_RAS# [17]

M_A_BS#0 [17]

M_A_A2 [17]

M_A_BS#1 [17]

M_A_A10 [17]

M_A_A1 [17]

M_A_A0 [17]

M_A_A3 [17]

M_A_A4 [17]

TP12

SM_VREF [17]

SMDDR_VREF_DQ0_M3 [17]

SMDDR_VREF_DQ1_M3 [18]

DDR_VTT_CNTL [4,18]

20mils width

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

U17C

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

*SKL_ULT

REV = 1

?

SKL_ULT

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

NIL-DDR CH B

Need apply PN

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

PDC

DDR1_PAR

3 OF 20

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

M_B_A12

M_B_A11

M_B_A15

M_B_A14

M_B_A13

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

M_A_DQSN4

M_A_DQSP4

M_A_DQSN5

M_A_DQSP5

M_B_DQSN4

M_B_DQSP4

M_B_DQSN5

M_B_DQSP5

M_A_DQSN6

M_A_DQSP6

M_A_DQSN7

M_A_DQSP7

M_B_DQSN6

M_B_DQSP6

M_B_DQSN7

M_B_DQSP7

DDR1_PAR

SM_DRAMRST#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

TP14

R159 121/F_4

R162 80.6/F_4

R163 100/F_4

M_B_CLKN0 [18]

M_B_CLKN1 [18]

M_B_CLKP0 [18]

M_B_CLKP1 [18]

M_B_CKE0 [18]

M_B_CKE1 [18]

M_B_CS#0 [18]

M_B_CS#1 [18]

M_B_DIM0_ODT1 [18]

M_B_A5 [18]

M_B_A9 [18]

M_B_A6 [18]

M_B_A8 [18]

M_B_A7 [18]

M_B_BS#2 [18]

M_B_A12 [18]

M_B_A11 [18]

M_B_A15 [18]

M_B_A14 [18]

M_B_A13 [18]

M_B_CAS# [18]

M_B_WE# [18]

M_B_RAS# [18]

M_B_BS#0 [18]

M_B_A2 [18]

M_B_BS#1 [18]

M_B_A10 [18]

M_B_A1 [18]

M_B_A0 [18]

M_B_A3 [18]

M_B_A4 [18]

+1.35VSUS

R285

470/F_4

DDR3_DRAMRST# [17,18]

A A

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

04 -- SKYPAKE 3/20(DDR3-A I/F)

04 -- SKYPAKE 3/20(DDR3-A I/F)

NB5

NB5

5

4

3

2

NB5

04 -- SKYPAKE 3/20(DDR3-A I/F)

Date: Sheet of

Date: Sheet of

Date: Sheet

1

1A

1A

1A

3 49Wednesday, May 13, 2015

3 49Wednesday, May 13, 2015

3 49Wednesday, May 13, 2015

of

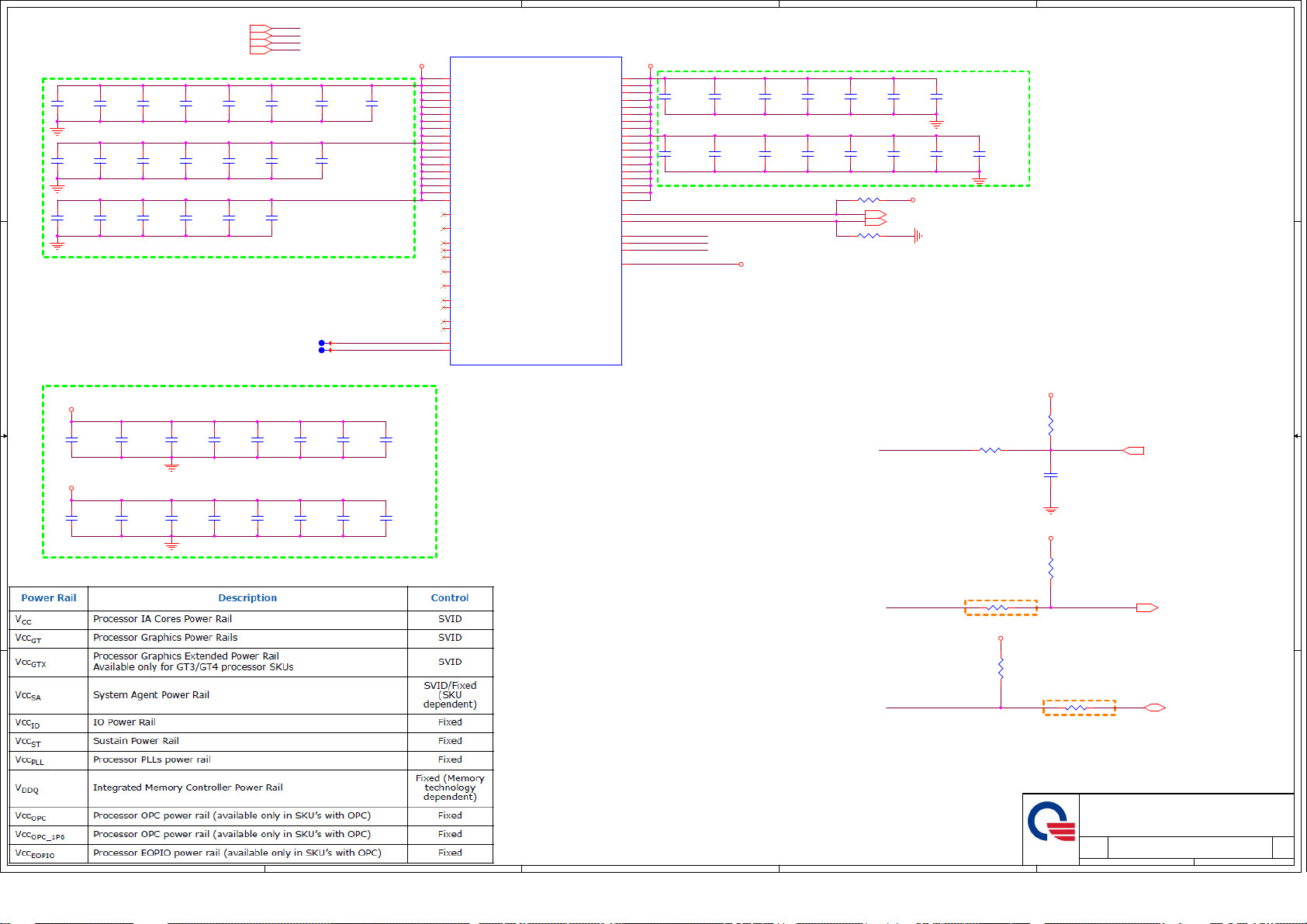

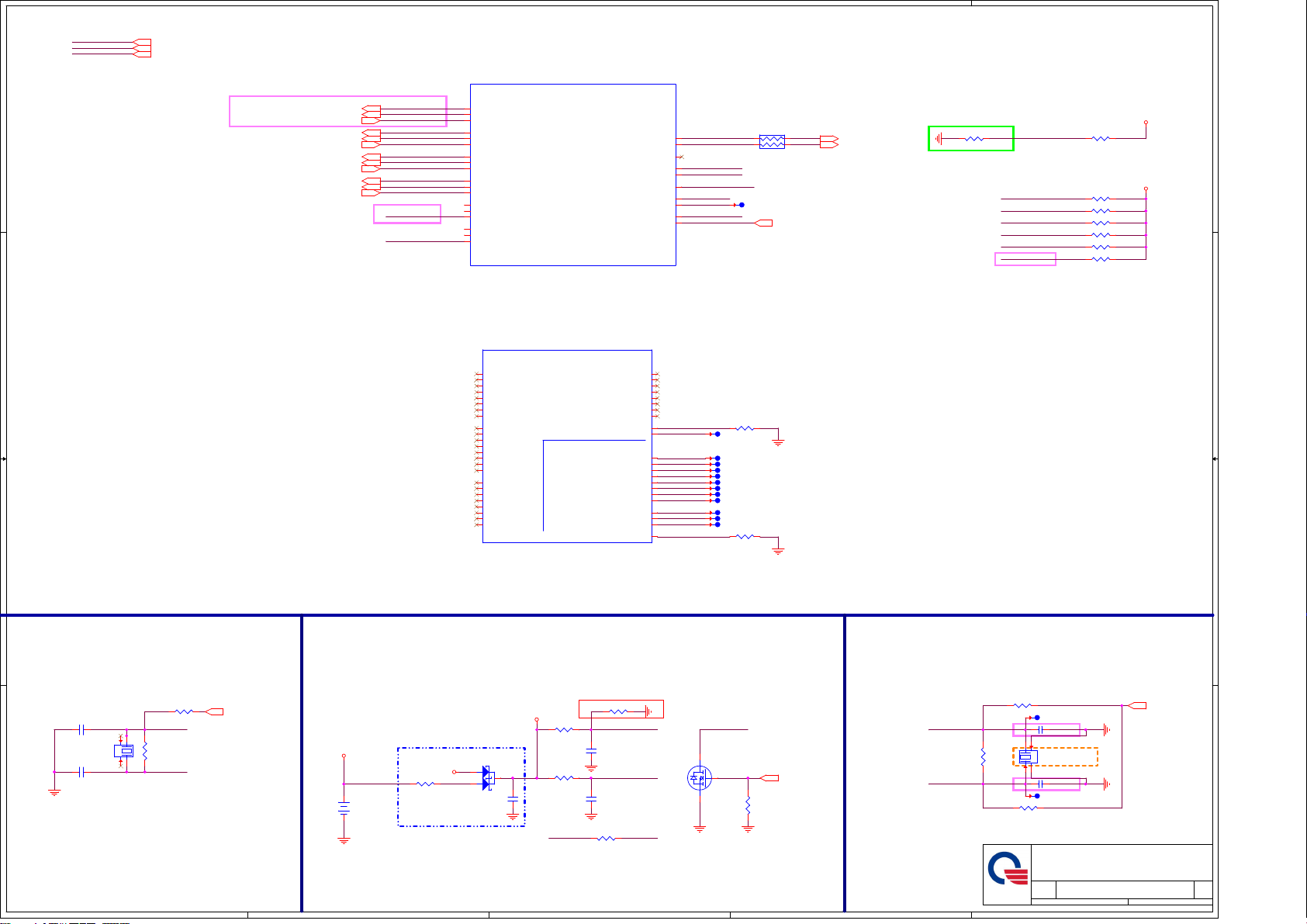

Page 4

5

+3V_DEEP_SUS[10,11,12,14,15,16,18]

+3V[2,10,11,12,13,14,15,16,17,18,27,28,29,30,31,32,33,34,35,41,43]

+3VS5[10,15,16,32,34,35,37,39,40,43,44,46]

+VCCSTPLL[2,5,6,9,40,41]

+1.0V[2,6,16,32,35,40]

D D

RSMRST#[35]

SUSWARN#

SUSACK#_EC[35]

R196*0_4

R1990_4

SYS_RESET#[16]

EC26

*220P/50V_4 C560 *0.1U/16V_4

SYS_PWROK[16]

EC_PWROK[16,35]

SUSWARN#_EC[35]

0423 change to shortpad

PCIE_WAKE#[30,34,35]

DDR_VTT_CNTL[3,18]

Need check circuit!!!!

Should be delete

R394 *10K_4

R192 *0_4/S

4

PLTRST#

SYS_RESET#

RSMRST#

PROCPWRGD

H_VCCST_PWRGD

SYS_PWROK

PCH_PWROK

DSWROK_EC_R

SUSWARN#

SUSACK#

PCIE_WAKE#

LAN_WAKE#

DDR_VTT_CNTL

AN10

AY17

BA20

BB20

AR13

AP11

BB15

AM15

AW17

AT15

A68

B65

B5

B6

U17K

*SKL_ULT

REV = 1

SYSTEM POWER MANAGEMENT

GPP_B13/PLTRST#

SYS_RESET#

RSMRST#

PROCPWRGD

VCCST_PWRGD

SYS_PWROK

PCH_PWROK

DSW_PW ROK

GPP_A13/SUSW ARN#/SUSPWRDNACK

GPP_A15/SUSACK#

WAKE#

GPD2/LAN_WAKE#

GPD11/LANPHYPC

GPD7/RSVD

SKL_ULT

?

Need apply PN

3

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW #

GPP_A11/PME#

GPP_B11/EXT_PW R_GATE#

INTRUDER#

GPP_B2/VRALERT#

11 OF 20

C

AT11

PCH_SLP_S0_N

AP15

BA16

AY16

AN15

SLP_SUS#_EC

AW15

BB17

GPD9

AN16

BA15

DNBSWON#

AY15

AC_PRESENT_EC

AU13

RF_OFF_PCH

AU11

AP16

INTRUDER#_R

AM10

AM11

GPP_B2

?

TP105

R1651M_4

TP10

2

PCH_SLP_S0_N [16,35]

SUSB# [16,35]

SUSC# [16,35]

SLP_S5# [16]

SLP_SUS#_EC [35]

SLP_A# [16]

DNBSWON# [35]

AC_PRESENT_EC [20,35]

RF_OFF_PCH [34]

+3V_RTC

PCH Pull-high/low(CLG)

SUSWARN#

SUSACK#

RF_OFF_PCH

PCIE_WAKE#

AC_PRESENT_EC

LAN_WAKE#

SYS_RESET#

RSMRST#

DSWROK_EC

R193 10K_4

R200 10K_4

R187 10K_4

R204 1K_4

R203 *10K_4

R591 *10K_4

R415 10K_4

R208 10K_4

R224 100K/F_4

1

04

+3V_DEEP_SUS

+3VS5

+3V

C C

For DS3 Sequence For HWPG, +1.0V and +VCCSTPLL Sequence

For DS3 -->Ra

Non-DS3 -->Rb

RSMRST#

DSWROK_EC[35]

PLTRST#(CLG)

Check Q2010 Rise/Fall time less than 100ns

R14

B B

100K/F_4

Rb

R212 *0_4

R215 0_4

Ra

PLTRST# [16,19,30,32,34,35]

DSWROK_EC_R

+VCCSTPLL

+1.0V

R380

1K_4

HWPG[16,35,37,38,39]

D12 RB500V-40

21

H_VCCST_PWRGD_R

C543

*10P/50V_4

1216 colayout

+VCCSTPLL & +1.0V

R379

*1K_4

R395 60.4/F_4

R395 close to CPU side

H_VCCST_PWRGD trace 0.3" - 1.5"

H_VCCST_PWRGD

+1.0V

R26

15K/F_4

+1.0V_PWRGD_G1

C32

0.1U/16V_4

R21

100K_4

2

R23

100K_4

+1.0V_PWRGD_G2

Q6

METR3904-G

1 3

1110 Add Citcuit for +1.0V Power Good

System PWR_OK(CLG)

R411 0_4

A A

EC_PWROKSYS_PWROK

R412

10K/F_4

+3VS5+5VS5

R30

10K_4

R16

100K_4

HWPG

3

2

Q5

2N7002K

1

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

06 -- SKYPAKE 5/20(Power Manger)

06 -- SKYPAKE 5/20(Power Manger)

NB5

NB5

5

4

3

2

NB5

06 -- SKYPAKE 5/20(Power Manger)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

4 49Friday, May 22, 2015

4 49Friday, May 22, 2015

4 49Friday, May 22, 2015

Page 5

2

C194

1U/6.3V_4

C182

1U/6.3V_4

+VCC_CORE

VCC_SENSE [41]

VSS_SENSE [41]

H_CPU_SVIDALRT#

Under U17

C162

1U/6.3V_4

C122

1U/6.3V_4

R398 220/F_4

C112

1U/6.3V_4

100- ±1%

pull-up to VCC

near processor.

+VCCSTPLL

R385

56.2/F_4

C534

*0.1U/16V_4

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

?

3

+VCC_CORE

H_CPU_SVIDALRT#

VR_SVID_CLK_R

H_CPU_SVIDDAT

C566

1U/6.3V_4

C568

1U/6.3V_4C193

C155

1U/6.3V_4

C133

1U/6.3V_4

C169

1U/6.3V_4

C147

1U/6.3V_4

C529

1U/6.3V_4

C195

1U/6.3V_4

R98 *100/F_4

R99 *100/F_4

+VCCSTG

C567

1U/6.3V_4

C140

1U/6.3V_4

Layout note: need routing together and ALERT need between CLK and DATA.

CLOSE TO CPU

PLACE THE PU RESISTORS

C166

C524

22U/6.3V_6

47U/6.3VS_8

4

+VCC_CORE

C152

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

U17L

*SKL_ULT

REV = 1

SKL_ULT

CPU POWER 1 OF 4

VCC_A30

VCC_A34

33A

VCC_A39

VCC_A44

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

RSVD_K32

RSVD_AK32

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

?

Need apply PN

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG_G20

PDC

12 OF 20

5

+VCC_CORE[41]

+1.0V[2,4,6,16,32,35,40]

+VCCSTG[6]

+VCCSTPLL[2,4,6,9,40,41]

Under U17

C59

C47

10U/6.3V_6

22U/6.3V_6

10U/6.3V_4

C63

22U/6.3V_6

22U/6.3V_6

D D

C95

10U/6.3V_4

C523

22U/6.3V_6

C C

C52

C123

10U/6.3V_4

C83

22U/6.3V_6

C518

22U/6.3V_6

C180

10U/6.3V_4

C70

22U/6.3V_6

47U/6.3VS_8

C517

C181

10U/6.3V_4

C520

22U/6.3V_6

C519

22U/6.3V_6

C121

10U/6.3V_4

C55

22U/6.3V_6

TP13

TP8

C60

22U/6.3V_6

C547

10U/6.3V_4

VCCEOPIO_SENSE

VSSEOPIO_SENSE

Close U17

+VCC_CORE

C135

C136

47U/6.3VS_8

47U/6.3VS_8

+VCC_CORE

C151

47U/6.3VS_8

C522

47U/6.3VS_8

C521

47U/6.3VS_8

C167

47U/6.3VS_8

47U/6.3VS_8

1

05

SVID ALERT

VR_SVID_ALERT# [41]

C120

10U/6.3V_4

B B

C87

10U/6.3V_4

C93

10U/6.3V_4

C113

10U/6.3V_4

C535

10U/6.3V_4

C538

10U/6.3V_4

C565

10U/6.3V_4

C562

10U/6.3V_4

PLACE THE PU RESISTORS

CLOSE TO VR

PULL UP IS IN THE VR MODULE

CLOSE TO CPU

PLACE THE PU RESISTORS

VR_SVID_CLK_R

H_CPU_SVIDDAT

+VCCSTPLL

R383

*54.9/F_4

R403 *0_4/S

0423 change to shortpad

+VCCSTPLL

R397

100/F_4

R382 *0_4/S

SVID CLK

VR_SVID_CLK [41]

SVID DATA

VR_SVID_DATA [41]

0423 change to shortpad

A A

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

07 -- SKYPAKE 6/20 (POWER-1)

07 -- SKYPAKE 6/20 (POWER-1)

NB5

NB5

5

4

3

2

NB5

07 -- SKYPAKE 6/20 (POWER-1)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

5 49Wednesday, May 13, 2015

5 49Wednesday, May 13, 2015

5 49Wednesday, May 13, 2015

Page 6

2

C189

1U/6.3V_4

C170

1U/6.3V_4

Close U17

VCCIO_VCCSENSE

VCCIO_VSSSENSE

C178

1U/6.3V_4

C107

10U/6.3V_4

R135 100/F_4

R186 100/F_4

C192

1U/6.3V_4

C125

10U/6.3V_4

+VCCIO

C168

1U/6.3V_4

C542

10U/6.3V_4

+VCCIO

C551

10U/6.3V_4

C558

10U/6.3V_4

C258

1U/6.3V_4

+VCCSTPLL

+VCCSTG

+VCCPLL_OC

+VCCPLL

4

+1.35VSUS

120mA

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

AL23

A18

A22

K20

K21

U17N

CPU POWER 3 OF 4

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

E

*SKL_ULT

REV = 1

SKL_ULT

2A

0.12A

0.04A

0.12A

Need apply PN

?

VCCIO

3.1A

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

4.5A

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

14 OF 20

5

+VCCSTPLL [2,4,5,9,40,41]

+VCCSA [41,42]

+1.35VSUS [3,17,18,38,40]

+1.0V_DEEP_SUS [9,13,15,16,39,40]

+1.0V [2,4,16,32,35,40]

+3VPCU [13,30,31,32,33,34,35,36,37]

+VCCIO [2,16,40]

D D

C281

10U/6.3V_4

10U/6.3V_4

C297

C268

1U/6.3V_4

1U/6.3V_4

C271

C270

1U/6.3V_4

Close U17

C278

C269

C260

10U/6.3V_4

10U/6.3V_4

+VCCSTPLL

R556 0_4

+1.0V

R75 *0_4

+VCCIO

R589 *0_4

C C

R168 0_6

+1.35V_VCCPLL_OC

R588 *0_6

R67 *0_6/S

10U/6.3V_4

C273

10U/6.3V_4

+VCCSTG

0421 Add R588,R589

for Modern Stand By

+VCCPLL_OC+1.35VSUS

+VCCPLL+VCCSTPLL

C200

*10U/6.3V_4

C196

1U/6.3V_4

Close U17 Under U17

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

3

Under U17 Close U17Under U17

C161

1U/6.3V_4

Under U17

C544

1U/6.3V_4

C126

10U/6.3V_4

VCCIO_VCCSENSE

VCCIO_VSSSENSE

C188

1U/6.3V_4

C530

1U/6.3V_4

C108

10U/6.3V_4

C154

C190

10U/6.3V_4

1U/6.3V_4

C532

C67

1U/6.3V_4

1U/6.3V_4

C163

C179

10U/6.3V_4

10U/6.3V_4

VSSSA_SENSE [41]

VCCSA_SENSE [41]

C138

10U/6.3V_4

C80

1U/6.3V_4

C41

10U/6.3V_4

C145

10U/6.3V_4

C94

1U/6.3V_4

C91

10U/6.3V_4

1

+VCCSA

C86

10U/6.3V_4

C536

10U/6.3V_4

06

0423 change to shortpad

Under U17

+VCCSTG +VCCPLL_OC

C98

1U/6.3V_4

B B

C230

1U/6.3V_4

IO Thrm Protect

+3VPCU

For 65 degree, 1.8v limit, (SW)

R146

20K/F_4

1226 Add thermistor circuit for CPU & DDR

+3VPCU +3VPCU

For 65 degree, 1.8v limit, (SW)

R549

20K/F_4

For 65 degree, 1.8v limit, (SW)

R551

*20K/F_4

Close A18 Ball

+VCCSTPLL

C96

*1U/6.3V_4

C82

*22U/6.3V_6

For 75 degree, 1.2v limit, (HW)

THER_PIPE

R142

100K_4 NTC

C206

0.1U/16V_4

1 2

THRM_MOINTOR1 [35]

R550 close R44 R552 close U12

For 75 degree, 1.2v limit, (HW)

THER_CPU

R550

100K_4 NTC

C659

0.1U/16V_4

1 2

THRM_MOINTOR2 [35]

For 75 degree, 1.2v limit, (HW)

THER_DDR

R552

*100K_4 NTC

C660

*0.1U/16V_4

1 2

THRM_MOINTOR3 [35]

Close U17

+VCCSTPLL

C69

1U/6.3V_4

A A

C134

1U/6.3V_4

+VCCPLL

+1.35VSUS

Close U17

C229

10U/6.3V_6

5

C240

10U/6.3V_6

C237

10U/6.3V_6

C255

10U/6.3V_6

C228

10U/6.3V_6

4

C238

10U/6.3V_6

C257

1U/6.3V_4

C289

1U/6.3V_4

C279

1U/6.3V_4

C305

1U/6.3V_4

NB5

NB5

3

2

NB5

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

08 -- SKYPAKE 7/20 (POWER-2)

08 -- SKYPAKE 7/20 (POWER-2)

08 -- SKYPAKE 7/20 (POWER-2)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

6 49Friday, May 22, 2015

6 49Friday, May 22, 2015

6 49Friday, May 22, 2015

1A

1A

1A

Page 7

5

+VCCGT [41]

4

3

2

1

SKL_ULT

31A

Need apply PN

?

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

PDC

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

13 OF 20

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

+VCCGT

Close U17

C175

47U/6.3VS_8

C185

22U/6.3V_6

C148

22U/6.3V_6

C157

47U/6.3VS_8

C183

22U/6.3V_6

C127

22U/6.3V_6

C143

47U/6.3VS_8

C173

22U/6.3V_6

C115

22U/6.3V_6

C124

47U/6.3VS_8

C172

22U/6.3V_6

C184

22U/6.3V_6

C149

47U/6.3VS_8

C174

22U/6.3V_6

C137

22U/6.3V_6

C150

47U/6.3VS_8

C156

22U/6.3V_6

C165

22U/6.3V_6

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

M62

N63

N64

N66

N67

N69

A48

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

J70

J69

U17M

CPU POWER 2 OF 4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

*SKL_ULT

REV = 1

+VCCGT

Under U17

D D

C141

1U/6.3V_4

C160

C C

B B

1U/6.3V_4

C76

10U/6.3V_4

C111

10U/6.3V_4

C114

1U/6.3V_4

C92

1U/6.3V_4

C186

10U/6.3V_4

C142

10U/6.3V_4

C119

1U/6.3V_4

C85

1U/6.3V_4

C118

10U/6.3V_4

C129

10U/6.3V_4

C578

1U/6.3V_4

C64

1U/6.3V_4

VCCGT_SENSE[41]

VSSGT_SENSE[41]

C576

10U/6.3V_4

C159

10U/6.3V_4

C109

1U/6.3V_4

C563

1U/6.3V_4

C117

10U/6.3V_4

C130

10U/6.3V_4

C110

1U/6.3V_4

C131

1U/6.3V_4

07

A A

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

09 -- SKYPAKE 8/20 (POWER-3)

09 -- SKYPAKE 8/20 (POWER-3)

NB5

NB5

5

4

3

2

NB5

09 -- SKYPAKE 8/20 (POWER-3)

Date: Sheet of

Date: Sheet of

Date: Sheet

1

1A

1A

1A

7 49Wednesday, May 13, 2015

7 49Wednesday, May 13, 2015

7 49Wednesday, May 13, 2015

of

Page 8

5

4

3

2

1

08

AT63

AT68

AT71

AU10

AU15

AU20

AU32

AU38

AV68

AV69

AV70

AV71

AW10

AW12

AW14

AW16

AW18

AW21

AW23

AW26

AW28

AW30

AW32

AW34

AW36

AW38

AW41

AW43

AW45

AW47

AW49

AW51

AW53

AW55

AW57

AW6

AW60

AW62

AW64

AW66

AW8

AY66

BA10

BA14

BA18

BA23

BA28

BA32

BA36

BA45

AV1

B10

B14

B18

B22

B30

B34

B39

B44

B48

B53

B58

B62

B66

B71

BA1

BA2

F68

U17Q

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_ULT

REV = 1

AA65

AA68

AB15

AB16

AB18

AB21

AD13

AD16

AD19

AD20

AD21

AD62

AE64

AE65

AE66

AE67

AE68

AE69

AF10

AF15

AF17

AF63

AG16

AG17

AG18

AG19

AG20

AG21

AG71

AH13

AH63

AH64

AH67

AJ15

AJ18

AJ20

AK11

AK16

AK18

AK21

AK22

AK27

AK63

AK68

AK69

AL28

AL32

AL35

AL38

AL45

AL48

AL52

AL55

AL58

AL64

A67

A70

AA2

AA4

AB8

AD8

AF1

AF2

AF4

AH6

AJ4

AK8

AL2

AL4

A5

U17P

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_ULT

REV = 1

D D

C C

B B

G10

G22

G43

G45

G48

G52

G55

G58

G60

G63

G66

H15

H18

H71

K16

K18

K22

K61

K63

K64

K65

K66

K67

K68

K70

K71

G5

G6

J11

J13

J25

J28

J32

J35

J38

J42

L11

L16

L17

F8

J8

U17R

SKL_ULT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

*SKL_ULT

REV = 1

GND 3 OF 3

Need apply PN

?

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

18 OF 20

L18

L2

L20

L4

L8

N10

N13

N19

N21

N6

N65

N68

P17

P19

P20

P21

R13

R6

T15

T17

T18

T2

T21

T4

U10

U63

U64

U66

U67

U69

U70

V16

V17

V18

W13

W6

W9

Y17

Y19

Y20

Y21

?

SKL_ULT

GND 1 OF 3

Need apply PN

?

R

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

16 OF 20

?

AL65

AL66

AM13

AM21

AM25

AM27

AM43

AM45

AM46

AM55

AM60

AM61

AM68

AM71

AM8

AN20

AN23

AN28

AN30

AN32

AN33

AN35

AN37

AN38

AN40

AN42

AN58

AN63

AP10

AP18

AP20

AP23

AP28

AP32

AP35

AP38

AP42

AP58

AP63

AP68

AP70

AR11

AR15

AR16

AR20

AR23

AR28

AR35

AR42

AR43

AR45

AR46

AR48

AR5

AR50

AR52

AR53

AR55

AR58

AR63

AR8

AT2

AT20

AT23

AT28

AT35

AT4

AT42

AT56

AT58

SKL_ULT

GND 2 OF 3

Need apply PN

?

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PDC

17 OF 20

BA49

BA53

BA57

BA6

BA62

BA66

BA71

BB18

BB26

BB30

BB34

BB38

BB43

BB55

BB6

BB60

BB64

BB67

BB70

C1

C25

C5

D10

D11

D14

D18

D22

D25

D26

D30

D34

D39

D44

D45

D47

D48

D53

D58

D6

D62

D66

D69

E11

E15

E18

E21

E46

E50

E53

E56

E6

E65

E71

F1

F13

F2

F22

F23

F27

F28

F32

F33

F35

F37

F38

F4

F40

F42

BA41

?

A A

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

10 -- SKYPAKE 9/20 (GND-1)

10 -- SKYPAKE 9/20 (GND-1)

NB5

NB5

5

4

3

2

NB5

10 -- SKYPAKE 9/20 (GND-1)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

8 49Friday, May 22, 2015

8 49Friday, May 22, 2015

8 49Friday, May 22, 2015

Page 9

5

+1.0V_DEEP_SUS [13,15,16,39,40]

+1.8V_DEEP_SUS [15,39,46]

+VCCSTPLL [2,4,5,6,40,41]

CFG0-19 need Reserve TP

D D

+1.0V_DEEP_SUS

C C

B B

CFG0[16]

CFG1[16]

CFG2[16]

CFG3[16]

CFG4[16]

CFG5[16]

CFG6[16]

CFG7[16]

CFG8[16]

CFG9[16]

CFG10[16]

CFG11[16]

CFG12[16]

CFG13[16]

CFG14[16]

CFG15[16]

CFG16[16]

CFG17[16]

CFG18[16]

CFG19[16]

R97 49.9/F_4

R72 *1K_4

4

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG_RCOMP

AL25

AL27

BA70

BA68

E68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

E8

AY2

AY1

D1

D3

K46

K45

C71

B70

F60

A52

J71

J68

F65

G65

F61

E61

U17S

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD_AY2

RSVD_AY1

RSVD_D1

RSVD_D3

RSVD_K46

RSVD_K45

RSVD_AL25

RSVD_AL27

RSVD_C71

RSVD_B70

RSVD_F60

RSVD_A52

RSVD_TP_BA70

RSVD_TP_BA68

RSVD_J71

RSVD_J68

VSS_F65

VSS_G65

RSVD_F61

RSVD_E61

*SKL_ULT

REV = 1

SKL_ULT

RESERVED SIGNALS-1

PDC

?

3

Need apply PN

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_BB2

RSVD_BA3

RSVD_D5

RSVD_D4

RSVD_B2

RSVD_C2

RSVD_B3

RSVD_A3

RSVD_AW1

RSVD_E1

RSVD_E2

RSVD_BA4

RSVD_BB4

RSVD_A4

RSVD_C4

RSVD_A69

RSVD_B69

RSVD_AY3

RSVD_D71

RSVD_C70

RSVD_C54

RSVD_D54

VSS_AY71

RSVD_TP_AW71

RSVD_TP_AW70

PROC_SELECT#

19 OF 20

ZVM#

MSM#

BB68

BB69

AK13

AK12

BB2

BA3

AU5

TP5

AT5

TP6

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

TP4

A69

B69

AY3

R457 *0_4/S

D71

C70

C54

0423 change to shortpad

D54

AY4

TP1

BB3

TP2

AY71

R491 *0_4/S

AR56

AW71

AW70

AP56

C64

R396 *100K_4

+1.8V_DEEP_SUS

1226 Add R548, C658

for Cannonlake-U

reserved

R548 *0_4

+VCCSTPLL

1222 Cannonlake-U stuff, Skylake-U un-stuff

?

2

C658

*1U/6.3V_4

AW69

AW68

AU56

AW48

C7

U12

U11

H11

U17T

RSVD_AW69

RSVD_AW68

RSVD_AU56

RSVD_AW48

RSVD_C7

RSVD_U12

RSVD_U11

RSVD_H11

*SKL_ULT

REV = 1

SKL_ULT

?

SPARE

Need apply PN

RSVD_F6

RSVD_E3

RSVD_C11

RSVD_B11

RSVD_A11

RSVD_D12

RSVD_C12

RSVD_F52

20 OF 20

?

1

09

F6

E3

C11

B11

A11

D12

C12

F52

Processor Strapping

CFG3

(Physcial Debug Enable)

DFX Privacy

CFG4

(DP Presence Strap)

A A

5

The CFG signals have a default value of '1' if not terminated on the board.

1 0

Disable: Enable: Set DFX Enable in DFX interface MSR

Disable; No physical DP attached to eDP

4

Enable; An ext DP device is connected to eDP

3

CFG3

CFG4

Circuit

R387 *1K_4

R427 1K_4

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

13 -- SKYPAKE 12/20 (RSV-1)

13 -- SKYPAKE 12/20 (RSV-1)

NB5

NB5

2

NB5

13 -- SKYPAKE 12/20 (RSV-1)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

9 49Wednesday, May 13, 2015

9 49Wednesday, May 13, 2015

9 49Wednesday, May 13, 2015

Page 10

2

LAD0 [32,34,35]

LAD1 [32,34,35]

LAD2 [32,34,35]

LAD3 [32,34,35]

LFRAME# [32,34,35]

CLKRUN# [35]

SML0ALERT# [11]

SML1ALERT# [11]

TP19

R171 22/F_4

R166 22/F_4

R170 *22/F_4

EC25 18P/50V_4

CLK_24M_KBC [35]

CLK_24M_DEBUG [34]

EC21 18P/50V_4

CLK_PCI_TPM [32]

EC22

EMI(near PCH)

*18P/50V_4

SKL_ULT

3

?

Need apply PN

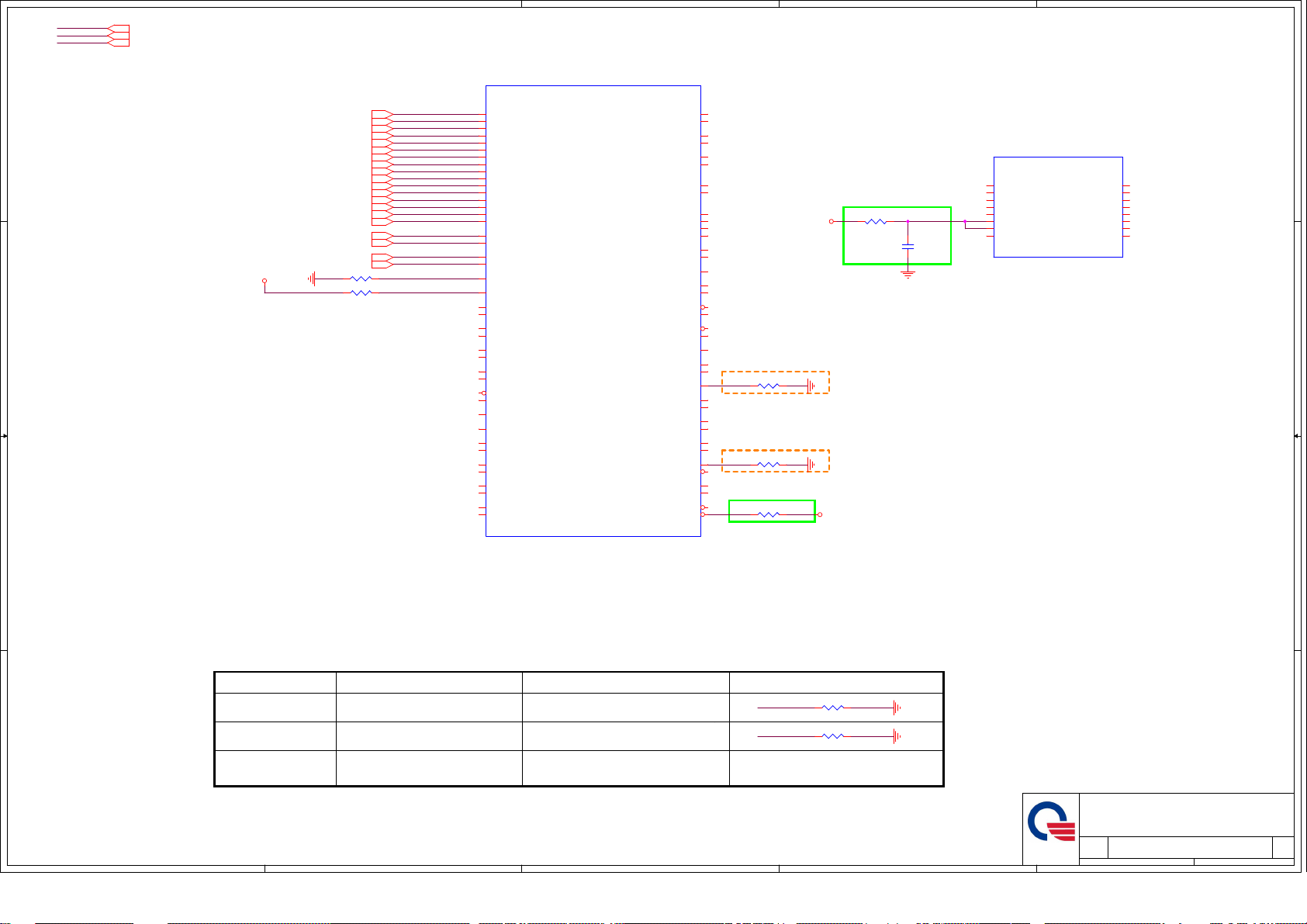

SMBUS, SMLINK

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

R7

R8

R10

R9

W2

W1

W3

V3

AM7

SMB_PCH_CLK

SMB_PCH_DAT

SML0ALERT#

SMB_ME0_CLK

SMB_ME0_DAT

SML1ALERT#

SMB_ME1_CLK

SMB_ME1_DAT

GPP_B23

D

5 OF 20

?

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

CLK_PCI_EC_R

CLK_PCI_LPC_R

CLKRUN#

LPC

PDC

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

5

+3V_DEEP_SUS [4,11,12,14,15,16,18]

+3V [2,4,11,12,13,14,15,16,17,18,27,28,29,30,31,32,33,34,35,41,43]

+3VS5 [4,15,16,32,34,35,37,39,40,43,44,46]

D D

SIO_EXT_SMI#[35]

PCI_SERR#[35]

EC_RCIN#[35]

C C

4

U17E

SPI - FLASH

PCH_SPI1_CLK

PCH_SPI1_SO

PCH_SPI1_SI

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

TP54

SPI1_CLK

SIO_EXT_SMI#

PCI_SERR#

SPI1_IO2

SPI1_IO3

TP66

TP65

SPI1_CS#

TP51

SERIRQ[32,35]

AW3

AW2

AW13

AY11

AV2

AV3

AU4

AU3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

*SKL_ULT

REV = 1

1

10

EMI(near PCH)

GPIO Pull UP

+3V +3V_DEEP_SUS

SERIRQ

CLKRUN#

SIO_EXT_SMI#

EC_RCIN#

PCI_SERR#

B B

R210 10K_4

R513 8.2K_4

R431 10K_4

R512 10K_4

R430 10K_4

SMB_PCH_CLK

SMB_PCH_DAT

SMB_ME0_CLK

SMB_ME0_DAT

SMB_ME1_CLK

SMB_ME1_DAT

SMBus/Pull-up(CLG)

Q34

MBCLK2[18,27,35]

MBDATA2[18,27,35]

A A

R89 4.7K_4

+3V

SMB_RUN_DAT[16,17,18,27,31]

R87 4.7K_4

+3V

SMB_RUN_CLK[16,17,18,27,31]

5

4 3

1

*2N7002KDW

Q11

4 3

1

2N7002KDW

+3V

5

SMB_ME1_CLK

2

6

SMB_ME1_DAT

+3V

5

SMB_PCH_DAT

2

6

SMB_PCH_CLK

CPU heat pipe local thermal sensor

DDR thermal sensor

RTD2136

EC

Touch Pad

XDP

DDR3-L

4

R91 2.2K_4

R88 2.2K_4

R103 499/F_4

R442 499/F_4

R439 1K_4

R436 1K_4

PCH SPI ROM(CLG)

Vender P/N

EON

Winbond

GigaDevice

Socket

TP66-71 need place to TOP

3

Size

8MB

8MB

TP43

TP78

TP75

TP44

TP40

TP67

+3VSPI

PCH_SPI_IO2

AKE3EZN0Q01 (EN25QH64-104HIP)8MB

AKE3EFP0N07 (W25Q64FVSSIQ)

AKE3EGN0Q01 (GD25B64BSIGR)

DFHS08FS023

PCH_SPI_CS0#_R[35]

PCH_SPI1_CLK_R[35]

PCH_SPI1_SI_R[35]

PCH_SPI1_SO_R[35]

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SI_R

PCH_SPI1_SO_R

BIOS_WP#

HOLD#

R401/R402/R410/R438/R443/R444 close to U15 pin

R401 15/F_4

PCH_SPI_CS0#

R444 15/F_4

PCH_SPI1_CLK

PCH_SPI1_SI

R438 15/F_4

R402 15/F_4

PCH_SPI1_SO

R409 1K_4C580 1U/10V_4

R410 15/F_4

PCH SPI ROM(CLG)

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SI_R

PCH_SPI1_SO_R

C577

22P/50V_4

BIOS_WP#

1222 change R409,R437 from 3.3K 1% to 1K 5%

2

+3V_DEEP_SUS

U15

1

CE#

6

SCK

5

SI

2

SO

3

WP#

*GD25B64BSIGR

AKE3EFP0N07

4M SPI ROM Socket

U16

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SI_R

PCH_SPI1_SO_R

BIOS_WP#

1

CE#

6

SCK

5

SI

2

SO

3

WP#

A25LQ32AM-F/Q

AKE3EFP0N07

91960-0084L-8P-SOCKET

U15&U16 footprint

R451 *0_4

+3VS5

R452 0_4

8

+3VSPI

VDD

HOLD#

VSS

7

4

R437 1K_4

HOLD#

R443 15/F_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet

8

+3VSPI

VDD

7

HOLD#

HOLD#

4

VSS

PCH_SPI_IO3

C583

0.1U/16V_4

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

15 -- SKYPAKE 14/20(SPI/LPC/SMBUS)

15 -- SKYPAKE 14/20(SPI/LPC/SMBUS)

15 -- SKYPAKE 14/20(SPI/LPC/SMBUS)

1

1A

1A

1A

10 49Friday, May 22, 2015

10 49Friday, May 22, 2015

10 49Friday, May 22, 2015

of

Page 11

5

4

3

2

1

11

D D

DESIGN NOTE:

WEAK PULL UP RESISTOR PRESENT ON THIS NET

ACZ_SPKR[14,29]

C C

SML0ALERT#[10]

B B

GSPI1_MOSI[14]

ACZ_SPKR

SML0ALERT#

GSPI1_MOSI

R458

*20K/F_4

+3V_DEEP_SUS

R95

1K_4

R94

*20K/F_4

R140

*20K/F_4

Functional Strap Definitions

TOP SWAP OVERRIDE

HIGH - TOP SWAP ENABLE

LOW-DISABLED

HIGH: LPC SELECTED FOR SYSTEM FLASH

WEAK INTERNAL PD

No Boot:

The signal has a weak internal pull-down.

0 = Disable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (no confidentiality).

1 = Enable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (with confidentiality). Must be

pulled up to support Intel AMT with TLS and Intel

SBA (Small Business Advantage) with TLS.

No Boot:

The signal has a weak internal pull-down.

This field determines the destination of accesses to the

BIOS memory range. Also controllable using Boot BIOS

Destination bit (Chipset Configuration Registers: Offset

3410h:Bit 10). This strap is used in conjunction with Boot

BIOS Destination Selection 0 strap.

Bit 10 Boot BIOS Destination

0 SPI

1 LPC

ACZ_SDOUT[14]

GPIO33_EC[35]

GPP_B18[14]

SML1ALERT#[10]

ACZ_SDOUT

R219 1K_4

GPP_B18

SML1ALERT#

+3V_DEEP_SUS

R492

*4.7K_4

ACZ_SDOUT

+3V

R144

*4.7K_4

R143

10K_4

+3V_DEEP_SUS

R441

*10K_4

R440

20K/F_4

No Boot:

The signal has a weak internal pull-down.

0 = Enable security measures defined in the Flash

Descriptor.

1 = Disable Flash Descriptor Security (override). This

strap should only be asserted high using external

pull-up in manufacturing/debug environments ONLY.

This function is useful when running ITP/XDP.

No Boot:

The signal has a weak internal pull-down.

0 = Disable No Reboot mode.

1 = Enable No Reboot mode

(PCH will disable the TCO

Timer system reboot feature).

This function is useful when running ITP/XDP.

No Boot:

The signal has a weak internal pull-down.

0 = LPC Is selected for EC.

1 = eSPI Is selected for EC.

A A

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

16 -- SKYPAKE 15/20(HDA)

16 -- SKYPAKE 15/20(HDA)

NB5

NB5

5

4

3

2

NB5

16 -- SKYPAKE 15/20(HDA)

Date: Sheet of

Date: Sheet of

Date: Sheet

1

1A

1A

1A

11 49Wednesday, May 13, 2015

11 49Wednesday, May 13, 2015

11 49Wednesday, May 13, 2015

of

Page 12

2

ACC_LED# [34]

ZERO_ODD_DP# [34]

SATA_LED# [34]

2

R584 100K_4

NB5

NB5

NB5

GPU_EVENT#

DGPU_HOLD_RST#

DGPU_PWR_EN

DGPU_PWROK

SATA_LED#

GC6_FB_EN

ODD_PRSNT#_R

ACC_LED#

PROJECT : X1A

PROJECT : X1A

PROJECT : X1A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

17 -- SKYPAKE 16/20 (PCIE/USB)

17 -- SKYPAKE 16/20 (PCIE/USB)

17 -- SKYPAKE 16/20 (PCIE/USB)

Date: Sheet of

Date: Sheet of

Date: Sheet of

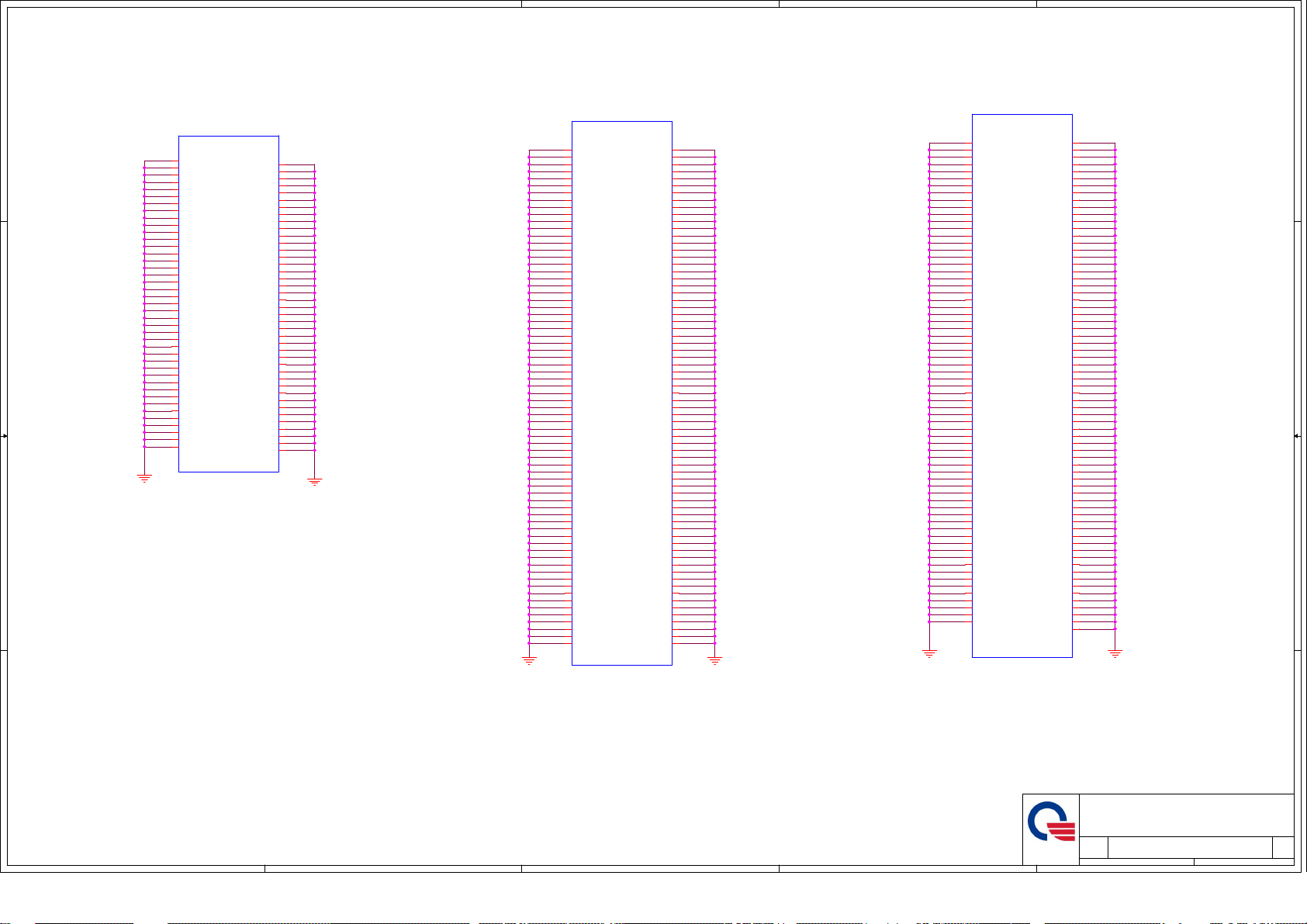

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

8 OF 20

?

3

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB30_RX1-

USB30_RX1+

USB30_TX1-

USB30_TX1+

USB30_RX2USB30_RX2+

USB30_TX2USB30_TX2+

USB30_RX3-

USB30_RX3+

USB30_TX3-

USB30_TX3+

USBP1USBP1+

USBP2USBP2+

USBP3USBP3+

USBP6USBP6+

USBP7USBP7+

USBP8USBP8+

USB2_COMP

R126 113/F_4

DGPU_HOLD_RST#

GPU_EVENT#

DGPU_PWR_EN

DGPU_PWROK

GC6_FB_EN

DEVSLP1

OCP_OC#

ACC_LED#

ODD_PRSNT#_R

SATAGP2

SATA_LED#_R

USB30_RX1+ [33]

USB30_RX2+ [33]

USB30_RX3+ [30]

USBP1- [33]

USBP1+ [33]

USBP2- [30]

USBP2+ [30]

USBP3- [28]

USBP3+ [28]

USBP6- [30]

USBP6+ [30]

USBP7- [34]

USBP7+ [34]

USBP8- [32]

USBP8+ [32]

R416 *0_4

R421 *0_4/S

0423 change to shortpad

USB2.0 Port Mapping Table

USB2.0 Function

PORT-1

PORT-2

PORT-3

PORT-4

PORT-5

PORT-6

PORT-7

PORT-8

PORT-9

PORT-10

3

Cobime USB3.0 MB-1

Cobime USB3.0 Smaii Board

Camera

NC

NC

Cobime USB3.0 Smaii Board

WLAN

Touch Screen

NC

NC

USB30_RX1- [33]

USB30_TX1- [33]

USB30_TX1+ [33]

USB30_RX2- [33]

USB30_TX2- [33]

USB30_TX2+ [33]

USB30_RX3- [30]

USB30_TX3- [30]

USB30_TX3+ [30]

USB3.0 (M/B-1)

USB3.0 (3D CAMERA)

USB3.0 Small Board

Combo USB3.0 MB-1

Combo USB3.0 Small Board

Camera

Combo USB3.0 Small Board

WLAN

Touch Screen

PLACE 'R10387' WITHIN 500 MILS

FROM USB2_COMP PIN WITH

TRACE IMPEDANCE LESS THAN 0.5 OHMS

DGPU_HOLD_RST# [19]

DGPU_PWR_EN [20,44,46]

DGPU_PWROK [20,35,44,46]

TP49

TP48

TP47

SATA_LED#

5

+3V [2,4,10,11,13,14,15,16,17,18,27,28,29,30,31,32,33,34,35,41,43]

+3V_DEEP_SUS [4,10,11,14,15,16,18]

PEG_RXN0[19]

PEG_RXP0[19]

PEG_TXN0[19]

D D

dGPU

Cardreader

WLAN

HDD

C C

ODD

LAN

B B

PEG_TXP0[19]

PEG_RXN1[19]

PEG_RXP1[19]

PEG_TXN1[19]

PEG_TXP1[19]

PEG_RXN2[19]

PEG_RXP2[19]

PEG_TXN2[19]

PEG_TXP2[19]

PEG_RXN3[19]

PEG_RXP3[19]

PEG_TXN3[19]

PEG_TXP3[19]

PCIE_RXN5_CARD[30]

PCIE_RXP5_CARD[30]

PCIE_TXN5_CARD[30]

PCIE_TXP5_CARD[30]

PCIE_RXN6_WLAN[34]

PCIE_RXP6_WLAN[34]

PCIE_TXN6_WLAN[34]

PCIE_TXP6_WLAN[34]

SATA_RXN0[34]

SATA_RXP0[34]

SATA_TXN0[34]

SATA_TXP0[34]

SATA_RXN1[34]

SATA_RXP1[34]

SATA_TXN1[34]

SATA_TXP1[34]

PCIE_RXN9_LAN[30]

PCIE_RXP9_LAN[30]

PCIE_TXN9_LAN[30]

PCIE_TXP9_LAN[30]

+3V_DEEP_SUS

XDP_PRDY#_CPU[16]

XDP_PREQ#_CPU[16]

C574 0.22U/10V_4

C573 0.22U/10V_4

C557 0.22U/10V_4

C556 0.22U/10V_4

C554 0.22U/10V_4

C555 0.22U/10V_4

C552 0.22U/10V_4

C553 0.22U/10V_4

C571 0.1U/16V_4

C572 0.1U/16V_4

C569 0.1U/16V_4

C570 0.1U/16V_4

C575 0.1U/16V_4

C564 0.1U/16V_4

R180 10K_4

PCIE_TXN5_CARD_C

PCIE_TXP5_CARD_C

PCIE_TXN6_WLAN_C

PCIE_TXP6_WLAN_C

PCIE_TXN9_LAN_C

PCIE_TXP9_LAN_C

R56 100/F_4

PEG_TXN0_C

PEG_TXP0_C

PEG_TXN1_C

PEG_TXP1_C

PEG_TXN2_C

PEG_TXP2_C

PEG_TXN3_C

PEG_TXP3_C

PIRQA#

BB11

H13

G13

B17

A17

G11

F11

D16

C16

H16

G16

D17

C17

G15

F15

B19

A19

F16

E16

C19

D19

G18

F18

D20

C20

F20

E20

B21

A21

G21

F21

D21

C21

E22

E23

B23

A23

F25

E25

D23

C23

F5

E5

D56

D61

E28

E27

D24

C24

E30

F30

A25

B25

PCI-E Port Mapping Table

PCI-E Port

Port1

Port2

Port3

Port4

Port5

Port6

A A

Port7

Port8

Port9

Port10

Function

dGPU

dGPU

dGPU

dGPU

CardReader

WLAN

HDD

ODD

LAN

Un-used

CLK RQ Port

5

Port0

Port1

Port2

Port3

Port4

Port5

Function

Un-used

CardReader

WLAN

LAN

VGA

Un-used

4

?

U17H

PCIE/USB3/SATA

PCIE1_RXN/USB3_5_RXN

PCIE1_RXP/USB3_5_RXP

PCIE1_TXN/USB3_5_TXN

PCIE1_TXP/USB3_5_TXP

PCIE2_RXN/USB3_6_RXN

PCIE2_RXP/USB3_6_RXP

PCIE2_TXN/USB3_6_TXN

PCIE2_TXP/USB3_6_TXP

PCIE3_RXN

PCIE3_RXP

PCIE3_TXN

PCIE3_TXP

PCIE4_RXN

PCIE4_RXP

PCIE4_TXN

PCIE4_TXP

PCIE5_RXN

PCIE5_RXP

PCIE5_TXN

PCIE5_TXP

PCIE6_RXN

PCIE6_RXP

PCIE6_TXN

PCIE6_TXP

PCIE7_RXN/SATA0_RXN

PCIE7_RXP/SATA0_RXP

PCIE7_TXN/SATA0_TXN

PCIE7_TXP/SATA0_TXP

PCIE8_RXN/SATA1A_RXN

PCIE8_RXP/SATA1A_RXP

PCIE8_TXN/SATA1A_TXN

PCIE8_TXP/SATA1A_TXP

PCIE9_RXN

PCIE9_RXP

PCIE9_TXN

PCIE9_TXP

PCIE10_RXN

PCIE10_RXP

PCIE10_TXN

PCIE10_TXP

PCIE_RCOMPN

PCIE_RCOMPP

PROC_PRDY#

PROC_PREQ#

GPP_A7/PIRQA#

PCIE11_RXN/SATA1B_RXN

PCIE11_RXP/SATA1B_RXP

PCIE11_TXN/SATA1B_TXN

PCIE11_TXP/SATA1B_TXP

PCIE12_RXN/SATA2_RXN

PCIE12_RXP/SATA2_RXP

PCIE12_TXN/SATA2_TXN

PCIE12_TXP/SATA2_TXP

*SKL_ULT

REV = 1

SKL_ULT

PDC

USB3.0 Port Mapping Table

USB3.0 Function

PORT-1

PORT-2

PORT-3

USB3.0 MB-1

USB3.0 (3D CAMERA)

Cobime USB3.0 Smaii Board

PORT-4 NC

4

Need apply PN

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

1

R413 *10K_4

R400 *10K_4

R73 10K_4

R414 10K_4

R425 10K_4

R424 *10K_4

R418 10K_4

R426 10K_4

1

12

+3V

+3V_DEEP_SUS

12 49Wednesday, May 13, 2015

12 49Wednesday, May 13, 2015

12 49Wednesday, May 13, 2015

1A

1A

1A

Page 13

5

4

3

2

1

+3V_RTC [4,15,32]

+1.8V_DEEP_SUS [9,15,39,46]

+3V [2,4,10,11,12,14,15,16,17,18,27,28,29,30,31,32,33,34,35,41,43]

?

?

Need apply PN

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

Need apply PN

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XCLK_BIASREF

TBT

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

9 OF 20

?

XTAL24_IN

XTAL24_OUT

RTCX1

RTCX2

SRTCRST#

RTCRST#

10 OF 20

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2