Page 1

1

2

3

4

5

6

7

8

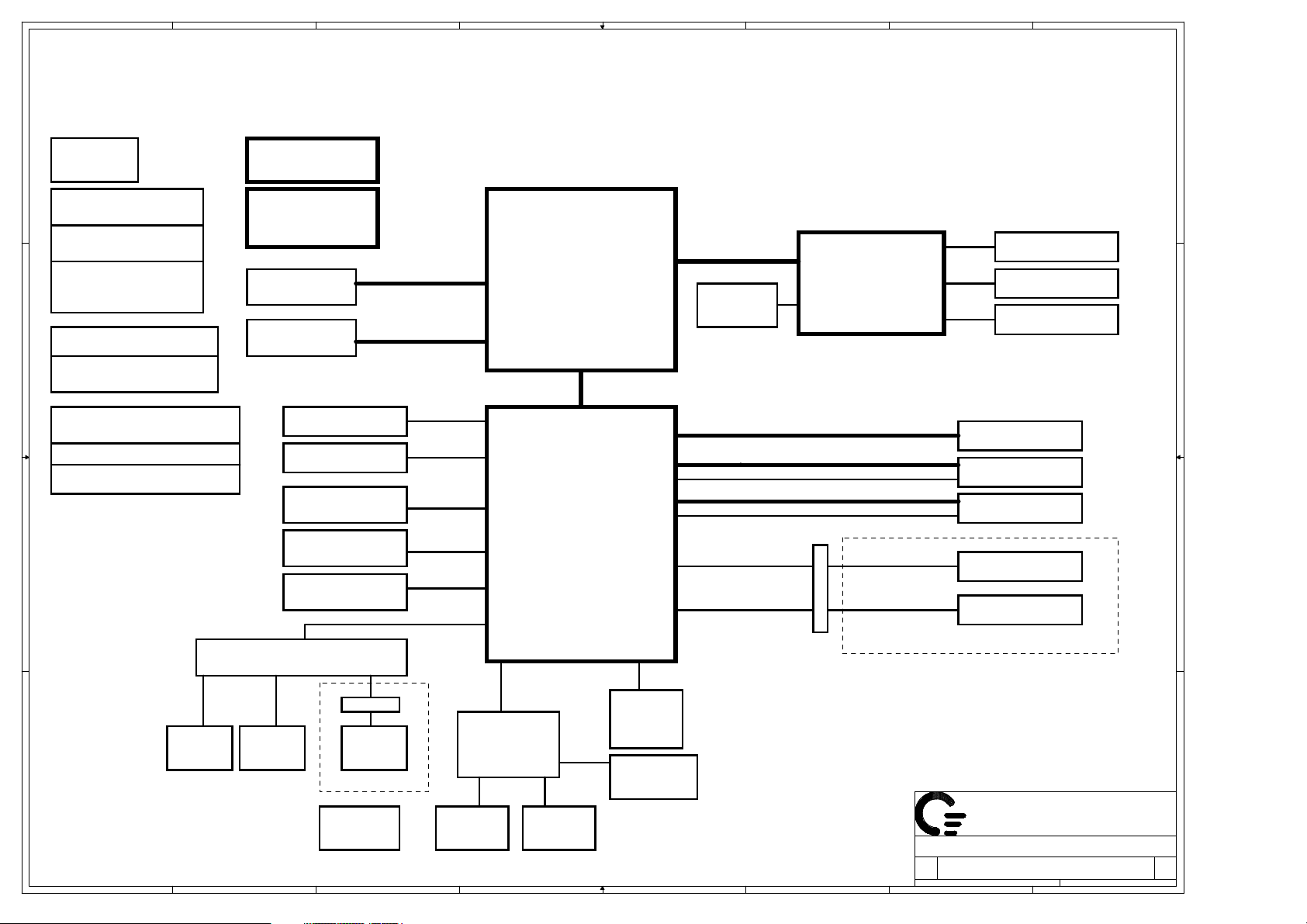

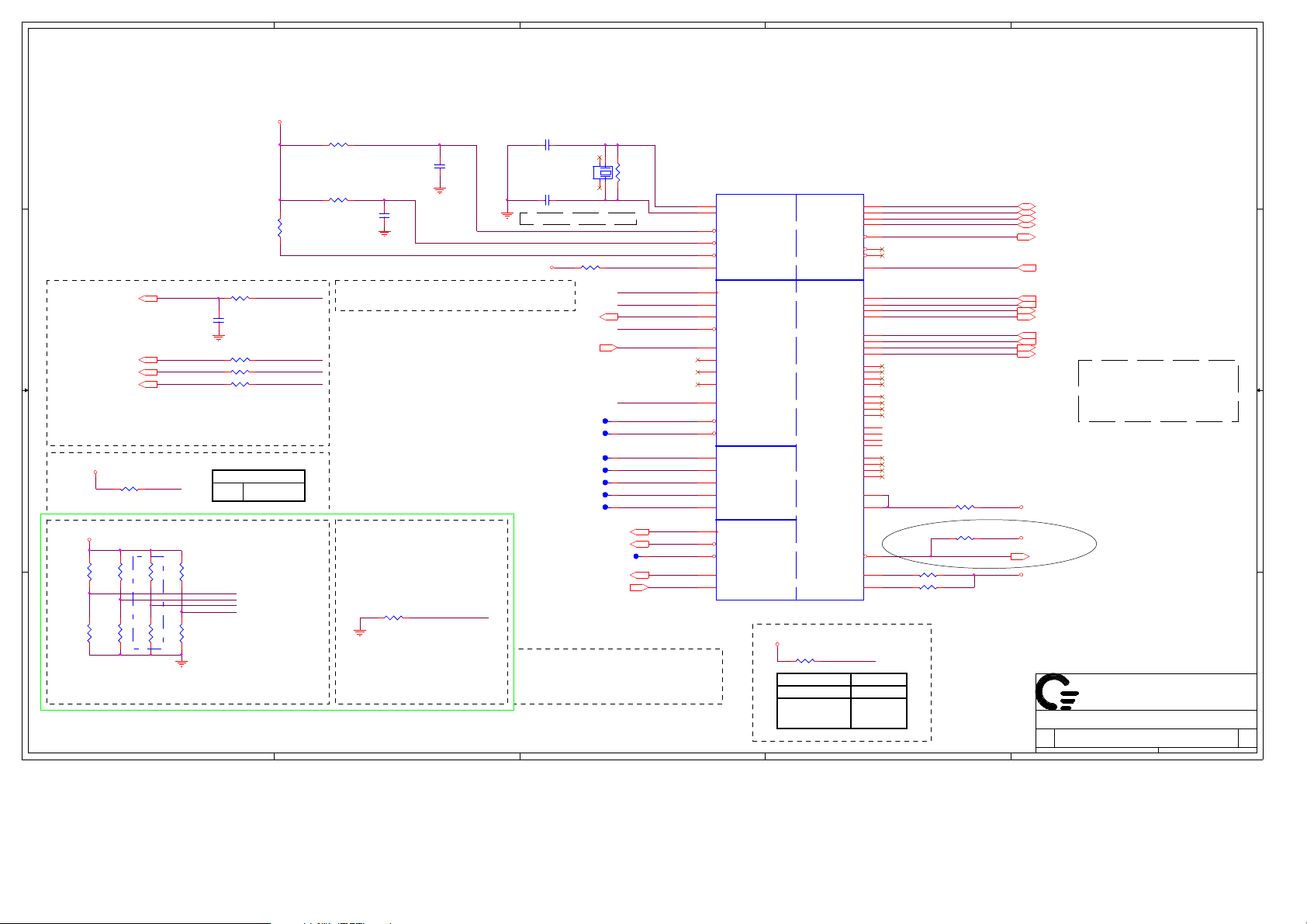

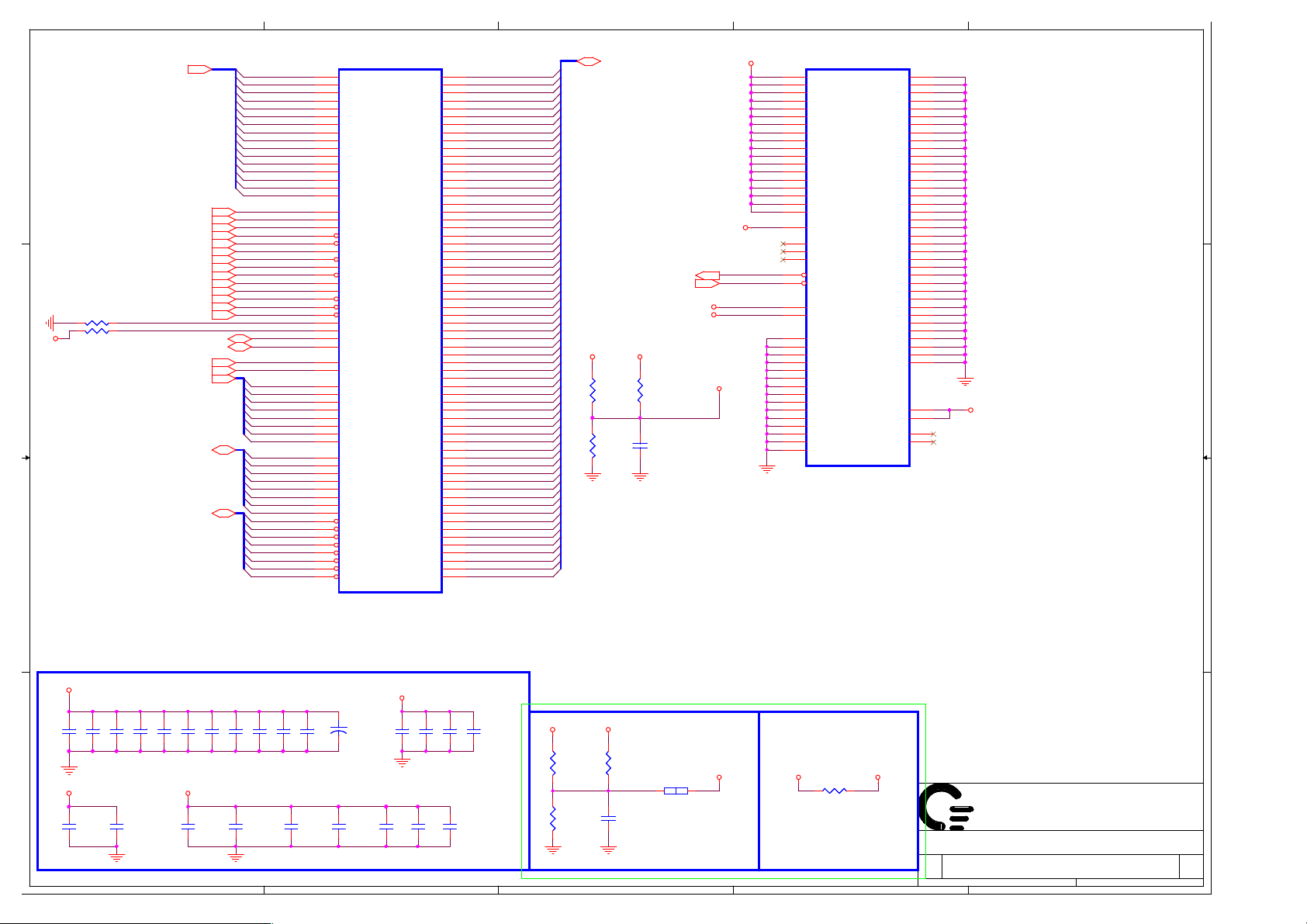

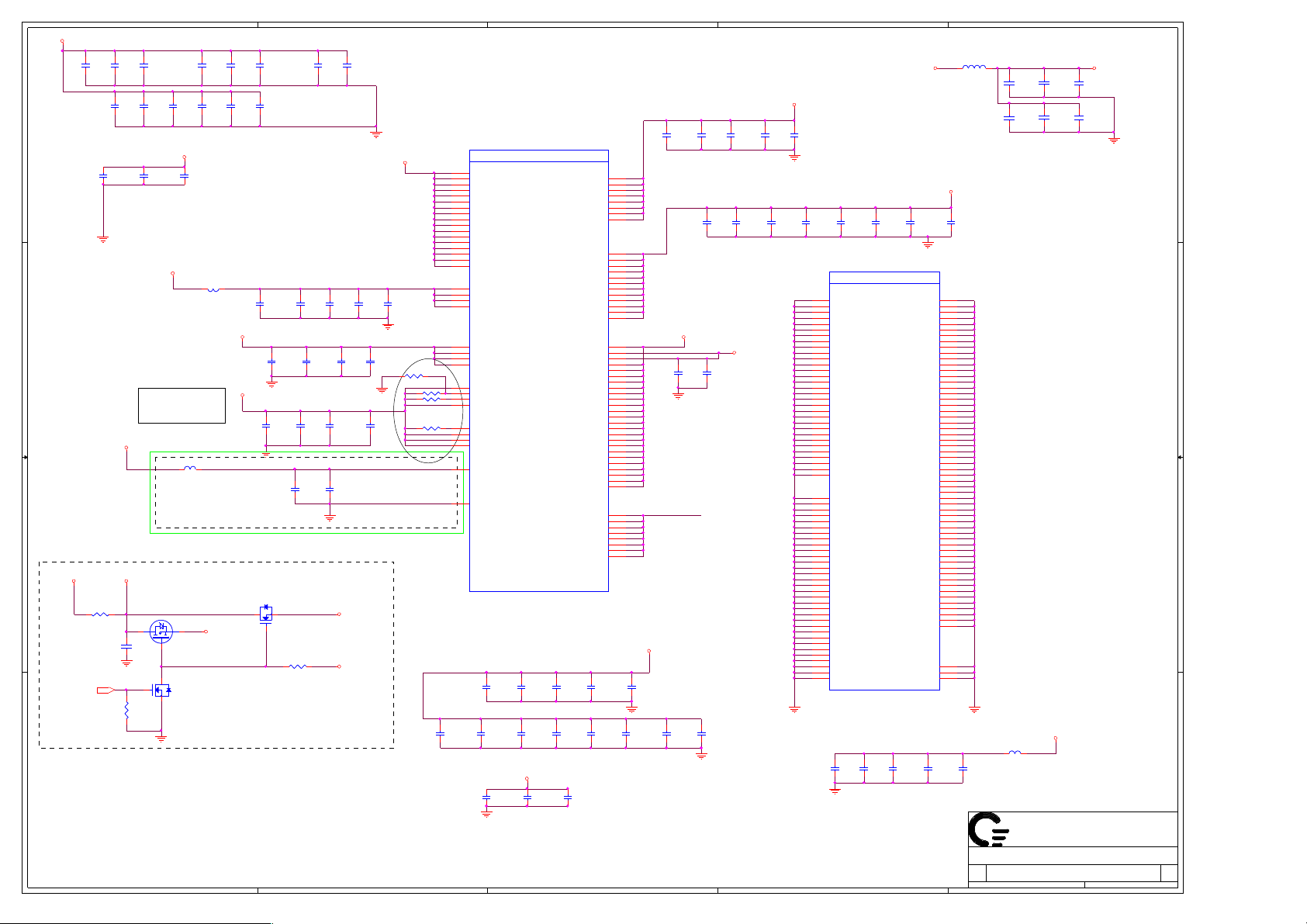

UM3/UM6 SYSTEM BLOCK DIAGRAM

POWER

A A

AC/BATT

CONNECTOR

PG 53

THERMAL

SMSC1422

PG 38

SYSTEM

RESET CIRCUIT

PG 42

BATT

CHARGER

RUN POWER SW

+3.3V_SUS/+5V_SUS

+5V/+3.3V/+1.8V

CPU VR

B B

DC/DC

+3.3V_ALW /+5V_ALW /

+15V_ALW

REGULATOR

+1.5V_SUS/+0.75V_DDR_VTT

+1.05V_PCH

+1.05V_VTT

C C

PG 45

PG 52

PG 51

PG 46

PG 47

PG 48

PG 49

A- MIC

conn

PG 39

D D

1

CLOCK

SLG8SP585VTR

(QFN-32)

DDR3-SODIMM1

RVS Type

PG 13

DDR3-SODIMM2

RVS Type

PG 14

SATA-ODD

SATA-HDD

USB conn x 1

Bluetooth BTB Conn

BT365

Camera

To LCD Conn

AUDIO/AMP

ALC269Q-GR

Audio

SPK conn

PG 39 PG 26

USER

INTERFACE

2

PG 15

Dual Channel DDR3

800/1066 1.5V

PG 35

PG 35

PG 33

PG 32

PG 24

PG 39

DB CONN

Audio

Jacks x2

IO Board

PG 37

3

SATA

SATA

USB2.0

USB2.0

USB2.0

IHDA

KBC

ITE8502

SPI PS/2

FLASH

1Mbytes

PG 30

Arrandale

( rPGA 989 )

LPC

PG 29

Touchpad

4

PG 3,4,5,6

DMI X 4

PCH

(HM55)

PG 7,8,9,10,11,12

17X8

PG 36

SPI

FLASH

4Mbytes

PG 30

Keyboard

PG 36

PCIEx16

DDR3 x 4

(512M 64bits)

PCIE 2.0

PCIE 2.0

USB2.0

PCIE 2.0

USB2.0

USB2.0

USB2.0

VER :C3B

PWA:

PWB:

5

PG 22

ATI M92-LP S2

PCI EXPRESS GFX

631 uFCBGA 23mm*23mm

PG 16,17,18,19,20,21,22

DB CONN

6

USB2.0

USB2.0

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

LVDS

HDMI

VGA

Panel Connector

HDMI CONN.

CRT CONN.

LOM

RTL8103E

PG 24

PG 24

PG 25

PG 41

MINI-CARD

WLAN

PG 32

MINI-CARD

WW AN

PG 31

USB conn x 2

CARD READER

RTS5159

IO Board

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Schematic Block Diagram

Schematic Block Diagram

Schematic Block Diagram

UM3 1C

UM3 1C

UM3 1C

7

PG 26

1 63Thursday, October 15, 2009

1 63Thursday, October 15, 2009

1 63Thursday, October 15, 2009

of

of

of

8

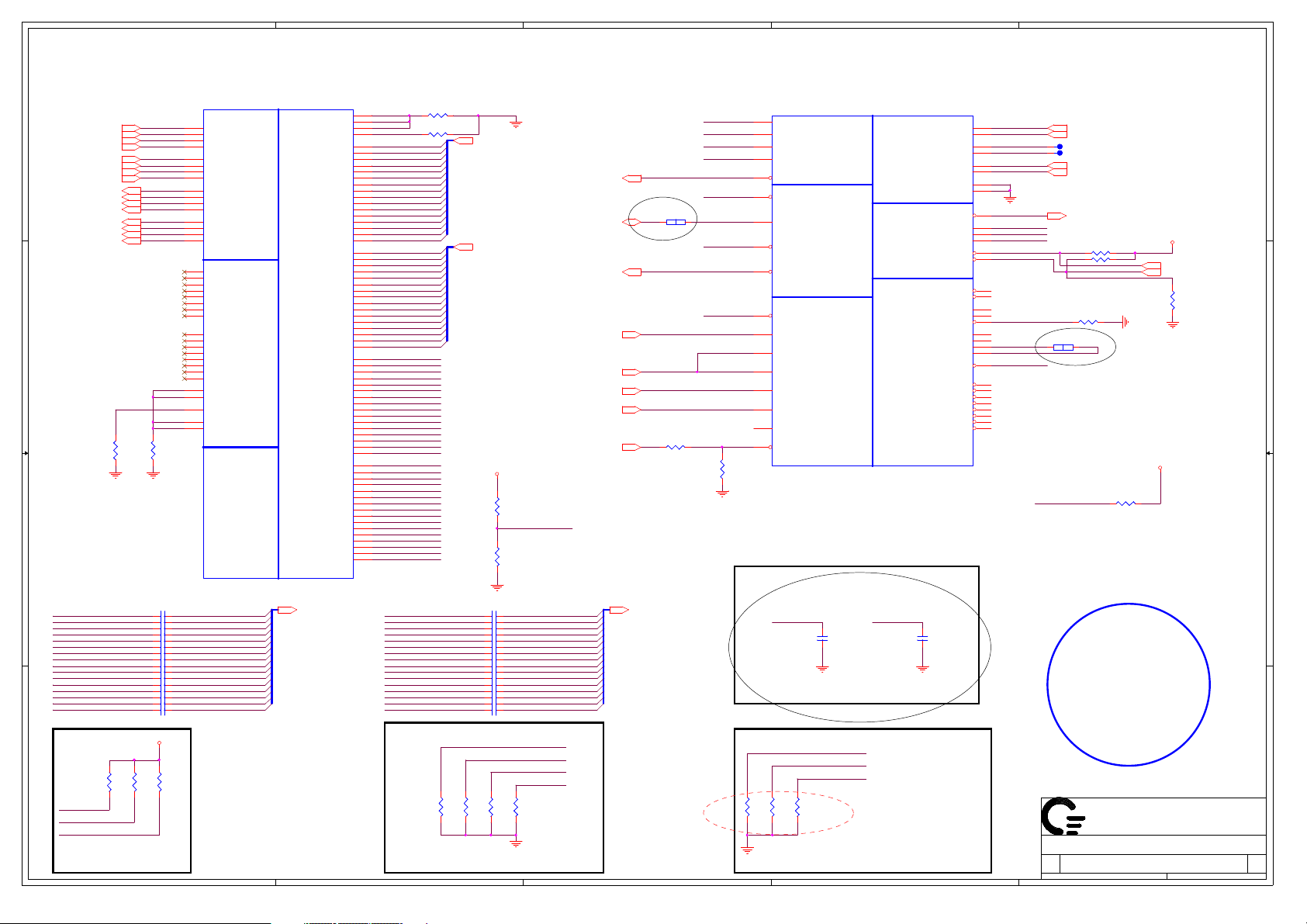

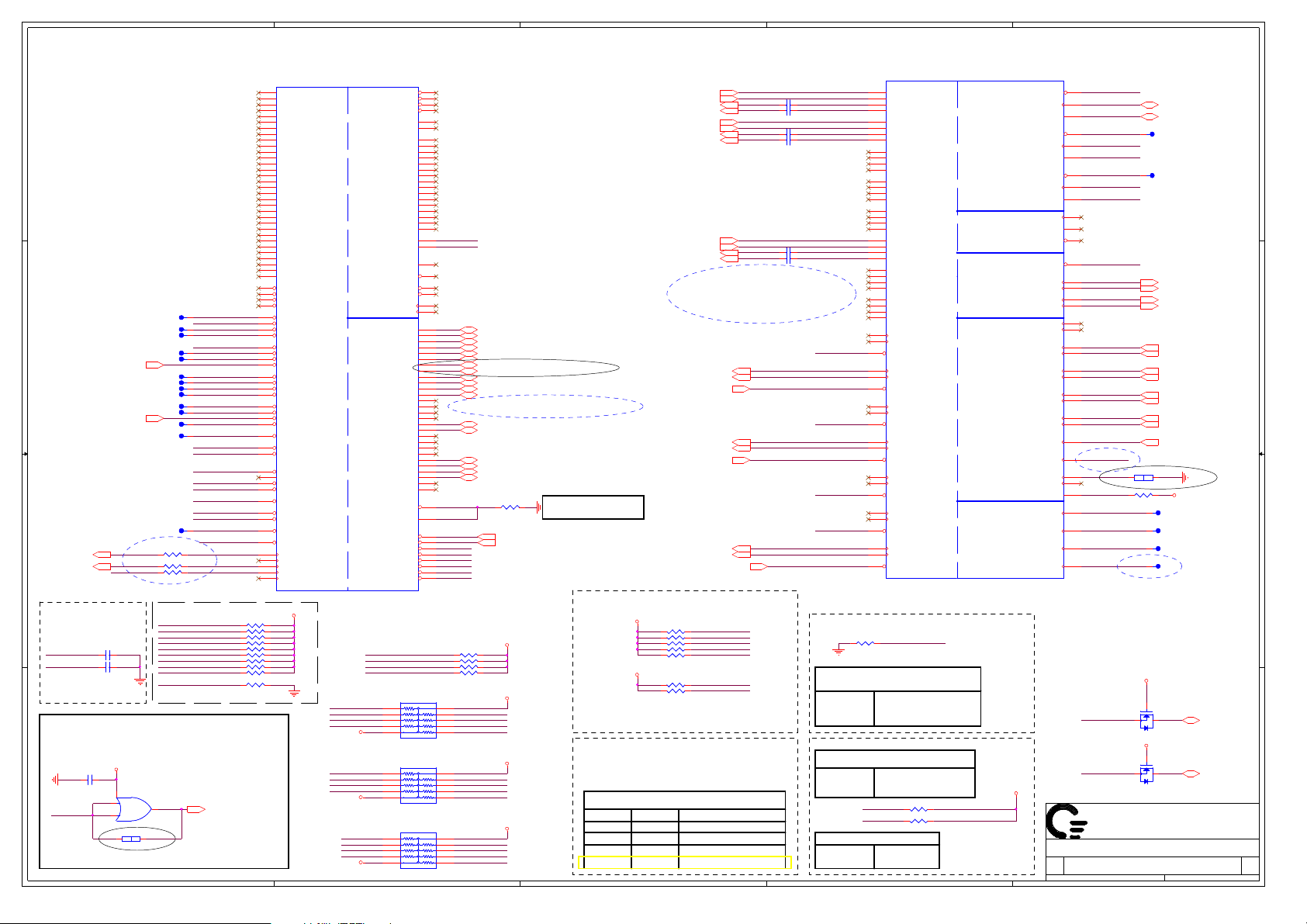

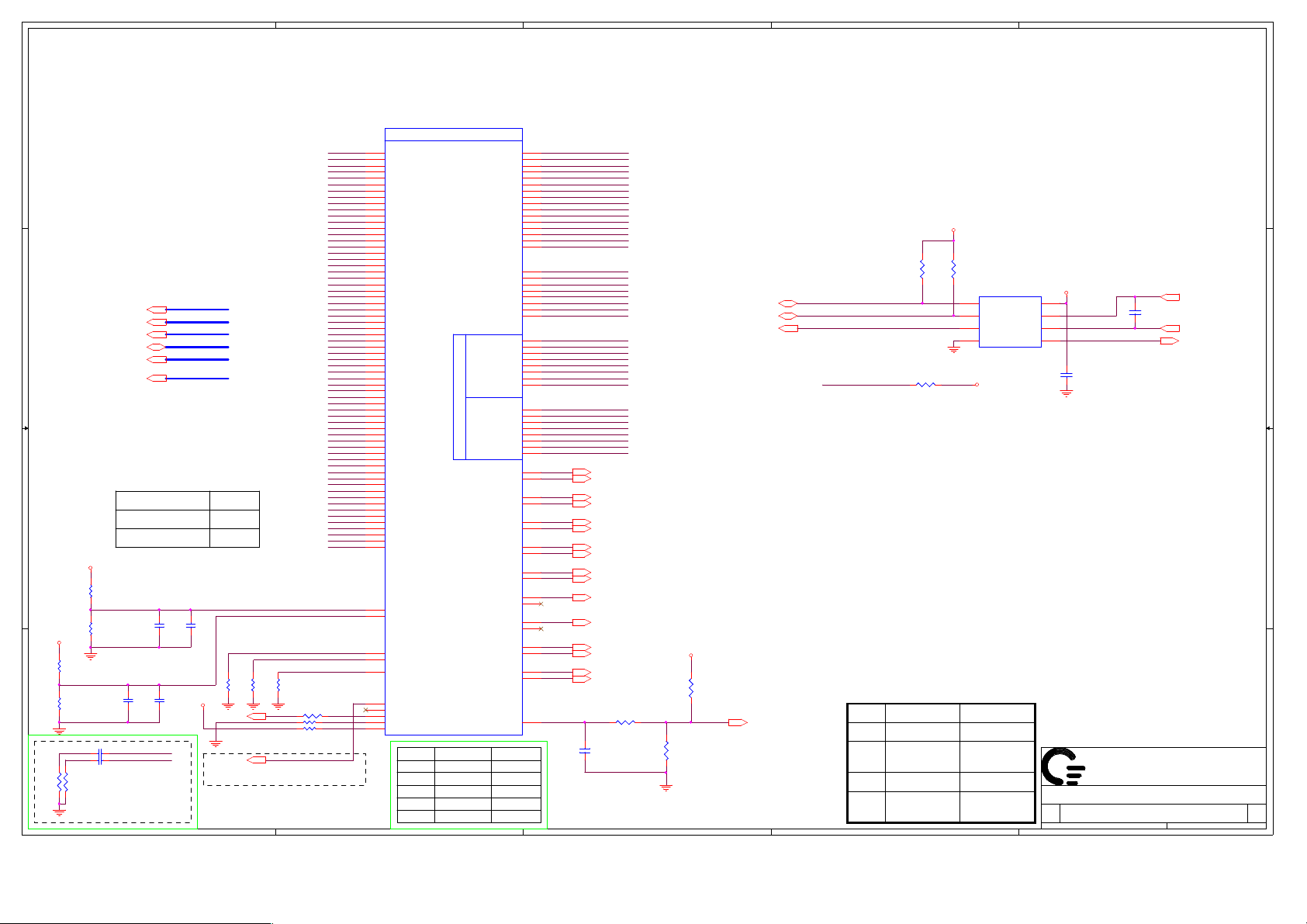

Page 2

1

2

3

4

5

6

7

8

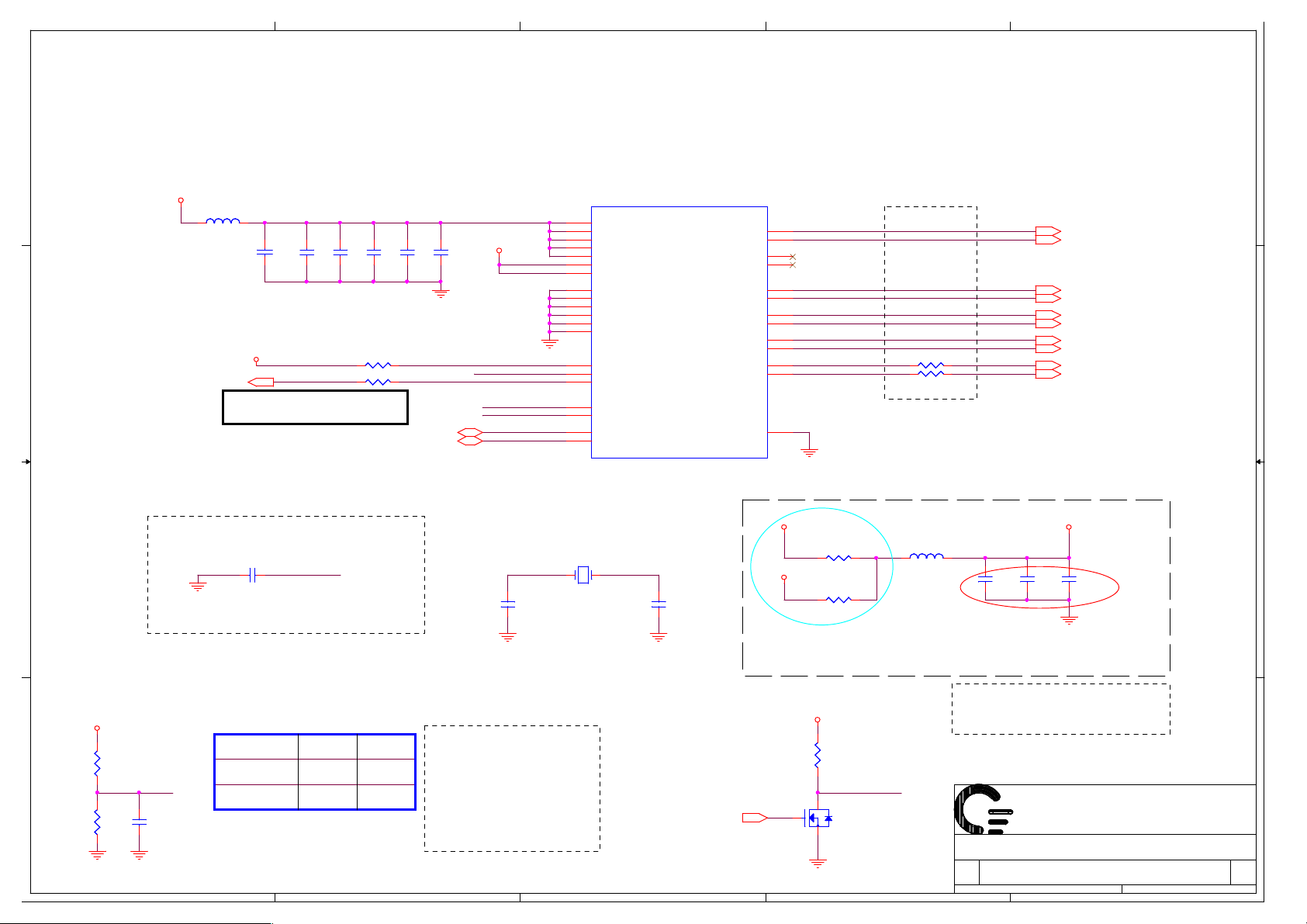

Table of Contents

PAGE DESCRIPTION

Schematic Block Diagram

1

Front Page

2

Clarksfield/Auburndale

A A

B B

3-6

PCH

7-12

13-14

DDRIII SO-DIMM(204P)

Clock Generator

15

M92-S2-XT

16-22

BLANK PAGE

23

LCD CONN / HDMI CONN

24

CRT CONN

25

DB CONN / R5U230

26

BLANK PAGE

27

BLANK PAGE

28

SIO (ITE8502)

29

FLASH / RTC

30

MINI-Card (WWAN)

31

MINI-Card (WLAN\WPAN)

32

Left PUSB/ESATA

33

BLANK PAGE

34

SATA (HDD & CD_ROM)

35

TP / KEYBOARD

36

SWITCH / /LED

37

POWER PLANE

+PW R_SRC

+RTC_CELL

+5V_SUS SLP_S5# CTRLD POW ER

+3.3V_SUS

+1.5V_SUS

+0.75V_DDR_VTT

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.5V_RUN

+1.1V_GFX_PCIE +1.1V

FAN / THERMAL

Azelia CODEC

39

BLANK PAGE

40

41

LAN(RTL8111DL/RJ-45)

System Reset Circuit

42

Blank Page

43

44451.8V_RUN(RT9018/RT9024)

+1.05V_PCH PCH POWER+1.05V 07,08,09,11,15,48 RUN_ON

+VCC_CORE

+LCDVCC

+1.05V_VTT

VOLTAGE PAGE

10V~+19V

+3.0V~+3.3V

+5V

+3.3V

+1.5V

+0.75V

+5V

+3.3V

+1.8V

+1.5V

+0.9V~+1.2V

+0.7V~+1.77V

+3.3V

24,45,46,47,48,49,50,51

08,11,29,30

11,26,33,37,46,48,51,52

07,08,09,10,11,,24,36,37,41,42,44,47,50,52

03,05,13,14,47,50,52

13,14,47

11,18,24,25,35,36,37,38,39,51,52

3,7,8,9,10,11,13,14,15,17,19,24,25,26,29,30

,31,32,35,38,39,41,42,51,52

05,11,44

11,18,19,20,31,32,52

18,21,50+VCC_GFX_CORE VGA POWER

18,50

05,51

24

03,05,10,11,49+1.1V

Power States

DESCRIPTION ACTIVE IN

MAIN POWER

RTC

LARGE POW ER+5V+5V_ALW 37,44,46,47,49,50,53 ALW _ON

CONTROL

SIGNAL

S0~S5

S0~S5

S0~S5

8051 POW ER 3.3V_ALW _ON S0~S5+3.3V 29,30,37,44,45,46,51,52,53+3.3V_ALW

SUS_ON

SLP_S5# CTRLD POW ER

SODIMM POWER

SODIMM POWER

SLP_S3# CTRLD POW ER

SLP_S3# CTRLD POW ER

SDVO POWER

VGA POWER

SUS_ON

SUS_ON

RUN_ON

RUN_ON

RUN_ON

RUN_ON

RUN_ON

GFX_ON

VGA POWER

GFX_+1.1_EN

VGA POWER+1.8V 17,18,21,22,44+1.8V_RUN_GFX GFX_+1.8_EN38

CPU CORE POW ER

LCD Power

CPU POWER

IMVP_VR_ON

LCDVCC_TST_EN

& ENVDD

RUN_ON

Charger (MAX8731)

46

3V/5V (TPS51427A)

47

1.5_DDR/0.75(TPS51116)

48

C C

1.05V_PCH(TPS51218)

1.05_VTT(TPS51218)

49

50

VGA_M92-XT(MAX8792)

51

CPU CORE(MAX17036)

52

Run Power Swi tch

53

DCin & Batt

54

PAD & SCREW

55

EMI CAP

56

SMBUS BLOCK

57

THERMAL MAP

58

Power Block Diagram

Power sequence Block

59

Blank Page

60

GND PLANE PAGE DESCRIPTION

GND

ALL

D D

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

1

2

3

4

5

6

Date: Sheet

COMPUTER

Index & Power Status

Index & Power Status

Index & Power Status

UM3 1A

UM3 1A

UM3 1A

7

of

of

of

2 63Thursday, October 15, 2009

2 63Thursday, October 15, 2009

2 63Thursday, October 15, 2009

8

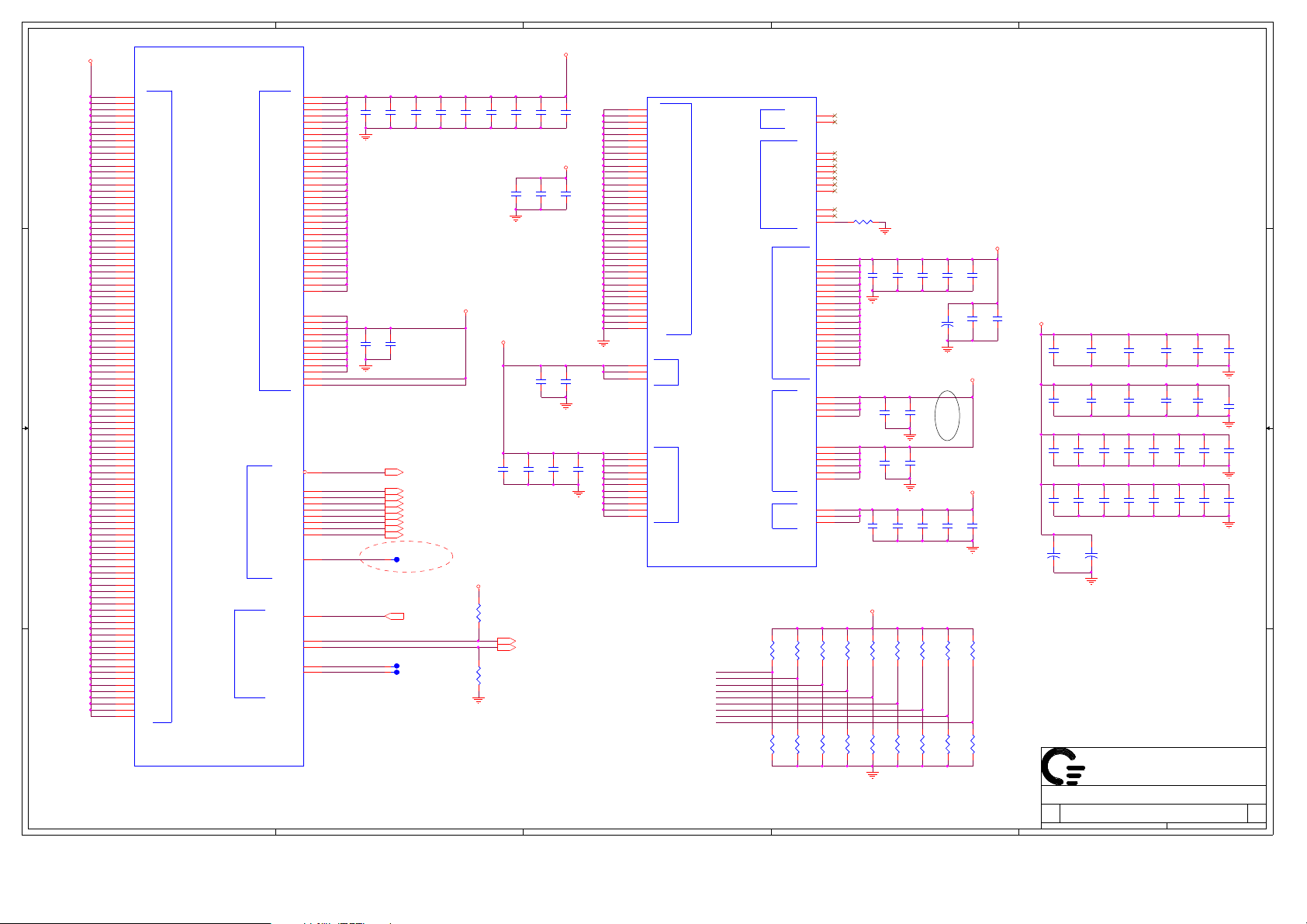

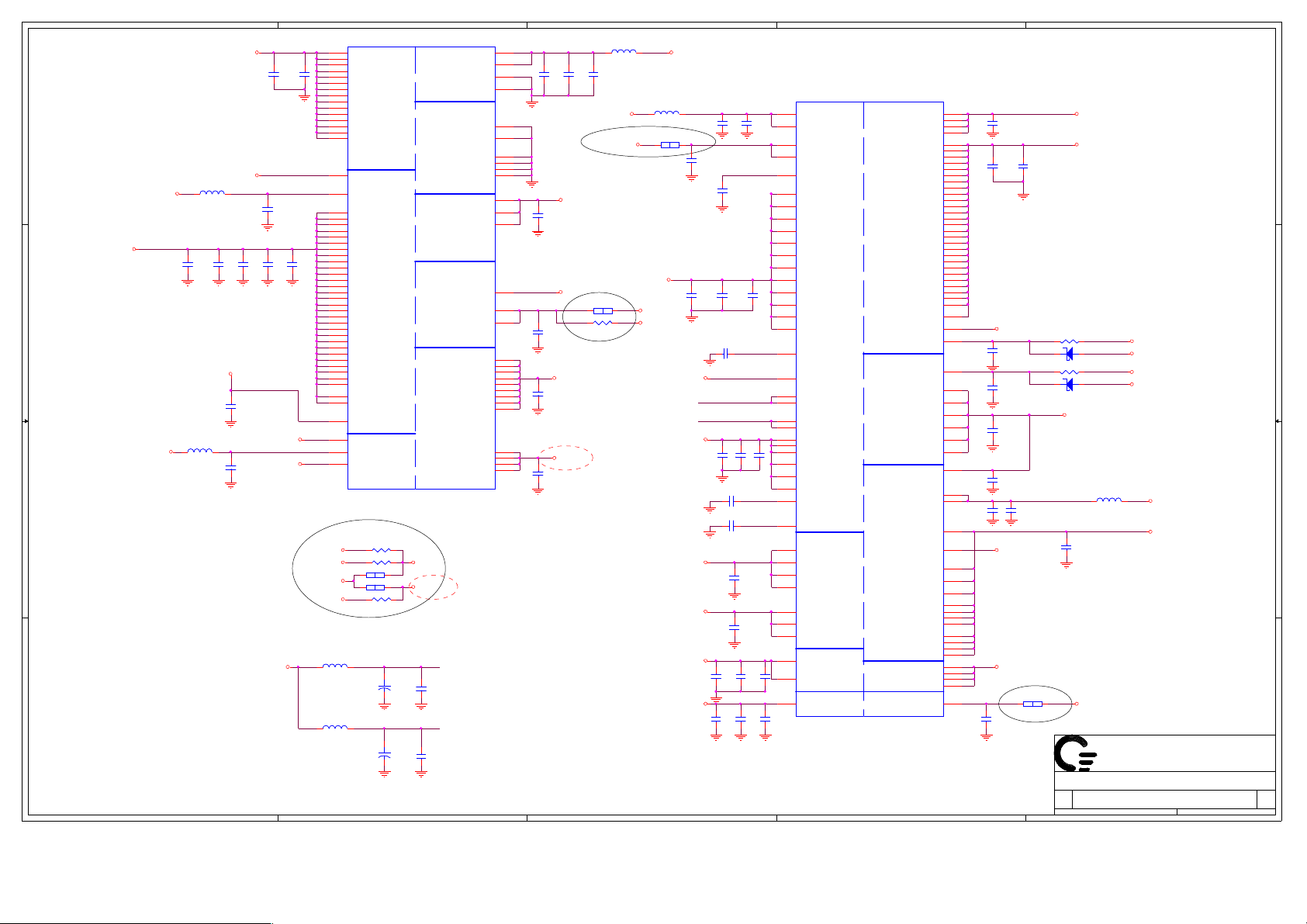

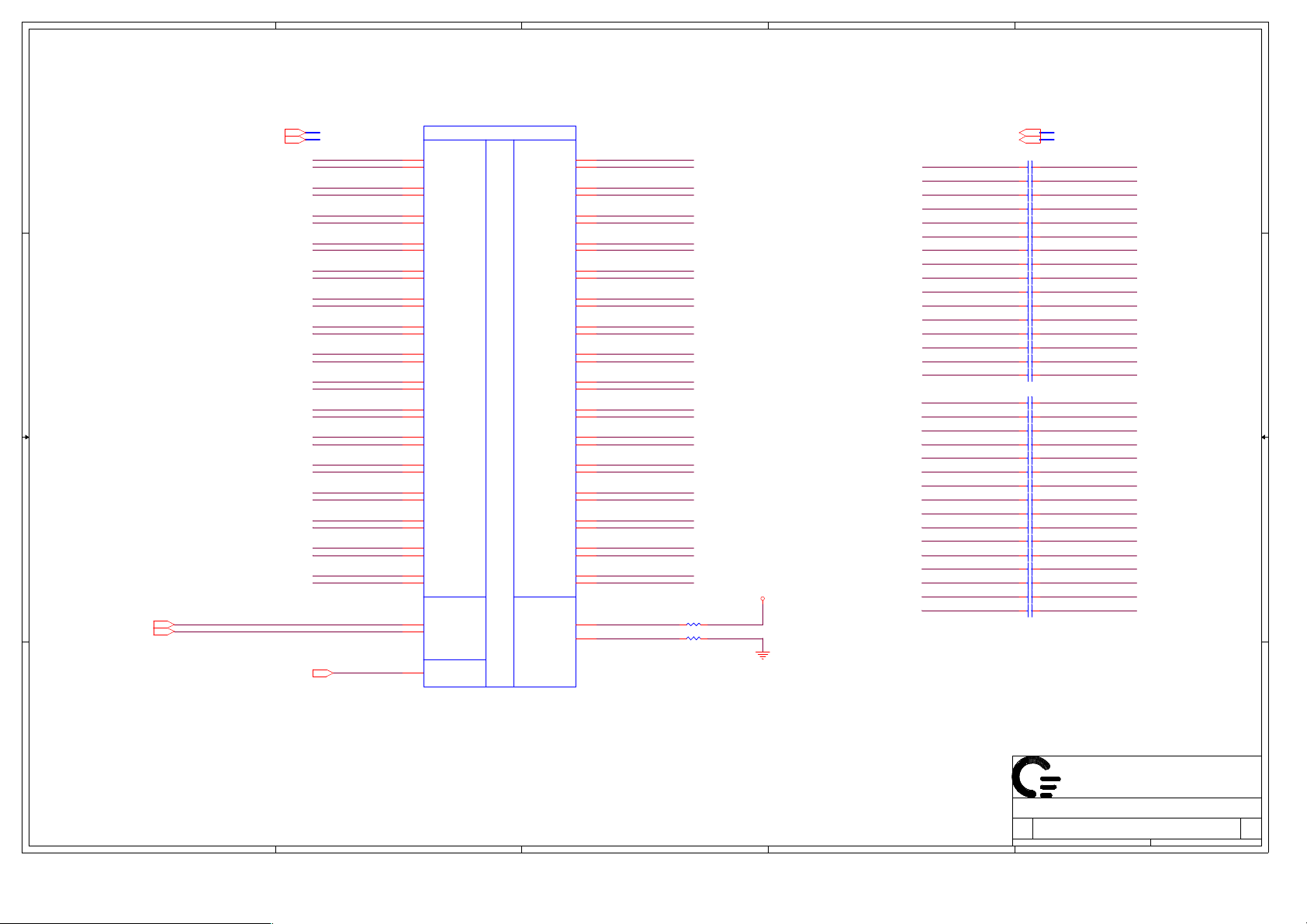

Page 3

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (DMI,PEG,FDI) AUBURNDALE/CLARKSFIELD PROCESSOR (CLK,MISC,JTAG)

U18A

U18A

DMI_TXN0[7]

D D

C C

DMI_TXN1[7]

DMI_TXN2[7]

DMI_TXN3[7]

DMI_TXP0[7]

DMI_TXP1[7]

DMI_TXP2[7]

DMI_TXP3[7]

DMI_RXN0[7]

DMI_RXN1[7]

DMI_RXN2[7]

DMI_RXN3[7]

DMI_RXP0[7 ]

DMI_RXP1[7 ]

DMI_RXP2[7 ]

DMI_RXP3[7 ]

R231KR23

1K

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

R241KR24

1K

0214

B B

Clarksfield /Auburndale

Clarksfield /Auburndale

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_ICOMPI

B26

A26

B27

A25

PCIE_MRX_GTX_N15

K35

PCIE_MRX_GTX_N14

J34

PCIE_MRX_GTX_N13

J33

PCIE_MRX_GTX_N12

G35

PCIE_MRX_GTX_N11

G32

PCIE_MRX_GTX_N10

F34

PCIE_MRX_GTX_N9

F31

PCIE_MRX_GTX_N8

D35

PCIE_MRX_GTX_N7

E33

PCIE_MRX_GTX_N6

C33

PCIE_MRX_GTX_N5

D32

PCIE_MRX_GTX_N4

B32

PCIE_MRX_GTX_N3

C31

PCIE_MRX_GTX_N2

B28

PCIE_MRX_GTX_N1

B30

PCIE_MRX_GTX_N0

A31

PCIE_MRX_GTX_P15

J35

PCIE_MRX_GTX_P14

H34

PCIE_MRX_GTX_P13

H33

PCIE_MRX_GTX_P12

F35

PCIE_MRX_GTX_P11

G33

PCIE_MRX_GTX_P10

E34

PCIE_MRX_GTX_P9

F32

PCIE_MRX_GTX_P8

D34

PCIE_MRX_GTX_P7

F33

PCIE_MRX_GTX_P6

B33

PCIE_MRX_GTX_P5

D31

PCIE_MRX_GTX_P4

A32

PCIE_MRX_GTX_P3

C30

PCIE_MRX_GTX_P2

A28

PCIE_MRX_GTX_P1

B29

PCIE_MRX_GTX_P0

A30

PCIE_MTX_GRX_C_N1 5

L33

PCIE_MTX_GRX_C_N1 4

M35

PCIE_MTX_GRX_C_N1 3

M33

PCIE_MTX_GRX_C_N1 2

M30

PCIE_MTX_GRX_C_N1 1

L31

PCIE_MTX_GRX_C_N1 0

K32

PCIE_MTX_GRX_C_N9

M29

PCIE_MTX_GRX_C_N8

J31

PCIE_MTX_GRX_C_N7

K29

PCIE_MTX_GRX_C_N6

H30

PCIE_MTX_GRX_C_N5

H29

PCIE_MTX_GRX_C_N4

F29

PCIE_MTX_GRX_C_N3

E28

PCIE_MTX_GRX_C_N2

D29

PCIE_MTX_GRX_C_N1

D27

PCIE_MTX_GRX_C_N0

C26

PCIE_MTX_GRX_C_P15

L34

PCIE_MTX_GRX_C_P14

M34

PCIE_MTX_GRX_C_P13

M32

PCIE_MTX_GRX_C_P12

L30

PCIE_MTX_GRX_C_P11

M31

PCIE_MTX_GRX_C_P10

K31

PCIE_MTX_GRX_C_P9

M28

PCIE_MTX_GRX_C_P8

H31

PCIE_MTX_GRX_C_P7

K28

PCIE_MTX_GRX_C_P6

G30

PCIE_MTX_GRX_C_P5

G29

PCIE_MTX_GRX_C_P4

F28

PCIE_MTX_GRX_C_P3

E27

PCIE_MTX_GRX_C_P2

D28

PCIE_MTX_GRX_C_P1

C27

PCIE_MTX_GRX_C_P0

C25

R359 49.9/FR359 49.9/F

R360 750/FR360 750/F

PCIE_MRX_GTX_N[0. .15] [16]

PCIE_MRX_GTX_P[0.. 15] [16]

+1.5V_SUS

R102

R102

1.1K/F

1.1K/F

PM_DRAM_PWRGD

R31

R31

3K/F

3K/F

U18B

0214

U18B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

Clarksfield /Auburndale

Clarksfield /Auburndale

MISC THERMAL

MISC THERMAL

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

SM_DRAMRST#

PM_EXT_TS#[0]

PM_EXT_TS#[1]

MISC

MISC

DDR3

DDR3

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

A16

B16

BCLK_ITP

AR30

BCLK_ITP#

AT30

E16

D16

A18

A17

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

AN15

AP15

AT28

AP27

AN28

TCK

AP28

TMS

XDP_TRST#

AT27

AT29

TDI

AR27

TDO

XDP_TDI_M

AR29

XDP_TDO_M

AP29

DBRESET#

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

CRB use a 1k pull-up to 3.3V_S for DBR#

TRST# use a 51ohm pull down.

R96 SJ_0402R96 SJ_0402

DBRESET#

112

CLK_CPU_BCLK [10]

CLK_CPU_BCLK# [10]

T6T6

T7T7

CLK_PCIE_3G PLL [9]

CLK_PCIE_3G PLL# [9]

DDR3_DRAMRST# [13,14]

R95 10KR95 10K

R94 10KR94 10K

R97 51R97 51

12

12

R93

R93

*12.4K/F_NC

*12.4K/F_NC

2

Intel Suggest to reserve 0 ohm

below for CPU AP29 and AR29 pins.

Add Test Point For XDP

+3.3V_RUN

R99 1KR99 1K

+1.05V_VTT

PM_EXTTS#0 [13]

PM_EXTTS#1 [14]

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_CPUDET#[29 ]

H_CATERR#

R92

H_PECI[10]

H_THERM[10]

PM_SYNC[7]

H_PWRGOOD[10]

PM_DRAM_PWRGD[7]

H_VTTPWRGD[42]

PLTRST#[9,16,29 ,31,32,41]

R92

112

SJ_0402

SJ_0402

R101 1.5K/FR101 1.5K/F

2

H_PROCHOT#

H_CPURST#

PM_DRAM_PWRGD

R100

R100

750/F

750/F

H_PECI_ISO

PCIE_MTX_GRX_N[0. .15] [16] PCIE_MTX_GRX_P[0.. 15] [16]

PCIE_MTX_GRX_C_P0

PCIE_MTX_GRX_C_P1

PCIE_MTX_GRX_C_P2

PCIE_MTX_GRX_C_P3

PCIE_MTX_GRX_C_P4

PCIE_MTX_GRX_C_P5

PCIE_MTX_GRX_C_P6

PCIE_MTX_GRX_C_P7

PCIE_MTX_GRX_C_P8

PCIE_MTX_GRX_C_P9

PCIE_MTX_GRX_C_P10

PCIE_MTX_GRX_C_P11

PCIE_MTX_GRX_C_P12

PCIE_MTX_GRX_C_P13

PCIE_MTX_GRX_C_P14

PCIE_MTX_GRX_C_P15

C508 0.1U16 C508 0.1U16

C510 0.1U16 C510 0.1U16

C511 0.1U16 C511 0.1U16

C512 0.1U16 C512 0.1U16

C515 0.1U16 C515 0.1U16

C516 0.1U16 C516 0.1U16

C519 0.1U16 C519 0.1U16

C520 0.1U16 C520 0.1U16

C523 0.1U16 C523 0.1U16

C524 0.1U16 C524 0.1U16

C527 0.1U16 C527 0.1U16

C529 0.1U16 C529 0.1U16

C536 0.1U16 C536 0.1U16

C538 0.1U16 C538 0.1U16

C542 0.1U16 C542 0.1U16

C544 0.1U16 C544 0.1U16

Processo r Compensation Signals DDR3 Comp ensation Signals

R25

R25

R73

R73

49.9/F

49.9/F

49.9/F

49.9/F

4

R74

R74

20/F

20/F

PCIE_MTX_GRX_P0

PCIE_MTX_GRX_P1

PCIE_MTX_GRX_P2

PCIE_MTX_GRX_P3

PCIE_MTX_GRX_P4

PCIE_MTX_GRX_P5

PCIE_MTX_GRX_P6

PCIE_MTX_GRX_P7

PCIE_MTX_GRX_P8

PCIE_MTX_GRX_P9

PCIE_MTX_GRX_P10

PCIE_MTX_GRX_P11

PCIE_MTX_GRX_P12

PCIE_MTX_GRX_P13

PCIE_MTX_GRX_P14

PCIE_MTX_GRX_P15

H_COMP0

H_COMP1

H_COMP2

H_COMP3

R75

R75

20/F

20/F

3

DDR3_DRAMRST# H_PWRGOOD

R27

R27

R28

R28

24.9/F

24.9/F

130/F

130/F

R33

R33

100/F

100/F

C654

C654

0.01U

0.01U

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

Layout Note: Place

these resistors

near Processor

C655

C655

0.01U

0.01U

Remove XDP Function

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

COMPUTER

AUBURNDA 1/4

AUBURNDA 1/4

AUBURNDA 1/4

UM3 1A

UM3 1A

UM3 1A

1

of

of

of

3 63Thursday, October 15 , 2009

3 63Thursday, October 15 , 2009

3 63Thursday, October 15 , 2009

R82

R82

*68_NC

*68_NC

PCIE_MTX_GRX_N0

PCIE_MTX_GRX_N1

PCIE_MTX_GRX_N2

PCIE_MTX_GRX_N3

PCIE_MTX_GRX_N4

PCIE_MTX_GRX_N5

PCIE_MTX_GRX_N6

PCIE_MTX_GRX_N7

PCIE_MTX_GRX_N8

PCIE_MTX_GRX_N9

PCIE_MTX_GRX_N10

PCIE_MTX_GRX_N11

PCIE_MTX_GRX_N12

PCIE_MTX_GRX_N13

PCIE_MTX_GRX_N14

PCIE_MTX_GRX_N15

PCIE_MTX_GRX_C_N0

PCIE_MTX_GRX_C_N1

PCIE_MTX_GRX_C_N2

PCIE_MTX_GRX_C_N3

PCIE_MTX_GRX_C_N4

PCIE_MTX_GRX_C_N5

PCIE_MTX_GRX_C_N6

PCIE_MTX_GRX_C_N7

PCIE_MTX_GRX_C_N8

PCIE_MTX_GRX_C_N9

PCIE_MTX_GRX_C_N1 0

PCIE_MTX_GRX_C_N1 1

PCIE_MTX_GRX_C_N1 2

PCIE_MTX_GRX_C_N1 3

PCIE_MTX_GRX_C_N1 4

PCIE_MTX_GRX_C_N1 5

Processo r

Pullups

A A

H_CATERR#

H_PROCHOT#

H_CPURST#

R32

R32

49.9/F

49.9/F

C507 0.1U16 C507 0.1U16

C509 0.1U16 C509 0.1U16

C513 0.1U16 C513 0.1U16

C514 0.1U16 C514 0.1U16

C517 0.1U16 C517 0.1U16

C518 0.1U16 C518 0.1U16

C521 0.1U16 C521 0.1U16

C522 0.1U16 C522 0.1U16

C525 0.1U16 C525 0.1U16

C526 0.1U16 C526 0.1U16

C534 0.1U16 C534 0.1U16

C535 0.1U16 C535 0.1U16

C539 0.1U16 C539 0.1U16

C541 0.1U16 C541 0.1U16

C546 0.1U16 C546 0.1U16

C547 0.1U16 C547 0.1U16

+1.05V_VTT

R81

R81

49.9/F

49.9/F

5

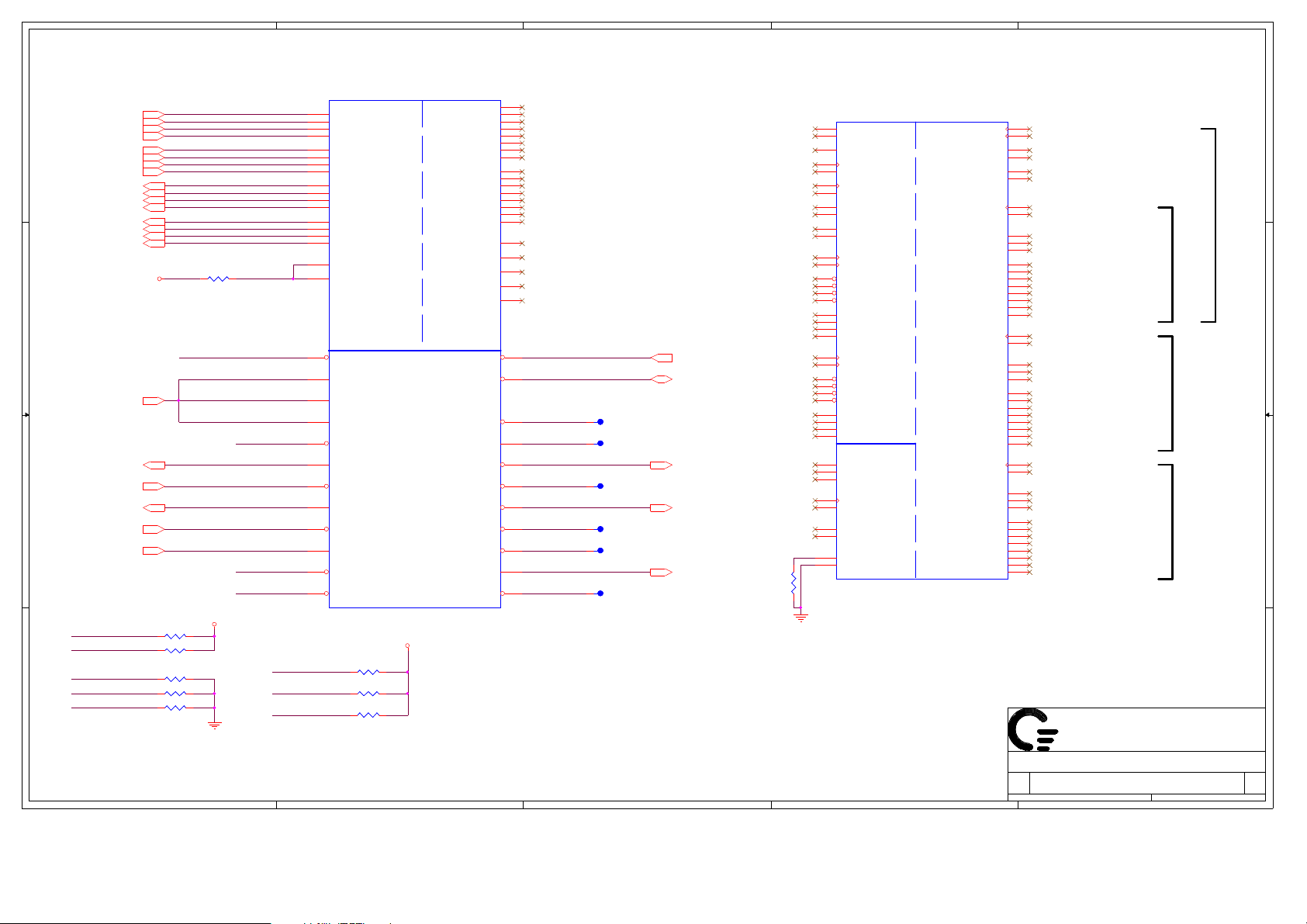

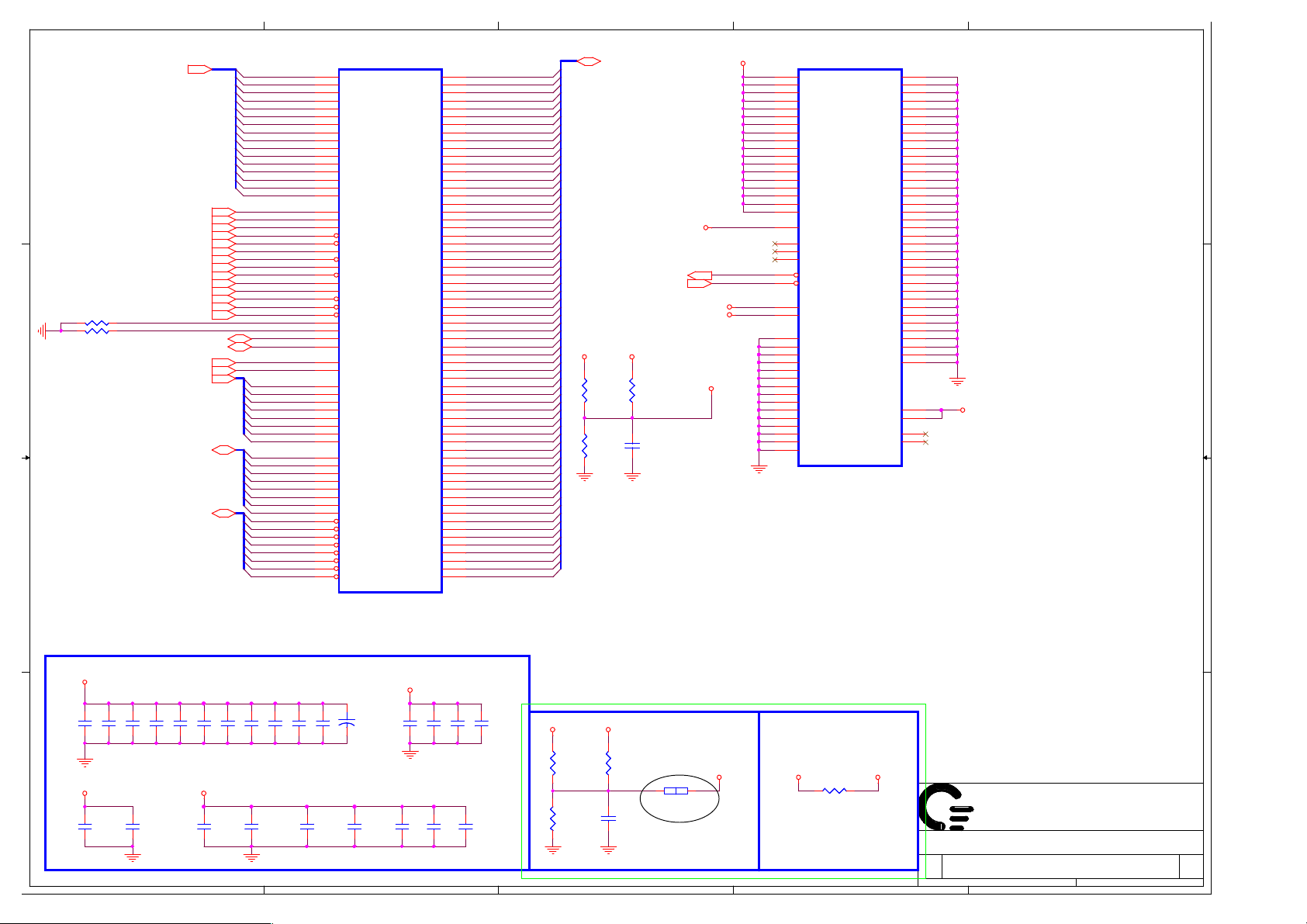

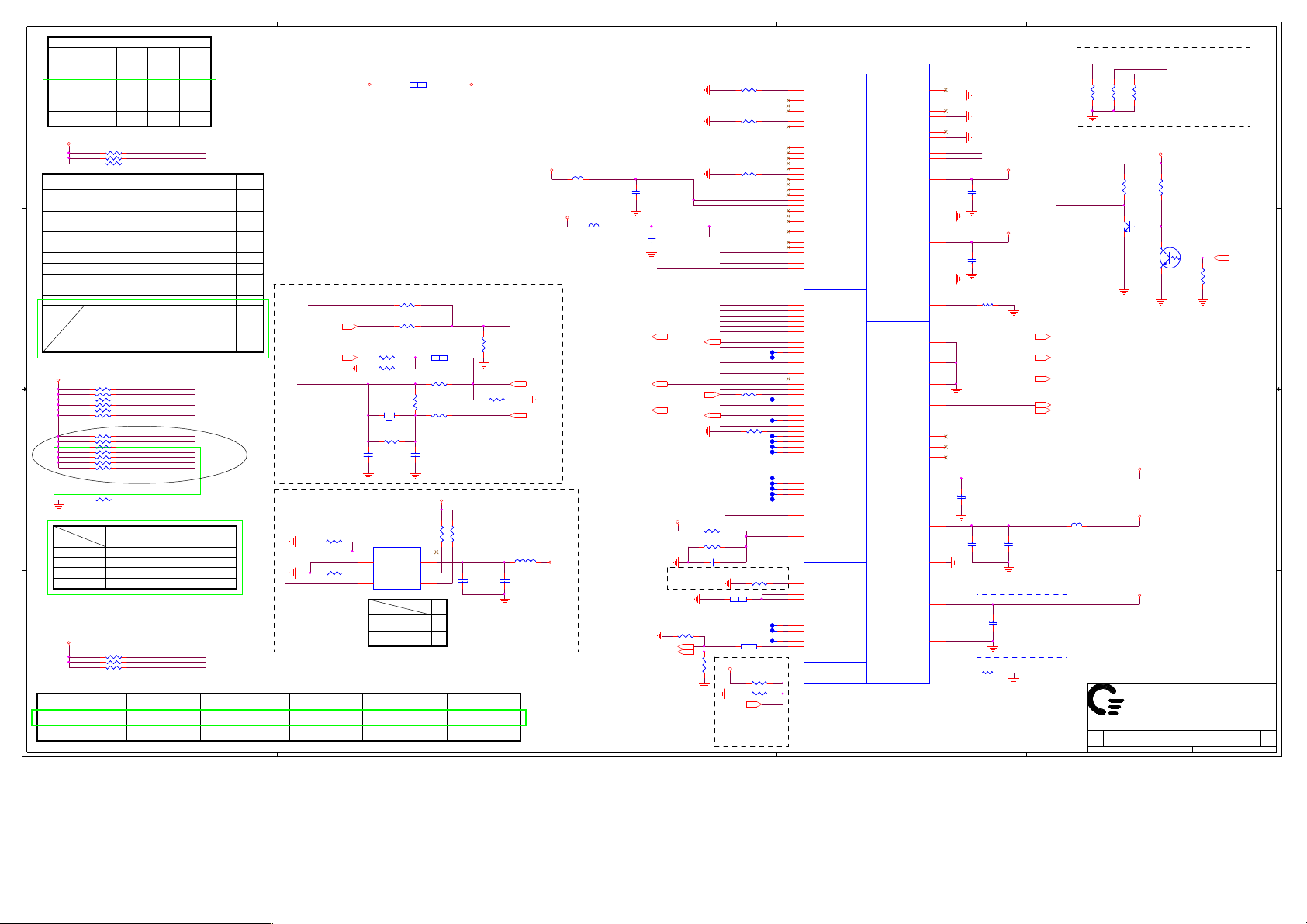

Page 4

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (DDR3)

U18D

AM6

AN2

AM4

AM3

AN5

AN6

AN4

AN3

AN7

AR10

AT10

AF3

AG1

AK1

AG4

AG3

AH4

AK3

AK4

AK5

AK2

AP3

AT4

AT5

AT6

AP6

AP8

AT9

AT7

AP9

AB1

AC5

AC6

AJ3

AJ4

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

M1

K5

K4

M4

N5

W5

R7

Y7

U18D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

W8

SB_CK[0]

W9

SB_CK#[0]

M3

SB_CKE[0]

V7

SB_CK[1]

V6

SB_CK#[1]

M2

SB_CKE[1]

AB8

SB_CS#[0]

AD6

SB_CS#[1]

AC7

SB_ODT[0]

AD1

SB_ODT[1]

M_B_DM0

D4

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLK0 [14]

M_B_CLK0# [14]

M_B_CKE0 [14]

M_B_CLK1 [14]

M_B_CLK1# [14]

M_B_CKE1 [14]

M_B_CS0# [14]

M_B_CS1# [14]

M_B_ODT0 [14]

M_B_ODT1 [14]

M_B_DM[7:0] [14]

M_B_DQS#[7:0] [14]

M_B_DQS[7:0] [14]

M_B_A[15:0] [14]

U18C

U18C

AA6

SA_CK[0]

D D

M_A_DQ[63:0][13]

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS0[13]

M_A_BS1[13]

M_A_BS2[13]

M_A_CAS#[13]

M_A_RAS#[13]

M_A_WE#[13]

C10

B10

D10

E10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

F10

J10

AJ7

AJ6

AJ9

AL7

AL8

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

J8

G7

J7

L7

M6

M8

L9

L6

K8

N8

P9

U7

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLK0 [13]

M_A_CLK0# [13]

M_A_CKE0 [13]

M_A_CLK1 [13]

M_A_CLK1# [13]

M_A_CKE1 [13]

M_A_CS0# [13]

M_A_CS1# [13]

M_A_ODT0 [13]

M_A_ODT1 [13]

M_A_DM[7:0] [13]

M_A_DQS#[7:0] [13]

M_A_DQS[7:0] [13]

M_A_A[15:0] [13]

M_B_DQ[63:0][14]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60M_A_A0

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS0[14]

M_B_BS1[14]

M_B_BS2[14]

M_B_CAS#[14]

M_B_RAS#[14]

M_B_WE#[14]

Clarksfield/Auburndale

A A

5

Clarksfield/Auburndale

Channel A DQ[15,32,48,54], DM[5]

Requires minimum 12mils spacing

with all other signals, including data signals.

4

Clarksfield/Auburndale

Clarksfield/Auburndale

Channel B DQ[16,18,36,42,56,57,60,61,62]

Requires minimum 12mils spacing

with all other signals, including data signals.

3

2

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

AUBURNDA 2/4

AUBURNDA 2/4

AUBURNDA 2/4

UM3 1A

UM3 1A

UM3 1A

1

of

of

of

4 63Thursday, October 15, 2009

4 63Thursday, October 15, 2009

4 63Thursday, October 15, 2009

Page 5

5

U18F

CPU Core Power

+VCC_CORE

D D

C C

B B

A A

U18F

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

Clarksfield /Auburndale

Clarksfield /Auburndale

AH14

VTT0_1

AH12

VTT0_2

AH11

VTT0_3

AH10

VTT0_4

J14

VTT0_5

J13

VTT0_6

H14

VTT0_7

H12

VTT0_8

G14

VTT0_9

G13

VTT0_10

G12

VTT0_11

G11

VTT0_12

F14

VTT0_13

F13

VTT0_14

F12

VTT0_15

F11

VTT0_16

E14

VTT0_17

E12

VTT0_18

D14

VTT0_19

D13

VTT0_20

D12

VTT0_21

D11

VTT0_22

C14

VTT0_23

C13

VTT0_24

C12

VTT0_25

C11

VTT0_26

B14

VTT0_27

B12

VTT0_28

A14

VTT0_29

A13

VTT0_30

A12

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

PSI#

VID0

AK35

VID1

AK33

VID2

AK34

VID3

AL35

VID4

AL33

VID5

AM33

VID6

AM35

DPRSLPVR

AM34

G15

VTT_SELECT:

High level 1.05V for Auburndale

Low level 1.1V for Clarksfield

AN35

AJ34

AJ35

VTT_SENSE

B15

TP_VSS_SENSE_VTT

A15

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

AUBURNDALE/CLARKSFIELD PROCESSOR (POWER)

5

C559

C559

*10U_NC

*10U_NC

C531

C531

22U

22U

4

C85

C85

10U

10U

C505

C505

22U

22U

H_PSI# [51]

VID0 [51]

VID1 [51]

VID2 [51]

VID3 [51]

VID4 [51]

VID5 [51]

VID6 [51]

DPRSLPVR [51]

T1T1

I_MON [51]

T47T47

T46T46

4

C94

C94

*10U_NC

*10U_NC

C64

C64

*10U_NC

*10U_NC

+1.05V_VTT

C506

C506

10U

10U

C32

C32

10U

10U

+1.05V_VTT

+VCC_CORE

R383

R383

100/F

100/F

R384

R384

100/F

100/F

C30

C30

10U

10U

C503

C503

22U

22U

C549

C549

*22U_NC

*22U_NC

VCCSENSE [5 1]

VSSSENSE [51]

C555

C555

22U

22U

+1.05V_VTT

C533

C533

*10U_NC

*10U_NC

+1.05V_VTT

C504

C504

22U

22U

C562

C562

22U

22U

C31

C31

22U

22U

C532

C532

*10U_NC

*10U_NC

C530

C530

*22U_NC

*22U_NC

C101

C101

22U

22U

C545

C545

22U

22U

3

2

AUBURNDALE/CLARKSFIELD PROCESSOR (GRAPHICS POWER)

U18G

U18G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

Clarksfield /Auburndale

Clarksfield /Auburndale

3

VSSAXG_SENSE

LINES

LINES

SENSE

SENSE

GRAPHICS

GRAPHICS

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

VID0

VID1

VID2

VID3

VID4

VID5

VID6

DPRSLPVR

H_PSI#

VAXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

R291KR29

1K

R34

R34

*1K_NC

*1K_NC

R621KR62

1K

R390

R390

*1K_NC

*1K_NC

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

R391KR39

1K

R40

R40

*1K_NC

*1K_NC

R98 1K/FR98 1K/F

+1.05V_VTT

R59

R59

*1K_NC

*1K_NC

R3931KR393

1K

Pop it when Arrandale Graphics disable.

+1.5V_SUS

C60

C60

10U

10U

C540

C540

*22U_NC

*22U_NC

C721UC72

1U

C56

C56

2.2U

2.2U

R387

R387

*1K_NC

*1K_NC

R3851KR385

1K

C781UC78

1U

+

+

C106

C106

330U

330U

7343

7343

2.5

2.5

+1.05V_VTT

+1.8V_RUN

C57

C57

4.7U/6.3 V

4.7U/6.3 V

R3891KR389

1K

R388

R388

*1K_NC

*1K_NC

C471UC47

1U

C95

C95

22U

22U

C528

C528

22U

22U

R50

R50

*1K_NC

*1K_NC

R3911KR391

1K

C651UC65

1U

C541UC54

1U

R53

R53

*1K_NC

*1K_NC

R3821KR382

1K

C77

C77

*10U_NC

*10U_NC

C33

C33

22U

22U

2

C551UC55

1U

C531UC53

1U

R521KR52

1K

R55

R55

*1K_NC

*1K_NC

C87

C87

22U

22U

1

+VCC_CORE

C68

C68

22U

22U

C560

C560

*22U_NC

*22U_NC

C89

C89

C125

C125

10U

10U

10U

10U

C105

C105

C63

C63

10U

10U

10U

10U

+

+

C208

C208

*470U_NC

*470U_NC

Title

Title

Title

AUBURNDA 3/4

AUBURNDA 3/4

AUBURNDA 3/4

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

UM3 1A

UM3 1A

UM3 1A

Date: Sheet

Date: Sheet

Date: Sheet

C552

C552

C568

C568

*22U_NC

*22U_NC

*22U_NC

*22U_NC

C93

C93

C537

C537

22U

22U

22U

22U

C59

C59

C100

C100

10U

10U

10U

10U

C580

C580

C84

C84

*10U_NC

*10U_NC

*10U_NC

*10U_NC

+

+

C567

C567

*470U_NC

*470U_NC

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

C111

C111

C556

C556

22U

22U

*22U_NC

*22U_NC

C128

C128

C76

C76

22U

22U

22U

22U

C554

C554

C97

C97

10U

10U

10U

10U

C79

C79

C550

C550

10U

10U

10U

10U

5 63Thursday, October 15 , 2009

5 63Thursday, October 15 , 2009

1

5 63Thursday, October 15 , 2009

C561

C561

10U

10U

C115

C115

10U

10U

C575

C575

*22U_NC

*22U_NC

C548

C548

22U

22U

C558

C558

*10U_NC

*10U_NC

C543

C543

*10U_NC

*10U_NC

of

of

of

Page 6

5

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (GND) AUBURNDALE/CLARKSFIELD PROCESSOR( RESERVED, CFG)

U18H

U18H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

VSS8

AR17

D D

C C

B B

VSS9

AR15

VSS10

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

VSS28

AM25

VSS29

AM20

VSS30

AM17

VSS31

AM14

VSS32

AM11

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

AL34

VSS37

AL31

VSS38

AL23

VSS39

AL20

VSS40

AL17

VSS41

AL12

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

AK29

VSS46

AK27

VSS47

AK25

VSS48

AK20

VSS49

AK17

VSS50

AJ31

VSS51

AJ23

VSS52

AJ20

VSS53

AJ17

VSS54

AJ14

VSS55

AJ11

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

AH35

VSS60

AH34

VSS61

AH33

VSS62

AH32

VSS63

AH31

VSS64

AH30

VSS65

AH29

VSS66

AH28

VSS67

AH27

VSS68

AH26

VSS69

AH20

VSS70

AH17

VSS71

AH13

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

AG10

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

AE35

VSS80

Clarksfield/Auburndale

Clarksfield/Auburndale

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

U18I

U18I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

Clarksfield/Auburndale

Clarksfield/Auburndale

VSS

VSS

U18E

U18E

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

CFG0

CFG3

CFG4

CFG7

J17

SA_DIMM_VREF

H17

SB_DIMM_VREF

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]

AN30

CFG[12]

AN32

CFG[13]

AJ32

CFG[14]

AJ29

CFG[15]

AJ30

CFG[16]

AK30

CFG[17]

H16

RSVD_TP_86

B19

RSVD15

A19

RSVD16

A20

RSVD17

B20

RSVD18

U9

RSVD19

T9

RSVD20

AC9

RSVD21

AB9

RSVD22

C1

RSVD_NCTF_23

A3

RSVD_NCTF_24

J29

RSVD26

J28

RSVD27

A34

RSVD_NCTF_28

A33

RSVD_NCTF_29

C35

RSVD_NCTF_30

B35

RSVD_NCTF_31

Clarksfield/Auburndale

Clarksfield/Auburndale

+M_VREF_DQ_DIMM0

+M_VREF_DQ_DIMM1

T3T3

T2T2

T5T5

AT35

VSS_NCTF1

AT1

VSS_NCTF2

AR34

VSS_NCTF3

B34

VSS_NCTF4

B2

VSS_NCTF5

B1

VSS_NCTF6

A35

VSS_NCTF7

NCTF

NCTF

No need to pull down RSVD17, 18, 64, & 65,

these resistors are for intel internal test only.

RESERVED

RESERVED

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

RSVD_TP_59

RSVD_TP_60

KEY

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

VSS

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

D15

C15

AJ15

AH15

No need to pull down RSVD17, 18, 64, & 65,

these resistors are for intel internal test only.

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

2

1

2

1

R394

R394

SJ_0402

SJ_0402

Can be left NC is Intel CRM

implementation; ESD/DG

recommendation to GND

1 0

CFG4

A A

The Clarkfield processor's PCI Express interface may

not meet PCI Express 2.0 jitter specifications. Intel

recommends placing a 3.01K +/- 5% pull down resistor to

VSS on CFG[7] pin for both rPGA and BGA components.

This pull down resistor should be removed when this

issue is fixed.

5

CFG3

4

R37 3.01K/FR37 3.01K/F

(Display Port

Presence)

CFG0

(PCI-Epress

Configuration Select)

CFG3

(PCI-Epress Static

Lane Reversal)

Disabled; No Physical Display Port

attached to Embedd ed Diplay Port

Single PEG

Normal Operation Lane Numbers Reversed

3

Enabled; An external Display port

device is connected to the Embedded

Display port

Bifurcation enabled

2

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: S heet

Date: S heet

Date: S heet

COMPUTER

AUBURNDA 4/4

AUBURNDA 4/4

AUBURNDA 4/4

UM3 1A

UM3 1A

UM3 1A

1

of

of

of

6 63Thursday, October 15, 2009

6 63Thursday, October 15, 2009

6 63Thursday, October 15, 2009

Page 7

5

4

3

2

1

IBEX PEAK-M (DMI,FDI,GPIO)

U23C

U23C

PM_RI#

PM_BATLOW#

PCIE_WAKE#

BC24

DMI0RXN

BJ22

DMI1RXN

AW20

DMI2RXN

BJ20

DMI3RXN

BD24

DMI0RXP

BG22

DMI1RXP

BA20

DMI2RXP

BG20

DMI3RXP

BE22

DMI0TXN

BF21

DMI1TXN

BD20

DMI2TXN

BE18

DMI3TXN

BD22

DMI0TXP

BH21

DMI1TXP

BC20

DMI2TXP

BD18

DMI3TXP

BH25

DMI_ZCOMP

BF25

DMI_IRCOMP

T6

SYS_RESET#

M6

SYS_PWROK

B17

PWROK

K5

MEPWROK

A10

LAN_RST#

D9

DRAMPWROK

C16

RSMRST#

M1

SUS_PWR_DN_ACK / GPIO30

P5

PWRBTN#

P7

ACPRESENT / GPIO31

A6

BATLOW# / GPIO72

F14

RI#

IbexPeak-M_QMGS

IbexPeak-M_QMGS

R182 10K/FR182 10K/F

R153 8.2K/FR153 8.2K/F

R248 1KR248 1K

System Power Management

System Power Management

+3.3V_SUS

4

DMI

FDI

DMI

FDI

CLKRUN# / GPIO32

SUS_STAT# / GPIO61

SUSCLK / GPIO62

SLP_S5# / GPIO63

SLP_LAN# / GPIO29

DMI_RXN0[3]

PCH_PWRGD[29,38]

PM_DRAM_PWRGD[3]

ICH_RSMRST#[29]

SUS_PWR_ACK[29]

SIO_PWRBTN#[29]

AC_PRESENT[29]

CLKRUN#

XDP_DBRESET#

PCH_PWRGD

ICH_RSMRST#

LAN_RST#

DMI_RXN1[3]

DMI_RXN2[3]

DMI_RXN3[3]

DMI_RXP0[3]

DMI_RXP1[3]

DMI_RXP2[3]

DMI_RXP3[3]

DMI_TXN0[3]

DMI_TXN1[3]

DMI_TXN2[3]

DMI_TXN3[3]

DMI_TXP0[3]

DMI_TXP1[3]

DMI_TXP2[3]

DMI_TXP3[3]

+1.05V_PCH

R415 49.9/FR415 49.9/F

XDP_DBRESET#

+3.3V_RUN

R113 8.2K/FR113 8 .2K/F

R118 10K/FR118 10K/F

R237 10K/FR237 10K/F

R196 10K/FR196 10K/F

R178 10K/FR178 10K/F

5

DMI_ZCOMP

LAN_RST#

ICH_RSMRST#

PM_BATLOW#

PM_RI#

D D

C C

B B

A A

FDI_RXN0

FDI_RXN1

FDI_RXN2

FDI_RXN3

FDI_RXN4

FDI_RXN5

FDI_RXN6

FDI_RXN7

FDI_RXP0

FDI_RXP1

FDI_RXP2

FDI_RXP3

FDI_RXP4

FDI_RXP5

FDI_RXP6

FDI_RXP7

FDI_INT

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

WAKE#

SLP_S4#

SLP_S3#

SLP_M#

TP23

PMSYNCH

BA18

BH17

BD16

BJ16

BA16

BE14

BA14

BC12

BB18

BF17

BC16

BG16

AW16

BD14

BB14

BD12

BJ14

BF13

BH13

BJ12

BG14

J12

Y1

P8

F3

E4

H7

P12

K8

N2

BJ10

F6

PCIE_WAKE#

CLKRUN#

RSV_LPCPD#

ICH_SUSCLK

SIO_SLP_S5#

SLP_S4#_R

SIO_SLP_S3#

SLP_M#_R

PM_SLP_LAN#_R

PCIE_WAKE# [41]

CLKRUN# [29]

T23T23

T17T17

SIO_SLP_S5# [29]

T20T20

SIO_SLP_S3# [29]

T21T21

T61T61

PM_SYNC [3]

T16T16

3

R2631KR263

1K

IBEX PEAK-M (LVDS,DDI)

U23D

U23D

AB48

AB46

AP39

AP41

AT43

AT42

AV53

AV51

BB47

BA52

AY48

AV47

BB48

BA50

AY49

AV48

AP48

AP47

AY53

AT49

AU52

AT53

AY51

AT48

AU50

AT51

AA52

AB53

AD53

AD48

AB51

T48

T47

Y48

Y45

V48

V51

V53

Y53

Y51

L_BKLTEN

L_VDD_EN

L_BKLTCTL

L_DDC_CLK

L_DDC_DATA

L_CTRL_CLK

L_CTRL_DATA

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSA_DATA#0

LVDSA_DATA#1

LVDSA_DATA#2

LVDSA_DATA#3

LVDSA_DATA0

LVDSA_DATA1

LVDSA_DATA2

LVDSA_DATA3

LVDSB_CLK#

LVDSB_CLK

LVDSB_DATA#0

LVDSB_DATA#1

LVDSB_DATA#2

LVDSB_DATA#3

LVDSB_DATA0

LVDSB_DATA1

LVDSB_DATA2

LVDSB_DATA3

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_VSYNC

DAC_IREF

CRT_IRTN

IbexPeak-M_QMGS

IbexPeak-M_QMGS

SDVO_TVCLKINN

SDVO_TVCLKINP

SDVO_STALLN

SDVO_STALLP

SDVO_CTRLCLK

SDVO_CTRLDATA

LVDS

LVDS

DDPC_CTRLCLK

DDPC_CTRLDATA

Digital Display Interface

Digital Display Interface

DDPD_CTRLCLK

DDPD_CTRLDATA

CRT

CRT

2

BJ46

BG46

BJ48

BG48

BF45

SDVO_INTN

BH45

SDVO_INTP

T51

T53

BG44

DDPB_AUXN

BJ44

DDPB_AUXP

AU38

DDPB_HPD

BD42

DDPB_0N

BC42

DDPB_0P

BJ42

DDPB_1N

BG42

DDPB_1P

BB40

DDPB_2N

BA40

DDPB_2P

AW38

DDPB_3N

BA38

DDPB_3P

Y49

AB49

BE44

DDPC_AUXN

BD44

DDPC_AUXP

AV40

DDPC_HPD

BE40

DDPC_0N

BD40

DDPC_0P

BF41

DDPC_1N

BH41

DDPC_1P

BD38

DDPC_2N

BC38

DDPC_2P

BB36

DDPC_3N

BA36

DDPC_3P

U50

U52

BC46

DDPD_AUXN

BD46

DDPD_AUXP

AT38

DDPD_HPD

BJ40

DDPD_0N

BG40

DDPD_0P

BJ38

DDPD_1N

BG38

DDPD_1P

BF37

DDPD_2N

BH37

DDPD_2P

BE36

DDPD_3N

BD36

DDPD_3P

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet of

SDVO

Display port BDisplay port CDisplay port D

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

IBEX PEAK-M 1/6

UM3 1A

UM3 1A

UM3 1A

7 63Thursday, October 15, 2009

7 63Thursday, October 15, 2009

7 63Thursday, October 15, 2009

of

1

of

Page 8

5

4

3

2

1

D D

R128

R128

20K

20K

R129

R129

10K

10K

R272 33R272 33

R266 33R266 33

R224 33R224 33

R262 33R262 33

SPKR

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_RST#

NC all Res. when

PCH is

production stage.

ICH_AZ_CODEC_BITCLK[39]

C C

ICH_AZ_CODEC_SYNC[39]

ICH_AZ_CODEC_RST#[29,39]

ICH_AZ_CODEC_SDOUT[39]

Place all series terms close to PCH except for SDIN input

lines,which should be close to source.Placement of R773, R775,

R776 & R777 should equal distance to the T split trace point.

Basically, keep the same distance from T for all series

termination resistors.

+3.3V_RUN

B B

A A

+3.3V_SUS

R111

R111

200

200

R116

R116

100

100

R142 *1K_NCR142 *1K_NC

Res. of TDI near PCH

R107

R107

200

200

R110

R110

100

100

1 2

R127

R127

R126

R126

SPKR

200

200

100

100

5

+RTC_CELL

C426

C426

*27P_NC

*27P_NC

50

50

No Reboot strap.

Low = Default.

High = No Reboot.

Res. of TDO

PCH ES1 stage : NC

PCH ES2 stage : pop

R2191MR219

1M

ACZ_BIT_CLK

ACZ_SYNC

ACZ_RST#

ACZ_SDOUT

R222 20K/FR222 20K/F

C377

C377

1U

1U

805

805

10

R240 20K/FR240 20K/F

C392

C392

1U

1U

805

805

10

10

INTVRMEN(Intern al Voltage Regu lator Enable) :

This signal ena bles the intern al 1.05 V regul ators.

This signal mus t be always pul led-up to VccRT C.

R130 51R130 5 1

Note : Only pop when PCH is production

stage & nee d "JTAG boundary Scan".

Reme mber to depop XDP side Re s.

10

PCH_JTAG_TCK_BUF

4

C317

C317

18P/50V

18P/50V

23

R187

R187

Y1

10M

32.768KHZY132.768KHZ

C329

C329

18P/50V

18P/50V

Cap values depe nd on Xtal

+RTC_CELL

JTAG

Test Pad s are n eed to p ut on

the same side o f mother board.

R213 330 KR213 330 K

ICH_AZ_CODEC_SDIN0[39]

10M

4 1

RTC_X1

RTC_X2

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INVRMEN

ACZ_BIT_CLK

ACZ_SYNC

SPKR[39 ]

SPKR

ACZ_RST#

ACZ_SDOUT

PCH_GPIO33

T27T2 7

PCH_GPIO13

T26T2 6

PCH_JTAG_TCK_BUF

T60T6 0

PCH_JTAG_TMS

T54T5 4

PCH_JTAG_TDI

T52T5 2

PCH_JTAG_TDO

T57T5 7

PCH_JTAG_RST#

T59T5 9

SPI_CLK[30]

SPI_CS0#[30]

SPI_SI[30]

SPI_SO[30]

SPI_CLK

SPI_CS0#

SPI_CS1#

T62T6 2

SPI_SI

SPI_SO

3

IBEX PEAK-M (HDA,JTAG,SATA)

U23A

U23A

B13

RTCX1

D13

RTCX2

C14

RTCRST#

D17

SRTCRST#

A16

INTRUDER#

A14

INTVRMEN

A30

HDA_BCLK

D29

HDA_SYNC

P1

SPKR

C30

HDA_RST#

G30

HDA_SDIN0

F30

HDA_SDIN1

E32

HDA_SDIN2

F32

HDA_SDIN3

B29

HDA_SDO

H32

HDA_DOCK_EN# / GPIO33

J30

HDA_DOCK_RST# / GPIO13

M3

JTAG_TCK

K3

JTAG_TMS

K1

JTAG_TDI

J2

JTAG_TDO

J4

TRST#

BA2

SPI_CLK

AV3

SPI_CS0#

AY3

SPI_CS1#

AY1

SPI_MOSI

AV1

SPI_MISO

IbexPeak-M_QMGS

IbexPeak-M_QMGS

FWH4 / LFRAME#

LDRQ1# / GPIO23

RTCIHDA

RTCIHDA

LPC

LPC

SATA

SATA

SATA0GP / GPIO21

SATA1GP / GPIO19

SPI JTAG

SPI JTAG

iTPM ENABLE/DISABLE

+3.3V_RUN

R157 *1K_NCR157 *1K_NC

TPM Fun ction

Enable Mount

Disable NC

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

LDRQ0#

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATALED#

SPI_SI

D33

B33

C32

A32

C34

A34

F34

AB9

AK7

AK6

AK11

AK9

AH6

AH5

AH9

AH8

AF11

AF9

AF7

AF6

AH3

AH1

AF3

AF1

AD9

AD8

AD6

AD5

AD3

AD1

AB3

AB1

AF16

AF15

SATA_ACT#

T3

Y9

V1

(Defaul t)

2

LPC_LAD0 [29 ,32]

LPC_LAD1 [29 ,32]

LPC_LAD2 [29 ,32]

LPC_LAD3 [29 ,32]

LPC_LFRAME# [29,32]

IRQ_SERIRQ [29]

SATA_RX0- [35]

SATA_RX0+ [35]

SATA_TX0- [35]

SATA_TX0+ [35]

SATA_RX1- [35]

SATA_RX1+ [3 5]

SATA_TX1- [35]

SATA_TX1+ [35]

SATA port 2/3 a re not support in HM55 .

They are only i n PM 55

SATA_COMP

R199 37.4/FR199 37.4/ F

R132 10K/FR132 10K/F

1 2

R186 10K/FR186 10K/F

1 2

R115 10K/FR115 10K/F

1 2

+1.05V_PCH

+3.3V_RUN

SATA_ACT# [29]

+3.3V_RUN

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

SATA HD D

SATA OD D

Distanc e betwee n the PC H and

cap on the "P" signal s hould b e

identic al dista ce betwe en the

PCH and cap on the "N" signal

for the same pa ir.

E-SATA

Stephen 7/31

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

IBEX PEAK-M 2/6

UM3 1A

UM3 1A

UM3 1A

1

8 63Thursd ay, October 15, 2009

8 63Thursd ay, October 15, 2009

8 63Thursd ay, October 15, 2009

of

of

of

Page 9

5

4

3

2

1

IBEX PEAK-M (PCI,USB,NVRAM)

U23E

U23E

H40

AD0

N34

AD1

C44

AD2

A38

AD3

C36

AD4

J34

AD5

A40

AD6

D45

D D

PCI_PIRQA#

T33T3 3

PCI_PIRQB#

PCI_PIRQC#

T41T4 1

PCI_PIRQD#

T69T6 9

C C

USB_MCARD1_DET#[32]

BT_DET#[32]

PCIRST#:

DG(V1.0) P277

Can be left unconnected.

PAR:

SC(V1.0) P36

Can be left unconnected

if not using PCI.

PME:

DG(V1.0) P277

Can be left unconnected.

CLK_LPC_DEBUG[ 32]

B B

CLK_PCI_8502[2 9]

CLKOUT_PCI[0..4]:

22 ohm series resistor is recommend

(single & double load) on PDG v1.1

Reserve capacitor pads for

improving WWAN.

CLK_LPC_DEBUG

CLK_PCI_8502

Non-iAMT

C396 *0.0 47U_NC

C396 *0.0 47U_NC

A A

PCI_PLTRST#

CLK_PCI_FB CLK_PCI_FB_C

50

50

C443 *27P_NC

C443 *27P_NC

50

50

C415 *27P_NC

C415 *27P_NC

Add Buffers as needed for

Loading and fanout concerns.

+3.3V_SUS

5

U10

U10

2

10

10

1

*TC7SZ32FU(T5 L,F,T)_NC

*TC7SZ32FU(T5 L,F,T)_NC

2

112

R235 SJ_0402R235 SJ_04 02

T39T3 9

T37T3 7

T36T3 6

T35T3 5

T31T3 1

T42T4 2

T38T3 8

T40T4 0

T34T3 4

T18T1 8

T15T1 5

R287 33R 287 33

R267 33R 267 33

R288 33R 288 33

RSV_SMBALERT#

RSV_ICH_CL_RST1#

ICH_SMBCLK

ICH_SMBDATA

SMB_CLK_ME0

SMB_DATA_ME0

SMB_CLK_ME1

SMB_DATA_ME1

LPD_SPI_INTR#

PEG_CLKREQ#

4

5

PCI_REQ0#

PCI_REQ1#

PCI_REQ2#

USB_MCARD1_DET#

PCI_GNT0#

PCI_GNT1#

PCI_GNT2#

PCI_GNT3#

PCI_PIRQE#

PCI_PIRQF#

BT_DET#

PCI_PIRQH#

PCI_RST#

PCI_SERR#

PCI_PERR#

PCI_IRDY#

PCI_DEVSEL#

PCI_FRAME#

PCI_PLOCK#

PCI_STOP#

PCI_TRDY#

PME#

PCI_PLTRST#

CLK_LPC_DEBUG_C

CLK_PCI_8502_ C

PLTRST# [3,16, 29,31,32,4 1]

AD7

E36

AD8

H48

AD9

E40

AD10

C40

AD11

M48

AD12

M45

AD13

F53

AD14

M40

AD15

M43

AD16

J36

AD17

K48

AD18

F40

AD19

C42

AD20

K46

AD21

M51

AD22

J52

AD23

K51

AD24

L34

AD25

F42

AD26

J40

AD27

G46

AD28

F44

AD29

M47

AD30

H36

AD31

J50

C/BE0#

G42

C/BE1#

H47

C/BE2#

G34

C/BE3#

G38

PIRQA#

H51

PIRQB#

B37

PIRQC#

A44

PIRQD#

F51

REQ0#

A46

REQ1# / GPIO50

B45

REQ2# / GPIO52

M53

REQ3# / GPIO54

F48

GNT0#

K45

GNT1# / GPIO51

F36

GNT2# / GPIO53

H53

GNT3# / GPIO55

B41

PIRQE# / GPIO2

K53

PIRQF# / GPIO3

A36

PIRQG# / GPIO4

A48

PIRQH# / GPIO5

K6

PCIRST#

E44

SERR#

E50

PERR#

A42

IRDY#

H44

PAR

F46

DEVSEL#

C46

FRAME#

D49

PLOCK#

D41

STOP#

C48

TRDY#

M7

PME#

D5

PLTRST#

N52

CLKOUT_PCI0

P53

CLKOUT_PCI1

P46

CLKOUT_PCI2

P51

CLKOUT_PCI3

P48

CLKOUT_PCI4

IbexPeak-M_QMGS

IbexPeak-M_QMGS

+3.3V_SUS

R17710K/F R17710K/F

R19310K/F R19310K/F

R1912.2K/F R1912.2K/F

R1512.2K/F R1512.2K/F

R1522.2K/F R1522.2K/F

R1552.2K/F R1552.2K/F

R2532.2K/F R2532.2K/F

R2522.2K/F R2522.2K/F

R19010K/F R19010K/F

R11910K/F R11910K/F

NV_DQ10 / NV_IO10

NV_DQ11 / NV_IO11

NVRAM

NVRAM

NV_DQ12 / NV_IO12

NV_DQ13 / NV_IO13

NV_DQ14 / NV_IO14

NV_DQ15 / NV_IO15

PCI

PCI

USB

USB

BT_DET#

PCI_REQ2#

PCI_PIRQE#

PCI_PIRQF#

OC7#

OC5#

OC4#

OC3#

+3.3V_SUS

PCI_PIRQH#

PCI_REQ0#

PCI_PIRQB#

USB_MCARD1_DET#

+3.3V_RUN

PCI_STOP#

PCI_PIRQA#

PCI_PIRQC#

PCI_IRDY#

+3.3V_RUN

NV_DQ0 / NV_IO0

NV_DQ1 / NV_IO1

NV_DQ2 / NV_IO2

NV_DQ3 / NV_IO3

NV_DQ4 / NV_IO4

NV_DQ5 / NV_IO5

NV_DQ6 / NV_IO6

NV_DQ7 / NV_IO7

NV_DQ8 / NV_IO8

NV_DQ9 / NV_IO9

NV_CE#0

NV_CE#1

NV_CE#2

NV_CE#3

NV_DQS0

NV_DQS1

NV_ALE

NV_CLE

NV_RCOMP

NV_RB#

NV_WR#0_RE#

NV_WR#1_RE#

NV_WE#_CK0

NV_WE#_CK1

USBP0N

USBP0P

USBP1N

USBP1P

USBP2N

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

USBP8N

USBP8P

USBP9N

USBP9P

USBP10N

USBP10P

USBP11N

USBP11P

USBP12N

USBP12P

USBP13N

USBP13P

USBRBIAS#

USBRBIAS

OC0# / GPIO59

OC1# / GPIO40

OC2# / GPIO41

OC3# / GPIO42

OC4# / GPIO43

OC5# / GPIO9

OC6# / GPIO10

OC7# / GPIO14

RP6

RP6

6

7

8

9

10

10P8R-8.2 K

10P8R-8.2 K

RP7

RP7

6

7

8

9

10

10P8R-8.2 K

10P8R-8.2 K

RP5

RP5

6

7

8

9

10

10P8R-8.2 K

10P8R-8.2 K

4

AY9

BD1

AP15

BD8

AV9

BG8

AP7

AP6

AT6

AT9

BB1

AV6

BB3

BA4

BE4

BB6

BD6

BB7

BC8

BJ8

BJ6

BG6

BD3

AY6

AU2

AV7

AY8

AY5

AV11

BF5

H18

J18

A18

C18

N20

P20

J20

L20

F20

G20

A20

C20

M22

N22

B21

D21

H22

J22

E22

F22

A22

C22

G24

H24

L24

M24

A24

C24

B25

D25

N16

J16

F16

L16

E14

G16

F12

T15

5

4

3

2

1

5

4

3

2

1

5

4

3

2

1

NV_ALE

NV_CLE

OC0# [26 ]

OC1# [33 ]

+3.3V_RUN

+3.3V_SUS

+3.3V_RUN

+3.3V_RUN

Right Side pair to DB

Right Side pair to DB

Left Side pair

Left Side pair for 17"

Mini Card (WLAN)

Mini Card (WWAN)

Mini Card (WPAN)

Camera

Card Reader

Note : place these

resistors near to PCIe

Slots

ICH_USBP0- [26]

ICH_USBP0+ [26]

ICH_USBP1- [26]

ICH_USBP1+ [26]

ICH_USBP2- [33]

ICH_USBP2+ [33]

ICH_USBP3- [33]

ICH_USBP3+ [33]

ICH_USBP4- [32]

ICH_USBP4+ [32]

ICH_USBP5- [31]

ICH_USBP5+ [31]

USB port 6/7 are not support in HM55 .

They are only in PM 55

ICH_USBP8- [32]

ICH_USBP8+ [32]

ICH_USBP11- [24]

ICH_USBP11+ [24 ]

ICH_USBP12- [26]

ICH_USBP12+ [26 ]

USB_BIAS

R257 22.6/FR257 22.6/F

OC0#

OC1#

OC2#

OC3#

OC4#

OC5#

OC6#

OC7#

R279 8.2K/FR279 8.2K/F

R282 8.2K/FR282 8.2K/F

R280 8.2K/FR280 8.2K/F

R285 8.2K/FR285 8.2K/F

OC2#

OC6#

OC1#

OC0#

PCI_TRDY#

PCI_FRAME#

PCI_REQ1#

PCI_PIRQD#

PCI_SERR#

PCI_PERR#

PCI_PLOCK#

PCI_DEVSEL#

Place TX DC blocking caps close PCH.

PCIE_RX1-[31]

MiniWWAN

MiniWLAN

Giga Bit LOM

MiniWLAN

MiniWWAN

10/100 LOM

PCIE_RX1+[31]

PCIE_TX1-[31]

PCIE_TX1+[31]

PCIE_RX2-[32]

PCIE_RX2+[32]

PCIE_TX2-[32]

PCIE_TX2+[32]

PCIE_RX6-/GLAN_RX-[41]

PCIE_RX6+/GLAN_RX+[41]

PCIE_TX6-/GLAN_TX-[41]

PCIE_TX6+/GLAN_TX+[41]

PCI-E port 7/8 are not support in HM55 .

They are only in PM 55

CLK_PCIE_MINI1#[32 ]

CLK_PCIE_MINI1[32 ]

MINI1CLK_REQ#[32]

CLK_PCIE_MINI2#[31 ]

CLK_PCIE_MINI2[31 ]

MINI2CLK_REQ#[31]

CLK_PCIE_LOM#[41]

CLK_PCIE_LOM[41]

PCIE Clock Request

+3.3V_SUS

R161 10KR161 10K

R150 10KR150 10K

R131 10KR131 10K

R156 10KR156 10K

R143 10KR143 10K

+3.3V_RUN

R144 10KR144 10K

R141 10KR141 10K

PCIECLKRQ{0,3,4,5,6,7}# should have a

10K pull-up to +V3.3A.PCIECLKRQ{1,2}

should have a 10K pull-up to +3.3S

Boot BIOS Strap

PCI_GNT0# PCI_GNT1#

0 0

0

1

1 1

1

0

3

Boot BIOS Location

LPC

PCI

Reserved (NAND)

SPI

LOM_CLK_REQ#[41]

CLK_PCIE_REQ0#

MINI2CLK_REQ#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

LOM_CLK_REQ#

MINI1CLK_REQ#

CLK_PCIE_REQ2#

C376 0.1UC376 0.1U

C375 0.1UC375 0.1U

C390 0.1UC390 0.1U

C389 0.1UC389 0.1U

C406 0.1UC406 0.1U

C407 0.1UC407 0.1U

IBEX PEAK-M (PCI-E,SMBUS,CLK)

U23B

U23B

BG30

PERN1

BJ30

PCIE_TXN1_C

PCIE_TXP1_C

PCIE_TXN2_C

PCIE_TXP2_C

PCIE_TXN6_C

PCIE_TXP6_C

CLK_PCIE_REQ0#

MINI1CLK_REQ#

CLK_PCIE_REQ2#

MINI2CLK_REQ#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

R286 *1K/F_NCR28 6 *1K/F_NC

A16 swap override Strap/Top-Block

Swap Override jumper

PCI_GNT3#

PERP1

BF29

PETN1

BH29

PETP1

AW30

PERN2

BA30

PERP2

BC30

PETN2

BD30

PETP2

AU30

PERN3

AT30

PERP3

AU32

PETN3

AV32

PETP3

BA32

PERN4

BB32

PERP4

BD32

PETN4

BE32

PETP4

BF33

PERN5

BH33

PERP5

BG32

PETN5

BJ32

PETP5

BA34

PERN6

AW34

PERP6

BC34

PETN6

BD34

PETP6

AT34

PERN7

AU34

PERP7

AU36

PETN7

AV36

PETP7

BG34

PERN8

BJ34

PERP8

BG36

PETN8

BJ36

PETP8

AK48

CLKOUT_PCIE0N

AK47

CLKOUT_PCIE0P

P9

PCIECLKRQ0# / GPIO73

AM43

CLKOUT_PCIE1N

AM45

CLKOUT_PCIE1P

U4

PCIECLKRQ1# / GPIO18

AM47

CLKOUT_PCIE2N

AM48

CLKOUT_PCIE2P

N4

PCIECLKRQ2# / GPIO20