Quanta R09, R09A, Inspiron 5720, Inspiron 7720 Schematic

1

2

3

4

5

6

7

8

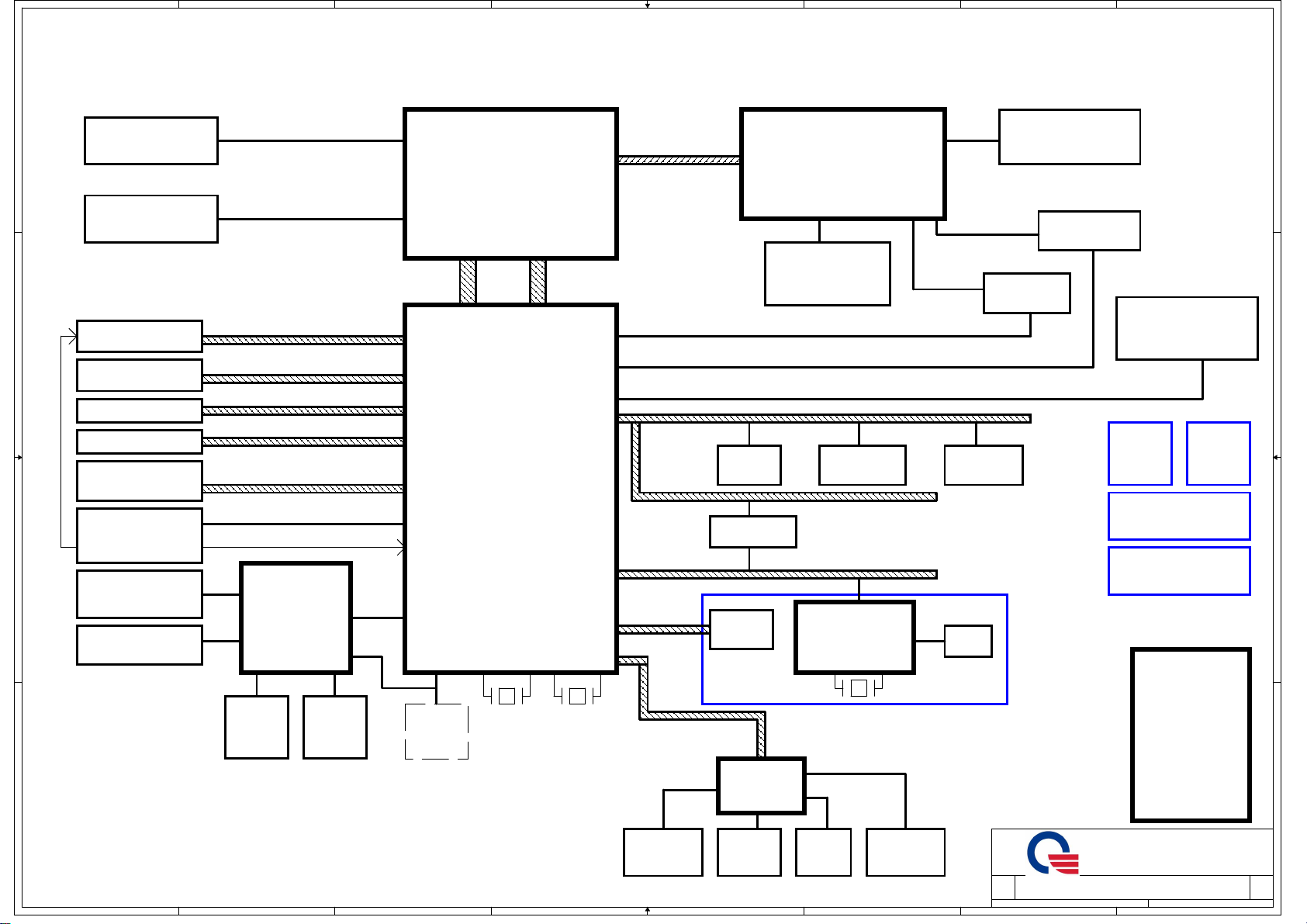

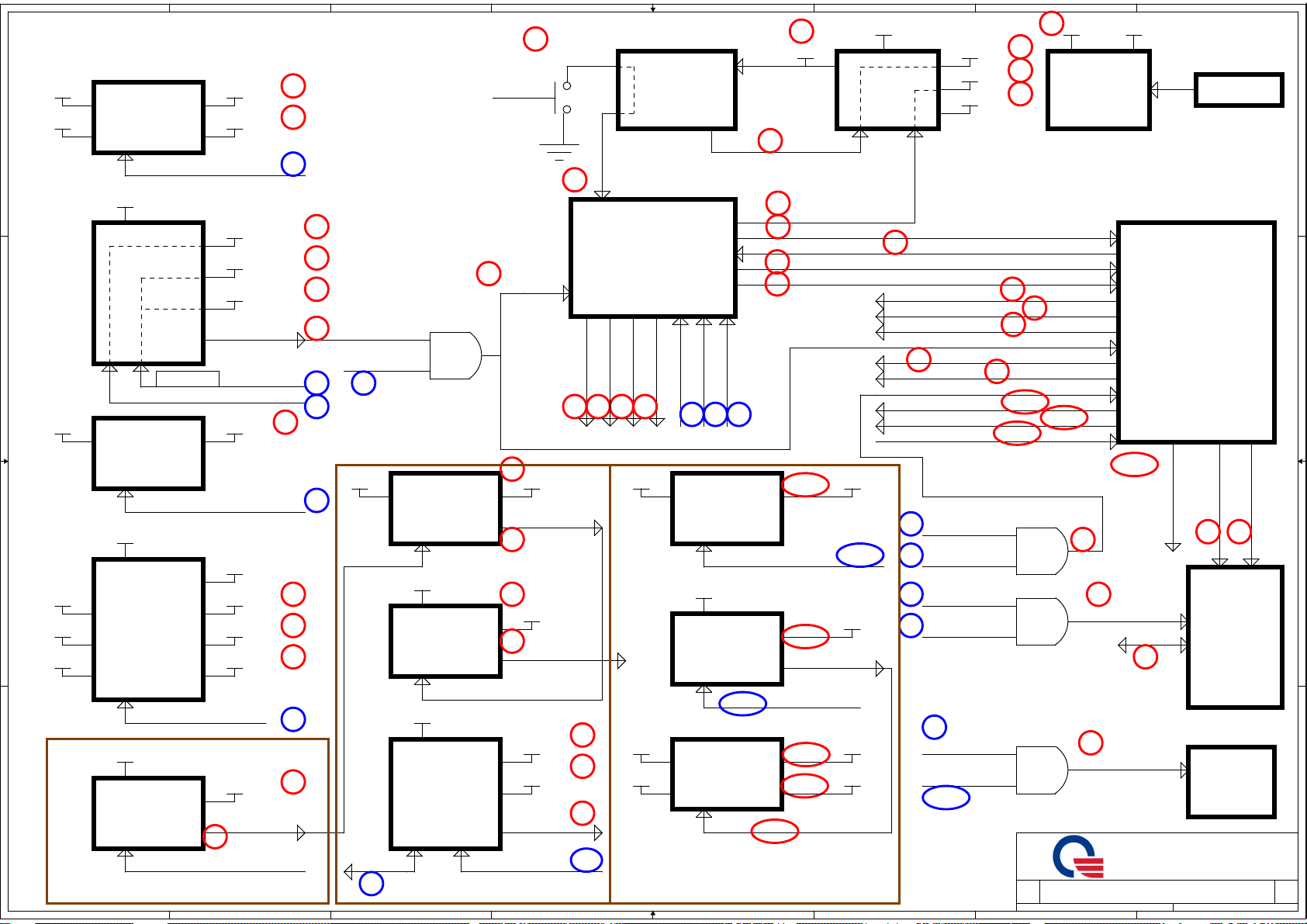

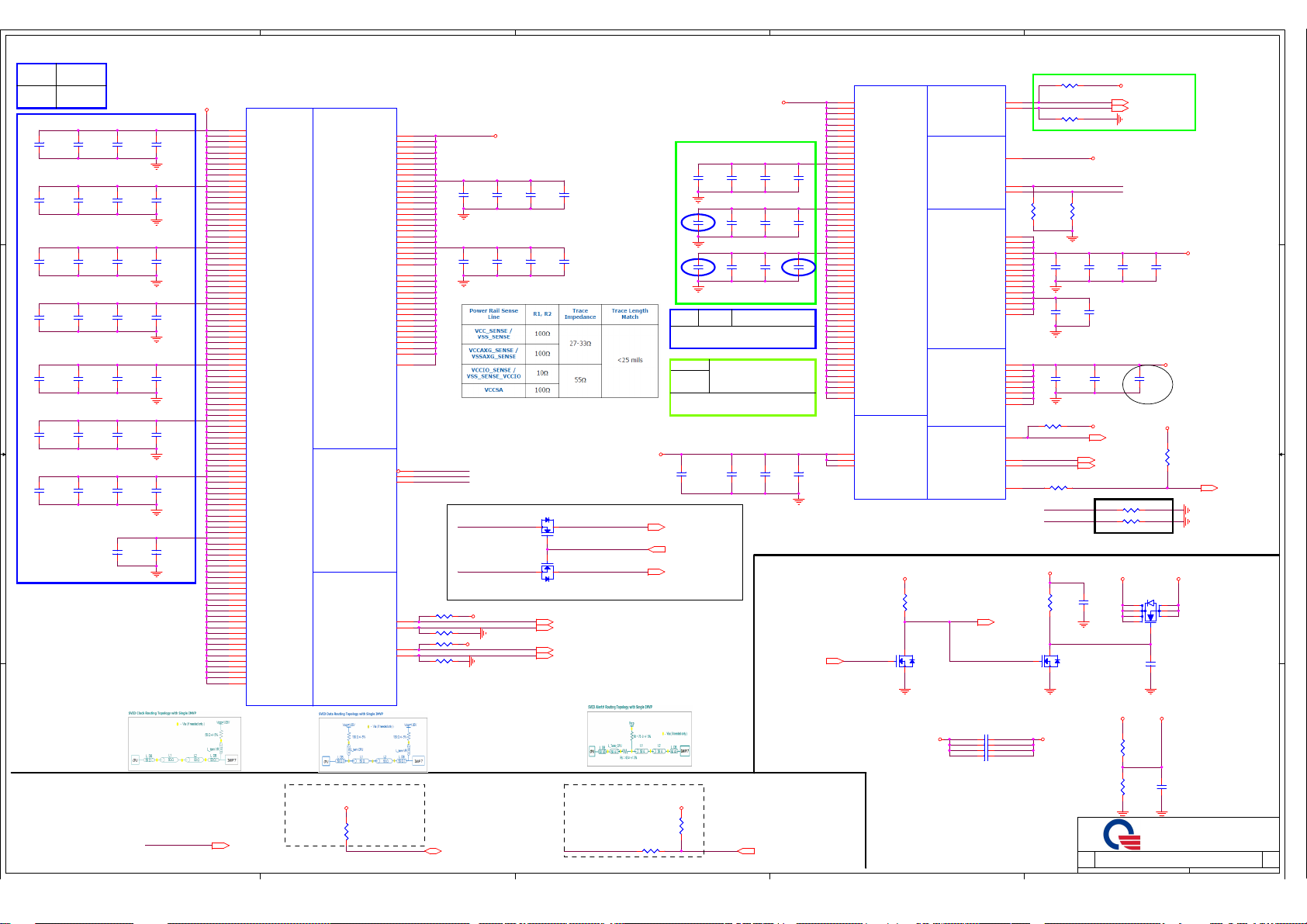

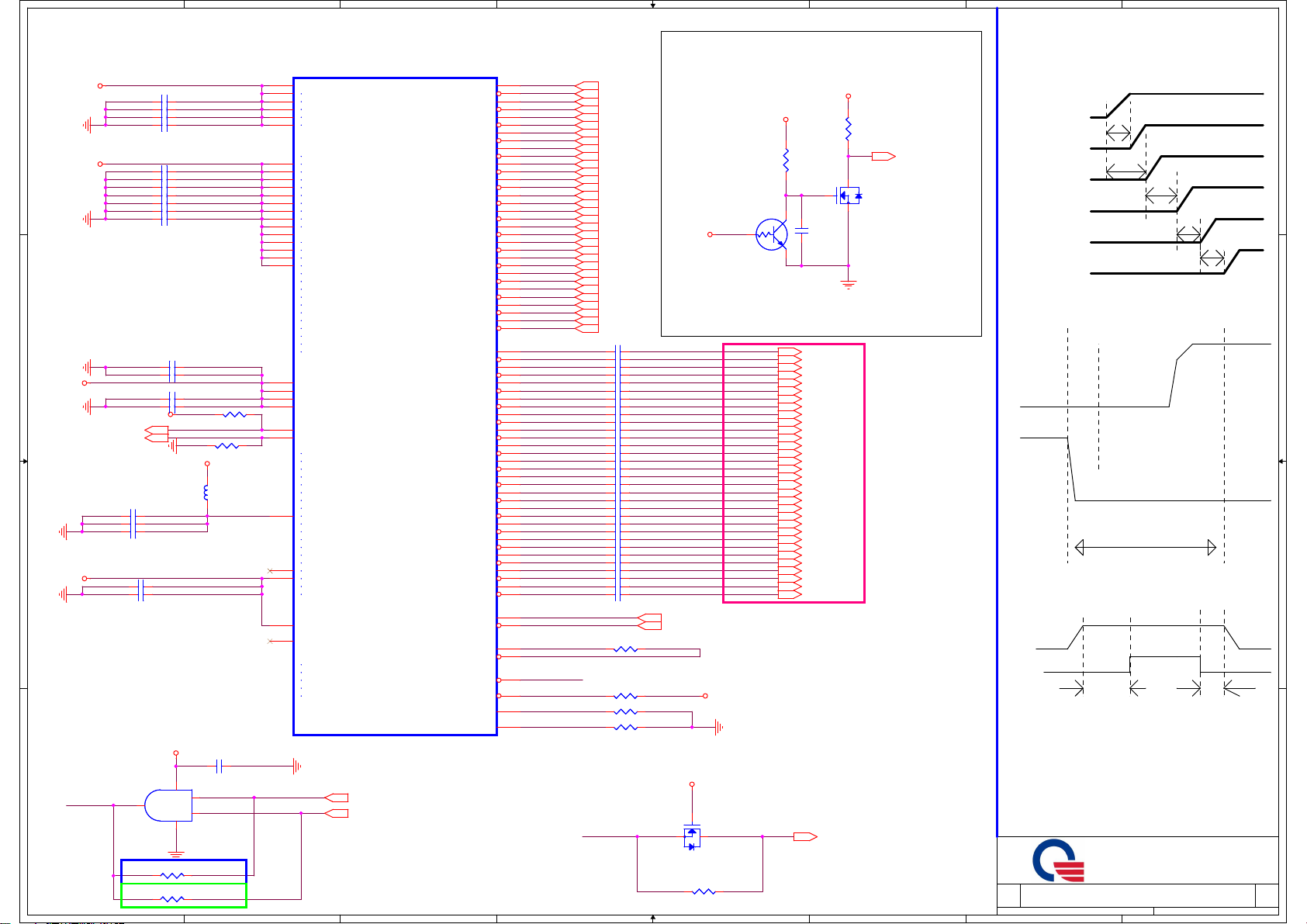

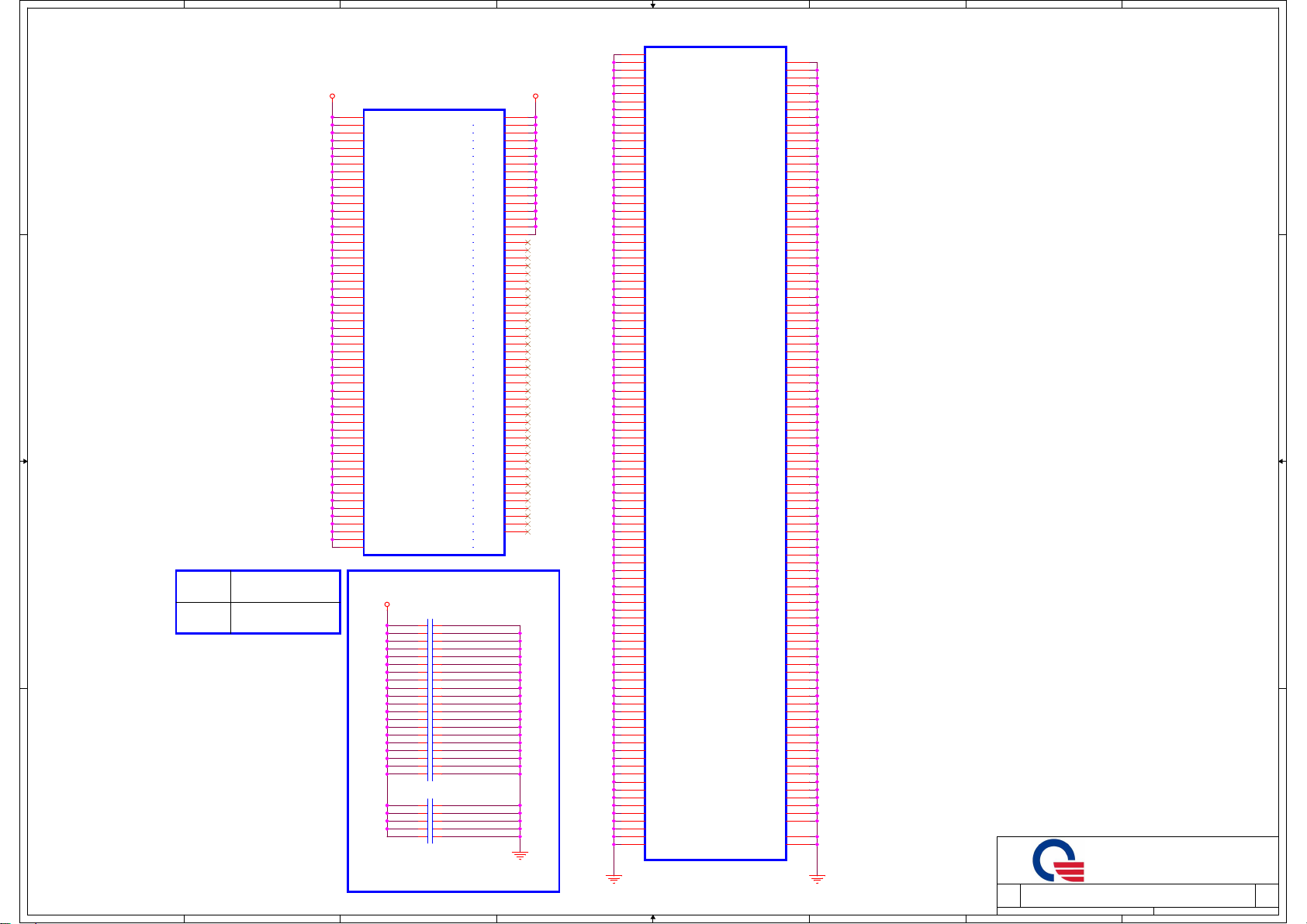

R09/A 17" OPT BLOCK DIAGRAM

A A

DDRIII-SODIMM1

H=4mm

PAGE12

DDRIII-SODIMM2

H=8mm

SATA -HDD(Main)

B B

SATA -HDD(Second)

m-SATA

ODD

USB3.0 Ports x2

USB Power share port1

3-axis Fall Sensor

FFS_INT2_R

C C

D D

FFS LNG3DMTR

Keyboard Conn.

Touch Pad

PAGE11

PAGE34

PAGE34

PAGE41

PAGE34

PAGE35, 36

PAGE33

PAGE40

PAGE40

HDD_FALL_INT1

PWM FAN

&Thermal

DDRIII 1600 MT/s

DDRIII 1600 MT/s

SATA0 Gen3

SATA1 Gen3

SATA2 Gen2

SATA3 Gen2

USB3.0/2.0

SMBUS

KBC

ITE 8518

PAGE38

SPI ROM

8MB

PAGE44 PAGE39

FDI LINK

LPC

CPU

Ivy Bridge/

Sandy Bridge

35W / 45W CPU

PGA 988

2.7GT /s

Mobile Intel

Series 7 Chipset

PCH

HM77

Panther Point

BGA 989

25 mm X 25 mm

SPI

SPI ROM

8MB

PAGE39

25MHz

PAGE6~10

DMI LINK

5GT /s

iGFX Interfaces

PAGE20~26

32.768KHz

PCIEx16

HDMI 1.4a

CRT

LVDS

USB2.0

PCI-E

USB3.0/2.0

IHDA

N13P-GT/GV

(128bit/64bit)

USB[12]

Camera

PAGE27 PAGE32

USB[4]

WLAN/BT

PAGE41

PCIE[1]

USB3.0

Ports x1

DB1

Audio Codec

IDT 92HD94

PAGE30

Nvidia

29mm X 29mm

BGA 973

GDDR5 2GB/1GB

128Mbx16bitx8

128Mbx16bitx4

PAGE18,19

Card reader

RTS5179GR

LAN 10/100/1000

RTL8111F/8105E

PAGE13~17

HDMI 1.4a

USB[11]

PCIE[5]

25MHz

eDP

CRT

Finger print

RJ45

3D LCD CONN

1920 x 1080 (FHD)

CRT CONN

HDMI CONN

PAGE29

USB[8]

PAGE27

PAGE27

PAGE28

LCD CONN

1600 x 900 (HD+)

1920 x 1080 (FHD)

DB2

Hot key

board

DB3

USB3.0

Ports x1

DB4

Poewr button board

DB5

TP button board

PCB STACK UP

6L

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : BOT

PAGE27

DIS

Subwoofer

TI TPA3111

PAGE31 PAGE30 PAGE30 PAGE27

1

2

3

4

5

Jack x 2Speaker Digital-MIC

6

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 20, 2012

Date: Sheet of

Monday, February 20, 2012

Date: Sheet of

Monday, February 20, 2012

7

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

R09A

R09A

R09A

1 58

1 58

1 58

8

3A

3A

3A

1

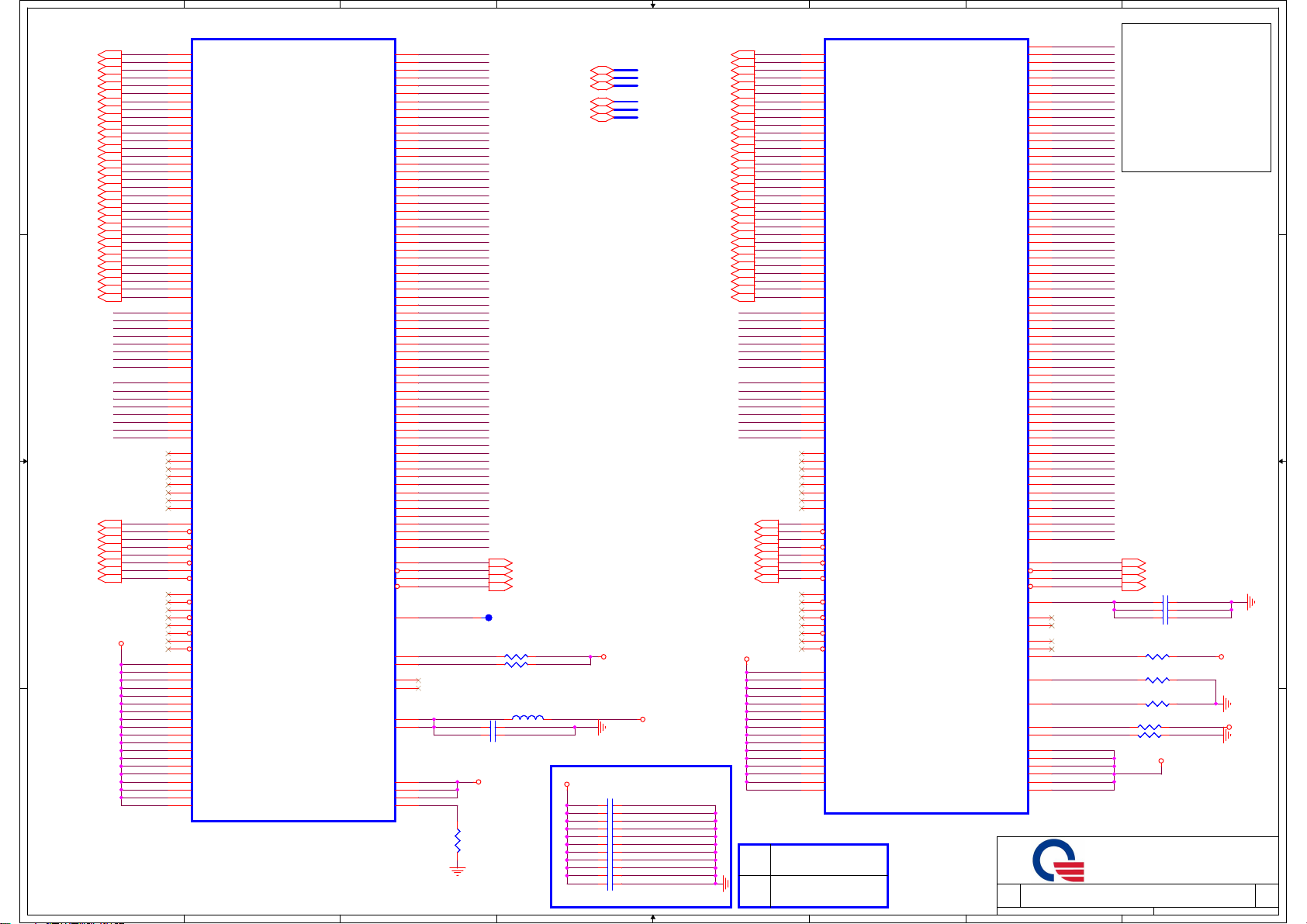

A A

2

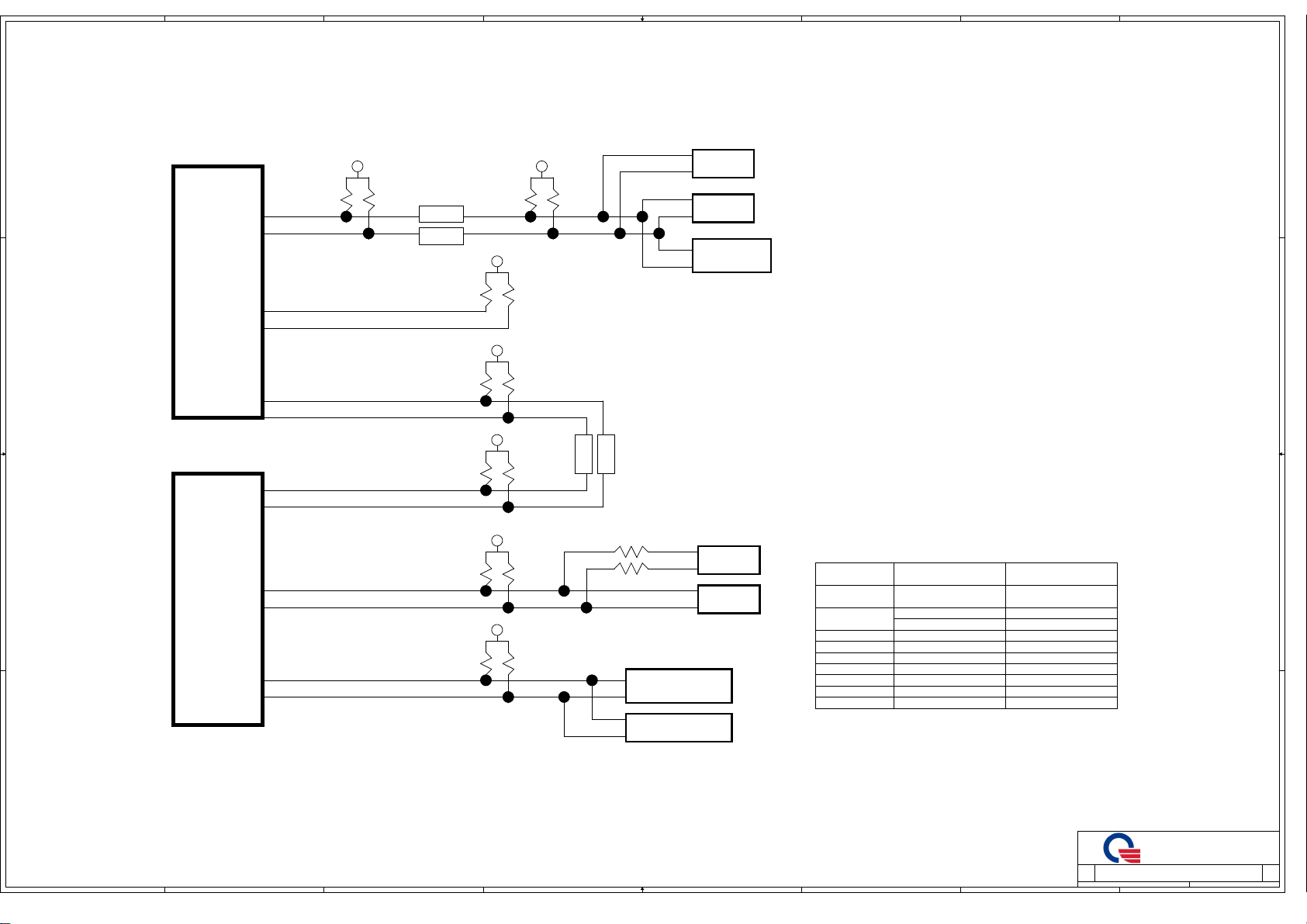

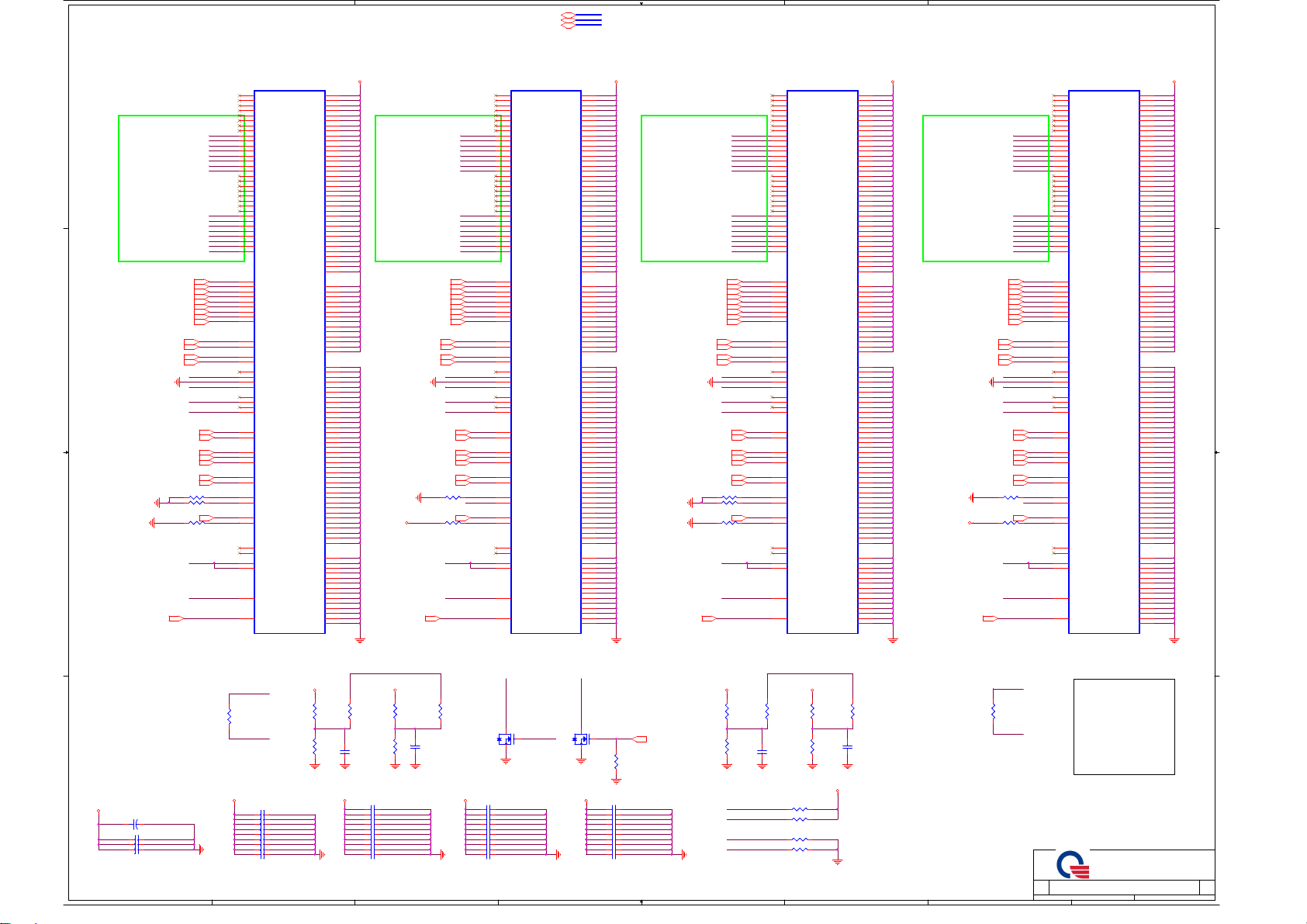

+3.3V_SUS

3

+3.3V_RUN

4

5

JDIM1A

A0

6

7

8

2.2K

2.2K2.2K

JDIM2A

FALL SENSOR

STM LNG3DM

A4

50

2.2K2.2K

SMBCLK

H14

SMBDATA

C9

PCH

C8

SML0CLK

G12

SML0DATA

B B

+3.3V_RUN

N-MOSFET

N-MOSFET

+3.3V_RUN

2.2K

WLAN_SCLK

WLAN_SDATA

+3.3V_SUS

+3.3V_SUS

2.2K2.2K

E14

SMB_CLK_ME1

M16

SMB_DATA_ME1

+3.3V_ALW

2.2K2.2K

SMBDAT1116

SMBCLK1

115

+3.3V_ALW

C C

SIO

ITE8518E

110

SMBCLK0

111 SMBDAT0

2.2K2.2K

+3.3V_RUN

2.2K2.2K

SMBCLK3

94

SMBDAT3

95

N-MOS

N-MOS

+3.3V_SUS

+3.3V_SUS

100

100

Battery

Charger

THERMAL(NCT7718W)

16h

Function

12

DDR3

Thermal IC

Charge IC

Battery

Fall Sensor

98

JDIM1A A0

JDIM2A A4

G781-1P8

EMC1422

BQ24707ARGRR

Battery

LNG3DM

SMBus AddressIC

1001101xb (9Ah)

1001100xb (98h)

0b00010010 (0x12)

16h

01010000 (50h)

THERMAL(G781-1)

9A

For GPU

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, February 08, 2012

Date: Sheet of

Wednesday, February 08, 2012

Date: Sheet of

1

2

3

4

5

6

7

Wednesday, February 08, 2012

PROJECT :

SMB/SCREW PAD

SMB/SCREW PAD

SMB/SCREW PAD

8

R09A

R09A

R09A

2 58

2 58

2 58

3A

3A

3A

1

2

3

4

5

6

7

8

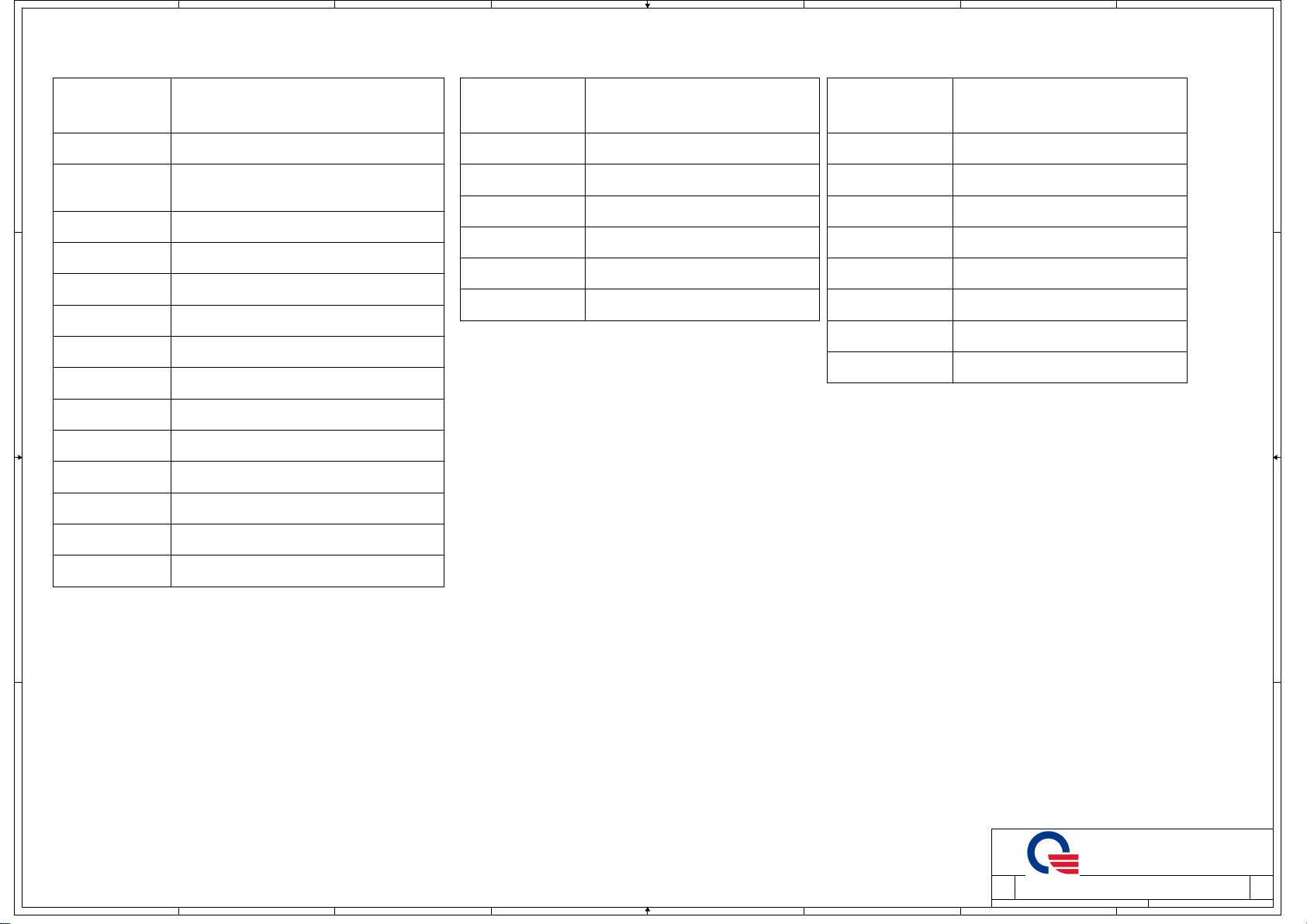

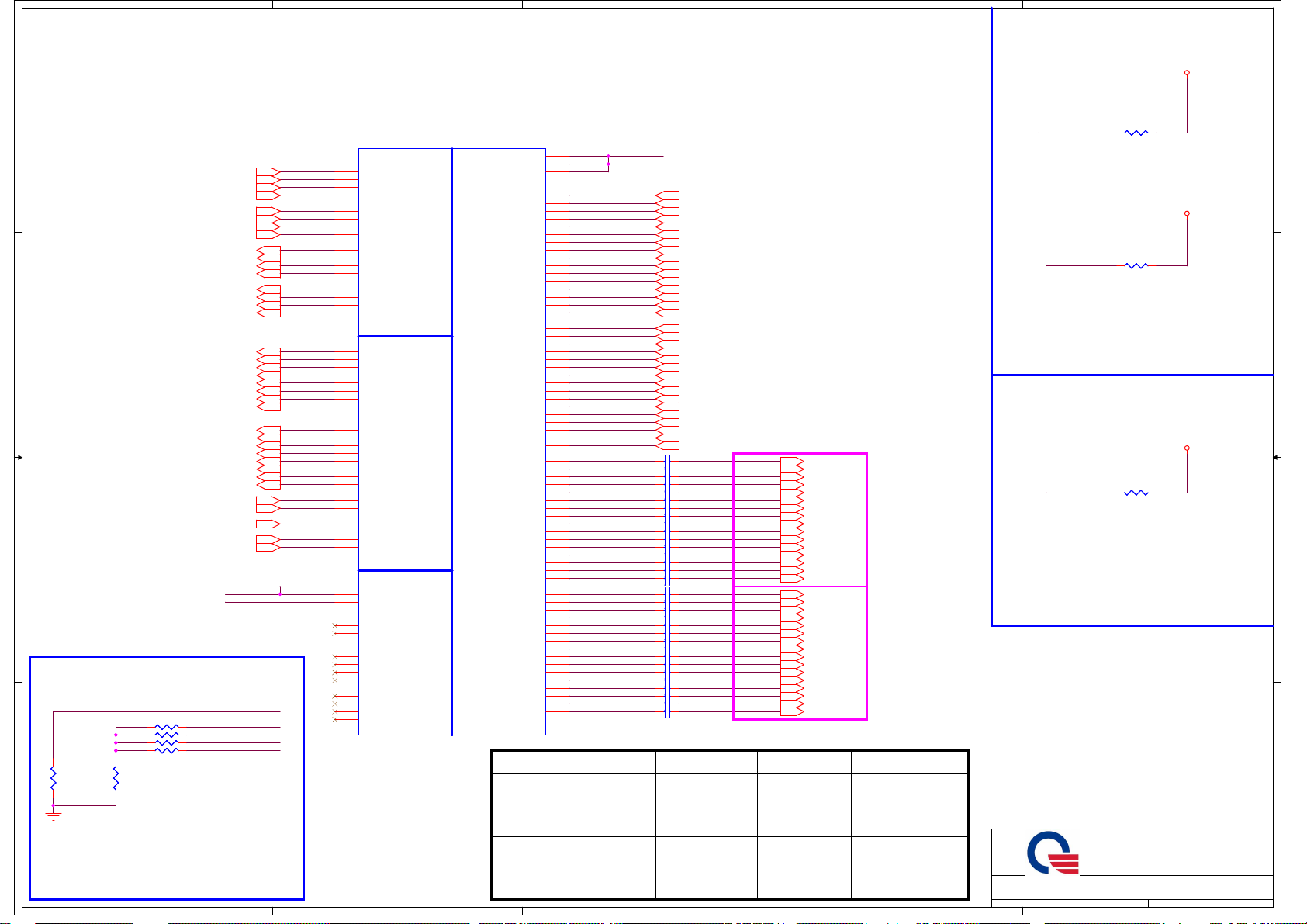

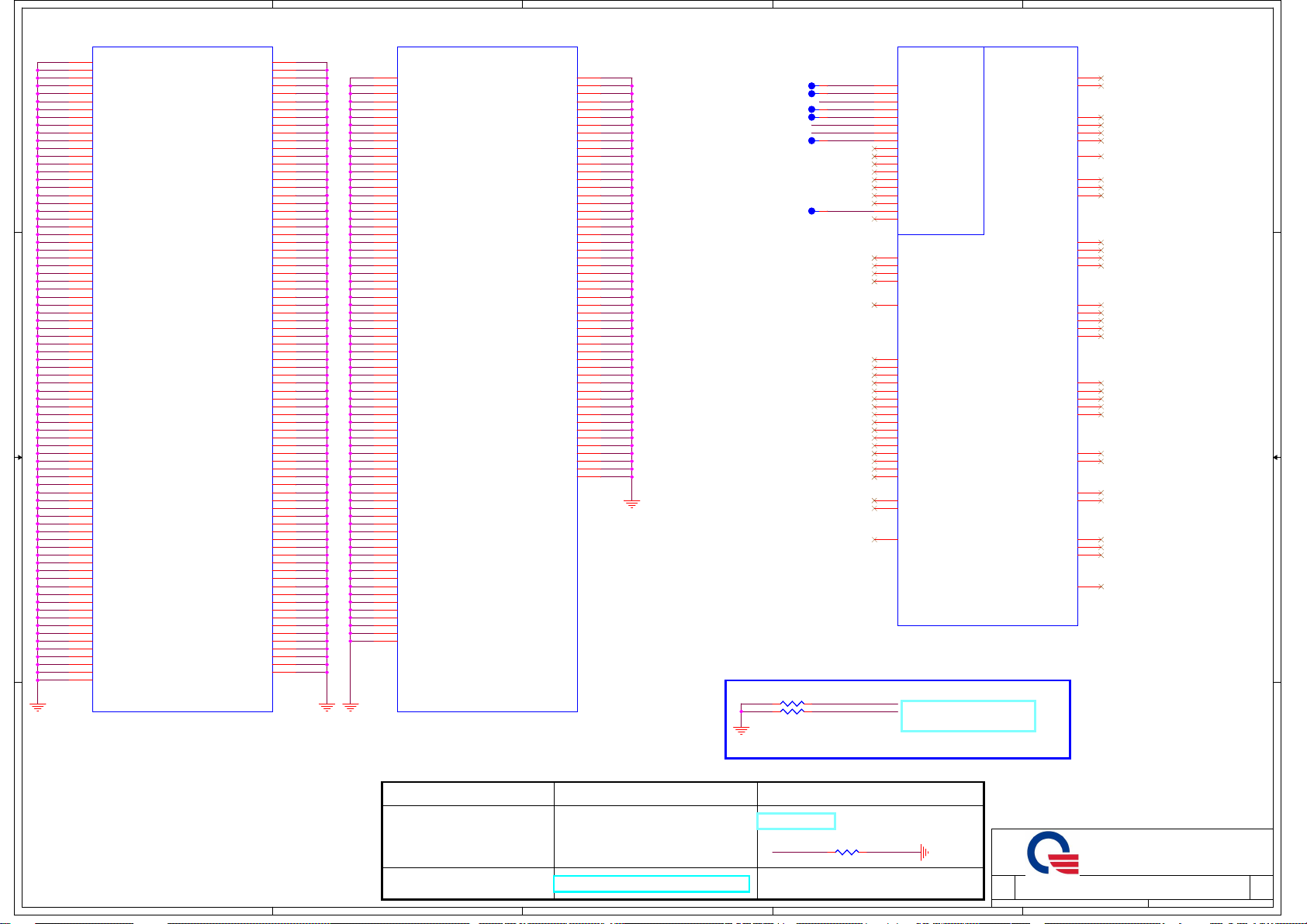

USB Master

A A

USB0

USB1

USB2

USB3

USB4

USB5

B B

USB6

Port Assignment

External port#1 (USB3.0)

External port#2

(USB3.0 / Power share)

External port#3 (USB3.0)

External port#4 (USB3.0)

MiniCard 1 (WLAN/BT/WiMAX)

NC

X(FOR HM77)

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

Port AssignmentSATA Master

HDD Main

HDD Second

mSATA

ODD

NC

NC

PCIE 1

PCIE 2

PCIE 3

PCIE 4

PCIE 5

PCIE 6

PCIE 7

Port AssignmentPCIE Master

WLAN

NC

NC

NC

LAN

NC

NC

NCPCIE 8

USB7

X(FOR HM77)

FingerprintUSB8

USB9

USB10

USB11

USB12

NC

Card Reader

Express Card

Camera

C C

D D

USB13

1

NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, February 08, 2012 3 58

Date: Sheet of

Wednesday, February 08, 2012 3 58

Date: Sheet of

2

3

4

5

6

Wednesday, February 08, 2012 3 58

7

PROJECT :

PORT ASSIGNMENT

PORT ASSIGNMENT

PORT ASSIGNMENT

R11

3A

3A

3A

8

5

4

3

2

1

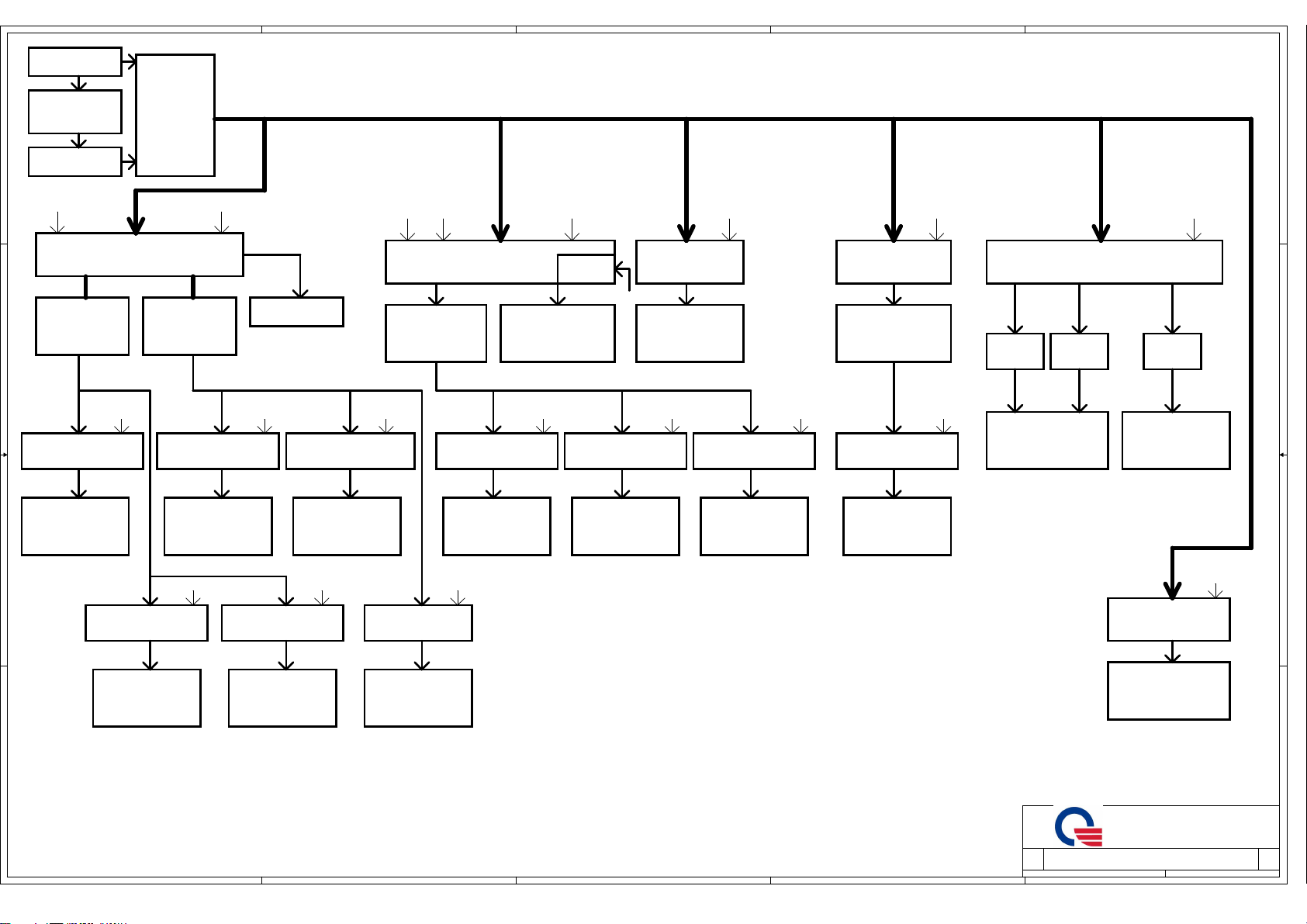

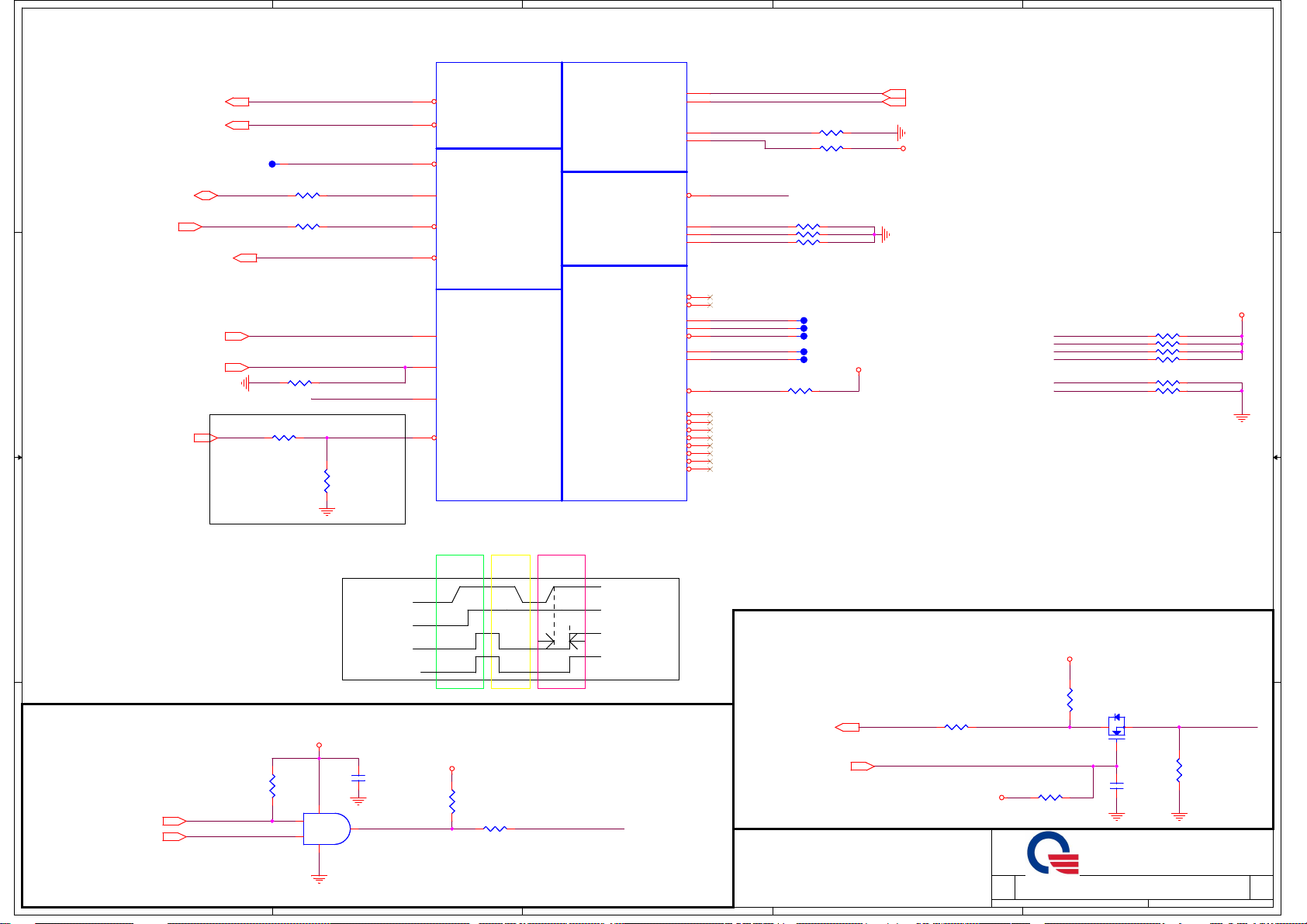

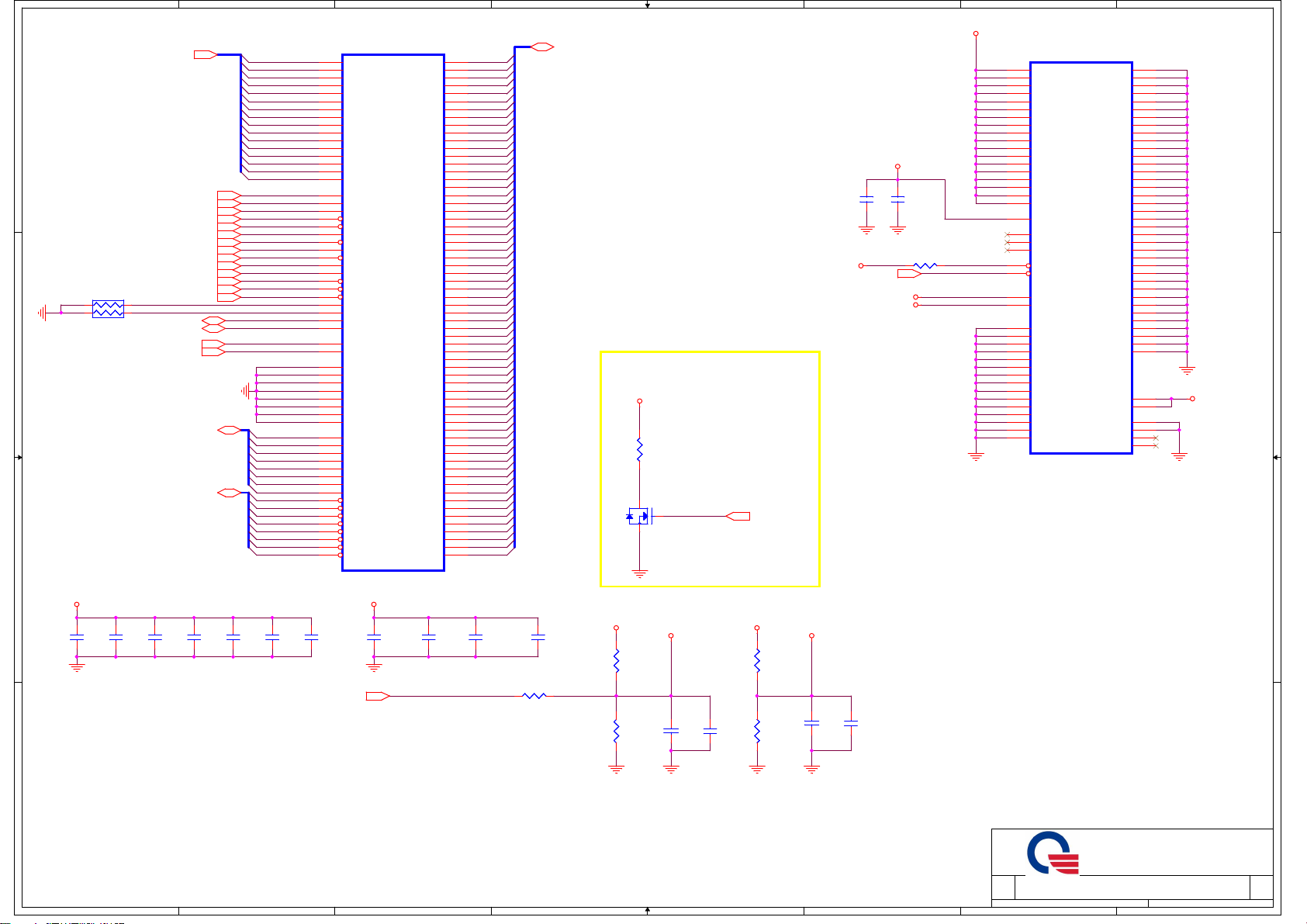

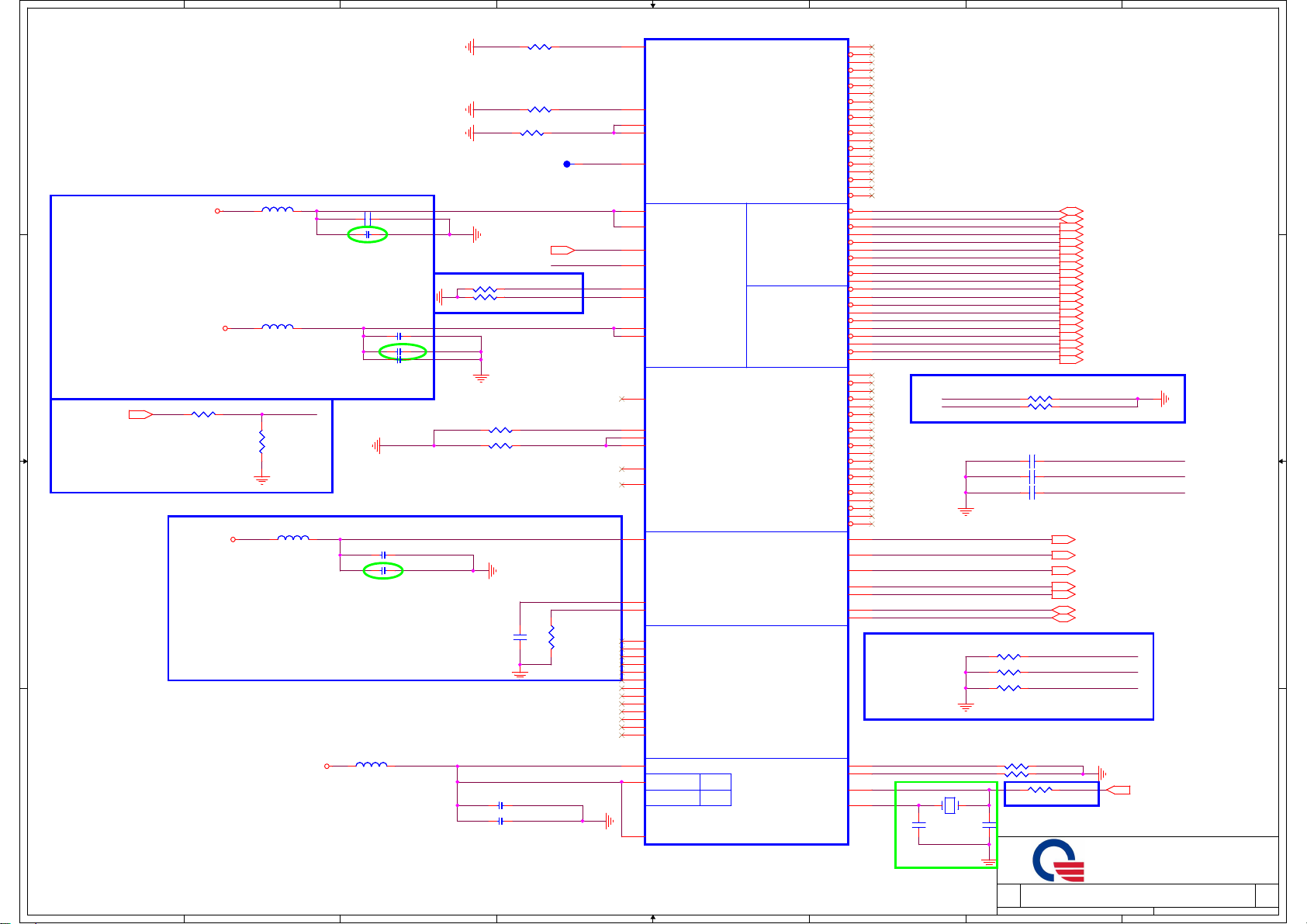

Adapter 90W

Charger

BQ24707RGRR

D D

PWR_SRC

Shapes: 280mil

Via: 10

VER : 1A

Battery 3S2P

+3.3V_EN2 ALW_ON

TI (PU1)

TPS51125ARGER

+3.3V_ALW

TDC: 6.2A

Shapes: 155mil

C C

Via: ?

SUS_ON

Load Switch(PQ18)

FDC655BN

+3.3V_SUS

TDC: 0.226A

Shapes: 8mil

Via: ?

B B

+5V_ALW

TDC: 10.8A

Shapes: 720mil

Via: ?

Load Switch(PQ24)

FDC655BN

+5V_SUS

TDC: 0.1A

Shapes: 56.4mil

Via: ?

RUN_ON

Load Switch(PQ23)

MDV1522URH

+3.3V_RUN

TDC: 2.6A

Shapes: 140.8mil

Via: ?

+15V_ALW

SUS_ON

Load Switch(PQ17)

MDV1522URH

+5V_RUN

TDC: 4.13A

Shapes: 140mil

Via: ?

DGPU_PWR_EN

Load Switch(PQ20)

FDC655BN

For dGPU only

+3.3V_GFX

TDC: 0.966A

Shapes: 8mil

Via: ?

SIO_SLP_S3#

+1.5V_SUS

TDC: 16A

Shapes: 326mil

Via: ?

RUN_ON

RichTek(PU5)

RT8068AZQW

+1.8V_RUN

TDC: 0.869A

Shapes: 40.8mil

Via: ?

SIO_SLP_S4#

TI(PU2)

TPS51216RUKR

+0.75V_DDR_VTT

Load Switch(PQ25)

FDC655BN

+1.5V_RUN

TDC: 0.922A

Shapes: 40mil

Via: ?

1.05V_PCH_PWRGD

1.5V_SUS_PWRGD

LDO

TDC: 1A

Shapes: 40mil

Via: ?

RUN_ON

Load Switch(PQ26)

MDV1522URH

VCCSA_EN

RichTek(PU4)

RT8241DGQW

RichTek(PU3)

RT8240BGQW

+1.5V_SUS

+VCCSA_CORE

TDC: 4.2A

Shapes: 168mil

Via: ?

DGPU_PWR_ON#

SIO_SLP_S3#

Load Switch(Q4)

AON7410

For dGPU only For dGPU only

+1.5V_GFX

TDC: 7.9A

Shapes: 40mil

For dGPU

Via: ?

+1.5V_CPU

TDC: 5A

Shapes: 200mil

Via: ?

+1.05V_PCH

Load Switch(PQ28)

MDV1522URH

TDC: 13.4A

Shapes: 415.6mil

Via: ?

+1.05V_GFX

TDC: 2.7A

Shapes: 40mil

Via: ?

+3.3V_RUN

DGFX_VR_PWRGD

IMVP_VR_ON

ON(PU7)

NCP6132A

PQ34 PQ35 PQ36

+VCC_CORE

TDC: 52A

Shapes: 1696mil

Via: ?

+VCC_iGFX_CORE

TDC: 38A

Shapes: 920mil

Via: ?

ON(PU10)

NCP3218MNR2G

+VCC_DGFX_CORE

TDC: 60A

Shapes: 1600mil

Via: ?

+3V_GFX

For dGPU only

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Power Block Diagram

Power Block Diagram

Power Block Diagram

Date: Sheet of

Wednesday, February 08, 2012 4 58

Date: Sheet of

Wednesday, February 08, 2012 4 58

Date: Sheet of

5

4

3

2

Wednesday, February 08, 2012 4 58

PROJECT :

R09A

R09A

R09A

3A

3A

3A

1

1

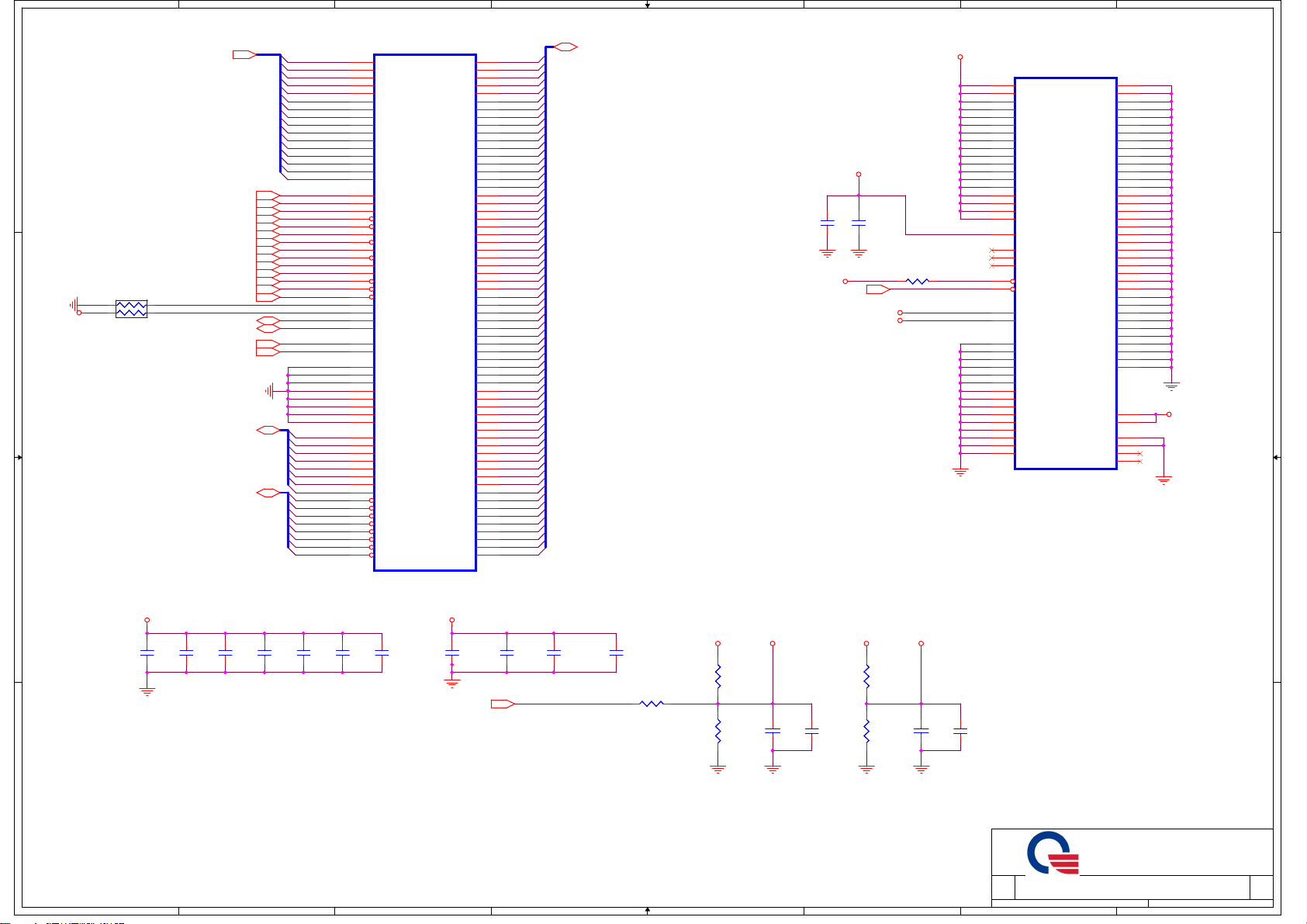

Battery Mode

+5V_ALW

+3.3V_ALW

A A

B B

C C

+5V_ALW

+3.3V_ALW

+1.5V_SUS

D D

SUS

SW

G

+PWR_SRC

DDR/0.75V

S3

S4

SLP_S3

SWITCH

G

+PWR_SRC

RUN PWR

SWITCH

G

+PWR_SRC

1.05V

VR

EN

1

PG

RC Delay

PG

2

+5V_SUS

+3.3V_SUS

SUS_ON

+1.5V_SUS

+DDR_VTTREF

+0.75V_DDR_VTT

1.5V_SUS_PWRGD

SIO_SLP_S3#

SIO_SLP_S4#

+1.5V_CPU+1.5V_SUS

SIO_SLP_S3#

+GFX_PWR_SRC

+5V_RUN

+3.3V_RUN

+1.5V_RUN

RUN_ON

+1.05V_PCH

1.05V_PCH_PWRGD

30

+3.3V_RUN

2

21

11

12

10

26

27

28

25

29

20

22

23

24

19

18

19

VCCSA_PWRGD

34

+5V_ALW

SVID

42

3

1.8V

VR

EN

+PWR_SRC

VCCSA

VR

EN

+PWR_SRC

IMVP

VR

3

EN

CPUPCH

35

HWPG

PG

PG

PG

IMVP_VR_ON

31

32

33

34

4

3

POWER_SW_IN0#

7

SUS_ON

10

+1.8V_RUN

VCCSA_EN

+VCCSA_CORE

VCCSA_PWRGD

VCCSA_EN

+VCC_CORE

+VCC_GFX_CORE

IMVP_PWRGD

43

47

44

36

4

SYS_PWR_SW#

RUN_ON

25

+3.3V_ALW

+1.5V_SUS

5

2

+5V_ALW2

PWR SW VR

3.3V_ALW_ON

4

6

ALW_ON

13

RSMRST#

ME_SUS_PWR_ACK

AC_PRESENT

EC

EC_PWROK

IMVP_VR_ON

3637

SIO_SLP_S5#17SIO_SLP_S4#18SIO_SLP_S3#

19

GPU PWR

15

SIO_PWRBTN#

16

35.2

+3V_GFX

SWITCH

G

DGPU_PWR_EN

+PWR_SRC

GPU

VR

EN

35.3

GPU PWR

SWITCH

G

PG

35.5

+VCC_DGFX_CORE

35.4

DGFX_VR_PWRGD

DGPU_VREN

35.6

35.7

DGFX_VR_PWRGD

+1.5V_GFX

+1.05V_GFX+1.05V_PCH

GPU

5

3V/5V

EN2

35.1

6

+PWR_SRC

14

38

44

37

38

37

6

+3.3V_ALW

+5V_ALW

+15V_ALW

EN1

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

PM_DRAM_PWRGD

PCH_CLK

SYS_PWROK

DGPU_PWR_EN

DGPU_VREN

SYS_PWROK

IMVP_PWRGD

EC_PWROK

PM_DRAM_PWRGD

EC_PWROK

46

PLTRST#

DGPU_HOLD_RST#

35.10

7

1

+VCHGR+PWR_SRC

8

5

8

9

17

19

39

35.1

CHARGER Battery

DPWROK

SUSWARN#

ACPRESENT

PWRBTN#

18

SLP_S5#

SLP_S3#

APWROK

DRAMPWROK

SYS_PWROK

PCH

35.3

35.8

GPIO17DGPU_PWROK

PROCPWRGD

35.10

H_PWRGOOD

41

45

DGPU_HOLD_RST#

40

U2

SM_SDRAMPWROK

SVID

42

47

GPU_RST#

GPU

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, February 08, 2012 5 58

Date: Sheet of

Wednesday, February 08, 2012 5 58

Date: Sheet of

Wednesday, February 08, 2012 5 58

7

PROJECT :

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

R09

8

46

UNCOREPWRGOOD

CPU

PLTRST#

RESET# PLTRST#

3A

3A

3A

5

4

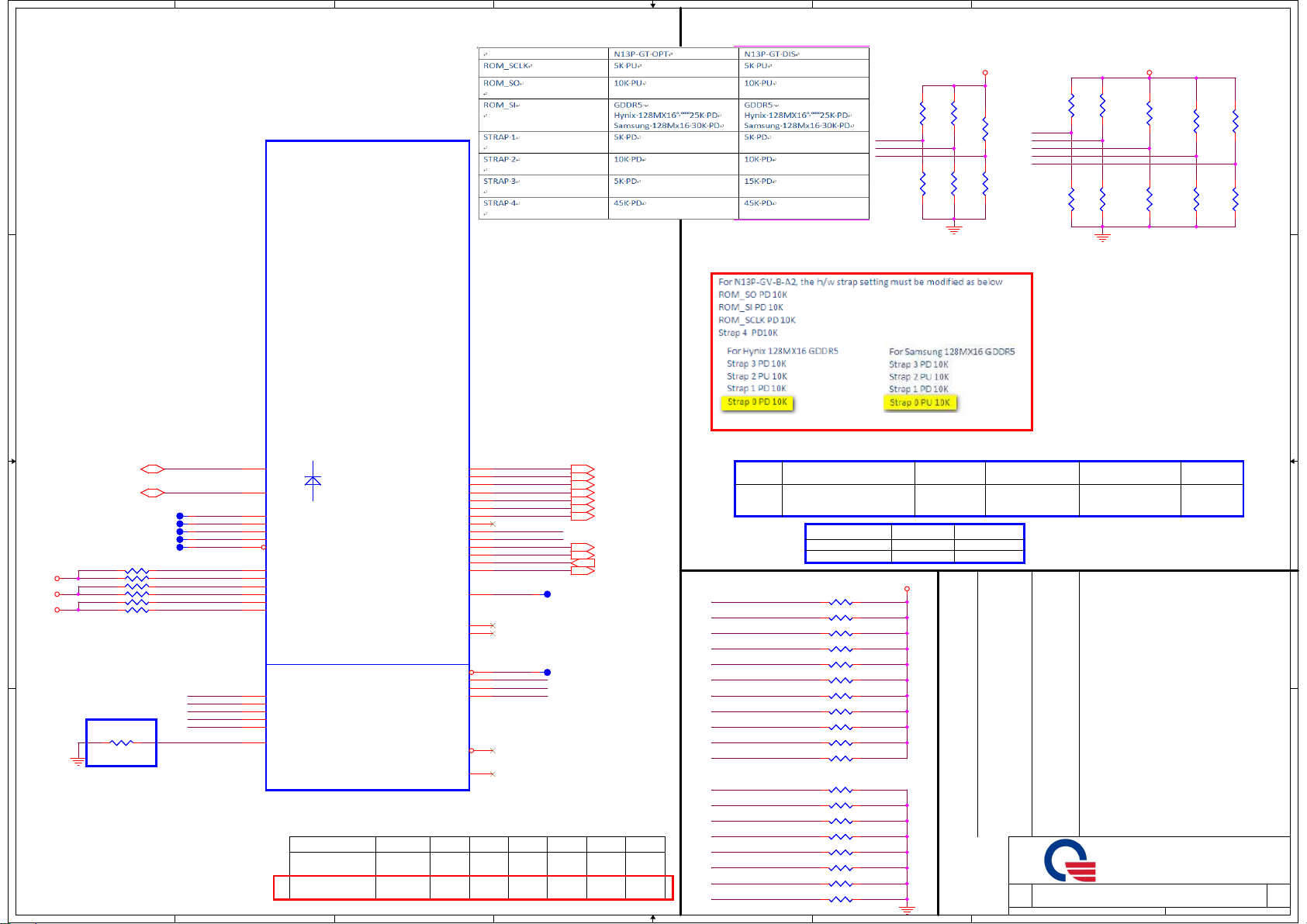

Ivy Bridge Processor (RESERVED, CFG)

3

2

1

DP & PEG Compensation

+1.05V_PCH

D D

U29A

U29A

DMI_TXN0[20]

DMI_TXN1[20]

DMI_TXN2[20]

DMI_TXN3[20]

DMI_TXP0[20]

DMI_TXP1[20]

DMI_TXP2[20]

DMI_TXP3[20]

DMI_RXN0[20]

DMI_RXN1[20]

DMI_RXN2[20]

DMI_RXN3[20]

DMI_RXP0[20]

DMI_RXP1[20]

DMI_RXP2[20]

DMI_RXP3[20]

C C

B B

eDP_ICOMPO 12mil

eDP_COMPIO 4mil

Programing Disable eDP interface(BIOS)

FDI_TXN0[20]

FDI_TXN1[20]

FDI_TXN2[20]

FDI_TXN3[20]

FDI_TXN4[20]

FDI_TXN5[20]

FDI_TXN6[20]

FDI_TXN7[20]

FDI_TXP0[20]

FDI_TXP1[20]

FDI_TXP2[20]

FDI_TXP3[20]

FDI_TXP4[20]

FDI_TXP5[20]

FDI_TXP6[20]

FDI_TXP7[20]

FDI_FSYNC0[20]

FDI_FSYNC1[20]

FDI_LSYNC0[20]

FDI_LSYNC1[20]

FDI_INT[20]

eDP_COMP

INT_eDP_HPD

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

FDI Disabling (Discrete Only)

FDI_INT

R190 0_4_DISR190 0_4_DIS

1 2

R200 0_4_DISR200 0_4_DIS

1 2

R185 0_4_DISR185 0_4_DIS

1 2

R197 0_4_DISR197 0_4_DIS

1 2

R184

R184

1K_4_DIS

1K_4_DIS

A A

DIS: POP

UMA/ OTP: NC

R186

R186

1K_4_DIS

1K_4_DIS

FDI_FSYNC can gang

all these 4

signals together

and tie them with

only one 1K

resistor to GND

(DG V0.5 Ch2.2.9).

5

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

4

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

VGA(U3)

N13P-GV

N13P-GT

PEG_ICOMPO 12mil

PEG_ICOMPI, PEG_RCOMPO 4mil,

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_COMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0_C

PEG_TXN1_C PEG_TXN1

PEG_TXN2_C

PEG_TXN3_C

PEG_TXN4_C

PEG_TXN5_C

PEG_TXN6_C

PEG_TXN7_C

PEG_TXN8_C

PEG_TXN9_C

PEG_TXN10_C

PEG_TXN11_C

PEG_TXN12_C

PEG_TXN13_C

PEG_TXN14_C

PEG_TXN15_C

PEG_TXP0_C

PEG_TXP1_C

PEG_TXP2_C

PEG_TXP3_C

PEG_TXP4_C

PEG_TXP5_C

PEG_TXP6_C

PEG_TXP7_C

PEG_TXP8_C

PEG_TXP9_C

PEG_TXP10_C

PEG_TXP11_C

PEG_TXP12_C

PEG_TXP13_C

PEG_TXP14_C

PEG_TXP15_C

C497 0.22U/16V_4C497 0.22U/16V_4

C496 0.22U/16V_4C496 0.22U/16V_4

C494 0.22U/16V_4C494 0.22U/16V_4

C490 0.22U/16V_4C490 0.22U/16V_4

C482 0.22U/16V_4C482 0.22U/16V_4

C484 0.22U/16V_4C484 0.22U/16V_4

C481 0.22U/16V_4C481 0.22U/16V_4

C474 0.22U/16V_4C474 0.22U/16V_4

C472 0.22U/16V_4C472 0.22U/16V_4

C467 0.22U/16V_4C467 0.22U/16V_4

C463 0.22U/16V_4C463 0.22U/16V_4

C461 0.22U/16V_4C461 0.22U/16V_4

C456 0.22U/16V_4C456 0.22U/16V_4

C455 0.22U/16V_4C455 0.22U/16V_4

C451 0.22U/16V_4C451 0.22U/16V_4

C452 0.22U/16V_4C452 0.22U/16V_4

C491 0.22U/16V_4C491 0.22U/16V_4

C495 0.22U/16V_4C495 0.22U/16V_4

C493 0.22U/16V_4C493 0.22U/16V_4

C489 0.22U/16V_4C489 0.22U/16V_4

C480 0.22U/16V_4C480 0.22U/16V_4

C486 0.22U/16V_4C486 0.22U/16V_4

C479 0.22U/16V_4C479 0.22U/16V_4

C471 0.22U/16V_4C471 0.22U/16V_4

C473 0.22U/16V_4C473 0.22U/16V_4

C465 0.22U/16V_4C465 0.22U/16V_4

C459 0.22U/16V_4C459 0.22U/16V_4

C460 0.22U/16V_4C460 0.22U/16V_4

C457 0.22U/16V_4C457 0.22U/16V_4

C454 0.22U/16V_4C454 0.22U/16V_4

C453 0.22U/16V_4C453 0.22U/16V_4

C450 0.22U/16V_4C450 0.22U/16V_4

PEG_RXN0 [13]

PEG_RXN1 [13]

PEG_RXN2 [13]

PEG_RXN3 [13]

PEG_RXN4 [13]

PEG_RXN5 [13]

PEG_RXN6 [13]

PEG_RXN7 [13]

PEG_RXN8 [13]

PEG_RXN9 [13]

PEG_RXN10 [13]

PEG_RXN11 [13]

PEG_RXN12 [13]

PEG_RXN13 [13]

PEG_RXN14 [13]

PEG_RXN15 [13]

PEG_RXP0 [13]

PEG_RXP1 [13]

PEG_RXP2 [13]

PEG_RXP3 [13]

PEG_RXP4 [13]

PEG_RXP5 [13]

PEG_RXP6 [13]

PEG_RXP7 [13]

PEG_RXP8 [13]

PEG_RXP9 [13]

PEG_RXP10 [13]

PEG_RXP11 [13]

PEG_RXP12 [13]

PEG_RXP13 [13]

PEG_RXP14 [13]

PEG_RXP15 [13]

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

0.22uF AC coupling Caps for PCIE GEN1/2/3 - GT

0.1uF AC coupling Caps for PCIE GEN1/2 - GV

AC coupling Cap

0.1uF

CAP CHIP 0.1U 16V(10%,X7R,0402)

0.22uF

CAP CHIP 0.22U 16V(10%,X7R,0402)

3

PN

CH4103K1B08

CH4223K1B00

PEG_TXN0

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

PEG_TXN0 [13]

PEG_TXN1 [13]

PEG_TXN2 [13]

PEG_TXN3 [13]

PEG_TXN4 [13]

PEG_TXN5 [13]

PEG_TXN6 [13]

PEG_TXN7 [13]

PEG_TXN8 [13]

PEG_TXN9 [13]

PEG_TXN10 [13]

PEG_TXN11 [13]

PEG_TXN12 [13]

PEG_TXN13 [13]

PEG_TXN14 [13]

PEG_TXN15 [13]

PEG_TXP0 [13]

PEG_TXP1 [13]

PEG_TXP2 [13]

PEG_TXP3 [13]

PEG_TXP4 [13]

PEG_TXP5 [13]

PEG_TXP6 [13]

PEG_TXP7 [13]

PEG_TXP8 [13]

PEG_TXP9 [13]

PEG_TXP10 [13]

PEG_TXP11 [13]

PEG_TXP12 [13]

PEG_TXP13 [13]

PEG_TXP14 [13]

PEG_TXP15 [13]

TX location RX location(page13)

C452,C451,C455,

C456,C461,C463,

C467,C472,C450,

C453,C454,C457,

C460,C459,C465,

C473

C125,C126,C147

C145,C123,C124

C152,C153,C121

C122,C151,C150

C119,C120,C149

C148

ALL ALL

2

eDP_COMP

R432 24.9/F_4R432 24.9/F_4

eDP_COMPIO and ICOMPO signals should

be shorted near balls and

routed within 500 mils

PEG_COMP

PEG_ICOMPI and RCOMPO signals should

be routed within 500 mils

PEG_ICOMPO signals should

be routed within 500 mils

1 2

+1.05V_PCH

R183 24.9/F_4R183 24.9/F_4

1 2

eDP Hot-plug (Disable)

+1.05V_PCH

R434

INT_eDP_HPD

CAD Note: Place PU resistor within 2 inches

of CPU

This signal can be left as no connect if

entire eDP interface is disabled.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Ivy Bridge 1/5

Ivy Bridge 1/5

Ivy Bridge 1/5

Monday, March 05, 2012

Monday, March 05, 2012

Monday, March 05, 2012

R434

12

*10K_4_NC

*10K_4_NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

R09A

R09A

R09A

6 58

6 58

6 58

3A

3A

3A

5

4

3

2

1

Ivy Bridge Processor (CLK,MISC,JTAG)

U29B

U29B

SNB_IVB# N.A at SNB EDS #27637 0.7v1

H_SNB_IVB#[23]

D D

IMVP7_PROCHOT#[38,53,55]

Over 130 degree C will

drive low

C C

H_CPUDET#[38]

PECI_EC[38]

H_PM_SYNC[20]

H_PWRGOOD[25]

PLTRST#[13,23,38,41,57]

PECI_EC

IMVP7_PROCHOT#

PM_THRMTRIP#[25]

H_PWRGOOD

R146 1.5K/F_4R146 1.5K/F_4

H_SNB_IVB#

H_CPUDET#

TP10TP10

CATERR#

R150 43_4R150 43_4

1 2

R151 56_4R151 56_4

1 2

PM_THRMTRIP#

12

R13610K_4 R13610K_4

12

SM_DRAMPWROK

CPU_PLTRST#_RPLTRST#

12

R147

R147

750/F_4

750/F_4

PECI_EC_R

H_PROCHOT#

C26

PROC_SELECT#

AN34

SKTOCC#

AL33

CATERR#

AN33

PECI

AL32

PROCHOT#

AN32

THERMTRIP#

AM34

PM_SYNC

AP33

UNCOREPWRGOOD

V8

SM_DRAMPWROK

AR33

RESET#

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

CLOCKS

CLOCKS

DDR3

DDR3

JTAG & BPM

JTAG & BPM

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

MISC

MISC

A28

BCLK

A27

BCLK#

CLK_DP_P_R

A16

CLK_DP_N_R

A15

CPU_DRAMRST#

R8

SM_RCOMP_0

AK1

SM_RCOMP_1

A5

SM_RCOMP_2

A4

SM_RCOMP_0, SM_RCOMP_1 20mil / SM_RCOMP_2 15mil.

AP29

PRDY#

AP27

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

XDP_TCLK

AR26

XDP_TMS

AR27

XDP_TRST#H_PM_SYNC

AP30

XDP_TDI XDP_TDO

AR28

XDP_TDO

AP26

XDP_DBRST#

AL35

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

CLK_CPU_BCLKP

CLK_CPU_BCLKN

R436 1K_4R436 1K_4

1 2

R438 1K_4R438 1K_4

1 2

R236 140/F_4R236 140/F_4

1 2

R231 25.5/F_4R231 25.5/F_4

1 2

R230 200/F_4R230 200/F_4

1 2

TP3TP3

TP5TP5

TP7TP7

TP6TP6

TP4TP4

+3.3V_RUN

1 2

R152 1K_4R152 1K_4

CLK_CPU_BCLKP [24]

CLK_CPU_BCLKN [24]

+1.05V_PCH

For internal eDP (Disable)

XDP_TMS

XDP_TDI

IMVP7_PROCHOT#

XDP_TCLK

XDP_TRST#

+1.05V_PCH

R142 *51_4_NCR142 *51_4_NC

R143 *51_4_NCR143 *51_4_NC

R141 *51_4_NCR141 *51_4_NC

R139 62_4R139 62_4

R129 *51_4_NCR129 *51_4_NC

R144 *51_4_NCR144 *51_4_NC

1 2

1 2

12

12

12

12

Intel spec VinH min =VCCIO X 0.7

B B

Boot S3

S3 RSM

+1.5V_CPU

DRAM_PWRGD

SYS_PWROK

100 ns after +1.5V_CPU

reaches 80%

Follow #DG1.5 471984 P130

DRAMRST# Routing Illustration

+1.5V_SUS

SM_DRAMPWROK

Follow #DG1.5 471984 P119

Follow #DG1.5 471984 P128

DDR Power Gating Topology

A A

PM_DRAM_PWRGD[20]

EC_PWROK[20,38]

PM_DRAM_PWRGD

+3.3V_SUS

12

R460

R460

200_4

200_4

2

1

U30

U30

74AHC1G09GW

74AHC1G09GW

3 5

12

C585

C585

0.1U/16V_4

0.1U/16V_4

4

+1.5V_CPU

R229

R229

200_4

200_4

1 2

R225 130_4R225 130_4

1 2

SM_DRAMPWROKSM_DRAMPWROK_R

DDR3_DRAMRST#[11,12]

DDR_HVREF_RST_PCH[9,24]

R464 1K_4R464 1K_4

DDR_HVREF_RST_PCH

when 1,2 is high, 4 is high-impedance OFF-state

5

4

3

2

12

+3.3V_SUS

1 2

R462 1K_4R462 1K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Ivy Bridge 2/5

Ivy Bridge 2/5

Ivy Bridge 2/5

Friday, March 02, 2012

Friday, March 02, 2012

Friday, March 02, 2012

Q45

Q45

R463

R463

2N7002W

2N7002W

1K_4

1K_4

1 2

3 1

2

12

C586

C586

0.047U/10V_4

0.047U/10V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

12

R461

R461

4.99K/F_4

4.99K/F_4

R09A

R09A

R09A

7 58

7 58

7 58

CPU_DRAMRST#DDR3_DRAMRST#_RDDR3_DRAMRST#

3A

3A

3A

5

4

3

2

1

Ivy Bridge Processor (DDR3)

U29D

D10

K10

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

C9

A7

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

K9

J10

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

R6

J7

J8

J9

U29D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

M_B_CLKP0

AE2

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CLK[2]

SB_CLK#[2]

SB_CKE[2]

SB_CLK[3]

SB_CLK#[3]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

M_B_CLKN0

M_B_CKE0

M_B_CLKP1

M_B_CLKN1

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_ODT0

M_B_ODT1

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLKP0 [12]

M_B_CLKN0 [12]

M_B_CKE0 [12]

M_B_CLKP1 [12]

M_B_CLKN1 [12]

M_B_CKE1 [12]

M_B_CS#0 [12]

M_B_CS#1 [12]

M_B_ODT0 [12]

M_B_ODT1 [12]

M_B_DQSN[7..0] [12]

M_B_DQSP[7..0] [12]

M_B_A[15..0] [12]

U29C

U29C

D D

C C

B B

M_A_DQ[63..0][11]

M_A_BS0[11]

M_A_BS1[11]

M_A_BS2[11]

M_A_CAS#[11]

M_A_RAS#[11]

M_A_WE#[11]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CAS#

M_A_RAS#

M_A_WE#

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

AF9

F10

AJ5

AJ6

AJ8

AJ9

C5

D5

D3

D2

D6

C6

C2

C3

F8

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

M8

N8

N7

M9

N9

M7

V6

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_CLK#[0]

SA_CLK#[1]

SA_CLK#[2]

SA_CLK#[3]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CLK[0]

SA_CKE[0]

SA_CLK[1]

SA_CKE[1]

SA_CLK[2]

SA_CKE[2]

SA_CLK[3]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

M_A_CLKN0

M_A_CKE0

M_A_CLKP1

M_A_CLKN1

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_ODT0

M_A_ODT1

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLKP0 [11]

M_A_CLKN0 [11]

M_A_CKE0 [11]

M_A_CLKP1 [11]

M_A_CLKN1 [11]

M_A_CKE1 [11]

M_A_CS#0 [11]

M_A_CS#1 [11]

M_A_ODT0 [11]

M_A_ODT1 [11]

M_A_DQSN[7..0] [11]

M_A_DQSP[7..0] [11]

M_A_A[15..0] [11]

M_A_CLKP0

M_B_DQ[63..0][12]

M_B_BS0[12]

M_B_BS1[12]

M_B_BS2[12]

M_B_CAS#[12]

M_B_RAS#[12]

M_B_WE#[12]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS0

M_B_BS1

M_B_BS2

M_B_CAS#

M_B_RAS#

M_B_WE#

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

A A

5

4

3

Ivy Bridge_rPGA_2DPC_Rev0p61

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, February 08, 2012

Date: Sheet of

Wednesday, February 08, 2012

Date: Sheet of

Wednesday, February 08, 2012

PROJECT :

Ivy Bridge 3/5

Ivy Bridge 3/5

Ivy Bridge 3/5

1

R09A

R09A

R09A

8 58

8 58

8 58

3A

3A

3A

5

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

12

10U/6.3V_6

10U/6.3V_6

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

CPU Core Power

IVY, SNB: 35W ~ 53A

IVY, SNB: 45W ~ 94A

10F x24

C216

C216

C210

C210

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

C523

C523

C209

C209

12

10U/6.3V_6

10U/6.3V_6

C524

C524

C186

C186

12

10U/6.3V_6

10U/6.3V_6

C528

C528

C527

C527

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

C206

C206

C187

C187

12

10U/6.3V_6

10U/6.3V_6

C529

C529

C188

C188

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

C184

C184

C220

C220

12

10U/6.3V_6

10U/6.3V_6

C545

C545

C183

C183

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

5

+VCC_CORE

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

12

10U/6.3V_6

10U/6.3V_6

VR_SVID_CLK

U29F

U29F

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

VR_SVID_CLK [53]

POWER

POWER

CORE SUPPLY

CORE SUPPLY

SENSE LINES SVID

SENSE LINES SVID

Place PU resistor close to CPU

+1.05V_PCH +1.05V_PCH

35W

16pcs

45W 24pcs

C224

C224

C205

C205

12

D D

*10U/6.3V_6_NC

*10U/6.3V_6_NC

C208

C208

C207

C207

12

10U/6.3V_6

10U/6.3V_6

C537

C537

C222

C222

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

C526

C526

C525

C525

12

10U/6.3V_6

10U/6.3V_6

C C

C535

C535

C556

C556

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

C555

C555

C185

C185

12

10U/6.3V_6

10U/6.3V_6

C225

C225

C534

C534

12

*10U/6.3V_6_45W_NC

*10U/6.3V_6_45W_NC

B B

A A

Layout note: need routing

together and ALERT need

between CLK and DATA

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

PEG AND DDR

PEG AND DDR

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SVID DATA SVID ALERTSVID CLK

12

R148

130_4

130_4

4

4

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

1.05V_PCH

SNB: 8.5A

IVY: 8.5A

10F x12

C564

C564

C227

C227

H_CPU_SVIDALRT#

VR_SVID_CLK

VR_SVID_DATA

R155 100/FR155 100/F

R156 100/FR156 100/F

1 2

R445 10_4R445 10_4

1 2

R447 10_4R447 10_4

VR_SVID_DATA [53]

+1.05V_PCH

C228

C228

10U/6.3V_6

10U/6.3V_6

12

12

10U/6.3V_6

10U/6.3V_6

C230

C230

10U/6.3V_6

10U/6.3V_6

12

12

10U/6.3V_6

10U/6.3V_6

SMDDR_VREF_DQ0_M3_C

*AP2302GN_NC

*AP2302GN_NC

SMDDR_VREF_DQ1_M3_C

*AP2302GN_NC

*AP2302GN_NC

+VCC_CORE

VCCSENSE

VSSSENSE

+1.05V_PCH

VCCIO_SENSE

VSSIO_SENSE

C229

C229

*10U/6.3V_6_NC

*10U/6.3V_6_NC

12

C231

C231

12

10U/6.3V_6

10U/6.3V_6

C567

C567

C566

C566

Q43

Q43

2

2

Q44

Q44

3

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

12

10U/6.3V_6

10U/6.3V_6

+1.8V_RUN

CPU VCCPL

SNB: 1.2A

IVY: 1.2A

10uF x 1

M3 VREF

SMDDR_VREF_DQ0_M3

31

DDR_HVREF_RST_PCH

SMDDR_VREF_DQ1_M3

31

1uF x 2

Vgs=2.5V Rds=115m

VCCSENSE [53]

VSSSENSE [53]

VCCIO_SENSE [51]

VSSIO_SENSE [51]

Place PU resistor close to CPU

1 2

R149 43_4R149 43_4

3

CPU VGT

SNB: 33A

IVY: 33A

10uF x 12

+VCC_GFX_CORE

OTP/UMA

C548

C548

*10U/6.3V_6_NC

*10U/6.3V_6_NC

12

C221

C221

12

0_6

0_6

C223

C223

12

0_6

0_6

CS00003J951

RESISTOR CHIP 0 1/10W+-5%(0603)

UMA/OPT

10uF

CH6101M9905

CAP CHIP 10U 6.3V(+-20%,X5R,0603)

12

C596

C596

*10U/6.3V_6_NC

*10U/6.3V_6_NC

SMDDR_VREF_DQ0_M3 [11]

DDR_HVREF_RST_PCH [7,24]

SMDDR_VREF_DQ1_M3 [12]

R138

R138

75/F

75/FR148

VR_SVID_ALERT#H_CPU_SVIDALRT#VR_SVID_DATA

C539

C539

C202

C202

12

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

*10U/6.3V_6_NC

*10U/6.3V_6_NC

C554

C554

C536

C536

12

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

*10U/6.3V_6_NC

*10U/6.3V_6_NC

C213

C213

C217

C217

12

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

*10U/6.3V_6_NC

*10U/6.3V_6_NC

C221,C223,C2150 ohmDIS

C548,C202,C539,C530,C221,

C536,C554,C219,C223,C217,

C213,C215

12

12

C259

C259

C569

C569

10U/6.3V_6

10U/6.3V_6

1U/6.3V_4

1U/6.3V_4

VR_SVID_ALERT# [53]

2

Ivy Bridge Processor (GRAPHIC POWER)

POWER

POWER

1.8V RAIL

1.8V RAIL

+5V_ALW

12

34

5

2

GRAPHICS

GRAPHICS

R242

R242

10K_4

10K_4

Q19A

Q19A

DMN66D0LDW-7

DMN66D0LDW-7

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

SA_DIMM_VREFDQ

VREFMISC

VREFMISC

SB_DIMM_VREFDQ

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

VCCIO_SEL

PS_S3CNTRL

C273 0.1U/16V_4C273 0.1U/16V_4

1 2

C276 0.1U/16V_4C276 0.1U/16V_4

1 2

C275 0.1U/16V_4C275 0.1U/16V_4

1 2

C274 0.1U/16V_4C274 0.1U/16V_4

1 2

SM_VREF

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

R153 *100_4_UO_NCR153 *100_4_UO_NC

AK35

AK34

R154 *100_4_UO_NCR154 *100_4_UO_NC

+VDDR_REF_CPU

AL1

CAD Note: +VDDR_REF_CPU should

have 10 mil trace width

B4

D1

R458

R458

*1K_4_NC

*1K_4_NC

1 2

AF7

AF4

AF1

C258

C258

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

C254

C254

U1

P7

P4

P1

M27

M26

L26

J26

J25

J24

H26

H25

1 2

R180 100_4R180 100_4

H23

VCCSA_VID0

C22

VCCSA_VID1

C24

A19

1 2

+15V_ALW

PS_S3CNTRL [11]

2

C530

C530

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

C219

C219

12

*10U/6.3V_6_NC

*10U/6.3V_6_NC

C215

C215

12

0_6

0_6

12

C256

C256

*1U/6.3V_4_NC

*1U/6.3V_4_NC

SIO_SLP_S3#[20,38,49]

U29G

U29G

AT24

VAXG1

AT23

VAXG2

AT21

VAXG3

AT20

VAXG4

AT18

VAXG5

AT17

VAXG6

AR24

VAXG7

AR23

VAXG8

AR21

VAXG9

AR20

VAXG10

AR18

VAXG11

AR17

VAXG12

AP24

VAXG13

AP23

VAXG14

AP21

VAXG15

AP20

VAXG16

AP18

VAXG17

AP17

VAXG18

AN24

VAXG19

AN23

VAXG20

AN21

VAXG21

AN20

VAXG22

AN18

VAXG23

AN17

VAXG24

AM24

VAXG25

AM23

VAXG26

AM21

VAXG27

AM20

VAXG28

AM18

VAXG29

AM17

VAXG30

AL24

VAXG31

AL23

VAXG32

AL21

VAXG33

AL20

VAXG34

AL18

VAXG35

AL17

VAXG36

AK24

VAXG37

AK23

VAXG38

AK21

VAXG39

AK20

VAXG40

AK18

VAXG41

AK17

VAXG42

AJ24

VAXG43

AJ23

VAXG44

AJ21

VAXG45

AJ20

VAXG46

AJ18

VAXG47

AJ17

VAXG48

AH24

VAXG49

AH23

VAXG50

AH21

VAXG51

AH20

VAXG52

AH18

VAXG53

AH17

VAXG54

B6

VCCPLL1

A6

VCCPLL2

A2

VCCPLL3

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

SIO_SLP_S3#

1

OTP/UMA : POP

DIS : NC

1 2

1 2

SMDDR_VREF_DQ0_M3_C

SMDDR_VREF_DQ1_M3_C

R459

R459

*1K_4_NC

*1K_4_NC

1 2

C253

C253

12

10U/6.3V_6

10U/6.3V_6

C260

C260

12

10U/6.3V_6

10U/6.3V_6

12

C214

C214

10U/6.3V_6

10U/6.3V_6

VCCSA_SENSE

R429*0_4_NC R429*0_4_NC

VCCSA_VID0

VCCSA_VID1

12

R241

R241

100K_4

100K_4

PS_S3CNTRL_S

61

Q19B

Q19B

DMN66D0LDW-7

DMN66D0LDW-7

+1.5V_CPU+1.5V_SUS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VCC_GFX_CORE

VCC_AXG_SENSE [53]

VSS_AXG_SENSE [53]

For internal GFX

+VDDR_REF_CPU

CPU MCH

SNB: 5A

IVY: 5A

10uF x 6

C262

C262

C257

C257

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

CPU SA

SNB: 6A

IVY: 6A

12

12

C522

C522

10U/6.3V_6

10U/6.3V_6

+VCCSA_CORE

VCCSA_SENSE [52]

VCCSA_VID0 [52]

VCCSA_VID1 [52]

H_VTTVID1

1 2

R179 1K_4R179 1K_4

1 2

R176 1K_4R176 1K_4

S3 Power reduce

+1.5V_SUS +1.5V_CPU

Q20

12

EC101

EC101

2200P/50V_4

2200P/50V_4

Take care Q20 Vgs(MAX)=2.5

Q20

AON7410

AON7410

8

762

5

C272

C272

*4700P/25V_4_NC

*4700P/25V_4_NC

+VDDR_REF_CPU

+1.5V_CPU

R228

R228

1K/F_4

1K/F_4

1 2

R235

R235

1K/F_4

1K/F_4

1 2

Ivy Bridge 4/5

Ivy Bridge 4/5

Ivy Bridge 4/5

Monday, March 05, 2012

Monday, March 05, 2012

Monday, March 05, 2012

+1.5V_CPU

12

10U/6.3V_6

10U/6.3V_6

10uF x 3

+VCCSA_CORE

C203

C203

1U/25V_6

1U/25V_6

item18

+3.3V_RUN

12

R428

R428

10K_4

10K_4

R34 and R36 pull-down 1K

Spec:This will ensure the

VID is 00 prior to VCCIO stability.

5A

3

1

4

12

12

0.1U/16V_4

0.1U/16V_4

C263

C263

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

R09A

R09A

R09A

H_VTTVID1 [51]

9 58

9 58

9 58

3A

3A

3A

5

4

3

2

1

Ivy Bridge Processor (GND) Ivy Bridge Processor (RESERVED, CFG)

U29I

U29H

U29H

AT35

VSS1

AT32

VSS2

AT29

VSS3

AT27

VSS4

AT25

VSS5

AT22

VSS6

AT19

VSS7

AT16

VSS8

D D

C C

B B

A A

AT13

VSS9

AT10

VSS10

AT7

VSS11

AT4

VSS12

AT3

VSS13

AR25

VSS14

AR22

VSS15

AR19

VSS16

AR16

VSS17

AR13

VSS18

AR10

VSS19

AR7

VSS20

AR4

VSS21

AR2

VSS22

AP34

VSS23

AP31

VSS24

AP28

VSS25

AP25

VSS26

AP22

VSS27

AP19

VSS28

AP16

VSS29

AP13

VSS30

AP10

VSS31

AP7

VSS32

AP4

VSS33

AP1

VSS34

AN30

VSS35

AN27

VSS36

AN25

VSS37

AN22

VSS38

AN19

VSS39

AN16

VSS40

AN13

VSS41

AN10

VSS42

AN7

VSS43

AN4

VSS44

AM29

VSS45

AM25

VSS46

AM22

VSS47

AM19

VSS48

AM16

VSS49

AM13

VSS50

AM10

VSS51

AM7

VSS52

AM4

VSS53

AM3

VSS54

AM2

VSS55

AM1

VSS56

AL34

VSS57

AL31

VSS58

AL28

VSS59

AL25

VSS60

AL22

VSS61

AL19

VSS62

AL16

VSS63

AL13

VSS64

AL10

VSS65

AL7

VSS66

AL4

VSS67

AL2

VSS68

AK33

VSS69

AK30

VSS70

AK27

VSS71

AK25

VSS72

AK22

VSS73

AK19

VSS74

AK16

VSS75

AK13

VSS76

AK10

VSS77

AK7

VSS78

AK4

VSS79

AJ25

VSS80

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

5

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

U29I

T35

VSS161

T34

VSS162

T33

VSS163

T32

VSS164

T31

VSS165

T30

VSS166

T29

VSS167

T28

VSS168

T27

VSS169

T26

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

N35

VSS177

N34

VSS178

N33

VSS179

N32

VSS180

N31

VSS181

N30

VSS182

N29

VSS183

N28

VSS184

N27

VSS185

N26

VSS186

M34

VSS187

L33

VSS188

L30

VSS189

L27

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

K35

VSS199

K32

VSS200

K29

VSS201

K26

VSS202

J34

VSS203

J31

VSS204

H33

VSS205

H30

VSS206

H27

VSS207

H24

VSS208

H21

VSS209

H18

VSS210

H15

VSS211

H13

VSS212

H10

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

G35

VSS223

G32

VSS224

G29

VSS225

G26

VSS226

G23

VSS227

G20

VSS228

G17

VSS229

G11

VSS230

F34

VSS231

F31

VSS232

F29

VSS233

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

VSS

VSS

Processor Strapping

CFG2

(PCI-E Static x16 Lane Reversal)

CFG4

(DP Presence Strap)

4

F22

VSS234

F19

VSS235

E30

VSS236

E27

VSS237

E24

VSS238

E21

VSS239

E18

VSS240

E15

VSS241

E13

VSS242

E10

VSS243

E9

VSS244

E8

VSS245

E7

VSS246

E6

VSS247

E5

VSS248

E4

VSS249

E3

VSS250

E2

VSS251

E1

VSS252

D35

VSS253

D32

VSS254

D29

VSS255

D26

VSS256

D20

VSS257

D17

VSS258

C34

VSS259

C31

VSS260

C28

VSS261

C27

VSS262

C25

VSS263

C23

VSS264

C10

VSS265

C1

VSS266

B22

VSS267

B19

VSS268

B17

VSS269

B15

VSS270

B13

VSS271

B11

VSS272

B9

VSS273

B8

VSS274

B7

VSS275

B5

VSS276

B3

VSS277

B2

VSS278

A35

VSS279

A32

VSS280

A29

VSS281

A26

VSS282

A23

VSS283

A20

VSS284

A3

VSS285

GV - R470 POP

GT, UMA - ALL NC

The CFG signals have a default value of '1' if not terminated on the board.

1 0

Normal Operation

Disable; No physical DP attached to eDP

3

TP17TP17

TP20TP20

CFG2

TP16TP16

TP18TP18

CFG5

CFG6

TP8TP8

TP9TP9

R470 *1K_4_GV_NCR470 *1K_4_GV_NC

R471 *1K_4_NCR471 *1K_4_NC

12

12

Lane Reversed

CFG2

R145 1K_4R145 1K_4

Enable; An ext DP device is connected to eDP

U29E

U29E

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

CFG[6:5] (PCIE Port Bifurcation Straps)

CFG5

11: (Default) 1x16 PCI Express*

CFG6

10: 2x8 PCI Express*

01: Reserved

00: 1x8, 2x4 PCI Express*

12

2

CFG

CFG

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

RESERVED

RESERVED

VCC_DIE_SENSE

VSS_DIE_SENSE

#27636 SNB EDS0.7v1 no function.

AN35

BCLK_ITP

AM35

BCLK_ITP#

AT2

RSVD56

AT1

RSVD57

AR1

RSVD58

B1

KEY

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Saturday, March 03, 2012

Date: Sheet of

Saturday, March 03, 2012

Date: Sheet of

Saturday, March 03, 2012

PROJECT :

Ivy Bridge 5/5

Ivy Bridge 5/5

Ivy Bridge 5/5

1

R09A

R09A

R09A

10 58

10 58

10 58

3A

3A

3A

1

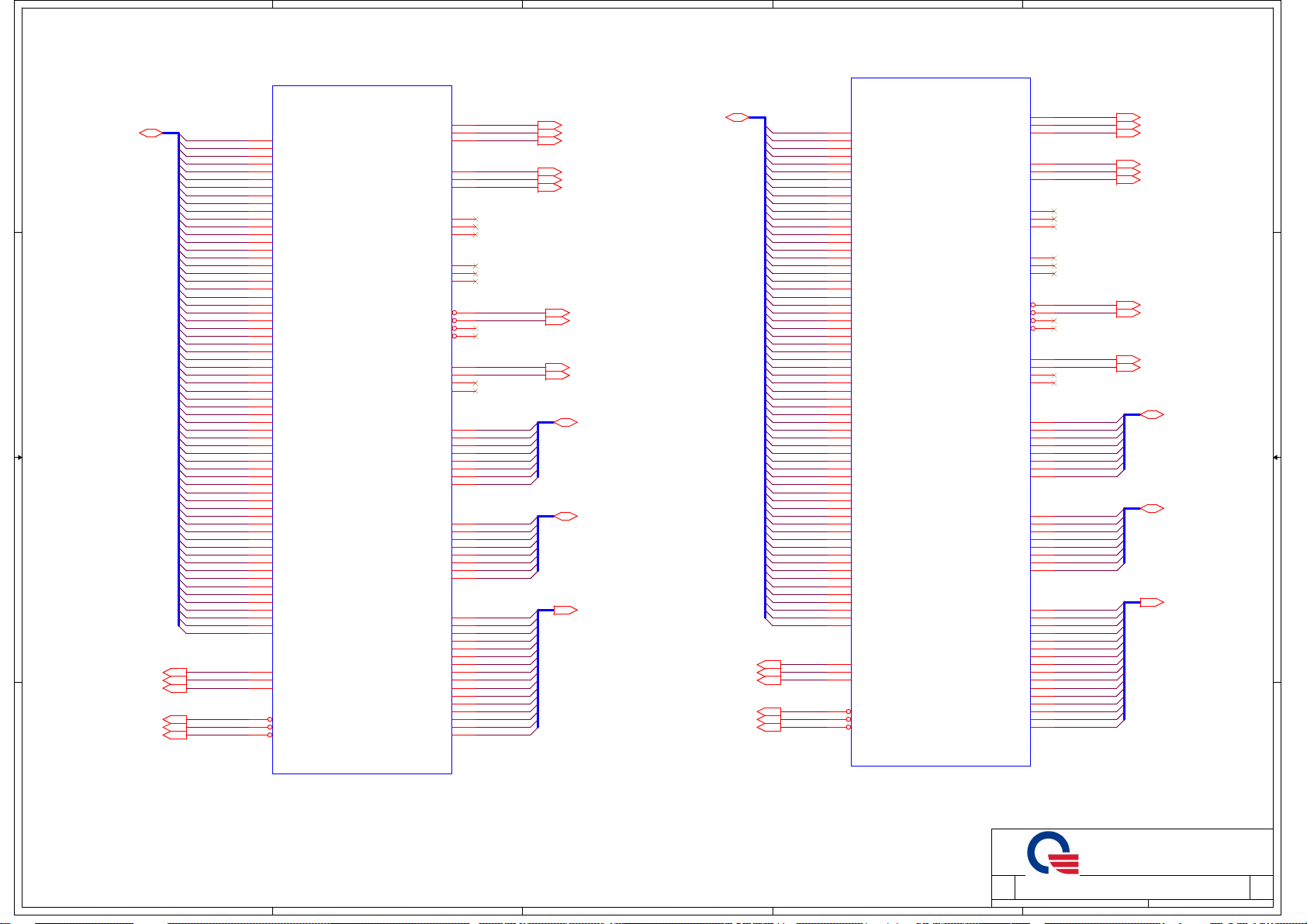

M_A_A[15..0][8]

A A

M_A_BS0[8]

M_A_BS1[8]

M_A_BS2[8]

M_A_CS#0[8]

M_A_CS#1[8]

M_A_CLKP0[8]

M_A_CLKN0[8]

M_A_CLKP1[8]

M_A_CLKN1[8]

M_A_CKE0[8]

M_A_CKE1[8]

M_A_CAS#[8]

RP21 10KX2RP21 10KX2

1

3

B B

C C

+1.5V_SUS

12

12

C313

C313

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

M_A_RAS#[8]

M_A_WE#[8]

2

4

WLAN_SCLK[12,24,33]

WLAN_SDATA[12,24,33]

M_A_ODT0[8]

M_A_ODT1[8]

M_A_DQSP[7..0][8]

M_A_DQSN[7..0][8]

Place these Caps near So-Dimm0.

C290

C290

12

C339

C339

0.1U/16V_4

0.1U/16V_4

12

0.1U/16V_4

0.1U/16V_4

C341

C341

2

C289

C289

12

10U/6.3V_8

10U/6.3V_8

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CS#0

M_A_CS#1

M_A_CLKP0

M_A_CLKN0

M_A_CLKP1

M_A_CLKN1

M_A_CKE0

M_A_CKE1

M_A_CAS#

M_A_RAS#

M_A_WE#

DIMM0_SA0

DIMM0_SA1

WLAN_SCLK

WLAN_SDATA

M_A_ODT0

M_A_ODT1

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

C317

C317

12

10U/6.3V_8

10U/6.3V_8

SMDDR_VREF_DQ0_M3[9]

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

114

121

101

103

102

104

73

74

115

110

113

197

201

202

200

116

120

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

C318

C318

12

10U/6.3V_8

10U/6.3V_8

JDIM1A

JDIM1A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

BA0

BA1

BA2

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DDRRK-20401-TP9D

DDRRK-20401-TP9D

+0.75V_DDR_VTT

12

C295

C295

1U/6.3V_4

1U/6.3V_4

SMDDR_VREF_DQ0_M3

M3 VREF

3

M_A_DQ5

5

DQ0

M_A_DQ4

7

DQ1

M_A_DQ7

15

DQ2

M_A_DQ6

17

DQ3

M_A_DQ1

4

DQ4

M_A_DQ0

6

DQ5

M_A_DQ3

16

DQ6

M_A_DQ2

18

DQ7

M_A_DQ8

21

DQ8

M_A_DQ9

23

DQ9

M_A_DQ15

33

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

(204P)

(204P)

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

M_A_DQ10

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ14

M_A_DQ20

M_A_DQ21

M_A_DQ18

M_A_DQ19

M_A_DQ16

M_A_DQ17

M_A_DQ23

M_A_DQ22

M_A_DQ29

M_A_DQ25

M_A_DQ27

M_A_DQ31

M_A_DQ28

M_A_DQ24

M_A_DQ26

M_A_DQ30

M_A_DQ36

M_A_DQ37

M_A_DQ34

M_A_DQ39

M_A_DQ32

M_A_DQ33

M_A_DQ38

M_A_DQ35

M_A_DQ45

M_A_DQ44

M_A_DQ42

M_A_DQ43

M_A_DQ41

M_A_DQ40

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ54

M_A_DQ55

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ61

M_A_DQ60

M_A_DQ62

M_A_DQ63

M_A_DQ56

M_A_DQ57

M_A_DQ59

M_A_DQ58

4

M_A_DQ[63..0] [8]

H=9.2mm,RVS

S3 Power reduce

+0.75V_DDR_VTT

R250

R250

22_4

22_4

1 2

Q22

Q22

31

PS_S3CNTRL

2

2N7002W

2N7002W

5

*2.2U/6.3V_6_NC

*2.2U/6.3V_6_NC

PS_S3CNTRL [9]

C602

C602

+3.3V_RUN

DDR3_DRAMRST#[7,12]

+SMDDR_VREF_DQ0

+SMDDR_VREF_DIMM0

6

+1.5V_SUS

+3.3V_RUN

12

12

C322

C322

0.1U/16V_4

0.1U/16V_4

R246 *10K_4_NCR246 *10K_4_NC

1 2

DDR3_DRAMRST#

7

JDIM1B

JDIM1B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

DDRRK-20401-TP9D

DDRRK-20401-TP9D

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

(204P)

(204P)

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

8

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

205

G1

206

G2

207

H1

208

H2

+0.75V_DDR_VTT

M1 VREF

12

C304

C304

1U/6.3V_4

1U/6.3V_4

+1.5V_SUS

1 2

1 2

R248

R248

1K/F_4

1K/F_4

R247

R247

1K/F_4

1K/F_4

+SMDDR_VREF_DIMM0

12

C288

C288

0.1U/16V_4

0.1U/16V_4

12

C287

C287

1U/6.3V_4

1U/6.3V_4

12

C332

C332

1U/6.3V_4

1U/6.3V_4

12

C597

C597

*1U/6.3V_4_NC

*1U/6.3V_4_NC

R255 *0_4_NCR255 *0_4_NC

12

1 2

C598

C598

*1U/6.3V_4_NC