Page 1

1

2

3

4

5

6

7

8

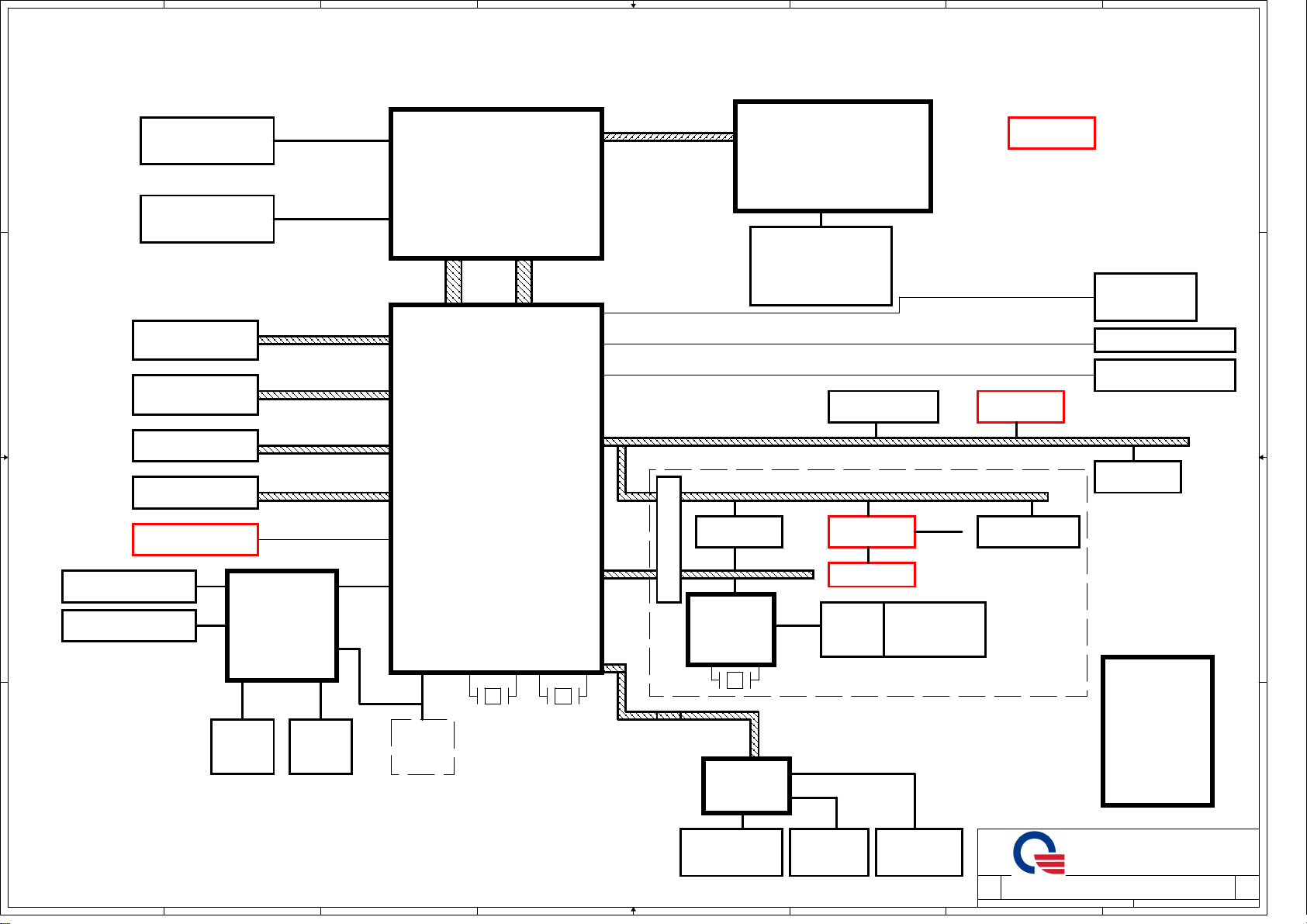

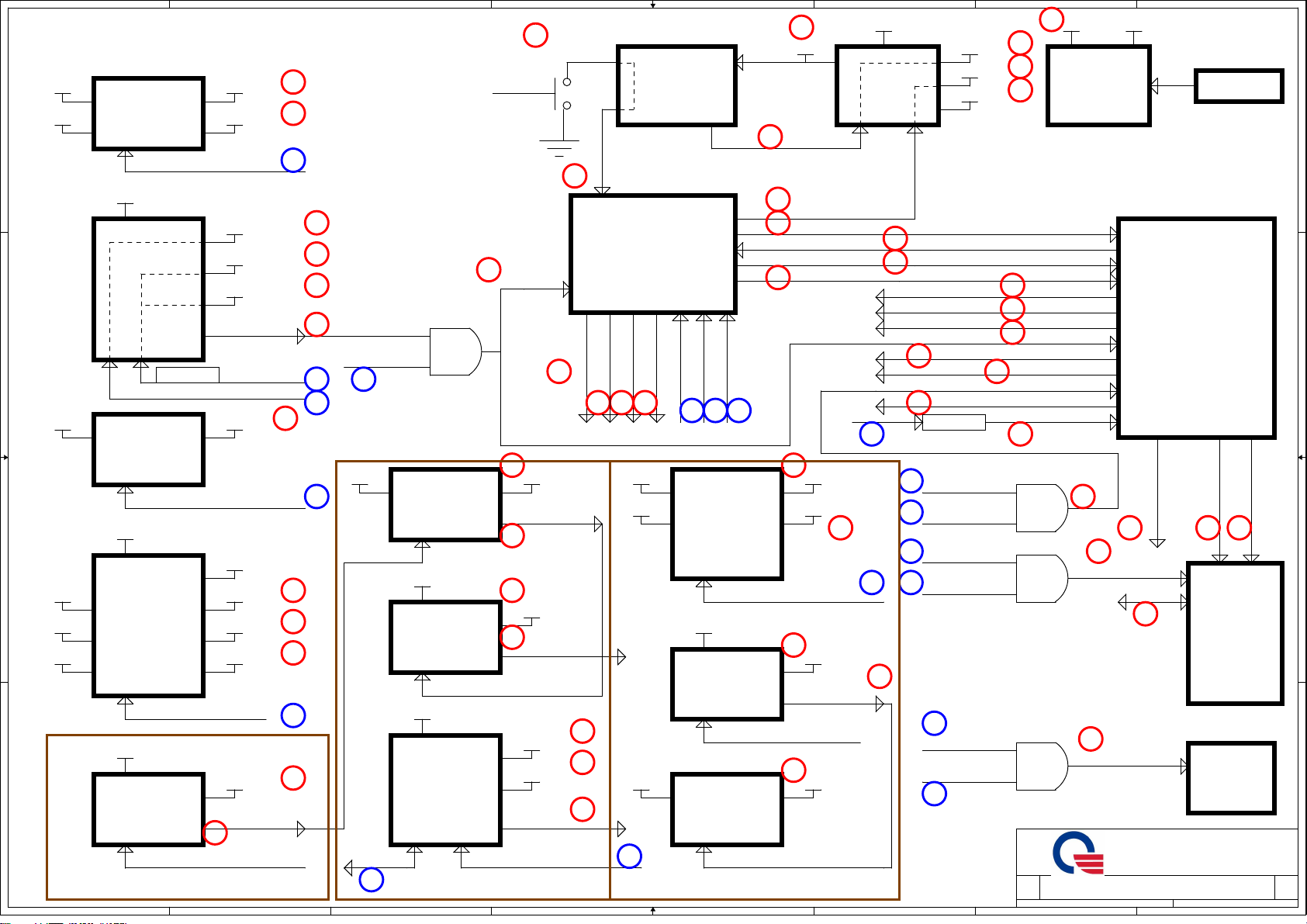

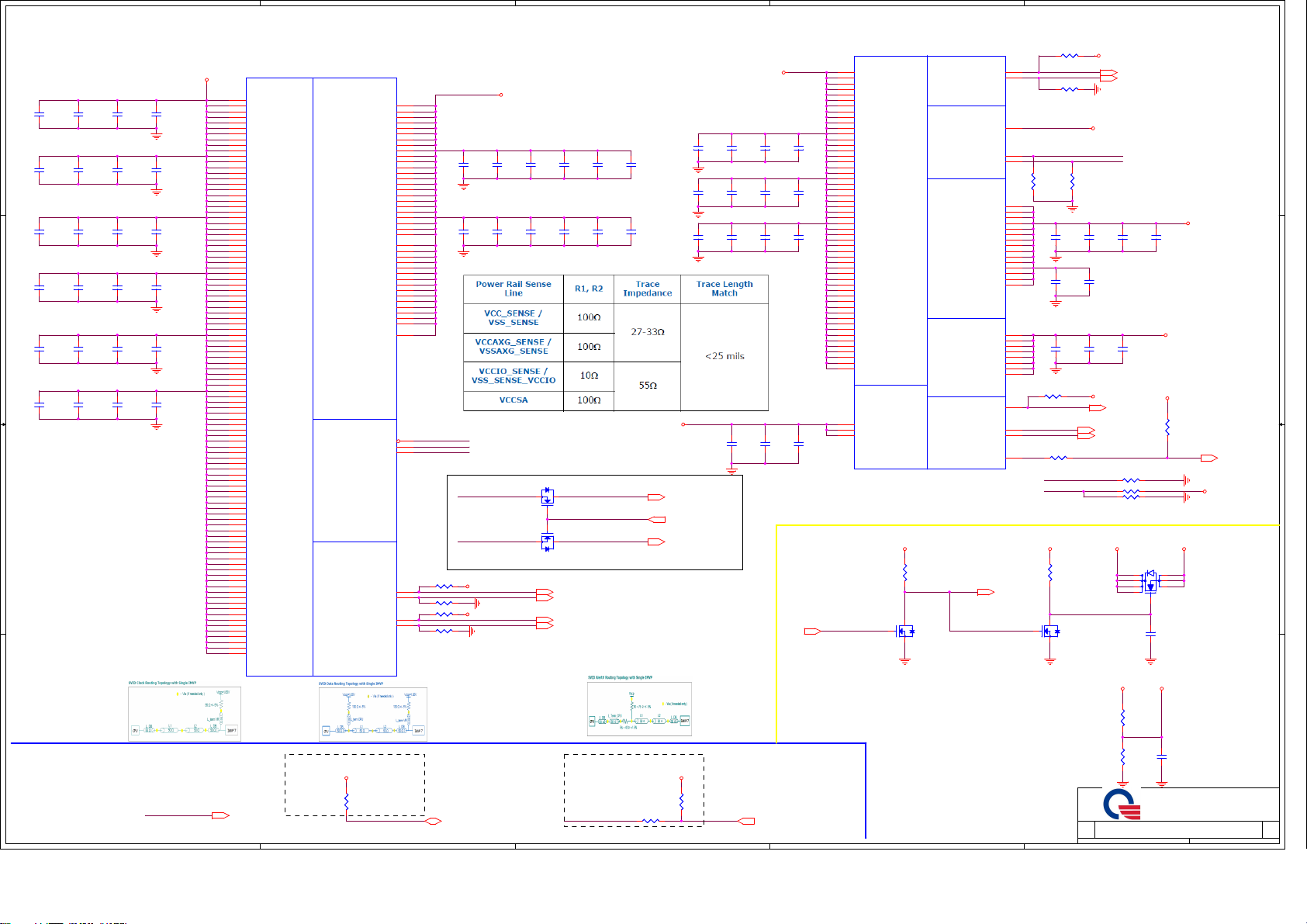

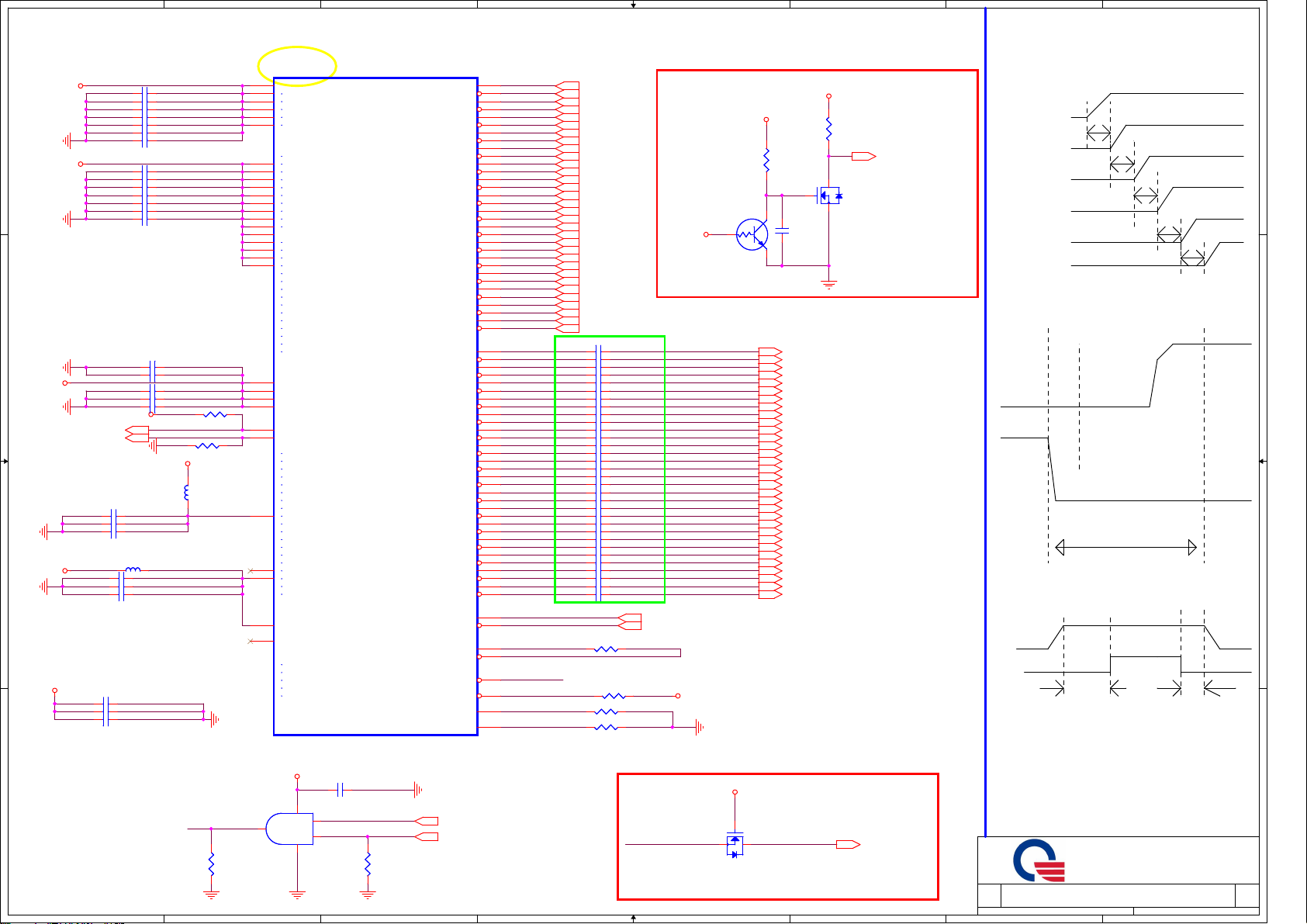

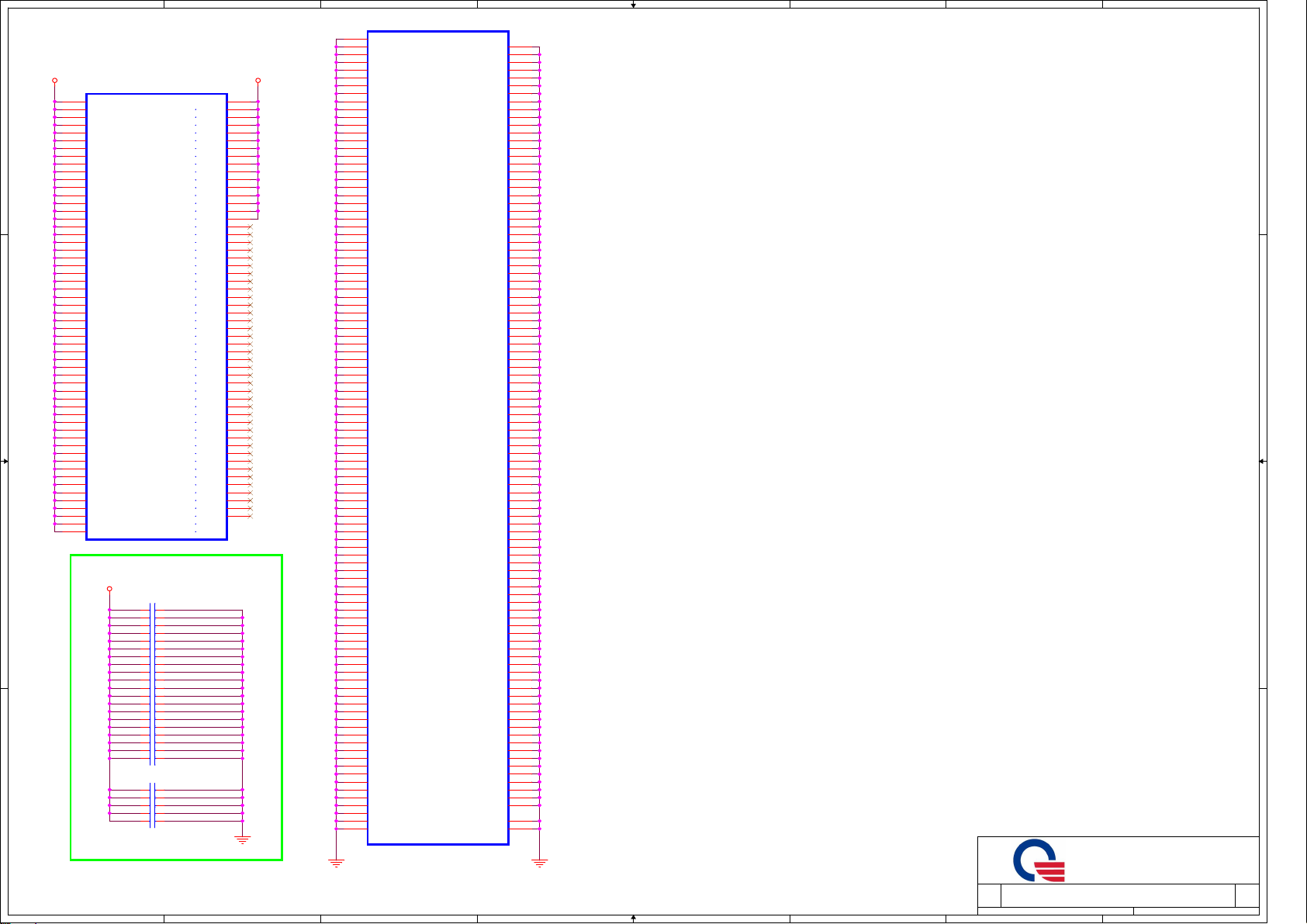

R08/V08 BLOCK DIAGRAM

A A

DDRIII-SODIMM1

H=4mm

PAGE11

DDRIII 1600 MT/s

CPU

Ivy Bridge 35W /

PCIEx16

N13P-GS (128bit)

N13P-GL (128bit)

Sandy Bridge

DDRIII-SODIMM2

H=8mm

PAGE12

DDRIII 1600 MT/s

PGA 988

PAGE 6~10

Nvidia

29mm X 29mm

BGA 908

PAGE 13~17

DDR3 1GB

V08x only

64Mx16bitx8

PCIE[1]

PCIE[5]

25MHz

DDR3 2GB

128Mx16bitx8

PAGE 18~19

USB[5]USB[4]

RJ45

Card Reader

SIM CARD

Page2

PAGE32 PAGE40

USB[10]

10/100 support

China Go-Rural

SATA1

Fingerprint

USB[8]

USB3.0 Ports x1

page4

IO SB

HDMI CONN

PAGE29

CRT CONN

LCD CONN

Camera

PAGE27

PAGE28

PAGE27

USB[12]

PCB STACK UP

6L

LAYER 1 : TOP

LAYER 2 : VCC

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : GND

LAYER 6 : BOT

DIS

FDI LINK

2.7GT /s

B B

SATA -HDD

PAGE34

ODD

PAGE34

SATA0 600MB /S

SATA3 300MB /S

Mobile Intel

DMI LINK

5GT /s

iGFX Interfaces

INT HDMI

INT CRT

INT Dual CHANNEL LVDS

Series 7 Chipset

USB3.0 Ports x2

USB PWR SHARE x1

PAGE31

PAGE31

USB3.0

USB3.0

PCH

HM77

USB2.0

Panther Point

3-axis Fall Sensor

C C

Keyboard Conn.

PAGE40

PAGE33

SMBUS

LPC

BGA 989

25 mm X 25 mm

PCI-E

KBC

Touch Pad

D D

PAGE40

ITE 8518

PAGE 38

SPI

PWM FAN

&Thermal

PAGE42 PAGE39 PAGE39

SPI ROM

8MB

SPI ROM

8MB

PAGE 20~26

25MHz

IHDA

32.768KHz

WLAN/BT WWAN/mSATA

page3 page3

PCI-E

LAN

AR8161(1G)

AR8162(10/100)

Page 2

IHDA

Audio Codec

PAGE37

JackSpeaker Digital-MIC

MB Side

PAGE37 PAGE37 PAGE27

1

2

3

4

5

X2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

6

Monday, February 13, 2012

7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

R08

R08

R08

1 55

1 55

1 55

8

1A

1A

1A

Page 2

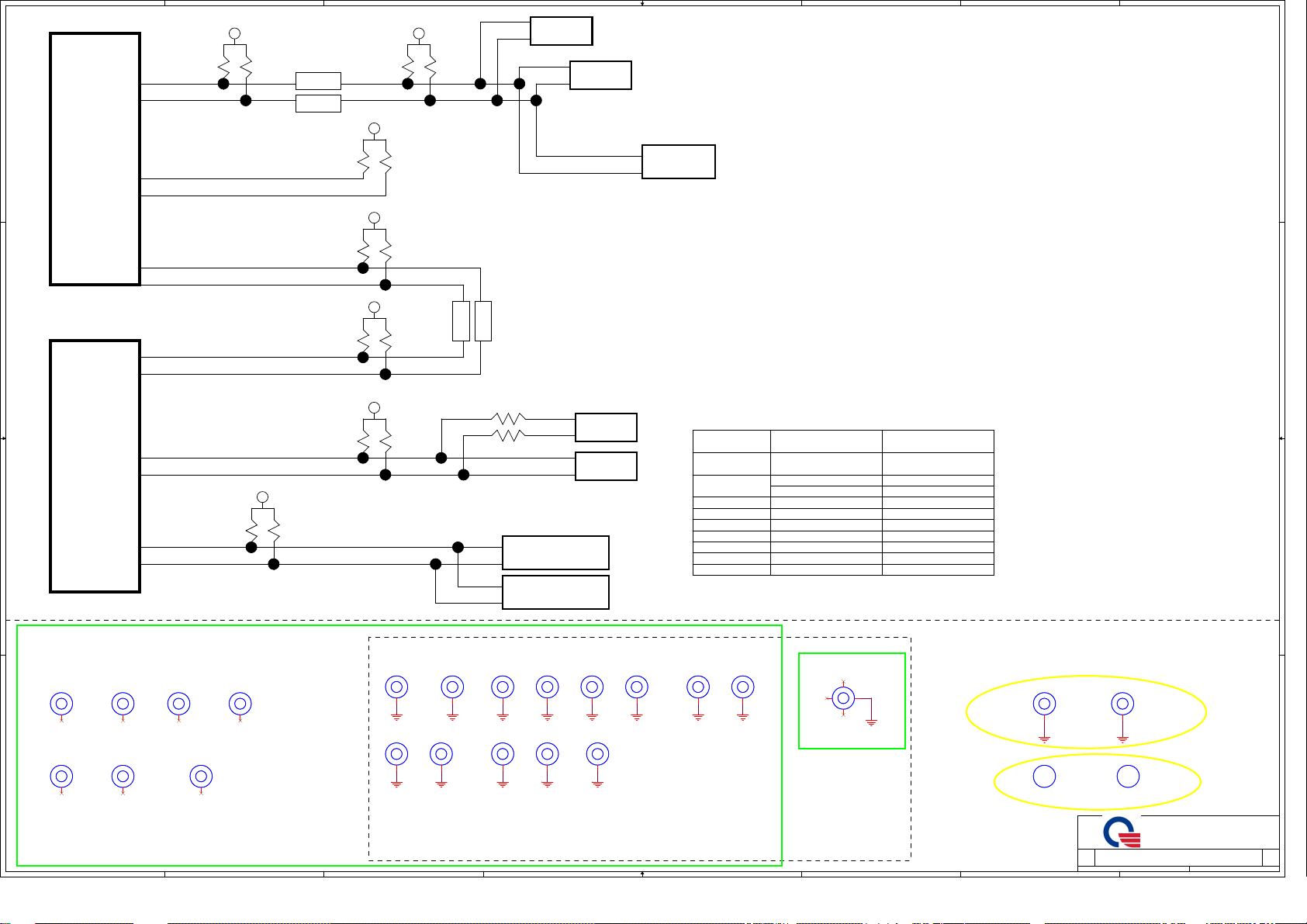

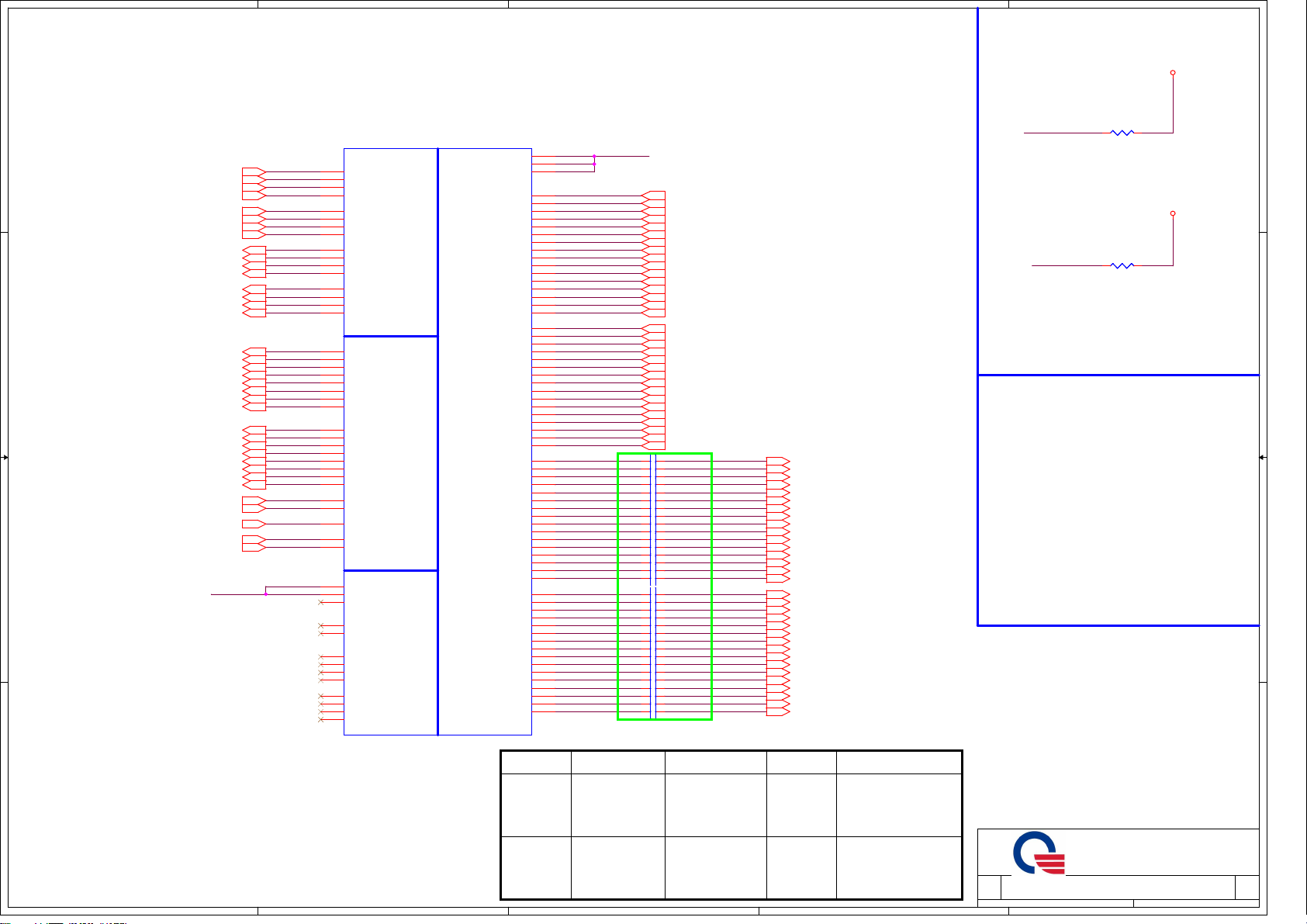

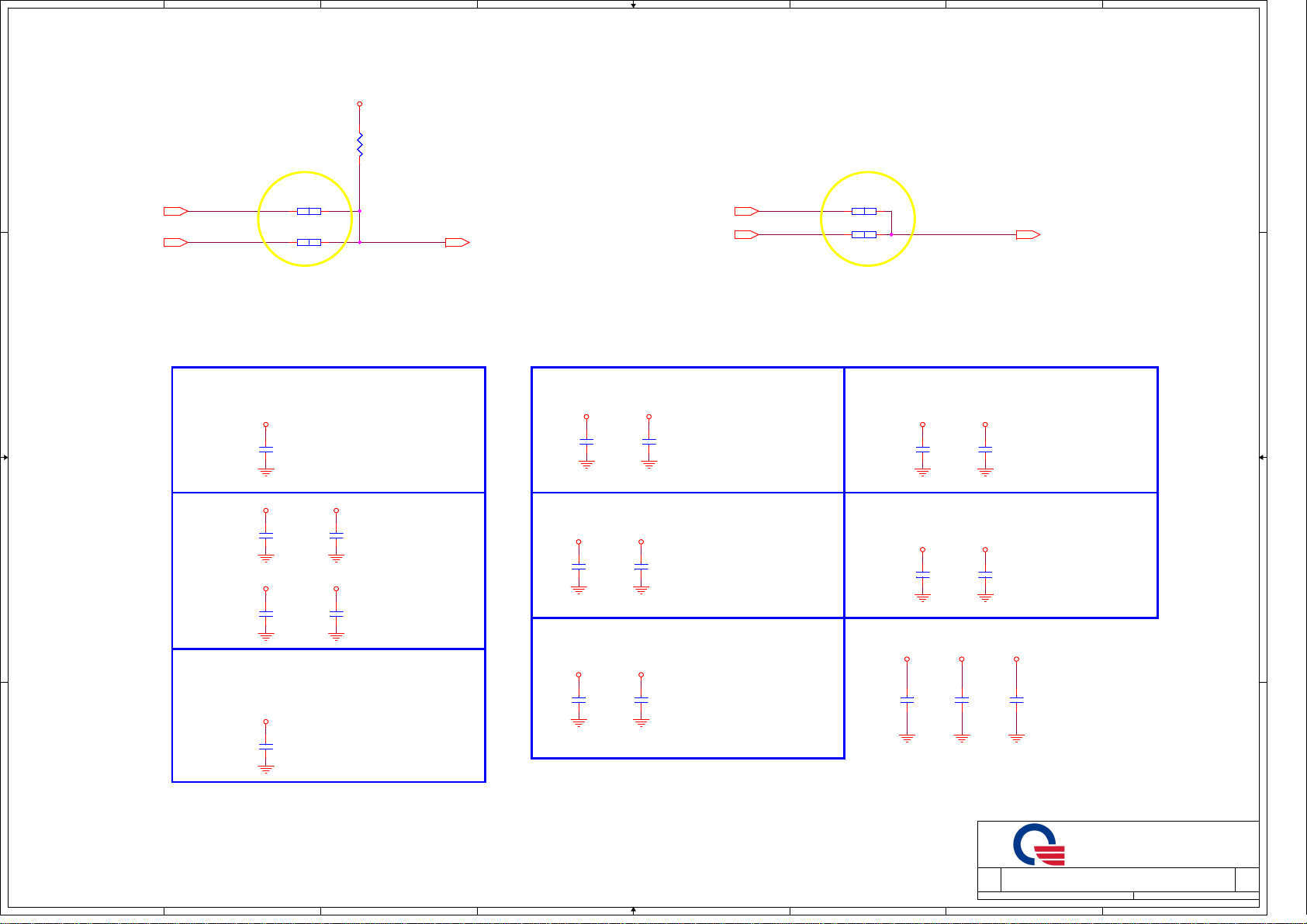

1

SMBCLK

H14

SMBDATA

C9

A A

PCH

C8

SML0CLK

G12

SML0DATA

+3.3V_SUS

2

2.2K2.2K

+3.3V_RUN

N-MOSFET

N-MOSFET

WLAN_SCLK

WLAN_SDATA

+3.3V_RUN

2.2K

3

+3.3V_RUN

+3.3V_SUS

2.2K

4

5

6

7

8

202

200

JDIM1A

2.2K2.2K

A0

202

200

JDIM2A

A4

6

FALL SENSOR

4

STM LNG3DM

50

+3.3V_SUS

2.2K2.2K

E14

SMB_CLK_ME1

M16

SMB_DATA_ME1

+3.3V_ALW

B B

SMBDAT1116

SMBCLK1

115

+3.3V_ALW

SIO

ITE8518E

110

SMBCLK0

111 SMBDAT0

+3.3V_RUN

2.2K2.2K

SMBCLK3

C C

94

SMBDAT3

95

SCREW PAD

H17

H16

H16

h-c154d154n

h-c154d154n

1

H21

H21

o-r08-1

D D

o-r08-1

1

H17

1

H22

H22

1

1

h-c154d154n

h-c154d154n

h-o118x142d118x142n

h-o118x142d118x142n

H18

H18

1

H-C142D142N

H-C142D142N

H23

H23

1

H-C276D276N

H-C276D276N

H19

H19

1

H-C142D142N

H-C142D142N

2

2.2K2.2K

2.2K2.2K

MB

H1

O-R08-2H1O-R08-2

1

H9

H9

H-C315IC158D118P2

H-C315IC158D118P2

1

3

+3.3V_SUS

H2

H2

H-C236D118P2

H-C236D118P2

1

H10

H10

H-C315IC158D118P2

H-C315IC158D118P2

1

N-MOS

N-MOS

8

7

8

7

H-C315IC158D118P2

H-C315IC158D118P2

H-TC236BC197D118P2

H-TC236BC197D118P2

+3.3V_SUS

100

100

H3

H3

H12

H12

1

1

3

4

9

8

Charger

THERMAL(EMC1422)

THERMAL (G781-1P8)

H4

H4

H5

H5

H-C315IC158D118P2

H-C315IC158D118P2

1

H13

H13

H-C315IC158D118P2-1

H-C315IC158D118P2-1

1

4

Battery

98

9A

H6

H6

H-TC236I20BC197D118P2

H-TC236I20BC197D118P2

1

1

H14

H14

H-C276D118P2

H-C276D118P2

1

16h

12

H-C315IC158D118P2

H-C315IC158D118P2

Function

DDR3

Thermal IC

Charge IC

Battery

Fall Sensor

H7

H7

H8

H8

H-C315IC158D118P2

H-C315IC158D118P2

1

1

5

JDIM1A A0h

SMBus AddressIC

JDIM2A A4h

EMC1422 1001100xb (98h)

G781-1P8

BQ24707ARGRR

Battery

STM LNG3DM

For CPU Use

H-C315IC158D118P2

H-C315IC158D118P2

20120206

Modify H11 pin1,2,3,4 no connect to GND

20120209

Modify H11 pin3 connect to GND

1001101xb (9Ah)

0b0001001x (0x12h)

16h

01010000 (50h)

H11

H11

2

*H-C283D146P2-r08_NC

*H-C283D146P2-r08_NC

intel-cpu-bkt2-r08

intel-cpu-bkt2-r08

34

1

6

20120204

Modify PV1 PV2 subsystem ID to OTH

20120204

Add two label PN HCR07003010 and HCJM5004013

PV1

PV1

emipad98x79-3_1h

emipad98x79-3_1h

1

LABEL68X5.5JM5

LABEL68X5.5JM5

LABEL1

LABEL1

7

PV2

PV2

emipad118x79-3_1h

emipad118x79-3_1h

1

30X6MM,ON SMT,R07

30X6MM,ON SMT,R07

LABEL2

LABEL2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

PROJECT :

SMB/SCREW PAD

SMB/SCREW PAD

SMB/SCREW PAD

R08

R08

R08

8

2 55

2 55

2 55

1A

1A

1A

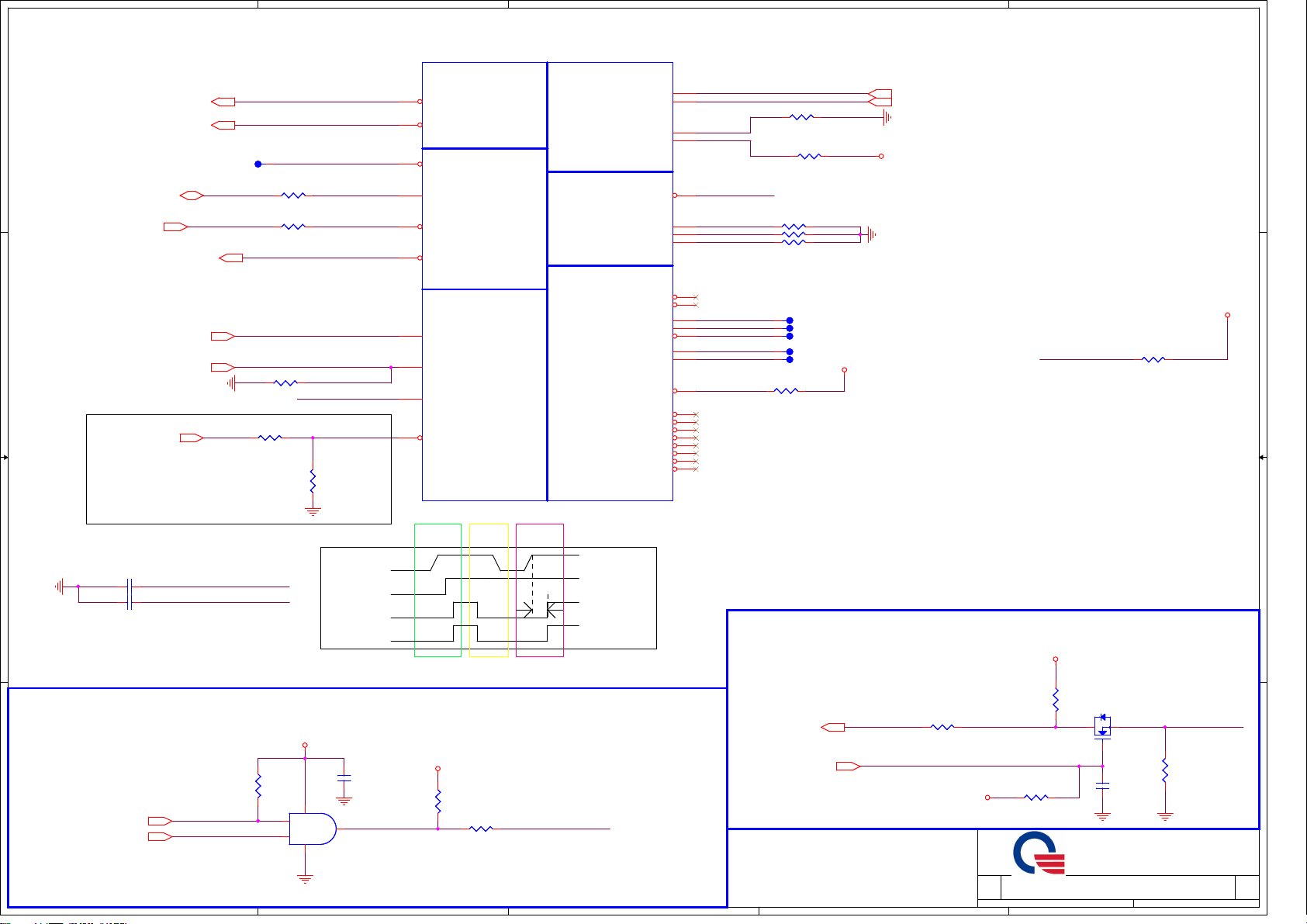

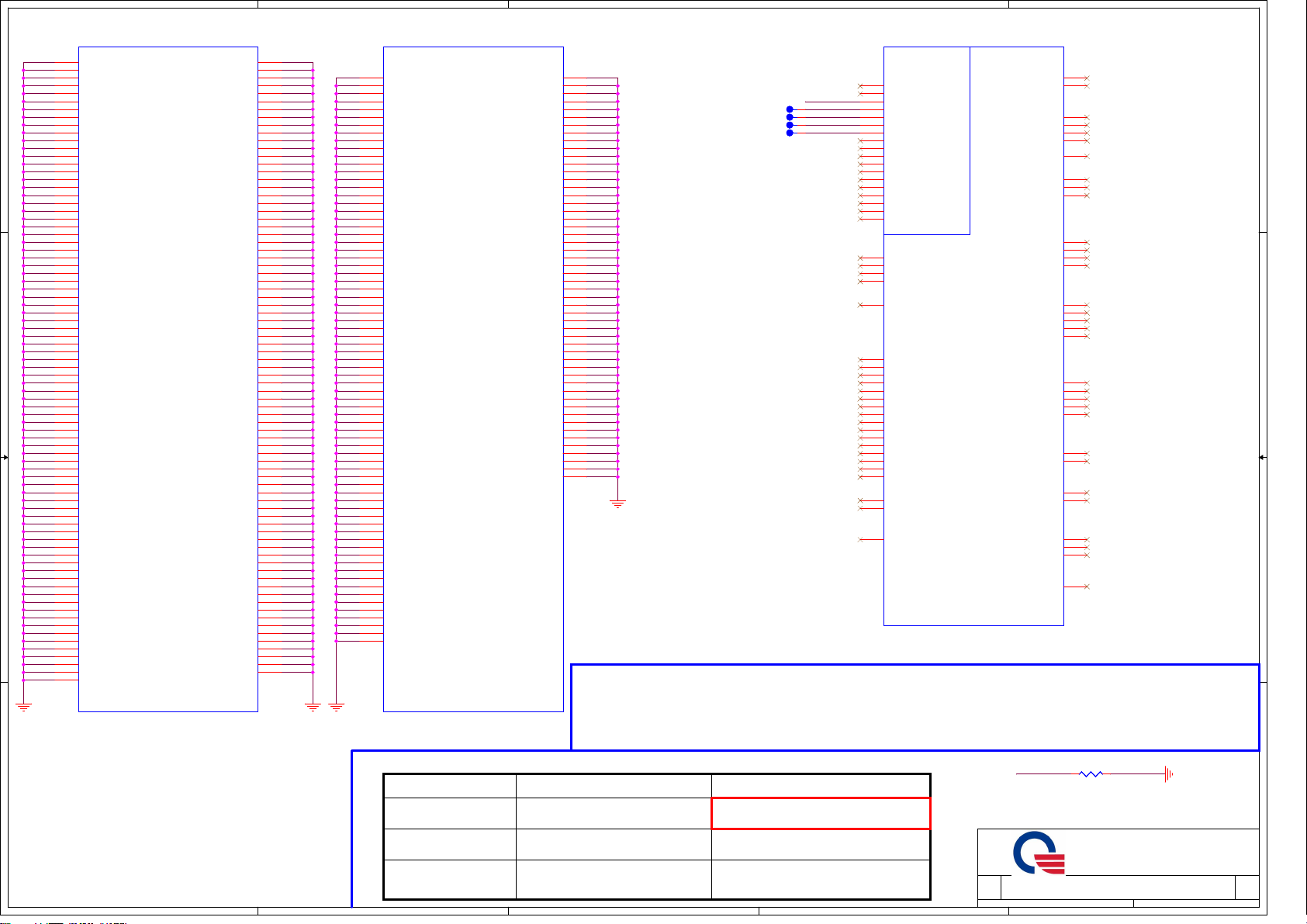

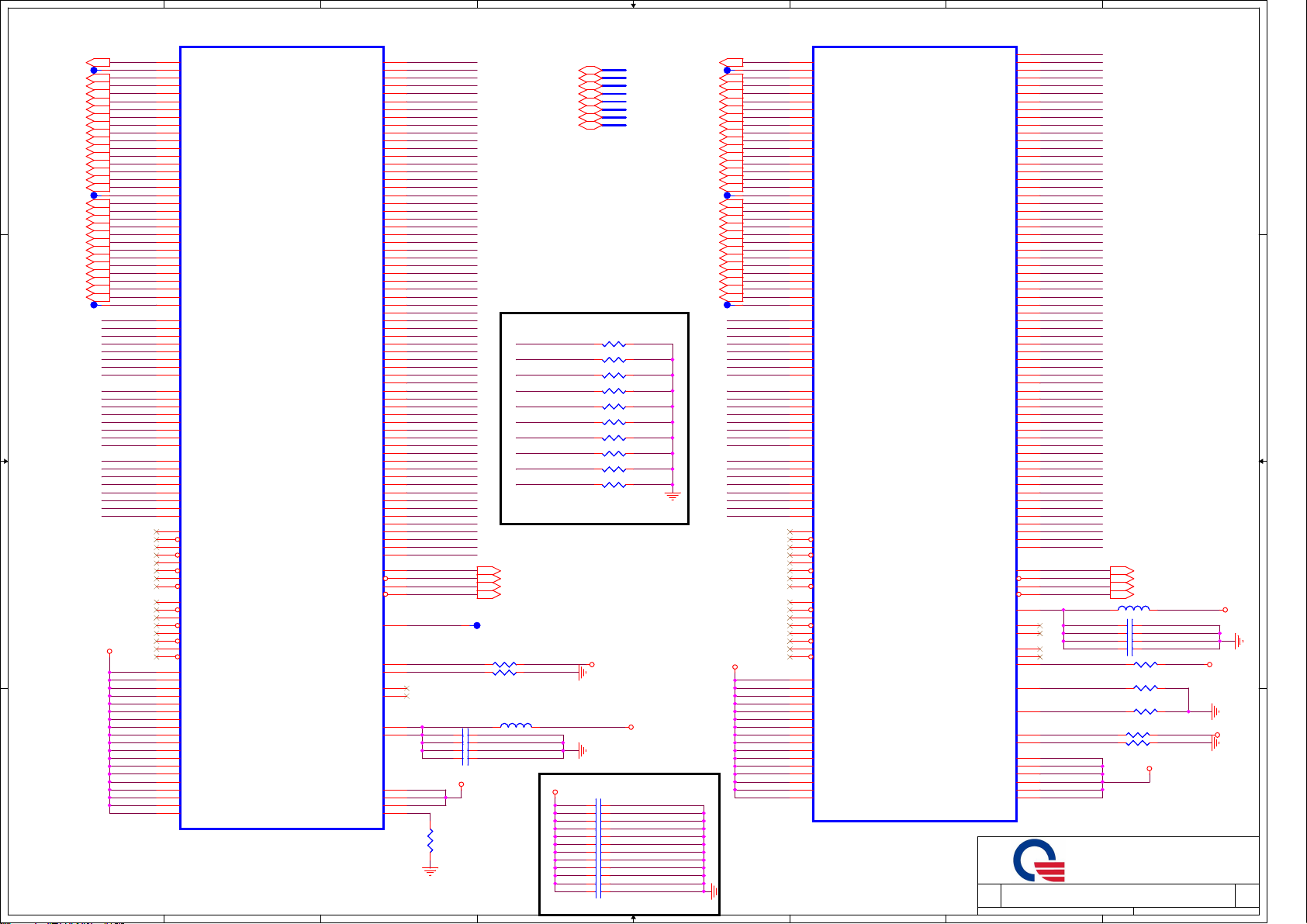

Page 3

1

2

3

4

5

6

7

8

USB Master

A A

USB0

USB1

USB2

USB3

USB4

USB5

B B

USB6

Port Assignment

External port#1 (USB3.0)

External port#2 (USB3.0/eSATA/

Power share/ debug port)

External port#3 (USB3.0)

External port#4 (USB3.0)

MiniCard 1 (WLAN/BT)

MiniCard 2 (WWAN/WiMAX)

X(FOR HM77)

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

Port AssignmentSATA Master

HDD

mSATA

NC

ODD

eSATA (NC)

NC

PCIE 1

PCIE 2

PCIE 3

PCIE 4

PCIE 5

PCIE 6

PCIE 7

Port AssignmentPCIE Master

WLAN

WWAN (NC)

Card reader (NC)

NC

LAN

Express card (NC)

NC

NCPCIE 8

USB7

X(FOR HM77)

FingerprintUSB8

USB9

USB10

USB11

USB12

Touch panel (NC, for debug)

Card Reader

Express Card (NC)

Camera

C C

D D

USB13

1

NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012 3 55

Date: Sheet of

Monday, February 13, 2012 3 55

Date: Sheet of

2

3

4

5

6

Monday, February 13, 2012 3 55

7

PROJECT :

PORT ASSIGNMENT

PORT ASSIGNMENT

PORT ASSIGNMENT

R08

1A

1A

1A

8

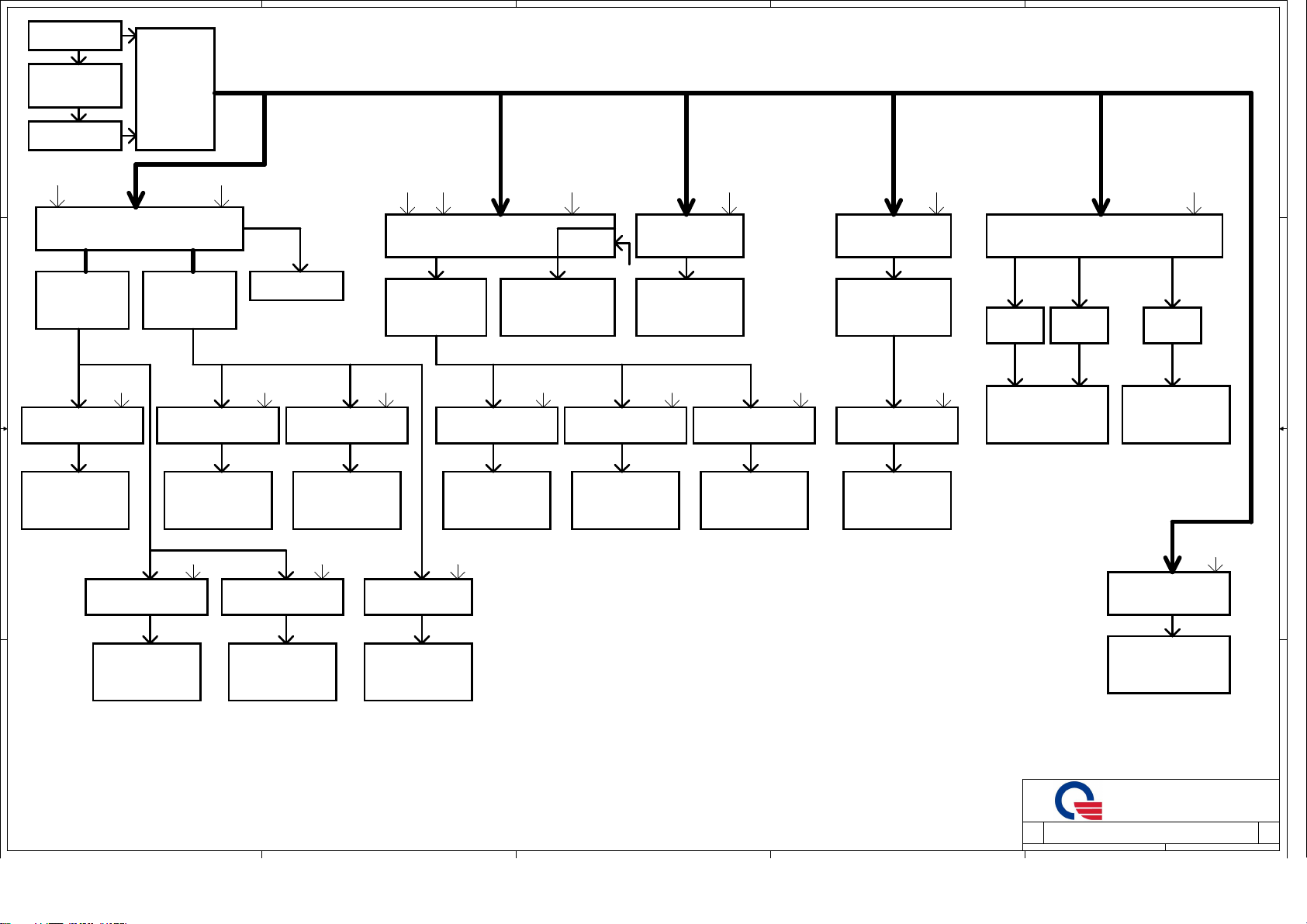

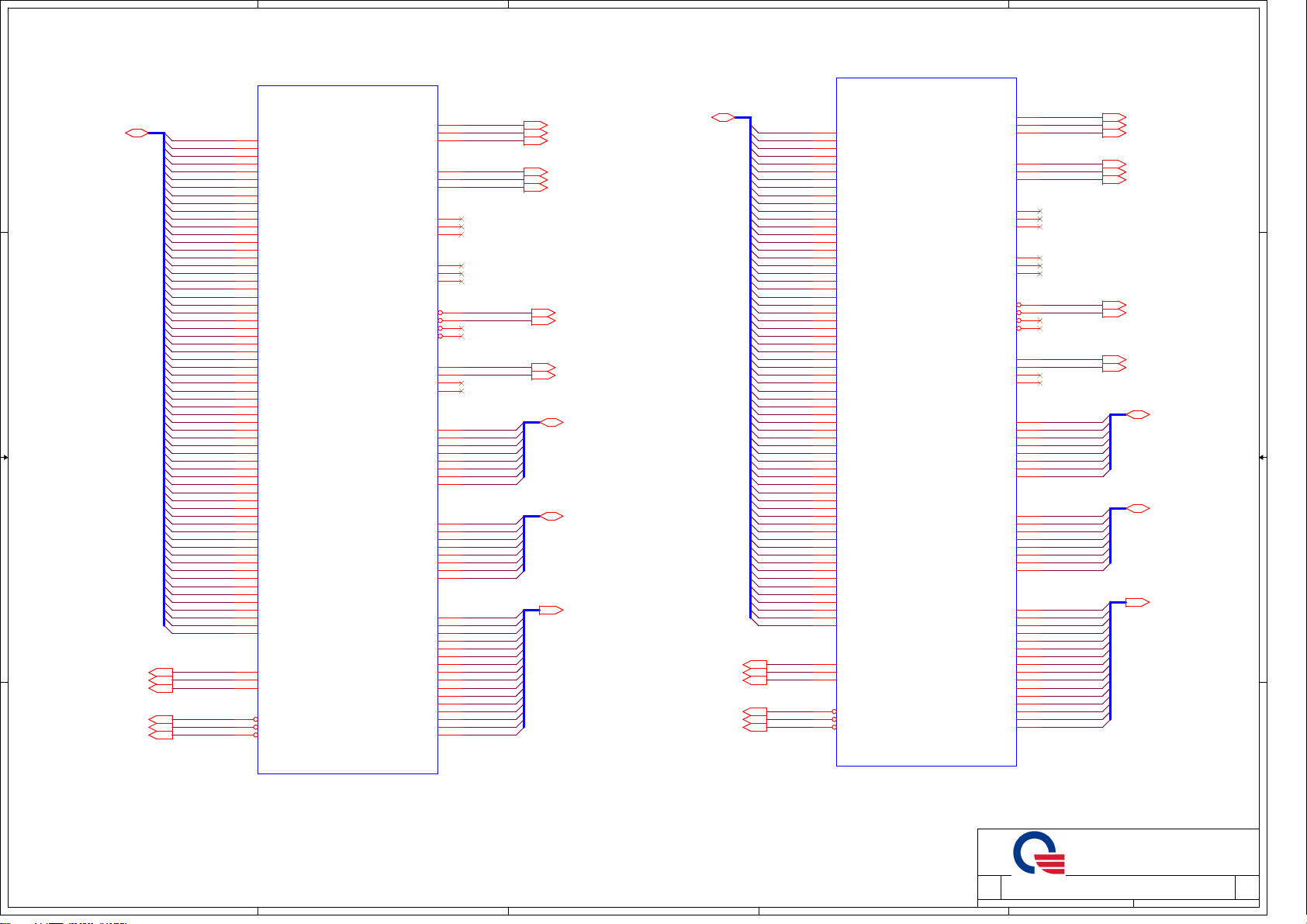

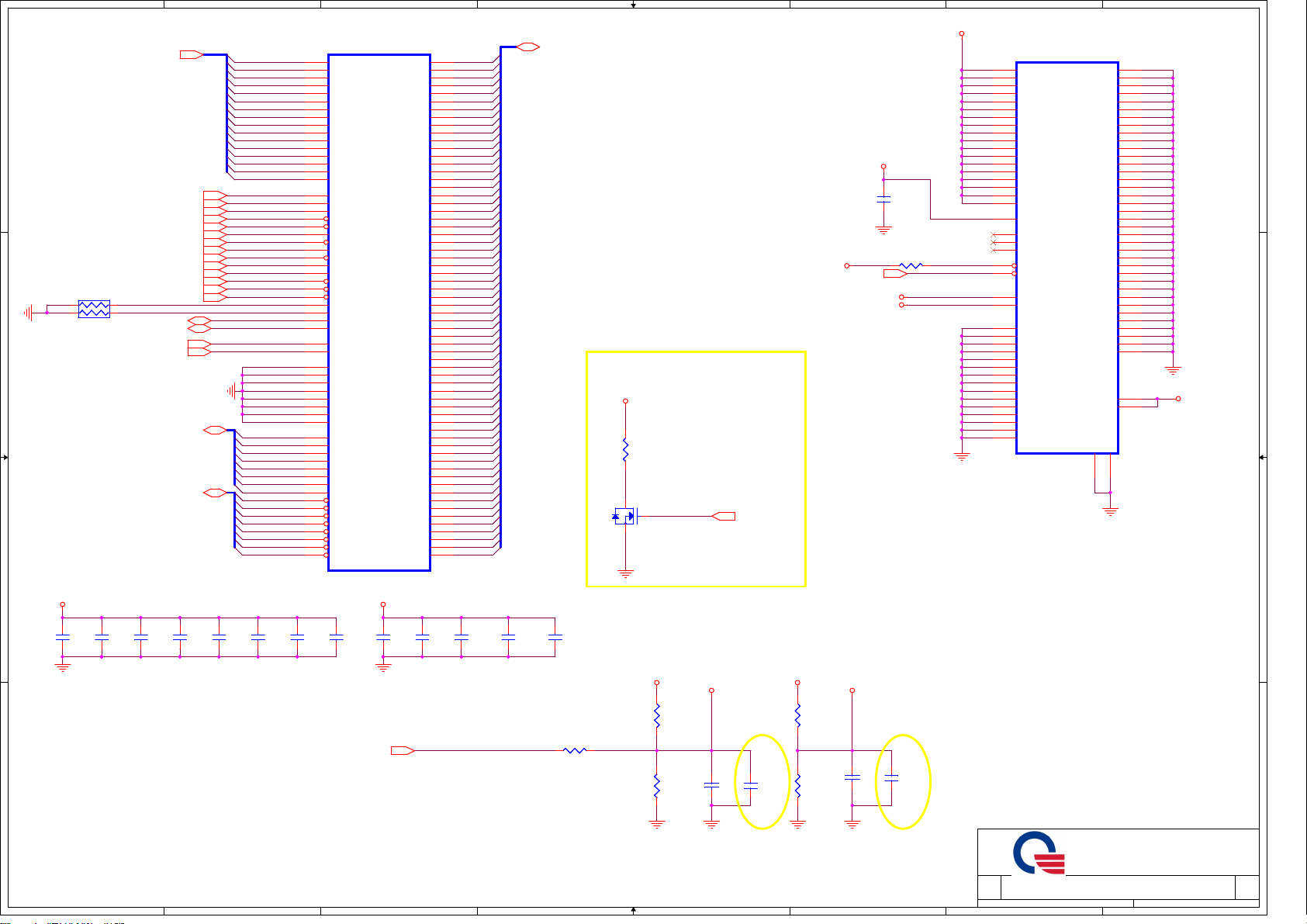

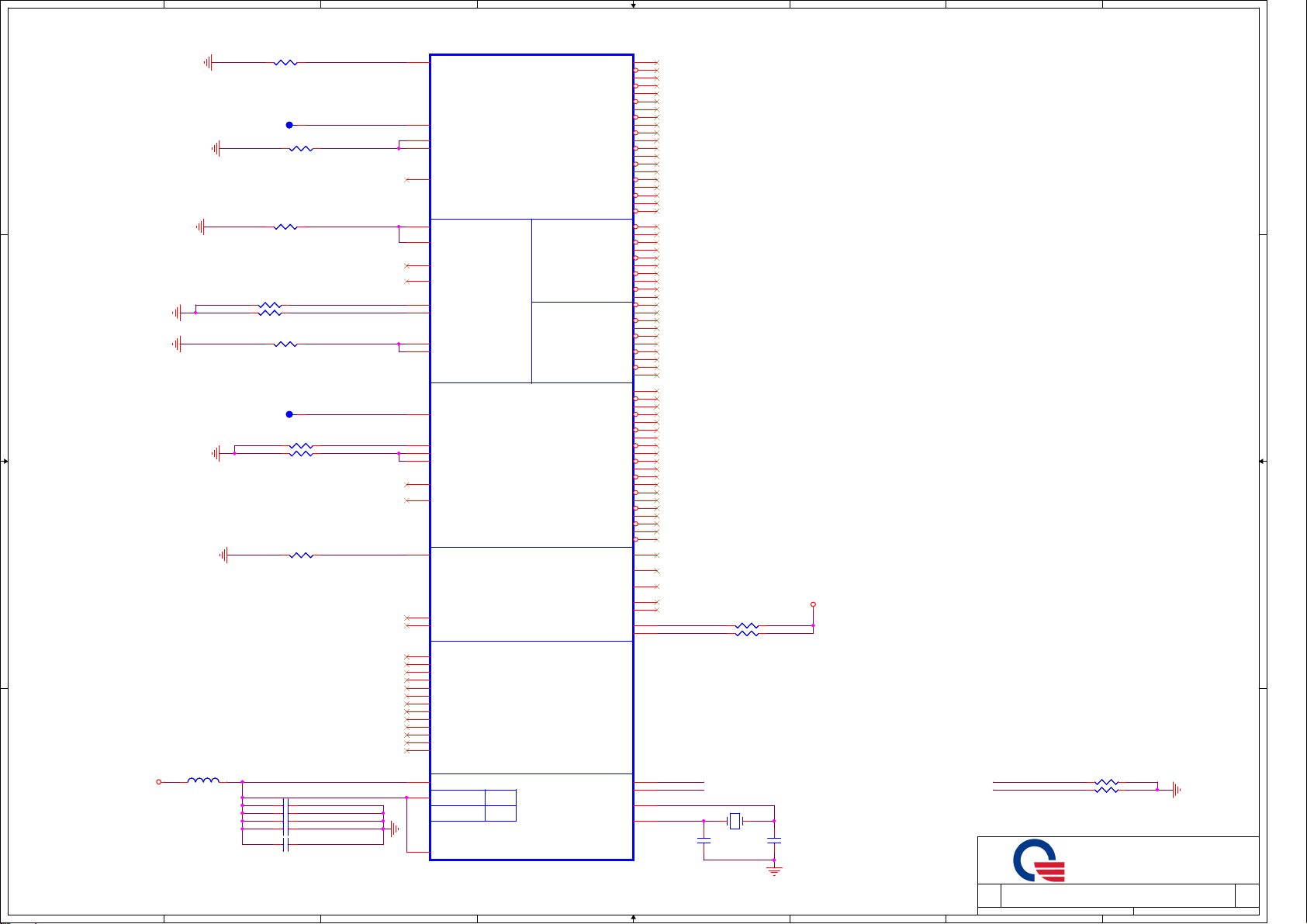

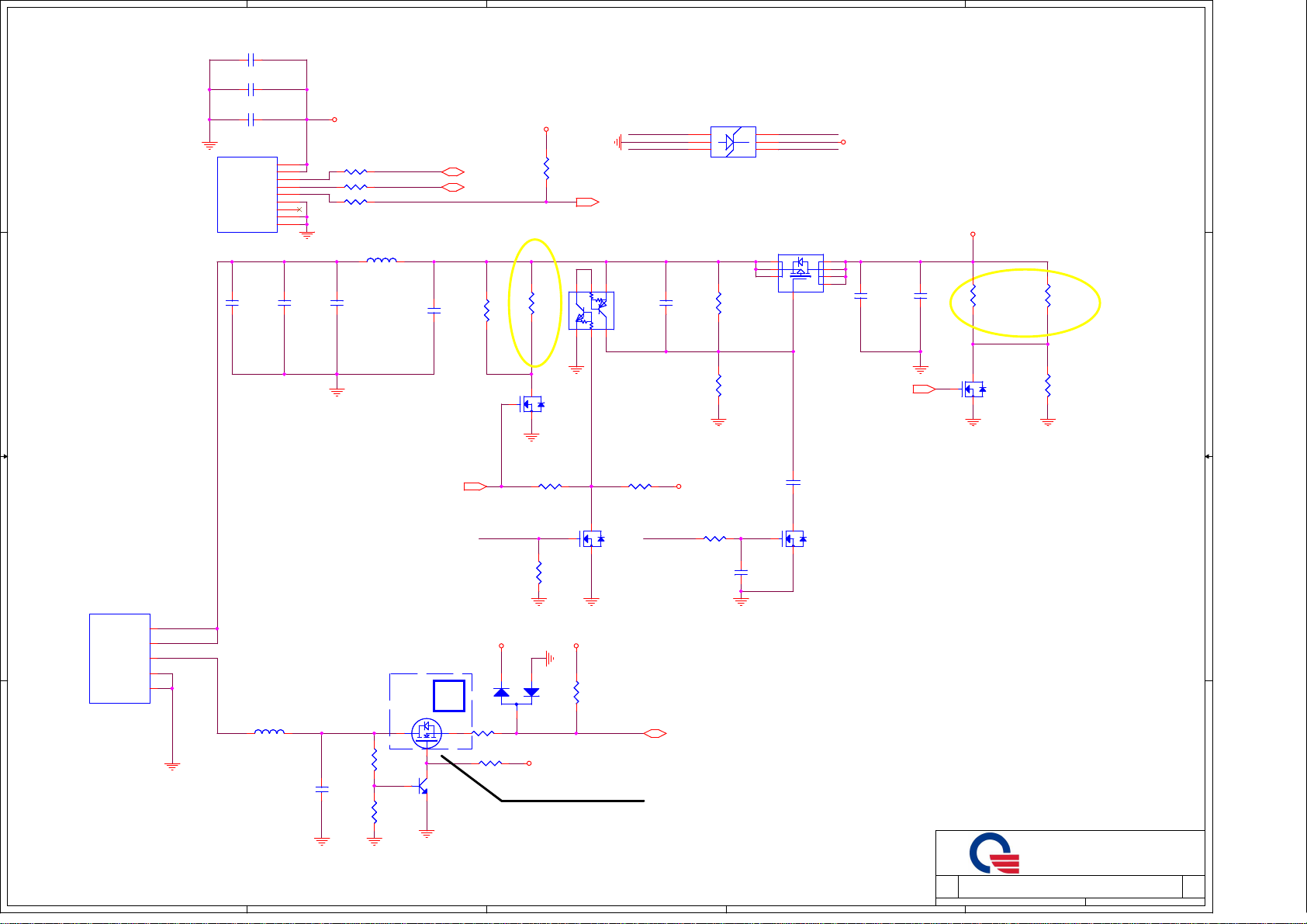

Page 4

5

4

3

2

1

Adapter 90W

Charger

BQ24707ARGRR

D D

PWR_SRC

Shapes: 280mil

Via: 10

VER : 1A

Battery 3S2P

+3.3V_EN2 ALW_ON

TI (PU1)

TPS51125ARGER

+3.3V_ALW

TDC: 3.87A

Shapes: 155mil

C C

Via: 6

SUS_ON

Load Switch(PQ17)

FDC655BN

+3.3V_SUS

TDC: 0.2A

Shapes: 8mil

Via: 1

B B

+5V_ALW

TDC: 18A

Shapes: 720mil

Via: 26

Load Switch(PQ23)

FDC655BN

+5V_SUS

TDC: 1.41A

Shapes: 56.4mil

Via: 2

RUN_ON

Load Switch(PQ22)

TPCC8065-H

+3.3V_RUN

TDC: 3.52A

Shapes: 140.8mil

Via: 5

+15V_ALW

SUS_ON

Load Switch(PQ16)

TPCC8065-H

+5V_RUN

TDC: 3.5A

Shapes: 140mil

Via: 5

DGPU_PWR_EN

Load Switch(PQ18)

FDC655BN

For dGPU only

+3V_GFX

TDC: 0.2A

Shapes: 8mil

Via: 1

SIO_SLP_S4#

SIO_SLP_S3#

+1.5V_SUS

TDC: 8.15A

Shapes: 326mil

Via: 12

RUN_ON

1.05V_PCH_PWRGD

RichTek(PU6)

RT8068AZQW

+1.8V_RUN

TDC: 1.02A

Shapes: 40.8mil

Via: 2

1.5V_SUS_PWRGD

TI(PU2)

TPS51216RUKR

+0.75V_DDR_VTT

TDC: 1A

Shapes: 40mil

Via: 2

RUN_ON

Load Switch(PQ25)

TPCC8065-H

+1.5V_RUN

TDC: 1A

Shapes: 40mil

Via: 2

LDO

RT8241DGQW

+1.5V_SUS

+VCCSA_CORE

RichTek(PU5)

TDC: 4.2A

Shapes: 168mil

Via: 6

DGPU_PWR_ON#

Load Switch(PQ24)

TPCC8065-H

For dGPU only For dGPU only

+1.5V_GFX

TDC: 1A

Shapes: 40mil

For dGPU

Via: 2

VCCSA_EN

SIO_SLP_S3#

Load Switch(Q4)

FDMS7670

+1.5V_CPU

TDC: 5A

Shapes: 200mil

Via: 8

RichTek(PU3)

RT8240BGQW

+1.05V_PCH

TDC: 10.39A

Shapes: 415.6mil

Via: 15

Load Switch(PQ27)

FDMS7670

+1.05V_GFX

TDC: 1A

Shapes: 40mil

Via: 2

+3.3V_RUN

DGFX_VR_PWRGD

IMVP_VR_ON

ON(PU7)

NCP6132A

PQ35 PQ36 PQ37

+VCC_CORE

TDC: 42.4A

Shapes: 1696mil

Via: 61

+VCC_iGFX_CORE

TDC: 23A

Shapes: 920mil

Via: 33

ON(PU11)

NCP3218MNR2G

+VCC_DGFX_CORE

TDC: 40A

Shapes: 1600mil

Via: 57

+3V_GFX

For dGPU only

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Power Block Diagram

Power Block Diagram

Power Block Diagram

Date: Sheet of

Monday, February 13, 2012 4 55

Date: Sheet of

Monday, February 13, 2012 4 55

Date: Sheet of

5

4

3

2

Monday, February 13, 2012 4 55

PROJECT :

R08

R08

R08

1A

1A

1A

1

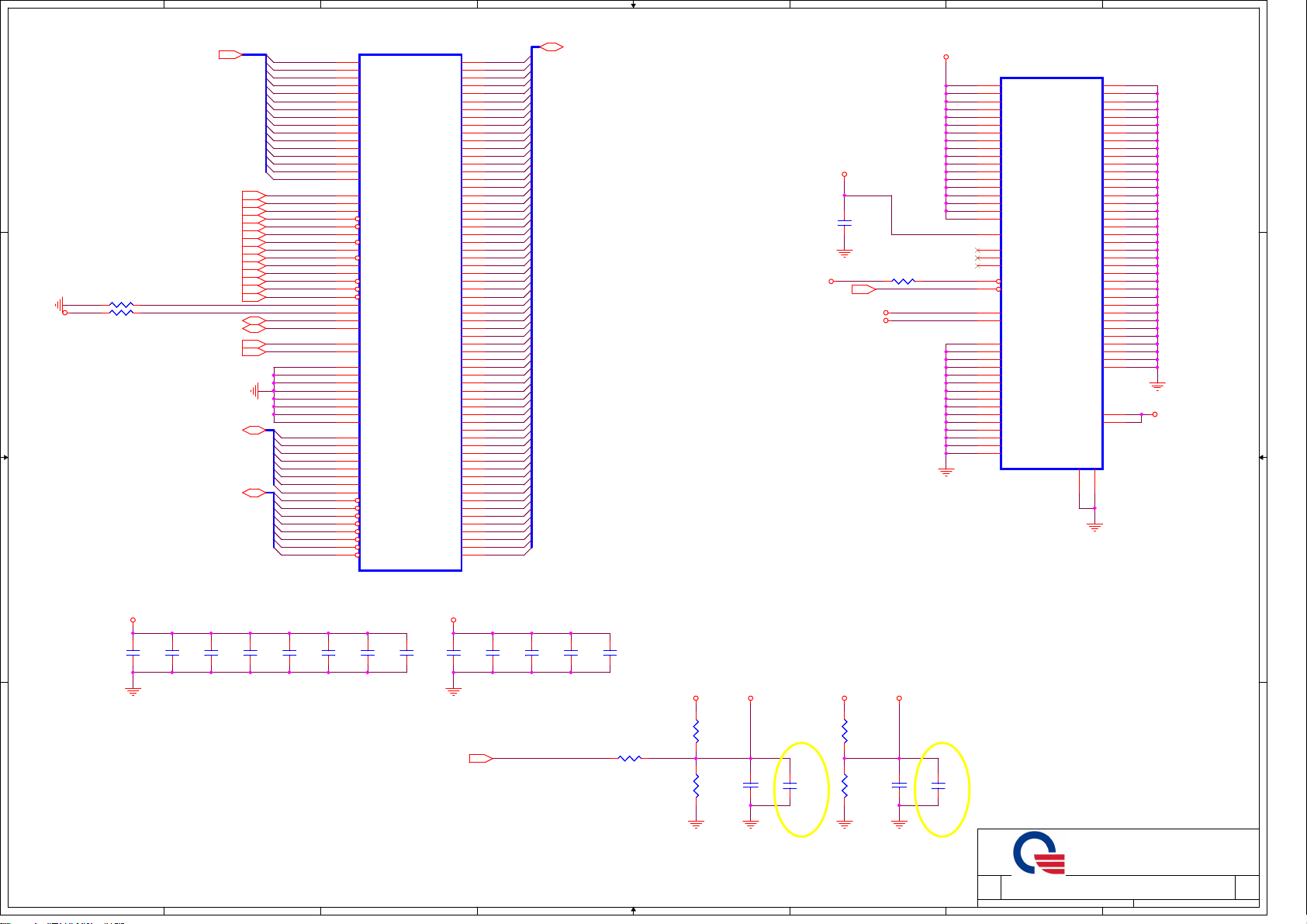

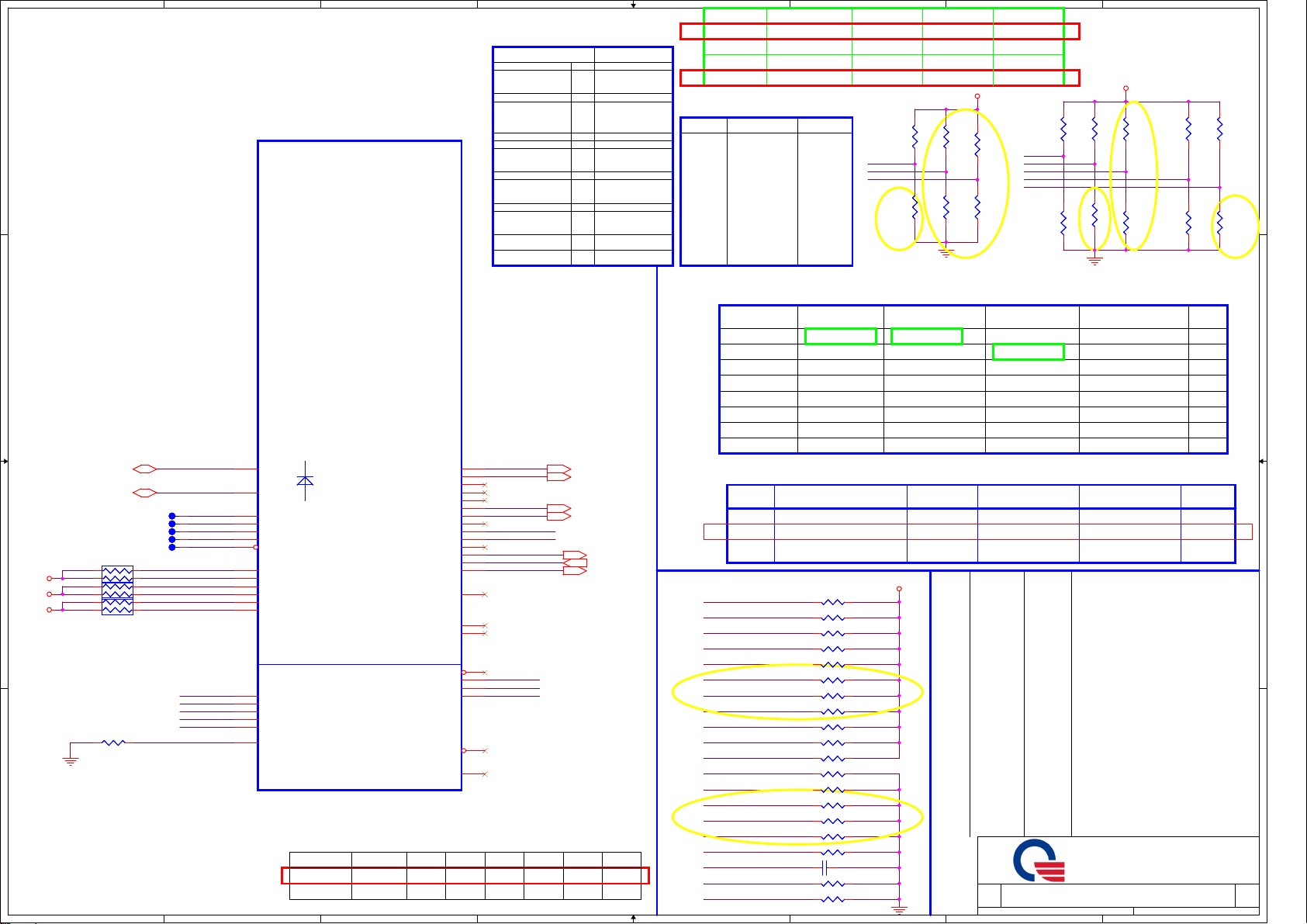

Page 5

1

Battery Mode

+5V_ALW

+3.3V_ALW

A A

B B

C C

+5V_ALW

+3.3V_ALW

+1.5V_SUS

D D

SUS

SW

G

+PWR_SRC

DDR/0.75V

S3

S4

SLP_S3

SWITCH

G

+PWR_SRC

RUN PWR

SWITCH

G

+PWR_SRC

1.05V

VR

EN

1

PG

RC Delay

PG

2

+5V_SUS

+3.3V_SUS

SUS_ON

+1.5V_SUS

+DDR_VTTREF

+0.75V_DDR_VTT

1.5V_SUS_PWRGD

SIO_SLP_S3#

SIO_SLP_S4#

+1.5V_CPU+1.5V_SUS

SIO_SLP_S3#

+GFX_PWR_SRC

+5V_RUN

+3.3V_RUN

+1.5V_RUN

RUN_ON

+1.05V_PCH

1.05V_PCH_PWRGD

30

+3.3V_RUN

2

21

11

12

10

26

27

28

25

29

20

22

23

24

19

18

19

VCCSA_PWRGD

34

+5V_ALW

SVID

42

3

1.8V

VR

EN

+PWR_SRC

VCCSA

VR

EN

+PWR_SRC

IMVP

VR

3

4

3

POWER_SW_IN0#

PWR SW VR

SYS_PWR_SW#

7

EC_PWROK

RUN_ON

+3.3V_ALW

+1.5V_SUS

36

3637

EC

IMVP_VR_ON

19

35

HWPG

10

SUS_ON

25

31

+1.8V_RUN

VCCSA_EN

PG

32

33

+VCCSA_CORE

34

VCCSA_PWRGD

PG

VCCSA_EN

+VCC_CORE

+VCC_GFX_CORE

IMVP_PWRGD

PG

EN

43

47

44

IMVP_VR_ON

4

5

SIO_SLP_S5#17SIO_SLP_S4#18SIO_SLP_S3#

GPU PWR

SWITCH

G

+PWR_SRC

GPU

VR

EN

GPU PWR

SWITCH

G

GPUCPUPCH

5

2

+5V_ALW2

3.3V_ALW_ON

4

6

ALW_ON

13

RSMRST#

ME_SUS_PWR_ACK

AC_PRESENT

SIO_PWRBTN#

16

49

+3V_GFX

+1.5V_GFX

DGPU_PWR_EN

50

+VCC_DGFX_CORE

DGFX_VR_PWRGD

PG

+3.3V_GFX

53

+1.05V_GFX+1.05V_PCH

DGFX_VR_PWRGD

52

6

+PWR_SRC

3V/5V

EN2

14

15

53

48

51

6

EN1

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

PM_DRAM_PWRGD

38

PCH_CLK

SYS_PWROK

DGPU_PWR_EN

48

Buffer

44

IMVP_PWRGD

37

EC_PWROK

38

PM_DRAM_PWRGD

37

EC_PWROK

46

PLTRST#

DGPU_HOLD_RST#

55

+3.3V_ALW

+5V_ALW

+15V_ALW

39

7

1

+VCHGR+PWR_SRC

8

5

8

9

17

18

19

DGPU_PWROK

54

CHARGER Battery

DPWROK

SUSWARN#

ACPRESENT

PWRBTN#

SLP_S5#

SLP_S3#

APWROK

DRAMPWROK

SYS_PWROK

SYS_PWROK

45

55

PCH

PROCPWRGD

H_PWRGOOD

DGPU_HOLD_RST#

41

46

40

U2

SM_SDRAMPWROK

SVID

42

UNCOREPWRGOOD

CPU

56

GPU_RST#

GPU

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012 5 55

Date: Sheet of

Monday, February 13, 2012 5 55

Date: Sheet of

Monday, February 13, 2012 5 55

7

PROJECT :

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

R08

8

PLTRST#

RESET# PLTRST#

1A

1A

1A

Page 6

5

4

Ivy Bridge Processor (RESERVED, CFG)

3

2

1

DP & PEG Compensation

+1.05V_PCH

D D

U1A

U1A

DMI_TXN020

DMI_TXN120

DMI_TXN220

DMI_TXN320

DMI_TXP020

DMI_TXP120

DMI_TXP220

DMI_TXP320

DMI_RXN020

DMI_RXN120

DMI_RXN220

DMI_RXN320

DMI_RXP020

DMI_RXP120

DMI_RXP220

DMI_RXP320

C C

B B

eDP_ICOMPO 12mil

eDP_COMPIO 4mil

Programing Disable eDP interface(BIOS)

FDI_FSYNC020

FDI_FSYNC120

FDI_LSYNC020

FDI_LSYNC120

FDI_TXN020

FDI_TXN120

FDI_TXN220

FDI_TXN320

FDI_TXN420

FDI_TXN520

FDI_TXN620

FDI_TXN720

FDI_TXP020

FDI_TXP120

FDI_TXP220

FDI_TXP320

FDI_TXP420

FDI_TXP520

FDI_TXP620

FDI_TXP720

FDI_INT20

eDP_COMP

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

VGA(U3)

A A

N13P-GL

N13P-GS

5

4

PEG_ICOMPO 12mil

PEG_ICOMPI, PEG_RCOMPO 4mil,

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_COMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0_C

PEG_TXN1_C PEG_TXN1

PEG_TXN2_C

PEG_TXN3_C

PEG_TXN4_C

PEG_TXN5_C

PEG_TXN6_C

PEG_TXN7_C

PEG_TXN8_C

PEG_TXN9_C

PEG_TXN10_C

PEG_TXN11_C

PEG_TXN12_C

PEG_TXN13_C

PEG_TXN14_C

PEG_TXN15_C

PEG_TXP0_C

PEG_TXP1_C

PEG_TXP2_C

PEG_TXP3_C

PEG_TXP4_C

PEG_TXP5_C

PEG_TXP6_C

PEG_TXP7_C

PEG_TXP8_C

PEG_TXP9_C

PEG_TXP10_C

PEG_TXP11_C

PEG_TXP12_C

PEG_TXP13_C

PEG_TXP14_C

PEG_TXP15_C

C1 0.1U/16V_4C1 0.1U/16V_4

C2 0.1U/16V_4C2 0.1U/16V_4

C3 0.1U/16V_4C3 0.1U/16V_4

C4 0.1U/16V_4C4 0.1U/16V_4

C5 0.1U/16V_4C5 0.1U/16V_4

C6 0.1U/16V_4C6 0.1U/16V_4

C7 0.1U/16V_4C7 0.1U/16V_4

C8 0.1U/16V_4C8 0.1U/16V_4

C9 0.1U/16V_4C9 0.1U/16V_4

C10 0.1U/16V_4C10 0.1U/16V_4

C11 0.1U/16V_4C11 0.1U/16V_4

C12 0.1U/16V_4C12 0.1U/16V_4

C13 0.1U/16V_4C13 0.1U/16V_4

C14 0.1U/16V_4C14 0.1U/16V_4

C15 0.1U/16V_4C15 0.1U/16V_4

C16 0.1U/16V_4C16 0.1U/16V_4

C17 0.1U/16V_4C17 0.1U/16V_4

C18 0.1U/16V_4C18 0.1U/16V_4

C19 0.1U/16V_4C19 0.1U/16V_4

C20 0.1U/16V_4C20 0.1U/16V_4

C21 0.1U/16V_4C21 0.1U/16V_4

C22 0.1U/16V_4C22 0.1U/16V_4

C23 0.1U/16V_4C23 0.1U/16V_4

C24 0.1U/16V_4C24 0.1U/16V_4

C25 0.1U/16V_4C25 0.1U/16V_4

C26 0.1U/16V_4C26 0.1U/16V_4

C27 0.1U/16V_4C27 0.1U/16V_4

C28 0.1U/16V_4C28 0.1U/16V_4

C29 0.1U/16V_4C29 0.1U/16V_4

C30 0.1U/16V_4C30 0.1U/16V_4

C31 0.1U/16V_4C31 0.1U/16V_4

C32 0.1U/16V_4C32 0.1U/16V_4

PEG_RXN0 13

PEG_RXN1 13

PEG_RXN2 13

PEG_RXN3 13

PEG_RXN4 13

PEG_RXN5 13

PEG_RXN6 13

PEG_RXN7 13

PEG_RXN8 13

PEG_RXN9 13

PEG_RXN10 13

PEG_RXN11 13

PEG_RXN12 13

PEG_RXN13 13

PEG_RXN14 13

PEG_RXN15 13

PEG_RXP0 13

PEG_RXP1 13

PEG_RXP2 13

PEG_RXP3 13

PEG_RXP4 13

PEG_RXP5 13

PEG_RXP6 13

PEG_RXP7 13

PEG_RXP8 13

PEG_RXP9 13

PEG_RXP10 13

PEG_RXP11 13

PEG_RXP12 13

PEG_RXP13 13

PEG_RXP14 13

PEG_RXP15 13

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

0.22uF AC coupling Caps for PCIE GEN3

0.1uF AC coupling Caps for PCIE GEN1/2

AC coupling Cap

0.1uF

0.22uF

CH4103K1B08 C1~C32

CH4223K1B00

3

PEG_TXN0

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

PN

PEG_TXN0 13

PEG_TXN1 13

PEG_TXN2 13

PEG_TXN3 13

PEG_TXN4 13

PEG_TXN5 13

PEG_TXN6 13

PEG_TXN7 13

PEG_TXN8 13

PEG_TXN9 13

PEG_TXN10 13

PEG_TXN11 13

PEG_TXN12 13

PEG_TXN13 13

PEG_TXN14 13

PEG_TXN15 13

PEG_TXP0 13

PEG_TXP1 13

PEG_TXP2 13

PEG_TXP3 13

PEG_TXP4 13

PEG_TXP5 13

PEG_TXP6 13

PEG_TXP7 13

PEG_TXP8 13

PEG_TXP9 13

PEG_TXP10 13

PEG_TXP11 13

PEG_TXP12 13

PEG_TXP13 13

PEG_TXP14 13

PEG_TXP15 13

20120203

Change C1~C32 to 0.1U/16V_4 (CH4103K1B08)

TX location RX location(page13)

C144 C145 C147 C149 C150

C152 C154 C156 C157 C158

C159 C160 C161 C162 C163

C164 C165 C166 C167 C168

C169 C171 C173 C175 C176

C177 C178 C179 C180 C182

C184 C185

C144 C145 C147 C149 C150

C152 C154 C156 C157 C158

C159 C160 C161 C162 C163

C1~C32

C164 C165 C166 C167 C168

C169 C171 C173 C175 C176

C177 C178 C179 C180 C182

C184 C185

2

eDP_COMP

eDP_COMPIO and ICOMPO signals should

be shorted near balls and

routed within 500 mils

PEG_ICOMPI and RCOMPO signals should

be routed within 500 mils

PEG_ICOMPO signals should

be routed within 500 mils

PEG_COMP

R1 24.9/F_4R1 24.9/F_4

1 2

+1.05V_PCH

R2 24.9/F_4R2 24.9/F_4

1 2

eDP Hot-plug (Disable)

CAD Note: Place PU resistor within 2 inches

of CPU

This signal can be left as no connect if

entire eDP interface is disabled.

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

PROJECT :

Ivy Bridge 1/5

Ivy Bridge 1/5

Ivy Bridge 1/5

1

R08

R08

R08

6 55

6 55

6 55

1A

1A

1A

Page 7

5

4

3

2

1

Ivy Bridge Processor (CLK,MISC,JTAG)

U1B

U1B

SNB_IVB# N.A at SNB EDS #27637 0.7v1

H_SNB_IVB#23

D D

IMVP7_PROCHOT#38,52,54

Over 130 degree C will

drive low

C C

H_CPUDET#38

PECI_EC38

H_PM_SYNC20

H_PWRGOOD25

PLTRST#13,23,35,38

PECI_EC

IMVP7_PROCHOT#

PM_THRMTRIP#25

H_PWRGOOD

R19 1.5K/F_4R19 1.5K/F_4

H_SNB_IVB#

H_CPUDET#

TP1TP1

CATERR#

R6 43_4R6 43_4

1 2

R7 56_4R7 56_4

1 2

PM_THRMTRIP#

12

R1710K_4 R1710K_4

12

SM_DRAMPWROK

CPU_PLTRST#_RPLTRST#

12

R20

R20

750/F_4

750/F_4

PECI_EC_R

H_PROCHOT#

Intel spec VinH min =VCCIO X 0.7

C26

PROC_SELECT#

AN34

SKTOCC#

AL33

CATERR#

AN33

PECI

AL32

PROCHOT#

AN32

THERMTRIP#

AM34

PM_SYNC

AP33

UNCOREPWRGOOD

V8

SM_DRAMPWROK

AR33

RESET#

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

Boot S3

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

S3 RSM

CLOCKS

CLOCKS

DDR3

DDR3

JTAG & BPM

JTAG & BPM

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

MISC

MISC

A28

BCLK

A27

BCLK#

CLK_DP_P_R

A16

CLK_DP_N_R

A15

CPU_DRAMRST#

R8

SM_RCOMP_0

AK1

SM_RCOMP_1

A5

SM_RCOMP_2

A4

SM_RCOMP_0, SM_RCOMP_1 20mil / SM_RCOMP_2 15mil.

AP29

PRDY#

AP27

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

AR26

AR27

AP30

AR28

AP26

AL35

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

XDP_TCLK

XDP_TMS

XDP_TRST#H_PM_SYNC

XDP_TDI

XDP_TDO

XDP_DBRST#

CLK_CPU_BCLKP

CLK_CPU_BCLKN

R4 1K_4R4 1K_4

1 2

R5 1K_4R5 1K_4

1 2

For eDP

R8 140/F_4R8 140/F_4

1 2

R9 25.5/F_4R9 25.5/F_4

1 2

R10 200/F_4R10 200/F_4

1 2

TP28TP28

TP37TP37

TP38TP38

TP41TP41

TP42TP42

+3.3V_RUN

1 2

R18 1K_4R18 1K_4

CLK_CPU_BCLKP 24

CLK_CPU_BCLKN 24

+1.05V_PCH

IMVP7_PROCHOT#

R14 62_4R14 62_4

12

+1.05V_PCH

DRAM_PWRGD

SYS_PWROK

SM_DRAMPWROK

U2

U2

74AHC1G09GW

74AHC1G09GW

3 5

+1.5V_CPU

12

C33

C33

0.1U/16V_4

0.1U/16V_4

SM_DRAMPWROK_R

4

4

+1.5V_CPU

R25

R25

200_4

200_4

1 2

R27 130_4R27 130_4

1 2

100 ns after +1.5V_CPU

reaches 80%

Follow #DG1.5 471984 P119

SM_DRAMPWROK

Follow #DG1.5 471984 P130

DRAMRST# Routing Illustration

+1.5V_SUS

Q1

Q1

R21

R21

2N7002W

2N7002W

1K_4

1K_4

1 2

DDR3_DRAMRST#11,12

DDR_HVREF_RST_PCH9,24

3

R22 1K_4R22 1K_4

DDR_HVREF_RST_PCH

2

12

+3.3V_SUS

1 2

R26 1K_4R26 1K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

3 1

2

12

C34

C34

0.047U/10V_4

0.047U/10V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Ivy Bridge 2/5

Ivy Bridge 2/5

Ivy Bridge 2/5

1

12

R23

R23

4.99K/F_4

4.99K/F_4

R08

R08

R08

7 55

7 55

7 55

CPU_DRAMRST#DDR3_DRAMRST#_RDDR3_DRAMRST#

1A

1A

1A

B B

Follow #DG1.5 471984 P128

DDR Power Gating Topology

A A

C854 *100P/50V_4_NCC854 *100P/50V_4_NC

12

C860 *100P/50V_4_NCC860 *100P/50V_4_NC

12

PM_DRAM_PWRGD20

EC_PWROK20,38

5

PM_DRAM_PWRGD

EC_PWROK

H_PROCHOT#

CPU_PLTRST#_R

12

R24

R24

200_4

200_4

+3.3V_SUS

2

1

Page 8

5

4

3

2

1

Ivy Bridge Processor (DDR3)

U1D

D10

K10

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

C9

A7

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

K9

J10

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

R6

J7

J8

J9

U1D

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

M_B_CLKP0

AE2

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CLK[2]

SB_CLK#[2]

SB_CKE[2]

SB_CLK[3]

SB_CLK#[3]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

M_B_CLKN0

M_B_CKE0

M_B_CLKP1

M_B_CLKN1

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_ODT0

M_B_ODT1

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_CLKP0 12

M_B_CLKN0 12

M_B_CKE0 12

M_B_CLKP1 12

M_B_CLKN1 12

M_B_CKE1 12

M_B_CS#0 12

M_B_CS#1 12

M_B_ODT0 12

M_B_ODT1 12

M_B_DQSN[7..0] 12

M_B_DQSP[7..0] 12

M_B_A[15..0] 12

U1C

U1C

D D

C C

B B

M_A_DQ[63..0]11

M_A_BS011

M_A_BS111

M_A_BS211

M_A_CAS#11

M_A_RAS#11

M_A_WE#11

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CAS#

M_A_RAS#

M_A_WE#

F10

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AJ5

AJ6

AJ8

AK8

AJ9

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

AF9

C5

D5

D3

D2

D6

C6

C2

C3

F8

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

M8

N8

N7

M9

N9

M7

V6

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_CLK#[0]

SA_CLK#[1]

SA_CLK#[2]

SA_CLK#[3]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CLK[0]

SA_CKE[0]

SA_CLK[1]

SA_CKE[1]

SA_CLK[2]

SA_CKE[2]

SA_CLK[3]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

M_A_CLKN0

M_A_CKE0

M_A_CLKP1

M_A_CLKN1

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_ODT0

M_A_ODT1

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLKP0 11

M_A_CLKN0 11

M_A_CKE0 11

M_A_CLKP1 11

M_A_CLKN1 11

M_A_CKE1 11

M_A_CS#0 11

M_A_CS#1 11

M_A_ODT0 11

M_A_ODT1 11

M_A_DQSN[7..0] 11

M_A_DQSP[7..0] 11

M_A_A[15..0] 11

M_A_CLKP0

M_B_DQ[63..0]12

M_B_BS012

M_B_BS112

M_B_BS212

M_B_CAS#12

M_B_RAS#12

M_B_WE#12

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS0

M_B_BS1

M_B_BS2

M_B_CAS#

M_B_RAS#

M_B_WE#

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

A A

5

4

3

Ivy Bridge_rPGA_2DPC_Rev0p61

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

PROJECT :

Ivy Bridge 3/5

Ivy Bridge 3/5

Ivy Bridge 3/5

1

R08

R08

R08

8 55

8 55

8 55

1A

1A

1A

Page 9

5

Ivy Bridge Processor

CPU Core Power

SNB: 53A

IVY: 53A

10uF x 24

C35

C35

C38

C43

C43

C58

C58

C76

C76

C82

C82

C89

C89

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

C38

C44

C44

C59

C59

C77

C77

C83

C83

C90

C90

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

C37

C37

12

D D

10U/6.3V_6

10U/6.3V_6

C51

C51

12

10U/6.3V_6

10U/6.3V_6

C57

C57

12

10U/6.3V_8

10U/6.3V_8

C75

C75

12

10U/6.3V_8

10U/6.3V_8

C C

C81

C81

12

10U/6.3V_6

10U/6.3V_6

C88

C88

12

10U/6.3V_6

10U/6.3V_6

B B

C50

C50

C36

C36

C60

C60

C78

C78

C84

C84

C91

C91

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_6

10U/6.3V_6

12

10U/6.3V_6

10U/6.3V_6

+VCC_CORE

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

POWER

POWER

U1F

U1F

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

CORE SUPPLY

CORE SUPPLY

SENSE LINES SVID

SENSE LINES SVID

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

PEG AND DDR

PEG AND DDR

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

4

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

1.05V_PCH

SNB: 8.5A

IVY: 8.5A

10F x12

C45

C45

C61

C61

H_CPU_SVIDALRT#

VR_SVID_CLK

VR_SVID_DATA

1 2

R39 100/F_4R39 100/F_4

1 2

R40 100/F_4R40 100/F_4

1 2

R41 10_4R41 10_4

1 2

R42 10_4R42 10_4

+1.05V_PCH

C52

C52

10U/6.3V_8

10U/6.3V_8

12

12

10U/6.3V_8

10U/6.3V_8

C62

C62

10U/6.3V_8

10U/6.3V_8

12

12

10U/6.3V_8

10U/6.3V_8

SMDDR_VREF_DQ0_M3_C

*AP2302GN_NC

*AP2302GN_NC

SMDDR_VREF_DQ1_M3_C

*AP2302GN_NC

*AP2302GN_NC

+VCC_CORE

VCCSENSE

VSSSENSE

+1.05V_PCH

VCCIO_SENSE

VSSIO_SENSE

C46

C46

C63

C63

10U/6.3V_8

10U/6.3V_8

12

10U/6.3V_8

10U/6.3V_8

12

Q2

Q2

Q3

Q3

C47

C47

C64

C64

2

2

C49

C49

C48

C48

10U/6.3V_8

10U/6.3V_8

12

12

10U/6.3V_8

10U/6.3V_8

C65

C65

C66

C66

10U/6.3V_8

10U/6.3V_8

12

12

10U/6.3V_8

10U/6.3V_8

M3 VREF

SMDDR_VREF_DQ0_M3

31

DDR_HVREF_RST_PCH

SMDDR_VREF_DQ1_M3

31

Vgs=2.5V Rds=115m

VCCSENSE 52

VSSSENSE 52

VCCIO_SENSE 50

VSSIO_SENSE 50

3

12

*10U/6.3V_8_NC

*10U/6.3V_8_NC

12

10U/6.3V_8

10U/6.3V_8

+1.8V_RUN

CPU VGT

SNB: 21.5A

IVY: 33A

10uF x 12

C39

C39

12

22U/6.3V_8

22U/6.3V_8

C53

C53

12

22U/6.3V_8

22U/6.3V_8

C67

C67

12

22U/6.3V_8

22U/6.3V_8

CPU VCCPL

SNB: 1.2A

IVY: 1.2A

10uF x 1

1uF x 2

SMDDR_VREF_DQ0_M3 11

DDR_HVREF_RST_PCH 7,24

SMDDR_VREF_DQ1_M3 12

+VCC_GFX_CORE

C40

C40

12

10U/6.3V_6

10U/6.3V_6

C54

C54

22U/6.3V_8

22U/6.3V_8

12

C68

C68

12

10U/6.3V_6

10U/6.3V_6

C92

C92

12

10U/6.3V_6

10U/6.3V_6

2

Ivy Bridge Processor (GRAPHIC POWER)

POWER

POWER

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

SM_VREF

SA_DIMM_VREFDQ

VREFMISC

VREFMISC

SB_DIMM_VREFDQ

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

VCCIO_SEL

PS_S3CNTRL 11

GRAPHICS

GRAPHICS

1.8V RAIL

1.8V RAIL

+5V_ALW +15V_ALW

12

R37

R37

10K_4

10K_4

PS_S3CNTRL

34

Q5A

Q5A

5

DMN66D0LDW-7

DMN66D0LDW-7

C41

C41

C55

C55

C93

C93

12

22U/6.3V_8

22U/6.3V_8

12

22U/6.3V_8

22U/6.3V_8

C69

C69

12

10U/6.3V_6

10U/6.3V_6

12

1U/6.3V_4

1U/6.3V_4

SIO_SLP_S3#20,38,48

C42

C42

C56

C56

22U/6.3V_8

22U/6.3V_8

C70

C70

C94

C94

12

10U/6.3V_6

10U/6.3V_6

12

12

22U/6.3V_8

22U/6.3V_8

12

1U/6.3V_4

1U/6.3V_4

AT24

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

SIO_SLP_S3#

B6

A6

A2

U1G

U1G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

VCCPLL1

VCCPLL2

VCCPLL3

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

1 2

R28 100_4R28 100_4

VCC_AXG_SENSE

AK35

VSS_AXG_SENSE

AK34

1 2

R29 100_4R29 100_4

+VDDR_REF_CPU

AL1

CAD Note: +VDDR_REF_CPU should

have 10 mil trace width

SMDDR_VREF_DQ0_M3_C

B4

SMDDR_VREF_DQ1_M3_C

D1

R31

R31

R30

R30

*1K_4_NC

*1K_4_NC

*1K_4_NC

*1K_4_NC

1 2

C71

C71

12

10U/6.3V_6

10U/6.3V_6

C79

C79

12

10U/6.3V_6

10U/6.3V_6

12

C85

C85

10U/6.3V_6

10U/6.3V_6

1 2

R399 100_4R399 100_4

VCCSA_SENSE

VCCSA_VID0

VCCSA_VID1

1 2

VCCSA_VID0

VCCSA_VID1

12

R38

R38

100K_4

100K_4

61

Q5B

Q5B

2

DMN66D0LDW-7

DMN66D0LDW-7

1 2

C72

C72

12

10U/6.3V_6

10U/6.3V_6

C80

C80

12

10uF x 3

12

10U/6.3V_6

10U/6.3V_6

R33*0_4_NC R33*0_4_NC

PS_S3CNTRL_S

10U/6.3V_6

10U/6.3V_6

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

M27

M26

L26

J26

J25

J24

H26

H25

H23

C22

C24

A19

Take care Q3 Vgs(MAX)=2.5

1

+VCC_GFX_CORE

VCC_AXG_SENSE 52

VSS_AXG_SENSE 52

+VDDR_REF_CPU

CPU MCH

SNB: 5A

IVY: 5A

10uF x 6

C74

C74

C73

C73

12

12

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

10U/6.3V_6

CPU SA

SNB: 6A

IVY: 6A

12

C86

C86

C87

C87

10U/6.3V_6

10U/6.3V_6

H_VTTVID1

5A

Q4

AON7410Q4AON7410

8

762

5

4

12

C95

C95

*4700P/25V_4_NC

*4700P/25V_4_NC

+VDDR_REF_CPU

+3.3V_RUN

3

1

+VCCSA_CORE

VCCSA_SENSE 51

VCCSA_VID0 51

VCCSA_VID1 51

1 2

R34 1K_4R34 1K_4

1 2

R35 *1K_4_NCR35 *1K_4_NC

1 2

R36 1K_4R36 1K_4

S3 Power reduce

+1.5V_SUS +1.5V_CPU

+1.5V_CPU

+1.5V_CPU

+VCCSA_CORE

12

R32

R32

10K_4

10K_4

H_VTTVID1 50

+1.05V_PCH

R43

R43

1K/F_4

1K/F_4

A A

Layout note: need routing

together and ALERT need

between CLK and DATA

5

VR_SVID_CLK

VR_SVID_CLK 52

Place PU resistor close to CPU

+1.05V_PCH +1.05V_PCH

SVID DATA SVID ALERTSVID CLK

12

R45

R45

130_4

130_4

4

VR_SVID_DATA 52

Place PU resistor close to CPU

12

R46

R46

75/F_4

1 2

R47 43_4R47 43_4

75/F_4

3

VR_SVID_ALERT#H_CPU_SVIDALRT#VR_SVID_DATA

VR_SVID_ALERT# 52

2

1 2

12

0.1U/16V_4

0.1U/16V_4

R44

R44

C96

C96

1K/F_4

1K/F_4

1 2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

Date: Sheet of

Monday, February 13, 2012

PROJECT :

Ivy Bridge 4/5

Ivy Bridge 4/5

Ivy Bridge 4/5

1

R08

R08

R08

9 55

9 55

9 55

1A

1A

1A

Page 10

5

4

3

2

1

Ivy Bridge Processor (GND) Ivy Bridge Processor (RESERVED, CFG)

U1H

U1H

AT35

VSS1

AT32

VSS2

AT29

VSS3

AT27

VSS4

AT25

VSS5

AT22

VSS6

AT19

VSS7

AT16

VSS8

D D

C C

B B

AT13

VSS9

AT10

VSS10

AT7

VSS11

AT4

VSS12

AT3

VSS13

AR25

VSS14

AR22

VSS15

AR19

VSS16

AR16

VSS17

AR13

VSS18

AR10

VSS19

AR7

VSS20

AR4

VSS21

AR2

VSS22

AP34

VSS23

AP31

VSS24

AP28

VSS25

AP25

VSS26

AP22

VSS27

AP19

VSS28

AP16

VSS29

AP13

VSS30

AP10

VSS31

AP7

VSS32

AP4

VSS33

AP1

VSS34

AN30

VSS35

AN27

VSS36

AN25

VSS37

AN22

VSS38

AN19

VSS39

AN16

VSS40

AN13

VSS41

AN10

VSS42

AN7

VSS43

AN4

VSS44

AM29

VSS45

AM25

VSS46

AM22

VSS47

AM19

VSS48

AM16

VSS49

AM13

VSS50

AM10

VSS51

AM7

VSS52

AM4

VSS53

AM3

VSS54

AM2

VSS55

AM1

VSS56

AL34

VSS57

AL31

VSS58

AL28

VSS59

AL25

VSS60

AL22

VSS61

AL19

VSS62

AL16

VSS63

AL13

VSS64

AL10

VSS65

AL7

VSS66

AL4

VSS67

AL2

VSS68

AK33

VSS69

AK30

VSS70

AK27

VSS71

AK25

VSS72

AK22

VSS73

AK19

VSS74

AK16

VSS75

AK13

VSS76

AK10

VSS77

AK7

VSS78

AK4

VSS79

AJ25

VSS80

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

U1I

U1I

T35

VSS161

T34

VSS162

T33

VSS163

T32

VSS164

T31

VSS165

T30

VSS166

T29

VSS167

T28

VSS168

T27

VSS169

T26

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

N35

VSS177

N34

VSS178

N33

VSS179

N32

VSS180

N31

VSS181

N30

VSS182

N29

VSS183

N28

VSS184

N27

VSS185

N26

VSS186

M34

VSS187

L33

VSS188

L30

VSS189

L27

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

K35

VSS199

K32

VSS200

K29

VSS201

K26

VSS202

J34

VSS203

J31

VSS204

H33

VSS205

H30

VSS206

H27

VSS207

H24

VSS208

H21

VSS209

H18

VSS210

H15

VSS211

H13

VSS212

H10

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

G35

VSS223

G32

VSS224

G29

VSS225

G26

VSS226

G23

VSS227

G20

VSS228

G17

VSS229

G11

VSS230

F34

VSS231

F31

VSS232

F29

VSS233

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

VSS

VSS

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

TP2TP2

TP5TP5

TP3TP3

TP4TP4

CFG2

U1E

U1E

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

Ivy Bridge_rPGA_2DPC_Rev0p61

Ivy Bridge_rPGA_2DPC_Rev0p61

VCC_DIE_SENSE

VSS_DIE_SENSE

CFG

CFG

RESERVED

RESERVED

AH27

AH26

L7

RSVD28

AG7

RSVD29

AE7

RSVD30

AK2

RSVD31

W8

RSVD32

AT26

RSVD33

AM33

RSVD34

AJ27

RSVD35

T8

RSVD37

J16

RSVD38

H16

RSVD39

G16

RSVD40

AR35

RSVD41

AT34

RSVD42

AT33

RSVD43

AP35

RSVD44

AR34

RSVD45

B34

RSVD46

A33

RSVD47

A34

RSVD48

B35

RSVD49

C35

RSVD50

AJ32

RSVD51

AK32

RSVD52

#27636 SNB EDS0.7v1 no function.

AN35

BCLK_ITP

AM35

BCLK_ITP#

AT2

RSVD56

AT1

RSVD57

AR1

RSVD58

B1

KEY

For rPGA socket, RSVD59 pin should be left NC

CFG[6:5] (PCIE Port Bifurcation Straps)

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

Processor Strapping

A A

5

CFG2

(PEG Static Lane Reversal)

CFG4

(DP Presence Strap)

CFG7

(PEG Defer Training)

4

Normal Operation Lane Reversed

Disable; No physical DP attached to eDP

PEG train immediately following

xxRESETB de assertion

The CFG signals have a default value of '1' if not terminated on the board.

1 0

Enable; An ext DP device is connected to eDP

PEG wait for BIOS training

3

CFG2

R48 1K_4R48 1K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Ivy Bridge 5/5

Ivy Bridge 5/5

Ivy Bridge 5/5

Monday, February 13, 2012

Monday, February 13, 2012

Monday, February 13, 2012

12

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

R08

R08

R08

10 55

10 55

10 55

1A

1A

1A

Page 11

1

M_A_A[15..0]8

A A

SO-DIMMA SPD Address is 0XA0

SO-DIMMA TS Address is 0X30

M_A_BS08

M_A_BS18

M_A_BS28

M_A_CS#08

M_A_CS#18

M_A_CLKP08

M_A_CLKN08

M_A_CLKP18

M_A_CLKN18

M_A_CKE08

M_A_CKE18

M_A_CAS#8

RP2 10KX2RP2 10KX2

1

3

B B

C C

+1.5V_SUS

12

12

C98

C98

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

0.1U/16V_4

D D

M_A_RAS#8

M_A_WE#8

2

4

WLAN_SCLK12,24,33

WLAN_SDATA12,24,33

M_A_ODT08

M_A_ODT18

M_A_DQSP[7..0]8

M_A_DQSN[7..0]8

Place these Caps near So-Dimm0.

C101

C101

12

C100

C100

0.1U/16V_4

0.1U/16V_4

12

0.1U/16V_4

0.1U/16V_4

C99

C99

2

C102

C102

12

10U/6.3V_8

10U/6.3V_8

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CS#0

M_A_CS#1

M_A_CLKP0

M_A_CLKN0

M_A_CLKP1

M_A_CLKN1

M_A_CKE0

M_A_CKE1

M_A_CAS#

M_A_RAS#

M_A_WE#

DIMM0_SA0

DIMM0_SA1

WLAN_SCLK

WLAN_SDATA

M_A_ODT0

M_A_ODT1

M_A_DQSP1

M_A_DQSP0

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_DQSN1

M_A_DQSN0

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

C103

C103

12

10U/6.3V_8

10U/6.3V_8

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

114

121

101

103

102

104

73

74

115

110

113

197

201

202

200

116

120

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

C104

C104

12

10U/6.3V_8

10U/6.3V_8

SMDDR_VREF_DQ0_M39

JDIM1A

JDIM1A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

BA0

BA1

BA2

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DDR3-DIMM0

DDR3-DIMM0

+0.75V_DDR_VTT

C105

C105

12

10U/6.3V_8

10U/6.3V_8

3

(204P)

(204P)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

C106

C106

12

10U/6.3V_8

10U/6.3V_8

M3 VREF

12

M_A_DQ12

5

DQ0

M_A_DQ11

7

DQ1

M_A_DQ9

15

DQ2

M_A_DQ14

17

DQ3

M_A_DQ8

4

DQ4

M_A_DQ10

6

DQ5

M_A_DQ15

16

DQ6

M_A_DQ13

18

DQ7

M_A_DQ4

21

DQ8

M_A_DQ5

23

DQ9

M_A_DQ3

33

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQ6

35

M_A_DQ0

22

M_A_DQ1

24

M_A_DQ7

34

M_A_DQ2

36

M_A_DQ20

39

M_A_DQ17

41

M_A_DQ19

51

M_A_DQ18

53

M_A_DQ16

40

M_A_DQ21

42

M_A_DQ22

50

M_A_DQ23

52

M_A_DQ29

57

M_A_DQ25

59

M_A_DQ30

67

M_A_DQ26

69

M_A_DQ28

56

M_A_DQ24

58

M_A_DQ27

68

M_A_DQ31

70

M_A_DQ33

129

M_A_DQ32

131

M_A_DQ35

141

M_A_DQ38

143

M_A_DQ37

130

M_A_DQ36

132

M_A_DQ34

140

M_A_DQ39

142

M_A_DQ44

147

M_A_DQ45

149

M_A_DQ43

157

M_A_DQ42

159

M_A_DQ41

146

M_A_DQ40

148

M_A_DQ47

158

M_A_DQ46

160

M_A_DQ49

163

M_A_DQ48

165

M_A_DQ54

175

M_A_DQ55

177

M_A_DQ53

164

M_A_DQ52

166

M_A_DQ50

174

M_A_DQ51

176

M_A_DQ60

181

M_A_DQ61

183

M_A_DQ62

191

M_A_DQ63

193

M_A_DQ56

180

M_A_DQ57

182

M_A_DQ59

192

M_A_DQ58

194

12

12

C107

C107

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

SMDDR_VREF_DQ0_M3

C108

C108

4

M_A_DQ[63..0] 8

12

*1U/6.3V_4_NC

*1U/6.3V_4_NC

12

EC830

EC830

EC829

EC829

*1U/6.3V_4_NC

*1U/6.3V_4_NC

R53 *0_4_NCR53 *0_4_NC

1 2

H=8mm,RVS

S3 Power reduce

+0.75V_DDR_VTT

R50

R50

22_4

22_4

1 2

Q7

Q7

31

PS_S3CNTRL

2

2N7002W

2N7002W

+1.5V_SUS

+SMDDR_VREF_DQ0

R51

R51

1K/F_4

1K/F_4

1 2

12

R54

R54

1K/F_4

1K/F_4

5

PS_S3CNTRL 9

M1 VREF

12

C109

C109

0.1U/16V_4

0.1U/16V_4

12

C110

C110

1U/10V_6

1U/10V_6

+3.3V_RUN

+1.5V_SUS

1 2

1 2

R52

R52

1K/F_4

1K/F_4

R55

R55

1K/F_4

1K/F_4

6

+3.3V_RUN

DDR3_DRAMRST#7,12

+SMDDR_VREF_DIMM0

R49 *10K_4_NCR49 *10K_4_NC

+SMDDR_VREF_DQ0

+SMDDR_VREF_DIMM0

12

C111

C111

0.1U/16V_4

0.1U/16V_4

12

C97

C97

0.1U/16V_4

0.1U/16V_4

1 2

12

C112

C112

1U/10V_6

1U/10V_6

+1.5V_SUS

DDR3_DRAMRST#

20120213

Change C110 C112 to 1U

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

199

77

122

125

198

30

1

126

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

7

JDIM1B

JDIM1B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDDSPD

NC1

NC2

NCTEST

EVENT#

RESET#

VREF_DQ

VREF_CA

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

DDR3-DIMM0

DDR3-DIMM0

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

(204P)

(204P)

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

GND

205

8

12

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

GND

206

+0.75V_DDR_VTT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.