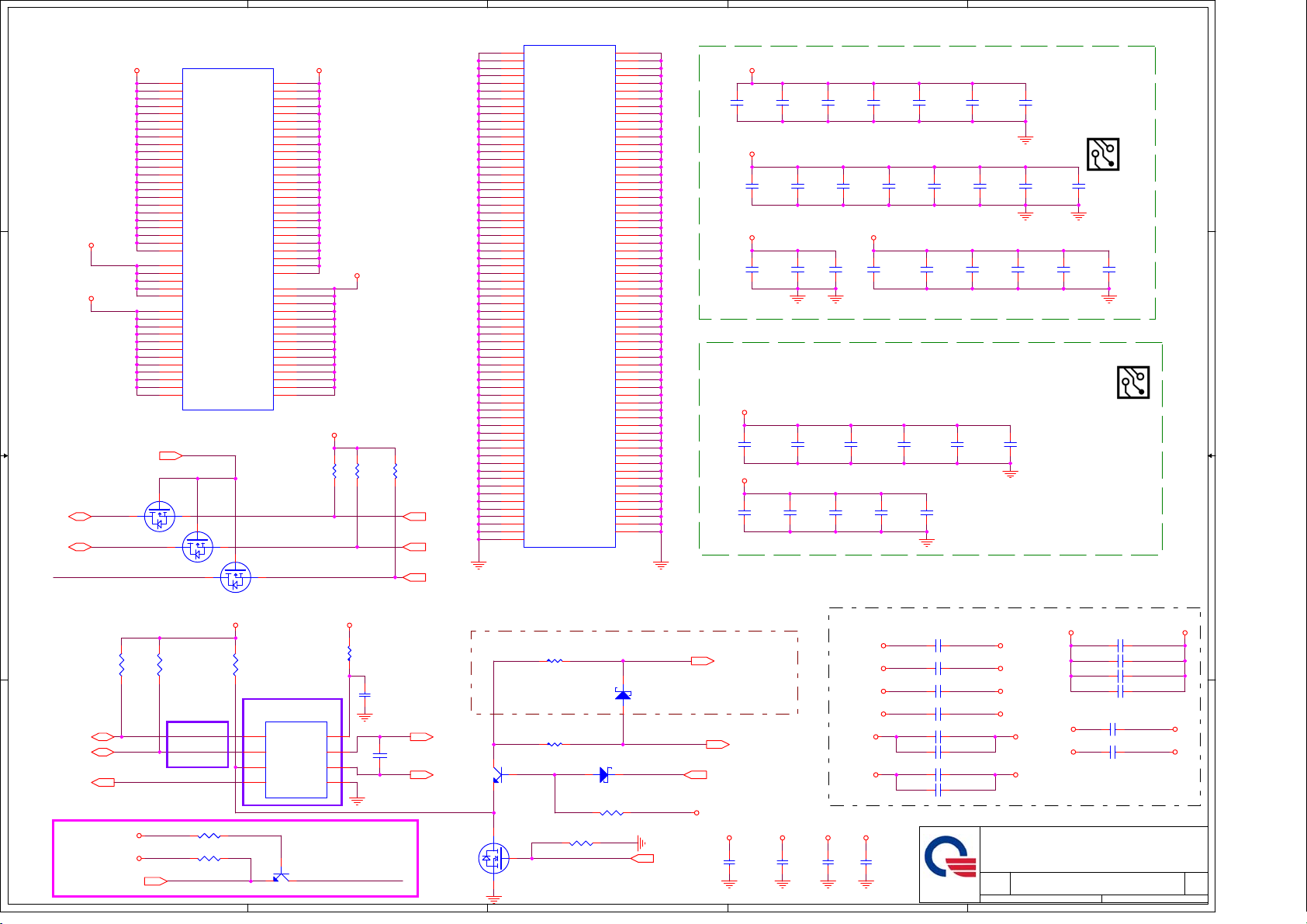

Page 1

1

2

3

4

5

6

7

8

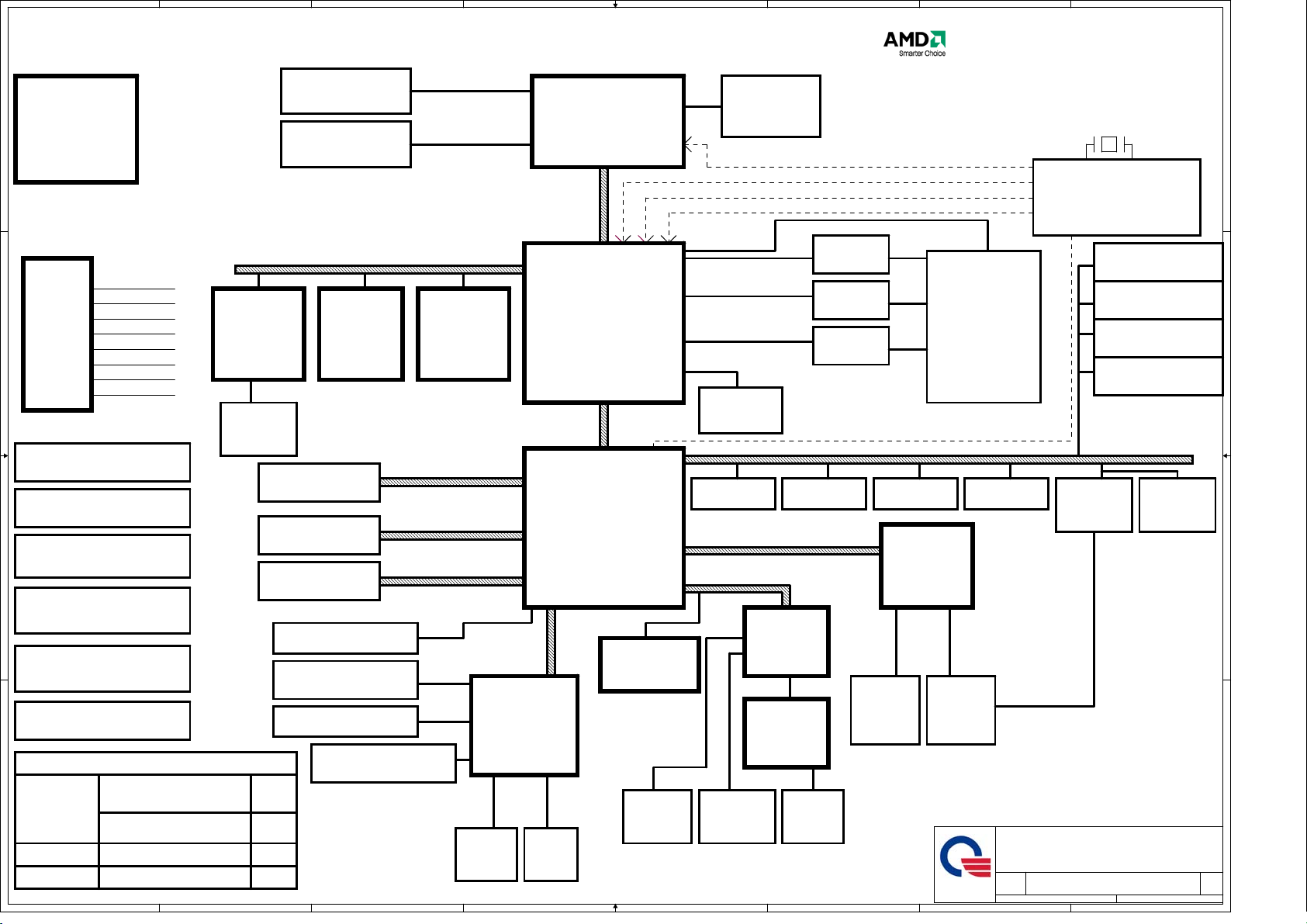

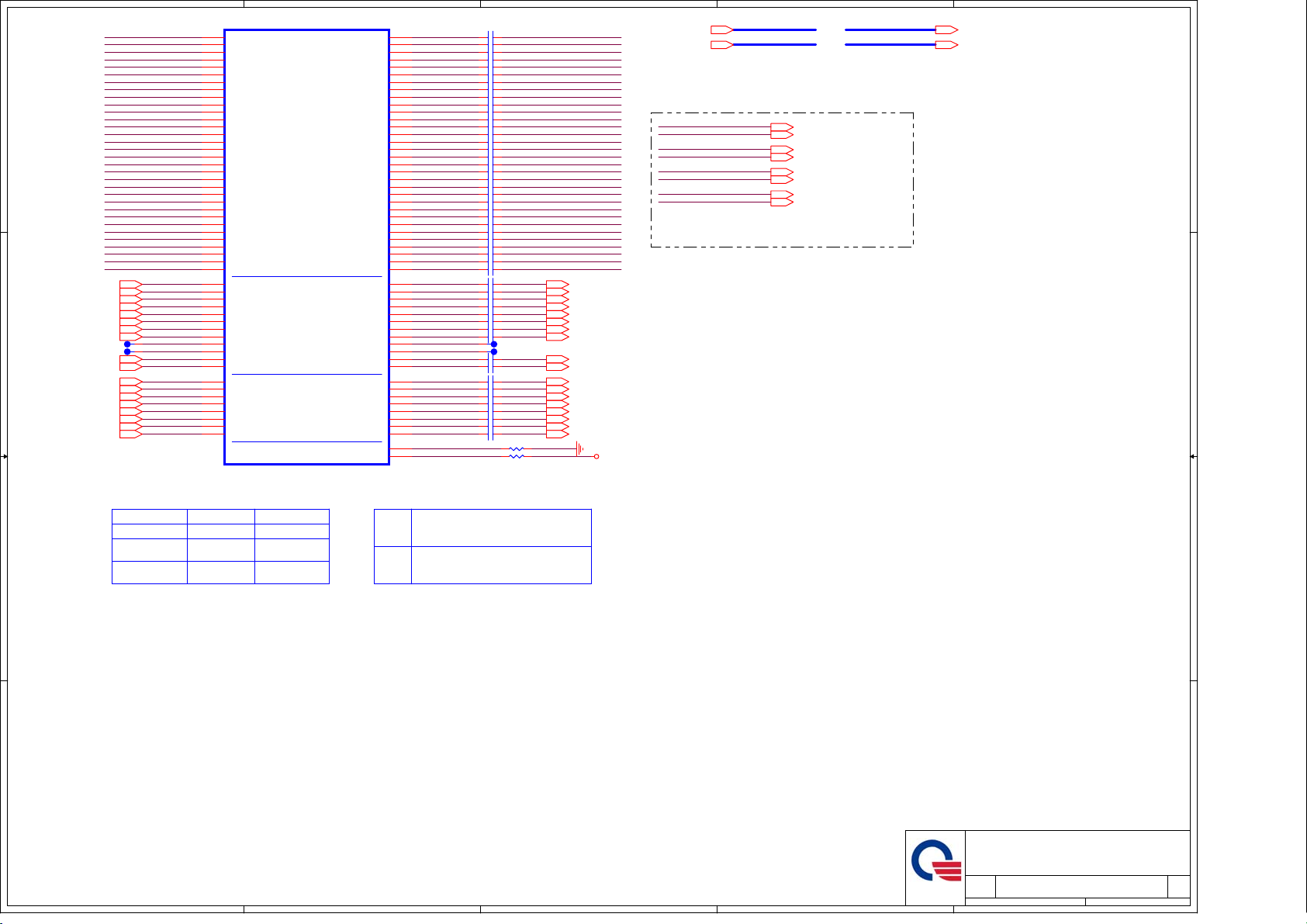

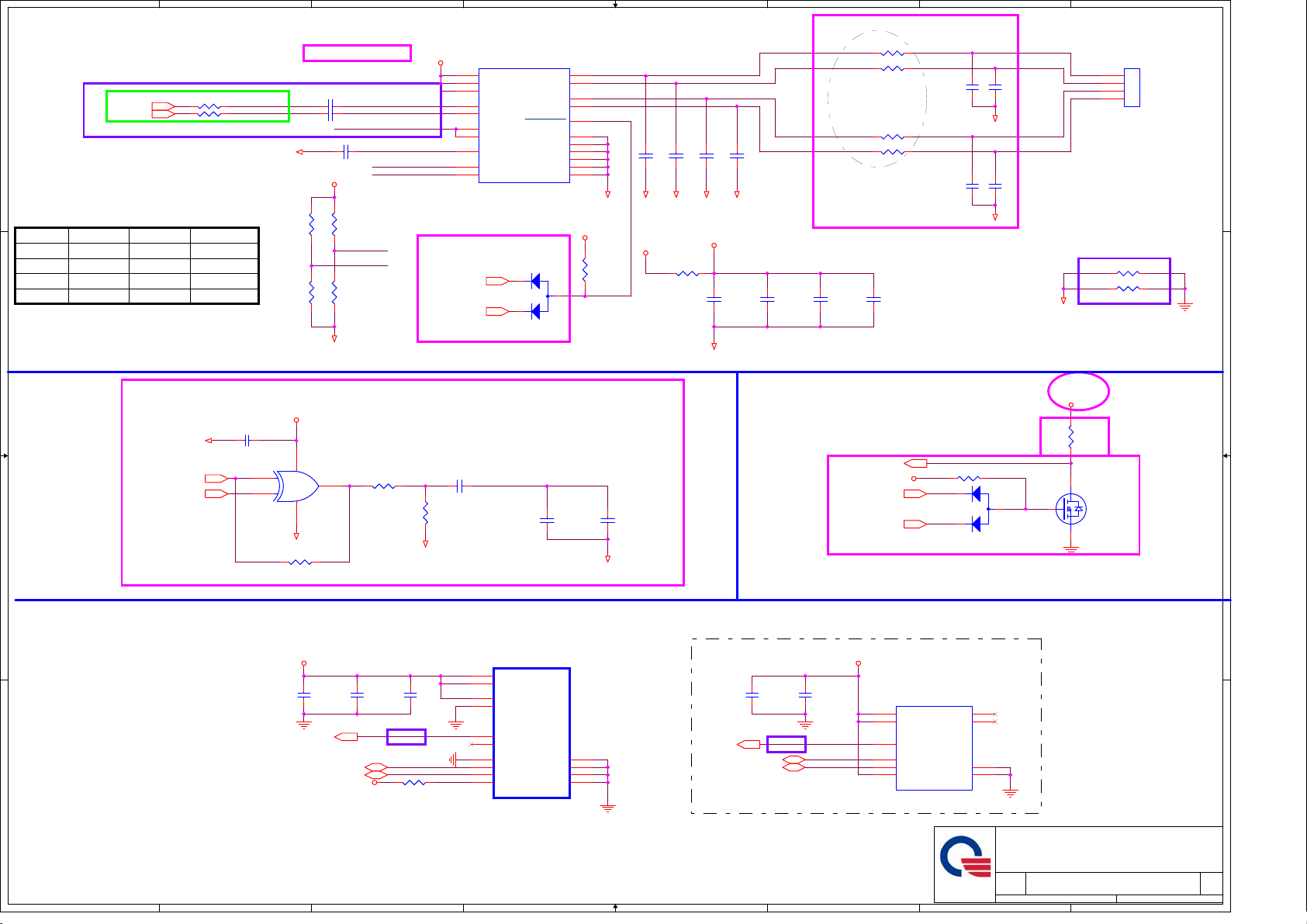

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : IN1

A A

LAYER 3 : IN2

LAYER 4 : VCC

LAYER 5 : IN3

LAYER 6 : BOT

Cable

Docking

VGA

RJ-45

CIR/Pwr btn

SPDIF Out

B B

Stereo MIC

Headphone Jack

USB Port

X1

LAN

Realtek

PCIE-LAN

RTL8102E/8111C

(10/100/GagaLAN)

PAGE 31,32

VOL Cntr

PAGE 37

RJ45

PAGE 31

SYSTEM CHARGER(ISL6251A)

PAGE 44

SYSTEM POWER ISL6236IRZA-T

PAGE 38

DDR II SMDDR_VTERM

1.8V/1.8VSUS(TPS51116REGR)

C C

VCCP +1.1V AND +1.2V(MAX8717)

PAGE 41

PAGE 39

VGACORE(1.1V~1.2V)Oz8118

PAGE 42

CPU CORE ISL6265A

PAGE 40

SMBUS TABLE

Clock gen/Robson/TV tuner

SB--SCL0/SD0

D D

EC --SCL/SD

EC--SCL2/SD2

/DDR2/DDR2 thermal/Accelerometer

epress card

Wlan Card

Battery charge/discharge

VGA thermal/system thermal

1

2

DDRII-SODIMM1

PAGE 7,8

DDRII-SODIMM2

PAGE 7,8

Express

Card

(NEW CARD)

TWO SATA - HDD

PAGE 33

SATA - CD-ROM

PAGE 33

E-SATA

PAGE 30

Accelerometer

LIS3LV02DL

Keyboard

Touch Pad

CIR (AUDIO CONN)

Capacitive Sense

+3V

+3VS5

+3VPCU

+3V

SW

X1

PAGE 33

PAGE 28

PAGE 34

PAGE 34

PAGE 27

DDRII 667/800 MHz

DDRII 667/800 MHz

X3

Mini PCI-E

Card

(Wireless LAN/TV

TUNNER)

PAGE 36

SATA0,1 150MB

SATA0 150MB

SATA4 150MB

PAGE 34

3

PCI-E

SMBUS

ENE KBC

KB3926 Cx

FAN

PAGE 37

AMD

Griffin

S1G2 Processor

Lion

Sabie

638P (uPGA)/35W

PAGE 3,4,5,6

HT3

CPU THERMAL

SENSOR

PCI-Express 16X

PAGE 5

CPU_CLK

NBGFX_CLK

NBGPP_CLK

SBLINK_CLK

HDMI

PAGE 23

NORTH BRIDGE

RX781

RS780MN

/

A12

21mm X 21mm, 528pin BGA

PAGE 8,9,10,11,

ALINK X4

SOUTH BRIDGE

Side port

256mb RAM

for UMA only

PAGE 8

USB2.0

1,8,9

PAGE 30 PAGE 30

X3

SB700 A12

21mm X 21mm, 528pin BGA

4.5W(Ext)

4.3W(Int)

PAGE 12,13.14.15.16 PAGE 27

LPC

MDC CONN

PAGE 29

PAGE 35

SPI

PAGE 35

4

PCIE BUS

Azalia

AUDIO CONNDigital MIC

(Phone/ MIC)

PAGE 27PAGE 30

5

IDT

92HD71B7

PAGE 27

AUDIO

Amplifier

TPA6017A2

PAGE 28

CRT

PAGE 24

LVDS

PAGE 23

5

BlueflameUSB2.0 Ports

Audio

Conn

PAGE 28

IEEE1394

connect for

Discrete

only

6

2

Webcam

X1

JMICRON

JMD380 for

Discrete

only

ATI M82-S

for

Discrete

only

64 Bit,DDR2*4

M82-SCE A11

PAGE 17,18,19

20,21,22

SBSRC_CLK

PAGE 30

Fingerprint

Memory

CardReader

PAGE 25PAGE 26

NB5/RD5

14.318MHz

CLOCK GEN

ICS9LPRS476AKLFT-->HP

SLG8SP626VTR-->HP

RTM880N-795 -->HP

10

PCI-E WLAN Card x1

11

TV-TUNER Card x1

7

Express Card x1

4

Cable Docking x1

6

PAGE 30

3

Flash Media

for UMA only

RTS5158

PAGE 25

PROJECT : QT8

Quanta Computer Inc.

Size Document Number Rev

Custom

Block Diagram

Date: Sheet

7

QT8 SYSTEM DIAGRAM

01

PAGE 2

PAGE 36

PAGE 36

PAGE 33

PAGE 37

Touch Screen

for Discrete

only

of

145Tuesday, February 19, 2008

8

1A

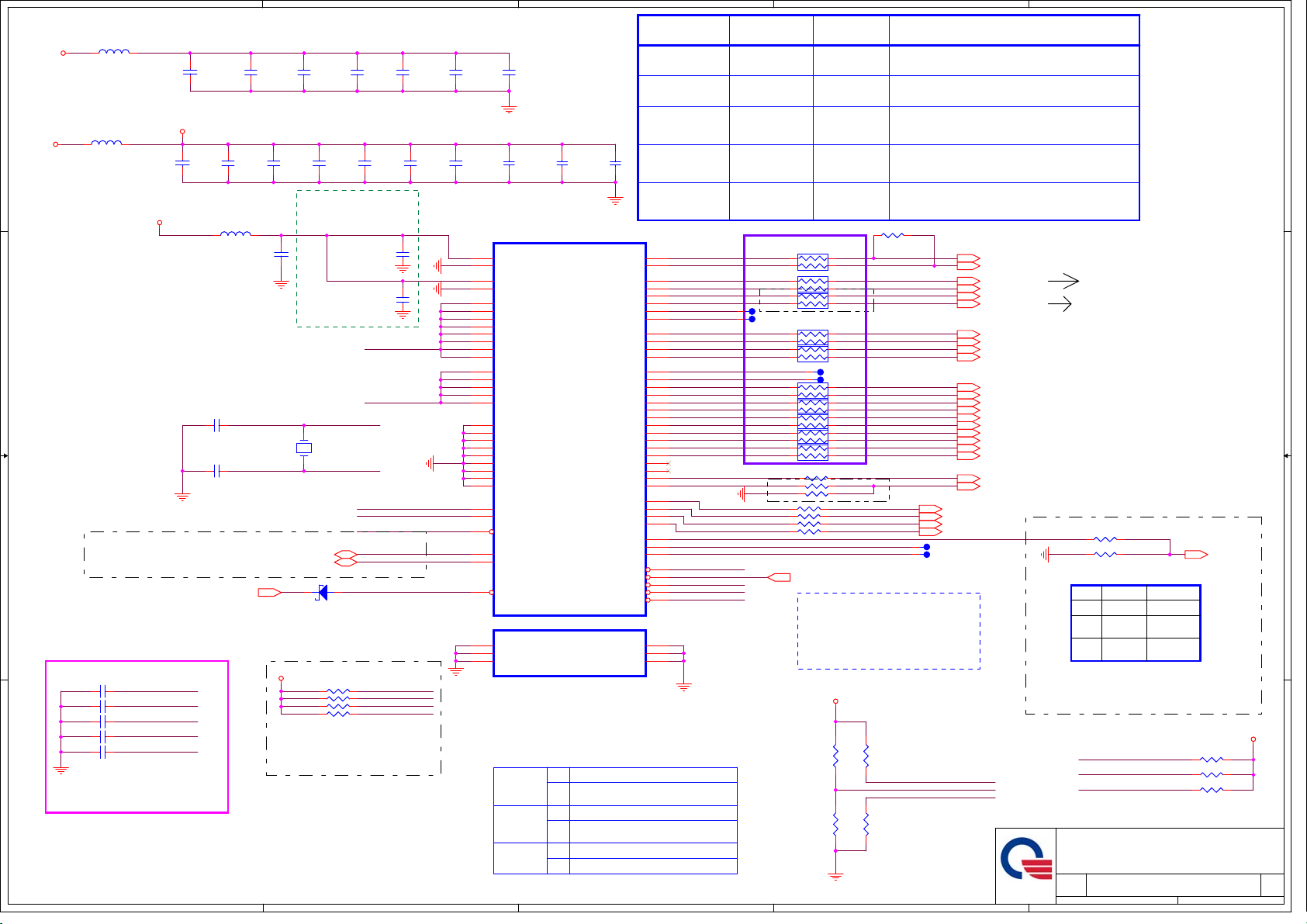

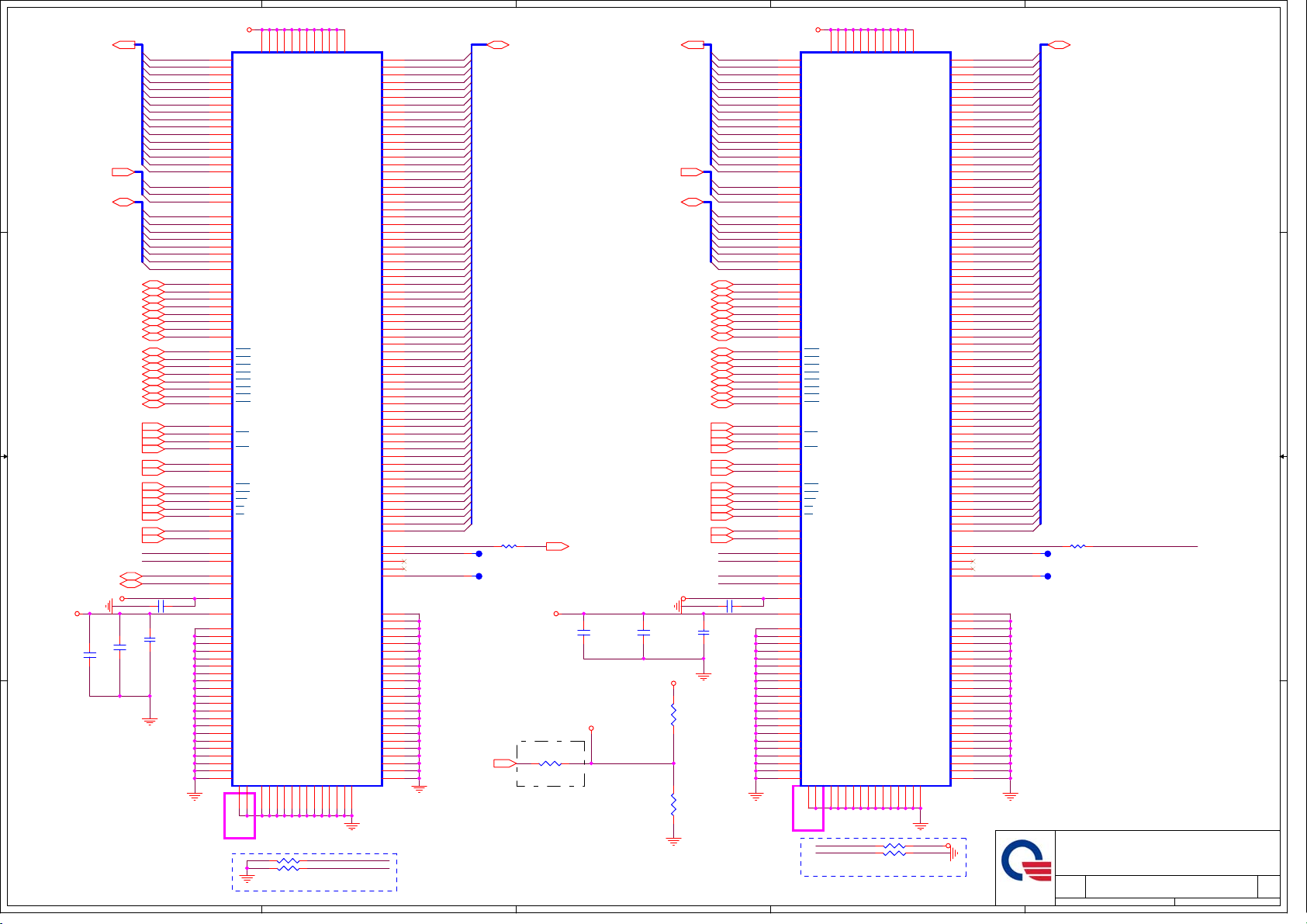

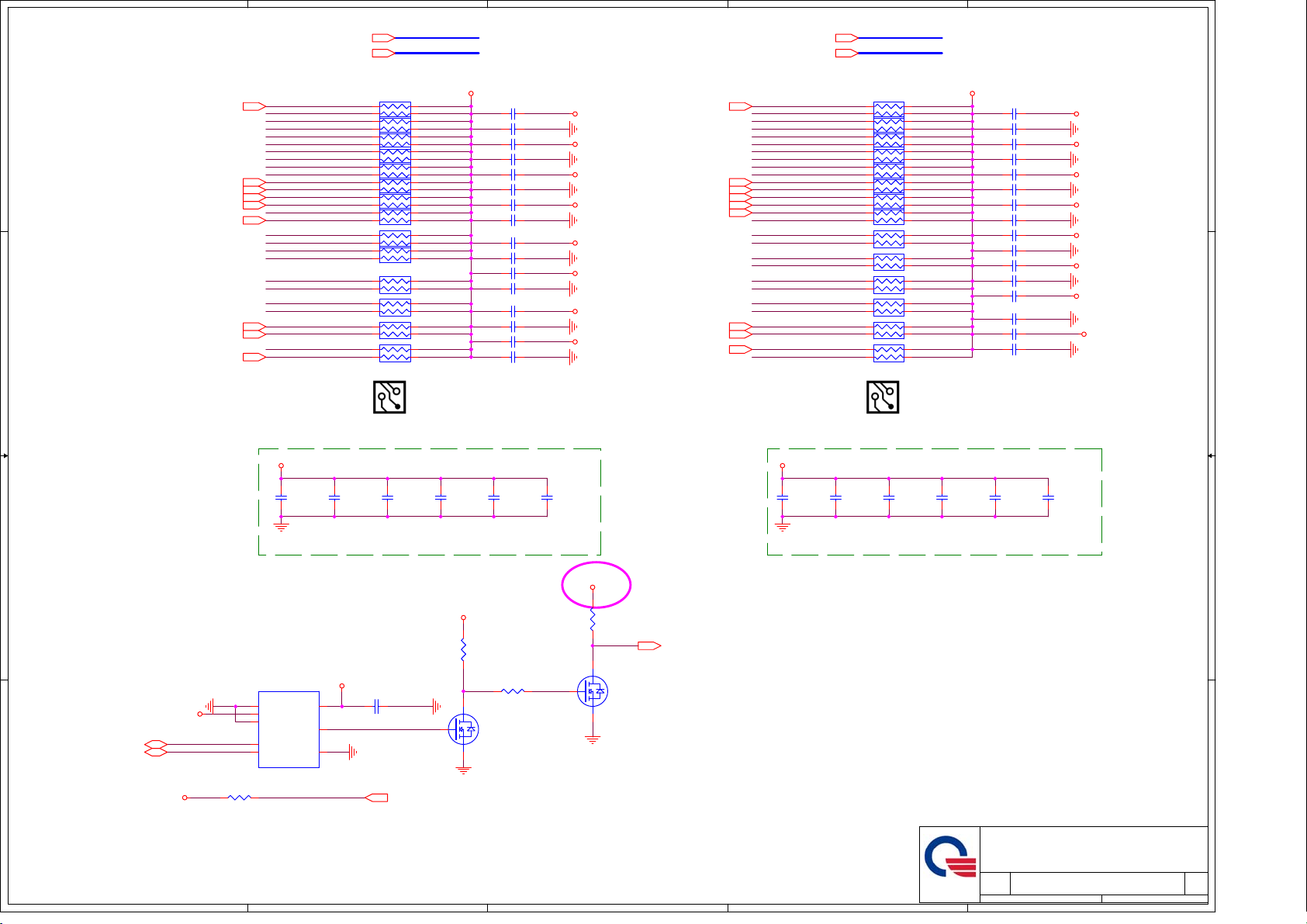

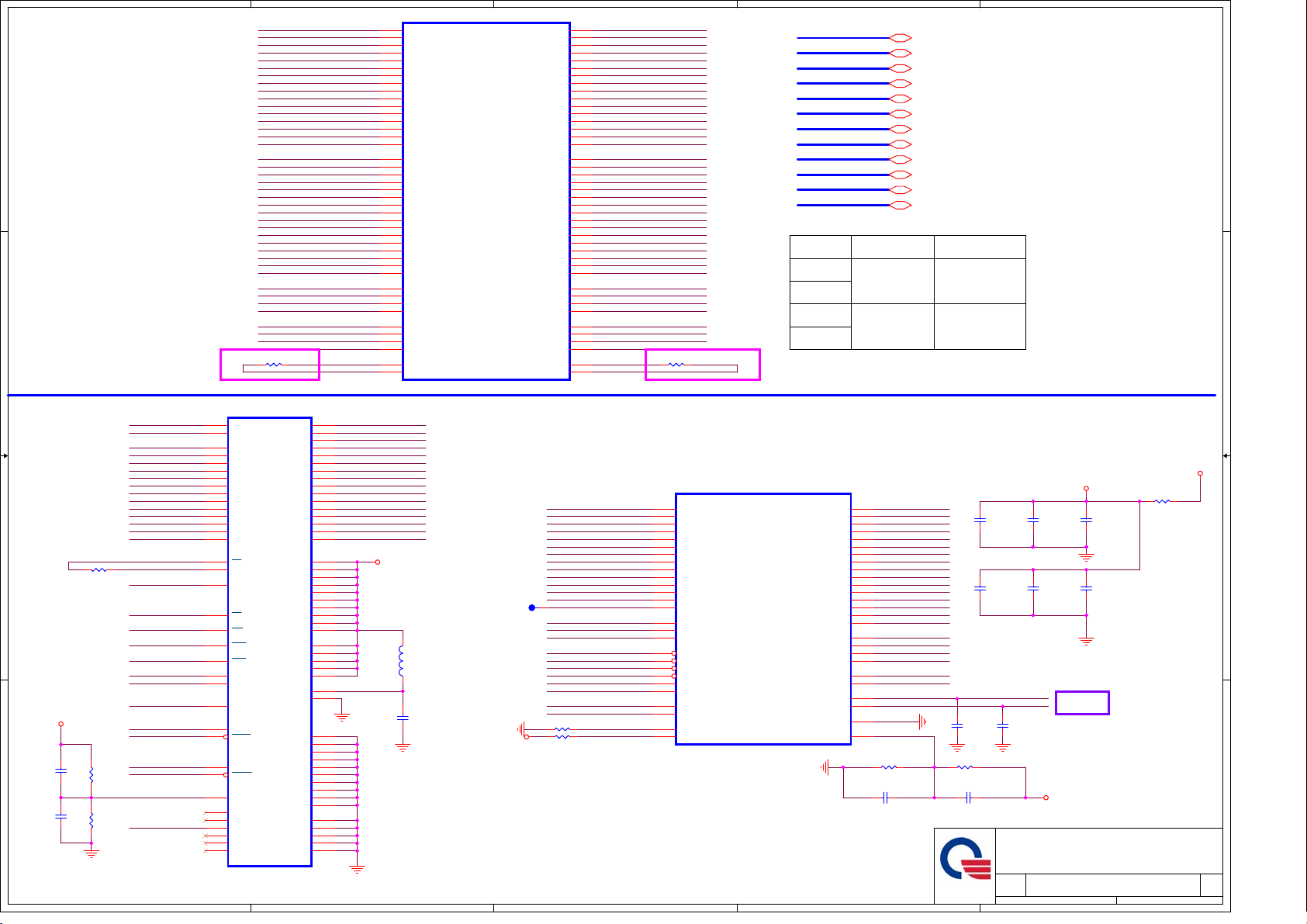

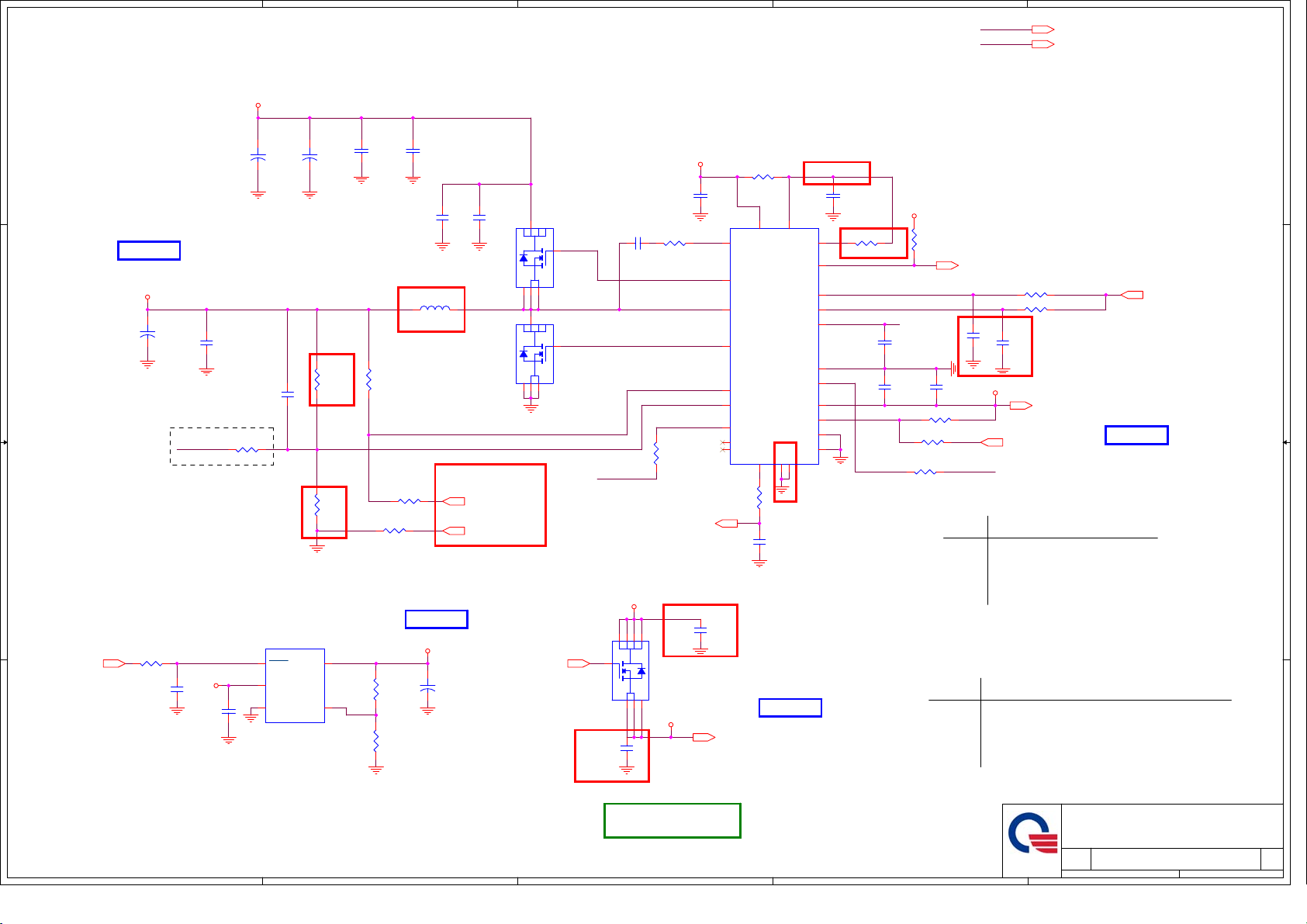

Page 2

5

4

3

2

1

L49

+1.2V

BLM18PG181SN1D(180,1.5A)_6

600 ohms@100Mhz

D D

+3V

C C

B B

A A

DCR: 0.5 ohm

600 ohms@100Mhz

L51

BLM18PG181SN1D(180,1.5A)_6

can remove MOSFET level shift

SB/clock gen / DDR2 is 3.3V/S0

power level

C952 *10P/50V_4

C953 *10P/50V_4

C954 *10P/50V_4

C955 *10P/50V_4

C956 *10P/50V_4

SI-1 modified -- reserve for EMT

60 ohm, 0.5A

C523

10U/6.3V_8

+3V_CLKVDD

C541

10U/6.3V_8

+3V_CLKVDD

BLM18PG181SN1D(180,1.5A)_6

CHIPSET_PCIE_SLOW_SB#14

when driven low

to reduced setpoint

EXT_NB_OSC

CLK_48M_USB

CLK_48M_CR

EVGA-XTALI

OSC_SPREAD

5

C518

0.1U/10V_4

60 ohm, 0.5A

C468

0.1U/10V_4

0.1U/10V_4

L42

10U/6.3V_8

C466 33P/50V_4

C465 33P/50V_4

C496

0.1U/10V_4

C473

C464

14.318MHZ

0.1U/10V_4

C512

0.1U/10V_4

Place very

close to

C/G

Y2

1 2

PCLK_SMB6,7,13,28,36

PDAT_SMB6,7,13,28,36

D17 *CH501H-40PT L-F

SB_SRC clocks slow

custom CG IC

+3V

R756 *8.2K_4

R757 *8.2K_4

R758 *8.2K_4

R759 *8.2K_4

if use clock

request pin , need

to pull Hi for

default sttting

+1.2V_CLKVDDIO

C527

0.1U/10V_4

+3V_CLKVDD

C522

0.1U/10V_4

+3V_CLK_VDDA

C482

0.1U/10V_4

+3V_CLK_VDDA

C470

0.1U/10V_4

CG_XIN

CG_XOUT

21

only supported with

C521

0.1U/10V_4

C508

0.1U/10V_4

+3V_CLKVDD

+1.2V_CLKVDDIO

CG_XIN

CG_XOUT

CLK_PD#

PCLK_SMB

PDAT_SMB

SB_SRC_SLOW#

CLKREQ0#

CLKREQ2#

CLKREQ3#

CLKREQ4#

4

C476

C500

0.1U/10V_4

C515

0.1U/10V_4

C474

0.1U/10V_4

49

48

62

66

69

29

54

61

38

17

44

3

53

28

37

12

18

72

27

6

52

58

47

36

11

19

67

68

57

1

2

41

73

74

75

0.1U/10V_4

U10A

VDDA

GNDA

VDDREF

GNDREF

VDD48

VDDATIG

VDDCPU

VDDHTT

VDDSB_SRC

VDDSRC

VDDSATA

VDDDOT

VDDCPU_IO

VDDATIG_IO

VDDSB_SRC_IO

VDDSRC_IO1

VDDSRC_IO2

GND48

GNDATIG1

GNDDOT

GNDCPU

GNDHTT

GNDSATA

GNDSB_SRC

GNDSRC1

GNDSRC2

X1

X2

PD#

SMBCLK

SMBDAT

SB_SRC_SLOW#

SLG8SP626VTR

eGND73

eGND74

eGND75

U10B

SLG8SP626VTR

C471

THERMAL GND

C469

0.1U/10V_4

CPUKG0T_LPRS

CPUKG0C_LPRS

ATIG0T_LPRS

ATIG0C_LPRS

ATIG1T_LPRS

ATIG1C_LPRS

ATIG2T_LPRS

ATIG2C_LPRS

SB_SRC0T_LPRS

SB_SRC0C_LPRS

SB_SRC1T_LPRS

SB_SRC1C_LPRS

SRC0T_LPRS

SRC0C_LPRS

SRC1T_LPRS

SRC1C_LPRS

SRC2T_LPRS

SRC2C_LPRS

SRC3T_LPRS

SRC3C_LPRS

SRC4T_LPRS

SRC4C_LPRS

SRC5T_LPRS

SRC5C_LPRS

SRC6T/SATAT_LPRS

SRC6C/SATAC_LPRS

SRC7T_LPRS/27Mhz_SS

SRC7C_LPRS/27Mhz_NS

HTT0T/66M_LPRS

HTT0C/66M_LPRS

48MHz_0

48MHz_1

REF0/SEL_HTT66

REF1/SEL_SATA

REF2/SEL_27

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

eGND77

eGND76

eGND78

CLK_VGA_27M_SS

CLK_VGA_27M_NSS

56

55

33

32

31

30

26

25

40

39

35

34

23

22

21

20

16

15

14

13

10

9

8

7

46

45

5

4

60

59

71

70

65

64

63

24

51

50

43

42

77

76

78

ICS ICS9LPR476BKLFT--AJRS4760000

SLG8SP626VTR--AJ006260000

SLG

RTM880N-795-- AJ008800000RTL

* default

SEL_HTT66

SEL_SATA

SEL_27 1027MHz non-spreading singled clock

66 MHz 3.3V single ended HTT clock

1

*01100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

100 MHz spreading differential SRC clock

*0

*

100 MHz spreading differential SRC clock

3

NBGFX_CLKP

NBGFX_CLKN

EXT_GFX_CLKP

EXT_GFX_CLKN

NBGPP_CLKP

NBGPP_CLKN

SBLINK_CLKP

SBLINK_CLKN

CPUCLKP

CPUCLKN

NBGFX_CLKP

NBGFX_CLKN

EXT_GFX_CLKN EXT_GFX_CLKN

CLK_PCIE_CARD

CLK_PCIE_CARD# CLK_PCIE_CARD#

NBGPP_CLKN_R

NBGPP_CLKN_L

PCIE_NEW_CLKP

PCIE_NEW_CLKN

PCIE_MINI1_CLKP

PCIE_MINI1_CLKN

SBSRC_CLKP SBSRC_CLKP

SBSRC_CLKN SBSRC_CLKN

PCIE_LAN_CLKN

CLK_VGA_27M_NSS

NBHTREFCLK0P

NBHTREFCLK0N

CLK_48M_CR_L

CLK48MUSB

SEL_HT66SEL_HT66SEL_HT66SEL_HT66

SEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATA

SEL_27

CLKREQ0#

EXT_NWD_CLK_REQ#

CLKREQ2#

CLKREQ3#

CLKREQ4#

RX780 RS780CLOCKS name

RP64 STUFF

RP66 STUFF to M82-S external reference clock -RX780 only

RP70 STUFF RP70 NC

RP72 STUFF RP72 STUFF

R653,R656,R612

STUFF

Place within 0.5"

of CLKGEN

RP43 *0_4P2R_4

4

2

RP54 *0_4P2R_4

4

2

RP53 *0_4P2R_4

4

2

T196

T84

RP48 *0_4P2R_4

4

2

RP55 *0_4P2R_4

4

2

RP51 *0_4P2R_4

4

2

RP49 *0_4P2R_4

4

2

RP47 *0_4P2R_4

4

2

RP45 *0_4P2R_4

4

2

RP44 *0_4P2R_4

4

2

R527 33_4

R215 75/F_4

R490 100/F_4

R193 0_4

R194 0_4

R201 33_4

R192 33_4

RP64 STUFF

to NB for VGA reference clock

RP66 NC

to NB for RX780 for PCIEX2 interface reference clock only

RS780 is internal share with AC-LINK clock,RS780 not need

to NB for AC-LINK reference clock

R653,R656,R612

NC

3

1

3

1

3

1

3

1

3

1

T59

T62

3

1

3

1

3

1

3

1

3

1

EXT_NWD_CLK_REQ# 33

Clock chip has internal serial

terminations

for differencial pairs, external resistors

are

reserved for debug purpose.

+3V_CLKVDD

R189

*8.2K_4

R203

8.2K_4

To M82-S 27Mhz - RX780 only

R196 *261_4

CPUCLKP

CPUCLKN

NBGFX_CLKP

NBGFX_CLKN

EXT_GFX_CLKPEXT_GFX_CLKP

PCIE_MINI2_CLKPPCIE_MINI2_CLKP

PCIE_MINI2_CLKNPCIE_MINI2_CLKN

CLK_PCIE_CARD

Del RP52 for NBGPP CLK

PCIE_NEW_CLKP

PCIE_NEW_CLKN

PCIE_MINI1_CLKP

PCIE_MINI1_CLKN

SBLINK_CLKPSBLINK_CLKP

SBLINK_CLKNSBLINK_CLKN

PCIE_LAN_CLKPPCIE_LAN_CLKP

PCIE_LAN_CLKN

OSC_SPREADCLK_VGA_27M_SS

NBHT_REFCLKP

NBHT_REFCLKN

CLK_48M_CR

CLK_48M_USB

R195

8.2K_4

R202

*8.2K_4

RS780M/RX780M

2

Clock pin function

Del RP for TP on PV

CPUCLKP 3

CPUCLKN 3

NBGFX_CLKP 10

NBGFX_CLKN 10

EXT_GFX_CLKP 17

EXT_GFX_CLKN 17

PCIE_MINI2_CLKP 36

PCIE_MINI2_CLKN 36

CLK_PCIE_CARD 26

CLK_PCIE_CARD# 26

PCIE_NEW_CLKP 33

PCIE_NEW_CLKN 33

PCIE_MINI1_CLKP 36

PCIE_MINI1_CLKN 36

SBLINK_CLKP 10

SBLINK_CLKN 10

SBSRC_CLKP 12

SBSRC_CLKN 12

PCIE_LAN_CLKP 31

PCIE_LAN_CLKN 31

OSC_SPREAD 18

EVGA-XTALI 18

NBHT_REFCLKP 10

NBHT_REFCLKN 10

CLK_48M_CR 25

CLK_48M_USB 13

T58

T167

SEL_27

SEL_SATA

SEL_HT66

to NB for external Graphics

reference clock

to M82-S -RX780 only

to TV TUNER CARD

to PCIE-CARD READER

to EPRESS CARD

to WLAN

to NB for AC-LINK reference clock

to SB

to PCIE-LAN

SI-1 Modified --remove

SSIN - for M82 - 3.3V level input

X_TALIN --for M82 -1.8V level input

Ra

R186 158/F_4

R184 90.9/F_4

1 2

Rb

1.8V

82.5RRa

130R

Rb

RES CHIP 130 1/16W +-1%(0402)L-F -->CS11302FB15

RES CHIP 158 1/16W +-1%(0402) -->CS11582FB00

RES CHIP 90.9 1/16W +-1%(0402) -->CS09092FB15

RES CHIP 82.5 1/16W +-1%(0402) -->CS08252FB11

EXT_NWD_CLK_REQ#

CLK_PD#

SB_SRC_SLOW#

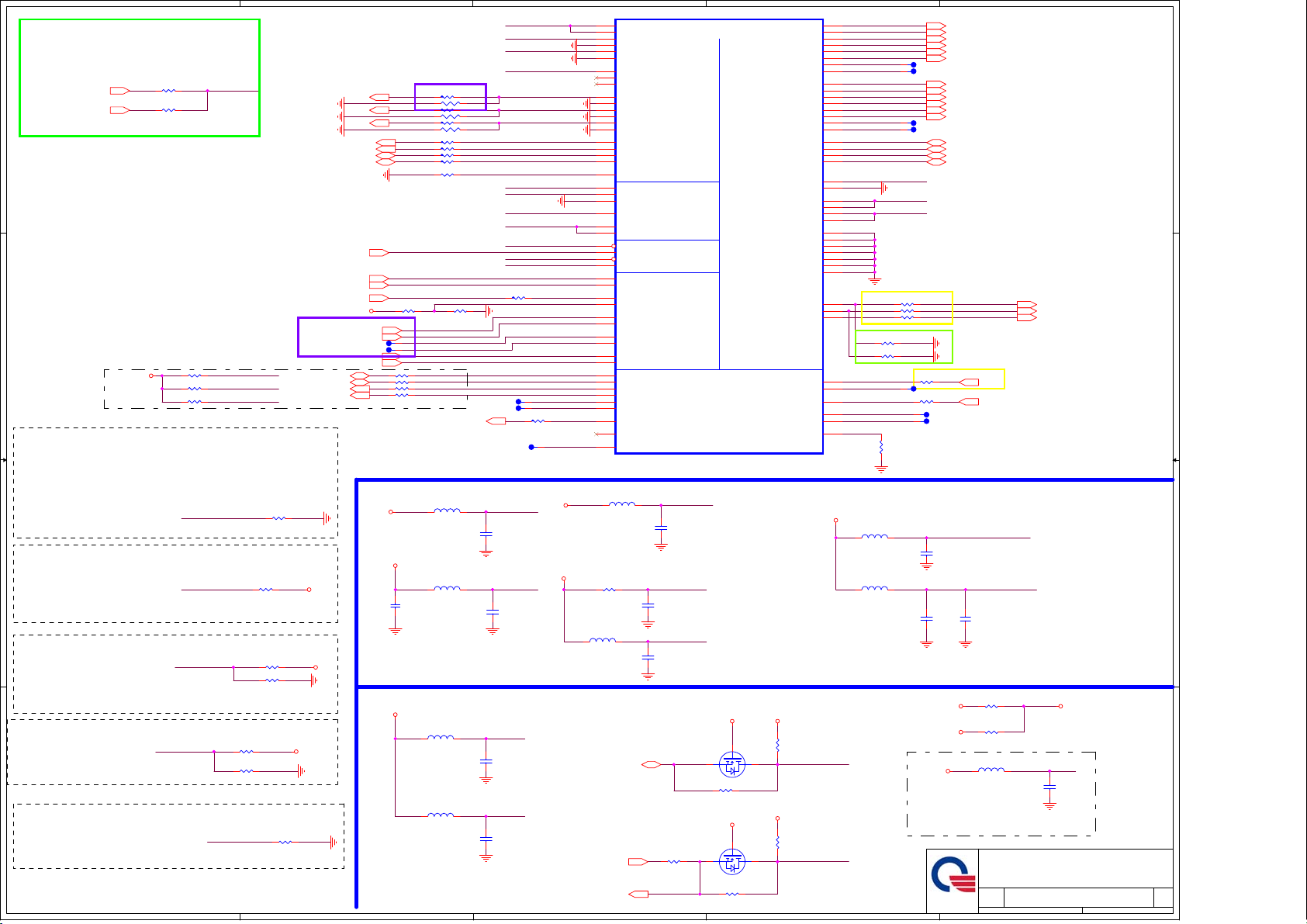

PROJECT : QT8

Quanta Computer Inc.

Size Document Number Rev

Custom

NB5/RD5

Clock Generator

Date: Sheet

to ROBSON

RS780RX780

1.1V

158R

90.9R

1

02

EXT_NB_OSC 10

R2198.2K_4

R2048.2K_4

R2618.2K_4

of

245Tuesday, February 19, 2008

+3V

1A

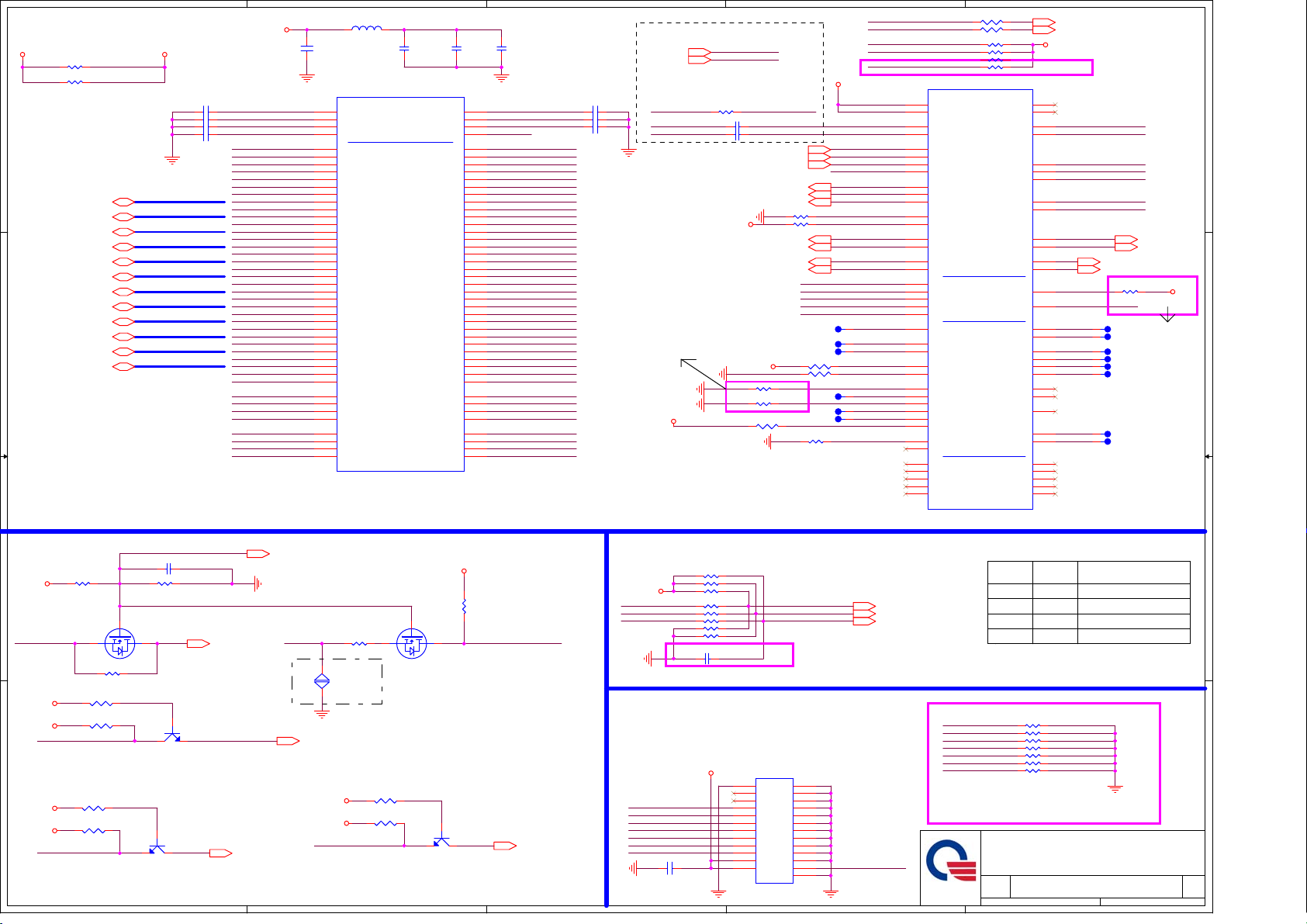

Page 3

5

+1.2V +1.2V_VLDT

R474 0_8

R473 0_8

D D

HT_NB_CPU_CAD_H[15..0]8

HT_NB_CPU_CAD_L[15..0]8

HT_NB_CPU_CLK_H[1..0]8

HT_NB_CPU_CLK_L[1..0]8

HT_NB_CPU_CTL_H[1..0]8

HT_NB_CPU_CTL_L[1..0]8

HT_CPU_NB_CAD_H[15..0]8

HT_CPU_NB_CAD_L[15..0]8

HT_CPU_NB_CLK_H[1..0]8

HT_CPU_NB_CLK_L[1..0]8

C C

HT_CPU_NB_CTL_H[1..0]8

HT_CPU_NB_CTL_L[1..0]8

FOX PZ63826-284R-41F

DG0^8000004 IC SOCKET SMD 638P S1(P1.27,H3.2)

MLX 47296-4131

DG0^8000003 IC SOCKET SMD 638P S1(P1.27,H3.2)

TYC 4-1903401-2

DG0^8000005 IC SOCKET SMD 638P S1(P1.27,H3.2)

+1.2V_VLDT

HT_NB_CPU_CAD_H[15..0]

HT_NB_CPU_CAD_L[15..0]

HT_NB_CPU_CLK_H[1..0]

HT_NB_CPU_CLK_L[1..0]

HT_NB_CPU_CTL_H[1..0]

HT_NB_CPU_CTL_L[1..0]

HT_CPU_NB_CAD_H[15..0]

HT_CPU_NB_CAD_L[15..0]

HT_CPU_NB_CLK_H[1..0]

HT_CPU_NB_CLK_L[1..0]

HT_CPU_NB_CTL_H[1..0]

HT_CPU_NB_CTL_L[1..0]

C739 4.7U/6.3V_6

C744 4.7U/6.3V_6

C758 0.22U/6.3V_4

C753 180P/50V_4

HT_NB_CPU_CAD_H0

HT_NB_CPU_CAD_L0

HT_NB_CPU_CAD_H1

HT_NB_CPU_CAD_L1

HT_NB_CPU_CAD_H2

HT_NB_CPU_CAD_L2

HT_NB_CPU_CAD_H3

HT_NB_CPU_CAD_L3

HT_NB_CPU_CAD_H4

HT_NB_CPU_CAD_L4

HT_NB_CPU_CAD_H5

HT_NB_CPU_CAD_L5

HT_NB_CPU_CAD_H6

HT_NB_CPU_CAD_L6

HT_NB_CPU_CAD_H7

HT_NB_CPU_CAD_L7

HT_NB_CPU_CAD_H8

HT_NB_CPU_CAD_L8

HT_NB_CPU_CAD_H9

HT_NB_CPU_CAD_L9

HT_NB_CPU_CAD_H10

HT_NB_CPU_CAD_L10

HT_NB_CPU_CAD_H11

HT_NB_CPU_CAD_L11

HT_NB_CPU_CAD_H12

HT_NB_CPU_CAD_L12

HT_NB_CPU_CAD_H13

HT_NB_CPU_CAD_L13

HT_NB_CPU_CAD_H14

HT_NB_CPU_CAD_L14

HT_NB_CPU_CAD_H15

HT_NB_CPU_CAD_L15

HT_NB_CPU_CLK_H0

HT_NB_CPU_CLK_L0

HT_NB_CPU_CLK_H1

HT_NB_CPU_CLK_L1

HT_NB_CPU_CTL_H0

HT_NB_CPU_CTL_L0

HT_NB_CPU_CTL_H1

HT_NB_CPU_CTL_L1

BLM21PG221SN1D(220,100M,2A)_8

+2.5V

C416

10U/6.3V_8

+1.2V_VLDT

+1.2V_VLDT

+1.2V_VLDT

+1.2V_VLDT

L36

LS0805-100M-N

U31A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

SOCKET_638_PIN

4

HT LINK

+CPUVDDA

C392

4.7U/6.3V_6

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

3

W/S= 15 mil/20mil

C368

0.22U/6.3V_4

C363

3300P/50V_4

+1.2V_VLDT

AE2

+1.2V_VLDT

AE3

+1.2V_VLDT CPU_SVC_R

AE4

+1.2V_VLDT

AE5

HT_CPU_NB_CAD_H0

AD1

HT_CPU_NB_CAD_L0

AC1

HT_CPU_NB_CAD_H1

AC2

HT_CPU_NB_CAD_L1

AC3

HT_CPU_NB_CAD_H2

AB1

HT_CPU_NB_CAD_L2

AA1

HT_CPU_NB_CAD_H3

AA2

HT_CPU_NB_CAD_L3

AA3

HT_CPU_NB_CAD_H4

W2

HT_CPU_NB_CAD_L4

W3

HT_CPU_NB_CAD_H5

V1

HT_CPU_NB_CAD_L5

U1

HT_CPU_NB_CAD_H6

U2

HT_CPU_NB_CAD_L6

U3

HT_CPU_NB_CAD_H7

T1

HT_CPU_NB_CAD_L7

R1

HT_CPU_NB_CAD_H8

AD4

HT_CPU_NB_CAD_L8

AD3

HT_CPU_NB_CAD_H9

AD5

HT_CPU_NB_CAD_L9

AC5

HT_CPU_NB_CAD_H10

AB4

HT_CPU_NB_CAD_L10

AB3

HT_CPU_NB_CAD_H11

AB5

HT_CPU_NB_CAD_L11

AA5

HT_CPU_NB_CAD_H12

Y5

HT_CPU_NB_CAD_L12

W5

HT_CPU_NB_CAD_H13

V4

HT_CPU_NB_CAD_L13

V3

HT_CPU_NB_CAD_H14

V5

HT_CPU_NB_CAD_L14

U5

HT_CPU_NB_CAD_H15

T4

HT_CPU_NB_CAD_L15

T3

HT_CPU_NB_CLK_H0

Y1

HT_CPU_NB_CLK_L0

W1

HT_CPU_NB_CLK_H1

Y4

HT_CPU_NB_CLK_L1

Y3

HT_CPU_NB_CTL_H0

R2

HT_CPU_NB_CTL_L0

R3

HT_CPU_NB_CTL_H1

T5

HT_CPU_NB_CTL_L1

R5

CPU CLK

CPUCLKP2

CPUCLKN2

Keep trace from resisor to CPU within 0.6"

keep trace from caps to CPU within 1.2"

C8404.7U/6.3V_6

C8180.22U/6.3V_4

C829180P/50V_4

SI-2 modified for AMD

sighting update

CPUCLKIN

CPUCLKP

CPUCLKN

SideBand Temp sense I2C

+1.8VSUS

CPUCLKP

CPUCLKN

R137 169/F_4

C408 3900P/25V_4

C409 3900P/25V_4

CPU_LDT_RST#10,12

CPU_LDT_STOP#10,12

+1.2V_VLDT

CPU_VDD0_RUN_FB_H40

CPU_VDD0_RUN_FB_L40

CPU_VDD1_RUN_FB_H40

CPU_VDD1_RUN_FB_L40

+1.8VSUS

R776 300/F_4

R777 300/F_4

R455 300_4

CPUCLKIN#

CPU_PWRGD12

CPU_SIC5

CPU_SID5

CPU_ALERT5

R128 44.2/F_4

R135 44.2/F_4

R141 510/F_4

R108 510/F_4

R535 0_4

2

+CPUVDDA

W/S= 15 mil/20mil

+CPUVDDA

+CPUVDDA

CPUCLKIN

CPUCLKIN#

CPU_LDT_RST#

CPU_PWRGD

CPU_LDT_STOP#

CPU_LDT_REQ#_CPU

CPU_SIC

CPU_SID

CPU_ALERT

CPU_HTREF0

CPU_HTREF1

place them to CPU within 1.5"

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

T7

T42

T45

T116

T118

T9

CPUTEST23

CPUTEST18

CPUTEST19

CPUTEST25H

CPUTEST25L

CPUTEST21

CPUTEST20

CPUTEST24

CPUTEST22

CPUTEST12

CPUTEST27

CPU_THERMDC

CPU_THERMDA

CPU_LDT_RST#

CPU_LDT_STOP#

CPU_PWRGD

CPU_LDT_REQ#_CPU

F8

F9

A9

A8

B7

A7

F10

C6

AF4

AF5

AE6

R6

P6

F6

E6

Y6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

G9

E9

E8

AB8

AF7

AE7

AE8

AC8

AF8

C2

AA6

A3

A5

B3

B5

C1

R569 0_4

R567 0_4

U31D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SIC

SID

ALERT_L

HT_REF0

HT_REF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

SOCKET_638_PIN

R142300_4

R140300_4

R144300_4

R563300_4

KEY1

KEY2

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

SVC

SVD

TDO

H_THRMDC 5

H_THRMDA 5

+1.8V

M11

W18

A6

CPU_SVD_R

A4

CPU_THERMTRIP_L#

AF6

CPU_PROCHOT_L#

AC7

CPU_MEMHOT_L#

AA8

CPU_THERMDC

W7

CPU_THERMDA

W8

VDDIO_FB_H

W9

VDDIO_FB_L

Y9

H6

G6

CPU_DBREQ#

E10

CPU_TDO

AE9

CPUTEST28H

J7

CPUTEST28L

H8

CPUTEST17

D7

CPUTEST16

E7

CPUTEST15

F7

CPUTEST14

C7

C3

K8

C4

CPUTEST29H

C9

CPUTEST29L

C8

H18

H19

AA7

D5

C5

1

03

SI-2 modified -confirm AMD R563

need to stuff

VDDIO_FB_H 41

VDDIO_FB_L 41

CPU_VDDNB_RUN_FB_H 40

CPU_VDDNB_RUN_FB_L 40

R775 300/F_4

SI-2

T40

modified for

T43

AMD sighting

T48

update

T46

T44

T49

T47

T50

+1.8VSUS

CNTR_VREF

B B

A A

R571 20K/F_4

+3V

Q39 *BSS138_NL/SOT23

1

R570 0_4

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

R59 10K/F_4

R62 300_4

CPU_MEMHOT_L# CPU_MEMHOT#

R453 10K/F_4

R452 300_4

CPU_PROCHOT_L#

C854 0.1U/10V_4

R574 34.8K/F_4

CNTR_VREF

2

3

2

2

Q35

1 3

MMBT3904

5

CPU_LDT_REQ# 10

Q11

MMBT3904

13

CNTR_VREF 5

CPU_LDT_RST#

CPU_PROCHOT# 12

R143

0_4

12

G1

*SHORT_ PAD1

for debug only

CPU_MEMHOT# 7,13

+1.8VSUS

+1.8VSUS

CPU_THERMTRIP_L#

2

1

R60 10K/F_4

R454 300_4

4

+3V

3

Q40

BSS138_NL/SOT23

2

Q10

MMBT3904

1 3

R577

1K/F_4

CPU_LDT_RST_HTPA#CPU_LDT_REQ#_CPU

CPU_THERMTRIP# 13

Serial VID

R145 *2.2K_4

R561 1K/F_4

+1.8VSUS

CPU_SVC_R

CPU_SVD_R CPU_SVD

CPU_PWRGD

R562 1K/F_4

R554 0_4

R553 0_4

R147 0_4

R560 *220_4

R559 *220_4

C926 *0.1U/10V_4

SI-2 remove for power up seq

HDT Connector

+1.8VSUS

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

C54 *0.1U/10V_4

3

CPU_SVC

CPU_PWRGD_SVID_REG

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

KEY

CN6 *HDT CONN

25

CPU_SVC 40

CPU_SVD 40

CPU_PWRGD_SVID_REG 40

CPU_LDT_RST_HTPA#

2

NB5/RD5

VFIX MODE

VID Override Circuit

SVC SVD Voltage Output

00

0

1

0

1

11

CPUTEST20

CPUTEST22

CPUTEST12

CPUTEST15

CPUTEST14

CPUTEST19

CPUTEST18

SI-2 reserve for AMD recommend

R798 *300/F_4

R799 *300/F_4

R800 *300/F_4

R801 *300/F_4

R802 *300/F_4

R803 *300/F_4

R804 *300/F_4

PROJECT : QT8

Quanta Computer Inc.

Size Document Number Rev

Custom

S1G2 HT,CTL I/F 1/3

Date: Sheet

1

1.4V

1.2V

1.0V

0.8V

345Tuesday, February 19, 2008

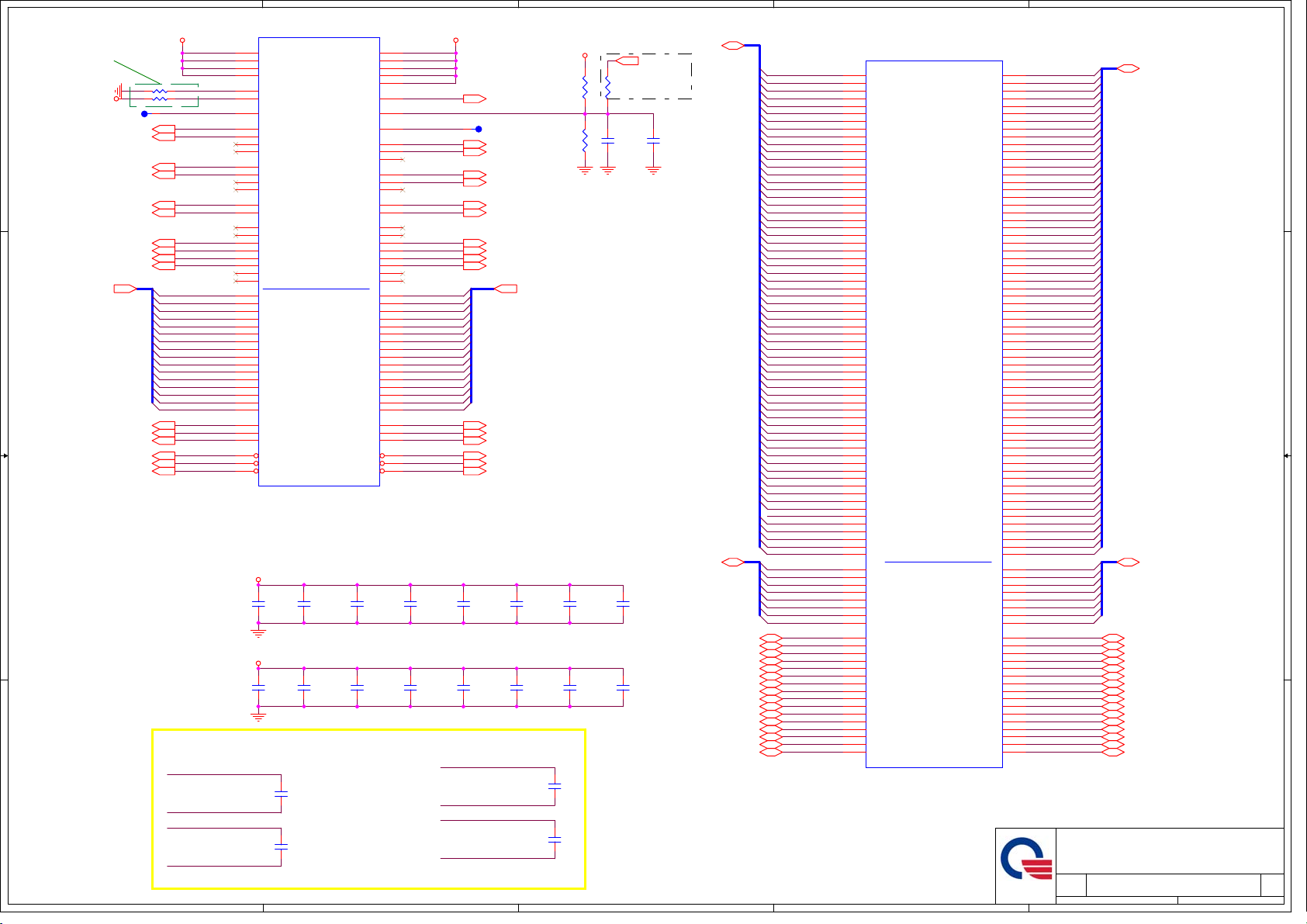

1A

of

Page 4

A

B

C

D

E

+0.9VSMVTT +0.9VSMVTT

PLACE THEM CLOSE TO

CPU WITHIN 1"

R459 39.2/F_4

MEM_MA0_ODT06,7

MEM_MA0_ODT16,7

MEM_MA0_CS#06,7

MEM_MA0_CS#16,7

MEM_MA_CLK1_P6

MEM_MA_CLK1_N6

MEM_MA_CLK7_P6

MEM_MA_CLK7_N6

MEM_MA_BANK06,7

MEM_MA_BANK16,7

MEM_MA_BANK26,7

MEM_MA_RAS#6,7

MEM_MA_CAS#6,7

MEM_MA_WE#6,7

MEM_MA_CKE06,7

MEM_MA_CKE16,7

R458 39.2/F_4

T41

A

+1.8VSUS

4 4

MEM_MA_ADD[0..15]6,7

3 3

2 2

1 1

M_ZP

M_ZN

MEM_MA_RESET#

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MB_CLK7_P

MEM_MB_CLK7_N

MEM_MB_CLK1_P

MEM_MB_CLK1_N

U31B

D10

VTT1

C10

VTT2

B10

VTT3

AD10

VTT4

AF10

MEMZP

AE10

MEMZN

H16

RSVD_M1

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L0

U19

MA0_CS_L1

U20

MA1_CS_L0

V20

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H5

N20

MA_CLK_L5

E16

MA_CLK_H1

F16

MA_CLK_L1

Y16

MA_CLK_H7

AA16

MA_CLK_L7

P19

MA_CLK_H4

P20

MA_CLK_L4

N21

MA_ADD0

M20

MA_ADD1

N22

MA_ADD2

M19

MA_ADD3

M22

MA_ADD4

L20

MA_ADD5

M24

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_L

SOCKET_638_PIN

+0.9VSMVTT

4.7U/6.3V_6

+0.9VSMVTT

1000P/50V_4

C736

1.5P/50V_4

C366

1.5P/50V_4

MEM:CMD/CTRL/CLK

VTT5

VTT6

VTT7

VTT8

VTT9

VTT_SENSE

MEMVREF

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

Place close to socket

C399

C112

4.7U/6.3V_6

C401

1000P/50V_4

Close to CPU within 1500 mils

C202

4.7U/6.3V_6

1000P/50V_4

C99

C400

W10

AC10

AB10

AA10

A10

CPU_VTT_SENSE

Y10

MEMVREF_CPU

W17

MEM_MB_RESET#

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

MEM_MB_ADD0

P24

MEM_MB_ADD1

N24

MEM_MB_ADD2

P26

MEM_MB_ADD3

N23

MEM_MB_ADD4

N26

MEM_MB_ADD5

L23

MEM_MB_ADD6

N25

MEM_MB_ADD7

L24

MEM_MB_ADD8

M26

MEM_MB_ADD9

K26

MEM_MB_ADD10

T26

MEM_MB_ADD11

L26

MEM_MB_ADD12

L25

MEM_MB_ADD13

W24

MEM_MB_ADD14

J23

MEM_MB_ADD15

J24

R24

U26

J26

U25

U24

U23

4.7U/6.3V_6

1000P/50V_4

B

C398

C185

750 mA

CPU_VTT_SENSE 41

T51

MEM_MB0_ODT0 6,7

MEM_MB0_ODT1 6,7

MEM_MB0_CS#0 6,7

MEM_MB0_CS#1 6,7

MEM_MB_CKE0 6,7

MEM_MB_CKE1 6,7

MEM_MB_CLK1_P 6

MEM_MB_CLK1_N 6

MEM_MB_CLK7_P 6

MEM_MB_CLK7_N 6

MEM_MB_BANK0 6,7

MEM_MB_BANK1 6,7

MEM_MB_BANK2 6,7

MEM_MB_RAS# 6,7

MEM_MB_CAS# 6,7

MEM_MB_WE# 6,7

C213

0.22U/6.3V_4

C183

180P/50V_4

MEM_MA_CLK7_P

MEM_MA_CLK7_N

MEM_MA_CLK1_P

MEM_MA_CLK1_N

R81

2K/F_4

R77

2K/F_4

MEM_MB_ADD[0..15] 6,7

C369

0.22U/6.3V_4

C189

180P/50V_4

C734

1.5P/50V_4

C367

1.5P/50V_4

+1.8VSUS

C364

0.22U/6.3V_4

C390

180P/50V_4

R82

*0_4

C197

0.1U/10V_4

0.22U/6.3V_4

180P/50V_4

MEM_MB_DATA[0..63]6

+0.9VSMVREF 6,41

Reserved

C177

1000P/50V_4

MEM_MB_DM[0..7]6

C201

C396

C

Processor Memory Interface

U31C

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DQS0_P6

MEM_MB_DQS0_N6

MEM_MB_DQS1_P6

MEM_MB_DQS1_N6

MEM_MB_DQS2_P6

MEM_MB_DQS2_N6

MEM_MB_DQS3_P6

MEM_MB_DQS3_N6

MEM_MB_DQS4_P6

MEM_MB_DQS4_N6

MEM_MB_DQS5_P6

MEM_MB_DQS5_N6

MEM_MB_DQS6_P6

MEM_MB_DQS6_N6

MEM_MB_DQS7_P6

MEM_MB_DQS7_N6

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

Y11

AE14

AF14

AF11

AD11

A12

B16

A22

E25

AB26

AE22

AC16

AD12

C12

B12

D16

C16

A24

A23

F26

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

SOCKET_638_PIN

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DATA[0..63] 6

MEM_MA_DM[0..7] 6

MEM_MA_DQS0_P 6

MEM_MA_DQS0_N 6

MEM_MA_DQS1_P 6

MEM_MA_DQS1_N 6

MEM_MA_DQS2_P 6

MEM_MA_DQS2_N 6

MEM_MA_DQS3_P 6

MEM_MA_DQS3_N 6

MEM_MA_DQS4_P 6

MEM_MA_DQS4_N 6

MEM_MA_DQS5_P 6

MEM_MA_DQS5_N 6

MEM_MA_DQS6_P 6

MEM_MA_DQS6_N 6

MEM_MA_DQS7_P 6

MEM_MA_DQS7_N 6

04

PROJECT : QT8

Quanta Computer Inc.

Size Document Number Rev

Custom

D

NB5/RD5

S1G2 DDRII MEMORY I/F 2/3

Date: Sheet

E

445Tuesday, February 19, 2008

1A

of

Page 5

5

4

3

2

1

U31F

AA4

VSS1

AA11

U31E

G4

VDD0_1

H2

VDD0_2

J9

VDD0_3

J11

VDD0_4

J13

VDD0_5

3

R149

10K/F_4

J15

VDD0_6

K6

VDD0_7

K10

VDD0_8

K12

VDD0_9

K14

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

L11

VDD0_14

L13

VDD0_15

L15

VDD0_16

M2

VDD0_17

M6

VDD0_18

M8

VDD0_19

M10

VDD0_20

N7

VDD0_21

N9

VDD0_22

N11

VDD0_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17

VDDIO12

SOCKET_638_PIN

2

Q14

1

3

*BSS138_NL/SOT23

R151

10K/F_4

D D

+CPUVDDNB

3A

+1.8VSUS

2A

C C

CNTR_VREF3

MBCLK218,35

MBDATA218,35

B B

Del R150, R152

on PV

PM_THERM#13

A A

MBCLK2

*BSS138_NL/SOT23

MBDATA2

*BSS138_NL/SOT23

SMBALERT#

MBCLK218,35

MBDATA218,35

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

2

Q15

1

2

3

10K/F_4

SI-2 Modified for H/W thermal shutdown

+1.8VSUS

+1.8VSUS

CPU_THERMTRIP_L#

5

R805 *10K/F_4

R806 *300_4

CPU_THERMTRIP_L# SMBALERT#

+VCORE1+VCORE0 +VCORE0

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

Q13

8

7

6

4

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

CPU_SIC

CPU_SID

CPU_ALERT

1

U36

SCLK

SDA

ALERT#

OVERT#

G781P8

2

1 3

MSOP

Q71

*MMBT3904

R164

390_4

VCC

DXP

DXN

GND

+1.8VSUS

R572

200/F_6

1

2

3

5

+1.8VSUS

R166

390_4

+3V+3V

Update U36 P/N

on PV

SMBALERT#

4

C856

0.1U/10V_4

C855

2200P/50V_4

R167

1K/F_4

CPU_SIC 3

CPU_SID 3

CPU_ALERT 3

H_THRMDA 3

H_THRMDC 3

PQ60

*2N7002E-G

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

SOCKET_638_PIN

PROCESSOR POWER AND GROUND

R170 *0_4

reserve for

power shutdown

( if can )

R168 0_4

Q16

MMBT3904

2

1 3

3

1

R760 *10K/F_4

2

ADD VGA TEMP_ FAIL function

M8X is active Hi , M7X acvite Low

J6

VSS66

J8

VSS67

J10

VSS68

J12

VSS69

J14

VSS70

J16

VSS71

J18

VSS72

K2

VSS73

K7

VSS74

K9

VSS75

K11

VSS76

K13

VSS77

K15

VSS78

K17

VSS79

L6

VSS80

L8

VSS81

L10

VSS82

L12

VSS83

L14

VSS84

L16

VSS85

L18

VSS86

M7

VSS87

M9

VSS88

AC6

VSS89

M17

VSS90

N4

VSS91

N8

VSS92

N10

VSS93

N16

VSS94

N18

VSS95

P2

VSS96

P7

VSS97

P9

VSS98

P11

VSS99

P17

VSS100

R8

VSS101

R10

VSS102

R16

VSS103

R18

VSS104

T7

VSS105

T9

VSS106

T11

VSS107

T13

VSS108

T15

VSS109

T17

VSS110

U4

VSS111

U6

VSS112

U8

VSS113

U10

VSS114

U12

VSS115

U14

VSS116

U16

VSS117

U18

VSS118

V2

VSS119

V7

VSS120

V9

VSS121

V11

VSS122

V13

VSS123

V15

VSS124

V17

VSS125

W6

VSS126

Y21

VSS127

Y23

VSS128

N6

VSS129

SYS_SHDN#

SYS_SHDN#

D34

*CH500H

2 1

D33

2 1

CH501H-40PT

R172 10K/F_4

3

3920_RST#

ECPWROK

TEMP_FAIL 18

BOTTOM SIDE DECOUPLING

C267

22U/6.3V_8

C285

0.22U/6.3V_4

C206

0.22U/6.3V_4

C284

22U/6.3V_8

C286

0.01U/16V_4

C226

0.01U/16V_4

C309

0.22U/6.3V_4

C301

180P/50V_4

C205

180P/50V_4

C247

0.22U/6.3V_4

C287

22U/6.3V_8

+VCORE1

+CPUVDDNB

C230

22U/6.3V_8

C264

22U/6.3V_8

C308

22U/6.3V_8

C272

22U/6.3V_8

C231

22U/6.3V_8

C307

22U/6.3V_8

C273

22U/6.3V_8

C279

22U/6.3V_8

22U/6.3V_8

+1.8VSUS

C306

C248

22U/6.3V_8

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.8VSUS

+1.8VSUS

SYS_SHDN# 38,44

3920_RST# 35,44

ECPWROK 16,35

+3V

*0.1U/10V_4

C750

4.7U/6.3V_6

C238

0.22U/6.3V_4

EC13

0.22U/6.3V_4

*0.1U/10V_4

C802

4.7U/6.3V_6

C751

EC14

C236

4.7U/6.3V_6

C752

0.01U/16V_4

+1.8VSUS +3VPCU

+1.8V

+3VPCU

+5V

+VGA_CORE +1.8V

+3V +1.8V+3VS5 +3VS5

EC11

*0.1U/10V_4

2

C120

0.01U/16V_4

EC12

*0.1U/10V_4

C749

4.7U/6.3V_6

0.22U/6.3V_4

C118

180P/50V_4

EC10 0.01U/16V_4

EC5 0.01U/16V_4R148

EC4 0.01U/16V_4

EC7 0.01U/16V_4

EC1 *0.01U/16V_4

EC2 *0.01U/16V_4

EC8 0.01U/16V_4

EC9 0.01U/16V_4

NB5/RD5

C803

Size Document Number Rev

Custom

Date: Sheet

C240

0.22U/6.3V_4

+3VPCU+1.8V

+3V

+3V

+1.8VSUS +5V

+3V

For fix HyperTransport nets

across plane splits

PROJECT : QT8

Quanta Computer Inc.

S1G2 PWR & GND 3/3

C225

0.01U/16V_4

C214

180P/50V_4

+VCORE0 +VCORE1

EC3 0.01U/16V_4

EC6 0.01U/16V_4

1

05

C315

180P/50V_4

C69 0.01U/16V_4

C71 0.01U/16V_4

C67 0.01U/16V_4

C64 0.01U/16V_4

545Tuesday, February 19, 2008

+3VPCU+5V

1A

of

Page 6

5

+1.8VSUS +1.8VSUS

103

111

104

112

MEM_MA_ADD[0..15]4,7

D D

MEM_MA_BANK[0..2]4,7

MEM_MA_DQS0_P4

MEM_MA_DQS1_P4

MEM_MA_DQS2_P4

MEM_MA_DQS3_P4

MEM_MA_DQS4_P4

MEM_MA_DQS5_P4

MEM_MA_DQS6_P4

MEM_MA_CLK1_P4

MEM_MA_CLK1_N4

MEM_MA_CLK7_P4

MEM_MA_CLK7_N4

MEM_MA_CKE04,7

MEM_MA_CKE14,7

MEM_MA_RAS#4,7

MEM_MA_CAS#4,7

MEM_MA_WE#4,7

MEM_MA0_CS#04,7

MEM_MA0_CS#14,7

MEM_MA0_ODT04,7

MEM_MA0_ODT14,7

PDAT_SMB2,7,13,28,36

PCLK_SMB2,7,13,28,36

MEM_MA_DQS7_P4

MEM_MA_DQS0_N4

MEM_MA_DQS1_N4

MEM_MA_DQS2_N4

MEM_MA_DQS3_N4

MEM_MA_DQS4_N4

MEM_MA_DQS5_N4

MEM_MA_DQS6_N4

MEM_MA_DQS7_N4

+3V

C370

2.2U/6.3V_6

C C

B B

A A

C391

0.1U/10V_4

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

DIM1_SA0

DIM1_SA1

PDAT_SMB

PCLK_SMB

C701

0.1U/10V_4

C849

1000P/50V_4

102

A0

101

A1

100

105

116

107

106

130

147

170

185

131

148

169

188

129

146

167

186

164

166

108

113

109

110

115

114

119

198

200

195

197

199

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

A10

90

A11

89

A12

A13

86

A14

84

A15

BA0

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

DM4

DM5

DM6

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

DQS4

DQS5

DQS6

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

DQS4

DQS5

DQS6

DQS7

30

CK0

32

CK0

CK1

CK1

79

CKE0

80

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

GND

GND

59

201

202

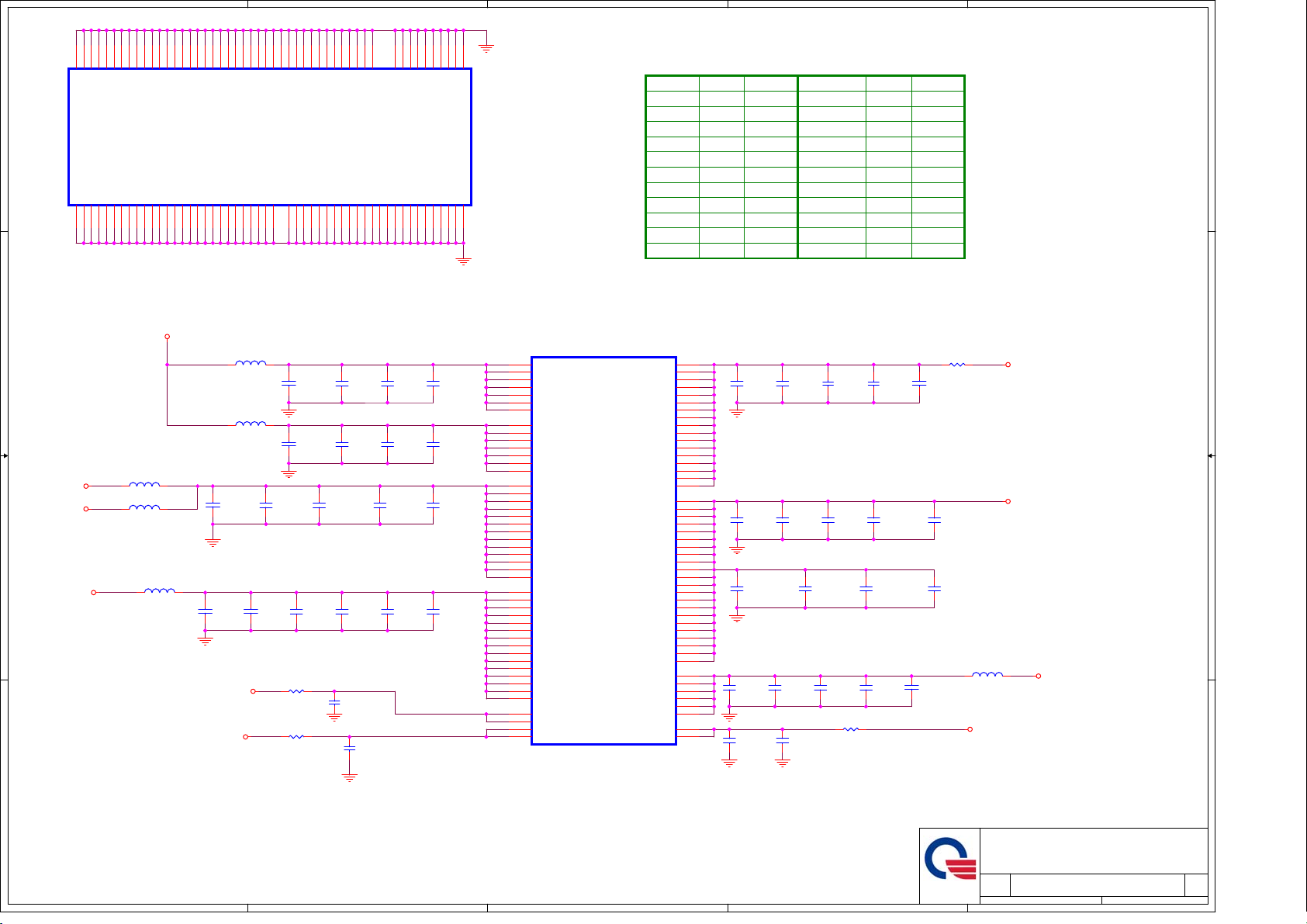

DDR SO-DIMM SOCKET 1.8V

H=5.2

R40 10K/F_4

R43 10K/F_4

SO-DIMM

117

VDD8

VDD7

VDD9

VDD10

(Normal)

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

127

122

121

SMbus address A0

5

118

VDD11

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

132

128

DIM1_SA0

DIM1_SA1

CN30

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

NC1

NC2

NC3

NC4

4

MEM_MA_DATA0

5

MEM_MA_DATA1

7

MEM_MA_DATA2

17

MEM_MA_DATA3

19

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA6

14

MEM_MA_DATA7

16

MEM_MA_DATA8

23

MEM_MA_DATA9

25

MEM_MA_DATA10

35

MEM_MA_DATA11

37

MEM_MA_DATA12

20

MEM_MA_DATA13

22

MEM_MA_DATA14

36

MEM_MA_DATA15

38

MEM_MA_DATA16

43

MEM_MA_DATA17

45

MEM_MA_DATA18

55

MEM_MA_DATA19

57

MEM_MA_DATA20

44

MEM_MA_DATA21

46

MEM_MA_DATA22

56

MEM_MA_DATA23

58

MEM_MA_DATA24

61

MEM_MA_DATA25

63

MEM_MA_DATA26

73

MEM_MA_DATA27

75

MEM_MA_DATA28

62

MEM_MA_DATA29

64

MEM_MA_DATA30

74

MEM_MA_DATA31

76

MEM_MA_DATA36

123

MEM_MA_DATA37

125

MEM_MA_DATA35

135

MEM_MA_DATA39

137

MEM_MA_DATA38

124

MEM_MA_DATA32

126

MEM_MA_DATA33

134

MEM_MA_DATA34

136

MEM_MA_DATA40

141

MEM_MA_DATA41

143

MEM_MA_DATA46

151

MEM_MA_DATA47

153

MEM_MA_DATA44

140

MEM_MA_DATA45

142

MEM_MA_DATA42

152

MEM_MA_DATA43

154

MEM_MA_DATA52

157

MEM_MA_DATA49

159

MEM_MA_DATA54

173

MEM_MA_DATA55

175

MEM_MA_DATA53

158

MEM_MA_DATA48

160

MEM_MA_DATA51

174

MEM_MA_DATA50

176

MEM_MA_DATA61

179

MEM_MA_DATA60

181

MEM_MA_DATA63

189

MEM_MA_DATA62

191

MEM_MA_DATA56

180

MEM_MA_DATA57

182

MEM_MA_DATA58

192

MEM_MA_DATA59

194

MEMHOT_SODIMM#_1

50

MEM_MA_RESET#1

69

83

120

MEM_MA_NC5

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

4

3

MEM_MA_DATA[0..63] 4

R106 0_4

T155

T115

+0.9VSMVREF_DIMM+0.9VSMVREF_DIMM

+0.9VSMVREF_DIMM

+0.9VSMVREF4,41

R139 *0_4

Only for reserved

MEM_MB_ADD[0..15]4,7 MEM_MB_DATA[0..63] 4

MEM_MB_BANK[0..2]4,7

MEM_MB_DM[0..7]4MEM_MA_DM[0..7]4

MEM_MB_DQS0_P4

MEM_MB_DQS1_P4

MEM_MB_DQS2_P4

MEM_MB_DQS3_P4

MEM_MB_DQS4_P4

MEM_MB_DQS5_P4

MEM_MB_DQS6_P4

MEM_MB_DQS7_P4

MEM_MB_DQS0_N4

MEM_MB_DQS1_N4

MEM_MB_DQS2_N4

MEM_MB_DQS3_N4

MEM_MB_DQS4_N4

MEM_MB_DQS5_N4

MEM_MB_DQS6_N4

MEM_MB_DQS7_N4

MEM_MB_CLK1_P4

MEM_MB_CLK1_N4

MEM_MB_CLK7_P4

MEM_MB_CLK7_N4

MEM_MB_CKE04,7

MEM_MB_CKE14,7

MEM_MB_RAS#4,7

MEM_MB_CAS#4,7

MEM_MB_WE#4,7

MEM_MB0_CS#04,7

MEM_MB0_CS#14,7

MEM_MB0_ODT04,7

MEMHOT_SODIMM# 7

C848

2.2U/6.3V_6

+0.9VSMVREF_DIMM

MEM_MB0_ODT14,7

+3V

C406

0.1U/10V_4

+1.8VSUS

R138

2K/F_4

R130

2K/F_4

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

DIM2_SA0

DIM2_SA1

PDAT_SMB

PCLK_SMB

C702

0.1U/10V_4

C397

1000P/50V_4

102

A0

101

A1

99

98

97

94

92

93

91

90

89

86

84

85

10

26

52

67

13

31

51

70

11

29

49

68

30

32

79

80

1

2

o

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

o

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

GND

202

201

GND

DIM2_SA0

DIM2_SA1

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

59

100

105

116

107

106

130

147

170

185

131

148

169

188

129

146

167

186

164

166

108

113

109

110

115

114

119

198

200

195

197

199

SMbus address A2

3

2

103

111

104

112

117

118

VDD8

VDD7

VDD9

VDD10

VDD11

NC/TEST

SO-DIMM

(REVERSE)

VSS33

VSS32

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

132

128

127

122

121

R423 10K/F_4

R424 10K/F_4

2

CN31

MEM_MB_DATA4

5

DQ0

MEM_MB_DATA5

7

DQ1

MEM_MB_DATA2

17

DQ2

MEM_MB_DATA3

19

DQ3

MEM_MB_DATA0

4

DQ4

MEM_MB_DATA1

6

DQ5

MEM_MB_DATA6

14

DQ6

MEM_MB_DATA7

16

DQ7

MEM_MB_DATA13

23

DQ8

MEM_MB_DATA12

25

DQ9

MEM_MB_DATA11

35

DQ10

MEM_MB_DATA10

37

DQ11

MEM_MB_DATA8

20

DQ12

MEM_MB_DATA9

22

DQ13

MEM_MB_DATA14

36

DQ14

MEM_MB_DATA15

38

DQ15

MEM_MB_DATA16

43

DQ16

MEM_MB_DATA17

45

DQ17

MEM_MB_DATA18

55

DQ18

MEM_MB_DATA19

57

DQ19

MEM_MB_DATA20

44

DQ20

MEM_MB_DATA21

46

DQ21

MEM_MB_DATA22

56

DQ22

MEM_MB_DATA23

58

DQ23

MEM_MB_DATA24

61

DQ24

MEM_MB_DATA25

63

DQ25

MEM_MB_DATA26

73

DQ26

MEM_MB_DATA27

75

DQ27

MEM_MB_DATA28

62

DQ28

MEM_MB_DATA29

64

DQ29

MEM_MB_DATA30

74

DQ30

MEM_MB_DATA31

76

DQ31

MEM_MB_DATA37

123

DQ32

MEM_MB_DATA36

125

DQ33

MEM_MB_DATA34

135

DQ34

MEM_MB_DATA35

137

DQ35

MEM_MB_DATA33

124

DQ36

MEM_MB_DATA32

126

DQ37

MEM_MB_DATA38

134

DQ38

MEM_MB_DATA39

136

DQ39

MEM_MB_DATA40

141

DQ40

MEM_MB_DATA45

143

DQ41

MEM_MB_DATA47

151

DQ42

MEM_MB_DATA46

153

DQ43

MEM_MB_DATA44

140

DQ44

MEM_MB_DATA41

142

DQ45

MEM_MB_DATA43

152

DQ46

MEM_MB_DATA42

154

DQ47

MEM_MB_DATA52

157

DQ48

MEM_MB_DATA53

159

DQ49

MEM_MB_DATA50

173

DQ50

MEM_MB_DATA51

175

DQ51

MEM_MB_DATA48

158

DQ52

MEM_MB_DATA49

160

DQ53

MEM_MB_DATA54

174

DQ54

MEM_MB_DATA55

176

DQ55

MEM_MB_DATA56

179

DQ56

MEM_MB_DATA60

181

DQ57

MEM_MB_DATA58

189

DQ58

MEM_MB_DATA59

191

DQ59

MEM_MB_DATA61

180

DQ60

MEM_MB_DATA57

182

DQ61

MEM_MB_DATA62

192

DQ62

MEM_MB_DATA63

194

DQ63

MEMHOT_SODIMM#_2

50

NC1

MEM_MB_RESET#2

69

NC2

83

NC3

120

NC4

MEM_MB_NC5

163

196

VSS56

193

VSS55

190

VSS54

187

VSS53

184

VSS52

183

VSS51

178

VSS50

177

VSS49

172

VSS48

171

VSS47

168

VSS46

165

VSS45

162

VSS44

161

VSS43

156

VSS42

155

VSS41

150

VSS40

149

VSS39

145

VSS38

144

VSS37

139

VSS36

138

VSS35

133

VSS34

DDR SO-DIMM SOCKET 1.8V

H=9.2

+3V

NB5/RD5

1

07

R105 0_4

T156

T114

Size Document Number Rev

Custom

Date: Sheet

MEMHOT_SODIMM#

PROJECT : QT8

Quanta Computer Inc.

DDR2 SODIMMS: A/B CHANNEL

1

645Tuesday, February 19, 2008

of

1A

Page 7

5

4

3

2

1

4

2

4

2

2

4

2

4

4

2

4

2

4

2

4

2

4

2

4

2

4

2

2

4

4

2

4

2

MEM_MA_ADD[0..15]

MEM_MA_BANK[0..2]

+0.9VSMVTT

3

1

3

1

1

3

1

3

3

1

3

1

3

1

3

1

3

1

3

1

3

1

1

3

3

1

3

1

C176 0.1U/10V_4

C256 0.1U/10V_4

C223 0.1U/10V_4

C104 0.1U/10V_4

C217 0.1U/10V_4

C96 0.1U/10V_4

C152 0.1U/10V_4

C271 0.1U/10V_4

C162 0.1U/10V_4

C101 0.1U/10V_4

C208 0.1U/10V_4

C102 0.1U/10V_4

C107 0.1U/10V_4

C270 0.1U/10V_4

C146 0.1U/10V_4

C269 0.1U/10V_4

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

MEM_MB_ADD[0..15]4,6

MEM_MB_BANK[0..2]4,6

MEM_MB_CKE04,6

MEM_MB_WE#4,6

MEM_MB_CAS#4,6

MEM_MB0_ODT14,6

MEM_MB0_CS#14,6

MEM_MB_CKE14,6

MEM_MB0_CS#04,6MEM_MA0_CS#04,6

MEM_MB_RAS#4,6

MEM_MB0_ODT04,6

MEM_MB_CKE0

MEM_MB_BANK2

MEM_MB_ADD12

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD5

MEM_MB_ADD3

MEM_MB_ADD1

MEM_MB_ADD10

MEM_MB_BANK0

MEM_MB_WE#

MEM_MB_CAS#

MEM_MB0_ODT1

MEM_MB0_CS#1

MEM_MB_CKE1

MEM_MB_ADD15

MEM_MB_ADD7

MEM_MB_ADD14

MEM_MB_ADD6

MEM_MB_ADD11

MEM_MB_ADD2

MEM_MB_ADD4

MEM_MB_BANK1

MEM_MB_ADD0

MEM_MB0_CS#0

MEM_MB_RAS#MEM_MA_RAS#

MEM_MB0_ODT0

MEM_MB_ADD13

+1.8VSUS

MEM_MA_ADD[0..15]4,6

MEM_MA_BANK[0..2]4,6

MEM_MA_CKE04,6

D D

MEM_MA_WE#4,6

MEM_MA_CAS#4,6

MEM_MA0_ODT14,6

MEM_MA0_CS#14,6

MEM_MA_CKE14,6

C C

MEM_MA_RAS#4,6

MEM_MA0_ODT04,6

MEM_MA_CKE0

MEM_MA_BANK2

MEM_MA_ADD12

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD5

MEM_MA_ADD3

MEM_MA_ADD1

MEM_MA_ADD10

MEM_MA_BANK0

MEM_MA_WE#

MEM_MA_CAS#

MEM_MA0_ODT1

MEM_MA0_CS#1

MEM_MA_ADD15

MEM_MA_CKE1

MEM_MA_ADD7

MEM_MA_ADD14

MEM_MA_ADD6

MEM_MA_ADD11

MEM_MA_ADD2

MEM_MA_ADD4

MEM_MA_BANK1

MEM_MA_ADD0

MEM_MA0_CS#0

MEM_MA_ADD13

MEM_MA0_ODT0

+1.8VSUS

RP40 47_4P2R_4

RP35 47_4P2R_4

RP28 47_4P2R_4

RP26 47_4P2R_4

RP20 47_4P2R_4

RP16 47_4P2R_4

RP10 47_4P2R_4

RP39 47_4P2R_4

RP33 47_4P2R_4

RP29 47_4P2R_4

RP24 47_4P2R_4

RP21 47_4P2R_4

RP14 47_4P2R_4

RP12 47_4P2R_4

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

MEM_MB_ADD[0..15]

MEM_MB_BANK[0..2]

+0.9VSMVTT

RP36 47_4P2R_4

4

3

2

RP32 47_4P2R_4

RP27 47_4P2R_4

RP25 47_4P2R_4

RP18 47_4P2R_4

RP15 47_4P2R_4

RP9 47_4P2R_4

RP38 47_4P2R_4

RP34 47_4P2R_4

RP30 47_4P2R_4

RP22 47_4P2R_4

RP19 47_4P2R_4

RP13 47_4P2R_4

RP11 47_4P2R_4

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

1

2

1

4

3

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

2

1

4

3

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

2

1

4

3

C193 0.1U/10V_4

C245 0.1U/10V_4

C154 0.1U/10V_4

C100 0.1U/10V_4

C137 0.1U/10V_4

C94 0.1U/10V_4

C190 0.1U/10V_4

C93 0.1U/10V_4

C160 0.1U/10V_4

C254 0.1U/10V_4

C173 0.1U/10V_4

C255 0.1U/10V_4

C126 0.1U/10V_4

C253 0.1U/10V_4

C178 0.1U/10V_4

C105 0.1U/10V_4

08

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

+1.8VSUS

C239

0.1U/10V_4

C121

0.1U/10V_4

C241

0.1U/10V_4

C242

0.1U/10V_4

PLACE CLOSE TO SOCKET( PER EMI/EMC)

B B

+3V

Close DDR2 socket

+VS

O.S

GND

+3V

C706 0.1U/10V_4

8

MEMHOT_SODIMM#

3

4

Address:92h

2

Q33

*2N7002E-G

MEMHOT_SODIMM# 6

U25

7

A0

+3V

PDAT_SMB2,6,13,28,36

PCLK_SMB2,6,13,28,36

A A

PDAT_SMB

PCLK_SMB

+3V

6

A1

5

A2

1

SDA

2

SCL

*DS75U+T&R

R422 10K/F_4

MEMHOT_SODIMM#

C117

0.1U/10V_4

R421

*10K/F_4

R416 *33_4

3

1

C235

0.1U/10V_4

2

Q32

*2N7002E-G

+3VS5

3

1

SI-2 modified --SB internal pull HI to 3vs5

R417

*10K/F_4

CPU_MEMHOT# 3,13

C122

0.1U/10V_4

C119

0.1U/10V_4

C237

0.1U/10V_4

PLACE CLOSE TO SOCKET( PER EMI/EMC)

C115

0.1U/10V_4

C116

0.1U/10V_4

C745

0.1U/10V_4

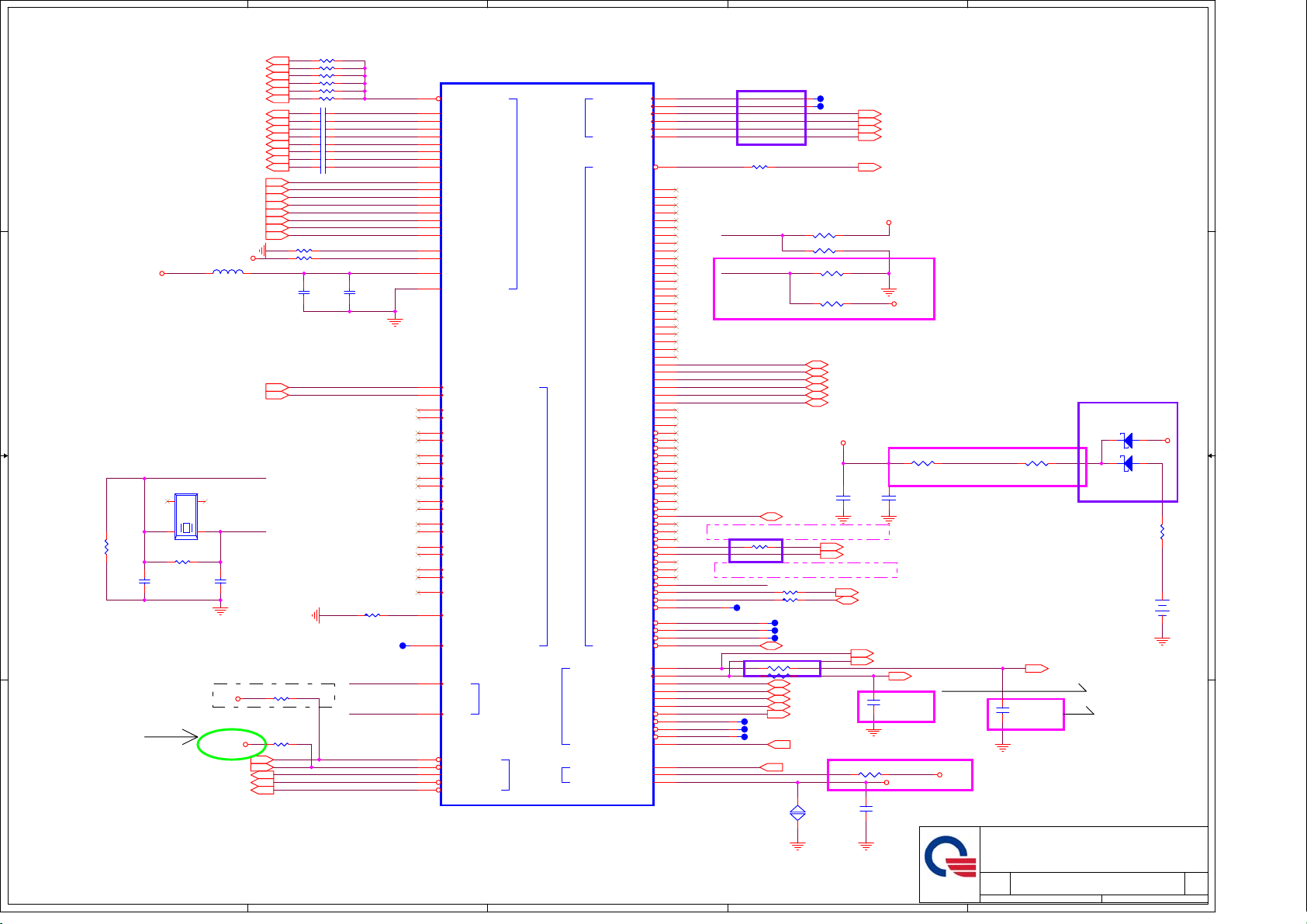

PROJECT : QT8

Quanta Computer Inc.

Size Document Number Rev

Custom

NB5/RD5

5

4

3

2

DDR2 SODIMMS TERMINATIONS

Date: Sheet

1

745Tuesday, February 19, 2008

1A

of

Page 8

5

HT_CPU_NB_CAD_H0

HT_CPU_NB_CAD_L0

HT_CPU_NB_CAD_H1

HT_CPU_NB_CAD_L1

HT_CPU_NB_CAD_H2

HT_CPU_NB_CAD_L2

HT_CPU_NB_CAD_H3

HT_CPU_NB_CAD_L3

HT_CPU_NB_CAD_H4

HT_CPU_NB_CAD_L4

HT_CPU_NB_CAD_H5

HT_CPU_NB_CAD_L5

R533 301/F_4

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

HT_CPU_NB_CAD_H6

HT_CPU_NB_CAD_L6

HT_CPU_NB_CAD_H7

HT_CPU_NB_CAD_L7

HT_CPU_NB_CAD_H8

HT_CPU_NB_CAD_L8

HT_CPU_NB_CAD_H9

HT_CPU_NB_CAD_L9

HT_CPU_NB_CAD_H10

HT_CPU_NB_CAD_L10

HT_CPU_NB_CAD_H11

HT_CPU_NB_CAD_L11

HT_CPU_NB_CAD_H12

HT_CPU_NB_CAD_L12

HT_CPU_NB_CAD_H13

HT_CPU_NB_CAD_L13

HT_CPU_NB_CAD_H14

HT_CPU_NB_CAD_L14

HT_CPU_NB_CAD_H15

HT_CPU_NB_CAD_L15

HT_CPU_NB_CLK_H0

HT_CPU_NB_CLK_L0

HT_CPU_NB_CLK_H1

HT_CPU_NB_CLK_L1

HT_CPU_NB_CTL_H0

HT_CPU_NB_CTL_L0

HT_CPU_NB_CTL_H1

HT_CPU_NB_CTL_L1

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

A9

VDDQ1

C1

VDDQ2

C3

VDDQ3

C7

VDDQ4

C9

VDDQ5

E9

VDDQ6

G1

VDDQ7

G3

VDDQ8

G7

VDDQ9

G9

VDDQ10

A1

VDD1

E1

VDD2

J9

VDD3

M9

VDD4

R1

VDD5

J1

VDDL

J7

VSSDL

A7

VSSQ1

B2

VSSQ2

B8

VSSQ3

D2

VSSQ4

D8

VSSQ5

E7

VSSQ6

F2

VSSQ7

F8

VSSQ8

H2

VSSQ9

H8

VSSQ10

A3

VSS1

E3

VSS2

J3

VSS3

N1

VSS4

P9

VSS5

D D

SI-2 modified

-- follow AMD

C C

B B

*0.1U/10V_4

A A

*0.1U/10V_4

R56 *100_4

Within 200mils

+1.8V_MEM_VDDQ

C95

C89

check list to

change part

number 300 ohm

to 301 ohm

SPM_BA0

SPM_BA1

SPM_A12

SPM_A10

SPM_A9

SPM_A8

SPM_A7

SPM_A6

SPM_A5

SPM_A4

SPM_A3

SPM_A2 SPM_DQ7

SPM_A1

SPM_A0

SPM_CLKN

SPM_CLKP

SPM_CKE

SPM_CS#

SPM_WE#

SPM_RAS#

SPM_CAS#

SPM_DM0

SPM_DM1

SPM_ODT

SPM_DQS0P

SPM_DQS0N

SPM_DQS1P

SPM_DQS1N

R63

*1K_4

R61

*1K_4

SPM_VREF

SPM_BA2

5

U27

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

*HYB18T512161B2F-25

HT_RXCALP

HT_RXCALN

SPM_DQ15

SPM_DQ14

SPM_DQ9

SPM_DQ12

SPM_DQ8SPM_A11

SPM_DQ10

SPM_DQ13

SPM_DQ11

SPM_DQ5

SPM_DQ3

SPM_DQ4

SPM_DQ1

SPM_DQ0

SPM_DQ2

SPM_DQ6

MEM_VDDQ_VDDL

4

U32A

Y25

HT_RXCAD0P

Y24

HT_RXCAD0N

V22

HT_RXCAD1P

V23

HT_RXCAD1N

V25

HT_RXCAD2P

V24

HT_RXCAD2N

U24

HT_RXCAD3P

U25

HT_RXCAD3N

T25

HT_RXCAD4P

T24

HT_RXCAD4N

P22

HT_RXCAD5P

P23

HT_RXCAD5N

P25

HT_RXCAD6P

P24

HT_RXCAD6N

N24

HT_RXCAD7P

N25

HT_RXCAD7N

AC24

HT_RXCAD8P

AC25

HT_RXCAD8N

AB25

HT_RXCAD9P

AB24

HT_RXCAD9N

AA24

HT_RXCAD10P

AA25

HT_RXCAD10N

Y22

HT_RXCAD11P

Y23

HT_RXCAD11N

W21

HT_RXCAD12P

W20

HT_RXCAD12N

V21

HT_RXCAD13P

V20

HT_RXCAD13N

U20

HT_RXCAD14P

U21

HT_RXCAD14N

U19

HT_RXCAD15P

U18

HT_RXCAD15N

T22

HT_RXCLK0P

T23

HT_RXCLK0N

AB23

HT_RXCLK1P

AA22

HT_RXCLK1N

M22

HT_RXCTL0P

M23

HT_RXCTL0N

R21

HT_RXCTL1P

R20

HT_RXCTL1N

C23

HT_RXCALP

A24

HT_RXCALN

RS780(RX780)

+1.8V_MEM_VDDQ

L76

*BLM18PG181SN1D(180,1.5A)_6

C757

*1U/10V_4

4

3

HT_NB_CPU_CAD_H0

PART 1 OF 6

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HYPER TRANSPORT CPU I/F

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

D24

HT_NB_CPU_CAD_L0

D25

HT_NB_CPU_CAD_H1

E24

HT_NB_CPU_CAD_L1

E25

HT_NB_CPU_CAD_H2

F24

HT_NB_CPU_CAD_L2

F25

HT_NB_CPU_CAD_H3

F23

HT_NB_CPU_CAD_L3

F22

HT_NB_CPU_CAD_H4

H23

HT_NB_CPU_CAD_L4

H22

HT_NB_CPU_CAD_H5

J25

HT_NB_CPU_CAD_L5

J24

HT_NB_CPU_CAD_H6

K24

HT_NB_CPU_CAD_L6

K25

HT_NB_CPU_CAD_H7

K23

HT_NB_CPU_CAD_L7

K22

HT_NB_CPU_CAD_H8

F21

HT_NB_CPU_CAD_L8

G21

HT_NB_CPU_CAD_H9

G20

HT_NB_CPU_CAD_L9

H21

HT_NB_CPU_CAD_H10

J20

HT_NB_CPU_CAD_L10

J21

HT_NB_CPU_CAD_H11

J18

HT_NB_CPU_CAD_L11

K17

HT_NB_CPU_CAD_H12

L19

HT_NB_CPU_CAD_L12

J19

HT_NB_CPU_CAD_H13

M19

HT_NB_CPU_CAD_L13

L18

HT_NB_CPU_CAD_H14

M21

HT_NB_CPU_CAD_L14

P21

HT_NB_CPU_CAD_H15

P18

HT_NB_CPU_CAD_L15

M18

HT_NB_CPU_CLK_H0

H24

HT_NB_CPU_CLK_L0

H25

HT_NB_CPU_CLK_H1

L21

HT_NB_CPU_CLK_L1

L20

HT_NB_CPU_CTL_H0

M24

HT_NB_CPU_CTL_L0

M25

HT_NB_CPU_CTL_H1

P19

HT_NB_CPU_CTL_L1

R18

HT_TXCALP

B24

HT_TXCALN

B25

R641R655

R534 301/F_4

SI-2 modified

-- follow AMD

check list to

change part

number 300 ohm

to 301 ohm

This block is for UMA RS780 only , RX780 can

remove all component

U32D

T24

R502 *40.2/F_4

R501 *40.2/F_4

+1.8V_MEM_VDDQ

SPM_A0

SPM_A1 SPM_DQ1

SPM_A2

SPM_A3

SPM_A4

SPM_A5

SPM_A6

SPM_A7

SPM_A8

SPM_A9

SPM_A10

SPM_A11

SPM_A12

SPM_A13

SPM_BA0

SPM_BA1

SPM_BA2

SPM_RAS#

SPM_CAS#

SPM_WE#

SPM_CS#

SPM_CKE

SPM_ODT

SPM_CLKP

SPM_CLKN

SPM_COMPP

SPM_COMPN

3

AB12

AE16

AE15