Page 1

5

4

3

2

1

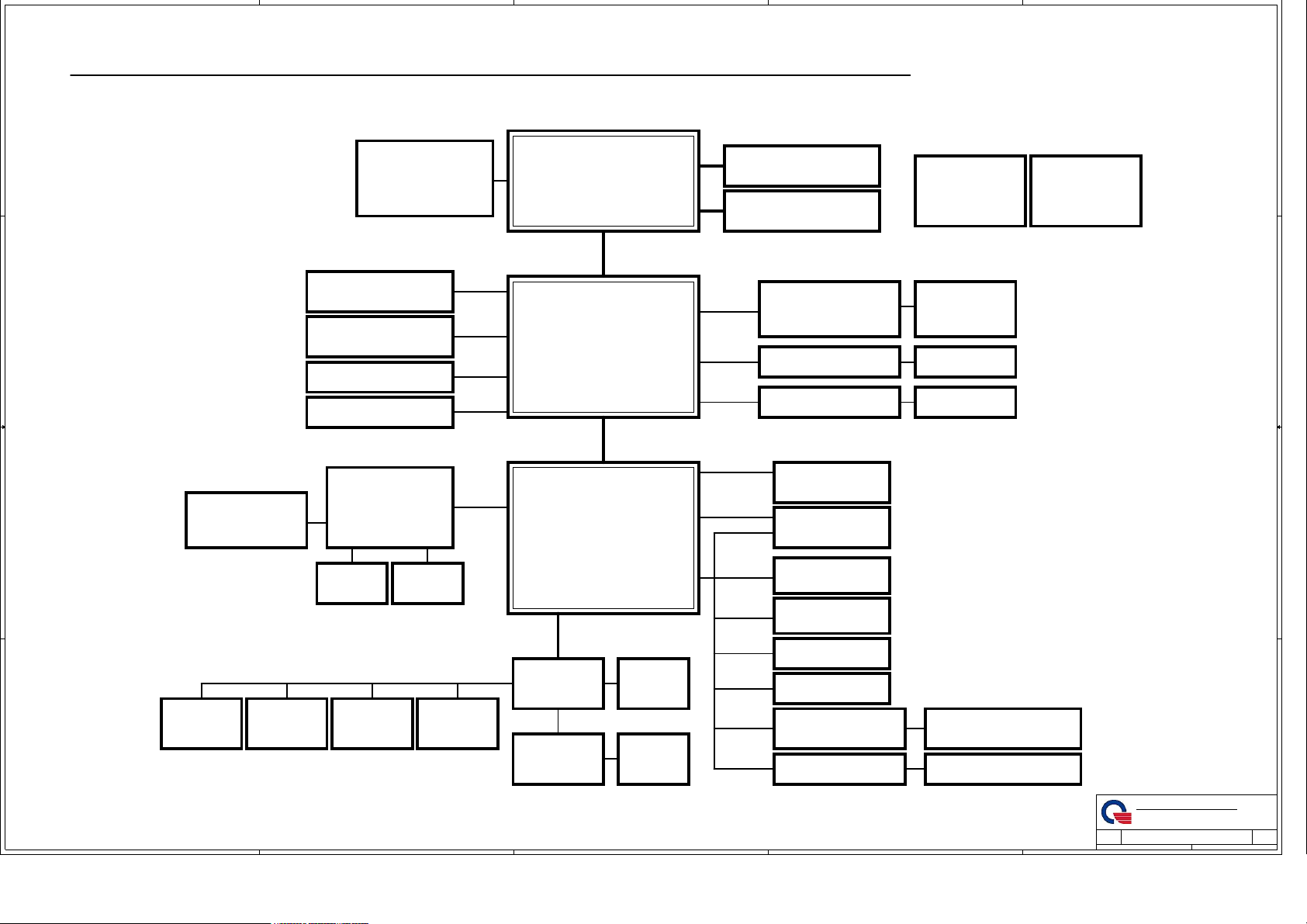

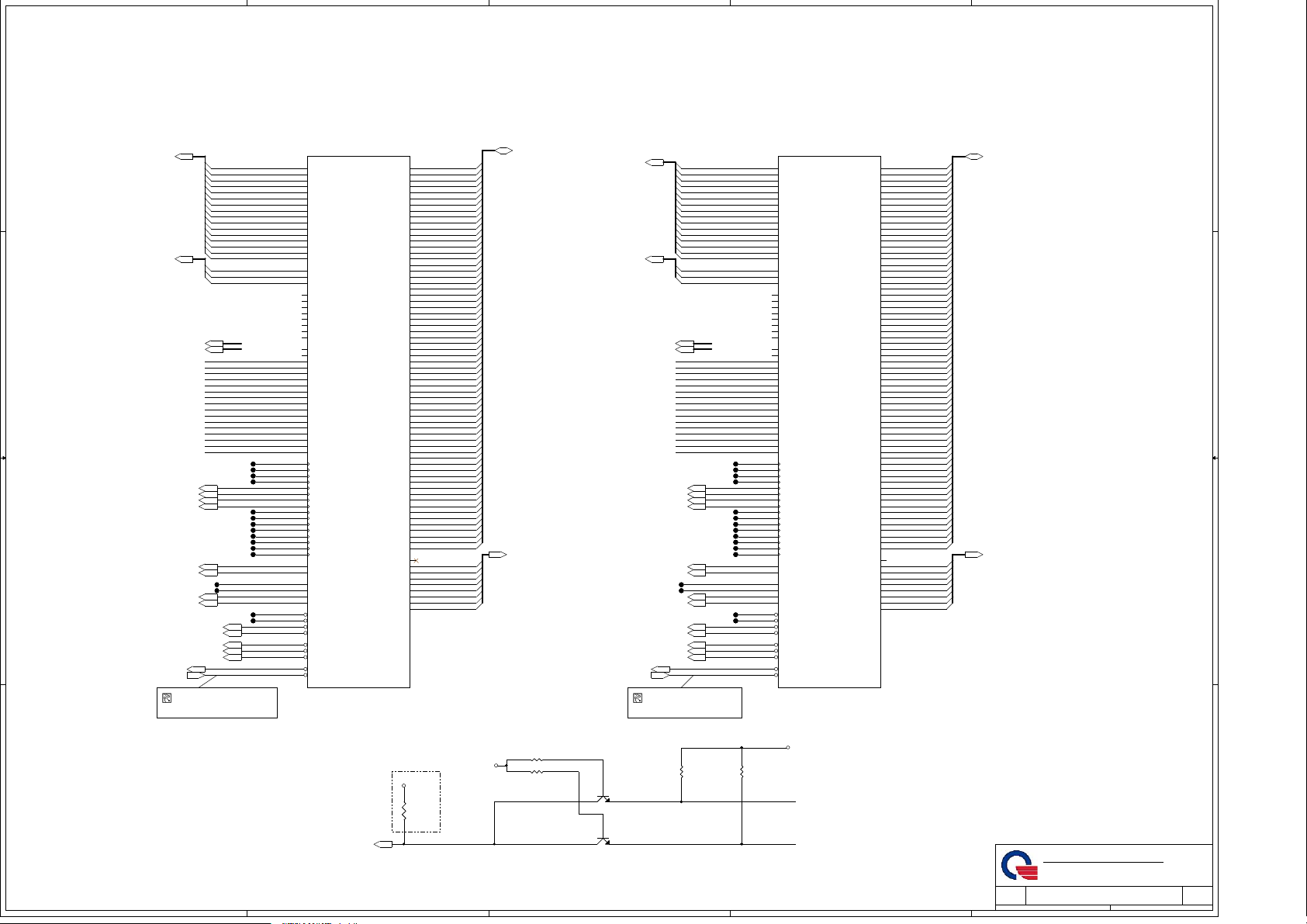

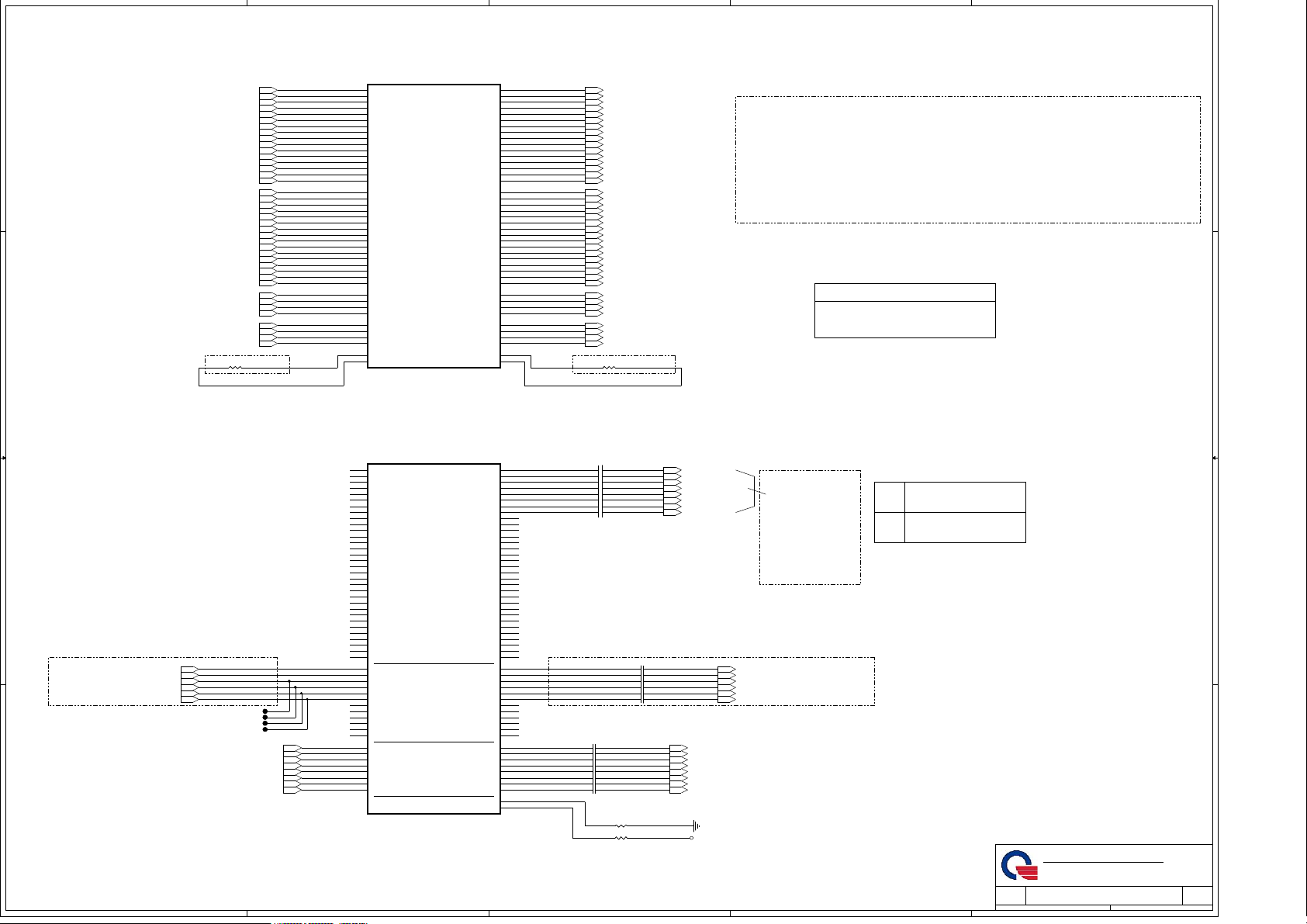

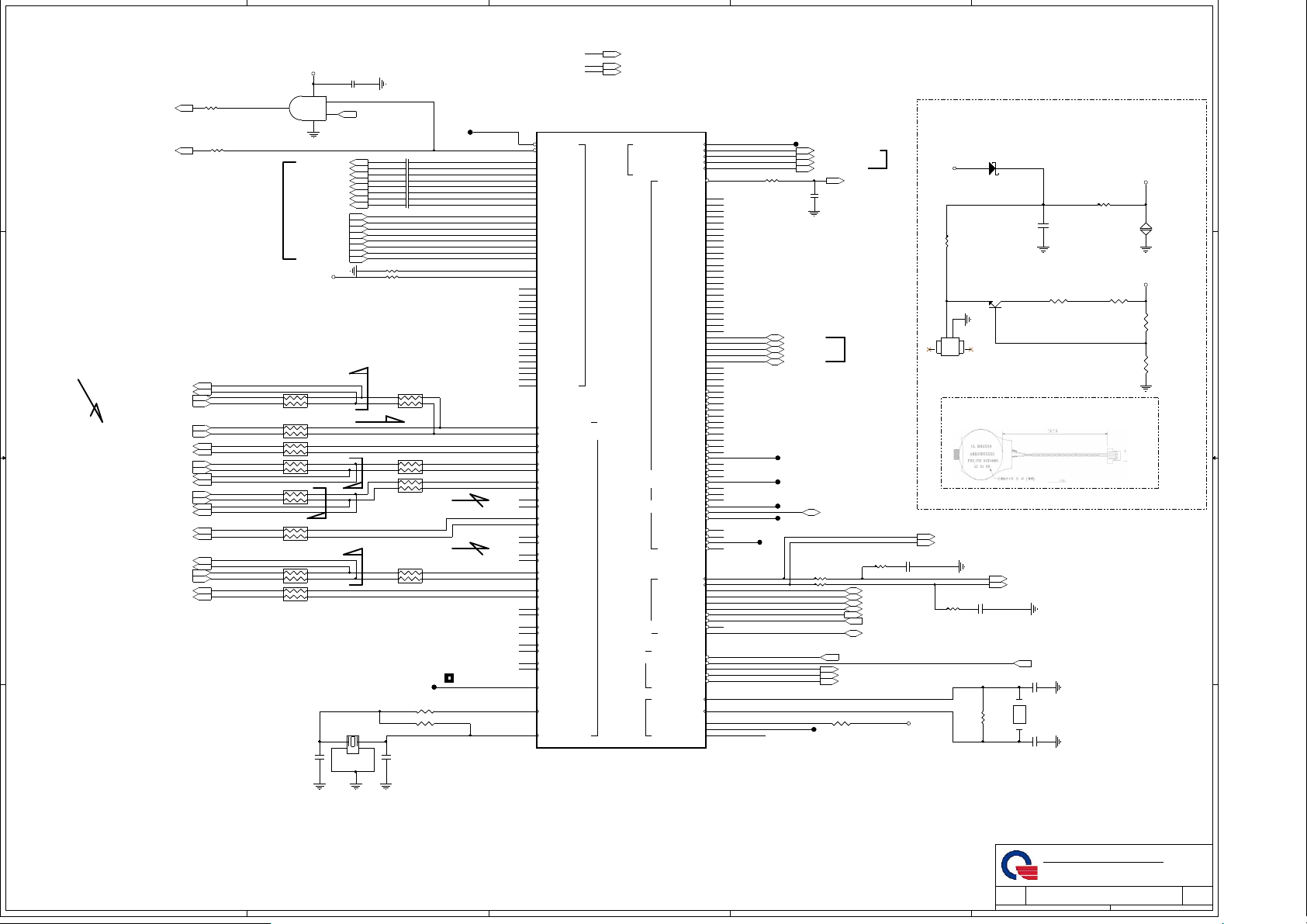

PS-Note Block Diagram -- AMD Nile ( PS2A )

D D

DDR3-800

SB Temperature

Sensor Interface

(SB-TSI)

( SMBus V2.0 )

Side

Frame Buffer (NU)

Port

DRR2 1Gb (128MB)

C C

13.3" HD

LVDS

(1366x768) LCD

CRT

HDMI

HDA CODEC

HP/Mic

Combo Jack

B B

Function Board

Conexant

CX20582

RGB

PCIe

HD

Audio

AMD ASB2 CPU

Geneva

AMD Family 10h Processor Rev C3

812 Balls

HyperTransport

HT3 @ 1.6GHz / HT1 @ 1.0GHz

NORTH BRIDGE

RS880M

A-LINK BUS

PCIe x4

SOUTH BRIDGE

SB820

DDR3 SO-DIMM 1

DDR3 SO-DIMM 2

PCIe #0

GEN-II

PCIe #1

GEN-II

PCIe #2

GEN-II

Ethernet / 1G

Realtek

RTL8111DL-VB-GR

i SATA

GEN-III

SATA 6Gb/s

e SATA

GEN-II

SATA 3Gb/s

USB# 0

2.5" HDD

e-SATA / USB

COMBO CNN

External Clock

Gengerator

( NU )

RJ-45

WLAN Mini PCIe Slot

WWANMini PCIe Slot

SIM Card

Thermal

Sensor

( NU )

Internal

MIC

Internal

SPK

USB# 1~2

USB PORT X 2

Function Board

Bluetooth

LPC

BUS

ITE8502E

G-SENSOR INT.

K/B

A A

TOUCH

PAD

TRACK

POINT

Charger

SPI

Flash

Battery

USB# 3

USB# 4

USB# 5

USB# 6

USB# 7

5

4

3

(BDC-2)

WWAN

WLAN

Card Reader

Realtek RTL5159

Camera Conn.

4 in 1 Socket

SD/MMC/MS/MS-Pro

Camera Module

2

LCD MODULE

Qua nta Comp uter Inc.

Qua nta Comp uter Inc.

Qua nta Comp uter Inc.

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Doc ument Numb er

Doc ument Numb er

Doc ument Numb er

Cus tom

Cus tom

Cus tom

Bloc k Diagram

Bloc k Diagram

Bloc k Diagram

Date:

Date:

Date:

06/14/2 010, 04 :47 PM

06/14/2 010, 04 :47 PM

06/14/2 010, 04 :47 PM

Rev.Size

Rev.Size

Rev.Size

< C >

< C >

of

of

of

1 43

1 43

1 43

< C >

Sheet :

Sheet :

1

Sheet :

Page 2

5

4

3

2

1

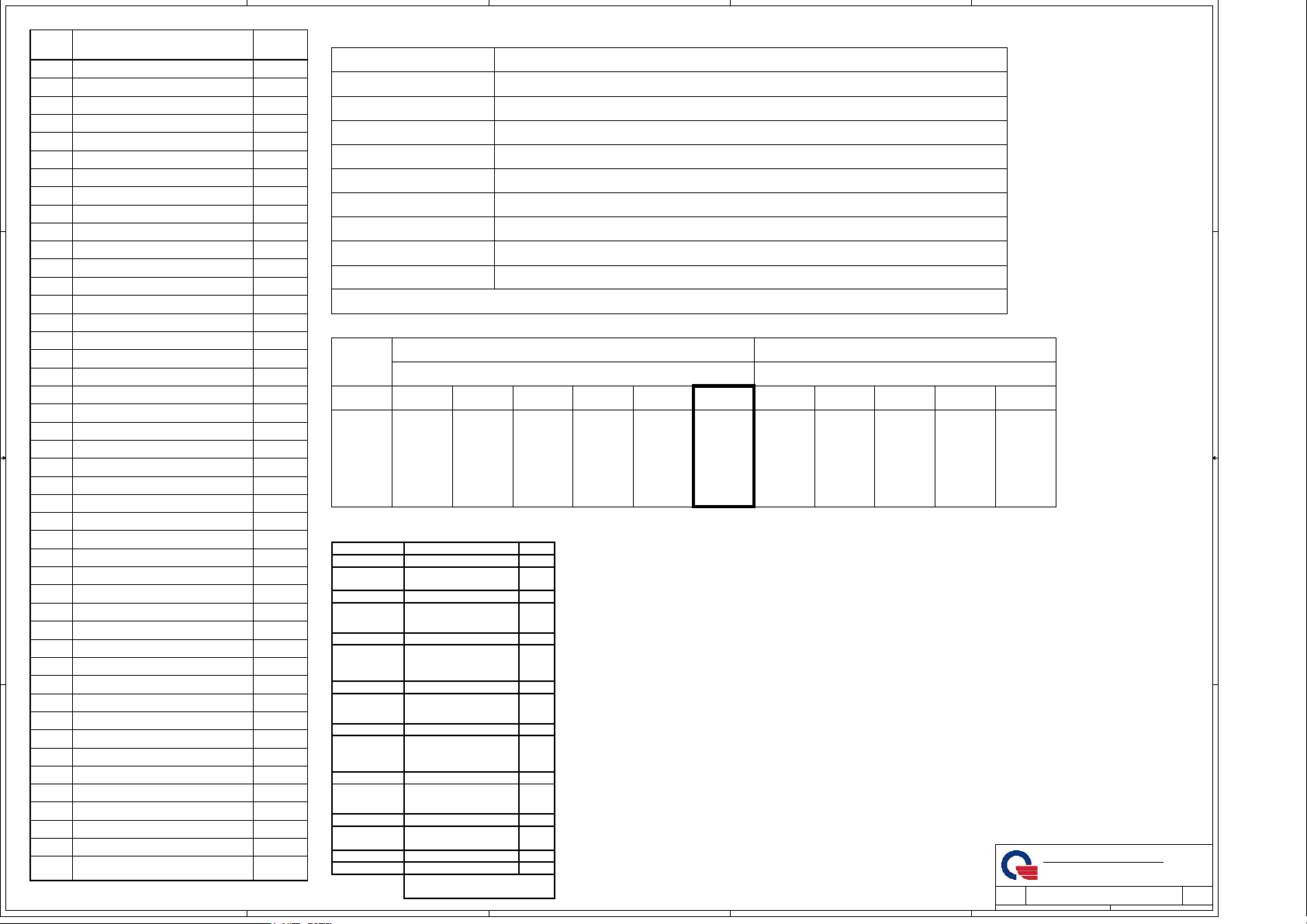

INDEX

DESCRIPTION

1

SCHEMATIC BLOCK DIAGRAM

2

SYSTEM INFORMATION

3

D D

C C

B B

A A

CLOCK GENERATOR (ICS9LPRS480)

4

ASB2 Geneva ( HT )

5

ASB2 Geneva ( DDR3 )

6

ASB2 Geneva ( CLK, T HM CTRL )

7

ASB2 Geneva ( PW R, GND )

8

DDR3 SO-DIMM ( DH-A, RVS )

9

DDR3 SO-DIMM ( CH-B, STD )

10

RS880M ( HT, PCIE, HDMI )

11

RS880M ( CLK, DISP, PLL )

12

RS880M ( SIDE PORT, VRAM )

13

RS880M ( PWR, GND )

14

SB820M ( PCIE, LPC, CPU I/F )

15

SB820M ( ACPI, GPIO, USB )

16

SB820M ( SATA, BIDs )

17

SB820M ( PWR, GND )

18

SB820M ( STRAPS, PWRGD )

19

LCD, CAMERA

20

CRT CONN

21

HDMI CONN

22

SATA, e-SATA+USB, THERMAL, FAN

23

WLAN, WWAN CONN

24

AUDIO/FUNCTION BOARD CONN

25

KB CONN, TOUCH PAD, TRACK POINT

26

BT, G-SENSOR, RFID

27

AUDIO ( CX20582, SPK )

28

LAN ( RTL8111DL-VB-GR )

29

KBC IT8502E

30

SCREW HOLE, EMI

31

POWER CHARGER

32

3V, 5V ( RT8206BGQW )

33

+CPU_CORE

34

+NB_CORE, +0.9V, +2.5V

35

DDR3 ( RT8207AGQW )

36

+1.1V, +1.1VS5, +1.8V

37

DISCHARGE

38

POWER BLOCK DIAGRAM

39

AMD NILE BIMINI SEQUENCE

40

PS2A SEQUENCE ( A-TEST )

41

HISTORY ( BEFORE A-TEST )

42

HISTORY ( A --> C1 )

43

HISTORY ( C1 --> C2 )

5

NOTEPAGE#

Resistor (R)

Capacitor (C)

Inductance(L)

Parallel Resistor (RP)

Parallel Capacitor (CA)

Diode (D)

Transistor(Q)

Crystal (Y)

Fuse (F)

Connector (CN)

33/J_4 --> ( Impedance/Tolerence_Size )

10U/10V/Y5V_8 --> (Capacitor Value/Max. Voltage/Capacitor Type_Size)

BLM15BB121SS1(120,0.3A)_4 --> ( Vender Part Number ( Impedance@100MHz, Max. Current)_Size)

0_4P2R_1/16W --> (Impedance_Port_Max. Power)

220PX4 --> (Capacitor Value X Port)

TVSS5VESPT(18.6V,9.4A) --> (Vender Part Number (Max. Voltage, Max Current )

ME2N7002E(60V,0.25A) --> ( Vender Part Number (Max. Voltage,Max. Current)

25MHZ(30PPM) --> (Frequecy(Tolerence))

FUSE_1A_6V --> (FUSE_Max. Current_Max. Voltage)

CONN DIP USB 4P 1R MR(P2,H5.16) --> (Connecotr Function Dimensions )

* : NU, J : +/- 5%, F : +/- 1%

LAYER

L1 - TOP

L3 - IN1

L4 - IN2

L6 - IN3

L8 - BOT

35 Ω ±10%

13/34.5

11/35.2

11/35.2

9/34.6

13/34.5

37 Ω ±10%

12/36.3

10/37.2

10/37.2

8/37

12/36.3

SINGLE END

TRACE / IMPEDANCE

40 Ω ±10%

10/40.3

9/39.4

9/39.4

7/40

10/40.3

50 Ω ±10%

6.5/50.2

5.5/50

5.5/50

4.5/49.2

6.5/50.2

55 Ω ±10%

5/56.3

4.5/54.4

4.5/54.4

3.5/54.4

5/56.3

UNIT : mil / Ω

60 Ω ±10%

( Default )

4/61.4

3.5/60

3.5/60

3/57.57

4/61.4

80 Ω ±10% 85 Ω ±10% 90 Ω ±10% 93 Ω ±10% 100 Ω ±10%

6.5_4/80

5.5_4/80.5

5.5_4/80.5

5_4/80

6.5_4/80

DIFFERENTIAL

TRACE_SPACE / IMPEDANCE

5.5_4/85

5_4.5/85.9

5_4.5/85.9

4.5_4.5/85.7

5.5_4/85

4.5_4/91

4_4/90

4_4/90

4_4.5/89.4

4.5_4/91

4.5_4.5/94

4_4.5/92.5

4_4.5/92.5

4_5.5/93.6

4.5_4.5/94

UNIT : mil _ mil / Ω

4_5/100.5

4_6/100

4_6/100

4_8/100

4_5/100.5

PS2A BOARD STACK (PDC)

S / M

L1 - TOP ( HS )

L2 - GND

L3 - IN1 ( HS )

L4 - IN2 ( LS )

L5 - VCC

L6 - IN3 ( HS )

L7 - GND

L8 - BOT ( HS )

S / M

4

0.5oz + planting

PP2116

1 oz

Core 5 mil

1 oz

PP7628

1 oz

Core 5 mil

1 oz

1 oz

Core 5 mil

1 oz

TOTAL : 48.12mil / 1.22mm

0.5

1.7

4.2

1.3

5.0

1.3

6.0

1.3

5.0

1.3

6.52PP7628

1.3

5.0

1.3

4.2PP2116

1.70.5oz + planting

0.5

3

2

Qua nta Computer Inc .

Qua nta Computer Inc .

Qua nta Computer Inc .

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Docu ment Nu mber

Docu ment Nu mber

Docu ment Nu mber

C

C

C

SYSTEM INFOR MATION

SYSTEM INFOR MATION

SYSTEM INFOR MATION

Date:

06/14/20 10, 04:47 PM

Date:

06/14/20 10, 04:47 PM

Date:

06/14/20 10, 04:47 PM

1

Part Naming Conventions

Sheet :

Sheet :

Sheet :

02

of

2 43

of

2 43

of

2 43

Rev.Size

Rev.Size

Rev.Size

< C >

< C >

< C >

Page 3

5

4

3

2

1

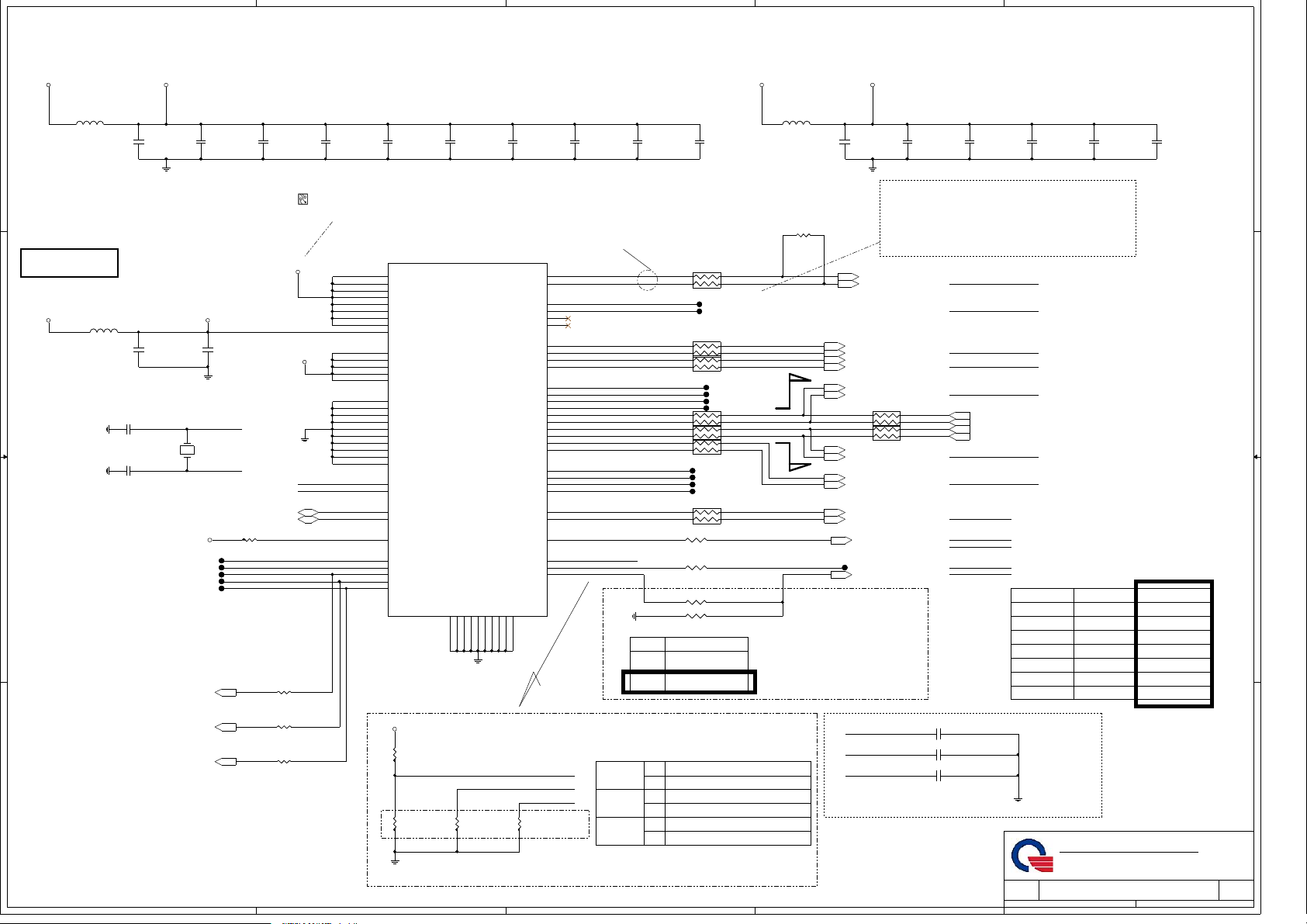

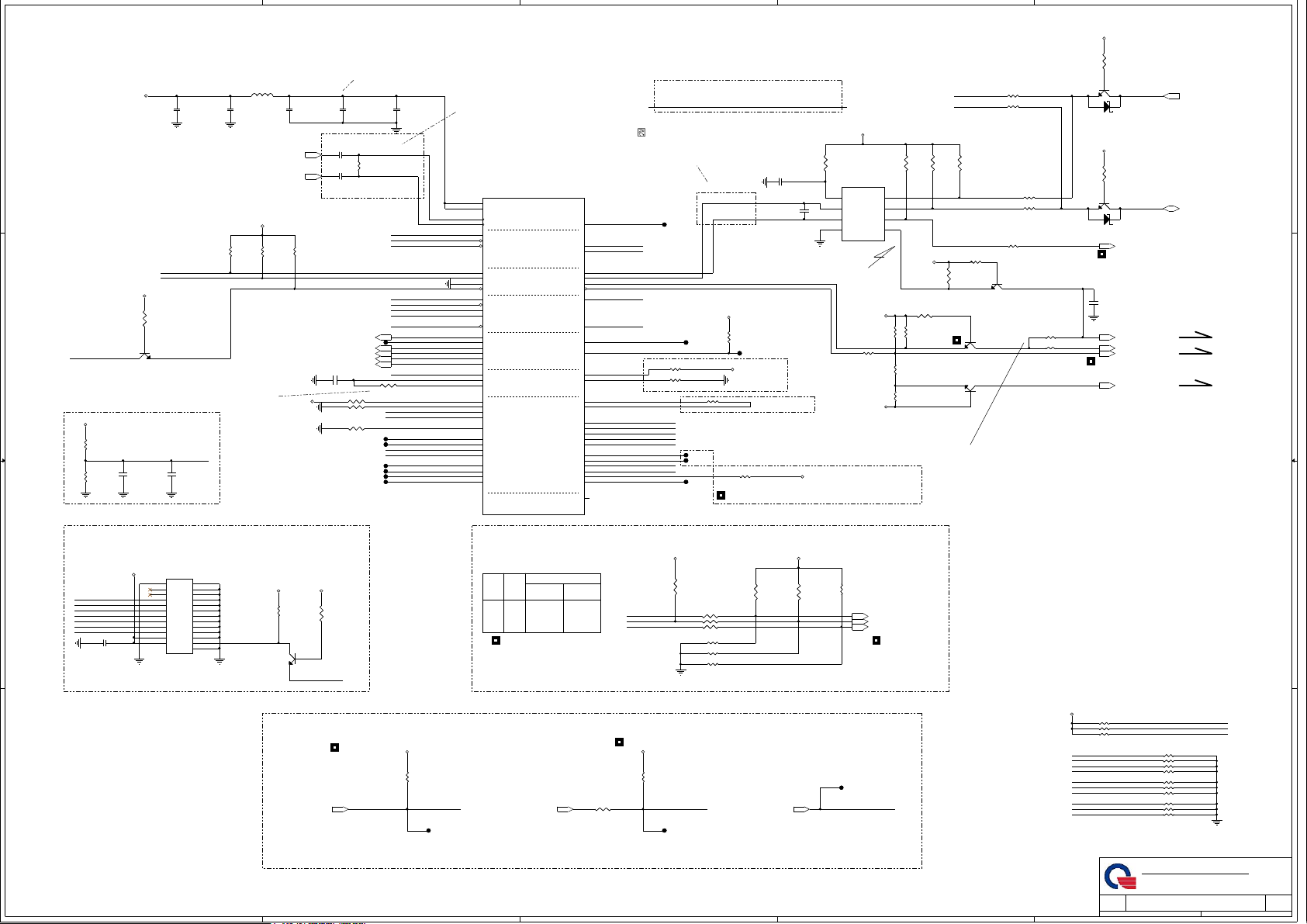

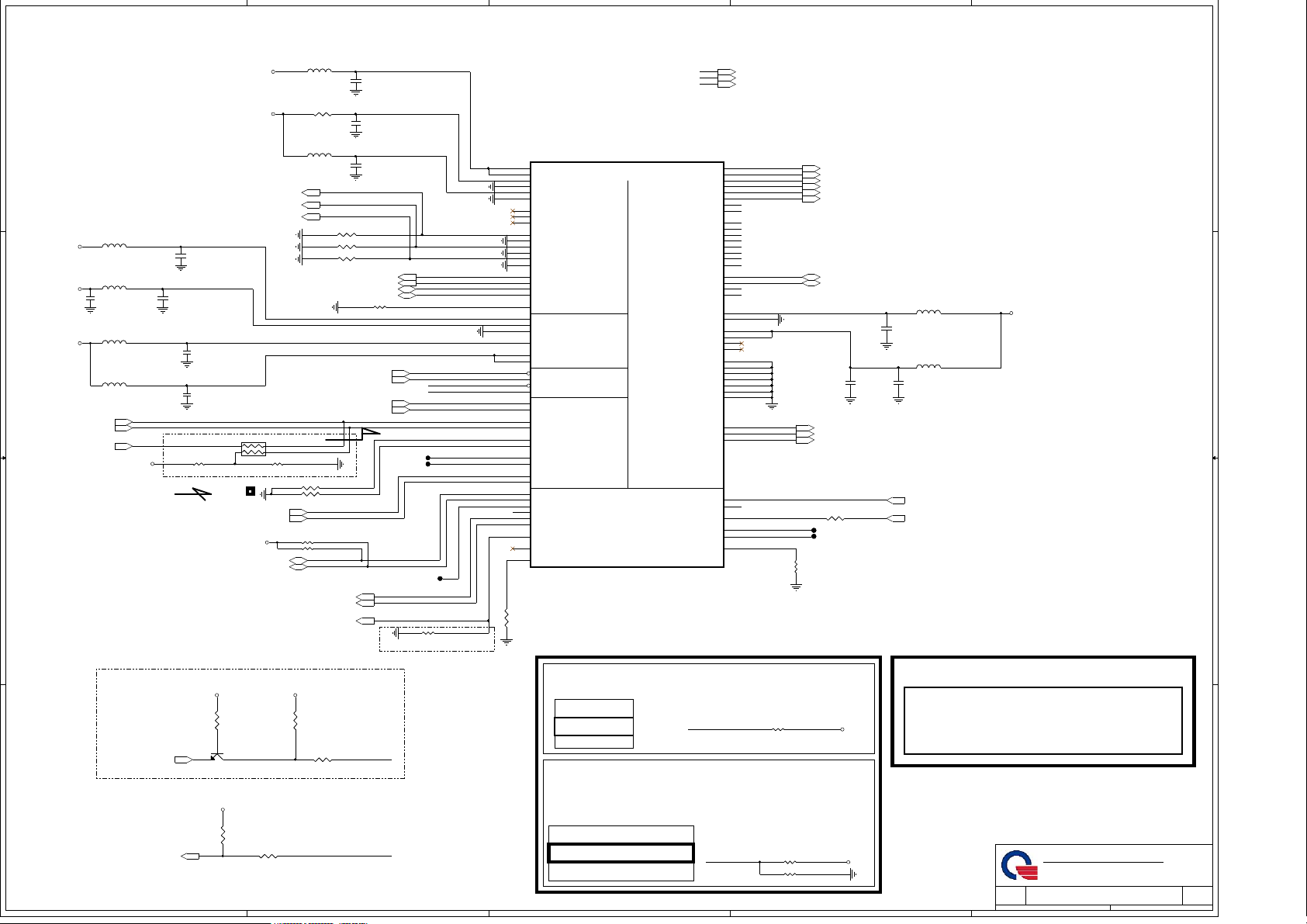

CLK_GEN

+3V +3V_CLK_VD D +1.1V_CLK_VDD IO+1.1V

L51

L51

*HCB1608KF-601T10(600,1A)_6

D D

*HCB1608KF-601T10(600,1A)_6

ICS9LPRS480

RTM880N-796-VB-GRT P/N : AL000880001

EC-20100512A-01

EC-20100430A-02

+3V

L49 *FCM1608KF-601T02_6L49 *FCM1608KF-601T02_6

C C

C179

C179

*33P/50V/COH_4

*33P/50V/COH_4

C178

C178

*33P/50V/COH_4

*33P/50V/COH_4

B B

3.3V(250mA)

C509

C207

C207

*22U/6.3V/X5R_8

*22U/6.3V/X5R_8

C509

*2200P/50V/X7R_4

*2200P/50V/X7R_4

P/N : ALPRS480000

+3V_CLK_48

C465

C465

*22U/6.3V/X5R_8

*22U/6.3V/X5R_8

CG_XIN

21

Y3

Y3

*14.318MHZ(30PPM)

*14.318MHZ(30PPM)

CG_XOUT

+3V_CLK_VD D

T109T109

T112T112

T113T113

T115T115

T116T116

3.3V(53mA)

C468

C468

*2.2U/6.3V/X5R_6

*2.2U/6.3V/X5R_6

PCLK_SMB(8,9,15,26)

PDAT_SMB(8,9,15,26)

R388 *8.2K/J_4R388 *8.2K/J_4

CLKREQ0#

CLKREQ1#

PCIE_REQ_WLAN#_R

PCIE_REQ_WWAN#_R

PCIE_REQ_LAN#_R

C492

C492

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

+3V_CLK_VD D

+1.1V_CLK_VDD IO

C505

C505

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

C506

C506

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

C512

C512

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

C494

C494

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

NOTE: +3V_CLK_VDD is better to have 0.1uF

for each power pin.

U34

U34

*RTM880N-796-VB-GRT

*RTM880N-796-VB-GRT

4

CG_XIN

CG_XOUT

CLK_PD#

VDDDOT

16

VDDSRC

26

VDDATIG

35

VDDSB_SRC

40

VDDSATA

48

VDDCPU

55

VDDHTT

56

VDDREF

63

VDD48

11

VDDSRC_IO0

17

VDDSRC_IO1

25

VDDATIG_IO

34

VDDSB_SRC_IO

47

VDDCPU_IO

1

GND48

7

GNDDOT

10

GNDSRC0

18

GNDSRC1

24

GNDATIG

33

GNDSB_SRC

43

GNDSATA

46

GNDCPU

52

GNDHTT

60

GNDREF

61

X1

62

X2

2

SMBCLK

3

SMBDAT

51

PD#

23

CLKREQ0#

45

CLKREQ1#

44

CLKREQ2#

39

CLKREQ3#

38

CLKREQ4#

QFN64

QFN64

TGND065TGND166TGND267TGND368TGND469TGND570TGND671TGND772TGND873TGND9

CPUK8_0T

CPUK8_0C

ATIG0T

ATIG0C

ATIG1T

ATIG1C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

SRC2C

SRC3T

SRC3C

SRC4T

SRC4C

SRC6T/SATAT

SRC6C/SATAC

SRC7T/27M_SS

SRC7C/27M_NS

HTT0T/66M

HTT0C/66M

48MHz_0

REF0/SEL_HTT66

REF1/SEL_SATA

REF2/SEL_27

74

C470

C470

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

Place within 0.5" of CLKGEN

CLK_CPUP_R

50

CLK_CPUN_R

49

CLK_NBGFXP_R

30

CLK_NBGFXN_R

29

28

27

CLK_SBREFP _R

37

CLK_SBREFN_R

36

CLK_SBSRCP _R

32

CLK_SBSRCN_R

31

NBGPP_CLKP_R

22

NBGPP_CLKN_R

21

CLK_PCIE_NEW_R

20

CLK_PCIE_NEW#_R

19

CLK_PCIE_WLANP_R

15

CLK_PCIE_WLANN_R

14

CLK_PCIE_WANP_R

13

CLK_PCIE_WANN_R

12

CLK_PCIE_LANP_R

9

CLK_PCIE_LANN_R

8

42

41

6

5

NBHT_REFCLKP_R

54

NBHT_REFCLKN_R

53

CLK_48M_USB_R

64

SEL_HTT66

59

SEL_SATA

58

SEL_27

57

C472

C472

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

RP28 *0_4P2RRP28 *0_4P2R

RP29 *0_4P2RRP29 *0_4P2R

RP27 *0_4P2RRP27 *0_4P2R

RP24 *0_4P2RRP24 *0_4P2R

RP23 *0_4P2RRP23 *0_4P2R

RP22 *0_4P2RRP22 *0_4P2R

RP26 *0_4P2RRP26 *0_4P2R

R153 *158/F_4R153 *158/F_4

R154 *90.9/F_4R154 *90.9/F_4

C495

C495

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

1

3

T111T111

T110T110

1

3

1

3

T107T107

T105T105

T104T104

T102T102

1

3

1

3

1

3

T117T117

T114T114

T100T100

T95T95

1

3

R336 *47/J_4R336 *47/J_4

R149 *47/J_4R149 *47/J_4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

R4004/R4005 (value may change)

NB_OSC

EC-20100426A-01

PCIE_REQ_WLAN#(15,23)

R400 *0/J_4R400 *0/J_4

1.8V 82.5R/130RRX780

RS780 1.1V 158R/90.9R

EC-20100430A-02

L50

L50

*FCM1608KF-601T02_6

*FCM1608KF-601T02_6

R392

R392

*261/F_4

*261/F_4

1.2V(53mA)

C209

C209

*22U/6.3V/X5R_8

*22U/6.3V/X5R_8

Clock chip has internal serial terminations for differencial pairs,

external resistors are reserved for debug purpose.

Place within 0.5" of CLKGEN

Differential clock da mping resistors

Delete after EA PAS S.

CPUCLKP (14)

CPUCLKN (14)

CLK_SBLINKP_B (14)

CLK_SBLINKN_B (14)

CLK_SBSRCP (14)

CLK_SBSRCN (14)

CLK_PCIE_WLANP_B (23)

CLK_PCIE_WLANN_B (23)

RP21 0_4P2RRP21 0_4P2R

1

3

RP25 0_4P2RRP25 0_4P2R

1

3

CLK_PCIE_WANP_B (23)

CLK_PCIE_WANN_B (23)

CLK_PCIE_LANP (14)

CLK_PCIE_LANN (14)

CLK_HT_REFCLKP (14)

CLK_HT_REFCLKN (14)

CLK_48M_USB (15)

EXT_SB_OSC_R

RES CHIP 82.5 1/16W +-1%(0402) --> CS08252FB11

RES CHIP 130 1/16W +-1%(0402)L-F --> CS11302FB15

RES CHIP 158 1/16W +-1%(0402) --> CS11582FB00

RES CHIP 90.9 1/16W +-1%(0402) --> CS09092FB15

T40T40

EXT_NB_OSC (11)

C510

C510

*2200P/50V/X7R_4

*2200P/50V/X7R_4

2

4

2

4

C208

C208

*2200P/50V/X7R_4

*2200P/50V/X7R_4

To CPU Diff 200MHz

To NB Diff 100MHz

To NB Diff 100MHz

To SB Diff 100MHz

To Mini PCIE Slot (WLAN)

CLK_PCIE_WLANP (14)

CLK_PCIE_WLANN (14)

CLK_PCIE_WWANP (14)

CLK_PCIE_WWANN (14)

To Mini PCIE Slot (WWAN)

To LAN Controller

To NB Diff 100MHz

To SB 48MHz

To RTS5159 48MHz

To SB 14.318MHz

To NB 14.318MHz

C490

C490

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

C473

C473

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

For RS880M's external graphics

( External Clock Mode )

EXT CLK GEN:

Provided free-running 100MHz clock

to SR820M PCIE_RCLKP/N.

EC-20100313A-01

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPPSB_REFCLK

RX780 RS780

100M DIFF

100M DIFF

14M SE (1.8V)

NC vref

100M DIFF

100M DIFF

100M DIFF

100M DIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

C471

C471

*0.1U/16V/X7R_4

*0.1U/16V/X7R_4

100M DIFF

100M DIFF

14M SE (1.1V)

100M DIFF

03

PCIE_REQ_WWAN#(15,23)

PCIE_REQ_LAN#(15,28)

A A

5

R402 *0/J_4R402 *0/J_4

R405 *0/J_4R405 *0/J_4

+3V_CLK_VD D

R150

R150

*8.2K/J_4

*8.2K/J_4

R151

R151

*8.2K/J_4

*8.2K/J_4

4

R371

R371

*8.2K/J_4

*8.2K/J_4

SEL_SATA

SEL_HTT66

SEL_27

R152

R152

*8.2K/J_4

*8.2K/J_4

SEL_HTT66

SEL_SATA

SEL_27

66 MHz 3.3V single ended HTT clock

1

*0 100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

1

0

100 MHz spreading differential SRC clock

*

27MHz and 27M SS outputs

1

0*

100 MHz SRC clock

* default

3

CLK_48M_USB_R

SEL_SATA

SEL_27

C462 *10P/50V/C0G_4C462 *10P/50V/C0G_4

C188 *10P/50V/C0G_4C188 *10P/50V/C0G_4

C189 *10P/50V/C0G_4C189 *10P/50V/C0G_4

EMI Cap placement close IC

2

Document Numbe r

Document Numbe r

Document Numbe r

Custom

Custom

Custom

CLOCK GEN SLG8SP628

CLOCK GEN SLG8SP628

CLOCK GEN SLG8SP628

Date:

Date:

Date:

06/15/2010, 10:00 AM

06/15/2010, 10:00 AM

06/15/2010, 10:00 AM

Quanta Computer In c.

Quanta Computer In c.

Quanta Computer In c.

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Sheet :

Sheet :

Sheet :

1

of

of

of

3 43

3 43

3 43

Rev.Size

Rev.Size

Rev.Size

< C >

< C >

< C >

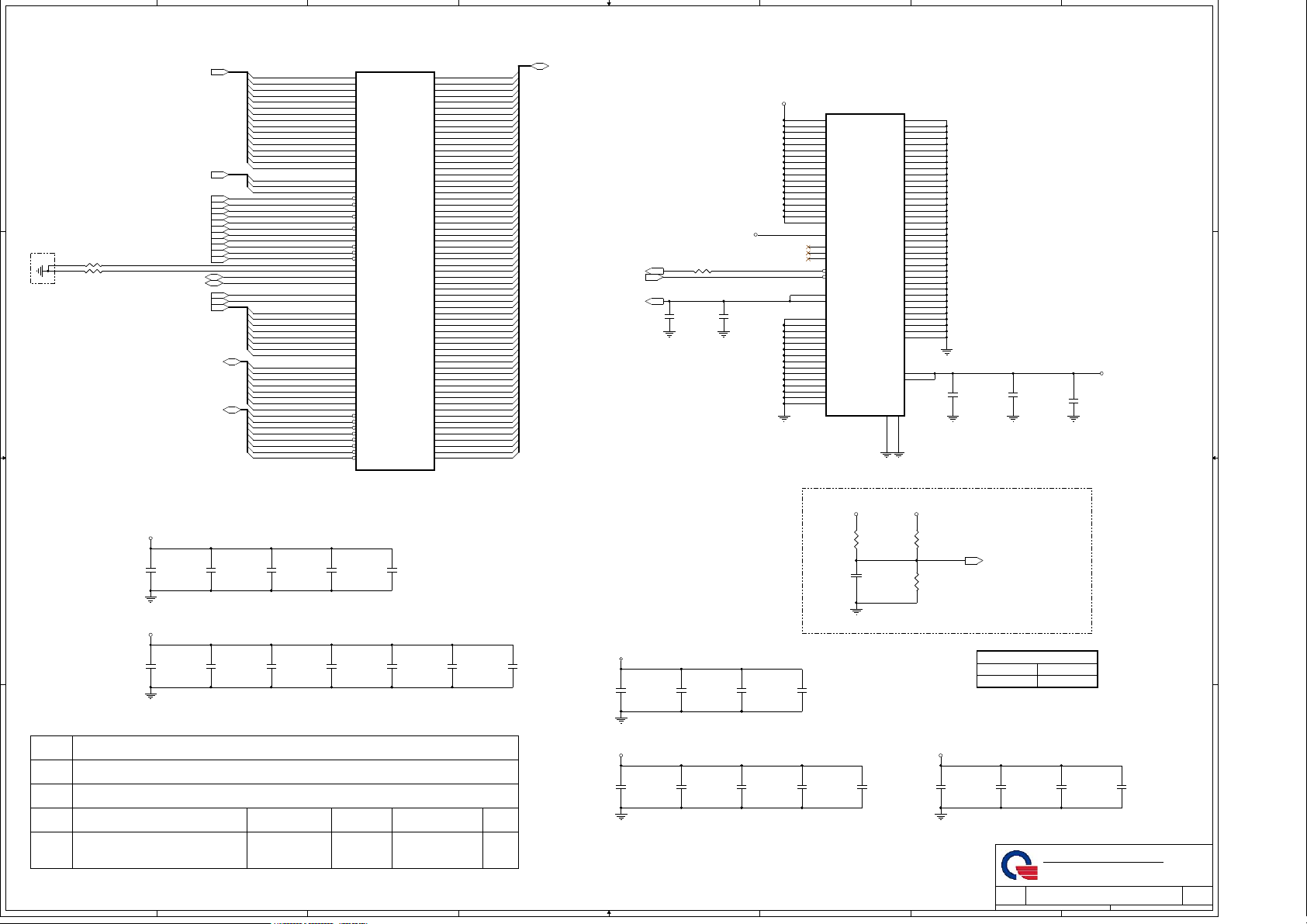

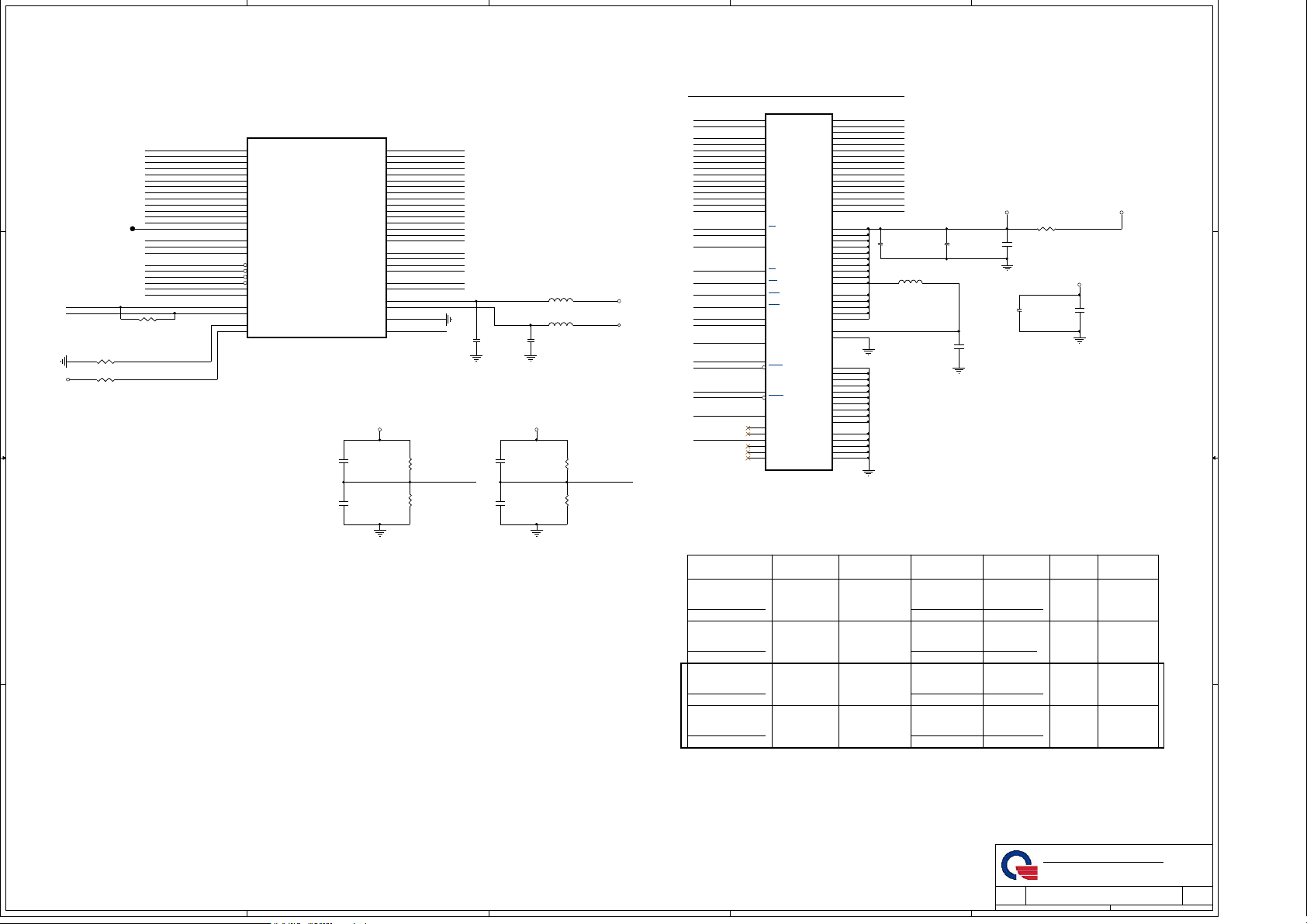

Page 4

5

4

3

2

1

04

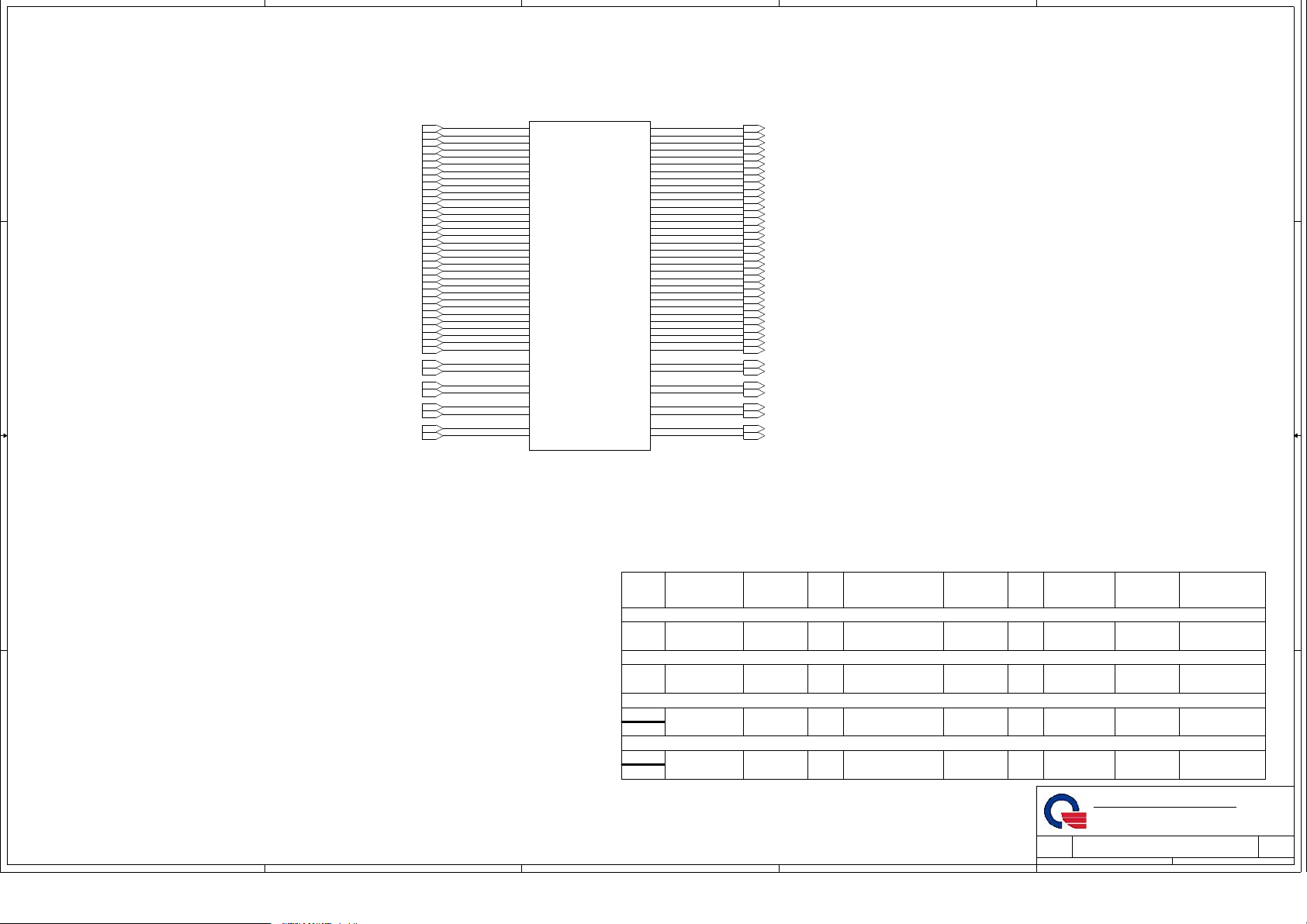

AMD Processor HT Interface

D D

C C

B B

HT_CADINP15(10)

HT_CADINN15(10)

HT_CADINP14(10)

HT_CADINN14(10)

HT_CADINP13(10)

HT_CADINN13(10)

HT_CADINP12(10)

HT_CADINN12(10)

HT_CADINP11(10)

HT_CADINN11(10)

HT_CADINP10(10)

HT_CADINN10(10)

HT_CADINP9(10)

HT_CADINN9(10)

HT_CADINP8(10)

HT_CADINN8(10)

HT_CADINP7(10)

HT_CADINN7(10)

HT_CADINP6(10)

HT_CADINN6(10)

HT_CADINP5(10)

HT_CADINN5(10)

HT_CADINP4(10)

HT_CADINN4(10)

HT_CADINP3(10)

HT_CADINN3(10)

HT_CADINP2(10)

HT_CADINN2(10)

HT_CADINP1(10)

HT_CADINN1(10)

HT_CADINP0(10)

HT_CADINN0(10)

HT_CLKINP1(10)

HT_CLKINN1(10)

HT_CLKINP0(10)

HT_CLKINN0(10)

HT_CTLINP1(10)

HT_CTLINN1(10)

HT_CTLINP0(10)

HT_CTLINN0(10)

HT_CADINP15

HT_CADINN15

HT_CADINP14

HT_CADINN14

HT_CADINP13

HT_CADINN13

HT_CADINP12

HT_CADINN12

HT_CADINP11

HT_CADINN11

HT_CADINP10

HT_CADINN10

HT_CADINP9

HT_CADINN9

HT_CADINP8

HT_CADINN8

HT_CADINP7

HT_CADINN7

HT_CADINP6

HT_CADINN6

HT_CADINP5

HT_CADINN5

HT_CADINP4

HT_CADINN4

HT_CADINP3

HT_CADINN3

HT_CADINP2

HT_CADINN2

HT_CADINP1

HT_CADINN1

HT_CADINP0

HT_CADINN0

HT_CLKINP1

HT_CLKINN1

HT_CLKINP0

HT_CLKINN0

HT_CTLINP1

HT_CTLINN1

HT_CTLINP0

HT_CTLINN0

W7

W6

U6

U5

R7

R6

P6

P5

L6

L5

J6

J5

H4

H3

G6

G5

T3

T4

T2

T1

P3

P4

P2

P1

M2

M1

K3

K4

K2

K1

H2

H1

M8

M7

M3

M4

Y6

Y5

V2

V1

U21A

U21A

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

HT LINK

HT LINK

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

AB6

AB5

AB9

AB8

AC7

AC6

AE6

AE5

AE9

AE8

AH3

AH4

AK3

AK4

AH1

AH2

Y1

Y2

Y4

Y3

AB1

AB2

AB4

AB3

AD4

AD3

AF1

AF2

AF4

AF3

AK1

AK2

AF6

AF5

AD1

AD2

Y8

Y9

V4

V3

HT_CADOUTP15

HT_CADOUTN15

HT_CADOUTP14

HT_CADOUTN14

HT_CADOUTP13

HT_CADOUTN13

HT_CADOUTP12

HT_CADOUTN12

HT_CADOUTP11

HT_CADOUTN11

HT_CADOUTP10

HT_CADOUTN10

HT_CADOUTP9

HT_CADOUTN9

HT_CADOUTP8

HT_CADOUTN8

HT_CADOUTP7

HT_CADOUTN7

HT_CADOUTP6

HT_CADOUTN6

HT_CADOUTP5

HT_CADOUTN5

HT_CADOUTP4

HT_CADOUTN4

HT_CADOUTP3

HT_CADOUTN3

HT_CADOUTP2

HT_CADOUTN2

HT_CADOUTP1

HT_CADOUTN1

HT_CADOUTP0

HT_CADOUTN0

HT_CLKOUTP1

HT_CLKOUTN1

HT_CLKOUTP0

HT_CLKOUTN0

HT_CTLOUTP1

HT_CTLOUTN1

HT_CTLOUTP0

HT_CTLOUTN0

HT_CADOUTP15 (10)

HT_CADOUTN15 (10)

HT_CADOUTP14 (10)

HT_CADOUTN14 (10)

HT_CADOUTP13 (10)

HT_CADOUTN13 (10)

HT_CADOUTP12 (10)

HT_CADOUTN12 (10)

HT_CADOUTP11 (10)

HT_CADOUTN11 (10)

HT_CADOUTP10 (10)

HT_CADOUTN10 (10)

HT_CADOUTP9 (10)

HT_CADOUTN9 (10)

HT_CADOUTP8 (10)

HT_CADOUTN8 (10)

HT_CADOUTP7 (10)

HT_CADOUTN7 (10)

HT_CADOUTP6 (10)

HT_CADOUTN6 (10)

HT_CADOUTP5 (10)

HT_CADOUTN5 (10)

HT_CADOUTP4 (10)

HT_CADOUTN4 (10)

HT_CADOUTP3 (10)

HT_CADOUTN3 (10)

HT_CADOUTP2 (10)

HT_CADOUTN2 (10)

HT_CADOUTP1 (10)

HT_CADOUTN1 (10)

HT_CADOUTP0 (10)

HT_CADOUTN0 (10)

HT_CLKOUTP1 (10)

HT_CLKOUTN1 (10)

HT_CLKOUTP0 (10)

HT_CLKOUTN0 (10)

HT_CTLOUTP1 (10)

HT_CTLOUTN1 (10)

HT_CTLOUTP0 (10)

HT_CTLOUTN0 (10)

Geneva Processor

OPNMODEL

CLOCK

SPEED

CACHETDP

CORES

ON DIE

FPU

MEMORY

SPEED

I/O BUS

SPEED

AMD Turion II Neo Dual-Core Mobile Processors

TMK625GAV23GM 1.5GHz 15W 2MB

K625

AJ0K625VT05

total dedicated L2

2 cores 128b DDR3-800

DDR3L-800

3.2 GT/s

AMD Athlon II Neo Dual-Core Processors

AMK325LAV23GM 1.3GHz 12W 2MB

K325

AJ0K325VT03

total dedicated L2

2 cores 64b DDR3-800

DDR3L-800

2.0 GT/s

AMD Athlon II Neo Dual-Core Processors

AMK125LAV13GM 1.7GHz 12W 1MB L2 1 core 64b DDR3-800

K125

DDR3L-800

2.0 GT/s

AMD V Series Processors

A A

V105

VMV105FDV12GM

1.2GHz 9W 512KB L2 1 core 64b DDR3-800

DDR3L-800

2.0 GT/s

AMD-V

Technology

Yes

Yes

Yes

Yes

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Document Number

Document Number

Document Number

Custom

Custom

Custom

AMD ASB2 HT LINK/THERMAL

AMD ASB2 HT LINK/THERMAL

AMD ASB2 HT LINK/THERMAL

06/15/2010, 10:00 AM

06/15/2010, 10:00 AM

06/15/2010, 10:00 AM

Date:

Date:

5

4

3

2

Date:

Shee t :

Shee t :

Shee t :

1

4 43

4 43

4 43

of

of

of

Rev.Size

Rev.Size

Rev.Size

< C >

< C >

< C >

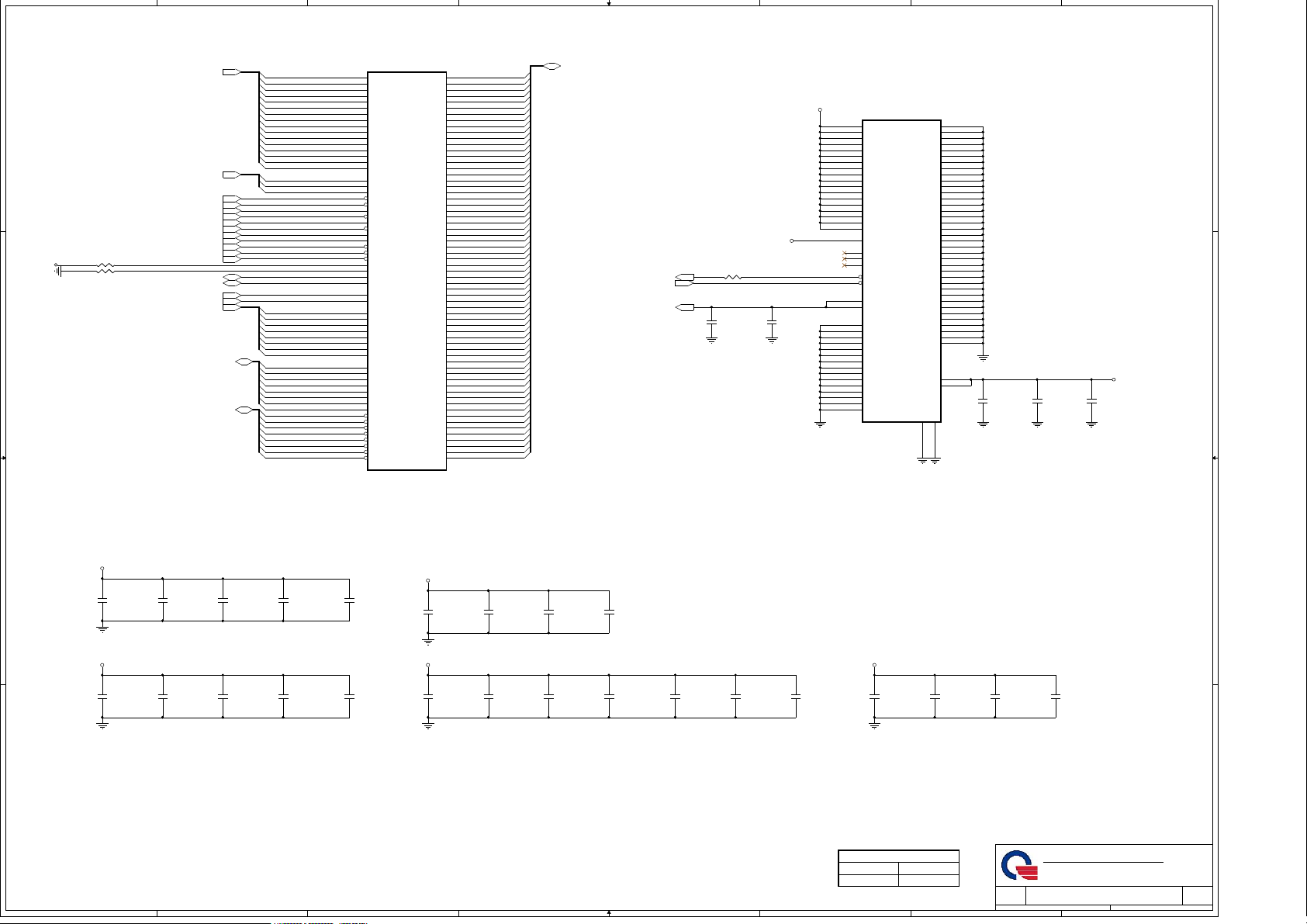

Page 5

5

4

3

2

1

AMD Processor DDR3 Memory Interface

D D

M_A_A[0..15](8)

M_A_BS[0..2](8)

C C

B B

M_A_RST#(8)

M_A_HOT#(8)

Channel-A to Solderdown MEM (DIMM socket close CPU.) Channel-B to SODIMM Connector

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

M_A_BS2

M_A_BS1

M_A_BS0

M_A_DQSP[0..7](8)

M_A_DQSN[0..7](8)

M_A_DQSP7

M_A_DQSN7

M_A_DQSP6

M_A_DQSN6

M_A_DQSP5

M_A_DQSN5 M_A_DQ26

M_A_DQSP4

M_A_DQSN4

M_A_DQSP3

M_A_DQSN3

M_A_DQSP2

M_A_DQSN2

M_A_DQSP1

M_A_DQSN1

M_A_DQSP0

M_A_DQSN0

M_A_CLKP0(8)

M_A_CLKN0(8)

M_A_CLKP1(8)

M_A_CLKN1(8)

M_A_CKE1(8)

M_A_CKE0(8)

T50T50

T42T42

M_A_ODT1(8)

M_A_ODT0(8)

M_A_CS#1(8)

M_A_CS#0(8)

M_A_RAS#(8)

M_A_CAS#(8)

M_A_WE#(8)

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

T63T63

T45T45

T43T43

T39T39

T38T38

T37T37

T36T36

T80T80

T32T32

T34T34

T30T30

MEM_MA1_ODT1

MEM_MA1_ODT0

T48T48

T41T41

M_A_HOT#

AG28

AC28

AB29

AC26

AC29

AE28

AK12

AG15

AH15

AH22

AG22

AG26

AH26

AK18

AH17

AG17

AB27

AB26

AG29

AH29

AE29

AH30

AC27

AE27

AJ11

AJ17

AJ29

AF27

AJ30

AF29

AF30

P30

M29

P28

T30

P27

R26

R27

U28

V30

U27

Y30

W29

R29

K30

J29

G29

F29

L28

L29

H29

H27

J27

J26

E28

F28

E25

F25

G17

H17

E12

F12

Y28

Y27

W27

W26

P26

M26

D18

F19

E20

E19

M30

M28

L27

M32

U21B

U21B

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_DQS_H8

MA_DQS_L8

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_CLK_H7

MA_CLK_L7

MA_CLK_H6

MA_CLK_L6

MA_CLK_H5

MA_CLK_L5

MA_CLK_H4

MA_CLK_L4

MA_CLK_H3

MA_CLK_L3

MA_CLK_H2

MA_CLK_L2

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA_CKE1

MA_CKE0

MA1_ODT1

MA1_ODT0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA0_CS_L1

MA0_CS_L0

MA_RAS_L

MA_CAS_L

MA_WE_L

MA_RESET_L

FREE|MA_EVENT_L

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

DDR III: CHANNEL A

DDR III: CHANNEL A

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM8

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

M_A_DQ62

AH11

M_A_DQ61

AJ12

M_A_DQ60

AJ14

M_A_DQ59

AF11

M_A_DQ58

AF12

M_A_DQ57

AG12

M_A_DQ56

AH12

M_A_DQ55

AK14

M_A_DQ54

AF15

M_A_DQ53

AH19

M_A_DQ52

AK20

M_A_DQ51

AF14

M_A_DQ50

AG14

M_A_DQ49

AF17

M_A_DQ48 M_B_A0

AG19

M_A_DQ47

AG20

M_A_DQ46

AJ20

M_A_DQ45

AF22

M_A_DQ44

AK24

M_A_DQ43

AF19

M_A_DQ42

AF20

M_A_DQ41

AJ23

M_A_DQ40

AG23

M_A_DQ39

AF23

M_A_DQ38

AF25

M_A_DQ37

AH27

M_A_DQ36

AK30

M_A_DQ35

AJ25

M_A_DQ34

AG25

M_A_DQ33

AJ26

M_A_DQ32

AJ28

M_A_DQ31

D28

M_A_DQ30

G28

M_A_DQ29

D26

M_A_DQ28

E26

M_A_DQ27

F30

E29

M_A_DQ25

F27

M_A_DQ24

H26

M_A_DQ23

H25

M_A_DQ22

D24

M_A_DQ21

H22

M_A_DQ20

E22

M_A_DQ19

F26

M_A_DQ18

G26

M_A_DQ17

D22

M_A_DQ16

G23

M_A_DQ15

G22

M_A_DQ14

G20

M_A_DQ13

G15

M_A_DQ12

F15

M_A_DQ11

D20

M_A_DQ10

F22

M_A_DQ9

D16

M_A_DQ8

E17

M_A_DQ7

H15

M_A_DQ6

H14

M_A_DQ5

G12

M_A_DQ4

H12

M_A_DQ3

E15

M_A_DQ2

E14

M_A_DQ1

E11

M_A_DQ0

F11

H30

M_A_DM7

AL12

M_A_DM6

AK16

M_A_DM5

AK22

M_A_DM4

AJ27

M_A_DM3

E27

M_A_DM2

E23

M_A_DM1

H19

M_A_DM0

G14

M_A_DQ63

AG11

M_A_DQ[0..63 ] (8)

M_A_DM[0..7] ( 8)

M_B_A[0..15](9)

M_B_BS[0..2](9)

M_B_DQSP[0..7](9)

M_B_DQSN[0..7](9)

M_B_RST#(9)

M_B_HOT#(9)

Layout: Route as 60 ohms

with 5/10 W/S from CPU pins.

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_BS2

M_B_BS1

M_B_BS0

M_B_DQSP7

M_B_DQSN7

M_B_DQSP6

M_B_DQSN6

M_B_DQSP5

M_B_DQSN5

M_B_DQSP4

M_B_DQSN4

M_B_DQSP3

M_B_DQSN3

M_B_DQSP2

M_B_DQSN2

M_B_DQSP1

M_B_DQSN1

M_B_DQSP0

M_B_DQSN0

T66T66

T68T68T47T47

T64T64

M_B_CLKP0(9)

M_B_CLKN0(9)

M_B_CLKP1(9)

M_B_CLKN1(9)

M_B_CKE1( 9)

M_B_CKE0( 9)

T49T49

T77T77

M_B_ODT1( 9)

M_B_ODT0( 9)

M_B_CS#1(9)

M_B_CS#0(9)

M_B_RAS#(9)

M_B_CAS#(9)

M_B_WE#(9)

T65T65

T82T82

T74T74

T83T83

T75T75

T71T71

T70T70

T72T72

T73T73

MEM_MB1_ODT1

MEM_MB1_ODT0

T78T78

T76T76

M_B_HOT#

AM14

AM20

AM26

AM30

AM22

AM21

AG33

AJ33

AD32

AC33

AD33

AE33

AN14

AL20

AN26

AN30

AN22

AN21

AA32

AA33

AB33

AB32

AB31

AB30

AD31

AD30

AK31

AH31

AK32

AH33

AK33

AF33

AJ32

AF31

AF32

AH32

P33

P31

T32

T31

T33

V32

U33

V33

V31

W33

Y31

Y33

Y32

R33

K33

K31

G32

F32

L33

K32

H31

G33

J33

H32

D33

D32

B28

A28

A21

B20

B16

A15

C22

B22

A22

A23

N33

P32

L32

M33

U21C

U21C

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_DQS_H8

MB_DQS_L8

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_CLK_H7

MB_CLK_L7

MB_CLK_H6

MB_CLK_L6

MB_CLK_H5

MB_CLK_L5

MB_CLK_H4

MB_CLK_L4

MB_CLK_H3

MB_CLK_L3

MB_CLK_H2

MB_CLK_L2

MB_CLK_H1

MB_CLK_L1

MB_CLK_H0

MB_CLK_L0

MB_CKE1

MB_CKE0

MB1_ODT1

MB1_ODT0

MB0_ODT1

MB0_ODT0

MB1_CS_L1

MB1_CS_L0

MB0_CS_L1

MB0_CS_L0

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

FREE|MB_EVENT_L

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

DDR III: CHANNEL B

DDR III: CHANNEL B

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM8

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

AL14

AL16

AN17

AN12

AM12

AM16

AN16

AL18

AN19

AM24

AN24

AM18

AN18

AL22

AN23

AM25

AL26

AN28

AL28

AL24

AN25

AN27

AM28

AM29

AL30

AL32

AL33

AK28

AN29

AM31

AM32

E33

D31

B31

A31

F33

F31

C32

B32

C30

A29

B26

A26

B30

A30

A27

C26

A24

B24

C18

A18

A25

C24

C20

A19

C16

A16

B14

A13

B18

A17

C14

A14

H33

AN15

AN20

AK26

AN31

C33

C28

A20

D14

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_DM7

M_B_DM6

M_B_DM5

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DQ63

AN13

M_B_DQ[0..63 ] (9)

M_B_DM[0..7] ( 9)

05

R287 2.2K/J_4R287 2.2K/J_4

+1.5VSUS

+3V_S5

A A

BIMINI PAGE-60

MEM_GEVEN#(1 5)

5

R291

R291

*10K/F_4

*10K/F_4

4

R289 2.2K/J_4R289 2.2K/J_4

EC-20100306A-04

Q28

Q28

2

MMBT3904LT 1G(40V,0.2A)

MMBT3904LT 1G(40V,0.2A)

13

Q29

Q29

2

MMBT3904LT 1G(40V,0.2A)

MMBT3904LT 1G(40V,0.2A)

13

3

R288

R288

2.2K/J_4

2.2K/J_4

R290

R290

2.2K/J_4

2.2K/J_4

M_A_HOT#

M_B_HOT#

+1.5VSUS

Qua nta Computer Inc .

Qua nta Computer Inc .

Qua nta Computer Inc .

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Docu ment Nu mber

Docu ment Nu mber

Docu ment Nu mber

C

C

C

AMD ASB2 CPU(DDR3 MEM I/F)

AMD ASB2 CPU(DDR3 MEM I/F)

AMD ASB2 CPU(DDR3 MEM I/F)

Date:

06/15/20 10, 10:00 AM

Date:

06/15/20 10, 10:00 AM

Date:

2

06/15/20 10, 10:00 AM

Sheet :

Sheet :

Sheet :

1

of

5 43

of

5 43

of

5 43

Rev.Size

Rev.Size

Rev.Size

< C >

< C >

< C >

Page 6

5

4

3

2

1

+1.5VSUS

CPU H/W MONITOR

C150

C150

0.22U /10V/X5R_4

0.22U /10V/X5R_4

C359

C359

3900 P/25V/X7R_4

3900 P/25V/X7R_4

C361

C361

3900 P/25V/X7R_4

3900 P/25V/X7R_4

CPU_ VDD0_R UN_FB_ L(33 )

CPU_ VDD0_R UN_FB_ H(33)

CPU_ VDDNB_ RUN_ FB_H(33)

CPU_ VDDIO_SU S_FB_H(35)

CPU_ VDDR_S ENSE(34 )

C352

C352

0.01U /25V/X7R_4

0.01U /25V/X7R_4

R273 510/F_ 4R2 73 510/F_4

R146 510/F_ 4R1 46 510/F_4

R145 *Shor t_4R145 * Short_4

W / S= 40 mil / 20 mil

+CPUVD DA

CPUC LKIN

R270

R270

169/F_ 4

169/F_ 4

CPUC LKIN#

T29T29

R265 39 .2/F_4R265 39.2/F_4

CPU_ TEST25_ H_BYPASSCL K_H

CPU_ TEST25_ L_BYPASSCL K_L

CPU_ TEST19_ PLLTEST0

CPU_ TEST18_ PLLTEST1

CPU_ TEST9_ANALOG IN

CPU_ TEST17_ BP3

T35T35

CPU_ TEST16_ BP2

T24T24

CPU_ TEST15_ BP1

CPU_ TEST14_ BP0

CPU_ TEST7_ANALOG _T

T25T25

CPU_ TEST6_D IECRACKMON

T44T44

CPU_ TEST3

T46T46

CPU_ TEST2

T52T52

C151

C151

3300 P/50V/X7R_4

3300 P/50V/X7R_4

CPU_ PWR_GD _L

CPU_ LDT_STOP #_L

CPU_ LDT_R ST#_L

CPU_ ALERT

CPU_ TDI

CPU_ TRST#

CPU_ TCK

CPU_ TMS

CPU_ DBREQ#

CPU_ VLDT_SEN SE

M_VREF

Keep trace from resisor to CPU within 0.6"

keep trace from caps to CPU within 1.2 "

U21D

U21D

A8

VDDA_1

B8

VDDA_2

A6

CLKIN_H

A7

CLKIN_L

D10

PWROK

E9

LDTSTOP_L

F9

RESET_L

AN4

SIC

AN5

SID

AM2

RSVD_SA0

AN3

ALERT_L

AM8

TDI

AL8

TRST_L

AK8

TCK

AN8

TMS

G9

DBREQ_L

D2

VSS_SENSE

E2

VLDT_SENSE

E1

VDD_SENSE

D1

VDDNB_SENSE

D3

VDDIO_SENSE

C2

VDDR_SENSE

A11

M_VREF

M_ZP

AM9

M_ZN_H

M_ZN

AN9

M_ZN_L

A9

BYPASSCLK_H

B9

BYPASSCLK_L

A5

PLLTEST0

B6

PLLTEST1

G8

ANALOGIN

F8

BP3

C8

BP2

D9

BP1

E8

BP0

C6

ANALOG_T

AH7

DIECRACKMON

AK5

GATE0

AJ7

DRAIN0

MISC

MISC

RSVD|CORE_TYPE

THERMDC

THERMDA

THERMTRIP_L

PROCHOT_L

DBRDY

RSVD3

CPU_PRESENT_L

HTREF1

HTREF0

FBCLKOUT_H

FBCLKOUT_L

SCANCLK1

TSTUPD

SCANSHIFTEN

SCANEN

SCANCLK2

PLLCHRZ_H

PLLCHRZ_L

SINGLECHAIN

BURNIN_L

ANALOGOUT

DIG_T

M_TEST

M31

C1

SVC

B2

SVD

AL6

AM5

AK6

AN6

AN7

TDO

H9

AM6

AJ9

V10

V9

B10

A10

AK7

AG8

AK9

AH9

AM7

G11

H11

AJ8

AM4

D7

B5

AG9

AL000786000 / IC OTHER(8P) G786P81U(MSOP) / GMT G786P81U

AL007461013 / IC(8P) ADT7461ARMZ(MSOP) / ADV ADT7461ARMZ

CPU THERM

Thermdc and Thermda should be routed away to VRM,

crystal, etc. Customer should follow the MBDG.

However, Bimini is using TSI so this does not applies to Bimini.

CPU_ CORE_T YPE

CPU_ SVC_R

CPU_ SVD_R

CPU_ THERMDC

CPU_ THERMDA

CPU_ THERMTRIP# _R

CPU_ PROCH OT#_R

CPU_ TDO

CPU_ DBRDY

RSVD3

CPU_ PRESEN T_L

CPU_HTREF1

CPU_HTREF0

CPU_ TEST29_ H_FBCL KOUT_P

CPU_ TEST29_ L_FBCL KOUT_N

CPU_ TEST24_ SCANCLK 1

CPU_ TEST23_ TSTUPD

CPU_ TEST22_ SCANSHIFTE N

CPU_ TEST21_ SCANEN

CPU_ TEST20_ SCANCLK 2

CPU_ TEST28_ H_PLL CHRZ_ P

CPU_ TEST28_ L_PLL CHRZ_ N

CPU_ TEST27_ SINGLEC HAIN

CPU_ TEST26_ BURNIN _L

CPU_ TEST10_ ANALOGOUT

CPU_ TEST8_D IG_T

T81T81

T62T62

R155 44.2/F_4R155 44.2/F_4

R148 44.2 /F_4R148 44.2 /F_4

R274 80.6/F_4R274 80.6/F_4

T31T31

T33T33

T26T26

R178

R178

*200 /J_4

*200 /J_4

1

2

3

5

U11

U11

VCC

DXP

DXN

GND

*G786 P81U

*G786 P81U

MSOP

+3V

OVERT#

+1.5VSUS

R260

R260

0/J_4

0/J_4

SCLK

ALERT#

SDA

R191

R191

300/J_ 4

300/J_ 4

EC-20100424A-02

+3V_THER M

C216

C216

*0.1U /16V/X7R_4

CPU_ THERMDA

CPU_ THERMDC

Thermal IC SMBUS

Address SPEC : 98H

OVERT# Check EC Setting Degree

+1.5VSUS

*0.1U /16V/X7R_4

C214

C214

*100 0P/50V/X7R_ 4

*100 0P/50V/X7R_ 4

THERMTRIP shut down temperature : MAX 125 C

R168

R168

1K/F_4

1K/F_4

T51T51

+CPU_ VLDT

place within 1.5"

Route as 80ohm, diff

route as differential, as short as possible,

testpoint under package

R140 *300 /J_4R140 *300/J_ 4

AMD BIMINI

R147 is installed ONLY when SCAN is enabled , R215, R185 internal ONLY

+CPU_ VLDT

+1.5VSUS

8

7

6

4

R188

R188

*10K/J_ 4

*10K/J_ 4

THERM_S HD#

R173

R173

10K/F_4

10K/F_4

R174

R174

1K/F_4

1K/F_4

R192

R192

*0/J_4

*0/J_4

EC_PR OCHOT# _L

R193

R193

*300 /J_4

*300 /J_4

R185

R185

*10K/J_ 4

*10K/J_ 4

SMBALERT#

+3V

L46

L46

BLM21PG 221SN 1D(22 0,100M,2A)_ 8

+2.5V

D D

EC-20100306A-04

EC-20100306A-05

C393

C393

*22U /6.3V/X5R_8

*22U /6.3V/X5R_8

EC-20100424A-01

CPU_ SIC

CPU_ SID

+1.5VSUS

EC-20100427A-01

C C

EC-20100306A-03

SMBALERT#

Connect with Ther mal Sensor Alert .

+1.5VSUS

R275

R275

1K/F_4

1K/F_4

R276

R276

1K/F_4

1K/F_4

R181

R181

*2K/F_4

*2K/F_4

Q13

Q13

2

*MMBT3904 LT1G(40 V,0.2A)

*MMBT3904 LT1G(40 V,0.2A)

C368

C368

0.01U /25V/X7R_4

0.01U /25V/X7R_4

13

M_VREF

C367

C367

1000 P/50V/X7R_4

1000 P/50V/X7R_4

BLM21PG 221SN 1D(22 0,100M,2A)_ 8

C392

C392

4.7U/6.3 V/X5R_6

4.7U/6.3 V/X5R_6

+1.5VSUS

R169

R169

390/J_ 4

390/J_ 4

CPU (PIN: M_ZN_L )

PLACE THEM CLOSE TO

CPU WITHIN 1"

CPUC LKP_B(14)

CPUC LKN_B(14 )

R189

R189

390/J_ 4

390/J_ 4

C391

C391

4.7U/6.3 V/X5R_6

4.7U/6.3 V/X5R_6

R183

R183

*1K/F_4

*1K/F_4

+1.5VSUS

EC-20100424A-01

CPU_ SIC

R423 0/J_4R423 0/J_4

CPU_ SID

R424 0/J_4R424 0/J_4

R186

R186

*10K/J_ 4

*10K/J_ 4

LM86_S MC

R425 *0/J_4R42 5 * 0/J_4

LM86_S MD

R426 *0/J_4R42 6 * 0/J_4

R184 *0/J_4R184 *0/J_4

R195 330/J _4R195 330/J_4

R172

R172

10K/J_ 4

10K/J_ 4

EC-20100306A-04

201003 25A - MK2 bring up.

When system b ooting, CPU_THERMTRIP # will pull down by SB8 20.

Make the SYS_SHDN# can' t pull HIGH a nd turned off the p ower.

So CPU_THE RMTRIP# & S YS_SHDN# can't connected direct.

Q16

Q16

2

MMBT3904L T1G(40V,0.2 A)

MMBT3904L T1G(40V,0.2 A)

1 3

Q12

Q12

MMBT3904L T1G(40V,0.2 A)

MMBT3904L T1G(40V,0.2 A)

2

1 3

Q14

Q14

*MMBT3904 LT1G(40 V,0.2A)

*MMBT3904 LT1G(40 V,0.2A)

1 3

2

SYS_SHD N#

EC-20100326A-01

R194 0/J_4R19 4 0/J_4

R430 *0/J_ 4R43 0 *0/J_4

EC-20100607A-02

AMD recommand : Connected to CPU P ROCHOT_L pin

a nd pulled up t o CPU_VDDIO (no l evel-shifter needed) .

B ut can't connect wi th thermal sensor.

1 3

+1.5VSUS

1 3

C248

C248

*1U/1 0V/X5R_6

*1U/1 0V/X5R_6

R428

R428

2K/F_4

2K/F_4

2

R429

R429

2K/F_4

2K/F_4

2

Q17

Q17

MMBT3904L T1G(40V,0.2 A)

MMBT3904L T1G(40V,0.2 A)

D27

D27

RB50 1V-40(40 V,0.1A)

RB50 1V-40(40 V,0.1A)

EC-20100607A-01

Q18

Q18

MMBT3904L T1G(40V,0.2 A)

MMBT3904L T1G(40V,0.2 A)

D28

D28

RB50 1V-40(40 V,0.1A)

RB50 1V-40(40 V,0.1A)

PM_THER M# (16)

SYS_SHD N# (22,32,3 7)

CPU_ THERMTRIP# (15)

CPU_ PROCH OT# (14)

EC_PR OCHOT# (29)

MBCLK_ THRM (29 )

MBDATA_THRM (29)

06

POWER

SB820

EC

R61 *Short_4R61 *Short_ 4

VID Override Circuit

+1.5VSUS +1.5V

R114

R114

*1K/J_4

*1K/J_4

CPU_ SVC_R

CPU_ SVD_R

CPU_ PWR_GD

R115 *Shor t_4R115 * Short_4

R113 *Shor t_4R113 * Short_4

R63 *Shor t_4R63 *Short_4

R112 *220 /J_4R112 *220/J_ 4

R109 *220 /J_4R109 *220/J_ 4

R54 *220/J_4R54 *220/J_4

EC-20100614A-01

+1.5V

R59

R59

300/J_ 4

300/J_ 4

CPU_ LDT_STOP #_L

T121T121

3

R108

R108

1K/J_4

1K/J_4

R102

R102

1K/J_4

1K/J_4

R60

R60

300/J_ 4

300/J_ 4

T119T119

EC-20100306A-04

CPU_ SVC (33)

CPU_ SVD (33)

CPU_ PWRGD_ SVID_REG (33)

To CPU VRM

2

+1.5VSUS

R256 1K/F_4R256 1K/F_4

R272 300/J _4R272 300/J_4

R165 1K/F_4R165 1K/F_4

CPU_ TEST21_ SCANEN

CPU_ TEST20_ SCANCLK 2

CPU_ TEST24_ SCANCLK 1

CPU_ TEST22_ SCANSHIFTE N

CPU_ TEST15_ BP1

CPU_ TEST14_ BP0

CPU_DBRDY

CPU_ TEST18_ PLLTEST1

CPU_ TEST19_ PLLTEST0

CPU_ TEST23_ TSTUPD

R166 1K/F_4R166 1K/F_4

R261 1K/F_4R261 1K/F_4

R262 1K/F_4R262 1K/F_4

R167 1K/F_4R167 1K/F_4

R110 *300 /J_4R110 *300/J_ 4

R147 *300 /J_4R147 *300/J_ 4

R144 *300 /J_4R144 *300/J_ 4

R269 1K/F_4R269 1K/F_4

R268 1K/F_4R268 1K/F_4

R164 1K/F_4R164 1K/F_4

Quanta Com pute r I nc.

Quanta Com pute r I nc.

Quanta Com pute r I nc.

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Doc ument Numb er

Doc ument Numb er

Doc ument Numb er

Cus tom

Cus tom

Cus tom

AMD ASB2 CPU(CTRL&DEBUG)

AMD ASB2 CPU(CTRL&DEBUG)

AMD ASB2 CPU(CTRL&DEBUG)

Date:

06/15/2 010, 10 :00 AM

Date:

06/15/2 010, 10 :00 AM

Date:

06/15/2 010, 10 :00 AM

CPU_ TEST26_ BURNIN _L

CPU_ DBREQ#

CPU_ TEST27_ SINGLEC HAIN

Sheet :

Sheet :

Sheet :

1

of

6 43

of

6 43

of

6 43

Rev.Size

Rev.Size

Rev.Size

< C >

< C >

< C >

HDT Connector

Can remove on MP------>LX

VID OVERIDE TABLE (VDD)

BOOT VOLTAGE(VDD)

SVC

SVD

(CPUVRM_PRO#

= VCC/GND)

0 0 1.1 1.1

0 1 1.0 1.2

1 0 0.9 1.0

1 1 0.8 0.8

Note: ( Refer AMD BIMINI schematic )

To override VID,

Remove R192, R194, R196, install R165

set VID via SW100

CPU_ LDT_STOP #(11,1 4)

(CPUVRM_PRO#

= OPEN)

CPU_ DBREQ#

CPU_ DBRDY

CPU_ TCK

CPU_ TMS

CPU_ TDI

CPU_ TRST#

CPU_ TDO

C390

C390

*0.1U /10V/X7R_4

*0.1U /10V/X7R_4

+1.5VSUS

5

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

KEY

KEY

CN18

CN18

*HDT C ONN

*HDT C ONN

25

CPU_ LDT_R ST_HTPA#

Q11

Q11

*MMBT3904 LT1G(40 V,0.2A)

*MMBT3904 LT1G(40 V,0.2A)

EC-20100306A-03

+1.5VSUS+3V

R180

R180

R162

R162

*10K/F_ 4

*10K/F_ 4

*1K/F_4

*1K/F_4

CNTR_VREF

2

1 3

CPU_ LDT_R ST#

+1.5V

R55

R55

300/J_ 4

300/J_ 4

CPU_ LDT_R ST#(14) CPU_ PWR_GD(14)

EC-20100306A-04

EC-20100426A-02 EC-20100426A-02

CPU_ LDT_R ST#_L CPU_ PWR_GD _L

T120T120

4

B B

A A

Page 7

5

4

3

2

1

07

+CPU_VLDT+1.1V

U21H

+VCORE +VCORE

D D

C C

+CPU_VLDT

+CPU_VLDT

B B

+0.9V

D4

D5

D6

E5

E6

E7

F5

F6

F7

H7

H8

J8

E4

J10

J12

J14

J18

J20

J21

J23

J9

K10

K12

K14

K18

K20

K21

K23

N4

L11

L13

L7

L9

M10

M12

R4

M5

N11

N24

N9

P15

P18

C163

C163

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C203

C203

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

U21E

U21E

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40W4VDD_46

VDD_41

VDD_42

VDD_43

C204

C204

0.22U/10V/X5R_4

0.22U/10V/X5R_4

AE12

VDD_85

AD9

VDD_84

AE21

VDD_83

AD21

VDD_82

AD18

VDD_81

AD14

VDD_80

AD12

VDD_79

AD11

VDD_78

AC5

VDD_77

AE18

VDD_76

AC24

VDD_75

AC12

VDD_74

AC10

VDD_73

AB13

VDD_72

AB11

VDD_71

AE14

VDD_70

AA24

VDD_69

AA12

VDD_68

AA10

VDD_67

Y19

VDD_66

Y16

VDD_65

Y14

POWER1

POWER1

VDD_64

W5

VDD_63

W20

VDD_62

W18

VDD_61

W15

VDD_60

AE23

VDD_59

V24

VDD_58

V19

VDD_57

V16

VDD_56

V14

VDD_55

T20

VDD_54

T18

VDD_53

T15

VDD_52

T10

VDD_51

R5

VDD_50

R19

VDD_49

R16

VDD_48

R14

VDD_47

AC4

P24

VDD_45

P20

VDD_44

C206

C206

0.01U/25V/X7R_4

0.01U/25V/X7R_4

Check placement requirement.

C171

C192

C192

10U/6.3V/X5R_8

10U/6.3V/X5R_8

C171

10U/6.3V/X5R_8

10U/6.3V/X5R_8

+1.5VSUS

C198

C198

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C182

C182

10U/6.3V/X5R_8

10U/6.3V/X5R_8

AG30

AG32

AA30

AB28

AE32

AC30

AC32

AE26

AE30

AF28

AD25

AA25

AC25

AB25

M27

Y26

U26

N32

U32

N30

P29

R28

R30

R32

U29

U30

W28

W30

W32

Y29

V25

P25

N25

M25

K25

Y25

U21F

U21F

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

VDDIO_5

VDDIO_6

VDDIO_7

VDDIO_8

VDDIO_9

VDDIO_10

VDDIO_11

VDDIO_12

VDDIO_13

VDDIO_14

VDDIO_15

VDDIO_16

VDDIO_17

VDDIO_18

VDDIO_19

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

VDDIO_30

VDDIO_31

VDDIO_32

VDDIO_33

VDDIO_34

L25

VDDIO_35

T25

VDDIO_36

VDDIO_37

VDDIO_38

Place close to socket

POWER2

POWER2

C196

C196

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C127

C127

22U/6.3V/X5R_8

22U/6.3V/X5R_8

R111 *Short_8R111 *Short_8

VLDT_A_1

VLDT_A_2

VLDT_A_3

VLDT_A_4

VLDT_B_1

VLDT_B_2

VLDT_B_3

VLDT_B_4

VDDR_1

VDDR_2

VDDR_3

VDDR_4

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

PROGEN_L

FREE_1

FREE_2

FREE_3

FREE_4

FREE_5

FREE_6

FREE_7

FREE_8

FREE_9

F1

F2

F3

F4

AL1

AL2

AL3

AL4

A12

B12

C12

D12

AK10

AL10

AM10

AN10

+VDDNB_CPU

A3

A4

B3

B4

C3

C4

B11

G7

B7

AH8

AJ6

B25

AM3

AN11

P9

P8

C153

C153

180P/50V/NPO_4

180P/50V/NPO_4

C155

C155

0.22U/10V/X5R_4

0.22U/10V/X5R_4

+0.9V

Characteristic

VLDT

VDD -0.3V to 1.575V

VDDNB

VTT -0.3V to 1.1V

VDDIO -0.3V to 2.2V

VDDR -0.3V to 1.5V

VDDA -0.3V to 3.0V

M_VREF -0.3V to VDDIO + 0.3V

DDR3 Power Sequencing

Group Definitions

Power Group A Power Group B

VDDIO

VDDA

+1.1V or +1.2V => CPU_VLDT

+0.9V => CPU_VDDR

+1.5V_SUS => CPU_VDDIO_SUS

CPU_VCORE => CPU_VDD_RUN

C157

C157

180P/50V/NPO_4

180P/50V/NPO_4

MAX Range

-0.3V to 1.5V

-0.3V to 1.575V

VDD

VDDNB

VLDT

VDDR

+VCORE

C170

C170

22U/6.3V/X5R_8

22U/6.3V/X5R_8

U21G

U21G

B1

VSS_1

N2

VSS_28

N22

VSS_29

N23

VSS_30

B13

VSS_2

B15

VSS_3

B17

VSS_4

M21

VSS_27

B19

VSS_5

B21

VSS_6

B23

VSS_7

B27

VSS_8

B29

VSS_9

B33

VSS_10

C10

VSS_11

P10

VSS_31

P14

VSS_32

P16

VSS_33

P19

VSS_34

P7

VSS_35

C31

VSS_12

D11

VSS_13

D13

VSS_14

D15

VSS_15

R1

VSS_36

D17

VSS_16

D19

VSS_17

D21

VSS_18

D23

VSS_19

D25

VSS_20

D27

VSS_21

R15

VSS_37

R18

VSS_38

R2

VSS_39

R20

VSS_40

D29

VSS_46

D30

VSS_47

D8

VSS_48

E30

VSS_49

E32

VSS_50

F14

VSS_51

F17

VSS_52

R8

VSS_53

T14

VSS_54

T16

VSS_55

F20

VSS_56

T19

VSS_57

T24

VSS_58

T9

VSS_59

U1

VSS_60

F23

VSS_61

N1

VSS_62

G1

VSS_63

G19

VSS_64

G2

VSS_65

G25

VSS_66

G27

VSS_67

N10

VSS_115

ASB2-1021

ASB2-1021

C180

C180

22U/6.3V/X5R_8

22U/6.3V/X5R_8

GND1

GND1

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

C186

C186

22U/6.3V/X5R_8

22U/6.3V/X5R_8

VSS_45

VSS_44

VSS_43

VSS_42

VSS_26

VSS_25

VSS_41

VSS_24

VSS_23

VSS_22

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

W19

W1

V20

V18

M11

L8

V15

L4

L30

L26

L24

L23

L22

L21

L2

L12

L10

L1

K9

M6

K24

K22

K16

M22

K13

M24

K11

M23

J7

W16

J4

W14

J32

J30

M13

J28

U8

J25

U4

J24

U7

U2

J2

J16

J13

J11

J1

H6

H5

H28

H23

H20

J22

M9

G4

G30

N12

BOTTOM SIDE DECOUPLING

C162

C167

C167

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C162

0.22U/10V/X5R_4

0.22U/10V/X5R_4

U21H

AM19

VSS_207

AF7

VSS_167

AF26

VSS_166

AE7

VSS_165

AF8

VSS_168

AF9

VSS_169

AG1

VSS_170

AG2

VSS_171

AG27

VSS_172

AG4

VSS_173

AG5

VSS_174

AG6

VSS_175

AG7

VSS_176

AE4

VSS_164

AE25

VSS_163

AE24

VSS_162

AE22

VSS_161

AE20

VSS_160

AE2

VSS_159

AE16

VSS_158

AE13

VSS_157

AH14

VSS_177

AE11

VSS_156

AE10

VSS_155

AE1

VSS_154

AD24

VSS_153

AD23

VSS_152

AD22

VSS_151

AH20

VSS_178

AH23

VSS_179

AH25

VSS_180

AH28

VSS_181

AD20

VSS_150

AD16

VSS_149

AD13

VSS_148

AD10

VSS_147

AC9

VSS_146

AC8

VSS_145

VSS_214A2VSS_215

AC23

VSS_144

AH5

VSS_182

AJ1

VSS_183

AJ15

VSS_184

W2

VSS_116

A32

VSS_213

W8

VSS_117

Y10

VSS_118

Y15

VSS_119

Y18

VSS_120

AJ19

VSS_185

AJ2

VSS_186

AJ22

VSS_187

AJ4

VSS_188

Y20

VSS_121

Y24

VSS_122

AK11

VSS_189

AK13

VSS_190

Y7

VSS_123

AA1

VSS_124

AA11

VSS_125

ASB2-1021

ASB2-1021

C197

C197

0.01U/25V/X7R_4

0.01U/25V/X7R_4

AK15

VSS_191

AK17

VSS_192

AK19

VSS_193

AK21

VSS_194

AA2

VSS_126

AA22

VSS_127

AA23

VSS_128

AK23

VSS_195

AA4

VSS_129

AA9

VSS_130

AB10

VSS_131

AB12

VSS_132

AB21

VSS_133

AB22

VSS_134

AB23

VSS_135

AB24

VSS_136

AK25

VSS_196

AK27

VSS_197

AK29

VSS_198

AJ5

VSS_199

AH6

VSS_200

AL31

VSS_201

AM1

VSS_202

AM13

VSS_203

AB7

VSS_137

AC1

VSS_138

AM15

VSS_205

AM17

VSS_206

AC11

VSS_139

AC13

VSS_140

GND2

GND2

AC2

VSS_141

AC21

VSS_142

AC22

VSS_143

AM23

VSS_208

AM27

VSS_209

AM33

VSS_210

AN2

VSS_211

AN32

VSS_212

AM11

C164

C156

C156

180P/50V/NPO_4

180P/50V/NPO_4

C164

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C360

C360

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

+0.9V

C378

C378

1000P/50 V/X7R_4

1000P/50 V/X7R_4

+1.5VSUS

A A

+1.5VSUS

C169

C169

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C190

C190

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C382

C382

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C374

C374

1000P/50 V/X7R_4

1000P/50 V/X7R_4

C381

C381

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C148

C148

1000P/50 V/X7R_4

1000P/50 V/X7R_4

C202

C202

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C173

C173

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C366

C366

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C354

C354

1000P/50 V/X7R_4

1000P/50 V/X7R_4

C195

C195

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C160

C160

0.01U/25V/X7R_4

0.01U/25V/X7R_4

C357

C356

C356

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C363

C363

180P/50V/NPO_4

180P/50V/NPO_4

C184

C184

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C205

C205

0.01U/25V/X7R_4

0.01U/25V/X7R_4

C362

C362

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C149

C149

180P/50V/NPO_4

180P/50V/NPO_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS PO SSIBLE

C166

C166

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C177

C177

180P/50V/NPO_4

180P/50V/NPO_4

C357

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C375

C375

180P/50V/NPO_4

180P/50V/NPO_4

C161

C161

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C165

C165

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C365

C365

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C152

C152

180P/50V/NPO_4

180P/50V/NPO_4

C183

C183

0.1U/10V/X7R_4

0.1U/10V/X7R_4

PROCESSOR POWER AND GROUND

5

4

3

+VCORE

+1.5VSUS

+VDDNB_CPU

C187

C187

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C185

C185

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C350

C350

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C181

C181

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C168

C168

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C349

C349

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C194

C194

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C175

C175

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C351

C351

22U/6.3V/X5R_8

22U/6.3V/X5R_8

2

C193

C193

22U/6.3V/X5R_8

22U/6.3V/X5R_8

C176

C176

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C159

C159

0.22U/10V/X5R_4

0.22U/10V/X5R_4

C158

C158

180P/50V/NPO_4

180P/50V/NPO_4

C199

C199

0.01U/25V/X7R_4

0.01U/25V/X7R_4

C200

C200

180P/50V/NPO_4

180P/50V/NPO_4

Qua nta Computer Inc .

Qua nta Computer Inc .

Qua nta Computer Inc .

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Docu ment Nu mber

Docu ment Nu mber

Docu ment Nu mber

C

C

C

AMD ASB2 CPU(PWR&GND)

AMD ASB2 CPU(PWR&GND)

AMD ASB2 CPU(PWR&GND)

Date:

06/14/20 10, 04:47 PM

Date:

06/14/20 10, 04:47 PM

Date:

06/14/20 10, 04:47 PM

C201

C201

180P/50V/NPO_4

180P/50V/NPO_4

C191

C191

10U/6.3V/X5R_8

10U/6.3V/X5R_8

1

Sheet :

Sheet :

Sheet :

C154

C154

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C174

C174

10U/6.3V/X5R_8

10U/6.3V/X5R_8

7 43

7 43

7 43

Rev.Size

Rev.Size

Rev.Size

< C >

< C >

< C >

of

of

of

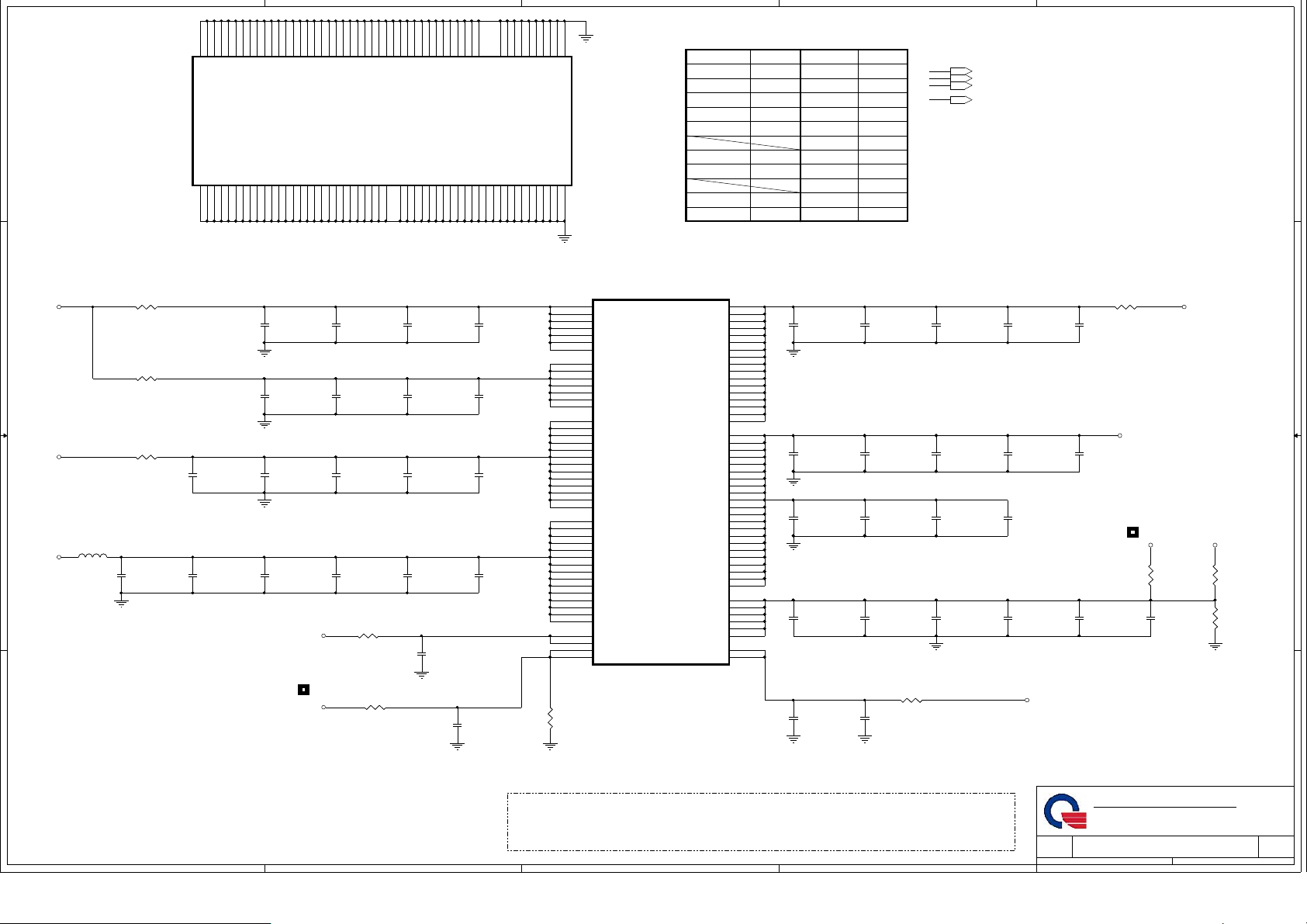

Page 8

1

2

3

4

5

6

7

8

08

CN20A

M_A_A[0..15](5)

A A

M_A_BS[0..2](5)

M_A_CS#0(5)

M_A_CS#1(5)

M_A_CLKP0(5)

M_A_CLKN0(5)

M_A_CLKP1(5)

M_A_CLKN1(5)

M_A_CKE0( 5)

M_A_CKE1( 5)

M_A_CAS#( 5)

M_A_RAS#( 5)

R206 10K/F_4R206 10K/F_4

R207 10K/F_4R207 10K/F_4

B B

M_A_WE#(5)

PCLK_SMB(3 ,9,15,26)

PDAT_SMB(3,9 ,15,26)

M_A_ODT0(5)

M_A_ODT1(5)

M_A_DM[0..7](5)

M_A_DQSP[7:0](5)

M_A_DQSN[7:0](5)

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CS#0

M_A_CS#1

M_A_CLKP0

M_A_CLKN0

M_A_CLKP1

M_A_CLKN1

M_A_CKE0

M_A_CKE1

M_A_CAS#

M_A_RAS#

M_A_WE#

DIMM0_SA0

DIMM0_SA1

PCLK_SMB

PDAT_SMB

M_A_ODT0

M_A_ODT1

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

BUS1_A2

+1.5VSUS

C C

C419

C419

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C421

C421

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C423

C423

0.1U/10V/X7R_4

0.1U/10V/X7R_4

CN20A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

CONN_DDR3_RVS

CONN_DDR3_RVS

C422

C422

0.1U/10V/X7R_4

0.1U/10V/X7R_4

(204P)

(204P)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

C426

C426

0.1U/10V/X7R_4

0.1U/10V/X7R_4

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

M_A_DQ0

5

DQ0

M_A_DQ1

7

DQ1

M_A_DQ7

15

DQ2

M_A_DQ3

17

DQ3

M_A_DQ4

4

DQ4

M_A_DQ5

6

DQ5

M_A_DQ6

16

DQ6

M_A_DQ2

18

DQ7

DQ8

DQ9

M_A_DQ8

21

M_A_DQ9

23

M_A_DQ14

33

M_A_DQ11

35

M_A_DQ13

22

M_A_DQ12

24

M_A_DQ10

34

M_A_DQ15

36

M_A_DQ20

39

M_A_DQ21

41

M_A_DQ22

51

M_A_DQ23

53

M_A_DQ17

40

M_A_DQ16

42

M_A_DQ18

50

M_A_DQ19

52

M_A_DQ24

57

M_A_DQ29

59

M_A_DQ27

67

M_A_DQ26

69

M_A_DQ28

56

M_A_DQ25

58

M_A_DQ31

68

M_A_DQ30

70

M_A_DQ36

129

M_A_DQ37

131

M_A_DQ39

141

M_A_DQ34

143

M_A_DQ32

130

M_A_DQ33

132

M_A_DQ38

140

M_A_DQ35

142

M_A_DQ41

147

M_A_DQ45

149

M_A_DQ43

157

M_A_DQ42

159

M_A_DQ44

146

M_A_DQ40

148

M_A_DQ46

158

M_A_DQ47

160

M_A_DQ48

163

M_A_DQ49

165

M_A_DQ54

175

M_A_DQ50

177

M_A_DQ53

164

M_A_DQ52

166

M_A_DQ51

174

M_A_DQ55

176

M_A_DQ60

181

M_A_DQ61

183

M_A_DQ63

191

M_A_DQ62

193

M_A_DQ56

180

M_A_DQ57

182

M_A_DQ58

192

M_A_DQ59

194

M_A_DQ[0..63 ] (5)

+1.5VSUS

+3V

C257

C257

0.1U/10V/X7R_4

0.1U/10V/X7R_4

MEM_A_HOT#

M_A_HOT#(5)

M_A_RST#(5 )

+0.75VSMVREF_DIM(9)

R211 *Short_4R211 *Short_4

C418

C418

0.01U/25V/X7R_4

0.01U/25V/X7R_4

CN20B

CN20B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

CONN_DDR3_RVS

CONN_DDR3_RVS

+DDR_VREF_DIMM

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

(204P)

(204P)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

VTT1

VTT2

GND

205

R200

R200

*Short_6

*Short_6

C264

C264

470P/50V/X7R_4

470P/50V/X7R_4

GND

206

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

+1.5VSUS

R196

R196

*10K/F_4

*10K/F_4

R198

R198

*10K/F_4

*10K/F_4

C291

C291

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

+0.75VSMVREF_DIM (9 )

C277

C277

0.1U/10V/X7R_4

0.1U/10V/X7R_4

+0.75V_DDR_ VTT

C278

C278

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

+1.5VSUS

+1.5VSUS

C427

C213

C416

C416

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

Power supply : 1.5V +/- 0.075V. The component VDD and VDDQ are connected to the module VDD.

VDD

VDDSPD

VREFCA

D D

Temperature sensor/SPD EEPROM power supply : +3.0V to +3.6V.

Reference voltage : Control, command, and address (VDD/2).

Termination reference current from VTT

Ivtt

Termination reference voltage (DC)

VTT

- command / address bus

1

C417

C417

4.7U/6.3V/X5R_6

4.7U/6.3V/X5R_6

C213

2.2U/6.3V/X5R_6

2.2U/6.3V/X5R_6

C246

C246

2.2U/6.3V/X5R_6

2.2U/6.3V/X5R_6

-600

0.49 * VDD -20mV 0.5 * VDD 0.51 * VDD + 20mV

2

C427

1U/6.3V/X5R_4

1U/6.3V/X5R_4

---

3

C420

C420

1U/6.3V/X5R_4

1U/6.3V/X5R_4

+600 mA

V

C226

C226

1U/6.3V/X5R_4

1U/6.3V/X5R_4

4

+1.5VSUS

C424

C424

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C220

C220

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C425

C425

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C234

C234

0.1U/10V/X7R_4

0.1U/10V/X7R_4

5

C215

C215

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C242

C242

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C217

C217

0.1U/10V/X7R_4

0.1U/10V/X7R_4

C253

C253

0.1U/10V/X7R_4

0.1U/10V/X7R_4

+0.75V_DDR_ VTT

C283

C283

0.22U/10V/X5R_4

C238

C238

0.1U/10V/X7R_4

0.1U/10V/X7R_4

6

0.22U/10V/X5R_4

SM_MEM BUS ADDRESS

SO-DIMM0 1010 000

SO-DIMM1

Date:

Date:

Date:

7

1010 001

C282

C282

0.22U/10V/X5R_4

0.22U/10V/X5R_4

Qua nta Computer Inc .

Qua nta Computer Inc .

Qua nta Computer Inc .

PROJECT : PS2A

PROJECT : PS2A

PROJECT : PS2A

Docu ment Nu mber

Docu ment Nu mber

Docu ment Nu mber

C

C

C

DDR3 SO-DIMM(200P)