Page 1

1

2

3

4

5

6

7

8

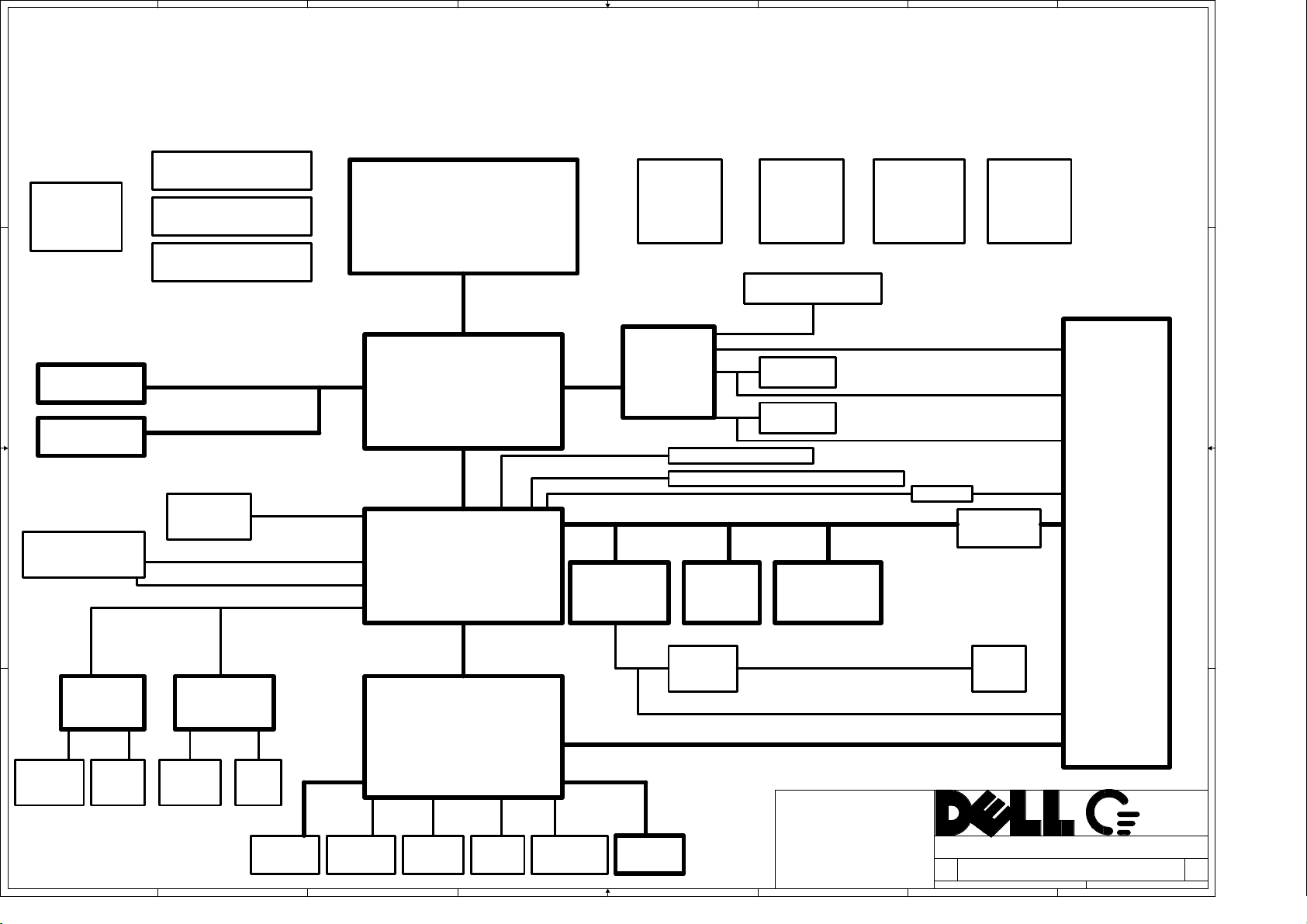

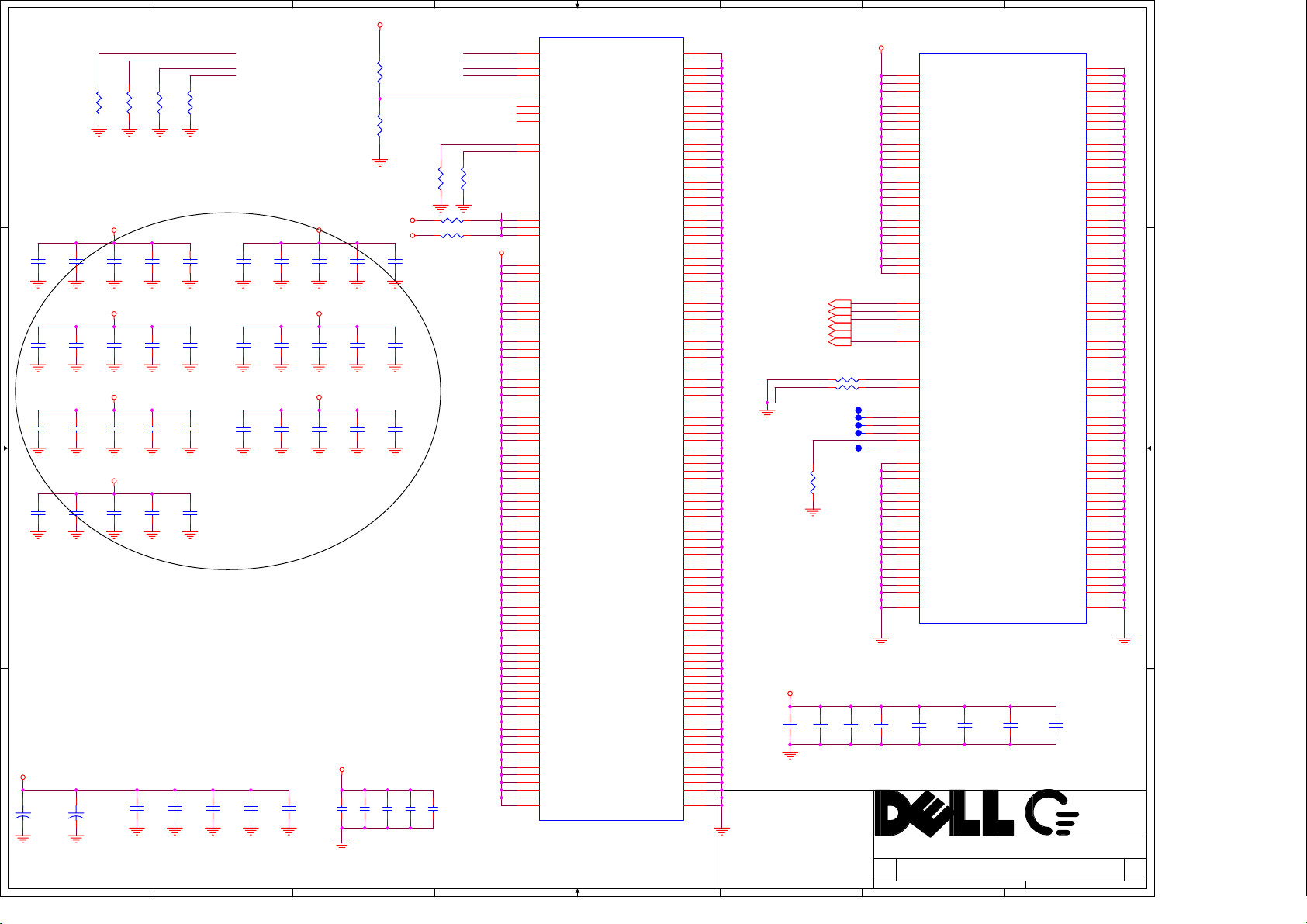

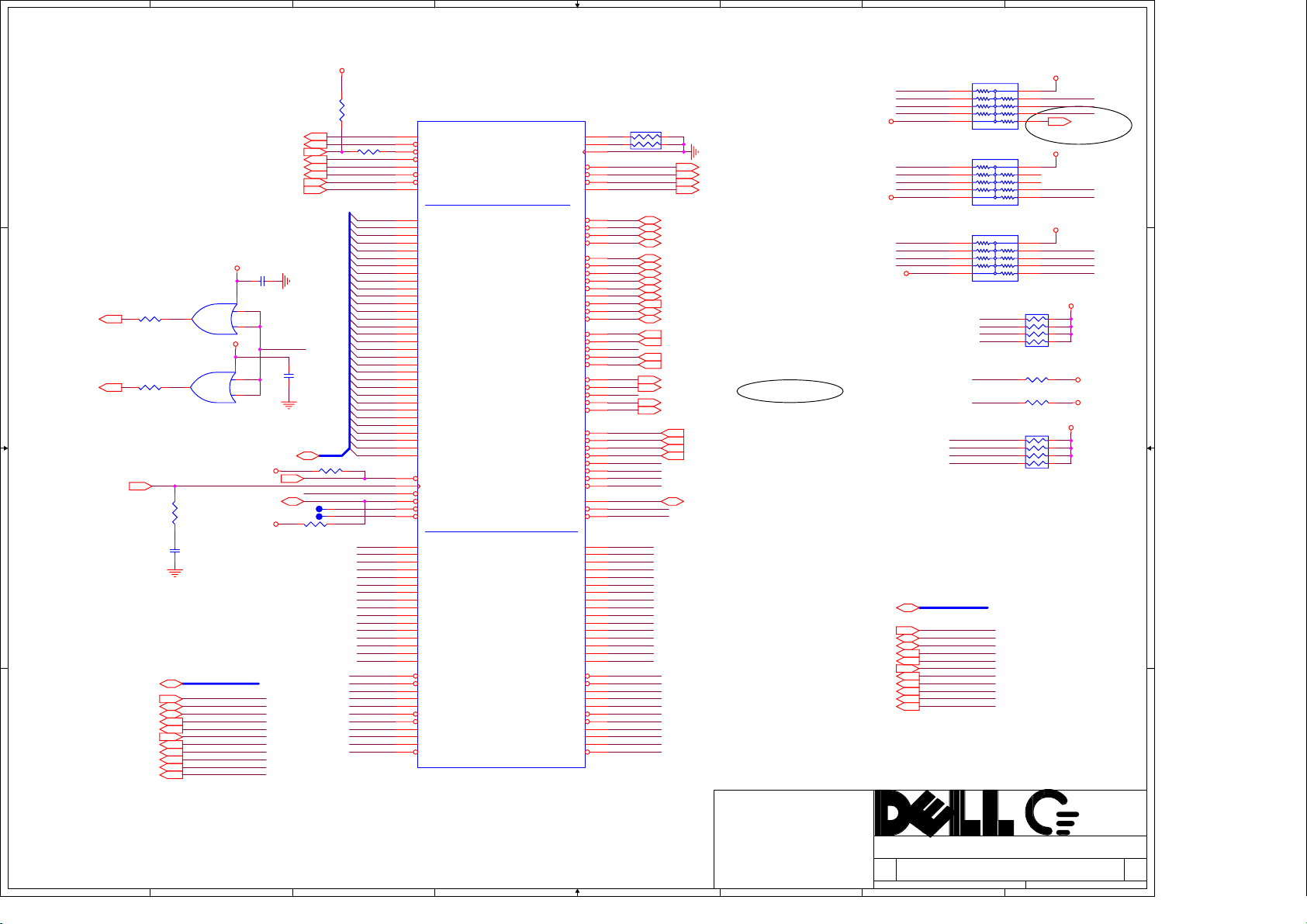

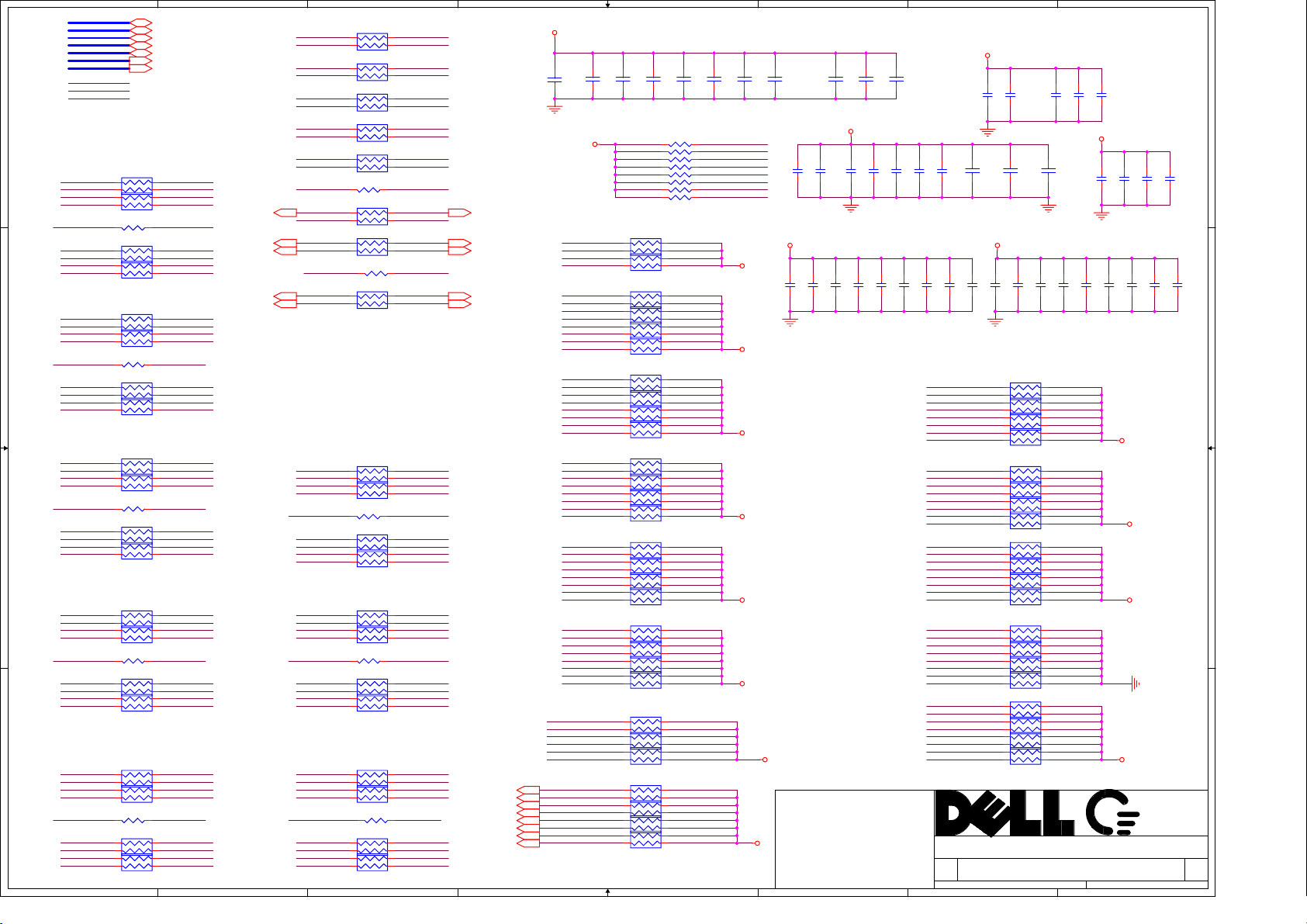

BONDI II

A A

RUN POWER

SW

PG 47

AC/BATT

CONNECTOR

BATT

SELECTOR

BATT

CHARGER

PG 49

PG 41

PG 42

Banias

(Micro-FCPGA)

PG 4,5

DC/DC

PG 46

PWA:4U853, Rev A04

SCH: 7U239, Rev A03

CPU VR

PG 43

CLOCKS

PG 14

RESET CKT

PG 40

Panel Connector

LVDS

PG 23PG 35

PG 18

S-Video

PG 31(IO)

VGA

PG 19

PG 31(IO)

PG 30(Bluetooth)

33MHZ, 3.3V PCI

CARDBUS

OZ711EC1

DVI

PG 22

1 Port

Q-SWITCH

PG 38

DOCKING

CONNECTOR

PG 39

4X100MHZ

B B

ODEM

DDR-SODIMM1

266/200 MHZ DDR

PG 12,13

266/200 MHZ DDR

DDR-SODIMM2

PG 12,13

66(266)MHZ, 1.8V

HUB I/F

IDE1 - HDD

ATA 66/100

PG 20

Internal Media Bay

C C

CD-ROM

PG 20

USB2.0 1 port

ATA 66/100

AC97

MCH-M

593 Micro-FCBGA

PG 6,7, 8

ICH4-M

421 BGA

PG 9,10,11

AGP

BroadCom

Lan(5702)

Video

Controller

PG 15,16,17

2 Rear Ports

1 Port for Bluetooth.

MINI-PCI

Wireless LAN

Bluetooth

LPC

AUDIO

PG 33,34

MDC

PG 24

SIO(Macallen)

256 Pins LBGA

S/PDIF to

DOCK

D D

PG 39

Audio

Jacks

PG 34

RJ11 to

DOCK

PG 39

Tip

Ring

PG 24

PG 25,26

X-Bus

PS/2

IrDA

PG 37

1

2

Keyboard

PG 26

Serial

PG 27

3

Parallel

PG 28

Touchpad/

Stick point

PG 30

4

Flash

PG 29

Magnetics

PG 36

5

DOCK LPC

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

6

RJ45

PG 36

QUANTA

Title

Schematic Block Diagram1

Size Document Number Rev

JM2 3K

B

星期五, 六月

Date: Sheet

06, 2003

7

COMPUTER

of

149

8

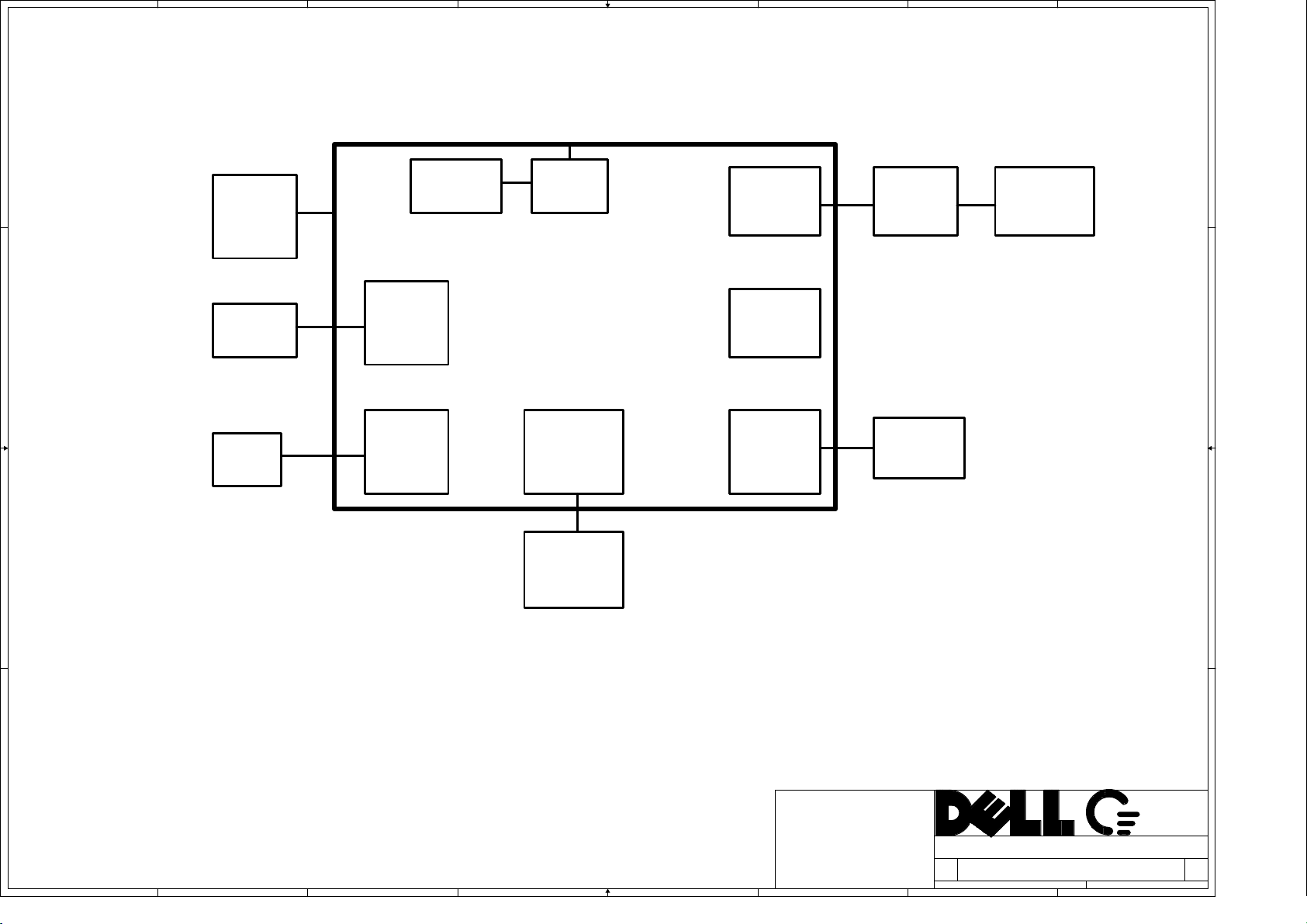

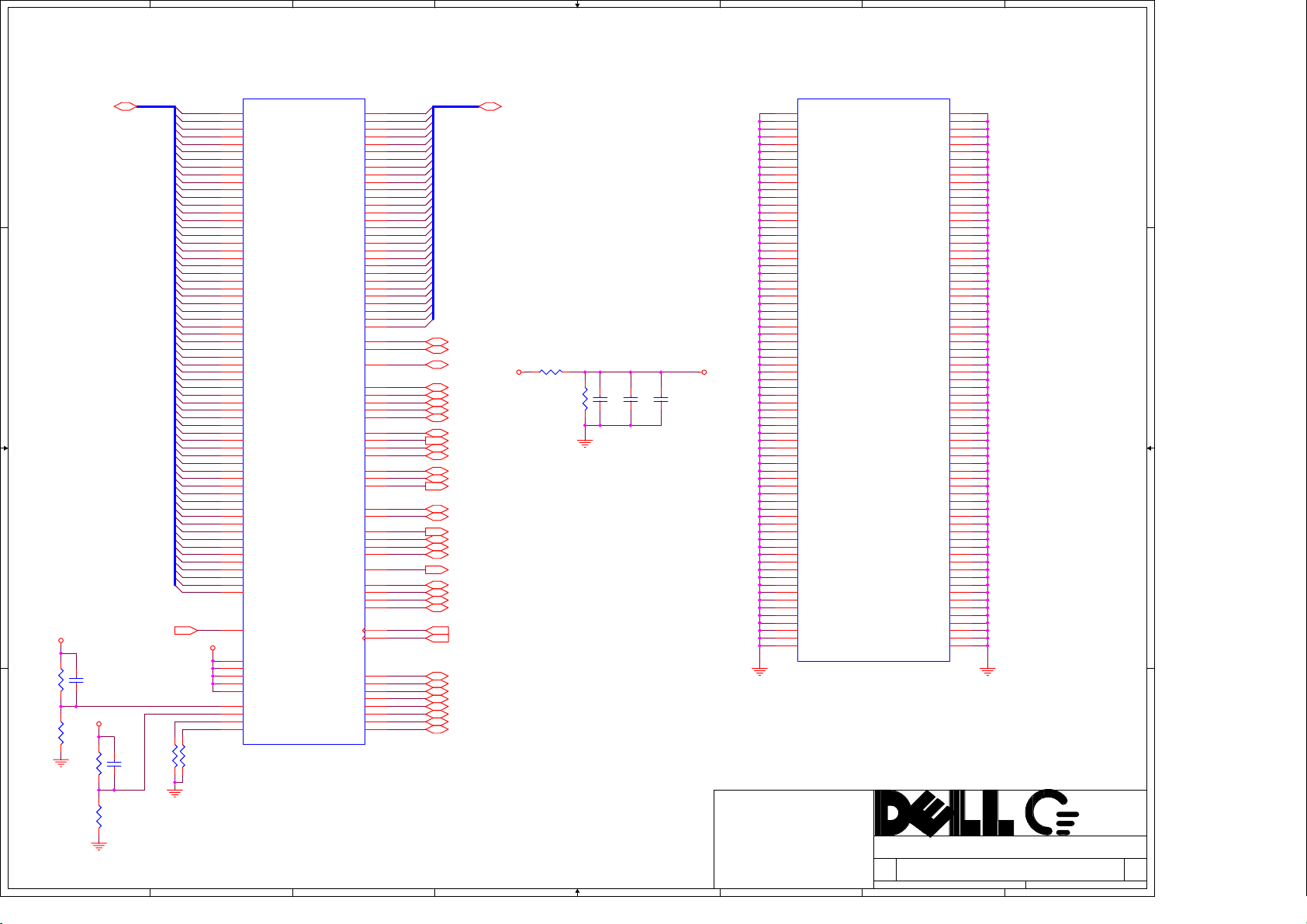

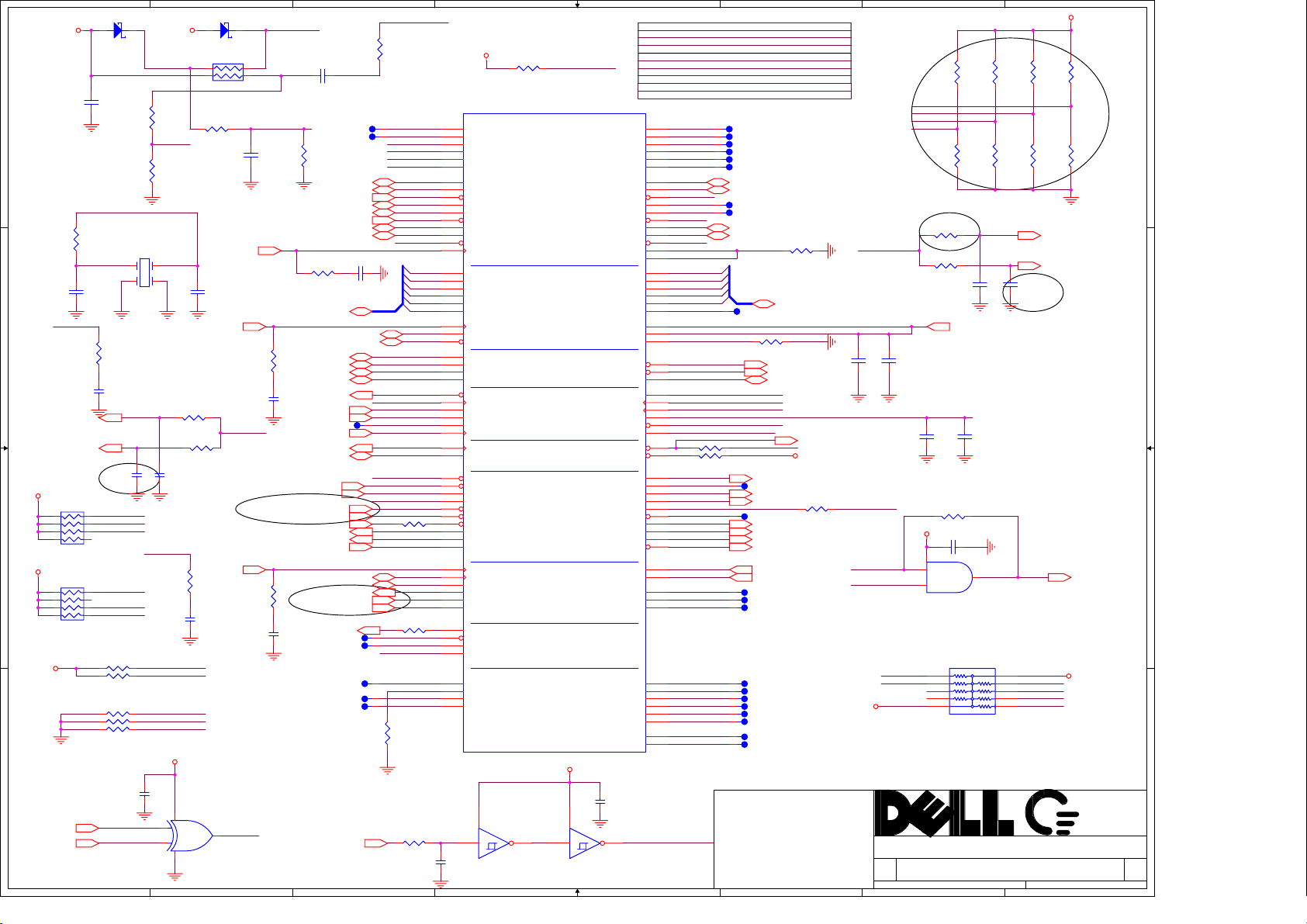

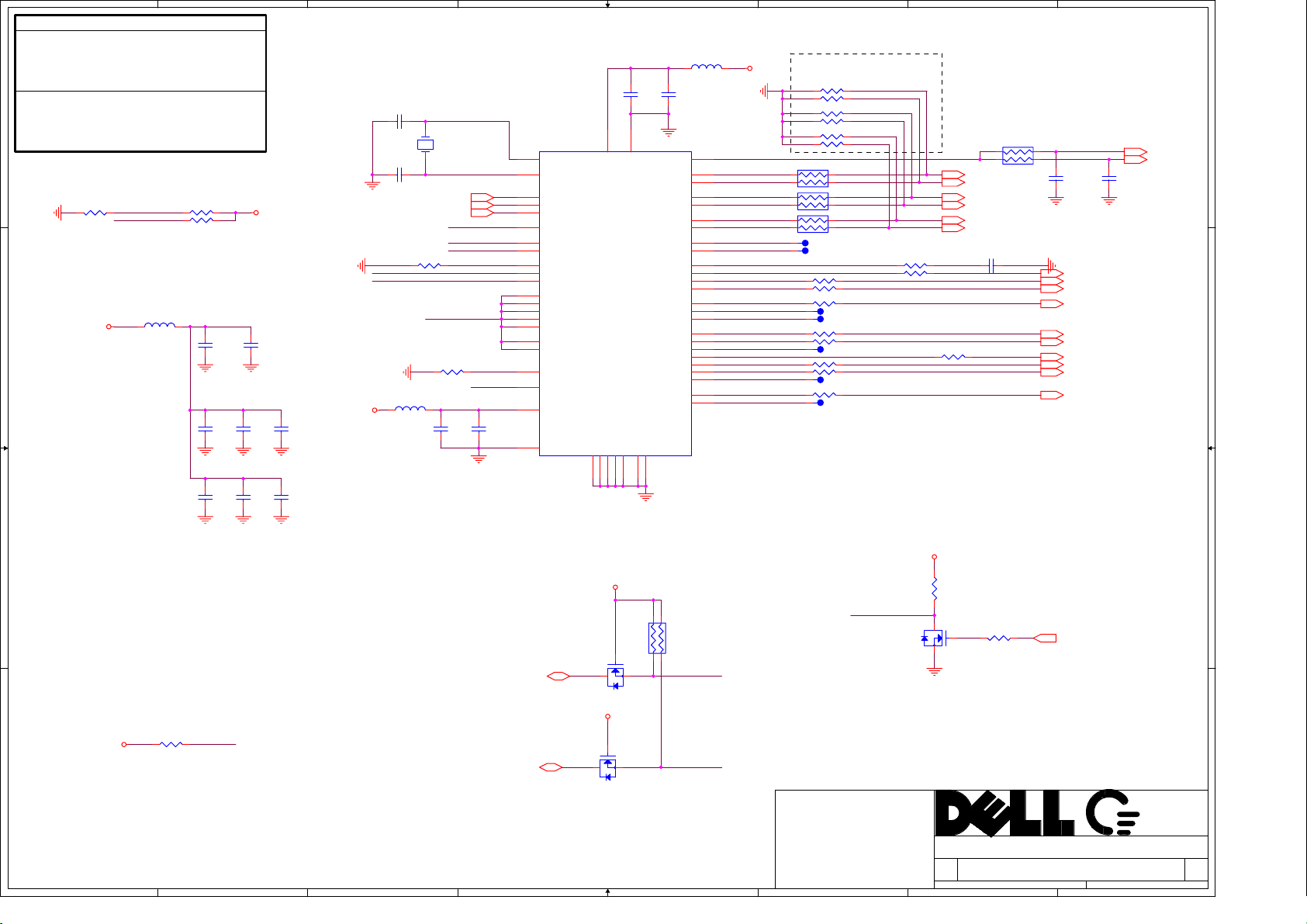

Page 2

1

A A

2

3

4

5

6

7

8

Embed 16MB

Spread

Spectrum

Video RAM

PG 18

DAC1

VGA

B B

Connector

PG 19

(CRT)

Interface

ATI Mobility

M7D/M9CSP32 Core Logic

Memory

Interface

Integrated

TMDS

Interface

External

TMDS

Interface

DOCK

Connector

PG 39

DVI Connector

in DOCK

PG 4, 5

DAC2

S-Video

(TV/CRT2))

Interface

PG 31

C C

Power &

Ground

Interface

Voltage

Regulation

PCI/AGP

LVDS

GPIOs

LCD Connector

PG 18

PG 48

D D

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

1

2

3

4

5

Dell's express written consent."

6

Title

Schematic Block Diagram2

Size Document Number Rev

JM2 1A

B

星期五, 六月

Date: Sheet

06, 2003

7

QUANTA

COMPUTER

of

249

8

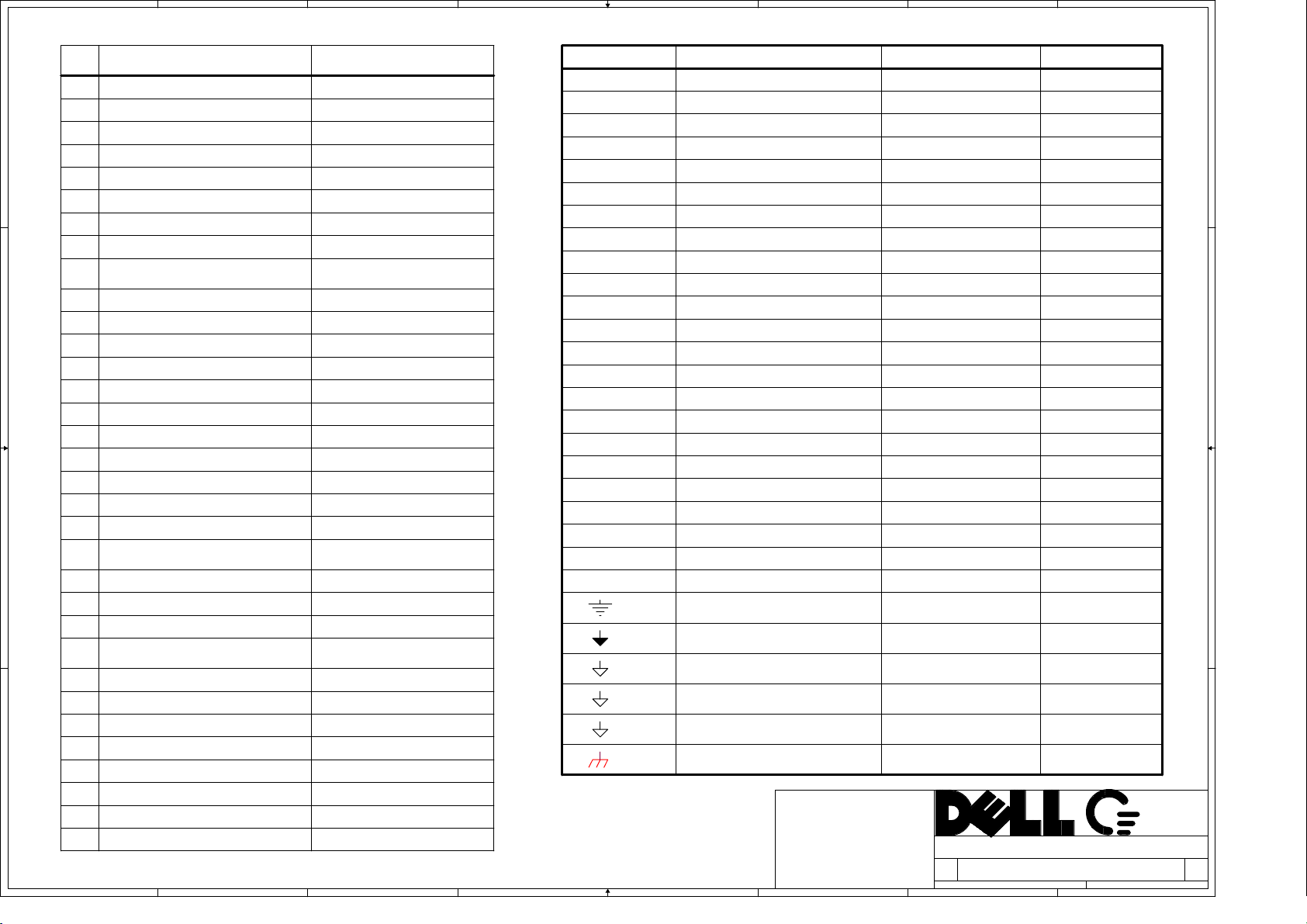

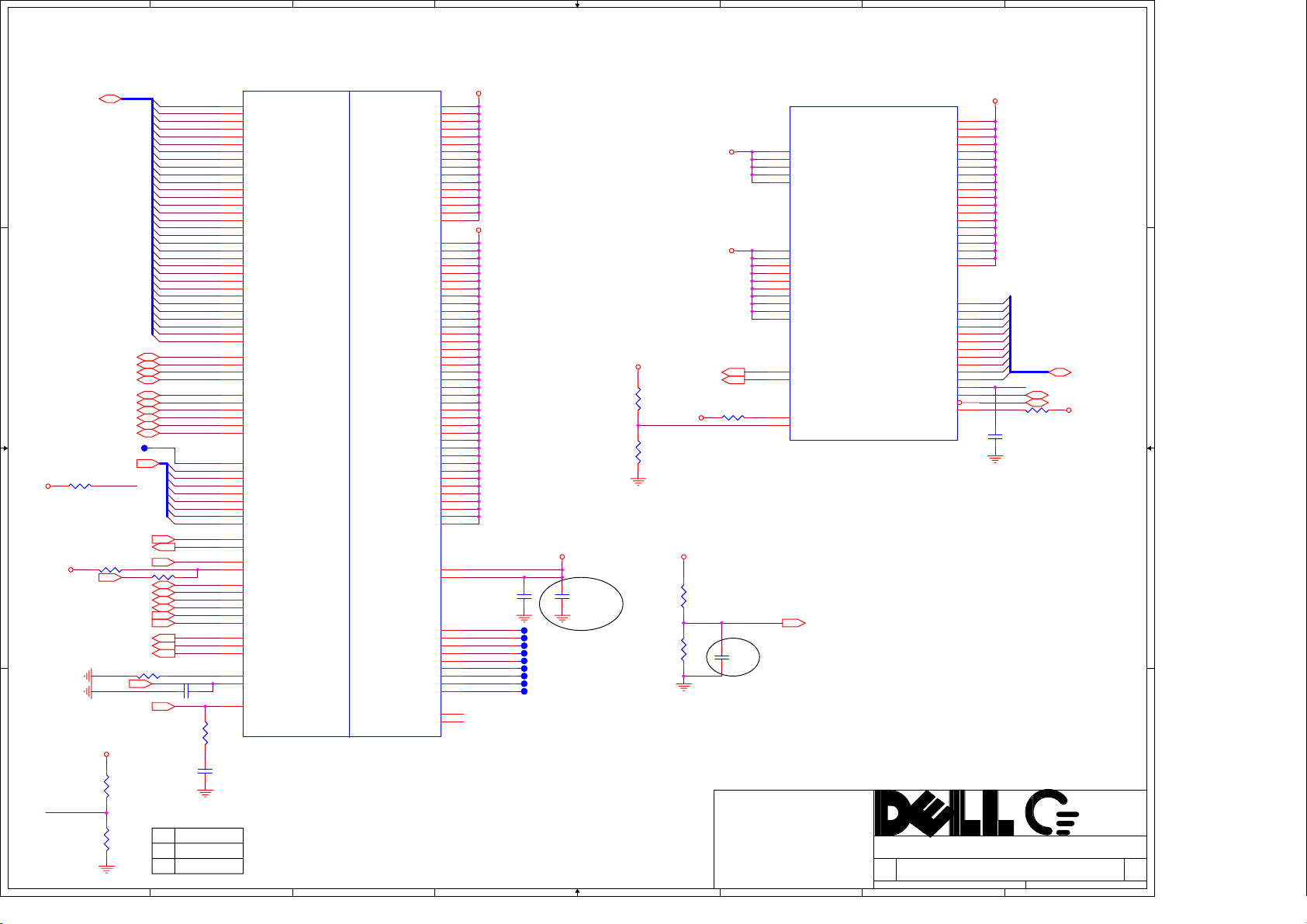

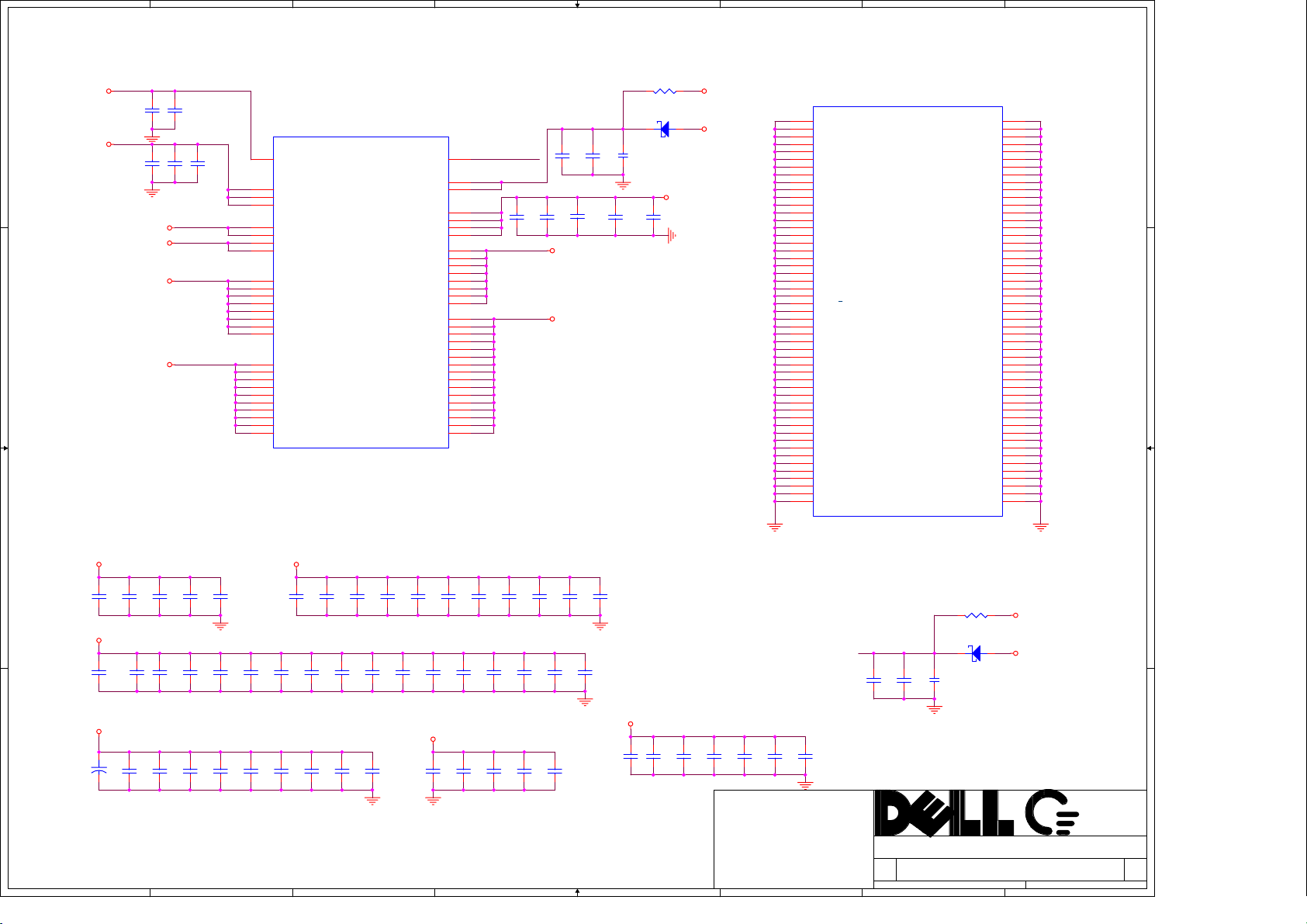

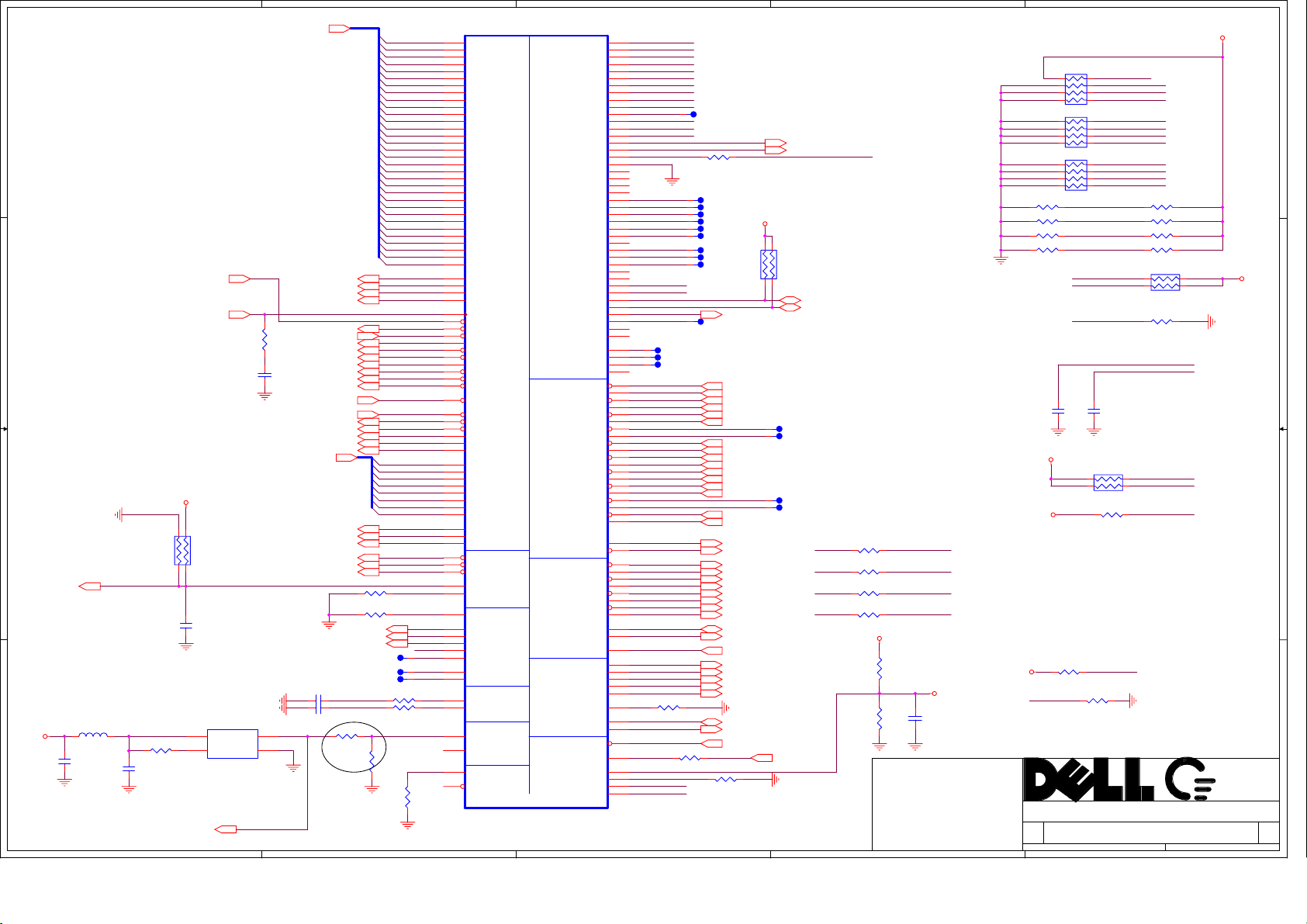

Page 3

1

2

3

4

5

6

7

8

INDEX

Pg# Description

1

Schematic Block Diagram 1

2

A A

B B

C C

D D

Schematic Block Diagram 2

3

FRONTPAGE

4-5

Banias

6-8

Odem MCH-M

9-11

ICH4

12-13

DDR SO-DIMM(200P)

14

CLOCK GENERATOR

15-17

M7/M9 Graphics

18-19

LCD CONN,CY25245 & CRT CONN

20

IDE (HDD&CD_ROM)

21

PAD& SCREW

O2_OZ711E1&CONN

22

23-24

MINI-PCI & MDC CONN

SIO

25-26

SERIAL & PARALLEL

27-28

FLASH

29

30-31

TOUCH PAD & SWITCH&LED

32

FAN & THERMAL

33-34

AC97 CODEC & connector

35-36

LAN(KENAI32-LAVON) & JACK

FIR

37

38-39

DOCKING Buffer and connector

40

Reset circuit

RTC BATTERY

41

42-43

Battery Selector & Charger

44

CPU Power

45 1.2V,1.5V,1.8VS.2.5VS

46

D/D Power

47

RUN POWER SW

48

VGA DC/DC

49

DCIN,Batt

50

CPU I/O Power

1

2

DNI LIST

3

Label Description

DC_IN+

PBATT+

PWR_SRC

RTC_PWR3_3V

+12V +12V

VHCORE

V1_2RUN AGTL+ POWER (1.2V)

+3VRUN

+3VSUS

+5VALW

+5VRUN

+5VSUS

+5VHDD

+5VMOD

STRB#/5V

+5VFAN1, +5VFAN2

VDDA

1_8VSUS

1_8VRUN

+3VALW 8051 POWER (3V)

V1_5RUN

GND

AGND

GNDP

CGNDP CHARGER GND

DGNDP DC/DC POWER GND

LANGND

4

ALL PAGES DIGITAL GROUND

5

Power & Ground

Pg#

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

6

Control Signal

AC ADAPTER (20V)

MAIN BATTERY + (10~17V)

MAIN POWER (10~20V)

RTC & PCL POWER

CPU CORE POWER (1.25/1.15V)

SLP_S3# CTRLD POWER

SLP_S5# CTRLD POWER

8051 POWER (5V)

SLP_S3# CTRLD POWER

SLP_S5# CTRLD POWER

HDD POWER (5V)

MODULE POWER (5V)

EXTERNAL FDD POWER (5V)

FAN POWER (5V)

AUDIO ANALOG POWER (5V)

RESUME WELL IN ICH

SLP_S3# CTRLD POWER

AGP I/O POWER

AUDIO GND

CPU POWER GND

COMBO CONN GND

Title

Size Document Number Rev

Date: Sheet

(3_3V)

DRUNPWROK

RUNPWROK

RUNPWROK

RUN_ON

SUS_ON

RUN_ON

SUS_ON

HDDC_EN#

MODC_EN#

FDD/LPT#

FAN_OFF/ON#

RUN_ON

Index, DNI, Power & Ground

JM2 1A

B

星期五, 六月

06, 2003

7

QUANTA

COMPUTER

of

349

8

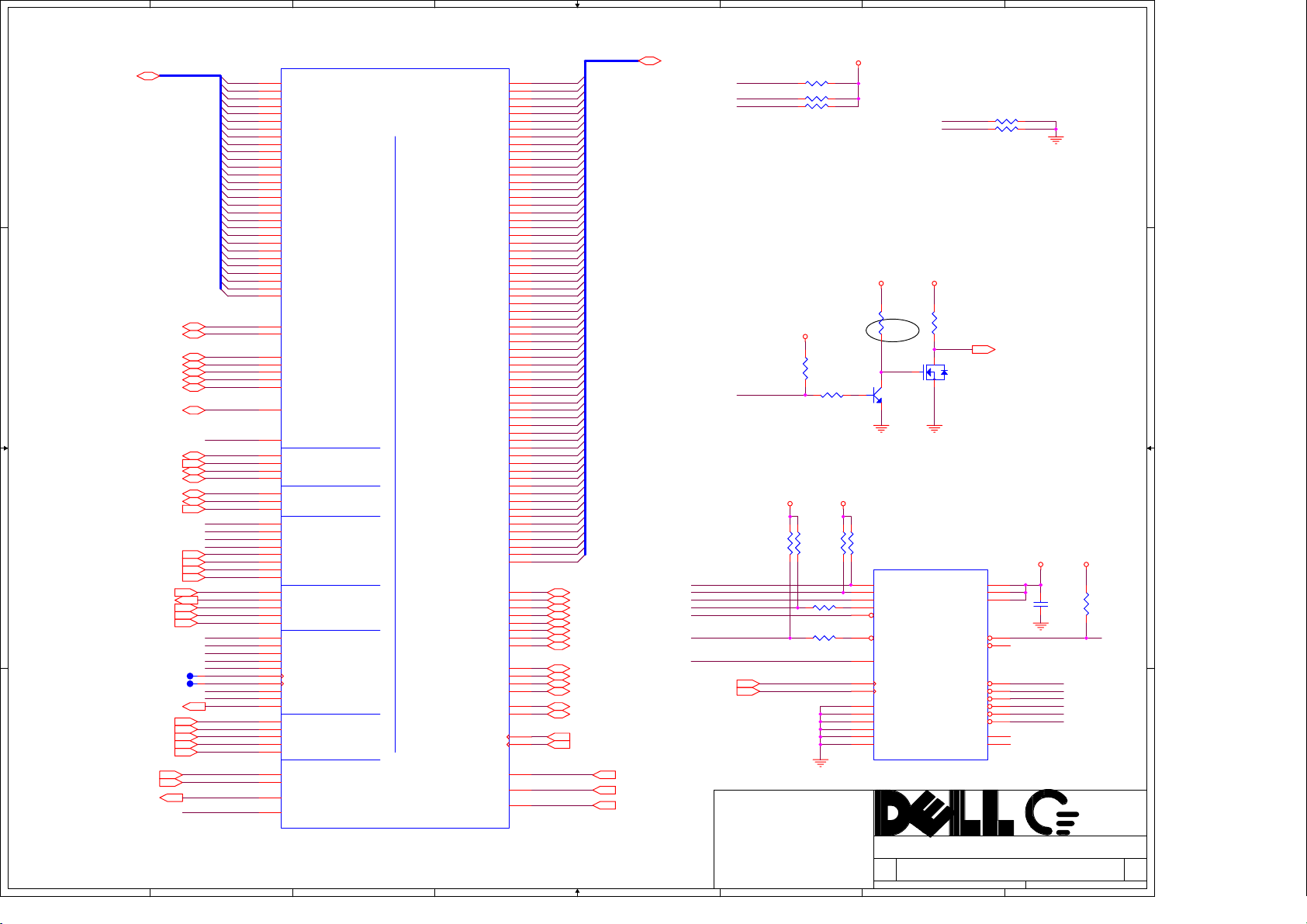

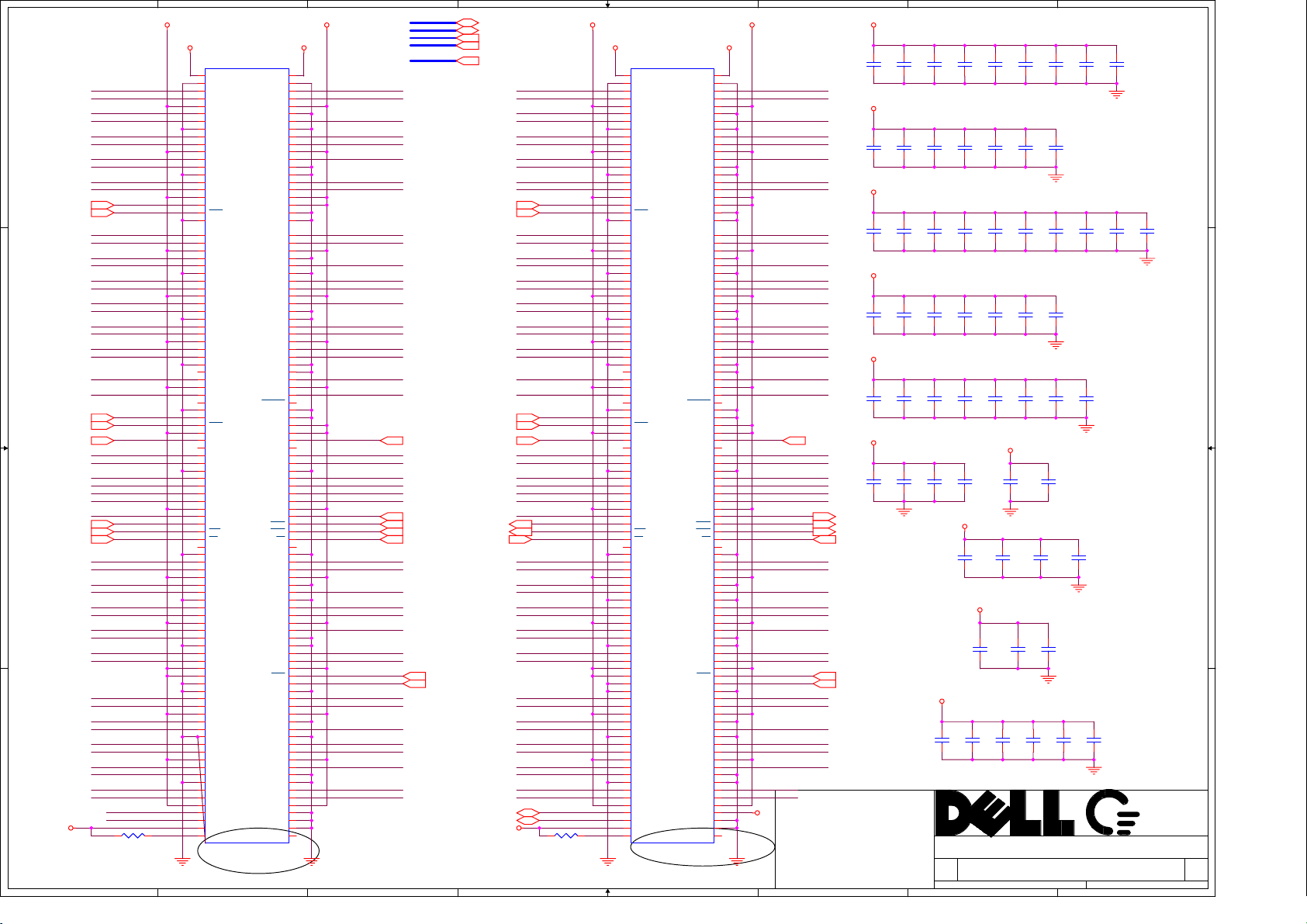

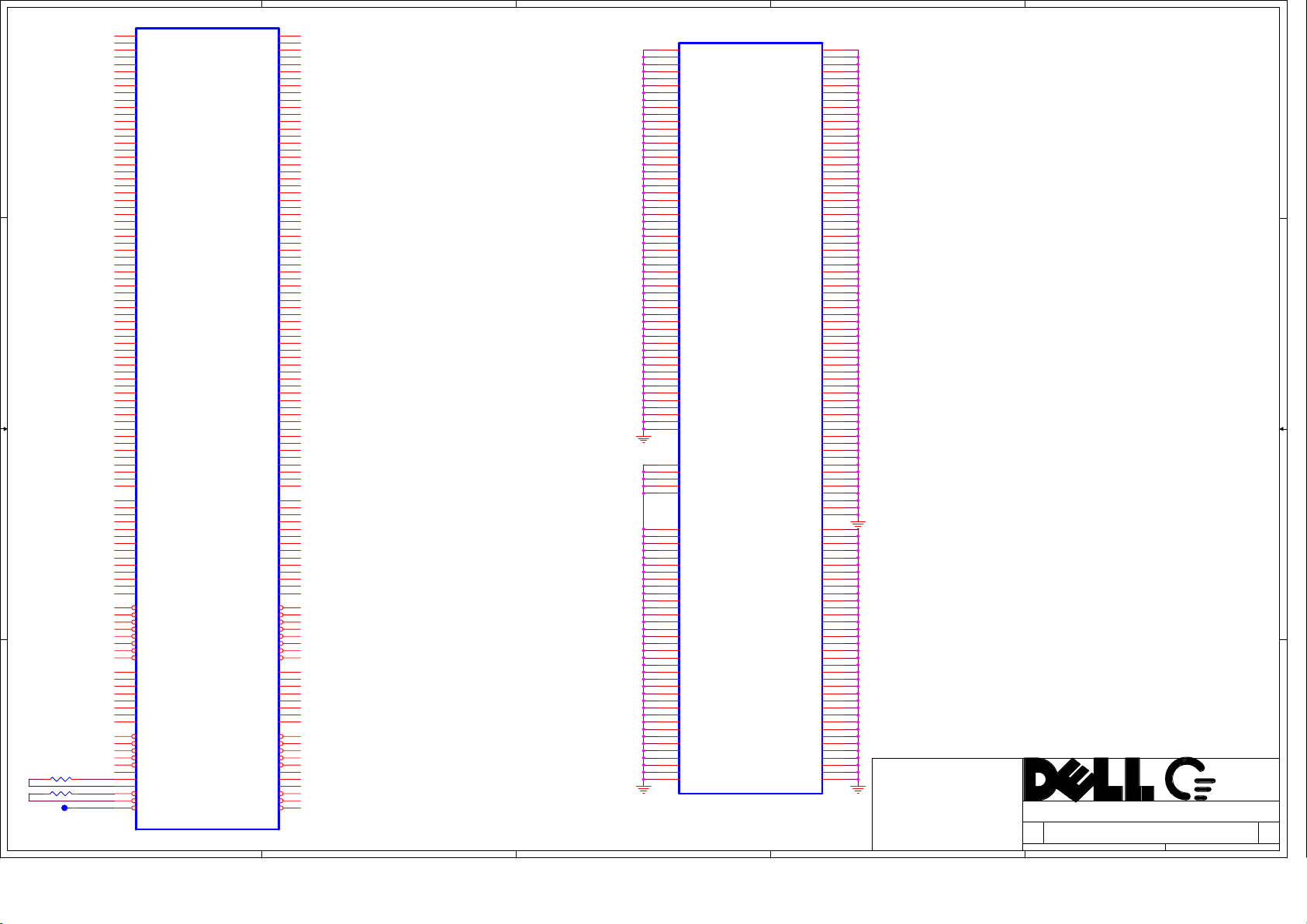

Page 4

1

2

3

4

5

6

7

8

R867 schould be close to ICH4

THERMTRIP#

IERR#

CPUPWRGD

R546 should be place within 2" of the processor ; others place near ITP

R561

56

CPU_PROCHOT#

VTT VTT

R564

54.9/F

TDI

TMS

TCK

TDO

TRST#

CPURST#

TCK

HCLK_ITP#14

HCLK_ITP14

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

6

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

HDSTBN0# 6

HDSTBP0# 6

HDSTBN1# 6

HDSTBP1# 6

HDSTBN2# 6

HDSTBP2# 6

HDSTBN3# 6

HDSTBP3# 6

HDBI0# 6

HDBI1# 6

HDBI2# 6

HDBI3# 6

DBSY# 6

DRDY# 6

HCLK_CPU# 14

HCLK_CPU 14

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A13

A12

C12

C11

B13

A16

A15

B10

A10

B18

A18

C17

B17

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

U3

R2

P3

T2

P1

T1

N2

A4

N4

J3

L1

J2

K3

K4

L4

C8

B8

A9

C9

M3

H1

K1

L2

C2

D3

A3

E4

B4

A7

D1

D4

C6

A6

B7

U79A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB0#

ADSTB1#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BPM0#

BPM1#

BPM2#

BPM3#

TRDY#

RS0#

RS1#

RS2#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TCK

TDO

TDI

TMS

TRST#

ITP_CLK0

ITP_CLK1

PREQ#

PRDY#

DBR#

LINT0

LINT1

STPCLK#

SLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

Banias Processor

Banias

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

3

1 OF 3

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DBI0#

DBI1#

DBI2#

DBI3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

CPUINIT#

B5

CPURST#

B11

C19

4

INTR9

NMI9

STPCLK#9

CPUSLP#9

HADSTB0#6

HADSTB1#6

HREQ#06

HREQ#16

HREQ#26

HREQ#36

HREQ#46

HBREQ0#6

HLOCK#6

DEFER#6

HTRDY#6

A20M#9

FERR#9

IGNNE#9

SMI#9

T195 PAD

T196 PAD

DBR#40

DPSLP#7,9

ADS#6

BPRI#6

BNR#6

HITM#6

RS#06

RS#16

RS#26

HA#[3..31]

HIT#6

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

IERR#

BPM0#

BPM1#

BPM2#

BPM3#

A20M#

FERR#

IGNNE#

CPUPWRGD

SMI#

TCK

TDO

TDI

TMS

TRST#

PREQ#

PRDY#

DBR#

STPCLK#

CPU_SLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#

CPU_PROCHOT#

2

HA#[3..31]6

A A

B B

C C

CPUPWRGD10

D D

THERMDA32

THERMDC32

THERMTRIP#10

1

HD#[0..63] 6

CPUINIT# 9

CPURST# 6

DPWR# 7

5

R867 56

R538 56

R539 332/F

VTT

R562

330

R565

R566

54.9/F

39.2/F

R885 22.6/F

R573 22.6/F

VTT

R544 27

TCK

R546 680

TRST#

+3VRUN

2

12

3904

R567

150

JITP1

1

TDI

2

TMS

5

TCK

7

TDO

3

TRST#

12

RESET#

11

FBO

8

BCLKN

9

BCLKP

10

GND0

14

GND1

16

GND2

18

GND3

20

GND4

22

GND5

Title

Size Document Number Rev

Date: Sheet

+3VALW

R559

1.5K/F

1 2

3

Q182

1

R560

330

1 2

31

2

Q181

RHU002N06

Banias Processor (HOST)

JM2 3K

星期五, 六月

06, 2003

7

VTT0

VTT1

VTAP

DBR#

DBA#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

NC0

NC1

ITP700_NC

PROCHOT# 26

VTT +3VSUS

27

28

26

25

24

23

21

19

17

15

13

4

6

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

C1499

.1U

DBR#

R571

150

QUANTA

COMPUTER

of

449

8

Page 5

1

R578

R579

54.9/F

VHCORE

C997

10U_4V

VHCORE

C1007

10U_4V

C1017

10U_4V

VHCORE

10U_4V

1 2

C1051

27.4/F

C1061

0.1U

R580

C998

10U_4V

C1008

10U_4V

C1018

10U_4V

C1052

10U_4V

1 2

54.9/F

C995

10U_4V

C1005

10U_4V

C1015

10U_4V

C1049

10U_4V

1 2

C1059

150U/6.3V

SPC

CC7343

27.4/F

C996

10U_4V

C1006

10U_4V

C1016

10U_4V

C1050

10U_4V

1 2

C1060

+

150U/6.3V

SPC

CC7343

1

A A

B B

C C

VTT

D D

+

R581

C999

10U_4V

C1009

10U_4V

C1019

10U_4V

C1053

10U_4V

1 2

COMP0

COMP1

COMP2

COMP3

2

VHCORE

C1001

C1000

10U_4V

10U_4V

VHCORE

C1011

C1010

10U_4V

10U_4V

VHCOREVHCORE

C1041

C1040

10U_4V

10U_4V

1 2

1 2

C1002

10U_4V

C1012

10U_4V

C1042

10U_4V

1 2

3

R574

1K/F

R582

2K/F

C1003

10U_4V

C1013

10U_4V

C1043

10U_4V

1 2

VTT

+1_8VRUN

+1_5VRUN

C1004

10U_4V

C1014

10U_4V

C1044

10U_4V

1 2

R586

1K_NC

Total caps = 2633 uF

ESR = 15m ohm/5 // 5m ohm/25 // 5m ohm/15

VTT

C1062

0.1U

C1063

0.1U

2

C1064

0.1U

C1065

0.1U

C1546

.1U

C1547

.1U

3

C1548

.1U

C1549

.1U

R935

R936

C1550

.1U

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

R587

1K_NC

CPU_VCCA

0_0805

0_0805_NC

4

VHCORE

4

P25

P26

AB2

AB1

AD26

E26

AC1

AC26

D18

D20

D22

E17

E19

E21

G21

H22

K22

V22

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

G1

C5

F23

N1

B1

F26

D6

D8

E5

E7

E9

F6

F8

F18

F20

F22

G5

H6

J5

J21

U5

V6

W5

Y6

U79B

COMP0

COMP1

COMP2

COMP3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TEST1

TEST2

VCCA3

VCCA2

VCCA1

VCCA0

VCC00

VCC01

VCC02

VCC03

VCC04

VCC05

VCC06

VCC07

VCC08

VCC09

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Banias Processor

Banias

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

5

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

E25

VSS

F1

VSS

F4

VSS

F5

VSS

F7

VSS

F9

VSS

F11

VSS

F13

VSS

F15

VSS

F17

VSS

F19

VSS

F21

VSS

F24

VSS

G2

VSS

G6

VSS

G22

VSS

G23

VSS

G26

VSS

H3

VSS

H5

VSS

H21

VSS

H25

VSS

J1

VSS

J4

VSS

J6

VSS

J22

VSS

J24

VSS

K2

VSS

K5

VSS

K21

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L22

VSS

L25

VSS

M1

VSS

M4

VSS

M5

VSS

M21

VSS

M24

VSS

N3

VSS

N6

VSS

N22

VSS

N23

VSS

N26

VSS

P2

VSS

P5

VSS

P21

VSS

P24

VSS

R1

VSS

VSS

5

Proprietary Note: This sheet of engineering

R4

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

6

CPU_VID043

CPU_VID143

CPU_VID243

CPU_VID343

CPU_VID443

CPU_VID543

CPU_VCCA

C1045

.01U

6

R886 54.9/F_NC

R887 54.9/F_NC

T177 PAD

T178 PAD

T179 PAD

T180 PAD

T182 PAD

R1062

1K_NC

C1047

C1046

.01U

.01U

7

VTT

Title

Size Document Number Rev

Date: Sheet

U79C

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L5

VCCP12

L21

VCCP13

M6

VCCP14

M22

VCCP15

N5

VCCP16

N21

VCCP17

P6

VCCP18

P22

VCCP19

R5

VCCP20

R21

VCCP21

T6

VCCP22

T22

VCCP23

U21

VCCP24

P23

VCCP25

W4

VCCP26

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AE7

VCCSENSE

AF6

VSSSENSE

B2

NC0

AF7

NC1

C14

NC2

C3

NC3

C16

TEST3

E1

PSI

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

C1048

.01U

Banias Processor (POWER)

JM2 3K

星期五, 六月

POWER, GROUND AND NC

C1522

10U_6.3V

X5R

06, 2003

7

Banias

3 OF 3

VID

Banias Processor

C1523

10U_6.3V

X5R

C1524

10U_6.3V

X5R

8

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24W22

VSSVSS

C1525

10U_6.3V

X5R

QUANTA

COMPUTER

of

549

8

Page 6

1

2

3

4

5

6

7

8

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AE5

AF3

AC6

AC3

AF4

AE2

AG4

AG2

AE7

AE8

AH2

AC7

AG3

AD7

AH7

AE6

AC8

AG8

AG7

AH3

AF8

AH5

AC11

AC12

AE9

AC10

AE10

AD9

AG9

AC9

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

J27

MCH_VREF

P8

M7

AA9

AB12

AB16

AD13

AA7

AC13

2

U80A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

RSTIN#

HVREF4

HVREF3

HVREF2

HVREF1

HVREF0

HSWNG1

HSWNG0

HRCOMP1

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADSTB0#

HADSTB1#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

BR0#

HOST BUS INTERFACE (Processor System

Bus)

BPRI#

BNR#

HLOCK#

HIT#

HITM#

DEFER#

DBSY#

DRDY#

HTRDY#

RS0#

RS1#

RS2#

CPURST#

DBI3#

DBI2#

DBI1#

DBI0#

BCLK

BCLK#

HDSTBN0#

HDSTBP0#

HDSTBN1#

HDSTBP1#

HDSTBN2#

HDSTBP2#

HDSTBN3#

HDSTBP3#HRCOMP0

T5

R2

U3

R3

P7

T3

P4

P3

P5

R6

N2

N5

N3

J3

M3

M4

M5

L5

K3

J2

N6

L6

L2

K5

L3

L7

K4

J5

R5

N7

U7

U2

T7

R7

U5

T4

V7

Y7

V3

W3

Y5

Y3

Y4

V5

W2

V4

W7

W5

W6

AE17

AD15

AH9

AG5

AD5

J8

K8

AD4

AD3

AF6

AG6

AD11

AE11

AC15

AC16AC2

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HADSTB0# 4

HADSTB1# 4

ADS# 4

HREQ#0 4

HREQ#1 4

HREQ#2 4

HREQ#3 4

HREQ#4 4

HBREQ0# 4

BPRI# 4

BNR# 4

HLOCK# 4

HIT# 4

HITM# 4

DEFER# 4

DBSY# 4

DRDY# 4

HTRDY# 4

RS#0 4

RS#1 4

RS#2 4

CPURST# 4

HDBI3# 4

HDBI2# 4

HDBI1# 4

HDBI0# 4

HCLK_MCH 14

HCLK_MCH# 14

HDSTBN0# 4

HDSTBP0# 4

HDSTBN1# 4

HDSTBP1# 4

HDSTBN2# 4

HDSTBP2# 4

HDSTBN3# 4

HDSTBP3# 4

HA#[3..31]

HA#3

U6

HA#[3..31] 4

VTT MCH_VREF

ODEM MCH-M

3

4

49.9/F

R590

R591

100/F

C1066

1U_10V

C1067

.1U

C1526

.1U

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

5

Dell's express written consent."

VTT

PCIRST#_19,15,35,38

C1069

.01U

HD#[0..63]

R594

27.4/F

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HSWNG1

HSWNG0

HRCOMP1

HRCOMP0

R595

27.4/F

A A

B B

C C

VTT

HD#[0..63]4

R592

C1068

301/F

.01U

R593

150/F

R596

D D

301/F

R597

150/F

1

E29

N29

U29

AA29

AE29

A27

K27

AJ27

E26

G26

R26

W26

AC26

AF25

A23

F24

M23

AC23

AH23

D21

H21

N22

T22

V22

Y22

AB22

AC21

AD22

AF21

AG22

AH21

A19

F20

H19

AB19

AC20

AD19

AE20

AF19

AG20

AH19

D17

H17

N17

R17

U17

AB17

AC18

AE18

AF17

AG18

AJ17

A15

F15

H15

N15

P16

R15

T16

U15

AB15

AD16

AF15

AJ15

D13

U80E

VSS

J29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J26

VSS

L26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L24

VSS

VSS

VSS

VSS

VSS

VSS

J22

VSS

L22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GROUND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E14

H13

N13

P14

R13

T14

U13

AB13

AD14

AF13

AJ13

A11

F12

H11

AB11

AD12

AF11

AJ11

D9

H9

AB9

AD10

AF9

AJ9

A7

F8

J7

L8

N8

R8

U8

W8

AA8

AD8

AF7

AJ7

D5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

AF5

AJ5

A3

J4

L4

N4

R4

U4

W4

AA4

AC4

AE4

AJ3

E1

J1

L1

N1

R1

U1

W1

AA1

AC1

AE1

AG1

ODEM MCH-M

QUANTA

Title

Odem ( HOST)

Size Document Number Rev

JM2 3B

星期五, 六月

6

Date: Sheet

06, 2003

7

COMPUTER

of

649

8

Page 7

1

2

3

4

5

6

7

8

GAD[0..31]15

A A

B B

GCBE0#15

GCBE1#15

GCBE2#15

GCBE3#15

GFRAME#15

GIRDY#15

GTRDY#15

GDEVSEL#15

GPAR15

GSTOP#15

T197

R891 1K

+1_5VRUN

Populate R918 for M9,

Unpopulate R918 for M7.

C C

+1_5VRUN

D D

SBA[0..7]15

ST2

R605

8.2K

AGP_WBF#15

ST1

R880

1K

R881

1K_NC

1

AGPVREF15

CLK66_MCH14

+1_5VRUN

AD_STBA15

AD_STBA#15

AD_STBB15

AD_STBB#15

SB_STB#15

PAD

GREQ#15

GGNT#15

RBF#15

R918 0_NC

SB_STB15

ST015

ST115

ST215

R606 36.5/F

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

PIPE#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

WBF#

ST0

ST1

ST2

AGPCOMP

C1084 .1U

R607

22

C1086

5P

ST MCH STRAP

TEST MODE

0

400MHZ

1

U80C

R27

R28

R25

U27

U28

V26

V27

U23

U24

U25

V24

Y27

Y26

AA28

AB25

AB27

AA27

AB26

Y23

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

V25

V23

Y25

AA23

Y24

W27

W24

W28

W25

W23

AF22

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AG24

AH25

AE22

AE23

R24

R23

AC27

AC28

AF27

AF26

AG25

AF24

AG26

AD25

AA21

P22

T25

T26

T27

T23

T24

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

G_CBE0#

G_CBE1#

G_CBE2#

G_CBE3#

G_FRAME#

G_IRDY#

G_TRDY#

G_DEVSEL#

G_PAR

G_STOP#

PIPE#

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

G_REQ#

G_GNT#

RBF#

WBF#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

SB_STB

SB_STB#

ST0

ST1

ST2

AGP_RCOMP

AGPREF

66IN

ODEM MCH-M

AGP INTERFACE

VCCAGP0

VCCAGP1

VCCAGP2

VCCAGP3

VCCAGP4

VCCAGP5

VCCAGP6

VCCAGP7

VCCAGP8

VCCAGP9

VCCAGP10

VCCAGP11

VCCAGP12

VCCAGP13

VCCAGP14

VCCAGP15

VCCSM0

VCCSM1

POWER INTERFACE

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCHA

VCCGA

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

AGPCOMP should be 10 mil within 500 mil from

Odem

2

3

+1_5VRUN

R29

W29

AC29

AG29

U26

AA26

AE26

AJ25

AD23

AF23

R22

U22

W22

AA22

AB21

AD21

+2_5VSUS

C29

G29

A25

D25

K26

D23

H24

K24

L23

A21

F22

H22

K22

D19

H20

A17

F18

H18

D15

F16

H16

A13

F14

H14

D11

H12

A9

F10

H10

D7

H8

K7

A5

E5

H5

J6

C1

G1

+1_8VRUN

T13

T17

G16

G10

G9

H7

G22

H3

G3

G2

H27

AD27

NC

AD26

NC

C1083

.01U

C1527

10U_4V

X6S

T183PAD

T184PAD

T185PAD

T186PAD

T187PAD

T188PAD

T189PAD

T190PAD

T191PAD

+2_5VSUS

R601

10K_NC

R604

0_NC

Place the divider circuit at the middle of MCH-M and ICH4

+1_8VRUN

VCC1_2_MCH

DPSLP#4,9

DPWR#4

+1_5VRUN

R603 4.7K_NC

ETS#

HUBREF = 0.5 * VCC1_8

+1_8VRUN

R608

150/F

1 2

HUBREF

R610

C1516

.1U

150/F

1 2

M22

H26

L29

L25

N26

N23

P17

N16

P15

R16

T15

U16

N14

P13

R14

U14

V8

Y8

H4

U80D

VCC1_8_0

VCC1_8_1

VCC1_8_2

VCC1_8_3

VCC1_8_4

VCC1_2_0

VCC1_2_1

VCC1_2_2

VCC1_2_3

VCC1_2_4

VCC1_2_5

VCC1_2_6

VCC1_2_7

VCC1_2_8

VCC1_2_9

DPSLP#

DPWR#

TESTIN#

ETS#

HUBREF 10

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

HUB INTERFACE

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HI_REF

HUB_PSTRB

HUB_PSTRB#

HI_RCOMP

ODEM MCH-M

Routing 4/8 and match

AG23

AJ23

AE21

AG21

AJ21

AB20

AC19

AE19

AF20

AG19

AJ19

AB18

AD18

AF18

AB14

AB10

M8

T8

AB8

AD20

P25

P24

N27

P23

M26

M25

L28

L27

M27

N28

M24

P26

N25

N24

P27

VTT

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

HUBREF

HI_RCOMP

C1515

.01U

HL[0..10]

R602 36.5/F

HL[0..10] 10

HLSTB 10

HLSTB# 10

+1_8VRUN

HLSTB/HLSTB# within 10

mils

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

4

5

Dell's express written consent."

6

Title

Odem (AGP & POWER)

Size Document Number Rev

JM2 3K

星期五, 六月

Date: Sheet

06, 2003

7

QUANTA

COMPUTER

of

749

8

Page 8

1

2

3

4

5

6

7

8

MD[0..63]

A A

MD[0..63] 12,13

R_MD[0..63]

R_MA[0..12]

R_SM_DQS[0..7]MA[0..12]

R_MD[0..63] 13

R_MA[0..12] 12,13

R_SM_DQS[0..7] 13MA[0..12] 12,13

+1_8VRUN +2_5VSUS

C1090

10U_6.3V

C1091

.01U

C1092

.1U

C1093

.1U

U80B

G28

F27

C28

E28

H25

G27

F25

B28

E27

C27

B25

C25

B27

D27

D26

E25

D24

E23

C22

E21

C24

B23

D22

B21

C21

D20

C19

D18

C20

E19

C18

E17

E13

C12

B11

C10

B13

C13

C11

D10

E10

C9

D8

E8

E11

B9

B7

C7

C6

D6

D4

B3

E6

B5

C4

E4

C3

D3

F4

F3

B2

C2

E2

G4

C16

D16

B15

C14

B17

C17

C15

D14

R_MD0

R_MD1

R_MD2

R_MD3

R_MD4

R_MD5

R_MD6

R_MD7

R_MD8

R_MD9

R_MD10

R_MD11

R_MD12

R_MD13

R_MD14

R_MD15

R_MD16

R_MD17

R_MD18

R_MD19

R_MD20

R_MD21

R_MD22

R_MD23

R_MD24

R_MD25

R_MD26

R_MD27

R_MD28

R_MD29

R_MD30

R_MD31

R_MD32

R_MD33

R_MD34

R_MD35

R_MD36

R_MD37

R_MD38

R_MD39

R_MD40

R_MD41

R_MD42

R_MD43

R_MD44

R_MD45

R_MD46

R_MD47

R_MD48

R_MD49

R_MD50

R_MD51

R_MD52

R_MD53

R_MD54

R_MD55

R_MD56

R_MD57

R_MD58

R_MD59

R_MD60

R_MD61

R_MD62

R_MD63

T169PAD

T170PAD

T171PAD

T172PAD

T173PAD

T174PAD

T175PAD

T176PAD

C1142

.1U

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

R_SM_DQS0

R_SM_DQS1

R_SM_DQS2

R_SM_DQS3

R_SM_DQS4

R_SM_DQS5

R_SM_DQS6

R_SM_DQS7

R_SM_DQS8

R_BMWEA#

R_SRASA#

R_SCASA#

R_BA0

R_BA1

CKE0

CKE1

CKE2

CKE3

SMRCOMP

RCVENIN#

+1_5VRUN

C1539

.1U

C1540

.1U

C1541

.1U

C1542

.1U

C1543

.1U

C1544

.1U

C1545

.1U

SM_CS0#12,13

SM_CS1#12,13

SM_CS2#12,13

SM_CS3#12,13

T158 PAD

R_BMWEA#12,13

B B

C C

SMDDR_VTERM

SMDDR_VREF

C1141

.1U

CLK_SDRAM012

CLK_SDRAM112

CLK_SDRAM212

CLK_SDRAM312

CLK_SDRAM412

CLK_SDRAM512

CLK_SDRAM0#12

CLK_SDRAM1#12

CLK_SDRAM2#12

CLK_SDRAM3#12

CLK_SDRAM4#12

CLK_SDRAM5#12

R_SRASA#12,13

R_SCASA#12,13

R_BA012,13

R_BA112,13

CKE012,13

CKE112,13

CKE212,13

CKE312,13

R612 30.1/F

C1528

.1U

R_MA0

R_MA1

R_MA2

R_MA3

R_MA4

R_MA5

R_MA6

R_MA7

R_MA8

R_MA9

R_MA10

R_MA11

R_MA12

C26

C23

B19

D12

E15

G11

G12

G13

G23

E22

H23

E12

E16

G17

G18

E18

G20

G19

E20

G21

G24

G25

K23

K25

E24

G15

G14

E9

F7

F9

E7

F26

C8

C5

E3

F11

G8

F23

F17

F19

F21

F13

J25

G5

G6

F5

J24

G7

J23

J28

J21

J9

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_SDQS0

SM_SDQS1

SM_SDQS2

SM_SDQS3

SM_SDQS4

SM_SDQS5

SM_SDQS6

SM_SDQS7

SM_SDQS8

SM_WE#

SM_RAS#

SM_CAS#

SM_BA0

SM_BA1

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

SM_CLK0

SM_CLK1

SM_CLK2

SM_CLK3

SM_CLK4

SM_CLK5

SM_CLK0#

SM_CLK1#

SM_CLK2#

SM_CLK3#

SM_CLK4#

SM_CLK5#

SMRCOMP

SDREF0

SDREF1

RCVENIN#

RCVENOUT#

SM_MD0

SM_MD1

SM_MD2

SM_MD3

SM_MD4

SM_MD5

SM_MD6

SM_MD7

SM_MD8

SM_MD9

SM_MD10

SM_MD11

SM_MD12

SM_MD13

SM_MD14

SM_MD15

SM_MD16

SM_MD17

SM_MD18

SM_MD19

SM_MD20

SM_MD21

SM_MD22

SM_MD23

DDR INTERFACE

SM_MD24

SM_MD25

SM_MD26

SM_MD27

SM_MD28

SM_MD29

SM_MD30

SM_MD31

SM_MD32

SM_MD33

SM_MD34

SM_MD35

SM_MD36

SM_MD37

SM_MD38

SM_MD39

SM_MD40

SM_MD41

SM_MD42

SM_MD43

SM_MD44

SM_MD45

SM_MD46

SM_MD47

SM_MD48

SM_MD49

SM_MD50

SM_MD51

SM_MD52

SM_MD53

SM_MD54

SM_MD55

SM_MD56

SM_MD57

SM_MD58

SM_MD59

SM_MD60

SM_MD61

SM_MD62

SM_MD63

SM_MD64

SM_MD65

SM_MD66

SM_MD67

SM_MD68

SM_MD69

SM_MD70

SM_MD71

+2_5VSUS

+2_5VSUS

VTT

C1116

.1U

+1_5VRUN

+

C1094

22U

C1102

22U

.1U

.1U

C1095

C1103

C1096

.1U

C1104

.1U

C1097

.1U

C1105

.1U

C1098

.1U

C1106

.1U

C1099

.1U

C1107

.1U

C1100

.1U

C1108

.1U

Place the bypass caps close to Odem MCH-M

C1118

C1119

C1117

.1U

.1U

C1126

100U

.1U

C1127

10U_6.3V

.1U

10U_6.3V

VCC1_2_MCH VCC1_2_MCH

C1136

+

150U/6.3V

SPC

CC7343

C1120

C1128

C1121

.1U

C1137

+

150U/6.3V

SPC

CC7343

C1129

.1U

C1122

.1U

C1130

.1U

C1123

.1U

C1101

.1U

C1109

.1U

C1131

.1U

C1110

.1U

2.2U

X5R

C1132

.1U

C1138

C1111

.1U

.1U

C1088

+

150U/6.3V

SPC

CC7343

.1U

C1133

C1143

.22U

C1112

C1134

.1U

C1537

.1U

C1144

.047U

C1089

+

150U/6.3V

SPC

CC7343

C1538

.1U

.022U

C1145

C1146

.015U

C1147

.01U

ODEM MCH-M

D D

RCVENIN# and RCVENOUT#

ROUTING RULE

L1 - MCH-M Feedback Signal Pin to Signal Via: Max = 40 mils

L2 - MCH-M RCVENOUT# Signal Via to RCVENIN# Signal Via: Must = 100 mils +/- 5mils

L3 - Signal Via to MCH-M Feedback Signal Pin: Max = 40 mils

1

2

3

4

5

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

6

QUANTA

Title

Odem ( DDR )

Size Document Number Rev

JM2 2E

星期五, 六月

Date: Sheet

06, 2003

7

COMPUTER

of

849

8

Page 9

1

2

3

4

5

6

7

8

06, 2003

7

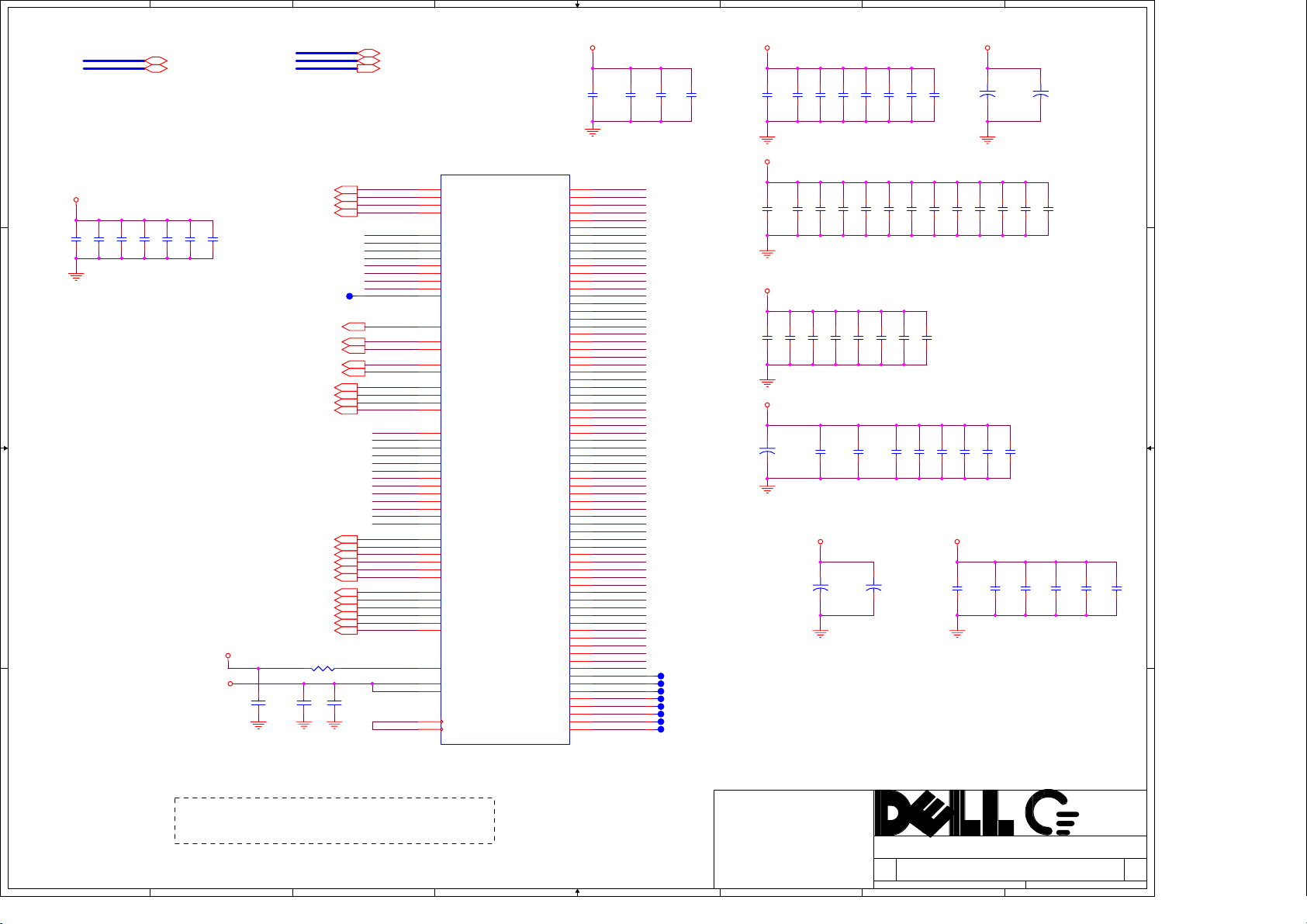

PCI Pullups

RP99

6

7

8

9

10

10P8R-8.2K

RP101

6

7

8

9

10

10P8R-8.2K

RP102

6

7

8

9

10

10P8R-8.2K

ICH_GPIO3

ICH_GPIO5

ICH_GPIO4

ICH_GPIO2

SDD[0..15]

SDDREQ

SDIOW#

SDIOR#

SIORDY

SDDACK#

IRQ15

SDA1

SDA0

SDCS1#

SDA2

SDCS3#

GNT0#

GNT2#

GNT3#

GNT1#

GNT4#

REQB#

+3VRUN

5

IRDY#

4

PERR#

3

DEVSEL#

2

1

+3VRUN

5

4

3

SERR#

2

PLOCK#

1

+3VRUN

5

REQA#

4

REQ1#

3

REQ4#

2

REQ0#

1

+3VRUN

RP103

7 8

5 6

3 4

1 2

8P4R-10K_NC

R623 10K_NC

1 2

R882 10K

1 2

+3VRUN

RP104

7 8

5 6

3 4

1 2

8P4R-8.2K

ICH4_GPIO7 10

+3VRUN

+3VRUN

QUANTA

COMPUTER

of

949

8

VTT

IRQ14

R613

.047U

1 2

1 2

PCIRST#

12

56

R933 56

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

PDCS1#

PDCS3#

PDA0

PDA1

PDA2

PDIOR#

PDIOW#

PIORDY

IRQ14

PDDREQ

PDDACK#

3

A A

NMI4

A20M#4

FERR#4

IGNNE#4

INTR4

CPUINIT#4

GATEA2026

+3VSUS

C1441

+3VSUS

PDD[0..15]

PDDREQ

PDIOW#

PDIOR#

PIORDY

PDDACK#

IRQ14

PDA1

PDA0

PDCS1#

PDA2

PDCS3#

2

5

2

1

5

2

1

+3VSUS

ICH_PME#25

CLKRUN#22,23,25,35

+3VRUN

.047U

AD[0..31]22,23,35,38

PCIRST#

T159 PAD

T118 PAD

C1442

R624 10K_NC

R626 10K

PCIRST#_16,15,35,38

B B

PCIRST#_222,23,25

C C

D D

1

R833

22

R834

22

PCLK_ICH14

PDD[0..15]20

PDDREQ20

PDIOW#20

PDIOR#20

PIORDY20

PDDACK#20

IRQ1420

PDA120

PDA020

PDCS1#20

PDA220

PDCS3#20

U108

4

12

7SH32

U109

4

12

7SH32

R625

33

1 2

C1155

18P

U81A

V21

NMI

AB23

A20M#

AA21

FERR#

W21

IGNNE#

AB22

INTR

V22

INIT#

U22

RCIN#

Y22

A20GATE

H5

AD0

J3

AD1

H3

AD2

K1

AD3

G5

AD4

J4

AD5

H4

AD6

J5

AD7

K2

AD8

G2

AD9

L1

AD10

G4

AD11

L2

AD12

H2

AD13

L3

AD14

F5

AD15

F4

AD16

N1

AD17

E5

AD18

N2

AD19

E3

AD20

N3

AD21

E4

AD22

M5

AD23

E2

AD24

P1

AD25

E1

AD26

P2

AD27

D3

AD28

R1

AD29

D2

AD30

P4

AD31

W2

PME#

P5

PCICLK

U5

PCIRST#

AC2

CLKRUN#/GPIO24

E8

GNTA#/GPIO16

C5

GNTB#/GNT5#/GPIO17

AB11

PDD0

AC11

PDD1

Y10

PDD2

AA10

PDD3

AA7

PDD4

AB8

PDD5

Y8

PDD6

AA8

PDD7

AB9

PDD8

Y9

PDD9

AC9

PDD10

W9

PDD11

AB10

PDD12

W10

PDD13

W11

PDD14

Y11

PDD15

Y13

PDCS1#

AB14

PDCS3#

AA13

PDA0

AB13

PDA1

W13

PDA2

AC12

PDIOR#

W12

PDIOW#

AB12

PIORDY

AC13

IRQ14

AA11

PDDREQ

Y12

PDDACK#

ICH4

CPU

PCI

REQB#/REQ5#/GPIO1

IDE

4

APICD0

APICD1

APICCLK

SMI#

STPCLK#

CPUSLP#

DPSLP#

C/BE0#

C/BE1#

C/BE2#

C/BE3#

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

PAR

SERR#

PERR#

PLOCK#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

PIRQA#

PIRQB#

PIRQC#

PIRQD#

PIRQE#/GPIO2

PIRQF#/GPIO3

PIRQG#/GPIO4

PIRQH#/GPIO5

SERIRQ

REQA#/GPIO0

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

SDCS1#

SDCS3#

SDA0

SDA1

SDA2

SDIOR#

SDIOW#

SIORDY

IRQ15

SDDREQ

SDDACK#

H19

K20

J19

W23

V23

U21

U23

J2

K4

M4

N4

F1

L5

F2

M3

F3

G1

K5

L4

M2

B1

A2

B3

C7

B6

C1

E6

A7

B7

D6

D5

C2

B4

A3

C8

D7

C3

C4

J22

B5

A6

W17

AB17

W16

AC16

W15

AB15

W14

AA14

Y14

AC15

AA15

Y15

AB16

Y16

AA17

Y17

AB21

AC22

AA20

AC20

AC21

Y18

AA18

AC19

AA19

AB18

AB19

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

RP100 4P2R-S-10K

3

1

C/BE0# 22,23,35,38

C/BE1# 22,23,35,38

C/BE2# 22,23,35,38

C/BE3# 22,23,35,38

FRAME# 22,23,35,38

IRDY# 22,23,35,38

TRDY# 22,23,35,38

DEVSEL# 22,23,35,38

STOP# 22,23,35,38

PAR 22,23,35,38

SERR# 22,23,35,38

PERR# 22,23,35,38

PLOCK# 38

REQ0# 39

REQ1# 22

REQ3# 23

REQ4# 35

GNT0# 38

GNT1# 22

GNT3# 23

GNT4# 35

ICH_GPIO2

ICH_GPIO3

ICH_GPIO4

ICH_GPIO5

REQA#

REQB#

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

SDCS1#

SDCS3#

SDA0

SDA1

SDA2

SDIOR#

SDIOW#

SIORDY

IRQ15

SDDREQ

SDDACK#

5

4

2

PIRQA# 15

PIRQB# 23,38

PIRQC# 35

PIRQD# 22,23

SERIRQ 22,25

SMI# 4

STPCLK# 4

CPUSLP# 4RCIN#25

DPSLP# 4,7

REQ0 : DOCKING

REQ1 : Card Bus

REQ2 : USB 2.0

REQ3 : MINI PCI

REQ4 : BCM5702 LAN

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

6

SDD[0..15]20

SIORDY20

SDDACK#20

SDA120

SDA020

SDCS1#20

SDA220

SDCS3#20

SERIRQ

REQ3#

IRQ15

+3VRUN

TRDY#

STOP#

FRAME#

PIRQB#

+3VRUN

PIRQA#

PIRQC#

PIRQD#

REQ2#

+3VRUN

SDDREQ20

SDIOW#20

SDIOR#20

IRQ1520

Title

ICH4-M (CPU,PCI,IDE)

Size Document Number Rev

JM2 3C

星期五, 六月

Date: Sheet

Page 10

1

47_NC

C1749

22P_NC

RP106

RP108

2 1

2.2U_10V_NC

CLK_32KX1

R638

10M

1 2

CLK_32KX2

C1159

15P

R1130

1 2

ICH_RI#

BATLOW#

SYS_RESET#

RI_OUT#

PCLK_SMB

PDAT_SMB

R654 10K_NC

R655 8.2K

R883 10K

R656 100K

R657 100K

1

D88

RB751V

C1157

C1743

C1172

.1U_NC

RI_OUT#

D_3VRTC

1 2

1 2

W2

14

23

32.768KHZ

10P_NC

IAC_BITCLK_ICH

22P_NC

IAC_SDATAO

THRM#

LAN_RST#

DELAY_IMVP_PWRGD

SUSPWROK

1

2

+3VSUS

R1067

22M_NC

VBIAS

R1069

2.4M/F_NC

R647 33

R1127 0

C1744

NC

R651

47_NC

C1169

+3VSUS

+RTC_PWR3_3V

A A

IAC_SDATAIN1

B B

IAC_SYNC_MDC24

IAC_SYNC_AUDIO33

+3VSUS

7 8

5 6

3 4

1 2

+3VSUS

+3VRUN

8P4R-10K

7 8

5 6

3 4

1 2

8P4R-10K

RI0#25,27

RI_OUT#22

C C

D D

1 2

53

2

D43

2 1

RB751V

RP105

4

2

4P2R-S-1K/F

R633 19.1/FK

12

CLK48_USB14

C1160

15P

CLK66_ICH14

IAC_SYNC

14M_ICH14

U83

7SH86_NC

ICH_RI#

4

2

3

VCCRTC

3

R_3VRTC

1

R645

R652

C1170

10P

C1156 .047U

RTCRST# delay 18-25ms

RTCRST# BID3

C1158

1U_16V

22

1 2

C1166

5P

IAC_SDATAIN033

IAC_SDATAIN124

IAC_BITCLK_ICH33

DELAY_IMVP_PWRGD40

33

1 2

VCORE_PWRGOOD40,43

T144 PAD

T146 PAD

R1068

1K_NC

1 2

R640

1 2

10

HL[0..10]7

LAD0/FWH025

LAD1/FWH125

LAD2/FWH225

LAD3/FWH325

IAC_RESET#24,33

T120 PAD

PCLK_SMB12,14,23,35

PDAT_SMB12,14,23,35

THRM#25

PWRBTN#25

SUSPWROK22,40

THERMTRIP#4

DPRSLPVR43

STP_AGP#15

AGP_BUSY#15

ICH4_GPIO79

CPUPWRGD4

T192 PAD

T193 PAD

T124 PAD

T127 PAD

T129 PAD

VBIAS

USB_VD0+31

USB_VD0-31

USB_VD2+31

USB_VD2-31

USB_VD4+20

USB_VD4-20

PCLK_SMB12,14,23,35

PDAT_SMB12,14,23,35

EXT_SMI#25

CLK_32KX1

R627

10M

1 2

OC0#31

OC2#31

C1161

10P

HLSTB7

HLSTB#7

IAC_SYNC

ICH_RI#

THRM#

DELAY_IMVP_PWRGD

BATLOW#

SUSPWROK

R934 56

DPRSLPVR

SPKR33

R653 68

CPUPERF#

SSMUXSEL

VCORE_PWRGOOD_D

R658

1K_NC

100K

3

BID0

BID1

BID2

BID3

OC0#

OC2#

OC4#

HL0

HL1

HL2

HL3

HL4

HL5

EXT_SMI#

R659

J20

G22

F20

G20

F21

H20

C20

D20

B15

C18

D18

A15

C16

D16

A14

F19

L19

L20

M19

M21

P19

R19

T21

P21

N20

T2

R4

T4

U2 T5

C13

C9

D13

A13

B13

B8

AC4

AB4

Y1

V1

AB6

AB2

AA1

AA6

W20

V20

T3

R2

J23

AC3

AB1

H23

R3

V4

Y23

Y20

J21

V19

C12

A8

D11

D10

C1173

.1U

4

VTT

R931 8.2K

U81B

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

USBP0P

USBP0N

OC0#

USBP2P

USBP2N

OC2#

USBP4P

USBP4N

OC4#

CLK48

HI0

HI1

HI2

HI3

HI4

HI5

HI_CLK

HL_STB/HL_STBS

HL_STB#/HLSTBF

LAD0/FWH0

LAD1/FWH1

LAD2/FWH2

LAD3/FWH3 LFRAME#/FWH4

AC_RST#

AC_SYNC

AC_SDIN0

AC_SDIN1

AC_SDIN2

AC_BITCLK

SMBCLK

SMBDATA

RI#

THRM#

PWROK

BATLOW#

PWRBTN#

RSMRST#

THRMTRIP#

DPRSLPVR

C3_STAT#/GPIO21

AGPBUSY#/GPIO6

CLK14

SMLINK0

SMLINK1

SPKR

GPIO7

GPIO8

CPUPWRGD

CPUPERF#/GPIO22

SSMUXSEL/GPIO23

VGATE/VRMPWRGD

EE_SHCLK

EE_DOUT

EE_DIN

EE_CS

5

1 6

AC97&RTC

MISC&GPIO

ICH4

U82A

7WZ14

4

CPUPERF#

USB

HUB LINK

LPC&FWH

SMBALERT#/GPIO11

SM

PM

SLP_S1#/GPIO19

STP_PCI#/GPIO18

STP_CPU#/GPIO20

SUS_STAT#/LPCPD#

SpeedStep

LAN

+3VRUN

U82B

5

3 4

7WZ14

GPIO38

GPIO39

GPIO40

GPIO41

GPIO42

GPIO43

USBP1P

USBP1N

OC1#

USBP3P

USBP3N

OC3#

USBP5P

USBP5N

OC5#

USBRBIAS

USBRBIAS#

HI10

HI11

HI_REF

HI_VSWING

HUB_RCOMP

LDRQ0#

LDRQ1#

VBIAS

RTCX1

RTCX2

VCCRTC

RTCRST#

AC_SDOUT

INTRUDER#

SLP_S3#

SLP_S4#

SLP_S5#

SUSCLK

LAN_RST#

SYS_RESET#

GPIO12

GPIO13

GPIO25

GPIO27

GPIO28

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2

LAN_CLK

LAN_RSTSYNC

C1171

.1U

VCORE_PWRGOOD_D

5

BID3 BID2 BID1 BID0

0

0

00

0

0

0

1000

1001 QT (A00)

10 01A01

F23

H22

G23

H21

F22

E23

A21

B21

C14

A19

B19

B14

A17

B17

D14

A23

B23

HL6

T20

HI6

HL7

R20

HI7

HL8

P23

HI8

HL9

L22

HI9

HL10

N22

K21

M23

R22

HUB_ICH_RCOMP

R23

U3

U4

Y6

AC7

AC6

AB5

W7

D9

W6

AA5

Y4

Y2

AA2

AA4

Y5

Y3

W18

Y21

W19

AB3

V5

W3

V2

MPCIACT#

W1

W4

A10

A9

A11

B10

C10

A12

C11

B11

5

0

1PROTO2

1

0

10

1

0

1110

USB_VD1+ 30

OC1#

OC3#

OC5#

HUBREF

LPC_DRQ0#

LPC_DRQ1#

LAN_RST#

SYS_RESET#

SUS_STAT#

EXT_WAK#

EXT_SCI#

USB_VD1- 30

USB_VD5+ 39

USB_VD5- 39

VBIAS

CLK_32KX1

CLK_32KX2

RTCRST#

IAC_SDATAO

R649 100K

R650 10K

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

0

0

1

0

1

0110

T145PAD

T147PAD

T148PAD

T149PAD

T150PAD

T151PAD

T152PAD

T153PAD

R639 22.6/F

HL[0..10] 7

T154PAD

R643 37.4/F

LPC_DRQ0# 26

LPC_DRQ1# 25

LFRAME#/FWH4 25

VCCRTC

SLP_S3# 25

T155PAD

SLP_S5# 25

SUSCLK 22

T122PAD

SLP_S1#_G

STP_PCI# 14

STP_CPU# 14,43

SUS_STAT# 15

EXT_WAK# 25

EXT_SCI# 25

T199PAD

T200PAD

T123PAD

T125PAD

T126PAD

T128PAD

T130PAD

T131PAD

T132PAD

T133PAD

T134PAD

6

Board Revision

PROTO1

PROTO3

PROTO4

PROTO4.5

Proto 5

Proto 5.5

Pre-QT

INTRUDER# 32

+3VSUS

R888 0_NC

6

12

+3VSUS

IAC_SDATAO

C1165

C1164

.01U

.01U

DELAY_IMVP_PWRGD

SLP_S1#_G

SLP_S3#

OC4#

OC5#

Title

ICH4-M (USB,HUB,LPC)

Size Document Number Rev

Date: Sheet

7

R629

R630

10K

10K_NC

1 2

R634

10K_NC

1 2

NC

HUBREF 7

C1517

.047U

RP109

10P8R-10K

C1168

1U_16V

4

1 2

R635

10K

1 2

C1742

10P_NC

5

4

3

2

1

BID0

BID1

BID2

R648 47

R1126 0

C1741

VCCRTC

C1167

.1U

R892 0_NC

+3VSUS

5

2

1

U112

7SH08

6

7

8

9

10

JM2 3I

星期五, 六月

06, 2003

7

8

+3VRUN

R631

R632

10K

10K_NC

1 2

1 2

R636

R637

10K_NC

10K

1 2

1 2

IAC_SDATAO_MDC 24

IAC_SDATAO_AUDIO 33

SLP_S1# 14

+3VSUS

OC3#

OC2#

OC1#

OC0#

QUANTA

COMPUTER

of

10 49

8

Page 11

1

+1_5VRUN

A A

VTT

B B

C1174

.1U

C1179

.1U

+3VSUS

+1_5VSUS

+1_5VRUN

+3VSUS

C1175

.01

C1180

.01

C1181

.01

2

U81C

C22

VCCPLL

AA23

V_CPU_IO_0

P14

V_CPU_IO_1

U18

V_CPU_IO_2

E9

VCCLAN3_3_1

F9

VCCLAN3_3_0

F6

VCCLAN1_5_0

F7

VCCLAN1_5_1

K10

VCC1_5_0

K12

VCC1_5_1

K18

VCC1_5_2

K22

VCC1_5_3

P10

VCC1_5_4

T18

VCC1_5_5

U19

VCC1_5_6

V14

VCC1_5_7

E11

VCCSUS3_3_0

F10

VCCSUS3_3_1

F15

VCCSUS3_3_2

F16

VCCSUS3_3_3

F17

VCCSUS3_3_4

F18

VCCSUS3_3_5

K14

VCCSUS3_3_6

V7

VCCSUS3_3_7

V8

VCCSUS3_3_8

V9

VCCSUS3_3_9

3

VCC

V5REF_SUS

V5REF1

V5REF2

VCCHI_0

VCCHI_1

VCCHI_2

VCCHI_3

VCCSUS1_5_0

VCCSUS1_5_1

VCCSUS1_5_2

VCCSUS1_5_3

VCCSUS1_5_4

VCCSUS1_5_5

VCCSUS1_5_6

VCCSUS1_5_7

VCC3_3_0

VCC3_3_1

VCC3_3_2

VCC3_3_3

VCC3_3_4

VCC3_3_5

VCC3_3_6

VCC3_3_7

VCC3_3_8

VCC3_3_9

VCC3_3_10

VCC3_3_11

VCC3_3_12

VCC3_3_13

VCC3_3_14

VCC3_3_15

ICH4

E15

E7

V6

L23

M14

P18

T22

E12

E13

E20

F14

G18

R6

T6

U6

A5

AC17

AC8

B2

H18

H6

J1

J18

K6

M10

P12

P6

U1

V10

V16

V18

V5REF_SUS

VCC5REF

4

C1177

C1176

.1U

.1U

C1184

C1183

C1182

.1U

.1U

+1_5VSUS

+3VRUN

22U

C1178

1U_16V_NC

CC0805

C1553

.1U

5

R661

D97

RB751V

C1554

.1U

1K

+1_8VRUN

6

12

+5VRUN

21

+3VRUN

N21

N23

P11

P13

P20

P22

R18

R21

T19

T23

U20

V15

V17

W22

Y19

A16

A18

A20

A22

AA12

AA16

AA22

AA3

AA9

AB20

AB7

AC1

AC10

AC14

AC18

AC23

AC5

B12

B16

B18

B20

B22

C15

C17

C19

U81D

VSS000

VSS001

N5

VSS002

VSS003

VSS004

VSS005

VSS006

P3

VSS007

VSS008

VSS009

R5

VSS010

T1

VSS011

VSS012

VSS013

VSS014

VSS015

VSS016

V3

VSS017

VSS018

W5

VSS019

W8

VSS020

VSS021

Y7

VSS022

A1

VSS023

VSS024

VSS025

VSS026

VSS027

A4

VSS028

VSS029

VSS030

VSS031

VSS032

VSS033

VSS034

VSS035

VSS036

VSS037

VSS038

VSS039

VSS040

VSS041

VSS042

VSS043

VSS044

VSS045

VSS046

B9

VSS047

VSS048

VSS049

VSS050

GND

7

C21

VSS051

C23

VSS052

C6

VSS053

D1

VSS054

D12

VSS055

D15

VSS056

D17

VSS057

D19

VSS058

D21

VSS059

D23

VSS060

D4

VSS061

D8

VSS062

D22

VSS063

E10

VSS064

E14

VSS065

E16

VSS066

E17

VSS067

E18

VSS068

E19

VSS069

E21

VSS070

E22

VSS071

F8

VSS072

G19

VSS073

G21

VSS074

G3

VSS075

G6

VSS076

H1

VSS077

J6

VSS078

K11

VSS079

K13

VSS080

K19

VSS081

K23

VSS082

K3

VSS083

L10

VSS084

L11

VSS085

L12

VSS086

L13

VSS087

L14

VSS088

L21

VSS089

M1

VSS090

M11

VSS091

M12

VSS092

M13

VSS093

M20

VSS094

M22

VSS095

N10

VSS096

N11

VSS097

N12

VSS098

N13

VSS099

N14

VSS100

N19

VSS101

8

100U

CC7343

+1_5VSUS

+3VRUN

C1192

22U

+1_5VRUN

C1203

1

C1185

22U

+

C1193

22U

C1186

.1U

C1204

22U

C1187

.1U

C1194

.1U

C1205

.1U

C1555

.1U

C1195

.1U

C1206

.1U

C1556

.1U

C1196

.1U

C1207

.1U

2

C C

D D

C1197

.1U

C1208

.1U

+3VSUS

C1188

22U

C1198

.1U

C1570

.1U

C1199

.1U

C1571

.1U

C1189

4.7U

C1200

.1U

C1572

.1U

C1190

.1U

3

C1201

.1U

C1573

.1U

C1191

.1U

C1202

.1U

C1209

22U

C1557

.1U

+3VSUS

C1564

.1U

C1558

.1U

C1565

.1U

C1210

.1U

C1559

.1U

C1566

.1U

C1211

.1U

4

C1560

.1U

C1567

.1U

C1212

.1U

C1561

.1U

C1568

.1U

C1213

.1U

C1562

.1U

C1569

.1U

10U_6.3V

C1563

.1U

C1214

+1_5VSUS

R923

12

1K

C1591

1U_16V_NC

CC0805

06, 2003

7

D99

RB751V

V5REF_SUS

C1590

C1589

.1U

.1U

C1216

C1215

.1U

5

C1217

C1574

.1U

.1U

.1U

Proprietary Note: This sheet of engineering

drawings and specifications contains

Confidential, Trade Secret and other Proprietary

information of Dell Computer Corporation

("Dell"). This document may not be transferred

or copied without the express written

authorization of Dell. In addition, neither this

sheet nor the information it contains may be

used by or disclosed to any third party without

Dell's express written consent."

C1575

.1U

C1576

.1U

Title

ICH4-M (POWER&GND)

Size Document Number Rev

JM2 3A

星期五, 六月

6

Date: Sheet

+5VSUS

21

+3VSUS

QUANTA

COMPUTER

of