Page 1

5

4

3

2

1

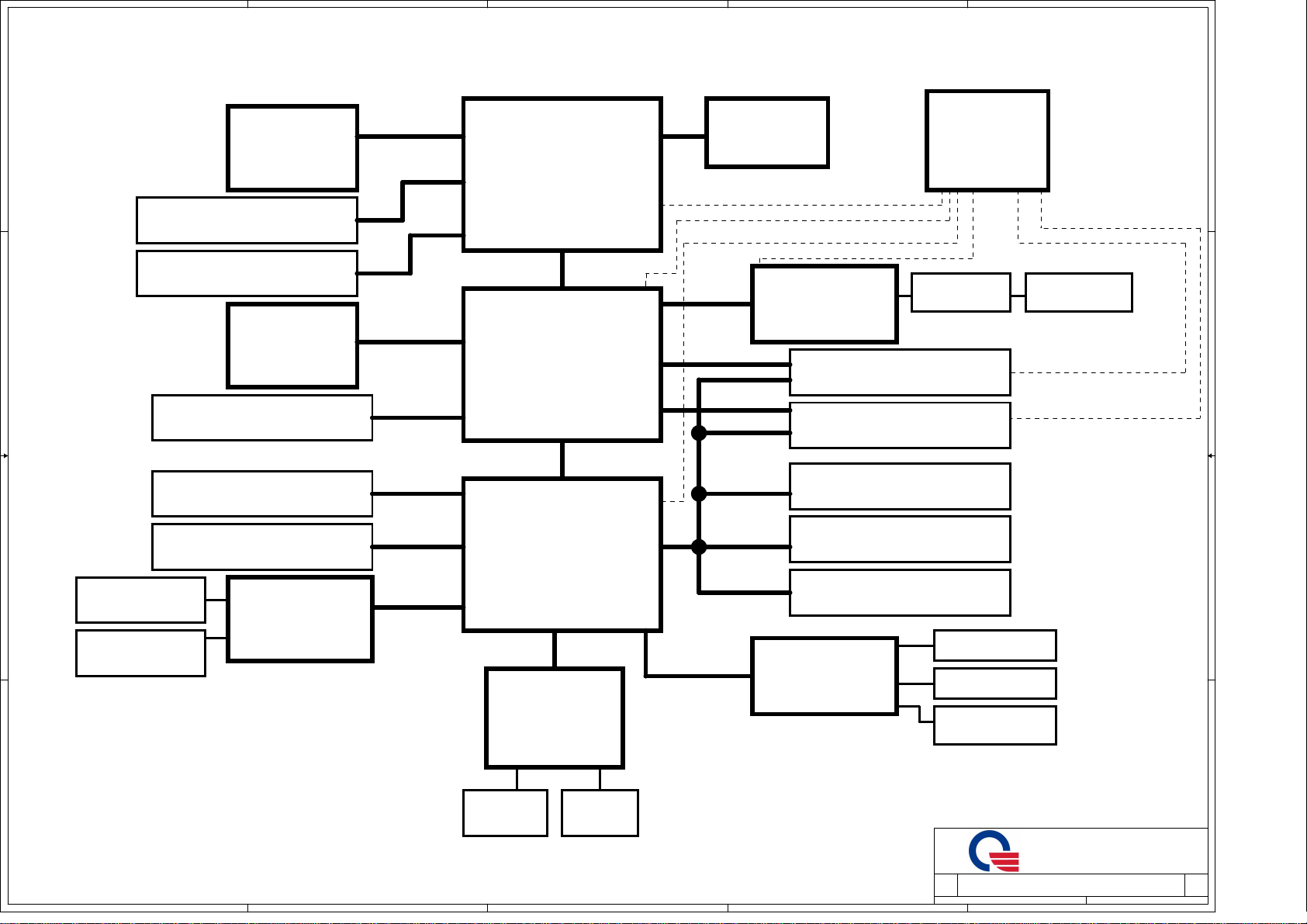

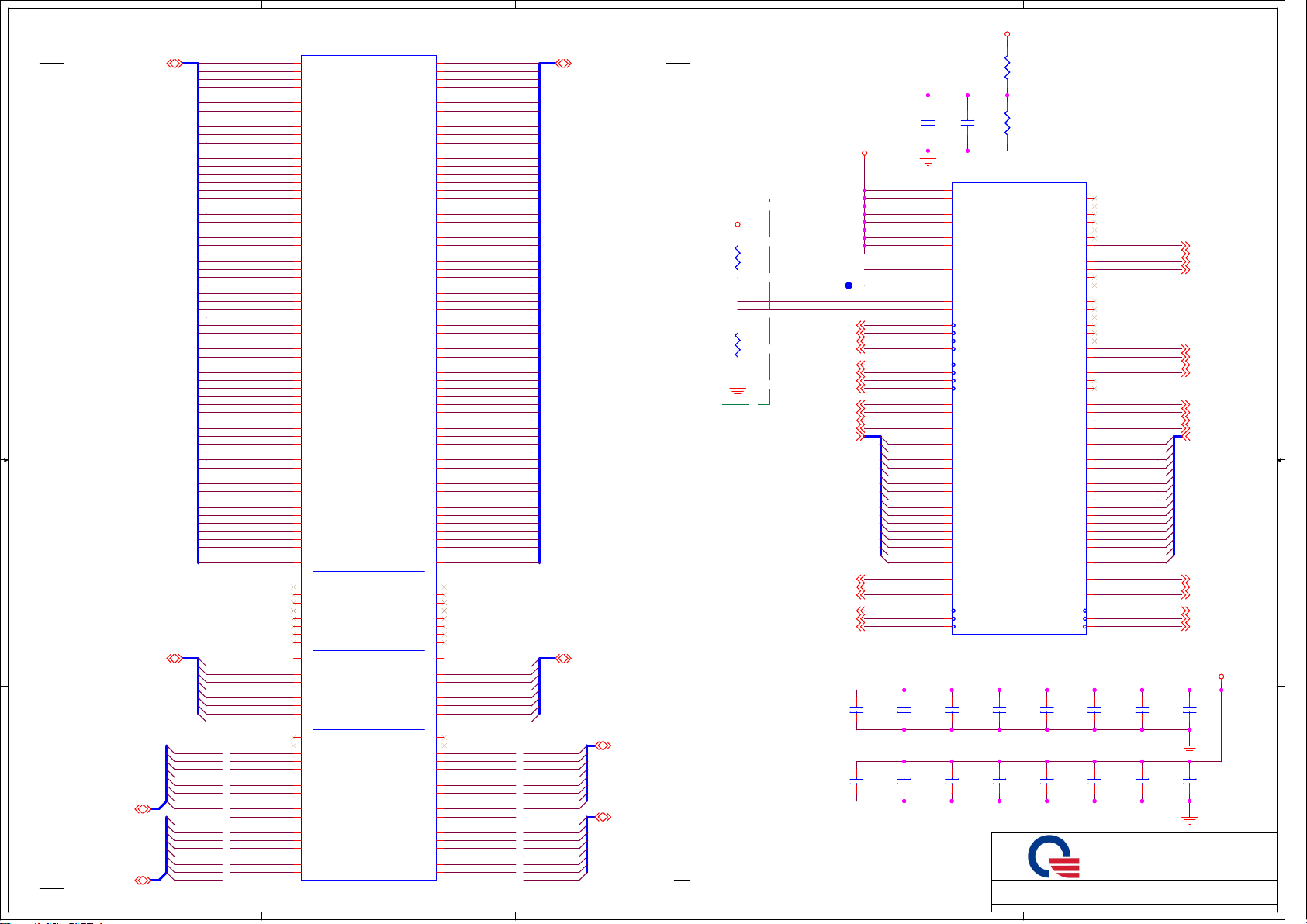

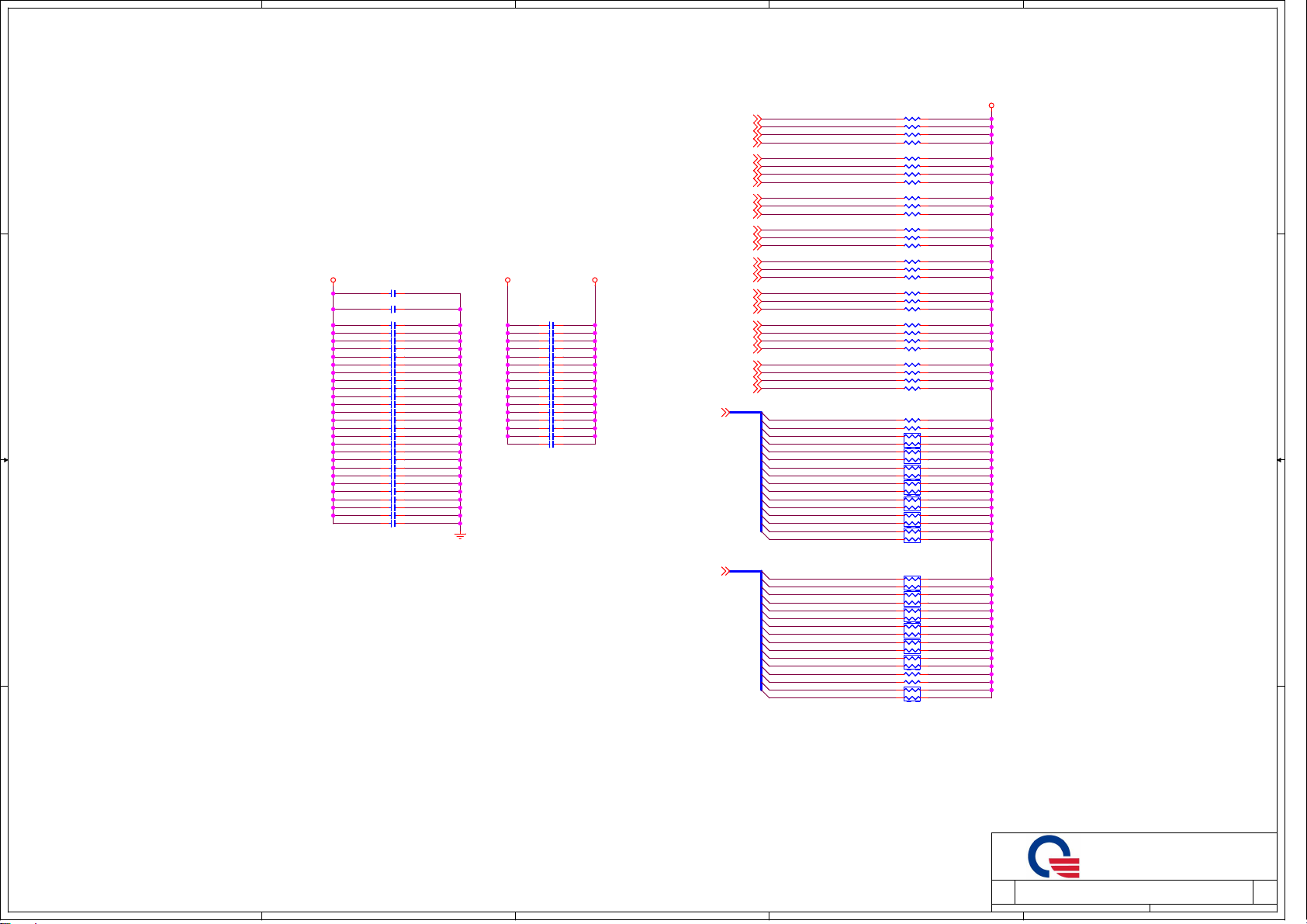

GT1 SYSTEM BLOCK DIAGRAM

D D

Thersmal Sensor

GMT CPU

G781

(MSSOP-8)

Page 6

DDRII 800

CPU

AMD

Athlon 2650(Single Core) 15W

Athlon x 2 3250(Dual Core) 22W

SO-DIMM

Max. 2GB

SO-DIMM

Max. 2GB

Page 8~9

Page 8~9

DDRII 800

HT_LINK 1

Thersmal Sensor

C C

GMT CPU

G781

(MSSOP-8)

18" LCD

24bit 1ch. 2 Lamp

Page 12

LVDS

Page 19

AM2

Page 4~7

North Bridge

AMD

RS690MC

(BGA 465)

21 x 21 mm

Page 10~13

FAN Driver

GMT

G995

Page 26

(SO8)

NBSRC_CLKP,NBSRC_CLKN,SBLINK_CLKP,SBLINK_CLKN

CPUCLKP,CPUCLKN

SBSRCCLKP,SBSRCCLKN

PCIE0

PCIE1

USB8

PCIE2

USB2

CLK_PCIE_LAN,CLK_PCIE_LAN#

LAN

Broadcom

Transformer RJ45

BCM5784M

(68 BGA)

Page 22

Mini Card (WLAN)

PCI Express

Mini Card (DTV)

PCI Express

CLOCK GEN

ICS

ICS951462

(64 Pin TSSOP)

Page 3

Page 22 Page 22

CLK_PCIE_WLAN,CLK_PCIE_WLAN#

Page 24

CLK_PCIE_TV,CLK_PCIE_TV#

Page 24

1

A-LINK (x4)

HDD

2.5" , 9.5mm

Page 25

ODD

B B

Card Reader

MS,SD

Page 21

1394

Page 20

NB Tray , 12.7mm

Media Card/1394

(128 Pin TQFP)

14 x 14 mm

Page 25

RICOH

R5C833

Page 20

SATA0

SATA1

PCI

South Bridge

AMD

SB600

(BGA 594)

23 x 23 mm

Page 14~18

LPC

USB0,3,4,5,7,9

USB6

USB1

Azallia

EC

ITE

ITE8502E

(128 Pin LQFP)

16 x 16 mm

A A

SPI

Page 28

USB IO Port

Single*2 , Dual*2 (total 6)

WEBCAM + DMIC

2.5" , 9mm

CIR OR

BLUETOOTH

Audio Codec

Realtek

ALC269

(QFN64)

6 x 6 mm

Page 23

Page 27

Page 19

Page 26/19

Headphone

Page 23

MIC

Page 23

Speaker

2W

Page 23

PS2BIOS ROM

1MB

Page 28 Page 26

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet

PROJECT :

GT1

GT1

GT1

A

A

A

of

36

36

36

1

1

1

1

Page 2

5

4

3

2

1

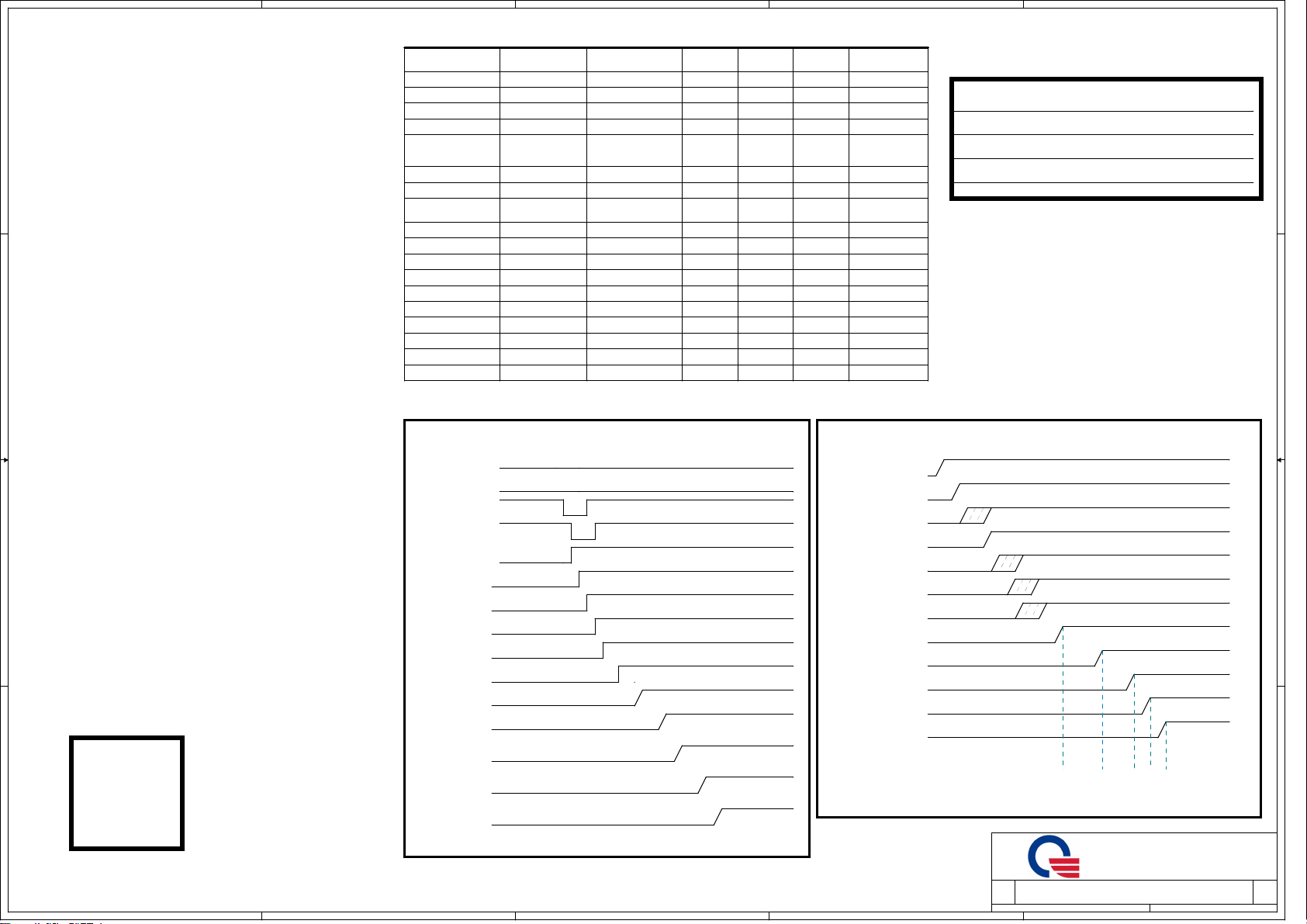

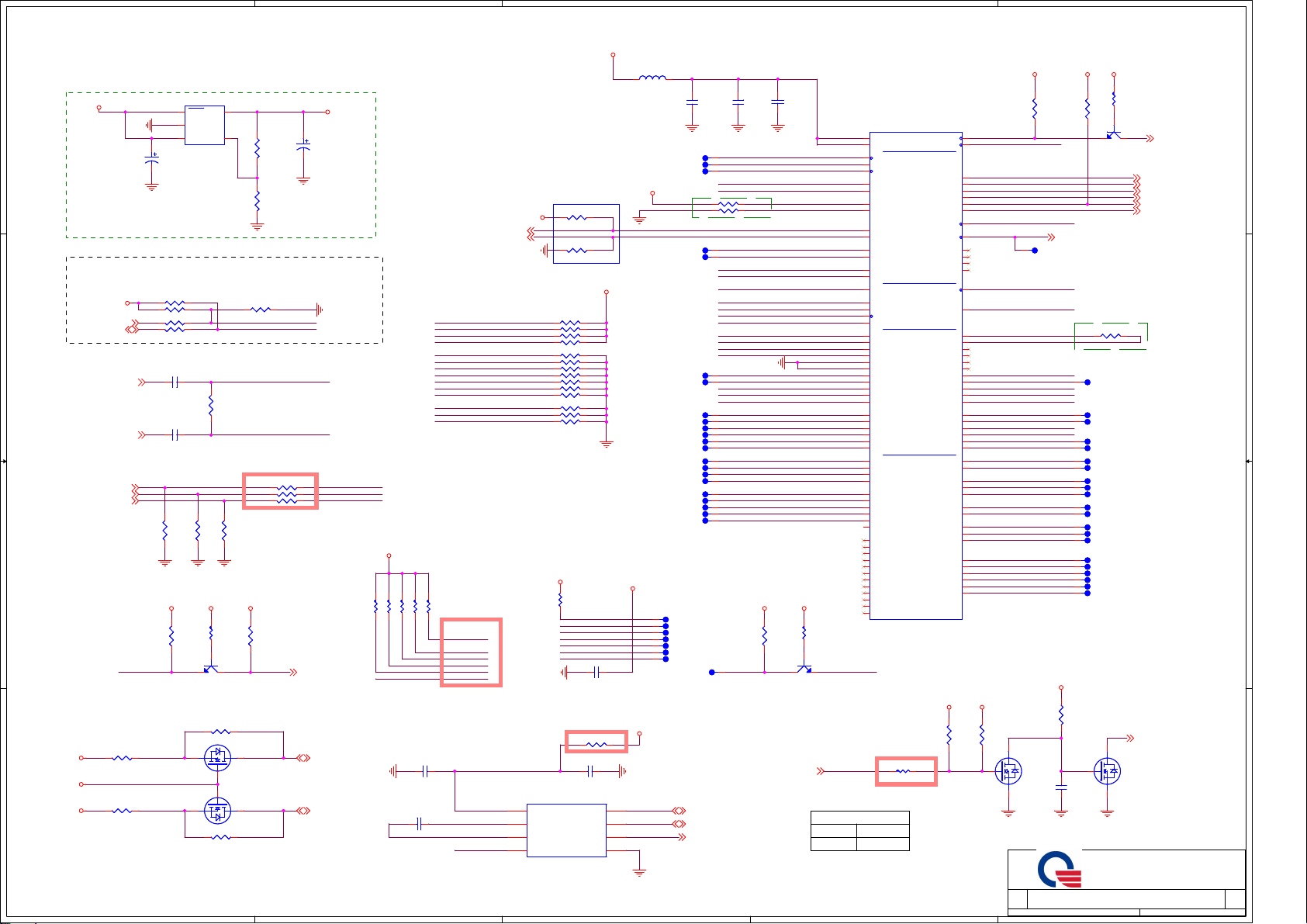

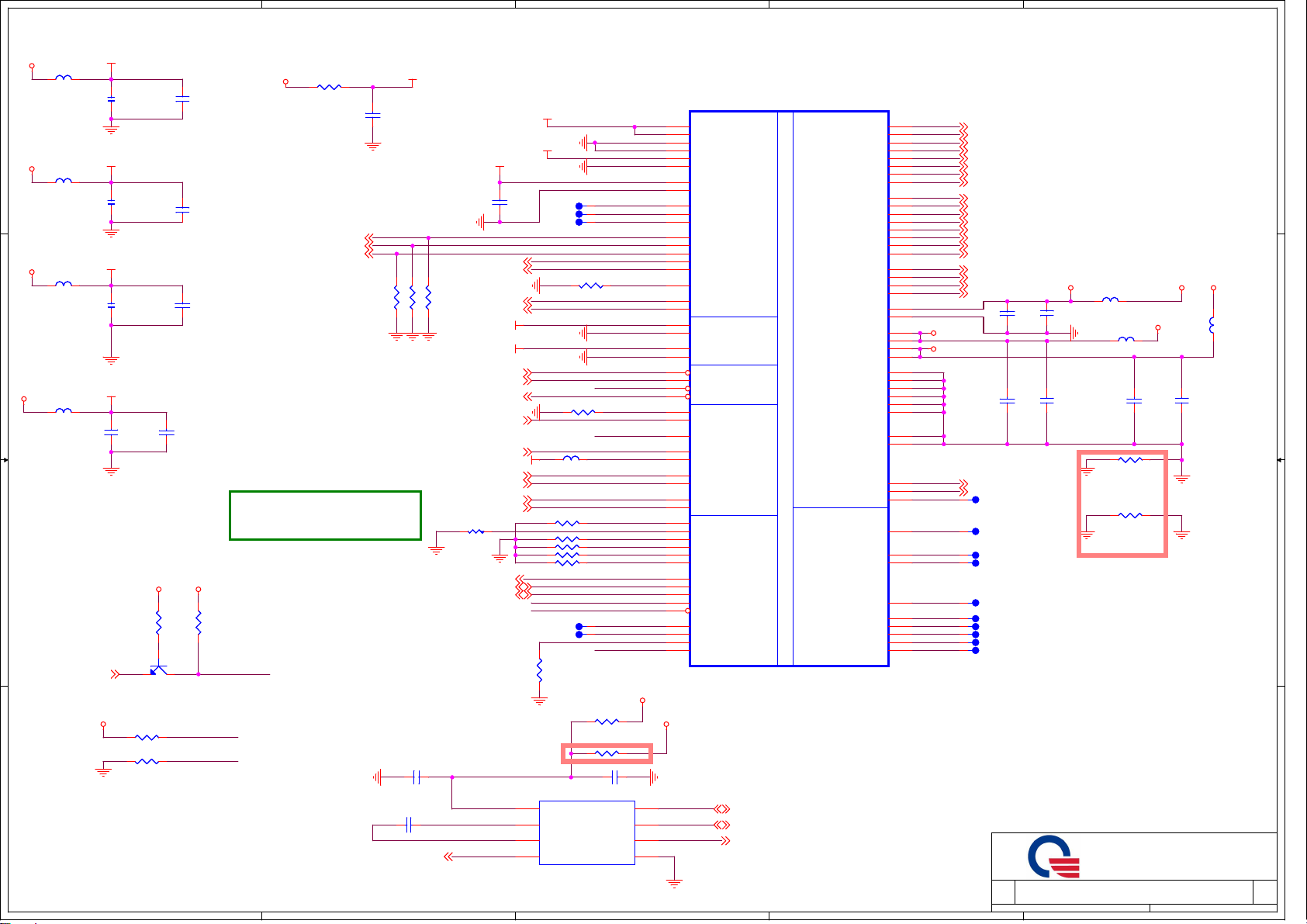

Voltage Rails

Power S0~S2 Ctl SignalS3 S4 S5

15VPCU

5VPCU

3VPCU

D D

VCCRTC

+3.3VALW

+1.2VALW 1.2V

5VSUS

3VSUS

1.8VSUS

SMDDR_VTERM

VCC5

VCC3

VCC1.8 1.8V

VCC1.5

VCC1.2 1.2V

C C

VLDT_RUN 1.2V

CPU_VCCA 2.5V V MAINON

CPU_CORE

Power On Sequence

ACIN

5VPCU/3VPCU/15VPCU

NBSWON#

PWRBTN#

RVCC_ON

B B

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : GND

A A

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : BOT

5

RSMRST#

SUSB#,SUSC#

SUSON

MAINON

VSUS,VCC

VR_ON

CPU_CORE

NB_PWRGD

PWROK

PCIRST#

4

Voltage

15V

5V

3V

3V

3V

5V

3V

1.8V SUSON

0.9V

5V

3V

1.5V

0.9V

V V V V

V V V V

V V V V

V V V

V V

VV

V

V

VV

VV

V V

V

V

V

V

V

V

V

V

3

V

V

V

STB_ON_D

STB_ON

SUSON

SUSON

SUSON

MAINON

MAINON

MAINON

MAINON

MAINON

VLDT_ON_D

VRON

+5VALW

RSMRST#

PS_ON, SLP_S3#, SLP_S5#

+12V,5V,3.3V

VDRM_PWRGD

VCC_NB_PWRGD

VRM_PWRGD

NB_PWRGD

SB_PWRGD

CPU_PWRGD

PCI_RST#

CPU_RST#

PCI DEVICES IRQ ROUTING

IDSEL# InterruptsPCI DEVICE REQ# / GNT#

NANB(RS690)

SB(SB600)

IDSEL INTA#/INTB#R5C833 REQ#/GNT#

NA NA NA

INTE# PCICLK0REQ0#/GNT0#DEVSEL#

BONEFISH POWER UP SEQUENCE

T2

T3T1

T1>= 70 ms

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

System Infromation

System Infromation

System Infromation

Date: Sheet

Date: Sheet

2

Date: Sheet

1ms < T2 < 10ms

1ms < T3 < 5ms

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

GT1

GT1

GT1

2 36Thursday, April 09, 2009

2 36Thursday, April 09, 2009

2 36Thursday, April 09, 2009

1

CLK

PCICLK

of

of

of

2

A

A

A

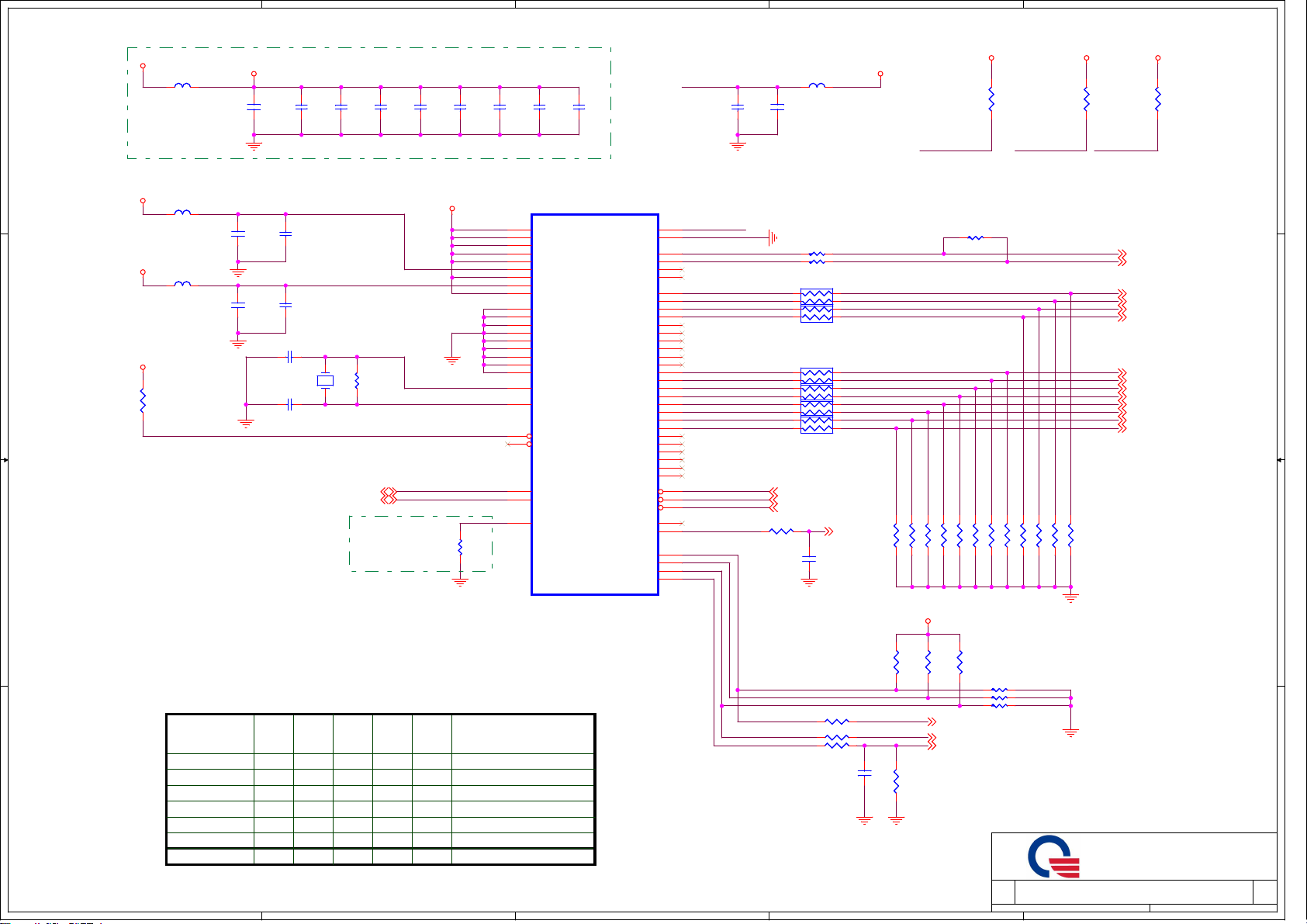

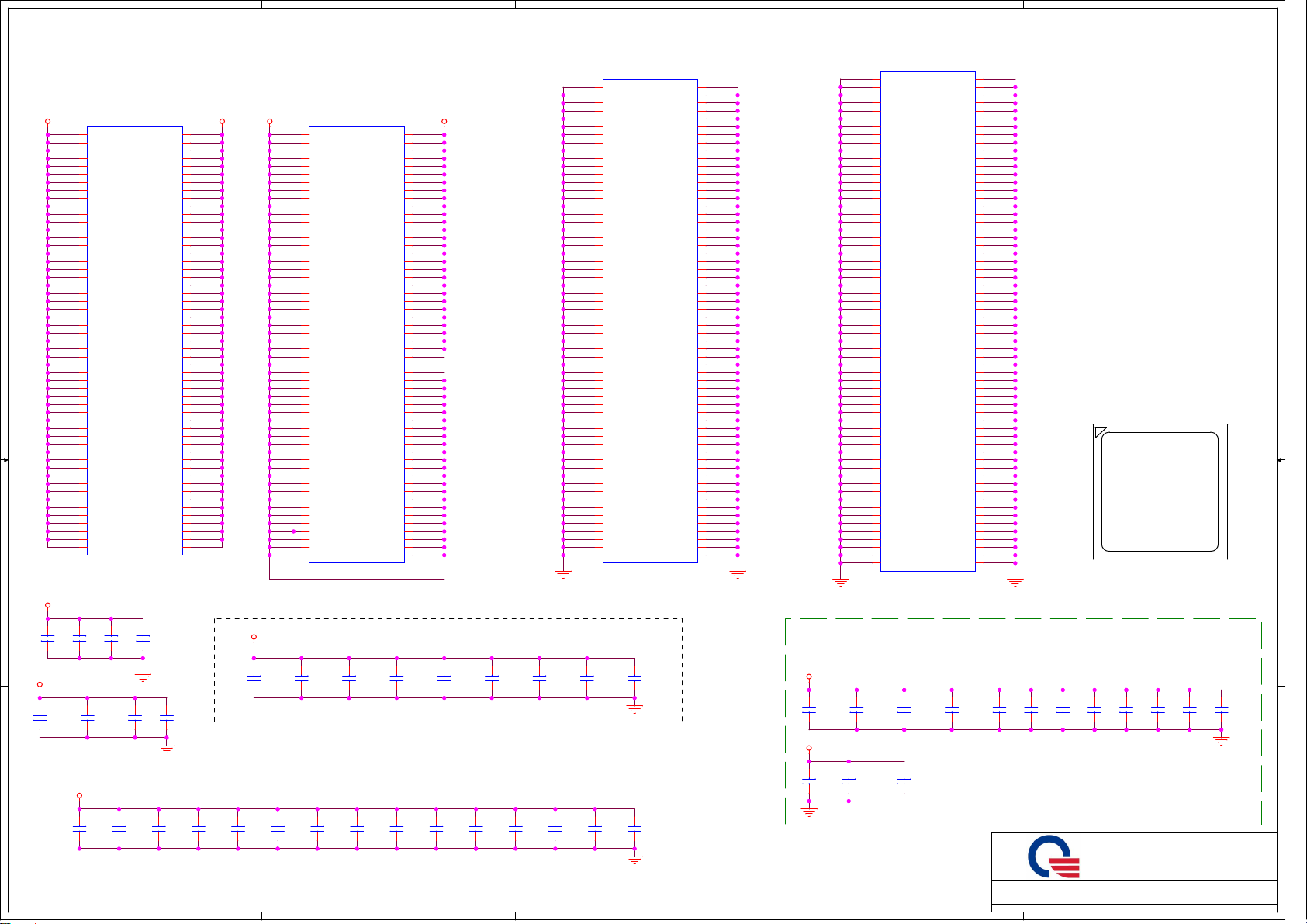

Page 3

5

4

3

2

1

VCC3

L421 BK1608HS600L421 BK1608HS600

D D

CLK_VDD

C521

C521

10U_0805

10U_0805

C203

C203

0.1U

0.1U

C217

C217

0.1U

0.1U

C523

C523

0.1U

0.1U

C208

C208

*0.1U

*0.1U

C207

C207

0.1U

0.1U

C233

C233

0.1U

0.1U

C223

C223

0.1U

0.1U

C234

C234

0.1U

0.1U

CLK_VDDA

L422 BLM18AG221SN1D_6L422 BLM18AG221SN1D_6

C533

C533

C534

C534

0.1U

0.1U

10U_0805

10U_0805

VCC3

CLKREQ_WLAN# CLKREQ_LAN# CLKREQ_TV#

VCC3 VCC3 VCC3

R574

R86

R86

10K

10K

R574

10K

10K

R570

R570

10K

10K

3

Put Decoupling Caps close to Clock Fen. power pin

VCC3

C202

C202

*0.1U

*0.1U

C191

C191

*0.1U

*0.1U

Y402

Y402

14.318MHZ

14.318MHZ

CLK_VDD_USB

CLK_VDD_REF

21

R535

R535

*1M

*1M

L11 BK1608HS600L11 BK1608HS600

C1921UC192

1U

VCC3

L12 BK1608HS600L12 BK1608HS600

C2011UC201

1U

C C

CLK_VDD

R87

R87

10K

10K

C522 33PC522 33P

C525 33PC525 33P

Parallel Resonance Crystal

SCLK0(8,15)

SDATA0(8,15)

Ioh = 5 * Iref

(2.32mA)

Voh = 0.71V @ 60 ohm

B B

EXT CLK FREQUENCY SELECT TABLE(MHZ)

FS0

FS1

FS2

0 0 0

0 0 1

A A

0 1 0

0 1 1

1 0 0

1 0 1

1 1 1

5

CPU

Hi-Z

X

180.00

220.00

100.00

133.33

200.00

SRCCLK

[2:1]

100.00

100.00

100.00

100.00

100.00

100.00

100.00

HTT

PCI

Hi-Z

Hi-Z

X/3 X/6

30.00

60.00

73.12

36.56

66.66

33.33

33.33

66.66

66.66

33.33 48.00

4

CLK_VDD

CLK_XIN

CLK_XOUT

R559

R559

475/F

475/F

CLKREQA# CONTROL SRC5,6,7

CLKREQB# CONTROL SRC2,3,4 ATIG3

CLKREQC# CONTROL SRC0,1 ATIG0,1,2

USB

48.00

48.00

48.00

48.00

48.00

48.00

COMMENT

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

54

14

23

28

44

5

39

2

60

53

15

22

29

45

8

38

1

58

3

4

11

61

9

10

48

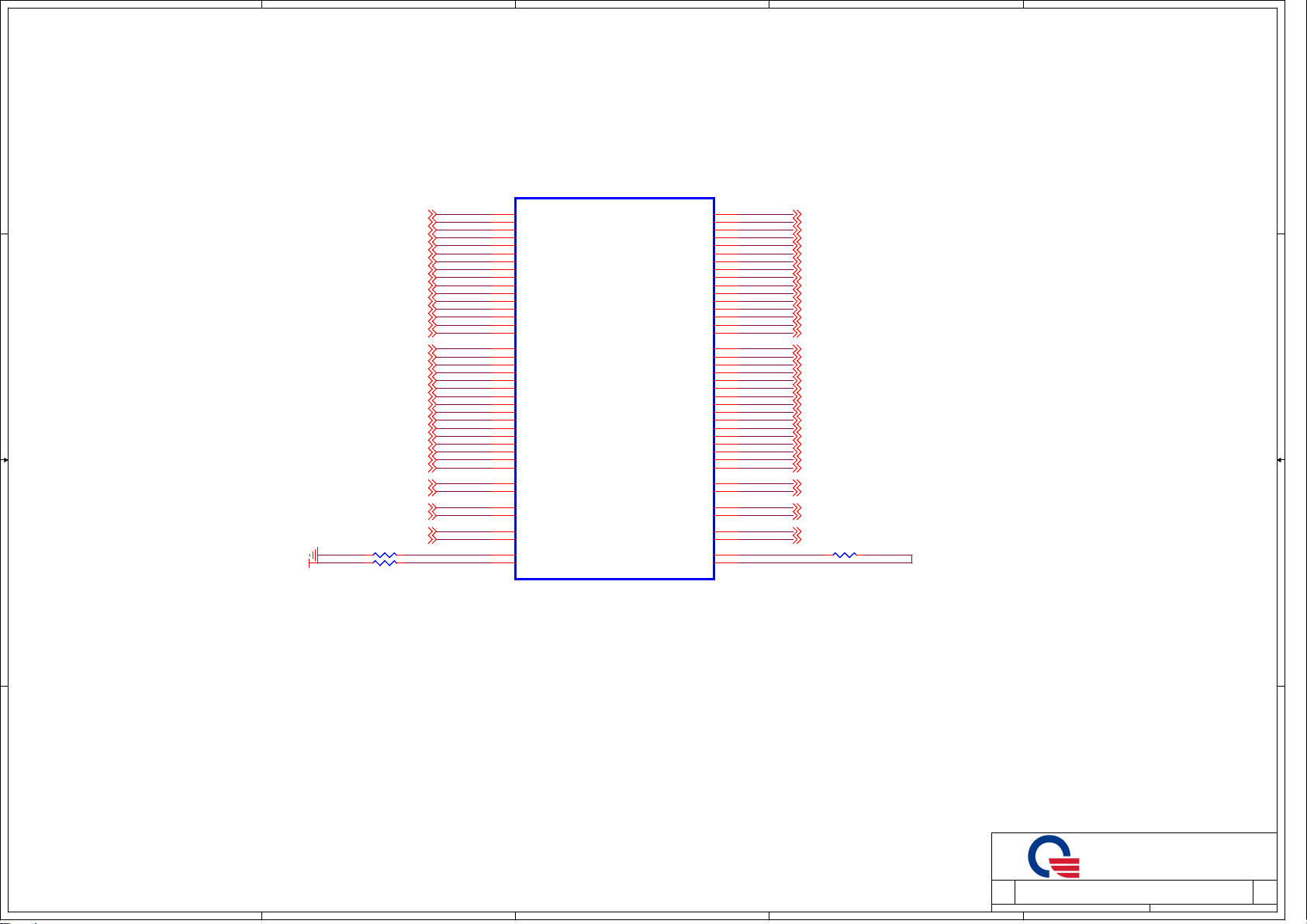

U409

U409

VDDCPU

VDD_SRC1

VDD_SRC2

VDD_SRC3

VDD_SRC4

VDD_48

VDD_ATIG

VDD_REF

VDDHTT

GND_CPU

GND_SRC1

GND_SRC2

GND_SRC3

GND_SRC4

GND_48

GND_ATIG

GND_REF

GNDHTT

XIN

XOUT

RESET_IN#

NC

SMBCLK

SMBDAT

IREF

ICS951462

ICS951462

Normal ATHLON64 operation

Check AMD clock

VDDA

GNDA

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

SRCCLKT6

SRCCLKC6

ATIGCLKT0

ATIGCLKC0

ATIGCLKT1

ATIGCLKC1

ATIGCLKT2

ATIGCLKC2

ATIGCLKT3

ATIGCLKC3

SRCCLKT5

SRCCLKC5

SRCCLKT4

SRCCLKC4

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT0

SRCCLKC0

SRCCLKT1

SRCCLKC1

SRCCLKT7

SRCCLKC7

CLKREQA#

CLKREQB#

CLKREQC#

48MHz_1

48MHz_0

FS1/REF1

FS0/REF0

FS2/REF2

HTTCLK0

3

50

49

56

55

52

51

16

17

41

40

37

36

35

34

30

31

18

19

20

21

24

25

26

27

47

46

43

42

12

13

57

32

33

7

6

63

64

62

59

CLK_VDDA

CPUCLK_EXT_R

CPUCLK#_EXT_R

SBLINK_CLKP_R

SBLINK_CLKN_R

NBSRC_CLKP_R

NBSRC_CLKN_R

SBSRC_CLKP_R

SBSRC_CLKN_R

GPP_CLK0P_R

GPP_CLK0N_R

GPP_CLK1P_R

GPP_CLK1N_R

GPP_CLK2P_R

GPP_CLK2N_R

CLKREQ_WLAN#

CLKREQ_LAN#

CLKREQ_TV#

CLK_48M_2_R

R546 47.5/FR546 47.5/F

R549 47.5/FR549 47.5/F

3

RP401 33X2RP401 33X2

1

1

RP404 33X2RP404 33X2

3

3

RP402

RP402

1

3

RP403

RP403

1

3

RP405

RP405

1

3

RP406

RP406

1

CLKREQ_WLAN# (24)

CLKREQ_LAN# (22)

CLKREQ_TV# (24)

R545 33R545 33

C527

C527

10P

10P

SB_OSCIN_R

NB_OSCIN_R

HTREFCLK_R

R77 33R77 33

R82 33R82 33

R541 33R541 33

4

2

2

4

4

33X2

33X2

2

4

33X2

33X2

2

4

33X2

33X2

2

4

33X2

33X2

2

USBCLK (15)

C526

C526

10P

10P

R572 49.9/FR572 49.9/F

R78

R78

10K

10K

R84

R84

49.9/F

49.9/F

2

R548 261/FR548 261/F

R565 49.9/FR565 49.9/F

R567 49.9/FR567 49.9/F

R571 49.9/FR571 49.9/F

CLK_VDD

R537

R537

10K

10K

SB_OSCIN (15)

NB_OSC (12)

HTREFCLK (12)

CPUCLKP (6)

CPUCLKN (6)

SBLINK_CLKP (12)

SBLINK_CLKN (12)

NBSRC_CLKP (12)

NBSRC_CLKN (12)

CLK_PCIE_WLAN (24)

CLK_PCIE_WLAN# (24)

CLK_PCIE_LAN (22)

CLK_PCIE_LAN# (22)

SBSRCCLKP (14)

SBSRCCLKN (14)

CLK_PCIE_TV (24)

CLK_PCIE_TV# (24)

R555 49.9/FR555 49.9/F

R558 49.9/FR558 49.9/F

R560 49.9/FR560 49.9/F

R83

R83

10K

10K

R79 *0R79 *0

R536 *0R536 *0

R80 *0R80 *0

R566 49.9/FR566 49.9/F

R564 49.9/FR564 49.9/F

R556 49.9/FR556 49.9/F

R557 49.9/FR557 49.9/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

R550 49.9/FR550 49.9/F

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Clock Generator

Clock Generator

Clock Generator

GT1

GT1

GT1

3 36Thursday, April 09, 2009

3 36Thursday, April 09, 2009

3 36Thursday, April 09, 2009

1

A

A

A

of

of

of

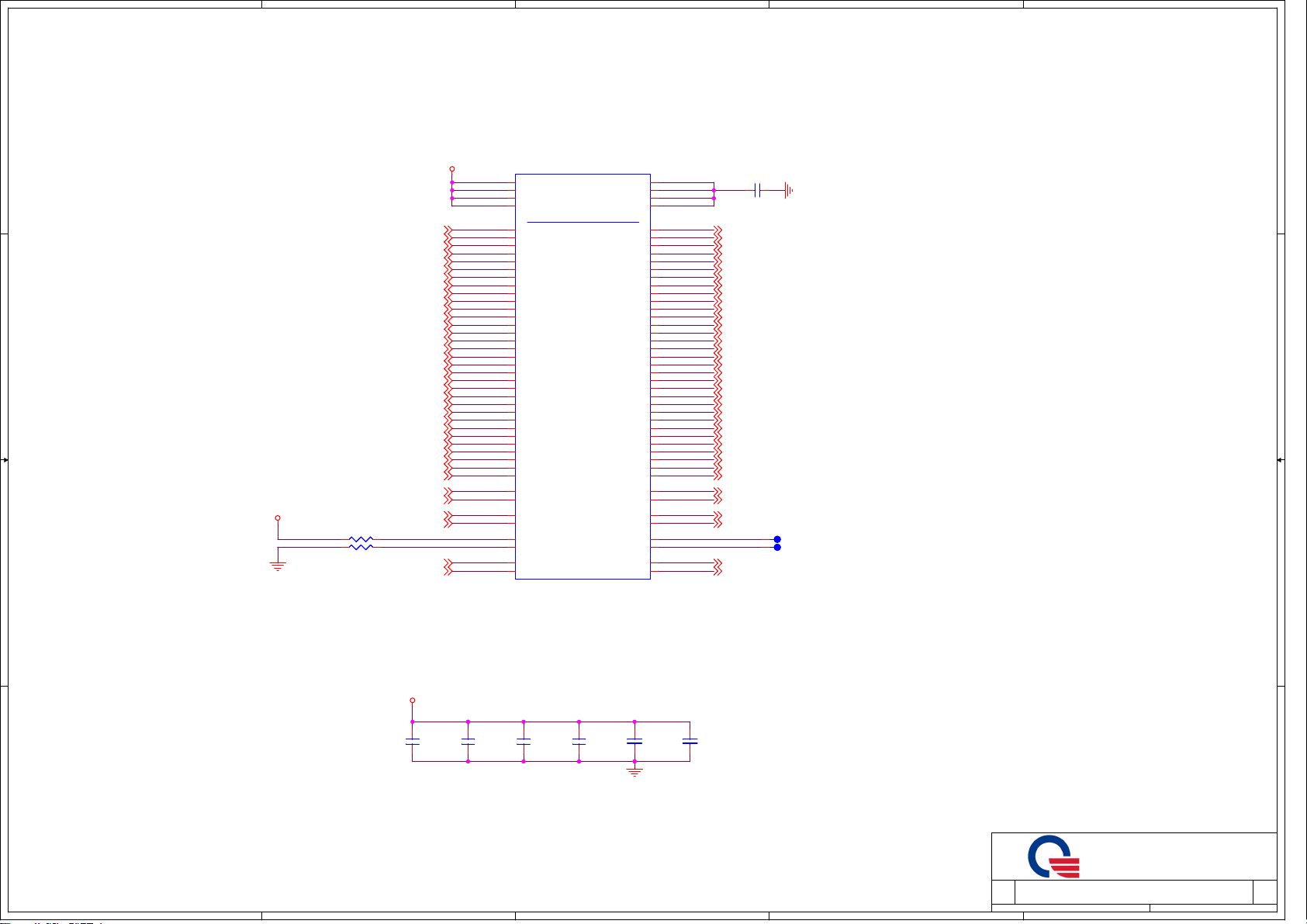

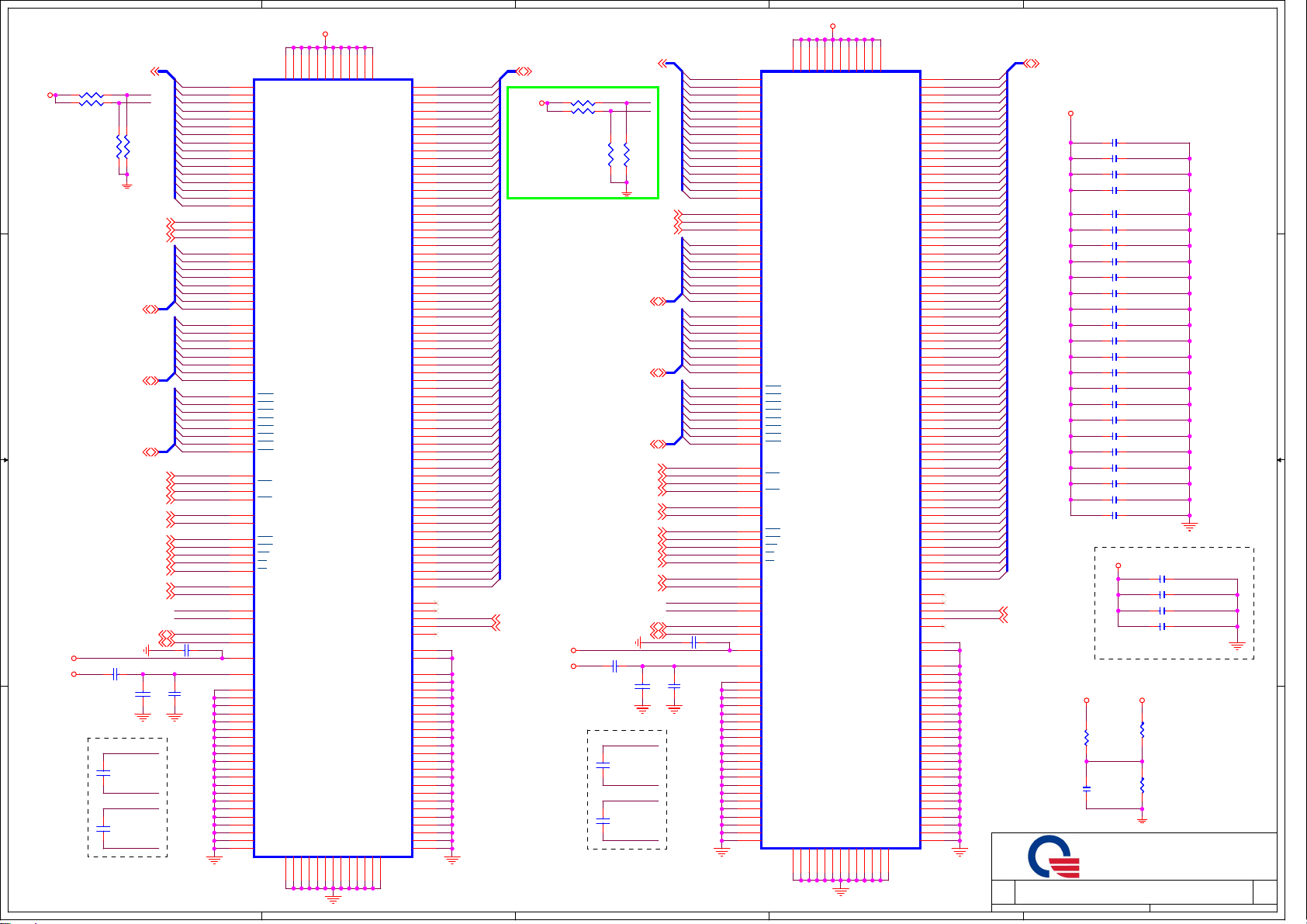

Page 4

5

4

3

2

1

4

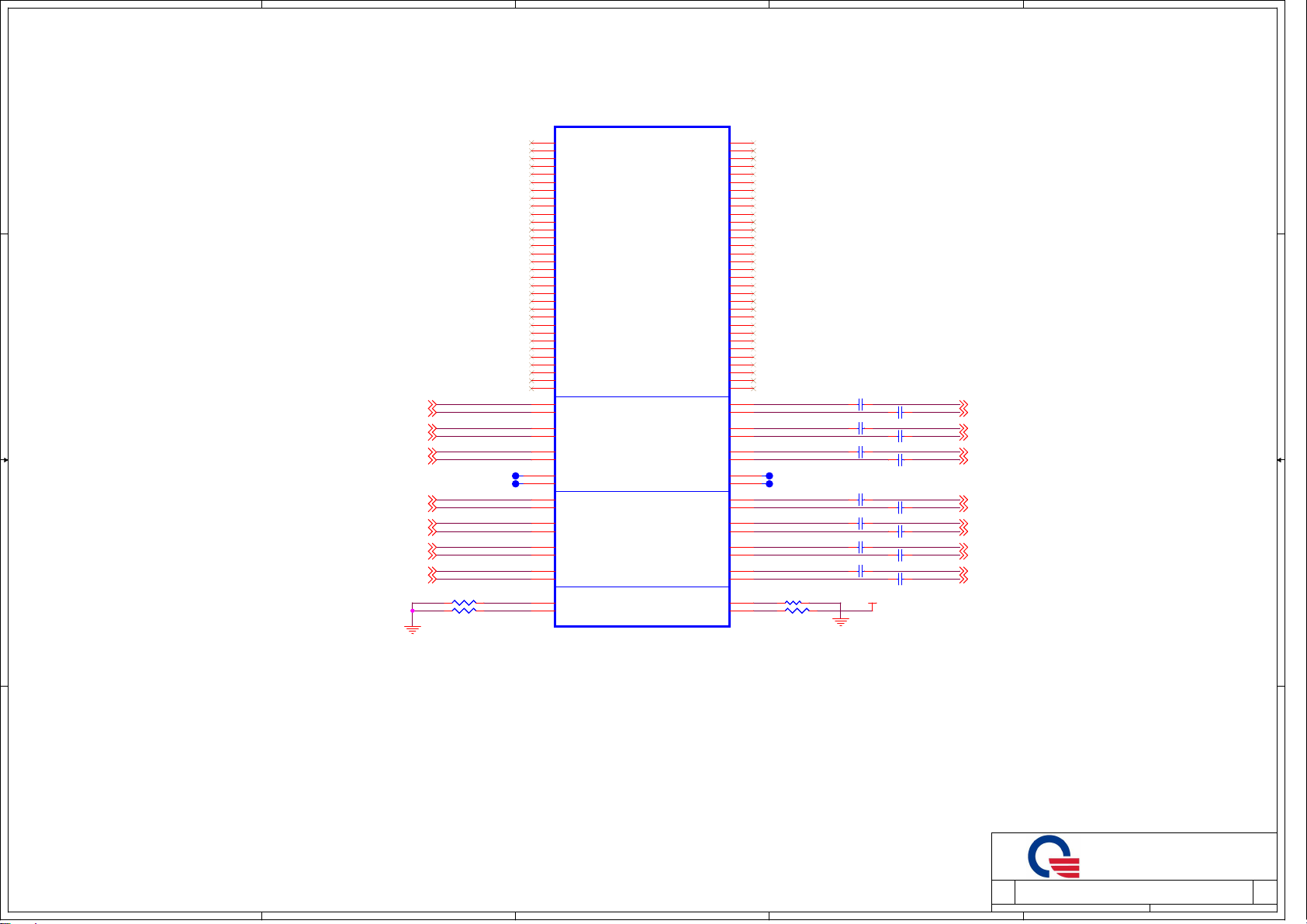

CPU HyperTransport Interface

D D

C C

VLDT_RUN

R10 49.9/FR10 49.9/F

R11 49.9/FR11 49.9/F

B B

VDDLDTRUNCPU is connected to the VDD_LDT_RUN power

supply through the package or on the die. It is only connected

on the board to decoupling near the CPU package.

VLDT_RUN

HT_CADIN15_P(10)

HT_CADIN15_N(10)

HT_CADIN14_P(10)

HT_CADIN14_N(10)

HT_CADIN13_P(10)

HT_CADIN13_N(10)

HT_CADIN12_P(10)

HT_CADIN12_N(10)

HT_CADIN11_P(10)

HT_CADIN11_N(10)

HT_CADIN10_P(10)

HT_CADIN10_N(10)

HT_CADIN9_P(10)

HT_CADIN9_N(10)

HT_CADIN8_P(10)

HT_CADIN8_N(10)

HT_CADIN7_P(10)

HT_CADIN7_N(10)

HT_CADIN6_P(10)

HT_CADIN6_N(10)

HT_CADIN5_P(10)

HT_CADIN5_N(10)

HT_CADIN4_P(10)

HT_CADIN4_N(10)

HT_CADIN3_P(10)

HT_CADIN3_N(10)

HT_CADIN2_P(10)

HT_CADIN2_N(10)

HT_CADIN1_P(10)

HT_CADIN1_N(10)

HT_CADIN0_P(10)

HT_CADIN0_N(10)

HT_CLKIN1_P(10)

HT_CLKIN1_N(10)

HT_CLKIN0_P(10)

HT_CLKIN0_N(10)

HT_CTLIN0_P(10)

HT_CTLIN0_N(10)

AJ4

AJ3

AJ2

AJ1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

N6

P6

N3

N2

V4

V5

U1

V1

U401A

U401A

VLDT_06

VLDT_05

VLDT_02

VLDT_01

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

Athlon 64 M2

Processor Socket

VLDT_08

VLDT_07

VLDT_04

VLDT_03

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

HT LINK

HT LINK

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

H6

H5

H2

H1

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

HT_CPU_CTLOUT1_PHT_CTLIN1_P

HT_CPU_CTLOUT1_NHT_CTLIN1_N

C406

C406

4.7U_0603

4.7U_0603

HT_CADOUT15_P (10)

HT_CADOUT15_N (10)

HT_CADOUT14_P (10)

HT_CADOUT14_N (10)

HT_CADOUT13_P (10)

HT_CADOUT13_N (10)

HT_CADOUT12_P (10)

HT_CADOUT12_N (10)

HT_CADOUT11_P (10)

HT_CADOUT11_N (10)

HT_CADOUT10_P (10)

HT_CADOUT10_N (10)

HT_CADOUT9_P (10)

HT_CADOUT9_N (10)

HT_CADOUT8_P (10)

HT_CADOUT8_N (10)

HT_CADOUT7_P (10)

HT_CADOUT7_N (10)

HT_CADOUT6_P (10)

HT_CADOUT6_N (10)

HT_CADOUT5_P (10)

HT_CADOUT5_N (10)

HT_CADOUT4_P (10)

HT_CADOUT4_N (10)

HT_CADOUT3_P (10)

HT_CADOUT3_N (10)

HT_CADOUT2_P (10)

HT_CADOUT2_N (10)

HT_CADOUT1_P (10)

HT_CADOUT1_N (10)

HT_CADOUT0_P (10)

HT_CADOUT0_N (10)

HT_CLKOUT1_P (10)

HT_CLKOUT1_N (10)

HT_CLKOUT0_P (10)

HT_CLKOUT0_N (10)

HT_CTLOUT0_P (10)

HT_CTLOUT0_N (10)

T9T9

T8T8

VLDT_RUN

C404

C404

4.7U_0603

4.7U_0603

A A

5

4

C405

C405

4.7U_0603

4.7U_0603

C410

C410

0.22U

0.22U

C407

C407

0.22U

0.22U

12

3

C408

C408

180P

180P

12

C411

C411

180P

180P

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AMD M2+ HT I/F

AMD M2+ HT I/F

AMD M2+ HT I/F

Date: Sheet

Date: Sheet

2

Date: Sheet

PROJECT :

GT1

GT1

GT1

A

A

A

4 36Thursday, April 09, 2009

4 36Thursday, April 09, 2009

4 36Thursday, April 09, 2009

of

of

1

of

Page 5

5

U401C

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_DM7

M_B_DM6

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

D D

C C

B B

A A

M_B_DQS[0..7](8)

M_B_DQS#[0..7](8)

5

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

K29

K31

G30

G29

L29

L28

H31

G31

AJ14

AH17

AJ23

AK29

C30

A23

B17

B13

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

J29

J31

J30

U401C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_DM8

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H8

MB_DQS_L8

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

Athlon 64 M2

Processor Socket

DDRII: DATA

DDRII: DATA

4

3

Processor DDR2 Memory Interface

M_A_DQ63

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_DM8

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H8

MA_DQS_L8

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

4

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

K25

J26

G28

G27

L24

K27

H29

H27

J25

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

J28

J27

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

F19

F15

G15

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_DM7

M_A_DM6

M_A_DM5M_B_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

To SODIMM socket A (near)To SODIMM socket B (Far)

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQ[0..63] (8)M_B_DQ[0..63](8)

M_A_DM[0..7] (8)M_B_DM[0..7](8)

M_A_DQS[0..7] (8)

M_A_DQS#[0..7] (8)

3

PLACE THEM CLOSE TO

CPU WITHIN 1"

1.8VSUS

R17

R17

39.2F

39.2F

1 2

R15

R15

39.2F

39.2F

1 2

M_A_CS#3(8,9)

M_A_CS#2(8,9)

M_A_CS#1(8,9)

M_A_CS#0(8,9)

M_B_CS#3(8,9)

M_B_CS#2(8,9)

M_B_CS#1(8,9)

M_B_CS#0(8,9)

M_CKE3(8,9)

M_CKE2(8,9)

M_CKE1(8,9)

M_CKE0(8,9)

M_A_A[0..15](8,9)

M_A_BS#2(8,9)

M_A_BS#1(8,9)

M_A_BS#0(8,9)

M_A_RAS#(8,9)

M_A_CAS#(8,9)

M_A_WE#(8,9)

SMDDR_VTERM

T21T21

M_ZN

M_ZP

C61

C61

4.7U_0603

4.7U_0603

C455

C455

1000P

1000P

2

CPU_M_VREF

CPU_M_VREF

VTT_SENSE

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

2

D12

C12

B12

A12

AK12

AJ12

AH12

AG12

AL12

F12

E12

AH11

AJ11

AD27

AA25

AC25

AA24

AE29

AB31

AE30

AC31

M31

M29

L27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

N25

Y27

AA27

AA26

AB25

AB27

C50

C50

4.7U_0603

4.7U_0603

C433

C433

1000P

1000P

C47

C47

0.1U

0.1U

1

1.8VSUS

R22

R22

2K/F

2K/F

C46

C46

R25

R25

1000P

1000P

2K/F

2K/F

U401B

U401B

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA1_CS_L1

MA1_CS_L0

MA0_CS_L1

MA0_CS_L0

MB1_CS_L1

MB1_CS_L0

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

Athlon 64 M2

Processor Socket

C67

C67

4.7U_0603

4.7U_0603

C457

C457

1000P

1000P

MA1_CLK_H2

MA1_CLK_L2

MA1_CLK_H1

MA1_CLK_L1

MA1_CLK_H0

MA1_CLK_L0

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA0_CLK_H0

MA0_CLK_L0

MB1_CLK_H2

MB1_CLK_L2

MB1_CLK_H1

MB1_CLK_L1

MB1_CLK_H0

MB1_CLK_L0

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_CLK_H0

MB0_CLK_L0

MB1_ODT0

MB0_ODT0

MA1_ODT0

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

MB_ADD10

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

C45

C45

4.7U_0603

4.7U_0603

C436

C436

1000P

1000P

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AMD M2+ DDR II Memory I/F

AMD M2+ DDR II Memory I/F

AMD M2+ DDR II Memory I/F

Date: Sheet

Date: Sheet

Date: Sheet

AE20

AE19

G20

G21

V27

W27

AG21

AG20

G19

H19

U27

U26

AL19

AL18

C19

D19

W29

W28

AJ19

AK19

A18

A19

U31

U30

AD31

AD29

AC27

AC28

M_B_A15

N28

M_B_A14

N29

M_B_A13

AE31

M_B_A12

N30

M_B_A11

P29

M_B_A10

AA29

M_B_A9

P31

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_WE_L

C75

C75

0.22U

0.22U

C463

C463

180P

180P

M_B_A8

R29

M_B_A7

R28

M_B_A6

R31

M_B_A5

R30

M_B_A4

T31

M_B_A3

T29

M_B_A2

U29

M_B_A1

U28

M_B_A0

AA30

N31

AA31

AA28

AB29

AC29

AC30

C32

C32

0.22U

0.22U

C439

C439

180P

180P

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

C83

C83

0.22U

0.22U

C464

C464

180P

180P

1

GT1

GT1

GT1

M_CLKOUT1 (8)

M_CLKOUT1# (8)

M_CLKOUT0 (8)

M_CLKOUT0# (8)

M_CLKOUT4 (8)

M_CLKOUT4# (8)

M_CLKOUT3 (8)

M_CLKOUT3# (8)

M_ODT3 (8,9)

M_ODT2 (8,9)

M_ODT1 (8,9)

M_ODT0 (8,9)

M_B_A[0..15] (8,9)

M_B_BS#2 (8,9)

M_B_BS#1 (8,9)

M_B_BS#0 (8,9)

M_B_RAS# (8,9)

M_B_CAS# (8,9)

M_B_WE# (8,9)

SMDDR_VTERM

C41

C41

0.22U

0.22U

C452

C452

180P

180P

5 36Thursday, April 09, 2009

5 36Thursday, April 09, 2009

5 36Thursday, April 09, 2009

of

of

of

5

A

A

A

Page 6

5

4

3

2

1

CPU_VDDA

L1 40ohm_600mAL1 40ohm_600mA

VCC3

D D

Vout =1.25(1+R1/R2)

= 1.25 (1+20K/20K)

= 2.5V

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 300-Ω (±5%) pulldown to VSS.

1.8VSUS

CPU_SIC(14)

CPU_SID(14)

C C

CPUCLKP(3)

CPUCLKN(3)

PU1

PU1

1

SHDN

2

GND

3

VIN

G923-330T1UF

G923-330T1UF

PC7

PC7

10U_0805

10U_0805

R414 *300R414 *300

R417 *300R417 *300

R418 *0R418 *0

R415 *0R415 *0

C423 3900PC423 3900P

C419 3900PC419 3900P

VO

SET

R436

R436

169_0603F

169_0603F

4

5

CPU_SIC_R

CPU_SID_R

PR2

PR2

20K_0603F

20K_0603F

PR3

PR3

20K_0603F

20K_0603F

R416300 R416300

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

PC6

PC6

10U_0805

10U_0805

CPU_VDDA

CPU_CORE

COREFB+V(32)

COREFB-(32)

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

close to CPU

R440 *300R440 *300

R413 300R413 300

R412 1K/FR412 1K/F

R448 510/FR448 510/F

R426 300R426 300

R423 *300R423 *300

R432 *300R432 *300

R437 *300R437 *300

R433 *300R433 *300

R33 *300R33 *300

R422 *300R422 *300

R444 510/FR444 510/F

R442 300R442 300

R32 300R32 300

VLDT_RUN

PR40710/F PR40710/F

PR40810/F PR40810/F

1.8VSUS

IRT

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_HT_RESET#

TALERT# (16)

MBDATA (28)

MBCLK (28)

1.8VSUS

R447 *220R447 *220

R438 *220R438 *220

R443 *220R443 *220

R4 *220R4 *220

R403 *220R403 *220

IF no use which Net

need pull-up or down

CPU_DBREQ#

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

C403 0.1UC403 0.1U

C4 2200P_0603C4 2200P_0603

4

CPU_TDO

H_THERMDA

H_THERMDC

SYS_SHDN#1

IRT

U1

U1

1

VCC

2

DXP

3

DXN

4

-OVT

G781-1

G781-1

MSOP8-4_9-65

MSOP8-4_9-65

HDT Test Point

1.8VSUS

R404

R404

300_4

300_4

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

IRT

R407 shortR407 short

C409 *0.1U/10V_4C409 *0.1U/10V_4

C402

C402

*0.1U

*0.1U

8

SMCLK

7

SMDATA

6

-ALT

5

GND

1.8VSUS

VCC3

THMCLKTHERM_VCC

THMDAT

THERM_ALERT#

3

T402T402

T407T407

T4T4

T424T424

T428T428

T427T427

T5T5

Thermal

Senser

R7

10KR710K

2

2

R420

R420

680

680

VCC3

Q403

Q403

2N7002E-LF

2N7002E-LF

3

3

Q405

Q405

2N7002E-LF

2N7002E-LF

R430 shortR430 short

R424 shortR424 short

R419 shortR419 short

R9

4.7KR94.7K

MBDATA

MBCLK

CPU_PWRGD(14)

LDT_STOP#(12,14)

LDT_RST#(14)

R425

R425

R431

R431

680

680

680

680

B B

1.8VSUS

1.8VSUS

R8

300R8300

2

H_PROCHOT#

R2 10KR2 10K

VCC3

VCC3

A A

VCC3

R3 10KR3 10K

5

THMDAT

THMCLK

1 3

MMBT3904Q2MMBT3904

Q2

R1 *0R1 *0

1

1

R408 *0R408 *0

VDDA_RUN

C29

C29

4.7U_0603

4.7U_0603

CPU_HT_RESET#

T411T411

CPU_ALL_PWROK

T422T422

CPU_LDTSTOP#

T423T423

CPU_SIC_R

CPU_SID_R

R13 44.2FR13 44.2F

R12 44.2FR12 44.2F

place them to CPU within 1"

CPU_VDDIO_SUS_FB_H

T12T12

CPU_VDDIO_SUS_FB_L

T13T13

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

T414T414

CPU_TEST16_BP2

T421T421

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST07_ANALOG_T

T408T408

CPU_TEST6_DIECRACKMON

T418T418

H_THERMDC

T1T1

H_THERMDA

T2T2

CPU_TEST3_GATE0

T7T7

CPU_TEST2_DRAIN0

T417T417

T45T45

T52T52

T47T47

T50T50

CPU_RSVD_MA0_CLK3_P

T40T40

CPU_RSVD_MA0_CLK3_N

T41T41

T36T36

CPU_RSVD_MB0_CLK3_P

T39T39

CPU_RSVD_MB0_CLK3_N

T44T44

T401T401

THMCLK (12)

THMDAT (12)

THERM_ALERT# (12,26)

ATHLON Control and Debug

12

C39

C39

C33

C33

0.22U

0.22U

3300pF

3300pF

U401D

U401D

C10

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

IRT

R406 shortR406 short

2

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

PSI_L

NC#1

NC#2

NC#3

NC#4

DBREQ_L

TEST29_H

TEST29_L

NC#5

NC#6

NC#7

NC#8

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

MISC

MISC

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

3VPCU

VID5

VID4

VID3

VID2

VID1

VID0

TDO

VCC3

CPU_HTREF1

CPU_HTREF0

R402

R402

*4.7K

*4.7K

*MMBT3904

*MMBT3904

SYS_SHDN#1(12)

1.8VSUS

Q402

Q402

D10

C7

C9

D8

AL6

AK6

V8

V7

G2

G1

AK11

AL11

A8

B8

B6

AL9

AH10

AJ10

AL10

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

L25

L26

L31

L30

W26

W25

AE27

U24

V24

AE28

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

R401

R401

*10K

*10K

2

CPU_HT_RESET#

13

SYS_SHDN#1

SMBUS SLAVE ADDRESS

G781

G781-1

AMD NPT M2 SOCKET

Processor Socket

98 (NB)

9A (CPU)

H_THERMTRIP#

AK7

H_PROCHOT#

AL7

D2

D1

C1

E3

E2

E1

CPU_PRESENT#

AL3

F1

H3

H4

H20

H21

CPU_DBREQ#

A5

CPU_TDO

AK10

CPU_TEST29_H_FBCLKOUT_P

C11

CPU_TEST29_L_FBCLKOUT_N

D11

AE7

AD19

AE8

AD18

CPU_TEST24_SCANCLK1

AK8

CPU_TEST23_TSTUPD

AH8

CPU_TEST22_SCANSHIFTEN

AJ9

CPU_TEST21_SCANEN

AL8

CPU_TEST20_SCANCLK2

AJ8

CPU_TEST28_H_PLLCHRZ_P

J10

CPU_TEST28_L_PLLCHRZ_N

H9

CPU_TEST27_SINGLECHAIN

AK9

CPU_TEST26_BURNIN#

AK5

CPU_TEST10_ANALOGOUT

G7

CPU_TEST08_DIG_T

D4

CPU_MA_RESET#

E20

CPU_MB_RESET#

B19

AL4

AK4

AK3

CPU_RSVD_VIDSTRB1

F2

CPU_RSVD_VIDSTRB0

F3

CPU_RSVD_VDDNB_FB_P

G4

CPU_RSVD_VDDNB_FB_N

G3

CPU_RSVD_CORE_TYPE

G5

Y31

Y30

AG31

V31

W31

AF31

VCC3

R409

R409

R410

R410

10K

10K

*10K

*10K

2

1.8VSUS

3

Q401

Q401

2N7002E-LF

2N7002E-LF

1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

1.8VSUS 1.8VSUS

R5

10KR510K

R411

R6

300R6300

T404T404

AMD M2+ CTRL & DEBUG

AMD M2+ CTRL & DEBUG

AMD M2+ CTRL & DEBUG

R411

300

300

2

1 3

MMBT3904Q1MMBT3904

Q1

VID5 (32)

VID4 (32)

VID3 (32)

VID2 (32)

VID1 (32)

VID0 (32)

PSI_L is a Power Status Indicator

PSI# (32)

signal. This signal is asserted when

the processor is in a low powerstate.

PSI_L should be connected to the power

supply controller, if the controller

supports “skipmode, or diode emulation

mode”. PSI_L is asserted by the

processor during the C3 and S1 states.

R441 80.6FR441 80.6F

PLACE IT CLOSE TO CPU WITHIN 1"

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

T10T10

T14T14

T15T15

T11T11

T416T416

T32T32

T20T20

T409T409

T419T419

T420T420

T410T410

T403T403

T413T413

T405T405

T412T412

T56T56

T60T60

T51T51

T71T71

T64T64

T54T54

VCC3

R405

R405

200K_0603

200K_0603

SYS_SHDN# (29,30)

3

Q404

Q404

2N7002E-LF

2N7002E-LF

2

C401

C401

0.01U_0603

0.01U_0603

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

SB_THERMTRIP# (15)

GT1

GT1

GT1

6 36Thursday, April 09, 2009

6 36Thursday, April 09, 2009

6 36Thursday, April 09, 2009

6

A

A

A

of

of

of

Page 7

5

4

3

2

1

PROCESSOR POWER AND GROUND

U401H

U401G

U401G

A3

VSS1

A7

VSS2

A9

VSS3

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AF2

AF3

AF8

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

Athlon 64 M2

Processor Socket

GND1

GND1

Y29

Y28

Y26

Y24

V30

V28

V26

V25

T30

T28

T26

T24

P30

P28

P26

P24

M30

M28

M26

M24

AF30

AD30

AD28

AD26

AC24

AB30

AB28

AB26

AB24

Y23

W22

V23

U22

T23

R22

P23

P21

N22

N20

M23

M21

L22

L20

AF11

AE12

AD23

AD11

AC22

AC20

AC18

AC16

AC14

AC12

1.8VSUS

CPU_CORE

D D

C C

B B

CPU_CORE

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

AC8

AC10

AD2

AD3

AD7

AD9

AE10

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

G10

G12

H11

H23

F11

A4

A6

B3

B5

B7

C2

C4

C6

C8

D3

D5

D7

D9

E4

E6

E8

F5

F7

F9

G6

G8

H7

U401E

U401E

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

Athlon 64 M2

Processor Socket

VDD106

VDD105

VDD104

VDD103

VDD102

VDD101

VDD100

VDD99

VDD98

VDD97

VDD96

VDD95

VDD94

VDD93

VDD92

VDD91

VDD90

VDD89

VDD88

VDD87

VDD86

VDD85

VDD84

VDD83

VDD82

VDD81

VDD80

VDD79

VDD78

VDD77

VDD76

POWER1

POWER1

VDD75

VDD74

VDD73

VDD72

VDD71

VDD70

VDD69

VDD68

VDD67

VDD66

VDD65

VDD64

VDD63

VDD62

VDD61

VDD60

VDD59

VDD58

VDD57

VDD56

VDD55

VDD54

CPU_CORE CPU_CORE

R10

R8

R5

R4

P19

P17

P15

P13

P11

P9

P7

N18

N16

N14

N12

N10

N8

M19

M17

M15

M13

M11

M9

M7

M3

M2

L18

L16

L14

Y19

Y17

L12

L10

L8

L5

L4

K23

K21

K19

K17

K15

K13

K11

K9

K7

J24

J22

J20

J18

J16

J14

J12

J8

R12

R14

R16

R18

R20

T11

T13

T15

T17

T19

T21

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

V21

W10

W12

W14

W16

W18

W20

Y11

Y13

Y15

Y21

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

U401F

U401F

VDD107

VDD108

VDD109

VDD110

VDD111

T2

VDD112

T3

VDD113

T7

VDD114

T9

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

U8

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

V9

VDD129

VDD130

VDD131

VDD132

VDD133

VDD134

VDD135

W4

VDD136

W5

VDD137

W8

VDD138

VDD139

VDD140

VDD141

VDD142

VDD143

VDD144

Y2

VDD145

Y3

VDD146

Y7

VDD147

Y9

VDD148

VDD149

VDD150

VDD151

VDD152

VDD153

VDD154

VDD155

VDD156

VDD157

VDD158

VDD159

VDD160

VDDIO28

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

VDDIO12

VDDIO11

VDDIO10

VDDIO9

VDDIO8

VDDIO7

VDDIO6

VDDIO5

VDDIO4

VDDIO3

VDDIO2

POWER2

POWER2

VDDIO1

VDD184

VDD183

VDD182

VDD181

VDD180

VDD179

VDD178

VDD177

VDD176

VDD175

VDD174

VDD173

VDD172

VDD171

VDD170

VDD169

VDD168

VDD167

VDD166

VDD165

VDD164

VDD163

VDD162

VDD161

VDDIO

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

H10

H8

G11

G9

F30

F28

F26

F24

F22

F20

F18

F16

F14

F4

E11

D30

D28

D26

D24

D22

D20

D18

D16

D14

C3

B30

B28

B26

B24

B22

B20

B18

B16

B14

B11

B9

B4

AL5

AK30

AK28

AK26

AK24

AK22

AK20

Y16

Y14

AK18

AK16

AK14

AK2

AH30

AH28

AH26

AH24

AH22

AH20

AH18

AH16

AH14

AG11

T22

T20

T18

T16

T14

T12

T10

R23

R21

R19

R17

R15

R13

R11

P22

P20

P18

P16

P14

P12

P10

N23

N21

N19

N17

Y18

K22

K20

K18

K16

K14

K12

K10

H30

H28

H26

H24

H22

H18

H16

H14

H12

U401H

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

T8

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

R9

VSS168

R7

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

VSS161

VSS160

P8

VSS159

P3

VSS158

P2

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

K8

VSS144

K3

VSS143

K2

VSS142

J23

VSS141

J21

VSS140

J19

VSS139

J17

VSS138

J15

VSS137

J13

VSS136

J11

VSS135

J9

VSS134

J7

VSS133

J5

VSS132

J4

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

GND2

GND2

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

A1

AL1

Athlon 64 S1g1

uPGA940

Top View

7

A31

BOTTOMSIDE DECOUPLING

1.8VSUS

C6

0.22UC60.22U

C162

C162

10U_0805

10U_0805

C9

0.22UC90.22U

C164

C164

10U_0805

10U_0805

C8

0.01UC80.01U

C110

C110

0.22U

0.22U

C7

180PC7180P

C159

C159

0.22U

0.22U

CPU_CORE

C15

C15

10U_0603

10U_0603

C16

C16

10U_0603

10U_0603

C19

C19

10U_0603

10U_0603

C17

C17

10U_0603

10U_0603

C12

C12

10U_0603

10U_0603

C13

C13

10U_0603

10U_0603

C14

C14

10U_0603

10U_0603

C11

C11

10U_0603

10U_0603

C23

C23

10U_0603

10U_0603

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

1.8VSUS

C165

1.8VSUS

C165

4.7U_0603

4.7U_0603

C160

C160

4.7U_0603

4.7U_0603

C101

C101

4.7U_0603

4.7U_0603

C161

C161

4.7U_0603

4.7U_0603

C112

C112

0.22U

0.22U

C120

C120

0.22U

0.22U

C109

C109

0.22U

0.22U

C121

C121

0.22U

0.22U

C116

C116

0.22U

0.22U

C105

C105

0.22U

0.22U

C122

C122

0.01U

0.01U

C107

C107

180P

180P

C111

C111

C99

A A

CPU_CORE

22U/6.3V_8

22U/6.3V_8

C36

C36

C34

C34

22U/6.3V_8

22U/6.3V_8

5

C37

C37

22U/6.3V_8

22U/6.3V_8

C38

C38

22U/6.3V_8

22U/6.3V_8

C35

C35

22U/6.3V_8

22U/6.3V_8

C54

C54

22U/6.3V_8

22U/6.3V_8

C52

C52

22U/6.3V_8

22U/6.3V_8

C55

C55

22U/6.3V_8

22U/6.3V_8

C53

C53

22U/6.3V_8

22U/6.3V_8

4

C51

C51

22U/6.3V_8

22U/6.3V_8

C76

C76

22U/6.3V_8

22U/6.3V_8

C77

C77

22U/6.3V_8

22U/6.3V_8

C78

C78

22U/6.3V_8

22U/6.3V_8

C79

C79

22U/6.3V_8

22U/6.3V_8

C74

C74

22U/6.3V_8

22U/6.3V_8

3

C99

0.01U

0.01U

180P

180P

C108

C108

180P

180P

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AMD M2+ PWR & GND

AMD M2+ PWR & GND

AMD M2+ PWR & GND

Date: Sheet

Date: Sheet

2

Date: Sheet

PROJECT :

GT1

GT1

GT1

A

A

A

7 36Thursday, April 09, 2009

7 36Thursday, April 09, 2009

7 36Thursday, April 09, 2009

of

of

1

of

Page 8

5

1.8VSUS

4

3

1.8VSUS

2

1

8

103

111

104

112

117

VDD7

SO-DIMM

SO-DIMM

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

121

VDD8

VDD9

VSS30

VSS29

127

122

118

CN405

CN405

DQ0

DQ1

DQ2

VDD10

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

GuidePin

GuidePin

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

DDRII_SODIMM_R

DDRII_SODIMM_R

132

128

2

M_B_DQ4

5

M_B_DQ5

7

M_B_DQ2

17

M_B_DQ7

19

M_B_DQ0

4

M_B_DQ1

6

M_B_DQ3

14

M_B_DQ6

16

M_B_DQ13

23

M_B_DQ9

25

M_B_DQ14

35

M_B_DQ11

37

M_B_DQ8

20

M_B_DQ12

22

M_B_DQ10

36

M_B_DQ15

38

M_B_DQ17

43

M_B_DQ21

45

M_B_DQ18

55

M_B_DQ22

57

M_B_DQ20

44

M_B_DQ16

46

M_B_DQ19

56

M_B_DQ23

58

M_B_DQ29

61

M_B_DQ28

63

M_B_DQ26

73

M_B_DQ27

75

M_B_DQ25

62

M_B_DQ24

64

M_B_DQ30

74

M_B_DQ31

76

M_B_DQ33

123

M_B_DQ32

125

M_B_DQ38

135

M_B_DQ35

137

M_B_DQ37

124

M_B_DQ36

126

M_B_DQ34

134

M_B_DQ39

136

M_B_DQ44

141

M_B_DQ40

143

M_B_DQ46

151

M_B_DQ47

153

M_B_DQ41

140

M_B_DQ45

142

M_B_DQ43

152

M_B_DQ42

154

M_B_DQ53

157

M_B_DQ52

159

M_B_DQ54

173

M_B_DQ50

175

M_B_DQ49

158

M_B_DQ48

160

M_B_DQ55

174

M_B_DQ51

176

M_B_DQ57

179

M_B_DQ56

181

M_B_DQ63

189

M_B_DQ59

191

M_B_DQ60

180

M_B_DQ61

182

M_B_DQ58

192

M_B_DQ62

194

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

103

111

104

112

117

VDD7

SO-DIMM

SO-DIMM

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

121

VDD8

VDD9

VSS30

VSS29

127

122

118

DQ0

DQ1

DQ2

VDD10

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

GuidePin

GuidePin

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

DDRII_SODIMM_R

DDRII_SODIMM_R

132

128

4

CN407

CN407

M_A_DQ1

5

M_A_DQ0

7

M_A_DQ3

17

M_A_DQ7

19

M_A_DQ5

4

M_A_DQ4

6

M_A_DQ2

14

M_A_DQ6

16

M_A_DQ9

23

M_A_DQ12

25

M_A_DQ10

35

M_A_DQ14

37

M_A_DQ13

20

M_A_DQ8

22

M_A_DQ15

36

M_A_DQ11

38

M_A_DQ17

43

M_A_DQ16

45

M_A_DQ19

55

M_A_DQ23

57

M_A_DQ21

44

M_A_DQ20

46

M_A_DQ22

56

M_A_DQ18

58

M_A_DQ24

61

M_A_DQ25

63

M_A_DQ27

73

M_A_DQ26

75

M_A_DQ28

62

M_A_DQ29

64

M_A_DQ31

74

M_A_DQ30

76

M_A_DQ37

123

M_A_DQ33

125

M_A_DQ39

135

M_A_DQ35

137

M_A_DQ32

124

M_A_DQ36

126

M_A_DQ38

134

M_A_DQ34

136

M_A_DQ44

141

M_A_DQ45

143

M_A_DQ43

151

M_A_DQ46

153

M_A_DQ41

140

M_A_DQ40

142

M_A_DQ42

152

M_A_DQ47

154

M_A_DQ49

157

M_A_DQ52

159

M_A_DQ51

173

M_A_DQ54

175

M_A_DQ48

158

M_A_DQ53

160

M_A_DQ50

174

M_A_DQ55

176

M_A_DQ57

179

M_A_DQ60

181

M_A_DQ63

189

M_A_DQ62

191

M_A_DQ56

180

M_A_DQ61

182

M_A_DQ58

192

M_A_DQ59

194

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

M_A_A[0..15](5,9)

R118 *4.7KR118 *4.7K

VCC3

R119 *4.7KR119 *4.7K

D D

SA0_A

SA1_A

12

12

R1220 R1220

R1210 R1210

SA_A : 00

M_A_BS#0(5,9)

M_A_BS#1(5,9)

M_A_BS#2(5,9)

M_A_DM[0..7](5)

C C

M_A_DQS[0..7](5)

M_A_DQS#[0..7](5)

M_CLKOUT0(5)

M_CLKOUT0#(5)

M_CLKOUT1(5)

M_CLKOUT1#(5)

M_CKE0(5,9)

M_CKE1(5,9)

M_A_RAS#(5,9)

M_A_CAS#(5,9)

M_A_WE#(5,9)

M_A_CS#0(5,9)

B B

VCC3

1.8VSUS

A A

M_A_CS#1(5,9)

M_ODT0(5,9)

M_ODT1(5,9)

SDATA0(3,15)

SCLK0(3,15)

C216 0.1UC216 0.1U

C224

C224

2.2U_0805

2.2U_0805

M_CLKOUT0

C147

C147

1.5P

1.5P

M_CLKOUT0#

M_CLKOUT1

C153

C153

1.5P

1.5P

M_CLKOUT1#

1 2

5

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_CLKOUT0

M_CLKOUT0#

M_CLKOUT1

M_CLKOUT1#

SA1_A

C204 0.1UC204 0.1U

MVREF_DIM

C232

C232

0.1U

0.1U

102

A0

101

A1

1

2

3

8

9

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

(H=6.5)

59

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

M_A_DQ[0..63] (5)

R102 *4.7KR102 *4.7K

VCC3

R101 4.7KR101 4.7K

SA_B : 10

ES2

M_A_CS#2 (5,9)

M_A_CS#3 (5,9)

VCC3

1.8VSUS

1.This part should not contain any substances which are specified in SS-00259-1

2.Purchase ink, paint, wire rods and molding resins only from the business partners that Sony approves as Green Partners.

M_B_A[0..15](5,9)

SA1_B

12

12

R90*0 R90*0

M_B_DM[0..7](5)

M_B_DQS[0..7](5)

M_B_DQS#[0..7](5)

M_CLKOUT3(5)

M_CLKOUT3#(5)

M_CLKOUT4(5)

M_CLKOUT4#(5)

M_CKE2(5,9)

M_CKE3(5,9)

M_B_RAS#(5,9)

M_B_CAS#(5,9)

M_B_WE#(5,9)

M_B_CS#0(5,9)

M_B_CS#1(5,9)

M_ODT2(5,9)

M_ODT3(5,9)

ES2 1121

SDATA0(3,15)

SCLK0(3,15)

C517 0.1UC517 0.1U

C516

C516

2.2U_0805

2.2U_0805

M_CLKOUT3

C150

C150

1.5P

1.5P

M_CLKOUT3#

M_CLKOUT4

C142

C142

1.5P

1.5P

M_CLKOUT4#

SA0_B

R910 R910

M_B_BS#0(5,9)

M_B_BS#1(5,9)

M_B_BS#2(5,9)

1 2

3

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_CLKOUT3

M_CLKOUT3#

M_CLKOUT4

M_CLKOUT4#

SA0_B

SA1_BSA0_A

C205 0.1UC205 0.1U

MVREF_DIM

C519

C519

0.1U

0.1U

102

A0

101

A1

1

2

3

8

9

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

(H=11)

59

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

M_B_DQ[0..63] (5)

1.8VSUS

M_B_CS#2 (5,9)

M_B_CS#3 (5,9)

SMDDR_VREF

DDRII SODIMM x2

DDRII SODIMM x2

DDRII SODIMM x2

*10U_0805C163 *10U_0805C163

*10U_0805C227 *10U_0805C227

10U_0805C274 10U_0805C274

10U_0805C225 10U_0805C225

0.1UC180 0.1UC180

0.1UC229 0.1UC229

0.1UC219 0.1UC219

0.1UC174 0.1UC174

0.1UC220 0.1UC220

0.1UC178 0.1UC178

0.1UC181 0.1UC181

0.1UC175 0.1UC175

0.1UC221 0.1UC221

0.1UC176 0.1UC176

0.1UC228 0.1UC228

0.1UC218 0.1UC218

0.1UC230 0.1UC230

0.1UC231 0.1UC231

0.1UC226 0.1UC226

0.1UC267 0.1UC267

0.1UC272 0.1UC272

0.1UC273 0.1UC273

0.1UC268 0.1UC268

0.1UC270 0.1UC270

1.8VSUS

*0.1UC179 *0.1UC179

*0.1UC177 *0.1UC177

*0.1UC269 *0.1UC269

*0.1UC271 *0.1UC271

For EMI

1.8VSUS

R103

R531*0R531

*0

MVREF_DIM

C5181UC518

1U

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

R103

1K/F

1K/F

R532

R532

1K/F

1K/F

1

GT1

GT1

GT1

8 36Thursday, April 09, 2009

8 36Thursday, April 09, 2009

8 36Thursday, April 09, 2009

of

of

of

A

A

A

Page 9

5

4

3

2

1

9

SMDDR_VTERM

D D

SMDDR_VTERM

*10U_0805C222 *10U_0805C222

*10U_0805C182 *10U_0805C182

0.1UC200 0.1UC200

0.1UC194 0.1UC194

0.1UC198 0.1UC198

C C

0.1UC213 0.1UC213

0.1UC210 0.1UC210

0.1UC193 0.1UC193

0.1UC209 0.1UC209

0.1UC245 0.1UC245

0.1UC235 0.1UC235

*0.1UC214 *0.1UC214

*0.1UC196 *0.1UC196

0.1UC195 0.1UC195

0.1UC215 0.1UC215

0.1UC212 0.1UC212

0.1UC199 0.1UC199

0.1UC248 0.1UC248

*0.1UC197 *0.1UC197

0.1UC211 0.1UC211

0.1UC236 0.1UC236

0.1UC237 0.1UC237

*0.1UC238 *0.1UC238

0.1UC239 0.1UC239

0.1UC246 0.1UC246

0.1UC247 0.1UC247

*0.1UC249 *0.1UC249

0.1UC250 0.1UC250

1.8VSUS

SMDDR_VTERM

0.1UC183 0.1UC183

0.1UC189 0.1UC189 R115 47_4R115 47_4

0.1UC254 0.1UC254

0.1UC253 0.1UC253

0.1UC190 0.1UC190

0.1UC184 0.1UC184

0.1UC185 0.1UC185

0.1UC186 0.1UC186

0.1UC187 0.1UC187

0.1UC188 0.1UC188

0.1UC256 0.1UC256

0.1UC252 0.1UC252

0.1UC255 0.1UC255

0.1UC257 0.1UC257

0.1UC258 0.1UC258

0.1UC259 0.1UC259

M_CKE0(5,8)

M_CKE1(5,8)

M_CKE2(5,8)

M_CKE3(5,8)

M_ODT0(5,8)

M_ODT1(5,8)

M_ODT2(5,8)

M_ODT3(5,8)

M_A_BS#0(5,8)

M_A_BS#1(5,8)

M_A_BS#2(5,8)

M_A_WE#(5,8)

M_A_CAS#(5,8)

M_A_RAS#(5,8)

M_B_BS#0(5,8)

M_B_BS#1(5,8)

M_B_BS#2(5,8)

M_B_WE#(5,8)

M_B_CAS#(5,8)

M_B_RAS#(5,8)

M_A_CS#0(5,8)

M_A_CS#1(5,8)

M_A_CS#2(5,8)

M_A_CS#3(5,8)

M_B_CS#0(5,8)

M_B_CS#1(5,8)

M_B_CS#2(5,8)

M_B_CS#3(5,8)

M_A_A[0..15](5,8)

M_A_A13

M_A_A10

M_A_A0

M_A_A2

M_A_A7

M_A_A6

M_A_A4

M_A_A11

M_A_A9

M_A_A12

M_A_A3

M_A_A1

M_A_A8

M_A_A5

M_A_A14

M_A_A15

R108 47_4R108 47_4

R129 47_4R129 47_4

R76 47_4R76 47_4

R94 47_4R94 47_4

R133 47_4R133 47_4

R114 47_4R114 47_4

R97 47_4R97 47_4

R73 47_4R73 47_4

R111 47_4R111 47_4

R130 47_4R130 47_4

R109 47_4R109 47_4

R112 47_4R112 47_4

R113 47_4R113 47_4

R131 47_4R131 47_4

R70 47_4R70 47_4

R95 47_4R95 47_4

R68 47_4R68 47_4

R71 47_4R71 47_4

R72 47_4R72 47_4

R96 47_4R96 47_4

R134 47_4R134 47_4

R107 47_4R107 47_4

R135 47_4R135 47_4

R98 47_4R98 47_4

R74 47_4R74 47_4

R75 47_4R75 47_4

R100 47_4R100 47_4

R132 47_4R132 47_4

R110 47_4R110 47_4

RP14 0404-47X2RP14 0404-47X2

1 2

3 4

RP13 0404-47X2RP13 0404-47X2

1 2

3 4

RP12 0404-47X2RP12 0404-47X2

1 2

3 4

RP8 0404-47X2RP8 0404-47X2

1 2

3 4

RP10 0404-47X2RP10 0404-47X2

1 2

3 4

RP9 0404-47X2RP9 0404-47X2

1 2

3 4

RP11 0404-47X2RP11 0404-47X2

1 2

3 4

B B

A A

5

4

M_B_A[0..15](5,8)

3

M_B_A0

M_B_A2

M_B_A7

M_B_A6

M_B_A4

M_B_A15

M_B_A3

M_B_A1

M_B_A8

M_B_A5

M_B_A9

M_B_A12