Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

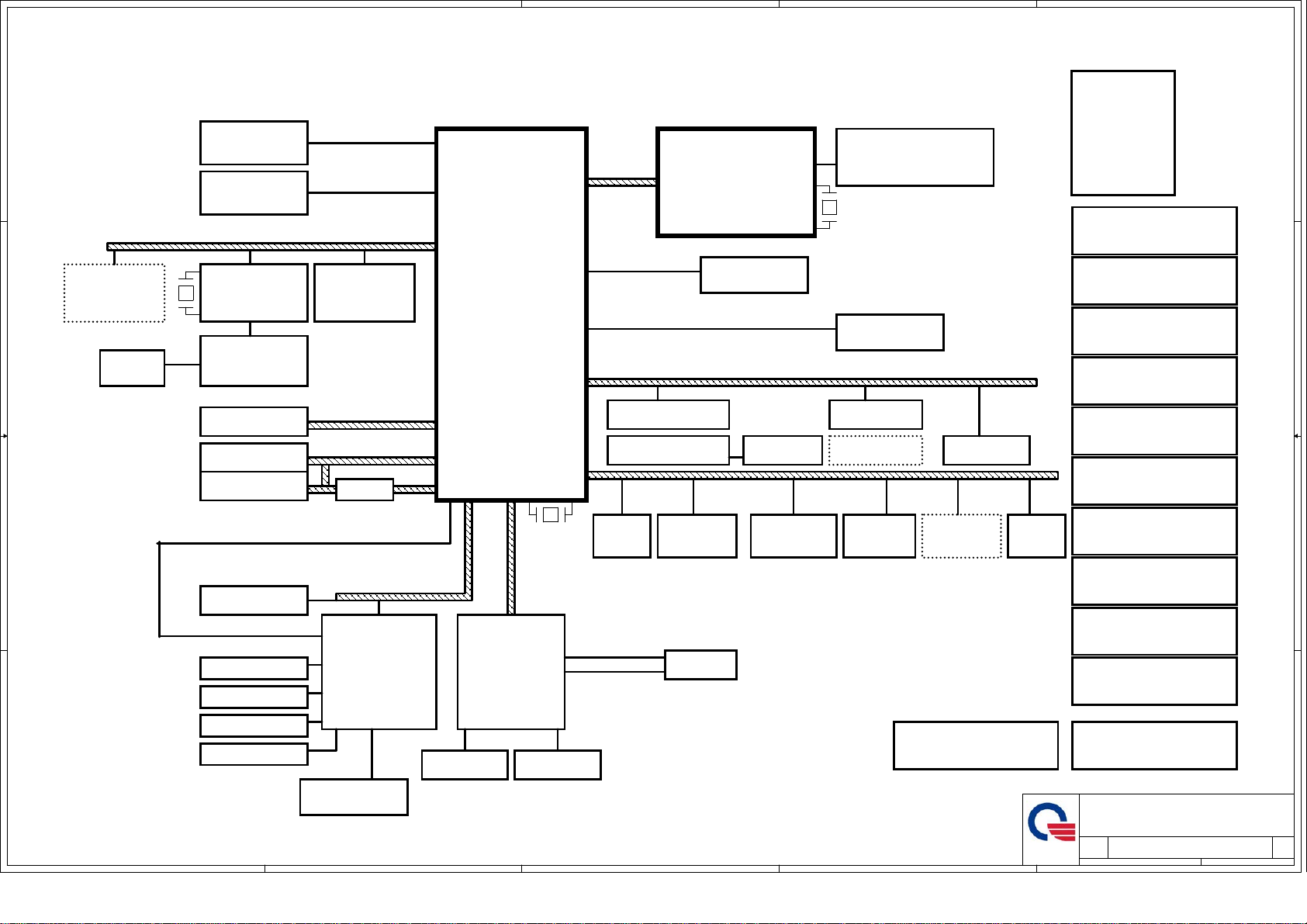

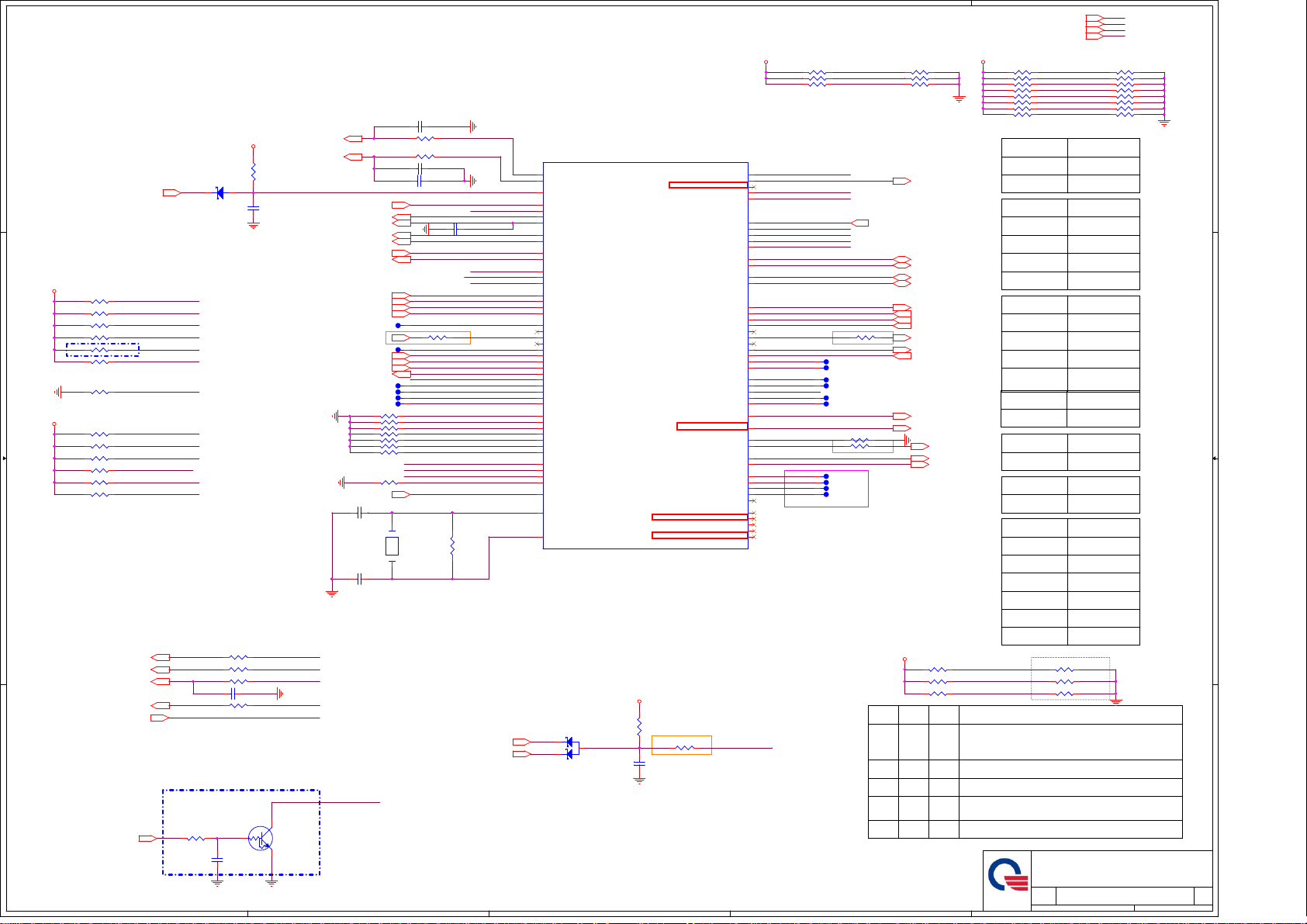

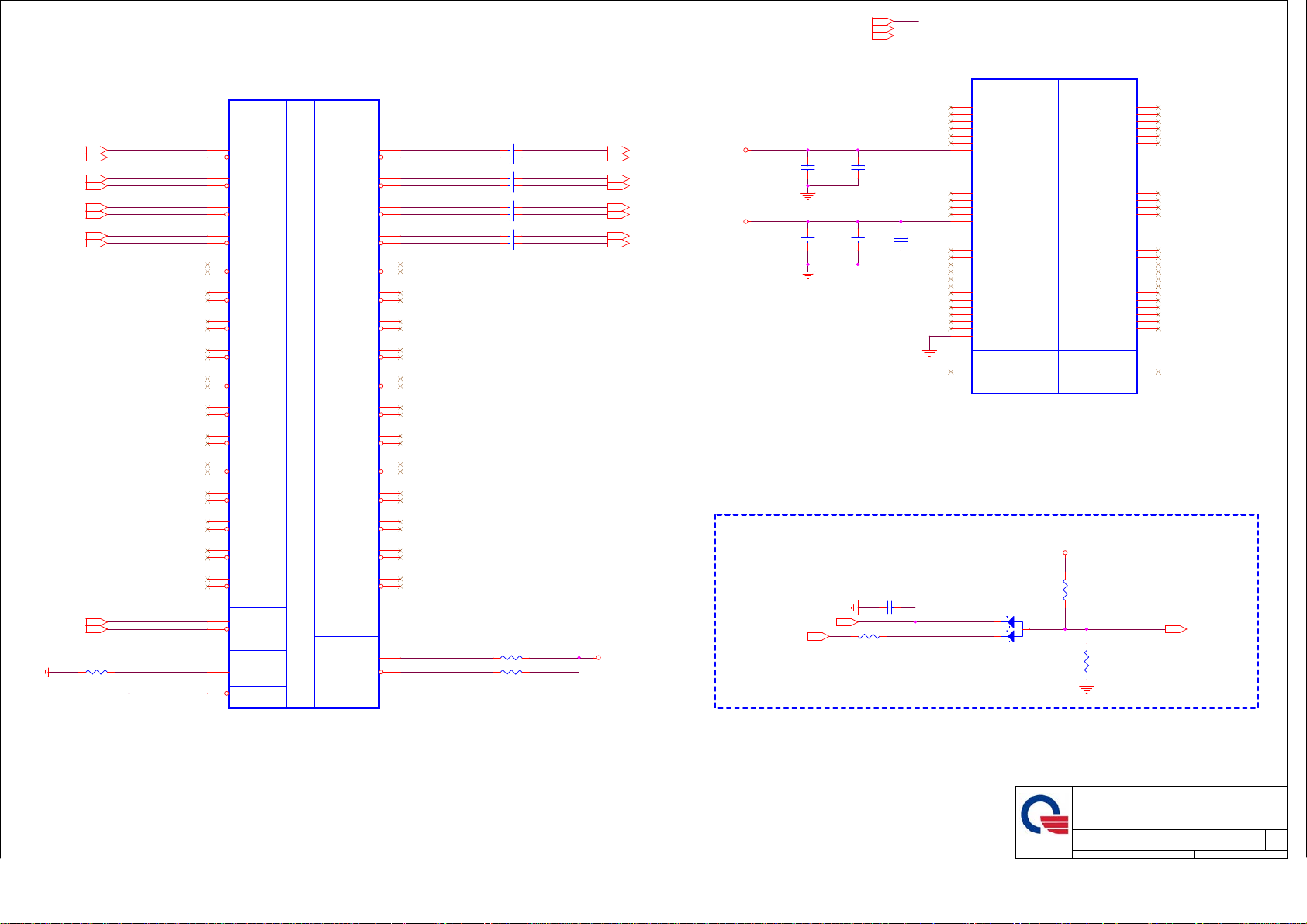

G94A 15.6"/17.3" 2SPD System Block Diagram-AMD Bristol FP4

01

PCB 8L STACK UP

LAYER 1 : TOP

LAYER 2 : SGND

D D

Port0 Port1 Port2

Realtek RTS5237

Card Reader

C C

PAGE 28

on DB

RJ45 Conn

PAGE 24

DDR4 SODIMM0

Maxima 8GBs

RVS

DDR4 SODIMM1

Maxima 8GBs

STD

25MHz

RTL8166EH-CG

RTL8111HSH-CG

LAN CHIP

NS681684

GST5009B

TRANSFORMER

SATA - SSD (NGFF)

PAGE 10

PAGE 11

PAGE 24

PAGE 24

PAGE 26SATA - HDD

PAGE 27

DDR4 1866 MT/s

DDR4 1866 MT/s

PCIE INTERFACE

M2230

WLAN/BT Combo

PAGE 27

SATA0 6GB/s

SATA0 6GB/s

Port0

Port1

AMD APU

Bristol Ridge FP4

Processor : Dual Core

Power : 15 (Wat t)

Package : FP4 BGA

AMD R17M-M1-70 64 bit

Gen3 x4 Lane

Power : 25 (Wat t)

Package : S3

Size : 23 x 23 (mm)

PAGE 13-17

DP Port1

HDMI CONN

HDMI 2.0

PAGE 21

DP Port0

USB3 INTERFACE

Port0

USB3 SW PI2EQX632

CC Logic

USB-C CONN PAGE 25 PAGE 28

TPS25810

VRAM DDR3 x 8 (1000 MHz)

256M x 16

Max 4GBs

27MHz

PAGE 14

PAGE 18.19

eDP CONN

PAGE 20

Port1 Port2

USB3.0 Re driver

PTN36001

USB3.0 CONN

USB3.0 CONN

on DB PAGE 28

SATA - ODD 15.6"

PAGE 26

17.3"

USB3 TO SATA BRIDGE

B B

VL711

SPI INTERFACE

Port4

PAGE 02-09

48MHz

Azalia

Port0/2 Port4Port3Port1 Port5

IR Camera

Camera

PAGE 20 PAGE 26PAGE 27

Touch screen

PAGE 20

WLAN/BT Combo

USB-C CONN

PAGE 28 PAGE 28

USB3.0 CONN

USB2.0 CONN

on DB

Port6

USB3 CONN

USB2 INTERFACE

TPM SLB9665TT2.0

FW5.6

Keyboard

Touch Pad

G-sensor

A A

5

FAN

PAGE 29

PAGE 30

PAGE 30

PAGE 29

PAGE 30

LPC INTERFACE

ENE KB9027B

Embedded Controller

TOP

Power :

Package : LQFP 128P

Size : 14 x 14 (mm)

System BIOS

SPI ROM

PAGE 31

PAGE 31

4

ALC3258-CG

Audio Codec

Power :

Package : MQFN

Size : 6 x 6 (mm)

Speaker

PAGE 22

PAGE 22

Digital MIC

PAGE 20

Hp

MIC

Combo Jack

PAGE 23

3

RT8068 A/APL35 23A

DGPU Power

(+0.95V_VGA/+3V _VGA/+1.8V_VGA )

PAGE 47

2

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : SVCC

LAYER 6 : IN3

LAYER 6 : SGND

LAYER 6 : BOT

Power Source

BQ2473 8H

System Charge Power

(+BATCHG)

PAGE 33

SY8208 B/SY828 6C

System Power

(+3VPCU/+5V PCU/+3VS5/+5 VS5)

PAGE 34

RT8231 B

System Memory Power

(+1.2VSUS/+0.6V_DDR_VTT/+2.5VSUS)

PAGE 35

APW882 6/APW8 826/G9 336

Processor Power

(+0.95 VS5/0.775VS 5)

PAGE 36

AOZ2260/ RT8068A ZQW

Processor Power

(+0.95V/+1 .8VS5)

PAGE 37

RT3662 AC

Processor Power

(+VCC_CORE/+VDDNB_CORE)

PAGE 38.39

RT3662EB

Processor Power

(+APU_VDDGFX)

PAGE 40.41

G2042, G9336AD

Processor Power

(+VDDCR_FCH_S5, 0.775VS5)

APL3523A *4

(+3/+3V LANVCC)

(+5V/+3VSUS)

RT3662 EB/AOZ1236

DGPU Power

(+VGA_CORE)

(+1.8V_ROM/+1.8V )

(+1.2V/+3 VLCD_CON)

PAGE 44~45

AOZ22 60

DGPU Power

(+1.5V_VGA)

PAGE 46

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Block Diagram

Block Diagram

NB5

NB5

NB5

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

PAGE 42

PAGE 43

1A

1A

1A

1 48Monday, January 16, 2017

1 48Monday, January 16, 2017

1 48Monday, January 16, 2017

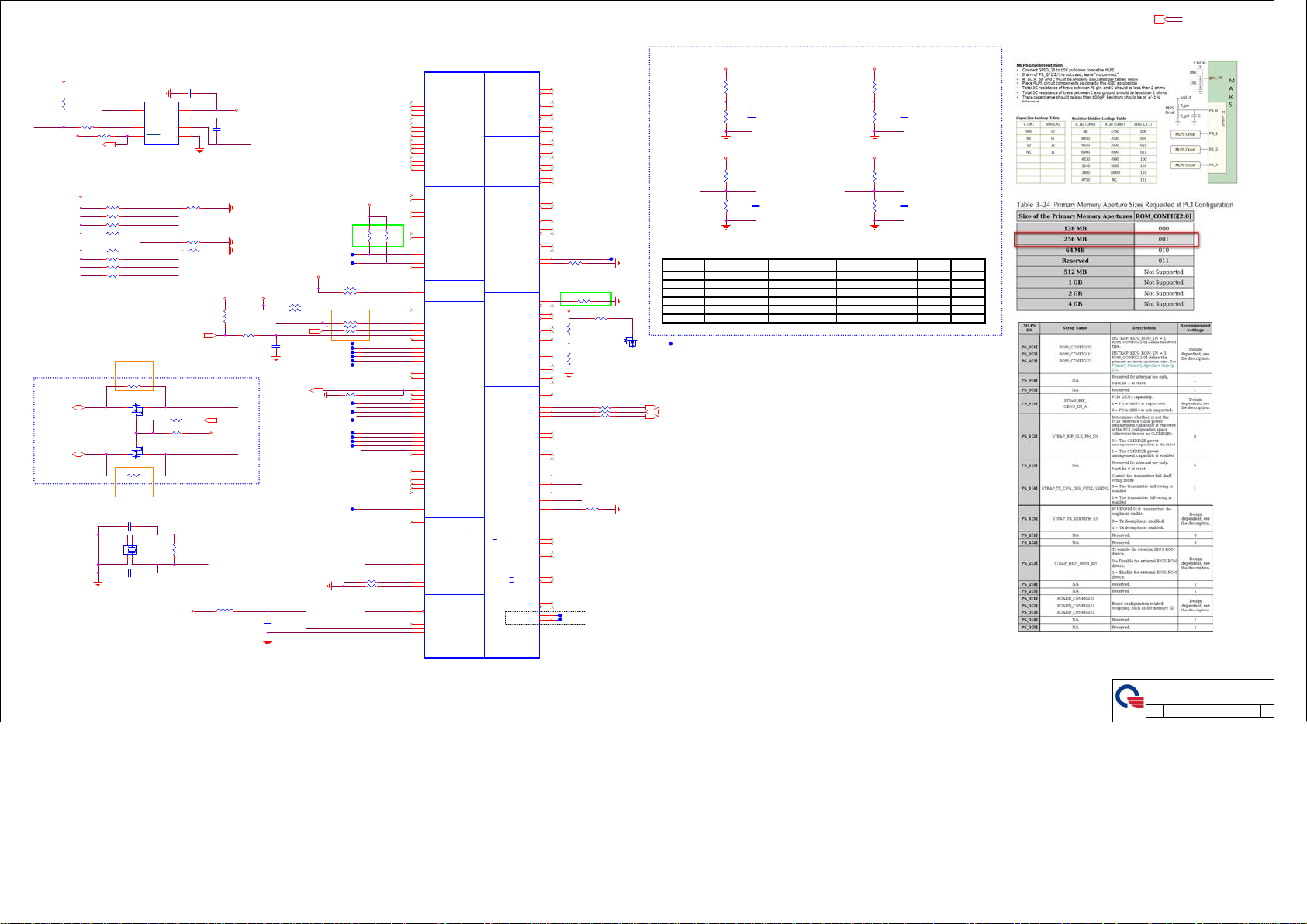

Page 2

5

4

3

2

1

+0.95V6,7,37

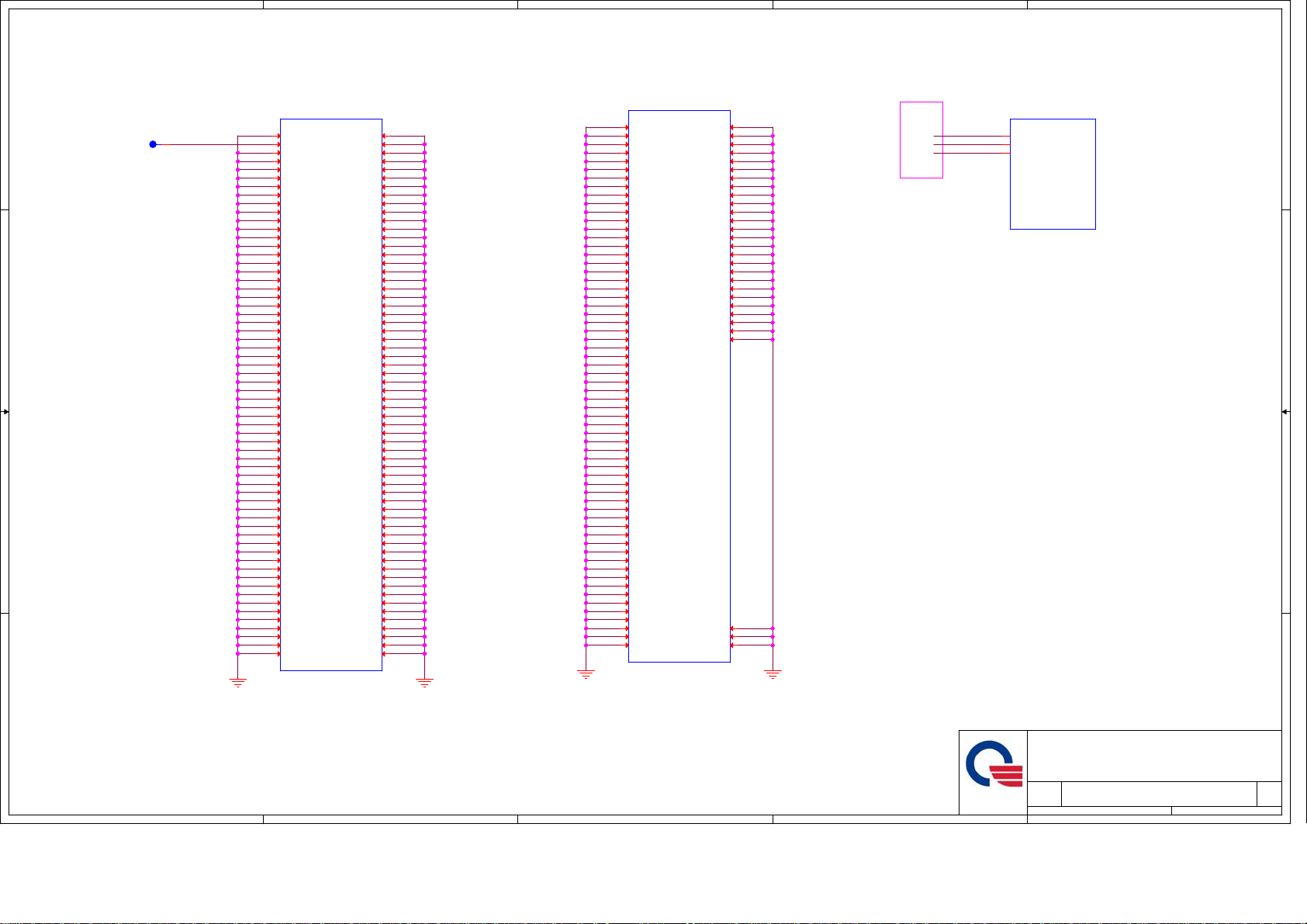

D D

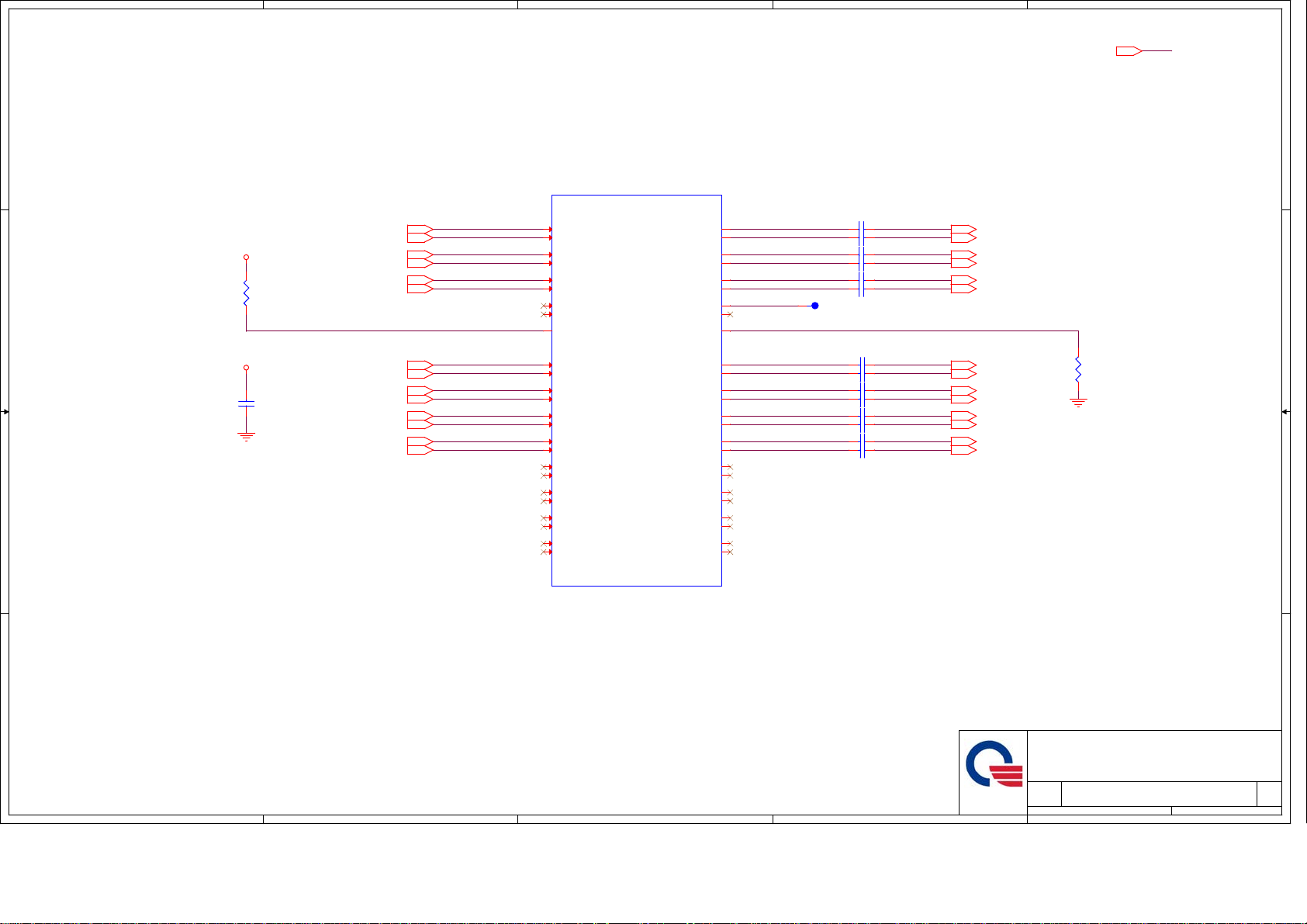

U1B

U10

P10

L10

U9

T6

T5

T9

T8

P7

P6

U7

P9

N6

N5

N9

N8

L7

L6

L9

K6

K5

K9

K8

J7

J6

P_GPP_RXP[0]

P_GPP_RXN[0]

P_GPP_RXP[1]

P_GPP_RXN[1]

P_GPP_RXP[2]

P_GPP_RXN[2]

P_GPP_RXP[3]

P_GPP_RXN[3]

P_ZVDDP

P_GFX_RXP[0]

P_GFX_RXN[0]

P_GFX_RXP[1]

P_GFX_RXN[1]

P_GFX_RXP[2]

P_GFX_RXN[2]

P_GFX_RXP[3]

P_GFX_RXN[3]

P_GFX_RXP[4]

P_GFX_RXN[4]

P_GFX_RXP[5]

P_GFX_RXN[5]

P_GFX_RXP[6]

P_GFX_RXN[6]

P_GFX_RXP[7]

P_GFX_RXN[7]

PCIE_RXP0_CARD28

+0.95V

R3

196_1%_4

C C

+0.95V

C24

0.1u/16V_4

B B

PCIE_RXN0_CARD28

PCIE_RXP1_LAN24

PCIE_RXN1_LAN24

PCIE_RXP2_WLAN27

PCIE_RXN2_WLAN27

PEG_RXP013

PEG_RXN013

PEG_RXP113

PEG_RXN113

PEG_RXP213

PEG_RXN213

PEG_RXP313

PEG_RXN313

PCIE

P_GPP_TXP[0]

P_GPP_TXN[0]

P_GPP_TXP[1]

P_GPP_TXN[1]

P_GPP_TXP[2]

P_GPP_TXN[2]

P_GPP_TXP[3]

P_GPP_TXN[3]

P_ZVSS/P_RX_ZVDDP

P_GFX_TXP[0]

P_GFX_TXN[0]

P_GFX_TXP[1]

P_GFX_TXN[1]

P_GFX_TXP[2]

P_GFX_TXN[2]

P_GFX_TXP[3]

P_GFX_TXN[3]

P_GFX_TXP[4]

P_GFX_TXN[4]

P_GFX_TXP[5]

P_GFX_TXN[5]

P_GFX_TXP[6]

P_GFX_TXN[6]

P_GFX_TXP[7]

P_GFX_TXN[7]

PCIE_TXP0_CARD_C

R1

PCIE_TXN0_CARD_C

R2

PCIE_TXP1_LAN_C

R4

PCIE_TXN1_LAN_C

R3

PCIE_TXP2_WLAN_C

N1

PCIE_TXN2_WLAN_C

N2

PCIE_TXP3

N4

N3

P_ZVSS_P_RX_ZVDD_095P_ZVDDP_P_TX_ZVDD_095

U6

GFX_TX0P_C

M2

GFX_TX0N_C

M1

GFX_TX1P_C

L1

GFX_TX1N_C

L2

GFX_TX2P_C

L4

GFX_TX2N_C

L3

GFX_TX3P_C

J1

GFX_TX3N_C

J2

J4

J3

H2

H1

G1

G2

G4

G3

C2 0.1u/16V_4

C3 0.1u/16V_4

C4 0.1u/16V_4

C5 0.1u/16V_4

C6 0.1u/16V_4

C7 0.1u/16V_4

TP2

C8 0.22u/10V_4

C9 0.22u/10V_4

C10 0.22u/10V_4

C11 0.22u/10V_4

C12 0.22u/10V_4

C13 0.22u/10V_4

C14 0.22u/10V_4

C15 0.22u/10V_4

PCIE_TXP0_CARD 28

PCIE_TXN0_CARD 28

PCIE_TXP1_LAN 24

PCIE_TXN1_LAN 24

PCIE_TXP2_WLAN 27

PCIE_TXN2_WLAN 27

PEG_TXP0 13

PEG_TXN0 13

PEG_TXP1 13

PEG_TXN1 13

PEG_TXP2 13

PEG_TXN2 13

PEG_TXP3 13

PEG_TXN3 13

R5

196_1%_4

02

For DIS GPU

FP4 REV 1.0

*FP4-BR

A A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

BR & SR 1/7(PCIE)

BR & SR 1/7(PCIE)

NB5

NB5

5

4

3

2

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

BR & SR 1/7(PCIE)

Monday, January 16, 2017 2 48

Monday, January 16, 2017 2 48

Monday, January 16, 2017 2 48

1

1A

1A

1A

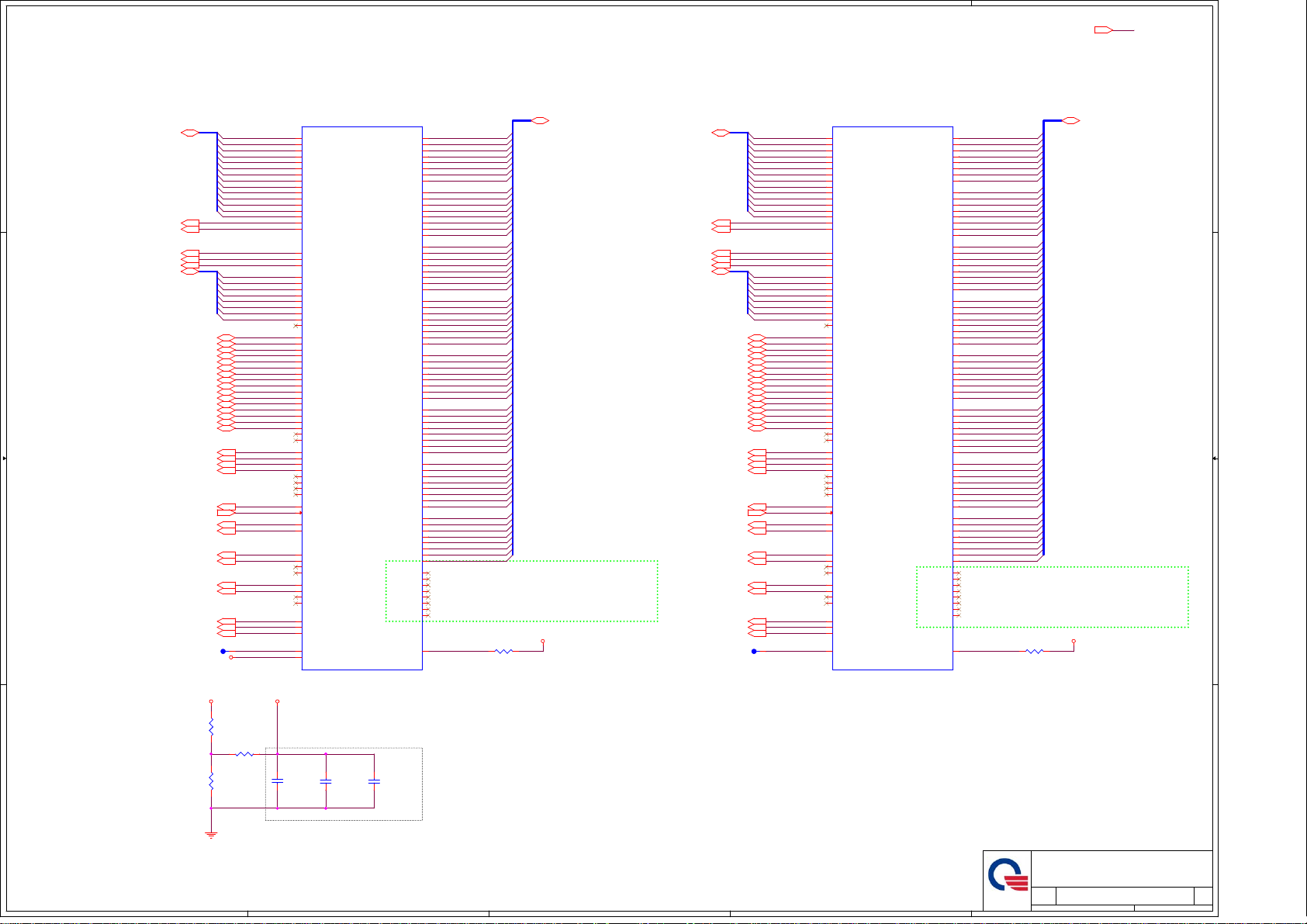

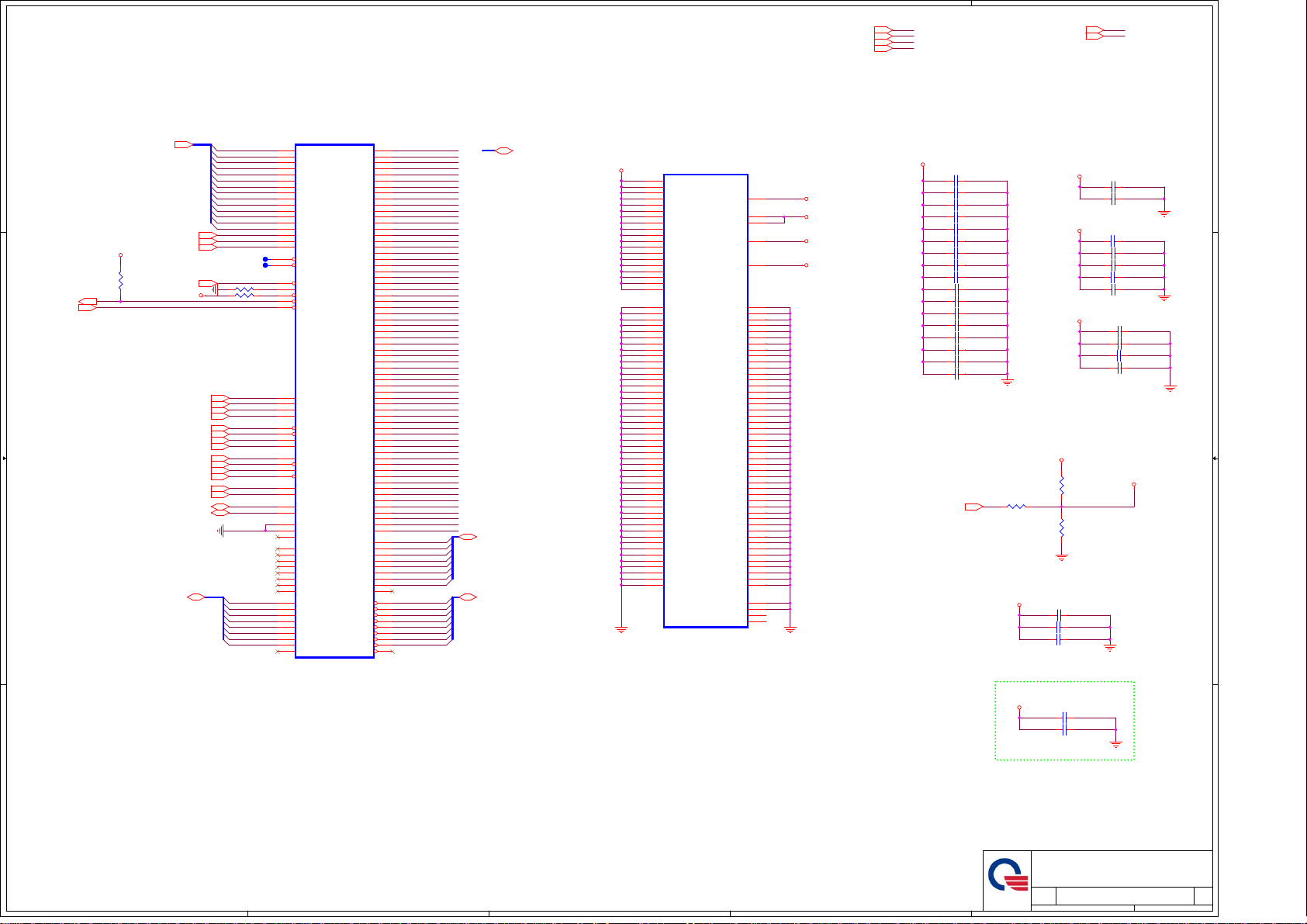

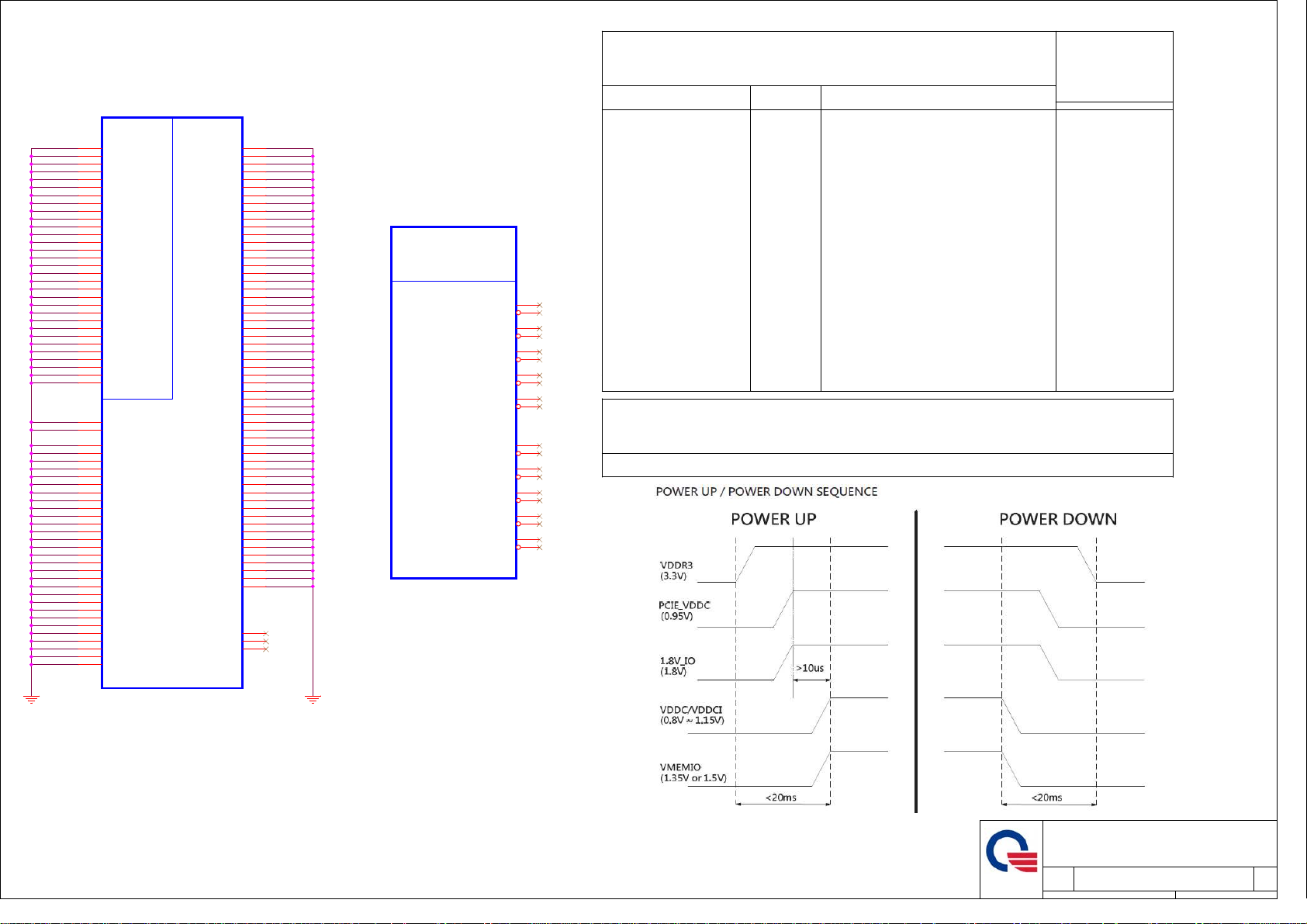

Page 3

5

4

3

2

1

+1.2VSUS7,10,11,35

03

SB only channel B

D D

C C

B B

M_A_A[13:0]10

M_A_BG#110

M_A_ACT#10

M_A_BS#010

M_A_BS#110

M_A_BG#010

M_A_DM[7..0]10

M_A_DQSP010

M_A_DQSN010

M_A_DQSP110

M_A_DQSN110

M_A_DQSP210

M_A_DQSN210

M_A_DQSP310

M_A_DQSN310

M_A_DQSP410

M_A_DQSN410

M_A_DQSP510

M_A_DQSN510

M_A_DQSP610

M_A_DQSN610

M_A_DQSP710

M_A_DQSN710

M_A_CLKP010

M_A_CLKN010

M_A_CLKP110

M_A_CLKN110

M_A_RST#10

M_A_EVENT#10

M_A_CKE010

M_A_CKE110

M_A_ODT010

M_A_ODT110

M_A_CS#010

M_A_CS#110

M_A_RAS#10

M_A_CAS#10

M_A_WE#10

TP65

M_VREF

+1.2VSUS

R8

*1K_1%_4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BG1

M_A_ACT#

M_A_BS#0

M_A_BS#1

M_A_BG0

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

AE28

MA_ADD[0]

Y27

MA_ADD[1]

Y29

MA_ADD[2]

Y26

MA_ADD[3]

W28

MA_ADD[4]

W29

MA_ADD[5]

W26

MA_ADD[6]

U29

MA_ADD[7]

W25

MA_ADD[8]

U26

MA_ADD[9]

AG29

MA_ADD[10]

U27

MA_ADD[11]

T28

MA_ADD[12]

AK26

MA_ADD[13]

T26

MA_ADD[14]/MA_BG[1]

T25

MA_ADD[15]/MA_ACT_L

AG26

MA_BANK[0]

AG27

MA_BANK[1]

T29

MA_BANK[2]/MA_BG[0]

E19

MA_DM[0]

D21

MA_DM[1]

K21

MA_DM[2]

F29

MA_DM[3]

AP28

MA_DM[4]

AV26

MA_DM[5]

AR22

MA_DM[6]

BC22

MA_DM[7]

K29

MA_DM[8]

H19

MA_DQS_H[0]

G19

MA_DQS_L[0]

B22

MA_DQS_H[1]

A22

MA_DQS_L[1]

F23

MA_DQS_H[2]

E23

MA_DQS_L[2]

G27

MA_DQS_H[3]

F27

MA_DQS_L[3]

AP25

MA_DQS_H[4]

AP26

MA_DQS_L[4]

AW27

MA_DQS_H[5]

AV27

MA_DQS_L[5]

AV22

MA_DQS_H[6]

AU22

MA_DQS_L[6]

BA21

MA_DQS_H[7]

AY21

MA_DQS_L[7]

L27

MA_DQS_H[8]

L26

MA_DQS_L[8]

AE25

MA_CLK_H[0]

AE26

MA_CLK_L[0]

AD26

MA_CLK_H[1]

AD27

MA_CLK_L[1]

AB28

MA_CLK_H[2]

AB29

MA_CLK_L[2]

AB25

MA_CLK_H[3]

AB26

MA_CLK_L[3]

N29

MA_RESET_L

AE29

MA_EVENT_L

P27

MA_CKE0

P29

MA_CKE1

AK27

MA0_ODT[0]

AL26

MA0_ODT[1]

AH25

MA1_ODT[0]

AL25

MA1_ODT[1]

AH26

MA0_CS_L[0]

AL29

MA0_CS_L[1]

AH29

MA1_CS_L[0]

AL28

MA1_CS_L[1]

AG24

MA_RAS_L/MA_RAS_L_ADD[16]

AK29

MA_CAS_L/MA_CAS_L_ADD[15]

AH28

M_A_VREFDQ M_A_ZVDDIO

MA_WE_L/MA_WE_L_ADD[14]

B19

MA_VREFDQ

T32

M_VREF

M_VREF

U1A

MEMORY A

FP4 REV 1.0

*FP4-BR

MA_DATA[0]

MA_DATA[1]

MA_DATA[2]

MA_DATA[3]

MA_DATA[4]

MA_DATA[5]

MA_DATA[6]

MA_DATA[7]

MA_DATA[8]

MA_DATA[9]

MA_DATA[10]

MA_DATA[11]

MA_DATA[12]

MA_DATA[13]

MA_DATA[14]

MA_DATA[15]

MA_DATA[16]

MA_DATA[17]

MA_DATA[18]

MA_DATA[19]

MA_DATA[20]

MA_DATA[21]

MA_DATA[22]

MA_DATA[23]

MA_DATA[24]

MA_DATA[25]

MA_DATA[26]

MA_DATA[27]

MA_DATA[28]

MA_DATA[29]

MA_DATA[30]

MA_DATA[31]

MA_DATA[32]

MA_DATA[33]

MA_DATA[34]

MA_DATA[35]

MA_DATA[36]

MA_DATA[37]

MA_DATA[38]

MA_DATA[39]

MA_DATA[40]

MA_DATA[41]

MA_DATA[42]

MA_DATA[43]

MA_DATA[44]

MA_DATA[45]

MA_DATA[46]

MA_DATA[47]

MA_DATA[48]

MA_DATA[49]

MA_DATA[50]

MA_DATA[51]

MA_DATA[52]

MA_DATA[53]

MA_DATA[54]

MA_DATA[55]

MA_DATA[56]

MA_DATA[57]

MA_DATA[58]

MA_DATA[59]

MA_DATA[60]

MA_DATA[61]

MA_DATA[62]

MA_DATA[63]

MA_CHECK[0]

MA_CHECK[1]

MA_CHECK[2]

MA_CHECK[3]

MA_CHECK[4]

MA_CHECK[5]

MA_CHECK[6]

MA_CHECK[7]

MA_ZVDDIO_MEM_S

H17

J17

F20

H20

E17

F17

K18

E20

A21

C21

C23

D23

B20

B21

B23

A23

G22

H22

E25

G25

J20

E22

H23

J23

F26

E27

J26

J27

H25

E26

G28

G29

AN26

AP29

AR26

AP24

AN29

AN27

AR29

AR27

AU26

AV29

AU25

AW25

AU29

AU28

AW26

AT25

AV23

AW23

AV20

AW20

AR23

AT23

AR20

AT20

BB23

BB22

BB20

AY19

BA23

BC23

BC21

BB21

K26

K28

N26

N28

J29

K25

L29

N25

AD29

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

R6 39.2_1%_4

M_A_DQ[0..63] 10

RAM No Support

BR: Support ECC

SR: No support ECC

+1.2VSUS +1.2VSUS

M_B_A[13:0]11

M_B_BG#111

M_B_ACT#11

M_B_BS#011

M_B_BS#111

M_B_BG#011

M_B_DM[7..0]11

M_B_DQSP011

M_B_DQSN011

M_B_DQSP111

M_B_DQSN111

M_B_DQSP211

M_B_DQSN211

M_B_DQSP311

M_B_DQSN311

M_B_DQSP411

M_B_DQSN411

M_B_DQSP511

M_B_DQSN511

M_B_DQSP611

M_B_DQSN611

M_B_DQSP711

M_B_DQSN711

M_B_CLKP011

M_B_CLKN011

M_B_CLKP111

M_B_CLKN111

M_B_RST#11

M_B_EVENT#11

M_B_CKE011

M_B_CKE111

M_B_ODT011

M_B_ODT111

M_B_CS#011

M_B_CS#111

M_B_RAS#11

M_B_CAS#11

M_B_WE#11

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_BG1

M_B_ACT#

M_B_BS#0

M_B_BS#1

M_B_BG0

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

TP66

M_B_VREFDQ

AG31

MB_ADD[0]

AC30

MB_ADD[1]

AC31

MB_ADD[2]

AB32

MB_ADD[3]

AA32

MB_ADD[4]

AA33

MB_ADD[5]

AA31

MB_ADD[6]

Y33

MB_ADD[7]

AA30

MB_ADD[8]

W32

MB_ADD[9]

AG32

MB_ADD[10]

Y32

MB_ADD[11]

W33

MB_ADD[12]

AL31

MB_ADD[13]

W30

MB_ADD[14]/MB_BG[1]

V32

MB_ADD[15]/MB_ACT_L

AH32

MB_BANK[0]

AG33

MB_BANK[1]

W31

MB_BANK[2]/MB_BG[0]

D25

MB_DM[0]

D29

MB_DM[1]

E33

MB_DM[2]

J33

MB_DM[3]

AR30

MB_DM[4]

AW30

MB_DM[5]

BC30

MB_DM[6]

BC26

MB_DM[7]

N33

MB_DM[8]

B26

MB_DQS_H[0]

A26

MB_DQS_L[0]

B30

MB_DQS_H[1]

A30

MB_DQS_L[1]

F32

MB_DQS_H[2]

E32

MB_DQS_L[2]

K32

MB_DQS_H[3]

J32

MB_DQS_L[3]

AR32

MB_DQS_H[4]

AR33

MB_DQS_L[4]

AW32

MB_DQS_H[5]

AW33

MB_DQS_L[5]

BA29

MB_DQS_H[6]

AY29

MB_DQS_L[6]

BA25

MB_DQS_H[7]

AY25

MB_DQS_L[7]

P32

MB_DQS_H[8]

N32

MB_DQS_L[8]

AE33

MB_CLK_H[0]

AE32

MB_CLK_L[0]

AE30

MB_CLK_H[1]

AE31

MB_CLK_L[1]

AD32

MB_CLK_H[2]

AD33

MB_CLK_L[2]

AC33

MB_CLK_H[3]

AC32

MB_CLK_L[3]

T33

MB_RESET_L

AG30

MB_EVENT_L

U32

MB_CKE0

U33

MB_CKE1

AL30

MB0_ODT[0]

AM32

MB0_ODT[1]

AJ32

MB1_ODT[0]

AM33

MB1_ODT[1]

AJ33

MB0_CS_L[0]

AL32

MB0_CS_L[1]

AJ30

MB1_CS_L[0]

AL33

MB1_CS_L[1]

AH33

MB_RAS_L/MB_RAS_L_ADD[16]

AK32

MB_CAS_L/MB_CAS_L_ADD[15]

AJ31

MB_WE_L/MB_WE_L_ADD[14 ]

A19

MB_VREFDQ

R9 *0_5%_4

R10

*1K_1%_4 C26

A A

C25

1000p/50V_4

0.1u/16V_4

C27

0.47u/6.3V_4

MEMORY B

FP4 REV 1.0

U1I

*FP4-BR

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_CHECK[0]

MB_CHECK[1]

MB_CHECK[2]

MB_CHECK[3]

MB_CHECK[4]

MB_CHECK[5]

MB_CHECK[6]

MB_CHECK[7]

MB_ZVDDIO_MEM_S

A25

C25

C27

D27

B24

B25

B27

A27

A29

C29

B32

D32

B28

B29

A31

C31

E30

E31

G33

G32

C33

D33

G30

G31

J30

J31

L33

L32

H32

H33

L30

L31

AN31

AP32

AT32

AU32

AN33

AN32

AR31

AT33

AU30

AV32

BA33

AY32

AU33

AU31

AW31

AY33

BC31

BB30

BB28

AY27

BB32

BA31

BC29

BB29

BB27

BB26

BB24

AY23

BA27

BC27

BC25

BB25

N30

N31

R33

R32

M32

M33

R30

R31

AF32

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_ZVDDIO

R7 39.2_1%_4

M_B_DQ[0..63] 11

RAM No Support

BR: Support ECC

SR: No support ECC

Place within 1000mil of the APU

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

Document Number R ev

Document Number R ev

Document Number R ev

BR & SR 2/7(MEM)

BR & SR 2/7(MEM)

NB5

NB5

5

4

3

2

NB5

BR & SR 2/7(MEM)

Date: Sheet o f

Monday, January 16, 2017 3 48

Date: Sheet o f

Monday, January 16, 2017 3 48

Date: Sheet o f

Monday, January 16, 2017 3 48

1

1A

1A

1A

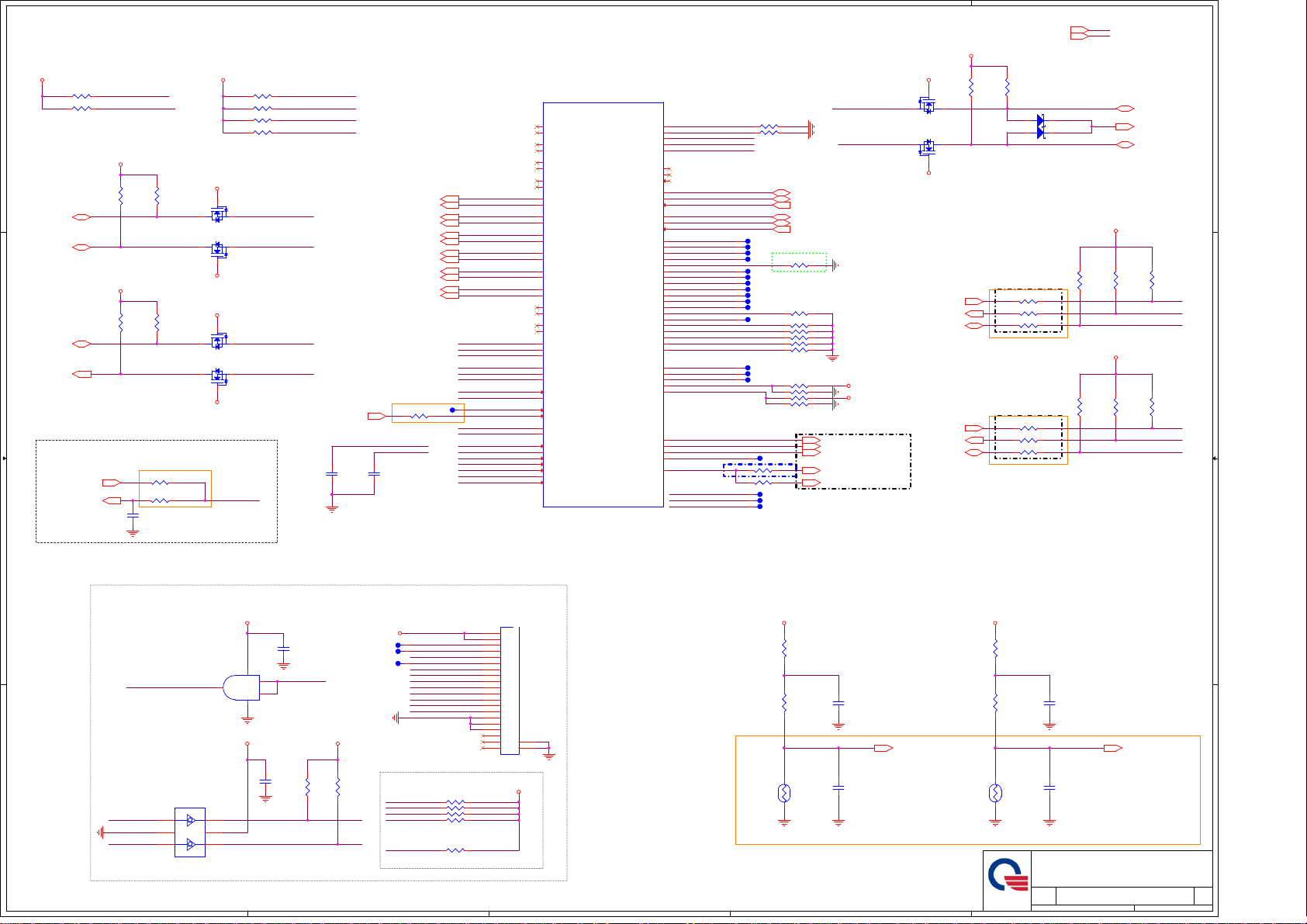

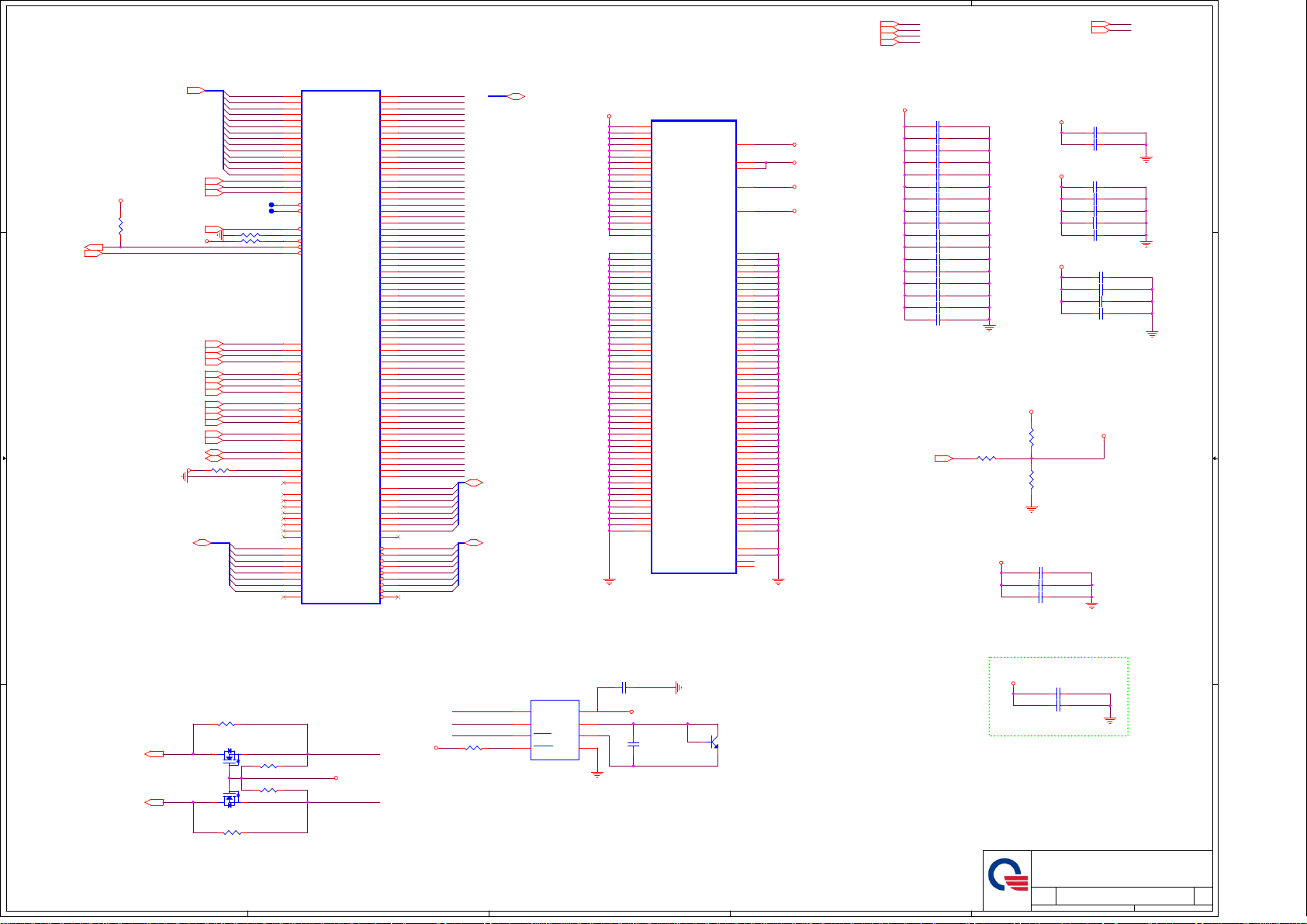

Page 4

5

+1.8V +1.8V

APU_SIC

APU_SID

APU_PROCHOT#_R

APU_ALERT#APU_PWRGD

APU_SIC

APU_SID

CPU_PWRGD_SVID_REG38,40

R13 301_1%_4

D D

C C

R11 301_1%_4

MBCLK211,31

MBDATA211,31

APU_PROCHOT#5

APU_DPST_PWM20

APU_RST#

+3V

R17

2.2K_5%_4

+3V

R25

2.2K_5%_4

APU_PROCHOT#

R22

2.2K_5%_4

R26

2.2K_5%_4

+1.8V

5

3 4

6 1

2

+1.8V

+1.8V

5

3 4

6 1

2

+1.8V

R12 1K_1%_4

R14 1K_1%_4

R15 1K_1%_4

R16 1K_1%_4

Q3A

DMN5L06DWK-7

Q3B

DMN5L06DWK-7

APU_PROCHOT#_R

Q4A

DMN5L06DWK-7

Q4B

DMN5L06DWK-7

APU_DPST_PWM_R

EC H_PROCHOT#

VRHOT38,40

H_PROCHOT#31

R42 *0_4/S

R44 *0_4/S

C30

220p/50V_4

APU_PROCHOT#

4

HDMI

eDP

Thermal Sensor

APU_RST#

APU_PWRGD

C29

C28

*150p/50V_4

*150p/50V_4

IN_D221

IN_D2#21

IN_D121

IN_D1#21

IN_D021

IN_D0#21

IN_CLK21

IN_CLK#21

INT_eDP_TXP020

INT_eDP_TXN020

INT_eDP_TXP120

INT_eDP_TXN120

R36 *0_4/S

3

U1C

DP2_TXP[0]

DP2_TXN[0]

DP2_TXP[1]

DP2_TXN[1]

DP2_TXP[2]

DP2_TXN[2]

DP2_TXP[3]

DP2_TXN[3]

DP1_TXP[0]

DP1_TXN[0]

DP1_TXP[1]

DP1_TXN[1]

DP1_TXP[2]

DP1_TXN[2]

DP1_TXP[3]

DP1_TXN[3]

DP0_TXP[0]

DP0_TXN[0]

DP0_TXP[1]

DP0_TXN[1]

DP0_TXP[2]

DP0_TXN[2]

DP0_TXP[3]

DP0_TXN[3]

SVT0

SVC0

SVD0

SVT1

SVC1

SVD1

SIC

SID

RESET_L

PWROK

PROCHOT_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

DISPLAY/SVI2/JTAG /TEST

FP4 REV 1.0

*FP4-BR

TEMPINRETURN

DP_STEREOSYNC/TEST36

VDDCR_GFX_SENSE

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

B6

A6

D7

C7

A7

B7

D9

C9

A2

A3

B4

A4

D5

C5

A5

B5

E2

E1

E3

E4

D1

D2

C1

B1

SVT

SVC

SVD

GFX_SVT_R

GFX_SVC_R

GFX_SVD_R

APU_SIC

APU_SID

APU_RST#

TP18

APU_PWRGD

APU_PROCHOT#_R

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

C15

D17

D19

B15

B16

A18

B18

C17

D15

C19

A15

B17

H15

H14

D13

G15

J14

C13

A11

DP_ZVSS

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP2_AUXP

DP2_AUXN

DP2_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

TEMPIN0

TEMPIN1

TEMPIN2

TEST28_H

TEST28_L

RSVD_1

TEST410

TEST411

TEST4

TEST5

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST11

TEST18

TEST19

TEST31

TEST37

A9

DP_AUX_ZVSS

B9

APU_LVDS_BLON_R

G5

APU_DISP_ON_R

G6

APU_DPST_PWM_R

F11

H9

G9

E9

F7

E7

F5

F8

E8

G8

K24

CORETYPE

APU_TEMPIN0

E15

APU_TEMPIN1

E14

APU_TEMPIN2

E12

APU_TEMPRETURN

F14

APU_TEST410

AK24

APU_TEST411

AL24

APU_THERMDA

P24

APU_THERMDC

N24

APU_TEST6

AN24

APU_TEST9

AB8

APU_TEST10

Y9

APU_TEST14

B10

APU_TEST15

D11

APU_TEST16

A10

APU_TEST17

C11

APU_TEST11

B11

APU_TEST18

A14

APU_TEST19

B14

APU_TEST28_H

A13

APU_TEST28_L

B13

APU_TEST31

P26

DP_STEREOSYNC

E11

APU_TEST37

A17

R19 2K_1%_4

R21 150_1%_4

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP75

TP11

TP12

TP13

TP14

TP15

TP16

TP17

DP_STEREOSYNC: HDMI enable pin.

H11

J12

G12

VDDP_SENSE

VDDP_SENSE

VSS_SENSE

AY18

VSS_SENSE

H12

CPU_VDD0_RUN_FB_H

CPU_VDDNB_RUN_FB_H

APU_VDDGFX_RUN_FB_H

TP19

R40 0_5%_4

R43 0_5%_4

TP20

TP21

TP22

INT_HDMI_AUXP 21

INT_HDMI_AUXN 21

HDMI_HPD_Q 21

INT_eDP_AUXP 20

INT_eDP_AUXN 20

EDP_HPD 20

R23 *0_5%_4

R24 *1K_1%_4

R27 *1K_1%_4

R28 *1K_1%_4

R29 *1K_1%_4

R30 1K_1%_4

R31 1K_1%_4

R32 1K_1%_4

R33 *1K_1%_4

R34 *1K_1%_4

R35 *1K_1%_4

DIFFERENTIAL ROUTING

BR: Stuff

SR: No Stuff

2

APU_LVDS_BLON_R

Q2A

DMN5L06DWK-7

Q2B

DMN5L06DWK-7

APU_DISP_ON_R

+1.8V

+1.8V

APU_VDDGFX_RUN_FB_H 40

CPU_VDDNB_RUN_FB_H 38

CPU_VDD0_RUN_FB_H 38

APU_VDDGFX_RUN_FB_L 40

CPU_VDD0_RUN_FB_L 38

+3V

+1.8V

5

2

+1.8V

R18

R20

2.2K_5%_4

2.2K_5%_4

34

D2 RB500V-40

61

D3 RB500V-40

APU Serial VID

Place near APU within 500mil

CPU_SVT38

CPU_SVC38

CPU_SVD38

R48 *0_4/S

R50 *0_4/S

R51 *0_4/S

GFX Serial VID

BR: Stuff

SR: No Stuff

Place near APU within 500mil

GFX_SVT40

GFX_SVC40

GFX_SVD40

R57 *0_4/S

R58 *0_4/S

R59 *0_4/S

1

+3V5,6,7,10,11,20,21,22,24,26,27,28,29,30,31,38,40,43

+1.8V5,22,25,28,38,40,43

2

1

2

1

+1.8V

R45

*1K_1%_4

+1.8V

R53

*1K_1%_4

APU_LVDS_BLON 20

PCIE_RST# 5,13,24,27,28

APU_DISP_ON 20

R46

R47

*1K_1%_4

*1K_1%_4

R55

R54

*1K_1%_4

*1K_1%_4

GFX_SVT_R

GFX_SVC_R

GFX_SVD_R

04

SVT

SVC

SVD

B B

HDT+ Connector for Debug only

Can remove on MP

CPU_LDT_RST_HTPA#

A A

APU_RST#

APU_PWRGD

U3

74LVC2G07GW

A1

1

2

GND

3

A24Y2

VCC

+3V +3VPCU

+1.8V

APU_TEST18_TP

TP73

C31

0.1u/16V_4

APU_RST#

3 5

+3V

APU_RST_L_BUF

APU_PWROK_BUF

1

2

U2

TC7SH08FU(F)

C34

0.1u/16V_4

R61

1K_1%_4

+1.8V

R62

1K_1%_4

4

Y1

6

5

APU_TEST19_TP

TP74

APU_RST_L_BUF

CPU_LDT_RST_HTPA#

TP23

APU_DBREQ#

APU_DBRDY

APU_TCK

APU_TMS

APU_TDI

APU_TRST#

APU_TDO

APU_PWROK_BUF

Close to HDT & No remove.

APU_TDI

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

R63 1K_1%_4

R64 1K_1%_4

R65 1K_1%_4

R66 1K_1%_4

R67 1K_1%_4

HDT

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

21

1

22

*HDT CONN

88511-2001-20p-l

+1.8V

CPU Thermal Protect

+3VPCU

R213

16.5K_1%_4

R214

3.3K_1%_4

12

TM0

100K_NTC_4_3%

C258

0.1u/16V_4

C259

0.1u/16V_4

THERMISTOR_SHDN 31

1/8: PV Change net name

5

4

3

2

Pipe Thermal Protect

R49

16.5K_1%_4

R52

3.3K_1%_4

12

TM1

100K_NTC_4_3%

NB5

NB5

NB5

C32

0.1u/16V_4

THERMISTOR 31

C33

0.1u/16V_4

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

Document Number R ev

Document Number R ev

Document Number R ev

BR & SR 3/7(DIS/MISC)

BR & SR 3/7(DIS/MISC)

BR & SR 3/7(DIS/MISC)

Date: Sheet o f

Monday, January 16, 2017 4 48

Date: Sheet o f

Monday, January 16, 2017 4 48

Date: Sheet o f

Monday, January 16, 2017 4 48

1

1A

1A

1A

Page 5

5

D D

+1.8VS5

R86

47K_1%_4

2

RSMRST#31

+3V

R87 2.2K_5%_4

R88 2.2K_5%_4

R89 10K_1%_4

R90 10K_1%_4

C C

B B

R92 10K_1%_4

R94 10K_1%_4

G2 *0_5%_4

+3VS5

R101 2.2K_5%_4

R103 2.2K_5%_4

R105 10K_1%_4

R108 10K_1%_4

R110 *10K_1%_4

R216 10K_1%_4

SMB_RUN_CLK

SMB_RUN_DAT

PCIE_CLKREQ_CARD#

CLKREQG#

AGPIO69

AGPIO65

SYS_RST#

SMB_ALW_CLK

SMB_ALW_DAT

DNBSWON#

PCIE_WAKE#

DGPU_PWROK

SSD_DET#

1

D4

RB500V-40

C39

1u/6.3V_4

to DDR3 SMBUS

BR: Stuff

SR: No Stuff

to TP SMBUS

KBC_RST#29,31

PCIE_RST#4,13,24,27,28

HDA INTERFACE

ACZ_SDOUT_AUDIO22

ACZ_SYNC_AUDIO22

BIT_CLK_AUDIO22

ACZ_RST#_AUDIO22

ACZ_SDIN022

R119 33_5%_4

R120 33_5%_4

R121 33_5%_4

EC1 15p/50V_4

R122 33_5%_4

ACZ_SDOUT_R

ACZ_SYNC_R

ACZ_BCLK_R

ACZ_RST#_R

ACZ_SDIN0

GPU CLK REQ

A A

DGPU_PR_EN31,44,47

5

DIS: Stuff

UMA: No Stuff

R125 30K_1%_4

C43

0.47u/6.3V_4

Q5

2

METR5213-G

1 3

APU_S5_MUX_CTRL42

PCIE_CLKREQ_CARD#28

PCIE_CLKREQ_LAN#24

PCIE_CLKREQ_WLAN#27

DNBSWON#31

DGPU_PWROK31,44,46,47

EC_RCIN#31

EC_A20GATE31

SIO_EXT_SCI#31

SIO_EXT_SMI#31

PCI_SERR#31

ODD_PWR26

CLKREQG#

SYS_RST#6

PCIE_WAKE#24,27,28

C40

18p/50V_4

C41

18p/50V_4

4

C35 150p/50V_4

R84 33_5%_4

R85 33_5%_4

C36 150p/50V_4

C38 *0.1u/16V_4

SUSB#31

SUSC#31

TP72

TP26

TP28

TP29

TP30

TP31

R96 1K_1%_4

R97 *10K_1%_4

R98 10K_1%_4

R99 10K_1%_4

R209 1K_1%_4

R208 1K_1%_4

R207 1K_1%_4

R109 10K_1%_4

RTC_CLK6

12

Y1

32.768KHZ/20ppm

4

C37 *100p/50V_4

R91 *0_4/S

LLB#

PCIE_CLKREQ_CARD#

CLKREQG#

JTAG_TRST#

JTAG_TDI

JTAG_TCK

JTAG_TDO

ACZ_BCLK_R

ACZ_SDIN0

ACZ_SDIN1

ACZ_SDIN2

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

BOARD_ID8

BOARD_ID9

BOARD_ID10

EGPIO148

SYS PWRGD

LPC_RST#_R

R112

20M_5%_4

CPU_VRM8380_PG38

PCIE_RST#_C

RSMRST#_R

DNBSWON#

SYS_PWRGD

SYS_RST#

PCIE_WAKE#

DGPU_PWROK

APU_TEST0

APU_TEST1

APU_TEST2

ODD_PLUGIN#

PCI_SERR#_R

32K_X1

32K_X2

ECPWROK31

BB12

LPC_RST_L

AN7

PCIE_RST_L/EGPIO26

S5

RSMRST_L

PWR_BTN_L/AGPIO0

PWR_GOOD

SYS_RESET_L/AGPIO1

S5

WAKE_L/AGPIO2

S5

SLP_S3_L

SLP_S5_L

S0A3_GPIO/AGPIO10

S5

S5_MUX_CTRL/EGPIO42

S5

TEST0

TEST1/TMS

TEST2

ESPI_RESET_L/KBRST_L/AGPIO129

GA20IN/AGPIO126

S0

LPC_PME_L/AGPIO22

S5

LPC_SMI_L/AGPIO86

S0

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

IR_TX0/USB_OC5_L/AGPIO13

IR_TX1/USB_OC6_L/AGPIO14

IR_RX1/AGPIO15

IR_LED_L/LLB_L/AGPIO12

CLK_REQ0_L/SATA_IS0_L/ SATA_ZP0_L/AGPIO92

CLK_REQ1_L/AGPIO115

CLK_REQ2_L/AGPIO116

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

CLK_REQG_L/OSCIN/EGPIO132

USB_OC0_L/TRST_L/AGPIO16

USB_OC1_L/TDI/AGPIO17

USB_OC2_L/TCK/AGPIO18

USB_OC3_L/TDO/AGPIO24

AZ_BITCLK/I2S_BCLK_MIC

AZ_SDIN0/I2S_DATA_MIC[0]

AZ_SDIN1/I2S_LR_PLAYBACK

AZ_SDIN2/I2S_DATA_PLAYBACK

AZ_RST_L/I2S_LR_MIC

AZ_SYNC/I2S_BCLK_PLAYBACK

AZ_SDOUT/I2S_DATA_MIC1

I2C0_SCL/EGPIO145

S0

I2C0_SDA/EGPIO146

S0

I2C1_SCL/EGPIO147

S0

I2C1_SDA/EGPIO148

S0

RTCCLK

X32K_X1

X32K_X2

D1

1

3

2

BAT54AW-L

AY15

BC19

BB13

BC15

BB17

BC17

BB18

BB16

BB10

AE4

AE1

BC9

AF2

AG2

AK7

AH5

AE8

AH8

AH6

AK8

AE3

AD7

AG3

AD5

AL8

AN8

AE2

AH9

AG1

AH2

AL9

AU6

AR8

AP6

AR5

AU9

AT9

AR7

BB9

BB7

BC7

AG7

AT1

AT2

3

ACPI/SD/AZ/GPIO/RTC/I2C/ UART/MI SC

X

X

S5

X

S5

X

Power Domain

CZ CZ-L

S0

S0

S0

S5

X

S5

S5

S5

S5

S5

S5

S5

S5

S5

S5

S5

S0

S0

S0

S0

S0

S0

S0

S0

S0

S5

S5

S5

S5

S5

S5

S5

S5

X

S0

S0

S0

FP4 REV 1.0

+3V

3

U1D

S0

S0

S0

S0

S0

S5

*FP4-BR

R123

10K_1%_4

R124 *0_4/S

C42

*2.2u/10V_4

SD0_WP/EGPIO101

S0

S0

SD0_PWR_CTRL/AGPIO102

X

S0

S0

S5

SD0_CLK/EGPIO95

S0

S0

SD0_CMD/EGPIO96

S0

S0

SD0_DATA0/EGPIO97

S0

S0

SD0_DATA1/EGPIO98

S0

S0

SD0_DATA2/EGPIO99

S0S5S0

SD0_DATA3/EGPIO100

S0S5S0

SD0_LED/EGPIO93

S0

S0

SCL0/I2C2_SCL/EGPIO113

S0

S0

SDA0/I2C2_SDA/EGPIO114

S0

S0

SCL1/I2C3_SCL/AGPIO19

S5

S5

SDA1/I2C3_SDA/AGPIO20

S5

S5

S5

S5

S5

S5

S5

AGPIO6/LDT_RST_L

S5

S5

AGPIO7/LDT_PWROK

S5

S5

S5

S5

S5

S5

VDDGFX_PD/AGPIO39

S5

X

S5

X

S0

S0

S0

S0

AGPIO66/SHUTDOWN_L

S0

S0

AGPIO68/SGPIO_CLK

S0

S0

AGPIO69/SGPIO_LOAD

S0

S0

AGPIO71/SGPIO_DATAOUT

S0

S0

AGPIO72/SGPIO_DATAIN

S0

S0

S0

S0

BLINK/USB_OC7_L/AGPIO1 1

S5

S0

GENINT1_L/AGPIO89

S0

S0

GENINT2_L/AGPIO90

S0

S0

FANIN0/AGPIO84

S0

S0

FANOUT0/AGPIO85

S0

S0

UART0_CTS_L/EGPIO135

S0

X

UART0_RXD/EGPIO136

S0

X

UART0_RTS_L/EGPIO137

S0

X

UART0_TXD/EGPIO138

X

S0

UART0_INTR/AGPIO139

X

S0

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

X

UART1_RXD/BT_I2S_SDI/EGPIO141

S5

UART1_RTS_L/EGPIO142

X

UART1_TXD/BT_I2S_SDO/EGPIO143

X

UART1_INTR/BT_I2S_LRCLK/AGPIO144

S0

SYS_PWRGD

SD0_CD/AGPIO25

AGPIO3

AGPIO4

AGPIO5

AGPIO8

AGPIO9

AGPIO40

AGPIO64

AGPIO65

SPKR/AGPIO91

BB2

BB5

BC2

BB4

AY5

BC3

BA3

BC5

BA5

BB6

BA15

AY17

AG5

AG4

AL5

AL6

AJ1

AJ3

AH1

AJ4

AK5

AD8

AG8

AW15

AU15

AT15

AU12

AT14

AR14

BC13

BA17

AN5

BB14

BA19

BC18

BB19

AY9

AW8

AV5

AV8

AW9

AV11

AU7

AT11

AR11

AP9

2

R219 *10K_1%_4

R221 *10K_1%_4

R223 *10K_1%_4

BOARD_ID5

BOARD_ID6

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID7

SMB_RUN_CLK

SMB_RUN_DAT

SMB_ALW_CLK

SMB_ALW_DAT

SSD_DET#

TP_INTH#

PROCHOT#_CTRL

AGPIO64

AGPIO65

AGPIO66

AGPIO68

AGPIO69

AGPIO71

AGPIO72

GENINT1

ACCEL_INTH#_1

GENINT1: Hardware Validated Boot function

Vss: Enabke

NC: Disable

BOARD_ID8

BOARD_ID9

BOARD_ID10

BOARD_ID1 20

R93 *0_4/S

TP71

TP67

TP27

TP76

TP69

TP70

R100 *0_5%_4

R102 *0_4/S

TP77

TP78

TP79

TP80

R104 10K_1%_4

R106 10K_1%_4

R107 10K_1%_4

VGA_RSTB 13

SMB_RUN_CLK 10,11

SMB_RUN_DAT 10,11

SMB_ALW_CLK 30

SMB_ALW_DAT 30

AGPIO3 6

SSD_DET# 27

ODD_DA#_FCH 26

TP_INTH# 30

APU_PROCHOT# 4

VDDGFX_PD 40

APU_VRM_GFX_PWRGD 40

ACZ_SPKR 22

AGPIO11 6

ACCEL_INTH# 29

12/7: SI Modify

Follow AMD checklist 53537_1_09 suggestion.

+3VS5

R113 *2.2K_5%_4

R115 *1K_1%_4

R117 *2.2K_5%_4

TEST2 TEST1 TEST0 Description

0

0 0

0

0

0

1

1

TMS

1 TMS

2

1

+3V4,6,7,10,11,20,21,22,24,26,27,28,29,30,31,38,40,43

+1.8V4,22,25,28,38,40,43

+3VS56,7,25,27,30,31,34,35,37,42,43,44,47

+1.8VS57,25,36,37,43,47

+3V+1.8V

R68 10K_1%_4

R70 10K_1%_4

R72 10K_1%_4

R74 10K_1%_4

R76 10K_1%_4

R78 *10K_1%_4

R80 *10K_1%_4

R82 *10K_1%_4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

BOARD_ID6

BOARD_ID7

R69 *10K_1%_4

R71 *10K_1%_4

R73 *10K_1%_4

R75 *10K_1%_4

R77 *10K_1%_4

R79 10K_1%_4

R81 10K_1%_4

R83 10K_1%_4

BOARD ID SETTING

Board ID 0 Defin itio n

0

1

Board ID [2:1]

00

01

10 17"

11 15.6" 2SPD

Board ID [4:3]

00

01

10

11

Board ID [5]

0/1

Board ID [6] Defi niti on

RF_OFF 27

VGA_ON_SB 31

0/1

Board ID [7] GPU

0/1 M1-70/ M1-30

Board ID [9:8] Definitio n

00

01

10

11

Board ID [10] Definiti on

0/1

APU_TEST0

APU_TEST1

APU_TEST2

FCH TAP accessible from APU when TAPEN is asserted

FCH JTAG pins are overloaded for multiple

functions, in this configuration the FCH JTAG are

used as non-JTAG pins

1

Reserved

X

Reserved

FCH JTAG multi-function pins are configured as

0

JTAG pins, in this configuration the FCH TAP

can be accessed from FCH JTAG pins

Use on ATE only

1

Yuba JTAG enabled

R114 15K_1%_4

R116 15K_1%_4

R118 15K_1%_4

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

NB5

NB5

NB5

Date: Sheet o f

Monday, January 16, 2017 5 48

Date: Sheet o f

Monday, January 16, 2017 5 48

Date: Sheet o f

Monday, January 16, 2017 5 48

UMA

DIS

Definiti on

14"

15.6" 1SPD

Definiti on

PORT0 SATA only

PORT0 SATA

PORT1 SSD

PORT0 SATA

PORT1 ODD

PORT0 SATA

PORT1 SSD

USB3.0 to ODD

Definiti on

BR/SR

VRAM Size X8/ X4

NFL-P

NFL-C

VINE -DF

Rese rve

Rese rve

Document Number R ev

Document Number R ev

Document Number R ev

BR & SR 4/7(GPIO/AZ/UART)

BR & SR 4/7(GPIO/AZ/UART)

BR & SR 4/7(GPIO/AZ/UART)

1

05

1A

1A

1A

Page 6

5

Follow Checklist

D D

C C

+3V

R129 10K_1%_4

R133 10K_1%_4

C44 5.6p/50V_4

Y2

48MHZ/15ppm

C45 5.6p/50V_4

SPK_ID

EGPIO119

1

2

R134

1M_5%_4

4

3

OPTION: ODD or SSD(M.2)

CLK_GFX_P13

CLK_GFX_N13

CLK_PCIE_CARDP28

CLK_PCIE_CARDN28

48M_X1

48M_X2

CLK_33M_DEBUG27

CLK_33M_KBC31

CLK_PCI_TPM29

CLK_PCIE_LANP24

CLK_PCIE_LANN24

CLK_PCIE_WLANP27

CLK_PCIE_WLANN27

C46 *10p/50V_4

C47 *10p/50V_4

C48 *10p/50V_4

SATA_LED#28

For EMI

EC2

*10p/50V_4

4

AU3

SATA_TXP026

SATA_TXN026

HDD

SATA_RXN026

SATA_RXP026

SATA_TXP126

SATA_TXN126

SATA_RXN126

SATA_RXP126

R130 1K_1%_4

+0.95V

SPK_ID22

BT_OFF27

R126 1K_1%_4

R132 *0_4/S

R225 *0_4/S

R226 *0_4/S

R227 *0_4/S

R228 *0_4/S

R229 *0_4/S

R230 *0_4/S

R231 *0_4/S

R232 *0_4/S

TP35

TP36

R138 22_5%_4

R139 *22_5%_4

R140 22_5%_4

ACC_LED#28

LFRAME#27,29,31

SERIRQ29,31

CLKRUN#31

R141

10K_1%_4

LAD027,29,31

LAD127,29,31

LAD227,29,31

LAD327,29,31

TP39

SATA_CALRN

SATA_CALRP

SPK_ID

BT_OFF

SB_SATA_LED#

TP33

TP34

CLK_GFX_P_R

CLK_GFX_N_R

CLK_PCIE_CARDP_R

CLK_PCIE_CARDN_R

CLK_PCIE_LANP_R

CLK_PCIE_LANN_R

CLK_PCIE_WLANP_R

CLK_PCIE_WLANN_R

GPP_CLK3P

GPP_CLK3N

TP37

TP38

APU_SPI_CLKAPU_SPI_CLK

APU_SPI_CS0#

EGPIO119

APU_SPI_SI

APU_SPI_SO

APU_SPI_WP

APU_SPI_HOLD#

48M_X1

48M_X2

LPC_CLK0

LPC_CLK1

LFRAME#

LDRQ#0

LPC_PD#

SATA_TX0P

AU4

SATA_TX0N

AV1

SATA_RX0N

AV2

SATA_RX0P

AY2

SATA_TX1P

AY1

SATA_TX1N

AW4

SATA_RX1N

AW3

SATA_RX1P

AW1

SATA_ZVSS

AW2

SATA_ZVDDP

AT17

DEVSLP[0]/EGPIO67

AT12

DEVSLP[1]/EGPIO70

BB15

SATA_ACT_L/AGPIO13 0

AU2

SATA_X1

AU1

SATA_X2

U4

GFX_CLKP

U3

GFX_CLKN

U1

GPP_CLK0P

U2

GPP_CLK0N

W4

GPP_CLK1P

W3

GPP_CLK1N

W1

GPP_CLK2P

W2

GPP_CLK2N

Y2

GPP_CLK3P

Y1

GPP_CLK3N

BC10

X25M_48M_OSC

T2

X48M_X1

T1

X48M_X2

AW14

LPCCLK0/EGPIO74

AY13

LPCCLK1/EGPIO75

BB11

LAD0

BA11

LAD1

AY11

LAD2

BA13

LAD3

AV14

LFRAME_L

BA1

ESPI_ALERT_L/LDRQ 0_L

BC14

SERIRQ/AGPIO87

BC11

LPC_CLKRUN_L/AGPIO88

AE9

LPC_PD_L/AGPIO21

BC6

SPI_CLK/ESPI_CLK /EGPIO117

BB8

SPI_CS1_L/EGPIO1 18

AW7

SPI_CS2_L/ESPI_C S_L/EGPIO119

BA9

SPI_DI/ESPI_DAT A/EGPIO120

AY7

SPI_DO/EGPIO121

AW11

SPI_WP_L/EGPIO1 22

BA7

SPI_HOLD_L/EGPIO133

AW12

SPI_TPM_CS_L/AGPIO76

3

U1E

CLK/SATA/USB/SPI/LPC

FP4 REV 1.0

*FP4-BR

USBCLK/25M_48M_OSC

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

USB_SS_3TXP

USB_SS_3TXN

USB_SS_3RXP

USB_SS_3RXN

AP8

AP5

AR2

AR1

AR3

AR4

AN2

AN1

AN3

AN4

AM1

AM2

AL2

AL1

AL3

AL4

AK2

AJ2

AD2

AD1

AA3

AA4

W9

W8

AA2

AA1

W5

W6

AC1

AC2

Y6

Y7

AC4

AC3

AB5

AB6

USB_ZVSS

USBSS_CALRN

USBSS_CALRP

R128 11.8K_1%_4

USBP0+ 20

USBP0- 20

USBP1+ 20

USBP1- 20

USBP2+ 20

USBP2- 20

USBP3+ 27

USBP3- 27

USBP4+ 25

USBP4- 25

USBP5+ 28

USBP5- 28

USBP6+ 28

USBP6- 28

USBP7+ 26

USBP7- 26

R135 1K_1%_4

R136 1K_1%_4

USB30_TX0+ 25

USB30_TX0- 25

USB30_RX0+ 25

USB30_RX0- 25

USB30_TX1+ 28

USB30_TX1- 28

USB30_RX1+ 28

USB30_RX1- 28

USB30_TX2+ 28

USB30_TX2- 28

USB30_RX2+ 28

USB30_RX2- 28

USB30_TX3+ 26

USB30_TX3- 26

USB30_RX3+ 26

USB30_RX3- 26

2

IR CAM

9/14: Modify

TOUCH SCREEN

CAMERA

BT

USB3.0 Type C CONN

USB3.0 CONN ON DB

USB3.0 CONN 9/8: Modify

USB3.0 to SATA10/3: Modify

USB2 & USB3 MAPPING (Use form Port4)

USB2 PORT4 => USB3 PORT0

USB2 PORT5 => USB3 PORT1

USB2 PORT6 => USB3 PORT2

USB2 PORT7 => USB3 PORT3

+0.95VS5

Support S3~S5 wake up

USB3.0 C CONN ON MB

USB3.0 CONN ON DB

USB3.0 CONN ON MB

9/8: New add

USB3.0 TO Sata ODD

+3VS5 +3VS5 +3VS5+3VS5+3V +3V +3V

1

+3VS55,7,25,27,30,31,34,35,37,42,43,44,47

+0.95VS57,36,42

+3V4,5,7,10,11,20,21,22,24,26,27,28,29,30,31,38,40,43

+1.8V_ROM7,31,43

06

STRAPS PINS

OVERLAP COMMON PADS WHERE

B B

+1.8V_ROM

H_MOSI 31

H_MISO 31

R173

*1K_1%_4

R157

APU_SPI_CS0#

APU_SPI_CLK

APU_SPI_SO

APU_SPI_SI

A A

APU_SPI_WP

APU_SPI_HOLD#

Close SPI ROM

R166 33_5%_4

R168 33_5%_4

R169 33_5%_4

R170 33_5%_4

R171 *0_5%_4

R174 *0_5%_4

5

10K_1%_4

H_SPICS# 31

H_SPICLK 31

APU SPI ROM

Vender

WND

EON

Socket

H_SPI_WP 31

4

Size

8M

8M

8M

DFHS08FS023

P/N (1.8V)

AKE5EZN0N00

AKE5EFN0Q00

R167

*10K_1%_4

H_SPI_HOLD# 31

3

POSSIBLE FOR DUAL-OP RESISTORS.

AGPIO35

RTC_CLK5

AGPIO115

SYS_RST#5

REQUIRED STRAPS

LPC_CLK0

PULL

HIGH

PULL

LOW

BOOT FAIL TIMER

ENABLED

BOOT FAIL TIMER

DISABLED

DEFAULT

Use 48Mhz crystal clock

and generate both internal

and external clocks

Use 100Mhz PCIE clock as

reference clock and generate

internal clocks only

LPC_CLK0

LPC_CLK1

LFRAME#

LPC_CLK1

DEFAULT

LFRAME#

SPI ROM

DEFAULT

LPC ROM

2

R143

R144

*10K_1%_4

10K_1%_4

R152

R151

*2K_1%_4

2K_1%_4

CZ-L BR & SR

1.8V SPI ROM

3.3V SPI ROM

DEFAULT

AGPIO3

Int Pull-Up

R146

R145

10K_1%_4

R153

*2K_1%_4

10K_1%_4

R154

*2K_1%_4

R147

*10K_1%_4

R150

2K_1%_4

R148

*10K_1%_4

R155

*2K_1%_4

12/2: SI Modify

RTC_CLK

Int Pull-Up Int Pull-Up Int Pull-Up

Enhanced reset logic

(for quicker S5 resume)

DEFAULT DEFAULT DEFAULT

Default to

traditional reset logic

Coin battery is

on board.

Coin battery is

not on board.

NB5

NB5

NB5

LDT_RST#/LDT_PWRGD

output to APU

LDT_RST#/LDT_PWRGD

output to Pads

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

Date: Sheet o f

Monday, January 16, 2017 6 48

Date: Sheet o f

Monday, January 16, 2017 6 48

Date: Sheet o f

Monday, January 16, 2017 6 48

R149

10K_1%_4

R156

*2K_1%_4

AGPIO11=BLINK

SYS_RST#

normal reset mode

DEFAULT

short reset mode

Document Number R ev

Document Number R ev

Document Number R ev

BR & SR 5/7(SATA/USB/SPI)

BR & SR 5/7(SATA/USB/SPI)

BR & SR 5/7(SATA/USB/SPI)

1

1A

1A

1A

Page 7

5

4

3

+3VS55,6,25,27,30,31,34,35,37,42,43,44,47

+1.8VS55,25,36,37,43,47

+0.95VS56,36,42

2

+VCC_CORE38,39

+APU_VDDGFX40,41

+1.2VSUS3,10,11,35

+VDDCR_FCH_S542

+0.95V2,6,37

+BAT_RTC30,33,48

1

07

U8

W7

W12

W15

W18

W21

Y8

Y10

Y13

Y16

Y19

Y22

AB7

AB9

AB12

AB15

AB18

AB21

AD6

AD10

AD13

AD16

AD19

AD22

AE7

AE12

AK9

AG10

AK10

AG13

AK13

AG16

AK16

AG19

AK19

AG22

AK22

AH7

AE18

AE21

AH21

AG6

AH12

AN6

AH15

AH18

AL7

AK6

AE15

L8

L13

L16

L19

L22

N7

N12

N15

N18

N21

P8

P13

P16

P19

P22

T7

F12

F15

G11

G14

J8

J9

J11

K7

K12

K13

K15

K16

T12

T15

T18

T21

U13

U16

U19

U22

K19

+VCC_CORE

+APU_VDDGFX

+BAT

1

23

4

+BAT_RTC

C62

C61

22U/6.3VS_6

22U/6.3VS_6

C78

C77

0.22u/10V_4

0.22u/10V_4

+0.95V

C105

C106

22U/6.3VS_6

22U/6.3VS_6

C117

C118

0.22u/10V_4

0.22u/10V_4

BR: Stuff

SR: No Stuff

12/2: SI Modify

R224 470_1%_4

R179 *470_1%_4

VDDBT_RTC

3

2

1

Q7

2N7002K

C63

22U/6.3VS_6

C79

0.22u/10V_4

C64

22U/6.3VS_6

C80

0.22u/10V_4

C65

22U/6.3VS_6

C81

0.22u/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

BOTTOM SIDE DECOUPLING UNDER APU

C94

C92

10U/6.3VS_6

C96

0.22u/10V_4

C107

22U/6.3VS_6

C119

0.22u/10V_4

C93

10U/6.3VS_6

C97

0.22u/10V_4

C108

22U/6.3VS_6

C120

0.22u/10V_4

10U/6.3VS_6

C98

0.22u/10V_4

C109

22U/6.3VS_6

C121

0.22u/10V_4

C95

10U/6.3VS_6

BOTTOM SIDE DECOUPLING UNDER APU

20MIL

+3VRTC

C148

0.1u/16V_4

+3VPCU

+VCCRTC_2

R218

10K_5%_4

2

3

1

D8 BAT54CW-7-F

EC_RTC_RST 31

1/8: PV Modify

C66

22U/6.3VS_6

C82

0.22u/10V_4

C99

0.22u/10V_4

C110

22U/6.3VS_6

C122

0.22u/10V_4

C67

22U/6.3VS_6

C100

0.22u/10V_4

C111

22U/6.3VS_6

U5

3

AP2138N-1.5TRG1

C149

1u/6.3V_4

C83

0.22u/10V_4

C123

0.22u/10V_4

VIN

VOUT

C69

C68

22U/6.3VS_6

22U/6.3VS_6

C84

C85

0.22u/10V_4

180p/50V_4

C102

C101

180p/50V_4

0.22u/10V_4

C112

C113

22U/6.3VS_6

22U/6.3VS_6

C125

0.22u/10V_4

+1.5V_RTC

C126

180p/50V_4

C124

0.22u/10V_4

2

GND

1

C145

10u/6.3V_6

+1.2VSUS

3A

P25

VDDIO_MEM_S3_1

P28

VDDIO_MEM_S3_2

T24

VDDIO_MEM_S3_3

T27

VDDIO_MEM_S3_4

C51

C52

22U/6.3VS_6

C53

22U/6.3VS_6

D D

22U/6.3VS_6

C54

22U/6.3VS_6

C55

22U/6.3VS_6

C70

0.22u/10V_4

C56

22U/6.3VS_6

C71

0.22u/10V_4

C57

22U/6.3VS_6

C72

0.22u/10V_4

C58

22U/6.3VS_6

C73

0.22u/10V_4

C59

*22U/6.3VS_6

C74

0.22u/10V_4

C60

*22U/6.3VS_6

C75

0.22u/10V_4

BOTTOM SIDE DECOUPLING UNDER APU

C87

C86

0.22u/10V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

ACROSS VDDNB AND VSS SPLIT

+0.95V +VDDP_GFX +VDDP_GFX

C C

BR: Always Stuff

SR: DIS Stuff

UMA No Stuff

R175 *0_6/S

C103

10U/6.3VS_6

C104

0.22u/10V_4

0.22u/10V_4

C88

0.22u/10V_4

R176

*0_5%_4

C89

0.22u/10V_4

C90

180p/50V_4

+APU_VDDIO_AZ

+VDDP_GFX

+APU_VDD_33

+1.8V_ROM

+APU_VDD_18_S5

+APU_VDD_33_S5

+VDDCR_FCH_S5 +VDDCR_FCH_S5_R

R177 *0_4/S

C114

10U/6.3VS_6

C115

10U/6.3VS_6

C116

0.22u/10V_4

+VDDP_S5

+VDDCR_FCH_S5_R

+0.95V

+VDDNB_CORE

C127

0.22u/10V_4

C128

0.22u/10V_4

C129

0.22u/10V_4

C130

0.22u/10V_4

C131

0.22u/10V_4

C132

22u/6.3V_6

C133

22u/6.3V_6

C134

22u/6.3V_6

ACROSS VDDNB AND VSS SPLIT

B B

C136

0.22u/10V_4

C137

0.22u/10V_4

C138

0.22u/10V_4

C139

0.22u/10V_4

C140

0.22u/10V_4

C141

0.22u/10V_4

C142

0.22u/10V_4

C143

0.22u/10V_4

C50

*22U/6.3VS_6

C76

180p/50V_4

C91

180p/50V_4

C135

22u/6.3V_6

C144

180p/50V_4

AB24

AB27

AB30

AB33

AD25

AD28

AD30

AE24

AE27

AF30

AF33

AG25

AG28

AH24

AH27

AH30

AK25

AK28

AK30

AK33

AL27

AM30

AR19

AP19

AP21

AP16

AP18

AP10

AP15

AR15

AN12

AP12

AP13

AR12

AW19

AU17

AU19

AV17

AV19

AW17

AL12

AL13

AL15

AL18

AL21

AN13

AN16

AN19

AN22

AR17

U25

U28

V30

V33

W24

W27

Y25

Y28

Y30

AE6

AE5

AR9

VDDIO_MEM_S3_5

VDDIO_MEM_S3_6

VDDIO_MEM_S3_7

VDDIO_MEM_S3_8

VDDIO_MEM_S3_9

VDDIO_MEM_S3_10

VDDIO_MEM_S3_11

VDDIO_MEM_S3_12

VDDIO_MEM_S3_13

VDDIO_MEM_S3_14

VDDIO_MEM_S3_15

VDDIO_MEM_S3_16

VDDIO_MEM_S3_17

VDDIO_MEM_S3_18

VDDIO_MEM_S3_19

VDDIO_MEM_S3_20

VDDIO_MEM_S3_21

VDDIO_MEM_S3_22

VDDIO_MEM_S3_23

VDDIO_MEM_S3_24

VDDIO_MEM_S3_25

VDDIO_MEM_S3_26

VDDIO_MEM_S3_27

VDDIO_MEM_S3_28

VDDIO_MEM_S3_29

VDDIO_MEM_S3_30

VDDIO_MEM_S3_31

VDDIO_MEM_S3_32

VDDIO_MEM_S3_33

VDDIO_MEM_S3_34

VDDIO_MEM_S3_35

0.2A

VDDIO_AUDIO

1.5A

VDDP_GFX_2

VDDP_GFX_1

0.2A

VDD_33_1

VDD_33_2

1.5A

VDD_18_1

VDD_18_2

0.5A

VDD_18_S5_1

VDD_18_S5_2

0.2A

VDD_33_S5_1

VDD_33_S5_2

0.8A

VDDP_S5_1

VDDP_S5_2

0.2A

VDDCR_FCH_S5_1

VDDCR_FCH_S5_2

7A

VDDP_6

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

12A

VDDCR_NB_1

VDDCR_NB_2

VDDCR_NB_3

VDDCR_NB_4

VDDCR_NB_5

VDDCR_NB_6

VDDCR_NB_7

VDDCR_NB_8

VDDCR_NB_9

VDDBT_RTC_G

BOTTOM SIDE DECOUPLING UNDER APU

20MIL

VDDBT_RTC

G1

C146

*0_5%_4

0.22u/10V_4

1.5V For HDA Only

1.8V For HDA or I2S

+APU_VDDIO_AZ

+1.8V_ROM

+1.8VS5 +APU_VDD_18_S5

U1F

POWER

FP4 REV 1.0

*FP4-BR

R178 1K_1%_4

C147

1u/6.3V_4

22~39A

VDDCR_CPU_1

VDDCR_CPU_2

VDDCR_CPU_3

VDDCR_CPU_4

VDDCR_CPU_5

VDDCR_CPU_6

VDDCR_CPU_7

VDDCR_CPU_8

VDDCR_CPU_9

VDDCR_CPU_10

VDDCR_CPU_11

VDDCR_CPU_12

VDDCR_CPU_13

VDDCR_CPU_14

VDDCR_CPU_15

VDDCR_CPU_16

VDDCR_CPU_17

VDDCR_CPU_18

VDDCR_CPU_19

VDDCR_CPU_20

VDDCR_CPU_21

VDDCR_CPU_22

VDDCR_CPU_23

VDDCR_CPU_24

VDDCR_CPU_25

VDDCR_CPU_26

VDDCR_CPU_42

VDDCR_CPU_31

VDDCR_CPU_43

VDDCR_CPU_32

VDDCR_CPU_44

VDDCR_CPU_33

VDDCR_CPU_45

VDDCR_CPU_34

VDDCR_CPU_46

VDDCR_CPU_35

VDDCR_CPU_47

VDDCR_CPU_36

VDDCR_CPU_28

VDDCR_CPU_29

VDDCR_CPU_40

VDDCR_CPU_30

VDDCR_CPU_37

VDDCR_CPU_49

VDDCR_CPU_38

VDDCR_CPU_39

VDDCR_CPU_48

VDDCR_CPU_41

VDDCR_CPU_27

22~30A

VDDCR_GFX_14

VDDCR_GFX_15

VDDCR_GFX_16

VDDCR_GFX_17

VDDCR_GFX_18

VDDCR_GFX_19

VDDCR_GFX_20

VDDCR_GFX_21

VDDCR_GFX_22

VDDCR_GFX_23

VDDCR_GFX_24

VDDCR_GFX_25

VDDCR_GFX_26

VDDCR_GFX_27

VDDCR_GFX_28

VDDCR_GFX_29

VDDCR_GFX_1

VDDCR_GFX_2

VDDCR_GFX_3

VDDCR_GFX_4

VDDCR_GFX_5

VDDCR_GFX_6

VDDCR_GFX_7

VDDCR_GFX_8

VDDCR_GFX_9

VDDCR_GFX_10

VDDCR_GFX_11

VDDCR_GFX_12

VDDCR_GFX_30

VDDCR_GFX_31

VDDCR_GFX_32

VDDCR_GFX_33

VDDCR_GFX_34

VDDCR_GFX_35

VDDCR_GFX_36

VDDCR_GFX_37

VDDCR_GFX_13

+1.5V_RTC

RTC1

*BAT_CONN

DFHD02MS107

R181 *0_4/S

+1.8VS5

A A

R217 *0_4/S

C150

1u/6.3V_4

C151

1u/6.3V_4

C152

1u/6.3V_4

C153

10U/6.3VS_6

C154

0.22u/10V_4

C155

10U/6.3VS_6

C156

0.22u/10V_4

+3V +APU_VDD_33

R182 *0_4/S

5

C157

10U/6.3VS_6

+3VS5 +APU_VDD_33_S5 +0.95VS5 +VDDP_S5

R183 *0_4/S

4

C158

10U/6.3VS_6

C159

0.22u/10V_4

R184 *0_6/S

C160

10U/6.3VS_6

C161

0.22u/10V_4

3

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

Document Number R ev

Document Number R ev

Document Number R ev

BR & SR 6/7 (POWER)

BR & SR 6/7 (POWER)

NB5

NB5

2

NB5

BR & SR 6/7 (POWER)

Date: Sheet o f

Monday, January 16, 2017 7 48

Date: Sheet o f

Monday, January 16, 2017 7 48

Date: Sheet o f

Monday, January 16, 2017 7 48

1

1A

1A

1A

Page 8

5

4

3

2

1

08

12/8: SI Del TP51/ TP53/ TP54

APU_U30

U30

APU_U31

U31

APU_AN30

AN30

RSVD_2

RSVD_3

RSVD_4

U1J

FP4 REV 1.0

*FP4-BR

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

U1G

GND

FP4 REV 1.0

*FP4-BR

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

L28

M4

M30

N10

N13

N16

N19

N22

N27

P1

P2

P4

P5

P12

P15

P18

P21

P30

P33

T4

T10

T13

T16

T19

T22

T30

U5

U12

U15

U18

U21

U24

V1

V2

V4

W10

W13

W16

W19

W22

Y4

Y5

Y12

Y15

Y18

Y21

Y24

AB1

AB2

AB4

AB10

AB13

AB16

AB19

AB22

AD4

AD9

AD12

AD15

AD18

AD21

AD24

AE10

AE13

AE16

AE19

AE22

AF1

AF4

AG9

AG12

AG15

AG18

AG21

AH4

AH10

AH13

AH16

AH19

AH22

AK1

AK4

AK12

AK15

AK18

AL16

AL19

AL22

AM4

AN9

AN10

AN15

AN18

AN21

AN25

AN28

AP1

AP2

AP4

AP7

AP22

AP27

AP30

AP33

AR6

AR25

AR28

AT4

AT19

AT22

AT30

AU5

AU8

AU11

AU14

AU20

AU23

AU27

AV4

AV7

AV9

AV12

AV15

AV25

D D

ORIENT_APU#

TP52

C C

B B

A12

A16

A20

A24

A28

A32

B12

B33

D10

D12

D14

D16

D18

D20

D22

D24

D26

D28

D30

F19

F22

F25

F30

F33

G17

G20

G23

G26

H30

J15

J19

J22

J25

J28

K10

K22

K27

K30

K33

L12

L15

L18

L21

L25

A8

B2

B8

C3

D4

D6

D8

F1

F2

F4

F9

G7

H4

J5

K1

K2

K4

L5

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

U1H

GND

FP4 REV 1.0

*FP4-BR

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_215

VSS_214

AV30

AV33

AW22

AY4

AY6

AY8

AY10

AY12

AY14

AY16

AY20

AY22

AY24

AY26

AY28

AY30

BB1

BB33

BC4

BC8

BC12

BC16

BC20

BC24

BC28

BC32

L24

AL10

AK21

A A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

BR & SR 7/7 (GND)

BR & SR 7/7 (GND)

NB5

NB5

5

4

3

2

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

BR & SR 7/7 (GND)

Monday, January 16, 2017 8 48

Monday, January 16, 2017 8 48

Monday, January 16, 2017 8 48

1

1A

1A

1A

Page 9

5

4

3

2

1

09

D D

<Reserved>

C C

B B

A A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

PROJECT:NFLP-G94A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size

Size

Size

Document Number R ev

Document Number R ev

Document Number R ev

C

C

C

Reserved

Reserved

NB5

NB5

5

4

3

2

NB5

Reserved

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1

1A

1A

1A

9 48Monday, January 16, 2017

9 48Monday, January 16, 2017

9 48Monday, January 16, 2017

Page 10

5

4

3

2

1

+3V4,5,6,7,11,20,21,22,24,26,27,28,29,30,31,38,40,43

+0.6V_DDR_VTT11,35

DDR_VTTREF10,11,35

+VREF_CA0

D D

M_A_A[13:0]3

M_A_WE#3

M_A_CAS#3

R185

1K_1%_4

M_A_RAS#3

M_A_ACT#3

+1.2VSUS

M_A_BS#03

M_A_BS#13

M_A_BG#03

M_A_BG#13

M_A_CS#03

M_A_CS#13

M_A_CKE03

M_A_CKE13

M_A_CLKP03

M_A_CLKN03

M_A_CLKP13

M_A_CLKN13

M_A_ODT03

M_A_ODT13

SMB_RUN_CLK5,11

SMB_RUN_DAT5,11

M_A_DM[7..0]3

+1.2VSUS

M_A_EVENT#3

M_A_RST#3

C C

B B

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

TP55

TP56

R186 *0_4/S C169 10U/6.3VS_6

R187 1K_1%_4

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

144

133

132

131

128

126

127

122

125

121

146

120

119

158

151

156

152

162

165

114

143

116

134

108

150

145

115

113

149

157

109

110

137

139

138

140

155

161

253

254

256

260

166

92

91

101

105

88

87

100

104

12

33

54

75

178

199

220

241

96

JDIM0A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14/WE#

A15/CAS#

A16/RAS#

S2#/C0

S3#/C1

ACT#

PARITY

ALERT#

EVENT#

RESET#

BA0

BA1

BG0

BG1

S0#

S1#

CKE0

CKE1

CK0

CK0#

CK1

CK1#

ODT0

ODT1

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DDR4 RVS H=4

M_A_DQ0

8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

(260P)

DDR4 SODIMM 260 PIN

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DQS#8

M_A_DQ4

7

M_A_DQ7

20

M_A_DQ3

21

M_A_DQ1

4

M_A_DQ5

3

M_A_DQ2

16

M_A_DQ6

17

M_A_DQ13

28

M_A_DQ9

29

M_A_DQ14

41

M_A_DQ10

42

M_A_DQ12

24

M_A_DQ8

25

M_A_DQ11

38

M_A_DQ15

37

M_A_DQ21

50

M_A_DQ17

49

M_A_DQ19

62

M_A_DQ18

63

M_A_DQ20

46

M_A_DQ16

45

M_A_DQ23

58

M_A_DQ22

59

M_A_DQ25

70

M_A_DQ24

71

M_A_DQ30

83

M_A_DQ26

84

M_A_DQ29

66

M_A_DQ28

67

M_A_DQ31

79

M_A_DQ27

80

M_A_DQ36

174

M_A_DQ37

173

M_A_DQ34

187

M_A_DQ38

186

M_A_DQ32

170

M_A_DQ33

169

M_A_DQ35

183

M_A_DQ39

182

M_A_DQ40

195

M_A_DQ41

194

M_A_DQ47

207

M_A_DQ46

208

M_A_DQ45

191

M_A_DQ44

190

M_A_DQ42

203

M_A_DQ43

204

M_A_DQ49

216

M_A_DQ48

215

M_A_DQ54

228

M_A_DQ50

229

M_A_DQ53

211

M_A_DQ52

212

M_A_DQ55

224

M_A_DQ51

225

M_A_DQ61

237

M_A_DQ60

236

M_A_DQ59

249

M_A_DQ63

250

M_A_DQ56

232

M_A_DQ57

233

M_A_DQ62

245

M_A_DQ58

246

M_A_DQSP0

13

M_A_DQSP1

34

M_A_DQSP2

55

M_A_DQSP3

76

M_A_DQSP4

179

M_A_DQSP5

200

M_A_DQSP6

221

M_A_DQSP7

242

97

M_A_DQSN0

11

M_A_DQSN1

32

M_A_DQSN2

53

M_A_DQSN3

74

M_A_DQSN4

177

M_A_DQSN5

198

M_A_DQSN6

219

M_A_DQSN7

240

95

M_A_DQ[63:0] 3

M_A_DQSP[7:0] 3

M_A_DQSN[7:0] 3

2.48A

+1.2VSUS

111

112

117

118

123

124

129

130

135

136

141

142

147

148

153

154

159

160

163

1

5

9

15

19

23

27

31

35

39

43

47

51

57

61

65

69

73

77

81

85

89

93

99

103

107

167

171

175

181

185

189

193

197

201

205

209

213

217

223

227

231

235

239

243

247

251

JDIM0B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

DDR4 RVS H=4

+1.2VSUS

255

VDDSPD

257

VPP1

259

VPP2

258

VTT

164

VREF_CA

2

VSS48

6

VSS49

10

VSS50

14

VSS51

18

VSS52

22

VSS53

26

VSS54

30

VSS55

36

VSS56

40

VSS57

44

VSS58

48

VSS59

52

VSS60

56

VSS61

60

VSS62

64

VSS63

68

VSS64

72

VSS65

78

VSS66

82

VSS67

86

VSS68

90

(260P)

DDR4 SODIMM 260 PIN

VSS69

94

VSS70

98

VSS71

102

VSS72

106

VSS73

168

VSS74

172

VSS75

176

VSS76

180

VSS77

184

VSS78

188

VSS79

192

VSS80

196

VSS81

202

VSS82

206

VSS83

210

VSS84

214

VSS85

218

VSS86

222

VSS87

226

VSS88

230

VSS89

234

VSS90

238

VSS91

244

VSS92

248

VSS93

252

VSS94

261

GND1

262

GND2

263

GND3

264

GND4

+3V

+2.5V_SUS

+0.6V_DDR_VTT

+VREF_CA0

1uF/10uF 4pcs on each side of SODIMM

Place these Caps near SODIMM

C162 180p/50V_4

C163 1u/6.3V_4

C164 1u/6.3V_4

C172 1u/6.3V_4

C165 1u/6.3V_4

C166 1u/6.3V_4

C173 1u/6.3V_4

C174 1u/6.3V_4

C176 1u/6.3V_4 C177 180p/50V_4

C179 10U/6.3VS_6

C180 10U/6.3VS_6

C181 10U/6.3VS_6

C183 10U/6.3VS_6

C185 10U/6.3VS_6

C187 10U/6.3VS_6

C189 10U/6.3VS_6