Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

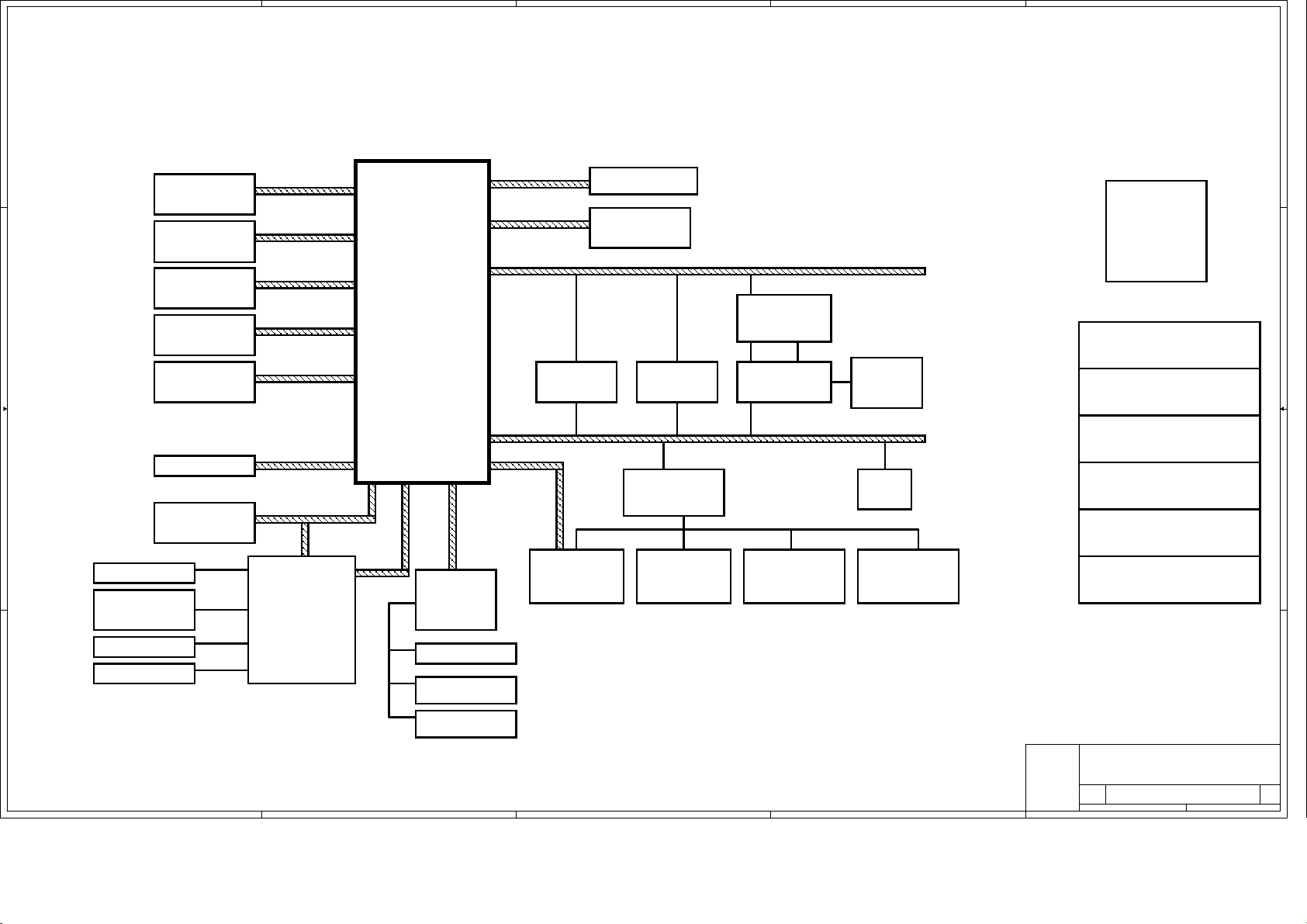

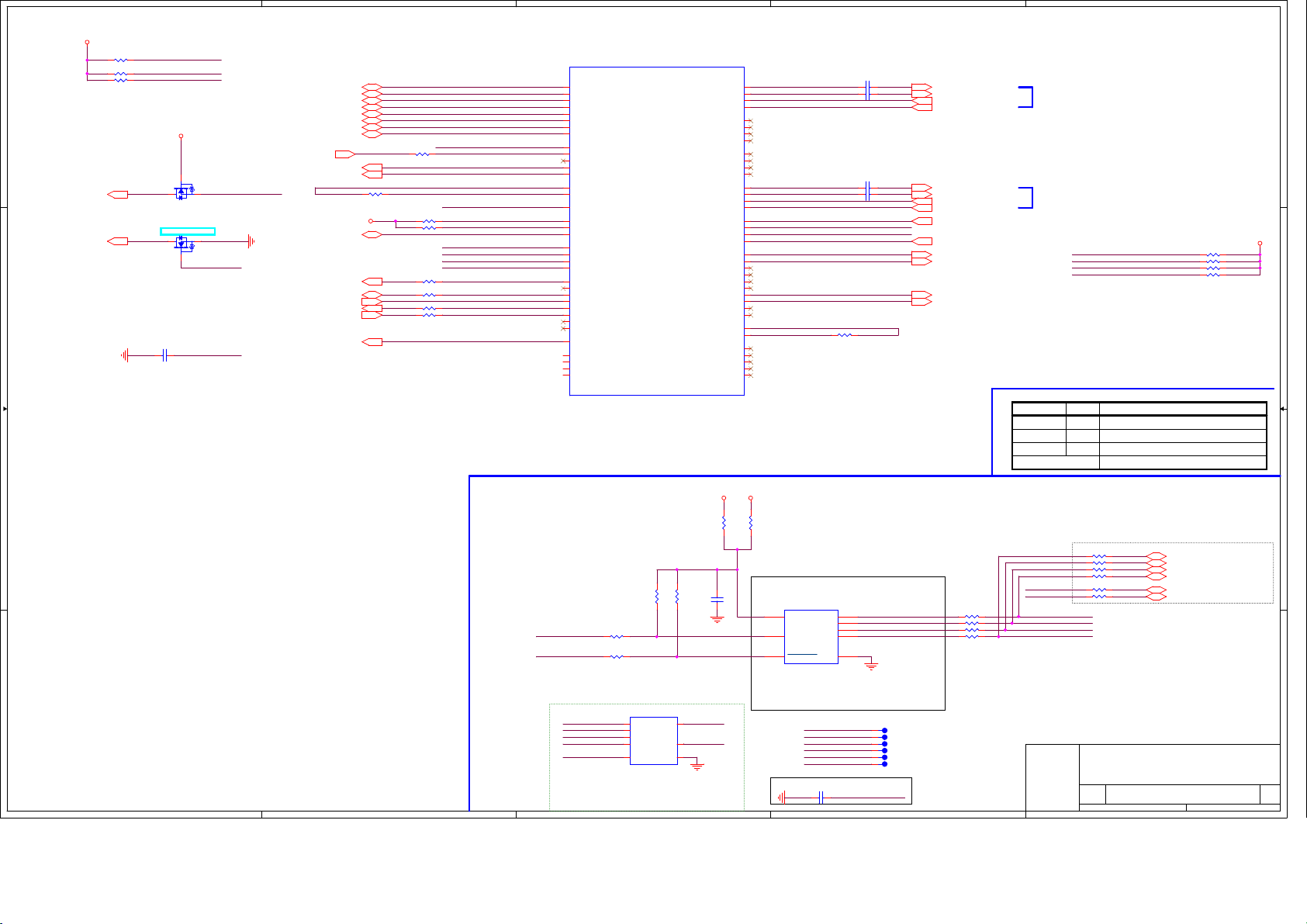

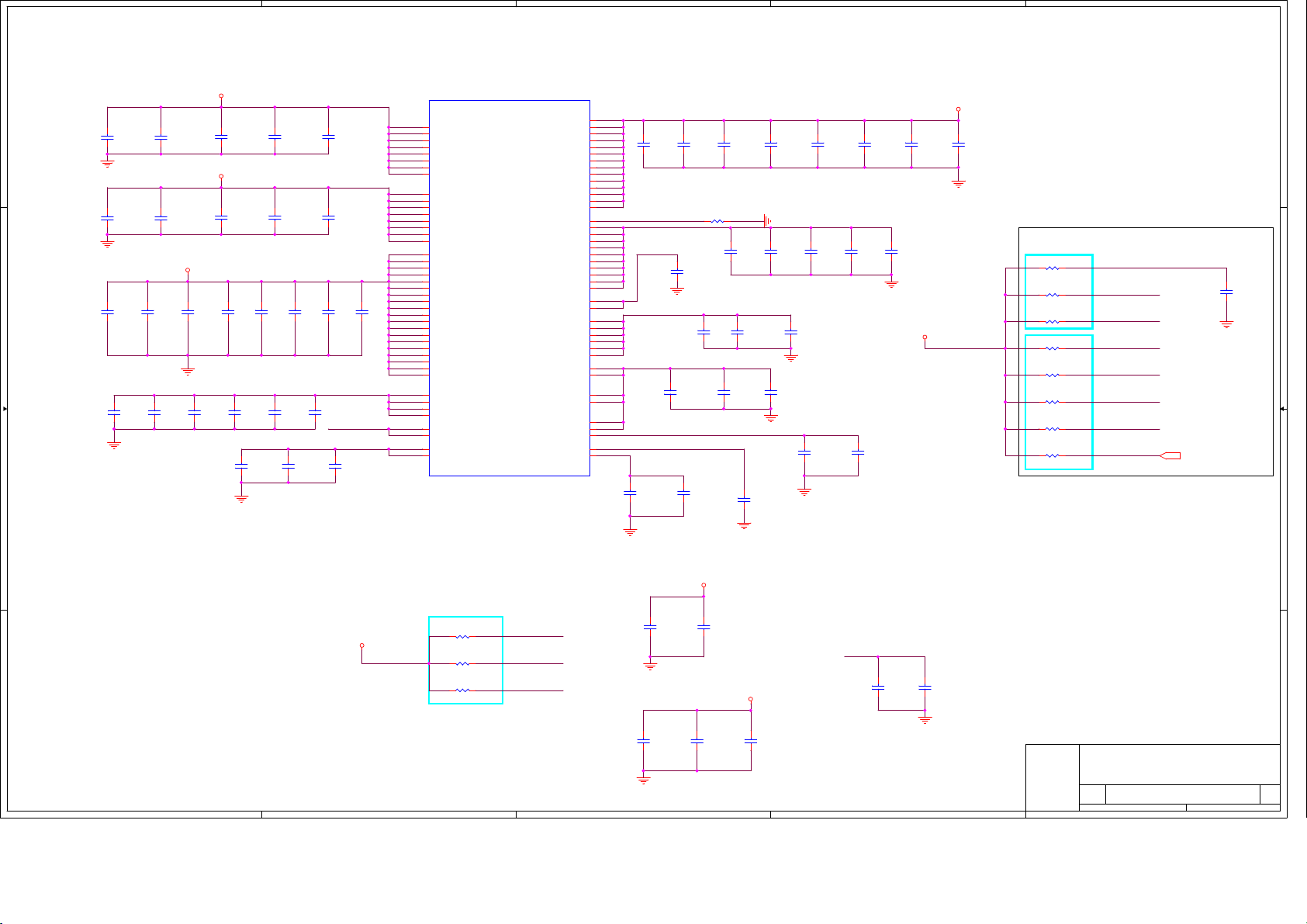

NFL-P G72D BSW UMA (14"/15.6")

01

D D

C C

B B

SPI ROM

G-Sensor

HP2DCTR

Keyboard

Touch Pad

A A

5

Intel Braswell-M Platform Block Diagram

DDR3L SODIMM1

Maxima 8GBs

PAGE 14

eMMC4.51

PAGE 20

SATA HDD

PAGE 20

SATA SSD

PAGE 21

LAN

RTL8111HSH

PAGE 18

SPI ROM

TPM SLB9665TT2.0

PAGE 26

PAGE 23

PAGE 24

PAGE 24

PAGE 5

PAGE 23

SM BUS

DDR3L-1600

Channel A

EMMC

SATA0 6GB/s

SATA0 6GB/s

PCIE PORT2

FSPI Interface

LPC Interface

Embedded Controller

KBC IT8887

PAGE 26

Intel Brasswell

Power : 6 (Watt)

Package : BGA1170

Size : 25 X 27 (mm)

HP

FAST SPI

Audio Codec

ALC3258-CG

Speaker

Combo Jack

Digital MIC

4

DDI1 Lane X2 eDP

DDI0

USB3.0

USB2.0

PCI-E PORT3

HDA

PAGE 17

PAGE 17

PAGE 22, DB

PAGE 15

HDMI CONN V1.4

PORT0 PORT1

USB3.0 CONN

PAGE 22, DB

PORT0 PORT1

WLAN/BT COMBO

(MINI PCIE)

USB HUB PORT2

PAGE 21

PAGE 15

PAGE 16

PORT2

USB SWITCH

CBTL02042A

PORT1

USB3.0 CONN

PAGE 22, DB

USB2.0 HUB

PORT3 GL850G-50

PAGE 23

Card Reader

RTS5141

USB HUB PORT1

PAGE 22, DB PAGE 15

3

USB TYPE-C CONN

PORT2

Touch Screen

USB HUB PORT3

PAGE 19

PORT2

PAGE 19

PD controller

TI

TPS25810

PORT3PORT4

Webcam

PAGE 15

IR CAM

USB HUB PORT4

2

PAGE 23

PCB 6L STACK UP

LAYER 1 : TOP

LAYER 2 : SVCC

LAYER 3 : IN1(LOW)

LAYER 4 : IN2(HIGH)

LAYER 5 : SGND

LAYER 6 : BOT

Charger

PG

.27

+3

VS5/+5VS5

PG

.28

DDR3L

PG.29

MO

IC

.30

PG

VG

G & VCC CORE

PG

.31, 32

SYS Power

PG

.33

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Si

ze Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswell Block Diagram

Custom Braswell Block Diagram

Custom Braswell Block Diagram

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

1

of

13

of

13

of

13

1A

1A

1A

5

5

5

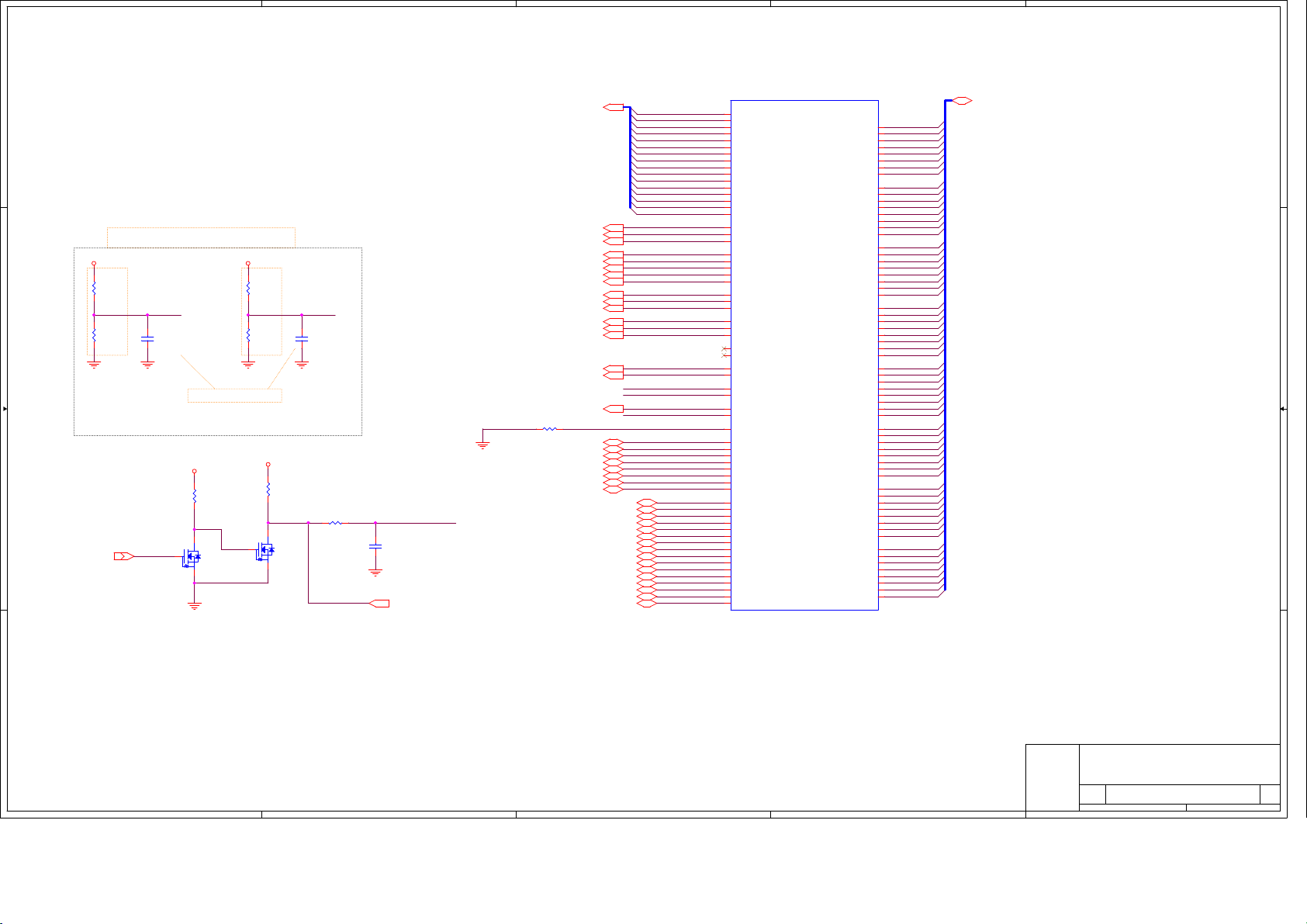

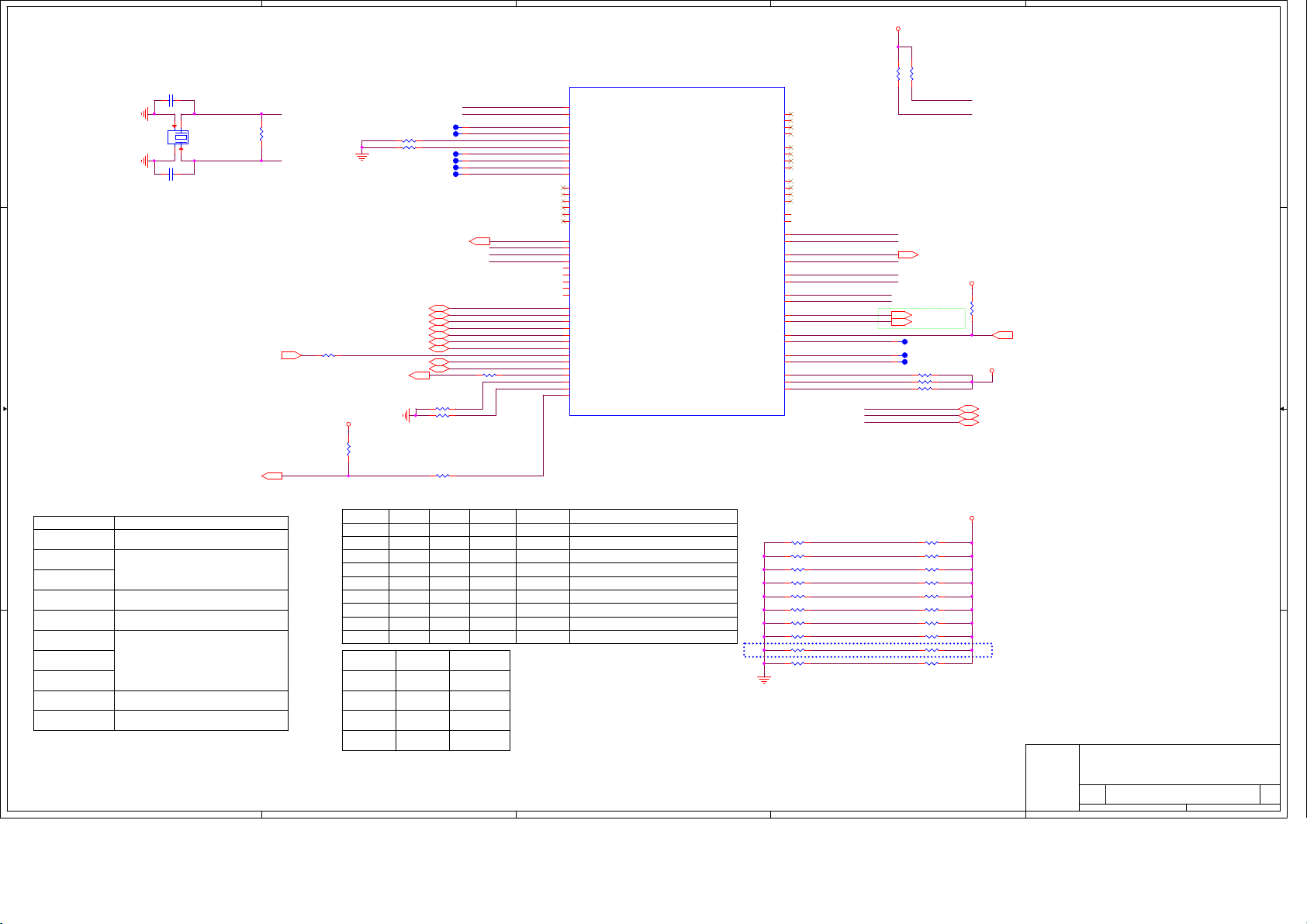

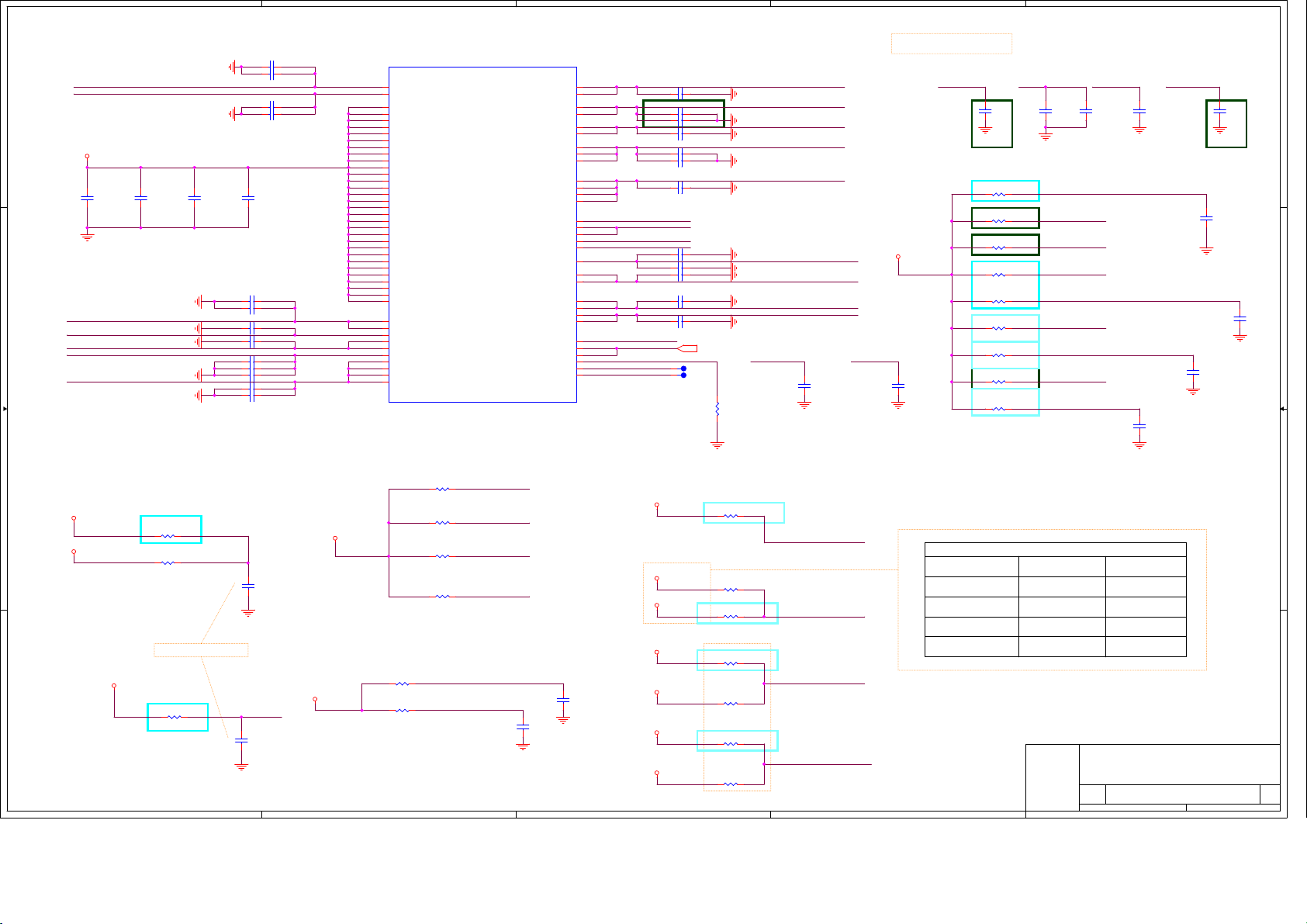

Page 2

5

4

3

2

1

02

BSW

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

A_DRAMRST#[14]

96 182/F_4

R1

M_

M_

M_

M_

M_

M_

M_

M_

A_A[15:0][14]

A_BS#2[14 ]

A_BS#1[14 ]

A_BS#0[14 ]

A_CAS#[14]

A_RAS#[14]

A_WE#[14]

A_CS#1[14]

A_CS#0[14]

M_

A_CLKP1[14]

M_

A_CLKN1[14 ]

A_CKE1[14]

A_CLKP0[14]

A_CLKN0[14 ]

A_CKE0[14]

M_

A_ODT0[14]

M_

A_ODT1[14]

A_DM7[14]

A_DM6[14]

A_DM5[14]

A_DM4[14]

A_DM3[14]

A_DM2[14]

A_DM1[14]

A_DM0[14]

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

A_DQSP7[14]

A_DQSN7[14]

A_DQSP6[14]

A_DQSN6[14]

A_DQSP5[14]

A_DQSN5[14]

A_DQSP4[14]

A_DQSN4[14]

A_DQSP3[14]

A_DQSN3[14]

A_DQSP2[14]

A_DQSN2[14]

A_DQSP1[14]

A_DQSN1[14]

A_DQSP0[14]

A_DQSN0[14]

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

M_A_BS#2

M_A_BS#1

M_A_BS#0

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_CS#1

M_A_CS#0

M_A_CLKP1

M_A_CLKN1

M_A_CKE1

M_A_CLKP0

M_A_CLKN0

M_A_CKE0

M_A_VREF_CA

M_A_VREF_DQ

M_A_DRAMRST#

SOC_DRAM_PWRO K

DRAM_RCOMP1

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQSP7

M_A_DQSN7

M_A_DQSP6

M_A_DQSN6

M_A_DQSP5

M_A_DQSN5

M_A_DQSP4

M_A_DQSN4

M_A_DQSP3

M_A_DQSN3

M_A_DQSP2

M_A_DQSN2

M_A_DQSP1

M_A_DQSN1

M_A_DQSP0

M_A_DQSN0

D D

ROUTE ALL VREF POWER SIGNALS AS THICK TRACES

PLACE TWO 4.7K RESISTORS CLOSE TO CPU PINS ON M_VREF

ROUTE THE VREF POWER SIGNALS WITH THICK TRACES

+1

.35VSUS

09

R2

C C

B B

*4.7K/F_4

M_A_VREF_CA

D

GN

SLP_S4#

72

C1

*0.1U/16V_4

5

+3

GN

12

R2

*4.7K/F_4

D

GN

02/09 No_Stuff Vref circuitry from SOC pages.

VOLTAGE DIVIDER FOR VREF IS FOR DDR3L DIMMS ONLY. SOC DOES NOT DRIVE VREF.

Follow TO BRASWELL SOC EDS AND PDG FOR MORE DETAILS ABOUT DDR VREF

SL

P_S4#[8,25]

+1

.35VSUS

25

R2

*4.7K/F_4

M_A_VREF_DQ

24

R2

*4.7K/F_4

D

GN

PLACE 0.1UF CAP CLOSE TO CPU

+1

VS5

43

R5

4.7K/F_4

DRM_PWOK_C1

34

9A

Q3

PJT138K

D

.35VSUS

DRM_PG SOC_DRAM_PWR OK

61

2

51

R5

10K/F_4

9B

Q3

PJT138K

GN

C1

*0.1U/16V_4

D

R5

96

53 *0_4/S

GN

C5

*0.1U/16V_4

D

DRM

12

_PG [29]

D

GN

BD49

BD47

BF44

BF48

BB49

BJ45

BE52

BD44

BE46

BB46

BH48

BD42

BH47

BJ48

BC42

BB47

BF52

AY40

BH46

BG45

BA40

BH44

AU38

AY38

BD38

BF38

AY42

BD40

BF40

BB44

AT30

AU30

AV36

BA38

AT28

AU28

BA42

AV28

BA28

BH30

BD32

AY36

BG41

BA53

AP44

AT48

AP52

BH32

BG31

BC30

BC32

AT32

AT34

BH40

BG39

AY52

BA51

AT42

AT41

AV47

AV48

AM52

AM51

U26A

DDR3

_M0_MA_15

DDR3

_M0_MA_14

DDR3

_M0_MA_13

DDR3

_M0_MA_12

DDR3

_M0_MA_11

DDR3

_M0_MA_10

DDR3

_M0_MA_9

DDR3

_M0_MA_8

DDR3

_M0_MA_7

DDR3

_M0_MA_6

DDR3

_M0_MA_5

DDR3

_M0_MA_4

DDR3

_M0_MA_3

DDR3

_M0_MA_2

DDR3

_M0_MA_1

DDR3

_M0_MA_0

DDR3

_M0_BS_2

DDR3

_M0_BS_1

DDR3

_M0_BS_0

DDR3

_M0_CASB

DDR3

_M0_RASB

DDR3

_M0_WEB

DDR3

_M0_CSB_1

DDR3

_M0_CSB_0

DDR3

_M0_CK_1

DDR3

_M0_CKB_1

DDR3

_M0_CKE_1

DDR3

_M0_CK_0

DDR3

_M0_CKB_0

DDR3

_M0_CKE_0

RS

VD1

RS

VD2

DDR3

_M0_ODT_0

DDR3

_M0_ODT_1

DDR3

_M0_OCAVREF

DDR3

_M0_ODQVREF

DDR3

_M0_DRAMRSTB

DDR3

_DRAM_PWROK

DDR3

_M0_RCOMPPD

DDR3

_M0_DM_7

DDR3

_M0_DM_6

DDR3

_M0_DM_5

DDR3

_M0_DM_4

DDR3

_M0_DM_3

DDR3

_M0_DM_2

DDR3

_M0_DM_1

DDR3

_M0_DM_0

DDR3

_M0_DQS_7

DDR3

_M0_DQSB_7

DDR3

_M0_DQS_6

DDR3

_M0_DQSB_6

DDR3

_M0_DQS_5

DDR3

_M0_DQSB_5

DDR3

_M0_DQS_4

DDR3

_M0_DQSB_4

DDR3

_M0_DQS_3

DDR3

_M0_DQSB_3

DDR3

_M0_DQS_2

DDR3

_M0_DQSB_2

DDR3

_M0_DQS_1

DDR3

_M0_DQSB_1

_M0_DQS_0

DDR3

_M0_DQSB_0

DDR3

*BSW_MCP_ EDS

_MCP_EDS

DDR0

1

OF 13

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

_M0_DQ_63

_M0_DQ_62

_M0_DQ_61

_M0_DQ_60

_M0_DQ_59

_M0_DQ_58

_M0_DQ_57

_M0_DQ_56

_M0_DQ_55

_M0_DQ_54

_M0_DQ_53

_M0_DQ_52

_M0_DQ_51

_M0_DQ_50

_M0_DQ_49

_M0_DQ_48

_M0_DQ_47

_M0_DQ_46

_M0_DQ_45

_M0_DQ_44

_M0_DQ_43

_M0_DQ_42

_M0_DQ_41

_M0_DQ_40

_M0_DQ_39

_M0_DQ_38

_M0_DQ_37

_M0_DQ_36

_M0_DQ_35

_M0_DQ_34

_M0_DQ_33

_M0_DQ_32

_M0_DQ_31

_M0_DQ_30

_M0_DQ_29

_M0_DQ_28

_M0_DQ_27

_M0_DQ_26

_M0_DQ_25

_M0_DQ_24

_M0_DQ_23

_M0_DQ_22

_M0_DQ_21

_M0_DQ_20

_M0_DQ_19

_M0_DQ_18

_M0_DQ_17

_M0_DQ_16

_M0_DQ_15

_M0_DQ_14

_M0_DQ_13

_M0_DQ_12

_M0_DQ_11

_M0_DQ_10

_M0_DQ_9

_M0_DQ_8

_M0_DQ_7

_M0_DQ_6

_M0_DQ_5

_M0_DQ_4

_M0_DQ_3

_M0_DQ_2

_M0_DQ_1

_M0_DQ_0

BG33

BH28

BJ29

BG28

BG32

BH34

BG29

BJ33

BD28

BF30

BA34

BD34

BD30

BA32

BC34

BF34

AV32

AV34

BD36

BF36

AU32

AU34

BA36

BC36

BH38

BH36

BJ41

BH42

BJ37

BG37

BG43

BG42

BB51

AW53

BC52

AW51

AV51

BC53

AV52

BD52

AV42

AP41

AV41

AT44

AP40

AT38

AP42

AT40

AV45

AY50

AT50

AP47

AV50

AY48

AT47

AP48

AP51

AR53

AK52

AL53

AR51

AT52

AL51

AK51

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_

A_DQ[63:0] [14]

A A

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Si

ze Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswell 1/11 (DDRA)

Custom Braswell 1/11 (DDRA)

Custom Braswell 1/11 (DDRA)

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

5

4

3

2

Tuesday, January 24, 2017

1

23

23

23

of

of

of

1A

1A

1A

5

5

5

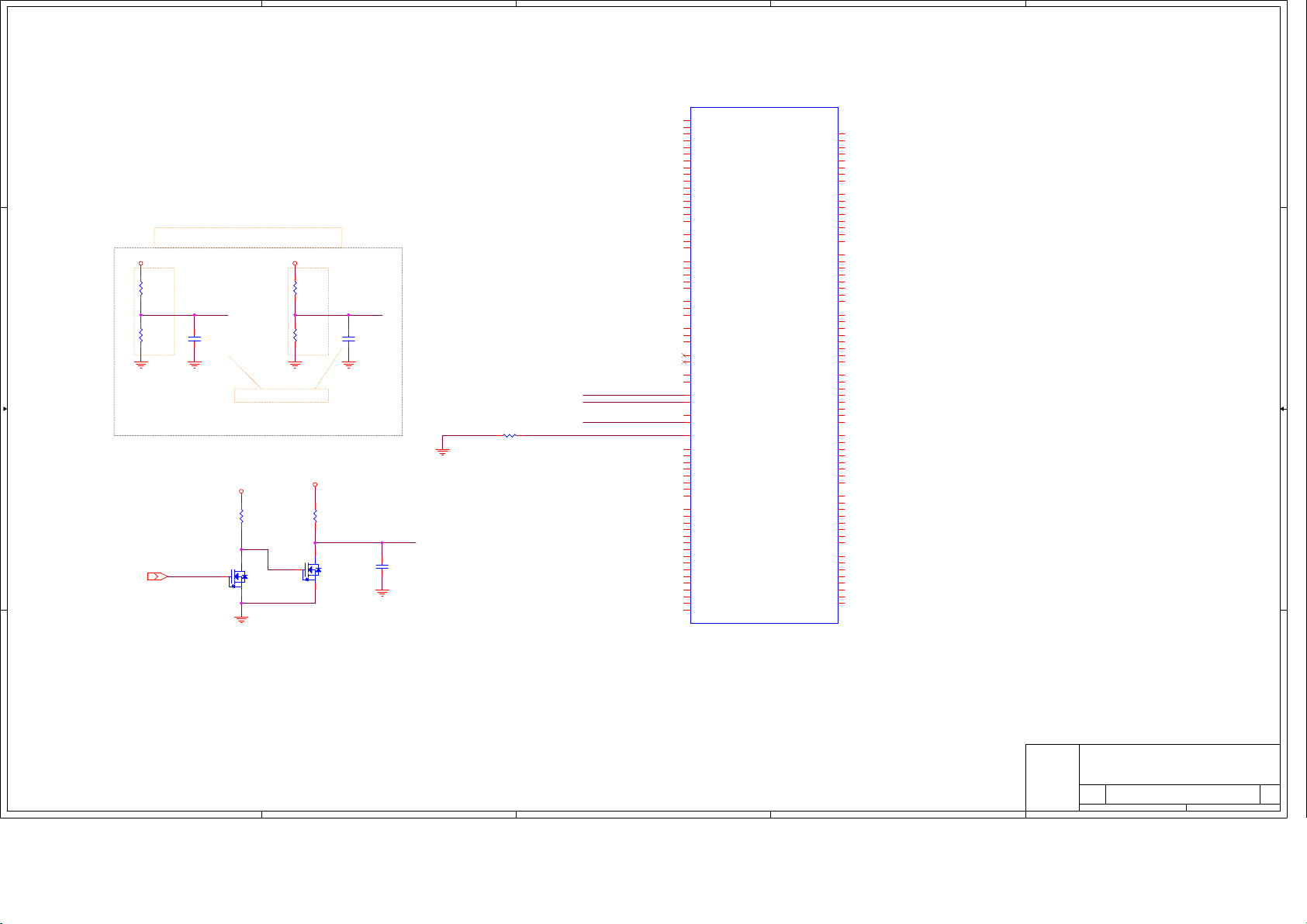

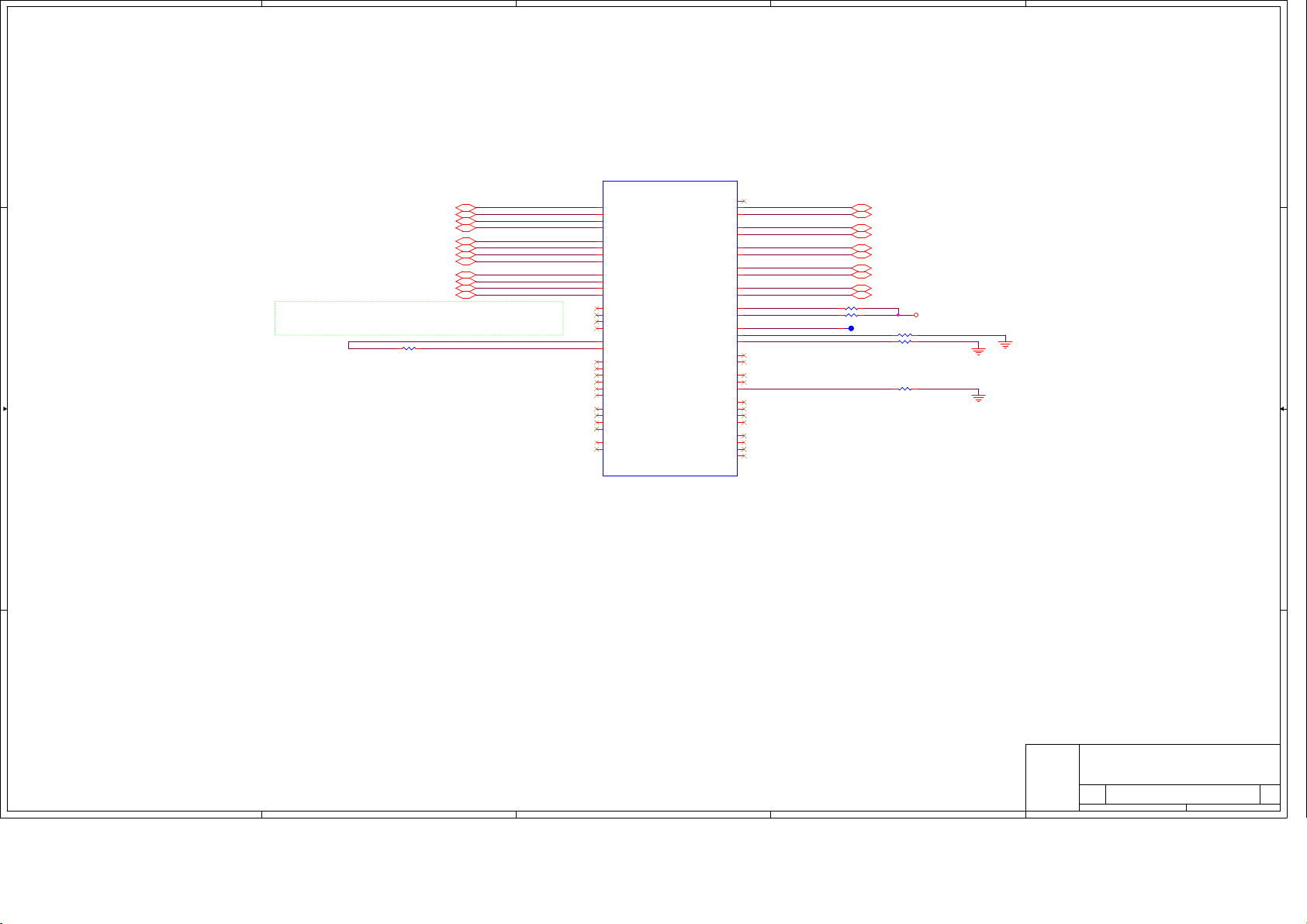

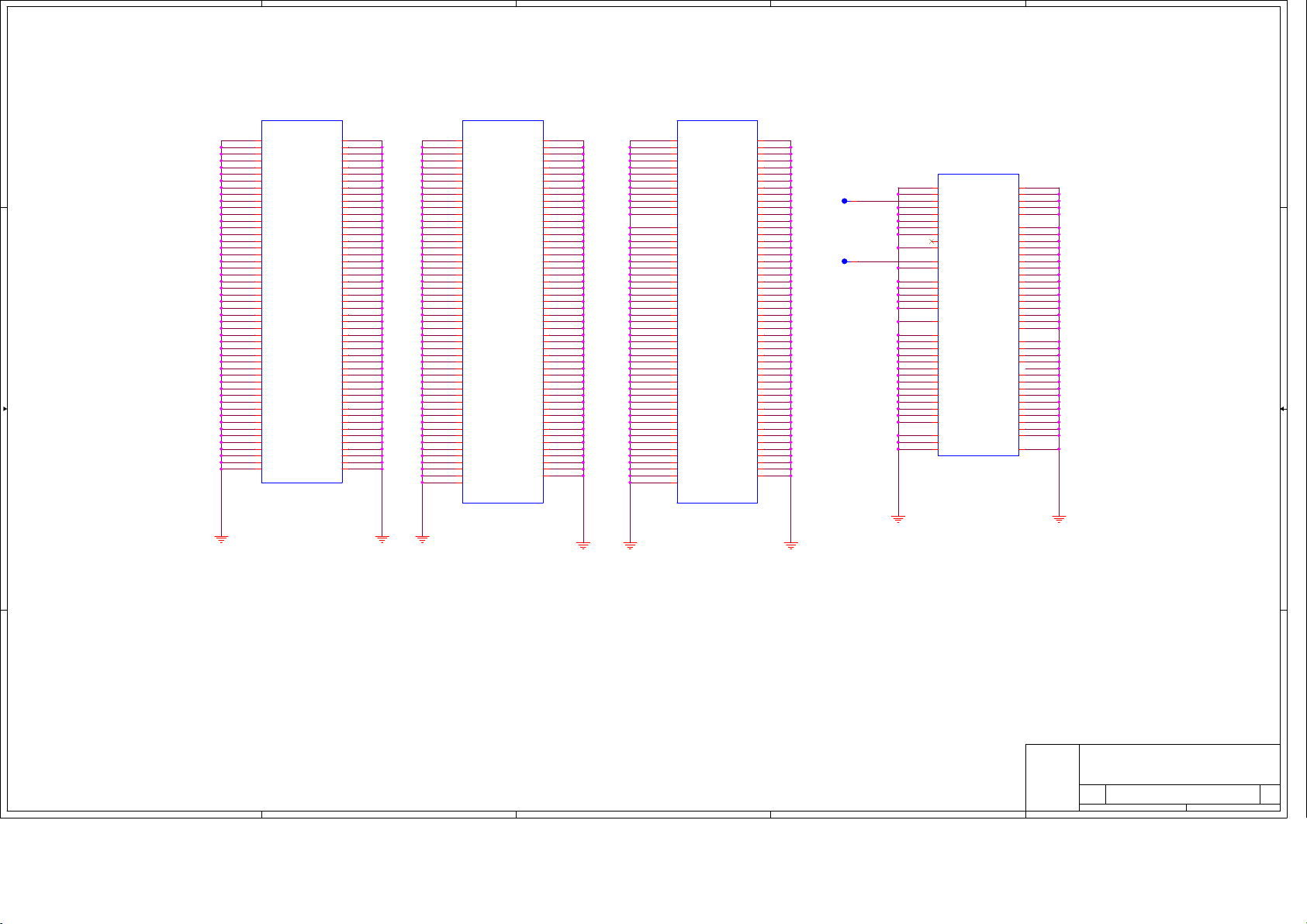

Page 3

5

4

3

2

1

03

_MCP_EDS

_M1_MA_15

_M1_MA_14

_M1_MA_13

_M1_MA_12

_M1_MA_11

_M1_MA_10

_M1_MA_9

_M1_MA_8

_M1_MA_7

_M1_MA_6

_M1_MA_5

_M1_MA_4

_M1_MA_3

_M1_MA_2

_M1_MA_1

_M1_MA_0

_M1_BS_2

_M1_BS_1

_M1_BS_0

_M1_CASB

_M1_RASB

_M1_WEB

_M1_CSB_1

_M1_CSB_0

_M1_CK_1

_M1_CKB_1

_M1_CKE_1

_M1_CK_0

_M1_CKB_0

_M1_CKE_0

VD1

VD2

_M1_ODT_0

_M1_ODT_1

_M1_OCAVREF

_M1_ODQVREF

_M1_DRAMRSTB

_VCCA_PWROK

_M1_RCOMPPD

_M1_DM_7

_M1_DM_6

_M1_DM_5

_M1_DM_4

_M1_DM_3

_M1_DM_2

_M1_DM_1

_M1_DM_0

_M1_DQS_7

_M1_DQSB_7

_M1_DQS_6

_M1_DQSB_6

_M1_DQS_5

_M1_DQSB_5

_M1_DQS_4

_M1_DQSB_4

_M1_DQS_3

_M1_DQSB_3

_M1_DQS_2

_M1_DQSB_2

_M1_DQS_1

_M1_DQSB_1

_M1_DQS_0

_M1_DQSB_0

BSW

DDR1

A

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

OF 13

2

_M1_DQ_63

_M1_DQ_62

_M1_DQ_61

_M1_DQ_60

_M1_DQ_59

_M1_DQ_58

_M1_DQ_57

_M1_DQ_56

_M1_DQ_55

_M1_DQ_54

_M1_DQ_53

_M1_DQ_52

_M1_DQ_51

_M1_DQ_50

_M1_DQ_49

_M1_DQ_48

_M1_DQ_47

_M1_DQ_46

_M1_DQ_45

_M1_DQ_44

_M1_DQ_43

_M1_DQ_42

_M1_DQ_41

_M1_DQ_40

_M1_DQ_39

_M1_DQ_38

_M1_DQ_37

_M1_DQ_36

_M1_DQ_35

_M1_DQ_34

_M1_DQ_33

_M1_DQ_32

_M1_DQ_31

_M1_DQ_30

_M1_DQ_29

_M1_DQ_28

_M1_DQ_27

_M1_DQ_26

_M1_DQ_25

_M1_DQ_24

_M1_DQ_23

_M1_DQ_22

_M1_DQ_21

_M1_DQ_20

_M1_DQ_19

_M1_DQ_18

_M1_DQ_17

_M1_DQ_16

_M1_DQ_15

_M1_DQ_14

_M1_DQ_13

_M1_DQ_12

_M1_DQ_11

_M1_DQ_10

_M1_DQ_9

_M1_DQ_8

_M1_DQ_7

_M1_DQ_6

_M1_DQ_5

_M1_DQ_4

_M1_DQ_3

_M1_DQ_2

_M1_DQ_1

_M1_DQ_0

BG21

BH26

BJ25

BG26

BG22

BH20

BG25

BJ21

BD26

BF24

BA20

BD20

BD24

BA22

BC20

BF20

AV22

AV20

BD18

BF18

AU22

AU20

BA18

BC18

BH16

BH18

BJ13

BH12

BJ17

BG17

BG11

BG12

BB3

AW1

BC2

AW3

AV3

BC1

AV2

BD2

AV12

AP13

AV13

AT10

AP14

AT16

AP12

AT14

AV9

AY4

AT4

AP7

AV4

AY6

AT7

AP6

AP3

AR1

AK2

AL1

AR3

AT2

AL3

AK3

BF10

BD10

BD12

BC12

AY14

BG9

BA14

BH10

AU16

AY16

BD16

BF16

AY12

BD14

BF14

BB10

AT24

AU24

AV18

BA16

AT26

AU26

BA12

AV26

BA26

BH24

BD22

AY18

BG13

AP10

BH22

BG23

BC24

BC22

AT22

AT20

BH14

BG15

AT12

AT13

AM2

AM3

BD5

BD7

BF6

BB5

BJ9

BE2

BE8

BB8

BH6

BH7

BJ6

BB7

BF2

BH8

BA1

AT6

AP2

AY2

BA3

AV7

AV6

U26B

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

RS

RS

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

DDR3

*BSW_MCP_ EDS

D D

ROUTE ALL VREF POWER SIGNALS AS THICK TRACES

PLACE TWO 4.7K RESISTORS CLOSE TO CPU PINS ON M_VREF

ROUTE THE VREF POWER SIGNALS WITH THICK TRACES

+1

.35VSUS

22

R2

C C

B B

EC

*4.7K/F_4

M_B_VREF_CA M_B_VREF_DQ

17

R2

*4.7K/F_4

D

GN

02/09 No_Stuff Vref circuitry from SOC pages.

VOLTAGE DIVIDER FOR VREF IS FOR DDR3L DIMMS ONLY. SOC DOES NOT DRIVE VREF.

Follow TO BRASWELL SOC EDS AND PDG FOR MORE DETAILS ABOUT DDR VREF

_PWROK[25,26]

D

GN

EC_PWROK

86

C1

*0.1U/16V_4

5

+3

+1

.35VSUS

26

R2

*4.7K/F_4

19

R2

*4.7K/F_4

D

GN

PLACE 0.1UF CAP CLOSE TO CPU

+1

VS5

R3

4.7K/F_4

DRM_PWOK_C2

34

Q2

PJT138K

GN

D

35

2A

.35VSUS

61

2

84

C1

*0.1U/16V_4

D

GN

47

R3

10K/F_4

SOC_VCCA_PWROK

2B

Q2

PJT138K

GN

C3

0.1U/16V_4

D

M_B_VREF_CA

M_B_VREF_DQ

SOC_VCCA_PWROK

89 182/F_4

R1

D

GN

71

DRAM_RCOMP2

A A

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Tuesday, January 24, 2017

Tuesday, January 24, 2017

5

4

3

2

Tuesday, January 24, 2017

Braswell 2/11 (DDRB)

Braswell 2/11 (DDRB)

Braswell 2/11 (DDRB)

1

33

33

33

1A

1A

1A

of

of

of

5

5

5

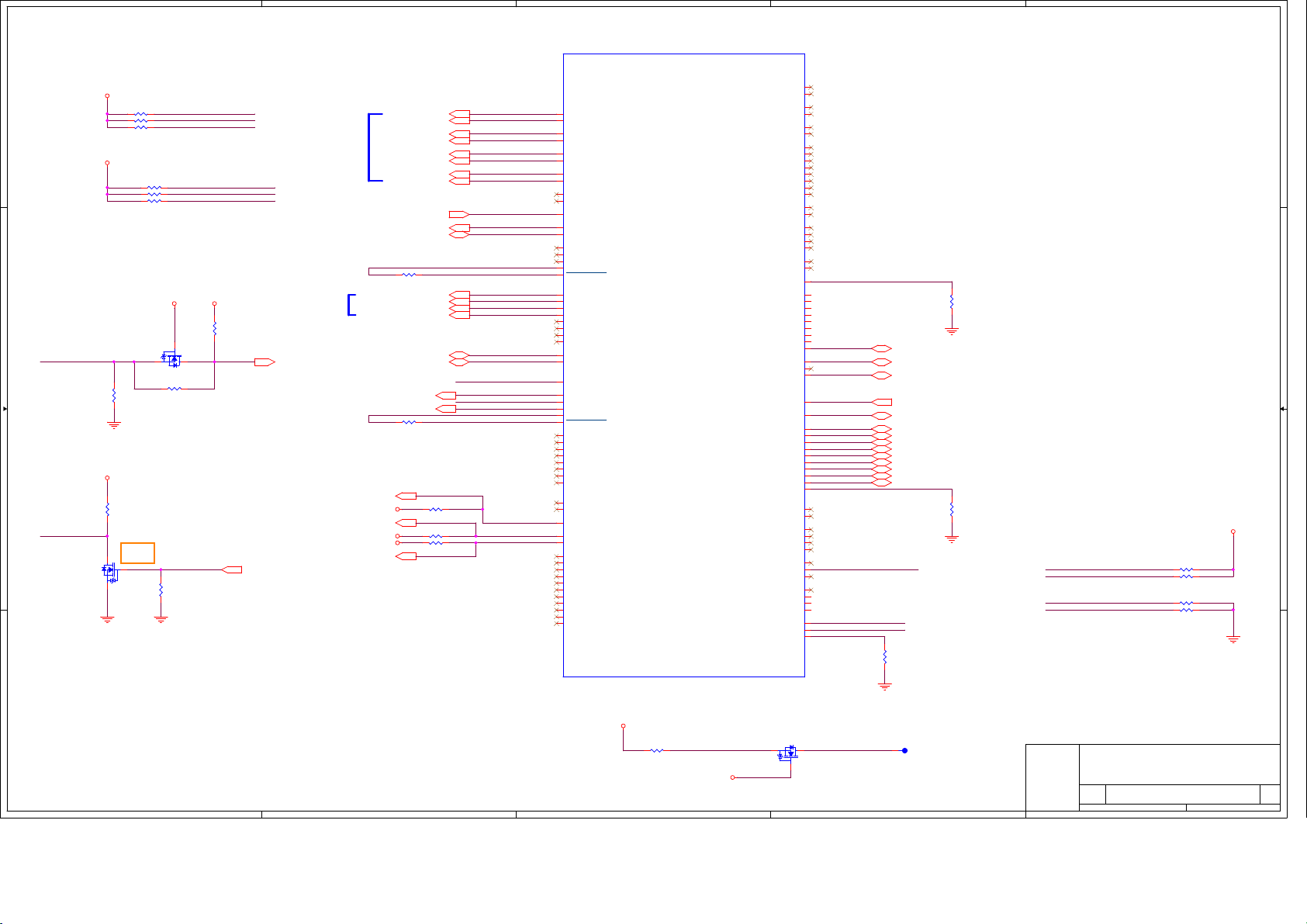

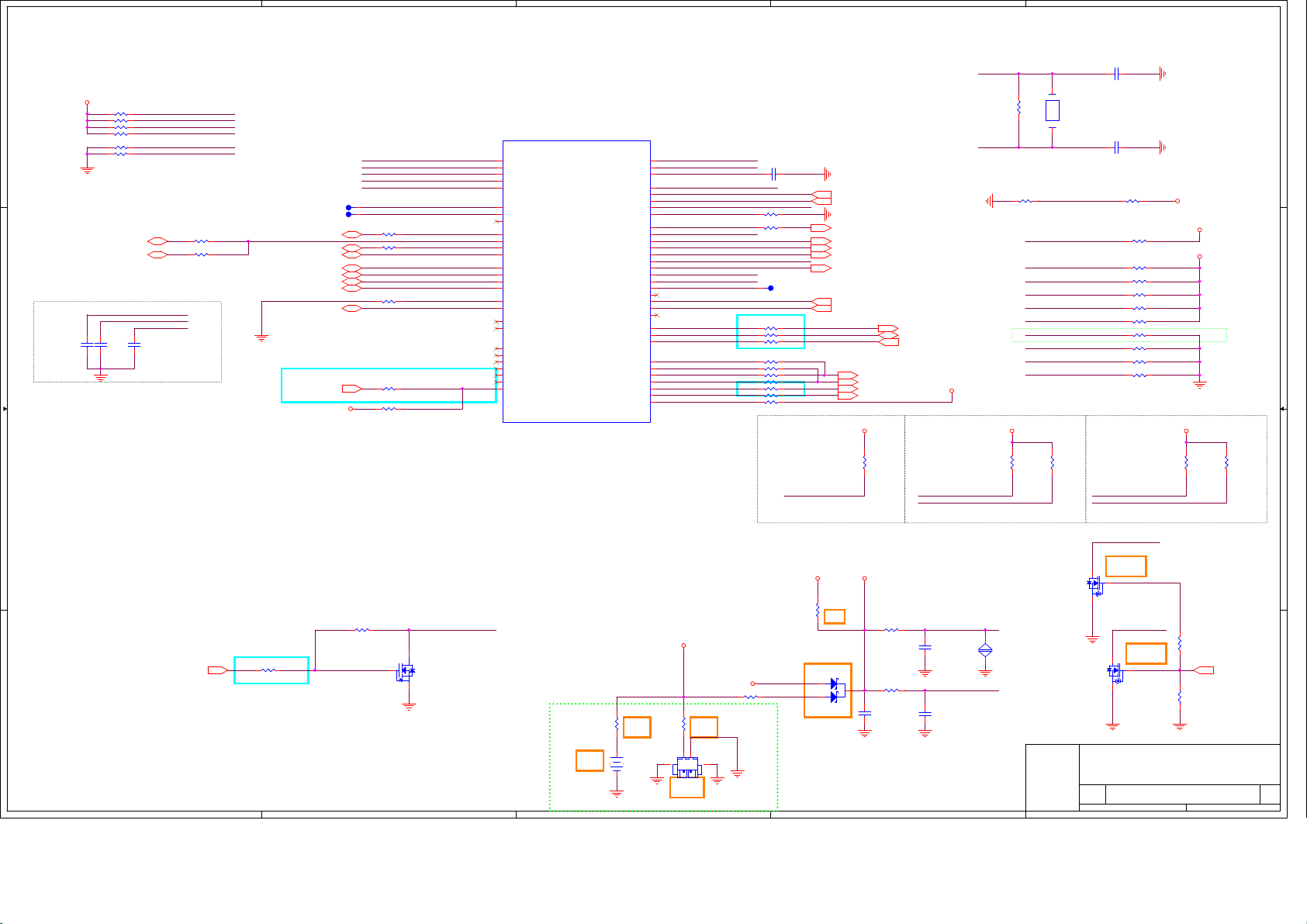

Page 4

5

4

3

2

1

BSW

DDI

0

DDI1

DDI2

R7

1 *2.2K_4

3

_MCP_EDS

M44

RS

VD15

K44

RS

VD12

K48

RS

VD14

K47

RS

VD13

SI_1_CLKP

SI_1_CLKN

SI_1_DP_0

SI_1_DN_0

SI_1_DP_1

SI_1_DN_1

SI_1_DP_2

SI_1_DN_2

SI_1_DP_3

SI_1_DN_3

SI_2_CLKP

SI_2_CLKN

SI_2_DP_0

SI_2_DN_0

SI_2_DP_1

SI_2_DN_1

RS

VD17

RS

VD16

MC

SI_COMP

MMC1_CLK

MMC1_CMD

SD

MMC1_D0

SD

MMC1_D1

SD

MMC1_D2

MMC

1_D5

MMC

1_D6

MMC

1_D7

MMC

1_RCLK

MMC2_CLK

MMC2_CMD

SD

MMC2_D0

SD

MMC2_D1

SD

MMC2_D2

MMC3_CLK

MMC3_CMD

MMC3_CD_B

SD

MMC3_D0

MMC3_D1

SD

MMC3_D2

SD

MMC3_D3

SD

Q7

MN53D0L-7

*D

1

2

T44

T45

Y47

Y48

V45

V47

V50

V48

T41

T42

P50

P48

P47

P45

M48

M47

T50

T48

P44

AB41

AB45

AB44

AC53

AB51

AB52

AA51

AB40

Y44

Y42

Y41

V40

M7

P6

M6

M4

P9

P7

T6

T7

T10

T12

T13

P13

K10

K9

M12

M10

K7

K6

F2

D2

K3

J1

J3

H3

G2

K2

L3

P12

3

M08

CA

M09

CA

M11

CA

BT_COMBO_EN#_R

VSDIO_1P8_EN

VSDIO_PWR_EN#

R1

44

80.6/F_4

BT_COMBO_EN#BT_COMBO_EN#_R

CA

CA

CA

SD

SD

SD

MMC4_DAT0 [20]

SD

MMC4_DAT1 [20]

SD

MMC4_DAT2 [20]

SD

MMC4_DAT3 [20]

SD

MMC4_DAT4 [20]

SD

MMC4_DAT5 [20]

SD

MMC4_DAT6 [20]

SD

MMC4_DAT7 [20]

SD

MMC4_RCLK [20]

GN

D

2

GN

M08 [12]

M09 [12]

M11 [12]

MMC4_CLK [20]

MMC4_CMD [20 ]

GN

TP9013

R4

150/F_4

D

R4

100/F_4

D

76

43

VSDIO_1P8_EN

VSDIO_PWR_EN#

VSDIO_1P8_EN

VSDIO_PWR_EN#

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswell 3/11 (Display)

Custom Braswell 3/11 (Display)

Custom Braswell 3/11 (Display)

Date: Sheet

Wednesday, January 25, 2017

Date: Sheet

Wednesday, January 25, 2017

Date: Sheet

Wednesday, January 25, 2017

38 *100K/F_4

R4

32 *10K/F_4

R4

R4

47 *100K/F_4

R4

40 *10K/F_4

1

MC

MC

MC

MC

MC

MC

MC

SI and Camera interface

MC

MC

MC

MC

MC

MC

MC

MC

MC

MC

GP

_CAMERASB00

GP

_CAMERASB01

GP

_CAMERASB02

GP

_CAMERASB03

GP

_CAMERASB04

GP

_CAMERASB05

GP

_CAMERASB06

GP

_CAMERASB07

GP

_CAMERASB08

GP

_CAMERASB09

GP

_CAMERASB10

GP

_CAMERASB11

SD

SD

SD

MMC1

SD

MMC1_D3_CD_B

MMC

1_D4_SD_WE

SD

MMC1_RCOMP

SD

SD

SDMMC2

SD

MMC2_D3_CD_B

SD

SD

SD

SDMMC3

OF 13

3

+1

.8VS5

MMC3_1P8_EN

SD

MMC3_PWR_ EN_B

SD

MMC3_RCOMP

SD

U26C

+1

.8VS5

D D

C C

DDI1_BKLT_CTRL_R

B B

DDI1_EDP_HPD_R

A A

33 2.2K_4

R4

41 2.2K_4

R4

88 10K/F_4

R4

.8VS5

+1

R4

R4

R4

R1

100K/F_4

D

GN

+1

.8VS5

R4

78

10K/F_4

3

1

GN

D

Q3

2N7002K

2

52 *100K/F_4

67 *100K/F_4

65 *100K/F_4

25

7

5

+1

1

Q9

38 *0_4

R1

EDP_HPD_C

GN

D

SDVO_DATA

SDVO_CLK

HDMI_HPD_DC#

.8V

2

3

DMN53D0L-7

74

R4

100K/F_4

DDI1_BKLT_EN

DDI1_BKLT_CTRL_R

EDP_PANEL_EN

+3

V

49

R1

4.7K/F_4

PWM 3.3V Level Output

UL

T_EDP_HPD [15]

HD

eDP

PC

H_DPST_PWM [15,25]

MI

DB

G_UART_SW#[22]

DB

G_UART_TXD[22]

DB

G_UART_RXD[22]

IN

IN

IN

IN

IN

IN

IN

IN

HDM

I_HPD_DC#[16]

SD

VO_CLK[16]

SD

VO_DATA[1 6]

33 402/F_4

R1

IN

T_EDP_TXP0[15]

IN

T_EDP_TXN0[15]

IN

T_EDP_TXP1[15]

IN

T_EDP_TXN1[15]

IN

T_EDP_AUXP[15]

IN

T_EDP_AUXN[15]

DDI

1_BKLT_EN[25]

ED

P_PANEL_EN[25]

39 402/F_4

R1

20150216: PV build

DBG_UART_SW=0 (UART)

DBG_UART_SW=1 (USB)

52 10K/F_4

R6

+1

.8VS5

53 10K/F_4

R6

+1

.8VS5

54 10K/F_4

R6

+1

.8VS5

4

_D2[16]

_D2#[16]

_D1[16]

_D1#[16]

_D0[16]

_D0#[16]

_CLK[16]

_CLK#[16]

SOC_DDIO_RCOMP

SOC_DDIO_RCOMP_P

DDI1_EDP_HPD_R

DDI1_BKLT_EN

DDI1_BKLT_CTRL_R

EDP_PANEL_EN

SOC_DDI1_RCOMP

SOC_DDI1_RCOMP_P

20150216: PV build

connect to daughter board

Add DBG_UART_SW for win7

HDMI_HPD_DC#

SDVO_CLK

SDVO_DATA

DBG_UART_SW#

DBG_UART_TXD

DBG_UART_RXD

W51

W53

D50

C51

H49

H50

F53

F52

G53

G52

H47

H46

Y51

Y52

V52

V51

F38

G38

J51

H51

K51

K52

L53

L51

M52

M51

M42

K42

R51

P51

P52

R53

F47

F49

F40

G40

J40

K40

F42

G42

D44

F44

D48

C49

U51

T51

T52

B53

A52

E52

D52

B50

B49

E53

C53

A51

A49

G44

DDI

0_TXP_0

DDI

0_TXN_0

DDI

0_TXP_1

DDI

0_TXN_1

DDI

0_TXP_2

DDI

0_TXN_2

DDI

0_TXP_3

DDI

0_TXN_3

DDI

0_AUXP

DDI

0_AUXN

HV

_DDI0_HPD

HV

_DDI0_DDC_SCL

HV

_DDI0_DDC_SDA

PAN

EL0_BKLTEN

PAN

EL0_BKLTCTL

PAN

EL0_VDDEN

DDI

0_PLLOBS_P

DDI

0_PLLOBS

DDI

1_TXP_0

DDI

1_TXN_0

DDI

1_TXP_1

DDI

1_TXN_1

DDI

1_TXP_2

DDI

1_TXN_2

DDI

1_TXP_3

DDI

1_TXN_3

DDI

1_AUXP

DDI

1_AUXN

HV

_DDI1_HPD

PAN

EL1_BKLTEN

PAN

EL1_BKLTCTL

PAN

EL1_VDDEN

DDI

1_PLLOBS_P

DDI

1_PLLOBS

DDI

2_TXP_0

DDI

2_TXN_0

DDI

2_TXP_1

DDI

2_TXN_1

DDI

2_TXP_2

DDI

2_TXN_2

DDI

2_TXP_3

DDI

2_TXN_3

DDI

2_AUXP

DDI

2_AUXN

HV

_DDI2_HPD

HV

_DDI2_DDC_SCL

HV

_DDI2_DDC_SDA

RS

VD6

RS

VD3

RS

VD9

RS

VD8

RS

VD5

RS

VD4

VD10

RS

VD7

RS

VD2

RS

VD1

RS

VD11

RS

*BSW_MCP_ EDS

NC's

+1

.8VS5

04

+1

.8VS5

GN

D

1A

1A

1A

of

43

of

43

of

43

5

5

5

Page 5

5

+1

.8V

19

C1

*22P/50V_4

Q1

SATA_LED_R_N

SATA0_DEVSLP_SOC

SATA1_DEVSLP_SOC

+1

.8V

321

4 DMN53D0L-7

Q8

*D

MN53D0L-7

321

ACC_LED_R#

BIT_CLK_AUDIO

HDD

SSD

SATA_LED_R_N

GN

SAT

A_TXP0[20]

SAT

A_TXN0[20]

SAT

A_RXP0[20]

SAT

A_RXN0[20]

SAT

A_TXP1[21]

SAT

A_TXN1[21]

SAT

A_RXP1[21]

SAT

A_RXN1[21]

SO

C_KBC_SCI[25]

SAT

A0_DEVSLP_SOC[21]

SAT

A1_DEVSLP_SOC[21]

AC

D

CEL_INTH#[23]

AC

Z_RST#_AUDIO[17]

BI

T_CLK_AUDIO[17]

AC

Z_SDIN0[17]

AC

Z_SYNC_AUDIO[17]

AC

Z_SDOUT_AUDIO[17]

ACZ_SPKR[17]

50 10K/F_4

R5

55 *10K/F_4

R6

46 *10K/F_4

R5

D D

SAT

A_LED#[20]

AC

C_LED#[20]

C C

GN

D

30 402/F_4

R1

+1

.8VS5

4

52 20/F_4

R5

55 *100K/F_4

R4

5 2.2K_4

R7

71 75/F_4

R1

62 75/F_4

R1

76 75/F_4

R1

68 75/F_4

R1

SATA_TXP0

SATA_TXN0

SATA_RXP0

SATA_RXN0

SATA_TXP1

SATA_TXN1

SATA_RXP1

SATA_RXN1

SATA_LED_R_N

SATA_GP0

SATA0_DEVSLP_SOC

SATA1_DEVSLP_SOC

SATA_RCOMP_DP

SATA_RCOMP_DN

SOC_SPI_CLK_R

SOC_SPI_CS#_R

ACC_LED_R#

ACCEL_INTH#

SOC_SPI_MOSI_R

SOC_SPI_MISO_R

SOC_SPI_WP#

SOC_SPI_HOLD#

ACZ_RST#

ACZ_BCLK

ACZ_SDIN0

ACZ_SYNC

ACZ_SDOUT

AF13

AF12

AF14

AK10

AK12

AK13

C31

B30

N28

M28

C29

A29

J28

K28

AH3

AH2

AG3

AG1

AF3

N30

M30

W3

AD6

AD9

AD7

AB9

AB7

AK9

V4

V6

V7

V2

V3

U1

U3

H4

SAT

A_TXP0

SAT

A_TXN0

SAT

A_RXP0

SAT

A_RXN0

SAT

A_TXP1

SAT

A_TXN1

SAT

A_RXP1

SAT

A_RXN1

SAT

A_LEDN

SAT

A_GP0

SAT

A_GP1

SAT

A_GP2

SAT

A_GP3

SAT

A_OBSP

SAT

A_OBSN

FS

T_SPI_CLK

FS

T_SPI_CS0_B

FS

T_SPI_CS1_B

FS

T_SPI_CS2_B

FS

T_SPI_D0

FS

T_SPI_D1

FS

T_SPI_D2

FS

T_SPI_D3

MF

_HDA_RSTB

MF

_HDA_SDI1

MF

_HDA_CLK

MF

_HDA_SDI0

MF

_HDA_SYNC

MF

_HDA_SDO

MF

_HDA_DOCKENB

MF

_HDA_DOCKRSTB

SPKR

GP

_SSP_2_CLK

GP

_SSP_2_FS

GP

_SSP_2_TXD

GP

_SSP_2_RXD

SATA

FAST SPI

AUDIO

BSW

4

3

_MCP_EDS

Y

OF 13

PC

PC

PC

IE_RXP0

PC

IE_RXN0

PC

PC

PC

PC

IE_RXN1

PC

PC

Ie

PC

PC

PC

IE_RXN2

PC

PC

PC

IE_RXP3

PC

IE_RXN3

PC

IE_CLKREQ0B

PC

IE_CLKREQ1B

PC

IE_CLKREQ2B

PC

IE_CLKREQ3B

CL

K_DIFF_P_0

CL

K_DIFF_N_0

CL

K_DIFF_P_1

CL

K_DIFF_N_1

CL

K_DIFF_P_2

CL

K_DIFF_N_2

CL

K_DIFF_P_3

CL

K_DIFF_N_3

PC

IE_OBSP

PC

IE_OBSN

SPI

SPI

1_CS0_B

SPI

SPI

1_CS1_B

SPI

SPI

*BSW_MCP_ EDS

U26D

IE_TXP0

IE_TXN0

IE_TXP1

IE_TXN1

IE_RXP1

IE_TXP2

IE_TXN2

IE_RXP2

IE_TXP3

IE_TXN3

RS

VD20

RS

VD21

1_CLK

1_MISO

1_MOSI

PCIE_TXP1_LAN_L

C24

PCIE_TXN1_LAN_L

B24

G20

J20

A25

C25

D20

F20

B26

C26

D22

F22

PCIE_TXP2_WLAN_C

A27

PCIE_TXN2_WLAN_ C

C27

G24

J24

PCIE_CLKREQ_LAN#

AM10

PCIE_CLKREQ_VGA#

AM12

PCIE_CLKREQ2#

AK14

PCIE_CLKREQ_WL AN#

AM14

CLK_PCIE_LANP

A21

CLK_PCIE_LANN

C21

C19

B20

C18

B18

CLK_PCIE_WLANP

C17

CLK_PCIE_WLANN

A17

C16

B16

SOC_PCIE_COMP

D26

SOC_PCIE_COMN

F26

V14

Y13

Y12

V13

V12

74 0.1U/16V_4

C4

73 0.1U/16V_4

C4

72 0.1U/16V_4

C4

71 0.1U/16V_4

C4

03 402/F_4

R1

2

1

05

PC

IE_TXP1_LAN [18]

PC

IE_TXN1_LAN [ 18]

PC

IE_RXP1_LAN [18]

PC

IE_RXN1_LAN [18]

PC

IE_TXP2_WLAN [21]

PC

IE_TXN2_WLAN [21]

PC

IE_RXP2_WLAN [21]

PC

IE_RXN2_WLAN [21]

PC

IE_CLKREQ_LAN# [18]

PC

IE_CLKREQ_WL AN# [21]

CL

K_PCIE_LANP [18]

CL

K_PCIE_LANN [18]

CL

K_PCIE_WLANP [21]

CL

K_PCIE_WLANN [21]

20150209 Update PV build SPI NOR FLASH

Vender

Winbond

Gi

gaDevice

EO

N

LAN

WIFI

PCIE_CLKREQ_LAN#

PCIE_CLKREQ_VGA#

PCIE_CLKREQ2#

PCIE_CLKREQ_WL AN#

Size

P/N

AKE5 EZN0N 01 (W 25Q6 4FWSS IQ)

8MB

AKE5 EG-0 Q01 (GD25 LB64C SIGR)

8MB

AKE5 EFN0Q 00 ( EN25S 64-1 04HIP )

8MB

78 10K/F_4

R1

72 10K/F_4

R1

35 10K/F_4

R5

50 10K/F_4

R1

+1

.8VS5

Socket (208mil) DFHS08FS023 (Firstly Stuff)

+1

+3

.8VS5

VS5

B B

753.3K/F_4

353.3K/F_4

R4

R4

C4

56

0.1U/16V_4

SOC_SPI_WP#

SOC_SPI_HOLD#

A A

5

4

R1

15 0_4

R1

11 0_4

U2

SOC_SPI_CS#_R2

SOC_SPI_CLK_R2

SOC_SPI_MOSI_R2

SOC_SPI_MISO_R2 SPI_7P

SPI_3P

SPI

ROM Socket

U21 & U22 footprint overlap

2

1

#

CE

VD

6

K

SC

5

SI

2

LD#

SO

HO

3

#

WP

VSS

*A25LQ32AM- F/Q

DFHS08FS023

91960-0084L-8P-SOCKET

3

GN

SPI_VCC

8

D

7

4

R4

R4

28

30

0_4

*0_4

SPI NOR FLASH

D

8

SPI_3P

3

SPI_7P

7

*SPI_FLASH

soic8-7_9-1_27

AKE5EZN0N01

IC FLASH (8P) W25Q64FWSSIQ (SOIC)

20150101: SI build change to AKE5EZN0N01

For EMI

1

U2

C

VC

#

SPI

WP

_HOLD

SPI

SOC_SPI_MOSI_R2

SOC_SPI_MISO_R2

SOC_SPI_CS#_R2

SOC_SPI_CLK_R2

SPI_3P

SPI_7P

73 0_4

R4

60 0_4

R4

68 0_4

R4

61 0_4

R4

SOC_SPI_WP#

SOC_SPI_HOLD#

SOC_SPI_MOSI_R2SPI_VCC

5

_SI

SPI

_SO

SPI

#

CS

_SCK

D

GN

C4

61*10P/50V_4

2

1

6

4

GN

SOC_SPI_CLK_R2

SOC_SPI_MISO_R2

SOC_SPI_CS#_R2

SOC_SPI_CLK_R2

D

46

TP

52

TP

53

TP

45

TP

51

TP

47

TP

2

R4

29 *10_4

R4

69 *10_4

R4

57 *33_4

R4

26 *10_4

20150225: PV build

change TP52, TP53, TP45, TP46

from TP2050 to TP2675 for ICT

SOC_SPI_MOSI_R

SOC_SPI_MISO_R

SOC_SPI_CS#_R

SOC_SPI_CLK_R

12 0_4

R1

08 0_4

R1

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Si

ze Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswel 4/11(SP/PC/SA/AU)

Custom Braswel 4/11(SP/PC/SA/AU)

Custom Braswel 4/11(SP/PC/SA/AU)

Date: Sheet

Date: Sheet

Date: Sheet

To EC for SHPI

SH

PI_SPI_CLK [26 ]

SH

PI_SPI_CS# [26 ]

SH

PI_SPI_MISO [26]

SH

PI_SPI_MOSI [26]

SH

PI_SPI_WP# [26 ]

PI_SPI_HOLD# [26]

SH

From CPU

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Wednesday, January 25, 2017

Wednesday, January 25, 2017

Wednesday, January 25, 2017

1

1A

1A

1A

of

53

of

53

of

53

5

5

5

Page 6

5

4

3

2

.8VS5

+1

1

06

R1

2.2K_4

BO

ARD_ID4 [17]

20161018 add

I2

C_5_SCL [24]

I2

C_5_SDA [24]

TP

56

TP

55

TP

54

09 2.2K_4

R5

04 2.2K_4

R5

92 1K/F_4

R1

SMB_SOC_DATA

SMB_SOC_CLK

SMB_SOC_ALERTB

2573

I2C_4_SCL

I2C_4_SDA

+1

.8VS5

R4

10K/F_4

+1

SM

SM

SM

90

PC

I_SERR# [26]

.8VS5

B_SOC_DATA [25]

B_SOC_CLK [2 5]

B_SOC_ALERTB [2 4]

2574

R1

_MCP_EDS

BSW

C11

RS

VD3

B10

RS

VD2

F12

RS

VD9

F10

RS

MF

_SMB_CLK

MF

_SMB_DATA

MF

_SMB_ALERTB

RS

RS

RS

RS

I2

C0_SCL

I2

C0_SDA

I2

C1_SCL

I2

C1_SDA

I2

C2_SCL

I2

C2_SDA

I2

C3_SCL

I2

C3_SDA

I2

C4_SCL

I2

C4_SDA

I2

C5_SCL

I2

C5_SDA

I2

C6_SCL

I2

C6_SDA

RS

RS

VD8

D12

RS

VD5

E8

RS

VD7

C7

RS

VD4

D6

RS

VD6

J12

VD11

F7

VD10

J14

VD12

L13

VD15

AK6

AH7

BOARD_ID2

AF6

BOARD_ID3

AH6

BOARD_ID4

AF9

BOARD_ID5

AF7

BOARD_ID6

AE4

BOARD_ID7

AD2

I2C_4_SCL

AC1

I2C_4_SDA

AD3

I2C_5_SCL

AB2

I2C_5_SDA

AC3

PCI_SERR#

AA1

I2C_6_SDA

AB3

I2C_NFC_SOC_SCL

AA3

VD21

VD22

Y2

AM6

AM7

AM9

I2C_NFC_SOC_SDA

SMB_SOC_CLK

SMB_SOC_DATA

SMB_SOC_ALERTB

iC

LK

TFM CLK's

PL

GPIO_DFX

GPIO_SUS

RE

SERVED

I2C

SMBUS

5

OF 13

AH45

AM40

AM41

AM44

AM45

AM47

AK48

AM48

AK41

AK42

AD51

AD52

AH50

AH48

AH51

AH52

AG51

AG53

AF52

AF51

AE51

AC51

AH40

P24

M22

J26

N26

P20

N20

P26

K26

M26

A9

C9

B8

B7

B5

B4

Y3

U26E

OS

CIN

OS

COUT

RS

VD13

RS

VD17

IC

LKICOMP

IC

LKRCOMP

RS

VD18

RS

VD14

RS

VD16

RS

VD1

MF

_PLT_CLK0

MF

_PLT_CLK1

MF

_PLT_CLK2

MF

_PLT_CLK3

MF

_PLT_CLK4

MF

_PLT_CLK5

GP

IO_DFX0

GP

IO_DFX1

GP

IO_DFX2

GP

IO_DFX3

GP

IO_DFX4

GP

IO_DFX5

GP

IO_DFX6

GP

IO_DFX7

GP

IO_DFX8

GP

IO_SUS0

GP

IO_SUS1

GP

IO_SUS2

GP

IO_SUS3

GP

IO_SUS4

GP

IO_SUS5

GP

IO_SUS6

GP

IO_SUS7

SEC

_GPIO_SUS9

SEC

_GPIO_SUS8

SEC

_GPIO_SUS10

SEC

_GPIO_SUS11

GP

IO0_RCOMP

GP

IO_ALERT

*BSW_MCP_ EDS

9 27P/50V_4

D D

C C

C6

D

GN

D

GN

C6

SOC_XTAL19_OUT

1

2

Y3

2MHZ +-30PPM

19.

4

3

SOC_XTAL19_IN

8 27P/50V_4

7

R8

200K/F_4

21 20/F_4

SO

C_KCB_SMI[12,25]

TP

_INTH#_SOC[6,24]

R5

+1

.8VS5

TP_INTH#_SOC SOC_COLD_RESET_N

GN

R6

10K/F_4

D

TP

56

R1

8 49.9/F_4

R9

BT

_OFF[12,21]

RF

_OFF[12,21]

TO

P_SWAP[12]

GP

IO_SUS3[12]

BI

OS_STRAP[12]

SO

C_Override[12]

GP

IO_SUS6[12]

SEC

_GPIO_SUS9[12]

GP

IO_SUS8[12]

_INTH#_SOC[6,24]

GN

40 2.49K/F_4

BO

R4

R1

D

R6

TP

18

TP

22

TP

20

TP

19

TP

21

TP

24

ARD_ID8[15]

93 10K/F_4

81 100/F_4

57 *0_4

SOC_XTAL19_IN

SOC_XTAL19_OUT

ICLK_ICOMP

ICLK_RCOMP

BOARD_ID8

BOARD_ID9

BOARD_ID0

BOARD_ID1

BT_OFF

RF_OFF

TOP_SWAP

GPIO_SUS3

BIOS_STRAP

SOC_Override

GPIO_SUS6

GPIO_SUS7

SEC_GPIO_SUS9

GPIO_SUS8

58 *0_4

R6

GPIO_SUS11

2.2K_4

+1

B B

Board ID

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BIOS Strap Description

(Reserve)

SATA/EMMC SELECT

1 = TPM

0 = Non-TPM

(Reserve)

SPK_ID

BOARD_ID5

BOARD_ID6

Memory Vendor BOARD_ID1

for MD USE

BOARD_ID7

BOARD_ID8 1 = Synaptics Touchpad

A A

BOARD_ID9

0 = ELAN Touchpad

1 = SO-DIMM

0 = Memory Down

5

BOARD_ID7

BOARD_ID6

0

0

0

0

1

0

0

1

1

0

1

0

1

1

1

1

BOARD_ID2

00

10

01

11

4

BOARD_ID5

0

1

0

1

0

1

0

1

EMMC only

EMMC +SATA

SATA only

(Reserve)

Vender

Quanta PN

Description

3

91 10K/F_4

R1

84 10K/F_4

R1

54 *10K/F_4

R1

46 *10K/F_4

R1

31 *10K/F_4

R1

R1

41 10K/F_4

R5

22 10K/F_4

R5

16 10K/F_4

R1

2583 *10K/F_4

R1

2584 *10K/F_4

GN

D

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

BOARD_ID6

BOARD_ID7

BOARD_ID8

BOARD_ID9

88 *10K/F_4

R1

85 *10K/F_4

R1

55 10K/F_4

R1

47 10K/F_4

R1

34 10K/F_4

R1

R1

42 *10K/F_4

R5

18 *10K/F_4

R5

17 *10K/F_4

R1

2581 10K/F_4

R1

2582 10K/F_4

2

.8VS5

NFL-P BSW default pull up

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswel 5/11(I2C/GPIO/CLK

Custom Braswel 5/11(I2C/GPIO/CLK

Custom Braswel 5/11(I2C/GPIO/CLK

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

1

of

63

of

63

of

63

1A

1A

1A

5

5

5

Page 7

5

4

3

2

1

07

D D

BSW_MCP_EDS

B3.0

US

US

HSICUART

US

RESERVED

6

OF 13

O

US

B_OTG_ID

US

B_DP0

US

B_DN0

US

B_DP1

US

B_DN1

US

B_DP2

US

B_DN2

US

B_DP3

US

B_DN3

US

B_DP4

US

B_DN4

USB2.0

US

B_OC1_B

US

B_OC0_B

RS

US

B_VBUSSNS

US

B_RCOMP

B_HSIC_0_STROBE

US

B_HSIC_0_DATA

B_HSIC_1_STROBE

US

B_HSIC_1_DATA

US

B_HSIC_RCOMP

UA

RT1_TXD

UA

RT1_RXD

UA

RT1_CTS_B

UA

RT1_RTS_B

UA

RT2_TXD

UA

RT2_RXD

UA

RT2_CTS_B

UA

RT2_RTS_B

B48

C42

B42

C43

B44

C41

A41

C45

A45

B40

C40

SOC_USB_OC1

P16

SOC_USB_OC0

P14

USB2_OBSP

B46

VD3

B47

USB_RCOMP

A48

M36

N36

K38

M38

USB_HSIC_RCOMP

N38

AD10

AD12

AD13

AD14

Y6

Y7

V9

V10

8 10K/F_4

R8

9 10K/F_4

R9

TP

US

BP0+ [22]

US

BP0- [22]

US

BP1+ [22]

US

BP1- [22]

US

BP2+ [19]

US

BP2- [19]

US

BP3_HUB+ [23]

US

BP3_HUB- [23]

US

BP4_TS+ [15]

US

BP4_TS- [15]

13

59 *0_4/S

R4

54 113/F_4

R4

45 45.3/F_4

R1

US

B 3.0 /2.0 Da ughte r Baa rd Up port

USB 3 .0/2 .0 Da ughter Ba ard Down port

USB T ypeC 2.0

USB 2 .0 HUB

TS

+1

.8VS5

D

GN

D

GN

D

GN

U26F

US

B30_P0_TX+[22]

US

USB 3 .0/2 .0 Da ughter Ba ard Up po rt

USB 3 .0/2 .0 Da ughter Ba ard Down port

USB T ypeC 3.0

C C

B B

USB T ypeC 3.0

1017 -->NC

B30_P0_TX-[22]

US

B30_P0_RX+[22]

US

B30_P0_RX-[22]

US

B3_P1_TX+[22]

US

B3_P1_TX-[22]

US

B3_P1_RX+[22]

US

B3_P1_RX-[22]

US

B3_P2_TX+[19]

US

B3_P2_TX-[19]

US

B3_P2_RX+[19]

US

B3_P2_RX-[19]

29 402/F_4

R1

USB_RCOMP_DP

USB_RCOMP_DN

B32

C32

F28

D28

A33

C33

F30

D30

C34

B34

G32

J32

C35

A35

G34

J34

D34

F34

C37

A37

F36

D36

M34

M32

C38

B38

G36

J36

N34

P34

US

B3_TXP0

US

B3_TXN0

US

B3_RXP0

US

B3_RXN0

US

B3_TXP1

US

B3_TXN1

US

B3_RXP1

US

B3_RXN1

US

B3_TXP2

US

B3_TXN2

US

B3_RXP2

US

B3_RXN2

US

B3_TXP3

US

B3_TXN3

US

B3_RXP3

US

B3_RXN3

US

B3_OBSP

US

B3_OBSN

RS

VD4

RS

VD1

RS

VD7

RS

VD6

RS

VD11

RS

VD10

RS

VD5

RS

VD2

RS

VD8

RS

VD9

RS

VD12

RS

VD13

*BSW_MCP_ EDS

A A

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswel 6/11 (USB/URAT)

Custom Braswel 6/11 (USB/URAT)

Custom Braswel 6/11 (USB/URAT)

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

5

4

3

2

Tuesday, January 24, 2017

1

73

73

73

1A

1A

1A

of

of

of

5

5

5

Page 8

5

.8VS5

EMI

C8

18P/50V_4

+1

38 51/F_4

R5

24 51/F_4

R5

07 51/F_4

R5

36 51/F_4

R5

60 51/F_4

R1

75 51/F_4

R1

D

GN

CL

K_PCI_TPM[23]

CL

K_24M_DEBUG[21 ]

3

4

C8

18P/50V_4

XDP_H_TDO

XDP_H_TMS

XDP_H_TDI

XDP_H_PREQ#

XDP_H_TRST#

XDP_H_TCK

CLK_24M_KBC

CLK_PCI_TPM

CLK_24M_DEBUG

1

C8

18P/50V_4

18 22_4

R1

14 22_4

R1

9028

TP

9029

TP

CL

K_24M_KBC[26]

L_C

LKRUN#[26]

LF

RAME#[21,23 ,26]

LA

D0[21,23,26]

LA

D1[21,23,26]

LA

D2[21,23,26]

LA

D3[21,23,26]

SO

C_SERIRQ[25,26]

D

GN

H_

PROCHOT#[26,31,32]

+1

.8VS5

D D

C C

4

21 22_4

R1

64 22_4

R4

35 100/F_4

R1

89 *0_4/S

R4

92 *20K/F_4

R4

XDP_H_TCK

XDP_H_TDI

XDP_H_TDO

XDP_H_TMS

XDP_H_TRST#

XDP_H_PRDY#

XDP_H_PREQ#

CLK_24M_KBC_R

CLK_33M_TPM_R

SOC_CLKRUN#

RAME#

LF

D0

LA

D1

LA

D2

LA

D3

LA

LPC_RCOMP

SOC_SERIRQ

SOC_PROCHOT#

AF42

AD47

AF40

AD48

AB48

AD45

AF41

AF50

AF48

AF44

AF45

AD50

M13

P2

R3

T3

P3

M3

M2

N3

N1

T4

T2

H5

H7

P28

P30

U26G

TC

K

TD

I

TD

O

TM

S

TR

ST_B

CX

_PRDY_B

CX

_PREQ_B

RS

VD5

MF

_LPC_CLKOUT0

MF

_LPC_CLKOUT1

LP

C_CLKRUNB

LP

C_FRAMEB

MF

_LPC_AD0

MF

_LPC_AD1

MF

_LPC_AD2

MF

_LPC_AD3

LP

C_HVT_RCOMP

IL

B_SERIRQ

RS

VD23

RS

VD24

RS

VD6

RS

VD7

RS

VD4

RS

VD3

RS

VD1

RS

VD2

PR

OCHOT_B

*BSW_MCP_ EDS

3

BSW

_MCP_EDS

RTC_X1

TCX1_PAD

TCX2_PAD

SR

TCRST_B

REPWROK

RS

MRST_B

RT

EST_B

RS

VD_VSS

SU

S_STAT_B

U_SUSCLK

U_SLP_S4_B

U_SLP_S3_B

U_PLTRST_B

U_WAKE_B

SVI

D0_CLK

SVI

D0_DATA

D0_ALERT_B

M18

RTC_X2

K18

BRTC_EXTPAD

F16

SRT_CRST#

D18

CORE_PWROK

G16

SOC_RSMRST#

F18

SOC_RTEST#

J16

G18

SUS_PWRDOW NACK

AE3

GPIO_J20

D14

SOC_SUSCLK SOC_REST_BTN

C15

SLP_S4#

C12

SLP_S3#

B14

SOC_REST_BTN

AF2

SOC_PLTRST#

F14

PMU_BATLOW#_R

C14

AC_PRESENT

C13

SLP_S0IX#

A13

B12

SOC_PMC_WAKE

N16

SOC_PWRBTN#

M16

P18

AD42

AD41

AD40

VCC0_SENSEP_R

AG32

VCC0_SENSEN_R

AJ32

VCC1_SENSEP_R

AD29

VCC1_SENSEN_R

AF27

VGG_SENSEP_R

AD24

VGG_SENSEN_R

AD22

VNN_REFIN_R

AC27

4 0.1U/16V_4

C7

02 10K/F_4

R1

2566 *0_4

R1

TP

63 *0_4/S

R1

70 *0_4/S

R1

67 *0_4/S

R1

53 2.2_4

R1

61 2.2_4

R1

58 2.2_4

R1

57 2.2_4

R1

65 *0_4/S

R1

69 *0_4/S

R1

26 *100/F_4

R1

GN

D

CO

RE_PWROK [25]

SO

C_RSMRST# [2 5]

GN

D

PC

H_SUSPWRDNACK [26]

SO

C_SUSCLK [21]

SL

P_S4# [2,25]

SL

P_S3# [25]

SO

C_PLTRST# [20,25]

49

SO

SO

VR_SVID_CLKSVID_CLK_SOC

VR_SVID_DATASVID_DATA_SOC

VR_SVID_ALERT#SVID_ALERT#_SOC

C_PMC_WAKE [25]

C_PWRBTN# [25]

BR

BR

BVC

PMU

PM

LPC

PWM

SVID

Voltage sense

UNCO

UNCO

7

OF 13

CRTC_EXTPAD

C

RT

CO

SU

SPWRDNACK

PM

PM

PM

U_RESETBUTTON_B

PM

PM

U_BATLOW_B

PM

U_AC_PRESENT

PM

U_SLP_S0IX_B

PM

U_SLP_LAN_B

PM

PM

U_PWRBTN_B

PM

U_WAKE_LAN_B

SVI

CO

RE_VCC0_SENSE

CO

RE_VSS0_SENSE

CO

RE_VCC1_SENSE

CO

RE_VSS1_SENSE

DDI

_VGG_SENSE

RE_VSS_SENSE2

RE_VSS_SENSE1

JTAG/ITP

Reserved

VC

C_SENSE [32]

VSS_

SENSE [32]

VG

G_SENSE [31]

VG

GSS_SENSE [3 1]

.05VS5

+1

2

VR

_SVID_CLK [31, 32]

VR

_SVID_DATA [31,3 2]

VR

_SVID_ALERT# [31 ,32]

+1

.05VS5

C Clock 32.768KHz

RT

RTC_X1

10M_4

27

R4

RTC_X2

6 *10K/F_4

R7

GN

D

.05VS5

+1

12

Y4

768KHZ/20ppm

32.

GPIO_J20

SOC_PLTRST#

PMU_BATLOW#_R

SUS_PWRDOW NACK

SOC_PMC_WAKE

AC_PRESENT

CORE_PWROK

SUS_PWRDOW NACK

AC_PRESENT

SOC_RSMRST#

1

08

53 15P/50V_4

C4

64 15P/50V_4

C4

7 *10K/F_4

R7

33 2.2K_4

R5

3 *1K/F_4

R8

8 20K/F_4

R7

27 *10K/F_4

R5

28 10K/F_4

R1

9 2.2K_4

R7

Sch check list V1.2 -->add 100 K PD

59 100K/F_4

R6

23 100K/F_4

R5

6 *10K/F_4

R8

5 100K/F_4

R8

D

GN

D

GN

+1

.8VS5

+1

.8VS5

+1

.8VS5

D

GN

.05VS5

+1

2

66

R1

200/F_4

VR_SVID_DATAVR_SVID_ALERT#

B B

ils

20m

AT_RTC

D1

2

1

BAT54CW

+3

V_RTC

R1

2588

*0_4

R4

11 20K/F_4

4

3

GN

C4

1U/6.3V_4

D

20K/F_4

36

2

+B

C Circuitry(RTC)

RT

AC Present: This input pin indicates when the platform is plugged into AC power.

R5

28 *0_4

R5

_PRESENT_EC[26]

AC

A A

5

29 *0_4/S

AC_PRESENT_NM

2

4

AC_PRESENT

61

Q3

8B

PJT138K

R12567/R12568 close D14

GN

D

option

CN9

12

4 3

GN

D

R1

2567

0_6

BAT_CONN

+3

V_RTC_0

C Power trace width 20mils.

RT

VPCU

+3

+3V_RTC_0 +3V_RTC_1

R4

12 1K/F_4

R1

2568

*0_6

1

2

4 3

GN

1

CN1

GN

D

*88266-02 0L

3

D

GN

D

VR_SVID_CLK

SOC_RTEST#

C4

38

1U/10V_4

GN

D

C4

37

1U/10V_4

GN

D

SRT_CRST#

R4

07

12

J1

*S

GN

D

R4

*301/F_4

OLDERJUMPER- 2

3

R4

*200/F_4

VR_SVID_DATA

VR_SVID_CLK

R1

*301/F_4

Close to VGG power controlClose to VCC power controlClose to CPU

SRT_CRST#

Q1

2504

3

2N7002K

2

1

SOC_RTEST#

9

Q2

3

*2N7002K

2

1

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswel 7/11(RTC/LPC/PMU)

Custom Braswel 7/11(RTC/LPC/PMU)

Custom Braswel 7/11(RTC/LPC/PMU)

Date: Sheet

Wednesday, January 25, 2017

Date: Sheet

Wednesday, January 25, 2017

Date: Sheet

Wednesday, January 25, 2017

R1

2590

0_4

R3

79

10K/F_4

1

0

6

R2

*200/F_4

_RTC_RST [26]

EC

of

83

of

83

of

83

5

5

5

1A

1A

1A

Page 9

5

4

3

2

1

09

+V

CORE

D D

20

C1

22U/6.3V_6

D

GN

50

C4

22U/6.3V_6

D

GN

75

C1

1U/10V_4

C4

7U/6.3VS_8

*4

36

1U/10V_4

D

GN

C C

B B

16

C1

22U/6.3V_6

52

C4

22U/6.3V_6

+V

GG

62

C4

C4

7U/6.3VS_8

*4

D

GN

37

C1

1U/10V_4

38

C1

C1

4.7U/6.3V_4

CORE

+V

C1

4.7U/6.3V_4

69

C1

/6.3V_4

10U

7U/6.3VS_8

*4

CORE_V1P15_PWR

25

C1

1U/10V_4

40

C1

1U/10V_4

GN

29

26

30

45

C1

1U/10V_4

DDI_1P15_PWR

1U/10V_4

D

C5

/6.3V_4

10U

C8

C1

4.7U/6.3V_4

C4

4.7U/6.3V_4

4

1U/10V_4

7

17

54

C1

/6.3V_4

10U

33

C1

1U/10V_4

31

5

C8

6.4A=256mils

22

C1

4.7U/6.3V_4

27

C1

4.7U/6.3V_4

11A=440mils

28

C1

/6.3V_4

10U

FUSE_1P15_PWR

32

C1

/6.3V_4

10U

AF36

AG33

AG35

AG36

AG38

AJ33

AJ36

AJ38

AF30

AG27

AG29

AG30

AJ27

AJ29

AJ30

AF29

AD16

AD18

AD19

AF16

AF18

AF19

AF21

AF22

AJ19

AG16

AG18

AG19

AG21

AG22

AG24

AJ21

AJ22

AJ24

AK24

AK30

AK35

AK36

AM29

AK33

AJ35

AM19

AK21

U26H

CO

RE_VCC1_S0IX3

CO

RE_VCC1_S0IX7

CO

RE_VCC1_S0IX8

CO

RE_VCC1_S0IX9

CO

RE_VCC1_S0IX10

CO

RE_VCC1_S0IX14

CO

RE_VCC1_S0IX15

CO

RE_VCC1_S0IX16

CO

RE_VCC1_S0IX2

CO

RE_VCC1_S0IX4

CO

RE_VCC1_S0IX5

CO

RE_VCC1_S0IX6

CO

RE_VCC1_S0IX11

CO

RE_VCC1_S0IX12

CO

RE_VCC1_S0IX13

CO

RE_VCC1_S0IX1

DDI

_VGG_S0IX1

DDI

_VGG_S0IX2

DDI

_VGG_S0IX3

DDI

_VGG_S0IX4

DDI

_VGG_S0IX5

DDI

_VGG_S0IX6

DDI

_VGG_S0IX7

DDI

_VGG_S0IX8

DDI

_VGG_S0IX15

DDI

_VGG_S0IX9

DDI

_VGG_S0IX10

DDI

_VGG_S0IX11

DDI

_VGG_S0IX12

DDI

_VGG_S0IX13

DDI

_VGG_S0IX14

DDI

_VGG_S0IX16

DDI

_VGG_S0IX17

DDI

_VGG_S0IX18

DDI

_VGG_S0IX19

CO

RE_V1P15_S0IX1

CO

RE_V1P15_S0IX2

CO

RE_V1P15_S0IX3

CO

RE_V1P15_S0IX4

FU

SE_V1P15_S0IX2

FU

SE_V1P15_S0IX1

DDI

_V1P15_S0IX2

DDI

_V1P15_S0IX1

*BSW_MCP_ EDS

BSW

_MCP_EDS

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

UNCO

8

OF 13

U

UNCO

RE_VNN_S41

UNCO

RE_VNN_S42

UNCO

RE_VNN_S43

UNCO

RE_VNN_S44

UNCO

RE_VNN_S45

UNCO

RE_VNN_S46

UNCO

RE_VNN_S47

UNCO

RE_VNN_S48

UNCO

RE_VNN_S49

UNCO

RE_VNN_S410

UNCO

RE_VNN_S411

UNCO

RE_VNN_S412

UNCO

RE_VNN_S413

UNCO

RE_VNN_S414

RE_V1P15_S0IX6

RE_V1P15_S0IX1

RE_V1P15_S0IX2

RE_V1P15_S0IX3

RE_V1P15_S0IX4

RE_V1P15_S0IX5

RE_V1P15_S0IX7

RE_V1P15_S0IX8

RE_V1P15_S0IX9

RE_V1P15_S0IX10

IC

LK_GND_OFF2

LKDDRPCIeSATAUSBFUSE

iC

IC

LK_GND_OFF1

DDR_

V1P05A_G31

DDR_

V1P05A_G34

DDR_

V1P05A_G32

DDR_

V1P05A_G35

DDR_

V1P05A_G36

DDR_

V1P05A_G33

PC

IE_V1P05A_G31

PC

IE_V1P05A_G32

SAT

A_V1P05A_G32

SAT

A_V1P05A_G31

US

B3_V1P05A_G32

US

B3_V1P05A_G31

US

BSSIC_V1P05A_G3

FU

SE3_V1P05A_G5

FU

SE_V1P05A_G3

.05VS5

3.5A=140mils

AA18

AA19

AA21

AA22

AA24

AA25

AC18

AC19

AC21

AC22

AC24

AC25

AD25

AD27

AA30

RS

VD1

V33

AA32

AA33

AA35

AA36

AC32

Y30

Y32

Y33

Y35

V19

V18

AM21

AM33

AM22

AN22

AN32

AM32

V22

V24

U24

U22

V27

U27

V29

N18

U19

1U/10V_4

VCCSRANSOCI_OBS

65mils

10mils

40mils

42mils

32mils

20mils

20mils

9

C9

D

GN

24

C1

1U/10V_4

ICLK_1P05_PWR

03

C1

1U/10V_4

D

GN

1U/10V_4

8

C9

1U/10V_4

FUSE3_1P05_PWR

FUSE_1P05_PWR

01

C1

1U/10V_4

C1

1U/10V_4

C1

BMPD_1P05_PW R

23

51 *0_4

R1

21

C1

1U/10V_4

DDR_1P05_PWR

44

5

C9

1U/10V_4

USBSSIC_1P05_PWR

C7

1U/10V_4

10

C1

1U/10V_4

6

GN

3

C4

1U/10V_4

54

C1

22U/6.3V_6

6

C8

1U/10V_4

D

GN

C1

1U/10V_4

GN

D

1U/10V_4

12

D

1U/10V_4

GN

C9

06

C1

53

C1

22U/6.3V_6

D

4

D

GN

15

C1

1U/10V_4

CORE_1P05_PWR

8

C4

1U/10V_4

60

C4

1U/10V_4

8

C8

22U/6.3V_6

C1

1U/10V_4

07

D

GN

+1

0

C9

22U/6.3V_6

+1

.05VS5

5.4A=216mils

GN

9

C8

22U/6.3V_6

D

total 1.9A=76mils

1 *0_8/S

R8

9 *0_8/S

R4

95 *0_8/S

R1

25 *0_6/S

R4

23 *0_6/S

R1

4 *0_6/S

R9

5 *0_6/S

R9

3 *0_6/S

R9

ICLK_1P05_PWR

CORE_1P05_PWR

DDR_1P05_PWR

USBSSIC_1P05_PWR

BMPD_1P05_PW R

FUSE3_1P05_PWR

FUSE_1P05_PWR

FUSE1_1P05_PWR

8

C7

*1U/10V_4

D

GN

FU

SE1_1P05_PWR [10]

+1

.05VS5

C2

47

8

22U/6.3V_6

C4

49

22U/6.3V_6

+1

.05VS5

C4

48

22U/6.3V_6

CORE_1P05_PWR

C5

2

1U/10V_4

C4

1U/10V_4

2

68

GN

D

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswell 8/11 (Power 1)

Custom Braswell 8/11 (Power 1)

Custom Braswell 8/11 (Power 1)

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

1

93

93

93

1A

1A

1A

of

of

of

5

5

5

GN

GN

D

C3

22U/6.3V_6

D

3

C4

22U/6.3V_6

3

R1

+1

.15VS5

0.7A=28mils

A A

5

4

77 *0_8/S

R1

32 *0_8/S

R5

41 *0_8/S

CORE_V1P15_PWR

DDI_1P15_PWR

FUSE_1P15_PWR

Page 10

5

4

3

2

1

PLACE THE CAPS UNDER THE PKG SHADOW

_MCP_EDS

BSW

T

DDR

9

OF 13

FUSE_1P8_PWR

GPIOCF2_1P8_PWR

USB_1P8_PWR

GPIOCF1_1P8_PWR

+PLLDDR_1P35_PWR

DDI

_VDDQ_G31

DDI

_VDDQ_G32

MI

PI_V1P2A_G32

MI

PI_V1P2A_G31

IC

LK_VSFR_G32

IC

LK_VSFR_G31

CO

RE_VSFR_G35

CO

RE_VSFR_G36

CO

RE_VSFR_G37

CO

RE_VSFR_G34

CO

RE_VSFR_G32

CO

RE_VSFR_G33

CO

RE_VSFR_G31

US

BHSIC_V1P2A_G3

US

B_VDDQ_G32

BRTCFUSE

US

B_VDDQ_G33

US

US

B_VDDQ_G31

US

BSSIC_V1P2A_G3

US

B_V1P8A_G3

US

B_V3P3A_G32

US

B_V3P3A_G31

RT

C_V3P3RTC_G52

RT

C_V3P3RTC_G51

RT

C_V3P3A_G51

RT

C_V3P3A_G52

FU

SE_V1P8A_G3

FU

SE1_V1P05A_G4

FU

SE0_V1P05A_G3

RS

C1

51

*1U/10V_4

GN

D

VD_VSS

RS

RS

GN

VD1

VD2

C1

*1U/10V_4

D

49

V36

Y36

T40

P40

Y27

Y25

P38

V30

AC30

AF35

AD35

AD38

AC36

M41

U35

V35

H44

P41

AA29

C23

B22

C5

B6

D4

E3

U16

H10

G10

A3

K20

M20

USBHSIC_1P24_PWR

USB_1P24_PWR

USB2_1P24_PWR

USBSSIC_1P24_PWR

FUSE_1P8_PWR

FUSE1_1P05_PWR

TP_FUSE_PW R

TP_FUSE_LDO

2 1U/10V_4

C9

7 0_4

C9

02 *1U/10V_4

C1

09 1U/10V_4

C1

1 1U/10V_4

C9

84 1U/10V_4

C4

18 1U/10V_4

C1

63 1U/10V_4

C4

58 1U/10V_4

C4

59 1U/10V_4

C4

85 1U/10V_4

C4

87 1U/10V_4

C4

+3

VS5_PRIME

0.2A=8mils

+3

VS5

0.2A=8mils

+1

.8VS5

+3

VS5_PRIME

0.2A=8mils

+1

.8VS5

+1

.5V

10mils

+1

.8VS5

3

FU

SE1_1P05_PWR [9]

TP

10

TP

17

D

GN

24 *0_6/S

R4

45 *0_6

R4

R4

44 *0_6/S

TWO PAD SHARING

R9

2 *0_6/S

R9

1 *0_6

R4

96 *0_6/S

R4

97 *0_6

GN

GN

GN

GN

GN

GN

GN

GN

GN

GN

39

R4

*10K/F_4

D

D

D

D

D

D

D

D

D

D

DDI_1P24_PWR

DPY_1P24_PWR

ICLK_VSFR_1P24_PWR

PLL_1P24_PW R

PLLCPU_1P24_PW R

USB_1P8_PWR

USB_3P3_PWR

+VRTC_3P3

RTC_3P3A_PWR

FUSE_1P8_PWR

GN

USB_3P3_PWR

CF3_3P3_PWR

SD3 IO SUPPLY

CF1_3P3_PWR

LPC IO SUPPLY

CORE_1P8_PWR

AUDIO IO SUPPLY

0.2A=8mils

0.2A=8mils

D

05

C1

1U/10V_4

0.2A=8mils

USBHSIC_1P24_PWR USB2_1P24_PWR USBSSIC_1P24_PWRUSB_1P24_PW R

Disable HSIC SSIC MIPI power.

+1

.24VS5

0.55A=22mils

FUSE1_1P05_PWR

5

C7

1U/10V_4

D

GN

VSDIO VOLTAGE SETTING (CF3_3P3_PWR)

SDMMC3_PWR_EN_N

0.2A=8mils

0.2A=8mils

10mils

2

1

0

0

AN27

AM25

BE53

BJ49

BH50

BH49

BG51

BJ51

BJ52

AY10

AY44

AV44

AV10

BE51

AV38

AV16

AU36

AU18

AN36

AN35

AN19

AN18

AM36

AM18

AD33

AK18

AF33

AK19

BE1

BJ2

BJ3

BJ5

BH5

BH4

BE3

BG3

E1

E2

G1

AH4

AF4

Y18

R1

94 *0_8/S

R1

98 *0_8/S

4

U26I

DDRS

FR_VDDQ_G_S4

DDR_

VDDQ_G_S42

DDR_

VDDQ_G_S416

DDR_

VDDQ_G_S419

DDR_

VDDQ_G_S426

DDR_

VDDQ_G_S427

DDR_

VDDQ_G_S428

DDR_

VDDQ_G_S429

DDR_

VDDQ_G_S425

DDR_

VDDQ_G_S424

DDR_

VDDQ_G_S423

DDR_

VDDQ_G_S422

DDR_

VDDQ_G_S417

DDR_

VDDQ_G_S421

DDR_

VDDQ_G_S420

DDR_

VDDQ_G_S430

DDR_

VDDQ_G_S431

DDR_

VDDQ_G_S414

DDR_

VDDQ_G_S415

DDR_

VDDQ_G_S413

DDR_

VDDQ_G_S410

DDR_

VDDQ_G_S418

DDR_

VDDQ_G_S412

DDR_

VDDQ_G_S411

DDR_

VDDQ_G_S49

DDR_

VDDQ_G_S48

DDR_

VDDQ_G_S47

DDR_

VDDQ_G_S46

DDR_

VDDQ_G_S45

DDR_

VDDQ_G_S44

DDR_

VDDQ_G_S43

DDR_

VDDQ_G_S41

SD

IO_V3P3A_V1P8A_G31

SD

IO_V3P3A_V1P8A_G32

SD

IO_V3P3A_V1P8A_G33

UNCO

RE_V1P8A_G32

UNCO

RE_V1P8A_G31

GP

IO_V1P8A_G35

GP

IO_V1P8A_G31

GP

IO_V1P8A_G33

GP

IO_V1P8A_G32

GP

IO_V1P8A_G34

*BSW_MCP_ EDS

6 *0_6/S

R9

2 *0_6/S

R8

23 *0_6/S

R4

01 *0_6/S

R5

+CLKDDR_1P35_PWR

43 1U/10V_4

C1

GN

D

50 22U/6.3V_6

GN

D

79

C1

22U/6.3V_6

C1

52 22U/6.3V_6

C1

39 1U/10V_4

C1

C1

22U/6.3V_6

79 1U/10V_4

C4

89 1U/10V_4

C4

9 1U/10V_4

C7

08 1U/10V_4

C1

11 1U/10V_4

C1

7 1U/10V_4

C7

1 1U/10V_4

C7

02 1U/10V_4

C5

01 1U/10V_4

C5

C4

0.1U/16V_4

GN

D

+VRTC_3P3

C4

77

0.1U/16V_4

GN

D

1.9A=76mils

85

+1

.8VS5

0.55A=22mils

78

+1

.35VSUS

1.9A=76mils

+PLLDDR_1P35_PWR

+CLKDDR_1P35_PWR

D D

.35VSUS

+1

87

C1

22U/6.3V_6

D

GN

C C

B B

A A

0.2A=8mils

0.2A=8mils

10mils

+3

VS5_PRIME

+3

VPCU

CF3_3P3_PWR

CF1_3P3_PWR

CORE_1P8_PWR

GPIOCF2_1P8_PWR

GPIOCF1_1P8_PWR

0.2A=8mils

+3

V_RTC

88

C1

22U/6.3V_6

GN

GN

42 *0_6/S

R4

34 *0_6

R4

CAPS PLACE NEAR SOC PIN

R4

37 *0_6/S

5

GN

D

GN

D

GN

D

D

D

RTC_3P3A_PWR

If MIPI, HSIC or SSIC are not used,

the interface supply power pins can be

connected to

ground.

3

C4

0_4

D

GN

0 *0_8/S

R8

50 *0_6

R4

22 *0_6

R4

46 *0_8/S

R4

31 *0_8/S

R4

21 *0_6/S

R4

52 *0_8/S

R1

51 *0_6

R4

53 *0_8/S

R4

55

C9

1U/10V_4

D

GN

ICLK_VSFR_1P24_PWR

USBSSIC_1P24_PWR

USBHSIC_1P24_PWR

USB_1P24_PWR

USB2_1P24_PWR

DDI_1P24_PWR

PLLCPU_1P24_PW R

DPY_1P24_PWR

PLL_1P24_PW R

88

C4

1U/10V_4

SDMMC3_1P8_EN1VSDIO (V)

0

1

0

1

PROJECT : G72D

PROJECT : G72D

PROJECT : G72D

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom Braswell 9/11 (Power 2)

Custom Braswell 9/11 (Power 2)

Custom Braswell 9/11 (Power 2)

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

Date: Sheet

Tuesday, January 24, 2017

10

GN

04

C1

*1U/10V_4

D

GN

C7

*1U/10V_4

D

91

C4

0_4

D

2

D

GN

of

10

of

10

of

10

67

C4

1U/10V_4

D

GN

GN

76

C4

*1U/10V_4

D

GN

0V

0V

3.3V

1.8V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

1

66

C4

*1U/10V_4

35

35

35

1A

1A

1A

Page 11

5

4

3

2

1

11

D D

C C

B B

D

GN

AN29

AN25

AN24

AN16

AN14

AN12

AN11

AM50

AM42

AM4

AM38

AM35

AH44

AM30

AM27

AM16

AK50

AK47

AK45

AK44

AK40

AK38

AK32

AK27

AK25

AM24

AK16

AJ53

AJ51

AJ25

AJ16

AH47

AH42

AH41

AH14

AH13

AH12

AH10

AG25

AF47

AN3

AN1

U25

P10

AD4

AK7

AK4

AJ3

AJ1

AH9

BSW

_MCP_EDS

U26J

Po

wer-VSS

VSS9

8

VSS9

7

VSS9

6

VSS9

5

VSS9

4

VSS9

3

VSS9

2

VSS9

1

VSS9

0

VSS8

9

VSS8

8

VSS8

7

VSS8

6

VSS8

5

VSS6

0

VSS8

4

VSS8

3

VSS1

00

VSS9

9

VSS8

1

VSS3

1

VSS8

0

VSS7

9

VSS7

8

VSS7

7

VSS7

6

VSS7

5

VSS7

4

VSS7

3

VSS7

2

VSS7

1

VSS7

0

VSS8

2

VSS6

9

VSS6

8

VSS6

7

VSS6

6

VSS6

5

VSS6

4

VSS6

3

VSS6

2

VSS6

1

VSS5

9

VSS5

8

VSS5

7

VSS5

6

VSS5

5

VSS5

4

VSS5

3

VSS5

2

*BSW_MCP_ EDS

BSW

21

VSS5

VSS1

VSS1

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS8

VSS8

VSS8

VSS8

VSS8

VSS1

VSS8

VSS1

VSS8

VSS8

VSS8

VSS8

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS7

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS6

VSS5

VSS5

VSS5

VSS5

VSS5

VSS5

30

VSS6

VSS5

_MCP_EDS

U26K

Po

wer-VSS

01

00

9

8

7

6

5

4

3

2

1

0

9

8

7

6

5

03

4

02

3

2

1

0

9

8

7

6

5

4

3

2

1

0

9

8

7

6

5

4

3

2

0

9

8

6

5

4

3

7

11

*BSW_MCP_ EDS

OF 13

VSS6

VSS5

VSS5

VSS5

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS4

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS3

VSS2

VSS2

VSS2